# DRAFT

#### 11/60 MICROPROGRAMMING

SPECIFICATION

(DRAFT D, 11-1-77)

(Please direct comments to Tom Sherman ML3-3/E71, x5300)

The information in this document is subject to change without notice and should not be contrued as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

Copyright (C) 1976, 1977, by DIGITAL Equipment Corp., Maynard, MA.

#### PREFACE

This manual is directed to the experienced assembylanguage programmer and to the hardware engineer with some programming experience.

Although the approach is tutorial, and some introductory information is included, this manual is not intended to teach a higher-level language programmer how to microprogram. A familiarity with the PDP-11, and with machine organization in general, is assumed.

This manual describes the 11/60 as seen from the microprogramming level. The cache, memory management, bus control, and floating point hardware are not described in detail.

A subset of the ISP notation is used in this manual to describe hardware functions. This notation is described in Appendix B. In programming examples, this ISP notation is used as if it were source code. Note that none of these examples will run on MICRO-11 or any other microassembler without the proper field and macro definitions.

Appendix C contains a selective annotated bibliography of recent work on microprogramming.

•

### TABLE OF CONTENTS

| CHAPTER | 1                                                  | INTRODUCTION                                                                                                                                                                    | 1-1                                            |

|---------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

|         | $1.1 \\ 1.1.1 \\ 1.1.2 \\ 1.1.3 \\ 1.1.4 \\ 1.1.5$ | What is Microprogramming?<br>The Datapath of a Computer<br>A Simple Datapath<br>Controlling the Datapath<br>Microprogramming and Machine State<br>Architecture and Organization | 1-1<br>1-3<br>1-4<br>1-5<br>1-8<br>1-10        |

|         | 1.2                                                | The 11/60 Processor                                                                                                                                                             | 1-11                                           |

|         | 1.3                                                | The User Control Store Option                                                                                                                                                   | 1-14                                           |

|         | 1.3.1                                              | The UCS Product                                                                                                                                                                 | 1-14                                           |

|         | 1.3.2                                              | Applications of WCS                                                                                                                                                             | 1-15                                           |

|         | 1.4                                                | User Investment Required                                                                                                                                                        | 1-16                                           |

|         | 1.4.1                                              | Detailed Understanding of 11/60                                                                                                                                                 | 1-17                                           |

|         | 1.4.2                                              | Detailed Analysis                                                                                                                                                               | 1-17                                           |

|         | 1.5                                                | Fundamental Microprogramming Parameters                                                                                                                                         | 1-20                                           |

|         | 1.5.1                                              | The 11/60 Microword                                                                                                                                                             | 1-20                                           |

|         | 1.5.2                                              | The Microcycle                                                                                                                                                                  | 1-24                                           |

|         | 1.5.3                                              | Microprogram Flow                                                                                                                                                               | 1-27                                           |

|         | 1.6                                                | Structure of Manual                                                                                                                                                             | 1-29                                           |

| CHAPTER | 2                                                  | THE 11/60 DATAPATH                                                                                                                                                              | 2-1                                            |

|         | 2.1 2.1.1 2.1.2 2.1.3 2.1.4 2.1.5 2.1.6            | The Heart of the Datapath<br>The ALU Field<br>The B and A Scratchpads<br>The D Register<br>Multiplexers<br>ALU Carry Bits<br>Setting the Condition                              | 2-1<br>2-2<br>2-4<br>2-5<br>2-6<br>2-7<br>2-10 |

|         | 2.2                                                | BUS BIN and BUS AIN                                                                                                                                                             | 2-12                                           |

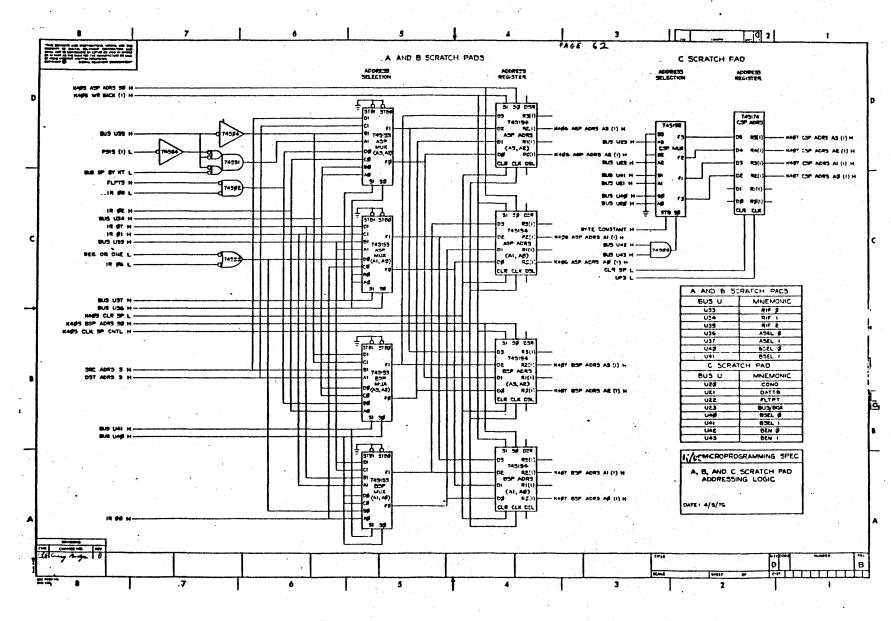

|         | 2.2.1                                              | Organization of ASP and BSP                                                                                                                                                     | 2-14                                           |

|         | 2.2.2                                              | Reading from the Scratchpads                                                                                                                                                    | 2-20                                           |

|         | 2.2.3                                              | Writing Back of ASP and BSP                                                                                                                                                     | 2-23                                           |

|         | 2.3                                                | The C Scratchpad                                                                                                                                                                | 2-26                                           |

|         | 2.3.1                                              | The Base Constants                                                                                                                                                              | 2-26                                           |

|         | 2.3.2                                              | Other Locations in the CSP                                                                                                                                                      | 2-28                                           |

|         | 2.3.3                                              | Writing to the CSP                                                                                                                                                              | 2-29                                           |

|         | 2.4                                                | The XMUX and the Shift Register                                                                                                                                                 | 2-31                                           |

|         | 2.4.1                                              | The Shift Register                                                                                                                                                              | 2-32                                           |

|         | 2.5<br>2.5.1<br>2.5.2<br>2.5.3          |                                                                                                   | 2-33<br>2-38<br>2-38<br>2-38         |

|---------|-----------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------|

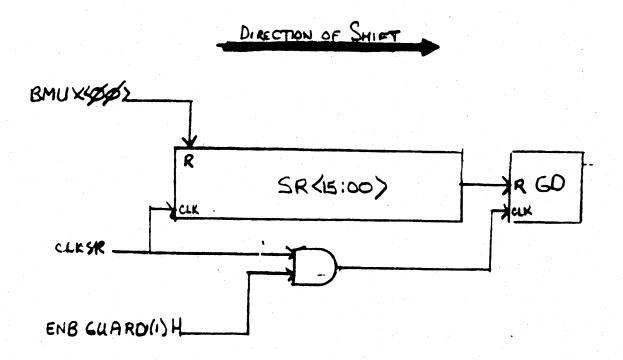

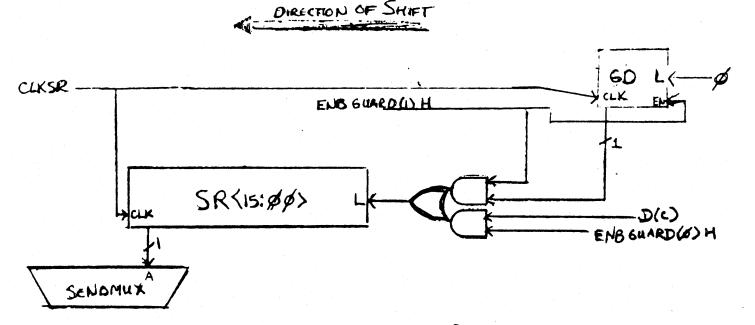

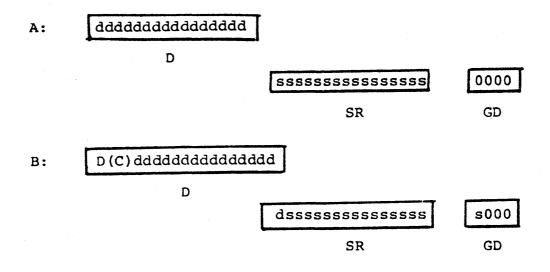

|         |                                         | Shifting with the Shift Register<br>The SR Guard<br>Right Shift<br>Left Shift                     | 2-41<br>2-41<br>2-42<br>2-43         |

|         | 2.7<br>2.7.1<br>2.7.2<br>2.7.3<br>2.7.4 | Shift Examples<br>Multiple-Word Shifts<br>ASL R0<br>ASR RI<br>ASH #-11, R0                        | 2-44<br>2-44<br>2-46<br>2-47<br>2-47 |

|         | 2.7A                                    | The Counter Register                                                                              | 2-48                                 |

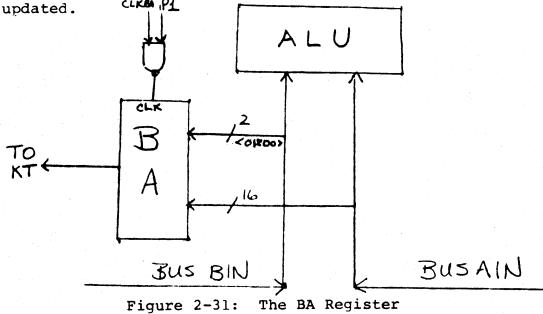

|         | 2.8                                     | The BA Register                                                                                   | 2-48                                 |

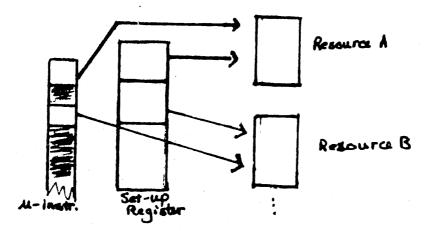

|         | 2.9<br>2.9.1<br>2.9.2                   | The Residual Control Concept<br>Set-up Registers<br>The RES Register                              | 2-50<br>2-50<br>2-51                 |

|         | 2.10                                    | Summary                                                                                           |                                      |

| CHAPTER | 3                                       | MICROINSTRUCTION SEQUENCING                                                                       | 3-1                                  |

|         | 3.1                                     | Chained and Instruction-Counter Sequencing                                                        | 3-1                                  |

|         | 3.2<br>3.2.1<br>3.2.2<br>3.2.3          | Timing<br>Control Timing<br>Intra-cycle Timing<br>Inter-cycle Timing                              | 3-3<br>3-4<br>3-6<br>3-8             |

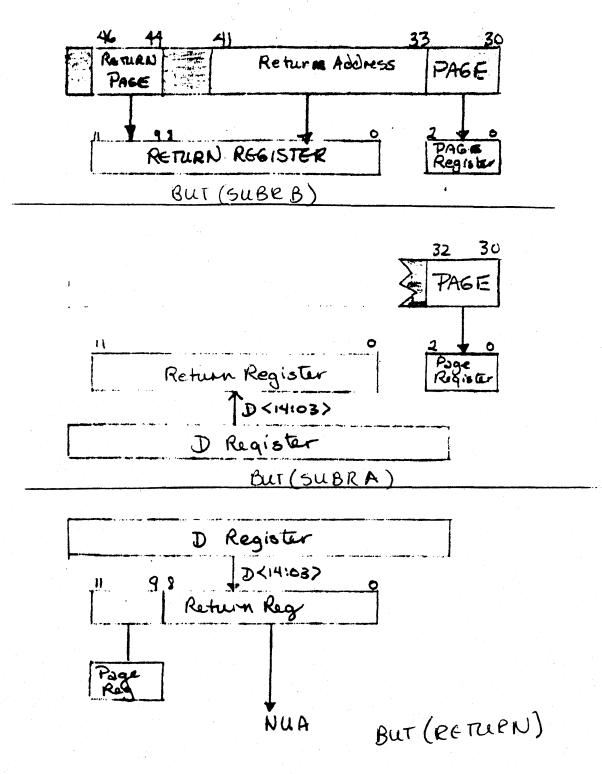

|         | 3.3<br>3.3.1<br>3.3.2<br>3.3.3          | Microcode Branching<br>BUTs<br>Timing Constraints<br>The BUT List                                 | 3-12<br>3-14<br>3-16<br>3-18         |

|         | 3.4                                     | The Case Branch                                                                                   | 3-19                                 |

|         | 3.5<br>3.5.1<br>3.5.2                   | Subroutines<br>BUTs for Subroutines<br>Using Subroutines                                          | 3-23<br>3-27<br>3-27                 |

|         | 3.6                                     | Page Changing                                                                                     | 3-28                                 |

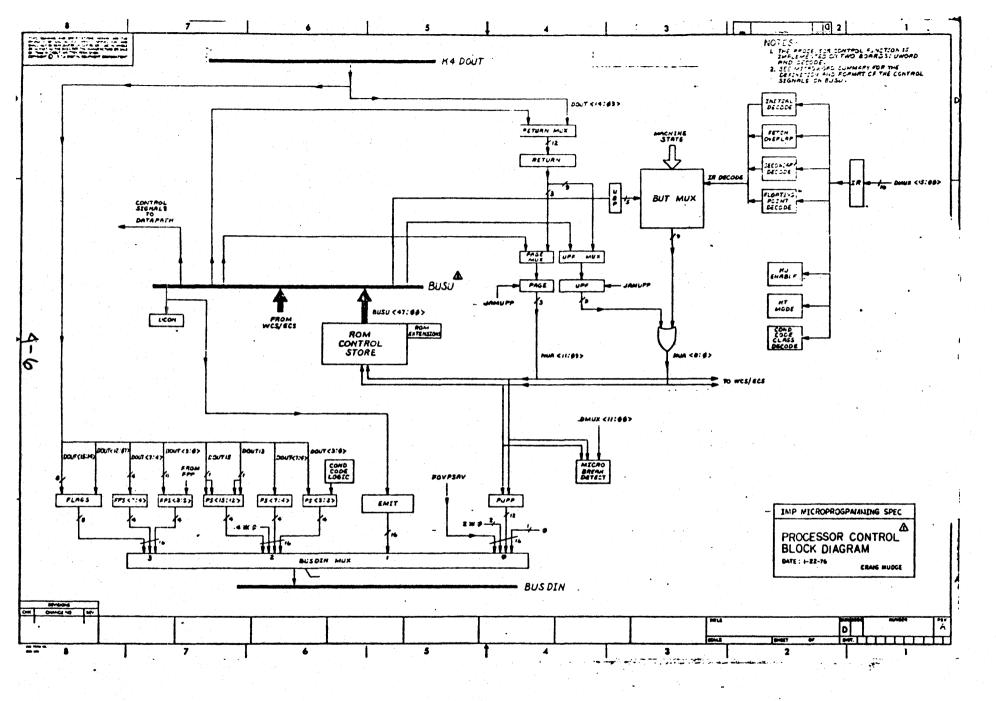

| CHAPTER | 4                                       | THE CENTRAL PROCESSOR                                                                             | 4-1                                  |

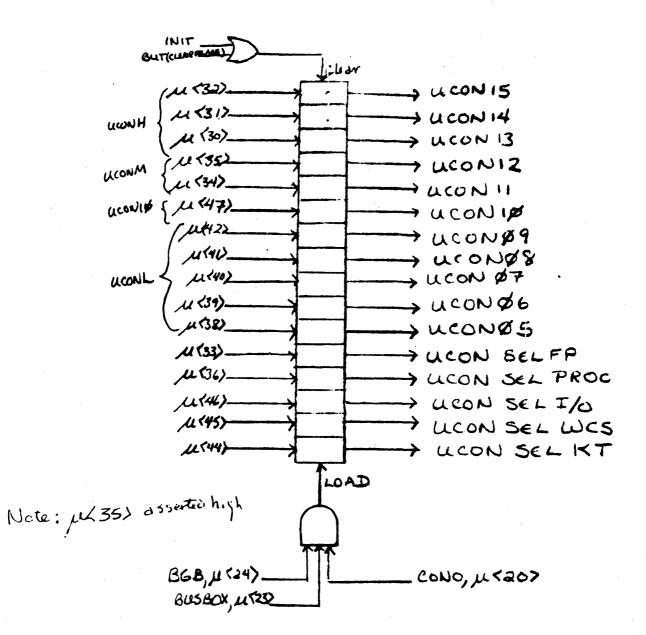

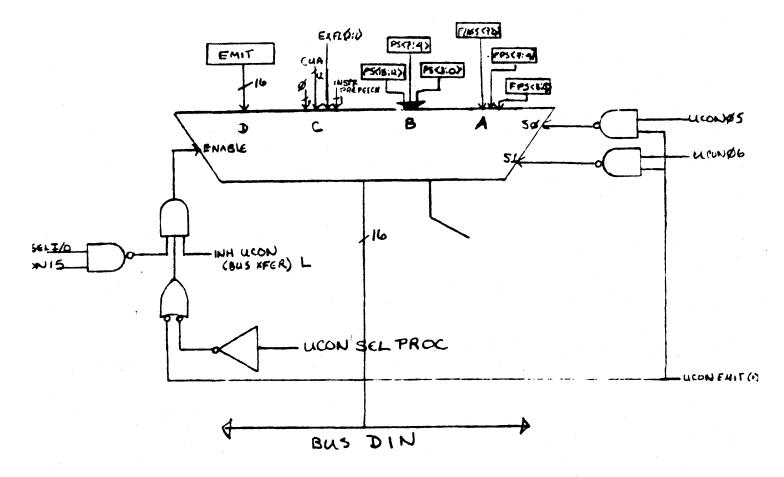

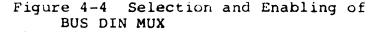

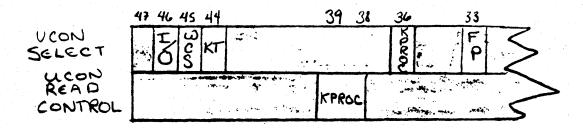

|         | 4.1<br>4.1.1<br>4.1.2<br>4.1.3          | Intra-Processor Communication<br>BUSDIN and DOUT<br>UCON Control Interface<br>UCON Control Fields | 4-1<br>4-1<br>4-2<br>4-4             |

|         | 4.2                                                                                                       | The Inner Machine                                                                                                                                                                                     | 4-5                                                                          |

|---------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

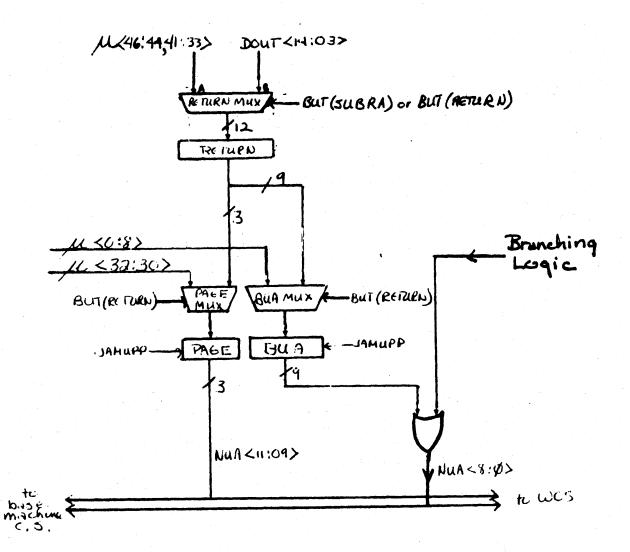

|         | 4.2.1                                                                                                     | Next Micro Address                                                                                                                                                                                    | 4-7                                                                          |

|         | 4.2.3                                                                                                     | Using the ll/60's Literal Facility                                                                                                                                                                    | 4-11                                                                         |

|         | 4.2.4                                                                                                     | Reading the Status Registers                                                                                                                                                                          | 4-13                                                                         |

|         | 4.2.5                                                                                                     | Writing the Status Registers                                                                                                                                                                          | 4-16                                                                         |

|         | 4.3                                                                                                       | Memory Operations                                                                                                                                                                                     | 4-19                                                                         |

|         | 4.3.1                                                                                                     | The Instruction Register                                                                                                                                                                              | 4-19                                                                         |

|         | 4.3.2                                                                                                     | Microword Bus Control Fields                                                                                                                                                                          | 4-20                                                                         |

|         | 4.3.3                                                                                                     | Internal Addresses                                                                                                                                                                                    | 4-23                                                                         |

|         | 4.3.4                                                                                                     | Timing Considerations                                                                                                                                                                                 | 4-26                                                                         |

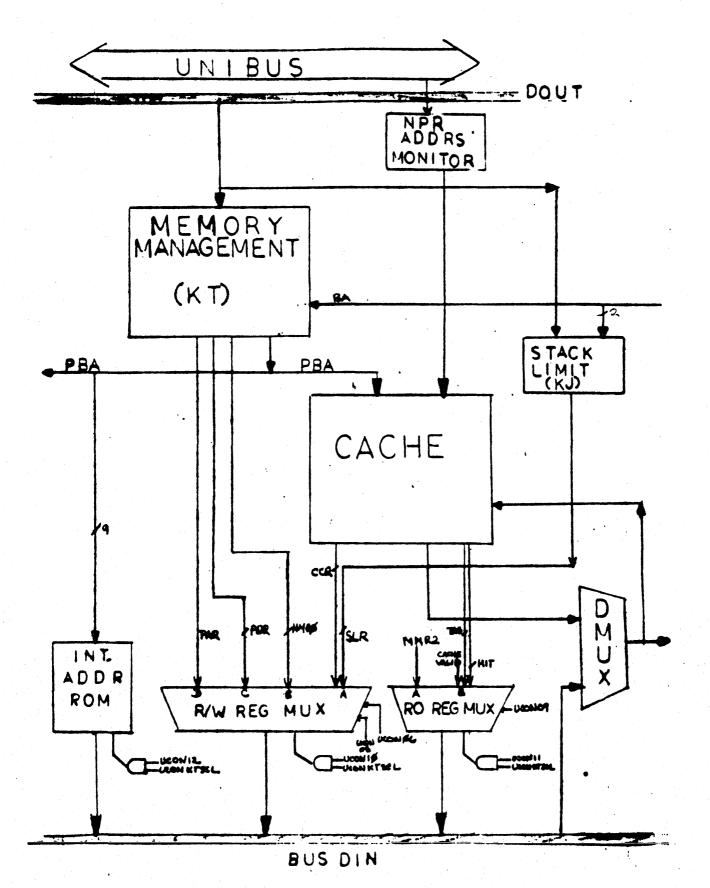

|         | 4.4                                                                                                       | The Cache/KT Section                                                                                                                                                                                  | 4-29                                                                         |

|         | 4.4.1                                                                                                     | The Cache                                                                                                                                                                                             | 4-29                                                                         |

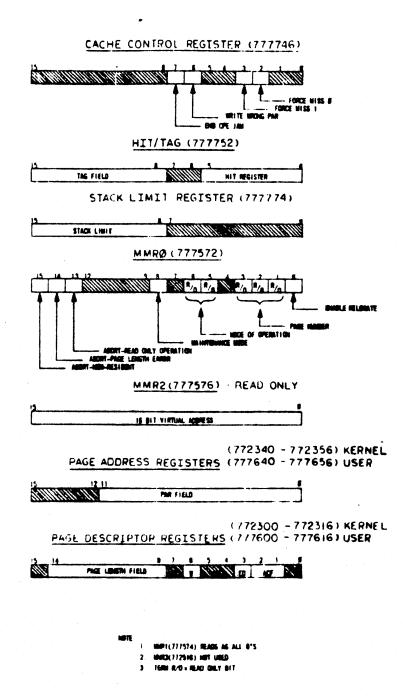

|         | 4.4.2                                                                                                     | Accessing KT/Cache Registers                                                                                                                                                                          | 4-32                                                                         |

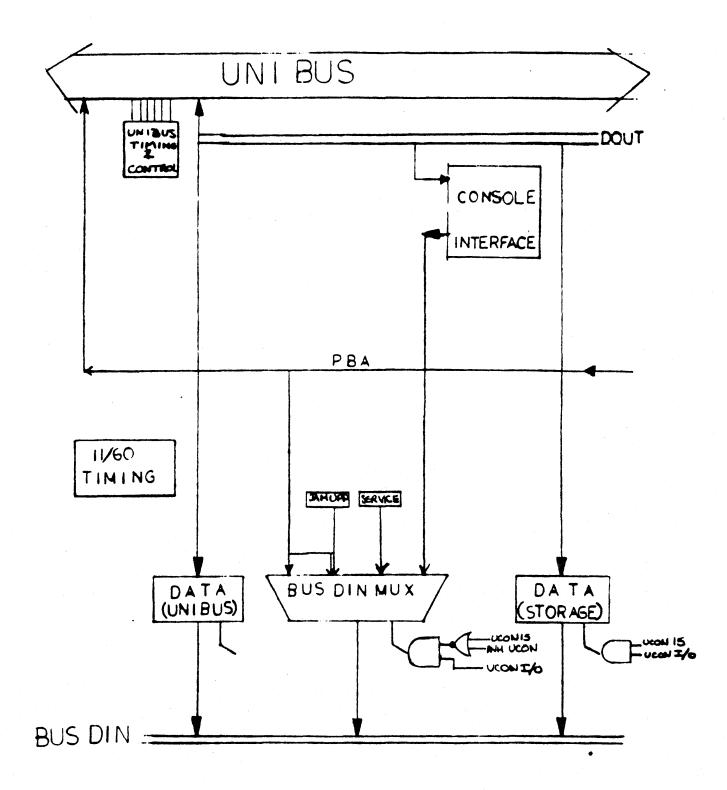

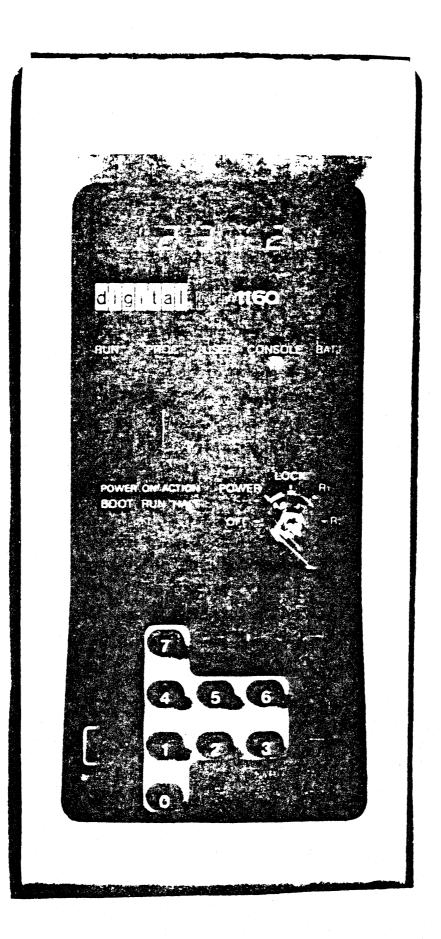

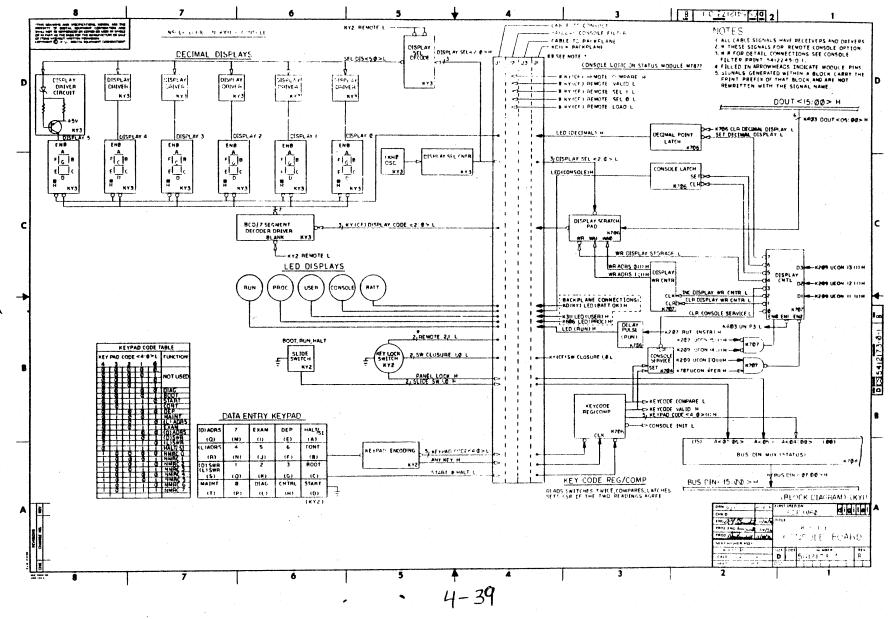

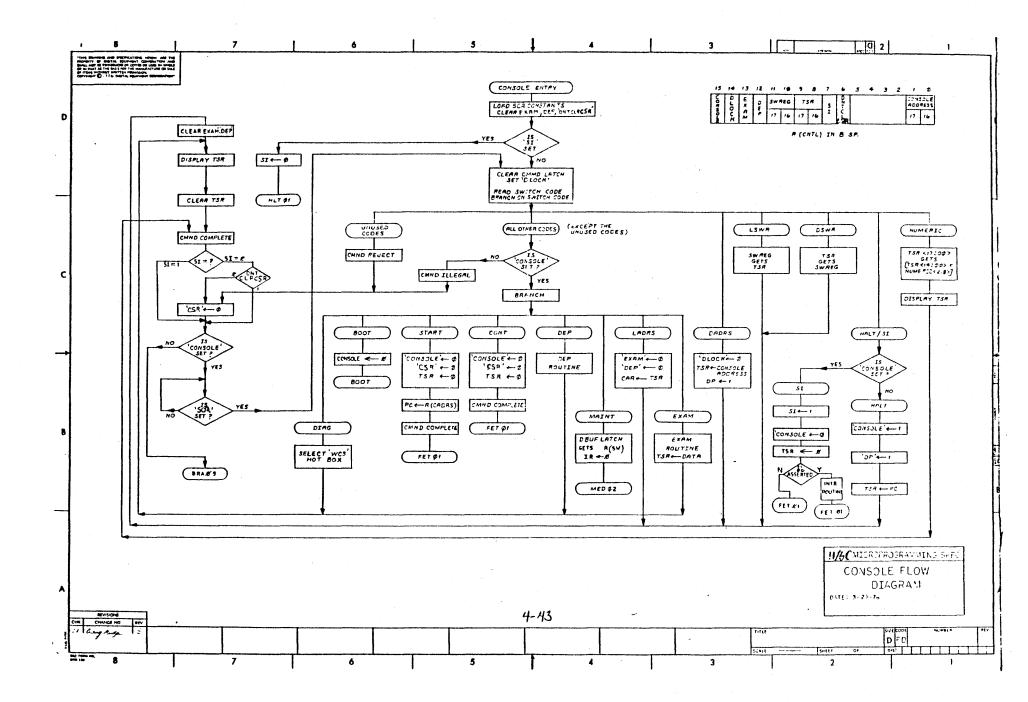

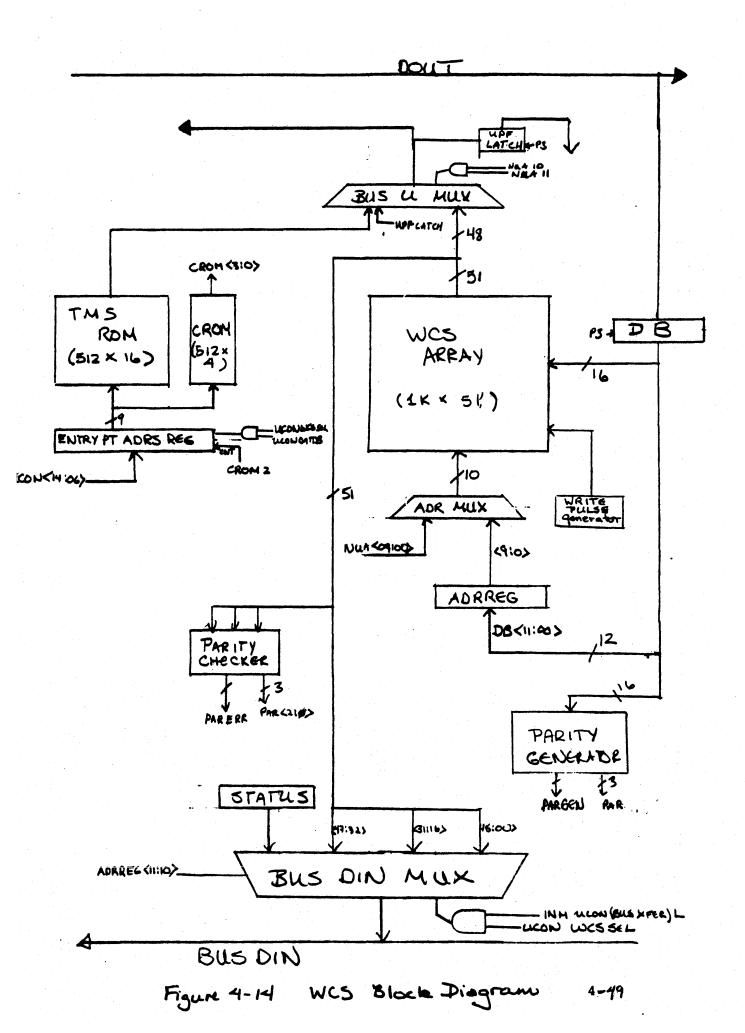

|         | 4.5<br>4.5.1<br>4.5.2<br>4.5.3<br>4.5.4<br>4.5.5<br>4.5.6<br>4.5.7                                        | The Bus Control Section<br>The Console<br>Console Datapath Registers<br>Console Microcode<br>Console Use of UCON<br>Bus Control BUSDIN Mux<br>The DS Register<br>Other Bus Control UCON               | 4-34<br>4-36<br>4-42<br>4-42<br>4-42<br>4-45<br>4-47                         |

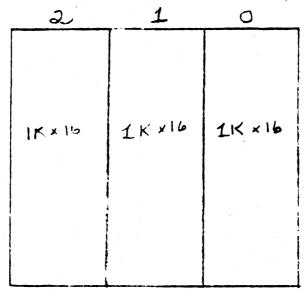

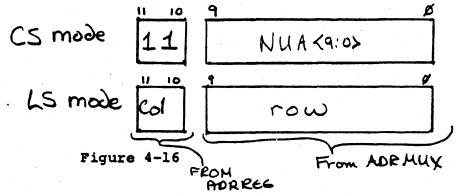

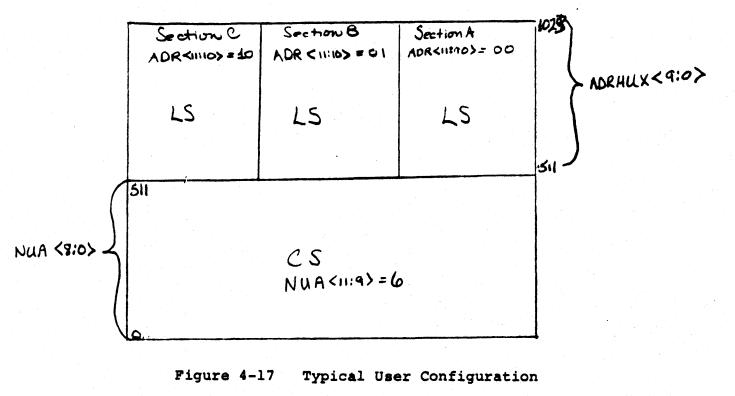

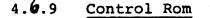

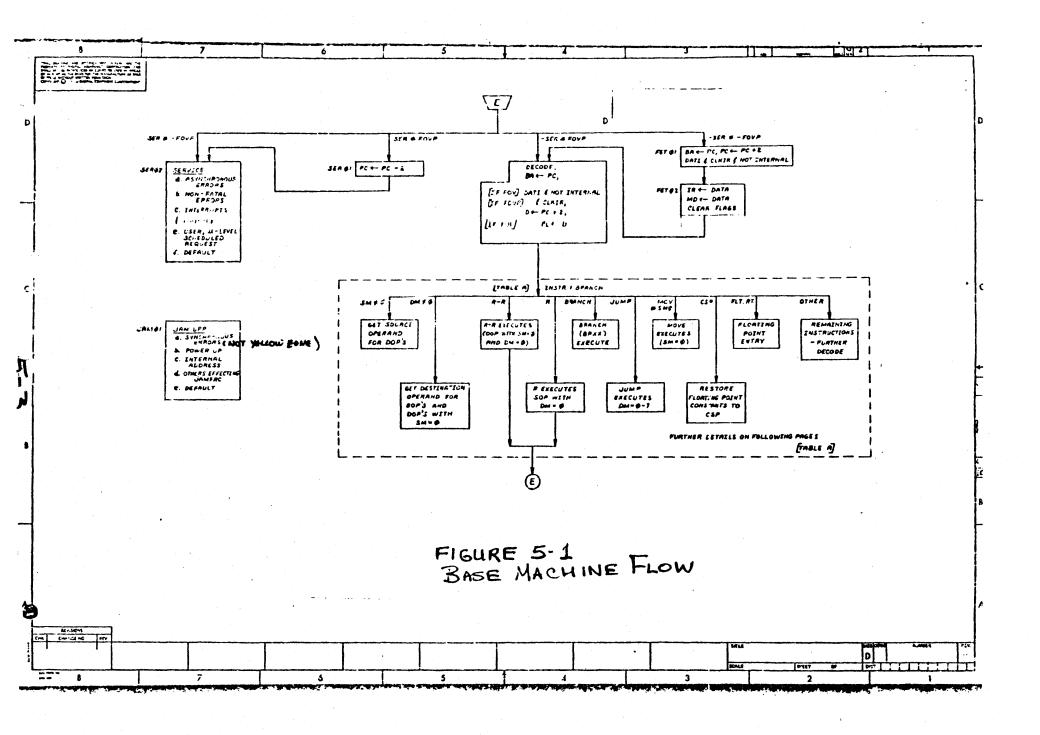

|         | $\begin{array}{r} 4.6\\ 4.6.1\\ 4.6.2\\ 4.6.3\\ 4.6.4\\ 4.6.5\\ 4.6.6\\ 4.6.7\\ 4.6.8\\ 4.6.9\end{array}$ | The WCS Section<br>Addressing Structure of The Array<br>Transfer of Control<br>DB Register<br>Array Address Register<br>Array Address Mux<br>The WCS Array<br>Bus U Mux<br>Bus Din Mux<br>Control ROM | 4-48<br>4-50<br>4-52<br>4-52<br>4-52<br>4-53<br>4-53<br>4-53<br>4-53<br>4-53 |

|         | 4.7                                                                                                       | Using WCS As A Local Store                                                                                                                                                                            | 4-54                                                                         |

|         | 4.8                                                                                                       | UCON Conventions                                                                                                                                                                                      | 4-57                                                                         |

| CHAPTER | 5                                                                                                         | MICROPROGRAM INTERFACES                                                                                                                                                                               | 5-1                                                                          |

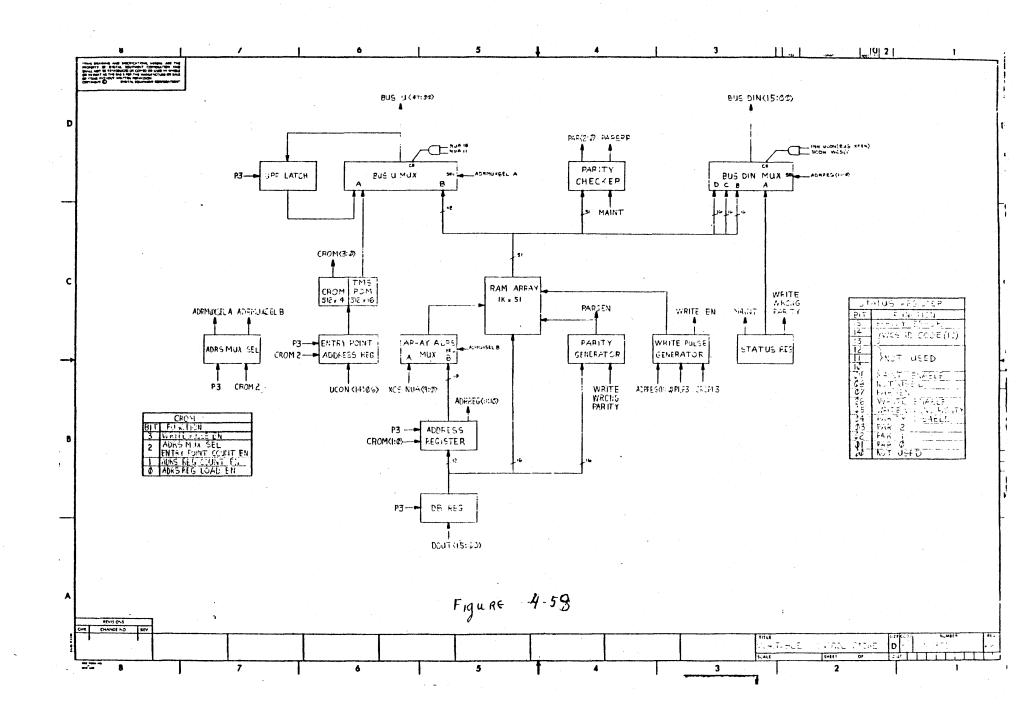

|         | 5.1                                                                                                       | Flow of Base Machine Code                                                                                                                                                                             | 5-2                                                                          |

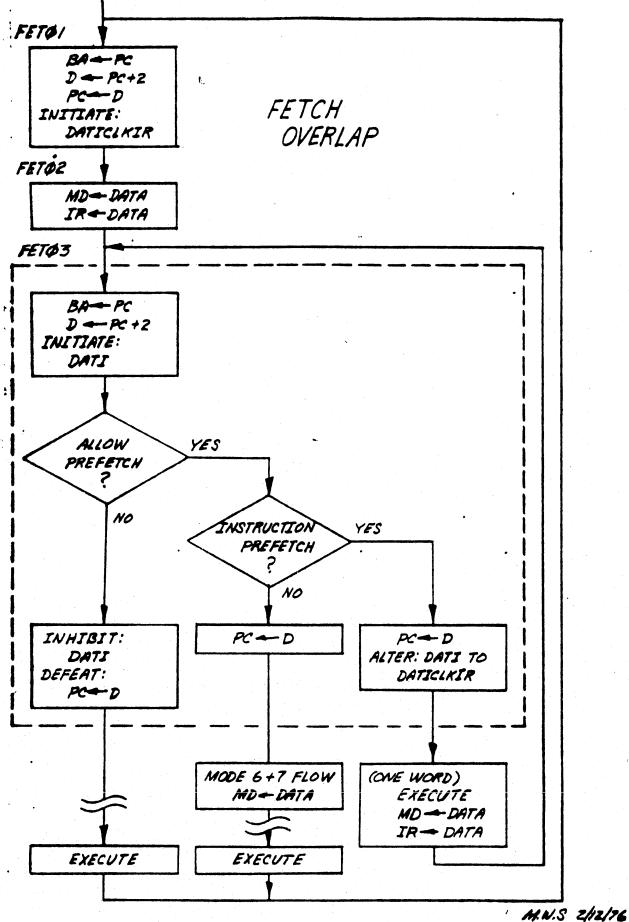

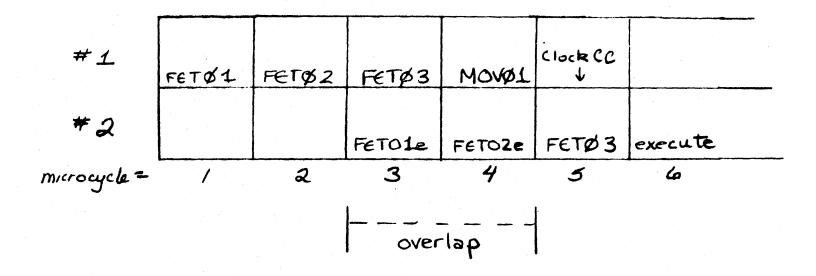

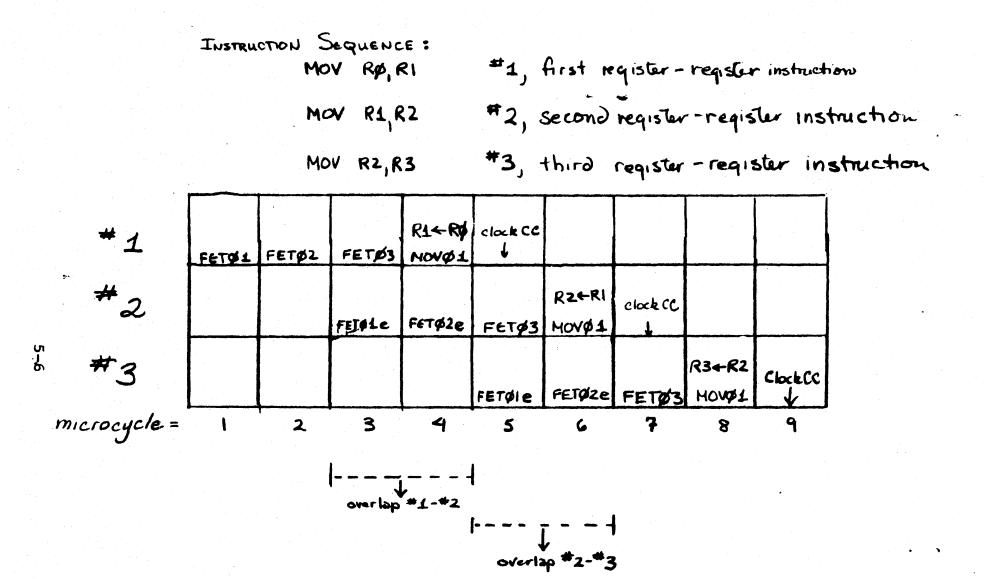

|         | 5.1.1                                                                                                     | Overlapped Fetch                                                                                                                                                                                      | 5-2                                                                          |

|         | 5.1.2                                                                                                     | Instruction Decoding                                                                                                                                                                                  | 5-7                                                                          |

|         | 5.1.3                                                                                                     | Instruction Execution                                                                                                                                                                                 | 5-8                                                                          |

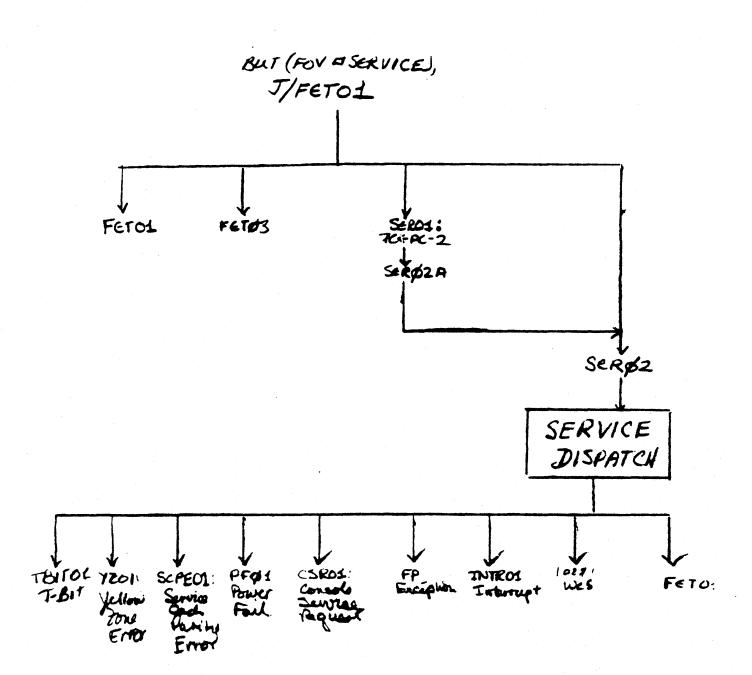

|         | 5.2<br>5.2.1<br>5.2.2                                                                                     | Micro-Level Interrupt Activities<br>Service<br>JAMUPP                                                                                                                                                 | 5-8<br>5-10                                                                  |

|         | 5.4                                                                                                       | Interface Definitions                                                                                                                                                                                 | 5-11                                                                         |

|         | 5.4.1                                                                                                     | Service                                                                                                                                                                                               | 5-11                                                                         |

|         | 5.4.2                                                                                                     | Generating a Trap                                                                                                                                                                                     | 5-13                                                                         |

| -        |                                                           |                                                                                                                                                                                   |                                               |

|----------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| CHAPTER  | 6                                                         | WCS USAGE GUIDELINES                                                                                                                                                              | 6-1                                           |

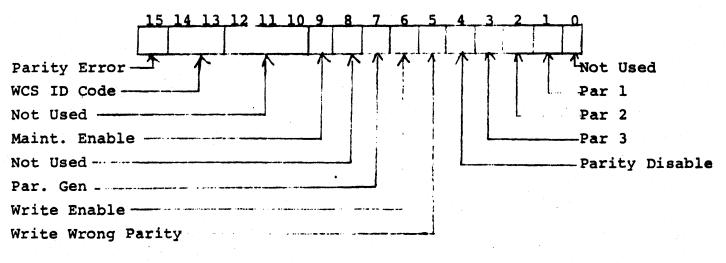

|          | 6.1                                                       | WCS Unibus Addresses                                                                                                                                                              | 6-1                                           |

|          | 6.2                                                       | WCS Entry Points                                                                                                                                                                  | 6-4                                           |

|          | 6.3                                                       | TMS ROM Routines                                                                                                                                                                  | 6-7                                           |

|          | 6.4<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>6.4.5          | Cautions and Warnings<br>Timing Considerations<br>Unibus Usage Conventions<br>Internal Scratched Use<br>PDP-11 Processor State Requirements<br>Complete Decoding of Opcode Groups | 6-10<br>6-10<br>6-11<br>6-11<br>6-11          |

| CHAPTER  | 7                                                         | EXAMPLES                                                                                                                                                                          | 7-1                                           |

|          | 7.1<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.5<br>7.1.6 | Blockmor<br>Instruction Specification<br>Specify Algorithm<br>Specify State<br>First-Pass Coding<br>Try To Condense The Code<br>Check for Interrupt Latency                       | 7-1<br>7-1<br>7-2<br>7-2<br>7-3<br>7-5<br>7-6 |

|          |                                                           |                                                                                                                                                                                   |                                               |

| APPENDIX | K A                                                       | Glossary                                                                                                                                                                          | A-1                                           |

| APPENDIX | ХB                                                        | ISP Notation                                                                                                                                                                      | B-1                                           |

| APPENDIX | X C                                                       | Bibliography                                                                                                                                                                      | C-1                                           |

| APPENDIX | XD                                                        | WCS Resident Section                                                                                                                                                              | D-1                                           |

| APPENDIX | ХE                                                        | TMS ROM Microcode                                                                                                                                                                 | E-1                                           |

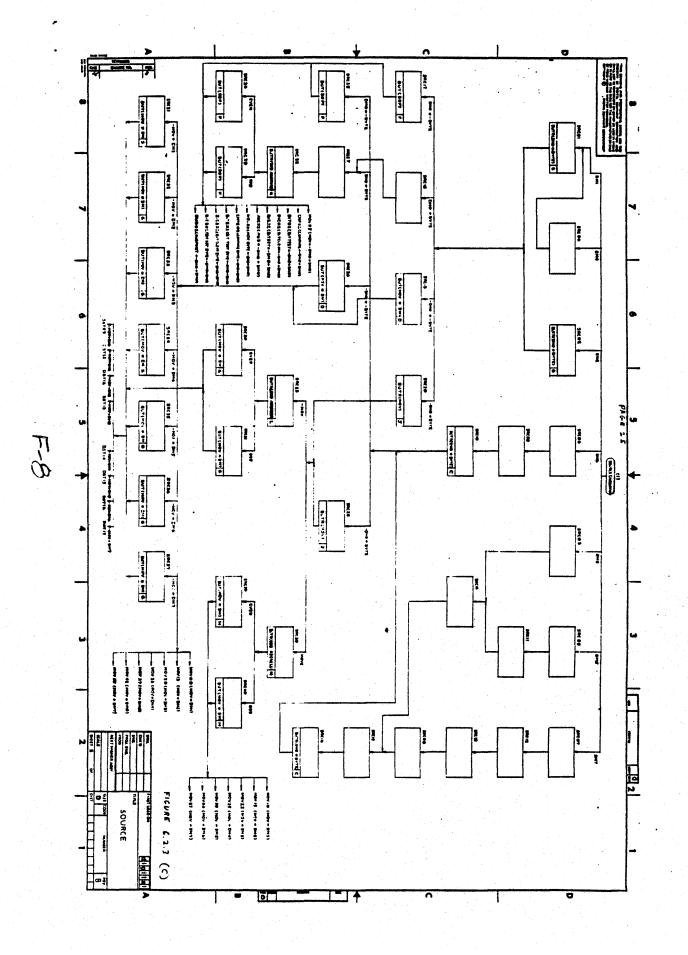

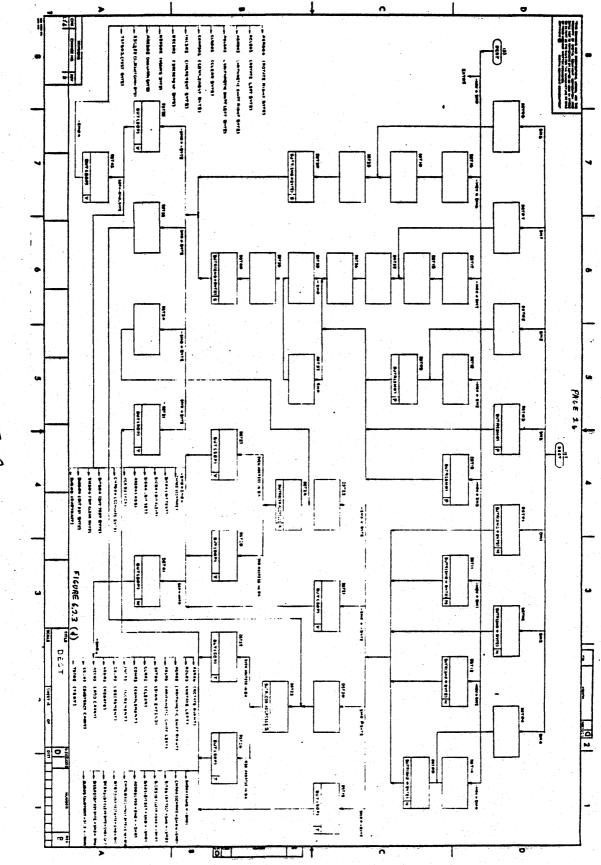

| APPENDIX | XF                                                        | Additional Diagrams                                                                                                                                                               | F-1                                           |

|          |                                                           |                                                                                                                                                                                   |                                               |

# DRAFT

## CHAPTER 1 INTRODUCTION

The 11/60 is a user-microprogrammable PDP-11 central processor. The Writable Control Store option, along with its associated software tools, provides a means by which you can tailor the CPU to your specific needs. The subject of this manual is the hardware environment visible to the microprogrammer.

To provide a secure basis for understanding the detailed information in later chapters, this chapter focuses on three topics:

- 1. What is microprogramming?

- 2. What is a datapath?

- 3. User microprogramming on the 11/60.

A short review of terms and concepts of hardware, architecture, and microprogramming, addressing the first two topics, precedes the discussion of 11/60 microprogramming. The final section of this chapter discusses the structure and scope of this manual.

#### 1.1 WHAT IS MICROPROGRAMMING?

Microprogramming is a method of controlling the functions of a computer. The essential ideas of microprogramming were first outlined by M.V. Wilkes in 1951<sup>1</sup>. Wilkes proposed a structured hardware design technique to replace prevailing <u>ad hoc</u> methods

7 \_ 7

<sup>&</sup>lt;sup>1</sup>Wilkes, M.V., "The Best Way to Design an Automatic Calculating Machine." Manchester Univ. Inaugural Conference, 1951, pp16-21.

of logic design. He observed that a machine-language instruction could be subdivided into a sequence of elementary operations which he called micro-operations. He likened the execution of the individual steps to the execution of the individual instructions in a program. This concept is the basis of all microprogramming.

For many years, microprogramming remained the province of the hardware designer. As new machines, incorporating advances in theory and technology, were designed, software for older, slower machines became obsolete. Microprogramming proved to be an attractive solution to this problem of incompatibility. New machines could be provided with additional read-only memory, or control store, which allowed them to emulate earlier computers. The use of emulation, or the interpretive execution of a foreign instruction set, was later extended to provide upward and downward compatibility among a number of computers in a family.

The IBM System 360 series was a landmark application of microprogramming to achieve compatibility. In this series, there is a common architecture, the 360, which is the target machine. The different models are 360 emulators implemented on different host machines. The performance range of the series is due to the varying characteristics of the different host machines.

Microprogramming as a tool of the user has evolved slowly. Three things had to happen before it became truly feasible. First, technological advances in the field of fast random-access memories was required. The use of read-only memories in a user environment was troublesome and expensive, because correction of programming errors, or bugs, required new memories. Second, user micro-

programming required the spread of previously specialized knowledge. When only those engineers actually involved in the design of microprogrammed computers knew what microprogramming involved, users and educators were at a severe disadvantage. In recent years, microprogramming has found a place in computer science curricula, and has been widely used throughout the electronics industry. The third, and most important prerequisite for user microprogramming is the inclusion of generality and extendability in the design of a computer. A machine designed solely to implement a given instruction set, and with no address space for user control programs, makes alteration an onerous task. A corollary to this point is that software tools must be developed, so that the user does not have to work solely with binary patterns.

#### 1.1.1 THE DATAPATH OF A COMPUTER

The heart of the 11/60 is a three-board microprocessor, whose operational unit is the datapath. A datapath is composed of three types of components:

- Combinational units, such as adders, decoders, or other logical circuits;

- 2. Sequential units, such as registers and counters;

- 3. Connections, such as wires.

The execution of a PDP-11 instruction involves a sequence of transfers from one register in the datapath to another; some of these transfers take place directly, others involve an adder or other logical circuit. Each step in this sequence is controlled by a microinstruction; a set of such microinstructions is known as a microprogram.

Microprograms are held in a control store, a block of high-speed memory which can be accessed once per machine cycle. (A machine cycle is the basic unit of time within a processor.)

The control of the hardware components of the datapath by a microprogram is best explained by a simple example.

#### 1.1.2 A SIMPLE DATAPATH

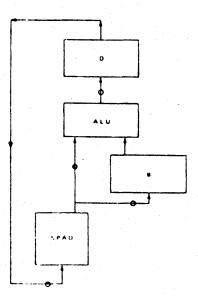

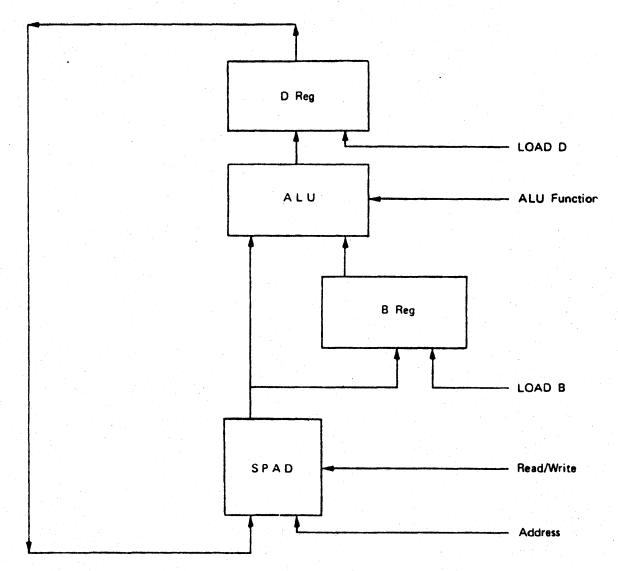

Figure 1-1 shows a simplified datapath. Its only combinational component is an Arithmetic/Logic Unit (ALU), which has two inputs. The ALU result, or output, is stored in D, which is a temporary holding register. The other components of this datapath are B, another holding register; a scratchpad (SPAD), which is a collection of 16 holding registers; and their interconnections. The circles in the diagram indicate gating logic.

Figure 1-1 A Simplified Datapath

The arrows in the figure represent the <u>flow of data</u> within this datapath. Two operands are presented to the ALU inputs; the ALU combines these and presents the result at the input to D. After storage in D, the result can be presented at the input of one of the registers in the scratchpad.

To route the flow of data between the components of this datapath, a set of gates, with corresponding control signals, is required. The set of control signals needed is determined by the topology of the interconnections between the sequential and combinational units of the datapath.

For this datapath, the following control signals are needed.

LOAD D - To store the ALU result in D

ALUF - To select the ALU function

LOAD B - To store data from the scratchpad in B

R/W - To specify reading from or writing to the scratchpad registers

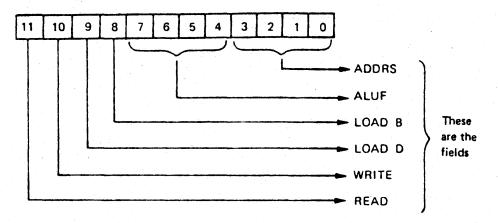

ADDRS - To specify a location in the scratchpad These signals are shown in Figure 1-2.

1.1.3 CONTROLLING THE DATAPATH

Now we can construct a microprogram to control this datapath. To perform a PDP-11 instruction, we must set up an initial constraint: the eight PDP-11 general registers will be stored in the first eight locations of the scratchpad. To perform the PDP-11 operation

ADD R2, R1

the second and third locations in the scratchpad must be added,

and the result stored in the second location R[1]. Symbolically, this is represented as:

$R[1] \leftarrow R[2] + R[1]$

(The back-arrow symbol is read as "gets".)

Figure 1-2 Simplified Datapath With Control Signals

It takes three steps, or machine cycles, to perform this operation with this simple datapath. This avoids conflicting data signals which would produce invalid results. First, R(2) is loaded into B; next, D is loaded with the sum of B and R(1); and lastly, the result is written back to R(1). The following are the basic machine steps:

| CYCLE | 1: | В | 4  | R | 2  |      |   |

|-------|----|---|----|---|----|------|---|

| CYCLE | 2: | D | ¢  | R | IJ | PLUS | B |

| CYCLE | 3: | R | 1] | 4 | D  |      |   |

A time state table can be constructed to indicate which control signals must be asserted in each of these steps, as shown in Figure 1-3. The N/A entries indicate that the assertion of the signal will not afffect the current operation.

|         |     | (      | CONTROL SIGN | IALS |         | ]          |

|---------|-----|--------|--------------|------|---------|------------|

| TIME    | R/W | LOAD D | LOAD B       | ALUF | ADDRESS | ]          |

| CYCLE 1 | R   | N/A    | YES          | N/A  | R[2]    | 1          |

| CYCLE 2 | R   | YES    | NO           | PLUS | R[1]    |            |

| CYCLE 3 | W   | NO     | N/A          | N/A  | R[1]    | ]          |

| Bits:   | 2   | 1      | 1            | 4    | 4 * *   | ע<br>12 נפ |

Figure 1-3 Time State Table

After creating the time state table, we find that twelve bits are needed to provide the control signals for this datapath. The ALU

is allocated four bits to allow for a variety of operations; the scratchpad is assumed to have 16 locations, and the READ/WRITE signal is allocated two bits for a "do nothing" state.

These twelve bits can be combined to form a format for a microinstruction.

This microinstruction format, or microword, is divided into fields. Each field comprises the bits which are used to control a particular signal or function.

Using the time state table and the microinstruction format, we can now write a microprogram to perform the PDP-11 instruction ADD R2, R1:

| CYCLE 1: | 1 | 0 | 0  | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

|----------|---|---|----|---|---|---|---|---|---|---|---|---|

| CYCLE 2: | 1 | 0 | 1. | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| CYCLE 3: | 0 | 1 | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

#### 1.1.4 MICROPROGRAMMING AND MACHINE STATE

The general registers form part of the processor state of a PDP-11. By defining the first eight locations of the scratchpad as the PDP-11 general registers, we have made our simple datapath

implement, in part, a PDP-11.

The <u>processor state</u> of a computer is the set of registers and flags that hold the information left upon the completion of one instruction available for use during the execution of the next instruction.

Programmers working at different levels of a machine see different machine states: an applications programmer may never be concerned with machine state at all. A machine-language, or macro-level programmer knows the PDP-11 processor state to be defined by the contents of  $R \not o$  through R7 and the Processor Status Word. Nearly 100 registers are included in the machine state known to 11/60 microprogrammers. At the nano- or hardware level, even more machine state is seen.

This concept of machine, or processor, state is fundamental to an understanding of microprogrammable processors like the 11/60. State changes at the microprogramming level can affect the macrolevel processor state.

For those readers with some exposure to the theory of finitestate machines, the analogy with a microprogrammed machine may be useful. A computer is made unique, or defined, by the functions it performs and the machine states it enters while performing those functions. Because of this, two machines can be built differently and yet perform identically. A microprogrammed machine changes state as it reads successive locations in the control store, emulating the state changes that would take place in a completely "hard-wired" machine. Additionally, the macro-level state, which

is a subset of the micro-level machine state, changes as if there were no machine but the macro-level machine. A PDP-11 is thus "covered" by an 11/60.

#### 1.1.5 ARCHITECTURE AND ORGANIZATION

To additionally distinguish the macro-level machine from the micro-level machine, it is useful to differentiate between the terms architecture and organization.

<u>Architecture</u>, in this manual, refers to that set of a computer's features that are visible to the programmer. To a PDP-11 machine-language programmer, this includes the general registers, the instruction set, and the Processor Status Word. It was architectural identity that made the members of the IBM System 360 series compatible.

Organization describes a level below architecture, and is concerned with many items that are invisible to the programmer.

The term architecture describes what facilities are provided, while organization is concerned with how those facilities are provided. (Occasionally, another term is included in this hierarchy: realization. This term is used to characterize the components used in a particular machine implementation, such as the type of logic and chips used.)

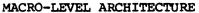

The macro-level organization, transparent to the macro-level programmer, defines the micro-level architecture of the machine. The concept is illustrated graphically in Figure 1-4.

PDP-11 Insturction set, General Registers, etc. Programs reside in main memory MACRO-LEVEL ORGANIZATION = MICRO-LEVEL ARCHITECURE 11/60 registers (#100) and operational capabilites. Programs reside in control store MICRO-LEVEL ORGANIZATION Hard-wired logic

> Figure 1-4 Hierarchical Structure of Memories, Architecture, and Organization

#### 1.2 THE 11/60 PROCESSOR

The 11/60 is a mid-range PDP-11 processor. It is a microprogrammed implementation of the standard PDP-11 architecture. A floating point unit, cache memory, stack limit, and memory management are

integral parts of the processor. With the Writable Control Store (WCS) option, the user can augment the architecture of the PDP-11.

The micro-level architecture of the 11/60 is radically different from the standard PDP-11 architecture, i.e., structure, visible to the macro-level programmer. To successfully microprogram the 11/60, you must familiarize yourself with the details of its micro-level architecture.

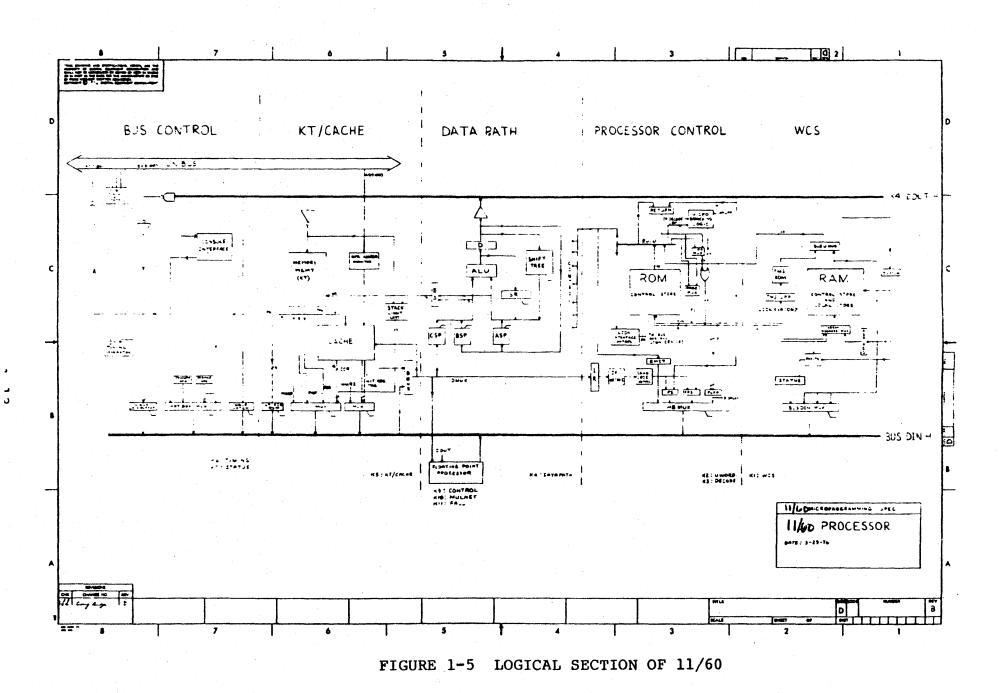

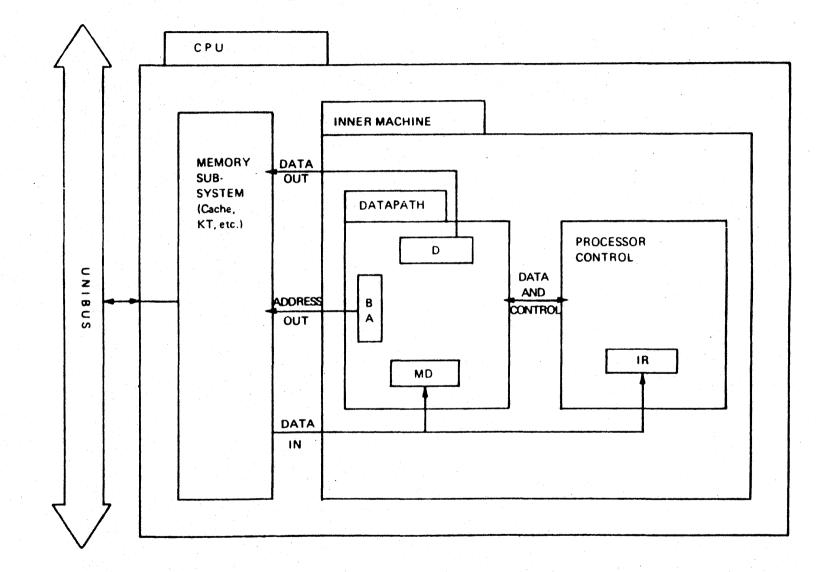

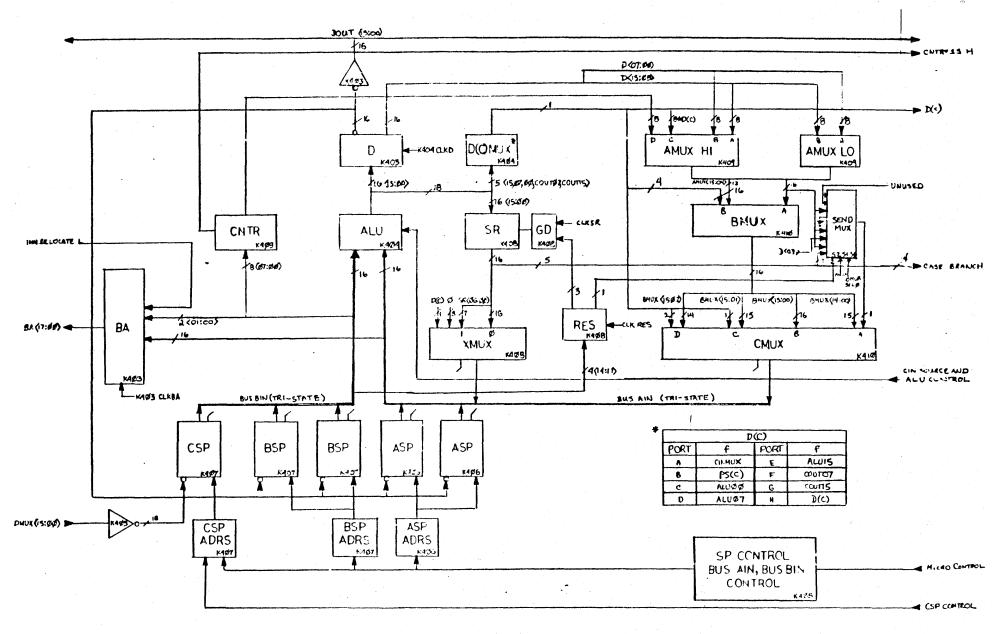

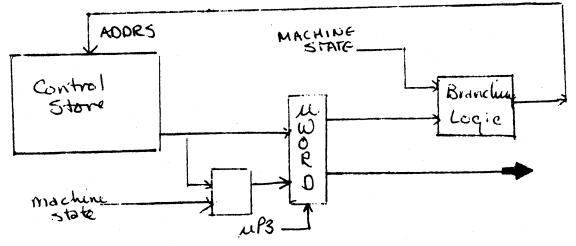

The 11/60 can be divided into five logical sections, as shown in Figure 1-5. The microprogrammer's task is to control the flow of data within each of these five basic sections, and sometimes between them. Of primary importance is the Datapath section, where most data handling functions are performed. The Datapath is described in detail in Chapter 2.

Each section will be discussed in more detail later in this manual; for the moment, it is only necessary to be aware of their general function.

The Bus Control section contains the Unibus control logic, the timing generator, and the console interface.

The KT/Cache section contains the memory management logic (KT); the stack limit register (KJ) and 1024 words of high-speed cache memory.

The Processor Control section contains the control store for the base machine in the form of a read-only memory, or ROM; other

control logic, the Processor Status word (PS) and the Floating Point Status register (FPS).

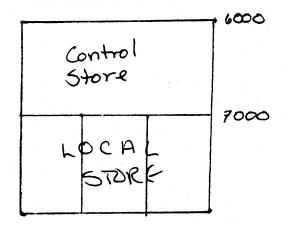

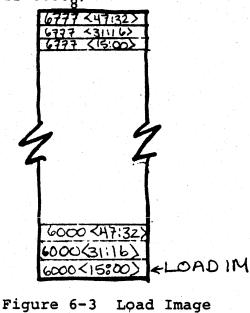

The WCS section contains additional control store for the user microprogrammer in the form of a RAM (Random Access Memory). This RAM can also be used as a high-speed local store with the aid of routines stored in the Transfer Micro store (TMS) ROM.

The main entry into the Writable Control Store is initiated by the XFC.USER opcode, 0767xx. This PDP-11 machine instruction causes control to be transferred to a special location, entitled USERDISPATCH, in the WCS RAM.

#### 1.3 THE USER CONTROL STORE OPTION

The principal use of the 11/60 microprocessor is the implementation of the PDP-11 instruction set. However, the processor has been designed with a dynamic control structure so that other functions can be implemented. The UCS option provides additional and alterable control store for the 11/60, enabling you to extend the capabilities of your PDP-11. Possible applications range from extending the PDP-11 instruction set to emulating a computer with a different instruction set.

#### 1.3.1 THE UCS PRODUCT

The Writable Control Store is a one-board hardware option for the 11/60 central processor, which includes a 1K-by-48 bit Random Access Memory (RAM). This hardware by itself is not the complete product.

To use the WCS hardware, that is, to do microprogram development and debugging, DIGITAL provides the following software tools: A MICRO-ASSEMBLER A LOADER

The software tools for the WCS option are described in the UCS Software Tools Reference Manual.

#### 1.3.2 APPLICATIONS OF WCS

By design, the PDP-11 is a general-purpose computer. Thus there are special-purpose computers which will perform better than will a PDP-11 on those applications for which they have been designed.

WCS enables you to tailor, or bias, the PDP-11 to your particular special-purpose needs. Such tailoring can be classified hierarchically as follows.

Class 0 - Instruction Set Extensions

Some functions were considered too specialpurpose to be included in the original PDP-11 design. These functions, such as block move and decimal arithmetic, can become new PDP-11 instructions. Their definition should conform to 11-instruction format and style.

Class 1 - Application Kernels

Most applications and systems programs have sections which are executed much more frequently than others. A useful rule of thumb is that 10% of the code is executed 90% of the time. Kernels within these critical sections can be microprogrammed for better throughput. Examples include the Fast Fourier Transform, an operating system's memory allocation routine, and Cyclic Redundancy Check calculation.

#### Class 2 - Emulation

The interpretive execution of an instruction set by software is generally called simulation. When this interpretation is done by hardware it is called emulation. Microprogramming provides a means for inexpensively emulating several different instruction sets on one piece of hardware. The tasks involved in emulation include instruction decode, address calculation, operand fetch, and I/O operation as well as instruction execution.

Class 0 applications are relatively simple and straightforward uses of microprogramming. Class 1 applications require more intensive study and possibly statistical analysis if they are to improve performance significantly.

The final class of applications, emulation, is best served by a machine specifically designed as a general purpose emulator. The 11/60 was designed to emulate a PDP-11; hence, the organization of its datapath is keyed to the 16-bit PDP-11 word and other characteristics of a PDP-11 computer system. These factors in large part determine what other computers can be emulated by the 11/60.

#### 1.3.3 EXTENDED CONTROL STORE

To Be Supplied

#### 1.4 USER INVESTMENT REQUIRED

To gain real benefit from use of the UCS option, you should invest time and resources in two areas of study prior to attempting any any WCS microprogramming. These two areas are: 1) understanding the 11/60 and 2) analyzing your proposed application.

1.4.1 DETAILED UNDERSTANDING OF THE 11/60

To microprogram the 11/60 effectively, you must study the internal details of the microprocessor--particularly the datapath. Although this is not a difficult task <u>per se</u>, users with little previous hardware exposure may have some problems in becoming accustomed to the hardware terminology and the notation used for hardware description. Moreover, the largely unprotected nature of the microprogramming environment may seem overly complex and unpredictable.

This manual discusses the 11/60 hardware at the functional level. Occasional references are made to the Engineering Drawings for the 11/60 (order no.): these references are provided only for those users whose curiosity would naturally lead them to the print set. Most users should find that this manual, used in conjunction with the UCS Tools Reference Manual, is all that is required to microprogram the 11/60 UCS effectively.

Appendix B of this manual contains a selective annotated bibliography of recent work on microprogramming and emulation.

1.4.2 DETAILED ANALYSIS OF PROPOSED APPLICATION

Of the three classes of microcode use described in Section 1.3.2., Application Kernels are the most likely "end-user" use of the Writable Control Store. Careful analysis is warranted.

Use of microprogramming will not always result in significant performance gains. Applications well-suited to microprogramming may improve performance by a factor of 5 to 10; poorly suited ones not at all. You must understand your application and analyze the execution of its individual instructions. This section is aimed at helping such analysis, but it is in no way a complete treatment of performance analysis.

A machine-language instruction goes through the following processing phases:

I-phase

Instruction fetched from memory and decoded.

0-phase

Operand addresses calculated; operands fetched from memory.

E-phase

Operation executed upon operands.

Each of these phases takes one or more microcycles. The total execution time, assuming no overlap of the phase, is the sum of these microcycles. Each phase can be seen as a candidate for elimination or for cycle-reduction through microprogramming, with resulting gains in performance.

The following generalizations can be made. COMPOSITE OPERATIONS SAVE I-CYCLES A block move on the PDP-11 can be programmed as:

|       | MOV COUNT, RØ    | ; INSTRUCTION 1 |                               |  |  |  |  |

|-------|------------------|-----------------|-------------------------------|--|--|--|--|

|       | MOV #A, Rl       | ; 2:            | FIRST SOURCE ADDRS TO R1      |  |  |  |  |

|       | MOV #B, R2       | ; 3:            | FIRST DESTINATION ADDRS TO R2 |  |  |  |  |

| LOOP: | MOV (R1)+, (R2)+ | ; 4:            | MOVE AND INCREMENT BOTH ADDRS |  |  |  |  |

|       | SOB RØ, LOOP     | ; 5:            | DECREMENT AND TEST COUNTER    |  |  |  |  |

Combining these operations into one instruction,

BLOCKMOV #A, #B, COUNT

eliminates I-cycles, with the predominant savings coming from instructions four and five.

USING PROCESSOR STORAGE SAVES O-CYCLES

The microprogrammer can use internal CPU storage (the hardware registers) for intermediate results. There are a number of hardware registers, in addition to the general registers  $R \emptyset$ -PC, which can be used by the microprogrammer to avoid memory cycles.

Because there is more parallelism at the micro-level, the inner machine (the microprocessor) is potentially more efficient than the outer machine (the PDP-11). Moreover, the microbranching logic structure of the microprocessor provides a broader decision logic capability which can be exploited, for example, in table search and string-edit operations.

In general, most cycle reductions which result from microprogramming come for the I- and O-phases of instructions.

When analyzing instuctions, you must also consider the ratio of the time used by the I- and O-phases to that of the E-phase:

E

In polynomial evaluation or vector scalar multiplication, for example, the cycles saved by a composite instruction are a small fraction of the overall execution time.

In summary, you should analyze your application to develop candidate sections for microprogramming, then apply detailed analysis to the instruction execution sequence within these sections before coding a microprogram.

1.5 FUNDAMENTAL MICROPROGRAMMING PARAMETERS

This section gives an overview of several topics which represent fundamental parameters of the microprogramming environment.

First, the 11/60 microword is described in general terms. Next, the basis for later discussion of timing is laid by a description of the microcycle. Finally, the central program flow of the base machine is described, and related to the discussion of I-, O-, and E-cycles in Section 1.4.2.

1.5.1 THE 11/60 MICROWORD

This section reviews the general concept of instruction formats as a foundation for describing the format of the 11/60 microword.

Note that an 11/60 microinstruction is exactly equivalent to one word of control store. Thus, the terms <u>microword</u> and <u>micro-</u> <u>instruction</u> are interchangeable. In this manual, however, a slight distinction has been made in the interest of clarity. <u>Microword</u> is used as a generic term for a control store word. <u>Micro-</u> <u>instruction</u> is used when focussing upon the control exerted by a particular microword.

1.5.1.1 INSTRUCTION FORMATS -- An instruction, whether at the macro-level or the micro-level, is the basic mechanism that causes a procedure to be invoked. Instructions usually take two source operands and produce a single result. This kind of instruction has five logical functions:

- 1 and 2) Specify the address (location in storage) of the two source operands

- Specify the address at which the result of the operation is to be stored

- 4) Specify the operation to be performed on the two source operands

- 5) Specify the address of the next instruction in the sequence.

These specifications may be explicit or implicit. Implicit specification saves space in the instruction at the expense of additional instructions in the sequence.

There are four common formats for instructions: three-address, two-address, single-address, and zero-address (stack-type). These categories indicate how many of the address specifications are

explicit in the instruction.

A normal PDP-11 instruction of the form OPR SRC DST uses a twoaddress instruction format. The address of both the source operands are explicitly specified. The result address is implicitly specified by the address of the destination operand. The next instruction to be executed is implicitly identified by the contents of the Program Counter.

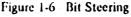

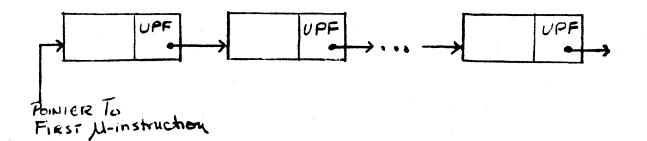

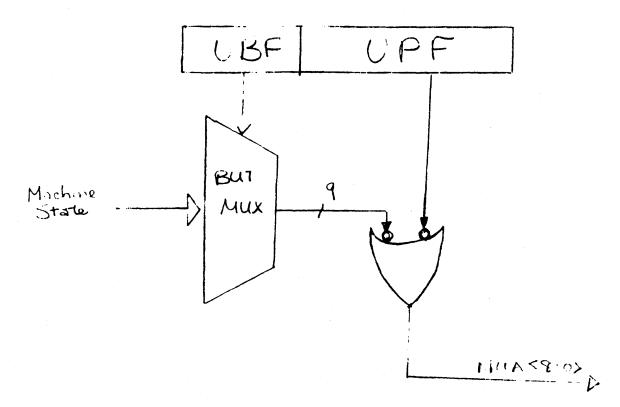

The 11/60 microword, on the other hand, uses a four-address instruction format: two source operand addresses; result address; and next instruction address are all explicitly identified in each instruction. There is no microprogram counter analogous to the PDP-11 PC.

1.5.1.2 SEQUENCING AND BRANCHING -- Because there is no incremental program counter at the microprogramming level in the 11/60, each microinstruction specifies the address of its successor. Therefore, there is no requirement that microinstructions execute sequentially according to their storage address.

Moreover, each microinstruction can also specify a branch condition to be tested before the next microinstruction is fetched. The result of the test can cause a different microinstruction to be fetched.

1.5.1.3 MICROWORD FIELDS -- The 11/60 microword is divided into fields, each of which is associated with a particular functional unit or control function. Not all fields are contiguous, and they

can overlap. That is, a single bit can be used to generate more than one control signal.

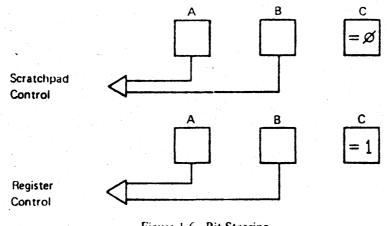

The interpretation of some overlapping fields in the 11/60 microword are controlled by a technique known as bit steering. A few bits in the microword are set aside to specify how the bits in other fields of the microword are to be interpreted.

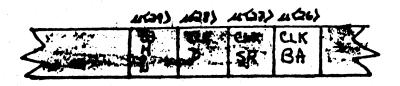

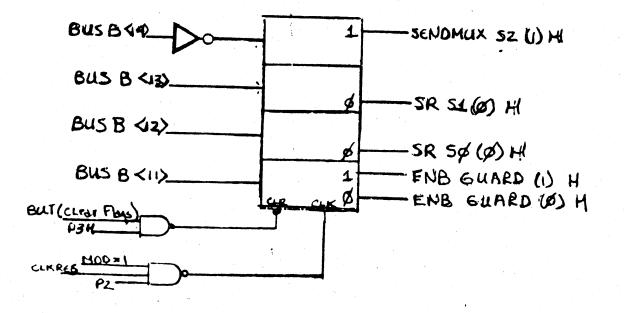

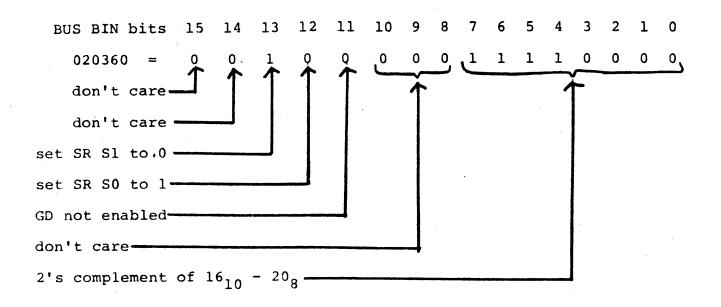

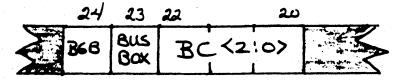

For example, there are two bits in the 11/60 microword that can be used either to control scratchpad writing or to clock registers on the datapath. A third bit is used to specify what the first two bits mean, as illustrated in Figure 1-6.

Other cases where fields overlap are protected from conflicts because the different uses of the same bits are mutually exclusive. For example, the literal field overlaps the ALU function field. A microinstruction which specifies a literal value will generally specify operations to store that data correctly in the datapath. Another microinstruction would manipulate that literal data. 1.5.1.4 WIDTH AND ENCODING OF THE MICROWORD -- The standard width of a control store word on the 11/60 is 48 bits. There are extensions in some sections of the base machine control store which make the microword 56 bits wide. This manual will discuss only the 48 bits available to the UCS user, because the 8 extension bits are highly specific to PDP-11 emulation.

The 11/60 employs what is known as a "horizontal" microword. That means that a majority of the bits in the microword are directly used to generate some signal within the machine. Some of the fields are encoded, meaning that the value represented by the bits in that field must be decoded before control signals are generated.

The term <u>horizontal</u> also implies a significant degree of parallelism within the 11/60 datapath. One microinstruction can, in some circumstances, be much more powerful than one macro-level instruction.

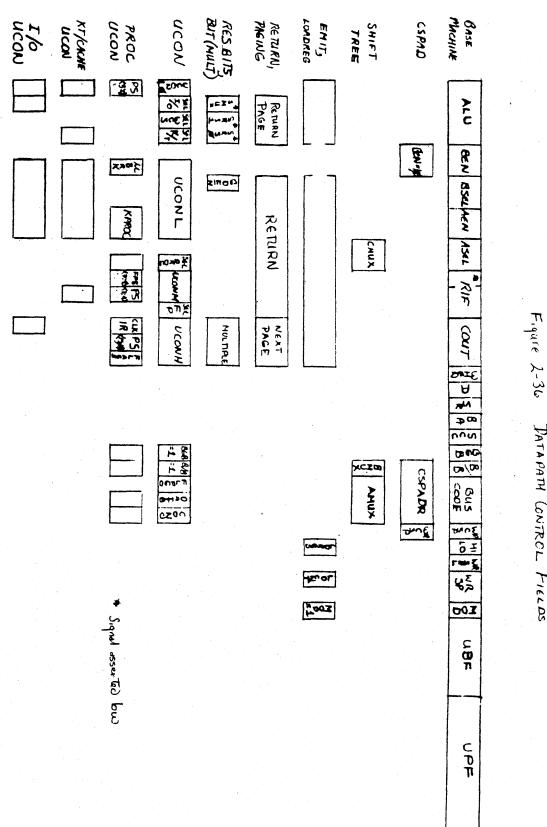

Figure 1-7 is a summary diagram of the 11/60 microword. Most of the notation will not make sense to you now, since each of the fields will not be described in detail until later chapters. It will be useful to refer back to this diagram from time to time to see how the pieces fit together.

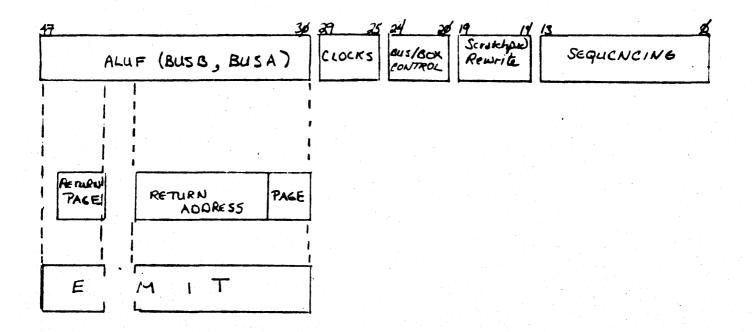

#### 1.5.2 THE MICROCYCLE

Timing is extremely important to the microprogrammer. It imposes constraints on the operations that can be done within one microinstruction, as well as what can be done within a group of microinstructions. An awareness of <u>what happens when</u> will help to avoid trivial, but troublesome, errors.

Figure 1-7 Microword Summary

A new microword is given control of the 11/60 at the beginning of each processor cycle, or microcycle. This microword controls the activity on the datapath throughout that microcycle.

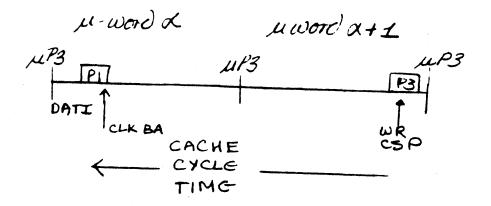

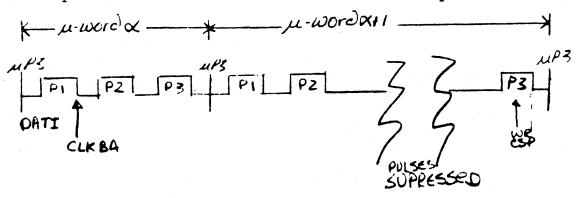

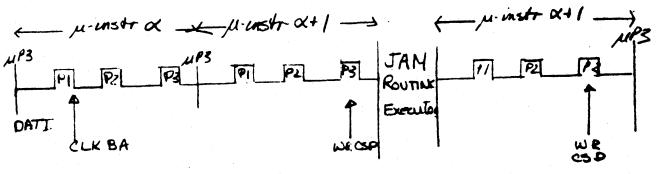

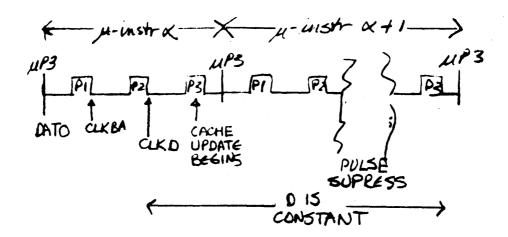

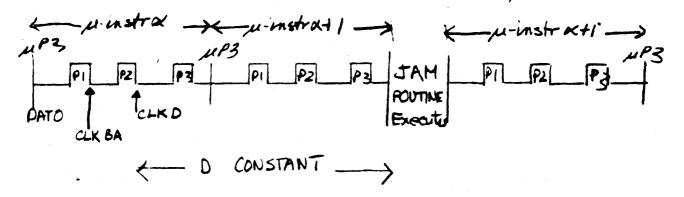

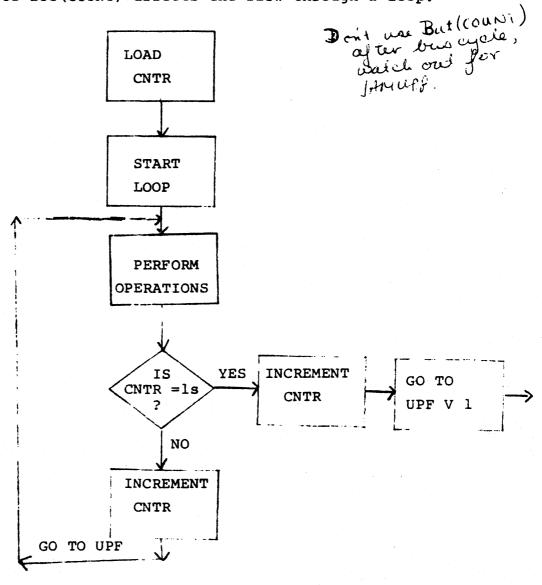

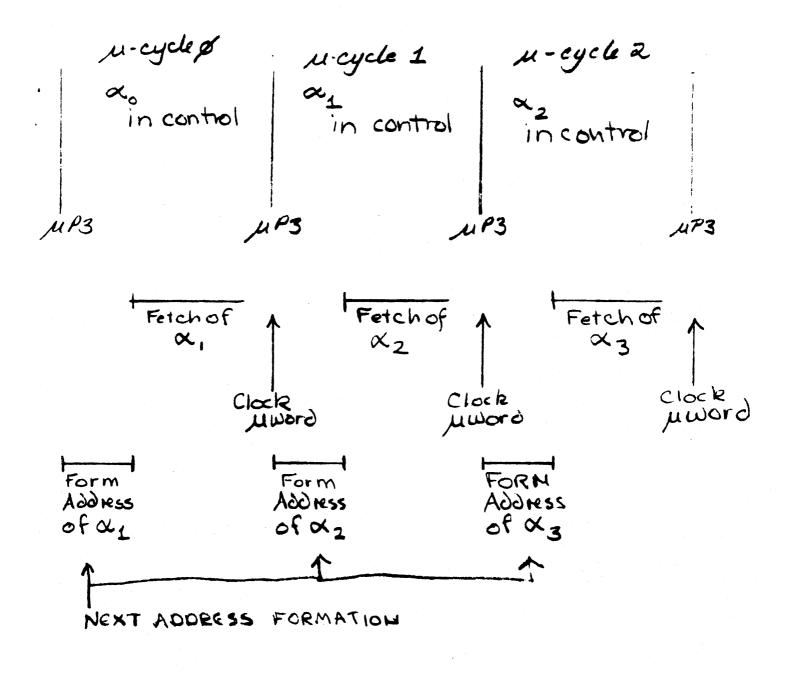

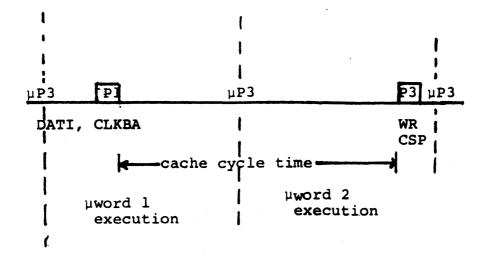

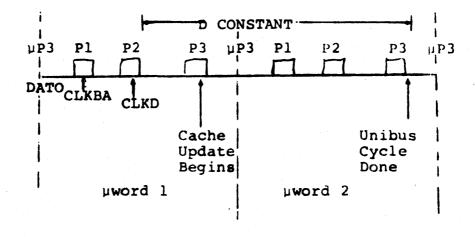

The 11/60 microcycle is 170 nanoseconds long. During this time, there are four clock pulses: Pl, P2, P3, and µP3 (micro-P3). The microcycle is defined as the time period between two consecutive trailing edges of µP3.

The other pulses, Pl, P2, and P3, control the timing of events on the datapath. You will primarily be concerned with the timing of register loading. Inputs to a register must be stable before the register is loaded, or invalid data will be stored.

For example, the result of an ALU operation can be loaded into a storage register at P2.

A microword, and the microcycle during which it is in control of the 11/60, is but one step in the execution of a PDP-11 instruction. Each of the three clock pulses P1, P2, and P3 further divide this step: a number of data transfers can occur during one 11/60 micro-cycle.

Figure 1-8 shows the relationship of the clock pulses to the microcycle.

#### 1.5.3 MICROPROGRAM FLOW

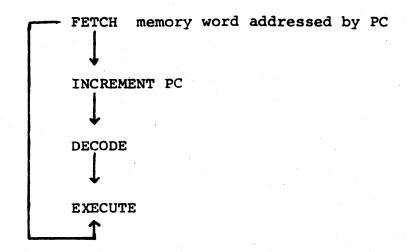

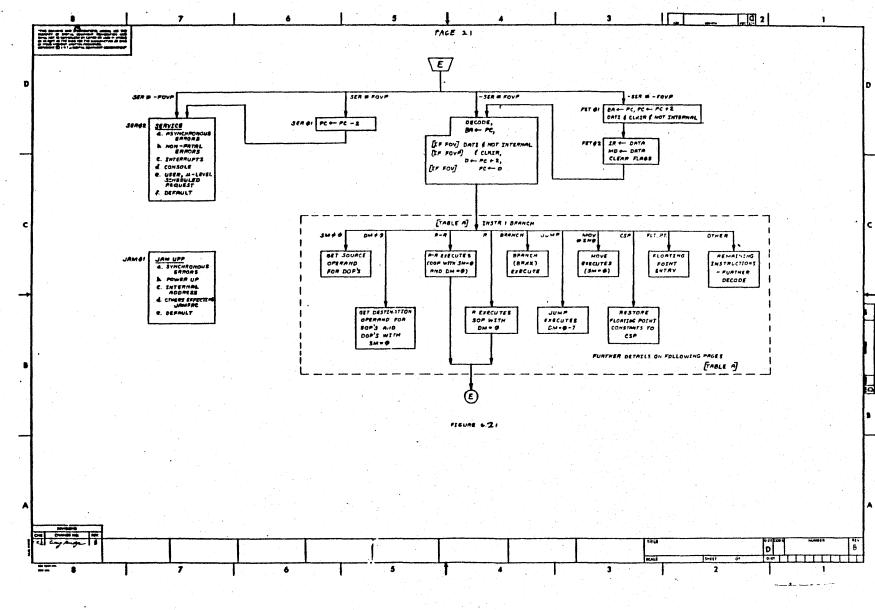

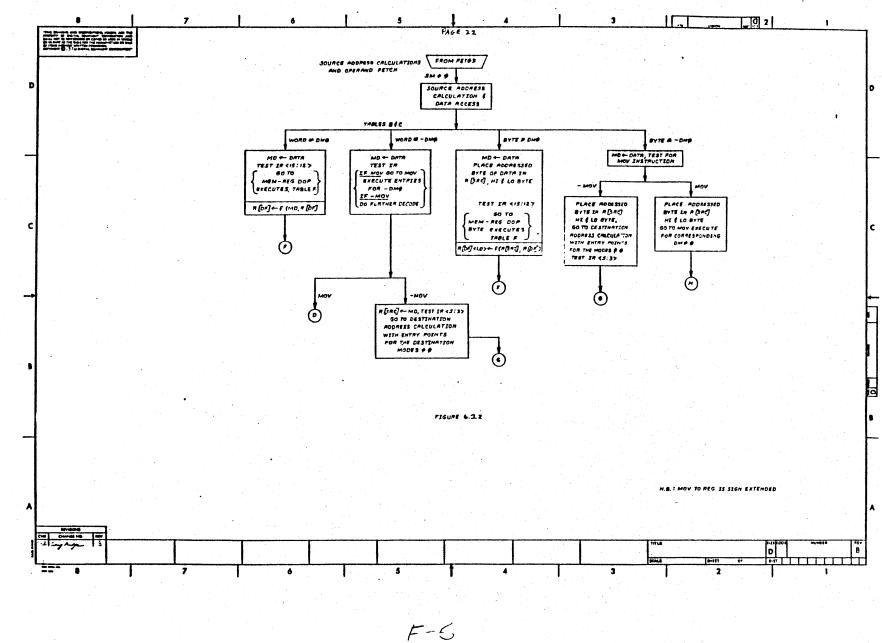

The basic interpretive loop of instruction execution in 11/60 microcode is as follows:

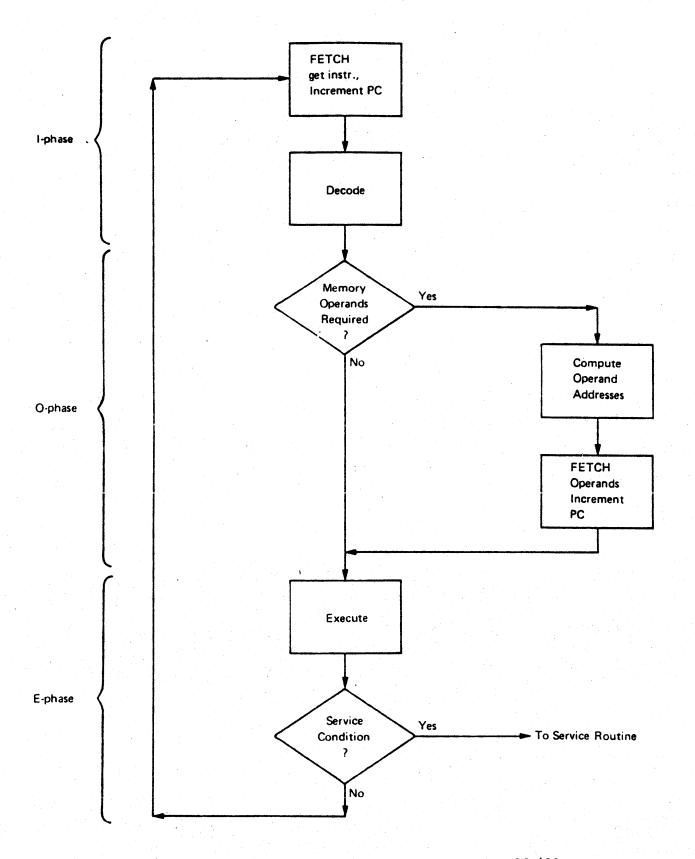

Every microprogram invoked by a PDP-11 opcode follows this pattern. The instruction currently pointed to by the contents of the PC is brought into the processor from main memory and stored in the Instruction Register, or IR. The PC is incremented by two so that it points at the next location to be accessed. The decode step identifies what instruction is to be executed, and dispatches control to the proper section of microcode. After the operation is performed, another instruction is fetched.

A slightly more detailed flow structure is shown in Figure 1-9. Note that at the completion of the instruction execution, a test is made for service conditions. If no service condition, such as an interrupt, exists, the next instruction is fetched. If a service condition does exist, control passes to another micro-

FIGURE 1-9 Program Flow in the 11/60

program which handles the interrupt or other condition. The I-, O-, and E-phases are noted at the left side of the diagram.

1.6 STRUCTURE OF MANUAL PRESENTATION

Two aspects of the  $11/\ell 0$  hardware are of prime concern to the microprogrammer: the data flow and the control flow, or control structure.

There are three distinct kinds of data flow in the ll/60: Data flow within the datapath Data flow within the inner machine Data flow to the rest of the world.

This data flow implies the model of the 11/60 in Figure 1-10. This model provides a different logical structure from that presented in Figure 1-5; this manual uses this new model as a conceptual framework for the discussion of the 11/60 hardware.

The microprogrammer's world is the Inner Machine: the datapath and processor control sections of the processor. There are three interfaces between the Inner Machine and the rest of the computer system: data in, data out, and address out.

This manual focusses on the Inner Machine and the microprogramming techniques for controlling it. Becuase these two major topics are interrelated, and because both must be understood before you can microprogram the 11/60, this manual discusses them in parallel.

The data flow within the 11/60 datapath is described in Chapter 2, with minimal reference to other parts of the model.

Chapter 3 introduces the control structure of the 11/60, and discusses timing considerations. Further details are contained in Chapter 5.

Chapter 4 extends the discussion of data flow to the inner machine, and then to the rest of the CPU.

The material in Chapter 2, 3, and 4 is highly interdependent. One result is the Chapter 2 may seem overly detailed until you have finished reading Chapter 4.

Similarly, the UCS Usage Guidelines and the Examples have been placed at the end of the manual so that they may be discussed in the context of previously presented information.

l'igure 1-10

# DRAFT

### CHAPTER 2 THE 11/60 DATAPATH

The datapath<sup>1</sup> section of the ll/60 routes, manipulates, and stores data within the processor.

This chapter describes the basic functional components of the datapath and the corresponding control fields in the microword. Looking at each component individually provides a secure basis for understanding the relationship of the datapath hardware to the overall problem of microprogramming the 11/60.

At the end.of this chapter is a block diagram of the complete datapath (Figure 2-37). As you read through the chapter, refer to this fold-out diagram to see how the pieces fit together.

#### 2.1 THE HEART OF THE DATAPATH

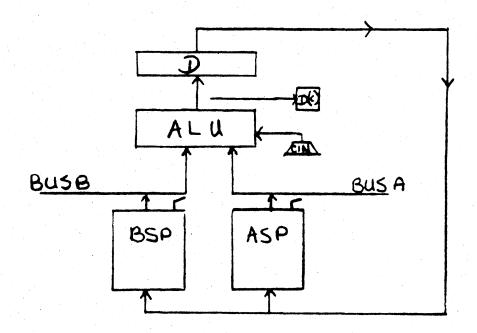

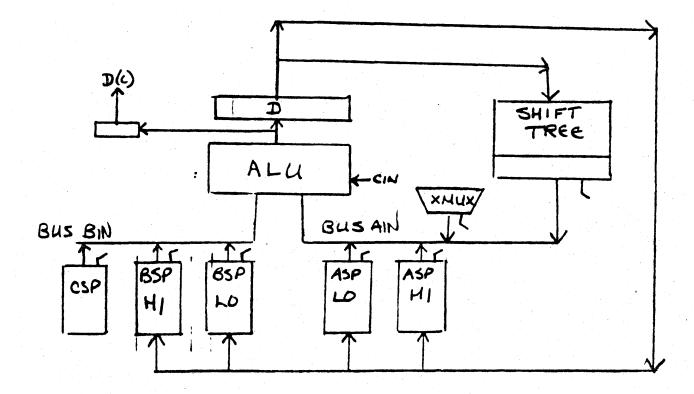

The heart of the 11/60 datapath is the computational loop shown in Figure 2-1.

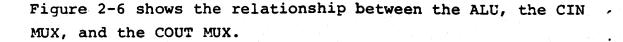

There are two scratchpads (ASP and BSP), each connected to a tri-state bus (BUS AIN and BUS BIN). These buses provide input to the ALU. The other ALU input comes from the CIN multiplexer, which provides the carry-in bit.

D is a 16-bit register which holds the output of the ALU. This data can be directed back to the scrathpads after

1.17874

storage in D. D(C) holds the selected carry-out bit from the ALU operation.

Figure 2-1: The Heart of the Datapath

Control of the data flow among these components is provided by the microword.

#### 2.1.1 The ALU Field of the Microword

The ALU<sup>2</sup> receives two 16-bit words from BUS BIN and BUS AIN, performs an arithmetic or logical operation upon them, and produces a 16-bit result.

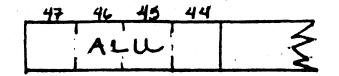

The operation performed by the ALU is determined by the ALU field of the microword. This field occupies bits 47 through 44, which is represented as  $\mu$ <47:44>. Each of the sixteen possible values of this field selects a unique ALU function<sup>3</sup>.

<sup>2</sup>74S181 in semiconductor vendors' catalogs.

<sup>&</sup>lt;sup>3</sup>The function codes shown in a vendor's catalog for the 74S181 are not the same as the codes used in the 11/60  $\mu word$ .

Figure 2-2: ALU Field of the  $\mu \text{word}$

Table 2-1 shows the function invoked by the various values of the ALU field and the corresponding source for the carry-in bit. (The carry-in is described in detail in Section 2.1.5).

:

ALU CONTROL FIELD ENCODING

| OCTAL VALUE | VERBAL DEFINITION                                    | CIN SOURCE |

|-------------|------------------------------------------------------|------------|

| 0           | Complement A                                         | 1          |

| 1           | A plus B plus PS(C)                                  | PS(C)      |

| 2           | (NOT A) and B                                        | PS(C)      |

| 3           | Generate 0                                           | PS(C)      |

| 4           | A plus B plus D(C)                                   | D(C)       |

| 5           | A plus (NOT B) plus D(C)                             | D(C)       |

| 6           | A Exclusive OR B                                     | D(C)       |

| 7           | A AND (NOT B)                                        | D(C)       |

| 10          | Subtract B from A if $D(C) = 1$<br>Add if $D(C) = 0$ | 0          |

| 11          | A plus B                                             | 0          |

| 12          | Select B                                             | 0          |

| 13          | A AND B                                              | 0          |

| 14          | A plus B plus l                                      | 1          |

| 15          | A minus B                                            | 1          |

| 16          | A Inclusive OR B                                     | 1          |

| 17          | Select A                                             | 1          |

Notice that ALU operations such as A plus B plus PS(C) and A plus B plus D(C) serve the same function as PDP-11 instructions like ADC, without requiring a separate micro-instruction for handling the carry.

#### 2.1.2 The B and A Scratchpads

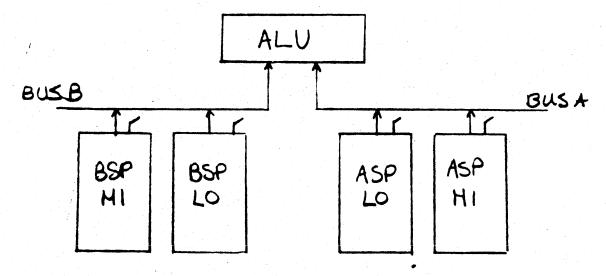

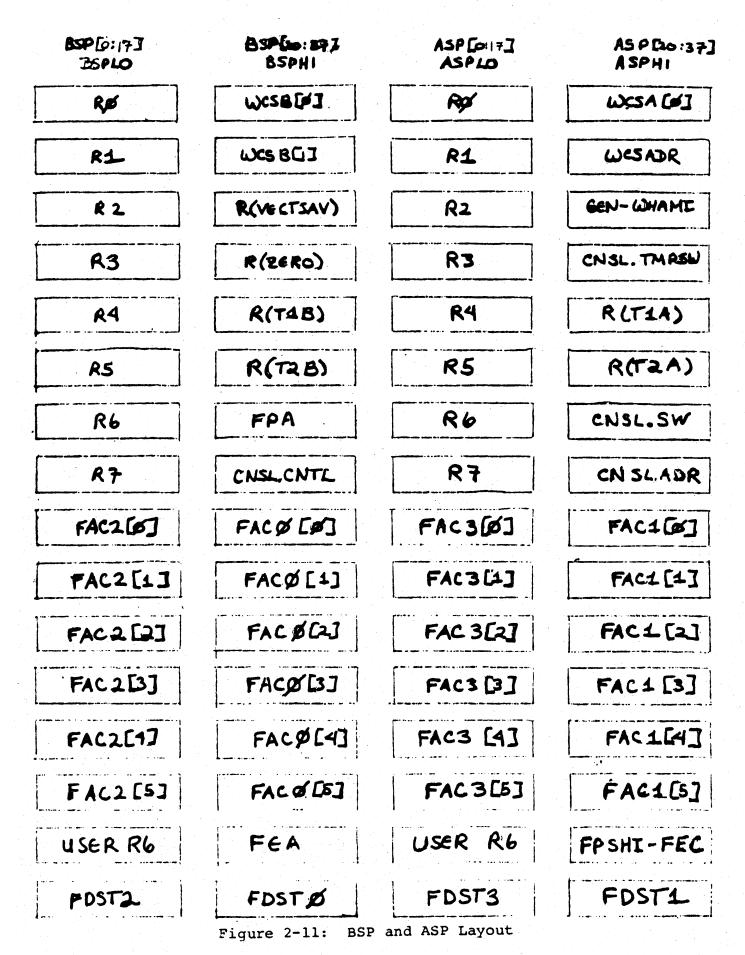

Primary data storage for the datapath is provided by the A and B scratchpads, each of which contains 32 registers.

Each of these scratchpads is divided into two sections of 16 words each; a HI section and a LO section: (refer to Appendix B for an explanation of the notation)

> BSPLO := BSP[0:17]<15:00> BSPHI := BSP[20:37]<15:00> ASPLO := ASP[00:17]<15:00> ASPHI := ASP[20:37]<15:00>

BSPLO and BSPHI have separate outputs onto BUS BIN; similarly, ASPLO and ASPHI have separate outputs onto BUS AIN, as shown in Figure 2-3.

Figure 2-3: BSP and ASP

#### 2.1.3 The D Register

The purpose of the D register is to store the ALU output, either for testing or for routing elsewhere in the datapath or the processor. The ALU result can be clocked into D either at P2 or P3. (When a register is clocked, the data at its input is immediately transferred to its output; the output does not change until the register is clocked again or cleared.)

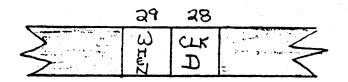

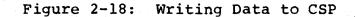

Two fields in the microword, each one bit wide, control the D register. CLKD,  $\mu$ <28>, specifies whether or not D will be loaded in the current microcycle. The time at which D is clocked is determined by the WHEN field,  $\mu$ <29>.

The D register is clocked only if the CLKD field contains a 1. If WHEN contains a 0, clocking occurs at P2; if WHEN contains a 1, clocking occurs at P3.

Figure 2-4: WHEN, CLKD Fields

After an ALU result has been clocked in the D register, it can be directed to a variety of places: other datapath logic; other sections of the processor; main memory; or temporary storage in the scratchpads.

#### 2.1.4 Multiplexers

A multiplexer is a component which has several data input ports and only one output. Selection signals control which input port's data is gated to the output. Data is neither modified no stored when it passes through a multiplexer.

Both the input ports and the selection signals for a multiplexer are numbered. The (control) data at the selection ports forms a binary number which designates one input port.

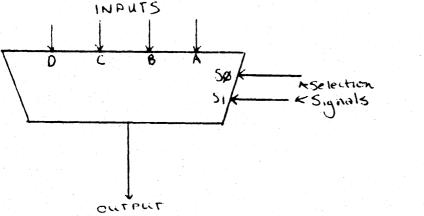

For example, a four-to-one multiplexer, **a.s** shown in Figure 2-5, has two selection signals, S0 and S1. There are four input ports, A, B, C, and D; where A is the low-order, or 0, port.

TRUTH TABLE

Poir Selected

Α

B

C.

D

SØ

Ø

1

Ø

1

51

Ø

Ø

1

Figure 2-5: Four-to-One Multiplexer

If S0 and S1 are both 0, then the data at port A is transferred to the output of the multiplexer. If S1 is 1, and S0 is 0, then the C port is selected. The truth table in Figure 2-5 illustrates this correspondence.

#### 2.1.5 ALU Carry Bits, CIN and D(C)

Section 2.1.1 described ALU function control and mentioned the carry-in bit, CIN. This section examines both the carryin and carry-out bits of the ALU and their relationship to each other. Both CIN and the carry-out bit D(C) are selected by multiplexers. The multiplexer which selects the CIN bit has four inputs: 0, 1, PS(C) (the C-bit of the PSW), and D(C), the last carry-out. Selection of this multiplexer is controlled by the ALU function code.

After an ALU operation is complete, the 16-bit result can be clocked into the D register. If the D register is clocked, D(C) is clocked at the same time. The bit which becomes D(C)may be the actual carry, or overflow bit of the ALU; hence the term carry-out is used. However, the overflow is not the only source for D(C).

It is best to consider D(C) as a state bit retained from an ALU operation - sort of an internal condition code. It has a number of different functions. As the carry output of the ALU, D(C) can be fed back into another ALU operation through CIN, thur providing a facility analogous to the PDP-11 operations ADC and SBC. D(C) is also used to load the C-bit of the Processor Status Word, and is also used as a test condition for microcode branching.

The source for D(C) is chosen by the COUT MUX. Unlike the multiplexer for CIN, the COUT MUX is controlled directly from the microword. Indirectly, this does affect CIN selection when the ALU function of the next microword uses D(C) as the CIN source. In these cases, the selection for the COUT MUX in one instruction will determine the source for the CIN bit in the next microinstruction.

Figure 2-6: CIN, COUT of ALU

#### 2.1.5.1 Selection of D(C) Source

COUT07 and COUT15 are, respectively, the byte and word carries from the ALU operation. This carry bit can then be clocked into the Processor Status word, PS, or fed back into a subsequent ALU operation. For example, during a 32-bit add, the carry-out bit from the addition of the low-order words becomes the carry-in bit for the addition of the high-order words. COUTØ7 and COUT15 are undefined when a logical operation is performed. ALU15 is bit 15 of the ALU result, the sign bit. Testing for a negative result and some shifting operations would select this source for D(C).

ALUg7 is bit 7 of the ALU result, which is the sign bit of a byte quantity.

ALU $\emptyset$  is the  $\emptyset$  bit of the ALU, which indicates an odd or even result.

CIN is the output of the CIN MUX, the same carry-in bit presented to the ALU. This allows you to select a 1 or a 0 for D(C) directly, depending on the ALU code.

PS(C) is the C bit of the Processor Status word; the base machine uses it as the D(C) source for those PDP-11 instructions in which the C bit of the PSW does not change.

D(C) is the D(C) bit generated by the previous CLK D specification. This allows you to save, or recycle, a D(C) value from the last time an ALU result was clocked into D.

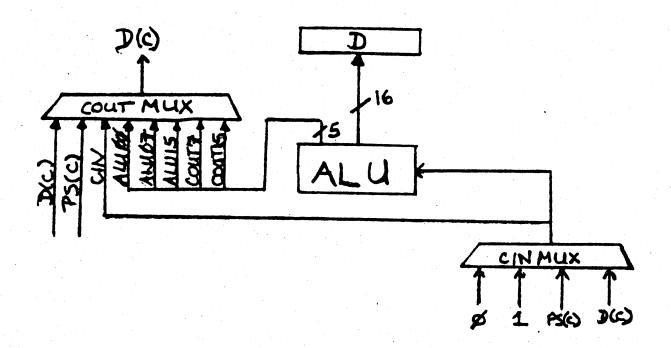

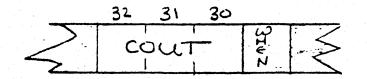

2.1.5.2 Control of COUT MUX -- The COUT MUX is controlled by the COUT field of the microword,  $\mu$ <32:30>.

Figure 2-7: COUT Field of Microword

The encoding of the COUT field of the microword is shown in Table 2-2.

Note that, regardless of COUT, D(C) is not changed unless CLK D = 1; D(C) is clocked at the time specified by the WHEN field.

|      | Table | 2-2      |

|------|-------|----------|

| COUT | FIELD | Encoding |

| D(C) SOURCE                       | MNEMONIC | COUT FIELD VALUE |

|-----------------------------------|----------|------------------|

| Output of CIN MUX                 | CIN      | 0                |

| C bit of the PSW                  | PS (C)   | 1                |

| Bit 0 of ALU result               | ALUØØ    | 2                |

| Bit 7 of ALU result               | ALUØ7    | 3                |

| Bit 15 of ALU result              | ALU15    | 4                |

| Byte Carry                        | COUT7    | 5                |

| Word Carry                        | COUT15   | 6                |

| Carry-out from previous operation | D(C)     | 7                |

#### 2.1.6 Setting the Condition Codes

The condition codes, N, Z, V, and C of the Processor Status Word, are macro-level state indicators whose values are defined for every PDP-11 instruction. Their purpose is not to record the status of the micro-level machine after every microcycle, and hence these bits are clocked only when specifically indicated by the microprogrammer.

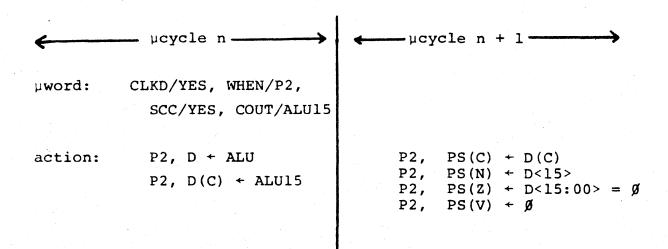

There are two ways to set the condition codes; only one of them will be discussed here. A second, more general method is described in Chapter 4. The Set Condition Codes (SCC) field,  $\mu < 25 >$ , controls the loading of the PDP-11 condition codes. When SCC contains a one, the condition codes are altered during the <u>next</u> micro-cycle. D and D(C) must be clocked at P2 for the condition codes to be set correctly. This timing relationship is illustrated in Figure 2-8.

Figure 2-8: Condition Code Clocking

If the IR contains an XFC or other reserved opcode, then the PDP-11 condition codes are clocked as follows. The C bit of the PSW is loaded with D(C). (From the previous discussion of D(C), you can see that there are actually eight sources for the PS(C).) The N and Z bits reflect the status of the D register at P2 of the microinstruction in which SCC was set. The V bit is loaded with 0.

D and D(C) must remain stable through P2 of the microcycle following the SCC/YES specification.

Whether or not you, as a WCS user, set the contition codes during a microcycle depends on the requirements, or expectations, of the macro-level program. For example, if your macro-level program needs to branch upon conditions resulting from an XFC instruction, you would clock the condition codes.

#### 2.2 BUS BIN AND BUS AIN

The buses that provide operand input to the ALU are tristate buses; that is, they connect a number of tri-state devices. The use of tri-state logic in the 11/60 allows a multiplexing function to be performed without actually using a multiplexer, with resulting hardware savings. The symbol  $\int$  denotes a tri-state device.

A number of sources on either side of the ALU can be selectively enabled onto BUS BIN or BUS AIN. Figure 2-9 shows the relationship of the ALU input sources to the portion of the datapath previously discussed.

On the B-side of the ALU, there are three sources: the two sections of the BSP, and another 16-location scratchpad, the CSP. On the A-side, there are four locations: ASPLO, ASPHI, the XMUX, and the Shift Tree. Each of these components will be described in detail in succeeding sections.

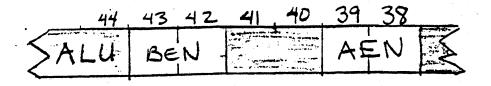

The BEN field of the microword,  $\mu$ <43:42>, controls which source is enabled onto BUS BIN; the AEN field,  $\mu$ <39:38>, determines which source is enabled onto BUS AIN. Table 2-3 defines the encoding of these fields. Two BEN codes are dedicated to the CSP because there are two methods of providing addresses to this scratchpad.

Figure 2-9: BEN, AEN Fields of Microword

# Figure 2-10: BUS BIN and BUS AIN Sources

|     | Tal    | ole 2-3 | 3        |  |

|-----|--------|---------|----------|--|

| Bus | Enable | Field   | Encoding |  |

| BUS B                    |          | BUS A        |                   |          |              |

|--------------------------|----------|--------------|-------------------|----------|--------------|

| SOURCE<br>ENABLED        | MNEMONIC | BEN<br>VALUE | SOURCE<br>ENABLED | MNEMONIC | AEN<br>VALUE |

| BSP[0:17]                | BSPLO    | 0            | XMUX              | XMUX     | 0            |

| BSP[20:37]               | BSPHI    | 1            | Shift Tree        | CMUX     | 1            |

| Arbitary CSP<br>location | CSP      | 2            | ASP[0:17]         | ASPLO    | 2            |

| Base Constants           | BASCON   | 3            | ASP[20:37]        | ASPHI    | 3            |

#### 2.2.1 Organization of ASP and BSP

The organization of the B and A scratchpads is shown in Figure 2-10.

The first eight locations of ASPLO and BSPLO are reserved for the PDP-11 general registers R0-PC. These registers are duplicated to allow concurrent access of two registers. This allows register-to-register operations to be performed in a single microinstruction. The User Stack Pointer is duplicated in BSP[16] and ASP[16].

Three locations are reserved for the WCS user; these are indicated in the illustration as WCSB[n] and WCSA[n]. The contents of these registers is not altered by any of the base machine or floating point microcode. The standard microcode floating point implementation uses ASP[10:15, 30:35] and BSP[10:15, 30:35] as the floating point accumulators. If the FP11-E floating point processor is present, these locations are also available for the WCS user. No other standard microcode uses these registers.

The remaining registers fall into two classes: those which the WCS user may alter, and those which you must not alter.

2.2.1.1 <u>Temporary Storage Registers</u> -- A WCS microprogram can use the registers which the base machine and floating point use for temporary storage during instruction execution.

The temporary storage registers used by the base machine are:

| BSPHI[4] | := | R(T1B)  |

|----------|----|---------|

| BSPHI[5] | := | R(T2B)  |

| ASPHI[4] | := | R(TlA)  |

| ASPHI[5] | := | R (T2A) |

The state of these registers is not saved if the base machine code is invoked. Thus, data stored in these registers may be overwritten by the base machine microcode that handles error conditions, or if a new macro-level instruction is fetched.

The following registers are used for temporary storage by the floating point microcode and by the FPll-E.

BSPLO[17] := FDST2 BSPHI[17] := FDST0 ASPLO[17] := FDST3 ASPHI[17] := FDST1

User data stored in these registers will be lost if a floating point instruction (17xxxx) is fetched.

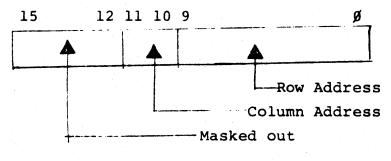

2.2.1.2 <u>Reserved System Registers</u> -- The remaining 11 registers in the B and A scratchpads are used to store console, status, address, and constant information. These registers are reserved for use by the base machine and <u>must</u> not be altered. They may, however, be read. WCSADR, ASPHI[1], has the contents of Unibus address 177542. It is used to specify an address within the WCS control store space to which data is to be written. (See Chapter 6)