EK-KE44A-TM-001

# KE44-A CISP Technical Manual

Prepared by Educational Services of Digital Equipment Corporation

•

#### Copyright • 1981 by Digital Equipment Corporation

All Rights Reserved

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DIGITAL | DECsystem-10 | MASSBUS     |

|---------|--------------|-------------|

| DEC     | DECSYSTEM-20 | OMNIBUS     |

| PDP     | DIBOL        | <b>OS/8</b> |

| DECUS   | EDUSYSTEM    | RSTS        |

| UNIBUS  | VAX          | RSX         |

|         | VMS          | IAS         |

## **CONTENTS**

| CHAPTER 1      | INTRODUCTION                                                                         | Page           |

|----------------|--------------------------------------------------------------------------------------|----------------|

| 1.1            | PURPOSE AND SCOPE                                                                    | . 1-1          |

| 1.2            | GENERAL DESCRIPTION                                                                  | . 1-1          |

| 1.2.1          | Commercial Instruction Set                                                           | . 1-1          |

| 1.2.2          | Suspension (Interrupt)                                                               | . 1-1          |

| 1.2.3          | The Microcode                                                                        |                |

| 1.2.4          | Hardware Description                                                                 | . 1-2          |

| 1.3            | RELATED HARDWARE MANUALS                                                             | . 1-2          |

| CHAPTER 2      | INTERFACING                                                                          |                |

| 2.1            | GENERAL                                                                              |                |

| 2.2            | INITIAL OPERATION                                                                    | . 2-3          |

| 2.3            | MICROCODE GENERATION                                                                 | . 2-3          |

| CHAPTER 3      | EXTENDED INSTRUCTION DATA TYPES                                                      |                |

| 3.1            | CHARACTER DATA TYPES                                                                 | . 3-1          |

| 3.1.1          | Character                                                                            |                |

| 3.1.2          | Character String                                                                     |                |

| 3.1.3          | Character Set                                                                        | . 3-2          |

| 3.2            | DECIMAL STRING DATA TYPES                                                            |                |

| 3.2.1          | Common Properties                                                                    |                |

| 3.2.2          | Decimal String Descriptors                                                           |                |

| 3.2.3          | Packed Strings                                                                       |                |

| 3.2.4          | Zoned Strings                                                                        |                |

| 3.2.5          | Overpunch Strings                                                                    |                |

| 3.2.6          | Separate Strings                                                                     |                |

| 3.3            | LONG INTEGER                                                                         | . 3-14         |

| CHAPTER 4      | THEORY OF OPERATION                                                                  |                |

| 4.1            | 2901A MICROPROCESSOR SLICER                                                          |                |

| 4.1.1          | 2901A RAM                                                                            |                |

| 4.1.2          | Arithmetic Logic Unit (ALU)                                                          | . 4-4          |

| 4.1.2.1        | Logical and Arithmetic Functions.<br>Logical Functions for G, P, $C_{N+4}$ , and OVR | . 4-5          |

| 4.1.2.2        | Logical Functions for G, P, C <sub>N+4</sub> , and OVR                               | . 4-6          |

| 4.1.3          | Q-Register                                                                           |                |

| 4.1.4          | Bit Shifting                                                                         |                |

| 4.1.5          | Status Bits                                                                          | . 4-8          |

| 4.1.6          | Carry Lookahead Logic                                                                | . 4-8          |

| 4.1.7          | 2901A Pin Definitions                                                                | . 4-8          |

| 4.2            | INSTRUCTION SUSPENSION (INTERRUPT)                                                   |                |

| 4.2.1<br>4.2.2 | Steps Leading to Suspension                                                          | . 4-9          |

| 4.2.2<br>4.3   | Returning from Suspension                                                            | . 4-9<br>. 4-9 |

| 4.3<br>4.3.1   |                                                                                      |                |

| 4.3.2          | IR Decode<br>CPC Branching                                                           |                |

| 4.3.3          | MPC Addressing                                                                       |                |

| 4.3.4          | MrC Addressing                                                                       |                |

| 4.3.5          | BCD Operation PROM                                                                   |                |

|                |                                                                                      |                |

| 4.4    | DETAILED BINARY DATA PATH                        | 4-13 |

|--------|--------------------------------------------------|------|

| 4.4.1  | Direct Data (ALU-In) Multiplexer                 | 4-13 |

| 4.4.2  | Constants Generation for 2901A                   |      |

| 4.4.3  | Saving Constants Before Suspension (Interrupt)   | 4-13 |

| 4.4.4  | Restoring Constants After Suspension (Interrupt) | 4-13 |

| 4.4.5  | 2901A Write Operations                           | 4-14 |

| 4.4.6  | 2901A Shift Operations                           | 4-14 |

| 4.4.7  | Input Multiplexers                               | 4-14 |

| 4.5    | DETAILED BCD ALU DESCRIPTION                     | 4-15 |

| 4.5.1  | BCD "A" Register/BCD "B" Register                | 4-16 |

| 4.5.2  | BCD Carry                                        |      |

| 4.5.3  | BCD Multiply                                     |      |

| 4.5.4  | BCD ASCII Encoding                               |      |

| 4.5.5  | BCD Sign Translation                             | 4-16 |

| 4.6    | DETAILED LOGIC DESCRIPTION OF STATUS BITS        | 4-17 |

| 4.6.1  | Status Bits                                      | 4-17 |

| 4.6.2  | Nonzero Conditions                               | 4-17 |

| 4.6.3  | Carry/Borrow                                     | 4-18 |

| 4.6.4  | Sign Bits                                        | 4-18 |

| 4.6.5  | Address Odd Conditions                           | 4-19 |

| 4.6.6  | Status Bit Operation with BR Interrupt Pending   | 4-19 |

| 4.6.7  | Return from Interrupt                            | 4-19 |

| 4.6.8  | Categorizing Instructions to Form N,Z,V,C Bits   |      |

| 4.6.9  | Arithmetic Condition Codes                       | 4-21 |

| 4.6.10 | Condition Code Output                            | 4-21 |

| 4.6.11 | Character String Condition Codes                 | 4-21 |

|        |                                                  |      |

## CHAPTER 5 MICROCODE

| 5.1    | INTRODUCTION         | 5-1 |

|--------|----------------------|-----|

| 5.1.1  | Design Guideline     | 5-1 |

| 5.1.2  |                      | 5-1 |

| 5.2    |                      | 5-1 |

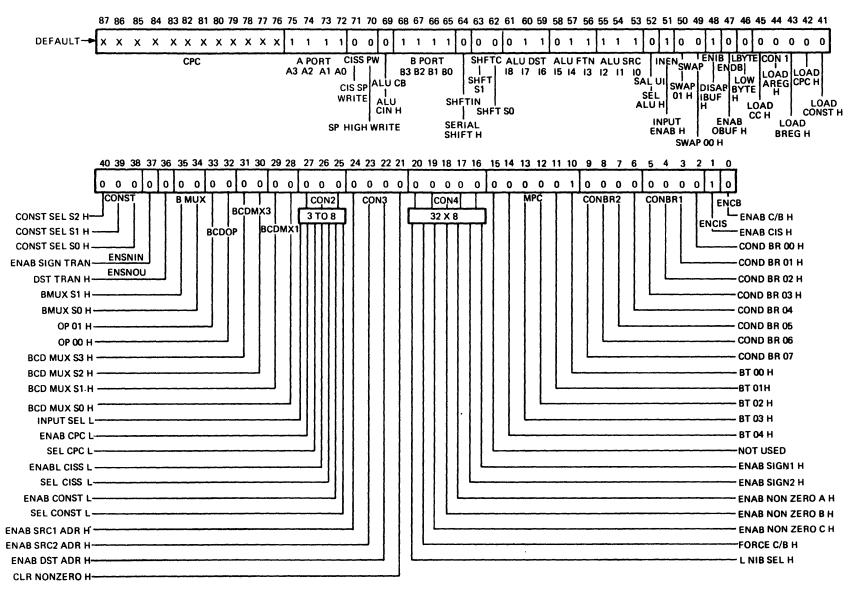

| 5.2.1  | CPC Field (87:76)    | 5-3 |

| 5.2.2  | APORT Field (75:72)  |     |

| 5.2.3  | CISSPW Field (71:70) |     |

| 5.2.4  | ALUCB Bit (69)       |     |

| 5.2.5  | BPORT Field (68:65)  | 5-3 |

| 5.2.6  | SHFTIN Bit (64)      |     |

| 5.2.7  |                      | 5-3 |

| 5.2.8  | ALUDST Field (61:59) | 5-3 |

| 5.2.9  | ALUFTN Field (58:56) | 5-3 |

| 5.2.10 | ALUSRC Field (55:53) | 5-3 |

| 5.2:11 | SALUI Bit (52)       | 5-3 |

| 5.2.12 | INEN Bit (51)        |     |

| 5.2.13 | SWAP Field (50:49)   |     |

| 5.2.14 | ENIB Bit (48)        |     |

| 5.2.15 | ENOB Bit (47)        | 5-4 |

| 5.2.16 | LBYTE Bit (46)       | 5-4 |

...

| 5.2.17     | CON1 Field (45:41)                                  | 5-4        |

|------------|-----------------------------------------------------|------------|

| 5.2.18     | CONST Field (40:38)                                 | 5-4        |

| 5.2.19     | ENSNIN Bit (37)                                     | 5-4        |

| 5.2.20     | ENSNOU Bit (36)                                     | 5-4        |

| 5.2.21     | BMUX Field (35:34)                                  | 5-4        |

| 5.2.22     | BCDOP Field (33:32)                                 | 5-4        |

| 5.2.23     | BCDMX3 Field (31:30)                                | 5-5        |

| 5.2.24     | BCDMX1 Field (29:28)                                | 5-5        |

| 5.2.25     | CON2 Field (27:25)                                  | 5-5        |

| 5.2.26     | CON3 Field (24:21)                                  | 5-5        |

| 5.2.27     | CON4 Field (20:16)                                  | 5-5        |

| 5.2.28     | MPC Field (15:10)                                   | 5-5        |

| 5.2.29     | CONBR2 Field (9:6)                                  | 5-5        |

| 5.2.30     | CONBR1 Field (5:2)                                  | 5-5        |

| 5.2.31     | ENCIS Bit (1)                                       | 5-5        |

| 5.2.32     | ENCB Bit (0)                                        | 5-5        |

| 5.3        | READING THE MICROCODE                               | 5-5        |

| 5.3.1      | The Field Definitions                               | 5-6        |

| 5.3.2      | The Microinstruction                                | 5-7        |

| 5.3.3      | Reading the Macrodefinitions                        |            |

| 5.4        | THE CIS MICROCODE INSTRUCTIONS                      | 5_10       |

| 5.4        |                                                     | 5-10       |

| CHAPTER 6  | INSTALLATION AND CHECKOUT                           |            |

| 6.1        | INSTALLATION                                        | 6-1        |

| 6.2        | CHECKOUT                                            |            |

| 0.2        |                                                     | 0-2        |

| CHAPTER 7  | MAINTENANCE                                         |            |

| 7.1        | GENERAL                                             | 7-1        |

| 7.2        | KE44-A DIAGNOSTICS                                  | 7-1        |

| 7.2.1      | CZKEEA Dragram Abstract                             | 7-1<br>7-1 |

| 7.2.2      | CZKEEA Program Abstract                             | 7-1        |

| 7.2.2.1    | Program Starting Procedure                          | 7-1<br>7-1 |

| 7.2.2.2    | Starting Address 200                                | 7-1        |

| 7.2.2.3    | Starting Address 204                                |            |

| 7.2.3      | Starting Address 210                                | 7-3<br>7-4 |

| 7.2.4      | Error Information                                   |            |

| 7.2.5      | Program Options                                     | 7-4        |

| 7.3        | Program Execution Times<br>ASCII PROGRAMMER CONSOLE | 7-4        |

| 7.5        | ASCII PROGRAMMER CONSOLE                            | 7-5        |

| APPENDIX A | EXTENDED-INSTRUCTION DEFINITIONS                    |            |

| APPENDIX B | CIS MPC FUNCTIONS                                   |            |

| APPENDIX C | CIS ABBREVIATIONS                                   |            |

| APPENDIX D | CISP MNEMONICS                                      |            |

•

## **FIGURES**

| Figure No. | Title                                      | Page |  |

|------------|--------------------------------------------|------|--|

| 2-1        | KE44-A/CPU Interface Lines                 |      |  |

| 4-1        | KE44-A Block Diagram                       |      |  |

| 4-2        | 2901A Detailed Block Diagram               |      |  |

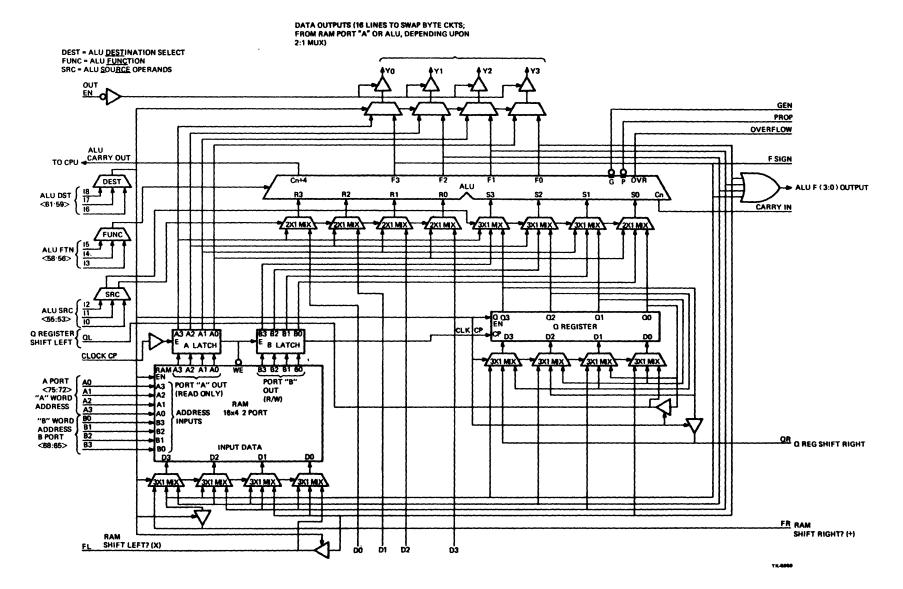

| 4-3        | AM2901A Pin Connections                    |      |  |

| 4-4        | MPC Timing                                 |      |  |

| 4-5        | 2901A Shift Operations                     |      |  |

| 4-6        | CIS Status Word                            |      |  |

| 5-1        | CIS Microword Field Map                    |      |  |

| 5-2        | Sample Page of Microcode Field Definitions |      |  |

| 5-3        | Sample Page of Microinstructions           |      |  |

| 5-4        | Sample Page of Macrodefinitions            |      |  |

| 6-1        | Module Placement in Processor Backplane    |      |  |

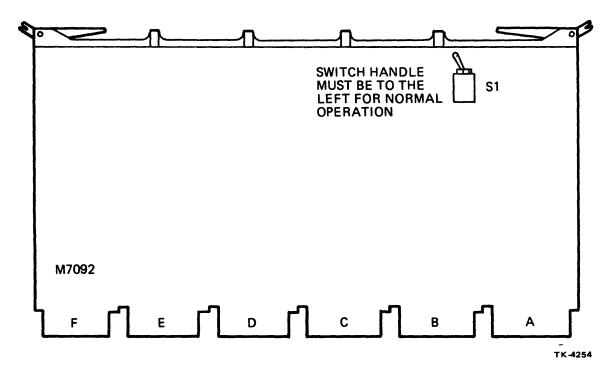

| 6-2        | KE44-A Data Path/Logic Module, M7092       |      |  |

# **TABLES**

## Table No.

## Title

| 2-1 | KE44-A/CPU Interface Line Definitions                  | 2-2  |

|-----|--------------------------------------------------------|------|

| 4-1 | Microcode Matrix for Source Operands and ALU Functions | 4-4  |

| 4-2 | ALU Logic Mode Functions                               | 4-5  |

| 4-3 | ALU Arithmetic Mode Functions                          | 4-6  |

| 4-4 | P, G, C <sub>N+4</sub> , and OVR Functions             | 4-7  |

| 4-5 | CPC Bits Affected by Branching Conditions              |      |

| 4-6 | BCD ALU Operations                                     | 4-12 |

| 4-7 | Sign Coding.                                           | 4-19 |

| 4-8 | Instruction Categories                                 |      |

| 4-9 | Condition Code Settings                                |      |

Page

,

## CHAPTER 1 INTRODUCTION

#### 1.1 PURPOSE AND SCOPE

This manual provides the data necessary for the installation and operation of the KE44-A Commercial Instruction Set Processor (CISP) option to the KD11-Z Central Processing Unit (CPU). The KE44-A option significantly extends the capability of the PDP-11/44 computer in the area of commercial data processing. The KE44-A option is installed in the PDP-11/44 cabinet.

CIS-specific abbreviations used in this manual are listed in Appendix C. Appendix D lists the CIS microword mnemonics.

#### **1.2 GENERAL DESCRIPTION**

#### 1.2.1 Commercial Instruction Set

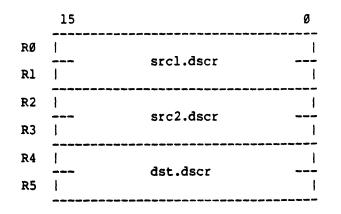

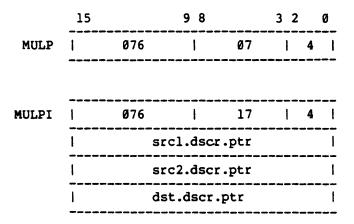

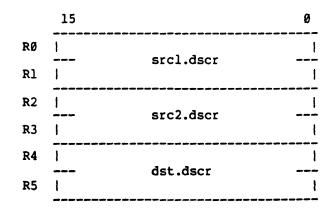

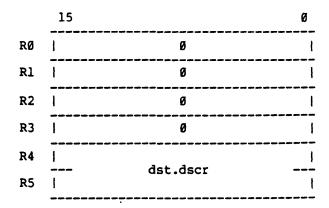

The CIS is a series of instructions for manipulating byte strings in order to provide improved COBOL performance, text editing and word processing capability. The instruction set includes instructions for character handling and decimal string operations. Each of these instructions has two forms: register and in-line.

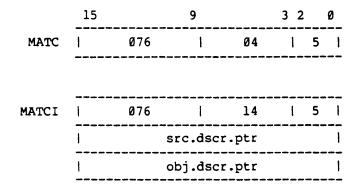

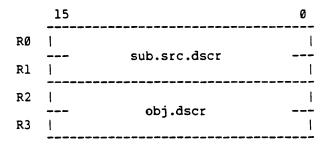

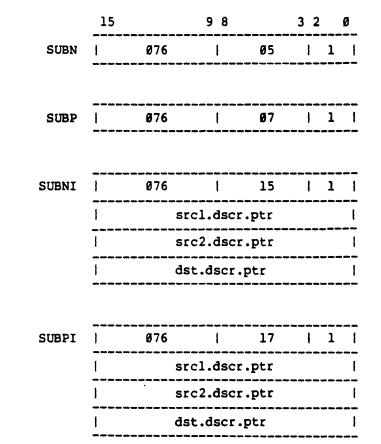

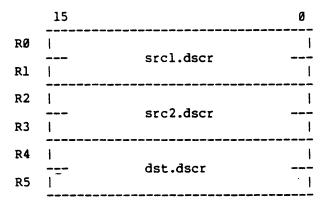

In the **register form** descriptors are loaded into the general registers before the instruction is performed. With the **in-line form**, descriptors are accessed by descriptor address pointers. The CIS also includes "load two" and "load three" descriptor instructions that augment the register form. The op code for all CIS instruction is 076 nnn.

#### 1.2.2 Suspension (Interrupt)

Since CIS instruction times may be long (due to large operands), a method is provided for giving system devices interrupt access to the processor. Thus, during CIS instructions, a test is made at specific points in the microcode for Bus Request (BR) interrupts. If an interrupt is detected, the CIS instruction is automatically interrupted, "suspended", on a BR priority basis. During suspension, the CIS instruction is stopped and control is returned to the KD11-Z. The interrupt routine will then run, executing one or more new CIS instructions during the period of suspension. At the end of this interrupt routine, control is returned to the KE44-A for completion of the suspended instructions. The entry point (microword address) for the suspended instruction is the same as the initial entry point. The control store contains a service interrupt save-state routine and a restore-from-service- interrupt routine.

#### 1.2.3 The Microcode

The CIS instructions are implemented in microcode. The KE44-A microstore comprises 1,000 88-bit words. When a valid op code is received, the starting microstore address is entered and the instruction is performed. All of the microwords necessary to perform the op code specified operation are sequenced through. Each 88-bit microword is subdivided into 32 fields. The CIS program counter (CPC) field  $\langle 87:76 \rangle$  of each microword is coded with the address of the next microword.

#### 1.2.4 Hardware Description

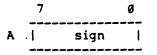

The main hardware elements of the KE44-A are a control store module and a data path module. The control store is a quad-height (M7091) board that contains the microcode in ROM form. The operational logic is on a hex-height (M7092) board that contains four basic sections.

- 1. Instruction Register (IR) Decode, CIS Program Counter (PC) and Microprocessor Code (MPC) Addressing logic

- 2. Binary data path logic

- 3. Decimal data path logic

- 4. Status Information and Condition Code Generation logic

These sections are described in detail in Chapter 4.

#### **1.3 RELATED HARDWARE MANUALS**

The following hardware manuals are related to the KE44-A and may be purchased from Digital Equipment Corporation.

| Title                                      | Document<br>Number | Availability               |

|--------------------------------------------|--------------------|----------------------------|

| PDP-11/44 CP Subsystem<br>Technical Manual | EK-KD11Z-TM        | Hardcopy and<br>Microfiche |

| PDP-11/44 System User's<br>Guide           | EK-11044-UG        | Hardcopy                   |

| FP11-F Floating-Point<br>Technical Manual  | EK-FP11F-TM        | Hardcopy and<br>Microfiche |

All purchase orders for hardware manuals should be forwarded to:

Digital Equipment Corporation Accessory and Supplies Group (P086) Cotton Road Nashua, NH 03060

Purchase orders must show shipping and billing addresses and state whether a partial shipment will be accepted.

All correspondence and invoicing inquiries should be directed to the above address.

For information concerning microfiche libraries, contact:

Digital Equipment Corporation Micropublishing Group BU/D2 12 Crosby Drive Bedford, MA 01730

## CHAPTER 2 INTERFACING

#### 2.1 GENERAL

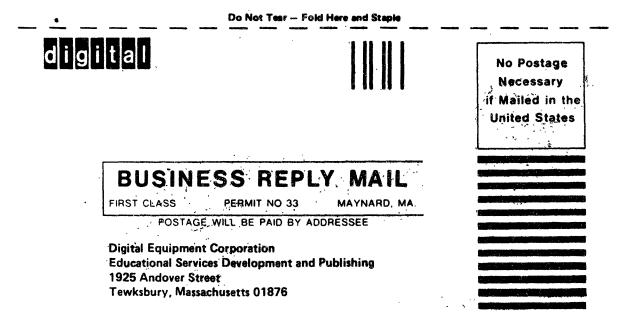

The KD11-Z CPU loads commercial instructions and operands into the CISP KE44-A. After the CISP executes the requested operation, the CPU reads the results and stores them in memory. Figure 2-1 shows the KE44-A/CPU interface lines; Table 2-1 describes the interface signals.

#### NOTE

The KE44-A does not directly interface with the UNIBUS, but is connected to the KD11-Z via a bus that is separate from the UNIBUS and uses the KD11-Z microcode for data transfers to and from memory.

TK-7232

Figure 2-1 KE44-A/CPU Interface Lines

| Mnemonic         | Signal Flow   | Function                                                                                                                                         |

|------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| MPC (00:08) L    | Bidirectional | Microprogram address lines. Used to sequence<br>the CPU through the microprogram. Derived<br>from KE44-A microcode. Cannot be altered by<br>CPU. |

| AMUX (00:15) L   | Bidirectional | Data lines used to transfer instructions and oper-<br>ands between CPU and KE44-A.                                                               |

| ENAB CIS L       | KE44-A to CPU | Forces CPU to a service state after the com-<br>pletion of a CIS instruction; i.e., when a low-to-<br>high signal transition occurs.             |

| CIS ABORT H      | CPU to KE44-A | Clears CIS CPC line when an abort condition exists in CPU.                                                                                       |

| PROC INIT L      | CPU to KE44-A | CPU initialize. Used to initialize status registers in KE44-A.                                                                                   |

| LOAD IR L        | CPU TO KE44-A | Cause KE44-A to load its instruction register (IR) from AMUX lines.                                                                              |

| TRI-STATE AMUX L | KE44-A to CPU | Causes CPU to remove data from AMUX lines.<br>Turns off the KD11-Z drivers, thus enabling<br>KE44-A access to the AMUX lines.                    |

| PFAIL BR PEND H  | CPU to KE44-A | When high, indicates that an interrupt needs servicing. Used by the KE44-A to suspend instructions in the middle of execution.                   |

| PAGE FAULT H     | CPU TO KE44-A | If high, indicates that a page of memory cannot<br>be written into. This signal is generated by prob-<br>ing, rather than writing to the page.   |

| FORCE CIS DATA L | CPU to KE44-A | Console-generated signal for monitoring MBUS data via the AMUX lines.                                                                            |

| FREE BUS H       | CPU to KE44-A | Console-generated signal that tri-states all main-<br>tenance that drive the AMUX lines.                                                         |

| EXT CLK A L      | CPU to KE44-A | CPU signal that clocks the control word through the control logic.                                                                               |

| FORCE CPC L      | CPU to KE44-A | Console-generated signal for monitoring the CPC lines via the AMUX lines.                                                                        |

## Table 2-1 KE44-A/CPU Interface Line Definitions

.

#### 2.2 INITIAL OPERATION

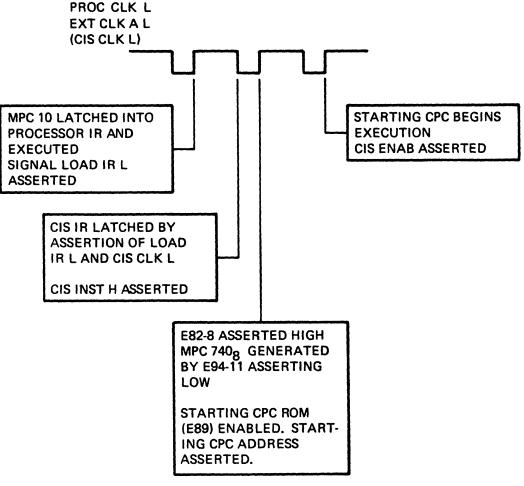

Initially, the CPU fetches an instruction from memory and decodes it in the CPU and CIS. During this fetch, LOAD IR L is asserted to load the CIS IR. Any instruction with an op code of 0760xx or 0761xx is a commercial instruction and requires the use of the KE44-A to process. The CIS next asserts 740 on the MPC 0-8 microprocessor code bus (MPC bus). Since CIS instructions are only recognized by the KE44-A option, the assertion of MPC 740 is required to prevent the CPU from trapping on an illegal instruction. MPC 740 is decoded by the KD11-Z to set up the CIS processor for an operation in the next CPU cycle. Concurrently with this decoding, a CPC (CIS program counter) address is asserted to the 88-bit control store of the KE44-A. This control word is clocked by EXT CLK A L from the CPU.

#### 2.3 MICROCODE GENERATION

A series of microcodes is generated in the KE44-A to control microprocessor operation during each instruction. During CIS operation, the KE44-A informs the CPU (via a microcode asserted on the MPC 0-8 lines) whenever data can be read from the AMUX 0-15 lines. The KE44-A also sends the CPU a TRI STATE AMUX L signal that enables it to read data from the AMUX lines. The CPU then stores this data and continues operation.

NOTE Chapter 3 has been duplicated directly from DECSTD168-PDP-11 Extended Instructions.

## CHAPTER 3 EXTENDED-INSTRUCTION DATA TYPES

#### 3.1 CHARACTER DATA TYPES

There are three different character data types. The 'character' is a single byte, and is an abbreviated string of length one. The 'character string' is a contiguous group of bytes in memory. The third is a 'character set'.

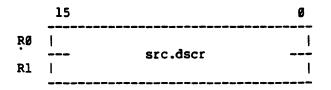

3.1.1 Character

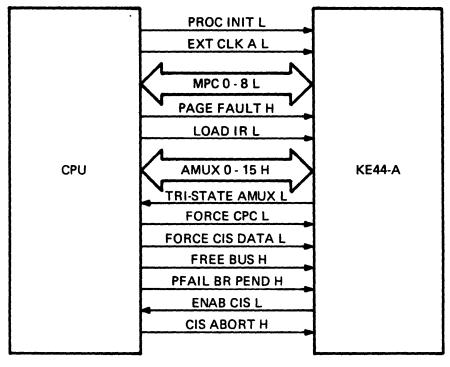

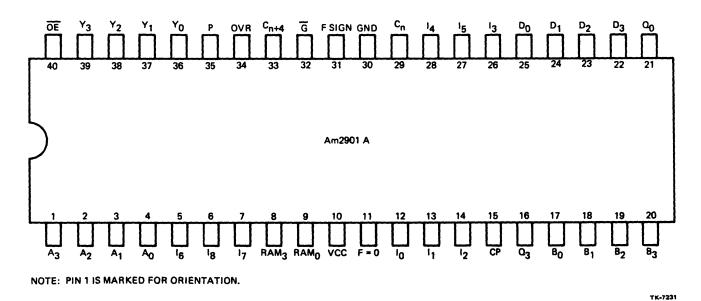

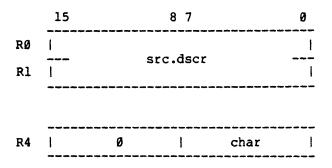

The character is an 8 bit byte:

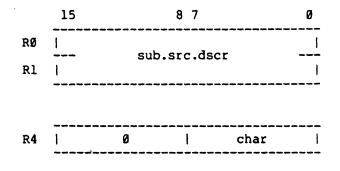

The character is used as an operand by CIS11 instructions. When it appears in a general register, the character is in the low order half; the high order half of the register must be zero. When it appears in the instruction-stream, the character is in the low order half of a word; the high order half of the word must be zero. If the high order half of a word which contains a character is non-zero, the effect of the instruction which uses it will be unpredictable.

#### 3.1.2 Character String

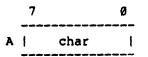

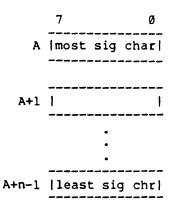

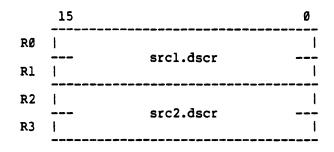

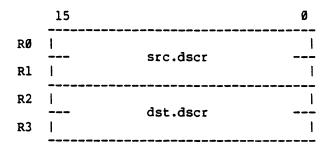

A character string is a contiguous sequence of bytes in memory that begins and ends on a byte boundary. It is addressed by its most significant character (lowest address). The highest address is the least significant character. It is specified by a two word descriptor with the attributes of length and lowest address. The length is an unsigned binary integer which represents the number of characters in the string and may range from 0 to 55,535. A character string with zero length is said to be vacant; its address is ignored. A character string with non-zero length is said to be occupied.

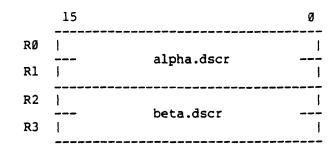

The character string descriptor is used as an operand by CIS11 instructions. It appears in two consecutive general registers, or in two consecutive words in memory pointed to by a word in the instruction stream. The following figure shows the descriptor for a character string of length 'n' starting at address 'A' in memory:

The following figure shows the character string in memory:

#### 3.1.3 Character Set

A 'character set' is a subset of the 256 possible characters that can be encoded in a byte. It is specified by a descriptor which consists of the address of a 256 byte table and an 8 bit mask. The address is of the zeroeth byte in the table. Each byte in the table specifies up to eight orthogonal character subsets of which the corresponding character is a member. The mask selects which combinations of these orthogonal subsets comprise the entire character set. In effect, each bit in the mask corresponds to one of eight orthogonal subsets that may be encoded by the table. The mask specifies the union of the selected subsets into the character set. Typical sets would be: upper case, lower case, non-zero digits, end of line, etc.

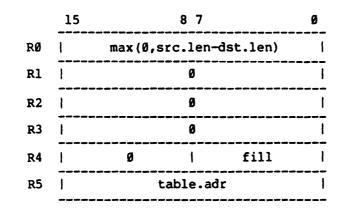

Operationally, a character (char) is considered to be in the character set if the evaluation of (M[table.adr+char] AND mask) is not equal to zero. The character is not in the character set if the evaluation is zero. Each byte in the table indicates which combination of up to eight orthogonal character subsets (i.e. one for each of the eight bit vectors 00000001(2), 00000010(2), 00000100(2), 00001000(2), 00010000(2), 00100000(2), 01000000(2) and 100000000(2)) the corresponding character is a member. The mask specifies which union of the eight orthogonal character subsets comprise the total character set. For example, if the eight bit vector 00000001(2) appearing in the table corresponds to the character subset of all upper case alphabetic characters, 00000010(2) appearing in the table corresponds to the character subset of all lower case alphabetic characters, and 00000100(2) appearing in the table corresponds to the decimal digits, then using the mask 00000011(2) with this table specifies the character set of all alphabetic characters, and using the mask 00000111(2) specifies the character set of all alphanumeric characters. The character set descriptor is used as an operand by CIS11 instructions. It appears in two consecutive general registers, or in two consecutive words in memory pointed to by a word in the instruction stream. If the high order half of the first descriptor word is non-zero, the effect of an instruction which uses a character set will be unpredictable.

|            |       | 15 |       | 87     |      | Ø |

|------------|-------|----|-------|--------|------|---|

| Rx         | ptr   | 1  | 0     | 1      | mask | 1 |

| or<br>Rx+1 | ptr+2 |    | table | addres |      | 1 |

|            |       |    |       |        |      |   |

#### 3.2 DECIMAL STRING DATA TYPES

Two classes of decimal string data types -- numeric strings and packed strings -- are defined. Both have similar arithmetic and operational properties; they primarily differ in the representation of signs and the placement of digits in memory.

The numeric string data types are signed zoned, unsigned zoned, trailing overpunch, leading overpunch, trailing separate and leading separate. The packed string data types are signed packed and unsigned packed. Instructions which operate on numeric strings permit each numeric string operand to be separately specified; similarly, packed string instructions permit each packed string operand to be separately specified. Thus, within each of the two classes of decimal strings, the operands of an instructions may be of any data type within the appropriate class.

#### 3.2.1 Common Properties

Decimal strings exist in memory as contiguous bytes which begin and end on a byte boundary. They represent numbers consisting of Ø to 31(10) digits in either sign-magnitude or absolute-value form. Sign-magnitude strings (SIGNED) may be positive or negative; absolute-value strings (UNSIGNED) represent the absolute value of the magnitude. Decimal numbers are whole integer values with an implied decimal radix point immediately beyond the least significant digit; they may be conceptually extended with zero digits beyond the most significant digit.

A 4-bit binary coded decimal representation is used for most digits in decimal strings. A four bit half byte is called a 'nibble' and may be used to contain a binary bit pattern which represents the value of a decimal digit. The following table shows the binary nibble contents associated with each decimal digit:

| digit | nibble      |

|-------|-------------|

|       |             |

| ø     | <b>0000</b> |

| 1     | 0001        |

| 2     | 0010        |

| 3     | ØØ11        |

| 4     | 0100        |

| 5     | Ø1Ø1        |

| 6     | Ø11Ø        |

| 7     | Ø111        |

| 8     | 1000        |

| 9     | 1001        |

Each decimal string data type may have several representations. These representations permit certain latitude when accepting source operands. Decimal String data types have a PREFERRED representation which is a valid source representation and which is used to construct the destination string. Additional ALTERNATE representations are provided for some decimal data types when accepting source operands.

Decimal strings used as source operands will not be checked for validity. Instructions will produce upredictable results

if a decimal string used as a source operand contains an invalid digit encoding, invalid sign designator, or in the case of overpunched numbers, an invalid sign/digit encoding.

When used as a source, decimal strings with zero magnitude are unique, regardless of sign. Thus, both positive and negative zero have identical interpretations.

Conceptually, decimal string instructions first determine the correct result, and then store the decimal string representation of the correct result in the destination string. A result of zero magnitude is considered to be positively signed. If the destination string can contain more digits than are significant in the result, the excess most significant destination string digits have zero digits stored in them. If the destination string can not contain all significant digits of the result, the excess most significant result digits are not stored; the instruction will indicate decimal overflow. Note that negative zero is stored in the destination string as a side effect of decimal overflow where the sign of the result is negative and the destination is not large enough to contain any non-zero digits of the result.

If the destination string has zero length, no result digits will be stored. The sign of the result will be stored in separate and packed strings, but not in zoned and overpunched strings. Decimal overflow will indicate a non-zero result.

#### 3.2.2 Decimal String Descriptors

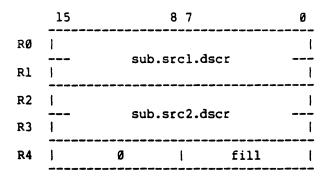

Decimal strings are represented by a two word descriptor. The descriptor contains the length, data type, and address of the string. It appears in two consecutive general registers (register form of instructions), or in two consecutive words in memory pointed to by a word in the instruction stream (in-line form of instructions). The unused bits are reserved by the architecture and must be Ø. The effect of an instruction using a descriptor will be unpredictable if any non-zero reserved fields in the descriptor contain non-zero values or a reserved data type encoding is used.

The design of the numeric and packed string descriptors are identical:

First Word:

length <4:0> - Number of digits specified as an unsigned binary

integer.

Second Word:

address <15:0> - Specifies the address of the byte which contains the most significant digit of the decimal string.

The following figure shows the descriptor for a decimal string of data type 'T' whose length is 'L' digits and whose most significant digit is at address 'A':

|      |    |       | 15 .14 | 1 1 | 2 11 |   | 54 |   | Ø |

|------|----|-------|--------|-----|------|---|----|---|---|

| Rx   |    | ptr   | ØI     | T   | ١    | Ø | ł  | L | I |

| Rx+1 | or | ptr+2 |        |     |      | A |    |   | ١ |

The encodings (in binary) for the NUMERIC string data type field are:

000 signed zoned 001 unsigned zoned 010 trailing overpunch 011 leading overpunch 100 trailing separate 101 leading separate 110 -- reserved by the architecture 111 -- reserved by the architecture The encodings (in binary) for the PACKED string data type field are:

000 -- reserved by the architecture 001 -- reserved by the architecture 010 -- reserved by the architecture 011 -- reserved by the architecture 100 -- reserved by the architecture 101 -- reserved by the architecture 101 signed packed 111 unsigned packed

#### 3.2.3 Packed Strings

Packed strings can store two decimal digits in each byte. The least significant (highest addressed) byte contains the the sign of the number in bits <3:0> and the least significant digit in bits <7:4>.

Signed Packed Strings -

The preferred positive sign designator is 1100(2); alternate positive sign designators are 1010(2), 1110(2) and 1111(2). The preferred negative sign designator is 1101(2); the alternate negative sign designator is 1011(2). Source strings will properly accept both the preferred and alternate designators; destination strings will be stored with the preferred designator.

Unsigned Packed Strings -

PACKED SIGN NIBBLE:

| Sign<br>Nibble | Preferred<br>Designator | Alternate<br>Designators |

|----------------|-------------------------|--------------------------|

|                |                         |                          |

| positive       | 1100(2)                 | 1010(2) 1110(2) 1111(2)  |

| negative       | 1101(2)                 | 1011(2)                  |

| unsigned       | 1111(2)                 |                          |

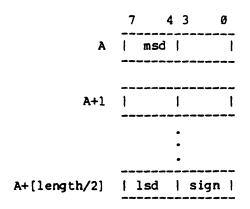

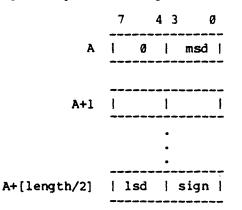

For other than the least significant byte, bytes contain two consecutive digits -- the one of lower significance in bits  $\langle 3:0 \rangle$  and the one of higher significance in bits  $\langle 7:4 \rangle$ . For numbers whose length is odd, the most significant digit is in bits  $\langle 7:4 \rangle$  of the lowest addressed byte. Numbers with an even length have their most significant digit in bits  $\langle 3:0 \rangle$  of the lowest addressed byte; bits  $\langle 7:4 \rangle$  of this byte must be zero for source strings, and are cleared to 0000(2) for destination strings. Numbers with a length of one occupy a single byte and contain their digit in bits  $\langle 7:4 \rangle$ . The number of bytes which represent a packed string is [length/2]+1 (integer division where the fractional portion of the quotient is discarded).

The following is a packed string with an odd number of digits:

The following is a packed string with an even number of digits:

A zero length packed string occupies a single byte of storage; bits  $\langle 7:4 \rangle$  of this byte must be zero for source strings, and are cleared to 0000(2) for destination strings. Bits  $\langle 3:0 \rangle$  must be a valid sign for source strings, and are used to store the sign of the result for destination strings. When used as a source, zero length strings represent operands with zero magnitude. When used as a destination, they can only reflect a result of zero magnitude without indicating overflow. The following is a zero length packed string:

A valid packed string is characterized by:

.

1. A length from Ø to 31(10) digits.

- 2. Every digit nibble is in the range 0000(2) to 1001(2).

- 3. For even length sources, bits <7:4> of the lowest addressed byte are 0000(2).

- 4. Signed Packed Strings sign nibble is either 1010(2), 1011(2), 1100(2), 1101(2), 1110(2) or 1111(2).

- 5. Unsigned Packed Strings sign nibble is 1111(2).

3.2.4 Zoned Strings

Zoned strings represent one decimal digit in each byte. Each byte is divided into two portions -- the high order nibble (bits <7:4>) and the low order nibble (bits <3:0>). The low order nibble contains the value of the corresponding decimal digit.

Signed Zoned Strings -

When used as a source string, the high order nibble of the least significant byte contains the sign of the number; the high order nibbles of all other bytes are ignored. Destination strings are stored with the sign in the high order nibble of the least significant byte, and 0011(2) in the high order nibble of all other bytes. 0011(2) in the high order nibble corresponds to the ASCII encoding for numeric digits. The positive sign designator is 0011(2); the negative sign designator is 0111(2).

Unsigned Zoned Strings -

When used as a source string, the high order nibbles of all bytes are ignored. Destination strings are stored with 0011(2) in the high order nibble of all bytes.

The number of bytes needed to contain a zoned string is identical to the length of the decimal number.

A zero length zoned string does not occupy memory; the address portion of its descriptor is ignored. When used as a source, zero length strings provide operands with zero magnitude; when used as a destination, they can only accurately reflect a result of zero magnitude (the sign of the operation is lost). An attempt to store a non-zero result will be indicated by setting overflow.

A valid zoned string is characterized by:

- 1. A length from Ø to 31(10) digits.

- The low order nibble of each byte is in the range ØØØØ(2) to 1001(2).

- 3. Signed Zoned Strings The high order nibble of the least significant byte is either 0011(2) or 0111(2).

#### 3.2.5 Overpunch Strings

Overpunch strings represent one decimal digit in each byte. Trailing overpunch strings combine the encoding of the sign and the least significant digit; leading overpunch strings combine the encoding of the sign and the most significant digit. Bytes other than the byte in which the sign is encoded are divided into two portions -- the high order nibble (bits  $\langle 7:4 \rangle$ ) and the low order nibble (bits  $\langle 3:0 \rangle$ ). The low order nibble contains the value of the corresponding decimal digit. When used as a source string, the high order nibble of all bytes which do not contain the sign are ignored. Destination strings are stored with 0011(2) in the high order nibble of all bytes which do not contain the sign. 0011(2) in the high order nibble corresponds to the ASCII encoding for numeric digits.

The following table shows the sign of the decimal string and the value of the digit which is encoded in the sign byte. Source strings will properly accept both the preferred and alternate designators; destination strings will store the preferred designator. The preferred designators correspond to the ASCII graphics 'A' to 'R', '{' and '}'. The alternate designators correspond to the ASCII graphics '0' to '9', '[', '?', ']', '!' and ':'.

#### OVERPUNCH SIGN/DIGIT BYTE:

| Overpunch  | Preferred   | Alternate                             |

|------------|-------------|---------------------------------------|

| Sign/Digit | Designator  | Designators                           |

|            |             |                                       |

| +Ø         | 01111011(2) | 00110000(2), 01011011(2), 00111111(2) |

| +1         | 01000001(2) | 00110001(2)                           |

| +2         | 01000010(2) | 00110010(2)                           |

| +3         | 01000011(2) | 00110011(2)                           |

| +4         | 01000100(2) | 00110100(2)                           |

| +5         | 01000101(2) | 00110101(2)                           |

| +6         | 01000110(2) | 00110110(2)                           |

| +7         | 01000111(2) | 00110111(2)                           |

| +8         | 01001000(2) | ØØ111000(2)                           |

| +9         | 01001001(2) | 00111001(2)                           |

| -0         | 01111101(2) | 01011101(2), 00100001(2), 00111010(2) |

| -1         | 01001010(2) |                                       |

| -2         | 01001011(2) |                                       |

| -3         | 01001100(2) |                                       |

| -4         | 01001101(2) |                                       |

| -5         | 01001110(2) |                                       |

| -6         | 01001111(2) |                                       |

| -7         | 01010000(2) |                                       |

| -8         | 01010001(2) |                                       |

| -9         | 01010010(2) |                                       |

.

The number of bytes needed to contain an overpunch string is identical to the length of the decimal number.

The following is a trailing overpunch string:

The following is a leading overpunch string:

A zero length overpunch string does not occupy memory; the address portion of its descriptor is ignored. When used as a source, zero length strings provide operands with zero magnitude; when used as a destination, they can only accurately reflect a result of zero magnitude (the sign of the operation is lost). An attempt to store a non-zero result will be indicated by setting overflow.

A valid overpunch string is characterized by:

- 1. A length from Ø to 31(10) digits.

- 2. The low order nibble of each digit byte is in the range 0000(2) to 1001(2).

- 3. The encoded sign/digit byte contains values from the above table of preferred and alternate overpunch sign/digit values.

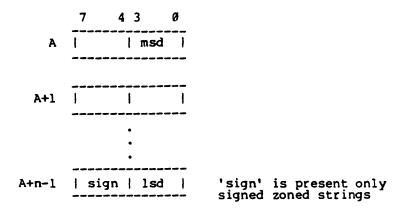

#### 3.2.6 Separate Strings

Separate strings represent one decimal digit in each byte. Trailing separate strings encode the sign in a byte immediately beyond the least significant digit; leading separate strings encode the sign in a byte immediately beyond the most significant digit. Bytes other than the byte in which the sign is encoded are divided into two portions -- the high order nibble (bits <7:4>) and the low order nibble (bits <3: $\emptyset$ >). The low order nibble contains the value of the corresponding decimal digit.

When used as a source string the high order nibbles of all digit bytes are ignored. Destination strings are stored with 0011(2) in the high order nibble of all digit bytes. 0011(2) in the high order nibble corresponds to the ASCII encoding for numeric digits. The preferred positive sign designator is 0010000(2). The negative sign designator is 00101101(2). These designators correspond to the ASCII encoding for '+', 'space' and '-'.

SEPARATE SIGN BYTE:

| Sign     | Preferred   | Alternate   |

|----------|-------------|-------------|

| Byte     | Designator  | Designators |

|          |             |             |

| positive |             | 00100000(2) |

| negative | 00101101(2) |             |

The number of bytes needed to contain a leading or trailing separate string is identical to length+1.

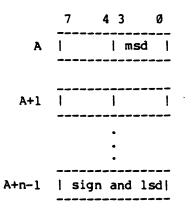

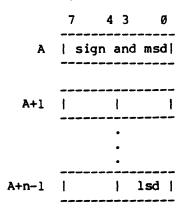

The following is a trailing separate string:

.

The following is a leading separate string:

A zero length separate string occupies a single byte of memory which contains the sign. When used as a source, zero length strings provide operands with zero magnitude; when used as a destination, they can only reflect a result of zero magnitude without indicating overflow; the sign of the result is stored.

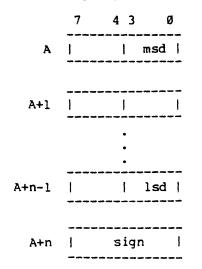

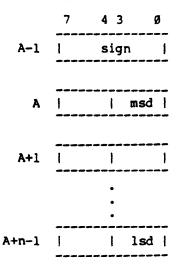

The following is a zero length trailing separate string:

The following is a zero length leading separate string:

A

A valid separate string is characterized by:

- 1. A length from Ø to 31(10) digits.

- The low order nibble of each digit byte is in the range 0000(2) to 1001(2).

- 3. The sign byte is either Ø0100000(2), Ø0101011(2) or Ø0101101(2).

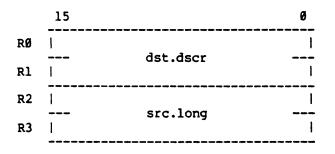

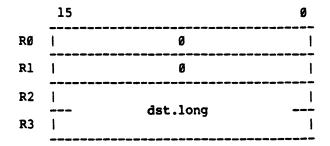

#### 3.3 LONG INTEGER

Long integers are 32 bit binary two's complement numbers organized as two words in consecutive registers or in memory -- no descriptor is used. One word contains the high order 15 bits. The sign is in bit<15>; bit<14> is the most significant. The other word contains the low order 16 bits with bit<0> the least significant. The range of numbers that can be represented is -2,147,483,648 to +2,147,483,647.

The register form of decimal convert instructions use a restricted form of long integer with the number in the general register pair R2-R3:

|    | 15 14 |                                                                       | Ø |

|----|-------|-----------------------------------------------------------------------|---|

|    |       | ه که که جو هو برد بن ناب که خد خط خد ده ده مد جو هو که که که نود از د |   |

| R2 | IS I  | hig <b>h</b>                                                          |   |

|    |       |                                                                       |   |

| R3 | 1     | low                                                                   | ł |

|    |       |                                                                       |   |

The in-line form of decimal convert instructions reference the long integer by a word address pointer which is part of the instruction stream:

|       | 15 14   |      | Ø |

|-------|---------|------|---|

| ptr   |         | low  | ł |

| ptr+2 | s  <br> | high |   |

Note that these two representations of long integers differ. There is no single representation of long integer among EAE, EIS, FPP and software. The "register form" was selected to be compatible with EIS; the "in-line form" was selected to be compatible with current standard software usage.

.

## CHAPTER 4 THEORY OF OPERATION

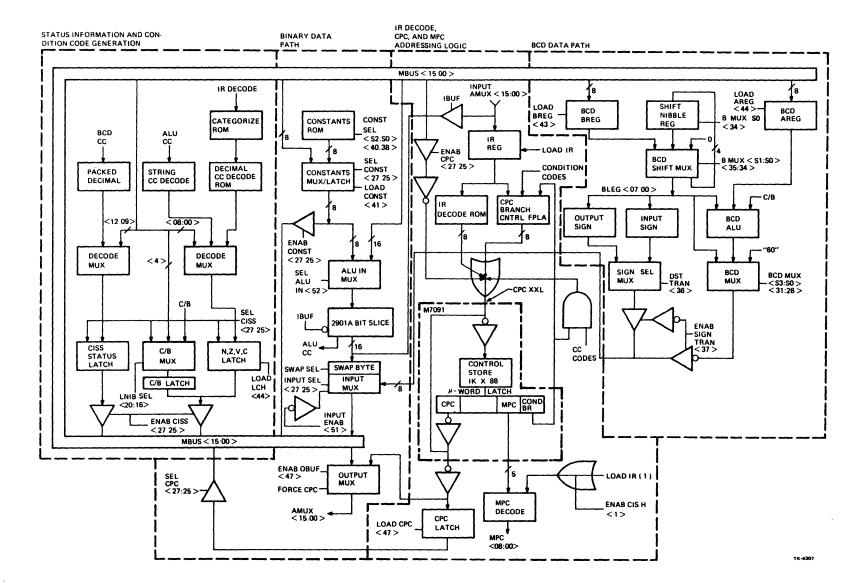

#### 4.1 2901A MICROPROCESSOR SLICER

A functional block diagram of the KE44-A (Figure 4-1) shows the use of 2901A in the binary data path. The 2901A has four 4-bit microprocessor slices that are configured for carry lookahead and external shift control in the 16-bit data path (Figure 4-2). The principal elements in each of the identical 2901As are: 1) a 16-location RAM, 2) a high-speed ALU, and 3) a separate, shiftable holding register called the Q-register. The RAM locations are used as KE44 working registers. The ALU, in conjunction with the working registers and the Q-register, performs the arithmetic and logical functions necessary to implement the macroinstruction set. Data enters the 2901As from the 2901A D bus; 2901A output data is transmitted on the 2901A Y bus. The output data is from either the 2901A ALU or the contents of a 2901A RAM (working register) location.

#### 4.1.1 2901A RAM

In the KE44-A, the RAM of the 2901As is the scratch pad area where the results of the arithmetic and logical operations can be temporarily stored. RAM contents are read into the ALU in response to microcode control signals received from the control store logic. Since each of the four 2901A microprocessors comprising this RAM has a  $16 \times 4$ -bit slice, the combination yields a total RAM capacity of sixteen 16-bit words.

The data in any of these words can be read from the A port via the 4-bit RAM APORT 0-3 H address line inputs. If the same address is applied to both A and B address lines, identical data appears at both RAM output ports. The RAM A and B outputs are applied to latches. When the RAM is write-enabled, new data is written into the RAM word selected by the RAM B input PORT 0-3 H. The RAM input data is received from a 3-input multiplexer (Figure 4-2). Multiplexer D0-D3 inputs from the ALU output permit the ALU result to be loaded into the RAM directly, or to be left- or right-shifted by one place.

Figure 4-1 KE44-A Block Diagram

4-2

Figure 4-2 2901A Detailed Block Diagram

#### 4.1.2 Arithmetic Logic Unit (ALU)

The ALU is the data path component that performs the arithmetic/logical operation under command of the microcode control word (Table 4-1) contained in the control store logic PROMs. ALU R inputs are from four 2-input multiplexers whose inputs are the direct data inputs D3-D0 and the A port outputs A3-A0 of the RAM. The S inputs, received via four 3-input multiplexers, include the A and B ports of the RAM and the Q-register outputs.

Decode of the ALU function (FUNC) lines 13–15 determines the arithmetic or logical function to be performed. Decode of the ALU destination (DEST) lines 18–16 determines which of the indicated registers the data is routed to or whether it will be a data output of the device itself. ALU output data F3–F0 can be routed to the Q-register or RAM, or placed on lines as Y3–Y0.

|                          | I <sub>210</sub> Octal           | 0     | 1     | 2    | 3    | 4          | 5     | 6     | 7    |

|--------------------------|----------------------------------|-------|-------|------|------|------------|-------|-------|------|

| I <sub>5 4 3</sub> Octal | ALU<br>Source<br>ALU<br>Function | A.Q   | A,B   | 0,Q  | O,B  | <b>0,A</b> | D,A   | D,Q   | D,O  |

| 0                        | $C_n = L$                        | A+Q   | A+B   | Q    | В    | Α          | D+A   | D+Q   | D    |

| 0                        | R Plus S<br>C <sub>n</sub> =H    | A+Q+1 | A+B+1 | Q+1  | B+1  | A+1        | D+A+1 | D+Q+1 | D+1  |

|                          | $C_n = L$                        | Q-A-1 | B-A-1 | Q-1  | B 1  | AI         | A-D-1 | Q-D-1 | -D-1 |

| 1                        | S Minus R<br>C <sub>n</sub> =H   | Q-A   | B-A   | Q    | В    | A          | A-D   | Q-D   | -D   |

| 2                        | $C_n = L$                        | A-Q-1 | A-B-1 | -Q-1 | -B-1 | -A-1       | D-A-1 | D-Q-1 | D-1  |

| 2                        | R Minus S<br>C <sub>n</sub> =H   | A-Q   | A-B   | -Q   | В    | -A         | D-A   | D-Q   | D    |

| 3                        | R OR S                           | A∨Q   | A∨B   | Q    | В    | A          | D-A   | D∨Q   | D    |

| 4                        | R AND S                          | A∧Q   | А∧В   | 0    | 0    | 0          | D∕∖A  | D∧Q   | 0    |

| 5                        | R AND S                          | Ā^Q   | Ā^B   | Q    | В    | A          | D∀A   | D∀Q   | 0    |

| 6                        | R EX-OR S                        | A∀Q   | A∀B   | Q    | В    | A          | D∀A   | D∀Q   | ·D   |

| 7                        | R EX-NOR S                       | Ā∀Q   | A∀B   | Q    | В    | A          | D∀A   | D₩Q   | D    |

#### Table 4-1 Microcode Matrix for Source Operands and ALU Functions

+ = Plus; - = Minus;  $\lor$  = OR,  $\land$  = AND;  $\forall$  = EX OR

The ALU source operand decode performs the actual register selection. All three of these functions are controlled by ALU instructions I8–I0 from the control store logic.

The ALU can perform three binary arithmetic and five logical operations on the two input words received via the R and S inputs. Each R input is driven by a separate 2 input multiplexer and each S input from a separate 3 input multiplexer. In the KE44-A CIS, the R input multiplexer can be used to select either the RAM A port data or a direct data input consisting of constants or MBUS data. The S input multiplexer selects the Q-register output or the RAM output of port A or B. Both multiplexers have an inhibit output capability that produces a source operand of zero.

**4.1.2.1** Logical and Arithmetic Functions – The ALU performs five logical and three arithmetic functions on eight source operand pairs. ALU logic functions and appropriate control bit values (source select I2–I0, and function select I5–I3) are described in Table 4-2. The carry input ( $C_n$ ) has no effect on operations in logic mode but does affect operations in arithmetic mode (Table 4-3), which defines carry-in high ( $C_n=1$ ) and carry-in low ( $C_n=1$ ) for this mode.

| Octal<br>I <sub>5 4 3</sub> , I <sub>2 1 0</sub> | Group  | Function                               | Octal<br>I <sub>543</sub> , I <sub>210</sub> | Group  | Function                                         |

|--------------------------------------------------|--------|----------------------------------------|----------------------------------------------|--------|--------------------------------------------------|

| 40                                               |        | A∧Q                                    | 74                                           | Invert | $\frac{\overline{A}}{D}$                         |

| 41                                               |        | A∧B                                    | 77                                           |        | D                                                |

| 4 5                                              | AND    | D∧A                                    |                                              |        |                                                  |

| 4 6                                              |        | D∧Q                                    | 62                                           |        | Q                                                |

|                                                  |        | -                                      | 63                                           |        | Q<br>B                                           |

| 30                                               |        | A∨Q                                    | 64                                           | Pass   | A                                                |

| 31                                               |        | A∨B                                    | 67                                           |        | D                                                |

| 35                                               | OR     | D∨A                                    |                                              |        |                                                  |

| 36                                               |        | D∨Q                                    | 3 2                                          |        | Q                                                |

|                                                  |        |                                        | 33                                           |        | Q<br>B                                           |

| 60                                               |        | A∀Q                                    | 34                                           | Pass   | A                                                |

| 61                                               |        | A∀B                                    | 37                                           |        | D                                                |

| 6 5                                              | EXOR   | D∀A                                    |                                              |        |                                                  |

| 66                                               |        | D∀Q                                    | 4 2                                          |        | 0                                                |

|                                                  |        |                                        | 43                                           |        | 0                                                |

| 70                                               |        | $\frac{\overline{A \lor Q}}{A \lor B}$ | 44                                           | "Zero" | 0<br>0                                           |

| 71                                               |        | A∨B                                    | 47                                           |        | 0                                                |

| 75                                               | EX NOR | DVA                                    |                                              |        |                                                  |

| 76                                               |        | DVQ                                    | 50                                           |        | Ā∧Q                                              |

|                                                  |        |                                        | 51                                           |        | $\overline{A} \land B$<br>$\overline{D} \land A$ |

| 72                                               |        | $\frac{\overline{Q}}{B}$               | 5 5                                          | Mask   | D∧A                                              |

| 73                                               |        | B                                      | 56                                           |        | $\overline{D}_{1}$                               |

Table 4-2

ALU Logic Mode Functions

| Octal              | C <sub>n</sub> = 0 (Low) |       | C <sub>n</sub> = 1 (H | ligh)    |

|--------------------|--------------------------|-------|-----------------------|----------|

| $I_{543}, I_{210}$ | Group Function           |       | Group                 | Function |

| 0.0                |                          | A+Q   |                       | A+Q+1    |

| 01                 | ADD                      | A+B   | ADD plus              | A+B+1    |

| 05                 |                          | D+A   | one                   | D+A+1    |

| 06                 |                          | D+Q   |                       | D+Q+1    |

| 02                 |                          | Q     |                       | Q+1      |

| 03                 | PASS                     | В     | Increment             | B+1      |

| 04                 |                          | A     |                       | A+1      |

| 07                 |                          | D     |                       | D+1      |

| 12                 |                          | Q-1   |                       | Q        |

| 13                 | Decrement                | B-1   | Pass                  | B        |

| 14                 |                          | A-1   |                       | A        |

| 27                 |                          | D-1   |                       | D        |

| 22                 |                          | -Q-1  |                       | -Q       |

| 23                 | l's Comp.                | -B-1  | 2's Comp.             | -B       |

| 24                 |                          | -A-1  | (Negate)              | -A       |

| 17                 |                          | -D-1  |                       | -D       |

| 10                 |                          | Q-A-1 |                       | Q-A      |

| 11                 | Subtract                 | B-A-1 | Subtract              | B-A      |

| 15                 | (1's Comp.)              | A-D-1 | (2's Comp.)           | A-D      |

| 16                 |                          | Q-D-1 |                       | Q-D      |

| 20                 |                          | A-Q-1 |                       | A-Q      |

| 21                 |                          | A-B-1 |                       | A-B      |

| 25                 |                          | D-A-I |                       | D-A      |

| 26                 |                          | D-Q-1 |                       | D-Q      |

Table 4-3

ALU Arithmetic Mode Functions

**4.1.2.2** Logical Functions for G, P,  $C_{N+4}$ , and OVR – When the microprocessor is in the add or subtract mode, signals G and P indicate carry lookahead,  $C_{n+4}$  indicates carry, and OVR indicates overflow conditions. However, OVR is not used in the CIS implementation. Table 4-4 gives the logic equations for the G, P and  $C_{n+4}$  signals for each of the eight ALU functions. The R and S inputs are the two inputs selected in accordance with Table 4-4.

#### 4.1.3 Q-Register

The Q-register, a file loaded from the ALU, functions as a temporary storage register. Q-register output can be loaded back into itself, or shifted right or left (e.g., during convert, multiply, divide or arithmetic shift operations).

| I543 | Function                       | Р                                                           | G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | C <sub>8+4</sub>                                                                     | OVR                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|------|--------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

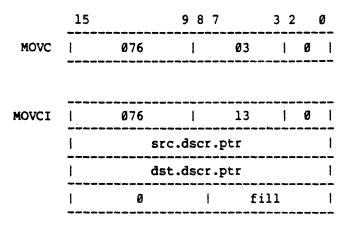

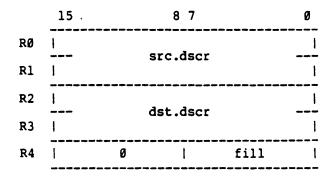

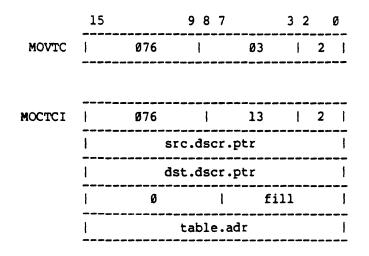

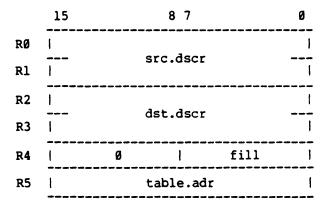

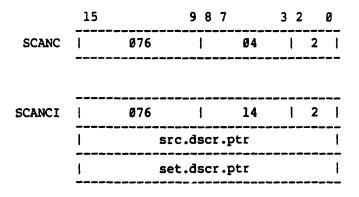

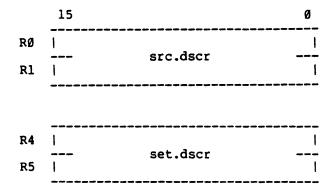

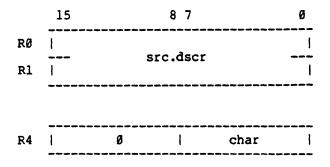

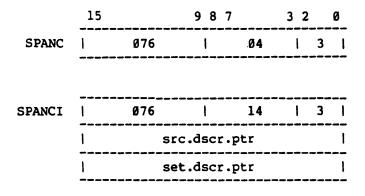

| 0    | R + S                          | $\overline{P_3P_2P_1P_0}$                                   | $\overline{\mathbf{G}_3 + \mathbf{P}_3\mathbf{G}_2 + \mathbf{P}_3\mathbf{P}_2\mathbf{G}_1 + \mathbf{P}_3\mathbf{P}_2\mathbf{P}_1\mathbf{G}_0}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | C <sub>4</sub>                                                                       | $C_3 \neq C_4$                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |