# KXT11-CA Single-Board Computer User's Guide

KXT11-CA Single-Board Computer User's Guide

digital

# KXT11-CA Single-Board Computer User's Guide

Prepared by Educational Services of Digital Equipment Corporation

1st Edition, May, 1984 2nd Edition, September 1984

© Digital Equipment Corporation 1984.

All Rights Reserved.

Printed in U.S.A.

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors that may appear in this manual.

The manuscript for this book was created on a DIGITAL Word Processing System and, via a translation program, was automatically typeset on DIGITAL's DECset Integrated Publishing System. Book production was done by Educational Services Development and Publishing in Marlboro, MA.

The following are trademarks of Digital Equipment Corporation:

| digital™     | MASSBUS      | TOPS-10        |

|--------------|--------------|----------------|

| DEC          | PDP          | TOPS-20        |

| DECmate      | P/OS         | UNIBUS         |

| DECsystem-10 | Professional | VAX            |

| DECSYSTEM-20 | Q-Bus        | VMS            |

| DECUS        | Rainbow      | VT             |

| DECwriter    | RSTS         | Work Processor |

| DIBOL        | RSX          |                |

## **CONTENTS**

## Page

### PREFACE

| CHAPTER 1 | INTRODUCTION                       |       |

|-----------|------------------------------------|-------|

| 1.1       | INTRODUCTION                       | . 1-1 |

| 1.2       | KXT11-CA HARDWARE                  | . 1-1 |

| 1.3       | KXT11-CA FEATURES                  | . 1-4 |

| 1.4       | KXT11-CA OPERATING MODES           | . 1-5 |

| 1.4.1     | Standalone Mode                    | . 1-5 |

| 1.4.2     | Peripheral Processor Mode          | . 1-5 |

| 1.5       | KXT11-CA SPECIFICATIONS            | . 1-5 |

| 1.6       | RELATED DOCUMENTS                  |       |

| CHAPTER 2 | KXT11-CA SBC ARCHITECTURE          |       |

| 2.1       | INTRODUCTION                       | . 2-1 |

| 2.2       | STANDALONE MODE                    |       |

| 2.3       | STANDALONE HARDWARE                | . 2-1 |

| 2.3.1     | Backplane Connections              | . 2-1 |

| 2.3.2     | Power Connections                  |       |

| 2.4       | DMA OPERATIONS                     | . 2-3 |

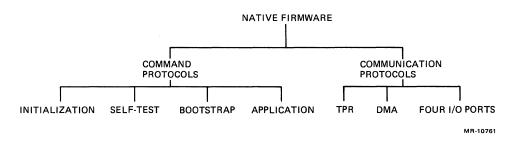

| 2.5       | NATIVE FIRMWARE                    | . 2-3 |

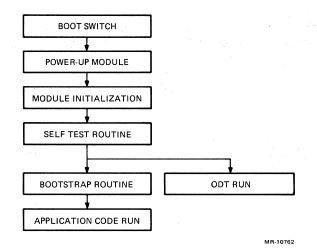

| 2.5.1     | Selftest/Boot Routines             |       |

| 2.5.2     | Start-Up Protocols                 |       |

| 2.5.2.1   | Initialization                     |       |

| 2.5.2.2   | Selftest                           |       |

| 2.5.2.3   | Booting                            | . 2-4 |

| 2.5.3     | Communication Protocols            | . 2-4 |

| 2.5.3.1   | I/O Port Booting                   |       |

| 2.5.3.2   | I/O Port Communications            |       |

| 2.6       | PERIPHERAL PROCESSOR MODE          |       |

| 2.7       | PERIPHERAL PROCESSOR ARBITER       |       |

| 2.8       | PERIPHERAL PROCESSOR/IOP HARDWARE  |       |

| 2.8.1     | Backplane Connections              |       |

| 2.8.2     | Power Connections                  |       |

| 2.9       | NATIVE FIRMWARE                    |       |

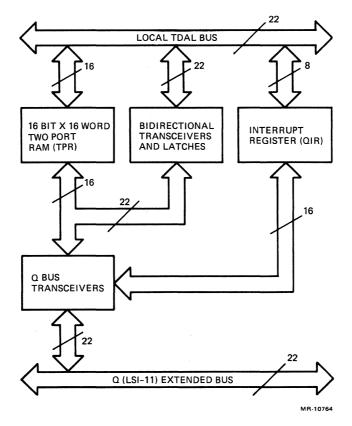

| 2.9.1     | Two-Port RAM (TPR)                 |       |

| 2.9.2     | DMA Operations                     |       |

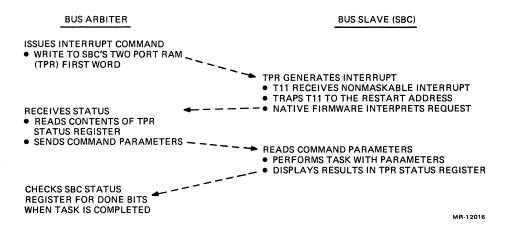

| 2.9.3     | Arbiter to SBC Interrupts          |       |

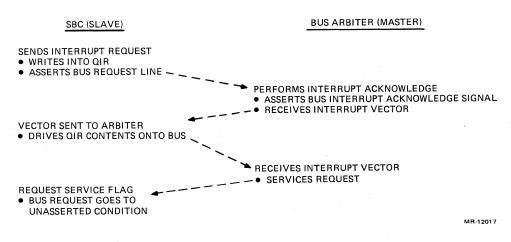

| 2.9.4     | KXT11-CA SBC to Arbiter Interrupts | . 2-8 |

| 2.9.5     | Selftest/Boot Switch                    | 2-8  |

|-----------|-----------------------------------------|------|

| 2.9.6     | Command Protocols                       |      |

| 2.9.6.1   | Start-Up                                |      |

| 2.9.6.2   | Selftest                                |      |

| 2.9.6.3   | Boot                                    |      |

| 2.9.7     | Communication Protocols                 |      |

| 2.9.7.1   | Two-Port RAM (TPR)                      |      |

| 2.9.7.2   | DTC Transfers                           |      |

| 2.9.7.3   | I/O Port Booting                        |      |

| 2.9.7.4   | I/O Port Communication                  | 2-10 |

| CHAPTER 3 | THEORY OF OPERATIONS                    |      |

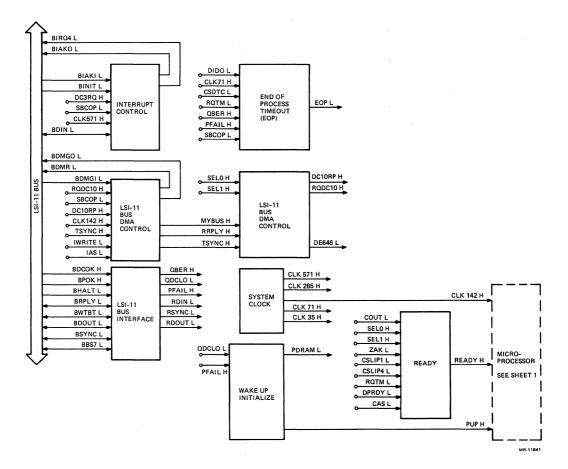

| 3.1       | INTRODUCTION                            | 3-1  |

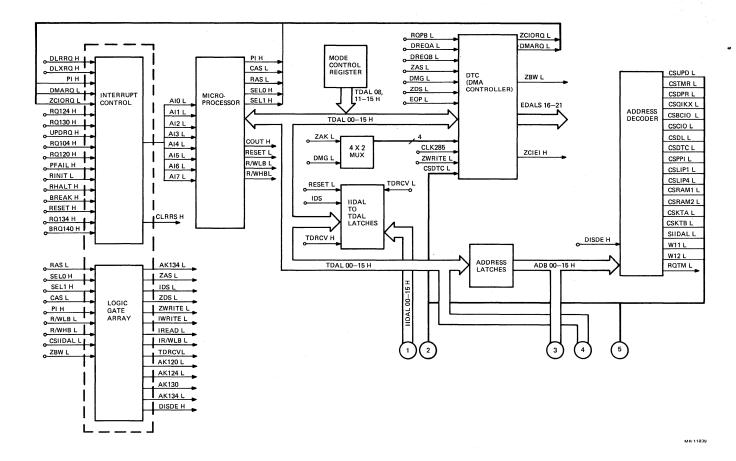

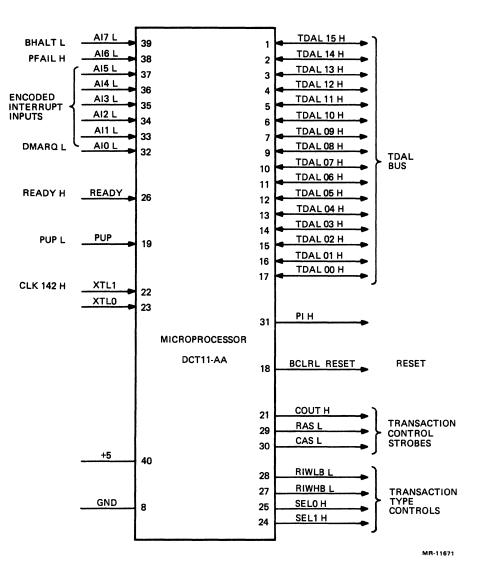

| 3.2       | MICROPROCESSOR                          |      |

| 3.2.1     | Microprocessor Initialization           |      |

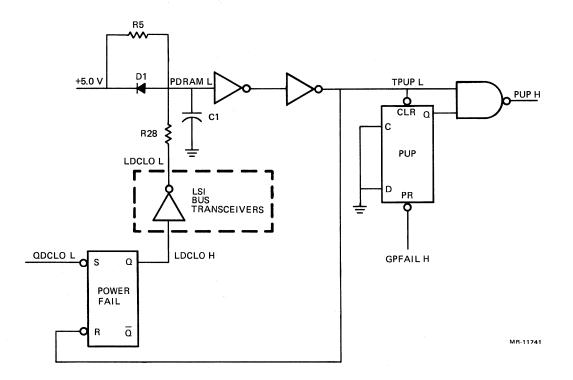

| 3.2.1.1   | Power-Up Input (PUP)                    |      |

| 3.2.1.2   |                                         |      |

| 3.2.2     | Reset Instruction                       |      |

|           | Microprocessor Control Signals.         |      |

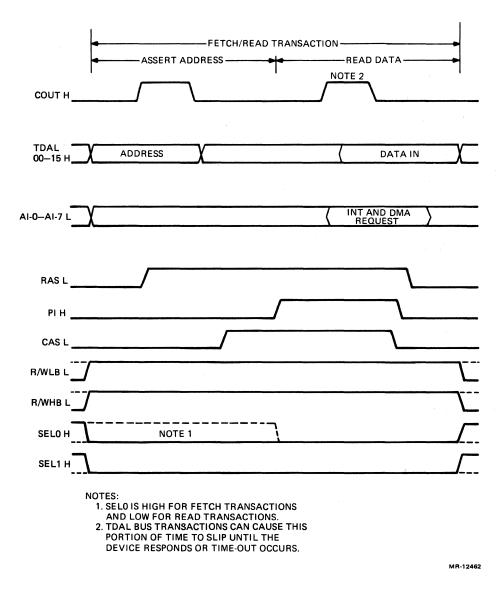

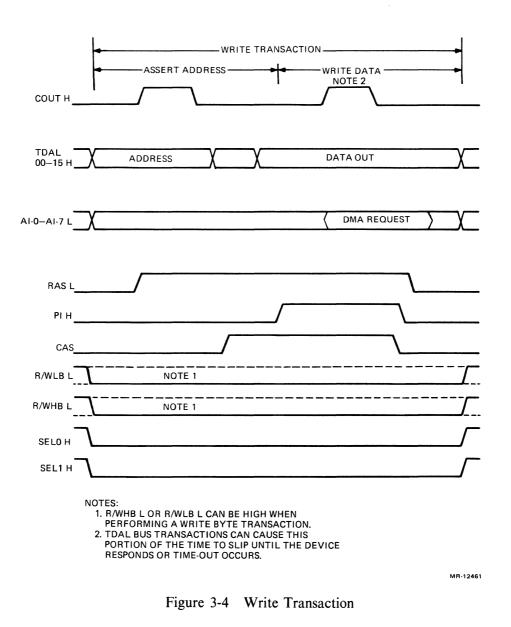

| 3.2.2.1   | ROW Address Strobe (RAS L)              | 3-6  |

| 3.2.2.2   | Column Address Strobe (CAS L)           |      |

| 3.2.2.3   | Priority In (PI H).                     | 3-6  |

| 3.2.2.4   | Read/Write (R/WHB L and R/WLB L)        |      |

| 3.2.2.5   | Select Output Flags (SEL0 H and SEL1 H) |      |

| 3.2.2.6   | Bus Clear (BCLR L).                     |      |

| 3.2.2.7   | Clock Out (COUT H)                      |      |

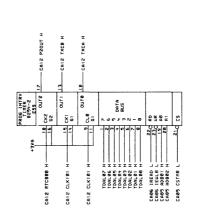

| 3.2.2.8   | CLOCK (CLK 142 H)                       |      |

| 3.2.2.9   | Ready (READY H)                         |      |

| 3.2.3     | Microprocessor Transactions             |      |

| 3.2.3.1   | Fetch/Read                              |      |

| 3.2.3.2   | Write                                   |      |

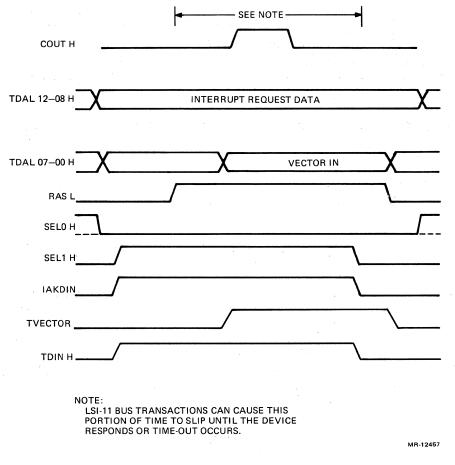

| 3.2.3.3   | IAK/Internal/External                   |      |

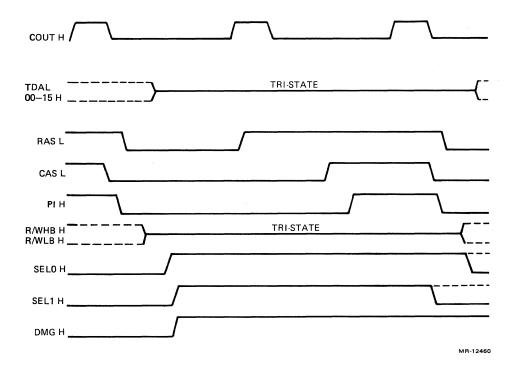

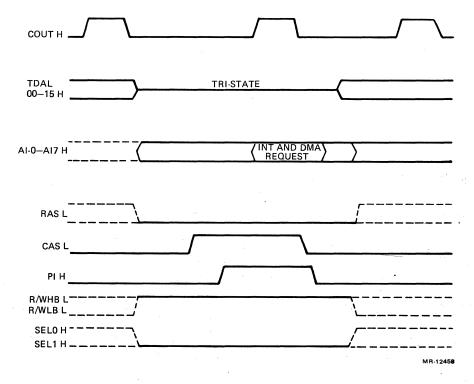

| 3.2.3.4   | DMA                                     |      |

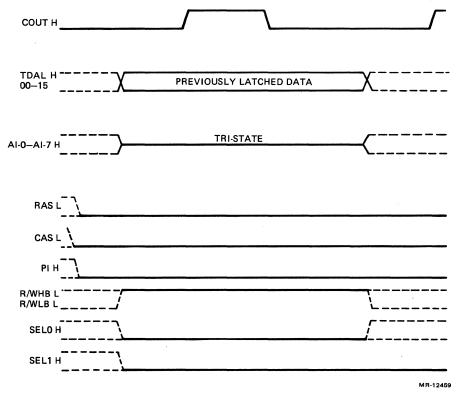

| 3.2.3.5   | ASPI                                    | 3-10 |

| 3.2.3.6   | NOP                                     | 3-12 |

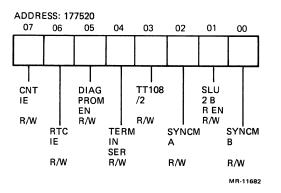

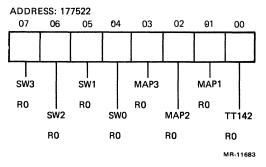

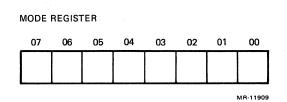

| 3.3       | MODE REGISTER                           |      |

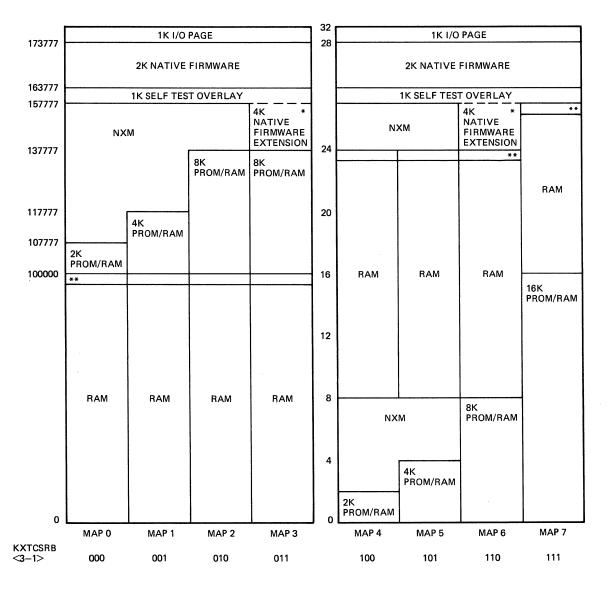

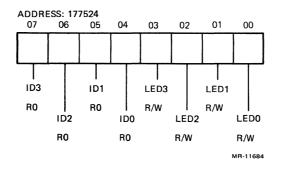

| 3.4       | CONTROL STATUS REGISTERS (KXTCSR)       | 3-13 |

| 3.4.1     | KXTCSR A                                | 3-13 |

| 3.4.2     | KXTCSR B                                | 3-13 |

| 3.4.3     | KXTCSR C                                | 3-13 |

| 3.4.4     | KXTCSR D                                | 3-13 |

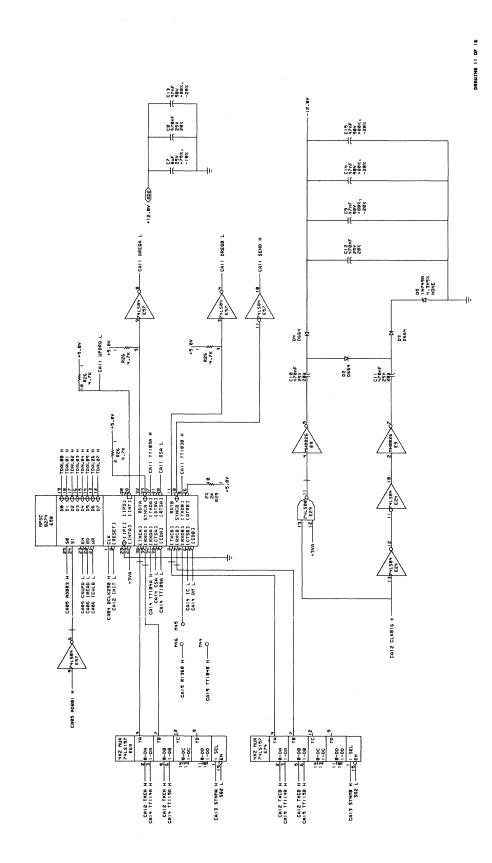

| 3.5       | SYSTEM CLOCKS                           | 3-14 |

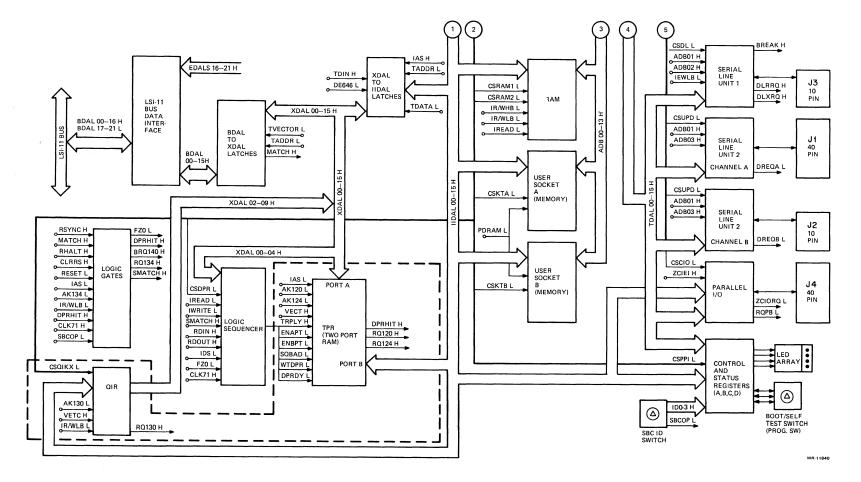

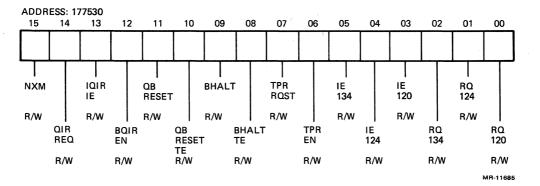

| 3.6       | Q-BUS INTERRUPT PROTOCOL CHIP (DC003)   |      |

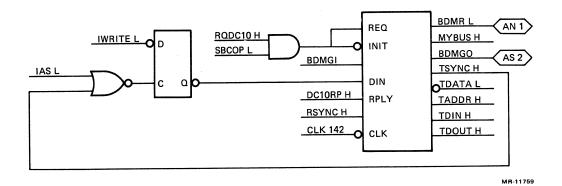

| 3.7       | Q-BUS DMA PROTOCOL CHIP (DC010)         |      |

| 3.8       | Q-BUS INTERFACE GATE ARRAY (DC340)      |      |

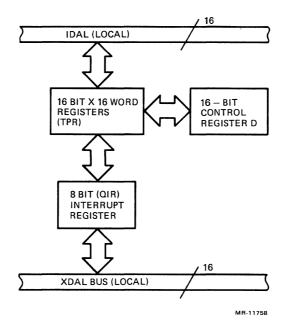

| 3.8.1     | Two-Port RAM (TPR)                      |      |

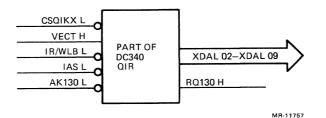

| 3.8.2     | Q-Bus Interrupt Register (QIR)          |      |

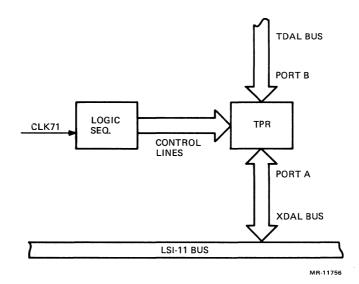

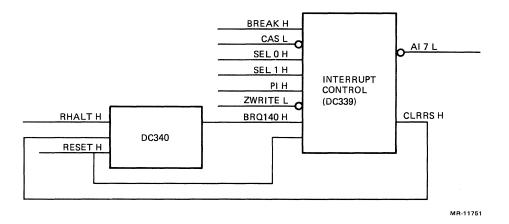

| 3.8.3     | Logic Sequencer                         |      |

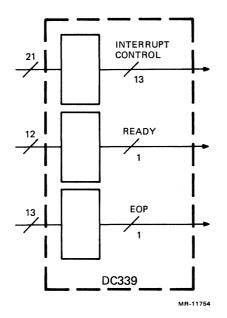

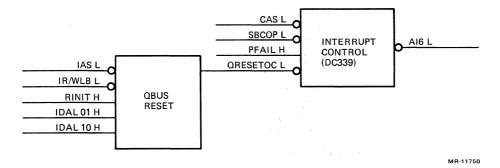

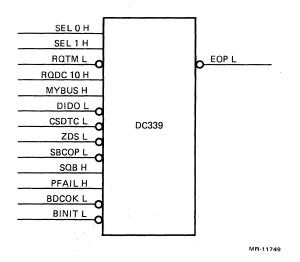

| 3.9       | INTERRUPT CONTROL GATE ARRAY (DC339)    | 3-21 |

## Page

| 3.10      | INTERRUPT CONTROL                    | 3-21  |

|-----------|--------------------------------------|-------|

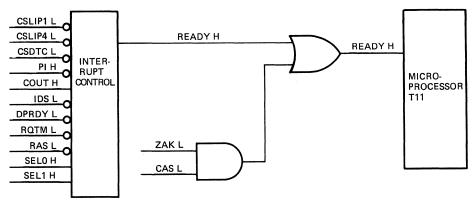

| 3.10.1    | Interrupt Hardware                   | 3-21  |

| 3.10.2    | Ready Logic                          |       |

| 3.10.3    | Restart Interrupts                   |       |

| 3.10.4    | Power-Fail (PFAIL)                   |       |

| 3.10.5    | External Vector Cycle                |       |

| 3.10.6    | Internal Vector Cycle                |       |

|           |                                      |       |

| 3.10.7    | DMA Request/Grant                    |       |

| 3.10.8    | End of Pass (EOP)                    |       |

| 3.11      | ADDRESS LATCH                        |       |

| 3.12      | MEMORY DECODE                        |       |

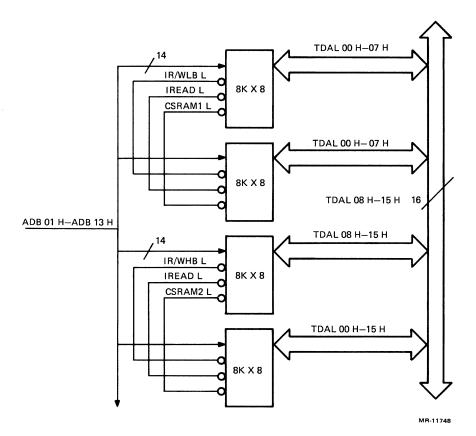

| 3.13      | RAM MEMORY                           | 3-28  |

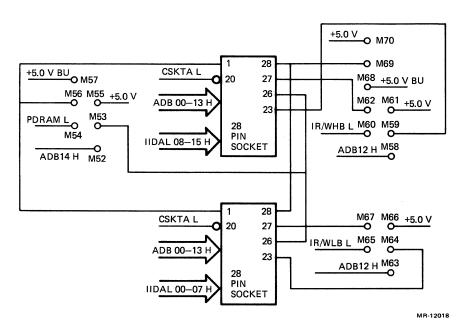

| 3.14      | USER MEMORY SOCKET SITES             | 3-28  |

| 3.15      | NATIVE FIRMWARE SOCKET SITES         |       |

| 3.16      | DTC OPERATONS                        |       |

| 3.16.1    | Flowthrough Transactions             |       |

| 3.16.1.1  | Local Transfers                      |       |

| 3.16.1.2  | Q-Bus Transfers                      |       |

|           |                                      |       |

| 3.16.1.3  | I/O Transfers                        |       |

| 3.16.2    | Exceptions                           |       |

| 3.16.2.1  | Timeout                              |       |

| 3.16.2.2  | SBC Mode                             |       |

| 3.16.2.3  | Power-Fail                           |       |

| 3.16.2.4  | Bus Initiation                       | 3-33  |

| 3.16.2.5  | Bus Halt                             | 3-33  |

| 3.17      | SERIAL I/O UNIT                      | 3-33  |

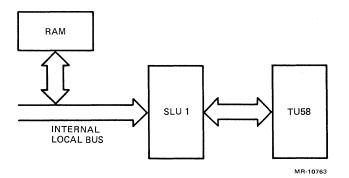

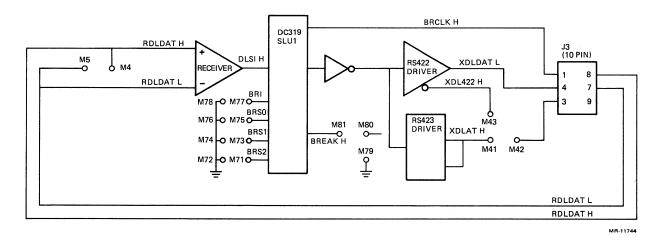

| 3.17.1    | Serial Line Unit 1 (SLU1)            |       |

| 3.17.2    | Serial Line Unit 2 (SLU2)            |       |

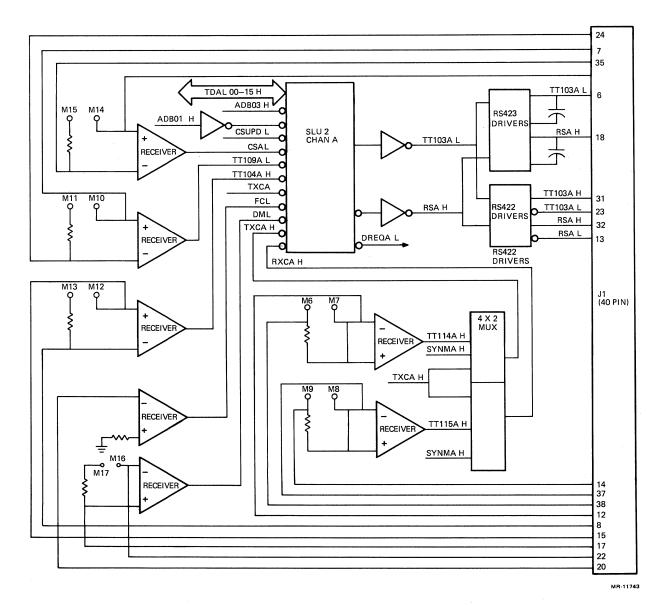

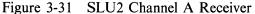

| 3.17.2.1  | Channel A                            |       |

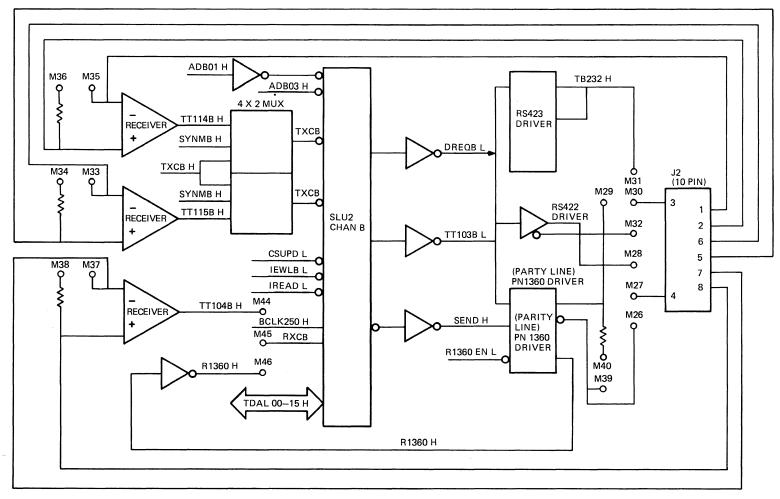

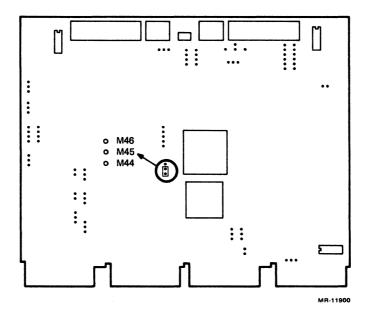

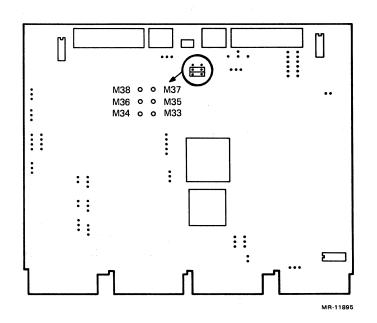

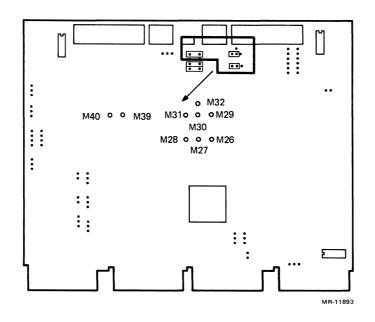

| 3.17.2.2  | Channel B                            |       |

| 3.18      |                                      |       |

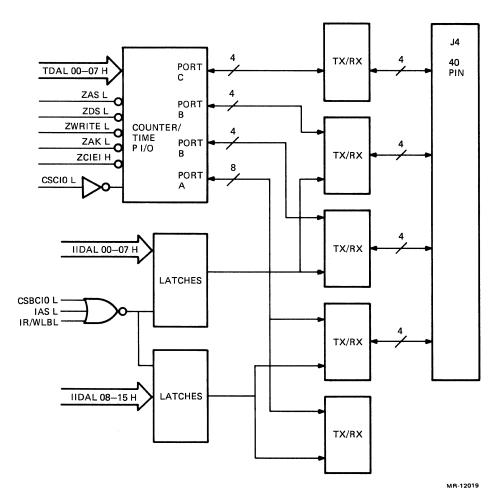

|           | PARALLEL I/O UNIT                    |       |

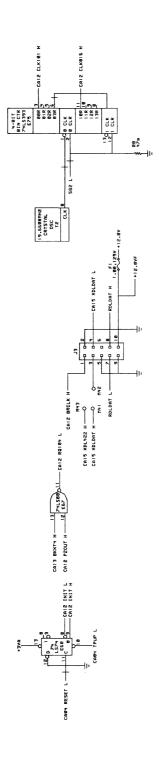

| 3.19      | POWER-UP                             | 3-38  |

|           |                                      |       |

| CHAPTER 4 | NATIVE FIRMWARE                      |       |

| 4.1       | INTRODUCTION                         | . 4-1 |

| 4.2       | NATIVE FIRMWARE                      |       |

| 4.3       | BOOTSTRAP/SELFTEST SEQUENCE          | 4-3   |

| 4.3.1     | SBC Set-Up Routine                   |       |

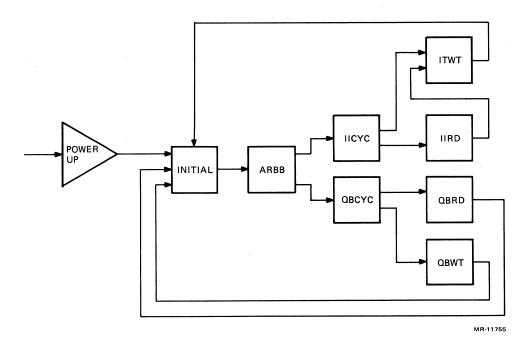

| 4.3.2     | Initialization                       |       |

| 4.3.3     |                                      |       |

|           | Battery Backup                       |       |

| 4.3.4     | Selftests                            |       |

| 4.3.5     | Booting.                             |       |

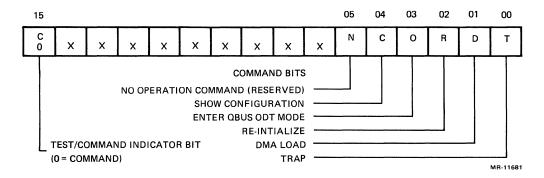

| 4.4       | COMMAND REGISTER                     |       |

| 4.4.1     | Control Commands                     | . 4-5 |

| 4.4.1.1   | Trap Command (Bit 0 Set)             |       |

| 4.4.1.2   | DMA Load Command (Bit 1 Set)         | . 4-6 |

| 4.4.1.3   | Reinitialization Command (Bit 2 Set) |       |

| 4.4.1.4   | Q-Bus ODT Command (Bit 3 Set)        |       |

| 4.4.1.5  | Show Command (Bit 4 Set)                                   | 4-6  |

|----------|------------------------------------------------------------|------|

| 4.4.1.6  | No Operation Command (Bit 5 Set)                           | 4-6  |

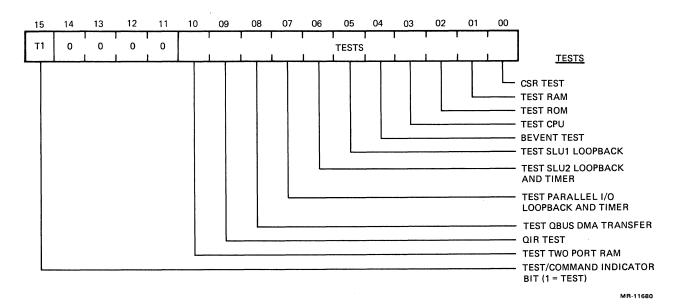

| 4.4.2    | Selftest Commands                                          | 4-6  |

| 4.4.2.1  | CSR Test Command (Bit 0 Set)                               | 4-6  |

| 4.4.2.2  | RAM Test Command (Bit 1 Set)                               |      |

| 4.4.2.3  | ROM Test Command (Bit 2 Set)                               |      |

| 4.4.2.4  | MPU Test Command (Bit 3 Set)                               |      |

| 4.4.2.5  | BEVNT Test Command (Bit 4 Set)                             |      |

| 4.4.2.6  | SLU1 Test Command (Bit 5 Set)                              |      |

| 4.4.2.7  | SLU2 Test Command (Bit 6 Set)                              |      |

| 4.4.2.8  | PIO Test Command (Bit 7 Set)                               |      |

| 4.4.2.9  | DMA Controller Test Command (Bit 8 Set)                    |      |

| 4.4.2.10 | QIR Test Command (Bit 9 Set)                               |      |

| 4.4.2.11 | Two-Port RAM (TPR) Test Command (Bit 10 Set)4-7            |      |

| 4.4.3    |                                                            | 4-7  |

| 4.4.3.1  | Q-Bus ODT Commands<br>Open and Examine Memory Command Code | 4-7  |

| 4.4.3.2  | Open and Examine Register Command Code                     |      |

| 4.4.3.3  | Deposit Command Code                                       |      |

| 4.4.3.4  | Go Command Code                                            |      |

| 4.4.3.5  | Proceed Command Code                                       |      |

| 4.4.3.6  | Exit Mode Command Code                                     | 4-8  |

| 4.5      | SERIAL ODT                                                 | 4-8  |

| 4.5.1    | Autobaud                                                   | 4-9  |

| 4.6      | LED DISPLAY                                                |      |

| 4.7      | MEMORY MAP CONFIGURATION                                   | 4-10 |

| 4.8      | RESTART HANDLING                                           | 4-10 |

| 4.9      | BOOT EXIT                                                  | 4-11 |

|          |                                                            |      |

#### CHAPTER 5 PROGRAMMING INFORMATION

| 5.1     | INTRODUCTION                      |      |

|---------|-----------------------------------|------|

| 5.2     | CONTROL STATUS REGISTERS (KXTCSR) |      |

| 5.2.1   | KXTCSR A Register                 |      |

| 5.2.2   | KXTCSR B Register                 |      |

| 5.2.3   | KXTCSR C Register                 |      |

| 5.2.4   | KXTCSR D Register                 |      |

| 5.3     | Q-BUS INTERRUPT REGISTER (QIR)    |      |

| 5.4     | TWO-PORT RAM (TPR)                |      |

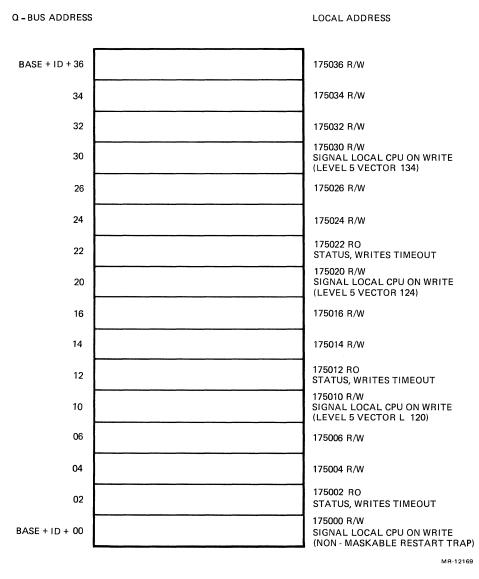

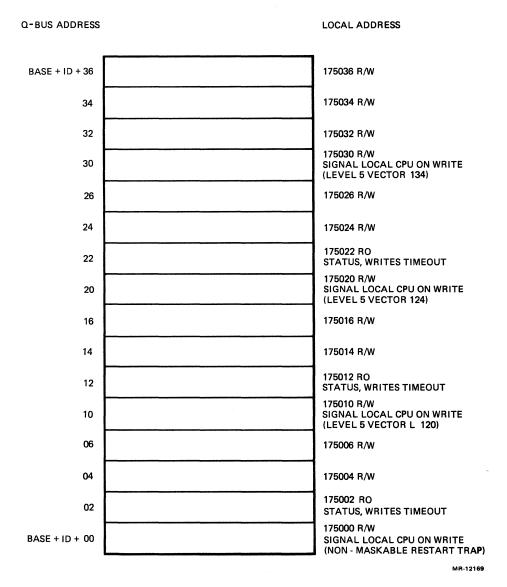

| 5.4.1   | Control Command Register (TPR 0)  | 5-10 |

| 5.4.1.1 | Control Commands                  |      |

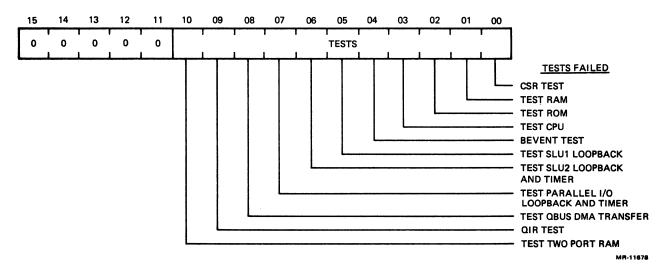

| 5.4.1.2 | Test Commands                     |      |

| 5.4.1.3 | ODT Commands                      |      |

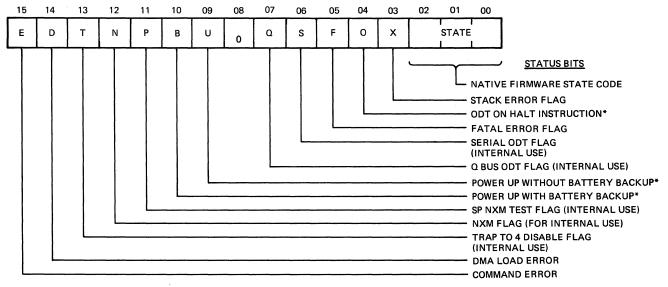

| 5.4.2   | Status Register 1 (TPR 1)         |      |

| 5.4.3   | Control Register 2 (TPR 2)        |      |

| 5.4.4   | Control Register 3 (TPR 3)        |      |

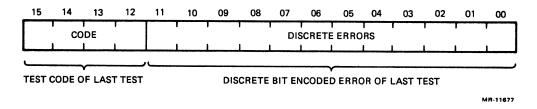

| 5.4.5   | ROM Test Status (Test Code = 03)  |      |

| 5.5     | DMA TRANSACTIONS                  |      |

| 5.5.1   | Master Mode Register (MM)         | 5-22 |

| 5.5.2   | COMMAND Register (CM)             |      |

|         |                                   |      |

## Page

| 5 5 2                                                                                                                                                                                                                                                                       | Chair Control Besister (CC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5.24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.5.3                                                                                                                                                                                                                                                                       | Chain Control Register (CC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.5.4                                                                                                                                                                                                                                                                       | Temporary Register (TMP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.5.5                                                                                                                                                                                                                                                                       | Current Address Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.5.6                                                                                                                                                                                                                                                                       | Special-Purpose Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.6                                                                                                                                                                                                                                                                         | ASYNCHRONOUS SERIAL LINE UNIT (SLU1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.6.1                                                                                                                                                                                                                                                                       | Operating Parameters Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.6.2                                                                                                                                                                                                                                                                       | Console Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.6.3                                                                                                                                                                                                                                                                       | Interrupt Vectors/Priorities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.6.4                                                                                                                                                                                                                                                                       | Address Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

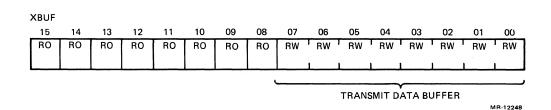

| 5.6.5                                                                                                                                                                                                                                                                       | Register Bit Assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

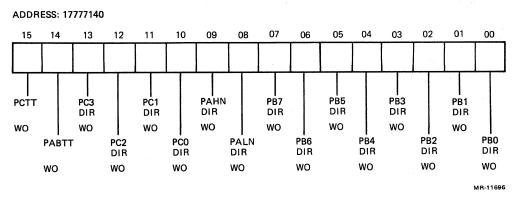

| 5.7                                                                                                                                                                                                                                                                         | PARALLEL I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.7.1                                                                                                                                                                                                                                                                       | Address Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.7.2                                                                                                                                                                                                                                                                       | Interrupt Vectors/Priorities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

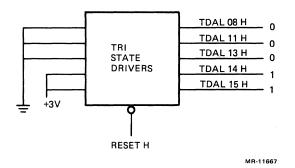

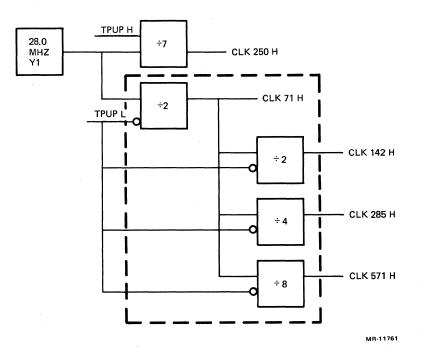

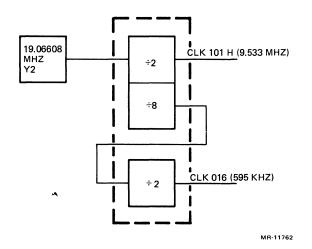

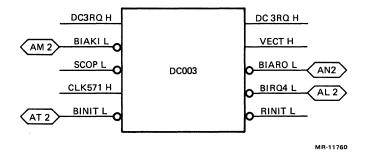

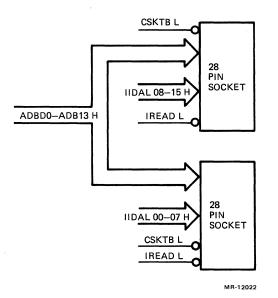

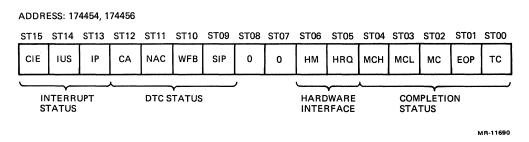

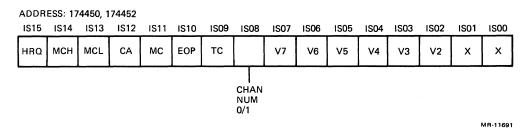

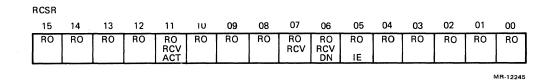

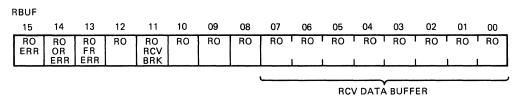

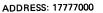

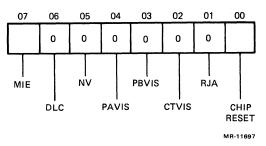

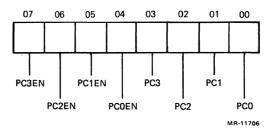

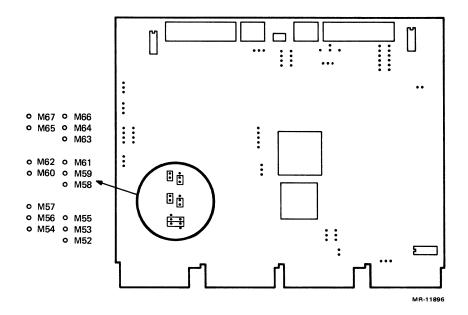

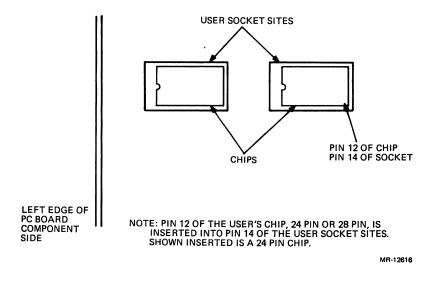

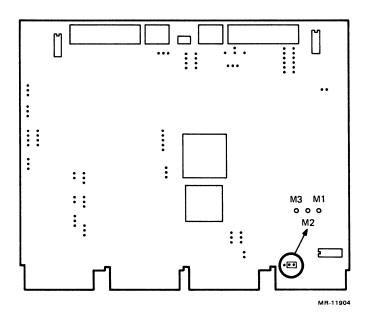

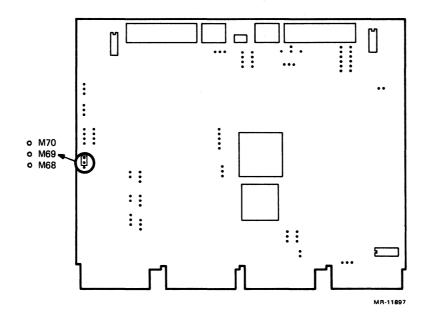

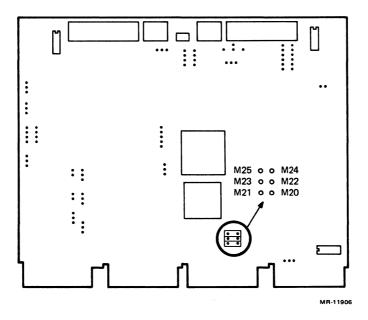

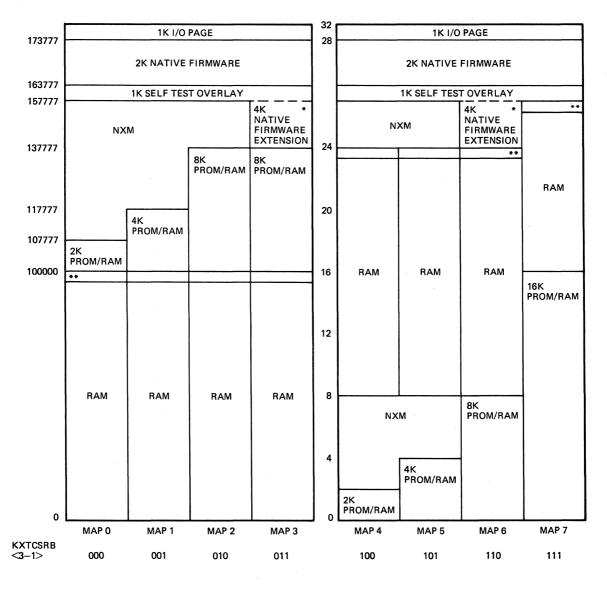

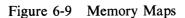

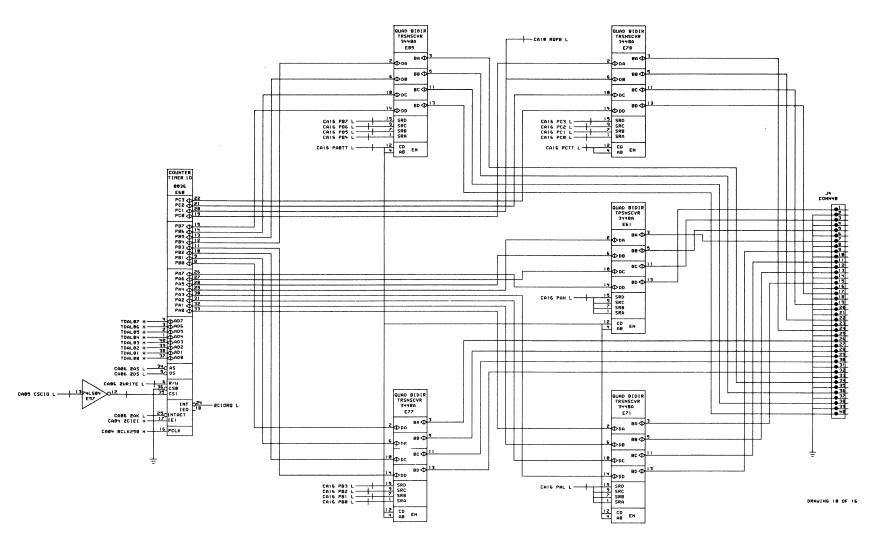

| 5.7.3                                                                                                                                                                                                                                                                       | Buffers and I/O Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |