# MG10 MAINTENANCE MANUAL

digital equipment corporation · maynard. massachusetts

# CHAPTER 1 INTRODUCTION

This chapter contains a general functional description of the MG10 Core Memory. It includes a system level description of the logic, a physical description, and general design specifications.

#### **1.1 GENERAL DESCRIPTION**

The MG10 (Figure 1-1) is a coincident current, ferrite core, 3-D, 3-wire memory, storing up to 131,072 37-bit words (36 data bits plus 1 parity bit), with a cycle time of 1  $\mu$ s. The MG10-A is the basic system and is capable of storing 32K word locations (32,768 actual locations). The MG10-E option is a 32K expansion unit, which, when installed in a basic MG10-A, yields a 64K MG10-G. Two MG10-E options installed in an MG10-G yield a 128K MG10-H. As many as 16 memory units may be physically connected to the memory bus.

#### **1.2 SYSTEM LEVEL DESCRIPTION**

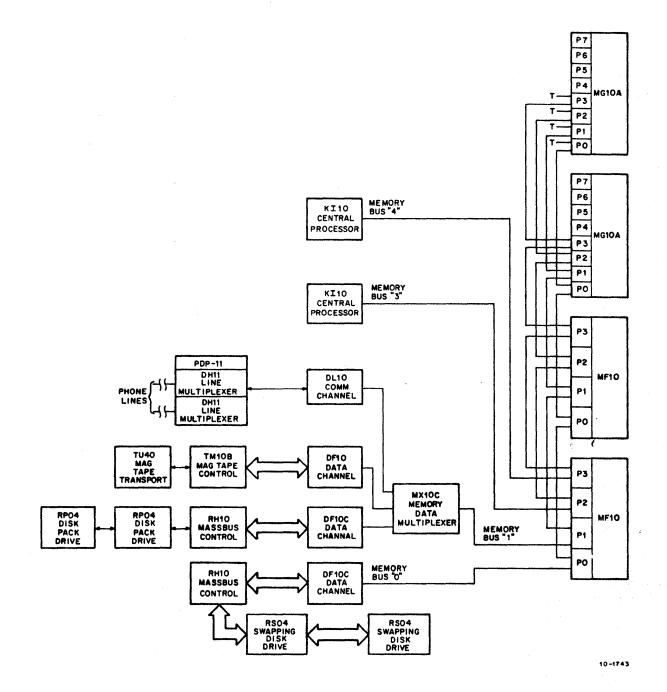

The operation of the MG10 within the DECsystem-10 is asynchronous; that is, access to memory units is governed by a "request/response" system, wherein the processor makes a memory cycle request and waits for a response from a memory unit. Communication between processor and memory unit takes place over the memory bus. Each processor in the system has an associated memory bus which is connected to an active port in each memory unit.

A memory unit may contain up to a maximum of eight access ports; each port is associated with one particular processor, data channel, multiplexor, etc. (Figure 1-2). If an MX10 Memory Data Multiplexor is included in the system, as many as eight DF10 Data Channels may be associated with one memory port. The MG10-G Additional Access Port option provides two additional access ports to MG10 memories that do not utilize all available access ports. Priority logic contained in each memory unit designates the sequence in which the processors are granted access in the event of simultaneous requests.

MG10s are compatible with all DECsystem-10 memories and processors. Two-way interleaving is provided within a single MG10 cabinet, and fourway interleaving is performed between two MG10 cabinets. Each unit, however, must contain equal amounts of storage. Interleaving rotates successive memory cycles between the interleaved memory units if the addressing is sequential. Operation in this mode effectively decreases cycle time, which, in turn, reduces processor idle time.

The MG10 incorporates additional features that allow for smooth degradation of memory performance and ease in checking malfunctions. A select switch is provided for each 32K bank of memory. A deselected bank is logically placed into the highest core in the cabinet, while other previously higher banks are automatically pushed down, so that no hole appears in the address base within a cabinet. Thus, a core stack malfunction results in less core being available, rather than immediately having to power down the cabinet to replace the malfunctioning stack; the latter can be replaced at the next scheduled maintenance time.

7370-11

Figure 1-1 MG10 Core Memory

The MG10 contains data parity checking logic for checking data being read out of memory and being written into memory. If a parity error is detected, the address, data, ACTIVE, RD RQ and WR RQ indicator lights are frozen without affecting regular MG10 operation. If the STOP switch is ON, the particular control with which the error is associated is halted.

#### **1.3 PHYSICAL DESCRIPTION**

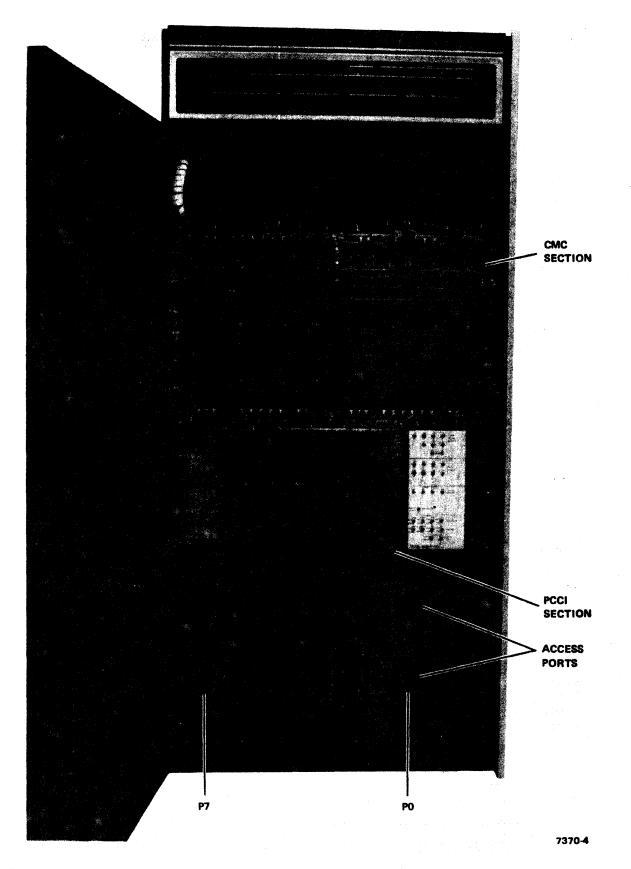

The MG10 is housed in a standard PDP-10 cabinet (Figures 1-1 and 1-4). The major physical differences in the MG10 and earlier DECsystem-10 memories are:

- 1. Higher storage capacity

- 2. Up to eight access ports available

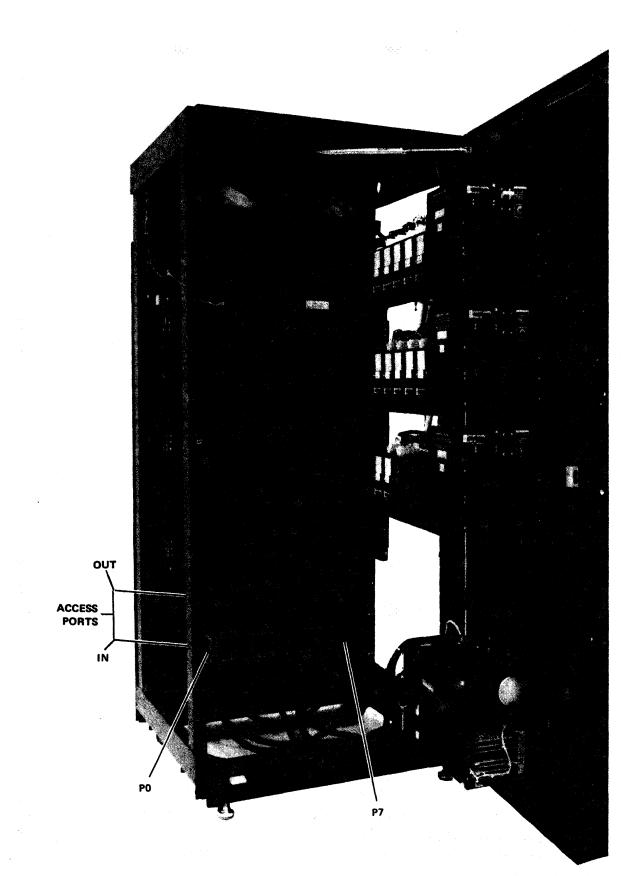

The use of Quick Latch bus connectors provides low maintenance and fast, easy attachment of the bus cable to the eight access ports (P0—P7) located at the lower rear of the logic frame (Figure 1-3). Two physical connectors (in/out) are associated with each port. They are wired in parallel, allowing Pn of one unit to be daisy-chained to the respective Pn of the next unit. These ports are the electrical inputs from the memory bus to the MG10.

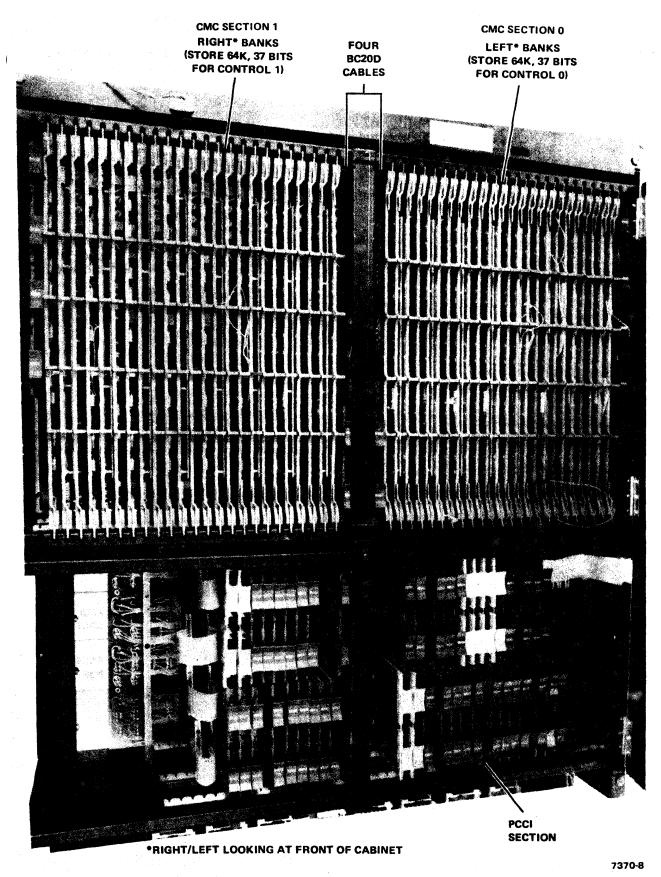

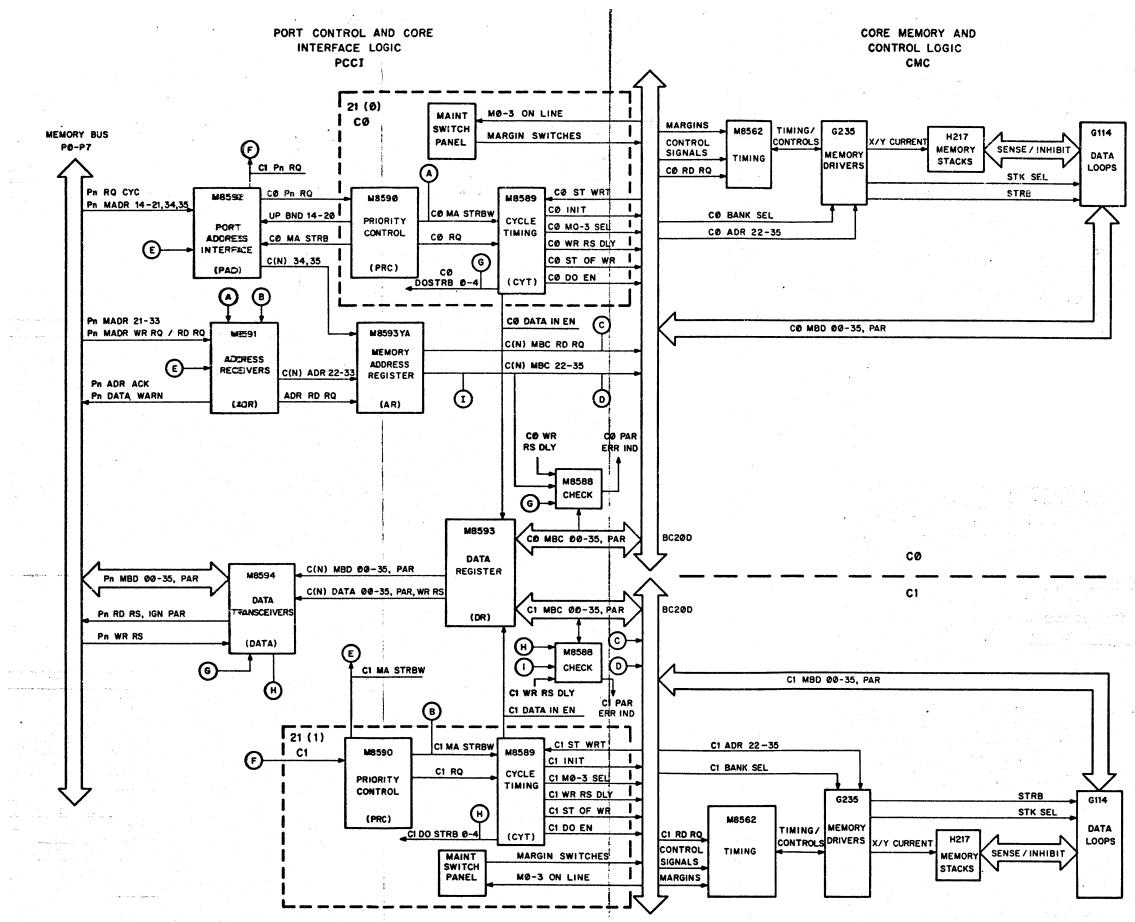

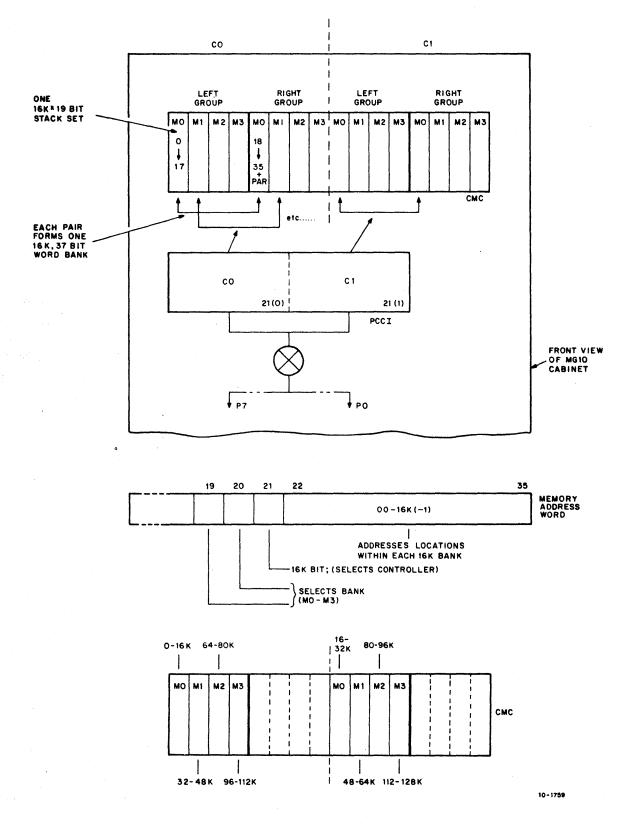

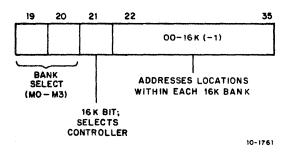

The MG10 is divided into two major logic sections: the Core Memory and Control (CMC) section, and the Port Control and Core Interface (PCCI) section. The CMC section is further subdivided into two separate controllers (C0 and C1), selected by address bits 21 (0) and 21 (1), respectively. The CMC and PCCI sections are connected by four BC20-D cables, as shown in Figure 1-5.

## **1.4 SPECIFICATIONS**

The MG10 Core Memory general specifications are listed in Table 1-1.

Figure 1-2 Typical System Diagram

# Figure 1-3 MG10 Rear View (Access Ports)

# Figure 1-4 MG10 Core Memory, Front View (Door Open)

1-6

| Characteristics           | Specification                                                                                                                                                                                                               |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Requirements        | 208Y/120 Vac +6%, -12%, 60 Hz ± 1 Hz                                                                                                                                                                                        |

| •                         | 380Y/220 Vac +6%, -12%, 50 Hz ± 1 Hz                                                                                                                                                                                        |

|                           | 416Y/240 Vac +6%, -12%, 50 Hz ± 1 Hz                                                                                                                                                                                        |

| Line Current, 60 Hz       | 18 A; 160 A inrush for one cycle                                                                                                                                                                                            |

| Line Current, 50 Hz       | 9 A; 80 A inrush for one cycle                                                                                                                                                                                              |

| Power Dissipation         | 2070 W                                                                                                                                                                                                                      |

| Internal Logic Potentials |                                                                                                                                                                                                                             |

| Positive Logic            | 0 V to +3 V                                                                                                                                                                                                                 |

| Negative Logic            | -3 V to 0 V                                                                                                                                                                                                                 |

| Stack Voltage             | +20 V and -5 V                                                                                                                                                                                                              |

| Power Interrupt           | Up to 20 ms with no effect on operation.                                                                                                                                                                                    |

|                           | No loss of stored data at power ON/OFF.                                                                                                                                                                                     |

| Cycle Time                | 1000 ns                                                                                                                                                                                                                     |

| Read Access Time          | 670 ns maximum, excluding cable delay                                                                                                                                                                                       |

| Address Acknowledge Time  | 230 ns maximum, excluding cable delay                                                                                                                                                                                       |

| Word Length               | 36 bits plus parity bit                                                                                                                                                                                                     |

| Memory Size               |                                                                                                                                                                                                                             |

| MG10-A                    | 32,768 words                                                                                                                                                                                                                |

| MG10-G                    | 65,536 words                                                                                                                                                                                                                |

| MG10-H                    | 131,072 words                                                                                                                                                                                                               |

| MG10-E                    | 32,768 words, expansion from MG10-A to MG10-G. A minimum of two MG10-E options is required to expand an MG10-G to an MG10-H.                                                                                                |

| Access Ports              | 8 maximum; simultaneous access by any two ports to each memory half.<br>The MG10-G Additional Access Port option provides two additional access<br>ports to MG10-G memories that do not utilize all available access ports. |

| Interleaving              | 2-way within one cabinet                                                                                                                                                                                                    |

|                           | 4-way between two cabinets                                                                                                                                                                                                  |

| Dimensions                |                                                                                                                                                                                                                             |

| Height                    | 72 in. (1.83 m)                                                                                                                                                                                                             |

| Width                     | 33 in. (0.84 m)                                                                                                                                                                                                             |

| Depth                     | 30 in. (0.76 m)                                                                                                                                                                                                             |

| Weight                    | 900 lb (409 kg)                                                                                                                                                                                                             |

Table 1-1 Specifications

| Characteristic        | Specification                |  |  |  |  |

|-----------------------|------------------------------|--|--|--|--|

| Operating Temperature | 60° to 95° F<br>15° to 35° C |  |  |  |  |

| Storage Temperature   | 40° to 110° F<br>5° to 45° C |  |  |  |  |

| Relative Humidity     | 20% to 80%                   |  |  |  |  |

| Heat Dissipation      | 7100 Btu/hr (1800 kg-cal/hr) |  |  |  |  |

.

# Table 1-1 (Cont) Specifications

# CHAPTER 2 INSTALLATION

#### **2.1 SCOPE**

This chapter, used with the PDP-10 Site Preparation Guide and the Engineering Drawings provided with each unit, contains the information required for MG10 installation.

#### **2.2 SITE PREPARATION**

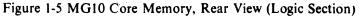

No special site requirements exist, other than those dictated by environmental conditions (Table 1-1) and service clearances (Figure 2-1). Subflooring is not normally required. The units are free standing; up to four units may be bolted together. The memory unit installed closest to the CPU should not be separated from it by more than 3 feet\* (0.914 m) less than 1/4 inch (0.635 cm).

### **2.3 INSTALLATION PROCEDURE**

After removing the equipment packing material, visually inspect the exterior and interior of the equipment: inspect external surfaces for surface, bezel, switch, and light damage, caved-in doors or other signs of the equipment being damaged. Internally inspect the cabinet for any obvious cable damage, loose or broken modules, fan damage, and loose nuts, bolts or screws: inspect external surfaces for surface, bezel, switch, and light damage, caved-in doors or other signs of the equipment being damaged. Internally inspect the cabinet for any obvious cable damage, loose or broken modules, fan damage, and loose nuts, bolts or screws. Ensure that all modules are properly seated.

<sup>\*</sup>Speedy, the processor timing program, is written for the standard 10-foot memory bus cable connection between the CPU and the first memory unit. If lengths in excess of 10 feet are used, Speedy timing printouts will not agree with the timing specification.

#### 2.3.1 Cabling

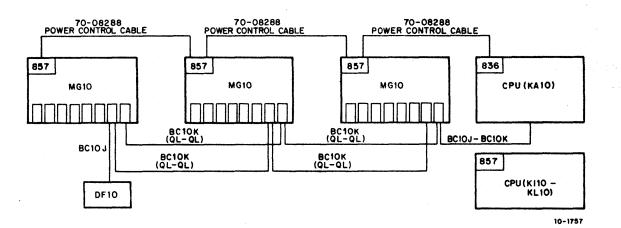

All cables enter or leave the memory unit through an access cutout at the bottom of the cabinet. Figure 2-2 illustrates a system configuration with cabling data.

2.3.1.1 Memory Bus — One memory bus cable is required to connect the unit to a processor or to another memory unit if more than one unit is included in the system. Two memory bus cables are included for each MG10-G Access Port option (all access ports are optional), with a maximum of eight ports per unit. The maximum allowable physical length of the memory bus is 100 feet, including wire-runs through each memory unit. The memory bus must be terminated in the last memory unit in the system using one H866 type terminator per access port.

#### CAUTION

Do not force connection when installing memory bus cable with Quick Latch cable connector.

2.3.1.2 AC Power — Each 60 Hz MG10 unit is furnished with a 3-wire ac power cable with the Hubbell 2611 Twist-Lok<sup>™</sup> plug to be mated with a Hubbell 2610 receptacle. For 50 Hz users, a Hubbell 2321 Twist-Lok plug is mated with a Hubbell 2320 receptacle. Ensure that the power supplies are jumpered for the appropriate line voltage (115 or 230 Vac). Appropriate jumper configurations are shown on the power supply label.

W Twist-Lok is a trademark of Harvey Hubbell, Inc.

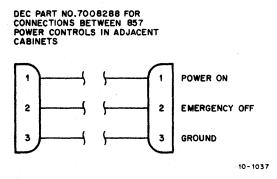

2.3.1.3 Power Control — The 857 Power Controls in all cabinets must be interconnected to enable central control of power ON/OFF from the PDP-10 console power switch. Three Mate-N-Lok connectors on each 857 Power Control are used for interconnection via a 3-wire bus (Figure 2-3). One 3wire bus cable is supplied with each cabinet to connect the 857 Power Control to the 857 Power Control in the next cabinet. Because each power control must connect to the power controls in the preceding and following cabinets, two Mate-N-Lok connectors are reserved for the intercabinet bus. A third connector is provided for connection to the cabinet-mounted thermal switches and to the PDP-10 console power switch.

If remote control is desired, ensure that the RE-MOTE/LOCAL toggle switch on the 857 Power Control is in the REMOTE position before operating the MG10 on-line with the processor. Also ensure that the ac line voltage select switch on the 857 Power Control selects the proper ac line voltage level (115 Vac or 240 Vac position).

2.3.1.4 Ground Mesh Cable — Connect a No. 4 gauge wire from the copper bolt on the bottom of the MG10 cabinet to the adjacent cabinet(s).

#### 2.3.2 Memory Address Switch Settings

The MG10 port address must be established prior to memory operation. The port address is established via the Lower Boundary Address toggle switches located on the memory maintenance panel.

Table 2-1 lists the address switch settings for a typical system having eight 32K MG10-A memories connected to one KA10, KI10 or the KL10 processor memory buses.

#### NOTE

### If the KA10 processor is used, only eight 32K MG10-A memories can be connected to the memory bus.

Note that KA10 based memory systems are limited in size. If a KA10 processor is used, the number of 32K MG10 memories connected to its bus must not exceed eight. This limitation is dictated by the memory addressing capability of the KA10 (256K word locations). The three-position port selection switch, relative to the KA10 in the system, is placed in the "KA" position. This causes the KA10 to ignore memory address bits 14-17. When 128K MG10-H memories are connected to the memory bus, a maximum of two memories can be connected to a KA10 processor memory bus due to the KA10 memory size limitation. Table 2-2 lists the address switch settings for a switch having eight 128K MG10-H memories connected to a K110 memory bus.

MG10 memories connected to a KA10 memory bus must have consecutive addresses. For example, if only five 32K MG10-A memories are connected to a KA10 memory bus, they must be addressed 0 through 4. If this addressing is not followed, holes are created in the memory address space and the KA10 attempts to address memory that does not exist.

When 64K MG10-G memories are connected to the memory bus, the Lower Bound Address toggle switches are set differently. Only four MG10-G memories can be connected to the KA10 processor memory bus due to the KA10 memory size limitation. Only switches 14 through 19 (instead of 14 through 20) are used. Again, the port switch relative to the KA10 processor is placed in the center (KA) of three positions, which, in effect, results in ignoring bits 14—17. Table 2-3 lists the address switch settings for a typical system having four 64K MG10-G memories connected to one KA10 memory bus or eight MG10-G memories connected to K110 or KL10 memory buses.

#### NOTE

If the KA10 processor is used, only eight 32K MG10-A memories can be connected to the memory bus.

| Memory Addresses | MG10-A | M  | lemory A | ddress (I | .ower Bo | und) Swi | tch Settir | ıgs |

|------------------|--------|----|----------|-----------|----------|----------|------------|-----|

|                  | No.    | 14 | 15       | 16        | 17       | 18       | 19         | 20  |

| 000000077777     | 0      | 0  | 0        | 0         | 0        | 0        | 0          | 0   |

| 100000-177777    | 1      | 0  | 0        | 0         | 0        | 0        | 0          | 1   |

| 200000-277777    | 2      | 0  | 0        | 0         | 0        | 0        | 1          | 0   |

| 300000-377777    | 3      | 0  | 0        | 0         | 0        | 0        | 1          | 1   |

| 400000-477777    | 4      | 0  | 0        | 0         | 0        | 1        | 0          | 0   |

| 500000-577777    | 5      | 0  | 0        | 0         | 0        | 1        | 0          | 1   |

| 600000677777     | 6      | 0  | 0        | 0         | 0        | 1        | 1          | 0   |

| 700000-777777    | 7      | 0  | 0        | 0         | 0        | 1        | 1          | 1   |

Table 2-1

MG10 (32K) Memory Address (Lower Bound) Switch Settings

| Table 2-2                     |

|-------------------------------|

| MG10-H (128K) Memory Address  |

| (Lower Bound) Switch Settings |

| Memory Address  | MG10-H | Memory Ad | ldress (L | ower Bou | nd) Swit | ch Settings |

|-----------------|--------|-----------|-----------|----------|----------|-------------|

|                 | No.    | 14        | 15        | 16       | 17       | 18          |

| 000000-377777   | 0      | 0         | 0         | 0        | 0        | 0 .         |

| 400000-777777   | 1      | 0         | 0         | 0        | 0        | 1           |

| 10000001377777  | 2      | 0         | 0         | 0        | 1        | 0           |

| 1400000-1777777 | 3      | 0         | 0         | 0        | 1        | 1           |

| 200000-2377777  | 4      | 0         | 0         | 1        | 0        | 0           |

| 2400000-2777777 | 5      | 0         | 0         | 1        | 0        | 1           |

| 300000-3377777  | 6      | 0         | 0         | 1        | 1        | 0           |

| 34000003777777  | 7      | 0         | 0         | 1        | 1        | 1           |

Table 2-3 MG10-G (64K) Memory Address (Lower Bound) Switch Settings

| Memory Addresses | MG10-G | Mem | ory Addr | ess (Low | er Bound | ) Switch | Settings |

|------------------|--------|-----|----------|----------|----------|----------|----------|

|                  | No.    | 14  | 15       | 16       | 17       | 18       | 19       |

| 000000-177777    | 0      | 0   | 0        | 0        | 0        | 0        | 0        |

| 200000-377777    | 1      | 0   | 0        | 0        | 0        | 0        | - 1      |

| 400000-577777    | 2      | 0   | 0        | 0        | 0        | 1        | 0        |

| 600000-777777    | 3      | 0   | 0        | 0        | 0        | 1 1      | 1        |

| 1000000-1177777  | 4      | 0   | 0        | 0        | 1        | 0        | 0        |

| 1200000-1377777  | 5      | 0   | 0        | 0        | 1        | 0        | 1        |

| 1400000-1577777  | 6      | 0   | 0        | 0        | 1        | 1        | 0        |

| 1600000-1777777  | 7      | 0   | 0        | 0        | 1        | 1        | 1        |

#### 2.3.3 Interleave Switch Settings

Interleaving MG10 memories is controlled by two toggle switches located on the memory maintenance panel. These switches are used to select normal (non-interleaved) operation, 2-way interleaved operation, and 4-way interleaved operation. Table 2-4 lists switch settings for the various interleaved situations.

#### NOTE

Only memory units with the same number of memory locations can be interleaved; i.e., a 32K memory cannot be interleaved with a 64K memory (Paragraph 4.3.3).

In 2-way interleaving, address bit MADR 35 is swapped with address bit MADR 21. The result is that all even addresses are accessed through Control 0 (C0) and all odd addresses are accessed through Control 1 (C1).

In 4-way interleaving, in addition to swapping MADR 35 for 21, MADR 34 is swapped with either MADR 20, 19, or 18 depending on the memory size in each cabinet. The result is that four consecutive words are obtainable from the four controls in the two cabinets.

| Mode   | Interleave Switches |      |  |  |

|--------|---------------------|------|--|--|

|        | 34                  | 35   |  |  |

| Normal | NORM                | NORM |  |  |

| 2-way  | NORM                | INTL |  |  |

| 4-way  | INTL                | INTL |  |  |

Table 2-4

Interleave Switch Settings

### 2.3.4 Port Selection Switch Settings and Priority

Eight three-position selection switches (P0-P7) are located on the maintenance panel. In the down position of a given switch, access to the memory by the port associated with that switch is denied. The middle position is used for accessing the MG10 from KA type processors only (address bits 14-17 are ignored). The up position is used for accessing the MG10 from KI or KL type processors.

In case of multiple simultaneous requests from all eight ports, the following priority scheme is used:

| Port             | Priority                                       | Associated<br>Devices                               |

|------------------|------------------------------------------------|-----------------------------------------------------|

| ( <sup>0</sup> ) | Highest; alternates<br>between P0 and P1       | Disks, drums,<br>and other<br>high-speed<br>devices |

| ( <sup>2</sup> ) | Second; alternates<br>between P2 and P3        |                                                     |

| 4<br>5<br>6<br>7 | Lowest; rotates<br>among P4, P5,<br>P6, and P7 | CPUs; e.g.,<br>KI or KL                             |

If two or more requests are received simultaneously by the MG10, the priority network enables the port that has the highest priority. For example, second priority is shared between ports P2 and P3, such that if P2 were serviced last in the previous memory cycles, then P3 would be given priority over P2, should simultaneous requests occur on those ports. Likewise, the highest priority is shared between ports P0 and P1.

The rotating scheme works differently. Priority goes downward from P4 to P7. For example, if P5 was the last serviced port, for subsequent simultaneous requests to those ports, priority would pass to P6, etc. After P7, the priority "rotates" back to P4.

#### 2.3.5 Memory Bank Switch Settings

Automatic selection and deselection of memory banks is provided by the four Memory Bank switches located on the maintenance panel; each BANK switch controls 32K of memory. A detailed description of the Memory Bank Selection logic is given in Paragraph 4.4.4.4.1. Table 2-5 lists the Memory Bank sizing.

Table 2-5 Memory Bank Selection Decoding

| M  | Memory Bank Switches* |    |    | Memory Size |

|----|-----------------------|----|----|-------------|

| MO | M1                    | M2 | M3 |             |

| 1  | 0                     | 0  | 0  | 32K         |

| 1  | 1                     | 0  | 0  | 64K         |

| 1  | 1                     | 1  | 1  | 128K        |

\*1 - Indicates switch in ON-LINE position.

0 - Indicates switch in OFF-LINE position.

# CHAPTER 3 OPERATION

#### 3.1 INTRODUCTION

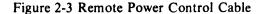

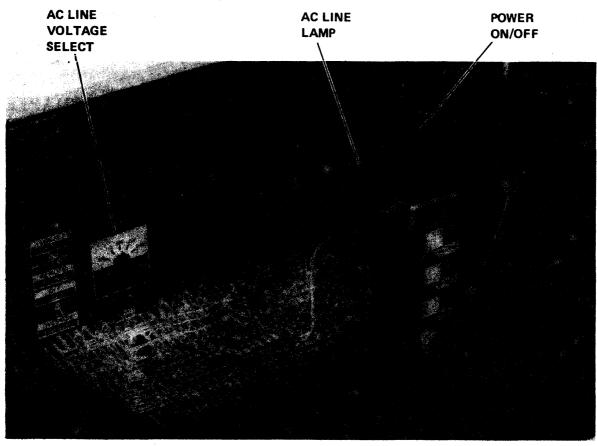

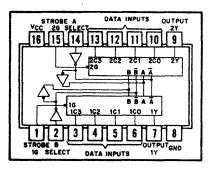

The MG10 controls and indicators are grouped on three separate panels: the maintenance panel, the indicator panel, and the 857 Power Control panel. The following paragraphs state the purpose of each panel and describe each control and indicator. Figure 3-1 shows the MG10 Maintenance Switch Panel. The 857 Power Control (Figure 3-2) is mounted on the rear cabinet door.

## **3.2 PANEL OPERATION**

Generally, the panels can be described as follows:

- 1. The 857 Power Control panel controls input power to the MG10.

- 2. The maintenance panel controls port addressing, port selection, sizing, and troubleshooting hardware.

- 3. The indicator panel provides fault detection and status indicators.

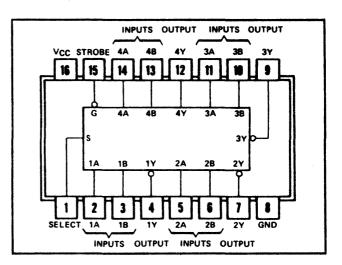

### 3.2.1 857 Power Control Panel

The 857 Power Control Panel (Figure 3-2) performs the following functions:

- 1. Adapts the MG10 to different ac line voltage inputs.

- 2. Enables central control of power turn ON/OFF from the PDP-10 console power switch.

- 3. Initiates power shut-down if any of the memory logic door interlocks or the air flow sense switches are activated (Para-graph 4.4.5.1.4).

- 4. Enables memory logic door interlocks and air flow sense switch to be overridden for maintenance purposes.

- 5. Provides circuit breaker protection against overloading.

7370-13

Figure 3-1 MG10 Maintenance Switch Panel

6619-1

Figure 3-2 857 Power Control Panel

Tables 3-1 and 3-2 describe the 857 Power Control panel switches and indicators.

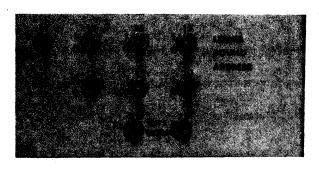

#### 3.2.2 Memory Address Switches

The memory address switches are located in the top section of the maintenance panel (Figure 3-3) and are labeled LOWER BOUND ADDRESS. These lower bound address switches establish the lowest address in the cabinet.

Also located on the memory address switch panel are the two interleave switches. Refer to Paragraph 2.3.3 for a complete explanation of their operation.

Table 3-3 summarizes the memory address switch panel switches.

#### 3.2.3 Maintenance Panel

The entire maintenance panel was shown in Figure 3-1. The sections of the panel previously discussed (i.e., memory address, port selection, and memory banks) comprise the three uppermost sections of the panel. The lowest section (Figure 3-4) contains the switches related strictly to maintenance. The top two rows of switches on this section are identical, except each row relates to a different controller (0 and 1).

Table 3-4 lists the maintenance panel section switch definitions. Definitions for the top two rows of switches are not duplicated, as the functions are identical except for the control section referenced.

|       | Table 3-1               |

|-------|-------------------------|

| Power | <b>Control Switches</b> |

| Switch                 | Function                                                                      |

|------------------------|-------------------------------------------------------------------------------|

| LOCAL/OFF/REMOTE       | Allows power turn ON/OFF from the CPU (REMOTE) or from the MG10 unit (LOCAL). |

| OVERRIDE               | Overrides the temperature sense switches and door interlock switches.         |

| AC SELECT LINE VOLTAGE | This switch is set for the ac line voltage that is supplied.                  |

| POWER ON/OFF           | This is the ac input line voltage circuit breaker.                            |

|               | Power Control Indicators                                                                                                              |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Indicator     | Function                                                                                                                              |

| PWR SW ON     | Lights when ac power is applied to all power supplies in the memory unit. A flash-<br>ing light means that the OVERRIDE switch is on. |

| DOORS OPEN    | Lights when either or both of the logic cabinet doors are open.                                                                       |

| CKT BRK TRP'D | Not used.                                                                                                                             |

| OVERTEMP      | Lights when an over-temperature condition exists.                                                                                     |

| AC LINE LAMP  | Lights when ac line voltage is present.                                                                                               |

Table 3-2

|        | Table 3-3                   |  |

|--------|-----------------------------|--|

| Memory | <b>Address Switch Panel</b> |  |

| Switch              | Function                                                                                                                                                                                       | Engineering Drawing No. |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|

| MADR 14-20*         | Two-position toggle switches which are set to<br>establish the lower bound address of the memory<br>unit, allowing memory address bits 14-20 to<br>select a particular unit (Paragraph 2.3.2). | M8592-0-PAD0<br>-PAD1   |  |

| INTL/NORM* (34, 35) | Two-position toggle switches which select 2- or<br>4-way interleave, or normal mode operation.<br>(See Table 2-4 for interleave switch settings).                                              | M8592-0-PAD0<br>-PAD1   |  |

\*All ports reflect this address.

| Switch       | Position | Function                                                                                                                                                                                                  |

|--------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STRB         | MAR      | Varies the internal strobe timing pulse ±7 ns, to check for marginal memory bank conditions reflected in marginal core switching speeds.                                                                  |

|              | NORM     | Normal operation.                                                                                                                                                                                         |

| THRESH       | MAR      | Varies the sense amplifier threshold amplitude to check for<br>marginal memory bank conditions reflected in marginal core<br>noise or amplitude condition.                                                |

|              | NORM     | Normal operation.                                                                                                                                                                                         |

| CUR          | MAR      | Varies the X/Y core selection currents by $\pm 7.5\%$ to check for marginal CMC conditions.                                                                                                               |

|              | NORM     | Normal operation.                                                                                                                                                                                         |

| DIR          | HIGH     | Permits the STRB, THRESH, or CUR switches to apply their respective margin values in the high (+) direction.                                                                                              |

|              | LOW      | Permits the STRB, THRESH, or CUR switches to apply their respective margin values in the low (-) direction.                                                                                               |

| DISPLAY      | CONT 0   | Data and memory address for Control 0 are displayed.                                                                                                                                                      |

|              | CONT 1   | Data and memory address for Control 1 are displayed.                                                                                                                                                      |

|              | OVERRIDE | Data, address, ACTIVE, RD RQ, and WR RQ lights continue displaying MG10 status even if parity error exists.                                                                                               |

|              | CHECK    | Data, address, ACTIVE, RD RQ, and WR RQ lights stop (MG logic does not stop) at a parity error.                                                                                                           |

| SINGLE STEP* | ON       | Prevents the completion of the memory cycle, but allows the completion of one memory cycle each time the RESET                                                                                            |

|              |          | switch is activated. (The request and acknowledge portion of<br>the cycle is allowed, but the read/write portion is inhibited.)                                                                           |

| ERROR STOP   | ON       | Causes the STOP indicator to light and prevents further mem-<br>ory cycles when a memory control logic error or data parity<br>error is detected. The STOP condition is cleared with the<br>RESET switch. |

| RESET        | ON       | Spring-loaded momentary switch which, when pressed, clears and initializes the memory.                                                                                                                    |

Table 3-4

Maintenance Panel Switches

\*All 0s are written into memory when SINGLE STEP is used on clear/write cycle.

.

#### **3.2.4 Indicator Panel**

The MG10 indicator panel (Figure 3-5) provides memory operation status indicators to aid in the maintenance of the MG10. Visual displays indicate memory operation and the contents of the Address and Buffer Registers. When an operation indicator lights, the function identified is active or true; when a register indicator lights, the particular bit position identified contains a binary 1. The register indicators (Table 3-5) are grouped in octal format to facilitate translation of the binary word segments.

The bottom two rows of indicators are identical, except for a single power supply (PSOK) light. Each row is relative to a particular controller, as indicated. Because the functions of both controllers are identical, only one set of indicators is listed in Table 3-5.

7370-13

7370-13

7370-9

| Indicator                              | Function (When Lighted)                                                                                                                   |  |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| BANK 0-3                               | Indicates which of the four memory banks is being used.                                                                                   |  |

| MEMORY ADDRESS 21-35                   | Indicates the current Memory Address.                                                                                                     |  |

| MEMORY BUFFER 0-35<br>and PAR (parity) | Indicates the contents of the Memory Buffer Register.                                                                                     |  |

| PSOK                                   | Power is applied to the unit and regulated voltages are within tolerances.                                                                |  |

| REQUESTS<br>AW                         | The memory control is free and awaiting a processor request for access.                                                                   |  |

| RD                                     | A read request is being processed or was the last memory cycle processed                                                                  |  |

| WR                                     | A write request is being processed or was the last memory cycle processed.                                                                |  |

| P0P7                                   | Indicates which processor port(s) is requesting access.                                                                                   |  |

| ACTIVE PO-P7                           | Indicates which port in a given priority level is presently being accessed.                                                               |  |

| LAST PO-P7                             | Indicates which port in a given priority level was last granted access.                                                                   |  |

| ENABLES<br>MB SEL                      | The active port memory bus transceivers are enabled to send or receive data to or from the processor.                                     |  |

| DATA IN                                | The data transfer from the PCCI data register to the CMC data latches is enabled.                                                         |  |

| DATA OUT                               | The CMC data bus drivers (on the G114 module) are enabled to transmit<br>the data from the CMC data latches to the PCCI bus transmitters. |  |

| INC RQ                                 | Indicates failure of a cycle completion 20 $\mu$ s from the start of the memory cycle.                                                    |  |

| RUN                                    | The memory unit is performing a memory cycle.                                                                                             |  |

| STOP                                   | An error was detected while in the error stop mode.                                                                                       |  |

| WR RS                                  | The Write Restart signal was received from the processor.                                                                                 |  |

| PAR ERR                                | A parity error was detected during the memory cycle.                                                                                      |  |

| Tabl            | le 3-5 |           |

|-----------------|--------|-----------|

| Indicator Panel | Lamp   | Functions |

# CHAPTER 4 PRINCIPLES OF OPERATION

### **4.1 INTRODUCTION**

This chapter contains detailed information on the logical operations of the MG10 Core Memory. To aid the reader, a discussion of drawing conventions and notations introduces the detailed theory.

Two levels of detailed theory are included in this chapter: interface and unit. The interface level of theory discusses all MG10 interfacing in a DECsystem-10 installation. The level of discussion is supported by a block diagram and additional related drawings. The text does not go beyond the level of the diagrams used and mainly describes interfacing logic.

The unit level theory discusses the MG10 logic at a detailed level, referencing block schematics, flow diagrams, and the MG10 print set logic schematics. This section defines how the various memory operations function.

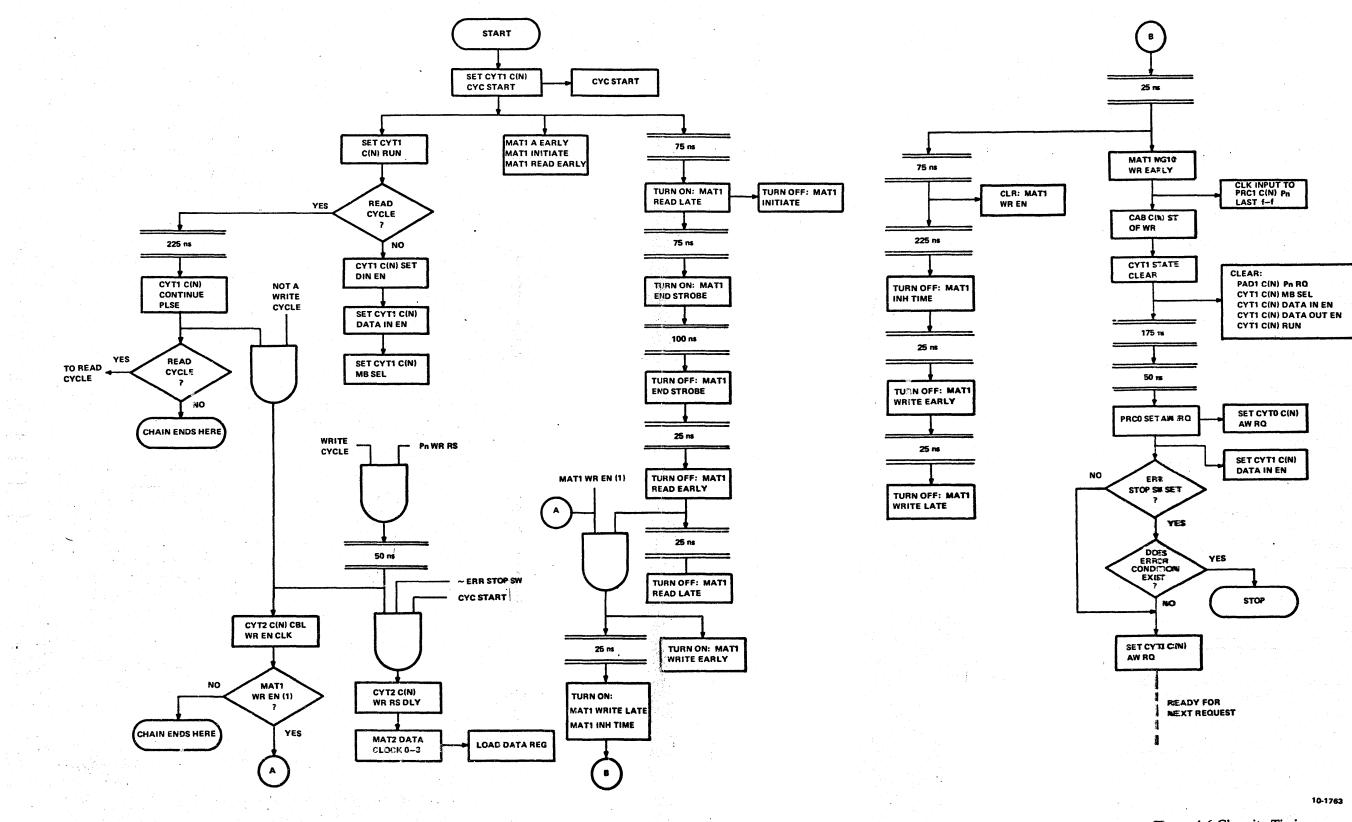

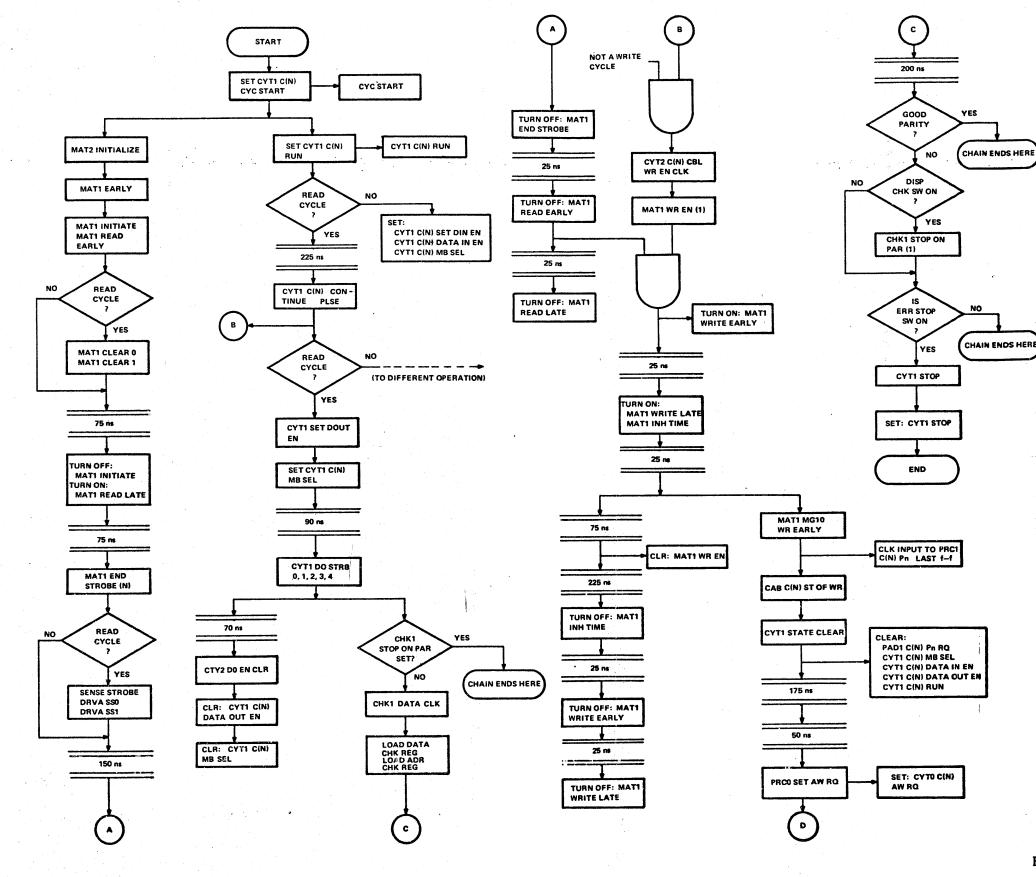

Emphasis here should be placed on referencing the main MG10 flow diagram (located in the print set), which provides the reader with an overall view of the various memory operations. Included in some of the operation descriptions are additional, simplified flows, that reflect just the immediate subject.

### **4.2 CONVENTIONS AND NOTATIONS**

Accompanying every MG10 Core Memory is a set of drawings that defines the memory physically, electrically, and functionally. Both the logic drawing and flow diagram conventions and notations are discussed in the following paragraphs.

#### 4.2.1 Logic Drawings

Various drawings (block schematics) show the function and location of every logic element used in the MG10. Just below the title in the lower right corner of each drawing is the drawing identification written in four boxes. In the left box is a letter indicating the size of the original drawing; a two-letter code indicating the type of drawing is in the next box. The third box contains the drawing number in three parts: the left part is the identification number of the module, the center digit names the drawing variation number, and the right digit identifies the individual drawing or a mnemonic code appears that identifies both the individual drawing and the material presented on it. For a drawing with several sheets, this mnemonic code runs consecutively (e.g., ARO, AR1). If a drawing is revised after being signed by the project engineer, the revision letter is written in the right box.

Almost all drawings are D size, but are reduced to B size for convenience. Some typical codes for drawing types are block schematic BS, flow diagram FD, circuit schematic CS, and module utilization MU. The modules are described in terms of the drawings that represent the standard production equipment at the time the manual was printed; the print set, however, reflects any later revisions and any special features unique to a given installation. The drawings associated with the text are all block schematics and flow diagrams that are often referred to as logic drawings and flow charts respectively (Table 4-1).

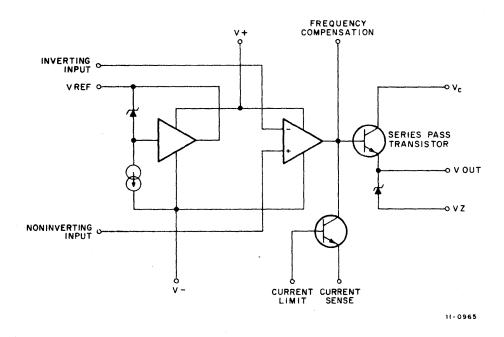

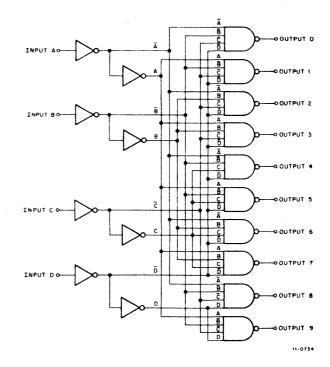

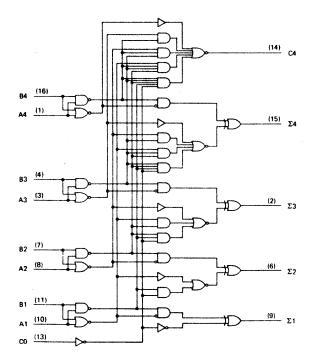

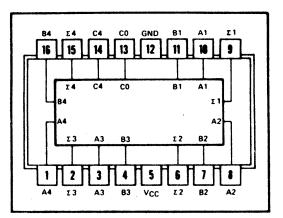

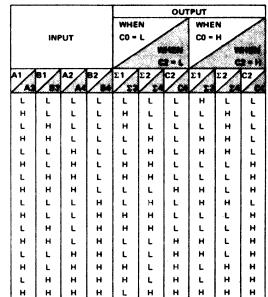

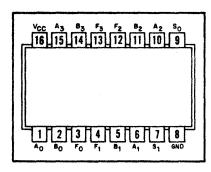

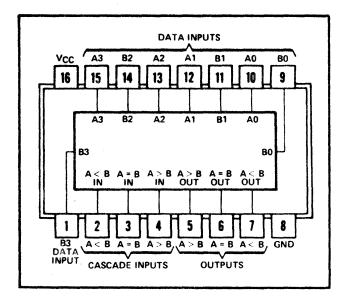

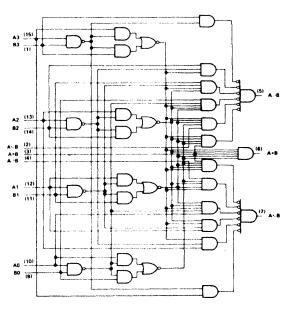

Standard logic symbols are used throughout the MG10 drawing set. Some of the newer chips used, however, are not familiar to everyone. Therefore, Appendix A is provided to list those unique chips, truth tables, and other pertinent information. Appendix A is a very beneficial supplement to this manual; refer to it when you are unsure of the operation of a particular chip.

| Signal Prefix* | Title                  | Module  | Drawing |

|----------------|------------------------|---------|---------|

| CHK(N)         | Parity Check           | M8588   | CHK0-1  |

| CYT(N)         | Cycle Timing           | M8589   | CYT0-2  |

| PRC(N)         | Priority Control       | M8590   | PRC0-2  |

| ADR(N)         | Address Receivers      | M8591   | ADR0-2  |

| PAD(N)         | Port Address Interface | M8592   | PAD0-2  |

| DR(N)          | MG10 Data Register     | M8593   | DR0-1   |

| AR(N)          | MG10 Address Register  | M8593YA | AR0-1   |

| DAT(N)         | MG10 Data Transceivers | M8594   | DAT0-1  |

| MAT(N)         | Memory Timing          | M8562   | MAT0-2  |

Table 4-1Signal/Drawing Identification

\*(N) refers to the relative sheet number of that particular module drawing.

Every element on the logic drawings is identified by the reference designation type number. The location of every element on that particular module is listed just below the reference number. Inputs or outputs shown as a plain line represent a high level; a line with a circle at its end represents a low level. For those familiar with traditional Digital logic symbology, the circle is equivalent to a solid diamond or arrowhead; the plain line is equivalent to an open diamond or arrowhead.

Simple gates are combined in a variety of ways to provide the OR and AND functions. The symbol for an exclusive OR gate (XOR) is the OR symbol with an extra line at the back of the arrowhead, as shown (for example) at the upper left in CHK1. Most of the remaining logic elements are represented by boxes that are labeled for the logic function, such as an adder, a comparator, or a mixer. It is recommended that you go through the MG10 drawings (and Appendix A) and familiarize yourself with all of these logic element symbols.

Flip-flops are all D-type and (for example) are represented by rectangular symbols as shown on DR0. A single module may have a number of independent flip-flops, or a group that has a common clock, clear, and set inputs. The flip-flops may be drawn horizontally or vertically, but the outputs are always on the top or right side, and the clock and data inputs are below or to the left of the figure.

When drawn horizontally, the clock input and clocked data input are always directly below the "0" and "1" outputs, respectively. When drawn vertically, the same inputs are directly to the left of the corresponding outputs. The unclocked clear and set inputs are always on the 0 and 1 sides, respectively. Note that the output terminals are drawn twice, showing the polarities associated with either state of the flip-flop. The polarities of the output terminals for the 0 state are shown over the 0; for the 1 state, the terminals have the polarities shown over the 1. This agrees with the convention that neither voltage level categorically represents 1 or 0, true or false. A given logic function may have different assertion levels in different places, depending upon gate input requirements. A signal is always regarded as true when it has the polarity shown for the input or output associated with it. In other words, if the signal X appears at an input with a circle, then X is true when low. The very same physical line may appear elsewhere without the circle but with the signal designation -X; this is equivalent, for now a high level on the line indicates that -X is true, i.e., X is false.

4.2.1.1 Signal Notation — All signal names are mnemonics that indicate both the function of the signal and its source. In almost all cases, signal names are meaningful phrases, although they are sometimes lengthy. Typical mnemonic terms used are IND indicator, PAR parity, CLK clock, STRB strobe, SEL select, CLR clear, EN enable, etc. The source of any signal can be determined from its first term or its first letters. Each register with associated logic and each control section, whether it occupies several drawings or only part of a drawing, has a mnemonic designation that appears in the drawing number and at the beginning of the name of any signal originating in that part of the logic. This source code may appear naturally as part of the signal name; if not, it is merely prefixed to the name. For example, all signals originated in the parity checking logic have names that begin with CHK.

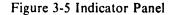

#### 4.2.2 Flow Charts

The flow charts show the major MG10 events and the flow of operations in a manner consistent with the actual gating and timing in the hardware, based on a sequence of level changes and timing pulses. In general, flow is downward. Upward flow occurs only upon returning to an earlier part of a sequence (as in a loop) or when going from one flow line to the next when several are on the same drawing; in any case, no conditions or events are ever shown along a rising line. Time pulses are indicated by ellipses. Events are shown in boxes that are at one side of a line, unless an event actually is responsible for further movement along the line. If an event occurs only on some conditions, those conditions are written at the left of a colon and the resulting event is written at the right.

Essentially, there is no passage of time along a continuous line. A break in a line indicates that movement along the line cannot continue beyond that point unless the condition written in the break is satisfied. This does not indicate any passage of time and the condition must be satisfied then; movement cannot restart should the condition later become true. Actual passage of time is indicated by horizontal lines breaking the flow line. A pair of single horizontal lines indicates a fixed delay, with the delay time written between the lines. Variable delay times have an arrow through the horizontal lines with a nominal time indicated.

### FLOW CHART CONVENTIONS

ACTION OR EVENT BOXES

#### **4.3 INTERFACE LEVEL DESCRIPTION**

This section defines the MG10 Core Memory on an interface level. Through the use of a block diagram, figures and text, an overview of all memory cycles is given and the major logic sections are defined.

#### 4.3.1 Operation Overview

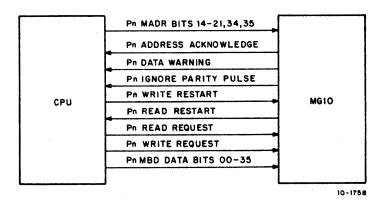

To begin operation, a processor requests access to a memory unit by placing the memory address on the memory bus along with the type of cycle requested (Figure 4-1). The cycle type is established by the Read Request ((Pn) RD RQ) and Write Request ((Pn) WR RQ) signals as follows:

- 1. Read/Restore Cycle = Pn RD RQ is true AND Pn WR RQ is false

- 2. Clear/Write Cycle = Pn RD RQ is false AND Pn WR RQ is true

- 3. Read/Modify/Write Cycle = Pn RD RQ is true AND Pn WR RQ is true

Memory address bits 14—21, 34, and 35 are inputs to the port address interface logic. In the event of simultaneous requests, the memory port priority logic determines the highest priority port request; then, the ADR ACK (Address Acknowledge) pulse is sent to the corresponding processor, signifying acceptance of the request.

**4.3.1.1 Read/Restore Cycle** — The Read/Restore cycle transfers data from a selected memory location to a requesting processor. During the read portion of this cycle, the memory reads data from the addressed memory location and loads it into the

memory data latches (registers). From there, the data is placed on the bus to the requesting processor. If the parity bit is to be ignored (for KA processors only), the IGN PAR (Ignore Parity) pulse is sent to the processor. At the same time as the data is sent, the RD RS (Read Restart) pulse is sent to the processor, indicating that the data requested has been sent. During the restore portion of the cycle, the memory disconnects from the bus and writes the data in the memory data latches back into the addressed memory location. This last step is necessary because the MG10 is a destructive readout memory.

**4.3.1.2 Clear/Write Cycle** — The Clear/Write cycle transfers data from a processor to a selected memory location. During the clear portion of the cycle, the memory reads data from the addressed memory location, discards it, and loads the data from the processor into the memory data latches by means of the WR RS (Write Restart) pulse sent by the processor. During the write portion of the cycle, the memory disconnects from the bus and the new data and parity bit contained in the memory data latches are written into the addressed memory location.

**4.3.1.3 Read/Modify/Write Cycle** — The Read/Modify/Write cycle transfers data from a selected memory location to a processor for modification and then transfers the modified data back to the selected memory location. During the read portion of the cycle, the memory reads the data from the addressed memory location, loads it into the memory data latches, places the data on the bus to the processor, clears the memory data latches, and

Figure 4-1 Memory Processor Interface

pauses. While the memory pauses, the processor modifies the data (modify portion) and initiates the write portion of the cycle by placing the modified data on the bus and sending the WR RS pulse. The memory then loads the modified data into the memory data latches and writes it into the same selected memory location.

#### 4.3.2 Major Logic Sections

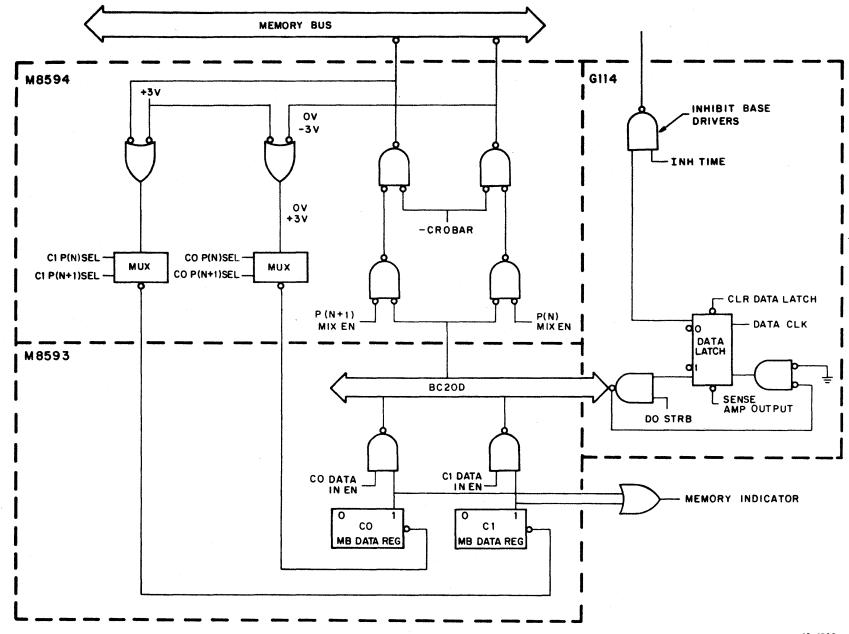

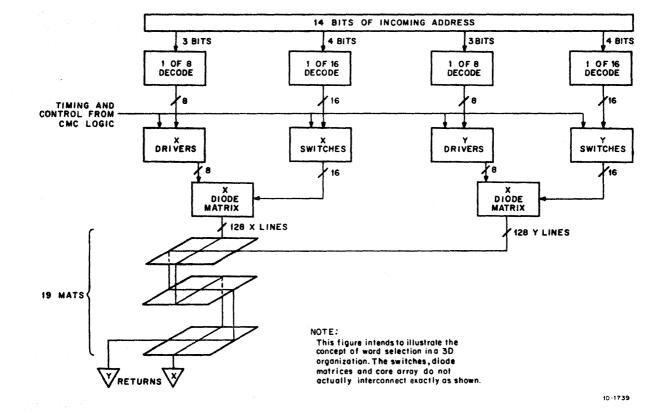

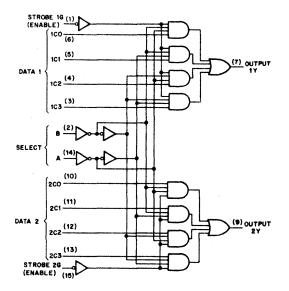

A brief description of the two major logic sections is presented in the following paragraphs. The PCCI section comprises the Request-Acknowledge and Priority Control logic, as well as logic that initiates and controls the interfacing of the two sections. The CMC section comprises the core memory stacks and the addressing and timing control logic for reading and writing the data words. Figure 4-2 shows major control signals and data flow, along with the logic subsection interconnections.

4.3.2.1 Port Control and Core Interface (PCCI) — The PCCI consists of two almost identical control sections: C0 and C1, of which both may be accessed by all eight ports (Figure 4-3). Of the total 128K 37-bit words, C0 controls the left 64K words and C1 controls the right 64K words. In the noninterleave mode, address bit MADR 21 determines which storage section is being accessed. The left 64K is being accessed if MADR 21 is a zero; the right 64K is being accessed if MADR 21 is a one. This means that one port may gain access through C0, while another port may simultaneously gain access through C1, resulting in a doubling of the data transfer rate as compared to earlier models.

Each control consists of the following logic sections:

- 1. Port Address Interface (PAD) Consists of the memory address bits and logic for selecting the proper MG10 cabinet (unit).

- 2. Priority Control (PRC) Consists of the logic that:

- a. Performs port priority selection in the event of simultaneous requests

- b. Generates strobe to load the Memory Address Register

- c. Generates the Upper Bound Address bits

- Cycle Timing (CYT) Consists of status logic (e.g., run, stop, etc.), the conditioning logic (e.g., restart, error stop, cycle start, single step, reset, etc.), and control timing pulses.

- 4. Address Receivers (ADR) Contains the Memory Address receivers and generates the ADR ACK and DATA WARN-ING pulses.

- 5. Data Register (DR) Contains the memory data bits.

- 6. Address Register (AR) Contains the memory address bits.

- Data Transceivers (DAT) Contains the data receivers which direct the data pulses to one of the two data registers. It also contains the drivers for strobing READ data out onto the correct memory bus. All eight ports can access both controls.

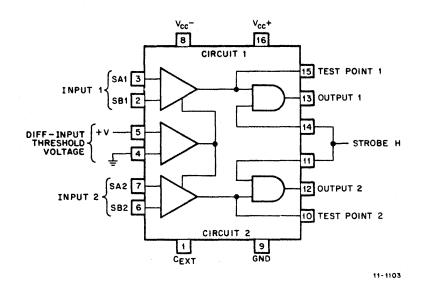

- Parity Check (CHK) Contains the control logic and registers for storing READ or WRITE data from which parity is checked. It also contains multiplexors for displaying inverted or noninverted inputs (e.g., data input is true LOW, address input is true HIGH).

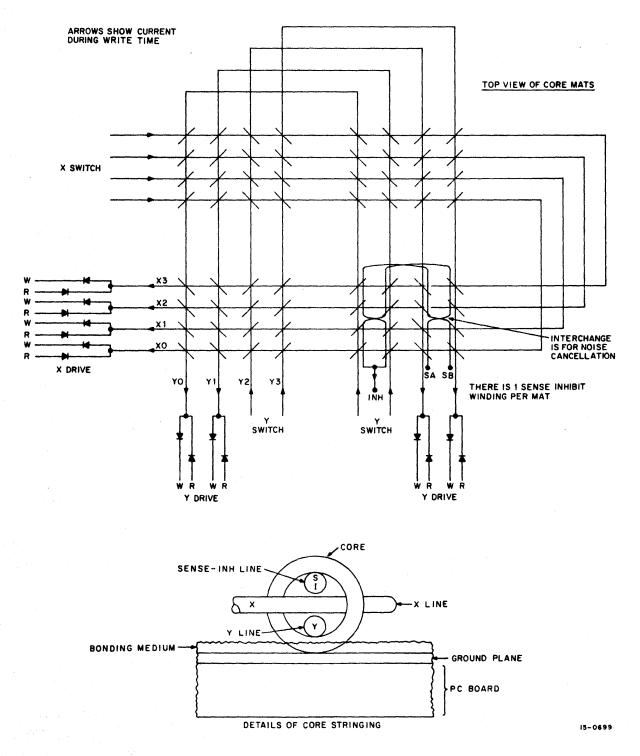

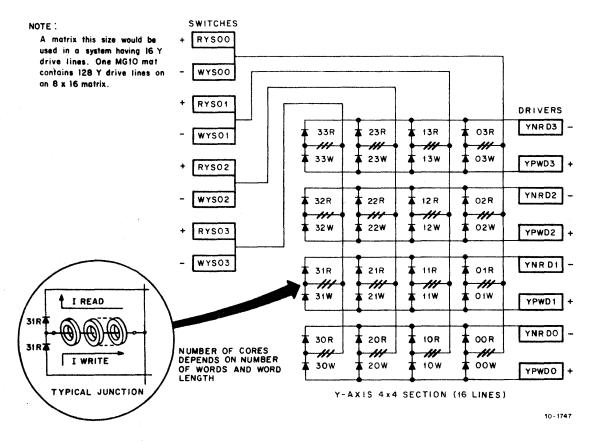

4.3.2.2 Core Memory and Control Section (CMC) (Figure 4-3) — This storage section is divided into a left half and a right half, with each half capable of storing up to  $64K \times 37$ -bit words. The left half is controlled by PCCI Control 0 and the right half is controlled by PCCI Control 1. Each half consists mainly of eight stack sets. The four leftmost stack sets store the low order bits (00—17), and the four rightmost stack sets store the high order bits (18—35, PAR). Each corresponding pair of stack sets is referred to as a memory bank. The four memory banks of each storage half are numbered M0, M1, M2, and M3.

The minimum memory size is 32K, 37-bit words, consisting of 16K, 37-bit word bank M0 in the left half section and 16K, 37-bit word bank M0 in the right half section. For ease of reference, each half section is prefixed by the mnemonic for its respective control, i.e., C0 and C1. The three different memory sizes offered are 32K, 64K, and 128K, 37-bit words.

Figure 4-2 MG10 Block Diagram

10-1753

Figure 4-3 CMC/PCCI Format

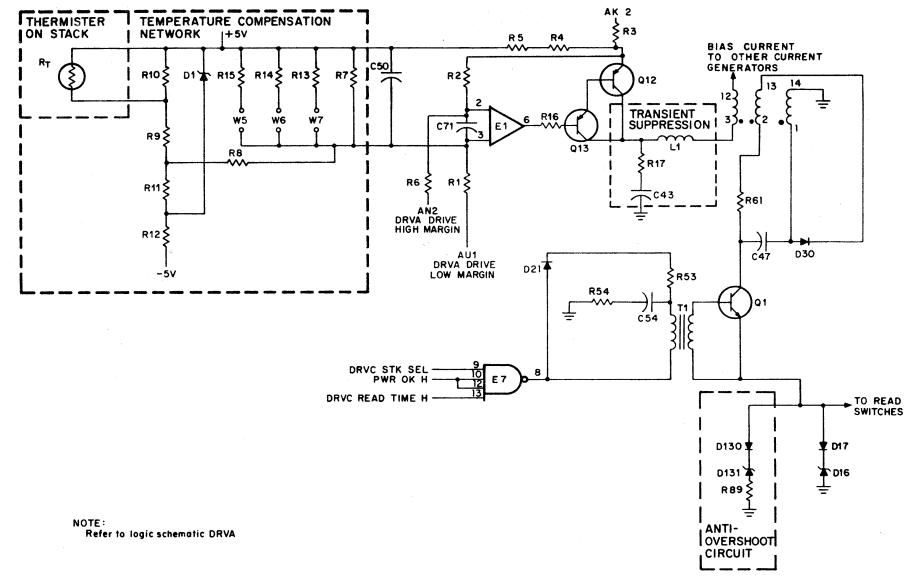

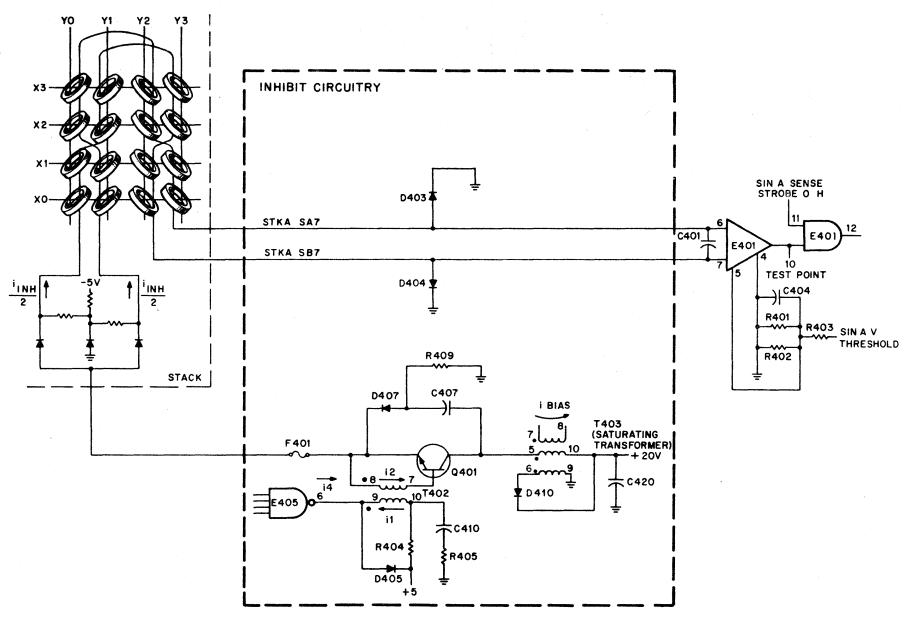

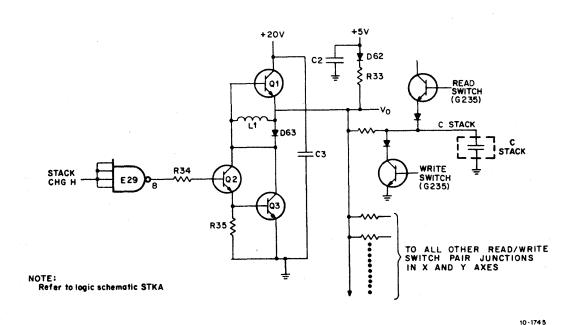

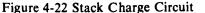

Each 16K, 19-bit stack set consists of three modules: G114 Sense Inhibit (Data Loops), H217 Stack, and G235 Memory Driver.

A bank, therefore, comprises two of each of these three modules. Additionally, for each half section, one M8562 is provided to manage the timing requirements of all the memory banks.

- 1. M8562 Timing This module generates the timing pulses for the READ and WRITE currents.

- 2. G114 Sense Inhibit This module contains the sense amplifiers, inhibit drivers, and data latches.

- 3. H217D Stack This module contains the ferrite core array, X-Y diode matrices, sense/inhibit terminations, stack charge circuit, and a thermistor to provide temperature compensation for the bias circuit.

- 4. G235 Memory Driver This module contains the decoders, X and Y drivers and switches, sense strobe control, bias source generator, and current sources.

### 4.3.3 Interleaving

Interleaving logic allows 32K, 64K, or 128K MG10 Core Memory units to be addressed in a manner that allows consecutive memory addresses to alternate between the two controls in one MG10, or rotate through the four controls in two MG10s.

Only memories of the same size and having consecutive port addresses with an even port address first may be 4-way interleaved. For example, 4-way interleaving can exist between memories 0 and 1, but not between 1 and 2. Interleaving is accomplished by swapping port address bits with word address bits. Functionally, the memory address can be divided into three segments:

| Memory<br>Size | Port<br>Address<br>Bits | Segments<br>Bank<br>Select Bits | Word<br>Address<br>Bits |

|----------------|-------------------------|---------------------------------|-------------------------|

| 32K            | 14-20                   | 21                              | 22-35                   |

| 64K            | 14—19                   | 20, 21                          | 22-35                   |

| 128K           | 14-18                   | 19-21                           | 22-35                   |

When 2-way interleaving is selected, bit 21 is swapped with the least significant word address bit, bit 35. In this configuration, should the processor generate consecutive addresses starting at address 0 or MG10 number 0, the subsequent memory cycles would alternate between MG10 Control 0 and Control 1, with all even addresses located through Control 0 and all odd addresses located through Control 1.

In 4-way interleaving, bit 21 is again swapped with bit 35 and bit 34 is swapped with bit 20, 19, or 18, depending on the storage size in each MG10. Thus, memory words would be addressed in the following sequence:

MG10-0 Control 0 0, 4, 10 etc. MG10-0 Control 1 1, 5, 11 etc. MG10-1 Control 0 2, 6, 12 etc. MG10-1 Control 1 3, 7, 13 etc.

#### **4.4 UNIT LEVEL DESCRIPTION**

A block diagram of the MG10 is shown in Figure 4-2, and circuit diagrams and flows are interspersed throughout this section. Engineering drawings are also referenced where applicable. Note again that the mnemonic prefix portion of signal names shown on the illustrations indicate the signal source. For example, the CYT1 C(N) CYC START H signal is generated on the Cycle Timing 1 logic drawing, D-CS-M8589-0-CYT1.

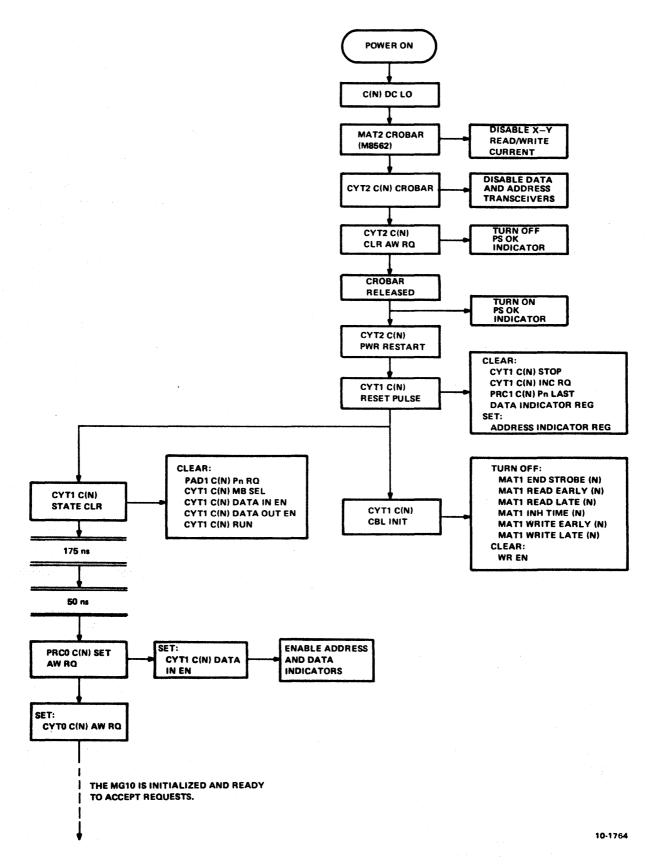

#### 4.4.1 Initial Conditions

Applying power to the MG10 initializes the memory system and places the MG10 in an idle state ready to respond to access requests from a processor. Refer to Figure 4-4, the MG10 Power Up Flow Diagram, while reading this section.

When power is initially turned on, CAB C(N) CRO-BAR INPUT (from DC LO of the H742 power supplies) is temporarily shorted to ground causing CYT2 C(N) CROBAR L to be true. This disables the data and address transceivers and prevents spurious pulses from being sent out on the memory bus. At the same time, CYT2 C(N) CLR AW RQ L clears the CYT0 C(N) AW RQ flip-flops, preventing access to both controls (C0 and C1). Signal CYT2 C(N) CLR AW RQ L is also wired to the PS OK indicator so that the indicator is temporarily not turned on. When DC LO (from the H742

Figure 4-4 MG10 Power-Up Flow Diagram

power supplies) is released to +3 V, the PS OK indicator light is turned on and a CYT2 C(N) PWR RESTART L pulse is generated which, in turn, generates CYT1 C(N) RESET PLSE L and CYT1 C(N) STATE CLR. Thus both controls (C0 and C1) are initialized. Approximately 300 ns later, PRC0 C(N) SET AW RQ L is generated to set the CYT0 C(N) AW RQ flip-flops, indicating that both controls are free to accept memory requests.

### 4.4.2 Request/Acknowledge

Basic request/acknowledge circuitry must be capable of recognizing an access request from a processor or other device and acknowledging that request when the memory is free to service it. However, the MG10 request/acknowledge circuitry is required to perform tasks in addition to the basic request/acknowledge tasks. Because the MG10 is required to service up to eight separate devices, the priority network allows access to the processor (or device) having highest priority. The priority control logic is shown on the PRC drawings. The following paragraphs explain the request/acknowledge sequence with reference to the PRC and CYT drawings.

**4.4.2.1 Single Access Request** — Two Priority Control modules (M8590) are used in each MG10: one for Controller 0 (C0), the other for Controller 1 (C1). Each controller can be accessed by all eight ports. This discussion continues the use of C(N) to represent either controller, as the logic for both is identical.

Assuming the memory is in the idle state, as explained in Paragraph 4.4.1, the sequence is initiated when a processor generates a Pn RQ signal and a memory address that is within the address boundaries of the specific MG10. The address boundaries are determined by the setting of the LOWER AD-DRESS BOUNDARY switches and the storage size of the MG10 as determined by the four MEM-ORY BANK switches.

When this happens, one of the port request (e.g., PAD1 C(N) P0 RQ L) signals asserts and generates signal PRC0 C(N) RQ H. This resets the CYT0 AW RQ flip-flop and generates the CYT0 C(N) MA CLR CLK L and CYTO C(N) MB CLR CLK L pulses. As long as the CYTO AW RQ flip-flop is reset, subsequent processor requests are ignored. The CYTO C(N) MA CLR CLK L clears the Memory Address Register, while the CYTO C(N) MB CLR CLK L clears the Memory Buffer Register and the WR RS DISPLAY flip-flop. The registers are now ready to receive the current memory address and data. The same port request (PAD1 C(N) Pn RQ L) that generated the main PRC0 C(N) RQ H signal also inverts and becomes PRC0 C(N) Pn RQ H, notifying the priority control logic that port Pn is requesting access.

After a delay of approximately 60 ns, the PRC0 RQ H signal generates two types of pulses: the 27 ns wide PRC0 C(N) MA STRB 0-3 H pulses are generated, which load the address into the Memory Address Register; the second pulse generator outputs the PRC0 C(N) MA STRBW (wide) pulse, which is approximately 107 ns wide. This signal is used to generate the ADR ACK (Address Acknowledge) signal. Signal PRC0 C(N) MA STRBW H (wide) is also used to generate CYT1 C(N) CAB CYC START H after a delay of approximately 65 ns. The latter signal starts the core read cycle.

**4.4.2.2 Simultaneous Access Requests** — Simultaneous access requests dictate the need for additional priority control. If two or more requests are received simultaneously by the MG10, the priority network enables the port having the highest priority. The priority scheme is as defined in Paragraph 2.3.4.

| Priority | Port                    |  |

|----------|-------------------------|--|

| First    | P0 and P1 (Alternating) |  |

| Second   | P2 and P3 (Alternating) |  |

| Third    | P4 — P7 (Rotating)      |  |

Second priority (for example) is alternated between ports P2 and P3 such that if P2 were serviced last in the previous memory cycles, then P3 would be given priority over P2 should simultaneous requests occur on those ports. The rotating priority goes downward from port 4 through 7, then back to 4 again. Priority logic for each control is located on the two M8590 Priority Control modules.

#### 4.4.3 Memory Cycle Timing

As previously stated (Paragraph 4.3.1), data may be read from memory and sent to a processor (Read/Restore cycle); data may be transferred from a processor and written into memory (Clear/Write cycle); or data may be read from memory, sent to a processor, returned to the memory, and written into the memory at the same location from which it was originally read (Read/Modify/Write cycle).

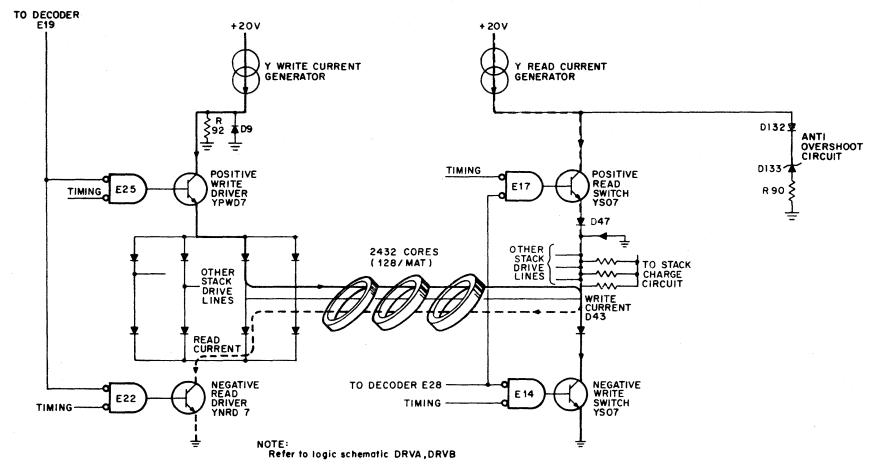

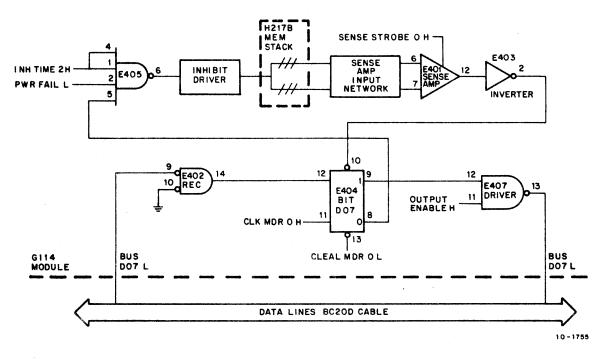

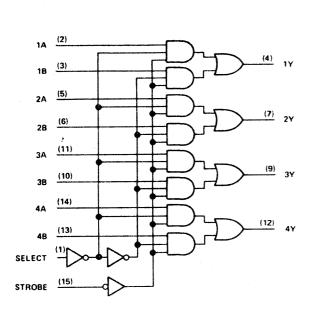

The basic operations of memory cycle timing, the read operation, and the write operation, are common to the three memory cycles. Figure 4-5 illustrates the data path of information written into and read from memory.

The following paragraphs describe the various memory cycle operations. The times stated are all approximate. Because the two memory controller sections can overlap their operations, timing diagrams are not used. However, flow diagrams readily lend themselves to describe the memory operations. The main MG10 flow diagram should be referenced as an overall guide through each discussion. Where necessary, sectional flows are also provided.

The power-up conditions prepare the memory for receiving requests. The memory may also become initialized (again) after completing an operation. Either way, the memory is idle, waiting for a request.

Assuming a single step request is not being made, the MA STRBW pulse (described in Single Access Request, Paragraph 4.4.2.1), is delayed approximately 65 ns. It causes signal CYT1 C(N) CYC START to be generated. Once a request has been received and acknowledged, this signal commences all memory operations. The following memory cycle operations all begin at this time.

**4.4.3.1 Clear/Write Cycle** — Refer to Figure 4-6, the Clear/Write Cycle Flow Diagram, while reading this section. The discussion assumes that the MG10 is initialized, CYT0 AW RQ is set, and CYT1 CYC START has been produced.

During a Clear/Write cycle, a read operation is performed first; however, the data is lost because the sense strobe lines are disabled and the data is not strobed from the sense amplifiers. In effect, this is a destructive read operation that clears memory prior to writing new data into memory. AT the beginning of this cycle, the CYT1 C(N) CYC START signal asserts and the CYT1 C(N) RUN flip-flop is set. Signals MAT1 A EARLY, MAT1 INITIATE, and MAT1 READ EARLY begin the destructive read operation. Additionally, setting CYT1 C(N) CYC START asserts CYT1 C(N) SET DIN EN L, which sets the CYT1 C(N) MB SEL and CYT1 C(N) DATA IN EN flip-flops.

The active controller ( $\dot{C}0$  or C1) signal (C(N) Pn ACT) is ANDed with its respective controller MB SEL signal to produce the PAD0 C(N) Pn SEL H signals. They are then inverted and become the DAT0 C(N) Pn SEL L and DAT0 C(N) Pn+1 SEL L signals, which enable the Memory Buffer receiver multiplexors for the proper ports to receive the data from the processor.

While the core read portion of the Clear/Write cycle is being performed, the processor, after receiving the ADR ACK pulse from the MG10, sends back a Pn WR RS pulse along with the data and parity bits. The data is received from the processor (along with Pn WR RS) and loaded into the Memory Buffer. The selected CYT1 C(N) DATA IN EN level allows the data to be transferred from the Memory Buffer through the BC20D Core Interface Cables to the data latches in the CMC section.

When MAT1 READ EARLY is negated, while the MAT1 WR EN flip-flop is set, the WRITE EARLY signal is asserted. This turns on the X and Y write current generators and the X and Y switches on the G235 module. The MAT1 WRITE LATE and MAT1 INH TIME signals are asserted 25 ns later; signal MAT1 WRITE LATE is actually MAT1 WRITE EARLY delayed 25 ns At the time of its assertion, it turns on the X and Y write drivers. Accordingly, the MAT1 INH TIME signal provides the timing required for turning on the inhibit drivers.

Another 25 ns delay is encountered; its trailing edge triggers another delay (75 ns) and also asserts MAT1 MG10 WR EARLY (N) L. This signal is sent to the controller as CAB C(N) ST OF WR. It is used to set the PRC1 C(N) Pn LAST flip-flop, stating which port is presently being accessed. Additionally, it asserts CYT1 STATE CLEAR, which resets the PAD1 C(N) Pn RQ, CYT1 C(N) MB SEL, DATA IN EN, DATA OUT EN, and RUN flipflops; this disconnects the memory from the memory bus.

Figure 4-5 Data Path Diagram

4-12

10-1760

Figure 4-6 Clearrite Timing Flow Diagram At the conclusion of the 75 ns delay, the MAT1 WR EN flip-flop is cleared. Another 225 ns delay times out and negates the MAT1 INH TIME signal, disabling the inhibit drivers. Signal MAT1 WRITE EARLY is negated 25 ns later. This turns off the same current generators (X and Y write) and switches (X and Y) that it had previously turned on. Then, the MAT1 WRITE LATE signal is negated, turning off the X and Y write drivers and signaling the end of the write sequence.

After approximately 300 ns, the PRC0 SET AW RQ signal asserts and sets the CYT0 C(N) AW RQ flip-flop, notifying the processor of the memory's availability for another access request. The CYT1 C(N) DATA IN EN flip-flop is also set at this time to gate out the contents of the data and address registers to the indicators.

The Pn WR RS signal, used to initiate the sending of the data and parity bits to the MG10, also triggers the CYT2 C(N) WR RS DLY. When it times out (after approximately 100 ns) it clocks the data into the CHK data register, where parity is checked. Parity is checked by comparing parity of the 36 data bits with the parity bit. If they are different, a parity error has occurred. Odd parity is used, meaning that if the number of ones in the data bits is even, the PARITY bit should be a one.

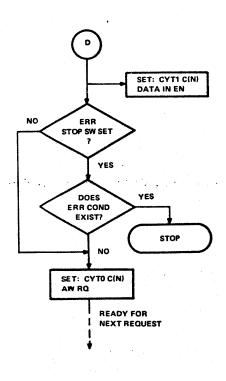

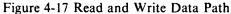

**4.4.3.2 Read/Restore Cycle Timing** — Refer to Figure 4-7, the Read/Restore Cycle Flow Timing Diagram, while reading this section. The Read/Restore cycle begins with the assertion of the CYT1 C(N) CYC START signal, which generates CYT1 C(N) RUN H and MAT1 A EARLY (N) L. The MAT1 A EARLY (N) L signal is advance timing to the G235 Driver Module to turn on the Y read current generator, Y read driver, Y read switch, X read current generator, and X read switch. The X read driver is not turned on at this time, but waits for MAT1 READ LATE (N) L.

Because this is a Read/Restore cycle, signals MAT1 CLEAR 0 (N) L and CLEAR 1 (N) L are produced to clear the G114 Data Register prior to the generation of the SENSE STROBE pulses. Approximately 75 ns after the CLEAR pulses reset the Data Register, the MAT1 INITIATE L signal is negated and the MAT1 READ LATE (N) L signal is asserted. This turns on the read X drivers, which cause the read X current to start flowing. Approximately 75 ns later, the MATI END STROBE (N) L signal goes high. The SENSE STROBE signals DRVA SS0 L and SS1 L are generated by the output of a one-shot gated with MAT1 END STROBE being high. The leading edge of the SENSE STROBE signals can be varied (marginally) by placing the appropriate STRB margin switch on the maintenance panel into the MARG position. This moves the leading edge of the SENSE STROBE signals, but does not affect the trailing edge. The sense strobe signals in the memory stacks are wide to allow additional time for the core outputs to be propagated along the long sense lines and to propagate through the associated signal path delays.

At the end of a 150 ns delay, the MAT1 END STROBE signal negates and turns off the strobe signal applied to the sense amplifiers. Then MAT1 READ EARLY (N) L negates, which turns off the X and Y current generators and the X and Y read drivers. When the MAT1 READ LATE (N) L signal negates approximately 25 ns later, the X and Y read switches are turned off.

The CYT1 C(N) CYC START pulse at the top of the flow diagram (Figure 4-7) was asserted after the MA STRB pulses had loaded the correct memory address and desired type of request. Signal CYT1 C(N) CYC START also sets the CYT1 C(N) RUN flip-flop. Approximately 225 ns later, the CYT1 C(N) CONTINUE pulse is asserted. This is AN-Ded with the Read cycle to set CYT1 C(N) DATA OUT EN and CYT1 C(N) MB SEL flip-flops. The CYT1 C(N) DO STRB 0-4 pulses are generated 90 ns later.

Signal CYT1 C(N) CBL DO EN H is sent to the G114 to gate out the strobed data residing in the G114 data latches. The gated out data is sent to the data bus transceivers.

Signal CYT1 C(N) MB SEL is gated with the active port signal PRC1 C(N) P(N) ACT H to generate the port selected signal PAD0 C(N) P(N) SEL H. This, in turn, is ANDed with CYT1 C(N) DO STRB to strobe the gated out data from the data bus transceivers out onto the bus of the selected port.

Figure 4-7 Read Restore Timing Flow Diagram

10-1762

.

The CYT1 C(N) DO STRB pulse is also used to clock gated out data from the G114 into the CHK data register, where parity is checked 200 ns later. Parity is checked by comparing the parity of the 36 data bits with the parity bit. If they are different, a parity error has occurred. Odd parity is used in the MG10, meaning that if the number of ones in the data bits is even, the PARITY bit should be a one.

The data read in the read portion of the Read/Restore cycle is sensed from the cores and strobed into the data latches. It is then gated by signal CYTO C(N) DO STRB 0-4 H to the memory bus transmitters. This data, retained in the data latches, is then rewritten into the same memory locations it was read from.

The restore portion of the Read/Restore cycle is similar to the write portion of the Clear/Write cycle. Refer to Paragraph 4.4.3.1 (Clear/Write Timing) for a detailed description of the write portion of the Clear/Write cycle.

**4.4.3.3 Read/Modify/Write Timing** — During a Read/Modify/Write cycle, the read operation is performed first. The data read is then sent to the processor for modification and the Memory Buffer is cleared. The memory then pauses (20  $\mu$ s maximum) to await the return of the modified data.

During the read operation, CYT1 C(N) DOUT EN sets the CYT1 C(N) MB SEL flip-flop, which remains set until CYT1 STATE CLR asserts. In addition, the AND of CYT0 C(N) WR RQ and CYT2 C(N) DOUT EN CLR (the DO STRB pulse delayed) sets the CYT1 C(N) DATA IN EN flip-flop, which also remains set until the assertion of CYT1 C(N) STATE CLR. When the modified data is sent from the processor along with Pn WR RS, a write operation is performed as in the Clear/Write cycle.

#### 4.4.4 Detailed Memory Description

This section of the manual provides the user with a detailed theory of operation and the diagrams necessary to understand the MG10 Core Memory and Control (CMC) logic.

**4.4.4.1 3-D 3-Wire Memory Fundamentals** — Data is stored in ferrite cores by magnetizing the iron compound in those cores. A core that has been magnetized so that the iron molecules align, as shown in Figure 4-8a, can be said (for example) to store a logic 1. Magnetization in the opposite direction (Figure 4-8b) would, then, represent a logic 0.

Figure 4-8 Magnetic States of Ferrite Cores

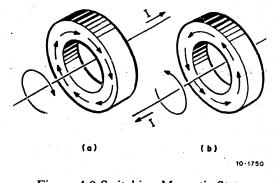

The magnetic state of the core can be switched from a logic 1 to a logic 0, and vice versa by a magnetic field induced by current flowing in a wire threaded through the core (Figure 4-9). Due to the hysteresis effect inherent in all ferro-magnetic materials, the current must be large enough to produce sufficient magnetic field intensity to switch the core. Once switched, the core remains in its new state.