dasfital

TITLE

- 1.0 System Description

- 1.1 General Information

The TU16/TM02 tape system will consist of between one and eight tape drives and a single electronics package which will serve as an interface between any one of those drives and a Massbus controller.

1.2 Definition

For the purposes of this specification, the following definitions apply:

1.2.1 Controller - any Massbus controller.

- 1.2.2 Slave a tape transport.

- 1.2.2.1 Selected Slave that slave whose select code appears in bits 0-2 of the Tape Control (TC) Register.

- 1.2.3 TM02 defined operationally. The TM02 electronics package interfaces to the controller. It accepts commands which a selected slave must execute while providing the controller with information about the status of the slave. During data transfers the TM02 controls fetching, formatting, and sending of data. The TM02 also oversees the handling of error conditions and slave servicing requirements.

- 1.2.4 Drive When bits 0-2 of the Tape Control Register in the TM02 contain the select code of an existing slave, then the Master and the selected slave together become equivalent to what is defined as a "drive" in the Massbus Specification. No more than one slave may be legally selected at any time, and commands can not be issued to unselected slaves. However, unselected slaves are able to make important status changes known to the Controller. (See SSC bit of Status Register.)

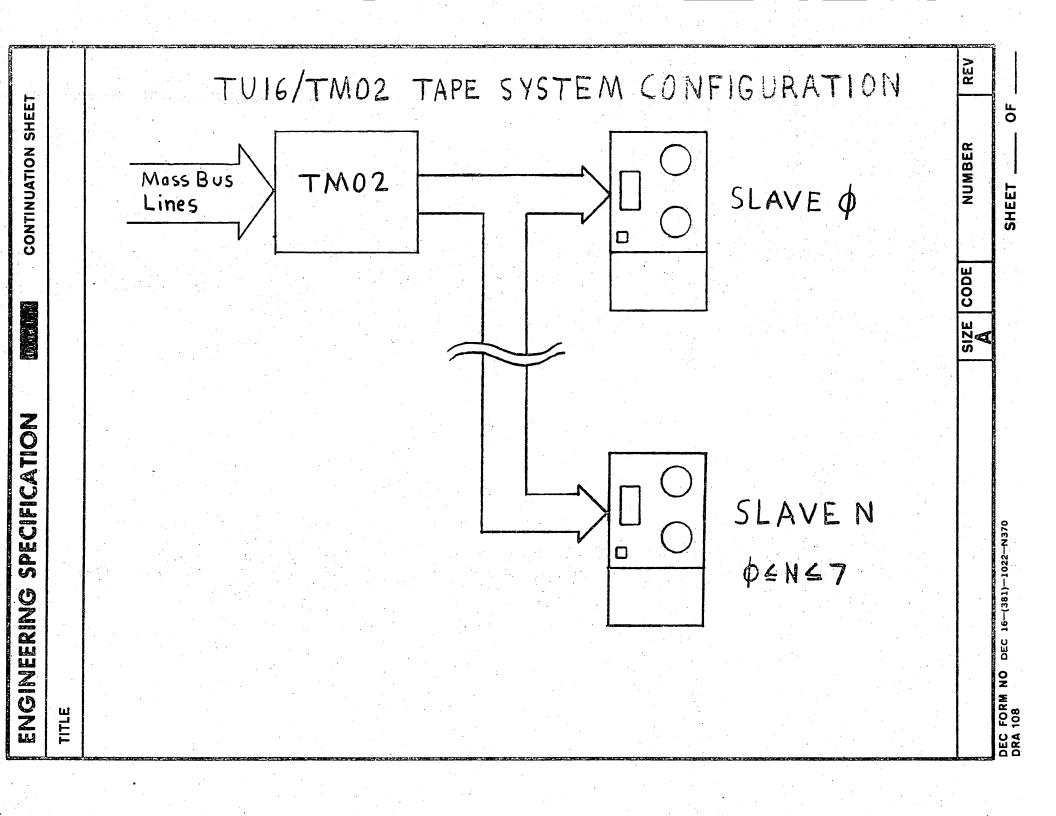

- 1.3 System Configuration

The following block diagram illustrates the configuration of a TU16/TM02 tape system:

|                            | <br>A                      | CODE |          | REV |

|----------------------------|----------------------------|------|----------|-----|

| <br>DEC 16-(381)-1022-N370 | de gant de sign e tra dire |      | SHEET OF |     |

તા આ કુલ કે તે કે

TITLE

### 1.4 Applicable Documents

Before reading this document, the reader should familiarize himself with the Massbus Specification. In addition, attempts to program the TU16/TM02 system should be prefaced by a thorough study of the programming manual for the particular Massbus controller with which the program will interface.

| DEC | FORM | NO | DEC 16-(381)-102 | 22-N370 |

|-----|------|----|------------------|---------|

| DRA | 108  |    |                  | 114     |

SHEET \_\_\_\_\_ OF \_

NUMBER

SIZE CODE

Δ

dagetat

TITLE

#### 2.0 Commands Implemented

2.1 Commands will be executed only if they are directed to ONLINE slaves. The following commands will be implemented on the TU16 tape system. Functions codes not listed here will be treated as illegal functions.

| F5 | F4 | F3  | F2 | Fl | Operation Name      |

|----|----|-----|----|----|---------------------|

| 0  | 0  | 0   | 0  | 0  | No-op               |

| 0  | 0  | 0   | 0  | 1  | Rewind, Offline     |

| 0  | 0  | 0   | 1  | 1  | Rewind              |

| 0  | 0  | 1   | 0  | 0  | Drive Clear         |

| 0  | 1  | 0   | 0  | 0  | Write Filemark      |

| 0  | 1  | 0.  | 1  | 0  | Erase               |

| 0  | 1  | 1   | 0  | 0  | Space Forward       |

| 0  | 1  | 1   | 0  | 1  | Space Reverse       |

| 1  | 0  | 1   | 0  | 0  | Write Check Forward |

| 1  | 0  | 1   | 1  | 1  | Write Check Reverse |

| 1  | 1  | 0   | 0  | 0  | Write Forward       |

| 1  | 1  | 1   | 0  | 0  | Read Forward        |

| 1  | 1  | . 1 | 1  | 1  | Read Reverse        |

- 2.1.1 The requirement for a "read-in" mode on the TU16/TM02 system will engender either one or two additional commands. Details of the "read-in" commands and sequencing will be published at a later date.

- 2.2 Description of Commands

- 2.2.1 NO-OP: Causes immediate reset of GO and assertion of DRY. No tape motion or status change occurs in the selected slave. No attention generated.

- 2.2.2 REWIND, OFFLINE: The selected slave begins rewinding and goes OFFLINE. GO is reset and DRY, SLA, SSC, and ATA become asserted (SLA and SSC are asserted because the slave has gone OFFLINE). Operator intervention is required to bring the slave back ONLINE.

NOTE: This command generates only one Attention, whereas a REWIND command may generate either one or two Attentions.

| SIZE | CODE | NUMBER | REV |

|------|------|--------|-----|

| A    |      |        |     |

|      |      |        |     |

TITLE

stram and ant

- 2.2.3 REWIND: The selected slave executes a rewind back to the reflective strip marking beginning of tape (BOT). Sequencing of a REWIND command proceeds as follows

- 2.2.3.1 When a REWIND command is loaded with GO = 1, the drive first checks the Settledown (SDWN) bit in the Status Register.

- a) If SDWN =  $\emptyset$ , the selected slave immediately begins rewinding.

- b) If SDWN = 1 (indicating that the selected slave is slowing to a halt after completion of a prior command) and the last command loaded called for tape motion in the REVERSE direction, the selected slave immediately begins rewinding.

- c) If SDWN = 1 and the last command loaded called for tape motion in the FORWARD direction, the TM02 delays execution of the REWIND until SDWN =  $\emptyset$ , indicating that the drive has stopped. The maximum length of the Settledown interval on TU16 is 15 milliseconds.

- 2.2.3.2 As soon as the slave has recognized the REWIND command, the drive returns to the ready state and DRY and ATA become asserted. In cases 2.2.3.1 a) and b), the time from initiation of the Control Bus write sequence which loads the REWIND command until re-assertion of DRY is less than 2 microseconds. In case c), re-assertion of DRY may not occur for up to 15 milliseconds after initiation of the REWIND sequence.

|      |                  | SIZE | CODE | NUMBER   | REV |

|------|------------------|------|------|----------|-----|

| <br> | -(381)-1022-N370 |      |      | SHEET OF |     |

TITLE

digistar

CONTINUATION SHEET

2.2.3.3 Once the selected slave reaches BOT, it will cause SLAVE ATTENTION (SLA) to become asserted, in turn causing SLAVE STATUS CHANGE (SSC) and ATA to become asserted. If the selected slave was already at BOT when the REWIND command was loaded, the ATA condition generated in section 2.2.3.2 and the ATA condition generated in section 2.2.3.3 will occur so close together in time that they will be indistinguishable to the programmer. 2.2.3.4 The following examples will indicate the states of important status bits during a rewind sequence. For simplicity, the possibility of SLA and SSC becoming asserted due to status changes in slaves other than the rewinding slave will not be treated. During the time between reception of a) the REWIND command and initiation of a rewind by the selected slave: DRY =  $\emptyset$ , ATA =  $\emptyset$ , SSC =  $\emptyset$ , SLA =  $\emptyset$ , SDWN =  $\emptyset$  or 1, PIP =  $\emptyset$ . b) After initiation of the rewind, if the selected slave was already at BOT: DRY = 1, ATA = 1, SSC = 1, SLA = 1, SDWN =  $\emptyset$ , PIP =  $\emptyset$ . After initiation of the rewind, if the C) selected slave was not at BOT: DRY = 1, ATA = 1, SSC =  $\emptyset$ , SLA =  $\emptyset$ , SDWN =  $\emptyset$ , PIP = 1. After completion of the rewind, if d) the selected slave was not already at BOT: DRY = 1, ATA = 1, SLA = 1, SSC = 1, SDWN =  $\emptyset$ , PIP =  $\emptyset$ . (Identical to case 2.2.3.4 b)

| <br> |                  | A | CODE | NUMBER   | REV |

|------|------------------|---|------|----------|-----|

|      | -(381)-1022-N370 |   |      | SHEET OF |     |

CONTINUATION SHEET

TITLE

- e) Note that SSC is an indication of status changes in <u>at least</u> one slave. Thus, it should not be cleared until all slaves have been polled to confirm their status.

- 2.2.3.5 In a multi-slave system the presence of rewinding slaves on the TM02-TU16 bus does not interfere with the execution of commands by selected slaves which are not rewinding. Any command recognized as a legal function by the TU16 may be issued to a rewinding slave if DRY = 1. If this is done, the following sequence of events will occur:

- a) When command is loaded, GO becomes asserted;

- b) Execution of command is deferred until rewind is complete (until PIP becomes negated); GO remains asserted;

- c) When rewind reaches completion, PIP becomes negated and SLA becomes asserted; command execution is initiated.

- d) When command reaches completion, ATA becomes asserted because of prior assertion of SLA.

NOTE THAT, WORST CASE, THIS SEQUENCE COULD CAUSE THE ENTIRE TU16 SYSTEM TO GO BUSY FOR UP TO 5 MINUTES. IF A DATA TRANSFER COMMAND IS ISSUED TO A REWINDING SLAVE, DATA BUS TIMING RESTRICTIONS MAY BE VIOLATED.

2.2.4 DRIVE CLEAR: Performs reset on TM02 and selected slave, does not affect unselected slaves. Like any other command, DRIVE CLEAR can be loaded into the TU16/TM02 system only if DRY = 1.

|                        | A | CODE |            | REV |

|------------------------|---|------|------------|-----|

| DEC 16-(381)-1022-N370 |   |      | SHEET OF . |     |

TITLE

CONTINUATION SHEET

DRIVE CLEAR command resets: SLA in selected slave, SSC (if no other slaves have current attentiondemanding conditions), IDB, ERR, ATA in STATUS Register; resets all but bit 6 of MAINTENANCE Register; resets FCL in TAPE CONTROL Register; resets all bits in ERROR Register except bit 14 (UNS), and resets UNS if the TMO2 is not experiencing a power-fail.

The time from reception of a DRIVE CLEAR command to re-assertion of DRY = 1 is 2 microseconds (maximum). If DRIVE CLEAR is issued to a TMO2 which is experiencing a power-fail, ATA and ERR will become asserted when DRY becomes asserted. DRIVE CLEAR cannot affect a rewinding slave.

- 2.2.5 WRITE FILEMARK: The selected slave writes an extended (3") inter-record gap, a filemark, and stops. ATA becomes asserted when DRY becomes asserted; EOF will be asserted if a detectable filemark was written (this is the normal case).

- 2.2.6 ERASE: The selected slave writes an extended interrecord gap and stops. ATA becomes asserted when DRY becomes asserted.

- 2.2.7 SPACE FORWARD: The selected slave spaces forward (towards EOT) over the number of records specified by the contents of the Frame Count Register. Detection of a filemark (EOF) causes a SPACE command to be aborted.

All data errors are inhibited during this operation. DRY becomes asserted when operation is complete and a valid inter-record gap found. ATA becomes asserted when DRY asserted.

2.2.8 SPACE REVERSE: Like SPACE FORWARD, except that detection of BOT or EOF will abort the operation, and that the direction of tape motion is in the reverse direction (towards BOT).

|                          | SIZE | CODE |          | REV |

|--------------------------|------|------|----------|-----|

| <br>: 16-(381)-1022-N370 |      |      | SHEET OF |     |

#### pleting that at 3

#### CONTINUATION SHEET

TITLE

#### 2.2.9 READ FORWARD/WRITE CHECK FORWARD:

The tape system makes no distinction between these commands.

The tape system reads one record. Data transmission will normally be terminated by detection of FRAME COUNT overflow. See Chapter 4 for a discussion of other causes of transmission terminations.

#### 2.2.10 READ REVERSE/WRITE CHECK REVERSE:

This operation is identical to READ (WRITE CHECK) FORWARD with the following exceptions: Massbus data transfers occur in the order shown in Chapter 6, and tape motion is on the reverse direction.

#### 2.2.11 WRITE:

Transport writes one record while moving forward. Record length is controlled by the FRAME COUNT Register. See Chapter 4 for a discussion of other types of terminations.

- 2.3 INIT: INIT differs from DRIVE CLEAR with the following aspects:

- a) INIT may be issued at any time,

- b) INIT affects all slaves, not just the selected slave;

- c) INIT clears EOF in the STATUS Register.

#### INIT resets:

GO, SLA (all slaves), SSC, EOF, IDB, ERR, and ATA in the STATUS Register; resets all but bit 6 of MAINTENANCE Register, resets FCL in TAPE CONTROL Register; resets all bits in ERROR Register except bit 14 (UNS), and resets UNS if the TMO2 is not experiencing a power-fail. INIT sets DRY. INIT, like DRIVE CLEAR, requires 2 microseconds (maximum) for completion. If the TMO2 is experiencing a power-fail when INIT is issued, ATA and ERR will be asserted at the completion of the system reset.

SIZE CODE

Δ

DEC FORM NO DEC 16-(381)-1022-N370 DRA 108

SHEET \_\_\_\_\_ OF \_

NUMBER

dry and the state

TITLE

INIT has no effect on a rewinding slave, but will halt a slave which is executing any other command.

NOTE: Issuing an INIT during a write operation ruins the record being written. The only safe recovery from INIT is a rewind.

|                        |                        | SIZE CODE NUMBER REV |

|------------------------|------------------------|----------------------|

| DEC FORM NO<br>DRA 108 | DEC 16-(381)-1022-N370 | SHEET OF             |

d fought ast

TITLE

### 3.0 Registers Implemented

3.1 The following registers will be implemented in the TU16 Tape System:

| Туре | Register | Name                   |

|------|----------|------------------------|

| R/W  | 00       | CONTROL I (CSI)        |

| Read | 01       | STATUS (DS)            |

| Read | 02       | ERROR (ER)             |

| R/W  | 03       | MAINTENANCE (MT)       |

| R/W  | 04       | ATTENTION SUMMARY (AS) |

| R/W  | 05       | FRAME COUNTER (FC)     |

| Read | 06       | DRIVE TYPE (DT)        |

| R/W  | 07       | TAPE CONTROL (TC)      |

| Read | 10       | CHECK CHARACTER (CC)   |

| Read | 11       | SERIAL NUMBER (SN)     |

|      |          |                        |

#### 3.2 Description of Control I Register

The CSI Register will be used as defined in the Massbus Specification. Loading this register with a GO Bit and a valid function code will initiate a cycle to check for the various possible error conditions and, if no errors are detected, initiate command execution.

#### 3.2.1 Bits in the Control Register

3.2.1.1 BIT 0 - GO BIT:

Loading a "1" in this bit initiates a command execution cycle. When this bit is set, the selected slave becomes busy, and no other slaves may be used. This bit is reset by the drive when the drive returns to the DRY condition. (Logical address of the current selected slave is described in TC Register discussion.) The GO bit is cleared by an INIT.

3.2.1.2 BITS 1 to 5 - F1 to F5

Function Code bits (See Section 2). INIT and DRIVE CLEAR have no effect on bits 1-5.

|                                               | size<br>A | CODE | NUMBER   | REV |

|-----------------------------------------------|-----------|------|----------|-----|

| DEC FORM NO DEC 16-(381)-1022-N370<br>DRA 108 |           |      | SHEET OF |     |

donau-Laga

TITLE

#### 3.2.1.3 BIT 11 - DRIVE AVAILABLE (DVA)

Always set in TU16.

3.2.1.4 For a description of the other CSI bits, consult the Massbus specification, and the various controller specifications.

3.3 Description of the STATUS Register:

The status register indicates the status of various sections of the drive. Individual bits which are generated in the selected slave will be followed by (SS). Bits which can be generated by any slaves will be followed by (S). Bits which are generated in the TM02 will be followed by (M).

3.3.1 Bits in the Status Register:

3.3.1.1 Bit 0 - SLAVE ATTENTION (SLA) - (SS):

Asserted by a selected slave which requires attention for one of the following reasons: REWIND completed, detection of power fail, coming ONLINE, going OFFLINE. SLA is cleared by DRIVE CLEAR or INIT (sections 2.2.4, 2.3.1).

3.3.1.2 BIT 1 - BEGINNING OF TAPE (BOT) (SS):

Asserted whenever the selected slave detects the BOT marker. INIT and DRIVE CLEAR cannot affect this bit.

3.3.1.3 BIT 2 - END OF FILE (EOF) (M):

Asserted when a filemark is detected: remains asserted until the next tape motion operation is initiated. The Phase Encoded filemark written by TU16 consists of 40 characters with zero's in tracks 1, 2, 4, 5, 7, and 8 and with tracks 3, 6, and 9 DC erased. The NRZI filemark written by the TU16 consists of a single character record followed by the LRC for that record.

SIZE CODE

А

DEC FORM NO DEC 16-(381)-1022-N370 DRA 108

SHEET \_\_\_\_\_ OF \_\_\_\_

NUMBER

il Stritter B

TITLE

The single record contains octal 023 on 9-Track slaves and octal 017 on 7-Track slaves. EOF should be high after the completion of a WRITE FILEMARK command,

INIT clears EOF, DRIVE CLEAR does not affect it.

3.3.1.4 BIT 3 - IDENTIFICATION BURST (IDB) (M):

Set on recognition of the PE identification burst. In the forward direction the bit remains set thru the READING, WRITING, OR SPACING operation. On a PE tape, IDB should be asserted after any tape motion operation which began from BOT. IDB becomes reset when another command is issued. Cleared by INIT or DRIVE CLEAR.

3.3.1.5 BIT 4 - SLOWING-SETTLING DOWN (SDWN) (SS):

This bit is set during the period when tape motion is stopping. DRY is asserted on the leading edge of SDWN. DRIVE CLEAR and INIT cannot affect this bit.

3.3.1.6 BIT 5 - PHASE ENCODED STATUS (PES) (SS):

This bit reflects the format mode in which the formatter is operating. PES originates in the selected slave and in TU16 should be identical to BIT 10 in TC register. It is asserted when selected slave in PE mode, negated when selected slave in NRZI mode. DRIVE CLEAR and INIT cannot affect this bit. (See also bits 8-10 of TAPE CONTROL Register) ter).

3.3.1.7 BIT 6 - SLAVE STATUS CHANGE (SSC) (M):

This bit is asserted and latched by the TM02 whenever any slave has an attention condition as defined in Section 3.3.1.1

SIZE CODE

A

DEC FORM NO DEC 16-(381)-1022-N370 **DRA 108**

SHEET OF

NUMBER

制、山口、白

#### CONTINUATION SHEET

TITLE

Setting SSC results in ATA becoming asserted as soon as DRY becomes asserted, (ATA becomes asserted immediately if DRY is already asserted.)

INIT always clears SSC. DRIVE CLEAR clears SSC if only the selected slave has a current attention condition. Note that power-fail in a slave is a transient attention condition, and that SSC should not be cleared before polling all slaves to confim their status.

3.3.1.8 BIT 7 - DRIVE READY (DRY) - (M):

Asserted at completion of any command. INIT sets DRY.

3.3.1.9 BIT 8 - DRIVE PRESENT (DPR) - (M):

Always asserted in the TU16 system.

3.3.1.10. BIT 9 - NEUTRAL (NTL) - (M):

Always negated in the TU16 system.

3.3.1.11 BIT 10 - END OF TAPE (EOT) - (SS):

When the EOT marker is recognized during forward tape motion, this bit is set. It is reset when the EOT Marker is passed over during reverse tape motion. DRIVE CLEAR and INIT do not affect EOT.

3.3.1.12 BIT 11 - WRITE LOCK (WRL) - (SS):

Asserted whenever a reel of tape without a write enable ring is loaded on the selected slave. DRIVE CLEAR and INIT cannot affect this bit.

3.3.1.13 BIT 12 - MEDIUM ON LINE (MOL) - (SS):

А

The selected slave is loaded and the online switch activated. This condition is necessary for response to any commands, i.e., if GO = 1 and  $MOL = \emptyset$ , command is aborted, and UNS and ATA become asserted. DRIVE CLEAR and INIT cannot affect this bit.

SIZE CODE

DEC FORM NO DEC 16-(381)-1022-N370 DRA 108 NUMBER

**~r**

$\mathbf{U}_{\mathbf{r}}(\mathbf{\hat{q}},\mathbf{\hat{r}},\mathbf{\hat{t}},\mathbf{\hat{t}},\mathbf{\hat{r}})$

TITLE

3.3.1.14 BIT 13 - POSITIONING IN PROCESS (PIP) -

Asserted during SPACE (M) and REWIND (SS) operations. Cleared by INIT during SPACE operations. Unaffected by DRIVE CLEAR or INIT during REWIND operations, DRIVE CLEAR cannot be issued during SPACE operations.

3.3.1.15 BIT 14 - COMPOSITE ERROR (ERR) - (M):

Asserted whenever any error bit in the Error (ER) register is asserted. Reset by Drive Clear or INIT. (See Sections 2.2.3.4 and 2.3.)

3.3.1.16 BIT 15 - ATTENTION ACTIVE (ATA) - (M):

See Section 5.

3.4 Description of the ERROR Register. See Section 4 for descriptions of error-handling algorithms.

3.4.1 Bits in the ERROR Register

.3.4.1.1 BIT 0 - ILLEGAL FUNCTION (ILF):

Asserted when GO bit is loaded with a "l", and BITS Fl to F5 of CSI do not denote a function implemented by the TU16. Cleared by INIT or DRIVE CLEAR.

3.4.1.2 BIT 1 - ILLEGAL REGISTER (ILR):

Asserted if the Controller addresses a register which is not implemented on the TU16. No register modification should occur. On a Control Bus read, all zeros are gated onto CONTROL lines. Cleared by INIT or DRIVE CLEAR.

SIZE CODE

Δ

DEC FORM NO DEC 16-(381)-1022-N370 DRA 108

SHEET \_\_\_\_\_ OF \_

NUMBER

0.5

TITLE

**DRA 108**

#### 3.4.1.3 BIT 2 - REGISTER MODIFICATION REFUSED (RMR):

Asserted whenever the controller attempts to write into any implemented TUL6 Register except Register 3 (Maintenance) or Register 4 (Attention Summary) while the GO bit is asserted. If RMR occurs, the addressed register is not modified; ATA becomes asserted as soon as DRY is asserted. Cleared by INIT or DRIVE CLEAR.

#### 3.4.1.4 BIT 3 - MASSBUS PARITY ERROR (PAR):

Asserted whenever a parity error is detected on the Massbus DATA Lines or CONTROL Lines when data is being transmitted from the Controller to the TM02. ATA becomes asserted as soon as DRY is asserted. No register modification should occur on CONTROL bus writes. Cleared by INIT or DRIVE CLEAR.

#### 3.4.1.5 BIT 4 - FORMAT ERROR (FMT):

Asserted whenever a data transfer command is loaded with GO = 1 and the tape format code loaded in the TC Register is not implemented on that TM02. Tape motion is inhibited; EXC and EBL are raised. DRY and ATA become asserted when EBL becomes negated. Cleared by INIT or DRIVE CLEAR.

#### 3.4.1.6 BIT 5 - FORMATTER PARITY ERROR (FPAR):

Asserted whenever a parity error is detected during the process of transforming tape word images into Massbus word images. (Will not be implemented on all tape formats.) ATA becomes asserted when DRY becomes asserted. Cleared by INIT or DRIVE CLEAR.

SIZE CODE NUMBER REV DEC FORM NO DEC 16-(381)-1022-N370 SHEET \_\_\_\_\_ OF \_

TITLE

3.4.1.7 BIT 6 - INCORRECTABLE DATA ERROR/VPE (INC/VPE):

> Asserted when performing a data transfer on a PE slave and multiple dead tracks, dead tracks without parity errors, parity errors without dead tracks, or skew overflow are detected.

> Asserted when performing a data transfer on an NRZ slave and a vertical parity error is detected. Cleared by DRIVE CLEAR or INIT.

3.4.1.8 BIT 7 - FORMAT ERROR/LRC (PEF/LRC):

In PE mode this bit is asserted whenever an invalid preamble or postamble is discovered. In NRZ mode, the bit is asserted when the LRC character generated from readback data does not match the LRC character read from tape. ATA becomes asserted when DRY becomes asserted. Cleared by INIT or DRIVE CLEAR.

#### 3.4.1.9 BIT 8 - BAD TAPE ERROR (BTE):

Asserted whenever any tape characters are read while the read head is scanning the first half of the inter-record gap. ATA becomes asserted when DRY becomes asserted. Cleared by INIT or DRIVE CLEAR.

3.4.1.10 BIT 9 - FRAME COUNT ERROR (FCE):

Asserted whenever a SPACE, READ, or WRITE terminates and the FRAME COUNTER contains any number but octal 0000. ATA becomes asserted when DRY becomes asserted. Detection of this error is affected by state of INHIBIT RECORD LENGTH ERROR and IGNORE FRAME COUNT bits in TAPE CONTROL Register. FCE cleared by INIT or DRIVE CLEAR. (See IFC bit, Section 3.9.8)

SIZE CODE

А

DEC FORM NO DEC 16-(381)-1022-N370 **DRA 108**

SHEET \_\_\_\_\_ OF

NUMBER

TITLE

# 3.4.1.11 BIT 10 - CORRECTABLE SKEW/ILLEGAL FILE MARK (CS/IFM):

In PE mode, this bit is asserted when excessive but correctable skew is detected in data read back from tape. It is a warning only, and does not indicate that bad data was read from tape.

In NRZ mode, this bit is asserted when a bit pattern is detected on tape which has the general characteristics of an NRZ filemark (specifically, a one-character record followed by another one-character record spaced an appropriate distance away from the first) but which does not contain the exact data expected in an NRZ filemark. When such a bit pattern is detected in NRZ mode, both EOF in the DS Register and CS/IFM in the ER Register will become asserted.

CS/IFM is cleared by DRIVE CLEAR or INIT. (See Figure 4.1.3.1.)

3.4.1.12 BIT 11 - NON-EXECUTABLE FUNCTION (NEF):

Asserted whenever one of the following occurs:

- 3.4.1.12.1 Write operation requested with WRL status bit asserted.

- 3.4.1.12.2 SPACE REVERSE OF READ REVERSE or WRITE CHECK REVERSE requested with BOT status bit asserted.

- 3.4.1.12.3 PE/NRZI bit loaded into TC Register does not agree with PES status bit asserted by selected slave.

|                                         |  | A | CODE | NUMBER   | REV |

|-----------------------------------------|--|---|------|----------|-----|

| DEC FORM NO DEC 16-(381)-102<br>DRA 108 |  |   |      | SHEET OF |     |

TITLE

- 3.4.1.12.4 SPACE, READ, or WRITE command is loaded with GO = 1 and FCL in TAPE CONTROL Register = Ø and IFC in TC Register = Ø.

3.4.1.12.5 READ or WRITE command is loaded

- with DEN2 in TAPE CONTROL Register = 0 and FRAME COUNT Register set to two's complement of 1 or 2 and IFC =  $\emptyset$ . (Minimum NRZ record length is 3 data characters.)

Cleared by INIT or DRIVE CLEAR.

3.4.1.13 BIT 12 - DRIVE TIMING ERROR (DTE):

Asserted whenever one of the following occurs:

- a) During a WRITE operation, a SCLK signal was generated, and a WCLK signal was not received in time to provide valid data for the next tape character written.

- b) A data transfer command was loaded into the TU16/TM02 system while OCC = 1.

Case a) can be distinguished from case b) by looking at the FRAME COUNT Register. In case a), the FC Register will have been incremented at least once since its loading. In case b), the FC Register will contain the same number with which it was loaded prior to the loading of the data transfer command. Also, DTE during a READ operation can occur only due to case b). DTE is cleared by INIT or DRIVE CLEAR.

|                        | SIZE | CODE | NUMBER   | REV |

|------------------------|------|------|----------|-----|

| DEC 16-(381)-1022-N370 |      |      | SHEET OF |     |

#### CON

CONTINUATION SHEET

TITLE

3.4.1.14 BIT 13-- OPERATION INCOMPLETE (OPI):

Asserted if no record is detected within 7 seconds after initiation of a READ or SPACE command. Asserted if no record is detected within 0.7 seconds after initiation of a WRITE command. (Initiation of a command = setting GO to 1 with bits F1 to F5 of CSI Register set to the Function Code for that command.) OPI is cleared by INIT or DRIVE CLEAR.

3.4.1.15 BIT 14 - DRIVE UNS (UNS):

Asserted if GO = 1 and MOL in ST Register =  $\emptyset$ . Also asserted if TMO2 detects imminent power-fail condition. (AC LO signal is asserted, DC LO signal not asserted. See A-SP-5409728-0-8.)

If UNS is caused by GO = 1 while MOL = 0, it is cleared by INIT or DRIVE CLEAR. If UNS is caused by a transient voltage - low condition, it can be cleared by INIT or DRIVE CLEAR when voltage returns to an acceptable level. If UNS is caused by a permanent voltage - low condition, it cannot be cleared. (See Figure 4.1.3.2.)

3.4.1.16 BIT 15 - CORRECTABLE DATA ERROR/CRC ERROR (COR/CRC):

> In PE mode, this bit becomes asserted whenever a tape parity error and a single dead track occur on the same tape character. In this case, the data bit in the dead track is inverted to correct the parity error.

In NRZ mode, this bit is asserted when the CRC character generated from readback data does not agree with the CRC read from tape.

COR/CRC is cleared by DRIVE CLEAR or INIT. (See Figure 4.1.3.1.)

|                                    | SIZE | CODE | NUMBER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | REV |

|------------------------------------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                                    |      |      | and the safety set of the start |     |

| DEC FORM NO DEC 16-(381)-1022-N370 |      |      | SHEET OF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

TITLE

3.4.2 Table 3.4.2 describes those errors which might reasonably be detected during normal operation of the TU16/TM02 system.

|        | ng ng ng ng také tang ng také tang ng n |                    |                                                                             | SIZE                                | CODE | NUMBER  | REV |

|--------|--------------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------|-------------------------------------|------|---------|-----|

| DEC FO | RM NO DEC                                                                | 16-(381)-1022-N370 | n ga kun nangan kun nangan kun nangan kan kan kan kan kan kan kan kan kan k | 27 R.P.B. (La King) & D.L. MAL 7047 |      | SHEET O | F   |

|               |       |                               | 6-1+ - G |       |           |       |                                            |      |         |         |                    |      |        |        | -  | 7. 18 b.b. 9 |                |             |                      |        | <b>2</b> %     |

|---------------|-------|-------------------------------|----------|-------|-----------|-------|--------------------------------------------|------|---------|---------|--------------------|------|--------|--------|----|--------------|----------------|-------------|----------------------|--------|----------------|

| IN SHEET      |       | OPERATIONS                    | 4        | ILR   | RMR       | PAR   | FMT                                        | FPAR | INC/VPE | PEF/LRC | BTE                | FC F | CS/IFM |        |    | TdO          | U NS           | COR/CRC     | ¥ Except<br>As or MT | ER REV | 0F             |

| CONTINUATION  |       | WRITE TO ANY REGISTER *       |          | X     | X         | X     |                                            |      |         | ·       |                    |      |        |        |    |              |                |             |                      | NUMBER |                |

| NU            |       | READ FROM ANY REGISTER        |          | X     |           |       |                                            |      |         |         |                    |      |        |        |    |              |                |             |                      | N I    | SHEET          |

| NTI           |       | LOAD NO-OP WITH GO=1          | X        | X     | X         | X     |                                            |      |         |         |                    |      |        | X      |    |              | X              | 1<br>1<br>1 |                      |        | HS             |

| ပိ            |       | LOAD REWIND OFF LINE WITH GOT | X        | X     | X         | X     |                                            |      |         |         |                    |      |        | X      |    |              | X              |             |                      |        |                |

|               |       | " REWIND " GO=1               | X        | X     | X         | X     |                                            |      |         |         |                    |      |        | X<br>X |    |              | X              |             |                      | DE     |                |

|               |       | " DRIVE CLEAR "GO=1           | X        | X     | X         | X     |                                            |      |         |         |                    |      |        |        |    |              | X              |             |                      | CODE   |                |

|               |       | WRITE FMK "GO=1               | X        | X     | X         | X     |                                            |      | X       | X       | X                  | X    | X      | X      |    | X            | X              |             |                      |        |                |

|               |       | " ERASE " GO=1                | X        | Х     | X         | X     |                                            |      | X       | X       | X                  | X    | X      | X      |    |              | X              |             |                      | sıze   |                |

|               |       | " SPACE FWD "GO=1             | X        | X     | X         | Х     |                                            |      |         |         |                    | X    | X      | X      |    | X            | X              |             |                      |        |                |

|               |       | " SPACE REV " GO=1            | X        | X     | X         | X     |                                            |      |         |         |                    | X    | X      | X      |    | X            | X              |             |                      |        |                |

| Z             |       | WRITE CHECK FWD "60=1         | XX       | X     | X         | X     | X                                          | X    | X       | X       | X                  | X    | X      | X      | X  | X            | X              | X           |                      |        |                |

| 0             |       | " WRITE CHECK REV" GO=1       | X        | X     | X         | X     | X                                          | X    | X       | X       | X                  | X    | X      | X      | X  | X            | X              | X           |                      |        |                |

| L             |       | " WRITE FWD "GO=1             | X        | X     | Х         | X     | X                                          | X    | X       | X       | X                  | X    | X      | X      | X  | X            | X              | X           |                      |        |                |

| C             |       | " READ FWD " GO=              | X        | X     | Х         | X     | X                                          | X    | X       | X       | X                  | X    | X      | X      | X  | X            | X              | X           |                      |        |                |

| 4             |       | " READ REV "GO=1              | X        | X     | X         | X     | X                                          | X    | X       | X       | Х                  | X    | X      | X      | X  | X            | X              | X           |                      |        |                |

| 2             |       | MASS BUS INIT                 |          |       | 1         |       |                                            |      |         |         |                    |      |        |        |    |              | X              |             |                      |        | N37(           |

| SPECIFICATION |       | WRITE TO AS OR MTREG          |          | X     |           | X     |                                            |      |         |         | $s_{ij}^{(i)} = 1$ |      |        |        |    |              |                |             |                      |        | 022-           |

|               |       |                               |          | i i i |           | •     |                                            |      |         |         |                    |      | -      | •      | •  |              |                |             |                      |        | [-[            |

| NO<br>NO      |       | TABLE 3.4.2 : TM              | 0        | 2     | 0         | )E    | RA                                         | 1T   | 10      | N (     | S                  | W    | /17    | H      | F  | ER           | RC             | RS          | S                    |        |                |

| 8             |       | WHICH COULD BE                | מ        | CT    | · E /     |       |                                            | D    | D       |         | 218                | de   | -7     | -11    | 20 | cr           |                |             |                      |        | C 16           |

| ш             |       |                               |          |       | · • .     |       |                                            |      |         |         |                    |      |        |        |    |              |                |             |                      |        | DEC            |

| ENGINEER      |       | OPERATIONS AND                | R        | E N   | AA        | IN    | <b>V</b>                                   | Á    | 55      | E       | RT                 |      | D      | A      | FI | Έ            | R              |             | τE                   |        | FORM NO<br>108 |

| 0             | w     | OPERATION IS CO               | M        | PI    | FT        | r F   | er a la l |      |         |         |                    | •    | 1      |        |    |              |                |             |                      |        | ORN<br>08      |

| Lu I          | TITLE |                               |          | • 64  | a Brian I | * 6-4 |                                            |      |         |         |                    |      |        |        |    |              | •              | ;           |                      |        | DEC F          |

| -             |       |                               |          |       |           |       |                                            |      |         |         |                    |      | -      |        |    |              | and the second |             |                      |        |                |

d eq. Call

TITLE

**DRA 108**

Description of MAINTENANCE (MT) Register 3.5

The MT Register will serve in the following capacity:

- It will provide data wraparound paths for checking the **a)** various sections of the data formatting logic in the TM02.

- b) It will provide a means for testing error detection circuitry within the TM02.

- It will act as a storage buffer for the Longitudinal c) Parity Check (LRC) Character when operating in NRZ mode.

Bits in the MT Register are allocated in the following manner:

3.5.1 BIT  $\emptyset$  - Maintenance Mode (MM)

Must be written to 'l' when any Maintenance Mode function is desired. Setting the MM bit to 'l' does not initiate any action on the part of the drive, but rather alters the manner in which the drive executes various commands. The manner in which command execution is altered depends on the Maintenance operation code resident in bits 1-4 of the MT Register.

The MM bit is cleared by DRIVE CLEAR or INIT.

3.5.2 BITS 1 to 4 - Maintenance Op Code bits (MOP  $\emptyset$ -3):

These bits control the Maintenance function which will occur when the MM bit is set to 'l' and the TM02 is loaded with the appropriate command.

MOP  $\emptyset$ -3 are cleared by DRIVE CLEAR or INIT.

3.5.3 BIT 5 - Maintenance Mode Clock (MC)

This bit controls the sequencing of data through the TM02 data paths when operating in Maintenance mode. Cleared by DRIVE CLEAR or INIT, or by writing the MM bit to 'Ø'.

|                                    | SIZE | CODE | NUMBER   | REV |

|------------------------------------|------|------|----------|-----|

| DEC FORM NO DEC 16-(381)-1022-N370 |      |      | SHEET OF |     |

#### an man a

### CONTINUATION SHEET

TITLE

### 3.5.4 BIT 6 - Selected Slave Clock (SCK):

This bit displays the signal WRT CLK, which is transmitted to the TMO2 from the selected slave. The frequency of this clock is dependent both upon the Density Select bits located in bits 8-10 of the Tape Control Register and upon the operating speed of the selected slave. Its purpose is to enable a check on the proper decoding of the Density Select bits by the selected slave.

This bit cannot be cleared.

3.5.5 BITS 7 to 15 - Maintenance Data Field (MDF  $\emptyset$ -8):

These bits act as a buffer for data generated during checks of the TMO2 data paths.

In addition, at the end of data transfer operations in NRZ mode, this field holds the LRC character for the last record read.

MDF  $\emptyset$  contains the parity bit for the maintenance data character. MDF 1 contains the least significant bit of the maintenance data character, and the remaining higher order bits are contained, in order, in MDF 2 through 8.

|                        |                        | SIZE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | NUMBER   | REV |

|------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----|

| DEC FORM NO<br>DRA 108 | DEC 16-(381)-1022-N370 | 2,21,9, <u>11,91</u> , <b>1</b> ,977, 97, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, 98,877, | SHEET OF |     |

#### all the Lot

TITLE

#### 3.6 ATTENTION SUMMARY Register

This Register will be handled in accordance with the Massbus Specification. During a Control Bus write to Register 04, the Control line corresponding to the TM02's logical address on the Massbus will be gated to the ATA bit. During a ControlBus read of Register 04, the TM02's ATA bit will be gated onto the C line corresponding to the TM02's logical address on the Massbus. For further discussion of the ATA bit, see Section 4.

3.7 Description of the FRAME COUNT Register

> The frame counter does exactly what its name implies: it counts tape frames.

During a data transfer operation, it is incremented each time a six-bit (for 7-track operation) or 8-bit (for 9-track operation) character is transferred to (write) or from (read) tape. During a SPACE operation, the frame counter is incremented once each time a record is detected on tape.

3.7.1 Frame Counter Operation During WRITE's:

Before a WRITE operation is initiated, the Frame Counter must be loaded with the 2's complement of the number of tape characters to be written. (The ratio of actual tape characters written on tape to processor core words involved in the transfer will depend on the tape format used.) Each time a tape character is written, the frame counter will be incremented. In normal circumstances a write operation will terminate when the frame counter overflows to zero.

#### 3.7.2 Frame Counter Operation During READ:

Before a READ operation can be initiated, the Frame Counter must be loaded with the 2's complement of the number of tape characters to be read. The counter is incremented each time a tape character is read. In normal circumstances, the TMO2 read timing section will detect the end of a record after the frame counter overflows to zero.

|                                    | A | CODE | NUMBER | REV |

|------------------------------------|---|------|--------|-----|

| DEC FORM NO DEC 16-(381)-1022-N370 |   |      | CUEET  | 0E  |

SHEET \_\_\_\_\_ OF \_\_\_\_

TITLE

3.7.3 Frame Counter Operation During Spacing Function

Before a Spacing Operation is initiated, the Frame Counter must be loaded with the 2's complement of the number of <u>records</u> to be spaced over. In normal circumstances a spacing operation will terminate when the frame counter overflows to zero.

3.7.4 Errors Related to Frame Counter

See NEF and FCE bits described in Section 3.4. See also IFC bit desribed in Section 3.9.8.

3.7.5 Clearing the Frame Counter

The Frame Counter will be cleared by writing zeros into it. DRIVE CLEAR and INIT cannot affect the bits of the Frame Counter.

3.8 DRIVE TYPE Register

The DT Register will be used to provide the following information:

- a) Number of slaves available in the TU16/TM02 system.

- b) Number and type of slaves which are in the power-on state.

- c) Standardized Massbus data field indicating the TU16/TM02's physical characteristics (bits 11-15).

- Bit assignments in the DT Register are the following:

3.8.1 Bits 0 to 8: DRIVE TYPE NUMBER (DT 0-8):

Contains the drive type number for the selected slave. If no slave has been assigned the select code resident in bits 0-2 of the TAPE CONTROL Register, the drive type code readback will be  $010_8$ . If a slave has been assigned the select code resident in bits 0-2 of the TC Register but is not in the power-on state, the drive type code will be  $010_8$ . If a slave has been assigned the select code resident in bits 0-2 of the TC Register and has power-on, the drive type code will be  $01X_8$ ,  $0 \leq X \leq 7$ .

|                                    | SIZE | CODE | NUMBER                                                                                            | REV |

|------------------------------------|------|------|---------------------------------------------------------------------------------------------------|-----|

|                                    | A    |      | nen al general els con trents y the constant offer the constants 2 (2 - 2 - 2 ) (2 - 2 ) (2 - 2 ) |     |

| DEC FORM NO DEC 16-(381)-1022-N370 |      |      | SHEET OF                                                                                          |     |

| ENGINEERING | SPECIFICATION                                                                                                                   | SUSSAIN                                                | CONTINUATION                                                       | I SHEET                    |

|-------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------|----------------------------|

| TITLE       |                                                                                                                                 |                                                        |                                                                    |                            |

|             | I                                                                                                                               | ,                                                      |                                                                    |                            |

| •           | The drive type cod<br>011 <sub>8</sub> . Neither INI<br>DTO-8.                                                                  | -                                                      |                                                                    |                            |

| 3.8.2       | 2 Bit 9 - spare                                                                                                                 |                                                        |                                                                    |                            |

|             | This bit is always                                                                                                              | negated.                                               |                                                                    | •<br>•<br>•                |

| 3.8.3       | B Bit 10 - SLAVE PRE                                                                                                            | SENT (SPR)                                             |                                                                    |                            |

|             | If a slave has been<br>dent in bits 0-2 of<br>asserted (even if<br>state). Otherwise<br>INIT nor DRIVE CLEA                     | f the TC Re<br>that slave<br>, this bit                | gister, this l<br>is not in a po<br>is negated. l                  | oit is<br>ower-on          |

| 3.8.4       | Bit 11 - DRIVE REQU                                                                                                             | UEST REQUIR                                            | ED (DRR):                                                          |                            |

|             | Never asserted in                                                                                                               | rul6/TMO2 s                                            | ystem.                                                             |                            |

| 3.8.5       | 5 Bit 12 - SEVEN CHAN                                                                                                           | NNEL (7CH)                                             |                                                                    |                            |

|             | Asserted if the set<br>unit. Negated if<br>channel unit. Also<br>either is not in a<br>physically present<br>INIT nor DRIVE CLE | the selecte<br>o negated i<br>power-on s<br>on the TMO | d slave is a s<br>f the selected<br>tate or else s<br>2-slave bus. | nine-<br>d slave<br>is not |

| 3.8.6       | 5 Bit 13 - MOVING HE                                                                                                            | AD (MOH):                                              |                                                                    |                            |

|             | Never asserted in                                                                                                               | TU16/TM02 s                                            | ystem.                                                             |                            |

| 3.8.        | 7 Bit 14 - TAPE (TAP                                                                                                            | ):                                                     |                                                                    |                            |

|             | Always asserted in                                                                                                              | TU16/TM02                                              | system.                                                            |                            |

| 3.8.8       | Bit 15 - NOT SECTO                                                                                                              | R ADDRESSED                                            | (NSA):                                                             |                            |

|             | Always asserted in                                                                                                              | TU16/TM02                                              | system.                                                            | •                          |

|             |                                                                                                                                 |                                                        |                                                                    |                            |

|   |  |  |                            |      |      |        | · |

|---|--|--|----------------------------|------|------|--------|---|

| • |  |  |                            |      |      |        |   |

|   |  |  | a national locality for an | SIZE | CODE | NUMBER | R |

TITLE

3.9 TAPE CONTROL Register

Bit assignments in the TC Register are the following.

3.9.1 Bits 0 to 2 - SLAVE SELECT CODE:

Specifies select code of selected slave. Unaffected by INIT or DRIVE CLEAR.

3.9.2 Bit 3 - EVEN PARITY

When this bit is written to 'l', even parity will be written on tape, and even parity will be expected when data is read.

This bit is ignored in Phase Encoded (PE) mode. Neither INIT nor DRIVE CLEAR affect this bit.

3.9.3 FORMAT SELECT CODE:

These bits determine the manner in which Massbus Data Characters will be mapped to tape characters during WRITE operations and in which tape characters will be mapped to Massbus Characters during READ operations.

Format codes are:

| 0000 - | PDP-10 | FORMAT: | '10-CORE DUMP'  |

|--------|--------|---------|-----------------|

| 0001 - | PDP-10 | FORMAT: | '10-7 TRACK'    |

| 0010 - | PDP-10 | FORMAT: | '10-ASCII'      |

| 0011 - | PDP-10 | FORMAT: | '10-COMPATIBLE' |

| 0110 - | PDP-8  | FORMAT: | '8 9-TRACK'     |

| 0111 - | PDP-8  | FORMAT: | '8 7-TRACK'     |

| 1100 - | PDP-11 | FORMAT: | '11-NORMAL'     |

| 1101 - | PDP-   | FORMAT: | '11-CORE DUMP'  |

| 1110 - | PDP    | FORMAT: | '15-NORMAL'     |

| 1111 - | PDP-   | FORMAT: | RESERVED        |

|        |        |         |                 |

Formats 0000 to 0011 will be implemented in TM02's containing an M5907 data formatting module. (NOTE: FORMAT CODE 0001 may not be used with a slave which has been programmed to operate in phase-encoded mode.)

SIZE CODE

NUMBER

| ·             |      |    |                        |                    |                                            |                             | A |                                                                                                                  |                                             |    |

|---------------|------|----|------------------------|--------------------|--------------------------------------------|-----------------------------|---|------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----|

| Second Second |      |    | Production of the last |                    | and the second second second second second | ALL DE MUNICIPAL CONTRACTOR |   | and the second | THE REPORT OF THE PARTY OF THE PARTY OF THE |    |

| DEC           | FORM | NO | DEC                    | 16-(381)-1022-N370 |                                            |                             |   |                                                                                                                  | CHEET                                       | OF |

| DRA           | 108  |    |                        |                    |                                            |                             |   |                                                                                                                  | SULLI                                       |    |

For-

TITLE

mats 1100 to 1111 will be implemented on TM02's containing an M5906 data formatting module. Codes not listed here are not implemented.

If the FORMAT SELECT bits specify a format not implemented on a given TU16/TM02 system, and a valid data transfer command is loaded into the CSI Register setting GO = 1, then FORMAT ERROR (FMT, bit 4 of ER Register) will become asserted, and the operation will be aborted.

Neither INIT nor DRIVE CLEAR affects the FORMAT SELECT bits.

3.9.4 Bits 8 to 10 - DENSITY SELECT CODE:

These bits determine the density of data which will be written on tape during WRITE operations and which will be expected of data read back from tape during READ operations.

| BIT | 10 | BIT | 9 | BIT | 8 | · · · · |      |     |

|-----|----|-----|---|-----|---|---------|------|-----|

| DEN | 2  | DEN | 1 | DEN | ø | DEI     | NSIT | Z   |

| 0   |    | 0   |   | 0   |   | 200     | BPI  | NRZ |

| 0   |    | 0   |   | 1   |   | 556     | BPI  | NRZ |

| 0   |    | 1   |   | .0  |   | 800     | BPI  | NRZ |

| 0   |    | 1   |   | 1   |   | 800     | BPI  | NRZ |

| 1   |    | 0   |   | 0   |   | 1600    | BPI  | NRZ |

| 1   |    | 0   |   | 1   |   | 1600    | BPI  | PE  |

| 1   |    | 1   |   | 0   |   | 1600    | BPI  | PE  |

| 1   |    | 1   | * | 1   |   | 1600    | BPI  | PE  |

|     |    |     |   |     |   |         |      |     |

Neither DRIVE CLEAR nor INIT affects the DENSITY SELECT bits.

3.9.5 Bit 11 - INHIBIT FCE ON SHORT RECORD

This bit, when written to 'l', will inhibit the setting of the FRAME COUNT ERROR bit (FCE, bit 9 of ER Register) when end of record is detected before Frame Count overflow occurs.

SIZE

CODE

NUMBER

REV

DEC FORM NO

DEC 16-(381)-1022-N370

SHEET \_\_\_\_\_ OF \_\_\_\_

TITLE.

NOTE: In some cases the controller will not respond to the TM02's assertion of END OF BLOCK (EBL: Consult Massbus Specification) by dropping the RUN line (again, consult Massbus Specification). Should this occur, the TM02 will assert FRAME COUNT ERROR, indicating to the controller that the TM02 has completed command execution. Consult the programming manual for the various Massbus Controllers for further details. Neither INIT nor DRIVE CLEAR affects this bit.

3.9.6 Bit 12 - ENABLE ABORT ON WRITE ERROR:

This bit, when written to '1', will cause a write operation to be aborted as soon as one of the following errors is detected:

- a) Parity error on Massbus Data Bus;

- b) COR/CRC, bit 15 of ER Register;

- c) FMT/LRC, bit 7 of ER Register;

- d) INC/VPE, bit 6 of ER Register;

- e) FPAR, bit 5, ER Register;

Neither DRIVE CLEAR nor INIT affects this bit.

3.9.7 Bit 13 - FRAME COUNT LOADED (FCL)

This bit becomes set to 'l' at the completion of a Massbus Control Bus write to the FC Register. It becomes reset when the FC Register is clocked from the all-l's state to the all-O's state. INIT and DRIVE CLEAR both cause this bit to become reset. Unless the IGNORE FRAME COUNT BIT is set, loading any SPACE, READ, or WRITE command with GO = 1 while FCL = 0 will cause NON-EXECUTABLE FUNCTION (NEF, bit 11 of ST Register) to become asserted and will cause command execution to be aborted. No tape motion will occur.

|                                               | SIZE CO |          | REV |

|-----------------------------------------------|---------|----------|-----|

| DEC FORM NO DEC 16-(381)-1022-N370<br>DRA 108 |         | SHEET OF |     |

TITLE

3.9.8 Bit 14 - IGNORE FRAME COUNT (IFC):

> When asserted, this bit inhibits all checks on the FRAME COUNT Register and FCL bit, allowing execution of SPACE, READ, or WRITE operations to commence regardless of the status of the FC Register or the FCL bit.

When IFC is asserted, READ operations will not terminate until the TMO2 detects the end of a record on tape. No check on record length will be made. READ operations which take place with IFC = 1 will not terminate with FCE = 1 unless the condition described in section 3.9.5 occurs. When IFC is asserted, READ or SPACE operations will still be terminated by FRAME COUNT overflow.

Neither DRIVE CLEAR nor INIT affects IFC.

3.9.9 Bit 15 - spare

3.10 CHECK CHARACTER REGISTER

3.10.1 CHECK CHARACTER DATA FIELD ( $CCD\emptyset$ -8)

After the completion of a READ or WRITE operation, this field contains either:

- a) In P.E. mode, the contents of the dead track register, or

- b) In NRZ mode, the contents of the LRC character.

SIZE CODE

3.10.1.1 Dead Track Register Operation

Consider a tape on which data has been recorded on all nine tracks and which has itself been mounted on a tape transport. Assign track numbers to the various data tracks: let track 1 be the data track farthest from the tape transport chassis; let track 9 be the data track closest to the tape transport chassis. Tracks 2 through 8 are arranged in numerical order between tracks 1 and 9.

| DEC | FORM | DEC 16-(381)- |  |

|-----|------|---------------|--|

| DRA |      |               |  |

SHEET \_\_\_\_\_ OF

NUMBER

TITLE

If, while reading a P.E. data record, the read circuitry examining track 1 detects either transient or total loss of signal, a '1' will be stored in bit  $\emptyset$  of the Dead Track Register. This '1' will be transferred (when the operation is complete) into CCD $\emptyset$  of the CC Register.

Similarly, a dropped bit or bits in Track 5 (the middle data track) will cause a 'l' to be stored in CCD4 at the end of the operation.

The relationship between track numbers and the binary weight of a bit stored in that track is as follows:

| TRACK NUMBER | BINARY WEIGHT  |

|--------------|----------------|

| 1            | 20             |

| 2            | 2 <sup>2</sup> |

| 3            | 2 <sup>4</sup> |

| 4            | P              |

| 5            | 2 <sup>5</sup> |

| 6            | 26             |

| 7            | 2/             |

| 8            | 2 <sup>1</sup> |

| 9            | 23             |

|              |                |

#### 3.10.1.2 CRC Character Storage

At the end of an NRZ READ or WRITE operation, the CRC parity bit will be stored in CCD8. The least significant bit will be stored in CCDØ, most significant in CCD7.

3.10.1.3

CAUTION: The CHECK CHARACTER register will contain the check characters described above at the end of a READ or WRITE operation when DRY changes from  $\emptyset$  to 1. CCD $\emptyset$ -8 will be guaranteed true only as long as DRY remains equal to 1.

|                                               |                                                                                                                  | SIZE COL                                                                                                        |          | REV |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------|-----|

| DEC FORM NO DEC 16-(381)-1022-N370<br>DRA 108 | e desindent of her checks where the set of the | nago Jan Jan Wey, kan ang sinis pada da Kang Kang da Ka | SHEET OF |     |

CONTINUATION SHEET

TITLE

3.11 SERIAL NUMBER Register

3.11.1 BITS 0 to 3 - SNØ1, SNØ2, SNØ4, SNØ8:

Least significant digit of DEC Serial Number of selected slave (BCD).

3.11.2 BITS 4 to 15 - SN11 to SN18, SN21 to SN28, SN31 to SN38:

Next three digits of DEC Serial Number of selected slave (BCD).

|                        | A | CODE |          | REV |

|------------------------|---|------|----------|-----|

| DEC 16-(381)-1022-N370 |   |      | SHEET OF |     |

|                 |       |        |                  |             |              |            |                                        |             |            |                                        |             |                 |                 |                 |                                       |                                 |                  |                             | •                                     |        |         |                       |          |              |

|-----------------|-------|--------|------------------|-------------|--------------|------------|----------------------------------------|-------------|------------|----------------------------------------|-------------|-----------------|-----------------|-----------------|---------------------------------------|---------------------------------|------------------|-----------------------------|---------------------------------------|--------|---------|-----------------------|----------|--------------|

|                 |       |        |                  | 15          | 14           | 1.3        | 12                                     | ++          | 10         | 9                                      | 8           | 7               | 6               | .5              | 4                                     | ŝ                               | 2                | ,                           | Ø                                     | 1      |         |                       | REV      | <u>ו</u> ון  |

| SHEET           |       |        | Øð<br>CONTROL    |             | -            | -          | -                                      | DYA         |            |                                        |             | -               | -               | F 5             | F٩                                    | F3                              | FZ               | FI                          | GO                                    |        |         |                       | <u>~</u> | 0F           |

| CONTINUATION SI |       |        | Ф 1<br>STATUS    | ATA         | ERR          | PIP        | mol                                    | WRL         | EOT        | NTL                                    | DPR         | 1. R.Y          | ssc             | PES             | SDWN                                  | 103                             | FOF              | Вот                         | SLA                                   |        | × .     |                       | NUMBER   |              |

| NNI             |       |        |                  |             | ·<br>·       | ·····      | ************************************** | 4           | *          | ************************************** | •           | ****            |                 | **********      | <b>∳∼∽</b> ∼∽∽∽                       | 9 · · · · · · · · · · · · · · · |                  | *                           | ·····                                 | •      | SHOW    |                       | N        | SHEET        |