# TK50 Tape Drive Subsystem

**Technical Manual**

# TK50 Tape Drive Subsystem

**Technical Manual**

Prepared by Educational Services of Digital Equipment Corporation 1st Edition, July 1985

Copyright O 1985 by Digital Equipment Corporation. All Rights Reserved. Printed in U.S.A.

The reproduction of this material, in part or whole, is strictly prohibited. For copy information, contact the Educational Services Department, Digital Equipment Corporation, Maynard, Massachusetts 01754.

The information in this document is subject to change without notice. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

CompacTape is a shared trademark of Digital Equipment Corporation and Minnesota Mining and Manufacturing Company.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts.

| digital | DECwriter | P/OS         | UNIBUS         |

|---------|-----------|--------------|----------------|

| DEC     | DIGITAL   | Professional | VAX            |

| DECmate | LA        | Rainbow      | VMS            |

| DECnet  | MASSBUS   | RSTS         | VT             |

| DECUS   | PDP       | RSX          | Work Processor |

|         |           |              |                |

#### CONTENTS

# CHAPTER 1 INTRODUCTION AND SPECIFICATIONS

| 1.1 | General                                      | 1-1 |

|-----|----------------------------------------------|-----|

| 1.2 | TK50 Tape Drive Unit Specifications          | 1-2 |

| 1.3 | Drive to Controller Interface Specifications | 1-2 |

# CHAPTER 2 DRIVE UNIT THEORY OF OPERATION

| 2.1     | General                                  | 2-1                        |

|---------|------------------------------------------|----------------------------|

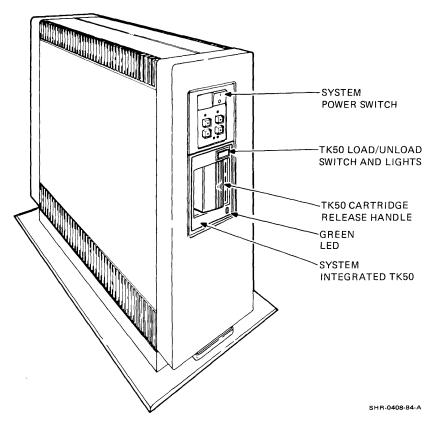

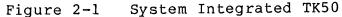

| 2.2     | Unit Designations                        | 2-1                        |

| 2.2.1   | Drive Unit Variations                    | 2-1                        |

| 2.2.2   | M7546 Controller                         | 2-2                        |

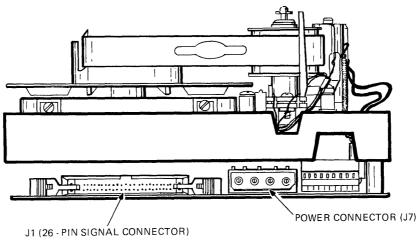

| 2.3     | Cabling                                  | 2-3                        |

| 2.4     | Power                                    | 2-4                        |

| 2.5     | Physical Description                     | 2-4                        |

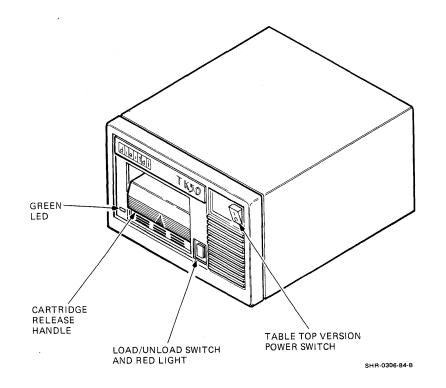

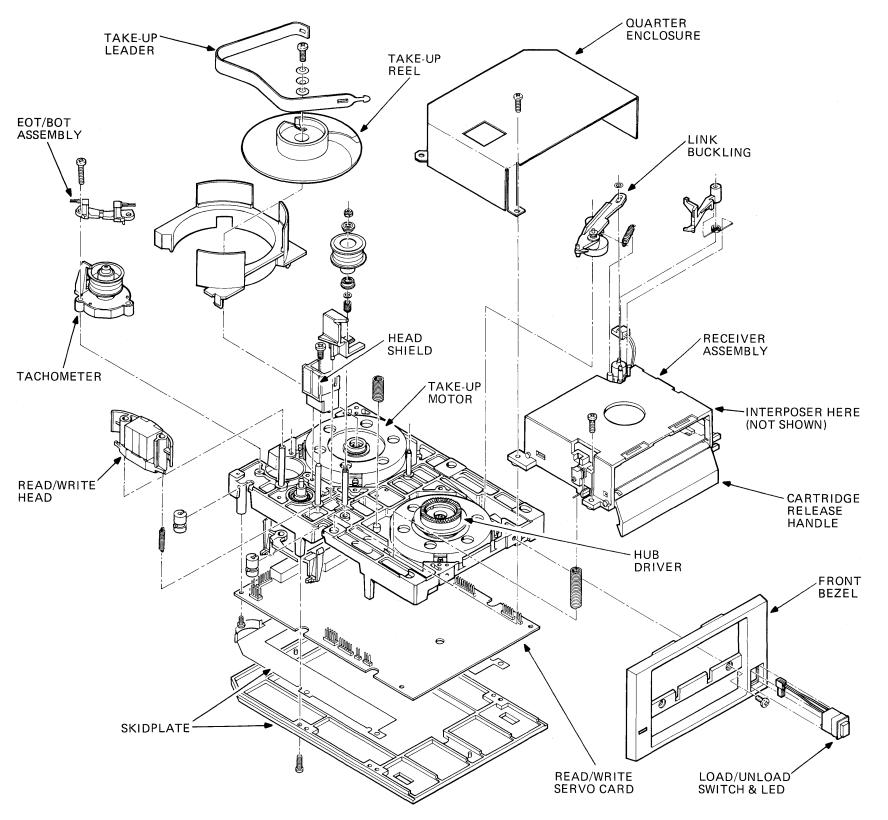

| 2.5.1   | Drive Board                              | 2-5                        |

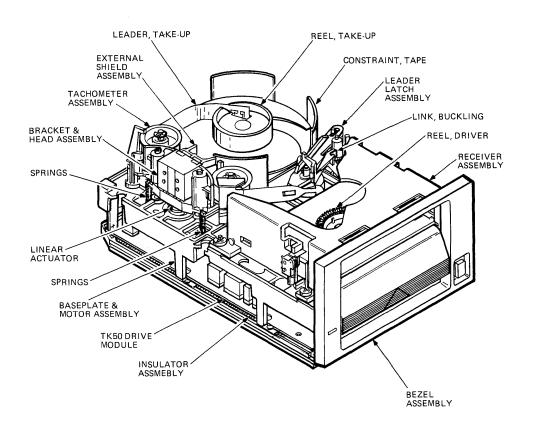

| 2.5.2   | Tape Transport                           | 2-6                        |

| 2.6     | Controls and Indicators                  | 2-6                        |

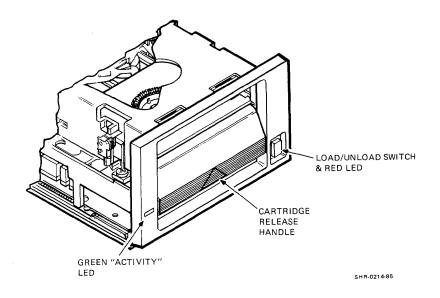

| 2.6.1   | Load Procedures                          | 2-7                        |

| 2.6.2   | Unload Procedures                        | 2-8                        |

| 2.6.3   | Lights                                   | 2-9                        |

| 2.7     | Drive Board Description                  | 2-10                       |

| 2.7.1   | Write Data Chain                         | 2-10                       |

| 2.7.2   | Write Erase                              | 2 - 11                     |

| 2.7.3   | Write Head Selection                     | $\bar{2} - \bar{1}\bar{1}$ |

| 2.7.4   | DC Low Circuit                           | 2 - 12                     |

| 2.7.4.1 | +12 Volt Path                            | 2 - 12                     |

| 2.7.4.2 | +5 Volt Path                             | 2 - 12                     |

| 2.7.4.3 | Low Voltage Effect                       | 2-13                       |

| 2.7.5   | DAC Reference Voltage Generation Circuit | 2-13                       |

| 2.7.6   | Automatic Gain Control Circuit           | 2 - 14                     |

| 2.7.7   | Read Head Select Circuitry               | 2 - 14                     |

| 2.7.8   | Read Amplifier Circuit                   | 2-15                       |

| 2.7.9   | Phase Lock Loop Circuit                  | 2-16                       |

| 2.7.10  | Pump Down Circuit                        | 2-16                       |

| 2.7.11  | Pump Up Circuit                          | 2 - 17                     |

| 2.7.12  | VCO Generation                           | 2 - 17                     |

| 2.7.13  | Pump Up and Pump Down Signal Generation  | 2-18                       |

| 2.7.14  | Data Detection                           | 2-19                       |

| 2.7.15  |                                          | 2-19                       |

| 2.8      | Tape Hub                                         | 2-20 |

|----------|--------------------------------------------------|------|

| 2.9      | Link Arms                                        | 2-20 |

| 2.10     | Tape Cartridge Insertion                         | 2-20 |

| 2.11     | Tape Load to Beginning of Tape                   | 2-20 |

| 2.12     | Tape Motion                                      | 2-21 |

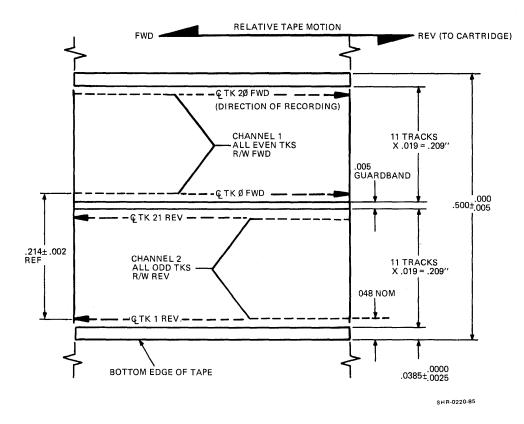

| 2.13     | Read/Write Head                                  | 2-21 |

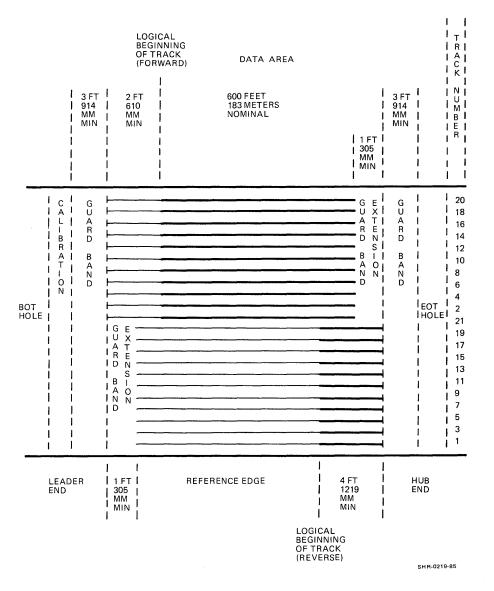

| 2.14     | Initialization: Writing and Reading CALTRACKS    | 2-21 |

| 2.15     | Writing Data                                     | 2-23 |

| 2.16     | Differential Signal Pair Description             | 2-26 |

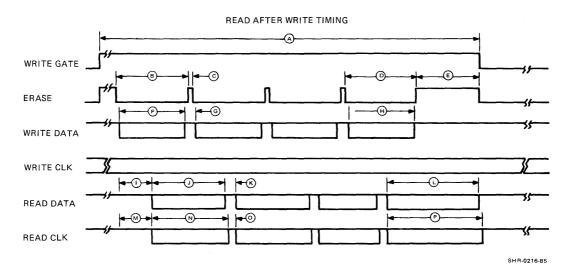

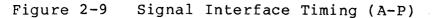

| 2.17     | Signal Interface Timing                          | 2-26 |

| 2.18     | Serial Controller to Drive Communications        | 2-29 |

| 2.19     | Basic Controller/Drive Communications Protocol . | 2-29 |

| 2.19.1   | Controller-to-Drive Command Protocol             | 2-30 |

| 2.19.2   | Drive-to-Controller Status Protocol              | 2-30 |

| 2.19.2.1 | Change of Drive State                            | 2-30 |

| 2.19.2.2 | Drive Detected Errors                            | 2-30 |

| 2.20     | TK50 Commands                                    | 2-31 |

| 2.21     | TK50 Drive States                                | 2-32 |

| 2.21.1   | Drive State Status                               | 2-32 |

| 2.21.1.1 | Done                                             | 2-33 |

| 2.21.1.2 | Enable Write Gate                                | 2-33 |

| 2.21.1.3 | Dropout Sensed                                   | 2-33 |

| 2.21.1.4 | Track Boundary                                   | 2-33 |

| 2.21.1.5 | Load/Run State Change                            | 2-33 |

| 2.21.2   | Drive Error Status                               | 2-34 |

|          |                                                  | - 01 |

# CHAPTER 3 DRIVE UNIT REPAIR

| 3.1    | General                                            | 1 |

|--------|----------------------------------------------------|---|

| 3.2    | Error Codes 3-3                                    | 1 |

| 3.2.1  | Failure to Load to Beginning of Tape 3-            | 1 |

| 3.2.2  | Failure to Load Tape into Cartridge 3-2            | 2 |

| 3.2.3  | General Motor or Tachometer Failure 3-2            | 2 |

| 3.2.4  | Motor A Failure 3-:                                | 3 |

| 3.2.5  | Motor B Failure 3-:                                | 3 |

| 3.2.6  | Drive Lost Control of Tape or Bad Tachometer . 3-3 | 3 |

| 3.2.7  | Excessive Drag in Tape Transport                   | 4 |

| 3.2.8  | Failure to Stop Tape or Remain Stopped 3-4         | 4 |

| 3.2.9  | Cartridge Insert Error 3-!                         | 5 |

| 3.2.10 | Cartridge Extract Error 3-!                        | 5 |

| 3.2.11 | Move Error                                         | 6 |

| 3.2.12 | Deceleration Error                                 | 6 |

| 3.2.13 | Reel Error 3-0                                     | б |

| 3.2.14 | Check Byte Error 3-                                | 7 |

| 3.2.15 | Unload Error 3-                                    | 7 |

| 3.2.16 | 8155 Memory Error 3-                               | 7 |

| 3.2.17 | 8155 Timer Error 3-3                               | 8 |

| 3.2.18 | Read Head 1 Error 3-3                              | 8 |

| 3.2.19 | Read Head 2 Error 3-8                              | 8 |

| 3.2.20 | Cartridge Insert/Extract Error                     | 9 |

| 3.2.21 | EOT Sensed in Read/Write/Seek State 3-             | - |

| 3.2.22 | BOT Sensed in Read/Write/Seek State                | 0 |

| 3.2.23 | Address Overflow Error                   | 3-10 |

|--------|------------------------------------------|------|

| 3.2.24 | Address Underflow Error                  | 3-11 |

| 3.2.25 | Servo Error                              | 3-11 |

| 3.2.26 | Failure in Tracking                      | 3-11 |

| 3.2.27 | Command Error                            | 3-12 |

| 3.2.28 | Illegal Command                          | 3-12 |

| 3.2.29 | Write Lock Error                         | 3-12 |

| 3.2.30 | Write Gate Signal Timing Error           | 3-13 |

| 3.2.31 | No Write Gate Error                      | 3-13 |

| 3.2.32 | Error Sensing CALTRACK1                  | 3-14 |

| 3.2.33 | Error Sensing CALTRACK2                  | 3-14 |

| 3.2.34 | CALTRACK1 Error                          | 3-15 |

| 3.2.35 | CALTRACK2 Error                          | 3-15 |

| 3.2.36 | CALTRACK2 Offset Error                   | 3-16 |

| 3.2.37 | Tape Edge Error                          | 3-16 |

| 3.2.38 | Top Tape Edge Tolerance Error            | 3-17 |

| 3.2.39 | Drive is Overheating                     | 3-17 |

| 3.2.40 | BOT Sensor Error                         | 3-17 |

| 3.2.41 | No Hall Switch Signals                   | 3-18 |

| 3.2.42 | No Tachometer Pulses Present             | 3-18 |

| 3.3    | Subassembly Remove/Replace Procedures    | 3-19 |

| 3.3.1  | Drive Board Removal                      | 3-19 |

| 3.3.2  | Front Bezel Removal                      | 3-19 |

| 3.3.3  | Read/Write Head Bracket Assembly Removal | 3-20 |

| 3.3.4  | Tachometer Removal                       | 3-20 |

| 3.3.5  | Solenoid/Interposer Removal              | 3-21 |

| 3.3.6  | Take-up Motor Removal                    | 3-21 |

| 3.3.7  | Stepper Motor Removal                    | 3-22 |

| 3.3.8  | Heat Sensor Removal                      | 3-22 |

| 3.3.9  | Supply Motor Removal                     | 3-23 |

| 3.3.10 | Receiver Assembly Removal                | 3-23 |

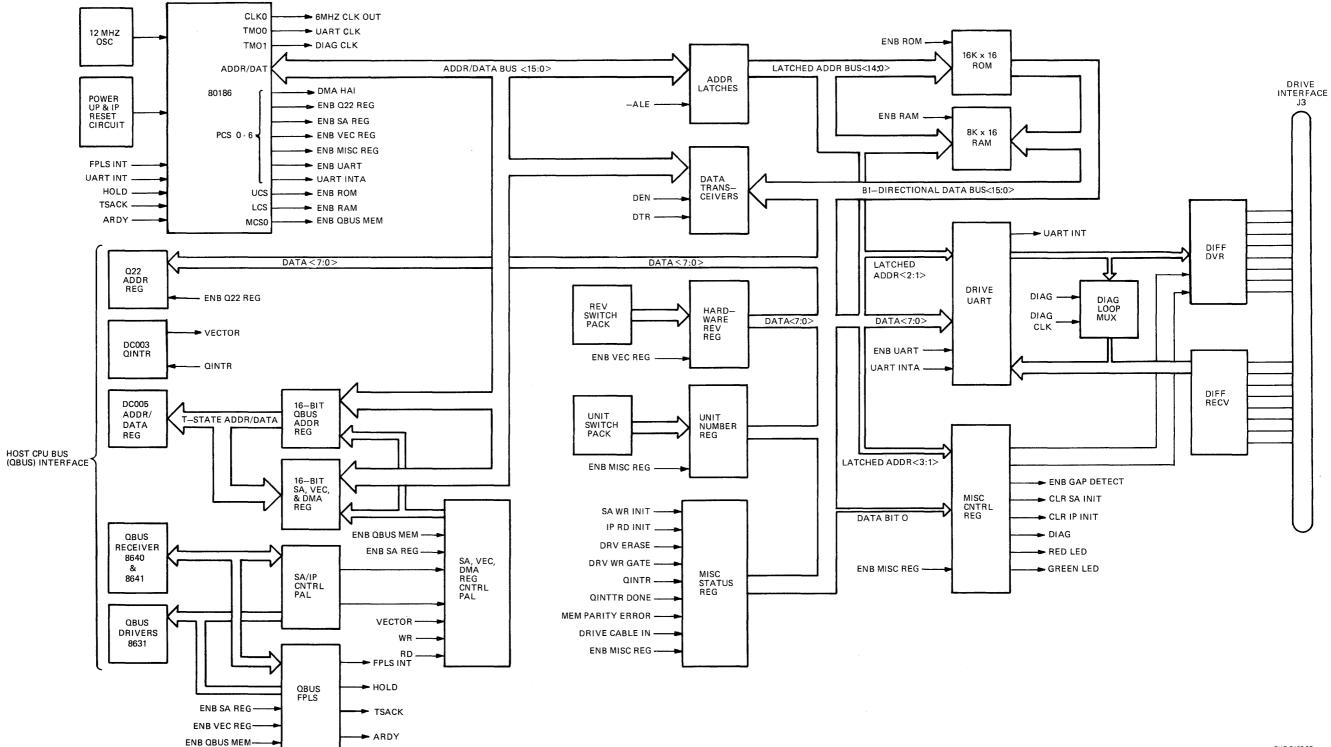

# CHAPTER 4 TQK50 CONTROLLER THEORY OF OPERATION

| 4.1     | General                   | 4-1   |

|---------|---------------------------|-------|

| 4.2     | The 80186 Microprocessor  | 4-3   |

| 4.2.1   |                           | 4-3   |

| 4.2.2   | Microprocessor Cycle Time | 4 - 4 |

| 4.2.3   |                           | 4 - 4 |

| 4.2.4   |                           | 4-5   |

| 4.2.5   | Interrupts                | 4-6   |

| 4.2.5.1 | MPSC Interrupts           | 4-6   |

| 4.2.5.2 | FPLS Interrupts           | 4-6   |

| 4.2.5.3 | Non-Maskable Interrupt    | 4-7   |

| 4.2.6   | DMA Operations            | 4-7   |

| 4.2.6.1 | DMA Write                 | 4-7   |

| 4.2.6.2 | DMA Read                  | 4-7   |

| 4.3     | Memory                    | 4-7   |

| 4.3.1   | EPROM                     | 4-7   |

| 4.3.2   | Data Transceivers         | 4-8   |

| 4.3.3   | RAM                       | 4-9   |

| 4.4       | Control and Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-9    |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 4.4.1     | Miscellaneous Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-9    |

| 4.4.1.1   | Drive Erase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4 - 10 |

| 4.4.1.2   | Drive Write Gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4 - 10 |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

| 4.4.1.3   | Enable Gap Detect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-10   |

| 4.4.1.4   | Clear SA Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-11   |

| 4.4.1.5   | Clear IP Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-11   |

| 4.4.1.6   | Diagnostic Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-11   |

| 4.4.1.7   | Reset LED 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-12   |

| 4.4.1.8   | Reset LED 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-12   |

| 4.4.2     | Unit Number and Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-12   |

| 4.4.2.1   | SA Write Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-12   |

| 4.4.2.2   | IP Read Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-12   |

| 4.4.2.3   | Drive Erase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-13   |

| 4.4.2.4   | Drive Write Gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-13   |

| 4.4.2.5   | Q-bus Interrupt Request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-13   |

| 4.4.2.6   | Q-bus Interrupt Request Done                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4-13   |

| 4.4.2.7   | Q-bus Memory Parity Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-13   |

| 4.4.2.8   | Drive Cable In                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-13   |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-13   |

| 4.4.2.9   | Unit Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |

| 4.4.3     | Vector Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-13   |

| 4.4.4     | Hardware Revision Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-14   |

| 4.4.5     | SA Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-14   |

| 4.4.6     | IP Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-16   |

| 4.4.7     | Module Starting Addresses/Interrupt Vectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-16   |

| 4.4.8     | Unit Number DIP Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-20   |

| 4.4.9     | Revision Level Switch Pack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-20   |

| 4.5       | Q22 Bus Interface Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-21   |

| 4.5.1     | FPLS Control Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-21   |