# ARALLEL

# digital

# PARALLEL DRUM TYPE 23

# INSTRUCTION MANUAL

# **COPY NO.** 0164

This manual contains proprietary information. It is provided to the customers of Digital Equipment Corporation to help them properly use and maintain DEC equipment. Revealing the contents to any person or organization for any other purpose is prohibited.

#### Copyright 1964 by Digital Equipment Corporation

#### PREFACE

This manual contains information on the principles of operation, and procedures for installation, operation, programming, and maintenance of the Digital Equipment Corporation Type 23 Parallel Drum. The parallel drum is designed for use as a data storage device to augment the main memory of a PDP-1D computing system. Section 1 of this manual presents information of a general nature which is applicable to the entire machine. Section 2 explains the principles of operation of the parallel drum as a system and of each functional element of the system. Sections 3 through 6 present information and procedures which allow personnel to install, operate, program, and maintain the equipment. Appendixes contain information on the diagnostic program used to test the parallel drum, circuit data for modules which are unique to drum systems, and engineering drawings.

# CONTENTS

| Section |                                                                | Page                 |

|---------|----------------------------------------------------------------|----------------------|

| 1       | INTRODUCTION                                                   | 1-1                  |

|         | Functional Description                                         | 1-1                  |

|         | Physical Description                                           | 1-2                  |

|         | Specifications                                                 | 1-4                  |

|         | Symbols and Terminology                                        | 1-4                  |

|         | Circuit Blocks                                                 | 1-8                  |

|         | Signals                                                        | 1-8                  |

|         | Subscripts                                                     | 1-10                 |

|         | Superscripts                                                   | 1-10                 |

|         | Other Notations                                                | 1-10                 |

|         | Pertinent Documents                                            | 1-10                 |

|         | Publications                                                   | 1-10                 |

|         | Engineering Drawings                                           | 1-11                 |

|         | Power Supply and Control<br>System Modules<br>Logic and Wiring | 1-11<br>1-11<br>1-12 |

| 2       | PRINCIPLES OF OPERATION                                        | 2-1                  |

|         | Recording and Playback Technique                               | 2-1                  |

|         | Block Diagram Discussion                                       | 2-1                  |

|         | Index and Clock Readers                                        | 2-3                  |

|         | Timing                                                         | 2-3                  |

|         | Control                                                        | 2-4                  |

|         | Drum Counter (DC)                                              | 2-4                  |

|         | Initial Location Register (IL)                                 | 2-5                  |

|         | Comparator                                                     | 2-5                  |

|         | Word Counter (WC)                                              | 2-5                  |

|         | Drum Core Location Counter (DCL)                               | 2-6                  |

|         | Read Control and Read Field Buffer (RFB)                       | 2-7                  |

|         | Write Control and Write Field Buffer (WFB)                     | 2-8                  |

# CONTENTS (continued)

| Section |                                     | Page |

|---------|-------------------------------------|------|

|         | Drum Field Select                   | 2-8  |

|         | Pulsed Bus Transceiver              | 2-9  |

|         | In Buffer (IB)                      | 2-9  |

|         | Out Buffer (OB)                     | 2-10 |

|         | Parity Formation                    | 2-11 |

|         | Parity Check                        | 2-12 |

|         | Data Writers                        | 2-12 |

|         | Data Readers                        | 2-13 |

|         | Data Head Selection and Drum Memory | 2-13 |

|         | Power Supply and Distribution       | 2-15 |

|         | Read-Write Cycle                    | 2-18 |

|         | Read Only Cycle                     | 2-21 |

|         | Write Only Cycle                    | 2-22 |

| 3       |                                     | 3-1  |

| 4       | INSTALLATION AND OPERATION          | 4-1  |

|         | Site Requirements                   | 4-1  |

|         | Signal and Power Connections        | 4-1  |

|         | Controls and Indicators             | 4-2  |

|         | Equipment Turn-On and Turn-Off      | 4-6  |

| 5       | PROGRAMMING                         | 5-1  |

| 6       |                                     | 6-1  |

|         | Drum Housing Locations and Wiring   | 6-2  |

|         | Preventive Maintenance              | 6-5  |

|         | Mechanical Checks                   | 6-6  |

|         | Power Supply Checks                 | 6-7  |

|         | Timing Checks                       | 6-7  |

# CONTENTS (continued)

| Section |                                                                                                                 | Page                                 |

|---------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------|

|         | Drum Sense Amplifier Checks                                                                                     | 6-8                                  |

|         | Index and Clock Head Spacing Checks                                                                             | 6-8                                  |

|         | Data Head Spacing Checks                                                                                        | 6-9                                  |

|         | Marginal Checks                                                                                                 | 6-11                                 |

|         | Corrective Maintenance                                                                                          | 6-14                                 |

|         | Preliminary Investigation                                                                                       | 6-14                                 |

|         | System Troubleshooting                                                                                          | 6-15                                 |

|         | Diagnostic Program<br>Signal Tracing<br>Aggravation Tests                                                       | 6-15<br>6-16<br>6-17                 |

|         | Circuit Troubleshooting                                                                                         | 6-17                                 |

|         | Module Circuits<br>In-Line Dynamic Tests<br>In-Line Marginal Tests<br>Static Bench Tests<br>Dynamic Bench Tests | 6-18<br>6-19<br>6-20<br>6-21<br>6-22 |

|         | Repair                                                                                                          | 6-23                                 |

|         | Validation Tests                                                                                                | 6-23                                 |

|         | Log Entry                                                                                                       | 6-24                                 |

# Appendix

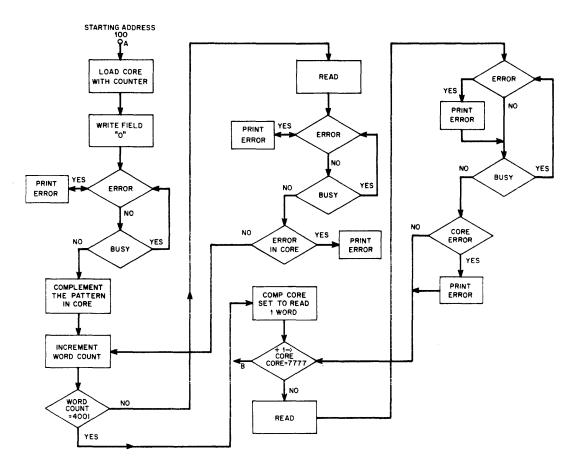

| 1 | TYPE 23 PARALLEL DRUM DIAGNOSTIC PROGRAM | A1-1 |

|---|------------------------------------------|------|

| 2 | DRUM MODULES                             | A2-1 |

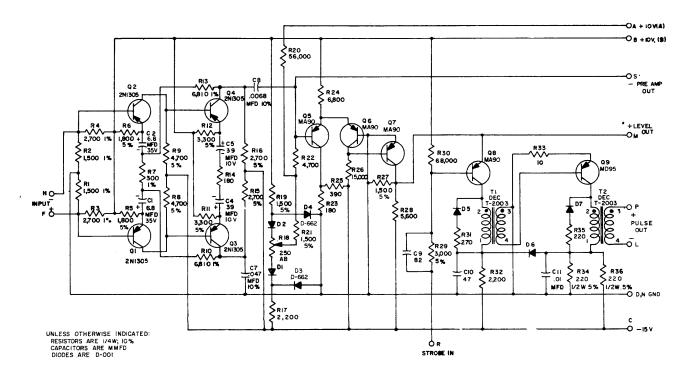

|   | Type 1537 Drum Sense Amplifier           | A2-1 |

|   | Controls                                 | A2-1 |

|   | Input                                    | A2-1 |

|   | Output                                   | A2-2 |

|   | Power                                    | A2-2 |

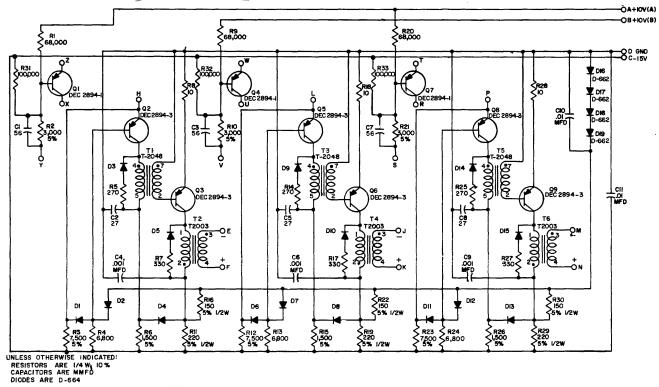

|   | Type 4518 Drum NRZ Writer                | A2-2 |

|   | Input                                    | A2-3 |

|   | Output                                   | A2-3 |

| Appendix                    | Page |

|-----------------------------|------|

| Power                       | A2-3 |

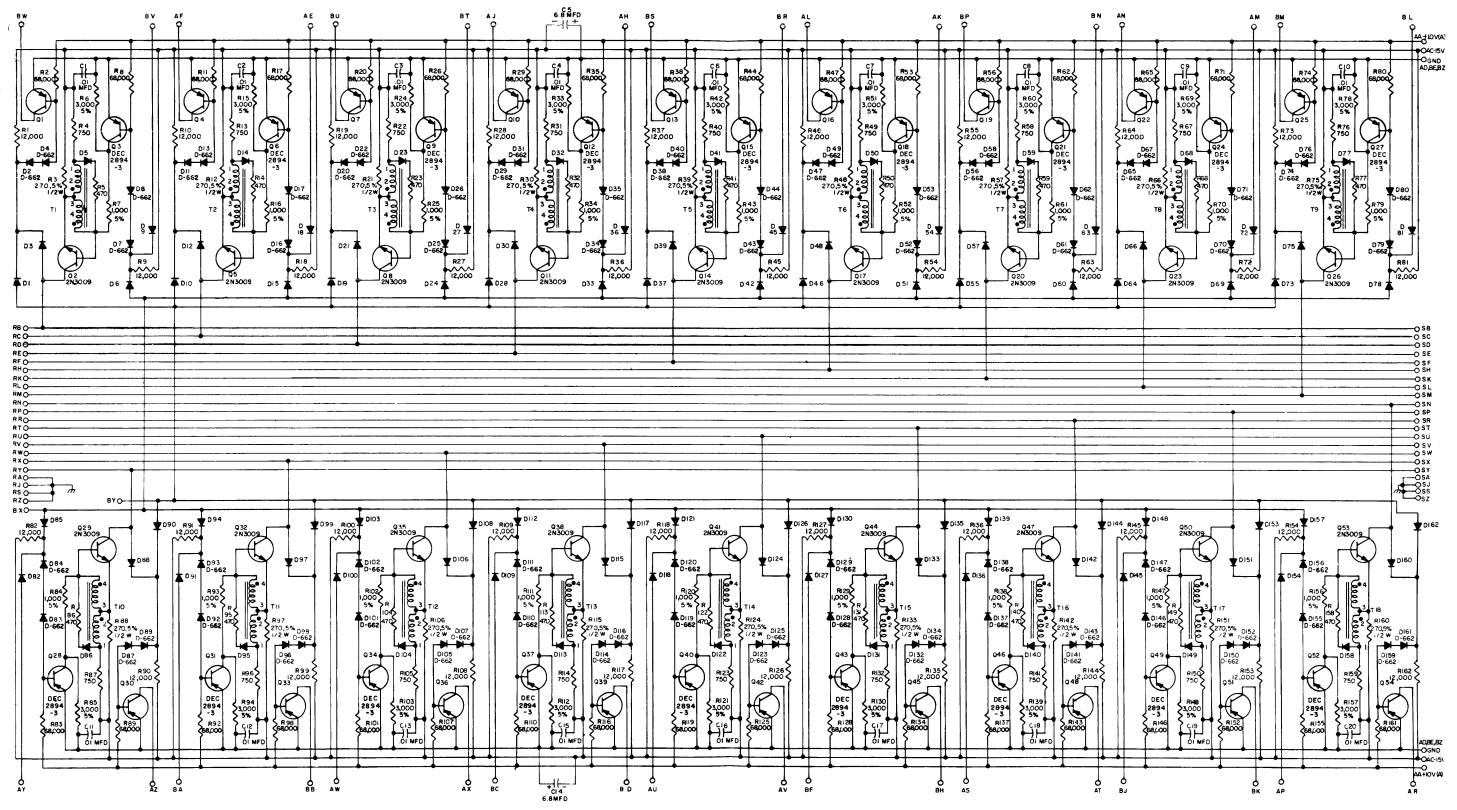

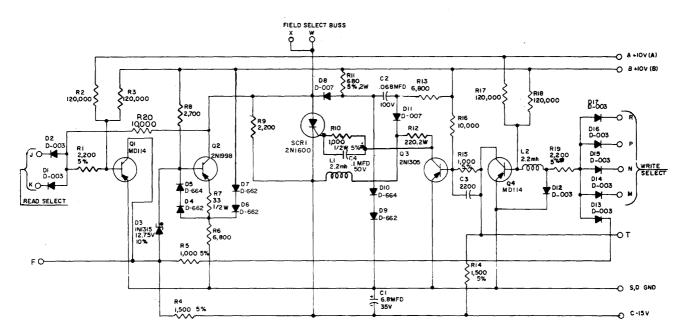

| Type 4519 Drum Field Select | A2-3 |

| Input                       | A2-4 |

| Output                      | A2-4 |

| Power                       | A2-5 |

|                             |      |

# CONTENTS (continued)

### TABLES

.

ENGINEERING DRAWINGS ...... A3-1

3

| Table |                                     | Page |

|-------|-------------------------------------|------|

| 3-1   | Inputs to Drum from PDP-1D          | 3-2  |

| 3-2   | Outputs from Drum to PDP-1D         | 3-4  |

| 3-3   | Inputs to Drum from Memory Control  | 3-5  |

| 3-4   | Outputs from Drum to Memory Control | 3-6  |

| 4-1   | Controls and Indicators             | 4-2  |

| 5-1   | Instructions                        | 5-1  |

| 6-1   | Maintenance Equipment               | 6-1  |

| A1-1  | Diagnostic Program Switch Usage     | A1-1 |

| A1-2  | Error Printouts                     | A1-1 |

## ILLUSTRATIONS

| Figure |                                       | Page |

|--------|---------------------------------------|------|

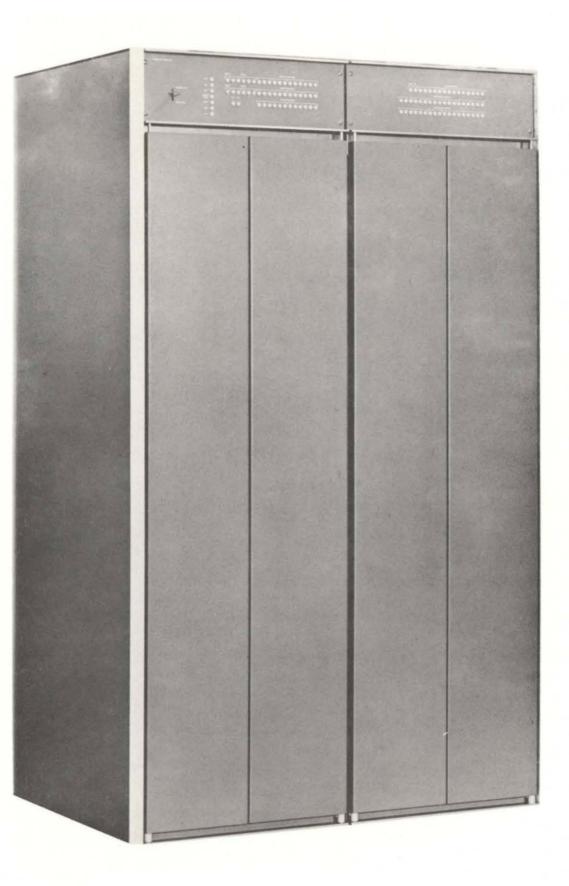

| 1-1    | Typical Parallel Drum System Type 23  | xii  |

| 1-2    | Component Locations                   | 1-3  |

| 1-3    | Logic Symbols                         | 1-6  |

| 2-1    | Typical Recording and Playback Timing | 2-2  |

| 2-2    | Data Head Selection                   | 2-16 |

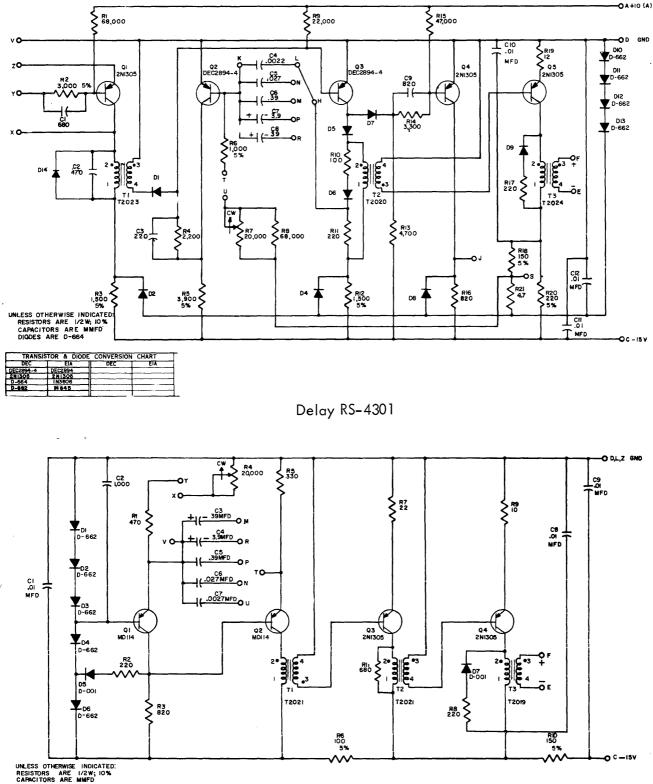

| 2-3    | Drum Power Circuit                    | 2-17 |

| 4-1    | Indicator Panels                      | 4-2  |

# ILLUSTRATIONS (continued)

1

| Figure |                            | Page |

|--------|----------------------------|------|

| 6-1    | Pad Location               | 6-2  |

| 6-2    | Head Wiring                | 6-3  |

| 6-3    | Diode Board Wiring         | 6-3  |

| 6-4    | Read/Write Head Components | 6-4  |

| A2-1   | Type 1537 Logic Diagram    | A2-1 |

| A2-2   | Type 4518 Logic Diagram    | A2-2 |

| A2-3   | Type 4519 Logic Diagram    | A2-4 |

# ENGINEERING DRAWINGS

| Drawing     |                          | Page  |

|-------------|--------------------------|-------|

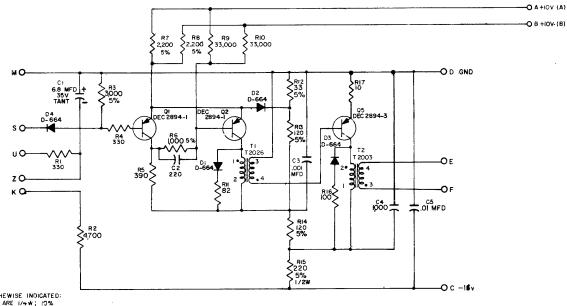

| RS-728      | Power Supply             | A3-1  |

| RS-813      | Power Control            | A3-1  |

| PW-D-23-0-8 | AC-DC Wiring             | A3-3  |

| RS-1000     | Clamped Load Resistors   | A3-5  |

| RS-1130     | Three-Bit Parity Circuit | A3-5  |

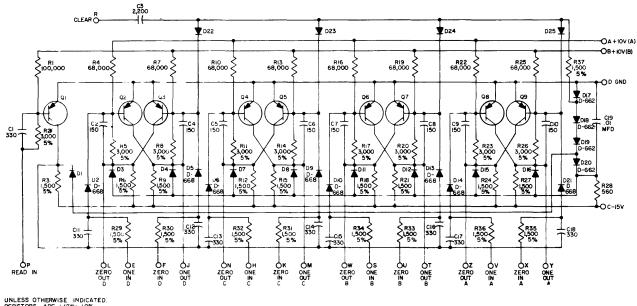

| RS-1304     | Delay                    | A3-6  |

| RS-1310     | Delay Line               | A3-6  |

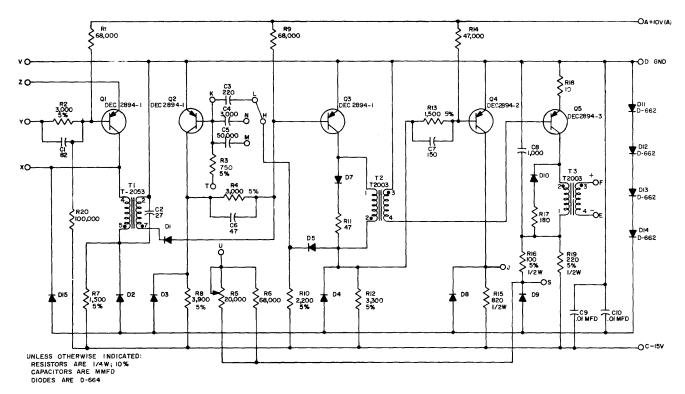

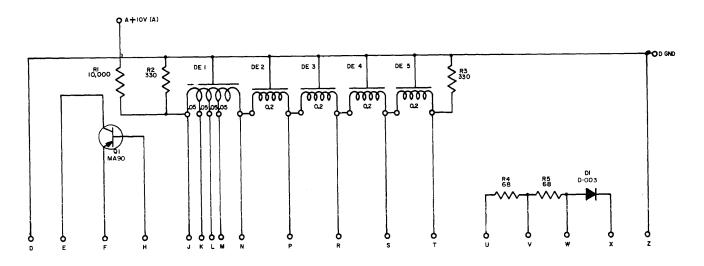

| RS-1410     | Pulse Generator          | A3-7  |

| RS-1537     | Drum Sense Amplifier     | A3-7  |

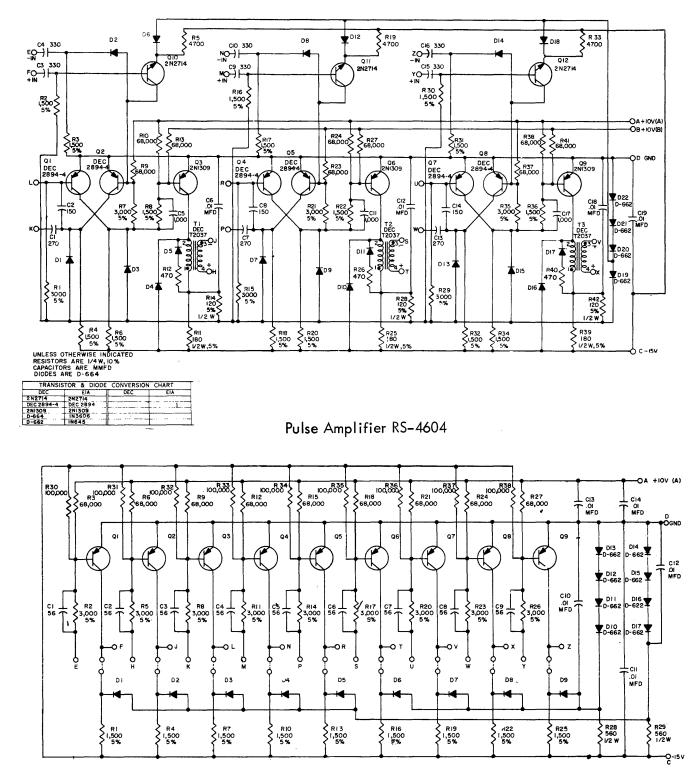

| RS-1607     | Pulse Amplifier          | A3-8  |

| RS-1665     | Pulsed Bus Transceiver   | A3-9  |

| RS-1684     | Bus Driver               | A3-11 |

| RS-4127     | Capacitor-Diode-Inverter | A3-11 |

| RS-4141     | Diode Unit               | A3-12 |

| RS-4151     | Binary-to-Octal Decoder  | A3-12 |

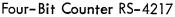

| RS-4217     | Four-Bit Counter         | A3-13 |

| RS-4218     | Quadruple Flip-Flop      | A3-13 |

| RS-4301     | Delay                    | A3-14 |

| RS-4401     | Clock                    | A3-14 |

# ENGINEERING DRAWINGS (continued)

| Drawing              |                                                                | Page  |

|----------------------|----------------------------------------------------------------|-------|

| RS-4518              | Drum NRZ Writer                                                | A3-15 |

| RS-4519              | Drum Field Select                                              | A3-15 |

| RS-4604              | Pulse Amplifier                                                | A3-16 |

| RS-6102              | Inverter                                                       | A3-16 |

| RS-6104              | Inverter                                                       | A3-17 |

| RS-6113              | Diode Unit                                                     | A3-17 |

| UML-D-23-0-7         | Utilization Module List (Sheet 1)                              | A3-19 |

| UML-D-23-0-7         | Utilization Module List (Sheet 2)                              | A3-21 |

| BD-D-23-0-17         | Interface and Block Diagram                                    | A3-23 |

| TFD-D-23-0-1         | Timing and Flow Diagram                                        | A3-25 |

| BS-D-23-0-2          | Control, Error Detection, Time Chain                           | A3-27 |

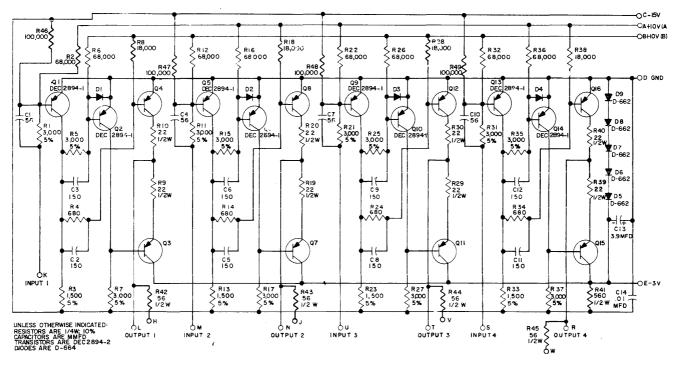

| BS-D-23-0-3          | In Out Buffers and Pulsed Bus Transceiver                      | A3-29 |

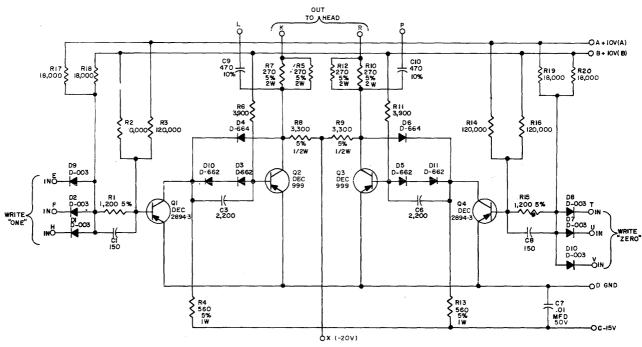

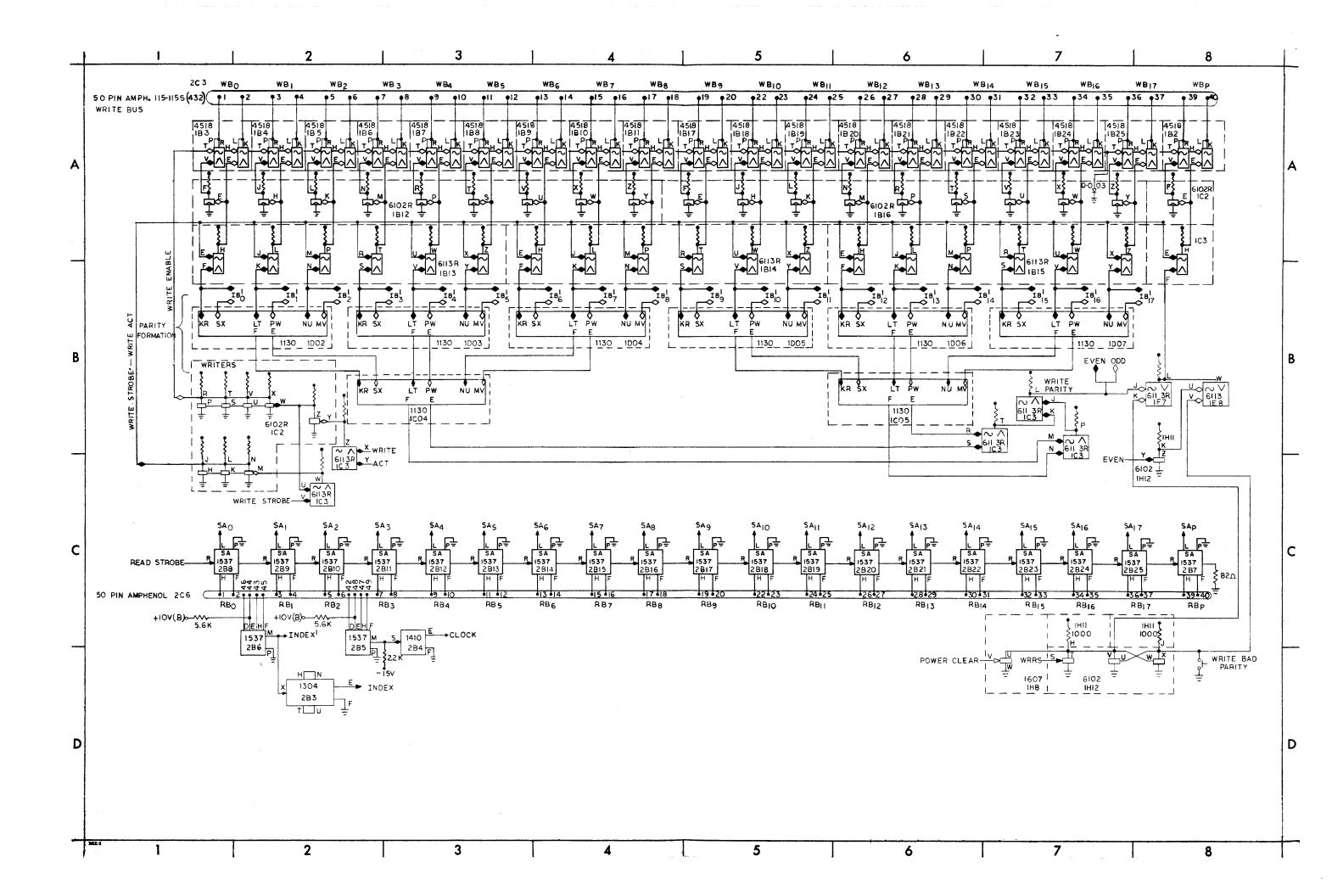

| BS-D-23-0-4          | Sense Amplifiers, Write Amplifiers, and Parity                 | A3-31 |

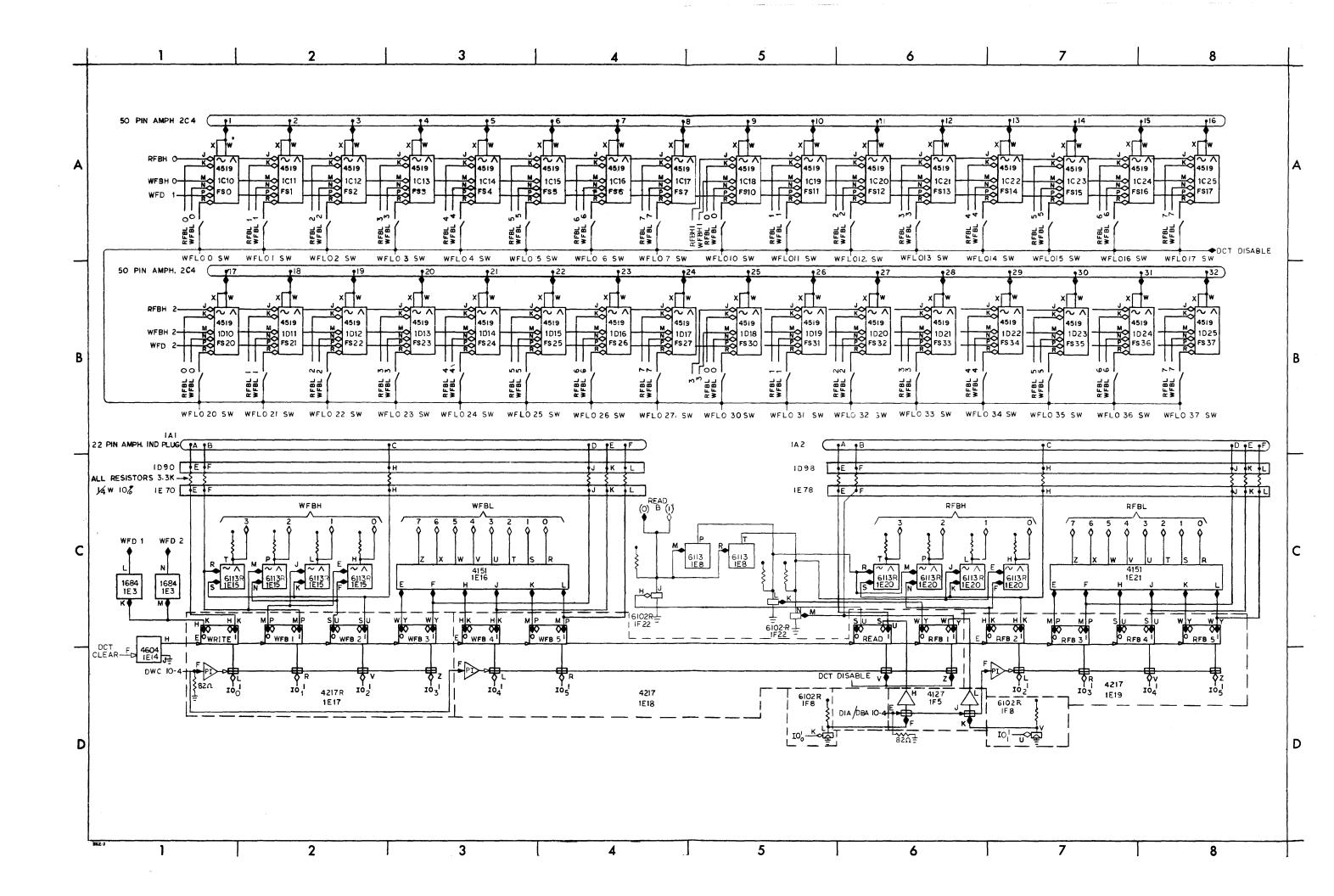

| BS-D-23-0-5          | Read/Write Field Buffers and Field Select                      | A3-33 |

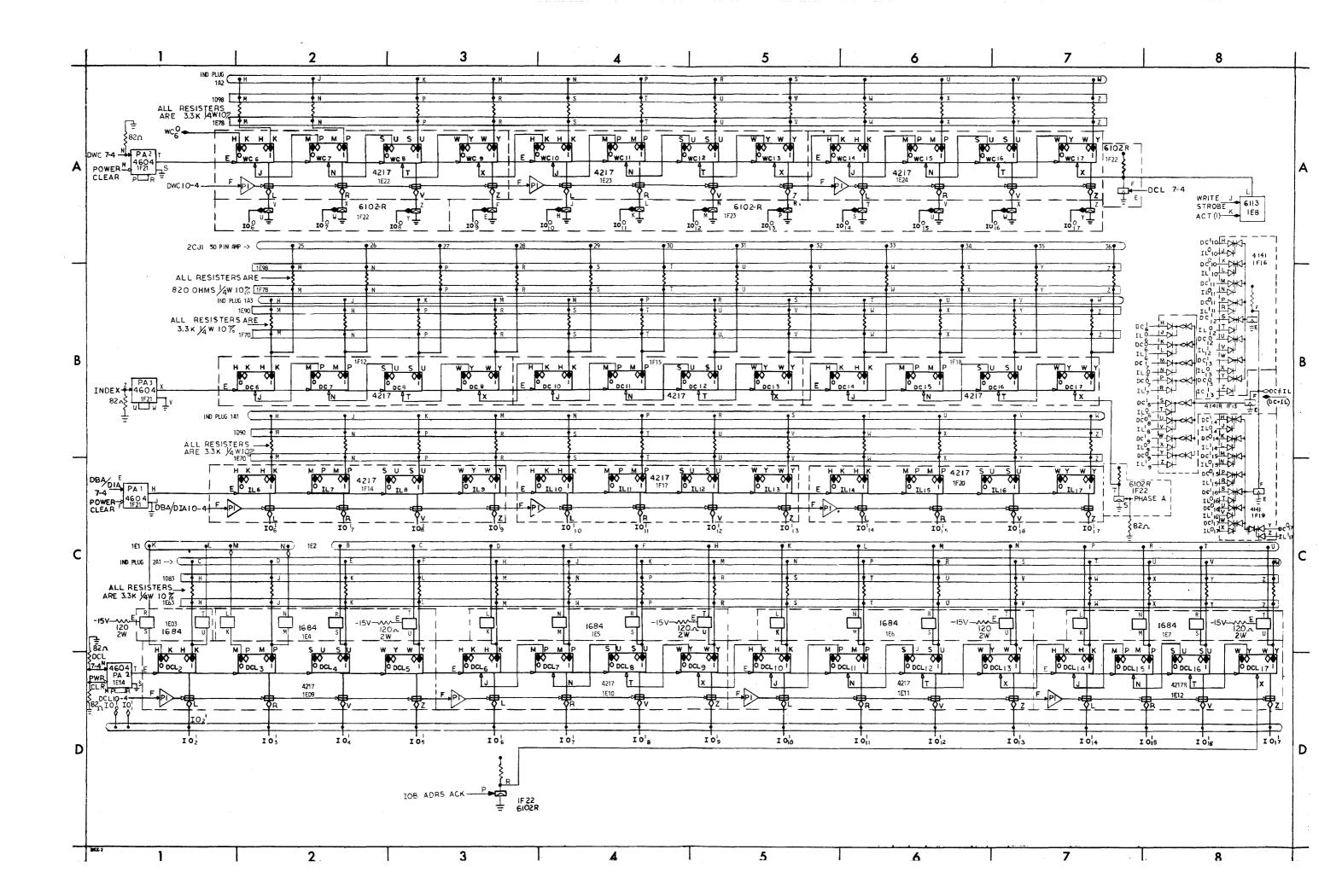

| BS-D-23-0-6          | Core Location, Drum Counter, Initial Location and Word Counter | A3-35 |

| CL-A-23-0-13         | Reader Output from Drum Housing (2CJ6)                         | A3-37 |

| CL-A-23-0-14         | Field Select Input to Drum Housing (2CJ4)                      | A3-38 |

| <b>C</b> L-A-23-0-15 | Writer Input to Drum Housing (2CJ3)                            | A3-39 |

| CL-A-23-0-16         | PDP-1D Interface With Drum (2CJ1)                              | A3-40 |

--

#### SECTION 1

#### INTRODUCTION

The Digital Equipment Corporation (DEC) Type 23 Parallel Drum serves as auxiliary data storage for the core memory of a Programmed Data Processor -1D and facilitates time shared use of the computer. Information in the computer can be stored (written) in the parallel drum and retrieved (read), or can be simultaneously read and written in a swap or data exchange. The drum contains 32 fields; each field is capable of storing 4096 words. Each word contains 18 information bits and an odd parity bit. The parity bit is generated within the drum during write operations and is checked during read operations to provide a means of checking the 18-bit information transfer between the drum and the computer. All transfers are completely automatic as controlled by the computer program. Transfers of from 1 to 4096 words can be executed at a rate of 8.5 microseconds per word, exclusive of set-up and access time. Transfer or exchange of 4096 words is accomplished in approximately 35 milliseconds.

#### FUNCTIONAL DESCRIPTION

The basic functions of the Type 23 Parallel Drum are data storage and retrieval, computer core memory address control, drum track and field selection, data request and transfer control, error checking, and power supply and distribution. Functional operation of the machine is initiated by receipt of IOT pulses from the computer. Three computer instructions produce all of the IOT pulses required to enact a transfer between the computer memory control and the parallel drum, regardless of the word length of the transfer.

A power supply and distribution network within the parallel drum produces and controls the operating voltages required by all circuits of the machine. One source of external ac power is required to energize the machine; control of this source within the machine can be exercised locally or remotely at the computer.

In response to IOT pulses from the computer the parallel drum receives the drum address from the computer, receives the number of words to be transferred and the read/write/exchange status of the transfer, and receives the core memory address of the transfer from the computer.

The transfer is then enacted in either the program interrupt or sequence break computer modes. Eighteen wits are simultaneously read from or written on the surface of the continually rotating drum and are transferred to or from the computer memory control element by means of a bidirectional pulse bus transceiver. During a write operation, a parity bit is generated within the drum for each word received from the computer so that 19-bit words are written on the drum surface. In reading data from the drum, the parity of the word is checked to assure proper transmission. Error circuits in the machine check for parity error during read cycles and check for data transmission timing during both read and write cycles. If bits are picked up or dropped out, if data received from the computer is late during a write cycle, or if data is late in being stored in the computer core memory during a read cycle, an error flag is set and a signal is sent to the computer and the transfer is halted. The computer program can interrogate the drum to determine the error status and the type of error detected when the error flag is set.

Control circuits within the parallel drum initiate the computer break status for the transfer, indicate the completion of a transfer by means of a flag, and signal the detection of an error, in addition to performing the normal internal control operations.

#### PHYSICAL DESCRIPTION

The parallel drum is constructed of two standard DEC computer cabinets bolted together to form a cabinet 60-1/8 inches high, 47 inches wide, and 27-1/16 inches deep. All indicators and the power control switch are located on panels at the front of the machine. Additional controls, used to inhibit writing in each of the drum fields independently and to force an incorrect parity bit as a check of the error circuits, are located on a switch panel inside the front doors of the right-hand cabinet. Eight casters allow mobility of the 900-pound machine.

Each cabinet is constructed of a welded steel frame covered with sheet steel. Double rear doors are held closed by magnetic latches. A full-width plenum door provides mounting for the Type 813 Power Control and two Type 728 Power Supplies inside the double rear doors. The plenum doors are latched by a spring-loaded pin at the top. Plug panels, which accept the signal cables from the computer, and module mounting panels are located in the front of the machine with the wiring side outward. A fan mounted in the bottom of each cabinet draws cooling air through a dust filter in the bottom, passes it over the electronic components, and exhausts it through louvered panels and openings in the cabinet.

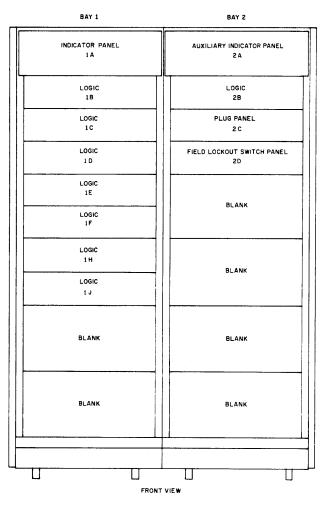

A coordinate system is used to locate cabinets, module mounting panels, modules and signal cable connectors, and terminals within the machine. As viewed from the front, cabinet 1 is on the left and cabinet 2 is on the right. Each 5–1/4 inch position on the front of the cabinet is assigned a capital letter, beginning with A at the top. Modules are numbered from 1 through 25 from left to right in a mounting panel, as viewed from the wiring side. Connectors on a plug panel are numbered from 1 through 6, from left to right as viewed from the front of the machine. Blank module and connector locations are numbered. Terminals on a module connector are designated by capital letters from top to bottom. The letters G, I, O, and Q are omitted from module and terminal designations. Therefore, 1C06J is in cabinet one (1), the third component location from the top (C), the sixth module from the left (06), and the ninth terminal from the top of the module (J). Components mounted on the plenum door are not identified by location. Figure 1–2 indicates the location of components within the parallel drum.

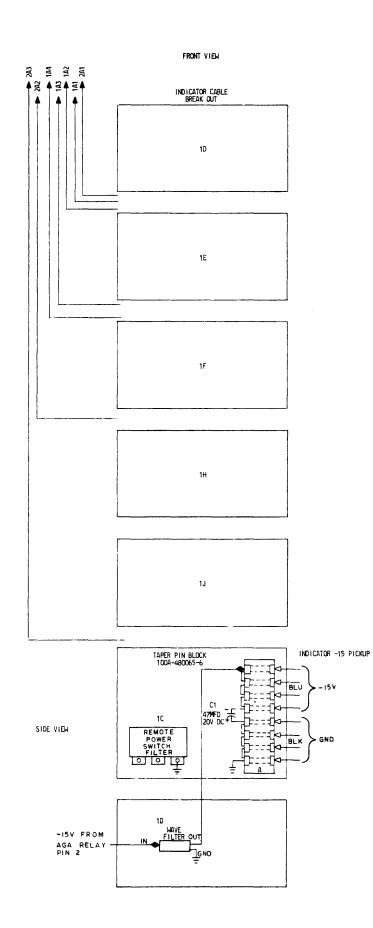

Figure 1-2 Component Locations

#### SPECIFICATIONS

| Dimensions                 | 47 inches wide, 27-1/16 inches deep,<br>69-1/8 inches high                                                                                                       |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Service Clearances         | 8–3/4 inches in front<br>14–7/8 inches in back                                                                                                                   |

| Weight                     | 1000 pounds                                                                                                                                                      |

| Power Required             | 115 volts, 60 cycles, single phase, 10-ampere<br>starting current, 9-amperes running current                                                                     |

| Power Dissipation          | 750 watts                                                                                                                                                        |

| Power Control Point        | Local or remote (computer)                                                                                                                                       |

| Initial Starting Delay     | 20 minutes                                                                                                                                                       |

| Heat Dissipation           | 2558 BTU/Hours                                                                                                                                                   |

| Signal Cables              | Three 50-wire shielded and one 18-wire<br>coaxial                                                                                                                |

| Temperature                | 32 to 105 degrees F operating range                                                                                                                              |

| Drum Motor                 | 115 volts, single phase, 4–pole induction capacitor start and run                                                                                                |

| Magnetic Head Interference | Maximum interchannel read cross talk at least<br>25 db below nominal signal level. Maximum<br>noise in any channel at least 25 db below<br>nominal signal level. |

| Write Current              | 1.75 amperes at – 14 volts for 19 heads                                                                                                                          |

| Read Current               | 20 milliamperes at +4 volts for 19 heads                                                                                                                         |

| Pulse Repetition Rate      | 8.5 microseconds                                                                                                                                                 |

| Drum Revolution Time       | 35 milliseconds                                                                                                                                                  |

#### SYMBOLS AND TERMINOLOGY

Engineering drawing numbers for this equipment contain five pieces of information, separated by hyphens. Read from left to right these bits of information are a 2-letter code specifying the type of drawing, a 1-letter code specifying the size of the drawing, the type number of the equipment, the manufacturing series of the equipment, and a 2-digit number specifying the number of a drawing within a particular series. The drawing type codes are:

- a. BS, block schematic or logic diagram

- b. CL, cable list

- c. PW, power wiring

- d. RS, replacement schematic

- e. TFD, timing and flow diagram

- f. UML, utilization module list

- g. WD, wiring diagram

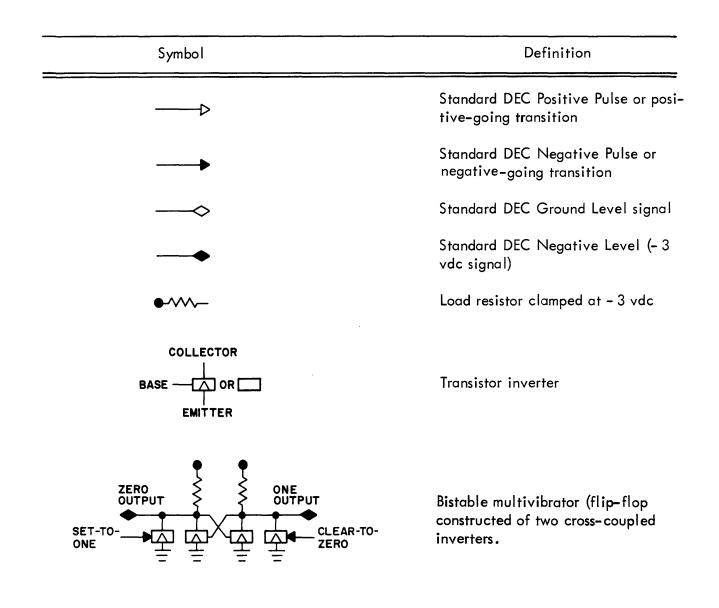

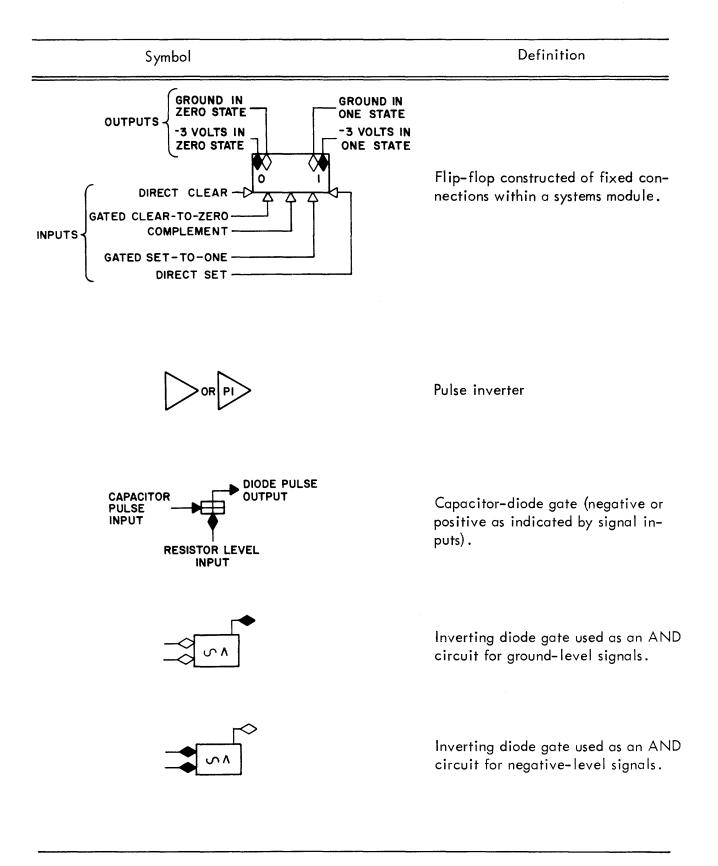

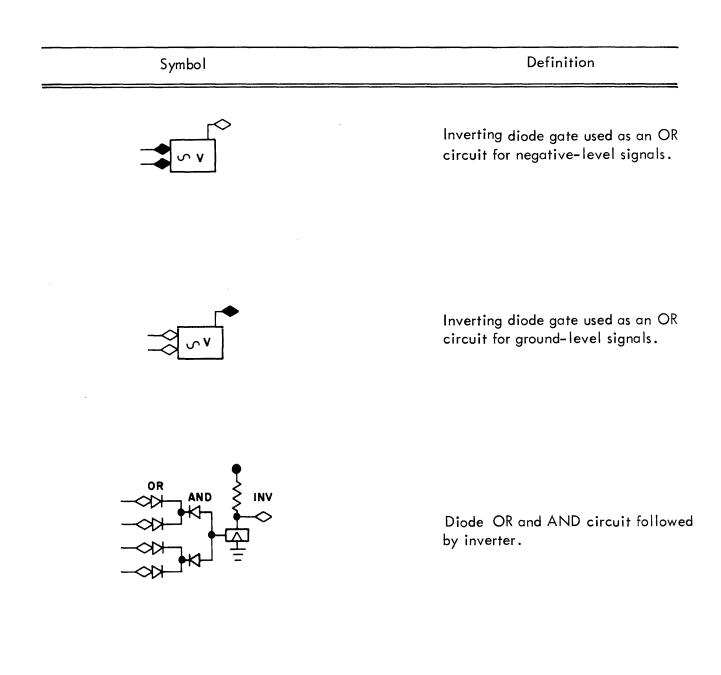

Symbols used on engineering drawings to represent basic logic circuits are defined in Figure 1-3.

Figure 1-3 Logic Symbols

Figure 1-3 Logic Symbols (continued)

Inverting diode gate used to trigger a pulse amplifier.

#### Figure 1-3 Logic Symbols (continued)

Abbreviations and conversions used in this manual, on the engineering drawings, or on panel markings are defined in the following list.

## Circuit Blocks

| ACT         | Active flip-flop                |

|-------------|---------------------------------|

| DBA SYNC    | Drum break address flip-flop    |

| DC          | Drum counter                    |

| DCL         | Drum core location              |

| DRA SYNC    | Drum read address flip-flop     |

| ERROR SYNC  | Error synchronization flip-flop |

| IL          | Initial location                |

| PA          | Pulse amplifier circuit         |

| PE          | Parity error flip–flop          |

| PI          | Pulse inverter circuit          |

| RFB         | Read field buffer               |

| RQ          | Request flip-flop               |

| SA          | Sense amplifier (reader)        |

| TRA         | Transfer status flip-flop       |

| TRANS ERROR | Transfer error flip-flop        |

| WC          | Word counter                    |

| WFB         | Write field buffer              |

#### Signals

.

| ACT             | Active flip-flop or level                   |

|-----------------|---------------------------------------------|

| ADRS ACK        | Address acknowledge pulse                   |

| DBA             | Drum break address instruction or flip-flop |

| DC=IL           | Level indicating C(DC) = C(IL)              |

| DC => IO STROBE | Pulse which strobes C(DC) => C(IO)          |

| DCL             | Drum core location instruction or register  |

| DCT CLEAR       | Drum control clear pulse                    |

| DCT DISABLE     | Drum control disable level                  |

| DIA             | Drum initial address instruction                                |

|-----------------|-----------------------------------------------------------------|

| DRA             | Drum request address instruction or flip-flop                   |

| DWC             | Drum word counter instruction                                   |

| IB              | In buffer register or level                                     |

| IO              | Input-output register or level                                  |

| IOB ADRS ACK    | Input–output buffered address ack now ledge<br>pulse            |

| MA              | Memory address register or levels from the DCL to this register |

| OB              | Out buffer register or levels                                   |

| PBT             | Pulsed bus transceiver                                          |

| PWR CLR         | Power clear pulse                                               |

| MB              | Memory buffer register or input-output levels of the PBT        |

| RD RS           | Read restart pulse                                              |

| RD REQ or RD RQ | Read request level                                              |

| RFBH            | Read field buffer high digit level                              |

| RFBL            | Read field buffer low digit level                               |

| RQ              | Request level                                                   |

| RQB             | Request level buffered                                          |

| SA              | Sense amplifier circuit (reader) or pulses                      |

| SBS RETURN      | Sequence break signal return pulse                              |

| TE or TR ER     | Transfer error level                                            |

| ТР              | Timing pulse                                                    |

| WC              | Word counter register or level                                  |

| WFBH            | Write field buffer high digit level                             |

| WFBL            | Write field buffer low digit level                              |

| WFD             | Write field disable buffer                                      |

| WFLO            | Write field lockout switch or level                             |

| WR REQ or WR RQ | Write request level                                             |

| WR WS           | Write restart pulse                                             |

|                 |                                                                 |

# Signals (continued)

#### Subscripts

| 0 through 6                 | Individual bit numbers of a register,<br>counter, or flip-flops                                                                     |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

|                             | Superscripts                                                                                                                        |

| 1                           | Signal condition for flip-flop binary 1 status                                                                                      |

| 0                           | Signal condition for flip-flop binary 0 status                                                                                      |

|                             |                                                                                                                                     |

|                             | Other Notations                                                                                                                     |

| V                           | Inclusive OR                                                                                                                        |

| <del>-\</del>               | Exclusive OR                                                                                                                        |

| ٨                           | AND                                                                                                                                 |

| C(A)                        | Contents of register A                                                                                                              |

| A => B                      | A replaces B or B is set to A                                                                                                       |

| $C(A)_{0-5} => C(B)_{6-11}$ | The contents of bits 6 through 11 of<br>register B are set to correspond with<br>the contents of bits 0 through 5 of<br>register A. |

#### PERTINENT DOCUMENTS

#### Publications

The following DEC documents serve as source material and complement the information in this manual:

a. Digital Modules Catalog, A-705. This book presents information pertaining to the function and specifications for the basic systems modules and accessories comprising the Type 23 Parallel Drum.

b. Silicon Modules Catalog C-6000. Information on the function and specifications for the 6000 series system modules is contained in this book.

c. PDP-1 Handbook, F-15. Programming information for the Programmed Data Processor - 1 is presented in this document. d. PDP-1 Supplements, F - 15(1D - 45) and F - 15(1D - 48). These documents describe the special instructions added to the PDP-1 when used in a typical PDP-1D configuration, such as that at Bolt Beranek and Newman, Inc. (45) and at Stanford University (48).

e. PDP-1 Maintenance Manual, F-17. Installation, operation, and maintenance of the standard PDP-1 and its central processor options are covered in this manual.

f. Parallel Drum Diagnostic Program Tape, DEC - 1 - 137 - M. A perforated- paper tape and program resume of a routine which tests the data reading, writing, and swapping operations of the drum system.

#### Engineering Drawings

Engineering drawings in the following list are reproduced in Appendix 3 of this manual as an aid to understanding and maintaining the Type 23 Parallel Drum. A complete set of formal engineering drawings is supplied separately with each system. Should any discrepancy exist between the drawings in this manual and those supplied with the equipment, assume the formal drawings to be correct.

#### Power Supply and Control

| Power Supply      | RS – 728        |

|-------------------|-----------------|

| Power Control     | RS <b>-</b> 813 |

| AC-DC Wiring PW-D | -23-0-8         |

#### System Modules

| Clamped Load Resistors           | RS-1000 |

|----------------------------------|---------|

| Three-Bit Parity Circuit         | RS-1130 |

| Delay (monostable multivibrator) | RS-1304 |

| Delay Line                       | RS-1310 |

| Pulse Generator                  | RS-1410 |

| Drum Sense Amplifier (reader)    | RS-1537 |

## System Modules (continued)

| Pulse Amplifier          | RS-1607          |

|--------------------------|------------------|

| Pulsed Bus Transceiver   | RS <b>-</b> 1665 |

| Bus Driver               | RS - 1684        |

| Capacitor-Diode-Inverter | RS-4127          |

| Diode Unit               | RS-4141          |

| Binary-to-Octal Decoder  | RS-4151          |

| Four-Bit Counter         | RS -4217         |

| Quadruple Flip-Flop      | RS-4218          |

| Delay                    | RS <b>-430</b> 1 |

| Clock                    | RS-4401          |

| Drum NRZ Writer          | RS-4518          |

| Drum Field Select        | RS-4519          |

| Pulse Amplifier          | RS-4604          |

| Inverter                 | RS-6102          |

| Inverter                 | RS-6104          |

| Diode Unit               | RS-6113          |

| Utilization Module List  | -23-0-7          |

#### Logic and Wiring

| Interface and Block Diagram BD-D-23-0-17                   |

|------------------------------------------------------------|

| Timing and Flow Diagram TFD-D-23-0-1                       |

| Control, Error Detection Time Chain BS-D-23-0-2            |

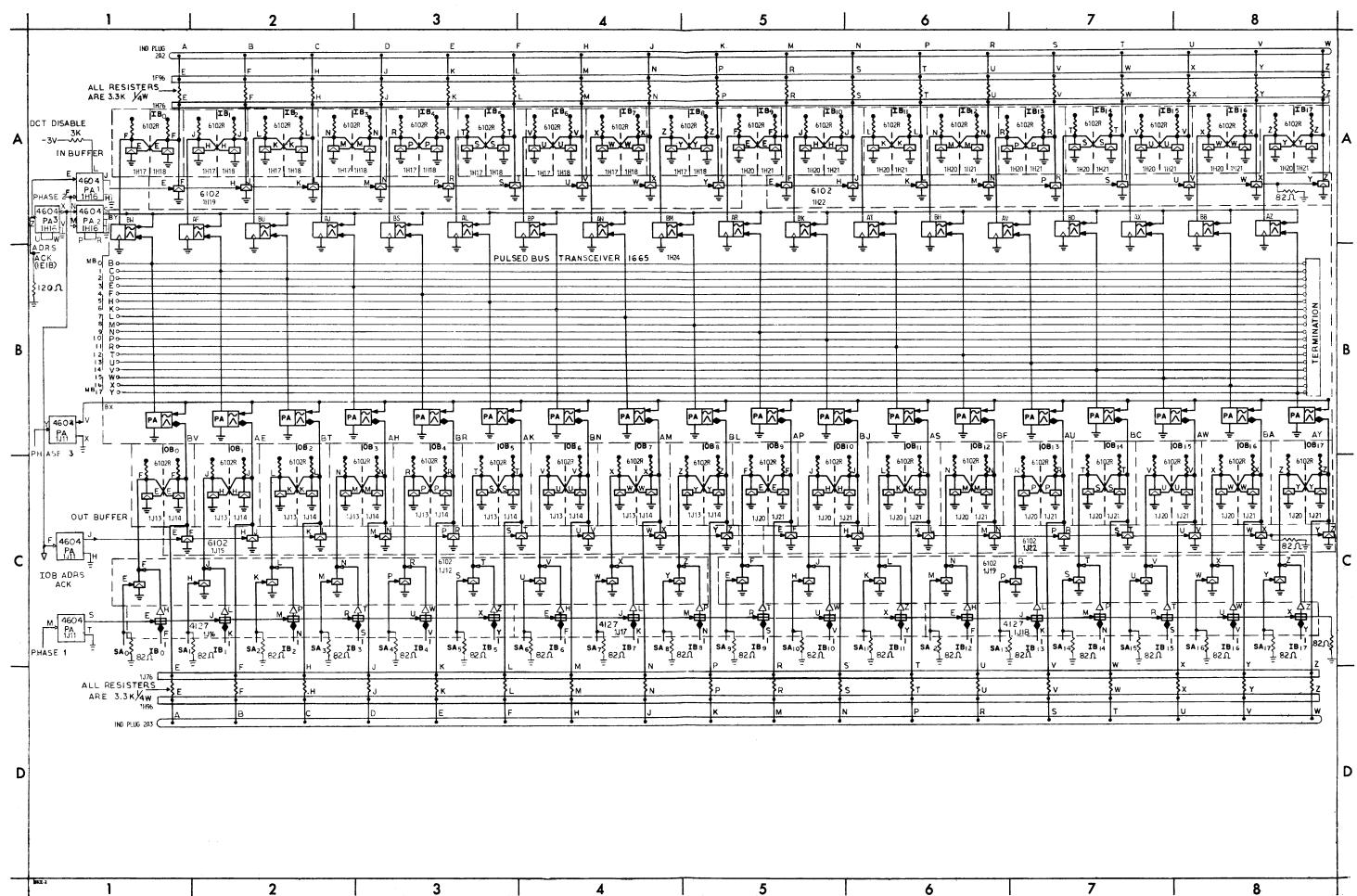

| In Out Buffers and Pulsed Bus Transceiver BS-D-23-0-3      |

| Sense Amplifiers, Write Amplifiers, and Parity BS-D-23-0-4 |

| Read/Write Field Buffers and Field Select BS-D-23-0-5      |

| Core Location, Drum Counter, Initial Location and          |

| Word Counter                                               |

| Reader Output from Drum Housing (2CJ6) CL-A-23-0-13        |

| Field Select Input to Drum Housing (2CJ4) CL-A-23-0-14     |

| Writer Input to Drum Housing (2CJ3) CL-A-23-0-15           |

| PDP-1D Interface With Drum (2CJ1) CL-A-23-0-16             |

#### SECTION 2

#### PRINCIPLES OF OPERATION

#### RECORDING AND PLAYBACK TECHNIQUE

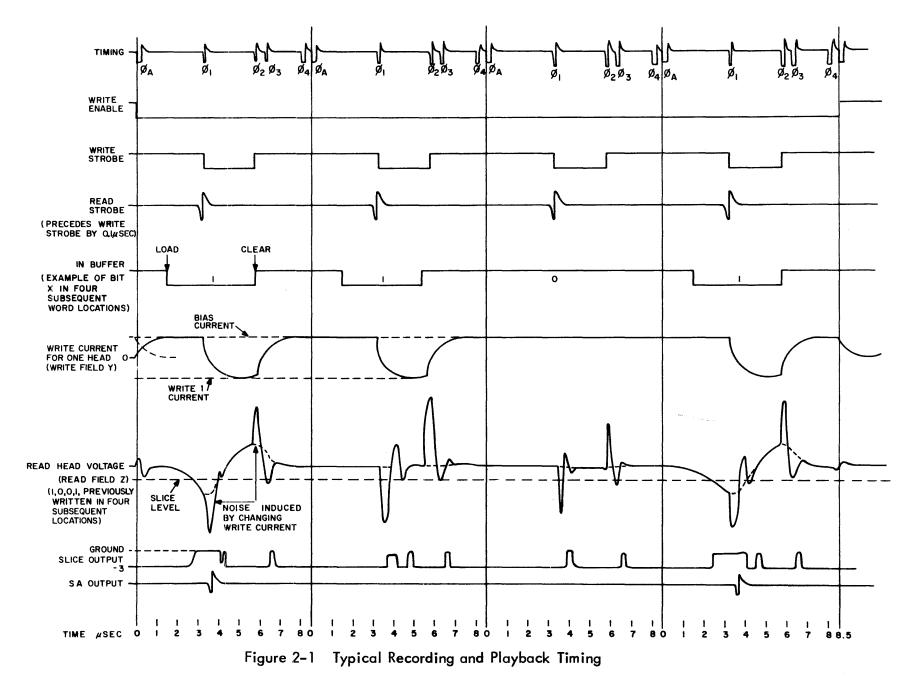

The Type 23 Parallel Drum utilizes return-to-bias recording techniques which lend themselves to the simultaneous read and write, or exchange, operation required of the drum. In each bit cell the new information to be written in a field is available just before the information is to be read from another field. Because of noise considerations, the read strobe must precede the write strobe. The effective advance of the read strobe over the write strobe, which previously wrote the information to be read, is possible because of the fringing of flux ahead of the data head gap. Before a transfer begins the read and write head select circuits are enabled. At the beginning of a transfer bias current is applied to the write-selected heads so that all transients occur and damp out before the occurrence of the read strobe. In a data exchange operation the read strobe is followed by the write strobe, and write noise is induced in the sense amplifier. This noise is commonly of greater amplitude than the read signal; however, this noise damps out before the next read strobe occurs. The read and write current waveforms and the timing of the read strobe and write strobe are indicated in Figure 2-1.

#### **BLOCK DIAGRAM DISCUSSION**

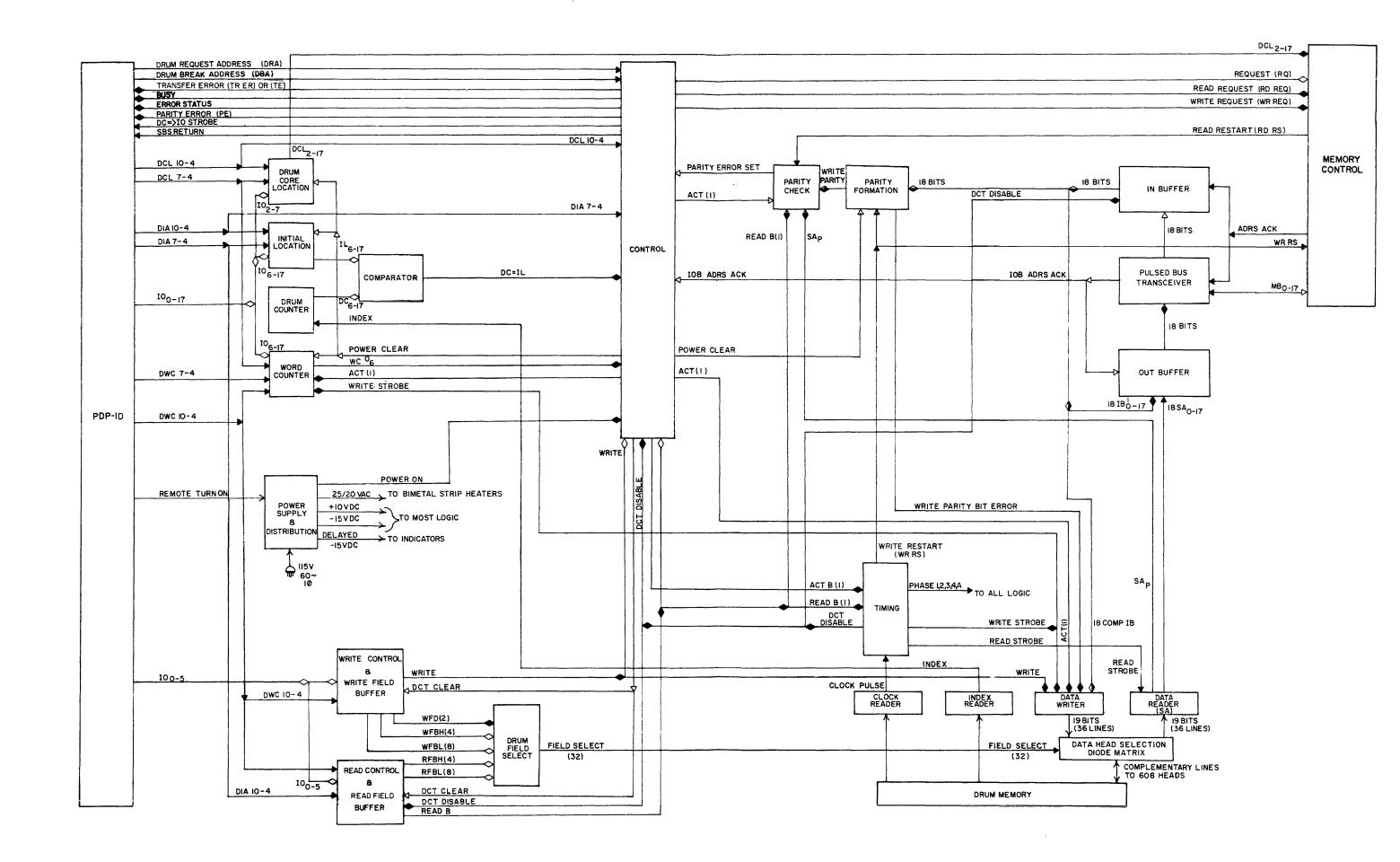

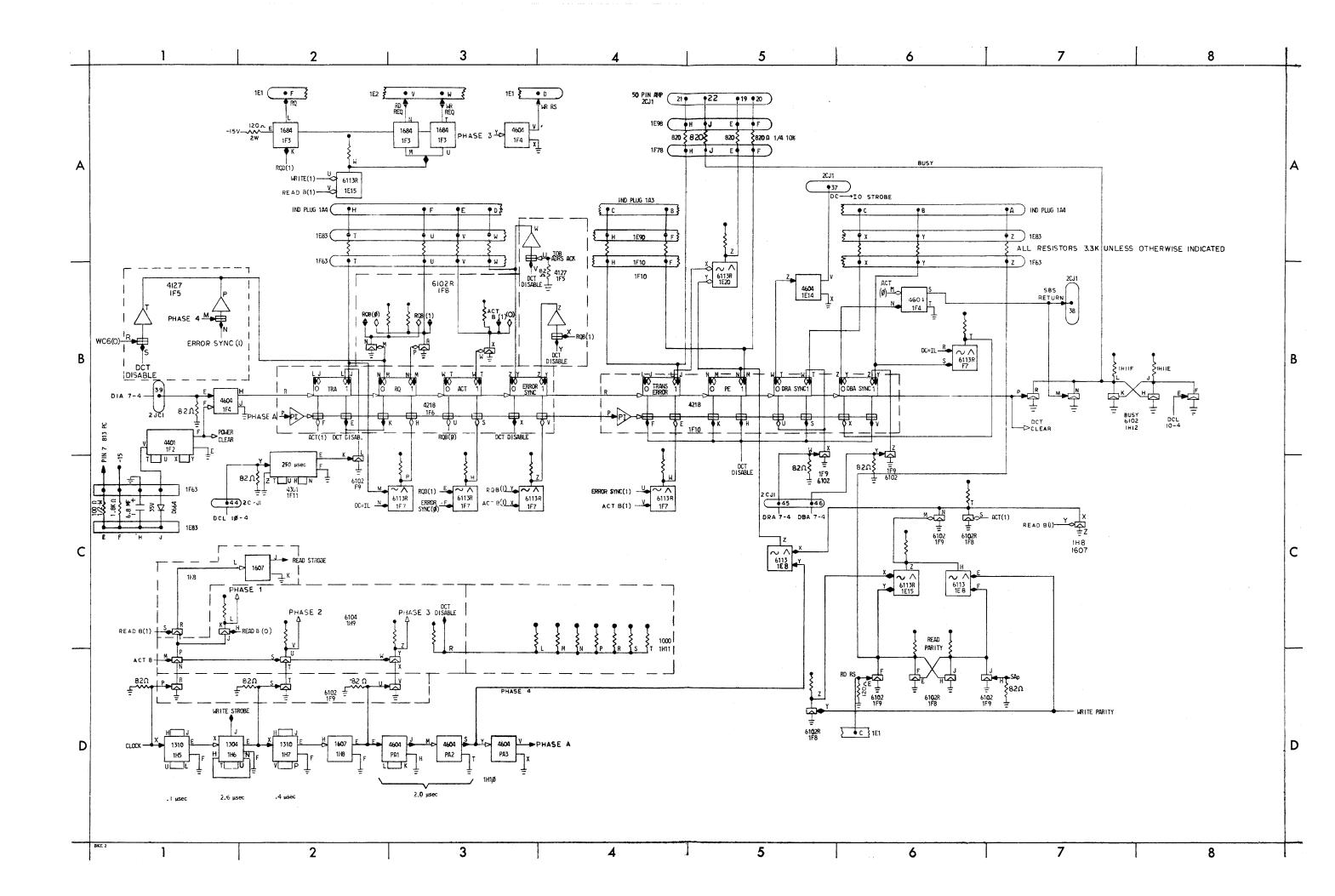

Functional elements of the parallel drum are shown on engineering drawing BD-D-23-0-17. This drawing indicates all signals which flow between the elements of the drum, and between drum elements and the PDP-1D and the Memory Control. The only signals which are not indicated are the phase signals out of the timing element which go to all logical blocks and the operating voltages which also are supplied to all elements from the power supply and distribution element. Detailed information on each of the functional blocks is indicated in block schematic engineering drawings BS-D-23-0-2 through 6, and complete information transfer flow in timing operations is indicated in engineering drawing TFD-D-23-0-1. The distribution and wiring of the power circuits within the parallel drum are indicated in engineering drawing PW-D-23-0-8. As reference is made to these drawings in the following text, only the final portion of the engineering drawing number will be used. Reference will also be made by means of the coordinates

on the drawing. These coordinates are A through D from top to bottom and 1 through 8 from left to right; so zone A1 is in the upper left hand corner, and zone D8 is in the lower right hand corner. Note that register bits are numbered to correspond with the computer register bits to which they transfer data. Therefore, most register bits are numbered so that the least significant bit is designated bit 17.

#### Index and Clock Readers

In addition to the normal data tracks recorded on the drum surface, two tracks provide timing information used in the control of normal drum operations. These two tracks are the index and the clock tracks. The information on these tracks is prerecorded and is read from the index track by the Type 1537 Drum Sense Amplifier module at location 2B6 and is read from the clock track by the Type 1537 module at location 2B5. One index bit is recorded on the surface of the drum to indicate the starting address of all words written on the data tracks. The output signal level from the index sense amplifier initiates operation of a Type 1304 Delay module whose negative pulse output clears the drum counter and signifies the start of each new drum cycle. The delay is provided to allow adjustment of the timing relationship of an index pulse so that it occurs exactly in the center of the time between the first and last clock pulse. The output of the clock sense amplifier initiates operation of a Type 1410 Pulse Generator module at location 2B4 to produce a standard DEC 70-nanosecond clock pulse which initiates operation of the timing element and controls the timing of all operations in the parallel drum. There are 4096 clock bits recorded around the surface of the drum; each clock pulse signifies a data bit cell location. Engineering drawing 4 contains this logic in the lower left hand corner.

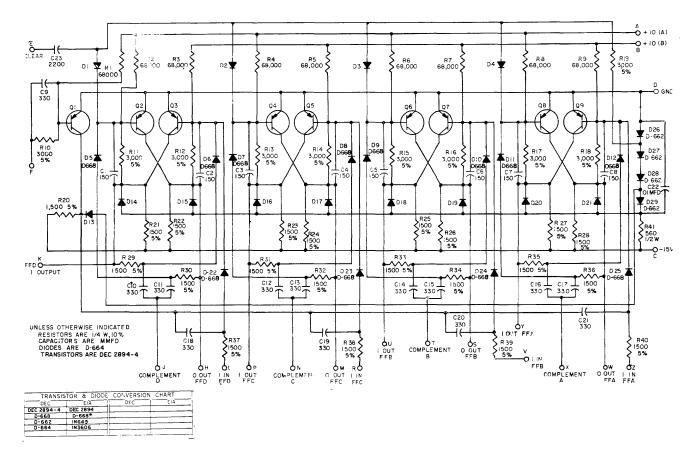

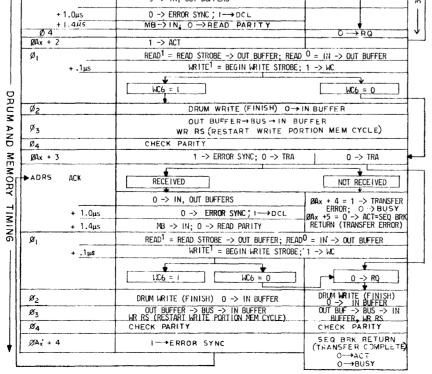

#### Timing

The timing element consists of a timing chain generator composed of delay lines, delays, and pulse amplifiers which produce the read strobe, write strobe, phase 1, phase 2, phase 3, phase 4, and phase A pulses. The timing chain is initiated by receipt of a clock pulse from the clock reader element. Transistor gating circuits allow generation of the read strobe signal only when the drum is in the read mode and in the active status. The phase 1 signal can be generated only when the drum is in the write mode and in the active status. The phase 2 and phase 3

signals are enabled only when the drum is in the active status. The phase 4 and phase A pulses cannot be disabled. In addition to these pulses the timing element produces the DCT disable signal, which is a constant – 3 vdc level produced by clamped load resistors. This level is used wherever constant enabling or disabling – 3 vdc levels are required. The phase 3 signal initiates operation of the Type 4604 Pulse Amplifier in location 1F4 whose output is the write restart (WR RS) signal, which is supplied to the memory control and to the parity formation element.

#### Control

The control element contains nine flip-flops (TRA, RQ, ACT, ERROR SYNC, TRANS ERROR, PE, DRA SYNC, DBA SYNC, and busy) which determine and control the status of the parallel drum. This element is shown on engineering drawing 2, above the timing element and the parity check element. When power is initially applied to the parallel drum, the Type 4401 Clock at location 1F2 is enabled by a ground level supplied to terminal B and produces repeated power clear pulses. The power clear pulses clear the parity formation element and various registers of parallel drum in addition to all of the flip-flops in the control element. After an initial delay period of approximately 30 seconds, the normally closed contacts of time-delay relay D2 of the Type 813 Power Control open to remove the ground potential from the integrating circuit at the input of the clock module to disable it.

The nine control flip-flops are also cleared by receipt of the DIA 7-4 command pulse, which is received during the first instruction in the initializing sequence. All of the flip-flops except the busy flip-flop are set to one or cleared to zero by the phase A pulse, as a function of the condition of level signals supplied to capacitor-diode gates. The busy flip-flop is constructed of two cross-coupled inverters which function as an unbuffered flip-flop. This flip-flop is cleared to zero by power clear pulses, the DIA 7-4 pulse, or a sequence break signal return and is set to 1 by the DCL 10-4 pulse. The function of the other flip-flops can be determined by the control signal or IOT pulse inputs required to set or clear them.

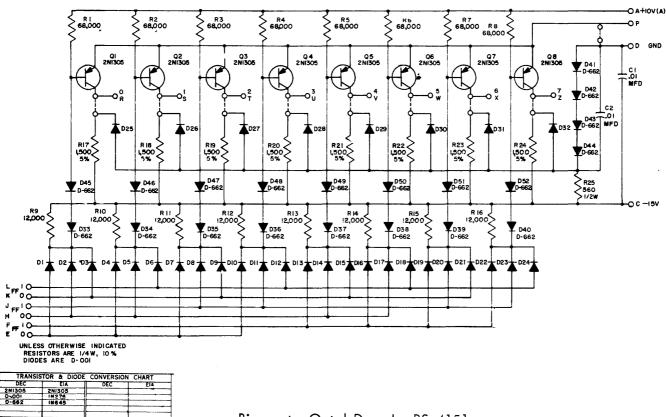

#### Drum Counter (DC)

The DC is a 12-bit counter which keeps track of the angular position of the continually rotating drum. This register is cleared by the index pulse provided by the index reader, and is incremented by one by each phase A pulse. Both the 1 and 0 outputs from each bit of this register are supplied to a comparator so that a data transfer is requested when the drum reaches the position, or drum address, set into the initial location register. The contents of this register can also be set (read) into the PDP-1D IO register to monitor the angular position of the drum. The logic circuits for the DC are shown on zone B of engineering drawing 6.

#### Initial Location Register (IL)

The IL is a simple set-and-reset 12-bit register which is used to store the initial address or first address at which the drum is to read or write. During either a DIA or DBA instruction, the register is cleared at computer 7 time and is set to the address contained in IO bits 6 through 17 at computer 10 time. Both the 1 and 0 outputs from this register are continually supplied to a comparator for comparison with the contents of the DC. This register is shown on zone C of engineering drawing 6.

#### Comparator

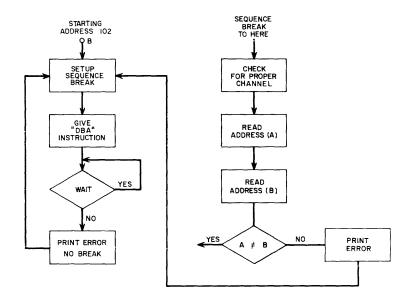

The comparator, shown on zone B8 and C8 of engineering drawing 6, continually monitors the contents of the DC and the IL. The circuit provides a bit-by-bit exclusive OR comparison of the contents of these two registers and supplies the negative DC = IL signal to the control circuit when the two registers contain the same drum address. This signal causes the control circuit to set the request flip-flop to the 1 status if the transfer flip-flop is also in the 1 status. The output of this flip-flop is then supplied to memory control to request a transfer. When using the DBA instruction, the DC = IL signal also initiates generation of the sequence break signal return pulse which is supplied to the computer to initiate a transfer through the sequence break mode, and clears the busy flip-flop.

#### Word Counter (WC)

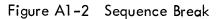

The WC is a 12-bit binary counter which controls the number of words transferred during any drum operation. The WC logic is shown on zone A of engineering drawing 6. During a DWC instruction, the contents of the computer IO register are set into the write control, the write field buffer, and the word counter. At this time the IO register information contained in bits 0 through 5 determines if writing is to occur in the following transfer and the write field to

be enabled. The contents of bits 6 through 17 of the IO register specify the number of words to be transferred. The 1's complement of the contents of bits 6 through 17 of the computer IO register is set into the contents of the word counter at computer time 10 (the WC is cleared at computer 7 time by the DWC instruction). During the ensuing DCL instruction, the contents of the WC are incremented by one by the DCL 7-4 IOT pulse; therefore when the transfer is initiated by the DCL instruction, the word counter holds the 2's complement of the number of words to be transferred. As each word is transferred, the write strobe pulse increments the contents of the WC. The write strobe pulse is used for this operation since both reading and writing have been completed at the current drum address when this pulse occurs. Therefore, when the specified number of words have been transferred, the most significant bit of the WC changes from the 1 state to the 0 state. The WC $_6^0$  signal clears the request flip-flop in the control element to signify to the computer that the transfer is complete.

#### Drum Core Location Counter (DCL)

The DCL is a 16-bit register which specifies the computer core memory address to or from which the next word is to be transferred. The contents of the DCL are sampled by the memory control and set into the contents of the core memory address register for each word of a transfer. Bits 6 through 17 of the DCL function as a setable counter which is automatically incremented by receipt of the IOB address acknowledge pulse from memory control. Bits 2 through 5 of the DCL are always transferred into the memory address register as they are set by computer IO register bits during the DCL instruction program initialization. Bits 2 and 3 specify one of four 16,384-word memory banks to be used for the transfer, and bits 4 and 5 specify one of four 4096-word memory modules within the memory bank. Therefore, the parallel drum is capable of operating with a computer containing 65,536 words of core memory with a maximum transfer word length of 4096 words. The DCL is shown on zones C and D of engineering drawing 6.

Before normal drum transfer operations, the DCL is cleared by the power clear pulses. During the third IOT instruction of the drum initialization program, the DCL instruction clears the DCL at computer 7 time and sets the contents of the IO register into the contents of the DCL at computer 10 time. Bits 6 through 17 of the DCL are incremented at the completion of each word transfer by the IOB address acknowledge pulse. All outputs from the DCL to the memory control are buffered by a non-inverting Type 1684 Bus Driver module.

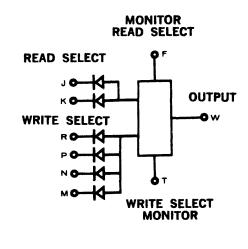

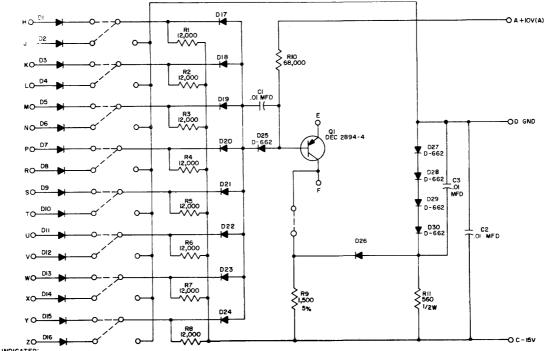

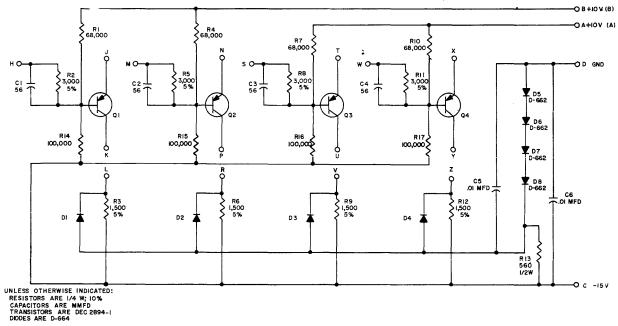

#### Read Control and Read Field Buffer (RFB)

Read control is a single flip-flop which determines if reading from the drum is enabled or disabled during any data transfer. The flip-flop is set to the 1 status (to enable reading) or to the 0 status (to disable reading) by the contents of IO register bit 0 during the first instruction of the drum initialization program (DIA or DBA instruction). The 0 output from the read flipflop is buffered by circuit HJ on the Type 6102 Inverter module at location 1F22 to produce the read buffered (B) signal. This buffered signal, supplied to the timing element and to the control element, is a - 3 vdc level when the flip-flop is in the 0 status and is a ground level signal when the flip-flop is in the 1 status. When the read flip-flop is in the 1 status, transistor gating circuits in the timing element are enabled to produce the read strobe pulse, thereby allowing read operations to take place. When the read flip-flop is in the 1 status, the read buffer signal supplies one input to the UVW circuit of the Type 6113 Diode Unit module at location 1E15 whose output is buffered by the Type 1684 Bus Driver at location 1F3 to provide both the read request (RD RQ) and write request (WR REQ) signals supplied to the memory control.

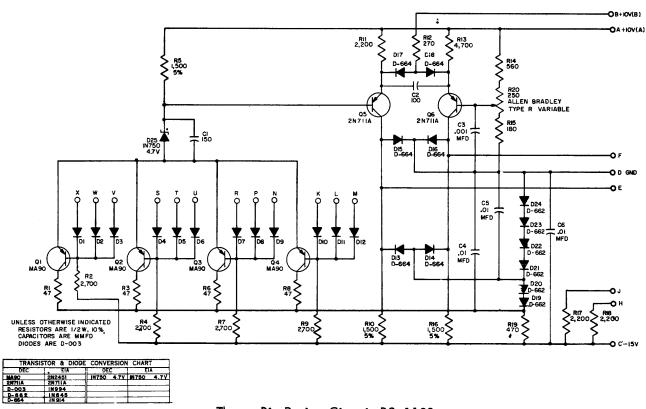

The 5-bit RFB specifies one of the 32 read fields which is to be activated during the ensuing transfer. The contents of the RFB designate a drum read field address of the transfer and are specified as a 2-digit octal number. Bits 1 and 2 of the RFB output are decoded to form the most significant bit of the octal number or the read field buffer high (RFBH) portion of the octal number which may run from 0 through 3. Bits 3 through 5 of the RFB are decoded to form the least significant bit or read field buffer lower (RFBL) portion of the octal drum address which may run from 0 through 7.

Both the read control flip-flop and the RFB are cleared by the DCT clear pulse, which is produced by the control element when the drum receives a DIA 7-4 command pulse. Both the read control flip-flop and the RFB are set to correspond with the contents of computer IO register bits 0 through 5 upon receipt of either a DIA 10-4 or DBA 10-4 command pulse from the computer. Note that the circuit contains inverters KL and UV on the module in location 1F8 which provide the required inversion for operation of the negative capacitor-diode gates at the input to the read control and RFB<sub>1</sub> flip-flops. The read control and RFB are shown on the lower right hand portion of engineering drawing 5.

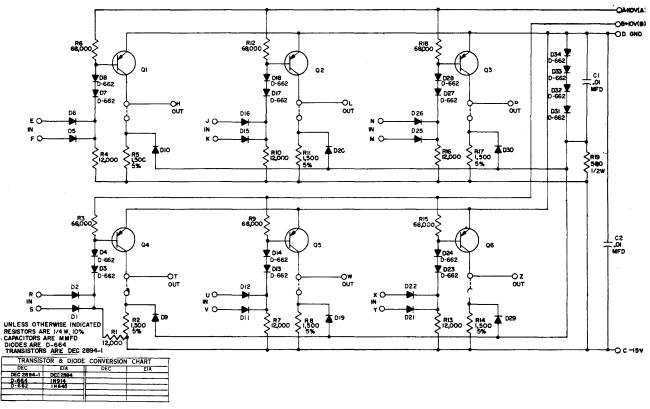

#### Write Control and Write Field Buffer (WFB)

The write control and WFB determine the write status of the drum and control the drum write field address. Both the write control and WFB flip-flops are cleared by the DCT clear pulse, which is produced when the control element receives a DIA 7-4 command pulse. Both the write control and WFB are set to correspond to the contents of the computer IO register bits 0 through 5 by the receipt of a DWC 10-4 command pulse from the computer. As in the read control and RFB, the output from the write control flip-flop is supplied to the control element to produce the read request and write request signals, and the five bits of the WFB are divided to produce a 2-digit octal number varying from 0 through 37. The 0 output of the write control flip-flop is buffered by two parallel-connected bus drivers in the module at location 1E3. This buffered output is supplied to each gate in the drum field select element to assure that writing does not occur when the write control flip-flop is in the 0 status. This logic is shown on the lower left hand corner of engineering drawing 5.

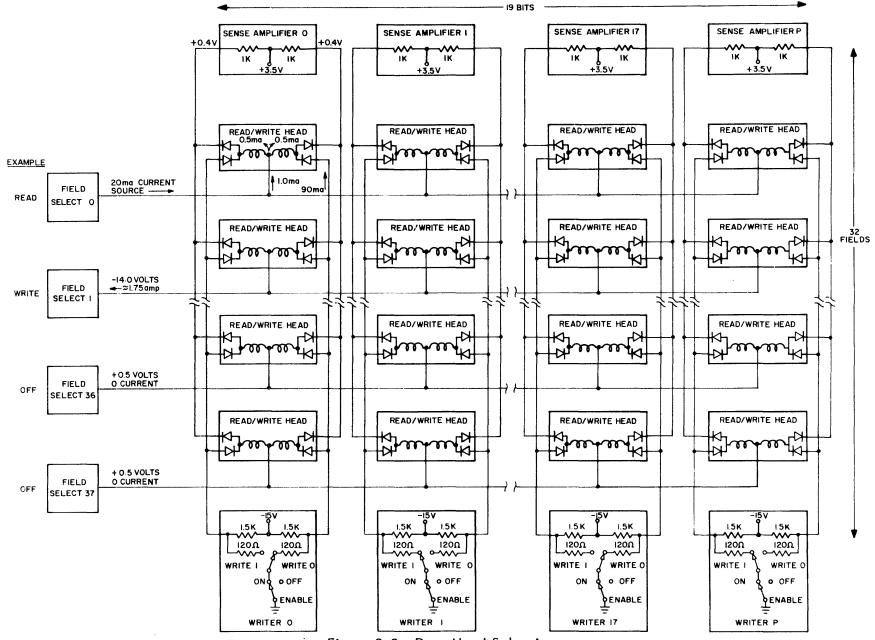

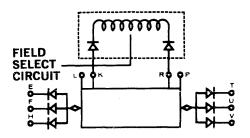

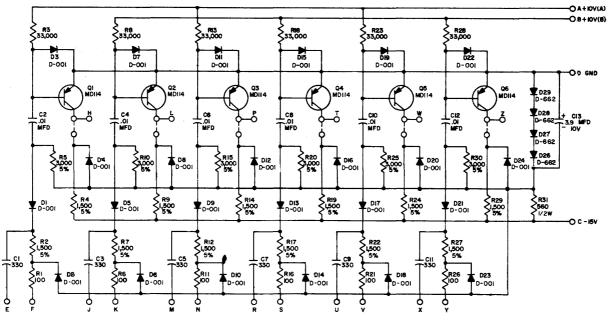

#### Drum Field Select

Selection of the drum field, or address, of a transfer is performed by decoding and gating circuits shown in zones A, B, and C of engineering drawing 5. The decoding involves negative AND gates which combine the appropriate outputs of the most significant bits of the WFB and RFB to produce the WFBH 0 through 3 signals and the RFBH 0 through 3 signals. Normal binaryto-octal decoders are used to combine the outputs of the four least significant bits of the WFB and RFB to produce the eight WFBL and RFBL signals (Type 4151 modules at location 1E16 and 1E21, respectively). Each of the 32 field select lines supplied to the data head selection diode matrix within the drum housing is connected to the output of two negative AND diode gates within a Type 4519 Drum Field Select module. Therefore, each line is selected by diode gating which combines the appropriate RFBH and RFBL information or which combines the appropriate WFBH and WFBL information with the condition that the write control flip-flop is in the 1 status and the appropriate WRITE FIELD LOCKOUT (WFLO) switch is in the down or enable position. The WRITE FIELD LOCKOUT switches are located on panel 2D at the front of the parallel drum and are used to inhibit writing in fields containing data which is not to be destroyed. Placing any of these octally numbered switches in the up position supplies the DCT disable - 3 vdc level signal to terminal R of the appropriate drum field select module, thus inhibiting writing. With

the switches in the down position a ground level is supplied to terminal R and the gating is enabled.

#### Pulsed Bus Transceiver

The pulsed bus transceiver provides a means of transmitting bidirectional data between the parallel drum and the memory control. The transceiver is a quadruple size standard DEC Type 1665 module located in positions 1H24 and 1J24. This module consists of two sets of 18 2-input negative AND diode gates and 18 output pulse amplifiers. Each of the pulse amplifiers is triggered by one of the diode gates. The 18 input diode gates all receive one input from a different bidirectional signal line which is connected by a coaxial cable to a similar pulsed bus transceiver within the memory control. The second input to each of the input diode gates is common to allow sampling of the information of the signal lines when the address acknowledge pulse is received from the memory control. The output from these diode gates provides a direct set input to the in buffer. Each of the 18 output diode gates receives an input from the output of one bit of the out buffer. The second input to each of the output diode gates is common and is connected to a pulse amplifier output which is triggered by the phase 3 pulse. The output from each of these diode gates triggers a pulse amplifier, causing it to pulse a bidirectional signal line. Therefore, when the phase 3 pulse occurs, the contents of the out buffer bits containing a 1 cause a negative pulse to be applied to the appropriate bidirectional signal line of the pulsed bus transceiver. Coaxial cables connect the pulsed bus transceiver in the parallel drum to a pulsed bus transceiver within the memory control, providing an efficient link of memory buffer register information between the two units. The pulsed bus transceiver module and the two pulse amplifier modules which functionally operate as the pulsed bus transceiver are shown in zones A and B of engineering drawing 3.

#### In Buffer (IB)

Data to be written on the drum is received in parallel from the 18 bits of the pulsed bus transceiver. The in buffer stores this information temporarily and supplies it to the data writers and to the parity formation circuit. When parity is formed, the write parity bit is also supplied to the data writer so that 19-bit words are written. The in buffer also functions in exactly the same manner during data reading so that the 19 information bits read by the data reader are

transferred to the out buffer, then are transferred from the out buffer to the pulse bus transceiver and then are transferred to the in buffer. The in buffer supplies the 18 bits of the word just read to the parity formation circuit, and a new write parity bit is formed. This bit is compared with the parity bit just read by the data reader and causes an error signal to be produced in the control element if the parity bit read in the new write parity bit formed is not identical.

Engineering drawing 3 shows the in buffer in zone A to consist of 18 flip-flops, each composed of two cross-coupled transistor inverters. Each flip-flop is set to the 1 status by a positive pulse from the output of the associated input diode gate in the pulsed bus transceiver, and is cleared by an inverted negative pulse produced at phase 2 time or when the address acknowledge pulse is received.

#### Out Buffer (OB)

The out buffer provides temporary storage of data, which has been read by the data readers, until the information can be sent to the memory control via the pulsed bus transceiver. Since the memory control uses a split memory cycle, information read from core memory is not rewritten automatically. Data transfer from memory control to the in buffer during a write only operation is transferred to the data writer and to the out buffer. The data can then be restored in core memory from the out buffer. This operation takes place as follows. At phase 1 time instead of strobing new information from the data readers into the out buffer, the word which was read from the memory control exists in the in buffer and is transferred to the out buffer. Writing takes place in the normal fashion, and at the end of the write strobe the in buffer is cleared. Then at phase 3 time the word in the out buffer is returned to memory control to restore the word which was previously read from computer core memory and written into the in buffer.

The out buffer is composed of 18 unbuffered flip-flops constructed of two cross-coupled transistor inverters and appropriate gating for set and clear inputs. This logic is shown on zone C of engineering drawing 3. Each bit of the out buffer is cleared by the inverted negative pulse produced by the IOB address acknowledge pulse. During a read operation, the data reader information (designated  $SA_0$  through  $SA_{17}$ ) is a negative pulse to signify a binary 1. The positive pulses produced by inverting  $SA_0$  through  $SA_{17}$  provide a direct set for the appropriate

bit of each out buffer flip-flop. During a write only operation, the contents of the in buffer are supplied to the level input of a Type 4127 Capacitor-Diode-Inverter module, which is triggered at phase 1 time to produce the positive pulse required to set the appropriate bit of the out buffer.

#### **Parity Formation**

The parity formation circuit continually generates the write parity signal according to the contents of the in buffer and supplies this signal to the control element and to the write parity bit of the data writer (for bit P). The write parity signal is generated by combining the outputs of eight Type 1130 Three-Bit Parity Circuit modules, each of which provides a parity check of three input bits. The first six Type 1130 modules compare the contents of three bits of the in buffer. The output from three Type 1130 modules is compared again in another Type 1130 module, and the output of the last two Type 1130 modules is combined in negative AND gates formed by three of the circuits on the Type 6113 Diode Unit at location 1C3. The write parity signal is at – 3 vdc if the in buffer contains an even number of ones or is at ground potential if the in buffer contains an odd number of ones. The status of the write parity signal is compared with the status of the write bad parity flip-flop to determine the status of the write parity bit supplied to the data writer P. The write bad parity flip-flop is composed of two cross-coupled transistor inverters, which are cleared by receipt of power clear pulses or by the write restart signal, and is set to the 1 status by pressing the WRITE BAD PARITY pushbutton on the write field lockout switch panel before the transfer commences. When this pushbutton is pressed, the flip-flop is set to 1, pin V of the negative AND gate at location 1E8 becomes a ground level, and pin K of the - AND gated location 1F7 becomes a - 3 vdc level. This gating inverts the signal supplied to the drum writer. After the first word has been transferred, the write restart pulse is received from the memory control to clear the write bad parity flip-flop and restore the normal conditions for generating the odd parity bit. The WRITE BAD PARITY pushbutton is a maintenance device which allows diagnostic programs to be written with an incorrect parity bit in the first word transferred; so a diagnostic program can check the operation of the parity error circuits of the drum, or a programmer can use this switch to test the error check routines within a given program. This switch is not used in normal data transfers.

#### Parity Check

The parity check element compares the contents of the parity bit read from the drum with the status of the write parity signal and generates a parity error set signal if an error is detected when the drum is active and in the read status. This signal is a standard DEC positive pulse which sets the parity error (PE) flip-flop in the control element. The logic which performs this operation is shown in the lower right hand corner of engineering drawing 2.

When bit P of the data reader detects a 1, the  $SA_p$  signal is a negative pulse which is supplied to the set-to-one gate of the read parity flip-flop. This flip-flop is cleared by receipt of the read restart signal from the memory control. The status of the read parity flip-flop is then compared with the write parity signal by the Type 6113 Diode Unit at location 1E15 and 1E8. The output at terminal H of module 1E8 becomes a ground level to indicate an error condition if the write parity signal is even, and if a 0 is read from the parity bit. The output from the module at location 1E15 is negative to indicate an error if the write parity signal is odd and the parity data reader detected a 1. This ground level error signal supplies one input to a 3-inverter ground-level AND gate. The output from this AND gate is a - 3 vdc error signal only when an error is detected, when the drum is in the active state, and the read control is active. This error signal is gated again by the negative AND gate which produces the positive parity error set signal when the output of the transistor AND gate is negative at phase 4 time.

#### Data Writers

The 18 bits of data to be written are stored in the in buffer. The binary 1 output from each flip-flop of the in buffer is supplied to a 2-input negative AND diode gate. The second input to each of these AND gates is provided in common by the write strobe – write active signal. This signal is generated by negative AND gates and is negative for the 2.6 microsecond duration of the write strobe pulse when the drum is in the active status and in the write mode. The output from each of the 2-input negative AND gates supplies the input to one side of one bit of a Type 4518 Drum NRZ Writer module. The inverted output of the 2-input negative AND gate supplies the input negative AND gate supplies the input to the second half of each bit of a Type 4518 module. Each half of each writer module is enabled by the write enable signal, which is a ground level signal produced by the drum being in the active state and in the write mode. The complementary outputs from each writer are supplied, through the data-head selection diode matrix, to opposite sides

of the read/write heads, through half of the head winding to the center tap. This logic is shown in zone A of engineering drawing 4.

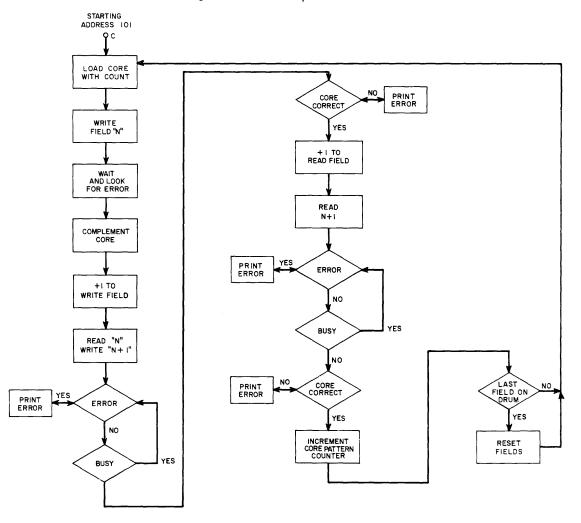

#### Data Readers

Data read from the drum surface by the read/write heads is supplied, through the data-head selection diode matrix, to the input terminals of the 19 data readers, or Type 1537 Drum Sense Amplifier modules. If the data read is in the 1 status at read strobe time, the sense amplifiers provide a Standard DEC negative Pulse which sets the 18 data bits into the contents of the out buffer and sets the parity bit into the contents of the read parity flip-flop of the parity check circuit. This logic is shown on zone C of engineering drawing 4.

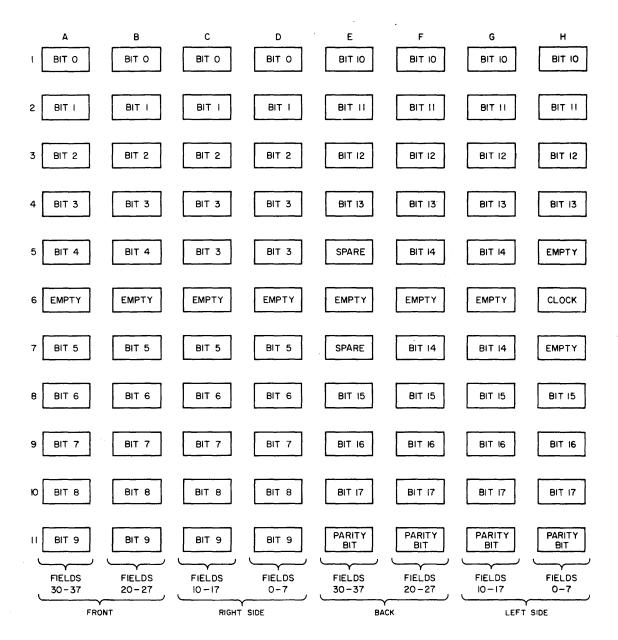

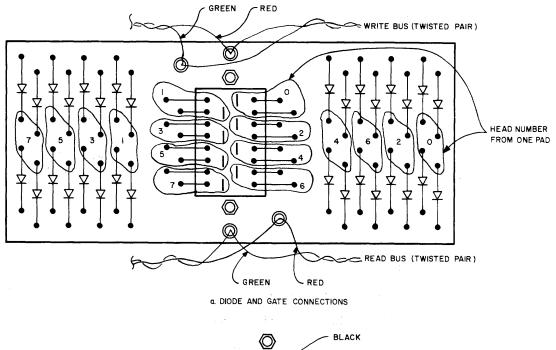

### Data Head Selection and Drum Memory

The drum housing mounted within cabinet 2 of the Type 23 Parallel Drum contains the data-head selection diode matrix, the read/write heads mounted on a shroud, and the rotating drum memory on which data is recorded. Panels attached to each side of the drum housing by means of captive screws are easily removed to allow access without disassembly or disconnection of power and signal connections. Thus, drum maintenance can be undertaken under system operating conditions. The drum housing is designed so that the fan action of the drum circulates air around the drum and head mounts, keeping the temperature differential within the housing to a minimum. Due to aerodynamic head suspension, thermal expansion is inconsequential; therefore, this internal circulation, together with the external discharge from the fan motor, also tends to maintain a minimum differential temperature from inside to outside, so that repeated stops and starts can be made without danger of head contact. The motor, which turns the drum, is of special design to provide the fastest starting time compatable with minimum power input and power losses at nearly synchronous speed. The fan for this single-phase, four-pole, induction, capacitor-start and run motor is fastened to the bottom of the spindle. Ambient air is drawn through a shroud and over the finned motor housing. This air current takes heat away from the motor, preventing localized temperature rise.

The rotating drum assembly is designed with minimum cross-section for proper heat transfer and dissipation. It is mounted on separable inner-ring angular-contact bearings, which are prelubricated for life. Preloading is accomplished by springs at the top end of the unit. The magnetic

coating on the surface of the drum is Grimaco 6037 – X high-density dispersion, heat-cured and lapped to its final finish. Dynamic runout is less than 0.0001 inch total indicated reading.

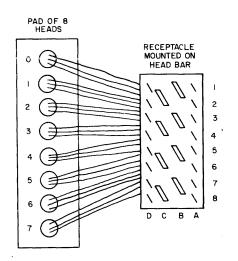

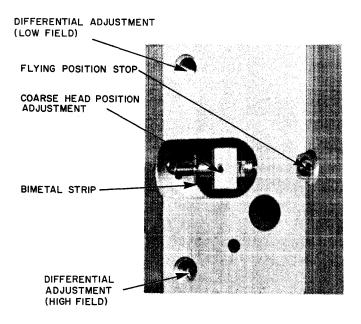

All data, index, and clock heads are mounted in pads of eight. The pads are suspended from the shroud surrounding the drum rotor, by flexible metal reeds. When the drum rotor reaches approximately 90 per cent of synchronous speed, a 60-cycle current is applied to a heater surrounding a bimetal strip, which in turn forces the head pad toward the drum surface. Total travel of the bimetal strip is limited by a stop screw. The final running clearance between head pole piece gap and the drum surface is set by the action of the precision flat ground head pad aerodynamically flying on the liminal air film which surrounds the drum surface when at nominal speed. Initial factory adjustments are made by two differential screws which torque the reed mounting to ensure that the pad is parallel to the drum surface and tangent at the pole piece gap.

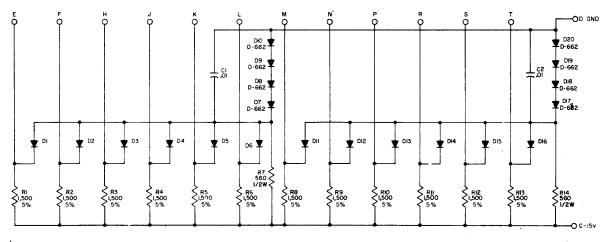

A printed-wiring board contains a 32-diode matrix used to select the eight heads on an associated pad. The connection of these diodes to a read/write head and connection to the logic elements of the drum system is indicated in Figure 2–2. This figure indicates the equivalent circuit of the logic elements as seen by the diode matrix, and indicates the flow of current using an example where field select 0 is in the read state, field select 1 is in the write state, and the balance of the field select circuits are deselected. When reading, a Type 4519 Field Select module supplies 20 milliamperes to the common field select line connected to all head centertaps for the appropriate field. A 1 milliampere current enters the centertap of each head and divides, 1/2 milliampere going through each of the forward biased diodes to the input of Type 1537 Drum Sense Amplifier (reader). The division of current is assured by the 1K equivalent resistance at each input terminal of the sense amplifier. This rise of 1/2 milliampere causes a 1/2 volt rise across each 1K resistor and places the common field select line at a read potential of +4 volts. When a field select circuit is in a write state, the centertap of the 19 common heads is returned via the field select to – 14 volts. When a field selector is in the write state, - 14.0 volts are applied to the center tap of the associated heads in the field. Since no current limiting exists, a short circuit between any potential more positive than -14.0 volts and either an outside head winding terminal or a write bus selected in this manner destroys (open) the head winding and/or the selection diodes. When the Type 4518 Drum NRZ Writers are gated on, each head returns approximately 90 milliamperes to this bus, for a total current

of approximately 1.75 amperes. A head in the read select status is isolated from the write bus by diodes which are back biased by a voltage of from 5 to 19 volts. A head which is in the write select state is disconnected from the read bus by diodes which are back biased by a voltage of from 5 to 19 volts also. Heads which are not selected are disconnected from the read bus by diodes which are back biased at 3.5 volts and are disconnected from the write bus by diodes which are back biased by a voltage from 1/2 to 15 volts, depending on the state of the writer.

In this manner it is possible to connect any of the bit sense amplifiers to a head for the same bit number in one of 32 fields, to connect the writer to one of the remaining 31 fields, and to have the remaining 30 fields back biased. Note that the common write bus for a bit is essentially coupled to a read bus by many back biased diodes. This coupling results in large noise spikes being induced in the read bus at write time. Because of the recording technique and timing used within the system, however, it is possible to strobe information from the sense amplifier before the write strobe is created, thereby storing the data in the out buffer before the large write transients occur.

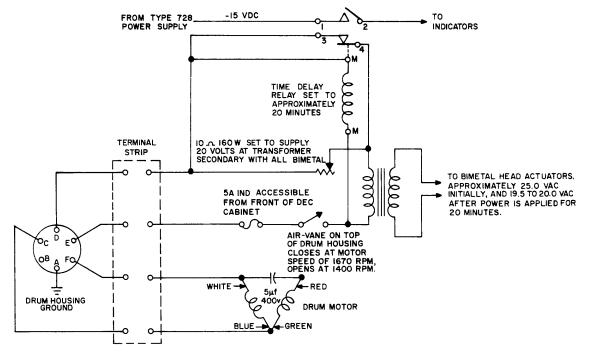

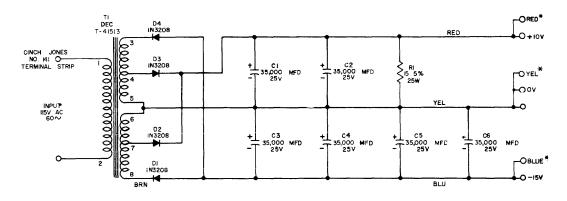

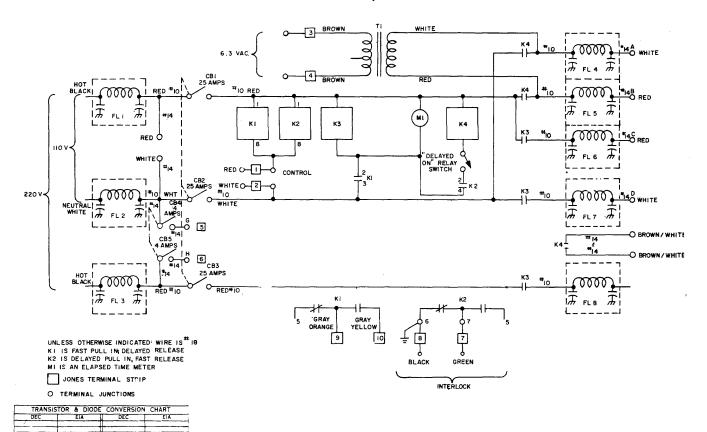

### Power Supply and Distribution

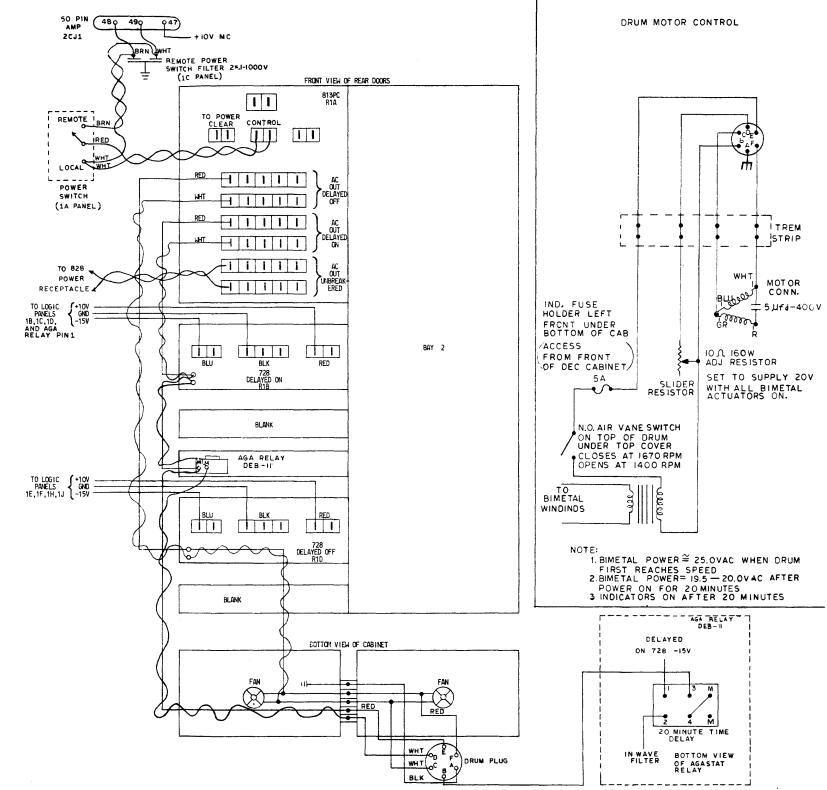

The parallel drum operates from a single source of 115-volt, 60-cycle, single-phase power. Control and overload protection for this power within the machine are exercised by a Type 813 Power Control. Operation of the power control can be controlled by the REMOTE ON/OFF/ LOCAL ON switch located on the indicator panel at the front of the machine, or by means of a contact closure provided from the computer when the computer is energized. The ac output of the power control operates the two cabinet fan motors, the two Type 728 Power Supplies, and the drum motor. Primary ac voltage is also supplied to a step down transformer through the normally closed contacts of a time-delay relay or (after the relay time has expired) through a voltage dropping resistor. This configuration provides a heater voltage to the bimetal strips in the drum of approximately 25 vac for the first 20 minutes of drum operation (current supplied to the transformer primary through the normally closed relay contacts) and supplies a heater voltage from 19.5 to 20.0 vac when the drum is ready for data transfers (current supplied to the primary of the transformer through the voltage dropping resistor). The primary of this transformer is also protected by a 5-ampere indicating type fuse and is interrupted if the vane

Figure 2-2 Data Head Selection

air switch on the top of the drum housing opens, indicating low drum speed. The bimetal heater voltage is supplied in parallel to all of the bimetal strip heaters. The – 15 volt output of the Type 728 Power Supply, which operates the indicator panel, is controlled by the normally open contact of the 20-minute time-delay relay. Therefore, the indicators do not light until the drum has been energized for 20 minutes, at which time the drum has reached synchronous speed and thermal stability and is ready to transfer data. All ac and dc wiring within the parallel drum is indicated on engineering drawing PW-D-23-0-8 and on Figure 2-3.

Figure 2-3 Drum Power Circuit

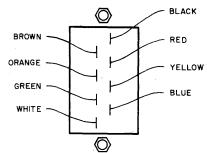

The normal module operating voltages of + 10 and - 15 vdc are supplied to each rack of logic through a color-coded connector at the right side of each rack, as seen from the module side. Marginal-check terminals on these connectors are connected in common on all module mounting panels within the machine so that the + 10 volt mc can be used to marginal check the + 10 vdc voltages supplied to any mounting panel within the machine. The color-coding of these connectors is as follows, from top to bottom.

- a. Green, +10 v mc from the computer

- b. Red, +10 vdc internal supply

- c. Black, ground

- d. Blue, 15 vdc internal supply

- e. Yellow, 15 vdc external marginal-check supply (unused)

Three single-pole double-throw switches at the end of each rack of logic allow selection of either the normal internal + 10 vdc power or an external marginal-check source of power for distribution to the logic. The top switch selects the + 10 vdc supply routed to terminal A of all modules in that mounting panel. In the down position the fixed internal + 10 volt supply connected to the red terminal is routed to all of the modules; in the up position the marginalcheck voltage connected to the green terminal is supplied to terminal A of all of the modules. The center switch performs the same selection as the top switch for connection of a + 10 volt supply to terminal B of all modules within a mounting panel. The bottom switch selects the - 15 volt supply to be routed to terminal C of all modules in a mounting panel. In the down position the fixed - 15 volt output of the internal power supply, received at the blue terminal, is supplied to all of the modules; in the up position a marginal-check voltage, supplied by an external supply connected to the yellow terminal, is supplied to terminal C of all modules. However, since the -15 volt supply is the collector load potential in most DEC modules and is normally clamped at - 3 volts, marginal checking of this source has very little effect upon the logical operation of the machine. Marginal checking of this line, however, does vary the output of modules containing an output pulse amplifier, and is therefore useful in checking the operation of circuits employing pulse amplifiers or in checking the operation of circuits which follow them.

#### READ-WRITE CYCLE

Three computer IOT instructions initialize and initiate a complete transfer. These instructions are the DIA or DBA, DWC, and DCL, and must occur in this order. Each of these instructions causes two 0.4 microsecond pulses to be supplied to the parallel drum, one at computer 7 time (TP7) and one at computer 10 time (TP10). The DIA instruction, for example, produces a DIA 7-4 pulse at computer 7 time and a DIA 10-4 pulse at computer 10 time. Normally the pulse supplied at computer 7 time clears a register and the pulse at computer 10 time, which is approximately 2.2 microseconds later, strobes information into or out of registers. In the three instruction sequence mentioned previously, the first command pulse received is a DIA 7-4 pulse, which clears all necessary control flip-flop registers. The DIA 10-4 pulse loads the read control flip-flop, loads the RFB, and loads the IL from the contents of the computer IO register. This same operation occurs during a DBA instruction except that the DBA 7-4 pulse also sets the DBA sync flip-flop. The second instruction clears the WC with a DWC 7-4 pulse,

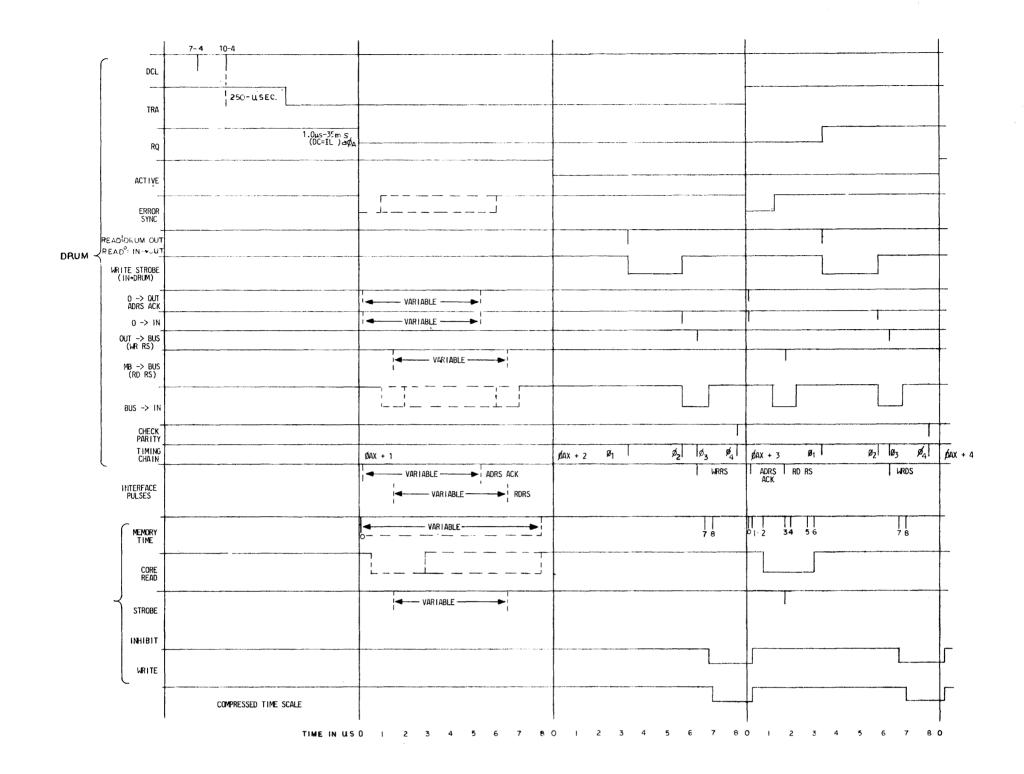

then loads the write control flip-flop, loads the WFB, and loads the WC from the contents of the computer IO register by means of the DWC 10-4 pulse. The third instruction increments the contents of the WC by one and clears the DCL by means of a DCL 7-4 pulse, then loads the contents of the computer IO register into the DCL and sets the busy flip-flop by means of the DCL 10-4 command pulse. This command pulse also initiates operation of the 250-microsecond delay (Type 4301 module at location 1F11) which eventually initiates the data transfer. After giving the DCL instruction, the computer continues in the main program. Engineering drawing 1 shows the timing of control signals and the flow of information during a transfer.

The 250-microsecond delay is necessary for the read and write field select circuits to assume their respective states. Settling time for the readers is between 50 and 100 microseconds. Therefore, the 250-microsecond delay allows all transients to settle before the transfer commences. When the 250-microsecond delay expires, the transfer request (TRA) flip-flop is set to 1, and the timing of the transfer is now in the control of the drum timing and control elements.

Every 8.5 microseconds the timing element produces a phase A pulse which increments the contents of the DC so that it keeps track of the angular position of the drum. When the drum position arrives at the drum address or initial location of the transfer, the DC=1L signal is produced. The next phase A pulse sets the request (RQ) flip-flop to the 1 state. The request flip-flop then signals the memory control that a transfer cycle is requested by the drum. The change of state of the request flip-flop from 0 to 1 sets the error sync flip-flop to the 1 status. When the request is honored by memory control, the address acknowledge pulse is returned from the memory control to the drum. This pulse immediately clears the error sync flip-flop. If the request is honored within approximately 5.1 microseconds, the next phase A pulse sets the active (ACT) flip-flop to the 1 state, and data transfers occur within the current clock cycle. If the address acknowledge pulse is not received more than 2 microseconds before the phase A time occurs, indicating that the request was not honored by memory control, the request flip-flop is cleared and the parallel drum goes into a waiting loop. The TRA flip-flop remains in the 1 status and again initiates a request when the DC=1L signal is generated. This takes one drum revolution or approximately 35 milliseconds.

Since the drum usually has the highest request priority, a drum request is normally honored by memory control. When a drum request is made, memory control usually completes the current cycle and then honors the drum request by supplying an address acknowledge pulse after a period of from 0.1 to 5.1 microseconds.