RJP04 moving head disk subsystem maintenance manual

1st Edition, August 1974 2nd Printing (Rev), February 1975

## Copyright © 1974, 1975 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC

**PDP**

**FLIP CHIP**

**FOCAL**

**DIGITAL**

**COMPUTER LAB**

**UNIBUS**

**MASSBUS**

## **CONTENTS**

|           |                                        | Page   |

|-----------|----------------------------------------|--------|

| CHAPTER 1 | SYSTEM AND PHYSICAL DESCRIPTION        |        |

| 1.1       | GENERAL                                | . 1-1  |

| 1.1.1     | Scope                                  | . 1-1  |

| 1.1.2     | Related Documentation                  | . 1-1  |

| 1.2       | DISK FILE SYSTEM                       | . 1-1  |

| 1.2.1     | Unibus                                 | . 1-1  |

| 1.2.2     | Massbus                                | . 1-2  |

| 1.3       | RH11 CONTROLLER                        | . 1-3  |

| 1.3.1     | Register and Control Path              | . 1-4  |

| 1.3.2     | DMA Data Path                          | . 1-4  |

| 1.3.2.1   | Write Operation                        | . 1-5  |

| 1.3.2.2   | Read Operation                         | . 1-6  |

| 1.3.2.3   | Write-Check Data Transfer              | . 1-8  |

| 1.3.2.4   | Data Transfer Rates                    | . 1-8  |

| 1.4       | RP04 DRIVE                             | . 1-9  |

| 1.5       | RJP04 SYSTEM SPECIFICATIONS            | . 1-11 |

| 1.5.1     | Unibus NPR Latency                     | . 1-11 |

| 1.5.2     | Data Format                            | . 1-11 |

| 1.5.3     | Error Correcting Code (ECC)            | . 1-11 |

| 1.5.4     | RH11 Massbus Controller Specifications |        |

| 1.5.5     | RP04 Drive Specifications              |        |

| CHAPTER 2 | MASSBUS INTERFACE                      |        |

| 2.1       | GENERAL                                | . 2-1  |

| 2.2       | DATA BUS                               | . 2-1  |

| 2.3       | CONTROL BUS                            | . 2-1  |

| 2.4       | COMMAND INITIATION                     | . 2-4  |

| 2.4.1     | Non-Data Transfer Commands             | . 2-4  |

| 2.4.2     | Data Transfer Commands                 | . 2-4  |

| 2.5       | READING AND WRITING DRIVE REGISTERS    | . 2-4  |

| 2.6       | DATA TRANSFER                          | . 2.5  |

| 2.7       | MASSBUS PHYSICAL DESCRIPTION           | . 2-5  |

| CHAPTER 3 | OPERATION AND PROGRAMMING              |        |

| 3.1       | GENERAL                                | . 3-1  |

| 3.2       | TRACK FORMATTING                       | . 3-1  |

| 3.2.1     | Header Format                          | . 3-1  |

| 3.2.2     | Header Field Handling                  | . 3-1  |

| 3.2.2.1   | Normal Header Compare                  | . 3-1  |

| 3.2.2.2   | Header Compare Inhibit                 |        |

| 3.2.2.3   | Key Field                              |        |

| 3.2.2.4   | Key Field Handling                     |        |

| 3.2.2.5   | Key Words Update                       |        |

| 3.2.2.6   | Header Compare Error Handling          |        |

| 3.2.3     | Data Format                            |        |

| 3.3       | FUNCTION CODES                         |        |

| 3.4       | DATA TRANSFER COMMANDS                 |        |

| 3.4.1     | Read Command                           |        |

|         | Pa <sub>i</sub>                                        | ge |

|---------|--------------------------------------------------------|----|

| 3.4.1.1 | Examining ECC for Error                                | 10 |

| 3.4.1.2 | Read with Implied Seek                                 | 11 |

| 3.4.1.3 | Spiral Read Capability                                 | 11 |

| 3.4.1.4 | Termination Conditions                                 |    |

| 3.4.1.5 | Error Handling                                         | 12 |

| 3.4.1.6 | Offset Recovery Procedure                              |    |

| 3.4.1.7 | Read Header and Data Command                           | 13 |

| 3.4.2   | Write Command Execution                                | 13 |

| 3.4.2.1 | Writing of ECC                                         |    |

| 3.4.2.2 | Termination                                            |    |

| 3.4.2.3 | Write Lock Operation                                   |    |

| 3.4.2.4 | Write Error Conditions                                 |    |

| 3.4.2.5 | Multisector Write Operation                            |    |

| 3.4.2.6 | Write Check Commands                                   |    |

| 3.5     | POSITIONING COMMANDS                                   |    |

| 3.5.1   | Unload (Standby)/Cycle-Up Operation (03 <sub>8</sub> ) |    |

| 3.5.2   | Seek Command (05 <sub>8</sub> )                        |    |

| 3.5.2.1 | Seek Command Initiation (05 <sub>8</sub> )             |    |

| 3.5.2.2 | Seek Command Execution                                 |    |

| 3.5.2.3 | Seek Command Termination                               |    |

| 3.5.2.4 | Incomplete Seek Handling                               |    |

| 3.5.2.5 | Implied Seek Operation                                 |    |

| 3.5.2.6 | Error Condition Handling                               |    |

| 3.5.2.7 | Mid-Transfer Seek Operation                            |    |

| 3.5.2.8 | Termination                                            |    |

| 3.5.2.9 | Error Handling                                         |    |

| 3.5.3   | Recalibrate Command (07 <sub>8</sub> )                 |    |

| 3.5.4   | Offset Command (15 <sub>8</sub> )                      |    |

| 3.5.5   | Return to Centerline (RTC) Command (17 <sub>8</sub> )  |    |

| 3.5.6   | Search Command (31 <sub>8</sub> )                      |    |

| 3.6     | DUAL CONTROLLER OPTION                                 |    |

| 3.6.1   | Unseized Operation                                     |    |

| 3.6.2   | Seized Operation                                       |    |

| 3.6.3   | Switching to Other Controller and Time-Out             |    |

| 3.6.4   | Returning to the Unseized State                        |    |

| 3.6.5   | Device Seize from Unseized State                       |    |

| 3.6.6   | Manual CONTROLLER SELECT Switch                        |    |

| 3.6.7   | Attention Summary Bits                                 |    |

| 3.6.8   | START/STOP and STANDBY Switches                        |    |

| 3.6.9   | Persistent Error Handling                              |    |

| 3.6.10  | Initialize in Dual Controller Operation                |    |

| 3.7     | ERROR CORRECTING CODE PROCESSING                       |    |

| 3.7.1   | Noncorrectable Errors                                  |    |

| 3.7.2   | Error Correction Techniques                            |    |

| 3.8     | ERROR CLASSIFICATION AND DATA RECOVERY                 |    |

|           |                                                              | Page   |

|-----------|--------------------------------------------------------------|--------|

| CHAPTER 4 | PROGRAMMING DEFINITIONS AND SPECIFICATIONS                   |        |

| 4.1       | GENERAL                                                      | . 4-1  |

| 4.2       | DEFINITIONS                                                  | . 4-1  |

| 4.3       | PROGRAMMING NOTES                                            | . 4-2  |

| 4.4       | INTERRUPT CONDITIONS                                         |        |

| 4.5       | TERMINATION OF DATA TRANSFERS                                |        |

| 4.6       | CONTROL (RPCS1) REGISTER (776700)                            |        |

| 4.7       | WORD COUNT (RPWC) REGISTER (776702)                          |        |

| 4.8       | UNIBUS ADDRESS (RPBA) REGISTER (776704)                      |        |

| 4.9       | DESIRED SECTOR/TRACK ADDRESS (RPDA) REGISTER (776706)        |        |

| 4.10      | STATUS (RPCS2) REGISTER (776710)                             |        |

| 4.11      | DRIVE STATUS (RPDS) REGISTER (776712)                        |        |

| 4.12      | ERROR (RPER1) REGISTER 01 (776714)                           |        |

| 4.13      | ATTENTION SUMMARY (RPAS) REGISTER (776716)                   |        |

| 4.13.1    | Read Capability                                              |        |

| 4.13.2    | Write Capability                                             |        |

| 4.13.3    | Attention Handling in Dual Controller Case                   |        |

| 4.13.4    | Attention Handling on a Persistent Error (Single Controller) |        |

| 4.14      | LOOK-AHEAD (RPLA) REGISTER (776720)                          |        |

| 4.15      | DATA BUFFER (RPDB) REGISTER (776722)                         |        |

| 4.16      | MAINTENANCE (RPMR) REGISTER (776724)                         |        |

| 4.17      | DRIVE TYPE (RPDT) REGISTER (776726)                          |        |

| 4.18      | SERIAL NUMBER (RPSN) REGISTER (776730)                       |        |

| 4.19      | OFFSET (RPOF) REGISTER (776732)                              |        |

| 4.20      | DESIRED CYLINDER (RPDC) REGISTER (776734)                    |        |

| 4.21      | CURRENT CYLINDER (RPCC) REGISTER (776736)                    |        |

| 4.22      | ERROR (RPER2) REGISTER 02 (776740)                           |        |

| 4.23      | ERROR (RPER3) REGISTER 03 (776742)                           |        |

| 4.24      | ECC POSITION (RPEC1) REGISTER (776744)                       |        |

| 4.25      | ECC PATTERN (RPEC2) REGISTER (776746)                        |        |

| 4.26      | RH11/RP04 REGISTER SUMMARY                                   |        |

|           |                                                              |        |

| CHAPTER 5 | THEORY OF OPERATION                                          |        |

| 5.1       | GENERAL                                                      |        |

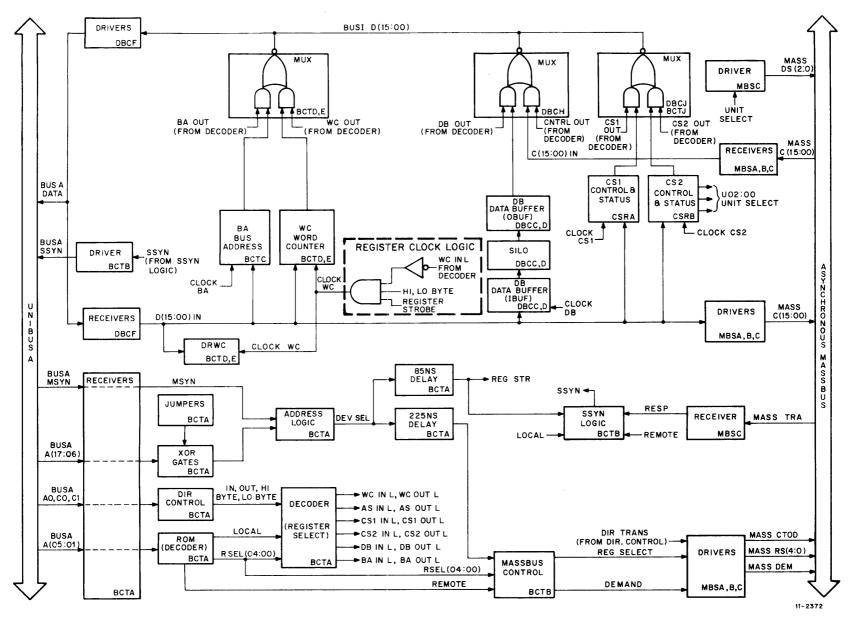

| 5.2       | REGISTER CONTROL PATH                                        |        |

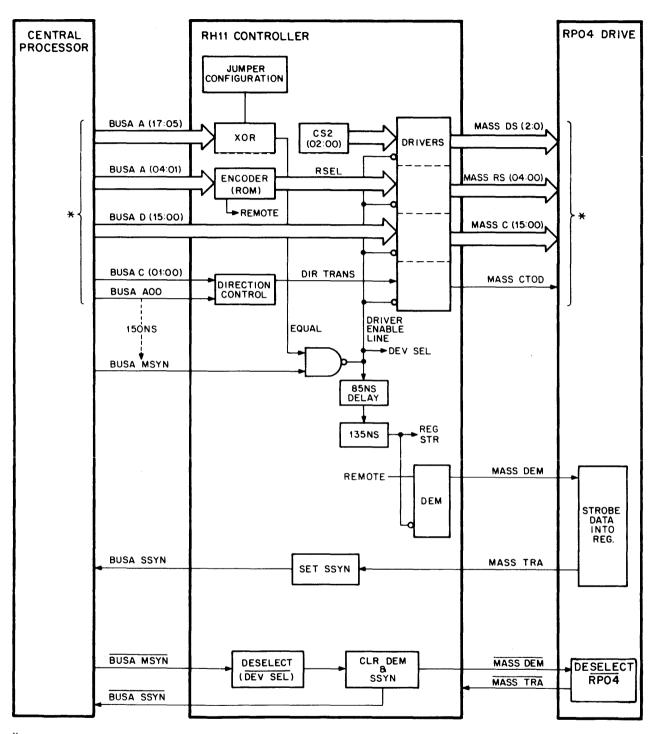

| 5.2.1     | Writing a Local Register                                     |        |

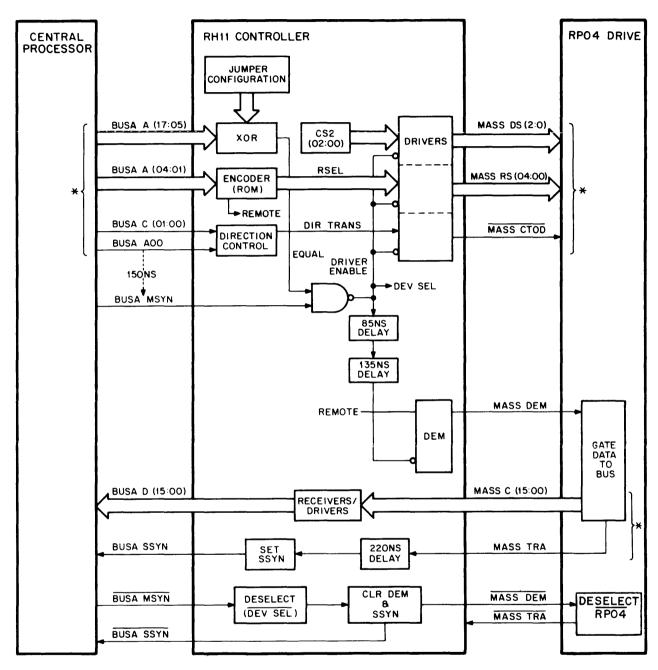

| 5.2.2     | Reading a Local Register                                     |        |

| 5.2.3     | Writing a Remote Register                                    |        |

| 5.2.4     | Reading a Remote Register                                    |        |

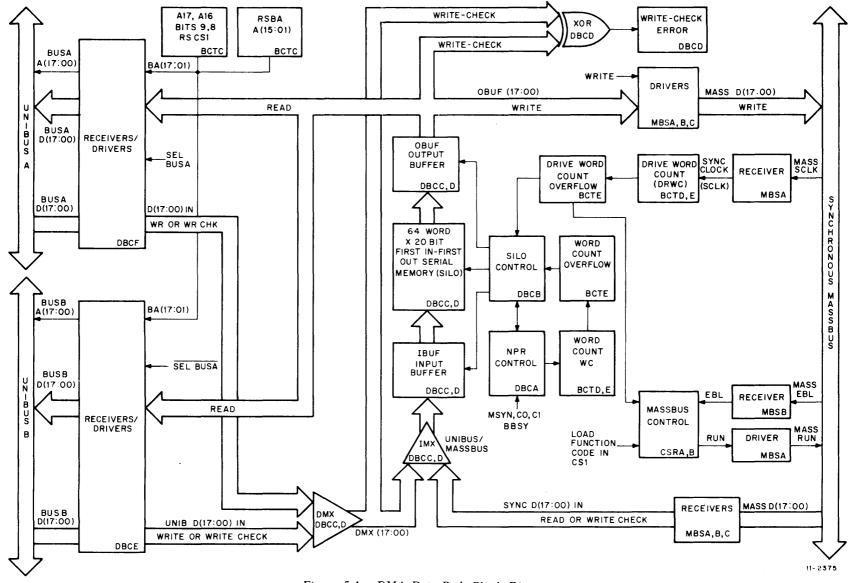

| 5.3       | DMA DATA PATH                                                |        |

| 5.3.1     | Write Block Transfer                                         |        |

| 5.3.2     | Read Block Transfer                                          |        |

| 5.3.3     | Write-Check Block Transfer                                   |        |

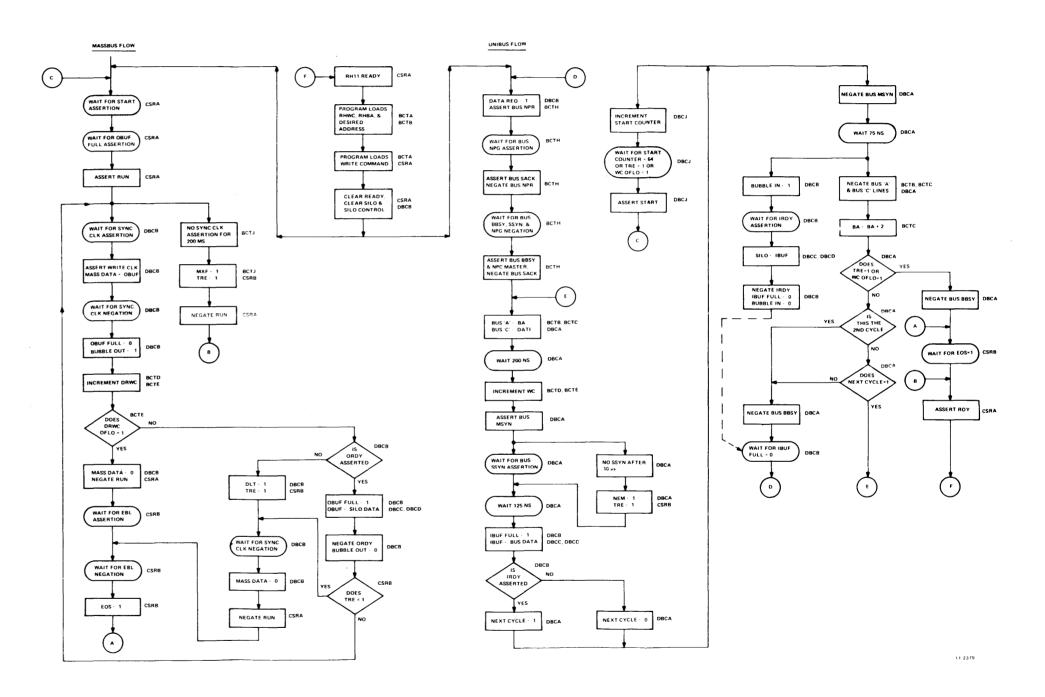

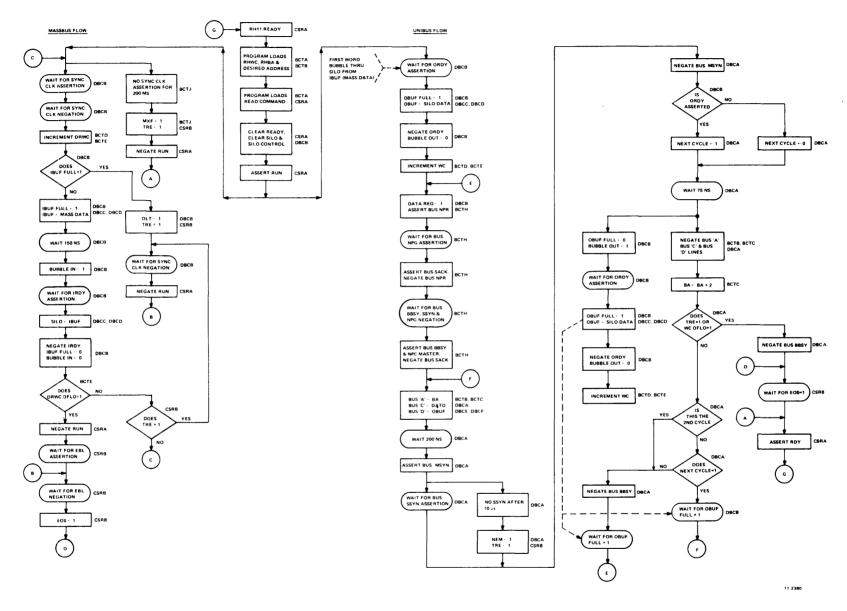

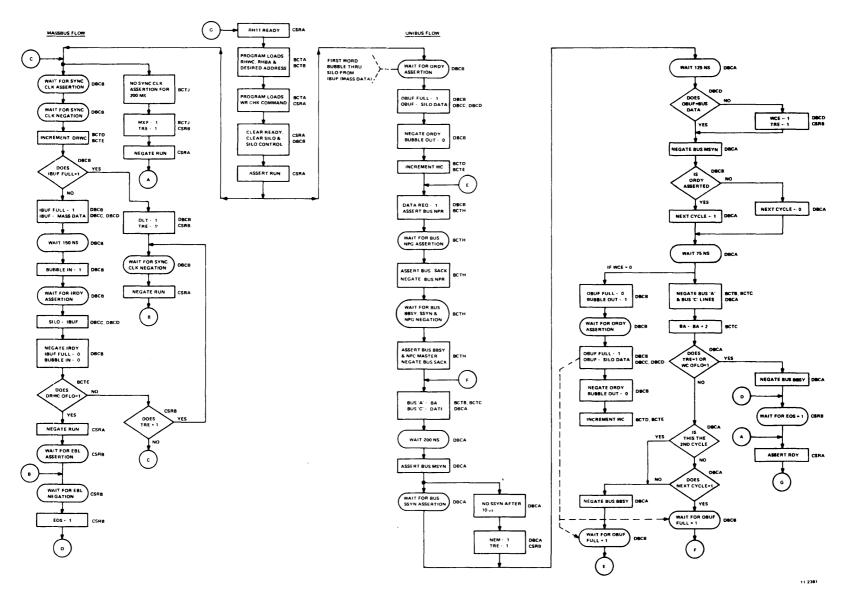

| 5.4       | WRITE FLOW DIAGRAM DESCRIPTION                               |        |

| 5.4.1     | Unibus Flow Description                                      |        |

| 5.4.2     | Massbus Flow Description                                     |        |

| 5.5       | READ FLOW DIAGRAM DESCRIPTION                                |        |

| 5.5.1     | Massbus Flow                                                 |        |

| 5.5.2     | Unibus Flow                                                  | . 5-17 |

|           |                                      | Page |

|-----------|--------------------------------------|------|

| 5.6       | WRITE CHECK FLOW DIAGRAM DESCRIPTION | 5-17 |

| 5.6.1     | Massbus Flow Description             | 5-19 |

| 5.6.2     | Unibus Flow Description              | 5-19 |

| CHAPTER 6 | DETAILED LOGIC DESCRIPTION           |      |

| 6.1       | GENERAL                              | 6-1  |

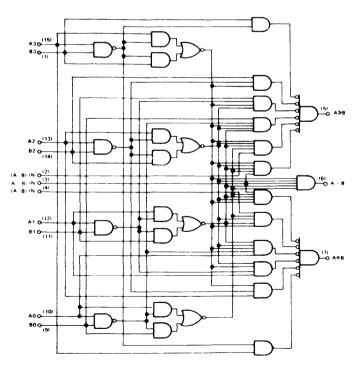

| 6.2       | BCTA LOGIC DIAGRAM                   |      |

| 6.2.1     | Local/Remote Register Selection      |      |

| 6.2.2     | RSEL Signals                         |      |

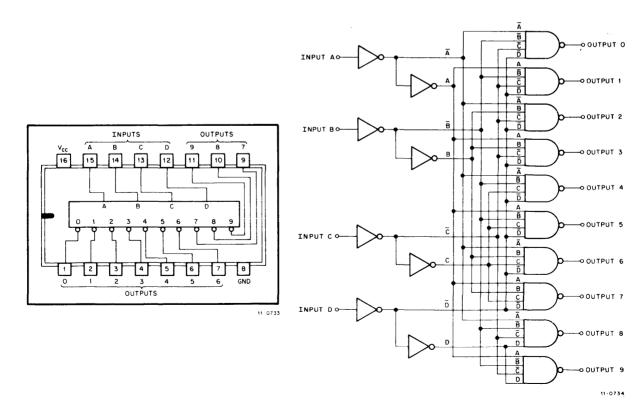

| 6.2.3     | Decoder Inputs                       | 6-7  |

| 6.2.4     | Decoder Outputs                      | 6-7  |

| 6.2.5     | Word or Byte Addressing              | 6-8  |

| 6.2.6     | Control Lines                        | 6-8  |

| 6.2.7     | ODD BYTE L Signal                    | 6-8  |

| 6.2.8     | <u> </u>                             | 6-8  |

|           | Device Select (DEV SEL) Logic        |      |

| 6.2.9     | Deskew Demand (DESK DEM)             |      |

| 6.2.10    | Register Strobe (REG STR)            | 6-8  |

| 6.2.11    | Control Out (CTRL OUT) Signal        |      |

| 6.2.12    | Gate Control (GATE CNTL) Signal      |      |

| 6.3       | LOGIC DIAGRAM BCTB                   |      |

| 6.3.1     | Deskew Demand (DESK DEM) Logic       |      |

| 6.3.2     | Response from Drive                  |      |

| 6.3.3     | SSYN Logic                           |      |

| 6.3.4     | Gating Address Onto Unibus           |      |

| 6.3.5     | Data Buffer Out Clock                |      |

| 6.4       | LOGIC DIAGRAM BCTC                   | 6-10 |

| 6.4.1     | Clocking Bus Address Register        | 6-11 |

| 6.4.2     | Address Bit 00                       | 6-11 |

| 6.4.3     | Count Down (CNT DW) Flip-Flop        | 6-11 |

| 6.4.4     | Bus Address Outputs                  |      |

| 6.5       | LOGIC DIAGRAM BCTD, BCTE             | 6-11 |

| 6.5.1     | Word Count Registers                 |      |

| 6.5.2     | Word Count or Bus Address Selection  |      |

| 6.5.3     | Clear Logic                          | 6-12 |

| 6.5.4     | Word Count Overflow                  |      |

| 6.6       | LOGIC DIAGRAM BCTF                   |      |

| 6.6.1     | Interrupt Request                    |      |

| 6.6.2     | Bus Request                          |      |

| 6.6.3     | Interrupt Done                       |      |

| 6.7       | LOGIC DIAGRAM BCTH                   |      |

| 6.7.1     |                                      |      |

| 6.7.1     |                                      |      |

| 6.7.3     | Acquiring Bus Mastership             |      |

|           | Completion of NPR Cycle              |      |

| 6.8       | LOGIC DIAGRAM BCTJ                   |      |

| 6.8.1     | MB INIT Signal                       |      |

| 6.8.2     | Gating High Byte of CS1/CS2          |      |

| 6.8.3     | MXF Error Flip-Flop                  |      |

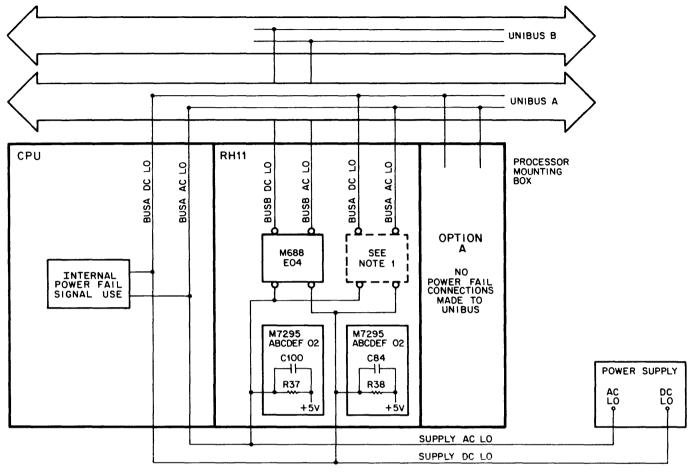

| 6.8.4     | AC LO and DC LO                      | 6-14 |

|                  | Page                                            | е |

|------------------|-------------------------------------------------|---|

| 6.9              | BCTK LOGIC DIAGRAM                              | - |

| 6.10             | LOGIC DIAGRAM CSRA                              |   |

| 6.10.1           | Data Transfer Command Logic                     |   |

| 6.10.2           | RUN Flip-Flop                                   | 6 |

| 6.10.3           | BUSY Flip-Flop                                  | 6 |

| 6.10.4           | Port Select Flip-Flop                           | 7 |

| 6.10.5           | CS1 Clocking Logic                              | 7 |

| 6.10.6           | Interrupt Requests                              | 7 |

| 6.11             | LOGIC DIAGRAM CSRB                              | 7 |

| 6.11.1           | CS2 Clocking Signals                            | 7 |

| 6.11.2           | Program Clear Bit                               |   |

| 6.11.3           | Bus Address Increment Inhibit                   | 7 |

| 6.11.4           | Unit Select Number                              |   |

| 6.11.5           | Parity Test Mode                                |   |

| 6.11.6           | Function Load                                   |   |

| 6.11.7           | Non-Existent Device                             |   |

| 6.11.8           | Transfer Error                                  |   |

| 6.11.9           | Program Error Flip-Flop                         |   |

| 6.11.10          | End of Sector (EOS) Flip-Flop                   |   |

| 6.11.11          | Unibus Parity Error (UPE) Flip-Flop             |   |

| 6.12             | LOGIC DIAGRAM DBCA                              |   |

| 6.12.1           | NPC MASTER Signal                               |   |

| 6.12.2           | ADDR TO BUS Signal                              |   |

| 6.12.3           | MSYN DESKEW                                     |   |

| 6.12.4           | MSYN Inhibit Conditions                         |   |

| 6.12.5           | MSYN Timeout                                    |   |

| 6.12.5<br>6.12.6 | DATA WAIT and MSYN WAIT One-Shot Multivibrators |   |

| 6.12.7           |                                                 |   |

| 6.12.7<br>6.12.8 | CYCLE COUNT and NEXT CYCLE Flip-Flops           |   |

|                  | ERROR Conditions                                |   |

| 6.12.9           | 1-Cycle Jumper                                  |   |

| 6.12.10          | BUS HOG Mode                                    |   |

| 6.13             | LOGIC DIAGRAM DBCB                              |   |

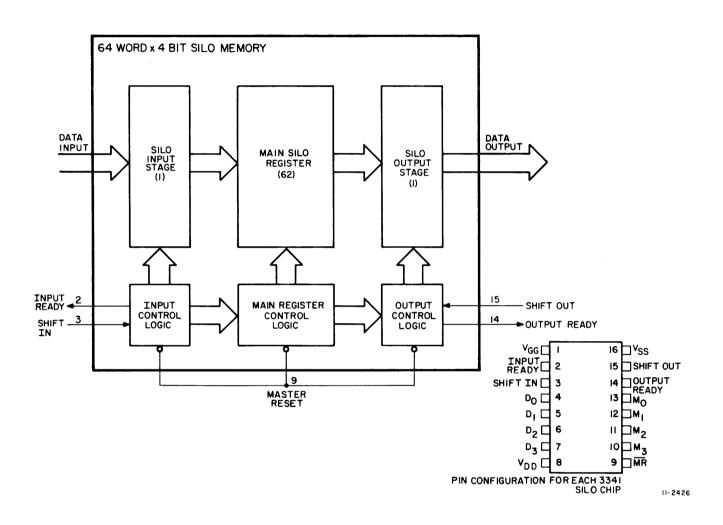

| 6.13.1           | Silo Input Logic                                |   |

| 6.13.2           | Silo Output Logic                               |   |

| 6.13.3           | Error Flip-Flop                                 |   |

| 6.13.4           | Generation of INH CLK L                         | ~ |

| 6.13.5           | SILO CLR Generation                             |   |

| 6.13.6           | Write Clock                                     |   |

| 6.13.7           | Gating Synchronous Data                         |   |

| 6.13.8           | Data Requests (Write Command)                   |   |

| 6.13.9           | Data Requests (Read or Write-Check)             |   |

| 6.13.10          | NEXT SIGNAL (Write)                             |   |

| 6.13.11          | NEXT SIGNAL (Read or Write-Check)               | 7 |

| 6.13.12          | Word Count Increment (Write Command)            | 7 |

| 6.13.13          | Word Count Increment (Read or Write-Check)      |   |

| 6.13.14          | EXCEPTION ERROR (Write Command)                 |   |

| 6.13.15          | EXCEPTION ERROR (READ or WRITE-CHECK)           |   |

| 6.14             | LOGIC DIAGRAM DBCC                              |   |

| 6.15             | LOGIC DIAGRAM DBCD                              |   |

|             |                                                  | Page   |

|-------------|--------------------------------------------------|--------|

| 6.16        | LOGIC DIAGRAM DBCE                               | . 6-28 |

| 6.17        | LOGIC DIAGRAM DBCF                               | . 6-28 |

| 6.18        | LOGIC DIAGRAM DBCH                               |        |

| 6.18.1      | Parity Jumpers                                   |        |

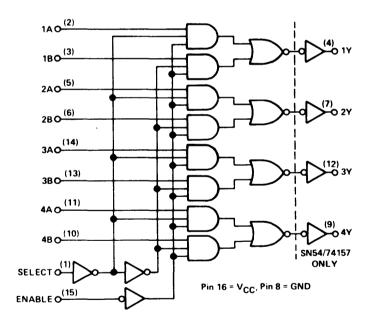

| 6.18.2      | 74157 Parity Multiplexer                         |        |

| 6.18.3      | 8234 Control Line/Data Buffer Multiplexing       |        |

| 6.19        | LOGIC DIAGRAM DBCJ                               |        |

| 6.19.1      | Start Counter                                    |        |

| 6.19.2      | CS1/CS2 Gating Onto BUSI                         |        |

| 6.19.3      | Voltage Regulator                                |        |

| 6.20        | M7297 PARITY CONTROL MODULE (PACA)               |        |

| 6.20.1      | Synchronous Massbus Parity                       |        |

| 6.20.2      | Read or Write-Check Parity                       |        |

| 6.20.3      | Write Parity                                     |        |

| 6.20.4      | Asynchronous Massbus Parity                      |        |

| 6.21        | M5904 MASSBUS TRANSCEIVER MBSA, MBSB, MBSC       |        |

| 6.22        | UNIBUS A CABLE DIAGRAM                           |        |

| 6.23        | UNIBUS B CABLE DIAGRAM                           |        |

| 6.24        | M9300 UNIBUS B TERMINATOR                        |        |

| 6.24.1      | NPR Arbitration and Issuance of NPG              |        |

| 6.24.2      | Prevention of NO-SACK TIMEOUT                    |        |

| 6.25        | G727 GRANT CONTINUITY MODULE                     |        |

| 6.26        | M688 POWER FAIL DRIVER                           |        |

| 6.27        | M5904 MASSBUS TRANSCEIVER MODULE                 |        |

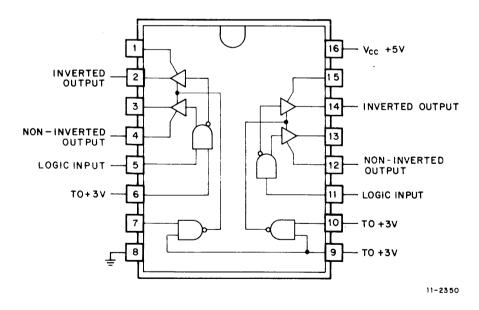

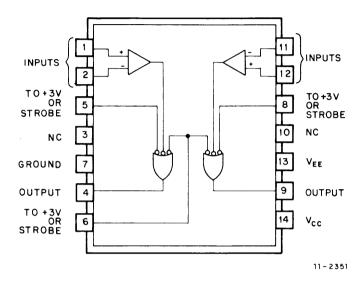

| 6.27.1      | 75113 Dual Differential Driver Chip              |        |

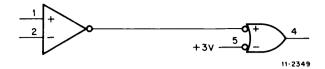

| 6.27.2      | 75107B Dual Differential Line Receiver Chips     |        |

| 6.28        | 7009938 TERMINATOR PACK ASSEMBLY                 |        |

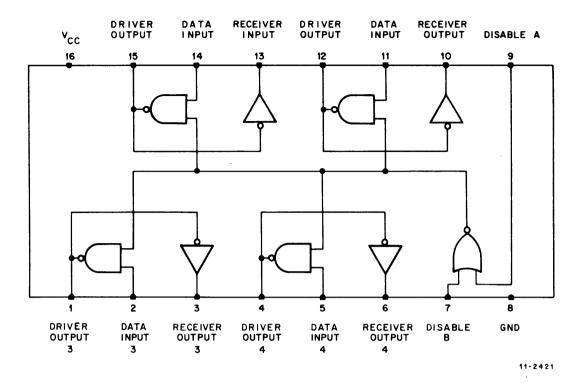

| 6.29        | M8838 UNIBUS TRANSCEIVER MODULE                  |        |

| 6.30        | UNIBUS TERMINATION                               |        |

|             |                                                  |        |

| CHAPTER 7   | INSTALLATION & MAINTENANCE                       |        |

| 7.1         | INTRODUCTION                                     | . 7-1  |

| 7.2         | INSTALLATION                                     | . 7-1  |

| 7.2.1       | Mechanical                                       | . 7-1  |

| 7.2.2       | Electrical                                       | . 7-1  |

| 7.2.2.1     | Power Cable Connections                          | . 7-1  |

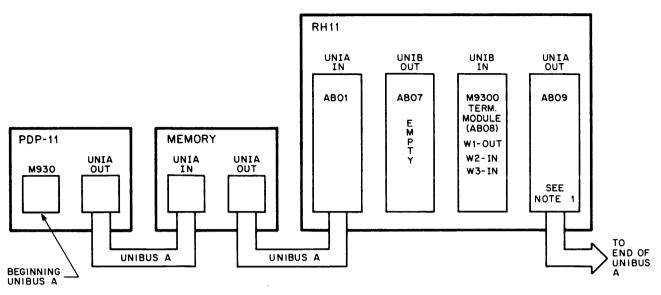

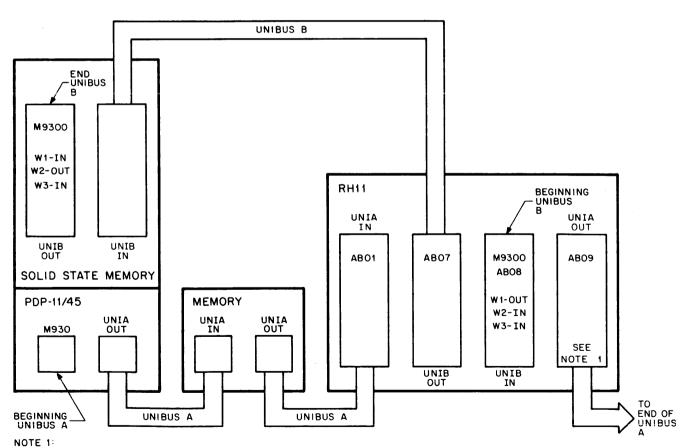

| 7.2.2.2     | Unibus Cable Connections                         | . 7-1  |

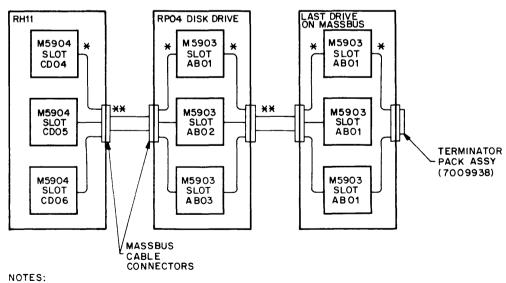

| 7.2.2.3     | Massbus Cables                                   | . 7-3  |

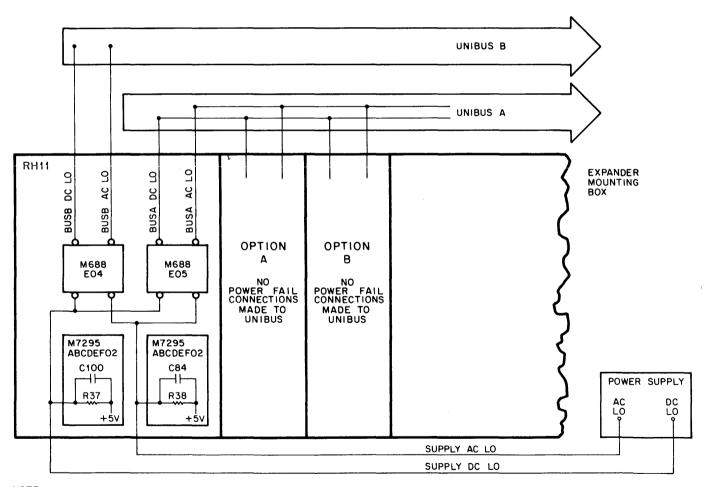

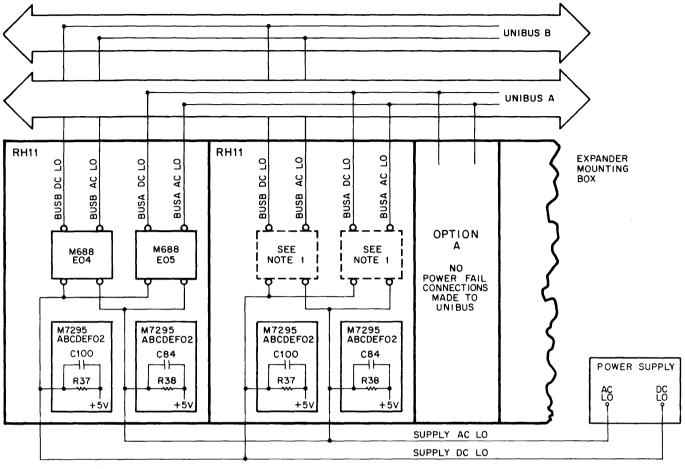

| 7.2.2.4     | AC LO, DC LO                                     | . 7-3  |

| 7.2.3       | Jumper Configurations                            | . 7-7  |

| 7.2.3.1     | BCT Module                                       | . 7-7  |

| 7.2.3.2     | DBC Module                                       | . 7-9  |

| 7.2.3.3     | CSR Module                                       | . 7-9  |

| 7.3         | VISUAL INSPECTION                                |        |

| 7. <b>4</b> | DIAGNOSTIC MAINTENANCE                           |        |

| 7.4.1       | MAINDEC-11-DZRPI RP04 Diskless Controller Test   | . 7-10 |

| 7.4.2       | MAINDEC-11-DZRPJ RP04 Functional Controller Test | . 7-10 |

| 7.4.3       | MAINDEC-11-DZRPK Mechanical Read/Write Test      | . 7-10 |

| 7.4.4       | MAINDEC-11-DZRPP and -DZRPQ Dual-Port Logic Test |        |

|             | (Parts 1 and 2)                                  |        |

| 7.4.5       | MAINDEC-11-DZRPR 20-Sector Mode Logic Test       | . 7-11 |

|            |                                                                 | Page  |

|------------|-----------------------------------------------------------------|-------|

| 7.4.6      | MAINDEC-11-DZRPN Multidrive Exerciser                           | 7-11  |

| 7.4.7      | MAINDEC-11-DZRPL Formatter Program                              | 7-11  |

| 7.4.8      | MAINDEC-11-DZRPM Head Alignment Verification Program            | 7-11  |

| 7.4.9      | MAINDEC-11-DZRPO Peripheral Test Generator Program              |       |

| APPENDIX A | INTEGRATED CIRCUIT DESCRIPTIONS                                 |       |

|            | ILLUSTRATIONS                                                   |       |

| Figure No. | Title                                                           | Page  |

| 1-1        | RH11 Simplified System Diagram                                  | . 1-2 |

| 1-2        | RH11 Multiport System                                           | . 1-3 |

| 1-3        | RH11 Combined With Unichannel 15 System                         |       |

| 1-4        | Dual Controller Option (With One Processor)                     |       |

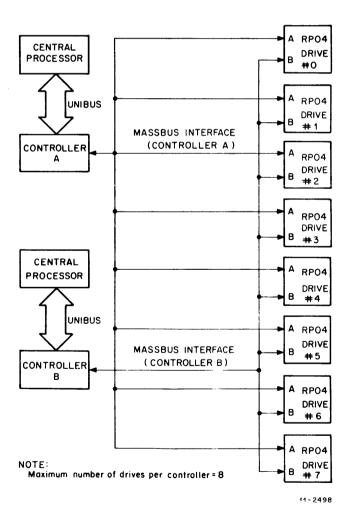

| 1-5        | Dual Controller Option (With Dual Processor)                    |       |

| 1-6        | RH11 Simplified Data Path Diagram                               |       |

| 1-7        | Read Command Data Transfer                                      |       |

| 1-8        | Write Data Transfer Sequence                                    |       |

| 1-9        | Read Header and Data Command Transfer                           |       |

| 1-10       | Write Header and Data Command Transfer (Pack Format Command)    |       |

| 2-1        | Massbus Interface Lines                                         |       |

| 2-2        | Single-Port Subsystem Cable Routing                             |       |

| 2-3        | Dual-Port Subsystem Cable Routing                               |       |

| 3-1        | RJP04 Subsystem Registers                                       |       |

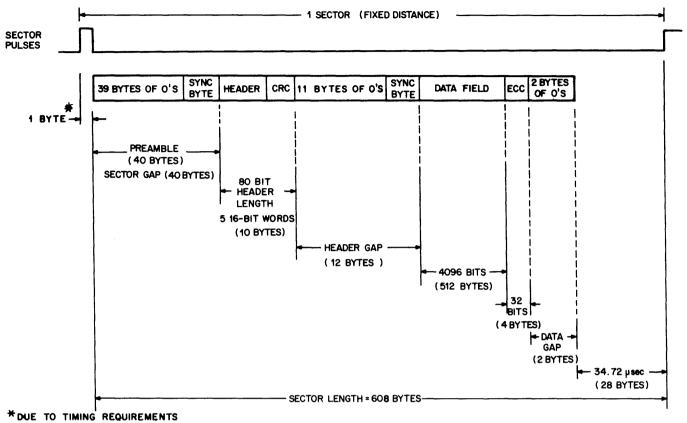

| 3-2        | Detailed Sector Format                                          |       |

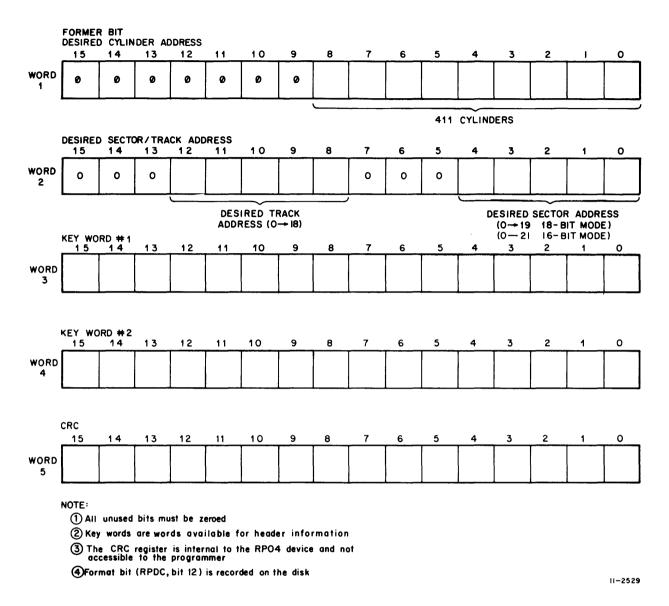

| 3-3        | Header Format                                                   |       |

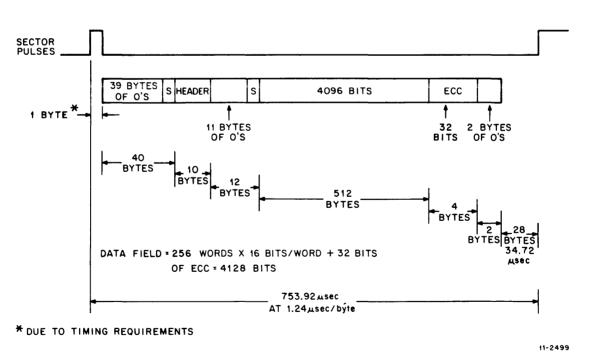

| 3-4        | Sector Timing (16-Bit Mode)                                     |       |

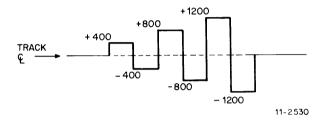

| 3-5        | Positioner Offset Settings                                      |       |

| 3-6        | Dual-Controller Configuration                                   |       |

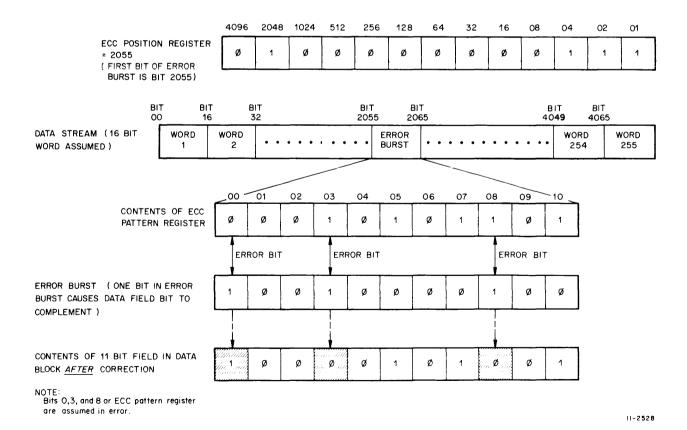

| 3-7        | Example of Error Correction Process                             |       |

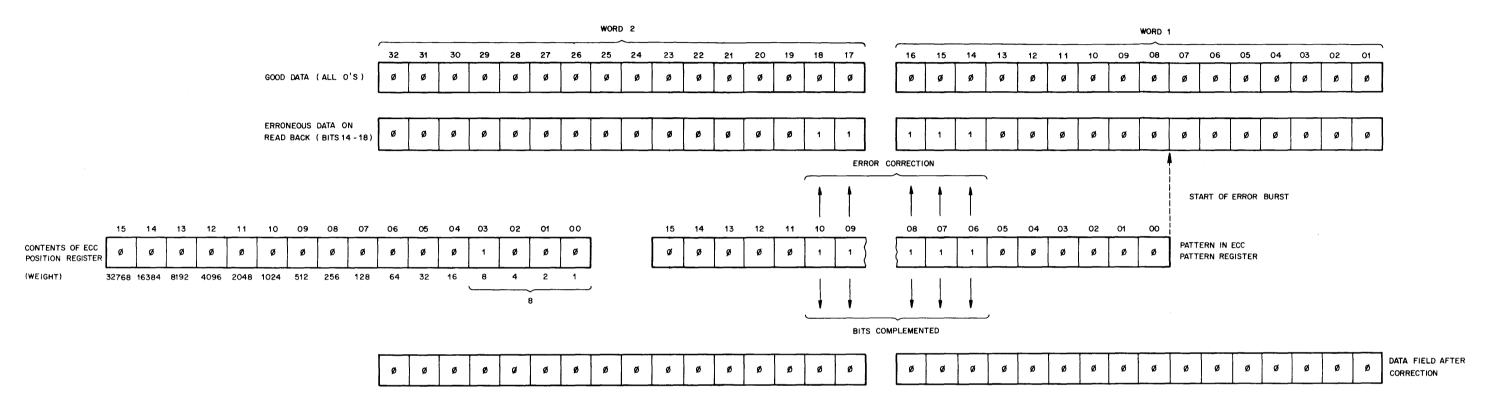

| 3-8        | Example of Five-Bit Error Correction                            |       |

| 3-9        | Example of Six-Bit Error Correction                             |       |

| 3-10       | Uncorrectable Error Flow Chart Example                          |       |

| 4-1        | Control (RPCS1) Register (776700) Bit Usage                     | 4-6   |

| 4-2        | Word Count (RPWC) Register (776702) Bit Usage                   |       |

| 4-3        | Unibus Address (RPBA) Register (776704) Bit Usage               |       |

| 4-4        | Desired Sector/Track Address (RPDA) Register (776706) Bit Usage |       |

| 4-5        | Status (RPCS2) Register (776710) Bit Usage                      |       |

| 4-6        | Drive Status (RPDS) Register (776712) Bit Usage                 |       |

| 4-7        | Error (RPER1) Register 01 (776714) Bit Usage                    |       |

| 4-8        | Attention Summary (RPAS) Register (776716) Bit Usage            |       |

| 4-9        | Look-Ahead (RPLA) Register (776720) Bit Usage                   |       |

| 4-10       | Data Buffer (RPDB) Register (776722) Bit Usage                  |       |

| 4-11       | Maintenance (RPMR) Register (776724) Bit Usage                  |       |

| 4-12       | Drive Type (RPDT) Register (776726) Bit Usage                   |       |

| 4-13       | Serial Number (RPSN) Register (776730) Bit Usage                |       |

| 4-14       | Offset (RPOF) Register (776732) Bit Usage                       |       |

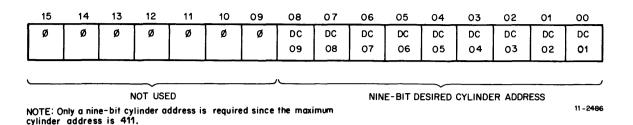

| 4-15       | Desired Cylinder Address (RPDC) Register (776734) Bit Usage     | 4-35  |

# ILLUSTRATIONS (Cont)

| Figure No. | Title                                                       | Page   |

|------------|-------------------------------------------------------------|--------|

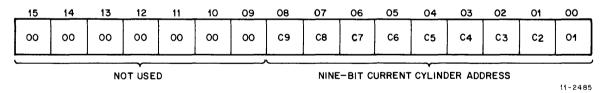

| 4-16       | Current Cylinder Address (RPCC) Register (776736) Bit Usage |        |

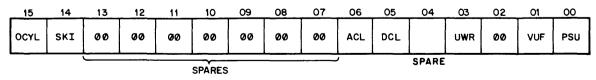

| 4-17       | Error (RPER2) Register 02 (776740) Bit Usage                |        |

| 4-18       | Error (RPER3) Register 03 (776742) Bit Usage                |        |

| 4-19       | ECC Position (RPEC1) Register (776744) Bit Usage            | . 4-41 |

| 4-20       | ECC Pattern (RPEC2) Register (776746) Bit Usage             |        |

| 4-21       | RH11/RP04 Register Summary                                  | . 4-42 |

| 5-1        | Register Control Path                                       | . 5-2  |

| 5-2        | Writing Remote Register Interface                           | . 5-4  |

| 5-3        | Reading Remote Register Interface                           | . 5-5  |

| 5-4        | DMA Data Path Block Diagram                                 |        |

| 5-5        | Write Cycle Interface Diagram                               | . 5-8  |

| 5-6        | Read Cycle Interface Diagram                                | . 5-10 |

| 5-7        | Write Check Cycle Interface Diagram                         | . 5-12 |

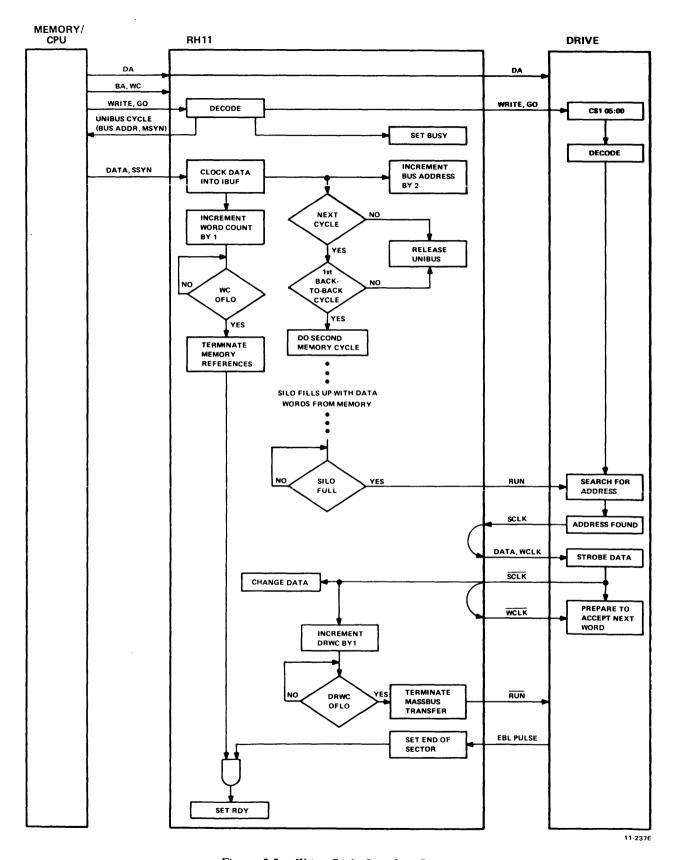

| 5-8        | Write Command Flow Diagram                                  | . 5-13 |

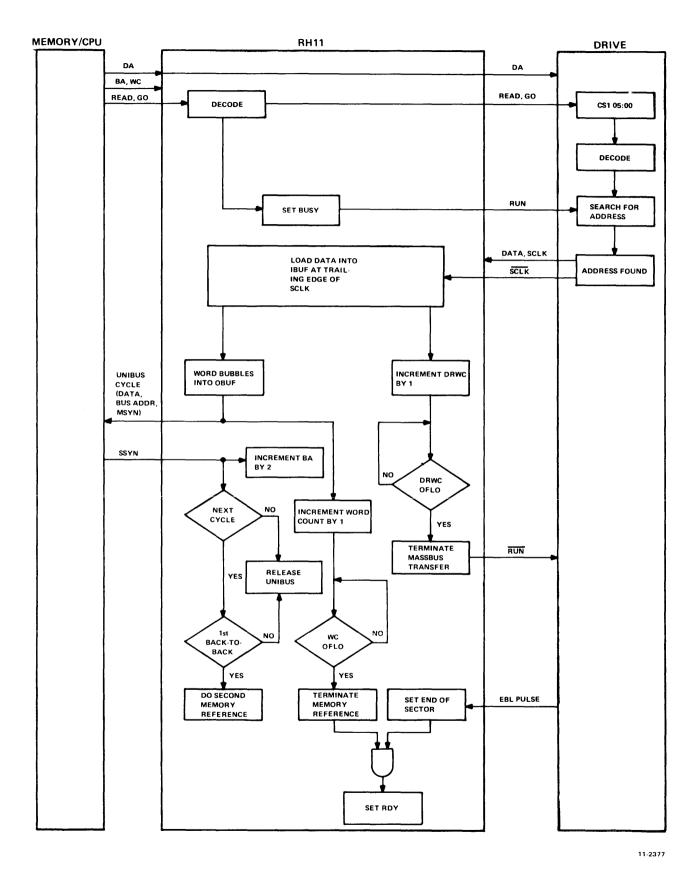

| 5-9        | Read Command Flow Diagram                                   | . 5-16 |

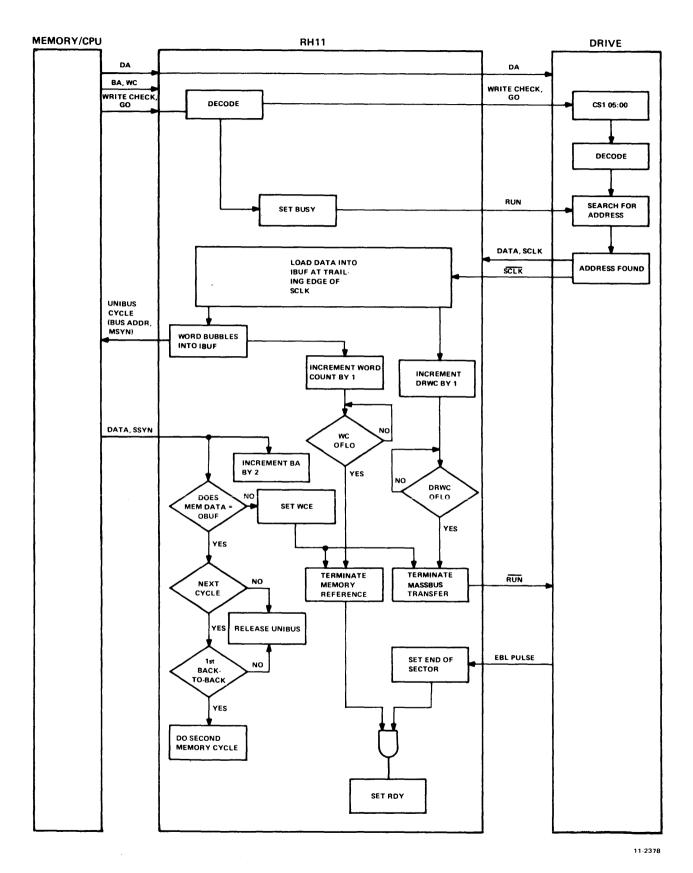

| 5-10       | Write Check Command Flow Diagram                            | . 5-18 |

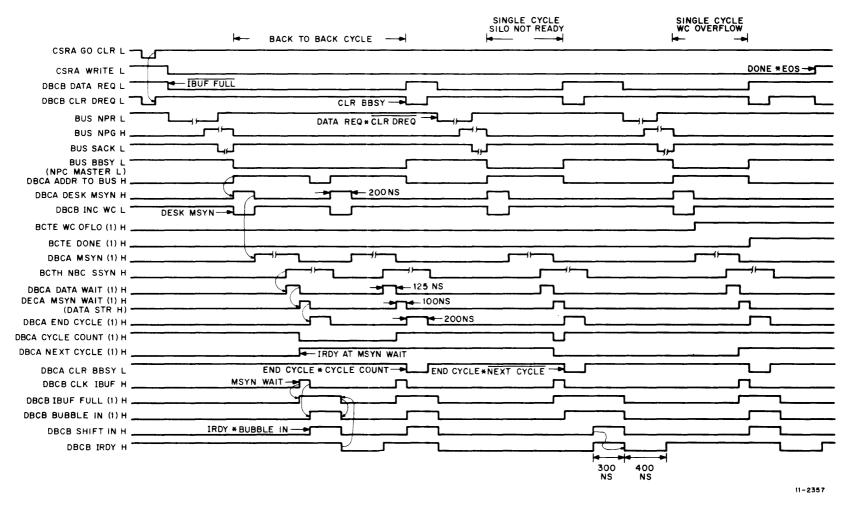

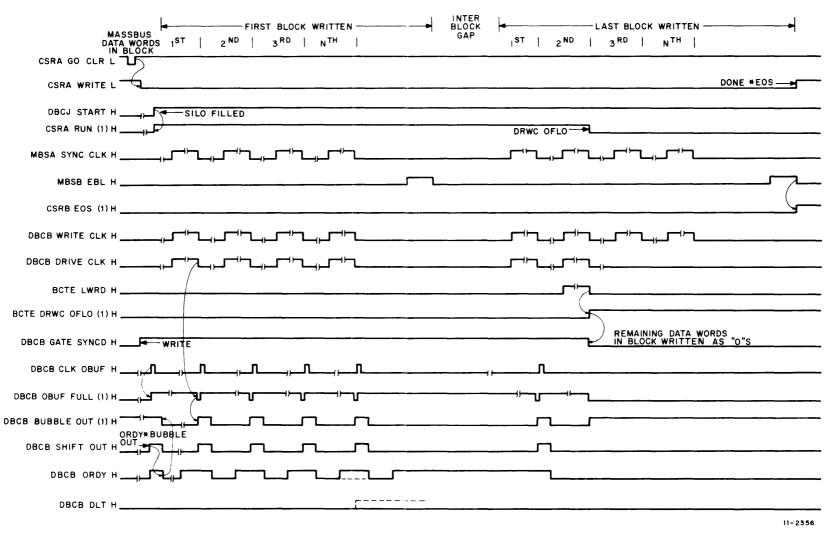

| 6-1        | Write UNIBUS Timing Diagram                                 | . 6-3  |

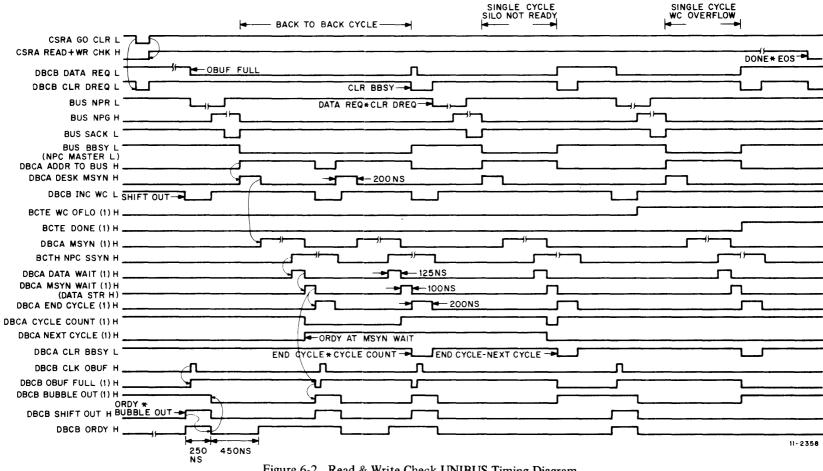

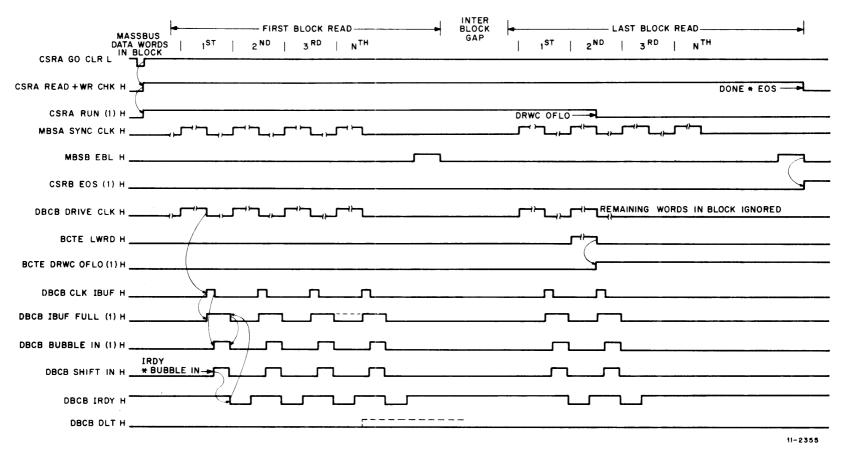

| 6-2        | Read & Write Check UNIBUS Timing Diagram                    | . 6-4  |

| 6-3        | Write MASSBUS Timing Diagram                                | . 6-5  |

| 6-4        | Read & Write Check MASSBUS Timing Diagram                   |        |

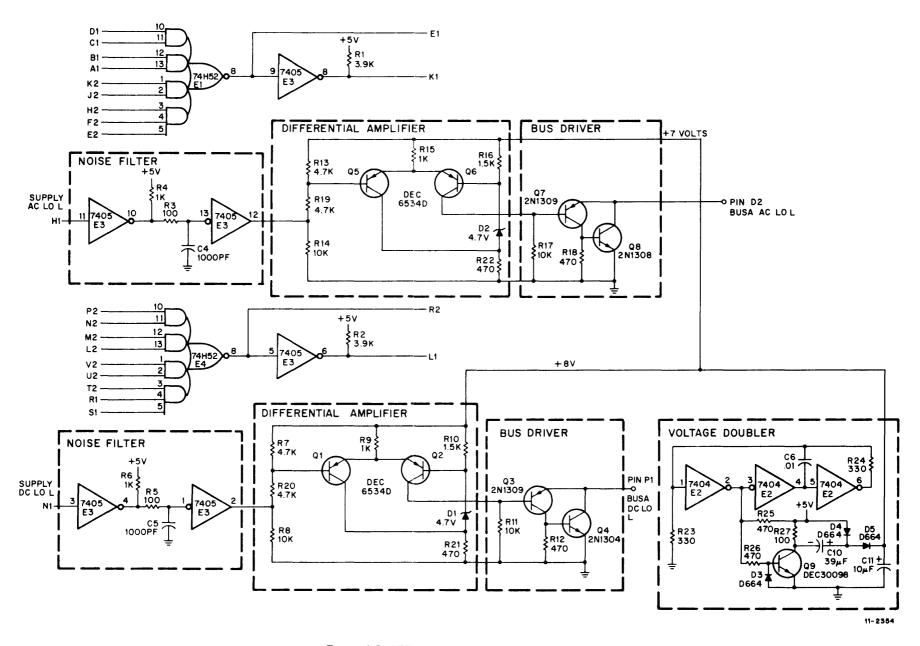

| 6-5        | UNIBUS Power Fail Drivers Schematic                         | . 6-34 |

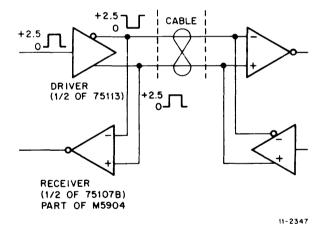

| 6-6        | Typical Differential Driver/Receiver Connection             | . 6-35 |

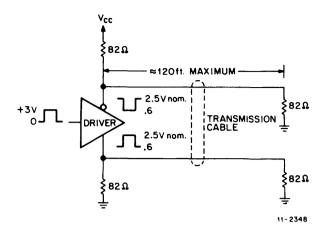

| 6-7        | Driver Termination                                          | . 6-35 |

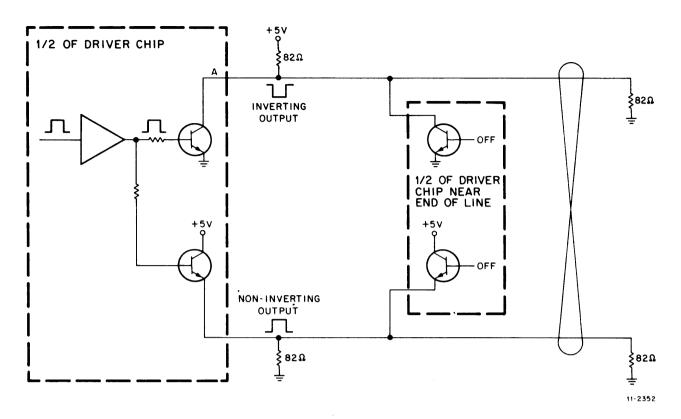

| 6-8        | Driver Chip Simplified Schematic                            | . 6-36 |

| 6-9        | Dual Differential Driver Pin Connection Diagram             | . 6-36 |

| 6-10       | Simplified Line Receiver Logic Diagram                      | . 6-37 |

| 6-11       | 75107B Differential Receiver Pin Connection Diagram         | . 6-37 |

| 6-12       | M8838 UNIBUS Transceiver Pin Connection Diagram             |        |

| 7-1        | RH11 Module Utilization                                     |        |

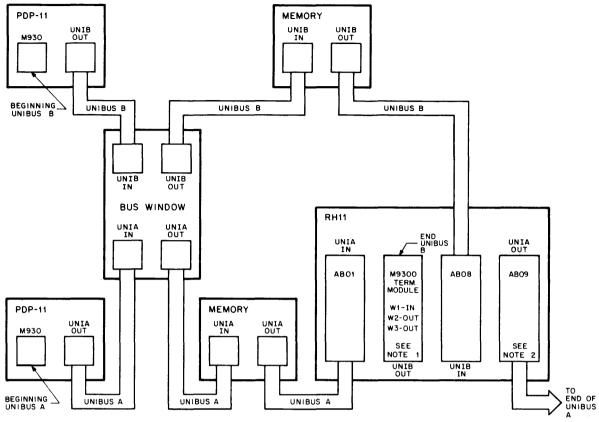

| 7-2        | Single-Port Unibus Configuration                            |        |

| 7-3        | Dual-Port Configuration — Memory on Unibus B                |        |

| 7-4        | Dual-Port Configuration — Memory and Processor on Unibus B  |        |

| 7-5        | Massbus Cable System Configuration                          |        |

| 7-6        | Typical Power Fail Configuration for RH11 and               |        |

|            | Options Mounted in Same Expander Box                        | . 7-6  |

| 7-7        | Typical Power Fail Configuration for Two                    | . •    |

|            | RH11s Mounted in Same Expander Box                          | . 7-7  |

| 7-8        | Typical Power Fail Configuration for RH11 and               |        |

|            | CPU Mounted in Processor Box                                | . 7-8  |

|            |                                                             |        |

## **TABLES**

| Table No. | Title                                                                 | Page   |

|-----------|-----------------------------------------------------------------------|--------|

| 1-1       | Related Documentation                                                 | . 1-1  |

| 2-1       | RH11/RP04 Registers                                                   |        |

| 2-2       | Massbus Signal Cable Designations                                     |        |

| 3-1       | RH11 and RP04 Device Registers                                        |        |

| 3-2       | Offset Positions                                                      | . 3-20 |

| 3-3       | Register Accesses on Dual Controller Operation                        | . 3-25 |

| 3-4       | RP04 Error Bits Classification                                        |        |

| 3-5       | Category F Classification of Errors                                   | . 3-36 |

| 4-1       | Results of Program-Controlled Clearing                                |        |

| 4-2       | Control (RPCS1) Register (776700) Bit Assignments                     | . 4-4  |

| 4-3       | Word Count (RPWC) Register (776702) Bit Assignments                   | . 4-6  |

| 4-4       | Unibus Address (RPBA) Register (776704) Bit Assignments               | . 4-7  |

| 4-5       | Desired Sector/Track Address (RPDA) Register (776706) Bit Assignments | . 4-8  |

| 4-6       | Status (RPCS2) Register (776710) Bit Assignments                      | . 4-9  |

| 4-7       | Drive Status (RPDS) Register (776712) Bit Assignments                 | . 4-12 |

| 4-8       | Error (RPER1) Register 01 (776714) Bit Assignments                    | . 4-18 |

| 4-9       | Attention Summary (RPAS) Register (776716) Bit Assignments            |        |

| 4-10      | Look-Ahead (RPLA) Register (776720) Bit Assignments                   |        |

| 4-11      | Data Buffer (RPDB) Register (776722) Bit Assignments                  |        |

| 4-12      | Maintenance (RPMR) Register (776724) Bit Assignments                  | . 4-26 |

| 4-13      | Drive Type (RPDT) Register (776726) Bit Assignments                   |        |

| 4-14      | Offset (RPOF) Register (776732) Bit Assignments                       | . 4-31 |

| 4-15      | Error (RPER2) Register 02 (776740) Bit Assignments                    | . 4-36 |

| 4-16      | Error (RPER3) Register 03 (776742) Bit Assignments                    | . 4-39 |

| 6-1       | Listing of RH11 Logic Diagrams                                        | . 6-2  |

# CHAPTER 1 SYSTEM AND PHYSICAL DESCRIPTION

#### 1.1 GENERAL

This manual describes the RJP04 Moving Head Disk subsystem manufactured by Digital Equipment Corporation. The RJP04 subsystem consists of an RH11 Device Controller and from one to eight RP04 Disk Drives. The RH11 interfaces with any PDP-11 processor via the Unibus and controls one to eight RP04 Drives.

### 1.1.1 Scope

This manual is designed to provide Digital Field Service and customer maintenance personnel with sufficient installation, operation, and servicing information to install and maintain the RH11. Because the RH11 is used with the RP04 Drives, a description of the RP04 is included in this manual. Detailed information on the RP04 Drive can be found in the RP04 Device Control Logic Maintenance Manual (DEC-00-HRP4M-A-D).

#### 1.1.2 Related Documentation

Table 1-1 lists related documentation that supplements the information in this manual.

Table 1-1

Related Documentation

| Title                                           | Document Number  |

|-------------------------------------------------|------------------|

| PDP-11 Peripherals<br>Handbook                  | 112.00973.2908   |

| RP04 Device Control<br>Logic Maintenance Manual | DEC-00-HRP4M-A-D |

| Digital Logic Handbook                          | 058.00173.2505   |

## 1.2 DISK FILE SYSTEM

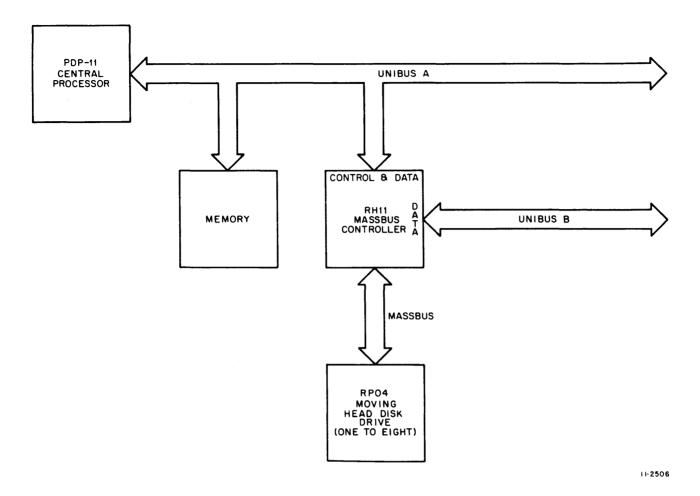

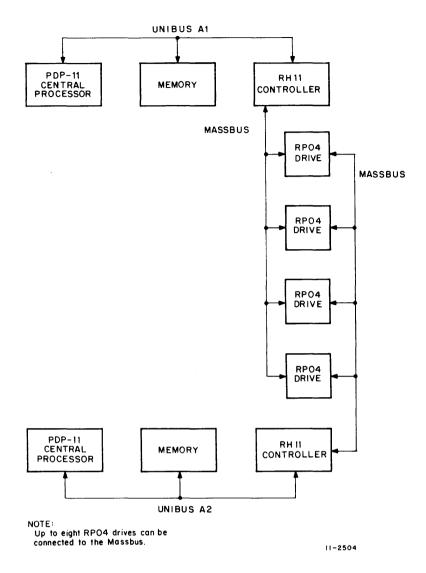

Figure 1-1 shows the major components of a PDP-11 system containing an RH11 Device Controller and one to

eight drives. The processor and memory components can be any of several types in the PDP-11 family since all of these components are equipped with the standard Unibus interface. This manual describes the RH11 Device Controller as it interfaces with the RP04 Drives.

#### 1.2.1 Unibus

The Unibus provides the interface between the processor, memory, and the RH11 Controller. All data transfers between memory and the RH11 are accomplished via the NPR data transfer facilities of the Unibus.

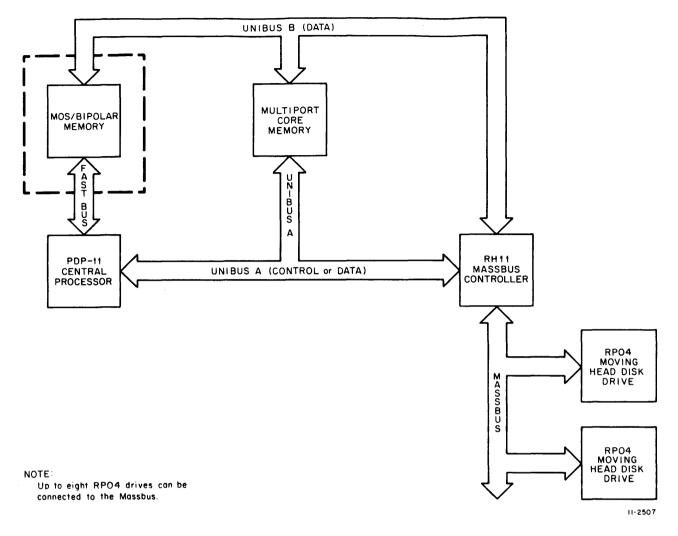

The RH11 contains two Unibus ports: one designated as a control port and the second as a data port. Data may be transferred through either port using the NPR transfer facility. For normal operation, with memory connected to Unibus A as shown in Figure 1-1, the data port is not used, and the control port serves for both control and data transfers. When memory is connected to Unibus B, a programmable port select bit can cause data to be routed through the data port. Figure 1-2 shows a system configuration using multiport memory and both the control port and data port.

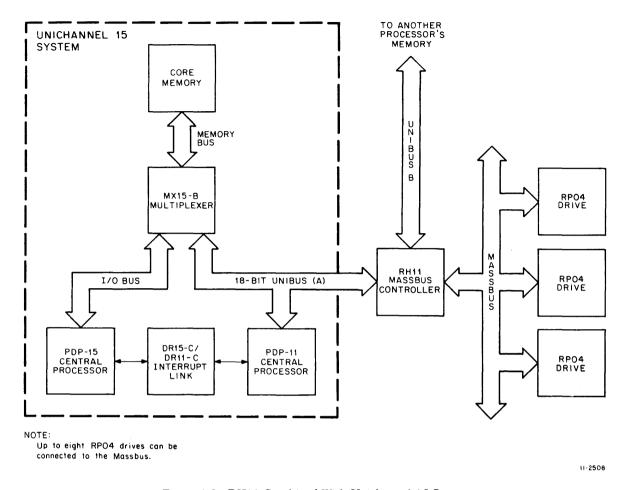

A third configuration which may be employed occurs in a multiprocessor environment. Figure 1-3 shows the RH11 system interfaced to a Unichannel 15 system and a remote processor. In this type of configuration, the PDP-15 can direct the PDP-11 to transfer data from common memory to the disk. The data could then be transferred to another memory bank associated with the remote processor on Unibus B.

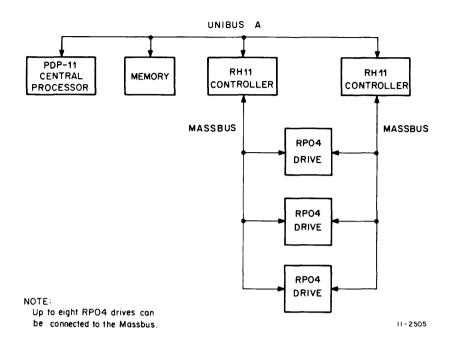

Figure 1-4 shows a dual controller configuration with a single processor; Figure 1-5 shows a dual controller configuration with two processors.

Figure 1-1 RH11 Simplified System Diagram

#### 1.2.2 Massbus

Massbus is the name of the interface between the RH11 Controller and the RP04 Drive. The Massbus provides a parallel data path between the RH11 and the disk devices, and has a total maximum external cable length of 60 ft between drives. Normally, a 25-ft cable connects the RH11 to the first RP04 and 2-ft cables connect one RP04 to the next. The Massbus comprises two sections: an asynchronous control bus and a synchronous data bus for high-speed data transmission.

The purpose of the asynchronous control bus is to:

1. Transmit commands and information from the controller to the drive for the purpose of reading or writing drive registers

- 2. Notify the controller when an Attention condition exists in one or more drives (refer to Chapter 3)

- 3. Transmit status information from the drive to the controller, and

- 4. Provide a master reset to all drives from the controller.

The purpose of the synchronous data bus is to transmit blocks of data at high speed between the controller and drives and to control the initiation and termination of block transmissions.

Figure 1-2 RH11 Multiport System

#### 1.3 RH11 CONTROLLER

The RH11 Controller, in conjunction with the RP04, provides an extremely fast and reliable mass storage system that can be employed in timesharing or real-time data storage applications. The following major functions are performed by the RH11:

- 1. Interfaces with one or two Unibus cables

- 2. Communicates directly with the main memory to fetch and store data

- Communicates with the central processor to receive commands, provides error and status information, and generates interrupts

- 4. Interfaces with one to eight drives.

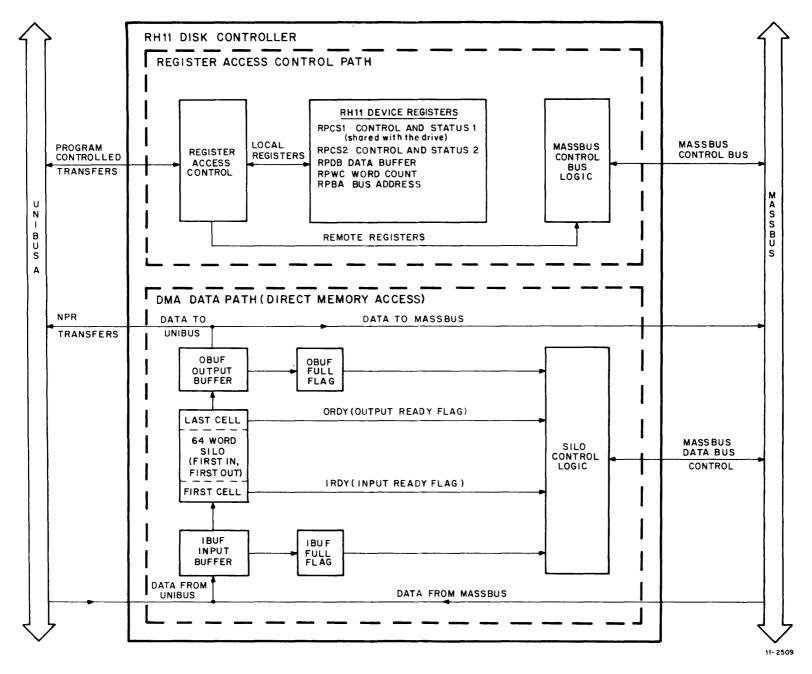

The RH11 is divided into two major functional groups: the register and control path and the DMA (direct memory access) data path (Figure 1-6).

The register and control path allows the program to read from and/or write into any register contained in the RH11 and the selected RP04 Drive. There are a total of 4 registers in the RH11, 15 registers in each drive, and 1 shared register that is partially contained in the RH11 and partially contained in the selected drive.

The DMA data path functionally consists of a 66-word by 18-bit first-in, first-out memory and associated control logic. The major function of this memory (hereafter referred to as the Silo) is to buffer data in order to compensate for fluctuations in NPR latency time on the Unibus.

Figure 1-3 RH11 Combined With Unichannel 15 System

#### 1.3.1 Register and Control Path

When a PDP-11 instruction addresses the RH11 to read or write any device register in the RH11 or in the drive, a Unibus cycle is initiated and this data is routed to or from the RH11 (refer to Chapter 3 for a detailed description of the registers). If the register to be addressed is local (contained within the RH11), the register control logic immediately gates the data to or from the appropriate register. If the register to be accessed is remote (contained in one of the RP04 Drives), the register control logic initiates a Massbus control bus cycle. Accesses to registers in a drive via the control bus do not interfere with DMA data transfers that may be going on at the same time. Local RH11 registers specify parameters such as bus address and word count while the drive registers specify parameters such as desired disk address, status information, etc.

#### 1.3.2 DMA Data Path

The DMA data path functionally consists of the Massbus data bus, a Silo memory, and the Unibus NPR logic. The

Silo memory compensates for fluctuations in NPR latency times by buffering data between the Unibus and Massbus data bus during DMA transfers.

Figure 1-6 shows a simplified block diagram of the DMA data path. A single Unibus configuration is shown with Unibus A serving as both the control port and the data port.

The three data transfer commands that can be performed by the RH11 and RP04 are Write, Read, and Write-Check. Before these data transfers occur, the program specifies a memory address (MA), a cylinder address (CA), a desired sector/track address (DA), and a word count (WC). The memory address represents the starting memory location which the data will be written into or read from. This address occupies the 16 bits of the RPBA register and bits 9 and 8 of the RPCS1 register (Chapter 3). The state of the PSEL bit in the RPCS1 register determines over which Unibus the transfer will take place.

Figure 1-4 Dual Controller Option (With One Processor)

The desired cylinder address is the cylinder address where the head is to be positioned. This address occupies bits 09 through 00 in the RPDC register. The desired sector/track address is the disk sector and track address and represents the starting location on the disk surface where the data is to be written or read from. This address is located in the RPDA register.

The word count is a count of the number of words to be transferred to or from the disk. The negative (2's complement) of this number is loaded in the Word Count (RPWC) register and is incremented toward 0 for each data word transferred into or from memory. At the normal completion of a transfer, the appropriate number of words have been transferred, and the RPWC register contains 0.

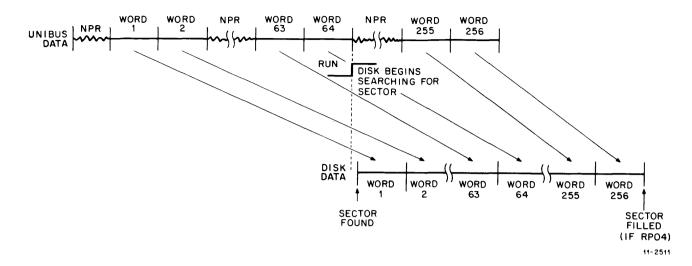

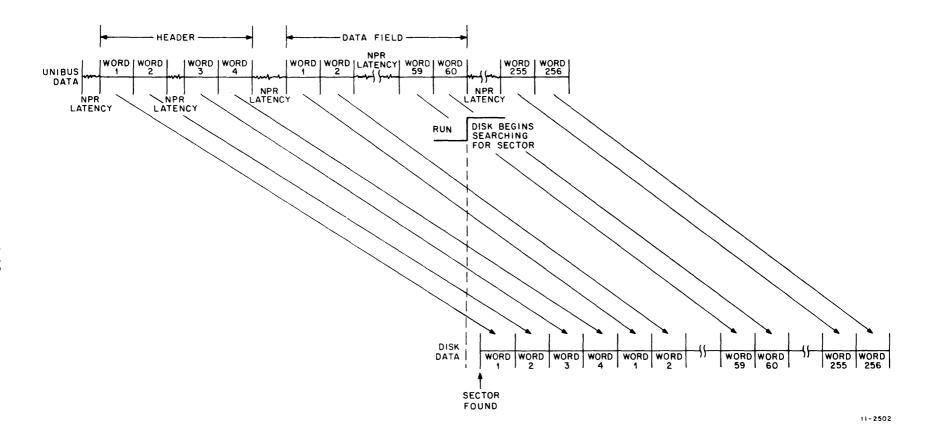

1.3.2.1 Write Operation — In a write operation, the data words are transferred from memory to the disk via the RH11. The data path functionally consists of the Unibus NPR logic, the Silo memory, and the Massbus data bus. The program initially selects a drive and loads the bus address, word count, and desired addresses (sector, track, and cylinder). The program then loads a Write command code (with the GO bit set) into the RPCS1 Control and Status register. Unibus NPR cycles are initiated by the RH11, and

the data words from memory are transferred to the input buffer (IBUF) of the Silo.

For each data word transferred, the word count is incremented by 1 and the bus address is incremented by 2. The data words are clocked into and "bubble" through the Silo. When the first data word reaches the top, it is automatically clocked into the Silo output buffer (OBUF). When the Silo is filled and a word is in OBUF, the RH11 asserts the RUN signal, which signals the drive to begin writing data on the disk.

After the RUN signal is asserted, the disk begins searching for the rotational position corresponding to the value in the Desired Address (RPDA) register. When this rotational position is found, the disk begins sending SCLK (sync clock) pulses to the RH11 and starts receiving data words from the RH11 via the Massbus data bus.

At the end of a transfer of each sector, the disk asserts the EBL (end of block) pulse and looks at the RUN signal. If the RUN signal is still asserted, the disk continues to receive the next sector of data and writes it on the disk surface. If the RUN signal is negated at the end of the EBL pulse, the drive disconnects from the Massbus data bus.

Figure 1-5 Dual Controller Option (With Dual Processor)

When less than a sector is transferred, the remainder of the sector will be written with 0s. The reason for this is that the RH11 negates the RUN signal at word count overflow; however, the disk does not respond to the negation of RUN until the end of EBL time, and therefore, the RH11 sends 0s on the Massbus data bus when word count overflow occurs.

Note that during a write operation, the Silo is filled or word count overflow occurs before the RH11 signals the drive to begin writing.

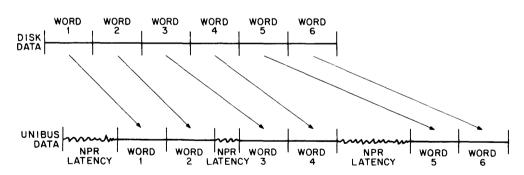

1.3.2.2 Read Operation — In a read operation, data words are transferred from the RP04 Drive to memory via the RH11 Controller. The data path functionally consists of the Massbus data bus, the Silo memory, and the Unibus NPR

logic. The program initially selects a drive and loads the bus address, word count, and desired sector, track, and cylinder addresses. The program then loads a Read command code (with the GO bit set) into the RPCS1 Control and Status register (Chapter 3). The RH11 immediately asserts the RUN line. The RPO4 Drive begins searching for the rotational position corresponding to the value in the Desired Address (RPDA) register. When the position is found, the disk begins sendig SCLK pulses to the RH11, along with the data words. The data is clocked into IBUF and is then gated into the Silo.

When the first data word has "bubbled" to the top of the Silo and has been clocked into OBUF, Unibus NPR cycles are initiated. Each time a word is transferred to the Unibus, the word count stored in the Word Count (RPWC) register is incremented by 1 and the bus address is incremented by 2.

Figure 1-6 RH11 Simplified Data Path Diagram

#### NOTE

The RH11 may perform either single-cycle or back-to-back memory references per NPR request.

At the end of each sector, the drive asserts the EBL pulse and looks at the RUN signal. If the RUN signal is still asserted, the disk continues sending the next sector of data to the RH11 via the Massbus data bus. If the RUN signal is negated at the end of the EBL pulse, the disk disconnects from the Massbus data bus and the transfer is terminated.

If the value initially stored in the RPWC register is less than the number of words in a full sector, the remaining words in the sector will be disregarded by the RH11. After word count overflow occurs, the RH11 stops performing Unibus data transfers and waits for the next EBL pulse. When EBL is received from the disk, the RH11 transitions to the ready state.

1.3.2.3 Write-Check Data Transfer — The third type of transfer is a Write-Check and is initiated when a Write-Check function is specified in RPCS1 and the GO bit in this register is set. In this operation, a block of data which has previously been written onto the disk is read from the disk. The data is compared to the data in memory originally used to write on the disk. The comparison is accomplished by Exclusive OR gates, and if any of the bits

fail to compare, a Write-Check Error occurs. This method allows automatic verification that the data on the disk surface agrees with the contents of memory.

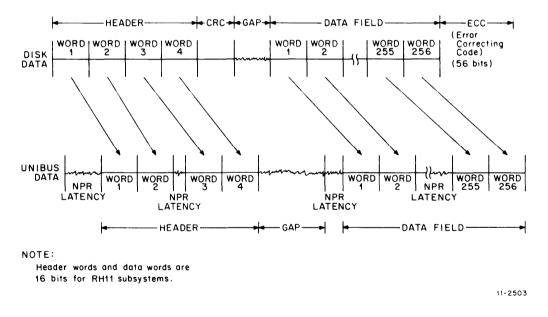

1.3.2.4 Data Transfer Rates — The data transfer rate from the drive is determined by a clock in the drive. The RP04 has an 18-bit format and a 16-bit format. The basic data transfer rate for the 18-bit format is a burst rate of 2.79  $\mu$ s per word. The basic data rate for the 16-bit format is a burst rate of 2.48 µs per word. The Unibus data transfer rate depends on NPR latency time and memory cycle time. Figure 1-7 shows the data transfer sequence for a read operation, and Figure 1-8 shows the sequence for a write operation. Figure 1-9 shows the data transfer sequence for a read header and data command and Figure 1-10 shows the data transfer sequence for a write header and data command. For lengthy data transfers, the average Unibus data transfer rate is equal to the average disk data transfer rate. Statistical fluctuations in NPR latency times are absorbed by the buffering in the Silo.

#### **NOTE**

By inserting a single-cycle jumper in the RH11, it is possible to perform one memory cycle for each NPR. If the jumper is left out, the RH11 will perform back-to-back memory cycles before releasing the Unibus, unless only one word remains to be transferred.

NOTE:

Average data transfer rate is 2.96 µsec for the 16-bit format (3.25 µsec for the 18-bit format). This rate includes data and header.

11-2510

Figure 1-7 Read Command Data Transfer

Figure 1-8 Write Data Transfer Sequence

Figure 1-9 Read Header and Data Command Transfer

#### 1.4 RP04 DRIVE

The RP04 Drive is a large capacity, high performance, direct access disk file which will accommodate one removable disk pack of the IBM 3336 type. The disk pack contains 10 magnetic disks, each 14 inches in diameter. The middle surface is prerecorded with positioning signal information for servo tracking and is a read-only surface. This leaves 19 surfaces available for recording. The 19 surfaces can store approximately 44 million 16-bit words or approximately 40 million 18-bit words. Total subsystem

capacity using eight RP04 disk files is  $352 \times 10^6$  16-bit words. The 16-bit format contains 22 sectors per track while the 18-bit format contains 20 sectors per track.

There is one head per surface which enables the RP04 to store or retrieve information at any location on a rotating disk pack. Information is recorded on the lower and upper surface of each disk (except for the servo surface at the middle of the disk pack).

Figure 1-10 Write Header and Data Command Transfer (Pack Format Command)

With the dual controller option, the drive can be connected to two RH11 controllers, allowing access to the drive from two separate computer systems or from one computer system via two separate paths.

The RP04 drive performs the following functions.

- 1. Records and plays back data in two format modes

- 2. Calculates error correction information

- 3. Generates gaps and synchronization marks on the recording medium

- 4. Provides clock signals to synchronize data transmission between drive and controller

- Maintains error and status indicators and generates an Attention signal when exceptional conditions occur

- 6. Locates data by address

- 7. Performs dual controller arbitration

- 8. Provides mechanisms for maintenance and diagnostic testing.

#### 1.5 RJP04 SYSTEM SPECIFICATIONS

This paragraph defines the parameters of the RH11 Massbus Controller and the RP04 Drive.

#### 1.5.1 Unibus NPR Latency

NPR latency time is from the assertion of a Unibus NPR by the RH11 until the RH11 takes control of the Unibus (asserts BBSY). The acceptable average NPR latency time is calculated as follows:

Average data word time of the disk minus time to transfer one word to or from memory plus the time for the RH11 to issue the next NPR.

If the jumper in the RH11 is cut for two memory cycles per NPR, average acceptable NPR latency time is doubled, and is calculated as follows:

Twice the average data word time of the disk minus time to transfer two words to or from memory plus the time for the RH11 to issue the next NPR. For example, if the average data word time of the disk is  $2.48 \,\mu s$  (16-bit format) and the time to transfer two words to or from memory is  $2 \,\mu s$  plus  $0.2 \,\mu s$  to

request the Unibus again, then the average acceptable NPR latency =  $(2 \times 2.48) \mu s - (2 + 0.2) \mu s = 2.94 \mu s$ .

If the actual NPR latency consistently exceeds the acceptable average NPR latency during a lengthy read or write operation, the 66 words of data buffering in the RH11 (Silo plus IBUF and OBUF) will eventually be insufficient. This condition is signaled by a Data Late Error (DLT) condition.

#### 1.5.2 Data Format

Data words are recorded on the disk in 16-bit format. Normally, for the RJP04 system, only 16 bits per word are transmitted between the controller and memory. To accomplish an 18-bit transfer via the Unibus, the Bus PA and Bus PB lines may be used as data bits BUS D16 and BUS D17, respectively. Both Unibus A and Unibus B are jumper selectable in the RH11 for this 18-bit mode. When a Unibus is not selected for 18-bit mode, the RH11, when reading, sends logical 0s on the Unibus PA and Unibus PB lines, and, when writing, sends 0s to the disk in bits 16 and 17 of the Massbus data bus.

In addition, the RH11 checks parity error conditions on the Unibus in the normal 16-bit mode when performing a write operation. A PDP-11 memory parity error is indicated when Unibus PA is negated and Unibus PB is asserted during an NPR data transfer from memory.

#### 1.5.3 Error Correcting Code (ECC)

The RP04 contains Error Correcting Code logic which will generate, detect, and correct an error by reconstructing a portion of the data (limited by the capability of the selected code). The ECC employed in the RP04 is called a Burst Error Correcting Code.

Within the fixed specified code word length, the Burst Error Correcting Code will correct an error which must fall within the specified length of the burst (11-bit burst). The actual location of that burst within the data field is immaterial to the operation of the ECC logic. Any errors outside the specified burst length will be detected but not corrected.

The RP04 logic will find the burst within which the read error is included and determine the actual location of the burst within the data field. The ECC Pattern register contains the actual error burst and the ECC Position register contains the address for determining the actual location of the error burst within the data field. Both registers are located in the RP04. The actual correction of the data field will be done by the processor under software control.

During a read, write, or write-check operation, both data errors and unusual drive conditions signal the RH11 via the Exception (EXC) line, which sets the TRE (Transfer Error) bit after the read/write operation is complete. During non-data transfer operations, the drive can signal unusual conditions or completion of non-data transfer operations by the Attention (ATTN) line. This line is shared by all drives connected to the RH11.

During a read, write, or write-check operation, errors in the RH11 (such as DLT, Unibus parity error, etc.) also set the TRE bit and cause the operation to be aborted.

Interrupts are generated as a result of the ATTN line being asserted or by completion of a read or write data transfer.

# 1.5.4 RH11 Massbus Controller Specifications Mechanical

Consists of a double hex-height system unit, which will mount in a BA11-FA, BA11-FB, BA11-BA, or BA11-BB mounting box (not supplied). Module usage is as follows:

RH11 Logic

2 hex-height, 2 double-height modules

Massbus Controller Transceivers

3 double-height modules

Unibus Cable Slots

4 double-height cable slots

Power Fail

2 single-height modules

#### **Electrical**

Power Requirements (RH11)

$+5.0 \pm 0.25$  Vdc at 16.0 A max

$-15.0 \pm 1.5$  Vdc at 0.58 A max

Logic Voltage

$H \approx +3 \text{ V}, L \approx 0 \text{ V}$

#### Environmental

Temperature

$32^{\circ} - 122^{\circ} \text{ F } (0^{\circ} - 50^{\circ} \text{ C}) \text{ Class C}$

Relative Humidity

8% to 90%, no condensation

Vibration Shock

1.89 g rms, 10-300 Hz

20 g, half sine, 30 ms duration, any plane

#### Data Transfers Memory/Controller

Accomplished via the NPR facility of the Unibus. Data can be transferred on either of two Unibuses (program selected). An 18-bit data path is optional (uses Unibus PA and Unibus PB lines as data).

#### Data Transfer Controller/Disk

All controller/disk transfers are accomplished as 18-bit parallel words over the synchronous section of the Massbus.

#### Data Rates

RP04 (16-Bit Format)

2.48 µs/word (burst rate)

$2.96 \mu s/word$  (average rate for multiple sector transfers)

RP04 (18-Bit Format)

2.79 µs/word (burst rate)

$3.25 \mu s/word$  (average rate for multiple sector transfers)

### **Number of Drives Per Controller**

Can handle up to eight RP04 Drives

#### Maximum Controller/Drive Cable Length

40-foot individual round Massbus cable (external) 60-foot total round Massbus cable (external)

#### 1.5.5 RP04 Drive Specifications

The RP04 Drive is a high performance, direct access, single head per surface drive which enables a data processing system to store or retrieve information at any location on a rotating disk pack. The RP04 is connected to the RH11 Controller via the Massbus interface.

#### **Features**

Error detection and correction capability hardware which is permanently installed

Two sector formats available:

20 sectors per data track (256 18-bit words per data field of each sector)

22 sectors per data track (256 16-bit words per data field of each sector)

Remote stand-by operation

#### **Options**

Dual controller capability

#### **Mechanical Specifications**

**Mounting**

Mounted in a free-standing cabinet, approximately 40 inches high, 31 inches wide, and 32 inches deep. The width includes a 10-inch chassis attached to the side of the basic cabinet.

Weight

600 lb

**Electrical Specifications**

Power Requirements

dc - None

ac -208/230 Vac  $\pm 10\%$ , 3-phase, 60 Hz  $\pm 1\%$ , or 380 Vac  $\pm 10\%$ , star with neutral, 50 Hz  $\pm 1\%$ , 3-phase - options include 240/408/220/420 Vac.

Starting current surge - less than 30 A

**Environmental Specifications**

Operating Temperature Range 60° F min, 90° F max

Non-operating Temperature Range 50° F min, 110° F max

Drive Cooling (Internal)

Forced Air

Maximum Wet Bulb Temperature 78° F

Heat Dissipation

7000 Btu/hour nominal 5500 Btu/hour nominal

Relative Humidity

20% min, 80% max (no condensation)

Vibration

0.25 g from 50 to 500 Hz

Shock

Operating: 3 g for 10 ms, 3 pulses in vertical direction only

Shipping: 6 g for 30 ms, 3 pulses in vertical direction only

**Maintainability**

The basic maintainability philosophy for the RP04 Drive is to provide on-line diagnostic capability. In addition to software diagnostics, an off-line hardware exerciser will also be provided.

Read/Write

Number of Read/Write Heads

19 (plus 1 read head for the servo)

Cylinders Per Disk Pack

411

Tracks Per Cylinder

19

Total Number of Tracks 7809 per disk pack

Data Bits Per Track, Maximum 107,520 (unformatted)

Data Bits Per Cylinder, Maximum 2,042,880 (unformatted)

Data Bits Per Disk Pack, Maximum 840,000,000 (unformatted)

Data Rate (Nominal) 6,448,000 bits/second

Data Words Per Disk Pack (Formatted Capacity) 43,980,288 (22-sector pack, 16-bit words) 39,982,080 (20-sector pack, 18-bit words)

**Data Compatibility**

The RP04 Drive allows for disk pack interchangeability between PDP-10/PDP-11/PDP-15 systems through software-controlled format and data word width settings.

**Access Times**

One Cylinder Seek

7 ms

Average Seek 27 ms

Maximum Seek 50 ms

Average Rotational Latency Time 8.33 ms

## Operation

Start-up Time (Brush Cycle and Head Load)

15 seconds

Disk Rotational Speed 3600 rpm, ±2.5% (counterclockwise)

Stop Time (Retract Heads and Stop Disk Rotation) 15 seconds

Disk Drive Motor

1 hp induction, 208/230 Vac, 3-phase

Bit-Cell Time 155 ns Disk Pack

Type

RP04P Pack (IBM 3336 Type)

Disk Diameter 14 inches

Number of Disks

10 magnetic disks (not including upper and lower protective disks)

Magnetic Recording Surfaces

19 (uppermost surface is numbered zero)

# CHAPTER 2 MASSBUS INTERFACE

#### 2.1 GENERAL

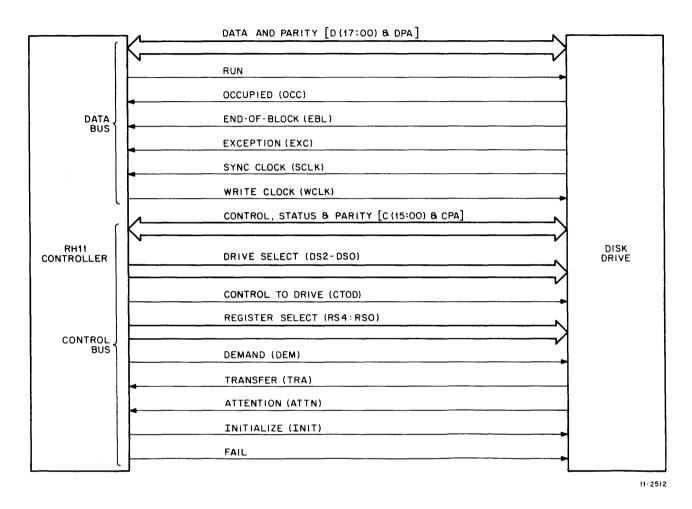

The Massbus provides the interface between the RH11 Controller and the RP04 Drives. The total external Massbus cable can be up to 60 ft in length, and up to eight drives may be connected in a daisy-chain configuration. The Massbus consists of two sections: a data bus section and a control bus section. These buses are described in the following paragraphs.

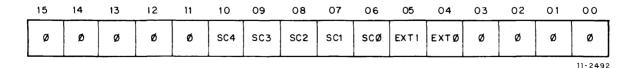

#### 2.2 DATA BUS

The data bus section of the Massbus consists of a 19-bit (18 data bits plus parity bit) parallel data path and 6 control lines (Figure 2-1). The control lines are described in the following paragraphs.

Parallel Data Path – The parallel data path consists of an 18-bit data path designated D00 through D17 and an associated parity bit (DPA). The data path is bidirectional and employs odd parity. Data is transmitted synchronously, using a clock generated in the drive.

RUN – After a data transfer command has been written into the Control register of a drive, the drive connects to the data bus. The controller asserts the RUN line to initiate the function. At the end of each sector, on the trailing edge of the EBL (end of block) pulse, RUN is strobed by the drive. If it is still asserted, the function continues for the next sector; if it is negated, the function is terminated.

Occupied (OCC) – This signal is generated by the drive to indicate "data bus busy." As soon as a valid data transfer command is written into a drive, the drive asserts OCC. Various errors may prevent a drive from executing a command. The controller will time out in these cases due to no assertion of OCC or of SCLK, and the MXF (Missed Transfer) error will be set in the controller. OCC is negated at the trailing edge of the last EBL pulse of a transfer.

End of block (EBL) – This signal is asserted by the drive for  $2 \mu s$  at the end of each sector (after the last SCLK

pulse). For certain error conditions, where it is necessary to terminate operations immediately, EBL is asserted prior to the normal time for the last SCLK. In this case, the data transfer is terminated prior to the end of the sector.

Exception (EXC) – This signal is asserted by the drive when an abnormal condition occurs in the drive during a data transfer. The drive asserts this signal to indicate an error during a data transfer command (Read, Write, or Write-Check). EXC is asserted at or prior to assertion of EBL and is negated at the negation of EBL.

Sync Clock (SCLK), Write Clock (WCLK) — These signals are the timing signals used to control the strobing of the data in the controller and/or in the drive. During a read operation, the RH11 strobes the data lines on the negation of SCLK and the drive changes the data on the assertion of SCLK. During a write operation, the controller receives SCLK and echoes it back to the drive as WCLK. On the assertion of WCLK, the drive strobes the data lines; on the negation of WCLK, the controller changes the data on the data lines.

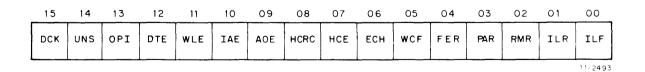

#### 2.3 CONTROL BUS

The control bus section of the Massbus consists of a 17-bit (16 bits plus parity) parallel control and status data path, and 14 control lines (Figure 2-1), which are described below.

Parallel Control – The parallel control path consists of a 16-bit parallel data path designated C00 through C15 and an associated parity bit (CPA). The control lines are bidirectional and employ odd parity.

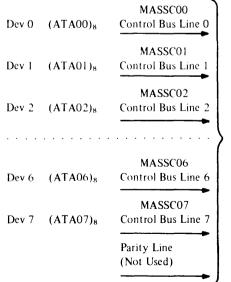

Drive Select [DS (2:0)] — These three lines transmit a 3-bit binary code from the controller to select a particular drive. The drive responds when the select (unit) number in the drive corresponds to the transmitted binary code.

Figure 2-1 Massbus Interface Lines

Controller-to-Drive (CTOD) – This signal is generated by the controller and indicates the direction in which control and status information is to be transferred. For a controller-to-drive transfer, the controller asserts CTOD. For a drive-to-controller transfer, the controller negates this signal.

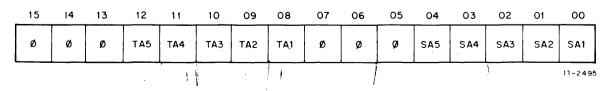

Register Select [RS (4:0)] – These five lines transmit a 5-bit binary code from the controller to the selected drive. The binary code selects one of the drive registers.

## NOTE

Sixteen registers are contained in the RP04 and are designated by RP codes 00 through 17<sub>8</sub>. Four registers are contained in the RH11. Table 2-1 lists the registers and their locations. If a register code higher than 17<sub>8</sub> is detected by the RP04 hardware, an Illegal Register (ILR) error occurs in the drive.

Table 2-1 RH11/RP04 Registers

| Massbus<br>Address<br>(Octal)                                                          | Register                                                                                                                                                                                                                                                                                | Mnemonic                                                                                                                           | Type                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                        | Drive Registers                                                                                                                                                                                                                                                                         |                                                                                                                                    |                                                                                                                                                                                                       |

| 00<br>01<br>02<br>03<br>04<br>05<br>06<br>07<br>10<br>11<br>12<br>13<br>14<br>15<br>16 | Control (shared) Drive Status Error Register 1 Maintenance Attention Summary Desired Sector/Track Address Drive Type Look-Ahead Error Register 2 Offset Desired Cylinder Address Current Cylinder Address Serial Number Error Register 3 ECC Position ECC Pattern  Controller Registers | RPCS1<br>RPDS<br>RPER1<br>RPMR<br>RPAS<br>RPDA<br>RPDT<br>RPLA<br>RPER2<br>RPOF<br>RPDC<br>RPCC<br>RPSN<br>RPER3<br>RPEC1<br>RPEC2 | Read/write<br>Read only<br>Read/write<br>Read/write<br>Read/write<br>Read only<br>Read only<br>Read/write<br>Read/write<br>Read only<br>Read only<br>Read only<br>Read only<br>Read only<br>Read only |

|                                                                                        | Word Count<br>Bus Address<br>Status<br>Data Buffer                                                                                                                                                                                                                                      | RPWC<br>RPBA<br>RPCS2<br>RPDB                                                                                                      | Read/write<br>Read/write<br>Read/write<br>Read/write                                                                                                                                                  |

Demand (DEM) — This signal is asserted by the controller to indicate a transfer is to take place on the control bus. For a controller-to-drive transfer, DEM is asserted by the

controller when data is present and settled on the control bus. For a drive-to-controller transfer, DEM is asserted by the controller to request data and is negated when the data has been strobed off the control bus. In both cases, the RS, DS, and CTOD lines are generated and allowed to settle before assertion of DEM.

Transfer (TRA) – This signal is asserted by the selected drive in response to DEM. For a controller-to-drive transfer, TRA is asserted after the data has been strobed and is negated after DEM is negated. For a drive-to-controller transfer, TRA is asserted after the data has been gated onto the bus and negated after the negation of DEM is received.

Attention (ATTN) — This line is shared by all eight drives attached to a controller; it may be asserted by any drive as a result of an abnormal condition or status change in the drive. An ATA status bit in each drive is set whenever that drive is asserting the ATTN line. ATTN may be asserted due to any of the following conditions:

- 1. An error while no data transfer is taking place (asserted immediately).

- 2. Completion of a data transfer command if an error occurred during the data transfer (asserted at the end of the data transfer).

- 3. Completion of a mechanical motion command (Seek, Calibrate, etc.) or of a search command.

- 4. As a result of the medium-on-line (MOL) bit changing states (except in the unload operation). In the dual controller configuration, a change in state of MOL will cause the assertion of ATTN to both controllers.

The ATA bit in a drive may be cleared by the following actions:

- 1. Asserting INIT on the Massbus (affects all eight drives).

- 2. Executing a reset instruction.

- 3. Causing Unibus A INIT by a console operation.

- 4. Writing a 1 into the CLR bit (controller clear).

- 5. Writing a 1 into the Attention Summary register (in the bit position for this drive). This clears the ATA bit; however, it does not clear the error.

6. Writing a valid command (with the GO bit asserted) into the RPCS1 register if no error occurs. Note that clearing the ATA bit of one drive does not always cause the ATTN line to be negated, because other drives may also be asserting the line.

#### NOTE

There are three cases in which ATA is not reset when a command is written into the Control register (with the GO bit set). These are: (1) if there is a Control Bus Parity error on the write, (2) if an error was previously set, or (3) if an illegal function (ILF) code is written.

Initialize (INIT) — This signal is asserted by the controller to perform a system reset of all the drives. It is asserted when a 1 is written into the CLR bit (bit 05 of RPCS2) and when Unibus INIT is asserted on Unibus A. When a drive receives the INIT pulse, it immediately aborts the execution of any current command and performs all actions described for the Drive Clear command.

#### NOTE

In the dual controller configuration, a drive will honor an INIT pulse only from the controller which has seized the drive, or from either controller if the drive is in the unseized state. In addition, the ATA and VV bits, which exist independently on each port of the RP04, can be cleared only from their respective controller.

FAIL – When asserted, this signal indicates a power-fail condition has occurred in the controller. While FAIL is asserted, the drive inhibits reception of the INIT and DEM signals at the drive.

#### 2.4 COMMAND INITIATION

To initiate a command in a drive via the Massbus, the controller (or the central processor via the controller) writes a word into the RPCS1 register. The function code and GO bit are transferred to the selected drive. If the command specified is valid and the GO bit is asserted, the selected drive executes the command.

Commands are of two types: non-data transfer commands (such as Drive Clear, Seek, etc.) and data transfer commands (such as Read, Write, and Write-Check). The command function code bits (05 through 00 including GO in RPCS1) are 01<sub>8</sub> through 47<sub>8</sub> for non-data transfer commands and are 51<sub>8</sub> through 77<sub>8</sub> for data transfer commands (not all are valid functions).

#### 2.4.1 Non-Data Transfer Commands

Non-data transfer commands affect only the state of the drive. The controller merely writes the command word (with GO bit set) into the drive's Control register. At the completion of the command execution, the drive typically asserts the ATTN line to signal its completion.

If the non-data transfer command code written into the drive is not recognized by the drive as a valid command, the drive will immediately signal an error by asserting the ATTN line. The Illegal Function (ILF) error is set.

#### 2.4.2 Data Transfer Commands

When any data transfer command code (with the GO bit set) is written into the drive's Control register, the controller expects data transfer on the data bus to begin soon thereafter. The controller resets its RDY (Controller Ready) bit as soon as the data transfer command code is written into a drive. The drive normally responds by asserting the OCC line. The controller asserts RUN and then data is transferred to or from the specified drive, after the proper address (sector, track, cylinder) is found.

If a Class B error occurs in a drive during a data transfer command, the drive asserts the EXC line. This line remains asserted until the trailing edge of the last EBL pulse. The RH11 Controller always negates the RUN line when it detects EXC asserted, so that the data transfer is terminated at the end of the sector in which the error was signaled.

#### 2.5 READING AND WRITING DRIVE REGISTERS

The process of reading or writing drive registers is accomplished via the asynchronous (control bus) portion of the Massbus (Figure 2-1). The RH11 initiates the action by selecting a drive (DS2-DS0), selecting a register (RS4-RS0) in that drive, selecting a direction of transfer (CTOD), and either reading or writing the register via the 17 bidirectional control lines [C(15:00) and CPA]. After a deskew delay to allow the control lines to stabilize, the RH11 asserts DEM. The drive, upon receiving the DEM assertion, checks the CTOD line to ascertain whether a read or write is to occur.

If a register read operation is specified, the drive will gate the contents of the specified register onto the control bus and will issue TRA. When the RH11 receives TRA, it will gate the control lines onto the Unibus. After a deskew delay, the RH11 asserts SSYN to the processor. When the processor receives the control data and SSYN, it clears MSYN. The clearing of MSYN negates SSYN and DEM. The negation of DEM causes TRA to be negated and completes the operation.

If a register write operation is specified, the RH11 gates the control data onto the control bus when it issues DEM. The drive will transfer the data from the control bus into the specified drive register and assert TRA, which causes the assertion of SSYN in the RH11. SSYN is transferred to the processor and causes MSYN to be cleared. The clearing of MSYN causes SSYN and DEM to be negated. The negation of DEM causes TRA to be negated to complete the operation.

The Massbus structure allows a register read operation (asynchronous control bus) to occur while a data transfer (synchronous data bus) is taking place. Any attempt by the RH11 to write a register in a drive performing a data transfer operation (except for the Maintenance and Attention Summary registers) will cause the RPO4 Drive to set the Register Modification Refused (RMR) error bit (Chapter 3).

#### 2.6 DATA TRANSFER

Before a data transfer takes place, the selected unit, desired sector/track address, cylinder address, bus address, and word count are specified by the program. The program then transfers the Read or Write data transfer command (with the GO bit asserted) to the RPCS1 register.

Upon receipt of the data transfer command, the drive will assert OCC, indicating that the data bus is busy. The RH11 logically connects to the Massbus data bus by asserting RUN and then waits for SCLK pulses from the drive. For a Write data transfer, each WCLK pulse causes a word to be written into a data register in the drive logic; for a Read data transfer, each SCLK pulse causes a word to be

transferred to the Massbus. When a sector of words has been written onto or read from the disk, the disk sends an EBL pulse to the RH11. If the RUN line is still asserted at this time, a sector of data words is transferred. If the RUN line is negated, the data transfer is terminated.

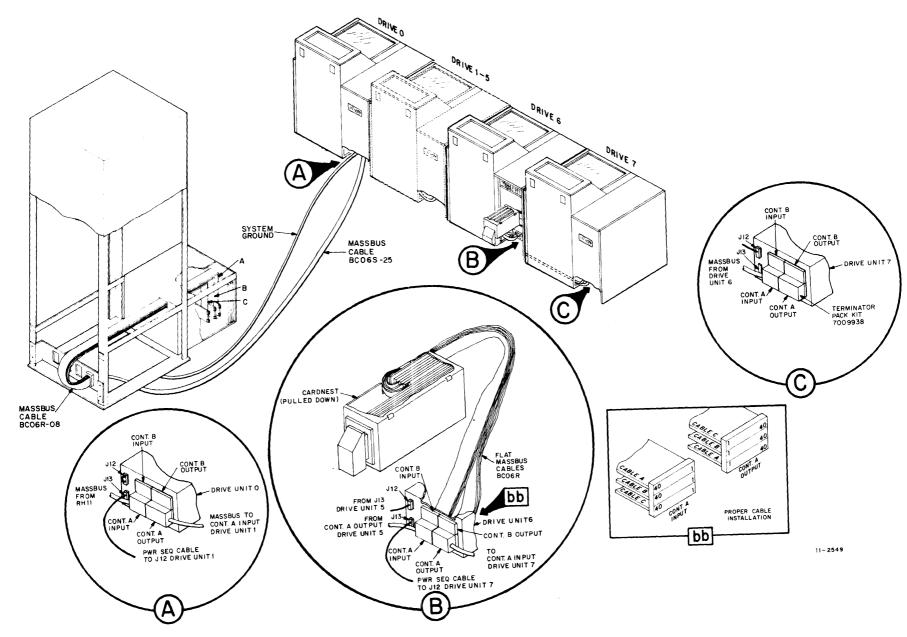

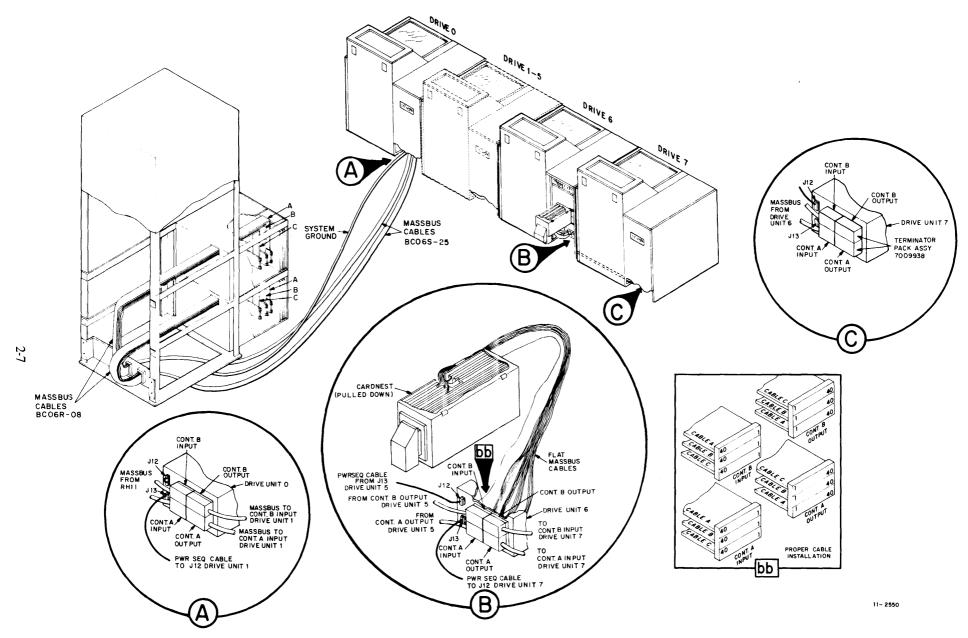

#### 2.7 MASSBUS PHYSICAL DESCRIPTION

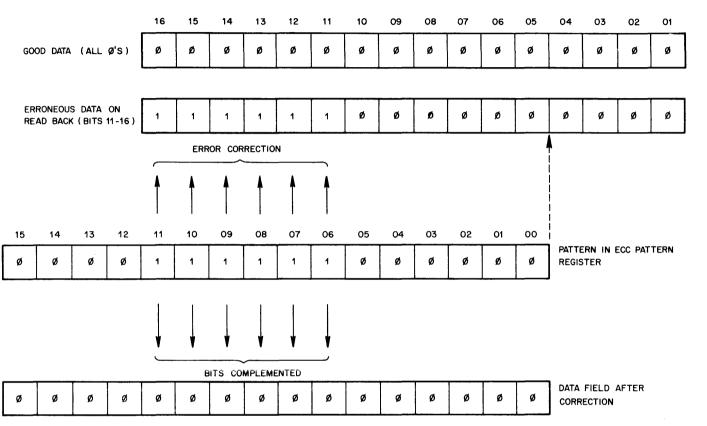

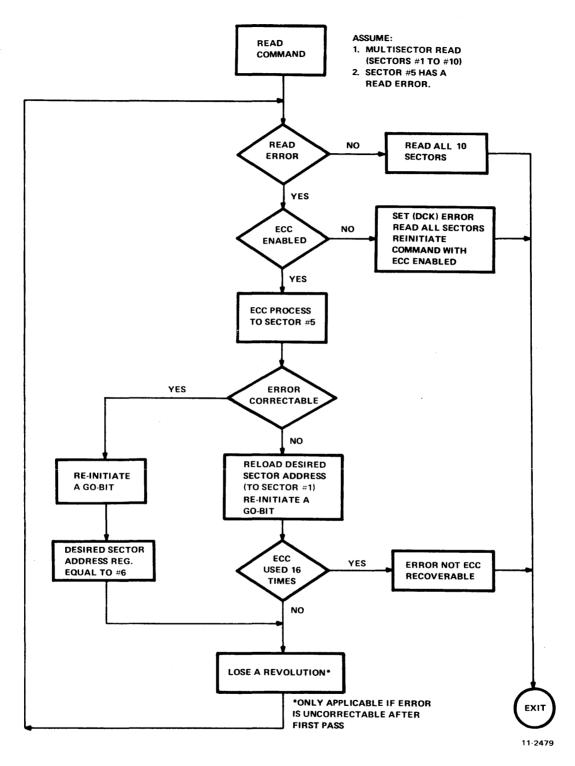

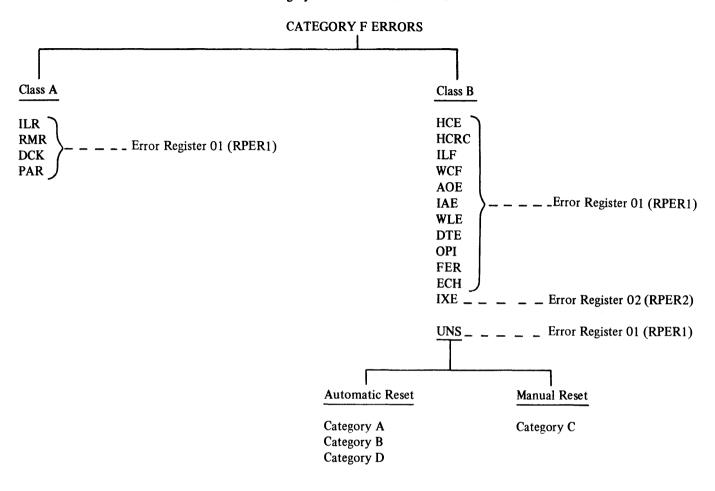

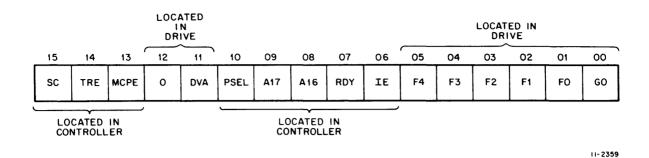

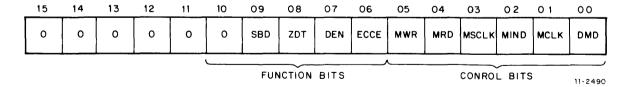

The Massbus consists of 56 signals, including data, control, status, and parity. These signals are routed externally to all cabinets via a round BC06S Massbus 60-pair cable (Figure 2-2). Standard cable length from the RH11 cabinet to the first drive is 25 ft and from drive to drive (daisy chain) is 2 ft. On special order, 40-ft and 10-ft cable lengths can be substituted. Under all conditions, the total external cable length must not exceed 60 ft. Figure 2-3 shows the cable routing for a dual-port subsystem.