SERIES 5091 MAGNETIC TAPE FORMATTER SYSTEMS

Peripheral Equipment Division

Model 5091

NRZ1 Formatter

Instruction Manual Publication No. 1800.6

# SERIES 5091 MAGNETIC TAPE FORMATTER SYSTEMS Э Selection of NRZ or phase-encoded formats with or without computer adapter interfaces and software Availability of adapters for a wide range of mini-computers. Control of as many as eight 7- and/or 9-track tape units (four per formatter) Compatibility with computer software while handling seven- or nine-track, multiple-speed, multiple-density tapes Expandability in the field simply by adding logic cards Front-panel controls and indicators • Internal power supply adequate for any desired configuration DTL/TTL IC formatter logic to assure maximum compatibility · Availability of blank circuit cards for "design your own" adapter Etched circuitry for highest reliability The DATUM Series 5091 Magnetic Tape Formatters satisfy all requirements for tapecontrol in mini-computer installations. The result of years of mini-computer interface experience, the 5091 Series consists of controls, cabinet, chassis and power supply and the formatters and computer adapters for which they provide slide-in accommodation. Whether the need be for a Formatter, for a Formatter with provision for a user-designed Computer Adapter or for a complete Tape Controller, the DATUM Series 5091 will provide the ideal instrumentation. This modularly designed series generates and reads IBM-compatible NRZ and phase-encoded formats and, with the addition of a Computer Adapter, will control as many as eight magnetic tape units. If desired, off-the-shelf Computer Adapters and software are available that will accommodate 90% of the commercially-available mini-computers. The Series 5091 design concept, a product of DATUM's wide experience in interfacing with different mini-computers, permits a high degree of compatibility with the hardware/software designs of the various computer manufacturers and with existing user-developed software. When ordered with a Computer Adapter installed, the 5091 instrument thus becomes a Tape Controller system custom-designed, both in hardware and software, to the mini-computer with which it is to function.

# FRONT-PANEL CONTROLS AND INDICATORS

**TAPE UNIT SELECT** switches allow any unit number (0, 1, 2, 3) to be assigned to any tape unit (A, B, C or D). **MODE** switch allows manual override control over parity and density selection for seven-track tape units in addition to standard program control. **PARITY** switch allows selection of ODD or EVEN parity. **DENSITY** switch allows selection of HIGH or LOW density. **VISUAL INDICATORS** display the tape unit, formatter, parity and density selected.

# **EQUIPMENT CONFIGURATIONS**

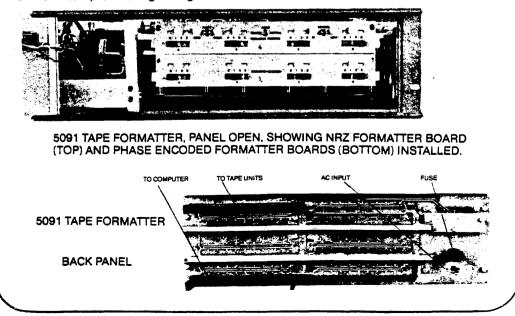

The basic Series 5091 Controller/Formatter will house and power three large circuitcards. One card slot is required for NRZ formatting, two card slots are required by the Phase-Encoding Formatter, and one card slot is necessary for the Computer Adapter. Therefore, two enclosures are necessary for some configurations.

|                                                                              | FORMATTERS REQUI |                  |                     | ORDER              |  |

|------------------------------------------------------------------------------|------------------|------------------|---------------------|--------------------|--|

| SYSTEM<br>CONFIGURATION                                                      |                  | PHASE<br>NCODED* | COMPUTER<br>ADAPTER | DATUM              |  |

| One to four 7- and/or 9-track<br>NRZ tape units.                             | One              |                  | Customer-Supplied   | 5091-1             |  |

| One to four 9-track<br>1600 PE tape units                                    |                  | One*             | Customer-Supplied   | 5091-2             |  |

| One to eight 7- and/or 9-track<br>NRZ tape units                             | Two**            |                  | Customer-Supplied   | 5091-3             |  |

| One to eight 9-track<br>1600 PE tape units                                   |                  | Two**            | Customer-Supplied   | 5091-4***          |  |

| One to four 7- and/or 9-track NRZ and<br>One to four 1600 PE tape units      | One**            | One*             | Customer-Supplied   | 5091- <del>5</del> |  |

| One to four 7- and/or 9-track<br>NRZ tape units                              | One              | ······           | One                 | 5091-6             |  |

| One to four 9-track<br>1800 PE tape units                                    |                  | One*             | One                 | 5091-10            |  |

| One to eight 7- and/or<br>9-track NRZ tape units                             | Two**            |                  | One                 | 5091-7             |  |

| One to eight 9-track<br>1600 PE tape units                                   |                  | Two**            | One                 | 5091-8**           |  |

| One to four 7- and/or 9-track NRZ tape units; one to four 1600 PE tape units | One **           | One*             | One                 | 5091-9**           |  |

\*Uses two card slots \*\*Two Formatters daisy-chained to a single Computer Adapter. "Requires two enclosures

# SPECIFICATIONS

80.00

3. Su

SIZE: 5-1/4" high, 19" (RETMA rack) wide: 24" deep. WEIGHT: 25 lbs. POWER SOURCE: 117 volts ± 10%, 60 Hz.

TEMPERATURE RANGE 0°-50°C. HUMIDITY RANGE: 4 95% to 95%; non-condensing.

1.1

1.5

VANDE AND DIMDERS 1. 24

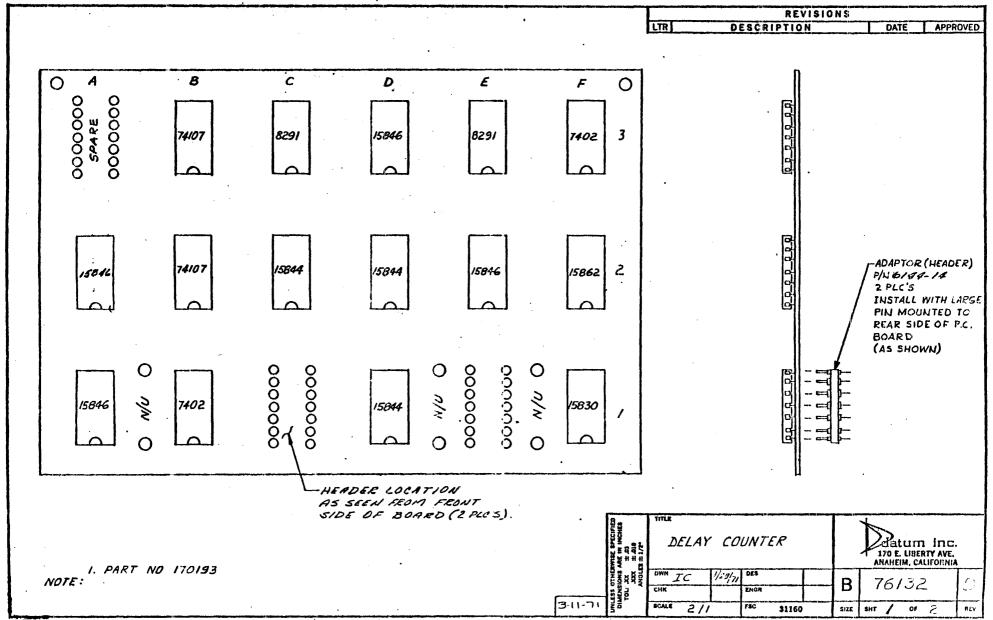

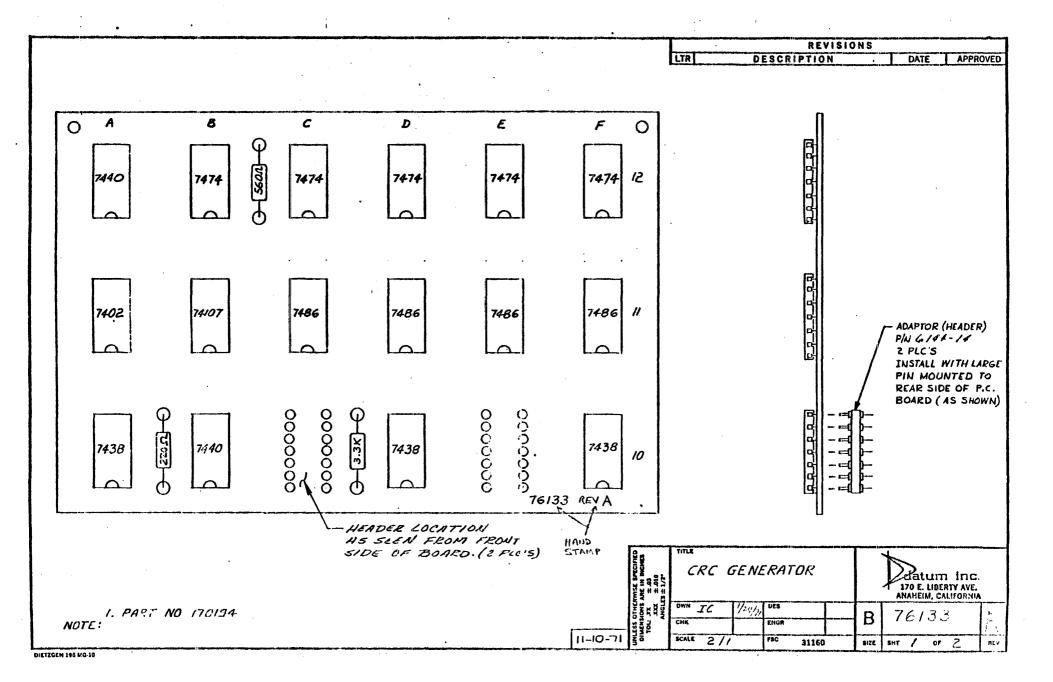

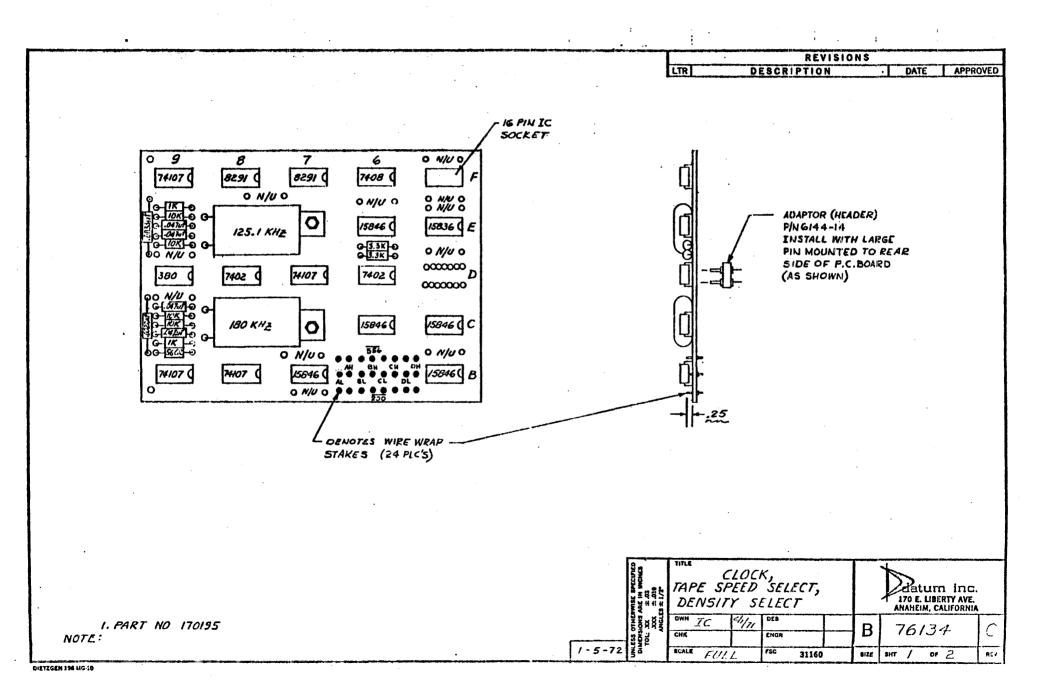

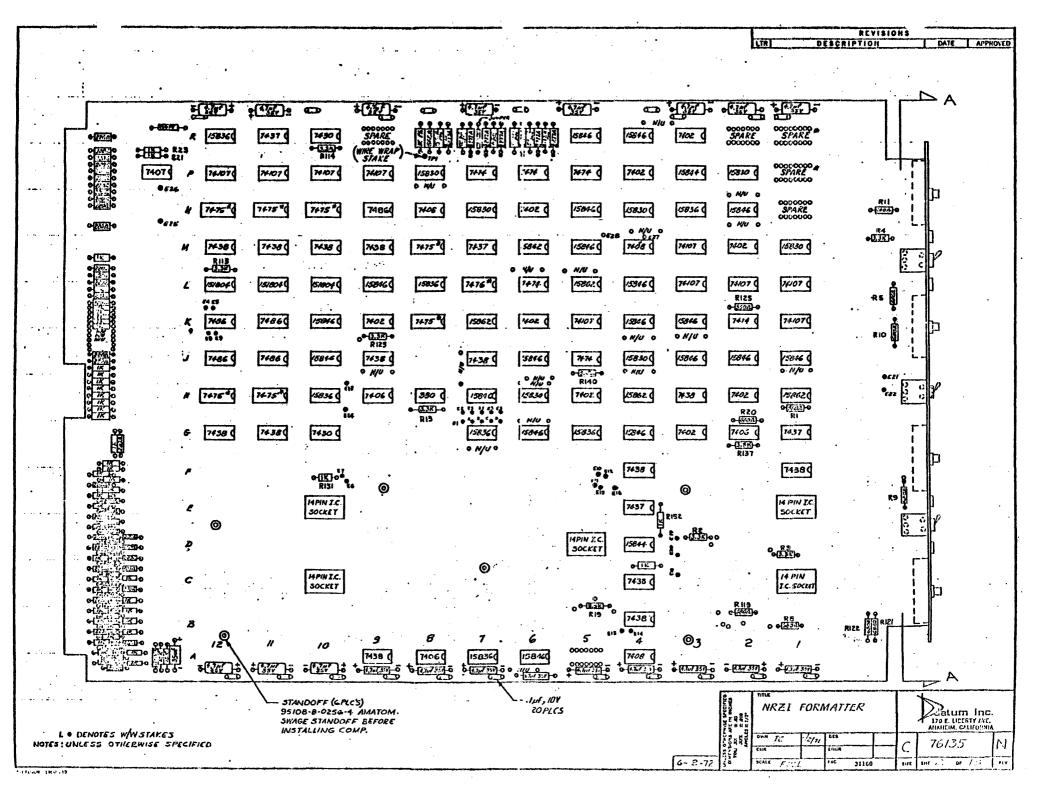

NRZ FORMATTER ELAY CONNTER

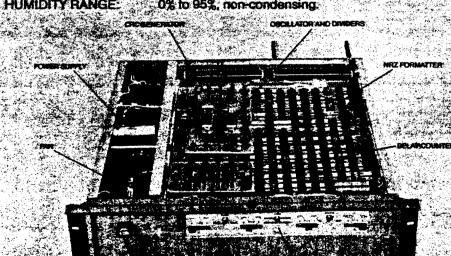

POWER ONVOFF **5091 MAGNETIC TAPE FORMATTER**

Service Service 5 - E.S.

CONTROL PANEL

### SPECIAL "DESIGNED-BY-DATUM" FEATURES **1. PROVEN HARDWARE AND SOFT**erase-then-write: Seven-track file-WARE, DATUM has delivered more mark in nine-track mode control, BCD than 150 complete computer-inter-10-to-zero conversion control. faced systems that included computer adapters and software. Typical com-3. PROFIT BY OUR EXPERIENCE. If you puters interfaced are: will be designing your own Computer Adapter, you will find that the features Computer Automation 816: Data General Nova: Digital Equipment Corp. already designed into the DATUM For-PDP-8, 8/e, 8/i, 8/L, 9, 9/L, 11, 12, 15; matter will save you as many as 25% of Hewiett-Packard 2114, 2115, 2116; the chips you would normally require Honeywell H316, H416, H516, H124A; in your Computer Adapter. IBM 1130; Microsystems 810; SDS/ 4. FRONT PANEL INDICATORS, UNIT-XDS CE16, CF16; Varian 620/i. SELECT SWITCHES AND PARITY/ **DENSITY SWITCHES.** 2. DESIGNED-IN SOFTWARE COMPAT-**IBILITY.** Multiple record spacing 5. NO ADJUSTMENT POTENTIOM-ETERS, NO ONE-SHOTS. with one command; Single-command 5091 NRZ FORMATTER CIRCUIT BOARD

# OTHER ESSENTIAL OPERATING AND DESIGN FEATURES

SPECIAL BUFFER REGISTERS in the Formatter for Read and Write make data available for the entire period between Read strobes. They will also accept Write data at any time the computer outputs the character. No external storage registers are required in the user's computer adapter.

A MIX OF ANY TWO TAPE SPEEDS can be accommodated by one Formatter within a range of 6.25 to 112.5 inches per second. Compatible with entire PEC or Wang tape-unit lines. Special speeds easily handled.

A MIX OF DIFFERENT HIGH/LOW DENSITY PAIRS of 7-track units on one NRZ formatter. For example, one transport could be 800/556 bpi, a second transport could be 556/200 bpi.

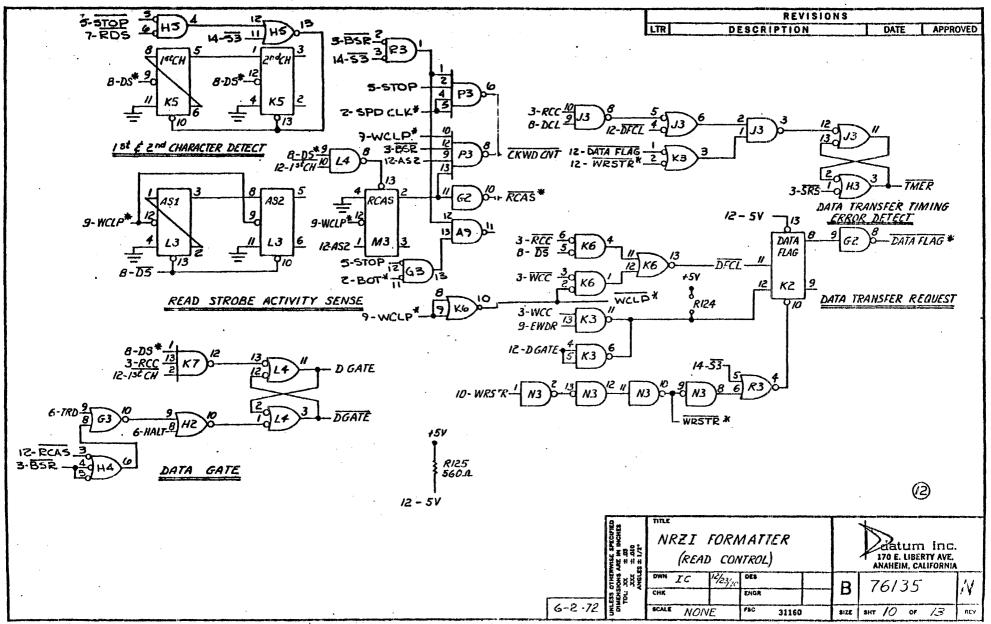

"DATA TRANSFER TIMING ERROR" status bit presented to the interface if a Read or Write data transfer is not accomplished before the next "Read" or "Write" strobe occurs.

FORWARD OR REVERSE READING with complete error-checking in either direction.

FORMATTER DIRECTLY COMPATIBLE with all general-purpose-computer timing requirements. Interface control pulses can be a minimum of 100 nanoseconds wide. The Formatter internally interlocks control signals to the tape units.

**CONTINUOUS READ OR WRITE CAPABILITY** (gapping "on-the-fly") provided by the Formatter to optimize data transfer rates.

and the set of the set of the

**NO FREQUENCY ADJUSTMENTS ARE NECESSARY.** Timing is referenced to a crystal-controlled oscillator followed by a divider chain that selects the desired frequencies. Any mixture of any two frequencies may be selected at the time of purchase. Since all delays are taken from this timing chain, no one-shots are used. **No adjust-pots are used.**

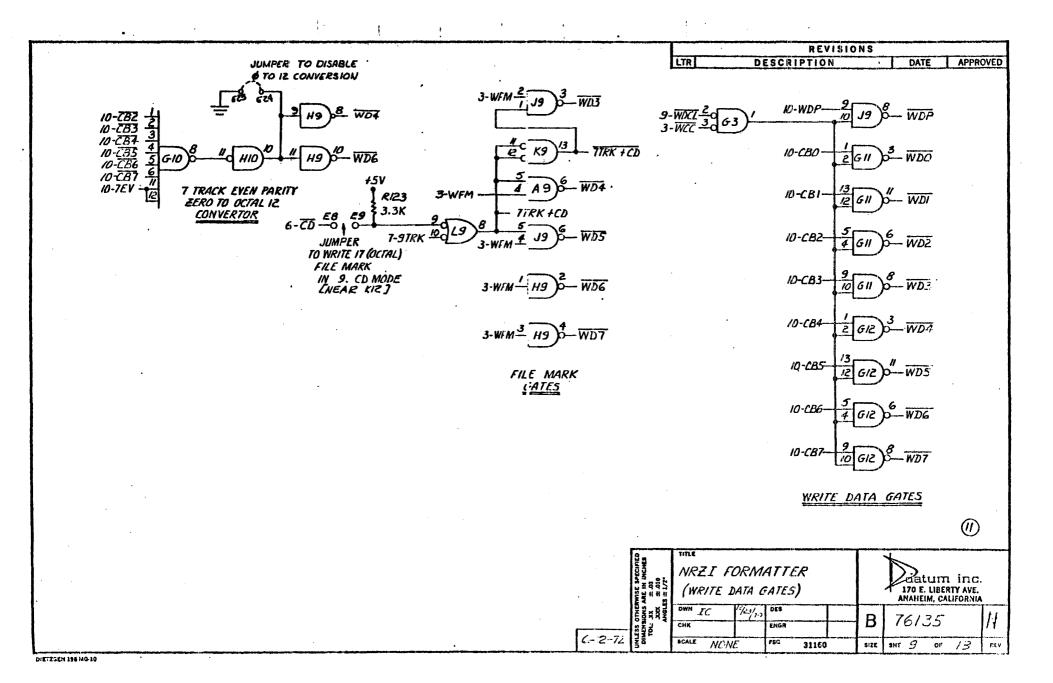

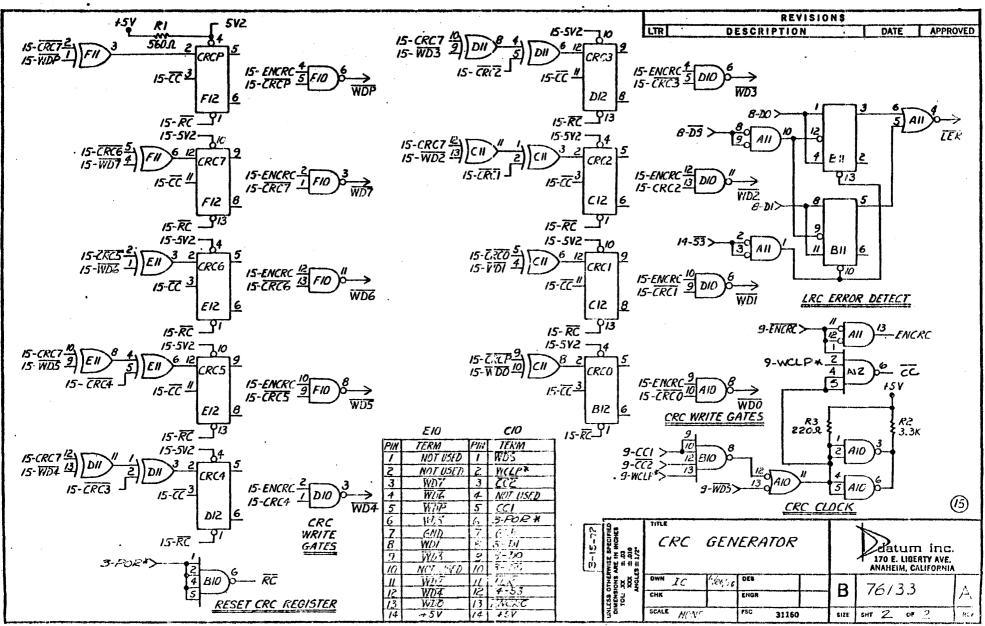

**READ, WRITE AND MOTION CONTROL LOGIC** included in the Formatter. **VRC, LRCC, CRCC** generated by the NRZ Formatter. VRC and LRCC checked. **FILE MARKS** written and recognized by Formatter.

SIMPLE TAPE UNIT EXPANSION in the field by adding additional tape units as they are needed.

TIMING FOR IBM-COMPATIBLE INTER-BLOCK GAPS and correct head positioning between records.

SINGLE GAP (write/read) AND DUAL GAP (read after write) transports can be "mixed."

**FIXED-LENGTH ERASE COMMANDS** and combination "erase then write" command provided by Formatter.

**SOFTWARE COMPATIBILITY MAINTAINED** with existing computer manufacturer's software, by providing ability to erase a three-inch gap and then, with one command, write a Record or File mark. Also with one command the user can space over any number of records, forward or backward.

**NO LOCK-UP AT LOAD POINT** when the Formatter is commanded to backspace or Read Reverse. Command rejected and Reject status returned to get attention of computer.

**PHASE-ENCODED FORMATTER CONTAINS ALL LOGIC** necessary to generate the pre-amble, post-amble, phase-encoded data and file mark patterns for recording. Read logic allows complete recovery of Read data, including data decoding, buffering, error and file mark detection and error correction.

# IF YOU ARE TO DESIGN YOUR OWN ADAPTER...

**TO ASSIST IN YOUR OWN COMPUTER ADAPTER DESIGN**, blank printed-circuit boards are available with which to build your own Computer Adapter or logic card. These boards plug directly into the existing enclosure, which provides complete interconnection. The boards can be supplied with as many as 196 IC sockets already mounted. Further, to assist in the development of your Adapter logic and software, DATUM can provide logic diagrams and actual software.

# EQUIPMENT CONFIGURATIONS

The basic Series 5091 Controller/Formatter will house and power three large circuitcards. One card slot is required for NRZ formatting, two card slots are required by the Phase-Encoding Formatter, and one card slot is necessary for the Computer Adapter. Therefore, two enclosures are necessary for some configurations.

| NRZ   | PHASE<br>ENCODED*              | COMPUTER                                         | DATIM                                                                                                                                                                                                                                                      |  |

|-------|--------------------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|       | LINGOULD                       | ADAPTER                                          | ORDER<br>DATUM<br>NUMBER                                                                                                                                                                                                                                   |  |

| One   |                                | Customer-Supplied                                | 5091-1                                                                                                                                                                                                                                                     |  |

|       | One*                           | Customer-Supplied                                | 5091-2                                                                                                                                                                                                                                                     |  |

| Two** |                                | Customer-Supplied                                | 5091-3                                                                                                                                                                                                                                                     |  |

|       | Two**                          | Customer-Supplied                                | 5091-4***                                                                                                                                                                                                                                                  |  |

| One** | One*                           | Customer-Supplied                                | 5091-5                                                                                                                                                                                                                                                     |  |

| One   |                                | One                                              | 5091-6                                                                                                                                                                                                                                                     |  |

|       | One*                           | One                                              | 5091-10                                                                                                                                                                                                                                                    |  |

| Two** |                                | One                                              | 5091-7                                                                                                                                                                                                                                                     |  |

|       | Twa**                          | One                                              | 5091-8***                                                                                                                                                                                                                                                  |  |

| Onem  | One*                           | One                                              | 5091-9***                                                                                                                                                                                                                                                  |  |

|       | Two**<br>One**<br>One<br>Two** | One* Two** Two** One* One One* Two** Two** Two** | One*     Customer-Supplied       Two**     Customer-Supplied       Two**     Customer-Supplied       One*     One*       One     One       One*     One       Two**     One       Two**     One       One*     One       Two**     One       Two**     One |  |

\*Uses two card slots. \*\*Two Formatters daisy chained to a single Computer Adapter. \*\*\*Requires two enclosures.

HUMIDITY RANGE: \_\_\_\_0% to 95%, non-condensing.

**5091 MAGNETIC TAPE FORMATTER** See the Second States of the 1. Star 51 8 . . . .

1.33

CONTROL PANEL

Ê

-6-14

1.4 67

## TABLE OF CONTENTS

| I         GENERAL DESCRIPTION AND SPECIFICATIONS         1-1           1.1         Functional Description         1-1           1.2         Physical Description         1-3           1.3         Controls and Indicators         1-3           1.4         Specifications         1-7           1.5         Magnetic Tape Formats         1-7           1.5         Magnetic Tape Formats         1-7           1.1         INTERFACE         2-1           2.1         Introduction         2-1           2.2         Formatter/Transport         2-2           2.2.1         Formatter to Transport         2-3           2.2.2         Transport to Formatter         2-5           2.3         Formatter to Computer Adaptor         2-7           2.3.1         General            2.3.2         Formatter to Computer Adaptor         2-8           2.3.3         Computer Adaptor to Formatter         2-18           111         THEORY OF OPERATION         3-1           3.1         Introduction         3-1           3.2         COBY                                                                                                                                                          | SECTION |                   |                                         | PAGE              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------|-----------------------------------------|-------------------|

| 1.2       Physical Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | I       | GENE              | RAL DESCRIPTION AND SPECIFICATIONS      | 1-1               |

| 2.1       Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         | 1.2<br>1.3<br>1.4 | Physical Description                    | 1-3<br>1-3<br>1-7 |

| 2.1       Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 11      | INTE              | RFACE                                   | 2-1               |

| 2.2       Formatter/Transport       2-2         2.2.1       Formatter to Transport       2-3         2.2.2       Transport to Formatter       2-5         2.3       Cormatter/Computer Adaptor Interface       2-7         2.3.1       General       2-7         2.3.2       Formatter to Computer Adaptor Interface       2-7         2.3.2       Formatter to Computer Adaptor       2-8         2.3.2       Formatter to Computer Adaptor       2-8         2.3.3       Computer Adaptor to Formatter       2-8         2.3.3       Computer Adaptor to Formatter       2-18         Introduction         3.1       Introduction       3-1         3.2       Block Diagram       3-1         3.2.1       Command Register and Valid/Reject Logic       3-4         3.2.3       Transport Control       3-4         3.2.4       Formatter Select       3-4         3.2.5       Tape Unit Select       3-4         3.2.6       State Counter and Main Control       3-5         3.2.7       Status Register       3-7         3.2.8       Parity Error Detect       3-8         3.2.10       Check Activity Sense       3-8         3.2.                                                                     | ••      |                   |                                         |                   |

| 2.3 Formatter/Computer Adaptor Interface       2-7         2.3.1 General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         | -                 | Formatter/Transport                     | 2-2<br>2-3        |

| 111       THEORY OF OPERATION       3-1         3.1       Introduction       3-1         3.2       Block Diagram       3-3         3.2.1       Command Register and Valid/Reject Logic       3-4         3.2.2       CBUSY       3-4         3.2.3       Transport Control       3-4         3.2.4       Formatter Select       3-4         3.2.5       Tape Unit Select       3-4         3.2.6       State Counter and Main Control       3-5         3.2.7       Status Register       3-7         3.2.8       Parity Control       3-7         3.2.9       Parity Control       3-7         3.2.9       Parity Control       3-7         3.2.10       Character Parity Check       3-8         3.2.11       LRC Check       3-8         3.2.12       Read Data Storage Register       3-8         3.2.13       Read Clock Activity Sense       3-9         3.2.14       File Mark Detect       3-10         3.2.15       Read Clock Activity Sense       3-10         3.2.13       Read Clock Activity Sense       3-10         3.2.14       File Mark Detect       3-10         3.2.15       Read Clock Activity Sens                                                                                    |         | 2.3               | Formatter/Computer Adaptor Interface    | 2-7<br>2-7<br>2-8 |

| 3.1       Introduction       3-1         3.2       Block Diagram       3-3         3.2.1       Command Register and Valid/Reject Logic       3-4         3.2.2       CBUSY       3-4         3.2.3       Transport Control       3-4         3.2.4       Formatter Select       3-4         3.2.5       Tape Unit Select       3-4         3.2.6       State Counter and Main Control       3-5         3.2.7       Status Register       3-7         3.2.8       Parity Control       3-7         3.2.9       Parity Error Detect       3-8         3.2.10       Character Parity Check       3-8         3.2.11       RC Check       3-8         3.2.12       Read Data Storage Register       3-9         3.2.13       Read Clock Activity Sense       3-9         3.2.14       File Mark Detect       3-10         3.2.15       Read Control Logic       3-12         3.2.16       Write Storage Register       3-12         3.2.17       Parity Generator       3-12         3.2.18       Write Data Select Gates       3-12         3.2.19       File Mark Generator       3-12         3.2.20       CRCC Generator<                                                                                    |         | TUCO              |                                         |                   |

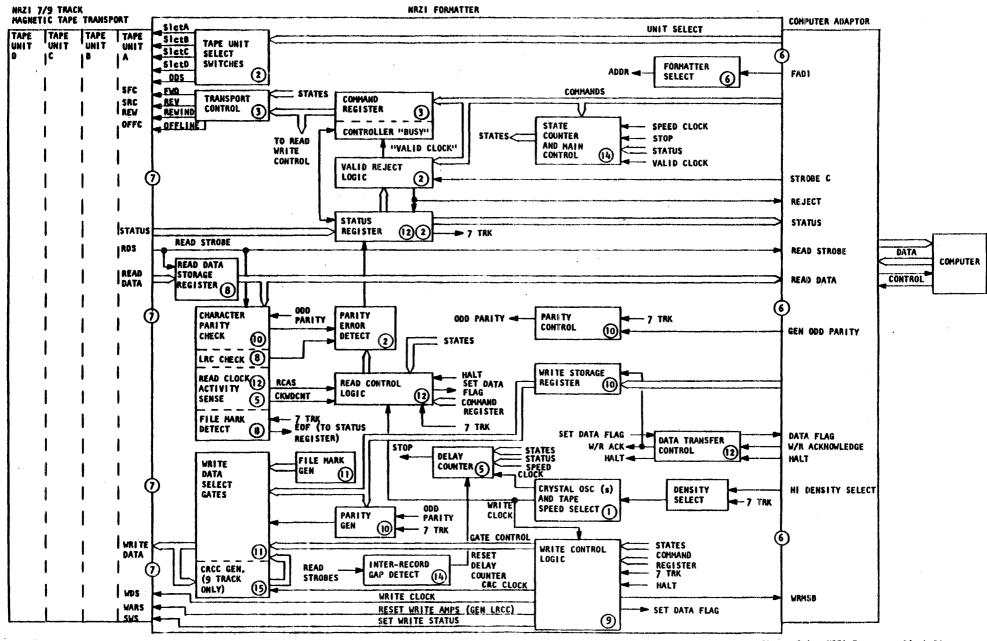

| 3.2       Block Diagram       3-3         3.2.1       Command Register and Valid/Reject Logic       3-4         3.2.2       CBUSY       3-4         3.2.3       Transport Control       3-4         3.2.4       Formatter Select       3-4         3.2.5       Tape Unit Select       3-4         3.2.6       State Counter and Main Control       3-5         3.2.7       Status Register       3-7         3.2.8       Parity Control       3-7         3.2.9       Parity Error Detect       3-8         3.2.11       LRC Check       3-8         3.2.12       Read Data Storage Register       3-9         3.2.13       Read Clock Activity Sense       3-9         3.2.14       File Mark Detect       3-10         3.2.15       Read Control Logic       3-10         3.2.16       Write Storage Register       3-12         3.2.17       Parity Generator       3-12         3.2.18       Write Data Select Gates       3-12         3.2.19       File Mark Generator       3-12         3.2.20       CRCC Generator       3-13         3.2.21       Write Control Logic       3-13         3.2.22       Crystal Os                                                                                    |         |                   |                                         | -                 |

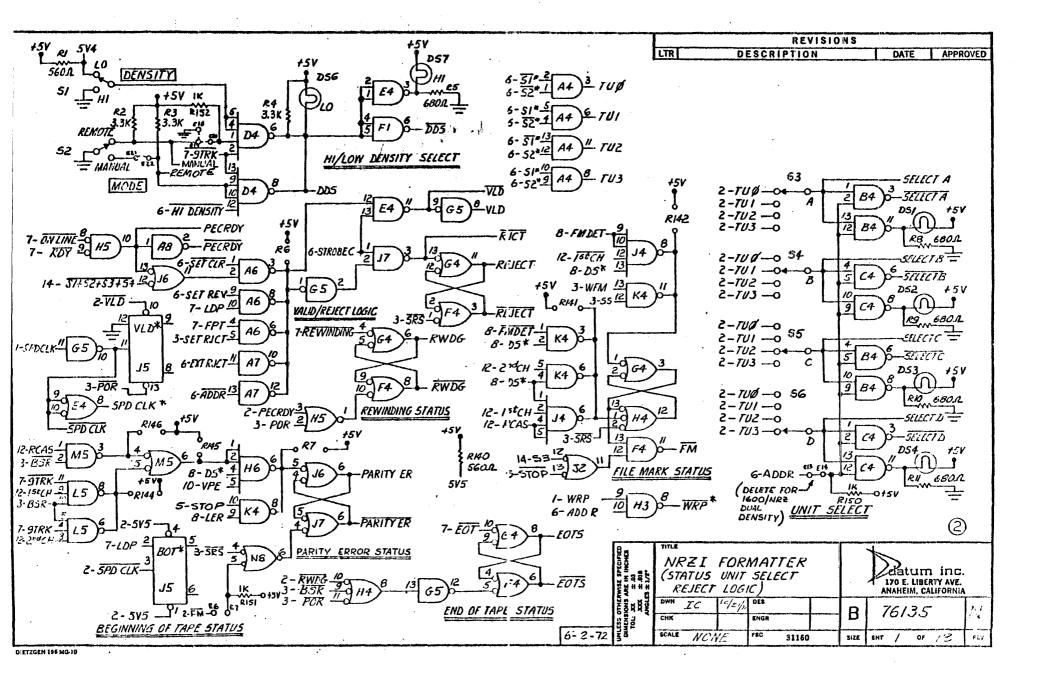

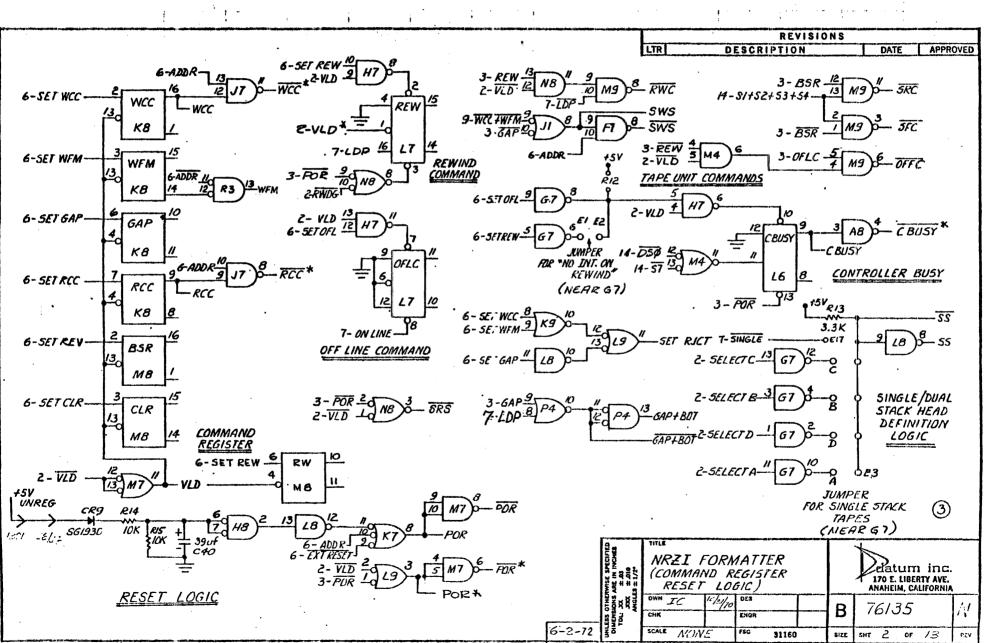

| 3.2.1       Command Register and Valid/Reject Logic       3-4         3.2.2       CBUSY       3-4         3.2.3       Transport Control       3-4         3.2.4       Formatter Select       3-4         3.2.5       Tape Unit Select       3-4         3.2.5       Tape Unit Select       3-5         3.2.6       State Counter and Main Control       3-5         3.2.7       Status Register       3-7         3.2.8       Parity Control       3-7         3.2.9       Parity Error Detect       3-8         3.2.10       Character Parity Check       3-8         3.2.11       LRC Check       3-8         3.2.12       Read Data Storage Register       3-8         3.2.13       Read Clock Activity Sense       3-9         3.2.14       File Mark Detect       3-10         3.2.15       Read Control Logic       3-10         3.2.16       Write Storage Register       3-12         3.2.17       Parity Generator       3-12         3.2.18       Write Data Select Gates       3-12         3.2.19       File Mark Generator       3-13         3.2.20       CRCC Generator       3-13         3.2.21       Wri                                                                                    |         |                   |                                         | -                 |

| 3.2.2       CBUSY       3-4         3.2.3       Transport Control       3-4         3.2.4       Formatter Select       3-4         3.2.5       Tape Unit Select       3-5         3.2.6       State Counter and Main Control       3-5         3.2.7       Status Register       3-7         3.2.8       Parity Control       3-7         3.2.9       Parity Error Detect       3-8         3.2.10       Character Parity Check       3-8         3.2.11       LRC Check       3-8         3.2.12       Read Data Storage Register       3-8         3.2.13       Read Clock Activity Sense       3-9         3.2.14       File Mark Detect       3-10         3.2.15       Read Clock Activity Sense       3-10         3.2.16       Write Storage Register       3-10         3.2.16       Write Storage Register       3-12         3.2.17       Parity Generator       3-12         3.2.18       Write Data Select Gates       3-12         3.2.19       File Mark Generator       3-12         3.2.20       CRCC Generator       3-13         3.2.21       Write Control Logic       3-13         3.2.22       Crysta                                                                                    |         | 2                 |                                         |                   |

| 3.2.3       Transport Control       3-4         3.2.4       Formatter Select       3-4         3.2.5       Tape Unit Select       3-5         3.2.6       State Counter and Main Control       3-5         3.2.7       Status Register       3-7         3.2.8       Parity Control       3-7         3.2.9       Parity Error Detect       3-8         3.2.10       Character Parity Check       3-8         3.2.11       LRC Check       3-8         3.2.12       Read Data Storage Register       3-8         3.2.13       Read Clock Activity Sense       3-9         3.2.14       File Mark Detect       3-10         3.2.15       Read Control Logic       3-10         3.2.16       Write Storage Register       3-11         3.2.17       Parity Generator       3-12         3.2.18       Write Data Select Gates       3-12         3.2.19       File Mark Generator       3-13         3.2.21       Write Control Logic       3-13         3.2.21       Write Control Logic       3-13         3.2.21       Write Control Logic       3-13         3.2.22       Crystal Oscillators and Tape Speed Select       3-14                                                                               |         |                   |                                         | -                 |

| 3.2.5       Tape Unit Select       3-5         3.2.6       State Counter and Main Control       3-5         3.2.7       Status Register       3-7         3.2.8       Parity Control       3-7         3.2.9       Parity Error Detect       3-8         3.2.10       Character Parity Check       3-8         3.2.11       LRC Check       3-8         3.2.12       Read Data Storage Register       3-8         3.2.13       Read Clock Activity Sense       3-9         3.2.14       File Mark Detect       3-10         3.2.15       Read Control Logic       3-10         3.2.16       Write Storage Register       3-10         3.2.17       Parity Generator       3-12         3.2.18       Write Data Select Gates       3-12         3.2.19       File Mark Generator       3-12         3.2.20       CRCC Generator       3-13         3.2.21       Write Control Logic       3-13         3.2.22       Crystal Oscillators and Tape Speed Select       3-14         3.2.23       Density Select       3-14         3.2.25       Delay Counter       3-15                                                                                                                                          |         |                   | 3.2.3 Transport Control                 | -                 |

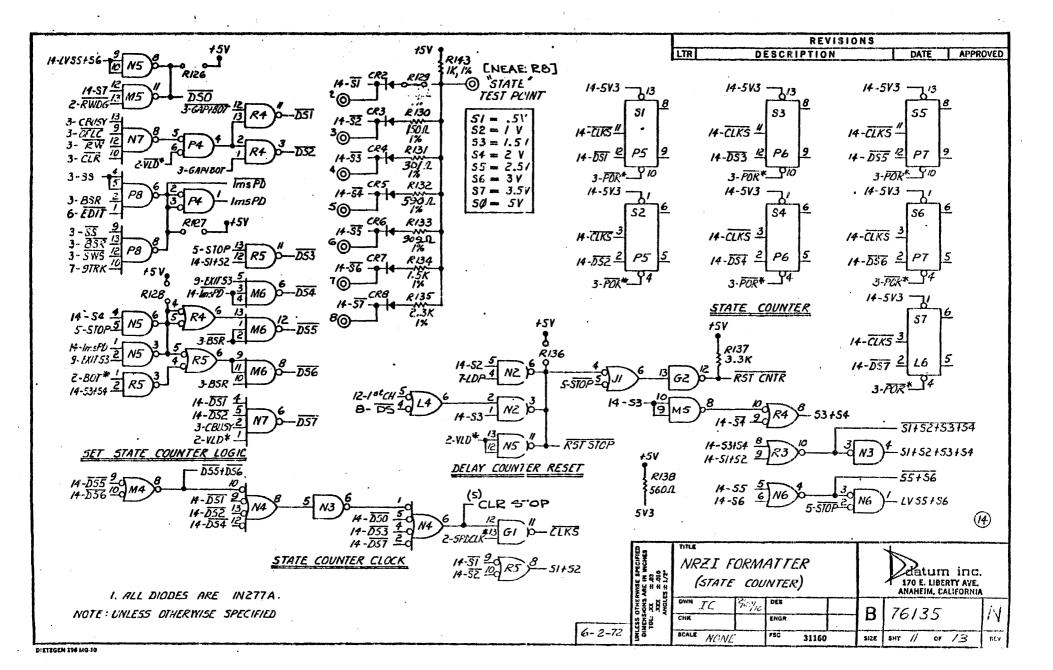

| 3.2.6       State Counter and Main Control       3-5         3.2.7       Status Register       3-7         3.2.8       Parity Control       3-7         3.2.9       Parity Error Detect       3-8         3.2.10       Character Parity Check       3-8         3.2.11       LRC Check       3-8         3.2.12       Read Data Storage Register       3-8         3.2.13       Read Clock Activity Sense       3-9         3.2.14       File Mark Detect       3-10         3.2.15       Read Control Logic       3-10         3.2.16       Write Storage Register       3-10         3.2.17       Parity Generator       3-12         3.2.18       Write Data Select Gates       3-12         3.2.19       File Mark Generator       3-12         3.2.19       File Mark Generator       3-12         3.2.19       File Mark Generator       3-13         3.2.20       CRCC Generator       3-13         3.2.21       Write Control Logic       3-13         3.2.22       Crystal Oscillators and Tape Speed Select       3-14         3.2.23       Density Select       3-14         3.2.25       Delay Counter       3-15 <td></td> <td></td> <td>• • • • • • • • • • • • • • • • • • • •</td> <td>-</td> |         |                   | • • • • • • • • • • • • • • • • • • • • | -                 |

| 3.2.7       Status Register       3-7         3.2.8       Parity Control       3-7         3.2.9       Parity Error Detect       3-8         3.2.10       Character Parity Check       3-8         3.2.11       LRC Check       3-8         3.2.12       Read Data Storage Register       3-8         3.2.13       Read Clock Activity Sense       3-9         3.2.14       File Mark Detect       3-10         3.2.15       Read Control Logic       3-10         3.2.16       Write Storage Register       3-10         3.2.17       Parity Generator       3-10         3.2.18       Write Storage Register       3-11         3.2.17       Parity Generator       3-12         3.2.18       Write Data Select Gates       3-12         3.2.19       File Mark Generator       3-12         3.2.20       CRCC Generator       3-13         3.2.21       Write Control Logic       3-13         3.2.22       Crystal Oscillators and Tape Speed Select       3-14         3.2.23       Density Select       3-14         3.2.24       Data Transfer Control       3-15         3.2.25       Delay Counter       3-15                                                                                        |         |                   |                                         |                   |

| 3.2.8       Parity Control       3-7         3.2.9       Parity Error Detect       3-8         3.2.10       Character Parity Check       3-8         3.2.11       LRC Check       3-8         3.2.12       Read Data Storage Register       3-8         3.2.13       Read Clock Activity Sense       3-9         3.2.14       File Mark Detect       3-10         3.2.15       Read Control Logic       3-10         3.2.16       Write Storage Register       3-11         3.2.17       Parity Generator       3-12         3.2.18       Write Data Select Gates       3-12         3.2.19       File Mark Generator       3-12         3.2.20       CRCC Generator       3-13         3.2.21       Write Control Logic       3-13         3.2.22       Crystal Oscillators and Tape Speed Select       3-14         3.2.23       Density Select       3-14         3.2.25       Delay Counter       3-15                                                                                                                                                                                                                                                                                                    | 4       |                   |                                         |                   |

| 3.2.9       Parity Error Detect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                   |                                         |                   |

| 3.2.10       Character Parity Check       3-8         3.2.11       LRC Check       3-8         3.2.12       Read Data Storage Register       3-8         3.2.13       Read Clock Activity Sense       3-9         3.2.14       File Mark Detect       3-10         3.2.15       Read Control Logic       3-10         3.2.16       Write Storage Register       3-11         3.2.17       Parity Generator       3-12         3.2.18       Write Data Select Gates       3-12         3.2.19       File Mark Generator       3-12         3.2.20       CRCC Generator       3-13         3.2.21       Write Control Logic       3-13         3.2.22       Crystal Oscillators and Tape Speed Select       3-14         3.2.23       Density Select       3-14         3.2.24       Data Transfer Control       3-15         3.2.25       Delay Counter       3-15                                                                                                                                                                                                                                                                                                                                             |         |                   |                                         |                   |

| 3.2.11 LRC Check                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |                   |                                         | -                 |

| 3.2.12 Read Data Storage Register       3-8         3.2.13 Read Clock Activity Sense       3-9         3.2.14 File Mark Detect       3-10         3.2.15 Read Control Logic       3-10         3.2.16 Write Storage Register       3-11         3.2.17 Parity Generator       3-12         3.2.18 Write Data Select Gates       3-12         3.2.19 File Mark Generator       3-12         3.2.20 CRCC Generator       3-13         3.2.21 Write Control Logic       3-13         3.2.22 Crystal Oscillators and Tape Speed Select       3-14         3.2.24 Data Transfer Control       3-15         3.2.25 Delay Counter       3-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | · .     |                   |                                         | -                 |

| 3.2.13 Read Clock Activity Sense       3-9         3.2.14 File Mark Detect       3-10         3.2.15 Read Control Logic       3-10         3.2.16 Write Storage Register       3-11         3.2.17 Parity Generator       3-12         3.2.18 Write Data Select Gates       3-12         3.2.19 File Mark Generator       3-12         3.2.20 CRCC Generator       3-13         3.2.21 Write Control Logic       3-13         3.2.22 Crystal Oscillators and Tape Speed Select       3-14         3.2.23 Density Select       3-14         3.2.25 Delay Counter       3-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |                   |                                         | -                 |

| 3.2.14 File Mark Detect       3-10         3.2.15 Read Control Logic       3-10         3.2.16 Write Storage Register       3-11         3.2.17 Parity Generator       3-12         3.2.18 Write Data Select Gates       3-12         3.2.19 File Mark Generator       3-12         3.2.20 CRCC Generator       3-13         3.2.21 Write Control Logic       3-13         3.2.22 Crystal Oscillators and Tape Speed Select       3-14         3.2.23 Density Select       3-14         3.2.25 Delay Counter       3-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |                   |                                         | -                 |

| 3.2.15 Read Control Logic       3-10         3.2.16 Write Storage Register       3-11         3.2.17 Parity Generator       3-12         3.2.18 Write Data Select Gates       3-12         3.2.19 File Mark Generator       3-12         3.2.20 CRCC Generator       3-13         3.2.21 Write Control Logic       3-13         3.2.22 Crystal Oscillators and Tape Speed Select       3-14         3.2.23 Density Select       3-14         3.2.24 Data Transfer Control       3-15         3.2.25 Delay Counter       3-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |                   | 3.2.14 File Mark Detect                 |                   |

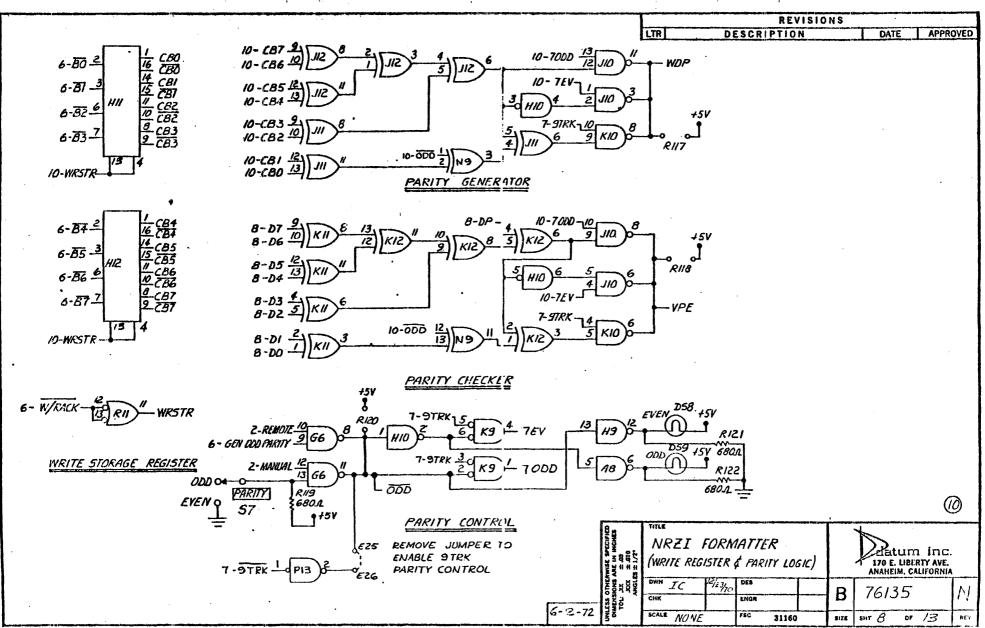

| 3.2.16 Write Storage Register       3-11         3.2.17 Parity Generator       3-12         3.2.18 Write Data Select Gates       3-12         3.2.19 File Mark Generator       3-12         3.2.20 CRCC Generator       3-13         3.2.21 Write Control Logic       3-13         3.2.22 Crystal Oscillators and Tape Speed Select       3-14         3.2.23 Density Select       3-14         3.2.25 Delay Counter       3-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                   |                                         | 3-10              |

| 3.2.17 Parity Generator       3-12         3.2.18 Write Data Select Gates       3-12         3.2.19 File Mark Generator       3-12         3.2.20 CRCC Generator       3-13         3.2.21 Write Control Logic       3-13         3.2.22 Crystal Oscillators and Tape Speed Select       3-14         3.2.23 Density Select       3-14         3.2.25 Delay Counter       3-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |                   | 3.2.16 Write Storage Register           | 3-11              |

| 3.2.18 Write Data Select Gates       3-12         3.2.19 File Mark Generator       3-12         3.2.20 CRCC Generator       3-13         3.2.21 Write Control Logic       3-13         3.2.22 Crystal Oscillators and Tape Speed Select       3-14         3.2.23 Density Select       3-14         3.2.24 Data Transfer Control       3-15         3.2.25 Delay Counter       3-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |                   | 3.2.17 Parity Generator                 | 3-12              |

| 3.2.20 CRCC Generator       3-13         3.2.21 Write Control Logic       3-13         3.2.22 Crystal Oscillators and Tape Speed Select       3-14         3.2.23 Density Select       3-14         3.2.24 Data Transfer Control       3-15         3.2.25 Delay Counter       3-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |                   | 3.2.18 Write Data Select Gates          | -                 |

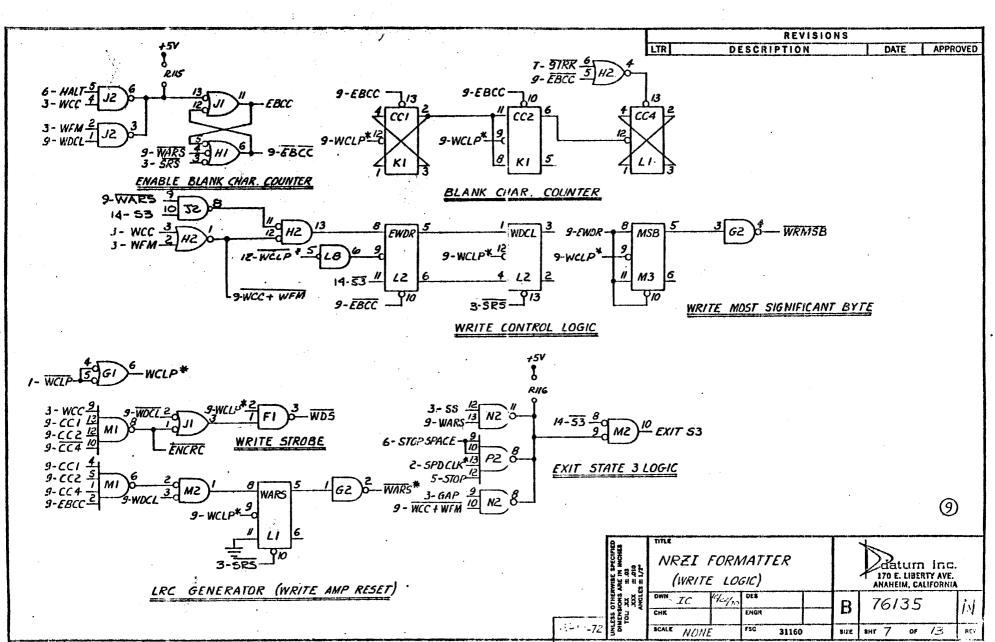

| 3.2.21 Write Control Logic       3-13         3.2.22 Crystal Oscillators and Tape Speed Select       3-14         3.2.23 Density Select       3-14         3.2.24 Data Transfer Control       3-15         3.2.25 Delay Counter       3-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | A.      |                   |                                         | -                 |

| 3.2.22 Crystal Oscillators and Tape Speed Select       3-14         3.2.23 Density Select       3-14         3.2.24 Data Transfer Control       3-15         3.2.25 Delay Counter       3-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |                   |                                         |                   |

| 3.2.23 Density Select       3-14         3.2.24 Data Transfer Control       3-15         3.2.25 Delay Counter       3-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |                   | 3.2.21 Write Control Logic              |                   |

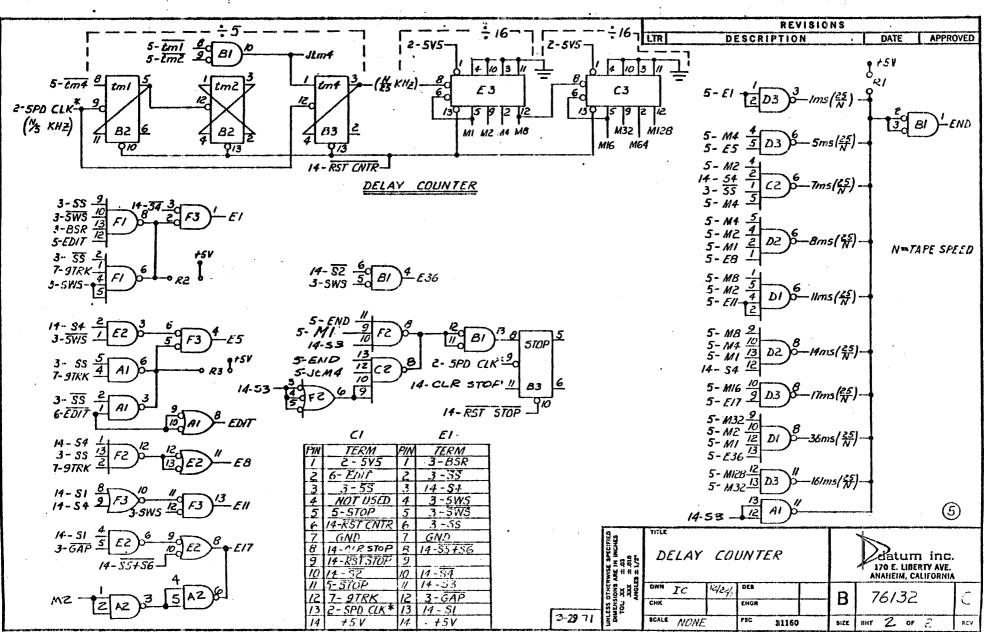

| 3.2.24 Data Transfer Control       3-15         3.2.25 Delay Counter       3-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                   |                                         |                   |

| 3.2.25 Delay Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |                   | 5.2.25 Density Select                   | -                 |

| 3.2.26 Inter Record Gan Detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |                   | 3.2.24 Vata Transfer Control            |                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                   | 3.2.27 Delay Counter                    |                   |

# TABLE OF CONTENTS (Continued)

| 3.3 | Commands ,                                                   | 3- |

|-----|--------------------------------------------------------------|----|

|     | 3.3.1 Basic Commands                                         | 3- |

|     | 3.3.2 Command and Mode Combinations                          | 3- |

| 3.4 |                                                              | 3- |

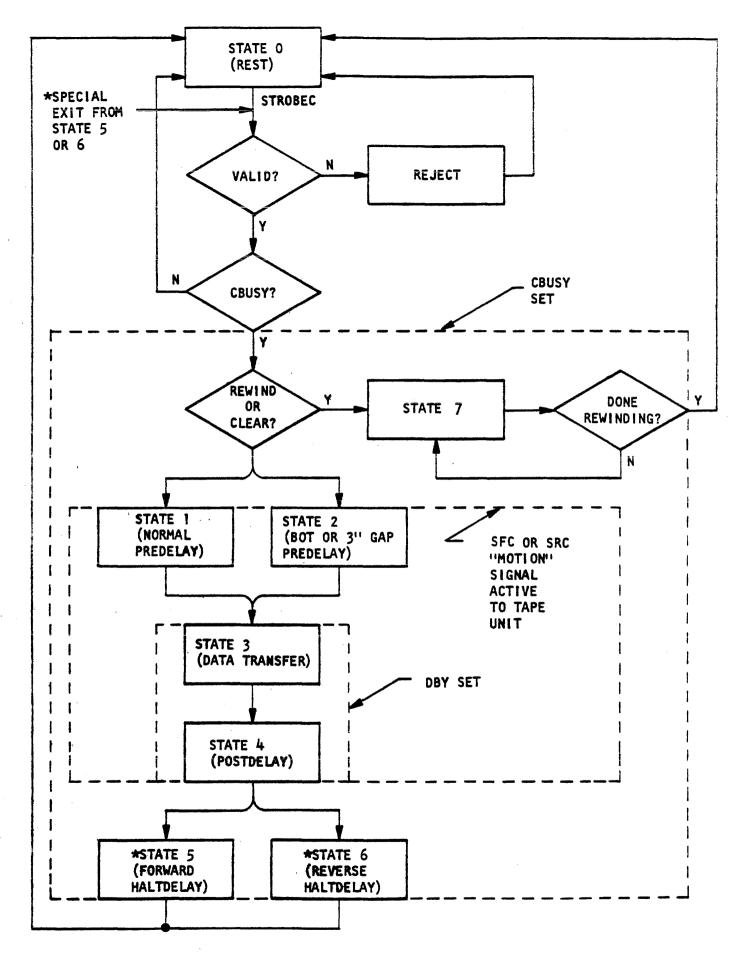

|     | 3.4.1 Simplified State Flow                                  | 3- |

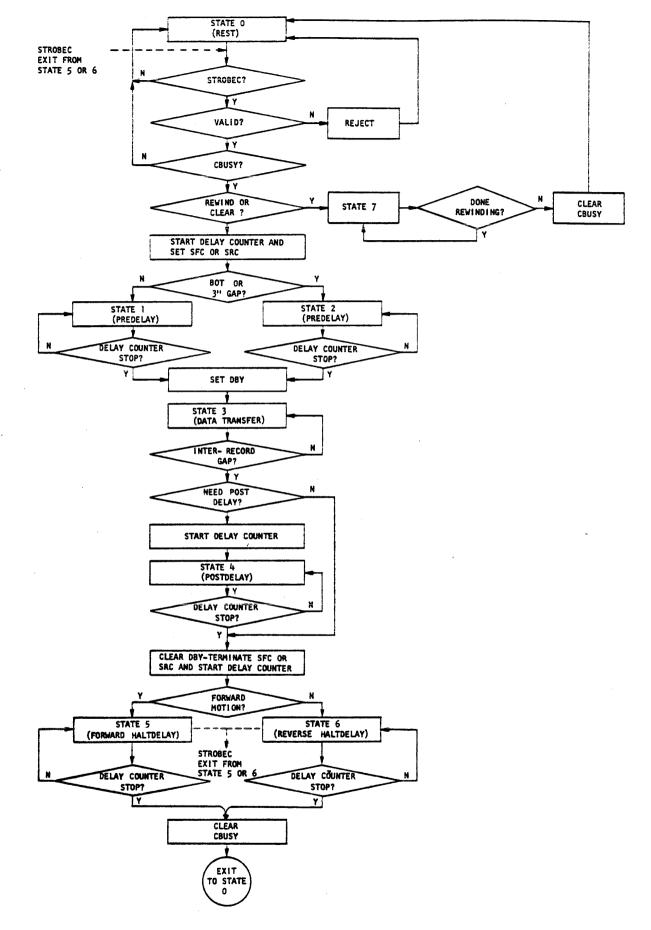

|     | 3.4.2 Detailed State Flow                                    | 3- |

| 3.5 | Command Execution and Timing                                 | 3- |

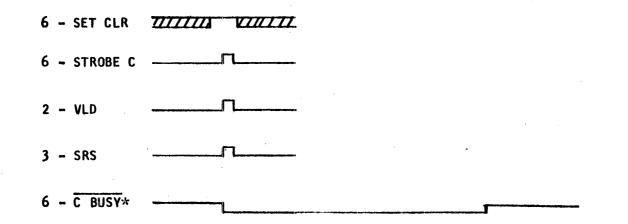

|     | 3.5.1 Clear                                                  | 3- |

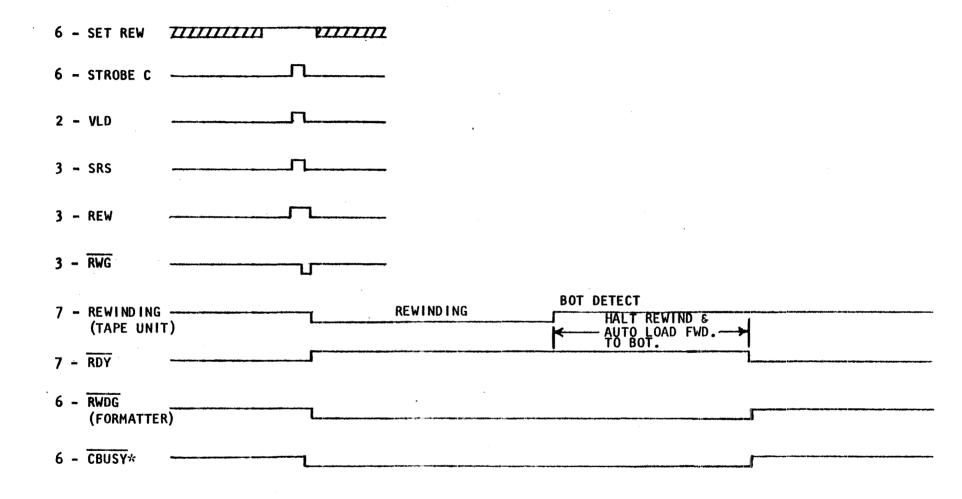

|     | 3.5.2 Rewind                                                 | 3- |

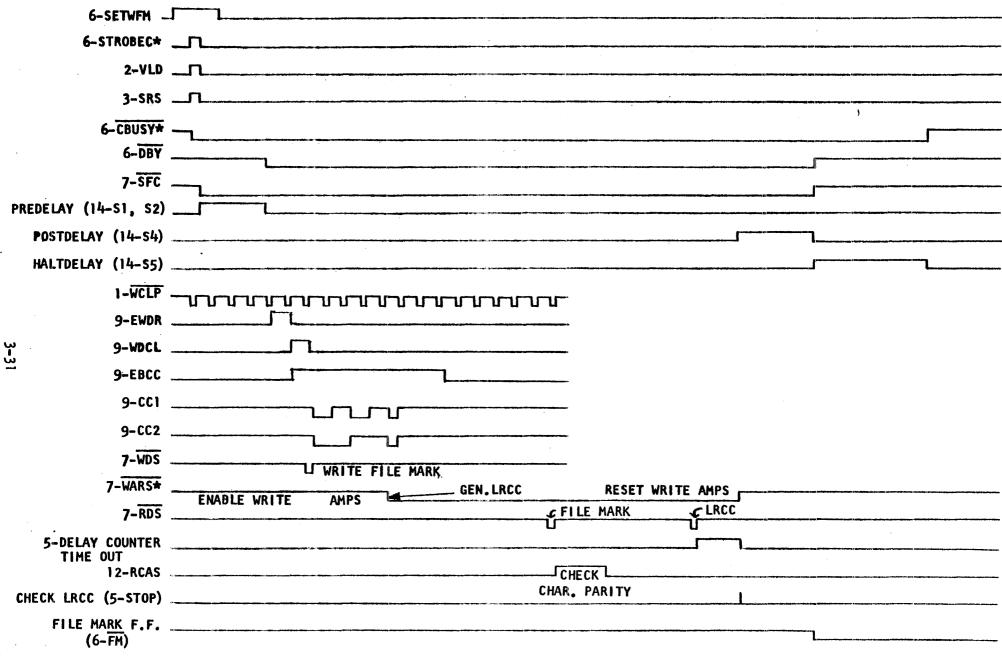

|     | 3.5.3 Write File Mark (7 Track)                              | 3- |

|     | 3.5.4 Write File Mark (9 Track)                              | 3- |

|     | 3.5.5 Forward Space One Record                               | 3- |

|     | 3.5.6 Backspace Record                                       | 3- |

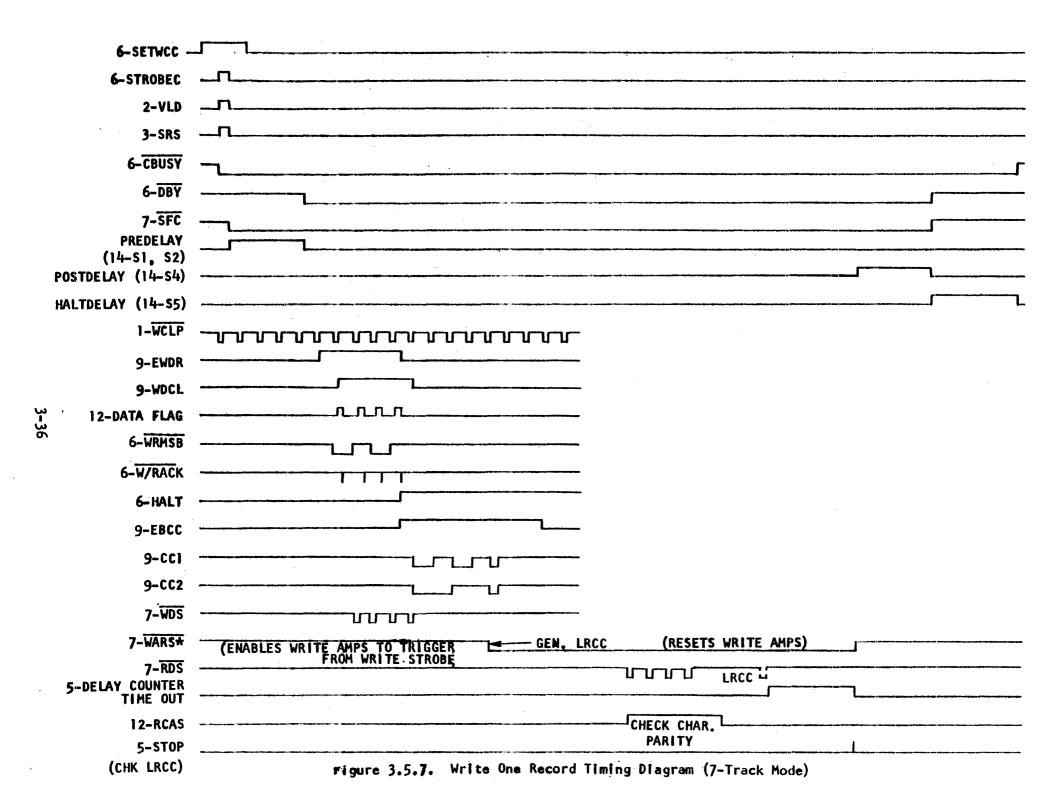

|     | 3.5.6 Write-One-Record (7 Track)                             | 3- |

|     | 3.5.8 Write One Record • • • • • • • • • • • • • • • • • • • | 3- |

|     | 3.5.9 Read One Record (7 Track)                              | 3- |

|     | 3.5.10 Read One Record                                       | 3- |

|     | 3.5.11 Erase 3 Inch Gap                                      | 3- |

| 3.6 |                                                              | 3- |

| 3.7 | Options                                                      | 3- |

|     | 3.7.1 Tape Speed                                             | 3- |

|     | 3.7.2 Dual Densities                                         | 3- |

|     | 3.7.3 Single/Dual Stack Head Selection                       | 3- |

|     | 3.7.4 BCD 10 to Zero Converter                               | 3- |

|     | 3.7.5 7 Track File Mark Code Write/Read on                   |    |

|     | 9 Track Unit                                                 | 3- |

|     | 3.7.6 No Parity Error for File Marks                         | 3- |

|     | 3.7.7 Rewind Interrupt                                       | 3- |

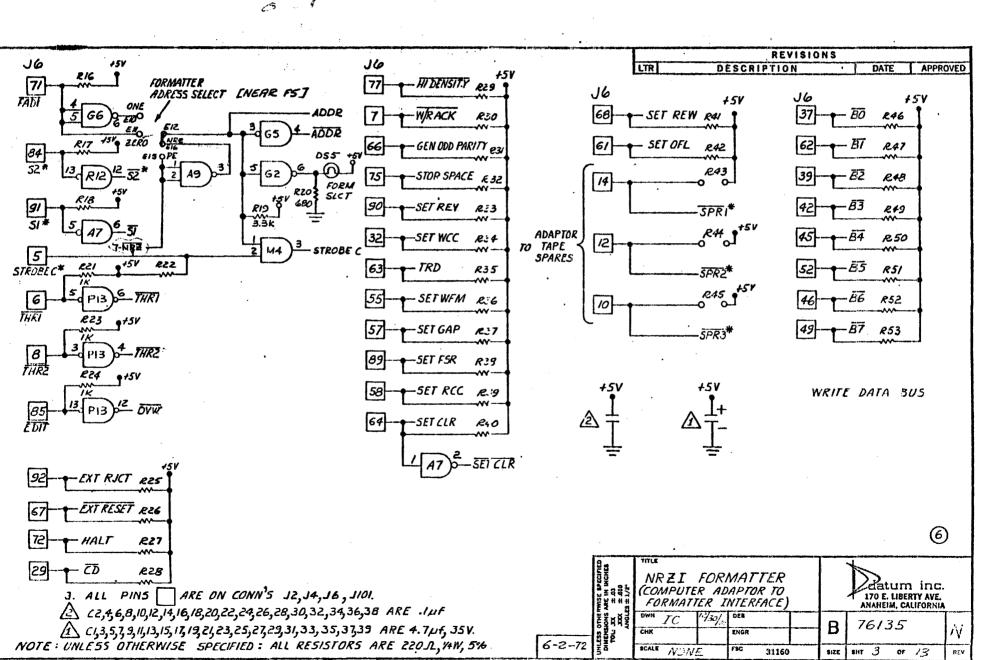

|     | 3.7.8 Formatter Address Select                               | 3- |

| 3.8 | Delay Times                                                  | 3- |

PAGE

SECTION

Ĕ

111

IV

DRAWINGS

11

# TABLE OF CONTENTS (Continued)

# LIST OF FIGURES

### FIGURE

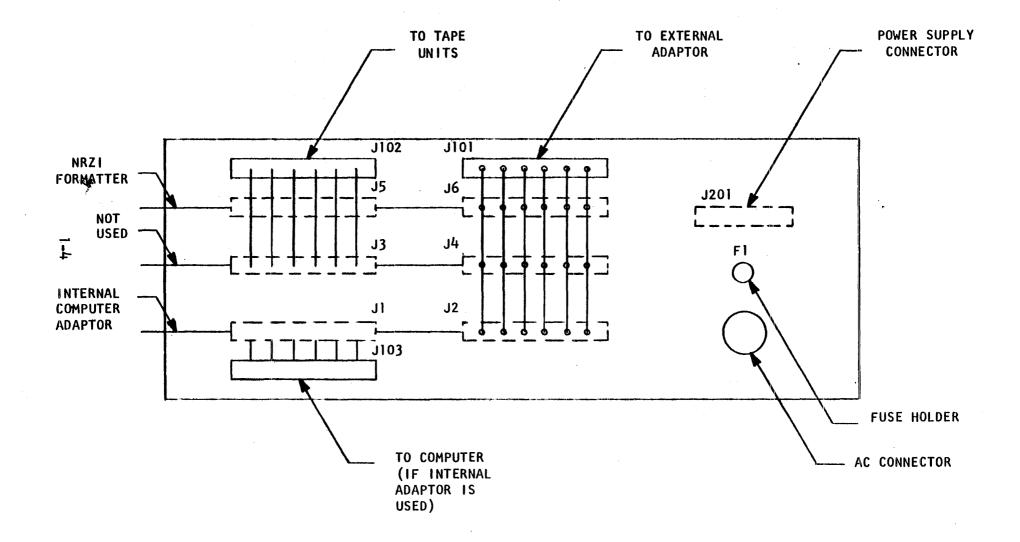

| 1-1-  | Rear View Formatter Connector                  | 1-4  |

|-------|------------------------------------------------|------|

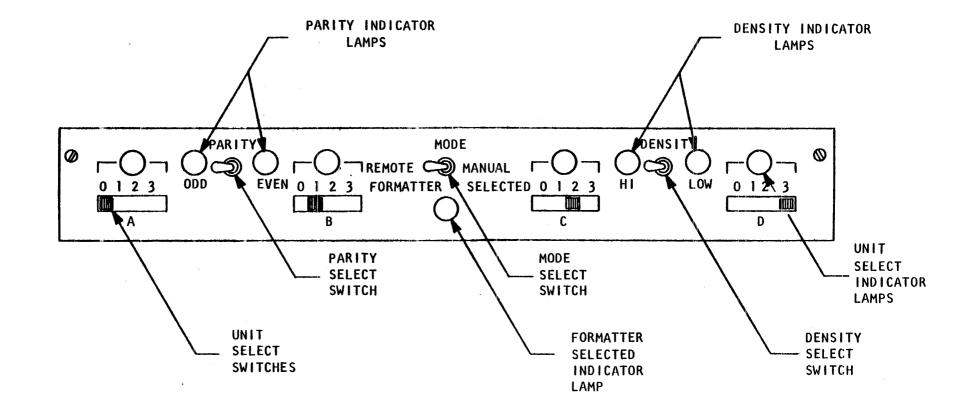

| 1-2   | Front Panel                                    | 1-5  |

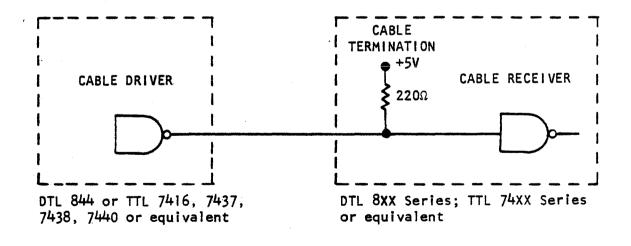

| 1-3   | Interface Circuits                             | 1-8  |

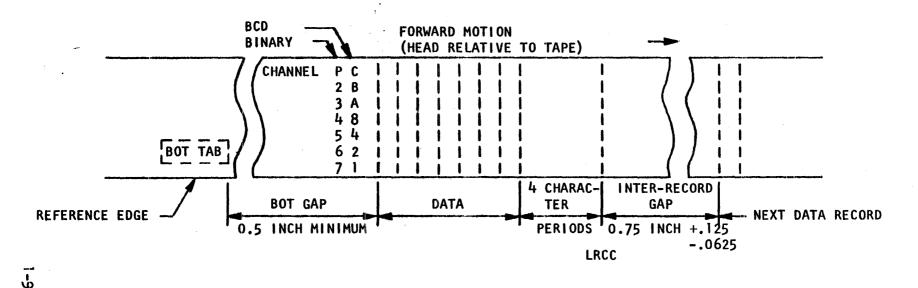

| 1-4   | 7-Track Format                                 | 1-9  |

| 1-5   | 9-Track Format                                 | 1-10 |

| 3-1   | NRZI Formatter Block Diagram                   | 3-19 |

| 3-2   | Simplified State Flow                          | 3-22 |

| 3-3   | Detailed State Flow                            | 3-25 |

| 3-5.1 | "Clear" Timing Diagram                         | 3-27 |

| 3-5.2 | Rewind Timing Diagram                          | 3-29 |

| 3-5.3 | Write File Mark Timing Diagram (7-Track Mode)  | 3-31 |

| 3-5.5 | Forward Space One Record Timing Diagram        | 3-34 |

| 3-5.7 | Write One Record Timing Diagram (7-Track Mode) | 3-36 |

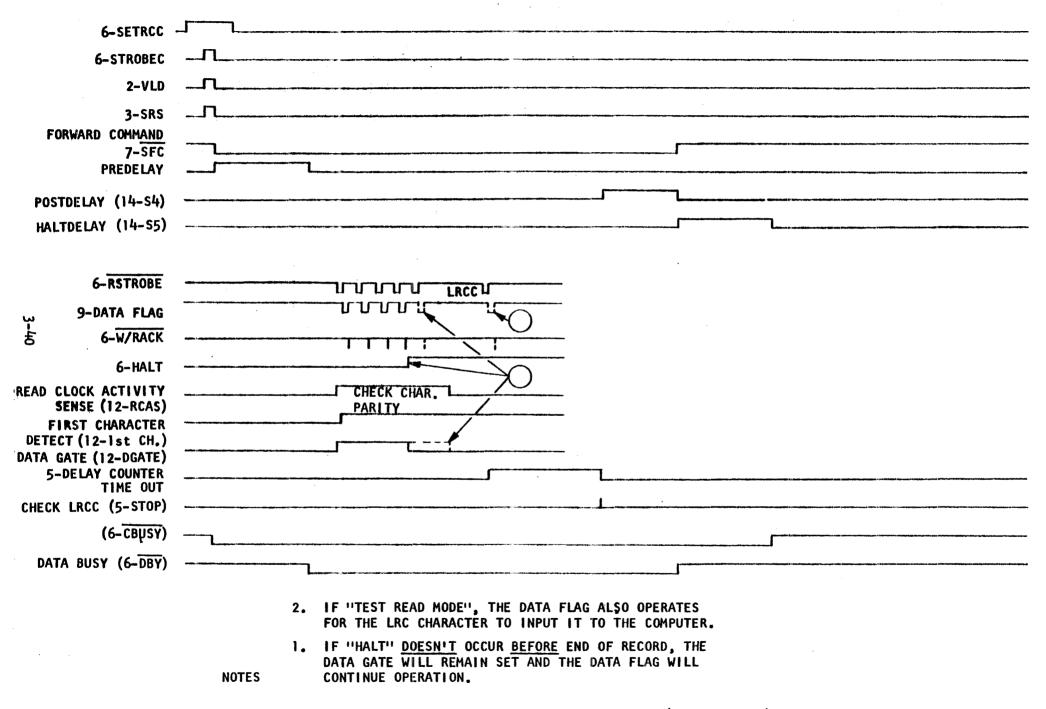

| 3-5.9 | Read One Record Timing Diagram (7-Track Mode)  | 3-40 |

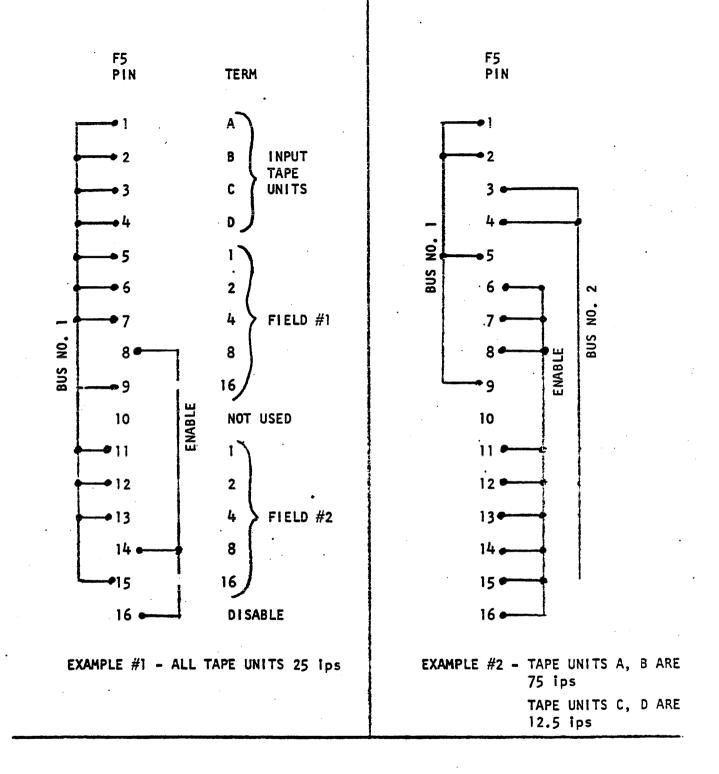

| 3-8   | Example Tape Speed Selection                   | 3-46 |

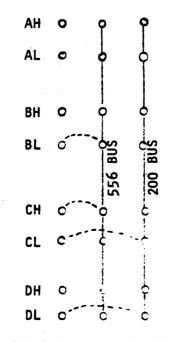

| 3-9   | Density Selection                              | 3-47 |

## LIST OF TABLES

### TABLES

| 2-1   | Formatter/Transport(s) Interface       | 2-2  |

|-------|----------------------------------------|------|

| 2-2   | Formatter/Computer Adaptor Interface   | 2-9  |

| 2-3   | Commands                               | 2-20 |

| 3-1   | Commann and Mode Combinations          | 3-19 |

| 3-7   | Tape Speed Selection                   | 3-45 |

| 3-7.8 | Formatter Address Selection            | 3-50 |

| 3-9   | Nine Track Pre/Post Delays (75 ips)    | 3-52 |

| 3-10  | Nine Track Pre/Post Delays (45 ips)    | 3-53 |

| 3-11  | Nine Track Pre/Post Delays (37.5 ips)  | 3-54 |

| 3-12  | Nine Track Pre/Post Delays (25 ips)    | 2-55 |

| 3-13  | Nine Track Pre/Post Delays (12.5 ips)  | 3-56 |

| 3-14  | Seven Track Pre#Post Delays (75 ips)   | 3-57 |

| 3-15  | Seven Track Pre/Post Delays (45 ips)   | 3-58 |

| 3-16  | Seven Track Pre/Post Delays (37.5 ips) | 3-59 |

| 3-17  | Seven Track Pre/Post Delays (25 ips)   | 3-60 |

| 3-18  | Seven Track Pre/Post Delays (12.5 ips) | 3-61 |

# INSTALLATION INSTRUCTIONS

MODEL 5091 FORMATTERS

### UNPACKING AND INSPECTION OF FORMATTER

- a. Visually inspect the Formatter to ascertain that there has been no physical damage. Should damage be observed, the carrier must be notified within ten days if an insurance claim is to be made.

- Make certain that all boards are plugged firmly into the mother boards.

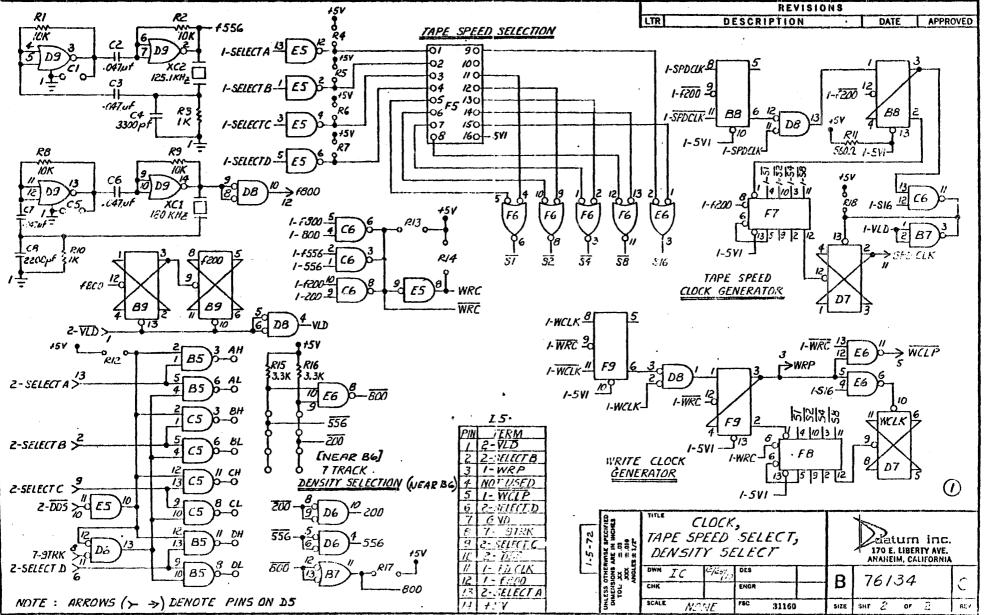

- c. Make certain that the speed chip (Assembly 701587) is installed. On the NRZ units, the speed chip is located on the lower righthand corner (F5) of the center board (Assembly 76134) of the three smaller boards mounted on the left side of the motherboard. On the Phase Encoded units, the speed chip is located on the lower right-hand corner (D28) of the left-most of the three smaller boards (Assembly 76191) mounted on the motherboard. Should the speed chip be removed and then replaced, be certain that pin 1 of the chip (the beveled corner) matches pin 1 etched on the circuit board.

- d. Make certain that the main boards are seated firmly in the rear

### MOUNTING THE FORMATTER

b.

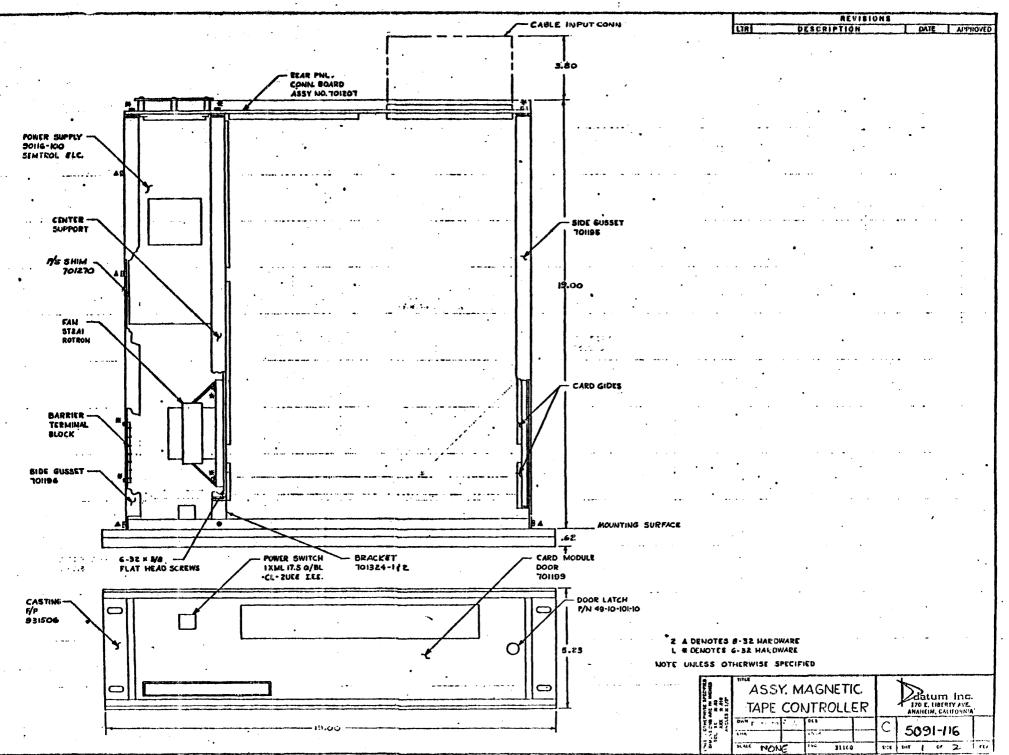

A small packet of mounting hardware containing 10-32 phillips-head screws, metal grommets and mylon chafing guards is included with each Formatter. The Formatter is mounted in the rack by lining its four mounting holes up with four threaded mounting holes in the rack and securing it with the grommet guards, grommets and 10-32 screws. The Formatter requires 24" of rack space behind the mounting surface. This 23"-deep rack allows for cable bend at the rear of the Formatter.

### MOUNTING THE TAPE UNITS

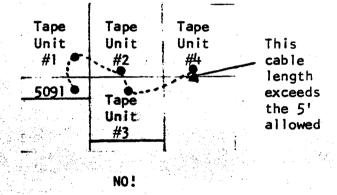

All tape units require rack mounting. Mounting of the tape units in a standard 19" RETMA rack is described in the tape unit manual. The 5091 Formatter and the tape units must be mounted such that five-foot tape-cable lengths will "daisy-chain" to all units. This requires that all units be mounted either directly above, below or beside the previous unit in the chain. (See sketch below.)

| Таре  | Tape        | Таре         |

|-------|-------------|--------------|

| Unit: | •Unit<br>#2 | ¶Unit<br>}#3 |

| 5091  |             | :Tape        |

| ÷.    |             | •Unit<br>#4  |

OK :

FIGU

The standard multiple-tape-unit "daisy-chain" configuration requires termination resistors to be deleted from <u>all but the last</u> tape unit. Therefore, the power to the last tape unit must be switched to "ON" when any tape unit is in use. This supplies power to the terminator.

### 3.1 Tape Unit Termination Option

The Tape Unit Termination Option provides termination circuits on printed-circuit boards that plug onto the last tape unit. This Option enables power to be applied from any tape unit that has power "ON". Installation of this option allows termination resistors to be deleted from <u>all</u> tape units and allows operation to continue, even when the last tape unit becomes defective to the extent that its power cannot be turned on.

INSTALLATION, MODEL 5091 FORMATTER

tion\_

The installation hardware consists of Cable 960076, the single-connector end of which attached, via P102, to J102, the upper-left-hand connector on the back panel of the Controller. Two 6/32 screws are supplied to secure this connec-

CAUTION: TO AVOID COSTLY DAMAGE TO EQUIPMENT, IT IS IMPERATIVE THAT THE CONNECTORS BE ATTACHED IN ACCORDANCE WITH THE FOLLOWING INSTRUCTIONS.

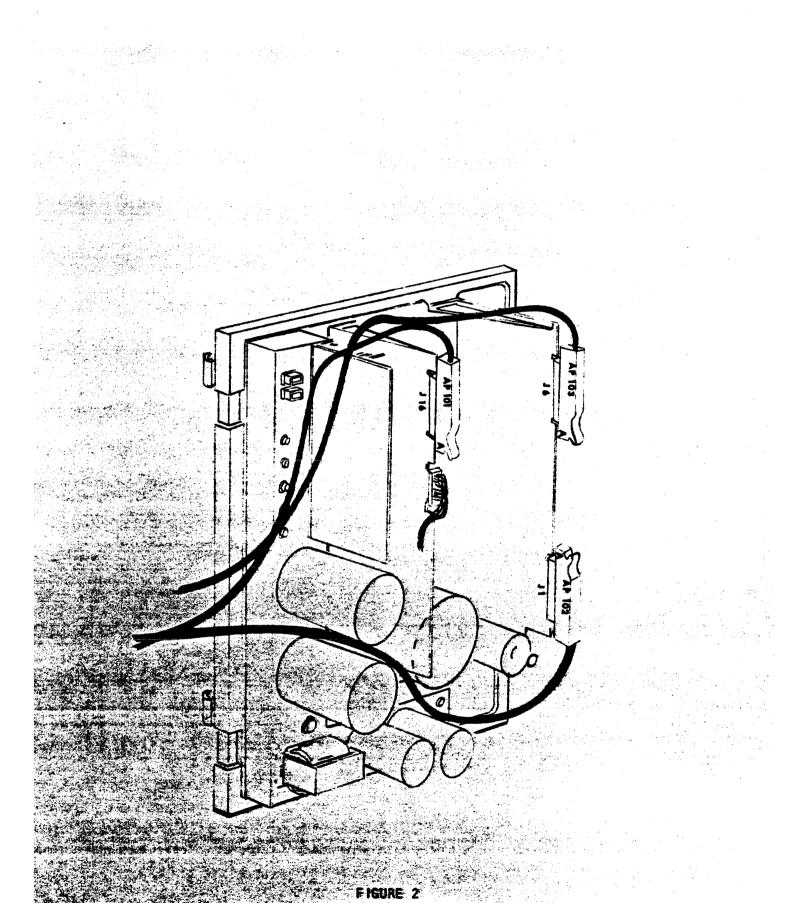

### To WANS MRZ Tape Units (Figure 2)

F. Connector AP101 attaches to J16 on the Wang Tape Unit, which is the upper connector (marked "J16") on the second printed-circuit board from the left as you face the back of the Wang unit. As shown in Figure 1, make certain that the cable enters from the upper end of the connector and that the "A" stamped on the connector designates the end furthest into the tape unit.

- 2. Connector AP103 attaches to J6 on the Wang Tape Unit, which is the upper connector (marked "J6") on the right-hand board (as you face the <u>back</u> of the tape unit). Ascertain, as in Step 1, that the cable enters from the top end of the connector and that "A" is stamped on the connector-end furthest into the unit.

- 3. Connector AP102 attached to J1, which is the bottom connector on the board designated in Step 2. Ascertain that the cable enters the lower end of the connector and that "A" is atamped on the connector-end furthest into the unit.

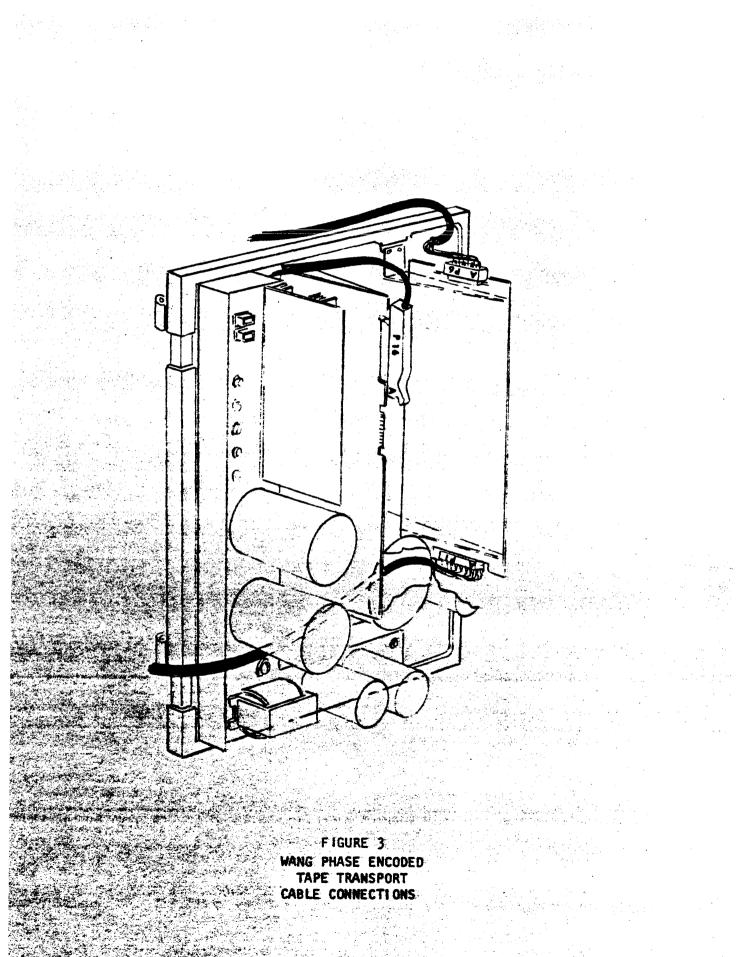

### To WANG PHASE ENCODED Units (Figure 3)

4.2

- Connector P16 connects to jack J16 on the upper leading edge of the first printed circuit board from the left, as you face the back of the Wang unit. As shown in Figure 3, make certain that the cable enters from the upper end of the connector and that the "A" stamped on the connector designates the end furthest into the tape unit.

- Connector P6 connects to jack J6 on the upper edge of the righthand printed circuit board (as you face the back of the unit). See Figure 3. Ascertain that the connector-end stamped "A" is shown in the Illustration.

- Connector PI connects to jack JI on the lower edge of the righthand circuit board. (See Figure 3.) Ascertain that the connectorend stamped "At is shown in the illustration.

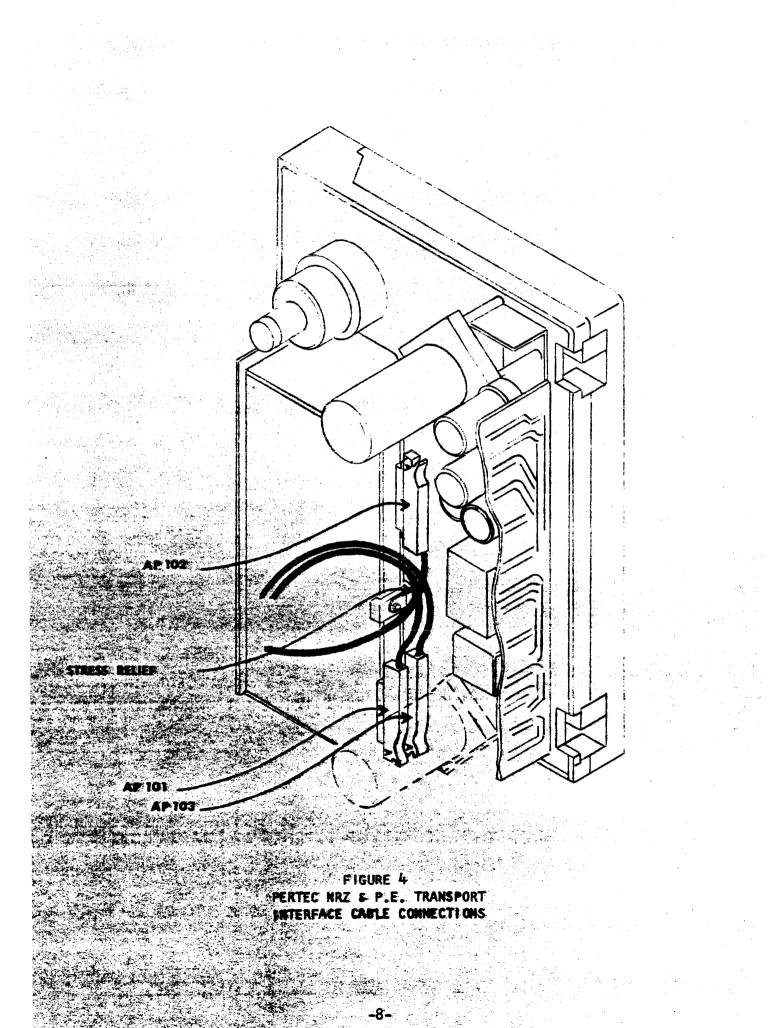

### 3 To PERTEC Units (Figure 4)

Connector AP10Z attaches to J10Z, the top connector on the innermost (Read/Write) circuit board. Make certain that the end of the

connector stamped "A" is toward the top of the tape unit, which means that the cable enters the connector from below.

Connector AP103 attaches to J103, the bottom connector on the 2. innermost (Read/Write) circuit board. Position the connector so that the end stamped "A" is closest to the bottom of the tape unit.

Connector AP101 attaches to J101, the bottom connector on the outermost (control) circuit board. Position the connector so that the end stamped "A" is closest to the bottom of the tape unit.

3.

der at a

FIGURE 2 WANG NRZ TRANSPORT INTERFACE CABLE CONNECTIONS

### SECTION I

### GENERAL DESCRIPTION AND SPECIFICATIONS

### 1.1 FUNCTIONAL DESCRIPTION

The DATUM NRZI Formatter provides for writing and reading IBM or USASCII compatible 9 track 800 BPI and/or 7 track 800/556/200 BPI magnetic tapes.

The NRZI Formatter provides a simplified computer oriented interface to minimize the task of interfacing to a digital computer. All major operations are performed automatically under control of the Formatter.

Individual selection and operation with up to four "Daisy Chained" tape transports is provided.

The transports can be a mixture of 7 and 9 track, any two tape speeds, Read/Write (single stack head) or Read-After-Write (dual stack head) configurations.

Tape transport motion control, CRCC and LRCC generation, and checking, LRCC checking, inter-record gap generation and status reporting are included. All write clocks and delay times are derived from a crystal controlled oscillator. No "one shots" or RC delays are utilized.

The NRZI Formatter is provided with a selection capability such that two formatters (NRZI or 1600 CPI phase encoded) can be "Daisy Chained" to one computer adaptor. This feature provides the capability of mixing 9 track 1600 CPI phase encoded, 9 track 800 BPI and 7 track 800/556/200 BPI tape units or providing up to eight tape units via one computer adaptor.

Card space and excess +5V power is available for computer adaptor (may be wire-wrapped) in the Formatter.

"On the Fly" operation (continuous read or write at maximum tape speed without stopping in each inter-record gap) is provided.

Writes the IBM compatible file mark (7 or 9 track formats) and recognizes file marks.

Provides for the "Edit" feature (allows a record anywhere on a previously recorded tape to be replaced with an updated record).

<u>No</u> calibration or adjustment potentiometers in the Formatter. All timing derived from crystal oscillator.

Compatible to entire 12.5 to 75 ips tape speed range without even changing crystals. Single field changeable jumper selects the frequencies needed for the tape speed.

Special low threshold data recovery feature provided for.

Controls and indicator lamps are provided to allow:

- Switchable assignment of any tape unit number (0, 1, 2 or 3) to any of the four tape units.

- 2. Lamp indication of Formatter selection

- 3. Lamp indication of tape unit selection

- Lamp indication of high or low density selection (7 track tape units only)

- 5. Lamp indication of odd or even parity selection (7 track tape units only)

- Remote or Manual control over density and parity selection (7 track tape units only)

7. Power on/off.

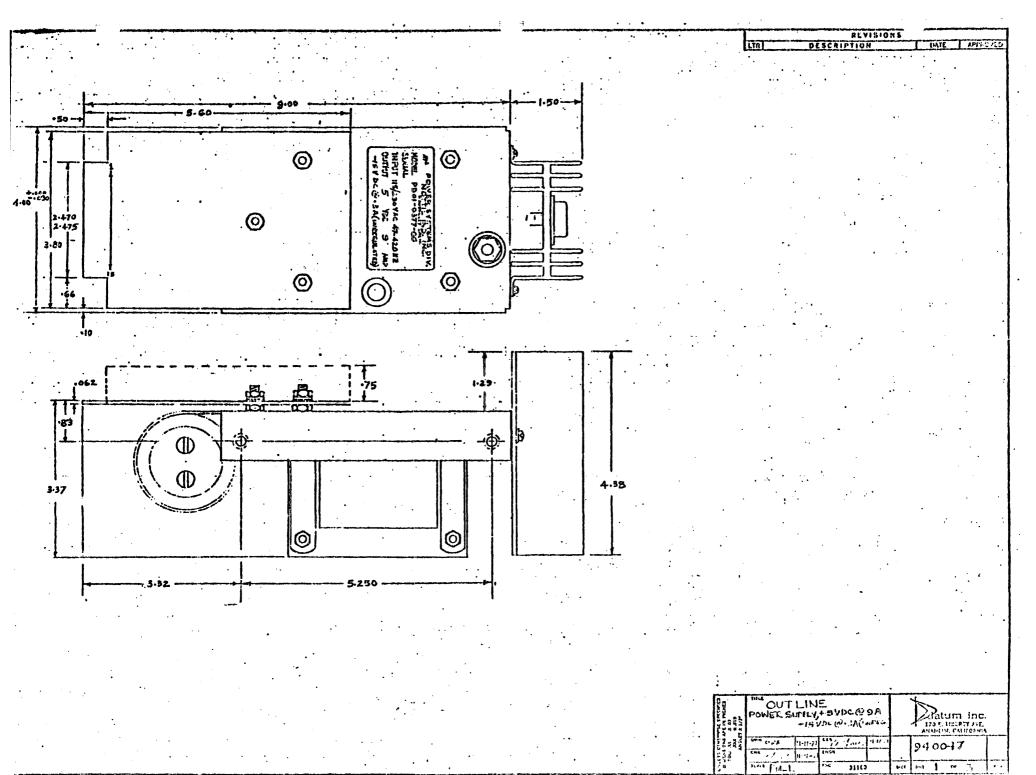

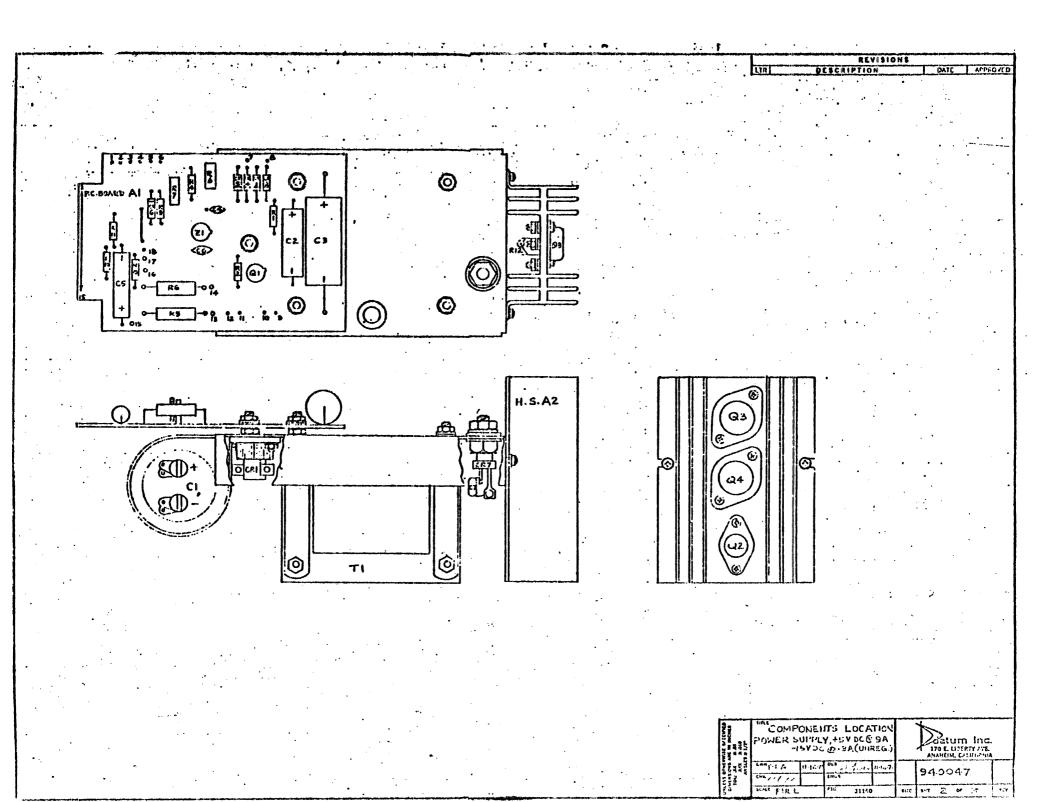

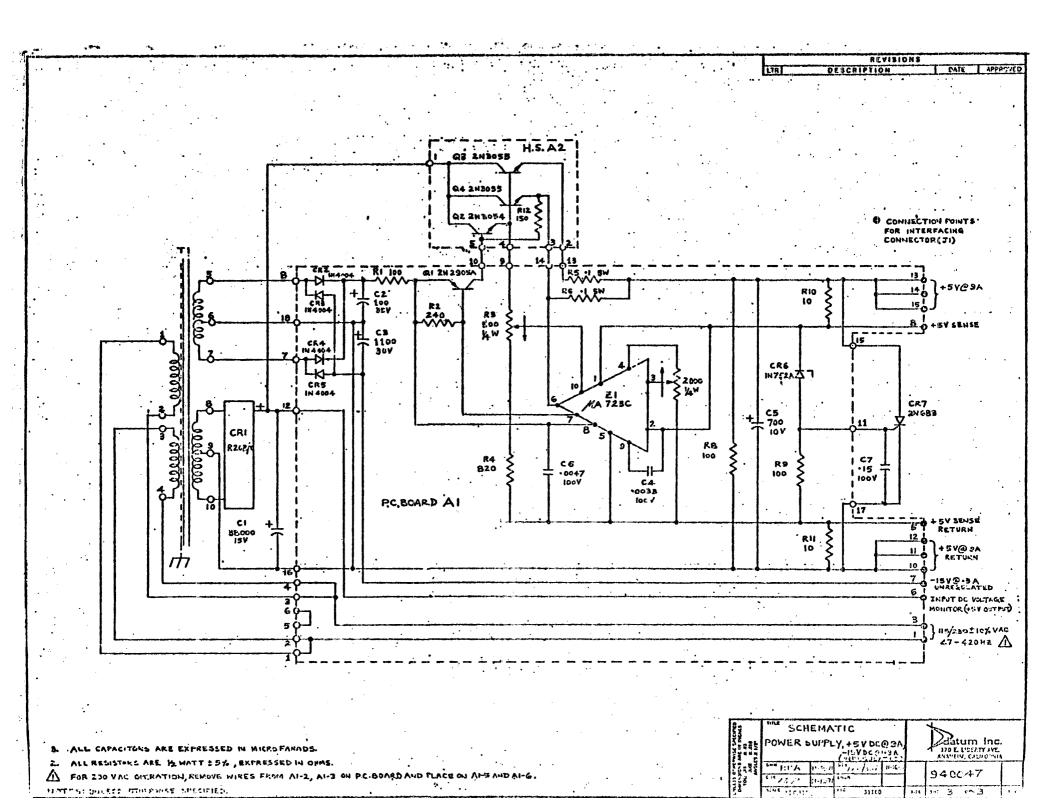

### 1.2 PHYSICAL DESCRIPTION

The DATUM Model 5091 NRZI Formatter is designed to be mounted in a standard 19" EIA rack. The Formatter has 5.25" front panel height and is 21" deep (allow 2" more for 1/0 cable service loop).

Top and bottom covers may be easily removed for access to integrated circuits.

Input/output cable connections are made at the rear of the . Formatter utilizing printed circuit edge connectors into which printed circuit cable termination cards can be plugged.

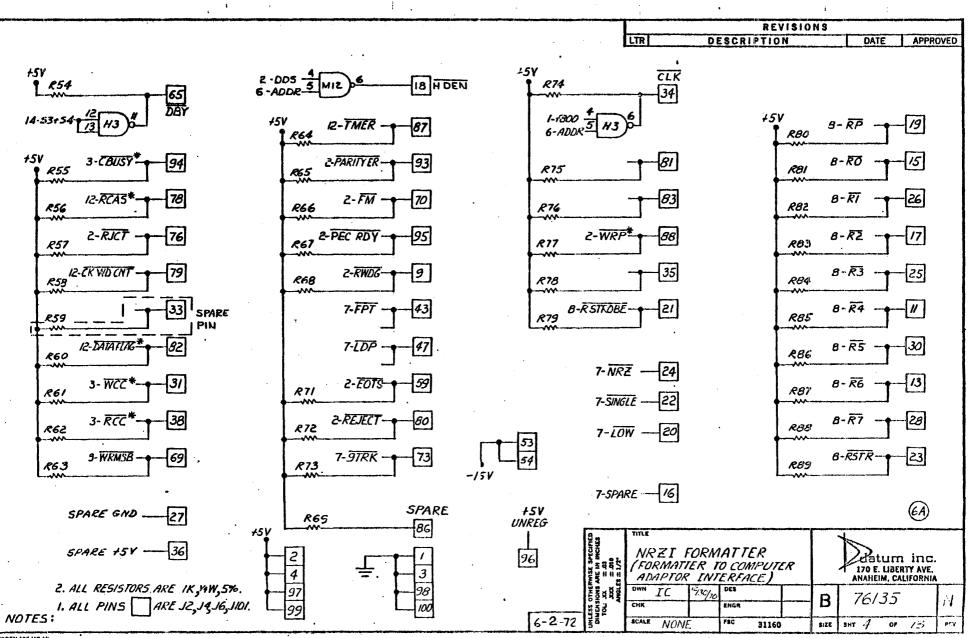

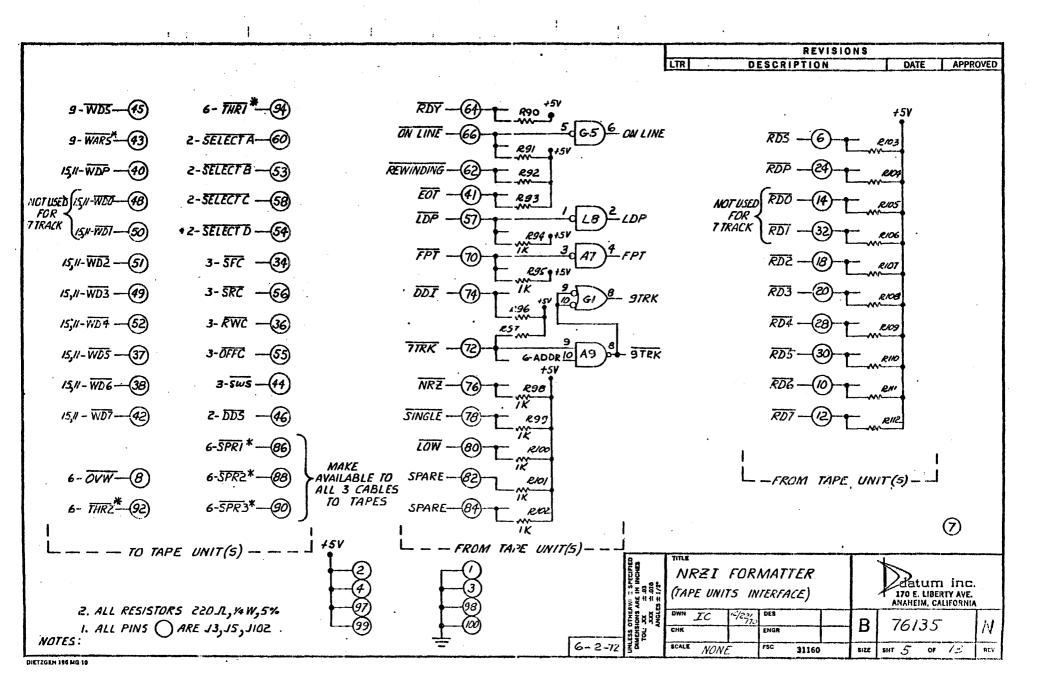

Figure 1-1 illustrates the connectors for interfacing the NRZI Formatter to an external or an internal computer adaptor and to the tape units. There is room for a third card to plug into the basic chassis to allow for the 1600 CPI Formatter which requires two card slots.

### 1.3 CONTROLS AND INDICATORS

The Front Panel controls and indicators are illustrated in Figure 1-2.

Figure 1-1. Rear View Formatter Connectors

.

ц Ч POWER The power switch controls main power to the Formatter.

FORMATTER SELECT Lamp indicates when the computer has selected the Formatter.

UNIT SELECT The four slide switches allow any unit number (0, 1, 2, 3) to be assigned to any physical tape unit (tape unit A, B, C, or D). Only <u>one</u> tape unit should be assigned to a particular unit number.

UNIT SELECT INDICATOR LAMPS Indicate which tape unit is selected.

MODE Allows selection of density and parity for 7 track tape units to be under computer control (REMOTE) or under operator switch selectable control (MANUAL).

DENSITY When the Formatter is in MANUAL MODE, the DENSITY switch controls the write/read density for 7 track tape units. 7 track tape units can be any <u>pair</u> of densities selected from 800/556/200 bits per inch. HI position selects the higher density of the pair, LOW selects the lower density of the pair. The indicator lamps give visual indication of the selected density whether under REMOTE or MANUAL control. The lamps are dark for 9 track tape units.

PARITY When the Formatter is in MANUAL MODE, the PARITY switch controls the selection of ODD or EVEN character parity for 7 track tape units. The indicator lamps indicate the selected parity whether under REMOTE or MANUAL control. The lamps are dark for 9 track tape units.

Inter-record gap (7 track)

inter-record gap (9 track)

Dimensions

Weight Mounting

Power

Circuits Operating Temperature Storage Temperature Altitude Relative Humidity Interface Voltages (DTL 900 series or TTL 7400 series compatible)

.75 inch nominal (.69 inch minimum) .6 inch nominal (.54 inch minimum) Height - 5.25 inches Width - 19 inches Depth - 21 inches 25 pound maximum Standard 19" EIA Rack 115 VAC ±10% 230 VAC ±10% 160 watts maximum 48-400 Hz frequency All silicon 0°to 50°C  $-40^{\circ}$  to  $+70^{\circ}C$ 0 to 20,000 feet 10 to 95% (non-condensing)

$1ow = 0V \pm .4V$ high = 3.9V ± 1.5V

The interface is designed such that an open circuit is interpreted as a "high" signal.

Figure 1-3 illustrates the configuration for which the interface has been designed.

### 1.5 MAGNETIC TAPE FORMATS

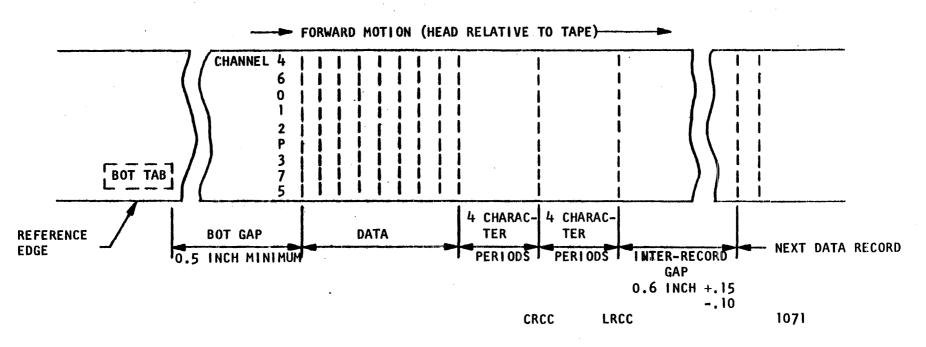

Figures 1-4 and 1-5 illustrate the IBM and USASCII magnetic tape formats for 7 track and 9 track tapes respectively.

\$

Figure 1-3. Interface Circuits

NOTES

- 1. TAPE SHOWN WITH OXIDE SIDE UP.

- 2. CHANNELS 2 THROUGH 7 CONTAIN DATA BITS IN DESCENDING ORDER OF SIGNIFICANCE.

- 3. CHANNEL P (PARITY) CONTAINS ODD DATA PARITY FOR BINARY TAPES, OR EVEN PARITY FOR BCD TAPES.

- 4. EACH BIT OF THE LRCC IS SUCH THAT THE TOTAL NUMBER OF "1" BITS IN THAT TRACK (INCLUDING THE LRCC) IS EVEN. IT IS POSSIBLE IN THE 7-TRACK FORMAT FOR THIS CHARACTER TO BE ALL ZEROES, IN WHICH CASE A READ DATA STROBE WILL NOT BE GENERATED.

- 5. A FILE MARK IS A SINGLE CHARACTER RECORD HAVING "1" BITS IN CHANNELS 4, 5, 6 AND 7 FOR BOTH THE DATA CHARACTER AND THE LRCC. THE FILE MARK IS SEPARATED BY NORMAL IRG'S (.75 INCH) FROM THE PREVIOUS AND FOLLOWING RECORDS. OPTION-ALLY, A 3.5 INCH GAP CAN BE ERASED PRIOR TO WRITING THE FILE MARK.

- 6. DATA PACKING DENSITY MAY BE 200, 556, or 800 BITS PER INCH.

NOTES

- 1. TAPE SHOWN WITH OXIDE SIDE UP.

- 2. CHANNELS O THROUGH 7 CONTAIN DATA BITS IN DESCENDING ORDER OF SIGNIFICANCE.

- 3. CHANNEL P (PARITY) ALWAYS CONTAINS ODD DATA PARITY.

- 4. EACH BIT OF THE LRCC IS SUCH THAT THE TOTAL NUMBER OF "1" BITS IN THAT TRACK (INCLUDING THE CRCC AND THE LRCC) IS EVEN. IN THE 9-TRACK FORMAT THE LRCC WILL NEVER BE AN ALL-ZEROES CHARACTER.

- 5. IT IS POSSIBLE FOR THIS CRCC CHARACTER TO BE ALL ZEROES, IN WHICH CASE A READ DATA STROBE WILL NOT BE GENERATED.

- 6. A FILE MARK IS A SINGLE CHARACTER RECORD HAVING "1" BITS IN CHANNELS 3, 6, AND 7 FOR BOTH THE DATA CHARACTER AND THE LRCC. THE CRCC CONTAINS ALL ZEROES. THE FILE MARK IS SEPARATED BY NORMAL IRG'S (.6 INCH) FROM THE PREVIOUS AND FOLLOWING RECORDS. OPTIONALLY, A 3.5 INCH GAP CAN BE ERASED PRIOR TO WRITING A FILE MARK.

Figure 1-5. 9-Track Format

### SECTION II

### INTERFACE

### 2.1 INTRODUCTION

There are two interfaces to the Formatter, one to the computer adaptor (J101 for external adaptor or J2 for internal adaptor) and one to the tape units (J102). (See Figure 1-1, page 1-4.)