# United States Patent [19]

Squires et al.

# [54] DISK DRIVE SYSTEM CONTROLLER ARCHITECTURE UTILIZING EMBEDDED REAL-TIME DIAGNOSTIC MONITOR

- [75] Inventors: John P. Squires, Jamestown; Thomas A. Fiers, Longmont; Louis J. Shrinkle, Boulder, all of Colo.

- [73] Assignee: Conner Peripherals, Inc., San Jose, Calif.

- [21] Appl. No.: 423,719

- [22] Filed: Oct. 18, 1989

# **Related U.S. Application Data**

- [63] Continuation of Ser. No. 58,289, Jun. 2, 1987, abandoned.

- [51] Int. Cl.<sup>5</sup> ..... G11B 17/00

# [56] References Cited

#### U.S. PATENT DOCUMENTS

| 4,700,243 | 10/1987 | Tsuyuguchi | 360/69 |

|-----------|---------|------------|--------|

| 4,717,971 | 1/1988  | Sawyer     | 360/69 |

# [11] Patent Number: 4,979,055 [45] Date of Patent: Dec. 18, 1990

Primary Examiner—A. J. Heinz Attorney, Agent, or Firm—Fliesler, Dubb, Meyer & Lovejoy

# [57] ABSTRACT

A disk drive control architecture provides for the storage and retrieval of data with respect to a rotating media and for the transfer of data with respect to a host in response to host commands. The control architecture provides for the execution of a plurality of background processes for controlling the spin speed of the rotating media, controlling the positioning of the sensor and controlling the reading and writing of data with respect to the rotating media. The control architecture further provides for foreground processes for controlling the background processes. The foreground processes include an interface task, for coordinating the background processes in the execution of host commands and a monitor task integral to the interface task such that the monitor task is capable of implementing diagnostic commands capable of accessing all of the resources of the control architecture. The transfer of diagnostic commands and resultant diagnostic information may be directed through a dedicated data communications channel separate from the data channel used for the transfer of commands and data with respect to the host.

# 14 Claims, 17 Drawing Sheets

FIGURE I

U.S. Patent

Sheet 4 of 17

FIGURE 4

FIGURE 5

4,979,055

U.S. Patent Dec. 18, 1990 Sheet 7 of 17 4,979,055 FIGURE 7

Dec. 18, 1990

4,979,055

FIGURE IIb

FIGURE IIc

FIGURE 12

4,979,055

.

-

5

#### 1

# DISK DRIVE SYSTEM CONTROLLER ARCHITECTURE UTILIZING EMBEDDED **REAL-TIME DIAGNOSTIC MONITOR**

This application a continuation of Ser. No. 058,289, filed June 2, 1987, now abandoned.

# CROSS-REFERENCE TO RELATED APPLICATIONS

The present application is related to the following Applications, all assigned to the Assignee of the present Application:

1. Disk Drive System Controller Architecture, invented by J. P. Squires et al, application Ser. No. 15 057,289, filed June 2, 1987;

2. Disk Drive Software System Architecture, invented by J. P. Squires, application Ser. No. 057,806, filed June 2, 1987;

3. Actuator for Disk Drive, invented by F. M. Ste-  $^{20}$ fansky, application Ser. No. 056,602, filed May 29, 1987;

4. Latch Mechanism for Disk Drives, invented by F. M. Stefansky et al, application Ser. No. 056,142, filed May 29, 1987;

5. Disk Drive Architecture, invented by F. M. Ste-<sup>25</sup> fansky et al, application Ser. No. 056,584; filed May 29, 1987.

6. Method and Apparatus for Brushless DC Motor Speed Control, invented by J. P. Squires et al, applica-30 tion Ser. No. 880,754; filed July 1, 1986.

#### FIELD OF THE INVENTION

The present invention is generally related to rotating media type data storage devices and, in particular, to an 35 efficient manner of implementing an integral monitor and diagnostic function in a software controlled secondary mass data storage device typically employing rotating magnetic media for the storage and retrieval of data.

#### BACKGROUND OF THE INVENTION

There has been and continues to be an ever-increasing demand for secondary mass storage peripherals capable of storing ever greater amounts of data in machine-readable form. This desire is coupled to a need to concur- 45 rently decrease the average time required to access any particular stored data. In addition, there is the commercial necessity to also reduce the costs associated with such secondary mass data storage devices.

disk drive type data storage peripherals have been made to generally satisfy, albeit temporarily, the aforementioned desires. The principal gains in total data storage capability come from improvements in the achievement of linear recording bit densities in excess of 14,000 flux 55 changes per inch and track densities of greater than 1,000 per inch. Some gains in the reduction of average access times have come from mechanical improvements in the actuator arm design and construction. Some measurable gains have also been achieved through the utili- 60 execution of host commands, and a monitor task intezation of dedicated electronic controllers to manage actuator seek operation and thereby yield a net reduction in the average access time. This use of dedicated hardware is often extended to provide dedicated control of the spin motor rate of rotation and the closed 65 agnostic information is through a dedicated data comloop actuator control needed to precisely follow a single track. This extended use of dedicated electronic control hardware is generally encouraged since it

broadly reduces the cost of manufacture and assembly of disk drives.

Unfortunately, the use of dedicated electronic hardware architecturally reduces the design, initial setup and long term operative flexibility of the disk drive. Unique trimming or tailoring of the electronic and mechanical components of a disk drive, particularly with respect to one another, is sacrificed for the low cost mass producibility of the dedicated electronic control 10 hardware.

The use of non-dedicated electronic hardware in place of dedicated hardware also raises problems. The coordination of multiple active processors in real time is difficult and the multiplicity of hardware, both the processors and the coordinating control logic, is expensive. Alternately, the utilization of a single active processor in place of the dedicated hardware conventionally is avoided due the apparently necessary intricacy of the diverse control functions that must be performed, each in real time.

Another problem with the use of dedicated hardware arises from the difficulty of testing and monitoring the dynamic operation of the disk drive system. In-depth testing is normally performed as part of final assembly quality control. The throughput of drive manufacture is limited by the length and complexity of such testing and the availability of dedicated testing stations. In addition, such testing is often desirable for monitoring the live operation of the drive system and for evaluating the cause of any premature failure. The use of dedicated testing hardware usually means that the drive must be removed from operation, thereby precluding live testing. In any case, potential drive faults must be diagnosed systematically again through the use of external testing hardware.

# SUMMARY OF THE INVENTION

A purpose of the present invention is therefore to 40 realize a highly flexible disk drive control system utilizing a single active processor that, by the architectural design of its embedded, real-time software, permits a high degree of self-testing and monitoring of operating conditions, both for initial quality control burn-in and during the live operation of the system.

This is achieved in the present invention by the use of a control architecture that provides for the storage and retrieval of data with respect to a rotating media and for the transfer of data with respect to a host in response to Advances in the development of conventional hard- 50 host commands, wherein the data is read and written by a sensor with respect to the rotating media. The control architecture includes a plurality of background processes for controlling the spin speed of the rotating media, the positioning of the sensor and the reading and writing of data with respect to the rotating media. The control architecture further provides for a forground process for controlling the transfer of data with respect to the host. The forground process includes an interface task, for coordinating the background processes in the gral to the interface task such that the monitor task is capable of implementing diagnostic commands having access to all of the resources of the control architecture. The transfer of diagnostic commands and resultant dimunications channel separate from the data channel used for the transfer of commands and data with respect to the host.

Thus, an advantage of the present invention is that the monitor is integral and embedded in the actual operational hardware, thereby requiring a minimal amount of external diagnostic hardware to perform quality control analysis. In addition, the embedded nature of the 5 monitor task allows a complete examination and analysis of the conditions and parameter values of the control architecture in managing mechanical and electromechanical hardware of the drive system during operation.

Another advantage of the present invention is that 10 the unique operating characteristics of the control system in operating the mechanical and electromechanical hardware can be displayed for evaluation and the corresponding optimal operational parameters then stored with respect to the individual unit. 15

A further advantage of the present invention is that the embedded monitor is capable of detecting dynamic and sporatically occurring exception conditions in real time and storing the corresponding operational parameters and other data relating to specific exception condi- 20 tions for subsequent display and analysis.

# BRIEF DESCRIPTION OF THE DRAWINGS

These and other attendant advantages and features of the present invention will become apparent and readily 25 appreciated as the same becomes better understood by reference to the following detailed description of the invention when considered in conjunction with the accompanying drawings, in which like reference numerals designate like parts throughout the figures 30 thereof, and wherein:

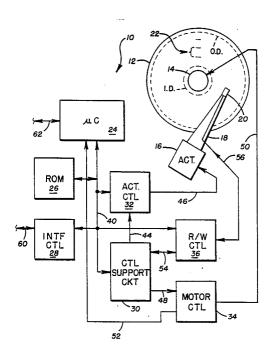

FIG. 1 is a simplified block diagram of the control system and its relationship to the actuator and rotating media in accordance with a preferred embodiment of the present invention;

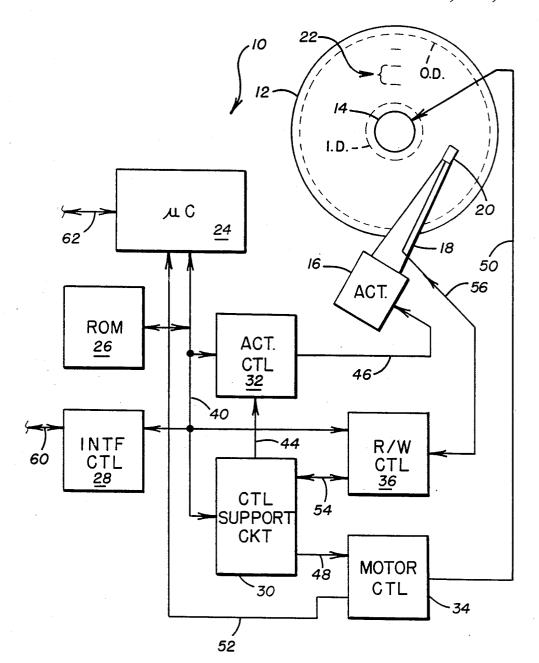

FIGS. 2*a*-*e* present a diagrammatic explosion of the format and constituency of a track sector in accordance with a preferred embodiment of the present invention;

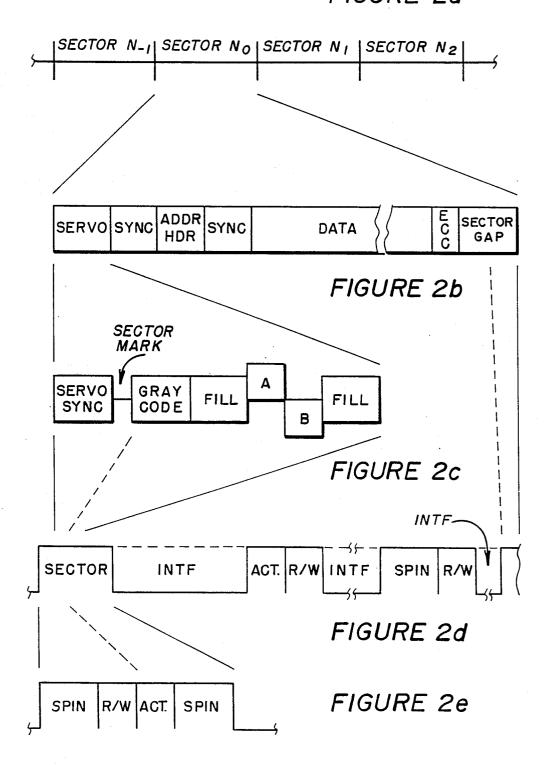

FIG. 3 provides a block diagram of the microcontroller and system support digital sections of the control 40 system of the present invention;

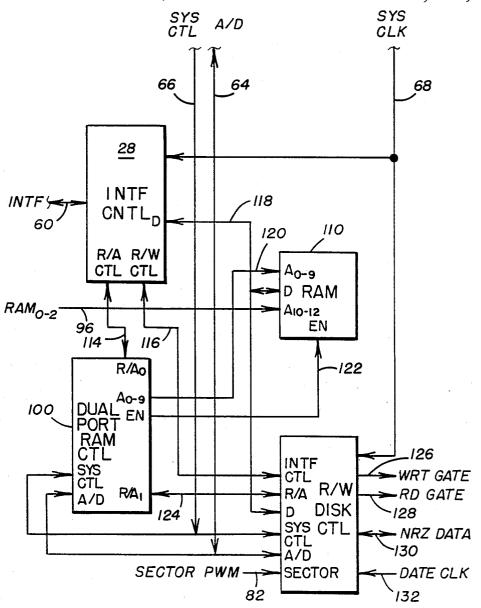

FIG. 4 provides a block diagram of the interface and digital control and data buffering section of the read/-write controller of the present invention;

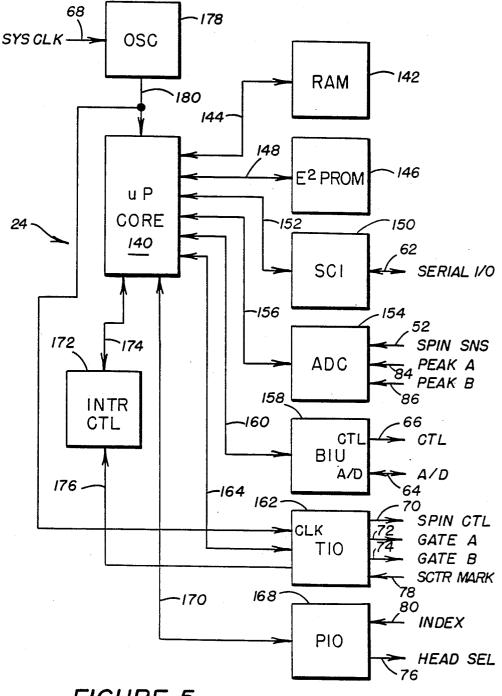

FIG. 5 is a detailed block diagram of the microcon- 45 toller preferred for use in conjunction with the present invention;

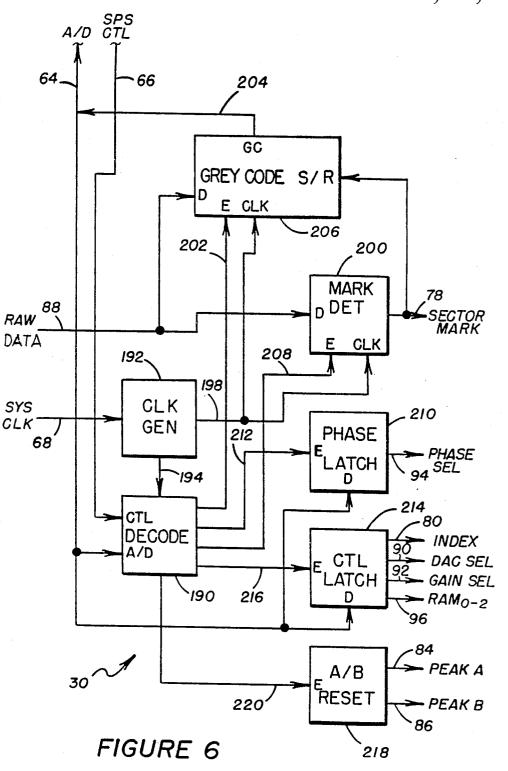

FIG. 6 is a detailed block diagram of the general system support digital hardware as implemented for a preferred embodiment of the present invention; 50

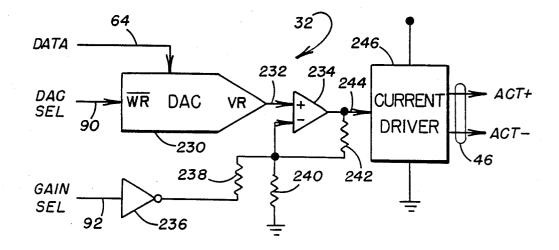

FIG. 7 is a schematic block diagram of a digital to analog converter/current driver circuit for controlling and adjusting the position of the actuator in accordance with the present invention;

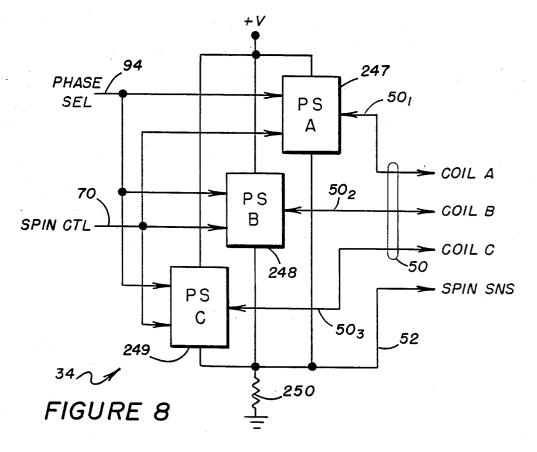

FIG. 8 is a block diagram of the motor control circuit 55 utilized to select and adjust the rotational position of the rotating media in accordance with the present invention;

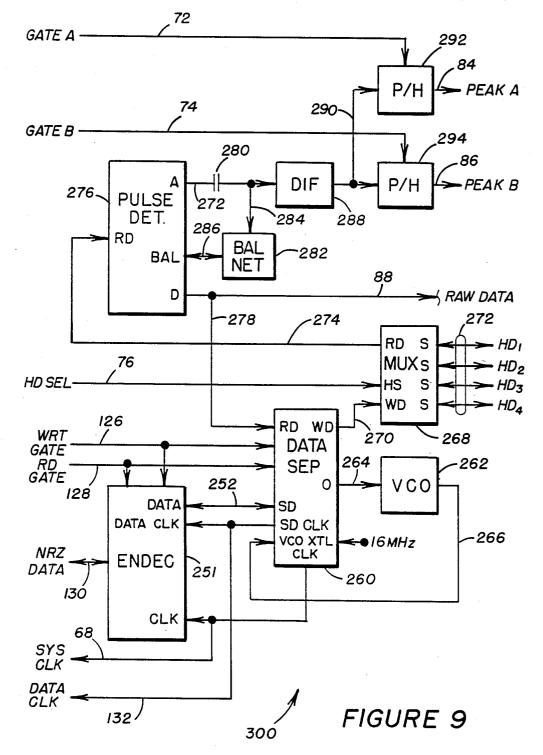

FIG. 9 is a detailed block diagram of the data channel circuitry utilized in a preferred embodiment of the pres- 60 ent invention;

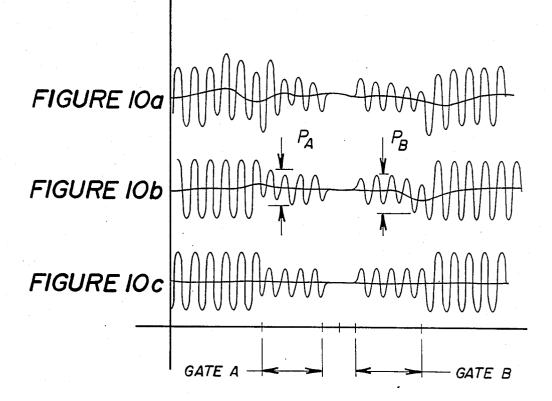

FIGS. 10*a-c* are successively processed raw data waveforms associated with an A/B burst;

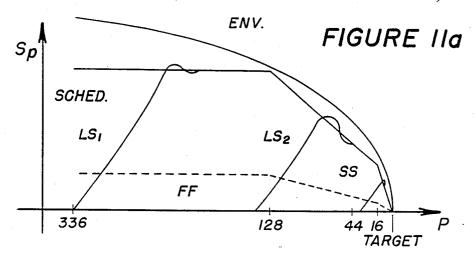

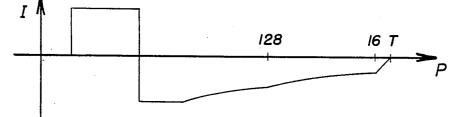

FIG. 11*a* is a diagram of position versus speed illustrating three separate actuator seek operations; 65

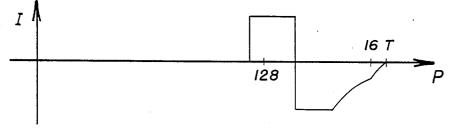

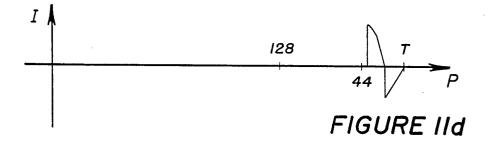

FIGS. 11b-d are diagrams of actuator current versus time for the respective seek operations illustrated in FIG. 11a;

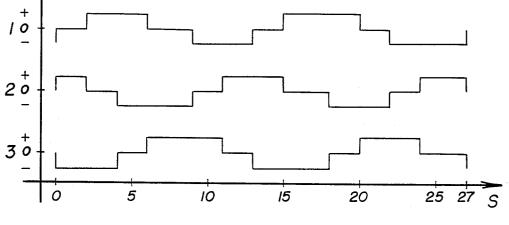

FIG. 12 is a timing diagram illustrating the commutation of a three-phase DC motor utilized to drive the rotating media in a preferred embodiment of the present invention;

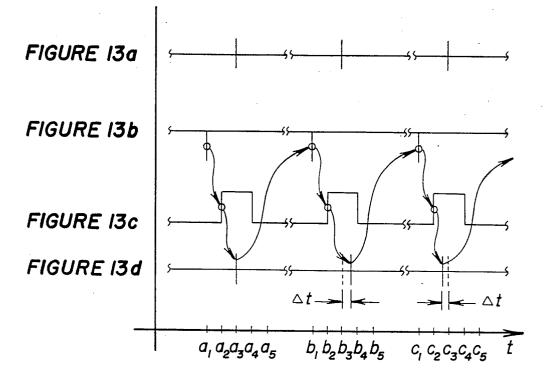

FIGS. 13*a*-*d* are diagrams illustrating the relation between the spin commutation period and the rotational speed of the rotating media in accordance with the present invention;

Another advantage of the present invention is that 10 e unique operating characteristics of the control sysm in operating the mechanical and electromechanical

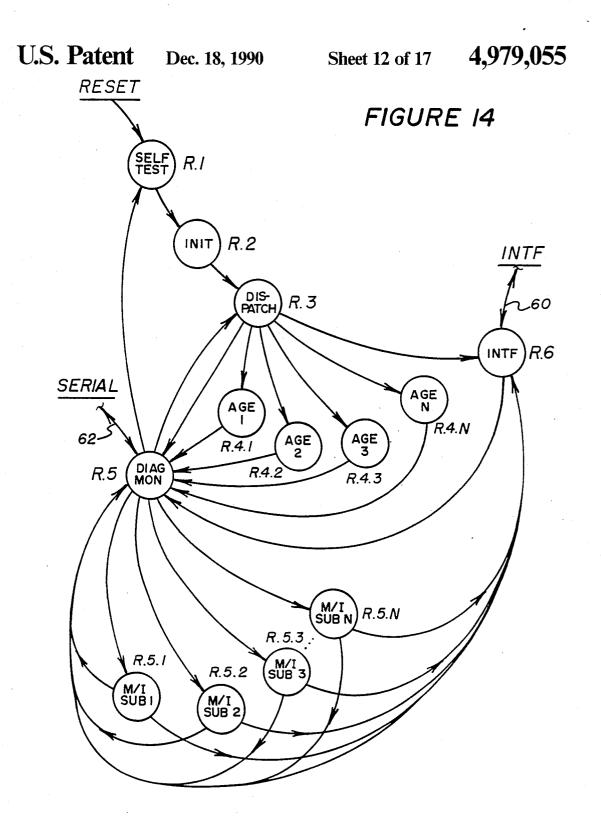

> FIG. 15 a software transition diagram illustrating an enhanced data exchange structure for exchanging data between a foreground interface and diagnostic monitor task and a number of background tasks as implemented in a preferred embodiment of the present invention;

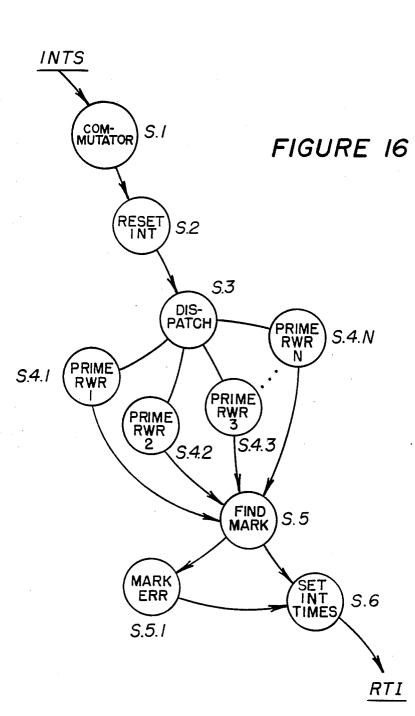

FIG. 16 is a software transition diagram illustrating the process control flow of a sector background task;

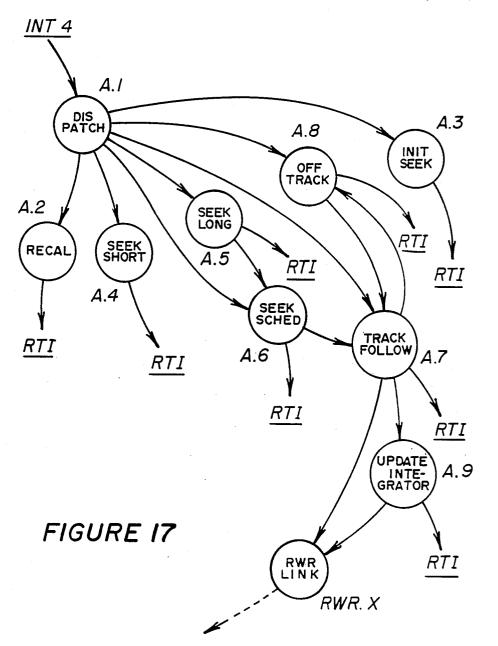

FIG. 17 is a software transition diagram illustrating the process control flow of an actuator control background task;

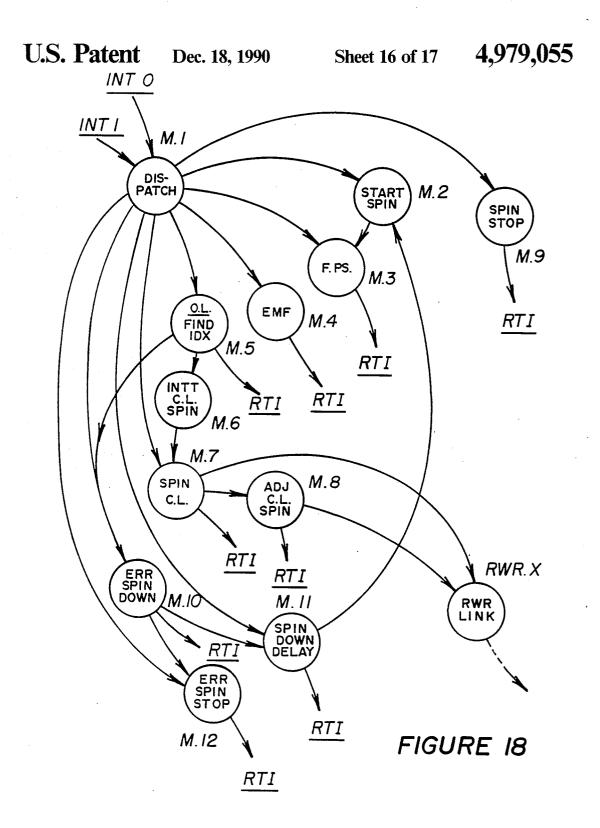

FIG. 18 is a software transition diagram illustrating the process control flow of a spin motor speed control background task; and

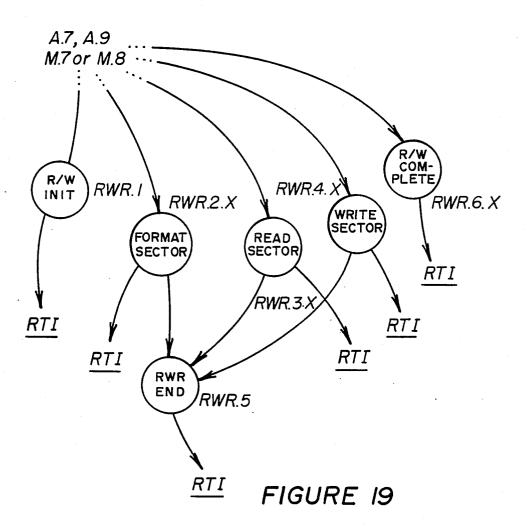

FIG. 19 is a software transition diagram illustrating the process control flow of a read/write background task.

# DETAILED DESCRIPTION OF THE INVENTION

# I. System Overview

A disk drive system controller, generally indicated by 35 the reference numeral 10 and having a system control architecture consistent with the principals of the present invention, is shown in FIG. 1. The preferred embodiments of the present invention utilize the system controller 10 to operate a rotating data storage media, such as a plated magnetic disk 12, driven by a DC, commutatorless spin motor 14, and to control an actuator 16 for the proper positioning of an arm 18 and one or more heads 20 so that data may be written to or read from a selected concentric track provided on the magnetic surface of the disk 12 for the storage of data. The mechanical structure, mechanical support and electromechanical operation of the rotating media 12, DC spin motor 14 and actuator assembly 16, 18, 20 is described in detail in the related applications Disk Drive Architecture, Actuator for Disk Drive and Latch Mechanism for Disk Drives noted above as related applications. These applications and the subject matter contained therein are hereby incorporated by reference. The distinctive mechanical and electromechanical aspects of the preferred embodiments of the present invention are the use of an essentially flat baseplate for the mounting of spin motor and actuator assemblies. The baseplate is flexibly attached to a faceplate. A cover encloses the baseplate and assemblies and is sealed to the faceplate. The spin motor assembly includes the spin motor 14 and one or more hard disk plates as the rotating media 12. The hard disk plates employ a plated magnetic layer on a 95 millimeter diameter substrate (a so-called 3.5 inch disk) to record concentric data tracks on both disk surfaces having, in alternate embodiments, 27 and 33 sectors per track to obtain data rates of eight and ten megabits per second, respectively at a disk spin speed of 3600 revolutions per minute. Each track sector is formatted

to provide embedded servo information and a data storage capacity of 512 bytes of data. All of the disk surfaces are available for the recording of data due to the use of the embedded servo information. Using two to eight surfaces, formatted data storage capacities of 20 to 5 over 100 megabytes can be readily achieved within a 3.5 inch, half-height form factor. Finally, due to the minimum rotating mass, and therefore reduced bearing friction, an efficient actuator voice coil driver and the minimal system controller electronics, the total power disa-10 pation of the preferred embodiments is less than about 7.7 watts, and more typically about 5 watts.

The system controller 10, in the preferred embodiments of the present invention, performs all of the essential support processes necessary to permit an external 15 host, typically a data processing system (not shown), to store and retrieve data from the rotating media 12. The central component of the system controller 10 is a microcontroller 24. In the preferred embodiments of the present invention, the microcontroller 24 is realized as a 20 Motorola MC68HC11 HCMOS single chip microcomputer. This particular microcontroller 24 is described in the Motorola Semiconductor Technical Data Book for the MC68HC11A8 HCMOS single chip Microcomputer Technical Data Book (ADI 1207) available from 25 Motorola, Incorporated, Motorola Literature Distribution, P. 0 Box 20912, Phoenix, Ariz. 85036. A read only memory (ROM) 26, coupled to the microcontroller 24 by an address, data and control bus 40, is utilized to store a control program for the microcontroller 24. As 30 will be described in greater detail below, this control program provides for the support of five principal tasks by the microcontroller 24. These tasks include interface, actuator, spin motor, read/write and monitor. An interface controller 28 is provided to support the mi- 35 crocontroller 24 in carrying out the interface task. The interface controller 28, in a preferred embodiment of the present invention, is an Adaptec AIC-500 Small Computer System Interface (SCSI) interface controller chip as manufactured and distributed by Adaptec, In- 40 corporated and described in the AIC-500 SCSI Interface Controller Data Sheet number 50000X-00 available from Adaptec, Incorporated, 580 Cottonwood Drive, Milpitas, Calif. 95035. The interface controller 28, in general, is required to provide the hardware interface 45 capability to support a communications bus 60 for the transfer of commands and data between the system controller 10 and the external host.

Hardware support of the actuator task of the microcontroller 24 is provided by the actuator controller 50 32. Directed by the microcontroller 24 through the provision of control signals and data via the address data and control bus 40, the actuator controller 32 drives the electromagnetic positioning voice coil of the actuator 16 by the selection of an appropriate voice coil 55 current drive level provided to the actuator by lines 46. The spin motor task is supported in hardware by the motor controller 34. A preferred motor control circuit and the principles of its operation are disclosed in Method and Apparatus for Brushless DC Motor Speed 60 Control, J. P. Squires, et al, Serial Number 880,754, filed July 1, 1986, and is expressly incorporated by reference. In brief, the motor controller 34 provides for the generation of the multiphase DC motor commutation signals to the DC spin motor 14 via the motor 65 winding drive lines 50. An analog feedback signal (SPIN SNS) is provided via line 52 to the microcontroller 24.

Finally, the read/write task is supported in hardware by a read/write controller 36. The principal functions of the read/write controller 36 are data buffering, encoding/decoding serialization, deserialization and data clock recovery. Serialized data is transferred to and from the read/write heads 20 of the actuator assembly 16, 18, 20 via data lines 56. The read/write controller 36 is controlled by and exchanges parallel data with the microcontroller 24 via the address, data and control bus 40.

Additional hardware support for the actuator controller 32, motor controller 34 and read/write controller 36 is provided by a control support circuit 30. The functions of the controller support circuit 30 are generally to process sector servo bursts and to provide latched control signals to the actuator, spin motor and read/write controllers 32, 34, 36 via control lines 44, 48, 54.

#### II. Sector-Data Storage Overview

Consistent with conventional disk drive data storage schemes, data is stored on the rotating media 12 of the present invention on concentric tracks centered about the spin axis of the media. Where there are multiple media surfaces for the recordation of data, data cylinders are defined as consisting of those tracks having a common spin radius. The tracks themselves are divided into track sectors defined as lying within a fixed radial arc. A portion of a single track is diagramed in FIG. 2a as a linear series of sectors. A single sector, N<sub>0</sub>, is exploded in FIG. 2b as generally indicated by the solid lines between the Figures to show its principal constituent data fields. In order, each sector, consistent with the present invention, is composed of a servo burst followed by a synchronization, or sync, field, a sector address header field, another sync field, a data field providing for the storage of typically 512 data bytes, and an error correction code (ECC) field. The ECC field is typically followed by an intersector gap extending to the beginning of the next sector's servo burst field.

The servo burst field of FIG. 2b is shown exploded into its constituent parts in FIG. 2c. as generally indicated by the solid lines between the Figures The initial field is a servo sync field that serves to allow the microcontroller 24 to generally synchronize itself, in realtime, to the servo burst field. Sector mark and grey code fields then follow in succession. The sector mark field is defined as a complete absence of servo data followed by a data transition. In the preferred embodiments of the present invention, the sector mark is represented as the first transition following the absence of any servo data for at least three servo sync clock cycles. By timing the period between detected sector marks, the rotational speed of the media 12 can be gauged quite accurately. The grey code field that immediately follows the sector mark is an FM encoded digital value representing the track or cylinder number of the sector currently under a head 20.

After a filler field, A/B Burst fields are provided. As diagrammatically shown, the A/B Burst fields are nonoverlapping and are physically written on the media 12 offset from the center line of the track. In the preferred embodiment of the present invention, the A/B Burst fields are both written utilizing a constant frequency and head voltage amplitude. This permits any difference in the relative head voltage amplitude upon each subsequent reading of the respective A/B Bursts to be

5

utilized as an indicator of the position of the head 20 relative to the center line of the track. Finally, a filler sync field completes the servo burst field.

# III. Microcontroller Software Architecture Overview

The control program provided in the ROM 26 enables the microcontroller 24 to support the complex and diverse processes of actuator control, spin motor control, read/write control and interface control, all in real time. The software architecture of the control program 10 establishes the interface process as a foreground, or nominally executing, task. The execution of the interface task requires the microcontroller 24 to support the interface controller 28 in the performance of commands received from the external host and in the coordination 15 of data transfers between the interface and read/write controllers 28, 36. The actuator, spin motor and read/write processes are supported as background tasks of nominally equal priority as between one another and higher priority with respect to the foreground interface 20 task. The nominally equal priority of the background tasks is achieved by scheduling the execution of each of the tasks throughout the rotational period of each sector or sector period as generally shown in FIG. 2d as generally indicated by the solid lines between the Figures 25 Where the actual sector period is not available, such as when the rotating media 12 is stopped or not rotating at full speed, a default sector period is used. A sector task, composed of subtasks including spin motor, read/write, and actuator tasks is initiated during the sector gap prior 30 to the beginning of the servo burst of each sector as generally indicated by the dashed lines between the FIGS. 2b and 2d. The subtasks of the sector task include commutating the spin motor 14, recognizing any new or pending messages from the interface process, and 35 signal (SPIN SNS) via line 52 at an input of an internal scheduling the initiation of actuator, spin motor and read/write process tasks during the current sector period as generally indicated by the dashed lines between the FIGS. 2b and 2d. In preferred embodiments of the present invention, the actuator task is initiated by set- 40 ting a timed interrupt to occur at about one-eighth of the duration of the sector period from the beginning of the current sector. At about the midpoint of the sector period, a second timed interrupt is set to occur to initiate the spin motor task. Finally, a timed interrupt to 45 reinitiate the sector task will be set to occur during the sector gap at the end of the current sector period. The timing of this last timed interrupt is chosen to control the spin motor. Depending on whether there is a new or pending read/write operation requested by the inter- 50 face task, either or both of the actuator and spin motor tasks will chain, in the preferred embodiments of the present invention, directly to the read/write task to perform any required read/write operation. The sector and read/write tasks, and the actuator and spin motor 55 tasks if they do not chain respectively to the read/write task, will each end by the execution of a return-frominterrupt microcontroller instruction that will restore the interrupted foreground interface task to active execution. Consequently, essentially all of the available 60 microcontroller processing capability is utilized in the performance of the processes necessary to implement the essential functions of the system controller 10. There is no execution time wasted in the performance of task scheduling operations or other overhead functions 65 as is typically required in conventional multi-tasking computer systems. Rather, the present invention achieves real time responsive, multi-tasking operation

through time-based task scheduling of the sector, actuator, spin motor and read/write processes.

#### IV. Digital System Controller

Referring now to FIG. 3, the microcontroller 24 supports a multiplexed address and data bus 64 and a control bus 66 as its principal means of communicating to the various higher level components of the system controller 10. The buses 64, 66 also permit the microcontroller 24 to obtain its control program instructions and initialization data from the ROM 26. A system clock signal (SYS CLK) nominally running at 16 megahertz, is provided on a clock line 68. In order to monitor and control various other elements of the control system 10, the microcontroller 24 sources a spin control signal (SPIN CTL) via line 70 to the motor controller 34, Gate A and B signals on lines 72, 74 to enable the detection of the A/B Burst, and head selection signals via line 76 to select a specific one of the potentially multiple, typically four, read/write heads 20 for use in a current read or write operation. The microcontroller 24 will receive a sector mark signal via line 78 from the control support circuit 30 when a sector mark is physically detected from the rotating media 12. On recognition of a proper sector mark, the microcontroller 24 will source a read/write timing signal (Sector PWM), via line 82, to synchronize the read/write controller 36 with the current sector. If the sector for which the current sector mark is determined to be the index sector of the current track, the microcontroller 24 will provide an index signal via line 80 from the controller support circuit 30 for the duration of the current index sector period.

The microcontroller 24 receives the analog spin sense analog-to-digital converter within the microcontroller 24. The spin sense signal is a voltage feedback signal indicative of a motor winding characteristic, such as current, provided by the motor controller 34. Other analog inputs of the internal analog to digital converter receive analog Peak A and Peak B signals via lines 84, 86. The Peak A and Peak B signals are indicative of the respective A and B burst amplitudes read from the A/B Burst Fields of the current sector.

The controller support circuit 30 is principally provided to perform low-level, high-speed functions that could not be conveniently performed directly by the microcontroller 24. These high-speed functions include detecting the occurrence of a sector mark and capturing the grey code value read from the grey code field of the current sector. Otherwise, the controller support circuit 30 operates as a simple latched output port expander for the microcontroller 24. The sector mark and grey code capture functions are driven by raw, clock separated data received from the read/write controller 36. The controller support circuit 30, functioning as a latched output port for the microcontroller 24, provides actuator enable and actuator gain select signals, via lines 90, 92 to the actuator controller 32. Similarly, commutation phase select signals are provided, via line 94, to the motor controller 34 and ram bank select signals, via lines 96, are provided to the read/write controller 36.

The interface controller 28 and the control and data buffering portion of the read/write controller 36 are shown in FIG. 4. The dual port ram controller 100 and the read/write disk controller 112 are preferably the Adaptec AIC-300 Dual Port Buffer Controller and the Adaptec AIC-010 Winchester Controller Chips, both

5

also available from Adaptec, Incorporated. The buffer function itself is performed by a random access memory (RAM) device 110. In the preferred embodiments of the present invention, the RAM 110 is a static 64 kilobit, single CMOS memory chip organized as 8K by 8 bit.

The interface controller 28 implements at least the common core of the high-level SCSI protocols, thereby permitting the host to communicate with the system controller via a standard SCSI bus. Alternately, the interface controller 28 may implement the buffering 10 control logic necessary to permit connection to a conventional "AT" type peripheral interface connector.

The disk controller 112 implements the control logic needed to support a low-level data channel circuit 300 (shown and described below with respect to FIG. 9) 15 that completes the read/write controller 36. Read and Write Gate signals, enabled in timed response to the receipt of the sector PWM signal from the microcontroller 24, are provided via lines 126, 128 to enable respective raw data read and write operations. Non- 20 return-to-zero (NRZ) data is bidirectionally exchanged with the data channel circuit 300 via data line 130. A data direction sensitive data clock signal (DATA CLK) is provided to the disk controller 112 via a data clock line 132. This data clock signal, as generated by the data 25 channel circuit 300, is specifically synchronized to the raw data as read or written with respect to the rotating media 12.

The dual port RAM controller 100 coordinates all memory accesses of the RAM 110. Requests for RAM 30 access are placed by the interface controller 28 via the request/acknowledge (R/A<sub>0</sub>) control lines 114 and by the disk controller 112 via the separate request/acknowledge  $(R/A_1)$  control lines 124 to the dual port RAM controller 100. Data transfers between the inter- 35 elements of the microcontroller 24. Central to the miface controller 28, the RAM 110 and the disk controller 112 occur over a dedicated data bus 118. RAM addresses and transfer enable control signals are generated by the dual port RAM controller 100 and provided to the RAM 110 via the address lines 120 and the enable 40 control lines 122. High-order RAM addresses, acting as memory bank select signals, are provided to the RAM 110 from the controller support circuit 30 via address lines 96. All accesses by the microcontroller 24 to the RAM 110 are through the disk controller 112.

The primary flows of data occurring ultimately between the external host and read/write heads 20 are buffered through the RAM 110. Typically, a command or request for the transfer of data will be placed by the external host to the interface controller 28 via the inter- 50 face bus 60. The interface controller 28, performing the necessary hardware and software protocol handshaking to receive the command request, will place a formatted command request in a reserved portion of the RAM buffer 110. If data is being provided by the external 55 host, the interface controller 28 will also provide for the transfer and storage of the received data into a buffer section of the RAM 110. The disk controller 112 is alerted to the presence of the pending command request by the interface controller 28 by the read/write control 60 lines 116. The microcontroller 24 may monitor the state of the read/write control lines 116 by periodically interrogating an internal register of the disk controller 112 via the control and address data buses 66, 64.

To implement a pending command/request, the mi- 65 crocontroller 24 will access the RAM 110 via the disk controller 112 and dual port controller 110 to determine the nature of the command and whether the command

may be honored. If honorable, the microcontroller 24 implements the command by programming and enabling the disk controller 112. If the command involves data provided by the external host to be transferred to the rotating media 12, the disk controller 112 is programmed by the microcontroller 24 as to the storage destination of the data and the quantity of data transfer. The disk controller 112 then obtains the data directly from the RAM 110, serializes the data and ultimately provides the data to the data channel circuit 248 via the NRZ data line 130.

If, however, the command request placed by the external host is for the transfer of the data from the rotating media 12, the microcontroller 24, again in response to the formatted command placed by the interface controller 28 in the RAM 110, will program the disk controller 112 to obtain the requested information from the sectors of the rotating media 12 specified by the command. When enabled, the disk controller will receive the data via the NRZ data line 130 and transfer the data into the buffer section of the RAM 110. On completion of the data transfer, or some unit portion thereof, the disk controller 112 will notify the interface controller 28 of the availability of the requested data by a signal placed via the read/write control lines 116. The interface controller 28 will then initiate the hardware handshaking or software protocol signalling necessary to alert the external host of the availability of the requested data. On acknowledgement by the host, the interface controller 2, will transfer the buffered data from the RAM 110 to the interface bus 60.

#### A. The Microcontroller

FIG. 5 provides a detailed block diagram of the sub crocontroller 24 is a microprocessor core component 140 that implements the standard functions of a conventional microcomputer, such as the Motorola 6800 family of microcomputers. The microprocessor core 140 is, however, extended to support its various on-chip peripheral devices. These peripheral devices include a 256 byte block of RAM memory 142 selectable as a source or destination of data by the microprocessor core 140 via control lines 144. An electrically erasable program-45 mable read-only memory (EEPROM) 146, having a capacity of 512 bytes of data is accessible by the microprocessor core 140 for reading and writing (programming) via control lines 148. A serial communications interface (SCI) 150 is provided to support a standard asynchronous serial input/output bus 62 and thereby establish a communications route to and from the system controller 10 independent of the host interface bus 60. The aforementioned analog-to-digital conversion capability is realized as an analog-to-digital converter (ADC) 154 having an integral multiplexed input controlled by the microprocessor core 140 via control lines 156 to permit the separate receipt of the SPIN SNS, PEAK A and PEAK B analog signals via respective analog multiplexer input lines 52, 84, 86. A bus interface unit (BIU) 158, controlled from the microprocessor core 140 via control lines 160, is provided to support the multiplexed address and data bus 64 and to supply the system control signals in support thereof via the control bus 66. A timer input/output (TIO) unit 162, controlled by the microprocessor core 140 via control lines 164, provides a bank of digital timers. For purposes of the present invention, three such digital timers are utilized to provide for the programmatically timed generation of the spin control, GATE A and GATE B signals on line 70, 72, 74. A fourth counter of the TIO 162 receives the sector mark signal as generated by the controller support circuit 30 via lines 78 to permit the accurate timing of sector periods. A parallel input/output (PIO) 5 unit 168 is utilized as a latched output port to provide the head select signals via lines 76 and to receive, as an input, the index signal, indicating whether the current sector is the index sector of the current track. The function of the PIO 168 is controlled by the microprocessor core 140 via the control lines 170. The final programmatically controlled unit of the microcontroller 24 is an interrupt controller 172. The various counters of the TIO 162 generate respective interrupts when they reach a programmatically defined count value. These inter- 15 rupts are respectively directed to the interrupt controller 172 via interrupt lines 176. The microprocessor core 140 is immediately called via interrupt controller lines 174, to service the interrupting event as identified by the respective interrupt that occurs. Finally, an on-chip 20 oscillator 178 is provided to generate the internal timing signals required by the microprocessor core 140 and the TIO unit 162. The oscillator 178 receives the system clock signal via clock line 68 and, in turn, generates a microcontroller internal clock signal that is provided 25 via internal clock line 180. Although not shown, the microcontroller 24 communicates with each of its onchip addressable peripheral devices by way of an internal data bus.

# B. Controller Support Circuit

FIG. 6 provides a detailed block diagram of the minimal controller support hardware required by the present invention as realized in the controller support circuit 30. The microcontroller 24 programmatically ac- 35 cesses and controls the controller support circuit 30 via a decoder 190 coupled to the address and data and control buses 64, 66. A clock generator 192, driven by the system clock signal provided via clock line 68, synchronizes all operations of the decoder **190** by the pro- 40 vision of an internal clock signal via clock line 194 to the decoder 190. A sector mark detection circuit 200 is provided within the controller support circuit to perform the actual task of detecting the occurrence, in real time, of a sector mark. For this purpose, the mark detec- 45 tor circuit 200 receives the raw, clock separated, data signal provided from the low level data channel circuit 300 via the raw data input line 88 and a date clock counting signal from the clock generator 192 via clock line 198. The microcontroller 24 enables the mark de- 50 tector 200 by accessing the decoder 190 to provide a search enable signal on line 203 and thereby initiate the beginning of a mark search. The mark detector circuit 200 fundamentally implements a clocked serial shift register circuit to that provides a signal on finding three 55 B 84, 86. successive data clock periods where there are no corresponding raw data transitions. Immediately on detecting the occurrence of such a circumstance, the mark detection circuit generates a sector mark pulse that is provided to the microcontroller 24 via the sector mark 60 signal line 78. The mark detector circuit then goes inactive until enabled for the next sector mark search.

A grey code shift register is provided within the controller support circuit 30 to capture the grey code value as it is read from the grey code field. Generally, 65 the grey code shift register is enabled by the microcontroller 24 at the same time that it initiates a sector mark search operation. However, for purposes of flexibility,

the grey code shift register receives a separate enable signal from the decoder 190 via enable line 202. The grey code shift register 206 also receives the raw data from data line 88 and data clock signal from clock line 198 in parallel with the mark detector circuit 200. The grey code shift register 206 receives the sector mark signal from the mark detector circuit 200 to initiate with the very next clock period the acquisition of the raw data from the raw data line 88. Fundamentally, the grey code shift register implements a serial-to-parallel shift register function. The serial-to-parallel conversion is halted sixteen data clock cycles after being enabled in response to the sector mark signal. That is, the grey code is realized as a two byte value identifying the current read/write cylinder. In the preferred embodiments, only 10 bits of the grey code are utilized, with successive cylinders being assigned grey code values successively differing by only one bit. The two bytes of the grey code value are then available on the grey code parallel output bus 204 to the address/data bus 64 in response to respective output enable control signals from the decoder 190 via control lines 202. Thus, the controller support circuit performs the mark detection and grey code acquisition operation substantially unattended by the microcontroller 24, though requiring a minimum of hardware.

A phase latch 210 is provided in the controller support circuit 30 to support the spin motor controller 34. The phase latch 210 functions essentially as a digital 30 latch for storing the phase winding value corresponding to the particular phase windings to be currently selected by the spin motor controller 34. The phase latch receives the phase value from the data bus portion of the address in data bus 64 on receipt of an enable signal 35 from the decoder 190 via an enable control line 212. The latched phase value is then immediately provided on the phase selection output lines 48.

A digital control signal latch 214 is similarly provided to support the actuator and read/write controllers 32, 36. A control word is written to the control signal latch 214 via the data bus portion of the address and data bus 64. The control word is latched by the control signal latch 214 on receipt of a latch enable signal from the decoder 190 via control line 216. The respective bits of the control word stored by the control signal latch are provided onto the index, actuator DAC select, gain select and RAM bank select control lines 80, 90, 92, 96.

Finally, an A/B reset circuit 218 is provided generally in support of the read/write controller 36. The A/B reset circuit 218 implements unlatched, open collector drivers that operate in response to a control signal from the decoder 190 via the control line 220. The outputs of the open collectors of the A/B reset circuit 218 are coupled to the analog signal lines PEAK A and PEAK B 84, 86.

#### V. Actuator Controller

The actuator controller 32 is shown in FIG. 7 in block diagram form. As disclosed in the above-identified application, Actuator for Disk Drive, the preferred actuator for use in conjunction with the present invention utilizes a voice coil driver permitting continuous selection of the pivotal position of the actuator arm 18 and heads 20. In the preferred embodiments of the present invention, the actuator controller 32 utilizes an eight-bit latched-input digital-to-analog converter 230 to generate an analog voltage value proportional to the desired actuator position. The latched inputs of the digital-to-analog converter 230 are enabled and then latched in response to the actuator DAC select signal as provided on the DAC select line 90. A digital output value, as determined by the microcontroller 24, is provided via the data bus portion of the address/data bus 5 64 to the digital-to-analog converter 230 for latching and conversion. The resulting analog output signal is provided via the DAC output line 232 to the plus input of an operational amplifier 234 configured by the connection of resistors 240, 242 as a non-inverting amplifier 10 having a gain value of approximately 2. The output of the operational amplifier 234 is provided via line 244 to a voltage following current driver circuit 246. Differential output lines 46 from the current driver 246 are connected to the two terminals of the actuator voice coil. 15 The current driver 246 provides for a differential current on the lines 46 proportional to the voltage value at the output of the operational amplifier 234.

Since, in the preferred embodiment of the present invention, the data bus portion of the address/data bus 20 64 has a width of 8 bits, the resolution range of the digital-to-analog converter 230 and, therefore the current driver 246, is limited to 256. However, the actuator controller 32 is required to support two substantially different actuator related operations. These operations 25 270 2,7 RLL Encoder/Decoder available from Adapare seeking and track following. The seeking operation involves rapidly moving the heads 20 from one track of the rotating media 12 to a substantially different track. Seeking over any extended number of tracks optimally requires the application of very large current values to 30 the actuator voice coil to minimize the total seek time. Conversely, the track following operation ideally involves very minute changes in the voice coil current as needed to closely follow a single track. Accordingly, the microcontroller 24 providing the gain select signal 35 to the actuator controller 32 via gain select line 92 to alter, preferably by a factor of 4, the total range of obtainable voice coil currents. The gain select signal is provided to a open collector buffer 236 connected through a resistor 238 to the negative input of the opera- 40 tional amplifier 234. Consequently, the microcontroller 24 is capable of directly altering the gain factor of the operational amplifier 234 between fixed gain factors with a concurrent realization of a proportional increase in the range of selectable current values.

#### VI. Spin Motor Controller

Referring now to FIG. 8, a block diagram of the motor controller 34 is shown. In the preferred embodiment of the present invention, the motor 14 is a DC 50 three phase commutatorless motor. The three commutation nodes of the phase coils, designated as nodes a, b, c, are driven by respective phase switches 247, 248, 249. The phase switches 247, 248, 249 are selectable to operate either as a current source, drawing current from a 55 positive voltage supply, or as a current sink, with the current load being passed through the reference resistor 250. The voltage value of the SPIN SNS signal on line 52 is, therefore, directly proportional to the motor winding current level passing through the reference 60 resistor 250. The phase select signal as provided by the phase latch 210 via the phase select control lines 94 determines whether the respective phase switches 247, 248, 249 are sourcing current, sinking current or set to a high output-impedance state on their output lines 501, 65 502, 503. The switches 247, 248, 249 also receive the spin control signal, in common, via control line 70. The spin control signal either enables the phase switches 247,

248, 249 to be responsive to the phase select value provided on the phase select lines 94 or to be commonly disabled such that they each present a high outputimpedance to the nodes a, b, c via coil winding lines  $50_1$ , 50<sub>2</sub>, 50<sub>3</sub>.

VII. Read/Write Controller Data Channel Circuit

The low level data channel circuit 300, as shown in FIG. 9, supports the bidirectional transfer of data to and from the individual heads 20 of the actuator sub-assembly 16, 18, 20. In brief, the write data path for data being written to the rotating media is through an ENDEC 251 where the serial data is encoded, to a data separator 260 where the encoded data is combined with the data clock signal, and finally to a multiplexor 268 for routing to a specific head 20.

Similarly, the read data path begins with data, originating from a specific one of the heads, being selected for transfer to a pulse detector 276 for initial wave form shaping, to the data separator 260 for extraction of the read data clock signal and finally back to the ENDEC 251 for decoding back into NRZ data before being provided to the disk controller 112.

In greater detail, the ENDEC (preferably an AICtec, Inc.) is responsive to the write and read gate signals generated by the disk controller 112 and provided via the control lines 126, 128. On receipt of the write gate signal, the ENDEC 251 begins converting NRZ data received from the disk controller 112 via NRZ data line 130 to a 2,7 RLL data format. The encoded data is then provided to the data separator 260. The data separator utilized in the preferred embodiments of the present invention is a conventionally constructed application specific integrated circuit (ASIC) utilizing the macro function libraries of Ferranti, Inc. 1500 Green Hills Rd., Scotts Valley, Cailf. 95066 as described in Ferranti ULA, Design Manual, R series, Document A/F102 issue 1.003, April 1989. The data separator 260 and the voltage controlled oscillator (VCO) 262, together, are functionally equivalent to the National Semiconductor NS8462 Data Separator and a conventional crystal controlled clock generator. The VCO 262 is preferably a discrete component voltage controlled oscillator, 45 utilizing a charge pump to convert the input digital clock stream to a VCO control level, of conventional design. The use of a discrete component VCO design was chosen over the use of the VCO internal to the NS8462 to permit a perceived greater control over the VCO's jitter tolerance specification. Another reason for chosing to use the ASIC data separator 260 was that it allowed precompensation to be used; pre-compensation is a conventional feature of disk drive data separators that is not available with the NS8462. Finally, the use of the ASIC ASIC data separator 262 allows a conventional 16 MHz crystal controlled clock generator to be placed on-chip. Since the NS8462 does not itself provide a clock generator function, an external, though conventional, clock generator would be needed.

The data separator 260 drives a 16 megahertz crystal to generate a controlled clock signal that is provided to the ENDEC 251 and the control system 10 in general via the system clock line system 68. The data separator 260 also provides the same system clock signal to its separated data (SD) clock line output and onto the data clock lines 132 in response to the write gate signal. The data separator 260 receives both the write and read gate signals via control lines 126, 128. The data clock signal

is used by the ENDEC 251 as the basis for clocking encoded data from the ENDEC 251 to the data separator via the data line 252. The encoded data from the ENDEC 251 is combined with the data clock signal and provided to the multiplexor 268 via the write data line 5 270. The multiplexor 268 also receives the head select control signals provided by the microcontroller 24 on select lines 76. In response, the multiplexor 268 routes the write data from the data separator 260 to a head select value corresponding one of the head data lines 10 272.

The reading of data from the rotating media 12 must serve two different but related purposes. The first, naturally, is reading the servo burst information from the beginning of every sector independent of whether a 15 read write, or other data operation is to occur. The reading of a servo burst is largely controlled by the microcontroller 24. Again responsive to the head select value provided on the head select control lines 76, the multiplexor 268 routes data read from a specific head 20 20 and its corresponding head data line 272 to the multiplexor read data output line 274. The multiplexor 268, in addition to performing its signal multiplexor function, further performs as a conventional pre-amplifier for the data received from any of the head data lines 272. The 25 amplified read data is then received by the pulse detector 276 (preferably a National Semiconductor NS8464 Pulse Detector, manufactured and distributed by National Semiconductor Corporation 2900 Semiconductor Drive, Santa Clara, Calif. 90501 and described in the 30 Advanced Peripheral Processor Solution Handbook No.1: Mass Storage National Semiconductor, 1986). After further amplification, the read data is passed from an analog output, A, of the pulse detector 276 through a DC blocking capacitor 280, preferably having a value 35 of 0.01 microfarads, to a balanced network 282 via analog line 284. The balanced network 282, with the exception of the capacitor 280, is a conventional implementation of the required analog waveform shaping circuitry intended and suggested for use with the pulse detector 40 276. The shaped analog signal is provided back to the pulse detector via analog line 286 for further analog signal processing and ultimate conversion to a digital serial data stream. The processed, digital version of the read data is then provided onto the raw data output line 45 88 from the pulse detector 276. This raw data is utilized by the controller support circuit 30 for synchronization, detection of the sector mark and for the extraction of the grey code.

The analog data stream passed through the capacitor 50 280 is also provided to a differentiator 288 before being provided to peak detector and hold circuits (peak hold) 292, 294 via analog lines 290. The peak hold circuits 292, 294 provide for the capture of the peak analog value of the differentiated data signal as provided on 55 line 290. The peak hold circuits 292, 294 are respectively enabled by the Gate A and Gate B signals, as provided on the Gate A and B control lines 72, 74 by the microcontroller 24. Under the control of the microcontroller 24, the peak hold circuits 92 and 294 are 60 enabled for the respective durations of the A and B bursts. The resulting Peak A and Peak B analog signals are provided by the peak hold circuits 292, 294 on the Peak A and Peak B analog lines 84, 86 to the microcontroller 24. After conversion of the Peak A and Peak B 65 analog signals, the microcontroller 24 may clear the peak hold circuits 292, 294 by temporarily shorting their outputs to ground in response to the operation of the

A/B reset circuit 218 of the controller support circuit 30. Consequently, the analog peak value held by the peak hold circuits 292 and 294 will be reset to zero.

Referring now to FIG. 10a, an exemplary analog wave form as might be received from the pulse detector on analog output line 272 is shown. The particular section of the servo burst shown graphically illustrates an A/B burst. A portion of filler sync just prior to the A burst illustrates, by its peak variation, the occurrence of dropout. That is, as a result of variations in the raw analog data received by the pulse detector, the analog wave form may carry a fluctuation DC bias of sufficient magnitude that sync waveform peaks fail to surpass their intended minimum threshold values. A consequence of such an error is that the balanced network 282 will be improperly perturbed. This source of signal fluctuation may in turn lead to errors during the reading and of the A/B Bursts, as well as with respect to other fields including the address header and date fields. In accordance with the present invention, the capacitor 282 is introduced into the analog signal path at the analog output of the pulse detector 276 to effectively remove the DC bias and thereby suppress the occurrence of dropout.

FIG. 10b illustrates the same portion of the analog data stream as shown in FIG. 10a, but as DC filtered and present on the analog data line 284. The preferred embodiments of the present invention utilize extremely short A/B bursts in order to maximize the portion of the linear track length available for other purposes, specifically including the storage of data. Accordingly, the duration of the respective A and B burst fields is constrained to a nominal 4 microseconds as opposed to a more conventional 30 microseconds. A consequence of utilizing such a short A/B burst period is that a significant amount of baseline drift, arises as a result of the slew between the high amplitude filler sync signal and the much lesser amplitude of the A/B burst signal. By including a baseline drift perturbed portion of the burst signal within the Gate A and Gate B enabled peak hold periods, false peak amplitude values, generally corresponding to the peak amplitudes indicated as  $P_a$ ,  $P_b$ , will be captured by the peak hold circuits 292, 294 and ultimately received by the microcontroller 24. Since the A/B burst values are utilized to determine the relative position of the head with respect to the center line of the track, errors in measuring the A/B bursts will directly correspond to an increased data error rate due to mispositioning of the heads relative to a track center line.

The differentiator 288 is provided in the preferred embodiments of the present invention to reduce, if not eliminate, the effect of baseline drift on the peak capture accuracy of the peak hold circuits 292, 294. The differentiator 288 is realized as an emitter follower configured bipolar transistor in the analog signal path between the analog line 284 and the analog line 290. A single pole high-pass filter is coupled to the emitter terminal of the emitter follower to implement the differentiator function. In the preferred embodiments, the filler sync and A/B signal frequency is approximately 2 megahertz. The differentiator high-pass pole is placed at about 9 megahertz to provide an adequate degree of differentiation of the A/B burst analog signals. The resultant signal provided to the inputs of the A/B burst peak hold circuits 292, 294 is shown in FIG. 10c. As shown, the peaks of each cycle of the respective A/B bursts are essentially constant as a direct consequence of

the removal of any perturbing effect due to baseline drift.

Referring again to FIG. 9, the second principal read function performed by the data channel circuit 300 is to read data from the address header, data and ECC fields 5 of data sectors. In response to the read gate signal as provided from the disk controller 112 via read gate control line 128, the data separator 260 begins providing separated data and its corresponding synchronized data clock signal to the ENDEC 251. To support this, the 10 data separator 260 drives a voltage controlled oscillator (VCO) 262 with the error output of a phase lock loop synchronized to the digital raw data from line 278. The VCO output is fed back via line 266 to the data separator 260. The resultant data clock signal, effectively 15 where separated from the digital raw data and synchronized to the data being provided via line 252, is gated onto the data clock line 132. The ENDEC 251 receives the separated data and synchronized data clock signal and decodes the data to provide NRZ data to the disk control-<sup>20</sup> ler 112 via the NRZ data line 130.

#### VIII. Seek Algorithm

FIG. 11a depicts a speed versus position graphed 25 profile of three exemplary seek operations illustrating the principles of the seek operation of the present invention. An envelope curve (ENV.) defines the maximum rate of deceleration achievable by the mechanical actuator assembly 16, 18, 20 that will achieve a zero radial 30 speed of the head 20 at a target track T. The present invention provides for a succession of scheduled velocities that lie within the envelope for every given distance from the target track T. In the preferred embodiments of the present invention, the scheduled velocity is im- 35 plemented as a three part linear approximation of the envelope curve, having a constant scheduled maximum speed for all distances greater than 128 tracks. A second portion of the scheduled velocity tracks a steadily decreasing maximum speed down to a distance of 16 40 tracks away from the target track T. The third and final part of the scheduled velocity curve extends at a still steeper scheduled decrease in speed down to a scheduled speed of zero at the target track T. Since the scheduled velocity never exceeds the envelope velocity at 45 any distance from the target track T, following the scheduled velocity will tend to ideally maximize the portion of the seek operation where the heads 20 are moving at their highest speed toward the target track T, subject to being decelerated to arrive at the target track 50 T without overshoot.

The seek operation, for preferred embodiments of the present invention, is realized as an iterative process described as follows:

#### Seek Algorithm

$$O = K_{Sgain}(S_{schd} - (S_{ave} + S_{ff})) + I_t$$

Eq. 1

where

O is the digital value output to the actuator DAC K<sub>Seain</sub> is a seek gain constant S<sub>schd</sub> is the scheduled velocity

$$S_{ave} = \frac{S_a + S_f}{2}$$

where

$S_a$  is the calculated actual velocity of the current sector

Sr is the predicted velocity for the next sector and

$$S_f = S_a + kS_a$$

Eq. 3

where

$|\mathbf{k}|$  is a constant having a typical value of 0.5

k>O for acceleration

k<O for deceleration

k=O for zero acceleration

$$S_{ff} = K_{Fgain}(S_{schd})$$

Eq. 4

KFgain is a feed forward gain constant having a typical value of 0.25

$I_t$  is an integrator target track band value determined from the track follow algorithm

The actuator voice coil current versus position profile for a long seek  $(LS_1)$  operation is shown in FIG. 11b. On initiation of the seek, the gain select signal is provided to the actuator controller 32 to select the largest range of current values obtainable from the current driver 246. Initially, the calculated actual velocity  $S_a$  is zero, resulting in a large actuator DAC output value O. Assuming that a positive actuator voice coil current moves the heads 20 in the direction of the target track T, a maximum current output is selected to maximally accelerate the heads 20 in the direction of the target track T. Maximum acceleration is maintained until the current velocity  $S_{ave}$  plus a feed forward speed value Sff exceeds the current scheduled velocity. The current velocity is determined as the average of the last measured actual velocity  $S_a$  of the heads 20 and the predicted velocity  $S_f$  of the next velocity calculation. The control data for calculating the measured actual velocity is obtained by measuring the elapsed time between passage of a particular head 20 from one track to the next. The processing speed of the microcontroller 24 is sufficient to process servo bursts at even at maximum acceleration and velocity of the heads 20 across the tracks. Thus, both the grey code and A/B burst for every sector can be obtained and used to determine current position of the heads 20. By determining the elapsed time between passage over neighboring trackcenters the actual velocity of the heads 20 can be determined. However, since the heads 20 are being accelerated and the computation to determine actual velocity occurs sometime after a servo burst is processed, a predicted next calculated velocity, S<sub>f</sub>, is averaged with the calculated actual velocity, Sa. The result, Save, is therefore a close approximation to the current speed of the heads 20. As given by Equation 3, the predicted next 55 calculated velocity S<sub>f</sub> is determined as a simple function of the last calculated actual velocity, Sa.

Due to the increasing acceleration of the heads 20, the current speed,  $S_{ave}$ , plus the schedule dependent speed feed forward value, S<sub>ff</sub>, will rapidly approach and then exceed the scheduled velocity. Consequently, the 60 actuator voice coil current, determined as the product of a conversion gain constant (K<sub>Sgain</sub>) and the computed error velocity value, will reverse a negative maximum current value until the head velocity is braked to that of Eq. 2 65 approximately the scheduled velocity less the feed forward speed. The actuator output value, 0, and the corresponding actuator voice coil current will then tend toward a zero current as the head speed equalizes with the scheduled speed. Again, the velocity of the heads 20 is repeatedly calculated, in accordance with the seek algorithm, from the time difference between passing over adjacent track-centers as determined by the continuous processing of the sector servo bursts.

At a distance from the target track T of 128 tracks, a value chosen for the preferred embodiments of the present invention to permit a close approximation of the velocity envelope, the scheduled velocity linearly decreases as a function of distance from the target track. 10 Accordingly the actuator output value and voice coil current will be increased to increase braking of the head velocity to continue to equalize the speed of the heads 20 with the scheduled velocity. The feed forward speed value  $S_{ff}$  is also proportionately reduced between tracks 15 128 and 16. At track 16, the scheduled velocity falls off at a greater rate resulting in a greater rate of head braking with an ultimate decrease of the actuator output value 0 and the voice coil current toward zero.

As described by Equation 1, the final actuator output 20 value 0 and corresponding voice coil current at the target track T is not in fact zero. Rather the output value 0 is equal to an integrator constant It. Although the actuator assembly 16, 18, 20 is preferably a balanced arm unit, there are a number of unbalanced forces act- 25 ing on the arm 18 and heads 20. These forces include windage and the non-zero, nonuniform servo loop force physically exerted by the head data lines 56 and actuator voice coil power lines 46. In accordance with the preferred embodiments of the present invention, a table 30 of integrator values,  $I_t$ , is kept where each table entry corresponds to the actuator output value 0 corresponding to a voice coil current sufficient to maintain the heads 20 over a corresponding track within a respective band of tracks 22, as generally shown in FIG. 1. For the 35 and preferred embodiments of the present invention, each band of tracks 22 is composed of 64 consecutive tracks. While the respective table entry values of  $I_t$  will vary, the preferred embodiments of the present invention in implementing the long seek algorithm utilize through- 40 out the seek operation the table  $I_t$  value corresponding to the target track band to which the target track T belongs. While such use of the integrator values  $I_t$  is quite adequate, successive use of the integrator table  $I_t$ values could be made as the heads 20 pass over the 45 corresponding track-bands 22.

Figures 11c-d illustrate the voice coil current versus position profiles for a second long seek (LS<sub>2</sub>) and a short seek (SS). The seek operation illustrated by FIG. 11c closely parallels that of the long seek operation 50 illustrated in FIG. 11b with the exception that the position of the heads 20, at their velocity intersection with the scheduled velocity, is within the 16 to 128 track distance from the target T. Consequently, the initial velocity equilibrium established between the velocity 55 schedule and the speed of the heads 20 is at a constant braking deceleration until just 16 tracks from the target track T. The final deceleration curve to the target track T is then the same for both long seeks  $LS_1$ ,  $LS_2$ .

FIG. 11d illustrates the actuator voice coil current 60 versus position profile of a relatively short seek. For the preferred embodiments of the present invention, any seek operation for less than 45 tracks is considered a short seek. This arises from the fact that the acceleration curve for any seek of less than 45 tracks will result 65 in a head speed intersection with a scheduled velocity within the last 16 tracks from the target track T. Consequently, still in full accordance with Equation 1, maxi-

mum acceleration is initiated and the microcontroller immediately begins to determine whether the scheduled velocity has sufficiently approached the rapidly decreasing scheduled velocity to begin breaking to then match the head speed with the scheduled velocity.

Finally, for seeks of less than 3 tracks, the algorithm described by Equation 1 is not used in preference to simply pulsing the actuator current to achieve head motion in the direction of the desired target track T.

#### IX. Track Follow Algorithm

The preferred embodiments of the present invention implement a closed loop servo operation to maintain the currently selected one of the heads 20 in alignment with a corresponding track at all times other than when seeking. Central to this operation is a track following algorithm, defined as follows:

#### Track Follow Algorithm

$$=K_{Tgain}(P_0 - J_x P_{-1}) + I_t$$

Eq. 5

where

0:

$K_{Tgain}$  is a track follow gain constant where

$$K_{Tgain} = K_1(|A_0| > |B_0| \text{ and } |A_0| > |A_{-1}|) \text{ or } (|A_0| > |B_0| \text{ and } |B_0| > |B_{-1}|)$$

$$K_{Tgain} = K_2$$

where  $(|A_0| \ge |B_0| \text{ and } |A_0| \le |A_{-1}|)$

or  $(A_0| \le |B_0| \text{ and } |B_0| \le |B_{-1}|)$

P<sub>0</sub> is the current off-track distance error

$P_{-1}$  is the previous off-track distance error where the distance error  $P_m$  is

$$\mathbf{P}_m = |(A_M - B_m)| \qquad \qquad \text{Eq. 6}$$

$A_m$  is the A Burst peak value  $B_m$  is the B Burst peak value  $j_x$  is a constant where

$0 < j_x < 1$

$I_t$  is the integrator-current track-band value where the present value of  $I_t$  is periodically updated as

$$I_{t1} = I_{t0} + m(A_{t0} - B_{t0})$$

Eq. 7

where m is a constant greater than 0

The track follow servo information is contained within the servo burst of each sector as detailed in FIG. 2c. As defined by Equation 5, the output value 0 utilized to specify the actuator voice coil current level is proportional to the sum of a position error value and the current track-band corresponding integrator table value  $I_t$ . The position error of a head 20 with respect to the center line of a corresponding track is determined as the difference in the digital peak value of the A and B burst fields, as indicated by Equation 6. In accordance with the preferred embodiments of the present invention, a scaling factor  $j_x$  is utilized to adjust the weight of the previous offtrack distance error,  $P_{-1}$ . The scaling factor  $j_x$  must be less than or equal to one and greater than or equal to zero in order for the closed loop gain of the track follow servo to be stable. However, within this range, the value of  $j_x$  may be chosen to approach one to yield a slow correction of the track following position of the heads 20 or, for  $j_x$  approaching zero, a very fast correction based increasingly on the current off-track

error position. In the preferred embodiments of the present invention  $j_x$  is provided with a value of 0.75.

The position gain error factor  $K_{Tgain}$  is utilized in accordance with the present invention to significantly optimize the track follow servo operation. The value of 5 the  $K_{Tgain}$  factor is selected depending on whether the movement of the head 20 is currently toward or away from the center line of the track being followed. Where the head is moving away, the value of the  $K_{Tgain}$  factor is increased to a value greater than one. A correspond- 10 ing increase in the actuator output value 0 in the proper direction to reverse head movement back toward the center line of the track being followed is therefore achieved. Conversely, where the direction of movement of the head 20 is toward the center line of the track 15 being followed, the gain factor  $K_{Tgain}$  is reduced to unity or less to obtain a damped approach of the head toward the center-line of the track and thereby minimize the likelihood of track center line overshoot.

As used in the seek algorithm, the integrator value  $I_t$  20 is used to account for unbalanced forces acting on the actuator assembly 16, 18, 20. Accordingly, the integrator value  $I_t$  is summed to the gain modified position error value to produce the final actuator output value 0. However, the track-following algorithm, in accordance 25 with the present invention, provides for the dynamic updating of the integrator values Ir. Whenever a particular track-band corresponding value It is being used, it is updated during every sector period in the manner defined by Equation 7. A small fraction (preferably on the 30 order of 0.1) of the current off-track error, defined by the current A/B burst difference, is summed with the current track-band integrator value  $I_{t0}$  to produce a new value  $I_{t1}$  for subsequent use. While, in the preferred embodiments of the present invention, the dynamically 35 updated integrator table values are not subsequently stored back to the default integrator table maintained in the EEPROM 144 (though they could), any difference from their default values will be quickly recovered following the instigation of track following. 40

#### X. Spin Motor Speed Control Algorithm

The present invention provides, in its preferred embodiments, for the "at speed" closed loop control over the rotational speed of the rotating media 12. In order to 45 prevent any significant negative impact on the accurate reading and writing of data to the rotating media 12, commutation of the spin motor phase windings is selected to occur only during the intersector gaps. The three phase, three state commutation waveforms utilized in a preferred embodiment of the present invention are shown in FIG. 12. This preferred embodiment utilizes a 27 sector, and therefore 27 intersector gap, track format. The three shared nodes of the phase windings are driven by the spin motor controller 34 as being 55 sourced current (plus), being a source of current (negative), or neutral (0).

FIG. 13 provides a timing control diagram illustrating the manner of speed control utilized in the preferred embodiments of the present invention. FIG. 13*a* is a 60 simple line diagram showing the ideal timing of consecutive sector marks as they would occur during the revolution of the rotating media precisely at its ideal speed. The spin motor commutation is initiated for each sector during the immediately preceding intersector gap, as 65 indicated in FIG. 2*e* and generally indicated in the line diagram of FIG. 13*b*. Commutation of the spin motor 14, for example, at time A is followed at  $A_2$  with the

initiation of a search by the microcontroller 24 for the anticipated occurrence of a sector mark. The microcontroller 24 establishes a maximum timed period beginning at  $A_2$  and extending through  $A_4$  for the search for the sector mark. Ideally, the sector mark occurs at  $A_3$ , as generally shown in the line digram of FIG. 13*d*. AT  $A_3$  the sector mark search is terminated and the spin commutation period for the current sector is subsequently calculated. The calculation of the spin commutation period is achieved through an application. This search window is generally indicated by the line diagram of FIG. 3*c*. in accordance with the present invention, of a spin algorithm defined as follows:

#### Spin Algorithm

$$S_{cp} = k_{cp}(t_0 - t_{-1}) - t_{nom}) + I_{cp}$$

where

$S_{cp}$  is the spin commutation period  $k_{cp}$  is a spin gain constant to is the current measured sector time  $t_{-1}$  is the previously measured sector time  $t_{nom}$  is a constant  $I_{cp}$  is a spin integrator value where

Ideal  $S_{cp} = I_{cp}$  Eq. 9

and where  $I_{cp}$  is updated periodically as

$$I_{cp1} = I_{cp0} - i$$

where  $t_0 > t_{-1}$

$Icpl = I_{cp0} + i$  where  $t_0 < t_{-1}$

$I_{cpl} = I_{cp0}$  where  $t_0 = t_{-1}$

where i is a small fraction of  $I_{cp}$ , preferably on the order of 1/256

The object of the spin algorithm is to maintain a constant rotational speed by slightly altering the spin commutation period of the individual track sectors. An accurate determination of each sector period can be obtained by timing the occurrence of the sector marks with respect to the system clock.

As defined by Equation 8, the spin algorithm utilizes the net difference in the timed sector periods as an error value to adjust the spin commutation period. Any increase in the net sector period, less a nominal "at speed" time period of a sector for the rotating media 12 rotating at its proper speed, will yield a corresponding increase in the sector commutation period  $S_{cp}$ . Since the net increase in sector period corresponds to the rotating media 12 spinning at a speed below its intended value, the increased sector commutation period will have the desired effect of increasing the rotational speed of the rotating media 12. This set of circumstances is graphically illustrated in FIG. 13d where the sector mark actually occurs after a time  $B_3$  equalling  $t_0$  minus  $t_{nom}$ . Conversely, where the sector period error is negative, the spin commutation period,  $S_{cp}$ , is proportionately decreased leading to a corresponding decrease in the rotational speed of the rotating media 12. As shown in FIG. 13d, the early arrival of the sector mark prior to time C<sub>3</sub>, corresponding to the rotating media 12 rotating at too high a speed, the net negative sector period error, as applied in Equation 8, reduces the spin commu-

Eq. 8

tation period to achieve a corresponding decrease in the rotational speed of the rotating media 12.

Since the value of  $t_0$ ,  $t_{-1} t_{nom}$  are time values, the spin gain constant  $k_{cp}$  is utilized to convert the nominal sector spin period to the commutation timer value for the 5 microprocessor 24. To account for deviations from ideal mechanical circumstances, such as due to losses caused by bearing friction, windage and other forces, a spin integrator value  $I_{cp}$  is summed as shown in Equation 8. Depending on how well the current sector per- 10 iod tracks the nominal sector period, the spin integrator value previous in subsequent iterations of the spin algorithm is either incremented, decremented or left unchanged. By the selection of a small incrementer value "i", the spin integrator value  $I_{cp}$  becomes and then re- 15 mains a damped reflection of the dynamic spin speed losses.