## CONTROL DATA® 3500 COMPUTER SYSTEM

**REFERENCE MANUAL**

#### 3500 CHARACTERISTICS

- Stored-program, solid-state, scientific and business data processing computer

- Integrated circuitry, 50-PAK logic module construction

- Transistor Current Switch (TCS) logic

- Upwards compatability with the 3100, 3200, and 3300 computer systems

- Parallel mode of operation

- Character and word addressing (4 characters per word)

- Address modification (indexing) and indirect addressing

- Parity chacking on data and addresses

- 28-bit storage word (24 data bits and 4 parity bits)

- Nonvolatile magnetic core storage

- Complete cycle time: 0.900 microseconds

- Storage access time: 0.500 microseconds

- Storage sharing and selected storage protection

- Single-precision (24-bit) and double precision (48-bit) binary arithmetic

- Floating point arithmetic

- Logical and sensing operations

- Block operations (I/O oriented buffer priority)

- Trapped instruction processign

- Complete interrupt system

- 64-word register file

- Real-time clock (1.0 millisecond incrementation)

- 12-bit and 24-bit bidirectional data channels

- Sit-down operator's console featuring on-line typewriter and complete display and control system

- Maintenance test facilities for arithmetic and I/O channels

- Compatible I/O media include magnetic tape, disk file, punched cards, paper tape, and printed forms

- Options include:

Business oriented Moves, Searches, Edit, Compares, Conversions, and BCD arithmetic

Address relocation hardware

Real-Time Interrupt Processor (RIP)

Memory expansion to 262, 144 words (over 1 million characters)

Additional 12-bit and 24-bit data channels

Complete Selection of advanced peripheral equipment

Register/Page File Parity

## CONTROL DATA® 3500 COMPUTER SYSTEM

**REFERENCE MANUAL**

|                | RECORD of REVISIONS                                                                               |  |  |  |

|----------------|---------------------------------------------------------------------------------------------------|--|--|--|

| REVISION NOTES |                                                                                                   |  |  |  |

| 01             | Training edition. Company distribution only.                                                      |  |  |  |

| (12-15-66)     |                                                                                                   |  |  |  |

| 02             | Preliminary edition. This printing obsoletes previous editions.                                   |  |  |  |

| (7-14-67)      |                                                                                                   |  |  |  |

| A              | Final Edition. This printing obsolete all previous editions.                                      |  |  |  |

| (11-15-69)     |                                                                                                   |  |  |  |

| В              | Manual revised; includes Engineering Change Order 33777, publications change only. Cover, Inside  |  |  |  |

| (5-14-73)      | front cover, v, 1-4, 1-5, 1-6, 1-7, 1-8, 1-12, 1-13, 2-6, 4-1, 4-8, 4-9, 5-2, 5-8. 6-51, 6-83 and |  |  |  |

|                | 7-2 are revised. Page 3-8 is added.                                                               |  |  |  |

| C              | Manual revised; includes Engineering Change Order 34320. Pages 6-65, 6-69, and 7-9 are revised.   |  |  |  |

| (2-4-74)       |                                                                                                   |  |  |  |

| D              | Manual revised; includes ECO 35032. Pages 5-1, 5-6, 6-69, 6-70, 6-136, 6-138, 6-155, and          |  |  |  |

| (8-7-74)       | 6-158 revised.                                                                                    |  |  |  |

|                |                                                                                                   |  |  |  |

|                |                                                                                                   |  |  |  |

|                |                                                                                                   |  |  |  |

|                |                                                                                                   |  |  |  |

|                |                                                                                                   |  |  |  |

|                |                                                                                                   |  |  |  |

|                |                                                                                                   |  |  |  |

|                |                                                                                                   |  |  |  |

|                |                                                                                                   |  |  |  |

|                |                                                                                                   |  |  |  |

|                |                                                                                                   |  |  |  |

|                |                                                                                                   |  |  |  |

|                |                                                                                                   |  |  |  |

|                |                                                                                                   |  |  |  |

|                |                                                                                                   |  |  |  |

|                |                                                                                                   |  |  |  |

|                | _                                                                                                 |  |  |  |

|                |                                                                                                   |  |  |  |

|                |                                                                                                   |  |  |  |

|                |                                                                                                   |  |  |  |

|                |                                                                                                   |  |  |  |

|                |                                                                                                   |  |  |  |

|                |                                                                                                   |  |  |  |

|                |                                                                                                   |  |  |  |

|                |                                                                                                   |  |  |  |

|                |                                                                                                   |  |  |  |

|                |                                                                                                   |  |  |  |

Address comments concerning this manual to:

Control Data Corporation Technical Publications Department 4201 North Lexington Avenue St. Paul, Minnesota 55112

or use Comment Sheet in the back of this manual.

Pub No. 60200300 © 1967, 1968, 1969, 1973, 1974 by Control Data Corporation Printed in United States of America

#### PREFACE

This manual provides information for the machine language use of the CONTROL DATA® 3500 Computer System. The purpose of this manual is to describe the capabilities of the hardware and to note programming restrictions.

COMPASS mnemonics are used to abbreviate titles of instructions; however, no software systems are used in describing instructions. Detailed descriptions for those systems in operation are available in the appropriate software reference manuals.

Programming information for most available peripheral equipment is contained in the 3000 Series Peripheral Equipment Reference Manual. For latest publications and revisions see the Control Data Literature Catalog.

#### CONTENTS

v

| 1. GENERAL SYSTEM DESCRIPTIO |

|------------------------------|

|------------------------------|

| Introduction                                 | 1-1      |

|----------------------------------------------|----------|

| 3500 Computer Configuration                  |          |

| Central Processors                           | 1-3      |

| Magnetic Core Storage                        | 1-4      |

| Input/Output Channel                         | 1-5      |

| Register/Page File Parity<br>Checking Option | 1-5      |

| Real-Time Interrupt Processor<br>or (RIP)    | r<br>1-5 |

| Internal Organization                        | 1-5      |

| Computer Word Format                         | 1-5      |

| Central Processor                            | 1-6      |

| Operational Modes                            | 1-12     |

| Status and Interrupts                        | 1-13     |

| Parity Checking System                       | 1-13     |

| Peripheral Equipment                         | 1-14     |

| 2. STORAGE SYSTEM                            |          |

| General Information                          | 2-1      |

| 3502 Storage Module                          | 2-1      |

| Access Channels                              | 2-2      |

| 3502 Access Channels                         | 2-2      |

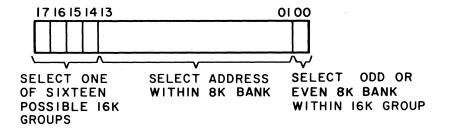

| Storage Addressing                           | 2-3      |

| Parity Checking                              | 2-3      |

| Address Parity                               | 2-4      |

| Data Parity                                  | 2-4      |

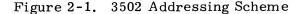

| Storage Protection                           | 2-4      |

| Permanent Protection                         | 2-4      |

| Selective Protection                         | 2-5      |

| 3. INPUT/OUTPUT SYSTEM                       |          |

| General Information                          | 3-1      |

| Channel Operating Modes                      | 3-2      |

| 12-Bit Mode                                  | 3-2      |

| 24-Bit Mode                                  | 3-3      |

| Interface Signals                            | 3-3      |

| Parity Checking During Input3-4Parity Checking During Output3-5Parity Checking During Function3-5Parity Checking During Function3-6Auto Load/Auto Dump3-6Transmission Rates3-7Parity Checking in<br>Register File3-84. INTERRUPT SYSTEM4-2Input/Output Interrupts4-2Input/Output Interrupts4-2Internal Condition Interrupts4-2Manual Interrupt4-4Manual Interrupt Control4-4Normal Interrupt Recognition4-6Abnormal Interrupt Recognition4-7Internal Condition Interrupt4-4Manual Interrupt4-4Normal Interrupt Recognition4-6Abnormal Interrupt Recognition4-6Abnormal Interrupt Recognition4-7Illegal Write Interrupt4-9Power Failure Interrupt4-9Power Failure Interrupt4-9Power Failure Interrupts4-10Real-Time Interrupts4-11Interrupt Addressing4-12Automatic Register Storage4-13Store Operational Registers4-14Restore Operational Registers4-14Restore Operational Registers4-14Automatic Register and Priority4-14 | Input/Output Transmission Parity     | 3-3  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------|

| Parity Checking During Output3-5Parity Checking During Function3-5Parity Checking During Function3-6Auto Load/Auto Dump3-6Transmission Rates3-7Parity Checking in<br>Register File3-84. INTERRUPT SYSTEM4-1Normal Interrupts4-2Input/Output Interrupts4-2Internal Condition Interrupts4-2Internal Condition Interrupts4-4Manual Interrupt4-4Normal Interrupt Control4-4Normal Interrupt Recognition4-6Abnormal Interrupt Recognition4-6Abnormal Interrupt Recognition4-7Illegal Write Interrupt4-9Power Failure Interrupt4-9Power Failure Interrupt4-9Power Failure Interrupts4-10Real-Time Interrupts4-11Interrupt Addressing4-12Automatic Register Storage4-13Store Operational Registers4-14Restore Operational Registers4-14Kestore Operational Registers4-14                                                                                                                                                           |                                      | 3-4  |

| Parity Checking During Connect3-5Parity Checking During Function3-5Executive Mode Input/Output3-6Auto Load/Auto Dump3-6Transmission Rates3-7Parity Checking in<br>Register File3-84. INTERRUPT SYSTEM4-1Normal Interrupts4-2Input/Output Interrupts4-2Internal Condition Interrupts4-2Executive Interrupt4-4Manual Interrupt4-4Normal Interrupt Control4-4Normal Interrupt Recognition4-6Abnormal Interrupt4-7Illegal Write Interrupt4-9Power Failure Interrupt4-9Power Failure Interrupt4-10Real-Time Interrupts4-10Real-Time Interrupts4-11Interrupt Addressing4-12Automatic Register Storage4-13Store Operational Registers4-14Restore Operational Registers4-14Kestore Operational Registers4-14                                                                                                                                                                                                                        |                                      | 3-5  |

| Parity Checking During Function3-5Executive Mode Input/Output3-6Auto Load/Auto Dump3-6Transmission Rates3-7Parity Checking in<br>Register File3-84. INTERRUPT SYSTEM4-1Mormal Interrupts4-2Input/Output Interrupts4-2Internal Condition Interrupts4-2Executive Interrupt4-4Manual Interrupt4-4Mormal Interrupt4-4Manual Interrupt4-4Normal Interrupt Control4-4Normal Interrupt Recognition4-6Abnormal Interrupt4-7Illegal Write Interrupt4-9Power Failure Interrupt4-9Power Failure Interrupt4-10Real-Time Interrupts4-10Real-Time Interrupts4-11Interrupt Addressing4-12Automatic Register Storage4-13Store Operational Registers4-14Restore Operational Registers4-14                                                                                                                                                                                                                                                    |                                      | 3-5  |

| Executive Mode Input/Output3-6Auto Load/Auto Dump3-6Transmission Rates3-7Parity Checking in<br>Register File3-84. INTERRUPT SYSTEM4-1General Information4-1Normal Interrupts4-2Input/Output Interrupts4-2Internal Condition Interrupts4-2Executive Interrupt4-4Manual Interrupt4-4Normal Interrupt Control4-4Normal Interrupt Recognition4-6Abnormal Interrupt4-7Illegal Write Interrupt4-9Power Failure Interrupt4-9Trapped Instruction Interrupts4-10Real-Time Interrupts4-11Interrupt Addressing4-12Automatic Register Storage4-13Store Operational Registers4-14Restore Operational Registers4-14Kestore Operational Registers4-14                                                                                                                                                                                                                                                                                      |                                      | 3-5  |

| Auto Load/Auto Dump3-6Transmission Rates3-7Parity Checking in<br>Register File3-84.INTERRUPT SYSTEMGeneral Information4-1Normal Interrupts4-2Input/Output Interrupts4-2Internal Condition Interrupts4-2Executive Interrupt4-4Manual Interrupt4-4Normal Interrupt Control4-4Normal Interrupt Recognition4-6Abnormal Interrupt Recognition4-7Illegal Write Interrupt4-9Power Failure Interrupt4-9Trapped Instruction Interrupts4-10Real-Time Interrupts4-11Interrupt Addressing4-12Automatic Register Storage4-13Store Operational Registers4-14Restore Operational Registers4-14Restore Operational Registers4-14                                                                                                                                                                                                                                                                                                            | • • •                                |      |

| Transmission Rates3-7Parity Checking in<br>Register File3-84. INTERRUPT SYSTEM4-1General Information4-1Normal Interrupts4-2Input/Output Interrupts4-2Internal Condition Interrupts4-2Executive Interrupt4-4Manual Interrupt4-4Normal Interrupt Control4-4Normal Interrupt Recognition4-6Abnormal Interrupt Error/No<br>Response Interrupt4-7Illegal Write Interrupt4-9Power Failure Interrupt4-9Power Failure Interrupts4-10Real-Time Interrupts4-11Enable/Disable RIP Interrupts4-11Automatic Register Storage4-13Store Operational Registers4-14Restore Operational Registers4-14Condition Register and Priority4-14                                                                                                                                                                                                                                                                                                      | • •                                  | 3-6  |

| Parity Checking in<br>Register File3-84. INTERRUPT SYSTEM4-1General Information4-1Normal Interrupts4-2Input/Output Interrupts4-2Internal Condition Interrupts4-2Executive Interrupt4-4Manual Interrupt4-4Manual Interrupt Control4-4Normal Interrupt Recognition4-6Abnormal Interrupt Sitt Error/No<br>Response Interrupt4-7Illegal Write Interrupt4-9Power Failure Interrupt4-9Power Failure Interrupts4-10Real-Time Interrupts4-11Enable/Disable RIP Interrupts4-11Automatic Register Storage4-13Store Operational Registers4-14Restore Operational Registers4-14Restore Operational Registers4-14Condition Register and Priority4-14                                                                                                                                                                                                                                                                                     | •                                    |      |

| Register File3-84. INTERRUPT SYSTEMGeneral Information4-1Normal Interrupts4-2Input/Output Interrupts4-2Internal Condition Interrupts4-2Executive Interrupt4-4Manual Interrupt4-4Associated Processor Interrupt4-4Normal Interrupt Control4-4Normal Interrupt Recognition4-6Abnormal Interrupt Recognition4-7Storage Parity Error/No<br>Response Interrupt4-7Illegal Write Interrupt4-9Power Failure Interrupts4-10Real-Time Interrupts4-11Interrupt Addressing4-12Automatic Register Storage4-13Store Operational Registers4-14Restore Operational Registers4-14Condition Register and Priority4-14                                                                                                                                                                                                                                                                                                                         |                                      |      |

| General Information4-1Normal Interrupts4-2Input/Output Interrupts4-2Internal Condition Interrupts4-2Executive Interrupt4-4Manual Interrupt4-4Associated Processor Interrupt4-4Normal Interrupt Control4-4Normal Interrupt Recognition4-6Abnormal Interrupts4-7Illegal Write Interrupt4-9Power Failure Interrupt4-9Trapped Instruction Interrupts4-11Real-Time Interrupts4-11Interrupt Addressing4-12Automatic Register Storage4-13Store Operational Registers4-14Restore Operational Registers4-14                                                                                                                                                                                                                                                                                                                                                                                                                          |                                      | 3-8  |

| General Information4-1Normal Interrupts4-2Input/Output Interrupts4-2Internal Condition Interrupts4-2Executive Interrupt4-4Manual Interrupt4-4Associated Processor Interrupt4-4Normal Interrupt Control4-4Normal Interrupt Recognition4-6Abnormal Interrupts4-7Illegal Write Interrupt4-9Power Failure Interrupt4-9Trapped Instruction Interrupts4-11Real-Time Interrupts4-11Interrupt Addressing4-12Automatic Register Storage4-13Store Operational Registers4-14Restore Operational Registers4-14                                                                                                                                                                                                                                                                                                                                                                                                                          |                                      |      |

| Normal Interrupts4-2Input/Output Interrupts4-2Internal Condition Interrupts4-2Executive Interrupt4-4Manual Interrupt4-4Associated Processor Interrupt4-4Normal Interrupt Control4-4Normal Interrupt Recognition4-6Abnormal Interrupts4-7Storage Parity Error/No<br>Response Interrupt4-7Illegal Write Interrupt4-9Power Failure Interrupt4-9Trapped Instruction Interrupts4-10Real-Time Interrupts4-11Interrupt Addressing4-12Automatic Register Storage4-13Store Operational Registers4-14Restore Operational Registers4-14Restore Operational Registers4-14                                                                                                                                                                                                                                                                                                                                                               | 4. INTERRUPT SYSTEM                  |      |

| Input/Output Interrupts4-2Internal Condition Interrupts4-2Executive Interrupt4-4Manual Interrupt4-4Associated Processor Interrupt4-4Normal Interrupt Control4-4Normal Interrupt Recognition4-6Abnormal Interrupts4-7Storage Parity Error/No<br>Response Interrupt4-9Power Failure Interrupt4-9Power Failure Interrupt4-10Real-Time Interrupts4-11Interrupt Addressing4-12Automatic Register Storage4-13Store Operational Registers4-14Restore Operational Registers4-14Condition Register and Priority4-14                                                                                                                                                                                                                                                                                                                                                                                                                  | General Information                  | 4-1  |

| Internal Condition Interrupts4-2Executive Interrupt4-4Manual Interrupt4-4Associated Processor Interrupt4-4Normal Interrupt Control4-4Normal Interrupt Recognition4-6Abnormal Interrupts4-7Storage Parity Error/No<br>Response Interrupt4-7Illegal Write Interrupt4-9Power Failure Interrupt4-9Trapped Instruction Interrupts4-10Real-Time Interrupts4-11Enable/Disable RIP Interrupts4-11Interrupt Addressing4-12Automatic Register Storage4-13Store Operational Registers4-14Restore Operational Registers4-14Condition Register and Priority4-14                                                                                                                                                                                                                                                                                                                                                                          | Normal Interrupts                    | 4-2  |

| Executive Interrupt4-4Manual Interrupt4-4Associated Processor Interrupt4-4Associated Processor Interrupt4-4Normal Interrupt Control4-4Normal Interrupt Recognition4-6Abnormal Interrupt Recognition4-6Abnormal Interrupt Recognition4-7Storage Parity Error/No<br>Response Interrupt4-7Illegal Write Interrupt4-9Power Failure Interrupt4-9Trapped Instruction Interrupts4-10Real-Time Interrupts4-11Interrupt Addressing4-12Automatic Register Storage4-13Store Operational Registers4-14Restore Operational Registers4-14Condition Register and Priority4-14                                                                                                                                                                                                                                                                                                                                                              | Input/Output Interrupts              | 4-2  |

| Manual Interrupt4-4Associated Processor Interrupt4-4Normal Interrupt Control4-4Normal Interrupt Recognition4-6Abnormal Interrupt Recognition4-6Abnormal Interrupts4-7Storage Parity Error/No<br>Response Interrupt4-7Illegal Write Interrupt4-9Power Failure Interrupt4-9Trapped Instruction Interrupts4-10Real-Time Interrupts4-11Interrupt Addressing4-12Automatic Register Storage4-13Store Operational Registers4-14Restore Operational Registers4-14Condition Register and Priority4-14                                                                                                                                                                                                                                                                                                                                                                                                                                | Internal Condition Interrupts        | 4-2  |

| Associated Processor Interrupt4-4Normal Interrupt Control4-4Normal Interrupt Recognition4-6Abnormal Interrupt Recognition4-7Storage Parity Error/No<br>Response Interrupt4-7Illegal Write Interrupt4-9Power Failure Interrupt4-9Trapped Instruction Interrupts4-10Real-Time Interrupts4-11Interrupt Addressing4-12Automatic Register Storage4-13Store Operational Registers4-14Restore Operational Registers4-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Executive Interrupt                  | 4-4  |

| Normal Interrupt Control4-4Normal Interrupt Recognition4-6Abnormal Interrupts4-7Storage Parity Error/No<br>Response Interrupt4-7Illegal Write Interrupt4-9Power Failure Interrupt4-9Trapped Instruction Interrupts4-10Real-Time Interrupts4-11Enable/Disable RIP Interrupts4-12Automatic Register Storage4-13Store Operational Registers4-14Restore Operational Registers4-14Condition Register and Priority4-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Manual Interrupt                     | 4-4  |

| Normal Interrupt Recognition4-6Abnormal Interrupts4-7Storage Parity Error/No<br>Response Interrupt4-7Illegal Write Interrupt4-9Power Failure Interrupt4-9Trapped Instruction Interrupts4-10Real-Time Interrupts4-11Enable/Disable RIP Interrupts4-12Automatic Register Storage4-13Store Operational Registers4-14Restore Operational Registers4-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Associated Processor Interrupt       | 4-4  |

| Abnormal Interrupts4-7Storage Parity Error/No<br>Response Interrupt4-7Illegal Write Interrupt4-9Power Failure Interrupt4-9Trapped Instruction Interrupts4-10Real-Time Interrupts4-11Enable/Disable RIP Interrupts4-11Interrupt Addressing4-12Automatic Register Storage4-13Store Operational Registers4-14Restore Operational Registers4-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Normal Interrupt Control             | 4-4  |

| Storage Parity Error/No<br>Response Interrupt4-7Illegal Write Interrupt4-9Power Failure Interrupt4-9Trapped Instruction Interrupts4-10Real-Time Interrupts4-11Enable/Disable RIP Interrupts4-11Interrupt Addressing4-12Automatic Register Storage4-13Store Operational Registers4-14Restore Operational Registers4-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Normal Interrupt Recognition         | 4-6  |

| Response Interrupt4-7Illegal Write Interrupt4-9Power Failure Interrupt4-9Trapped Instruction Interrupts4-10Real-Time Interrupts4-11Enable/Disable RIP Interrupts4-11Interrupt Addressing4-12Automatic Register Storage4-13Store Operational Registers4-14Restore Operational Registers4-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Abnormal Interrupts                  | 4-7  |

| Power Failure Interrupt4-9Trapped Instruction Interrupts4-10Real-Time Interrupts4-11Enable/Disable RIP Interrupts4-11Interrupt Addressing4-12Automatic Register Storage4-13Store Operational Registers4-14Restore Operational Registers4-14Condition Register and Priority4-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                      | 4-7  |

| Trapped Instruction Interrupts4-10Real-Time Interrupts4-11Enable/Disable RIP Interrupts4-11Interrupt Addressing4-12Automatic Register Storage4-13Store Operational Registers4-14Restore Operational Registers4-14Condition Register and Priority4-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Illegal Write Interrupt              | 4-9  |

| Real-Time Interrupts4-11Enable/Disable RIP Interrupts4-11Interrupt Addressing4-12Automatic Register Storage4-13Store Operational Registers4-14Restore Operational Registers4-14Condition Register and Priority4-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Power Failure Interrupt              | 4-9  |

| Enable/Disable RIP Interrupts4-11Interrupt Addressing4-12Automatic Register Storage4-13Store Operational Registers4-14Restore Operational Registers4-14Condition Register and Priority4-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Trapped Instruction Interrupts       | 4-10 |

| Enable/Disable RIP Interrupts4-11Interrupt Addressing4-12Automatic Register Storage4-13Store Operational Registers4-14Restore Operational Registers4-14Condition Register and Priority4-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Real-Time Interrupts                 | 4-11 |

| Automatic Register Storage4-13Store Operational Registers4-14Restore Operational Registers4-14Condition Register and Priority4-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                      | 4-11 |

| Store Operational Registers4-14Restore Operational Registers4-14Condition Register and Priority4-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Interrupt Addressing                 | 4-12 |

| Store Operational Registers4-14Restore Operational Registers4-14Condition Register and Priority4-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Automatic Register Storage           | 4-13 |

| Condition Register and Priority                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                      | 4-14 |

| Condition Register and Priority                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>Restore Operational Registers</b> | 4-14 |

| Considerations 4-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -                                    | 4-15 |

| RIP Parity Checking 4-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                      |      |

| Forced Interrupts                    | 4-17 |

|--------------------------------------|------|

| Real-Time Interrupt Response<br>Time | 4-17 |

| Interrupt Priority                   |      |

| Interrupts During Executive Mode     |      |

| Status                               |      |

| Internal/External Status             | 4-20 |

| Illegal Write Status                 | 4-21 |

#### 5. RELOCATION SYSTEM

| General Information            |     |

|--------------------------------|-----|

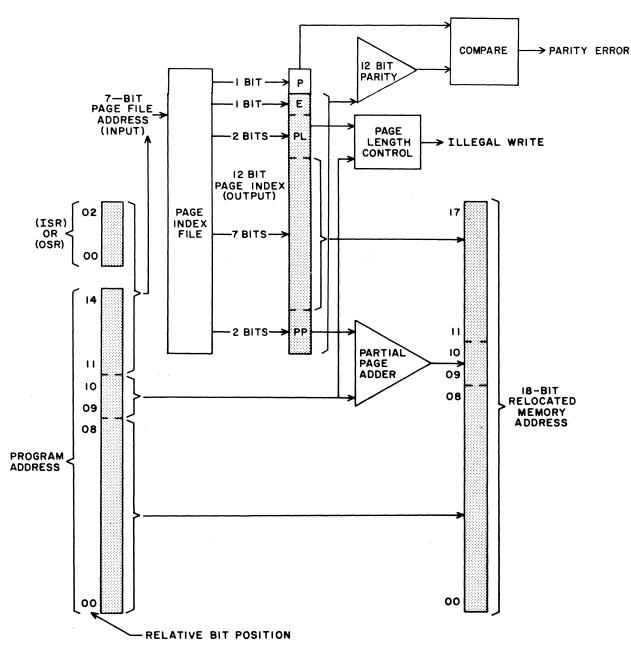

| Relocation Process             |     |

| Page Structure                 | 5-2 |

| Page Index File                | 5-3 |

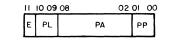

| Partial Page Adder             | 5-5 |

| Page Index Zero Considerations |     |

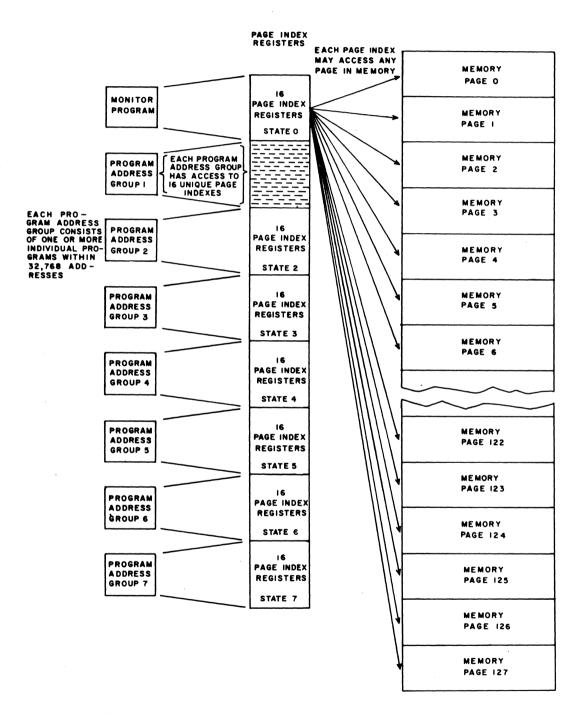

| Program Address Groups         | 5-6 |

| Program Protection             |     |

#### 6. INSTRUCTIONS

| General Information                          | 6-1  |

|----------------------------------------------|------|

| Instruction Parameters                       |      |

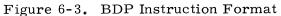

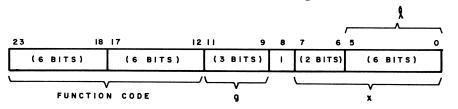

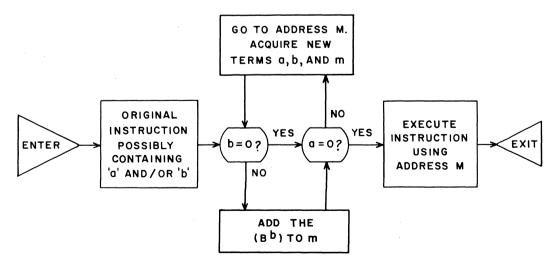

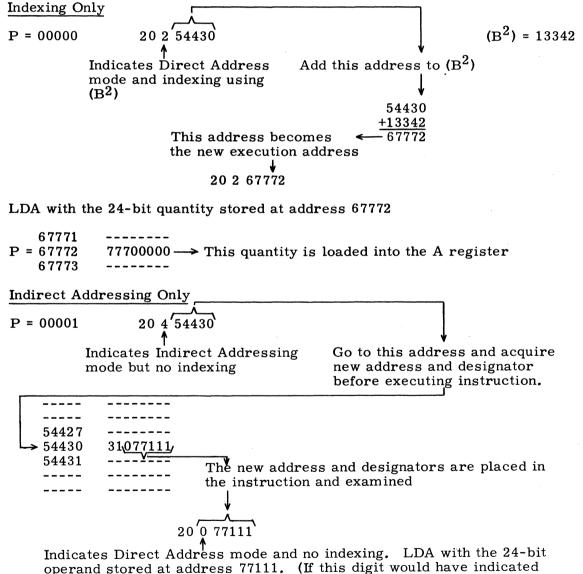

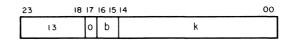

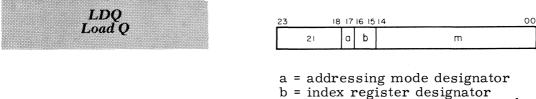

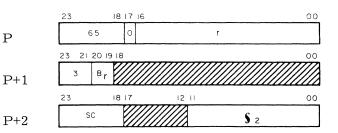

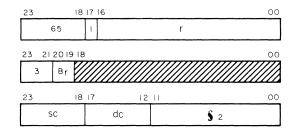

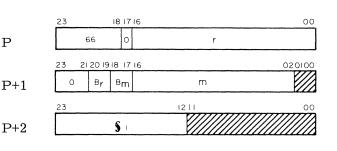

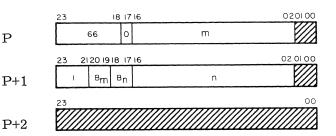

| Addressing and Instruction Formats           | 6-4  |

| Word Addressing                              | 6-4  |

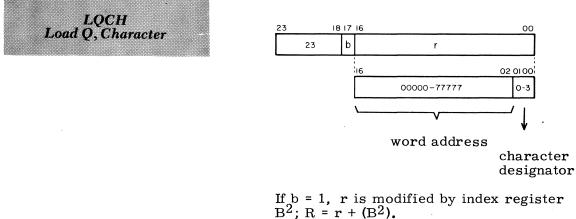

| Character Addressing                         | 6-4  |

| <b>RIP Instruction Format</b>                | 6-6  |

| Address Conversion                           | 6-7  |

| Addressing Modes                             | 6-7  |

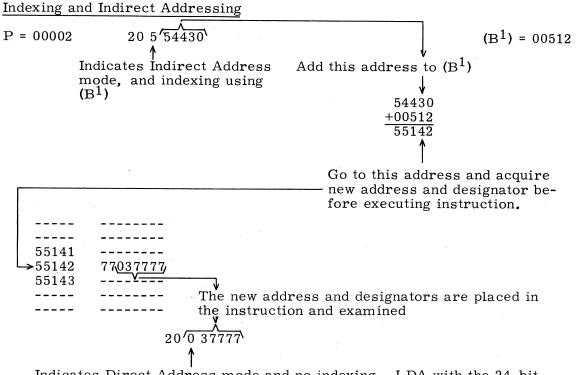

| Indexing and Indirect<br>Addressing Examples | 6-9  |

| Instruction List                             | 6-10 |

| <b>No-Operation Instructions</b>             | 6-11 |

| Trapped Instructions                         | 6-11 |

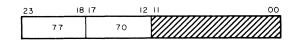

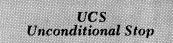

| Halt and Stop Instructions                   | 6-12 |

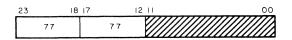

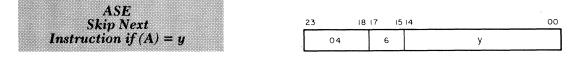

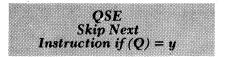

|   | Skip Instructions                              | 6-13  |

|---|------------------------------------------------|-------|

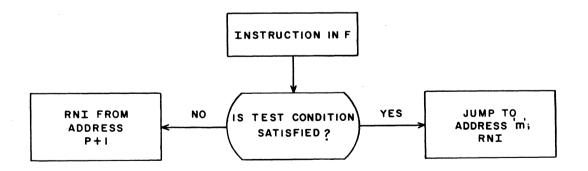

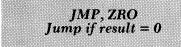

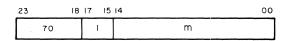

|   | Jump Instructions                              | 6-17  |

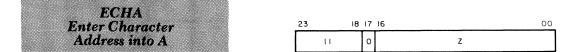

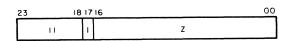

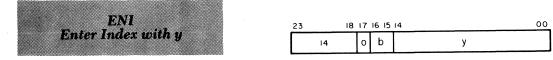

|   | Enter and Increase Instructions                | 6-25  |

|   | Inter-Register Transfer<br>Instructions        | 6-28  |

|   | Shift and Scale Instructions                   | 6-33  |

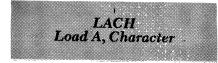

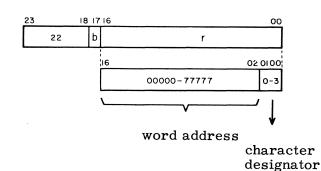

|   | Load Instructions                              | 6-36  |

|   | Store Instructions                             | 6-40  |

|   | Arithmetic Instructions                        | 6-44  |

|   | Logical Instructions                           | 6-51  |

|   | Search, Move, and Compare<br>Instructions      | 6-56  |

|   | Sensing Instructions                           | 6-65  |

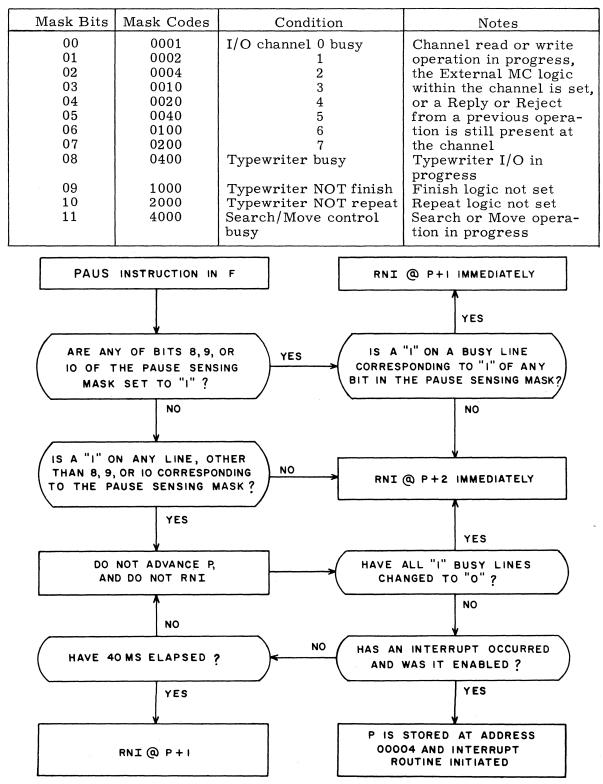

|   | Pause Instructions                             | 6-69  |

|   | Interrupt Instructions                         | 6-72  |

|   | Real-Time Interrupt<br>Instructions            | 6-76  |

|   | Program and Relocation<br>Control Instructions | 6-82  |

|   | Input/Output Instructions                      | 6-88  |

|   | Business Data Processing<br>Instructions       | 6-110 |

|   | CONSOLE AND COMPUTER<br>MAINTENANCE PANEL      |       |

| נ | eral Information                               | 7-1   |

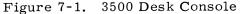

| n | sole                                           | 7-2   |

|   | Register Displays                              | 7-2   |

|   | Data Interchange Display                       | 7-3   |

|   |                                                |       |

# Gen

| Console                       | 7-2  |

|-------------------------------|------|

| Register Displays             | 7-2  |

| Data Interchange Display      | 7-3  |

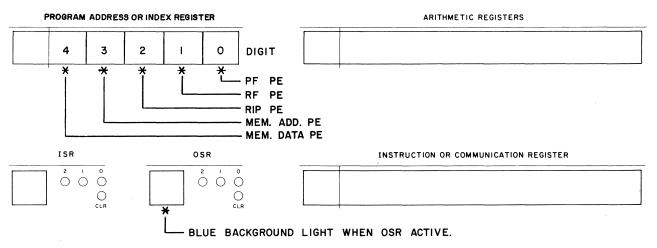

| Computer Status Display       | 7-4  |

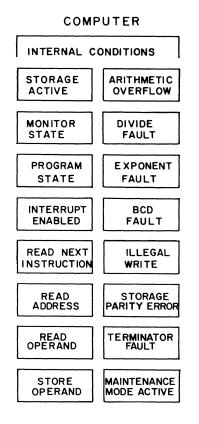

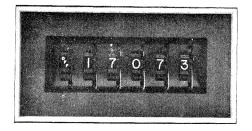

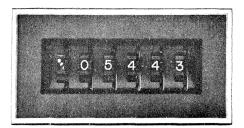

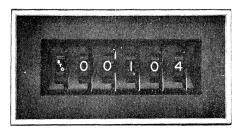

| Console Switch Panel          | 7-6  |

| Emergency Off                 | 7-11 |

| Examples of Switch Operations | 7-11 |

| Typewriter                    | 7-18 |

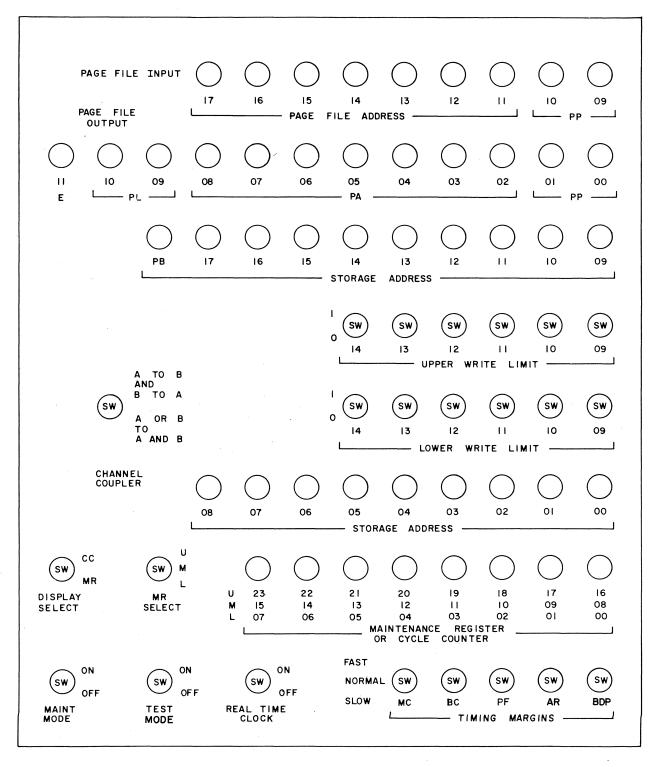

| Computer Maintenance Panel    | 7-23 |

| Maintenance Controls          | 7-23 |

7.

# Appendix A - Control Data 3100, 3200, 3300, 3500 Computer Systems Character Set and BCD/ASCII Code Conversions Appendix B - Supplementary Arithmetic Information Appendix C - Instruction Execution Times

#### Instruction Tables

#### Index

#### **FIGURES**

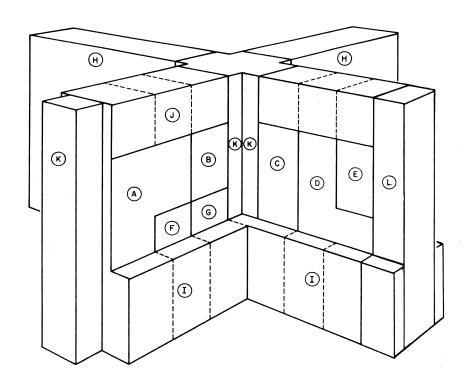

| 1-1 | 3500 Configuration                                                       | 1-2           |

|-----|--------------------------------------------------------------------------|---------------|

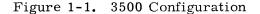

| 1-2 | Computer Word Format                                                     | 1-5           |

| 1-3 | Block Control Priority<br>Scheme                                         | 1-10          |

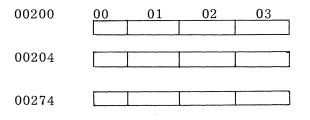

| 2-1 | 3502 Addressing Scheme                                                   | 2-3           |

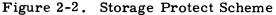

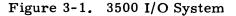

| 2-2 | Storage Protect Scheme                                                   | 2-5           |

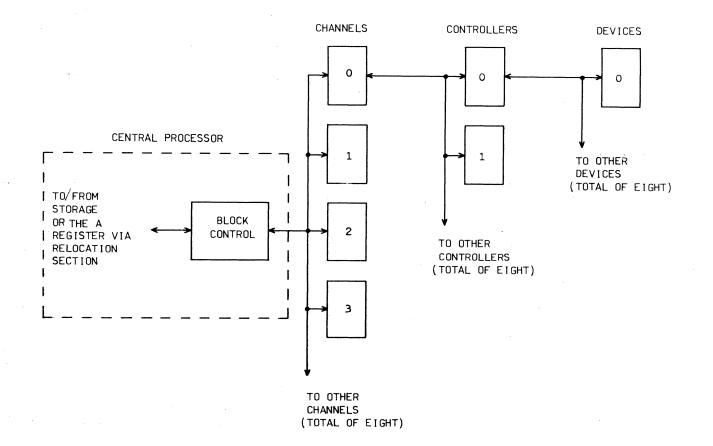

| 3-1 | 3500 I/O System                                                          | 3-2           |

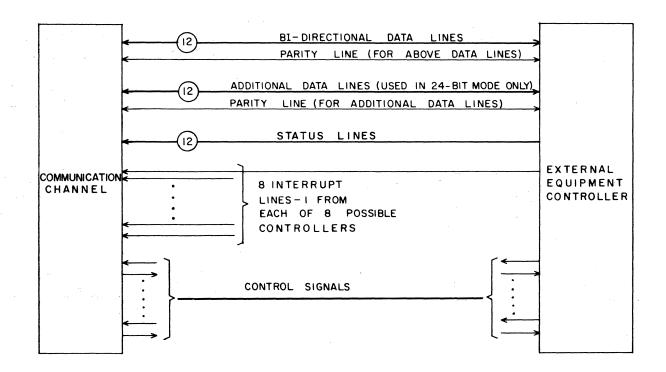

| 3-2 | I/O Interface Signals                                                    | 3-4           |

| 4-1 | Interrupt Address Format                                                 | 4-12          |

| 4-2 | Operational Registers Stored<br>in RIP Register File                     | 4 <b>-1</b> 3 |

| 5-1 | Relocation Process                                                       | 5-2           |

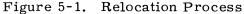

| 5-2 | Page Index Format                                                        | 5-3           |

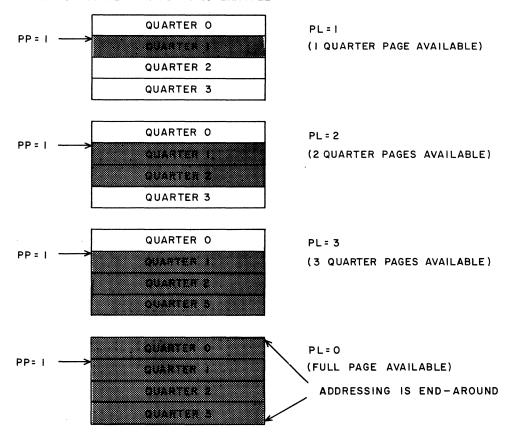

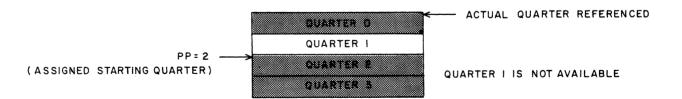

| 5-3 | Selecting Starting Quarters                                              | 5-3           |

| 5-4 | Page-Length Designator                                                   | 5-4           |

| 5-5 | Actual Quarter Referenced                                                | 5-5           |

| 5-6 | Program Address Groups                                                   | 5-7           |

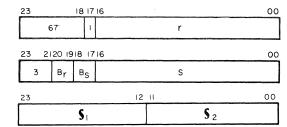

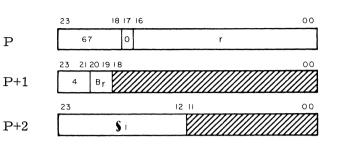

| 6-1 | Word Addressed Instruction<br>Format                                     | 6-4           |

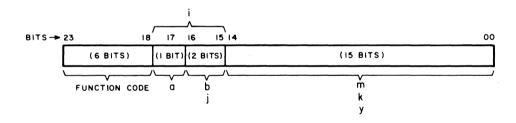

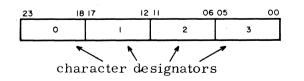

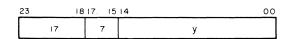

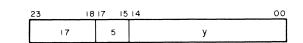

| 6-2 | Character-Addressed<br>Instruction Format                                | 6-5           |

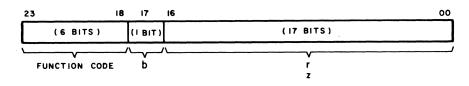

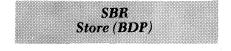

| 6-3 | BDP Instruction Format                                                   | 6-6           |

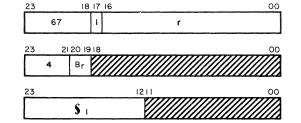

| 6-4 | <b>RIP</b> Instruction Format                                            | 6-6           |

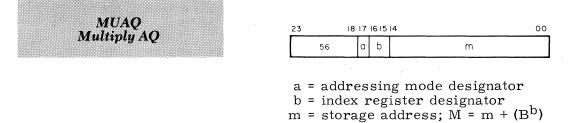

| 6-5 | Operand Formats and Bit<br>Allocations for MUAQ and<br>DVAQ Instructions | 6-47          |

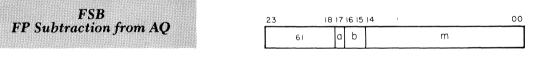

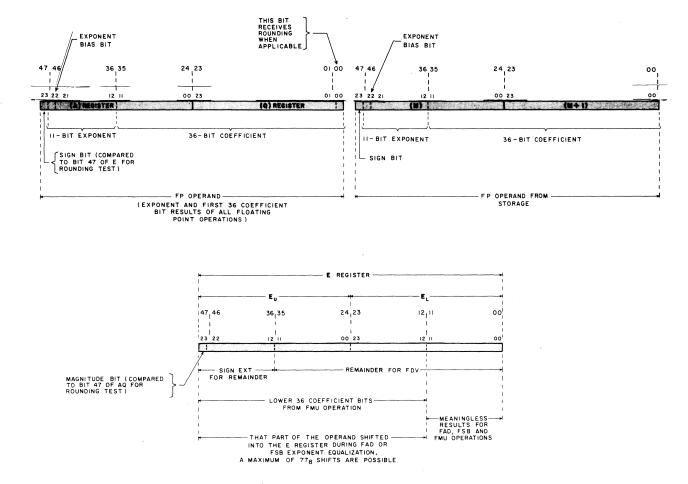

| -2<br>-5  | 6-6         | Operand Formats and Bit<br>Allocations for Floating Point<br>Arithmetic Instructions | 6-50  |

|-----------|-------------|--------------------------------------------------------------------------------------|-------|

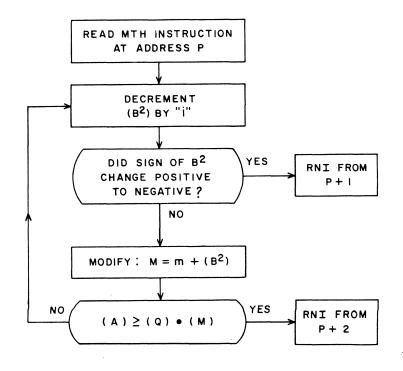

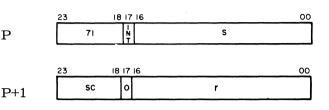

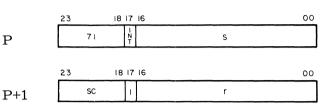

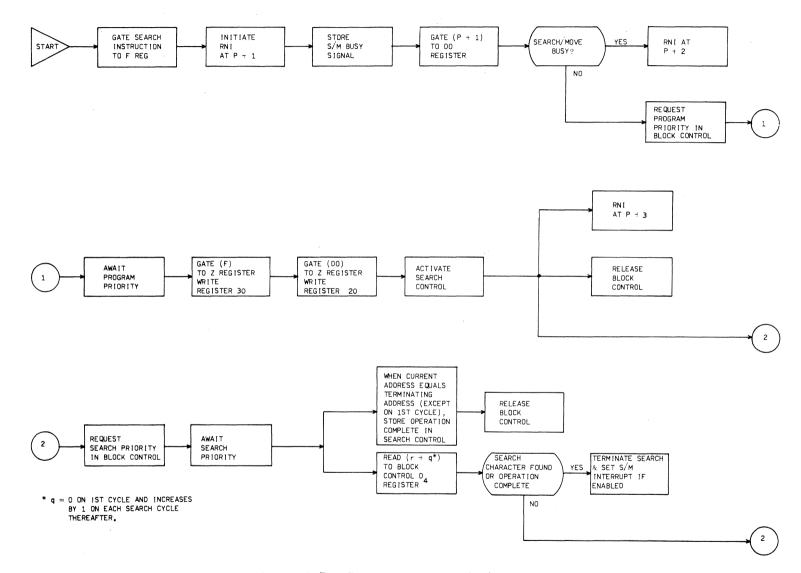

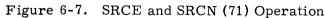

| -10       | 6-7         | SRCE and SRCN (71)<br>Operation                                                      | 6-61  |

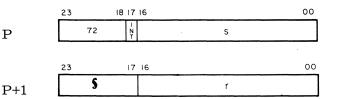

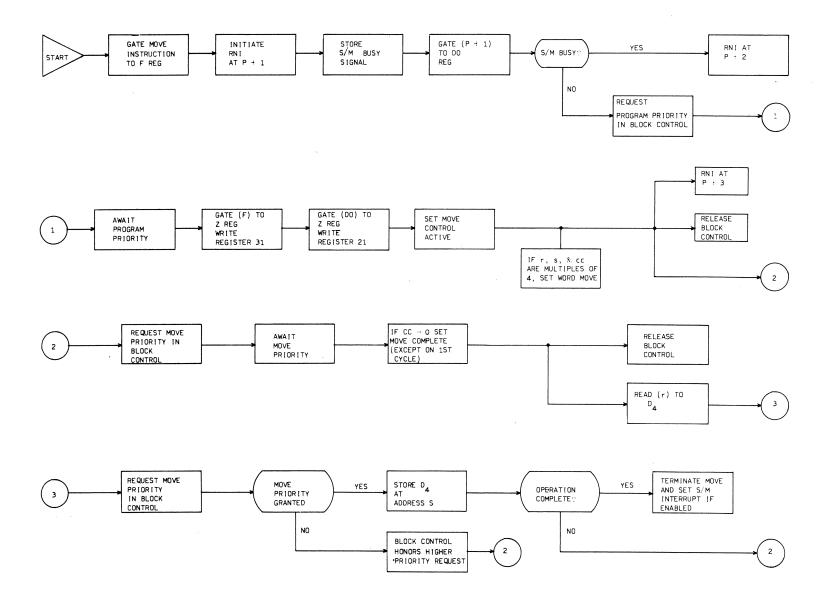

| -3        | 6-8         | MOVE (72) Operation                                                                  | 6-63  |

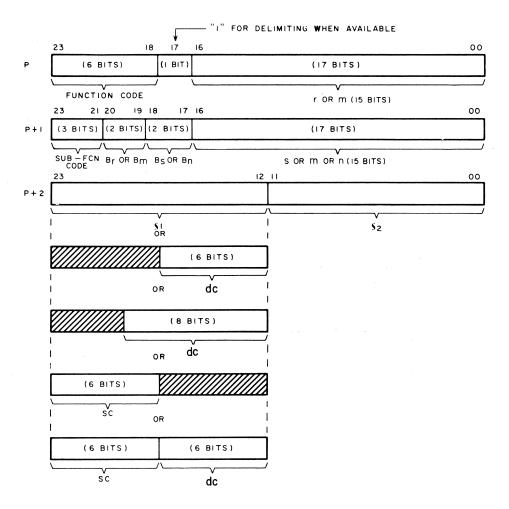

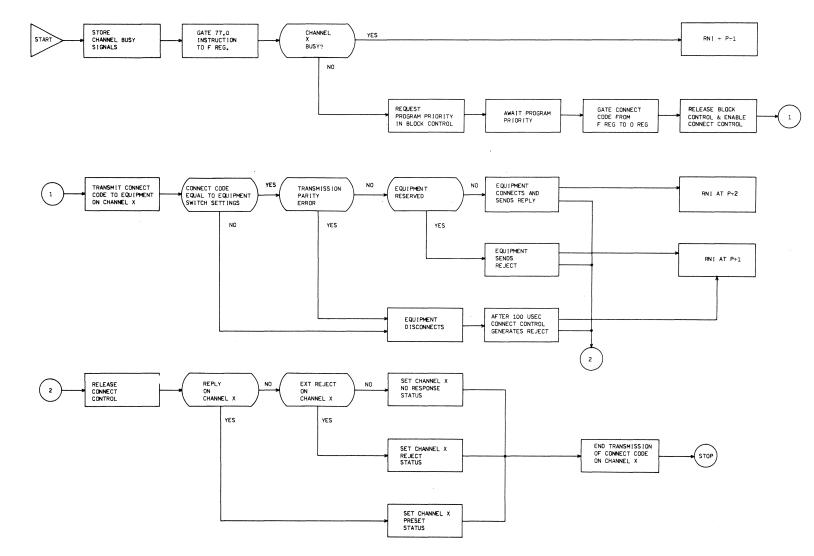

| -5        | <b>6-</b> 9 | Connect (77.0) Operation                                                             | 6-93  |

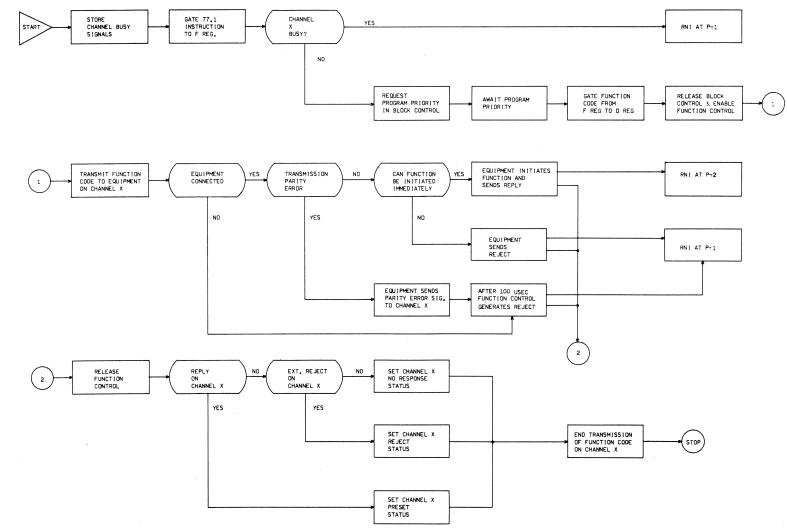

| -2<br>-4  | 6-10        | Select Function (77.1)<br>Operation                                                  | 6-95  |

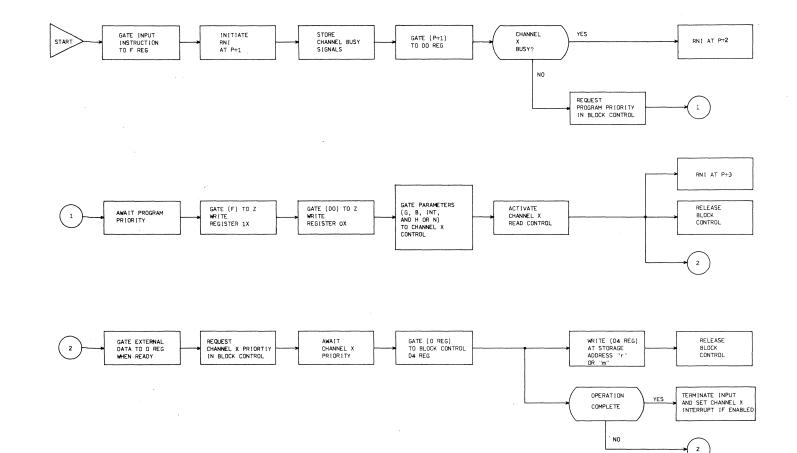

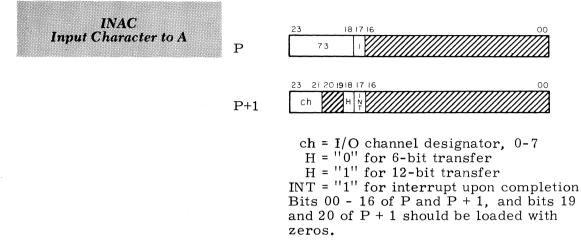

| -12       | 6-11        | Input to Storage (73 and 74)<br>Operation                                            | 6-100 |

| -13<br>-2 | 6-12        | Input to A (73 and 74)<br>Operation                                                  | 6-103 |

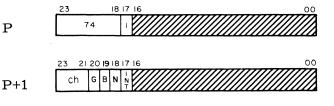

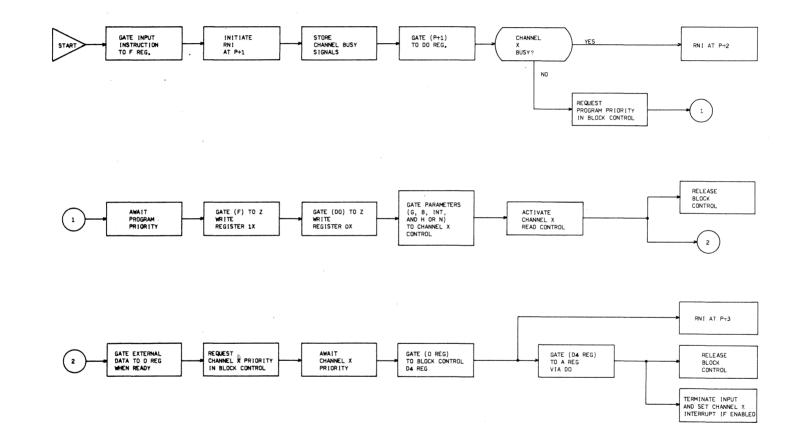

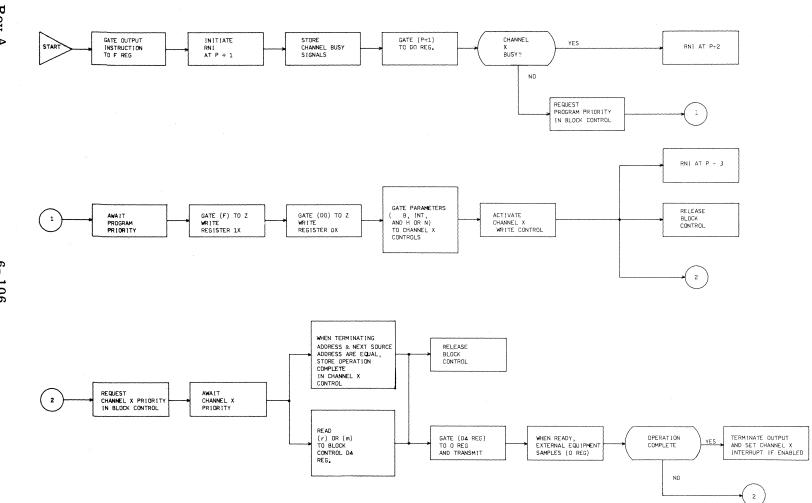

| -3        | 6-13        | Output from Storage (75 and 76) Operation                                            | 6-106 |

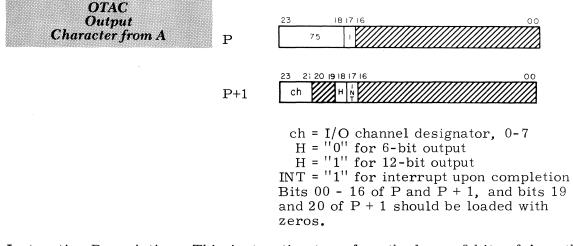

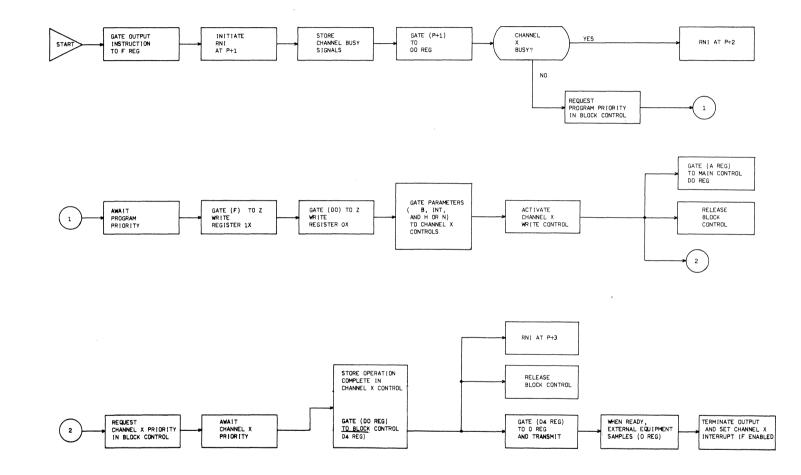

| -3<br>-4  | 6-14        | Output from A (75 and 76)<br>Operation                                               | 6-109 |

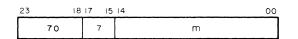

| -5        | 7-1         | 3500 Desk Console                                                                    | 7-1   |

| -7        | 7-2         | Register Displays                                                                    | 7-2   |

|           | 7-3         | Data Interchange Display                                                             | 7-3   |

| -4        | 7-4         | Computer Status Display                                                              | 7-5   |

| -5        | 7-5         | Console Switch Panel                                                                 | 7-7   |

| -6        | 7-6         | Breakpoint Switch Examples                                                           | 7-16  |

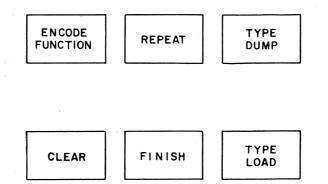

| -6        | 7-7         | Console Typewriter Switches                                                          | 7-18  |

| Ŭ         | 7-8         | Computer Maintenance Panel                                                           | 7-24  |

|           |             |                                                                                      |       |

#### TABLES

| 1-1 | Register File Assignments                  | 1-9  |

|-----|--------------------------------------------|------|

| 1-2 | Buffer Groups                              | 1-10 |

| 2-1 | Sample Storage Protect<br>Settings         | 2-6  |

| 3-1 | Transmission Rates                         | 3-7  |

| 4-1 | Interrupt Mask Register<br>Bit Assignments | 4-5  |

| 4-2 | Normal Interrupt Codes                     | 4-7  |

| 4-3 | Parity Error Interrupt Codes               | 4-8  |

| 4-4 | Trapped Instructions                       | 4-10 |

| 4-5 | Interrupt Priority                         | 4-19 |

| 4-6 | Condition Register Bit<br>Assignments      | 4-20 |

| 5-1 | Instruction and Operand<br>Referencing     | 5-6  |

| 6-1 | BDP Condition Register Codes               | 6-24 |

| 6-2 | Interrupt Mask Register Bit<br>Assignments | 6-66 |

| 6-3 | Internal Status Sensing Mask               | 6-67 |

| 6-4 | Interrupt Sensing Mask                     | 6-68 |

|     |                                            |      |

| 6-5          | Pause Sensing Mask                            | 6-70          |

|--------------|-----------------------------------------------|---------------|

| 6-6          | Interrupt Mask Register<br>Bit Assignments    | 6-74          |

| 6-7          | Modified I/O Instruction<br>Words             | 6 <b>-</b> 89 |

| 6-8          | Block Control Clearing Mask                   | 6-91          |

| 6 <b>-</b> 9 | Editing Examples                              | 6-131         |

| 7-1          | Data Interchange Indicator<br>Descriptions    | 7-4           |

| 7-2          | Computer Status Indicator<br>Descriptions     | 7-5           |

| 7-3          | Register Display Switches                     | 7-7           |

| 7-4          | Keyboard Switch Descriptions                  | 7-8           |

| 7-5          | Condition Switch Descriptions                 | 7-9           |

| 7-6          | Console Typewriter Switches<br>and Indicators | 7-19          |

| 7-7          | Console Typewriter Codes                      | 7-22          |

| 7-8          | Computer Maintenance<br>Panel                 | 7-24          |

|              |                                               |               |

#### 3500 COMPUTER SYSTEM

#### **1. GENERAL SYSTEM DESCRIPTION**

#### INTRODUCTION

The CONTROL DATA<sup>®</sup> 3500 Computer System is a general-purpose digital computing system of advanced design which features integrated circuitry and provides both scientific and business users with extremely high performance. A fully expanded system includes double precision and floating point arithmetic capabilities. It also has a comprehensive business data processing instruction set, an address relocation system that permits multiprogramming and full utilization of an expanded storage system, and a Real-Time Interrupt Processor which provides up to 64 additional priority interrupt lines and decreases interrupt response time.

All programs written for CONTROL DATA<sup>®</sup> 3100, 3200, and 3300 Computer Systems can be processed by a 3500. The I/O characteristics for the 3500 are identical to CONTROL DATA<sup>®</sup> 3000 Series computers. A wide selection of proven peripheral equipment is available for use in a 3500 system, including many new and advanced equipments.

Efficient software operating systems are available to complement the hardware. The Multiple Access Shared Time Executive Routine (MASTER) is a mass-storage-oriented multiprogramming executive operating system that can handle a multitude of real-time applications. It features multi-access capabilities for multiple on-line stations, for remote batch processing and for file manipulation. MASTER's greatest feature is that it increases total system throughput by overlapping activities of many tasks on compute modules and data channels. MASTER considers multiple jobs simultaneously so that activities can be found for processors whenever they become available.

The Mass Storage Operating System (MSOS) provides serial batch processing with concurrent execution of a special-purpose interrupt-controlled program. The operating system, software library, and user data areas are allocated to mass storage. MSOS features real-time priority-interrupt handling and a comprehensive mass storage input/ output system which is available to user programs. Certain non-standard real-time devices can be added to both operating systems; thus, the user can tailor the system to fit his needs. Detailed descriptions of these and other software systems are available upon request from the nearest Control Data sales office.

This manual describes the 3500 in terms of the Central Processor and its storage, I/O, and interrupt systems, and provides the programmer with a complete description of the hardware instruction set. Reference information is available in the Appendixes.

#### 3500 COMPUTER CONFIGURATION

The circuitry used in the 3500 allows a convenient packaging of logic components and assemblies. Individual integrated circuits are mounted on multi-layer printed circuit boards, forming 50 PAK logic modules. Fifty PAK's related logic functions form assemblies called logical units. The two wings that form the main computer contain the logical units for the Central Processor and I/O Channels, and also house the necessary power supply and cooling equipment. Figure 1-1 illustrates a typical 3500 configuration.

- (A) BLOCK CONTROL (INCLUDING I/O CHANNELS)

- (B) RELOCATION

- (C) MAIN CONTROL

- D ARITHMETIC

- (E) BUSINESS DATA PROCESSOR (BDP)

- (F) COMPUTER MAINTENANCE PANEL

- G CONSOLE DISPLAY INTERFACE

- (H) STORAGE MODULES

- (I) BLOWERS AND POWER SUPPLIES

- O POWER CONTROL PANELS (ONE PER COLUMN)

- (K) CONNECTOR PANELS

- C REAL-TIME INTERRUPT PROCESSOR

1-2

#### **Central Processors**

Several central processor models are available for 3500 systems. All central procesors are basically similar but some models have additional features designed for special applications.

Some of the most important central processor functions are:

- Performs all 24-/48-bit precision fixed point arithmetic

- Performs all floating point arithmetic

- Executes business data processing instruction set (some models)

- Executes Boolean (logical) and decision-making instructions

- Enables 24-bit word and 6-bit character data manipulation

- Controls real-time clock and register file references

- Controls standard search/move operations, external equipment and typewriter I/O

- Performs address relocation (some models)

- Recognizes and processes interrupts

- Provides memory protection

- Processes time-critical interrupts on a real-time basis (some models)

#### <u>3504-1 Central Processor</u>

This model performs all functions listed above except for real-time interrupt processing. It contains five functional sections:

- Main Control Section

- Arithmetic Section

- Block Control Section

- Address Relocation Section

- Business Data Processor (BDP)

#### <u>3514-4 Central Processor</u>

This model is similar to the 3504-1 with two major differences:

- 1. An optional 3522 Real Processor can be added. This unit adds up to 64 additional external interrupt lines and significantly reduces the time required to process interrupts from external sources.

- 2. The business data processing instruction set in the 3514-4 is somewhat different from the 3504-1 BDP instructions.

#### <u>3514-3 Central Processor</u>

This model is identical to the 3514-4 except that the Business Data Processor is not present. It includes the Main Control, Arithmetic, Block Control and Address Relocation sections.

#### <u>3514-2 Central Processor</u>

This model is identical to the 3514-4 except that the Address Relocation section is not present. It includes the Main Control, Arithmetic, Block Control and Business Data Processor sections.

#### <u>3514-1 Central Processor</u>

This model is identical to the 3514-4 except that neither the Business Data Processor nor Relocation section is installed. It includes the Main Control, Arithmetic and Block Control sections.

The optional 3522 Real Time Interrupt Processor may be added to any of the 3514 Central Processors but not to the 3504-1. Standard Option 10288 Register/Page File Parity Checking, may be added to the 3504 or 3514 Central Processors.

#### Magnetic Core Storage

The basic magnetic core storage\* for the 3500 system is the CONTROL DATA® 3502-32 Storage Module. The system can be expanded from this minimum of 32,768 words to a maximum of 262,144 words (1,048,576 characters). The number following the dash corresponds to the size of the storage module:

3502-32

Storage Module

----- 32,768 words

3502-65

Storage Module

----- 65,536 words

3502-262 Storage Module ----- 262,144 words

The storage shown in the configuration (Figure 1-1) consists of 65K words. Other storage configurations are available, including those with modules as stand-alone units. An option is available to expand the number of storage access channels to a maximum of four per module; one channel per module is standard. Refer to Section 2 for detailed storage information.

<sup>\*</sup> The word storage is used synonymously with memory throughout the text, and both refer to magnetic core storage unless otherwise stated.

#### Input/Output Channel

The input/output channel available in the 3500 system is the CONTROL DATA<sup>®</sup> 3507-1 Communication Channel. The channel operates in either of two modes to fit the particular application. A maximum of eight channels may be incorporated into a singleprocessor system.

In the 12-bit mode, the channel provides a 12-bit parallel data path with 12- to 24/24to 12-bit assembly/disassembly capabilities. In 24-bit mode the channel provides a 24-bit parallel data path for direct high-speed word transfers.

The channel conforms to the standard I/O specification for CONTROL DATA 3000 Series Computers. Refer to Section 3 for the interface signals used and for detailed information on the channel's two operating modes.

#### Real-Time Interrupt Processor (RIP)

The optional RIP available for 3514 central processors is the CONTROL DATA 3522 Real-Time Interrupt Processor. The RIP provides the system with up to 64 additional priority interrupt lines. Real-time interrupt capability provided by the RIP includes the following:

- 1. 16, 32, 48, or 64 real-time interrupt inputs to the RIP

- 2. Fixed interrupt priority 1 through 64

- 3. Automatic store of central processor operational registers when interrupting on lines 00  $17_8$

- 4. Automatic lockout of current and lower priority interrupts upon interrupt recognition

- 5. Unique interrupt address for each interrupt line.

The addition of an optional RIP enhances the system for real-time applications by providing reduced interrupt response time. Refer to Section 4 for detailed information regarding the Real-Time Interrupt Processor.

#### **REGISTER/PAGE FILE PARITY CHECKING OPTION**

Standard Option 10288 provides error detection in the register and page file and also provides detection of multiple parity errors and parity errors which occur when abnormal interrupt sensing is disabled. A corresponding coded interrupt is generated upon cover detection, adding three interrupts to abnormal interrupt system.

#### INTERNAL ORGANIZATION

#### **Computer Word Format**

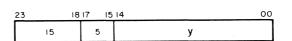

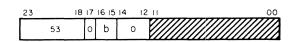

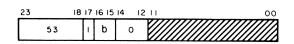

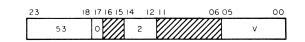

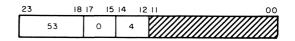

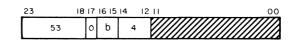

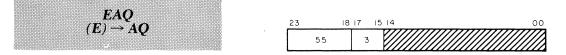

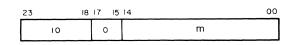

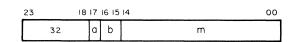

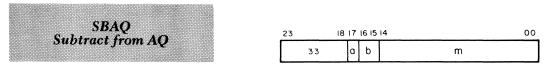

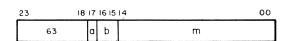

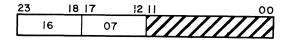

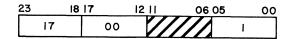

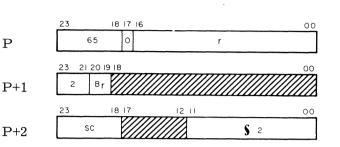

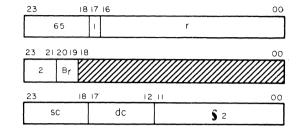

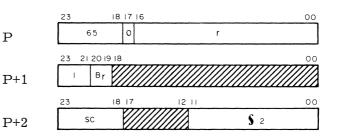

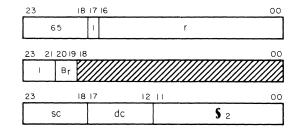

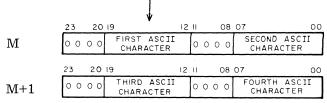

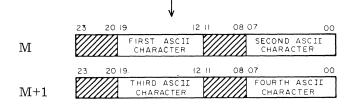

The standard 3500 computer word (Figure 1-2) consists of 24 bits (binary digits) grouped into four 6-bit characters. Parity is generated for each data character prior to entering storage; thus, the word length in storage is lengthened to 28 bits to accommodate the parity bits.

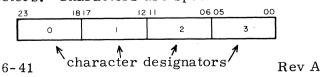

Figure 1-2. Computer Word Format

#### **Central Processor**

The Central Processor contains the necessary logic to control all sequences and synchronize internal operations within the storage modules and data channels. The processor is logically organized into five sections: Main Control, Block Control, Arithmetic, Business Data Processing (BDP), and Relocation. The BDP and the address relocation feature are optional in the 3514 but they are standard in the 3504.

#### Main Control Section

Main Control initiates execution of all instructions and enables subsequent action as required in either the Arithmetic, BDP, or Block Control sections for instruction completion.

The section has access to core storage via the Relocation section, and interfaces with the operator's console to provide synchronization and control of manual switches and keyboard operations. The principal registers in the section are described as follows:

<u>P Register (15 bits)</u>: The P register is the Program Address Counter. It provides program continuity by generating in sequence the basic storage addresses for retrieving the individual instructions. Normally P is incremented by 1 at the completion of each instruction. The address, which may be modified via the Relocation section, is sent to core storage to select the next instruction. On some models, blue background lights indicate parity errors.

A skip exit advances the count in P by 2, bypassing the next sequential instruction and executing the following one. For a jump exit, the execution address portion of the jump instruction is entered into P and is used to specify the starting address of a new sequence of instructions.

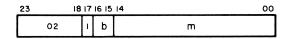

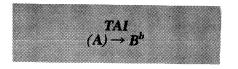

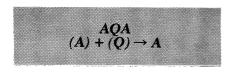

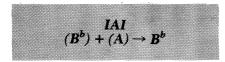

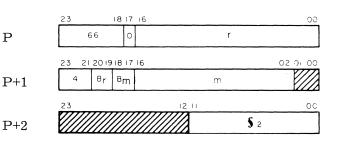

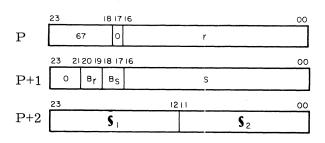

<u>F Register (24 bits)</u>: The F register receives the instruction from storage and retains it during interpretation and execution. During execution, the address portion of the instruction may be modified as follows:

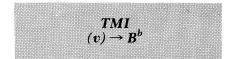

- Indexing A quantity in one of the index registers (B<sup>b</sup>) is added to the lower 15 bits of F for word-addressed instructions, or to the lower 17 bits of F for character-addressed instructions.

- Indirect Addressing The lower 18 bits of F are replaced by the lower 18 bits of the location specified by the original address. For load and store index instructions, bits 00-14 and bit 17 of F are replaced by the respective bits from the location specified by the original address.

The F register shares a display on the console with the Communication register. The F register is displayed whenever the keyboard is inactive and the computer is not in the Go mode.

<u>C Register (24 bits)</u>: Quantities to be entered into the A, Q, B<sup>b</sup>, or P registers, the Page File, Register File, or storage from the entry keyboard are temporarily held in the Communication (C) register until the TRANSFER switch is pressed. If an error is made while entering data into the Communication register, the KEYB CLR switch may be used to clear this register.

The C register displays words read from the Page File, Register File, or storage during certain manual operations. The (C)\* are displayed on the console whenever the keyboard is active.

\* The parentheses are an accepted method for expressing the words "the contents of" (in this case, "the contents of the C register").

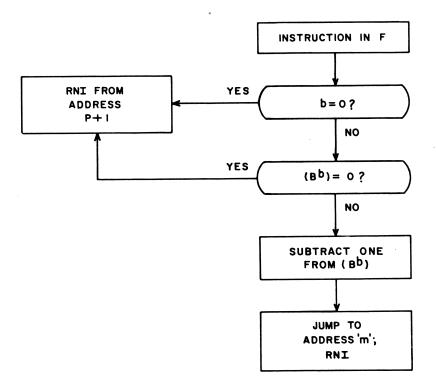

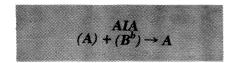

$\frac{B^{b}}{B^{b}}$  Registers (15 bits): The three index registers,  $B^{1}$ ,  $B^{2}$ , and  $B^{3}$ , are generally used for counting and indexing operations. When indexing is specified in an instruction, the contents of one of these registers is added to the original word or character address, thus forming a new execution address. The registers can be used for testing jump and skip conditions during a program, and for inter-register transfer operations.

Upon completion of certain business-oriented instructions, the  $B^3$  register is used to record the C field character count, BCD fault information, and other operating conditions (see Section 6). The index registers and P register share a display area on the console.

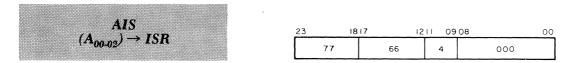

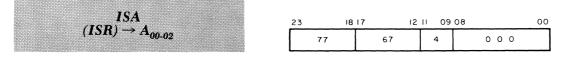

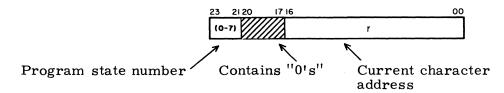

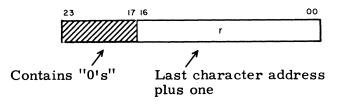

<u>Instruction State Register (3 bits)</u>: The ISR is used during Executive Mode operations to select one of eight areas within the relocation memory (Page Index File) that is addressed during an instruction memory reference. The (ISR) are appended to the basic 15-bit program address (P) to form an original 18-bit address. The register can be altered only during Monitor state of Executive mode. Refer to Section 5 for specific information on the use of this register.

Operand State Register (3 bits): The Operand State register (OSR) is used like the ISR except during operand references. The register can be altered only during Monitor state of Executive mode. Refer to Section 5 for specific information on the use of this register. Blue background light is on when OSR is active.

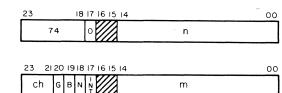

<u>Channel Index Register (3 bits)</u>: During Monitor state of Executive mode, the contents of the Channel Index register (CIR) are logically ORed (inclusive OR function) with the channel designator (ch) bits for the following instructions:

- 73-76 I/O instructions

- 77.0 Connect

- 77.1 Select Function

- 77.2 Sense External Status

- 77.2 Copy External Status

- 77.3 Sense Internal Status

- 77.3 Copy Internal Status

- 77.4 Sense Interrupt

This permits instructions to be written for Channel 0 and allows the monitor program to assign an available channel by altering the (CIR).

The (CIR) can be transferred by instruction to the lower 3 bits of the A register and vice versa. A switch is provided on the console for displaying (CIR) in the lowest digit position of the P register display.

<u>Condition Register (6 bits)</u>: Bits in the Condition register (CR) are used as flags to initiate computer action and to record current operating conditions during Executive mode. With the exception of bit 04, the register is not used during non-executive mode operations.

All register bits can be set or cleared with the ACR (77.634) instruction; selected bits are set or cleared by individual instructions and conditions. Refer to Section 4 for special considerations involving the register during interrupt processing. The register bit assignments are listed below:

- Bit 00 Boundary Jump

- Bit 01 Destructive Load A

- Bit 02 Operands Relocated Using OSR

- Bit 03 Program State Jump

- Bit 04 Interrupt System Enabled

- Bit 05 Program State

#### Block Control

Block Control is an auxiliary control section that is chiefly responsible for the following operations:

- I/O data transfers (including typewriter I/O)

- Search/Move

- Interrupt and status sensing

- Temporary storage (Register File)

- Real-time clock updating

Block Control shares access to storage with Main Control (via the Relocation section) and is capable of operating in parallel with the Arithmetic, BDP, and Main Control sections. Block Control interfaces directly with the console typewriter and the data channels.

The principal register within Block Control is the 24-bit  $D_4$  register. All data passing through Block Control during I/O operations is temporarily held in  $D_4$  Data is shifted in conjunction with the register to enable character and byte manipulation.

Register File: The Register File is a rapid-access flip-flop matrix containing 64 28-bit registers. It is used by Block Control for temporary storage and for address manipulation and control during block operations. Although the programmer has access to each register (lower 24 bits only) in the file with the inter-register transfer (53) instruction, reference should be made to Executive Interrupt in Section 4 for restrictions on the use of the file. Register file assignments are listed in Table 1-1.

Manual read/write operations with the Register File are possible using the Breakpoint switches on the operator's console (see Section 7).

A parity bit is generated and written for each transfer (27 bits) into the file. Parity is checked any time the file is referenced, if the PARITY STOP or PARITY INTERRUPT switch is active.

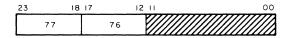

| Modified I/O instruction word (P+1) containing the current char-<br>acter address (Channel 0-7 control)                    |  |

|----------------------------------------------------------------------------------------------------------------------------|--|

| Modified I/O instruction word (P) containing the last address $\pm 1$ , depending on the instruction (Channel 0-7 control) |  |

| Search instruction word containing the current character address (search control)                                          |  |

| Move instruction word containing the current source character address (move control)                                       |  |

| econds)                                                                                                                    |  |

| Current character address (typewriter control)*                                                                            |  |

|                                                                                                                            |  |

| s + 1                                                                                                                      |  |

| Instruction word containing the current destination character address (move control)                                       |  |

|                                                                                                                            |  |

|                                                                                                                            |  |

|                                                                                                                            |  |

| ste                                                                                                                        |  |

#### TABLE 1-1. REGISTER FILE ASSIGNMENTS

<u>Block Control Priority</u>: Priority to Block Control is I/O oriented, with Channel 0 having highest priority. Any lower numbered channel has priority over a higher numbered channel and therefore should be used to service the fast I/O devices in a system. Once a channel request is honored, the request scanning process is reset to Channel 0. Requests for I/O are honored until a maximum number of active operations limit further honoring of requests, at which time Block Control is operating at its maximum rate.

The main program requires access to Block Control to initiate I/O and S/M buffer operations. This initiation consists of storing modified forms of the instruction words in the Register File, hence providing available operating information (addresses, channel number, etc.) to Block Control. Once the desired I/O operations have been initiated, high priority is not given to further initiation. Table 1-2 lists the different buffer groups, in their normal order of priority, and also shows the priority within groups.

TABLE 1-2. BUFFER GROUPS

| GROUP 1   | GROUP 2   | GROUP 3         |

|-----------|-----------|-----------------|

| Channel 0 | Channel 4 | Program         |

| Channel 1 | Channel 5 | Real-time Clock |

| Channel 2 | Channel 6 | Typewriter      |

| Channel 3 | Channel 7 | Search/Move     |

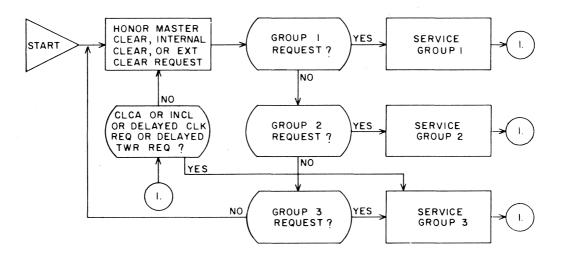

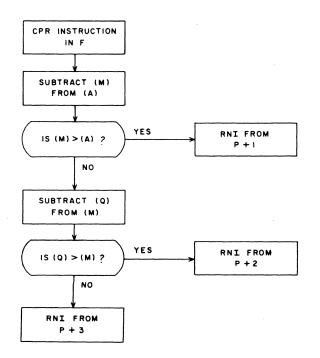

If the I/O system has not reached maximum transfer rate, the requests in Group 3 will be honored in their normal order of priority. However, since Block Control provides for maximum bursts of I/O without interruption, the honoring of requests for updating the real-time clock, clearing the channels via instruction (CLCA and INCL), and servicing typewriter I/O is delayed as long as possible so that burst rates may be achieved. These requests are then serviced with the highest priority after the delay. The flow chart in Figure 1-3 illustrates the priority scheme, including the special delayed requests. Note that Master Clear, Internal Clear, and External Clear requests are honored before any buffer requests.

Figure 1-3. Block Control Priority Scheme

<u>Real-Time Clock:</u> The real-time clock is a 24-bit counter that is incremented each millisecond to a maximum period of 16,777,216\* milliseconds. After reaching its maximum count the clock returns to zero and the cycle is repeated. The clock, controlled by 1 kilocycle signals, starts as soon as power is applied to the computer. The current time is stored in register 22 of the Register File and is removed for updating and comparison with register 32 once every millisecond. When necessary the clock may be reset to any 24-bit quantity by loading A and then transferring (A) into register 22.

A Real-Time Clock Interrupt condition is generated when the current time (register 22) equals the time specified by the clock mask (register 32). Performing a master clear

\*16, 777, 216 milliseconds equal approximately 4 hours and 40 minutes.

does not affect the clock count. For a special case involving the real-time clock, refer to the Priority Pause (PRP) instruction in Section 6.

#### <u>Arithmetic</u>

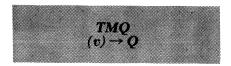

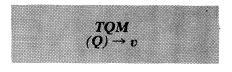

The Arithmetic section works in conjunction with the BDP and Main Control in performing all arithmetic (except address and index operations) and logical and shifting operations. This section contains the main operational registers. Those discussed here are displayed on the console. A and Q can be altered from the keyboard.

<u>A Register (24 bits)</u>: The A register (accumulator) is the principal arithmetic register. Some of the more important functions of this register are:

- Most arithmetic and logical operations use the A register in formulating a result. The A register is the only register with provisions for directly adding its contents to the contents of a storage location or another register.

- The A register may be shifted to the right or left separately or in conjunction with the Q register. Right shifting is end-off; the lowest bits are discarded and the sign is extended. Left shifting is end-around; the bit leaving the highest-order position appears in the lowest-order position after each shift; all other bits move one place to the left.

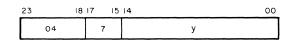

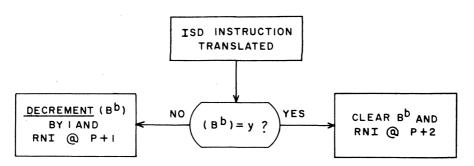

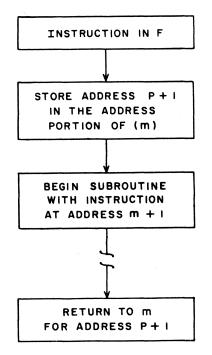

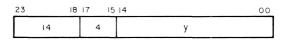

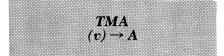

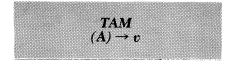

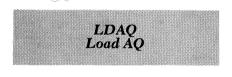

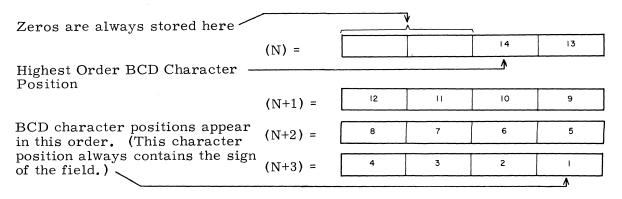

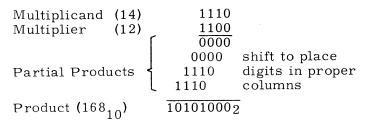

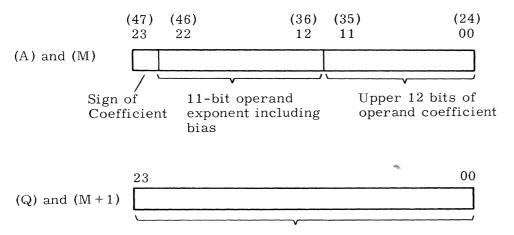

- I/O operations with the register are available (word and character).