### AE 500 Series

### EQUIPMENT REFERENCE MANUAL

COPYRIGHT C 1976, BURROUGHS MACHINES LIMITED, Hounslow, England COPYRIGHT C 1976, BURROUGHS CORPORATION, Detroit, Michigan 48232

PRICED ITEM

Printed in U.S. America

February 1976

Burroughs - Series AE500 Equipment Reference Manual

### LIST OF EFFECTIVE PAGES

NOTE: Insert latest changed page; dispose of superseded pages.

#### TOTAL NUMBER OF PAGES IN THIS MANUAL IS 166 CONSISTING OF THE FOLLOWING:

| TitleOriginalA PageOriginali thru ixOriginali thru ixOriginal $x$ BlankOriginal $1-1$ thru $1-4$ Original $2-1$ thru $2-7$ Original $2-1$ thru $2-7$ Original $2-8$ BlankOriginal $3-1$ thru $3-13$ Original $3-1$ thru $4-9$ Original $3-14$ BlankOriginal $4-1$ thru $4-9$ Original $4-1$ thru $5-13$ Original $5-1$ thru $5-13$ Original $5-1$ thru $5-13$ Original $5-14$ BlankOriginal $6-1$ thru $6-10$ Original $6-1$ thru $6-10$ Original $7-1$ thru $7-42$ Original $9-1$ thru $9-3$ Original $9-4$ BlankOriginal $10-1$ thru $10-3$ Original $10-4$ BlankOriginal $10-4$ BlankOriginal $10-4$ BlankOriginal $10-4$ BlankOriginal $10-4$ BlankOriginal $11-1$ thru $10-3$ Original $12$ thru $12$ Original $13$ thru $12$ Original <th>Page No.</th> <th></th> <th></th> <th></th> <th></th> <th></th> <th>Issue</th>                                | Page No.       |   |  |  |   |     | Issue    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---|--|--|---|-----|----------|

| A Page       Original         i thru ix       Original         x Blank       Original         1-1 thru 1-4       Original         2-1 thru 2-7       Original         2-1 thru 2-7       Original         2-8 Blank       Original         3-1 thru 3-13       Original         3-14 Blank       Original         3-14 Blank       Original         4-1 thru 4-9       Original         4-1 thru 4-9       Original         5-14 Blank       Original         5-14 Blank       Original         6-1 thru 5-13       Original         7-1 thru 7-42       Original         8-1 thru 6-10       Original         7-1 thru 7-42       Original         8-1 thru 8-18       Original         9-1 thru 9-3       Original         9-4 Blank       Original         10-1 thru 10-3       Original         10-4 Blank       Original         10-4 Blank       Original         11       Original         12       Original         13       Original         14       10         15       Original         16       Original                                                                                                                                 | Title          |   |  |  |   |     | Original |

| i thru ix       Original         x Blank       Original         1-1 thru 1-4       Original         2-1 thru 2-7       Original         2-1 thru 2-7       Original         2-8 Blank       Original         3-1 thru 3-13       Original         3-14 Blank       Original         3-14 Blank       Original         4-1 thru 4-9       Original         4-1 thru 5-13       Original         5-1 thru 5-13       Original         5-14 Blank       Original         6-1 thru 6-10       Original         7-1 thru 7-42       Original         8-1 thru 8-18       Original         9-1 thru 9-3       Original         9-1 thru 9-3       Original         10-1 thru 10-3       Original         10-4 Blank       Original         10-4 Blank       Original         10-4 Blank       Original         11       Original         12       Original         13       Original         14       12       Original         10-1 thru 10-3       Original         10-2 Blank       Original         11       Original         12<                                                                                                                       | A Page         |   |  |  |   |     | Original |

| x BlankOriginal1-1 thru 1-4Original2-1 thru 2-7Original2-8 BlankOriginal3-1 thru 3-13Original3-1 thru 3-13Original3-14 BlankOriginal4-1 thru 4-9Original4-1 thru 5-13Original5-1 thru 5-13Original5-1 thru 6-10Original6-1 thru 6-10Original7-1 thru 7-42Original8-1 thru 8-18Original9-4 BlankOriginal9-4 BlankOriginal10-1 thru 10-3Original10-4 BlankOriginal10-2 thru 10-3Original10-3Original10-4 BlankOriginal10-4 BlankOriginal10-1 thru 10-3Original10-1 thru 10-3Original10-1 thru 84Original11-1 thru 84Original12-1 thru 95Original13-1 thru 95Original14-1 thru 10-3Original15-1 thru 10-3Original16-1 thru 10-3Original17-1 thru 10-3Original18-1 thru 10-3Original19-1 thru 10-3Original10-1 thru 10-3Original10-1 thru 10-3Original11-1 thru 10-3Original12-1 thru 10-3Original13-1 thru 10-3Original14-1 thru 10-3Original15-1 thru 10-3Original16-1 thru 10-3Original17-1 thru 10-3Original                                                                                                                                                                                                                                          |                |   |  |  |   |     | Original |

| 1-1 thru $1-4$ Original $2-1$ thru $2-7$ Original $2-8$ BlankOriginal $3-1$ thru $3-13$ Original $3-1$ thru $3-13$ Original $3-14$ BlankOriginal $4-1$ thru $4-9$ Original $4-1$ thru $4-9$ Original $4-1$ thru $5-13$ Original $5-1$ thru $5-13$ Original $5-14$ BlankOriginal $5-14$ BlankOriginal $5-14$ BlankOriginal $5-14$ BlankOriginal $5-14$ BlankOriginal $6-1$ thru $6-10$ Original $7-1$ thru $7-42$ Original $9-1$ thru $9-3$ Original $9-1$ thru $9-3$ Original $9-4$ BlankOriginal $10-1$ thru $10-3$ Original $10-4$ BlankOriginal $11-4$ OriginalOriginal $11-4$ DriginalOriginal $11-4$ DriginalOriginal $11-4$ OriginalOriginal $11-4$ Origina                                                                                                                                        | x Blank        |   |  |  |   |     | Original |

| 2-8 Blank       Original         3-1 thru 3-13       Original         3-14 Blank       Original         4-1 thru 4-9       Original         4-1 thru 4-9       Original         4-10 Blank       Original         5-1 thru 5-13       Original         5-14 Blank       Original         6-1 thru 6-10       Original         7-1 thru 7-42       Original         8-1 thru 8-18       Original         9-1 thru 9-3       Original         9-1 thru 9-3       Original         9-4 Blank       Original         10-1 thru 10-3       Original         10-4 Blank       Original         110-4 Blank       Original         110-1 thru 10-3       Original         110-1 thru 10-3       Original         110-2 thru 10-3       Original         110-4 Blank       Original         110-1 thru 10-3       Original         110-1 thru 10-3 <td< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td>Original</td></td<> |                |   |  |  |   |     | Original |

| 3-1 thru 3-13       Original         3-14 Blank       Original         4-1 thru 4-9       Original         4-1 thru 4-9       Original         4-1 thru 4-9       Original         4-10 Blank       Original         5-1 thru 5-13       Original         5-14 Blank       Original         5-14 Blank       Original         6-1 thru 6-10       Original         7-1 thru 7-42       Original         8-1 thru 8-18       Original         9-1 thru 9-3       Original         9-4 Blank       Original         9-4 Blank       Original         10-4 Blank       Original         10-4 Blank       Original         10-4 Blank       Original         110-4 Blank       Original         110-1 thru 10-3       Original         110-2 Elank       Original         110-1 thru 10-3       Original         110-1 thru 10-3       Original         12 thru 8-1       Original                                                                                         | 2-1 thru 2-7.  |   |  |  |   |     | Original |

| 3-14 Blank       Original         4-1 thru 4-9       Original         4-10 Blank       Original         5-1 thru 5-13       Original         5-14 Blank       Original         5-14 Blank       Original         5-14 Blank       Original         5-14 Blank       Original         6-1 thru 5-13       Original         6-1 thru 6-10       Original         6-1 thru 6-10       Original         7-1 thru 7-42       Original         8-1 thru 8-18       Original         9-1 thru 9-3       Original         9-4 Blank       Original         9-4 Blank       Original         10-1 thru 10-3       Original         10-4 Blank       Original         10-4 Blank       Original         110-4 Blank       Original         110-4 Blank       Original         110-4 Blank       Original         1110-4 Blank       Original         1110-4 Blank       Original         1110-4 Blank       Original         1110-4 Blank       Original         1110-1 thru 10-3       Original         1110-1 thru 10-3       Original         1110-1 thru 10-3       Orig                                                                                    | 2-8 Blank      |   |  |  |   |     | Original |

| 4-1 thru 4-9       Original         4-10 Blank       Original         5-1 thru 5-13       Original         5-14 Blank       Original         6-1 thru 6-10       Original         7-1 thru 7-42       Original         8-1 thru 8-18       Original         9-1 thru 9-3       Original         9-1 thru 9-3       Original         9-4 Blank       Original         10-1 thru 10-3       Original         10-4 Blank       Original         10-4 Blank       Original         110-4 Blank       Original         110-1 thru 12       Original         110-2 thru 12       Original         110-4 Blank       Original         110-1 thru 12       Original         110-1 thru 12       Original         110-1 thru 12       Original         110-1 thru 12       Original                                                                                    | 3-1 thru 3-13  |   |  |  |   |     | Original |

| 4-10 Blank       Original         5-1 thru 5-13       Original         5-14 Blank       Original         6-1 thru 6-10       Original         7-1 thru 7-42       Original         8-1 thru 8-18       Original         9-1 thru 9-3       Original         9-4 Blank       Original         10-1 thru 10-3       Original         10-4 Blank       Original         10-4 Blank       Original         10-4 Blank       Original         10-1 thru 10-3       Original         10-2 Blank       Original         11 thru A12       Original         12 Driginal       Original         13 Driginal       Original         14 thru B4       Original         15 thru B4       Original         16 thru E2       Original         17 thru F2       Original         18 thru F2       Original         19 thru F2       Original                                                                                                                                                                                                                                                                                                                         | 3-14 Blank .   |   |  |  |   |     | Original |

| 5-1 thru 5-13       Original         5-14 Blank       Original         6-1 thru 6-10       Original         7-1 thru 7-42       Original         8-1 thru 8-18       Original         9-1 thru 9-3       Original         9-4 Blank       Original         10-1 thru 10-3       Original         10-4 Blank       Original         10-4 Blank       Original         10-4 Blank       Original         10-4 Blank       Original         10-2 Blank       Original         11 thru 84       Original         12 Blank       Original         13 C1       Original         14 thru B4       Original         15 thru B4       Original         16 thru B4       Original         17 thru F2       Original         18 thru B4       Original         19 thru F2       Original         10 thru F2       Original         17 thru F2       Original         18 thru F2       Original         19 thru F2       Original         11 thru F2       Original         11 thru F2       Original         11 thru F2       Original         11 t                                                                                                              | 4-1 thru 4-9.  |   |  |  |   |     | Original |

| 5-14 Blank       Original         6-1 thru 6-10       Original         7-1 thru 7-42       Original         8-1 thru 8-18       Original         9-1 thru 9-3       Original         9-4 Blank       Original         10-1 thru 10-3       Original         10-4 Blank       Original         10-4 Blank       Original         110-4 Blank       Original         12 Blank       Original         13 C1       Original         14 C1       Original         15 C2 Blank       Original         16 D1       Original         17 Hru F2       Original         18 Original       Original         19 Original       Original         10 Original       Original         10                                                                                                               | 4-10 Blank .   |   |  |  |   |     | Original |

| 6-1 thru 6-10       Original         7-1 thru 7-42       Original         8-1 thru 8-18       Original         9-1 thru 9-3       Original         9-4 Blank       Original         10-1 thru 10-3       Original         10-4 Blank       Original         10-2 Blank       Original         C1       Original         C2 Blank       Original         D1       Original         D2 Blank       Original         G1       Original         G1       Original                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-1 thru 5-13  |   |  |  |   |     | Original |

| 7-1 thru 7-42       Original         8-1 thru 8-18       Original         9-1 thru 9-3       Original         9-4 Blank       Original         10-1 thru 10-3       Original         10-4 Blank       Original         110-4 Blank       Original         110-1 C       Original         120 Blank       Original         121 Blank       Original         121 thru E2       Original         121 thru F2       Original         121 thru F2       Original         121 thru F2       Original                                                                                                                  | 5-14 Blank .   |   |  |  |   |     | Original |

| 8-1 thru 8-18       Original         9-1 thru 9-3       Original         9-4 Blank       Original         10-1 thru 10-3       Original         10-4 Blank       Original         110-4 Blank       Original         10-4 Blank       Original         10-4 Blank       Original         10-4 Blank       Original         110-4 Blank       Original         110-1 C       Original         1110-1 C <t< td=""><td>6–1 thru 6–10</td><td></td><td></td><td></td><td></td><td></td><td>Original</td></t<>                        | 6–1 thru 6–10  |   |  |  |   |     | Original |

| 9-1 thru 9-3       Original         9-4 Blank       Original         10-1 thru 10-3       Original         10-4 Blank       Original         10-4 Blank       Original         10-4 Blank       Original         10-4 Blank       Original         110-4 Blank       Original         10-4 Blank       Original         10-4 Blank       Original         10-4 Blank       Original         110-4 Blank       Original         120-4 Blank       Original         120-5 Blank       Original         120-6 Blank       Original         121-7       Original                                                                                                                                      | 7-1 thru 7-42  |   |  |  |   |     | Original |

| 9-1 thru 9-3.       Original         9-4 Blank       Original         10-1 thru 10-3       Original         10-4 Blank       Original         10-4 Blank       Original         A1 thru A12       Original         B1 thru B4       Original         C1       Original         D1       Original         D2 Blank       Original         E1 thru E2       Original         F1 thru F2       Original         G1       Original                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8-1 thru 8-18  |   |  |  |   |     | Original |

| 10-1 thru 10-3Original10-4 BlankOriginalA1 thru A12OriginalB1 thru B4OriginalC1OriginalC2 BlankOriginalD1OriginalD2 BlankOriginalF1 thru E2OriginalF1 thru F2OriginalG1OriginalG1OriginalOriginalOriginalOriginalOriginalOriginalOriginalOriginalOriginalOriginalOriginalOriginalOriginalOriginalOriginalOriginalOriginalOriginalOriginalOriginalOriginalOriginalOriginal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9-1 thru 9-3.  |   |  |  |   | ÷ . | Original |

| 10-4 BlankOriginalA1 thru A12OriginalB1 thru B4OriginalC1OriginalC2 BlankOriginalD1OriginalD2 BlankOriginalE1 thru E2OriginalF1 thru F2OriginalG1OriginalOriginalG1Original                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 9-4 Blank      |   |  |  |   |     | Original |

| A1 thru A12OriginalB1 thru B4OriginalC1OriginalC2 BlankOriginalD1OriginalD2 BlankOriginalE1 thru E2OriginalF1 thru F2OriginalG1OriginalOriginalG1Original                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10-1 thru 10-3 |   |  |  |   |     | Original |

| B1 thru B4OriginalC1OriginalC2 BlankOriginalD1OriginalD2 BlankOriginalD1 thru E2OriginalF1 thru F2OriginalG1OriginalOriginalOriginalOriginalOriginal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10-4 Blank .   |   |  |  |   |     | Original |

| C1OriginalC2 BlankOriginalD1OriginalD2 BlankOriginalD2 BlankOriginalE1 thru E2OriginalF1 thru F2OriginalG1Original                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | A1 thru A12 .  |   |  |  |   |     | Original |

| C2 BlankOriginalD1OriginalD2 BlankOriginalD2 BlankOriginalE1 thru E2OriginalF1 thru F2OriginalG1Original                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | B1 thru B4     |   |  |  |   |     | Original |

| D1OriginalD2 BlankOriginalE1 thru E2OriginalF1 thru F2OriginalG1Original                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | C1             |   |  |  |   |     | Original |

| D2 BlankOriginalE1 thru E2OriginalF1 thru F2OriginalG1Original                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | C2 Blank       |   |  |  |   |     | Original |

| E1 thru E2       .       .       .       Original         F1 thru F2       .       .       .       .       Original         G1       .       .       .       .       .       Original                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | D1             |   |  |  |   |     | Original |

| F1 thru F2         .         .         .         Original           G1         .         .         .         .         .         Original                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | D2 Blank       |   |  |  |   |     | Original |

| G1 Original                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | E1 thru E2     |   |  |  |   |     | Original |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | F1 thru F2.    |   |  |  |   |     | Original |

| G2 Blank Original                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | G1             |   |  |  |   |     | Original |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | G2 Blank       | • |  |  | • |     | Original |

1 30

Burroughs believes that the information described in this manual is accurate and reliable, and much care has been taken in its preparation. However, no responsibility, financial or otherwise, is accepted for any consequences arising out of the use of this material. The information contained herein is subject to change. Revisions may be issued to advise of such changes and/or additions. A PAGE

| Section |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Page                                                                                                   |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| 1       | GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                        |

|         | IntroductionMachine DescriptionI/O ChannelsProcessorMemoryKeyboardOperator Communication SystemPrinterForms HandlerMagnetic Tape Cassette SubsystemData CommunicationSystems Software                                                                                                                                                                                                                                                                                                                                              | $ \begin{array}{c} 1-1\\ 1-2\\ 1-2\\ 1-2\\ 1-2\\ 1-3\\ 1-3\\ 1-3\\ 1-3\\ 1-4\\ 1-4\\ 1-4 \end{array} $ |

| 2       | PROCESSOR AND MEMORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                        |

| 3       | General<br>Processor<br>Memory<br>Random Access Memory (RAM)<br>Read Only Memory (ROM)<br>Input/Output Interface<br>I/O Control.<br>Data Highway<br>Address Lines (ADDR)<br>Request Lines (REQ)<br>Direction (DIRN).<br>Control (CNTL)<br>Input/Output Exchange (IOX).<br>Device Dependent Controllers.                                                                                                                                                                                                                            | 2-1  2-1  2-3  2-4  2-5  2-6  2-6  2-6  2-6  2-6  2-6  2-6  2-6  2-6  2-6  2-7  2-7  2-7               |

|         | Keyboard         Ready Key         Numeric Keyboard         Numeric Keys         Decimal Point Key         Reset Key         Per Hundred Key (C).         Per Thousand Key (M)         Reverse Entry Key (RE)         Operation Control Keys (OCK)         Typewriter Keyboard         Typing Keys (64 Character)         Shift Keys (SHIFT)         Shift Lock Keys (SHIFT LOCK)         Line Advance Xeys         Repeat Keys (REPEAT)         Space Bar (Unmarked)         Backspace Key.         Operation Control Keys (OCK). | $\begin{array}{c} 3-1\\ 3-1\\ 3-2\\ 3-2\\ 3-2\\ 3-2\\ 3-2\\ 3-2\\ 3-2\\ 3-3\\ 3-3$                     |

|         | Group S Indicators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-4<br>3-4                                                                                             |

| Section |                                            | Page       |

|---------|--------------------------------------------|------------|

| 3       | Exception Condition Indicators             | 3-5        |

|         | Data Communication Indicators              | 3-5        |

|         | Console Printer.                           | 3-5        |

|         | Print Characters                           | 3-5        |

|         | Printer Ribbon.                            | 3-7        |

|         | Changing the Ribbon                        | 3-7        |

|         | Forms Handler.                             | 3–9        |

|         | Vertical Spacing                           | 3-9        |

|         | Visibility Mode (Clear Head Feature)       | 3-9        |

|         | Paper Loading                              | 3-10       |

|         | Forms Specifications.                      | 3-1        |

|         | Perforations                               | 3-1        |

|         | Sprocket Holes                             | 3-1        |

|         | Forms Handler Options                      | 3-1        |

|         | Other Operator Controls                    | 3-1        |

|         | Cold Start Button.                         | 3-1        |

|         | System Test Switch                         | 3-1        |

|         | Overload Cutout                            | 3-1        |

|         | Overload Catcat                            |            |

| 4       | PERIPHERALS                                |            |

|         | Manuatia Trans Crossitia                   | 4-1        |

|         | Magnetic Tape Cassette                     | 4—1<br>4—1 |

|         | Cassette                                   | 4—1<br>4—1 |

|         | Cassette Use                               | 4-1        |

|         | Data Recording Technique                   |            |

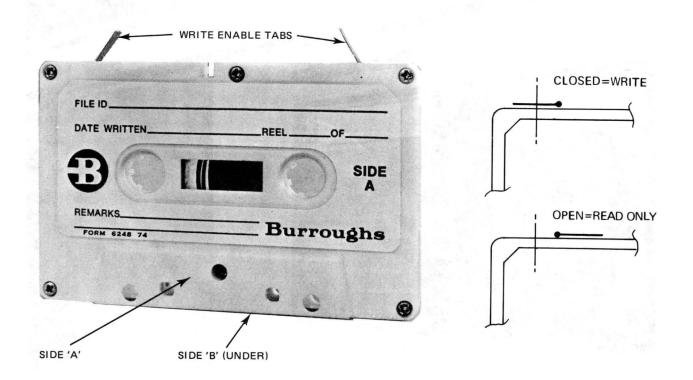

|         | Write Enable Tabs.                         | 4—2<br>4—2 |

|         | Tape Cassette Handling                     |            |

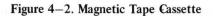

|         | Cassette Tape Format                       | 4-3        |

|         | Clear Leader                               | 4-3        |

|         | BOT Mark (Beginning of Tape)               | 4-3        |

|         | Inter-Record Gap                           | 4-3        |

|         | Records                                    | 44         |

|         | Preamble/Postamble Character               | 4-4        |

|         | Data Characters                            | 4-4        |

|         | CRC – Cyclical Redundancy Check Characters | 4-5        |

|         | NUL Character.                             | 4-5        |

|         | Tape Mark                                  | 4-5        |

|         | File                                       | 4-5        |

|         | EOT (End of Tape)                          | 4-5        |

|         | Cassette Drive Unit                        | 45         |

|         | Operating Functions and Speeds             | 4-5        |

|         | Controls                                   | 4-6        |

|         | Drive Unit Door                            | 4-6        |

|         | Drive Unit Power                           | 4-6        |

|         | Indicators                                 | 4-6        |

|         | Ready Light                                | 4-6        |

|         | Write Enable Light                         | 4—7        |

|         | Exception Condition Indicators             | 4-7        |

|         | Hardware Functions                         | 4-7        |

|         | Automatic Stop                             | 4—7        |

|         | Automatic Rewind to Clear Leader           | 4—7        |

|         | Cassette Function Overlap                  | 4—7        |

|         | Write Considerations.                      | 4-7        |

| Section |                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page                                                                                                                          |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| 4       | Programmatic FunctionsWriteWrite Tape MarkReadSearchForward to Tape MarkReverse to Tape MarkBackspaceRewindRewind and Inhibit WriteEraseMaintenance                                                                                                                                                                                                                                                                                                   | $\begin{array}{c} 4-8 \\ 4-8 \\ 4-8 \\ 4-8 \\ 4-9 \\ 4-9 \\ 4-9 \\ 4-9 \\ 4-9 \\ 4-9 \\ 4-9 \\ 4-9 \\ 4-9 \\ 4-9 \end{array}$ |

| 5       | DATA COMMUNICATIONS SUBSYSTEM                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                               |

|         | IntroductionData Communication NetworksCommunication ModesPhysical LinkingVoice Grade LinesDirect ConnectAE500 Data Communications HardwareAsynchronous Data Communications Controller.External Interface.Internal Interface.ADC Variable CharacteristicsNumber of Data BitsNumber of Stop Bits.Generate/Check ParityParity Even/Odd                                                                                                                  | $5-1 \\ 5-1 \\ 5-1 \\ 5-1 \\ 5-2 \\ 5-2 \\ 5-2 \\ 5-2 \\ 5-3 \\ 5-3 \\ 5-3 \\ 5-4 \\ 5-4 \\ 5-4 \\ 5-5 \\ 5-5 \\ 5-5 $        |

|         | Transmit/Receive Rate         Synchronous Data Communications Controller         External Interface         Internal Interface         SDC Variable Characteristics         SDC Variable Characteristics         Character Parity Options         Block Check Options         Transmit/Receive Rate         Concatenate/Wraparound/Modem Interface (CWM).         Connection to Data Set         Wraparound.         Two Wire Direct Interface (TDI). | 5-5<br>5-6<br>5-7<br>5-7<br>5-7<br>5-7<br>5-7<br>5-8<br>5-9<br>5-9<br>5-9<br>5-10<br>5-10                                     |

|         | Two Wire Direct Interface                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-10                                                                                                                          |

| Section |                                                       | Page |

|---------|-------------------------------------------------------|------|

| 6       | VIRTUAL SYSTEM                                        |      |

|         | Introduction                                          | 6-1  |

|         | Executive                                             | 6-1  |

|         | Control States                                        | 61   |

|         | Ready State                                           | 6-2  |

|         | Standby State                                         | 6-3  |

|         | Execute State                                         | 6-3  |

|         | Basic Virtual Machine                                 | 6-3  |

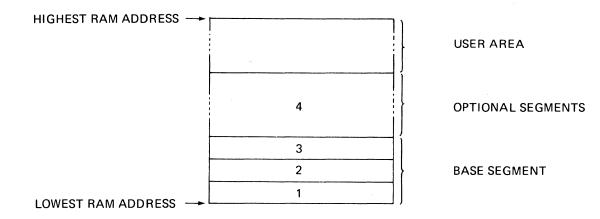

|         | Memory Organisation                                   | 6–3  |

|         | Interpreter Memory                                    | 6-3  |

|         | User Memory                                           | 6-3  |

|         | SL3 Instruction Format.                               | 6-4  |

|         | SL5 Instruction Format.                               | 6-5  |

|         | Data Communications Virtual Machine.                  | 6-5  |

|         | Implementation Using a Single Processor               | 6-7  |

|         | Virtual Machine Communication                         | 6-7  |

|         | Special Consideration                                 | 6–7  |

|         | Interpreter                                           | 6–8  |

|         | Base Segment                                          | 6-8  |

|         | Interpreter Registers                                 | 6-8  |

|         | Interpreter Work Areas                                | 6-8  |

|         | Micro-Coded Routines                                  | 6-8  |

|         | Interrupt Handling Facilities                         | 6-9  |

|         | Basic S-Language Instructions Routines                | 6-9  |

|         | Optional Segments                                     | 6–9  |

|         | Keyboard and Printer Translation Segment              | 6-9  |

|         | Data Communication Base Segment.                      | 6–9  |

|         | Data Communication Transmit and Receive Buffers (SL3) | 6-9  |

|         | Data Handling 1 Segment                               | 6-9  |

|         | Magnetic Tape Cassette Input/Output (I/O) Segment     | 6–9  |

|         | Magnetic Tape Cassette Translation Tables             | 6-10 |

|         | Software Special Segment                              | 6-10 |

|         | Check Digit Compute and Verify (CDC/V) Segment        | 6-10 |

|         | Cold Start                                            | 6-10 |

#### 7 SYSTEMS REGISTERS

| Basic Registers                     | 7-1 |

|-------------------------------------|-----|

| User Memory Base Address.           | 7-1 |

| User Memory Limit Address           | 7-1 |

| Type of Virtual Machine             | 7-2 |

| Clear Print Head Time-Out           | 7-2 |

| Monetary Safeguard Symbol           | 7–3 |

| European Punctuation                | 7–3 |

| Tape Cassette Ready Retry           | 7–4 |

| Tape Cassette Write Retry           | 7—4 |

| Tape Cassette Tape Mark Write Retry | 7—5 |

| Tape Cassette Input Translation     | 7—5 |

| Tape Cassette Output Translation    | 7–6 |

| SL3 Data Comm Line Procedure        | 7—7 |

| SL3 CTCC/Message Unpack             | 7-7 |

| Section |                                        | Page |

|---------|----------------------------------------|------|

| 7       | Data Communications Registers          | 7—8  |

|         | Idle Line Timer                        | 7-8  |

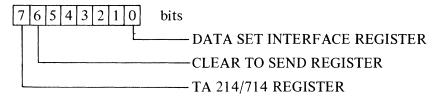

|         | Data Set Register Group                | 7–9  |

|         | Data Set Interface.                    | 7–9  |

|         | Clear to Send                          | 7-10 |

|         | TA214/714                              | 7-10 |

|         | D/C Buffer Length                      | 7-11 |

|         | Procedure Area 1                       | 7-11 |

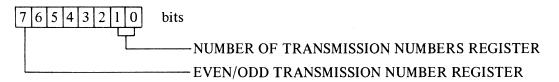

|         | Transmission Number Register Group     | 7-12 |

|         | Number of Transmission Numbers         | 7-12 |

|         | Even/Odd Transmission Number           | 7-13 |

|         | Synchronous Compare Character.         | 7-14 |

|         | Transmit/Receive Flags Register Group  | 7-14 |

|         | Parity                                 | 7-15 |

|         | VRC                                    | 7-15 |

|         | Synchronous Generate LRC/CRC Register  | 7-16 |

|         | Synchronous Check BCC                  | 7-16 |

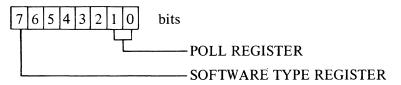

|         | D/C Operation Mode Register Group      | 7-17 |

|         | Poll                                   | 7-17 |

|         | Software Type                          | 7-17 |

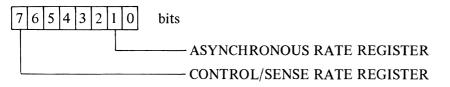

|         | Transmission Rate Register Group       | 7-18 |

|         | Asynchronous Rate                      | 7-18 |

|         | Control/Sense Rate                     | 7–19 |

|         | Four Wire Receive Delay                | 7–19 |

|         | Four Wire Transmit Delay               | 720  |

|         | Procedure Area 2                       | 7-21 |

|         | Ring Limit                             | 7-21 |

|         | Two Wire Receive Delay                 | 7–22 |

|         | Two Wire Transmit Delay                | 7—22 |

|         | D/C Send Buffer Address                | 7-23 |

|         | D/C Receive Buffer Address             | 7–23 |

|         | Transmit Machine Address               | 7–24 |

|         | Receive Machine Address                | 7–24 |

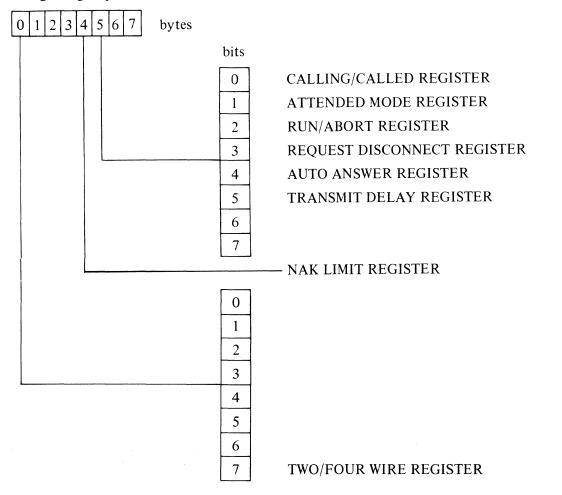

|         | Two/Four Wire Register                 | 7—25 |

|         | Calling/Called                         | 7–26 |

|         | Attended Mode                          | 7–26 |

|         | Run/Abort                              | 7—27 |

|         | Request Disconnect                     | 7–27 |

|         | Auto Answer                            | 7–28 |

|         | Transmit Delay                         | 7–28 |

|         | NAK Limit                              | 7–28 |

|         | Two/Four Wire                          | 7-29 |

|         | Send Transmission Number               | 7-29 |

|         | Expected Transmission Number           | 7–30 |

|         | Expected Group Transmission Number.    | 7–31 |

|         | Expected Broadcast Transmission Number | 7-31 |

|         | Transmission Header                    | 7-32 |

|         | Problem Flag                           | 7-32 |

|         | Special Options Byte                   | 7–33 |

|         | Accumulator                            | 7–33 |

|         | Index Registers                        | 7-34 |

|         | Remainder                              | 7-34 |

|         | Scale Register                         | 7–34 |

| Section |                                                             | Page         |

|---------|-------------------------------------------------------------|--------------|

| 7       | Program Select Key Table                                    | 7-35         |

|         | Program Select Key Enabled Register                         | 7-35         |

|         | Keyboard Base.                                              | 7–35         |

|         | Send Character Pointer                                      | 7-36         |

|         | Receive Buffer                                              | 7–36         |

|         | Receive Character Pointer                                   | 7–36         |

|         | Print Numeric Mask                                          | 7–37         |

|         | Position Register                                           | 7-37         |

|         | Left Forms Count.                                           | 7–37         |

|         | Left Forms Limit                                            | 7-38         |

|         | Right Forms Count                                           | 7–38         |

|         | Right Forms Limit                                           | 7–38         |

|         | Subroutine Stack                                            | 7–39         |

|         | Flag Registers                                              | 7–39         |

|         | Accumulator Flags (Group A).                                | 7-40         |

|         | Keyboard Buffer Flags (Group B)                             | 7-40         |

|         | Data Communications Flags (Group D).                        | 7-40         |

|         | Input/Output Exception Flags (Group E) (SL5 only)           | 7–40<br>7–40 |

|         | Operator Control Key Flags (Group K).                       | 7-41         |

|         | Scale Register Flags (Group L)                              | 7-41<br>7-41 |

|         | General Purpose Flags (Group P).                            | 7-41         |

|         | General Purpose Flags (Group R).                            | 7-41         |

|         | Test Flags (Group T).                                       | 7-42         |

|         | General Purpose Flags (Group X).                            | 7-42         |

|         | General Purpose Flags (Group Y).                            | 7-42         |

| 8       | DATA COMMUNICATIONS LINE PROCEDURES                         |              |

|         | Control Characters                                          | 8-1          |

|         | ACK – Acknowledgement                                       | 8-1          |

|         | AD1, AD2 – Address Characters 1 and 2                       | 8-1          |

|         | BCC – Block Check Character.                                | 8-1          |

|         | BSL – Broadcast Select.                                     | 8-1          |

|         | CON – Contention                                            | 8-1          |

|         | DEOT – Mandatory Disconnect                                 | 8 - 1        |

|         | DLE – Data Link Escape                                      | 8-1          |

|         | ENQ – Enquiry                                               | 8-1          |

|         | EOT – End of Transmission                                   | 8-1          |

|         | ETX – End of Text                                           | 8-1          |

|         | FSL – Fast Select.                                          | 8-2          |

|         | GSL – Group Select                                          | 8-2          |

|         | NAK – Negative Acknowledgement.                             | 8-2          |

|         | $POL - Poll \dots$                                          | 8-2          |

|         | RVI – Reverse Interrupt (DLE <)                             | 8-2          |

|         | SEL – Select                                                | 8-2          |

|         | SOH – Start of Header                                       | 8-2          |

|         | STX – Start of Text                                         | 8-2          |

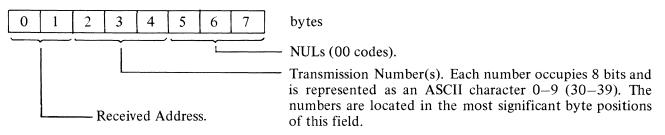

|         | TR $\#$ – Transmission Number                               | 8-2          |

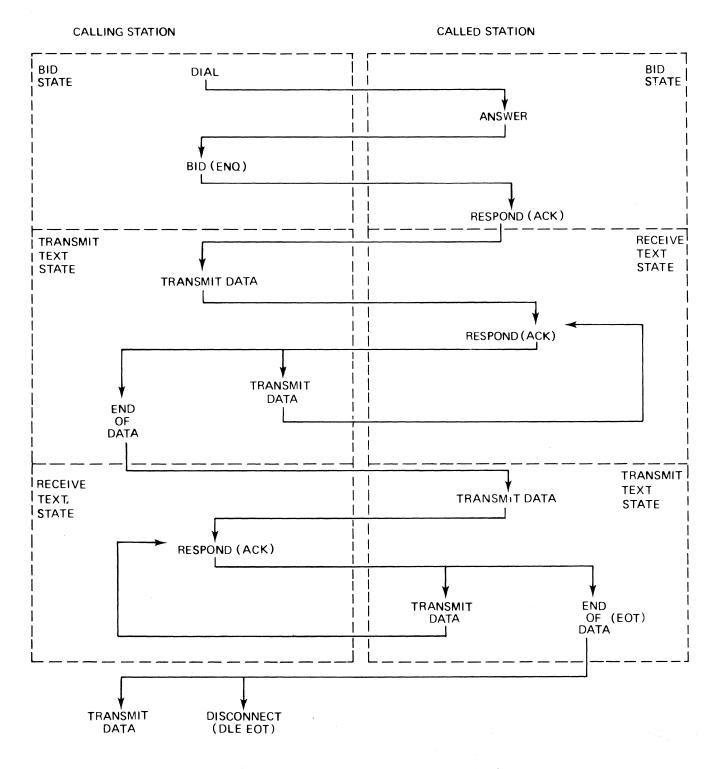

|         | Asynchronous Point to Point (Switched Batch) Line Procedure | 8-2          |

|         | Bid State                                                   | 8-4          |

|         | Idle Loop                                                   | 84           |

|         | Transmit Text State                                         | 8-4          |

|         | Receive Text State                                          | 8-5          |

|         | System Registers                                            | 8-8          |

Ĺ

| Section |                                                                      | Page           |

|---------|----------------------------------------------------------------------|----------------|

| 8       | Data Set Interface.                                                  | 8-8            |

|         | Clear to Send                                                        | 8-8            |

|         | TA 214/714                                                           | 8-8            |

|         | D/C Buffer Length                                                    | 8-9            |

|         | Procedure Area 1                                                     | 8-9            |

|         | Number of Transmission Numbers                                       | 8-9            |

|         | Parity                                                               | 8-9            |

|         | VRC                                                                  | 8-9            |

|         | Asynchronous Rate                                                    | 8–9            |

|         | Control/Sense Rate                                                   | 8-10           |

|         | Four Wire Receive Delay                                              | 8-10           |

|         | Four Wire Transmit Delay                                             | 8-10           |

|         | Two Wire Receive Delay                                               | 8-10           |

|         | Two Wire Transmit Delay                                              | 8-10           |

|         | D/C Send Buffer Address                                              | 8-11           |

|         | D/C Receive Buffer Address                                           | 8-11           |

|         | Transmit Machine Address                                             | 8-11           |

|         | Calling/Called                                                       | 8-11           |

|         | Attended Mode                                                        | 8-12           |

|         | Run/Abort                                                            | 8-12           |

|         | Request Disconnect                                                   | 8-13           |

|         | Auto Answer                                                          | 8-13           |

|         | Transmit Delay                                                       | 8-14           |

|         | NAK Limit                                                            | 8-14           |

|         | Two/Four Wire                                                        | 8-15           |

|         | Send Transmission Number.                                            | 8-15           |

|         | Expected Transmission Number                                         | 8-15           |

|         | Transmission Header                                                  | 8-15           |

|         | Problem Flag                                                         | 8-15           |

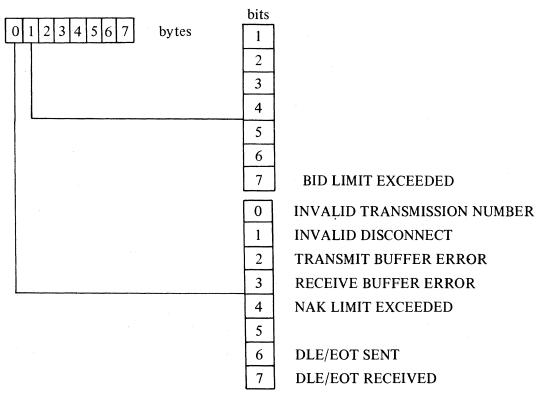

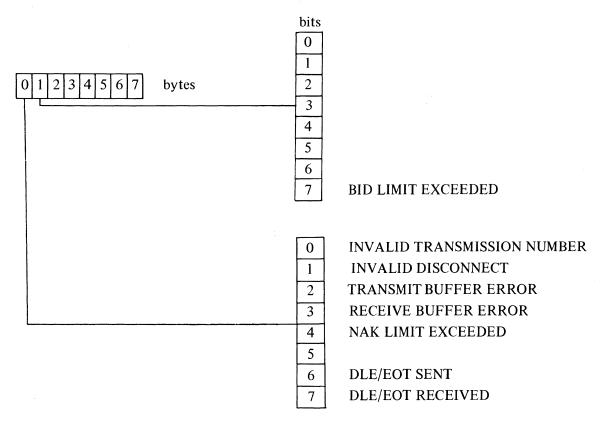

|         | Bid Limit Exceeded Flag                                              | 8-16           |

|         | Invalid Transmission Number Flag                                     | 8-16           |

|         | Invalid Disconnect Flag.                                             | 8-16           |

|         | Transmit Buffer Error Flag.                                          | 8-17           |

|         | Receive Buffer Error Flag                                            | 8-17           |

|         | NAK Limit Exceeded Flag.                                             | 8-17           |

|         | DLE/EOT Sent Flag                                                    | 8-17           |

|         | DLE/EOT Received Flag                                                | 8-17           |

|         | Data Communications Flags                                            | 8-17           |

|         | Data Comm Indicator Lights                                           | 8-17           |

|         | DTA R (Data Received)                                                | 8-17           |

|         | DTA S (Data Transmit Ready)                                          | $8-17 \\ 8-17$ |

|         | CTL R (Control Character Received)<br>CTL S (Control Character Sent) | 8—17<br>8—17   |

|         | Hardware Considerations                                              | 8-17           |

|         |                                                                      | 0-1/           |

#### 9 UTILITIES

| Concepts                        | 9-1 |

|---------------------------------|-----|

| Memory Load Routine             | 9-1 |

| Magnetic Tape Cassette S-Loader | 9-1 |

| Intrinsics                      | 9-1 |

| Magnetic Tape Cassette S-Dump   | 9-1 |

| Basic System Register Utility   | 9-1 |

| Section |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page                                                                                                   |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| 9<br>10 | Data Communications System Register UtilityTraceMemory ListS-Level UtilitiesBasic System Register UtilityData Communications System Register UtilityTranslation Table GeneratorCassette to Cassette/Print (Object)Cassette to Cassette/Print (Data)Cassette Copy (Data/Object)Cassette to Console (Data)Cassette to Console (Data)Customer Confidence ProgramENVIRONMENTAL SPECIFICATIONSIntroductionPower SupplyProtectionInternational StandardsLine CordElectrical Specification PlateCassette Drive UnitEnvironmental SpecificationsDimensionsConsole and Processor CabinetClearancesMaximum Heat OutputEnvironmental ConditionsTemperature | Page<br>9-1<br>9-2<br>9-2<br>9-2<br>9-2<br>9-2<br>9-3<br>9-3<br>9-3<br>9-3<br>9-3<br>9-3<br>9-3<br>9-3 |

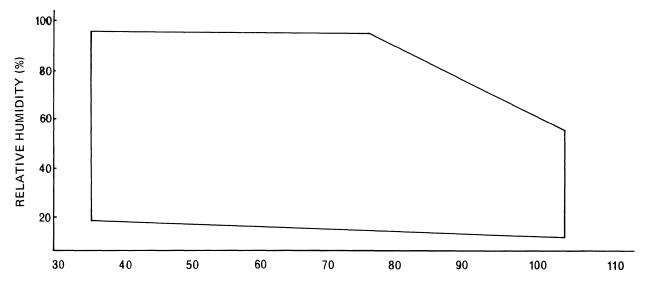

|         | Relative Humidity       Barometric Pressure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10–3<br>10–3                                                                                           |

| APPEN   | IDIX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                        |

| Α       | GLOSSARY OF TERMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                        |

| В       | ALPHA AND NUMERIC KEYBOARD VARIANTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                        |

| С       | EXCEPTION CONDITION INDICATORS Input/Output Errors Magnetic Tape Cassette System Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | C1<br>C1<br>C1                                                                                         |

| D       | USA STANDARD CODE FOR INFORMATION INTERCHANGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                        |

| Ε       | S-INSTRUCTIONS<br>Basic Segment<br>Data Handling/Segment<br>Data Comm Base Segment<br>Cassette I/O Segment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | E1<br>E1<br>E1<br>E2                                                                                   |

|         | Check Digit Compute/Verify Segment<br>Software Specials                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | E2<br>E2                                                                                               |

| FLAG SETTINGS          |            |

|------------------------|------------|

| Y and K Flags          | <b>F</b> 1 |

| E (L) Flags            | <b>F</b> 2 |

| Magnetic Tape Cassette | F2         |

#### RELATED DOCUMENTATION G

F

| LIST OF ILLUSTR. | ATIONS |

|------------------|--------|

|------------------|--------|

| Figure |                                                                   |       |

|--------|-------------------------------------------------------------------|-------|

| 1 - 1  | AE500 Intelligent Terminal System                                 | 1 - 1 |

| 1 - 2  | Panel Indicators                                                  | 1-3   |

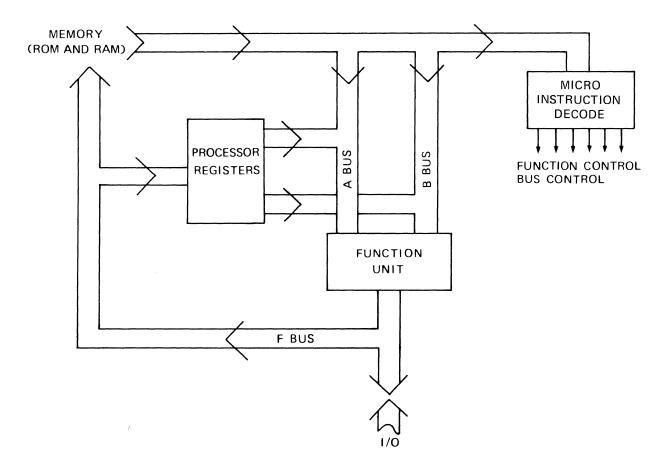

| 2 - 1  | The Processor                                                     | 2 - 1 |

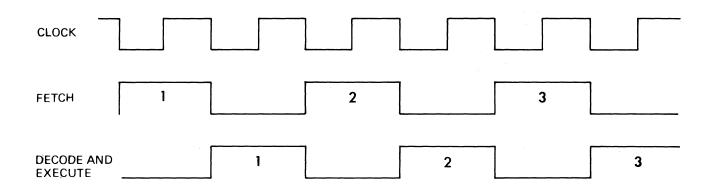

| 2-2    | Conventional Timing.                                              | 2-2   |

| 2-3    | Overlapped Timing                                                 | 2 - 2 |

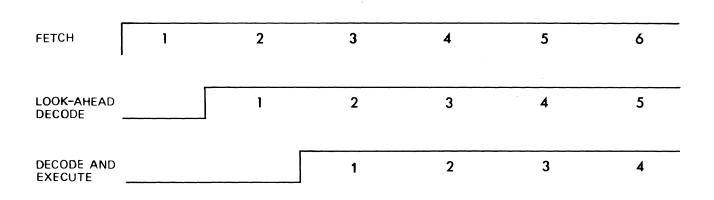

| 2–4    | Physical Memory Organisation                                      | 2-3   |

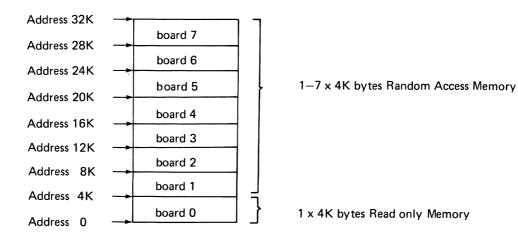

| 2-5    | Input/Output Interface                                            | 2-7   |

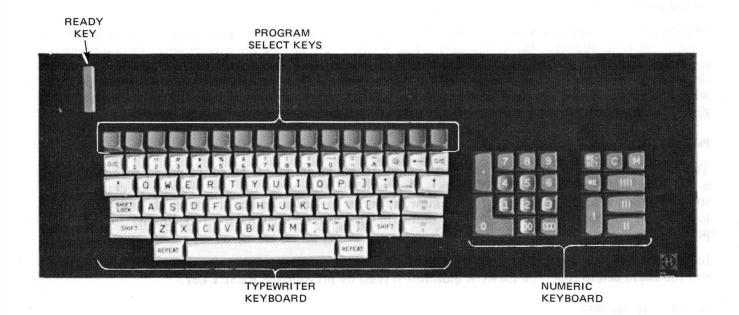

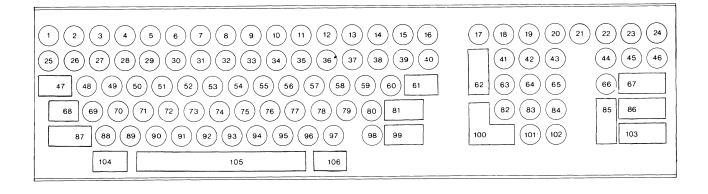

| 3-1    | AE500 Keyboard                                                    | 3-1   |

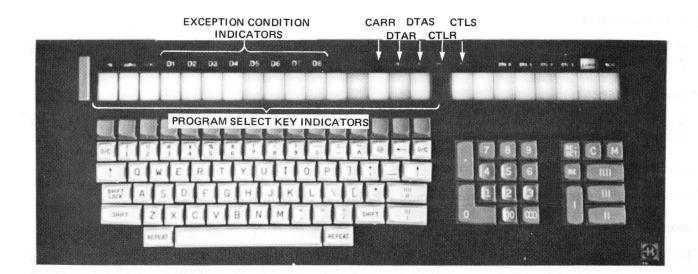

| 3-2    | Indicator Lights                                                  | 3-4   |

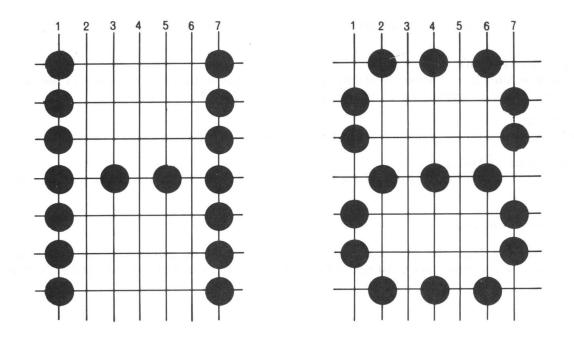

| 3–3    | AE500 Printed Characters.                                         | 3-6   |

| 3-4    | Console Printer                                                   | 3-6   |

| 3-5    | AE500 Basic Character Set                                         | 3–7   |

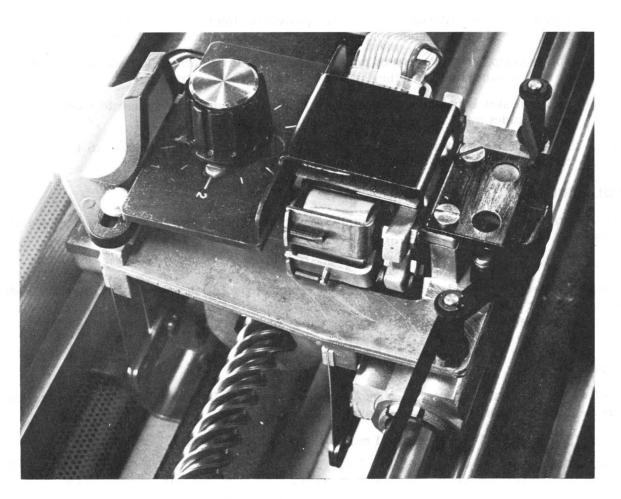

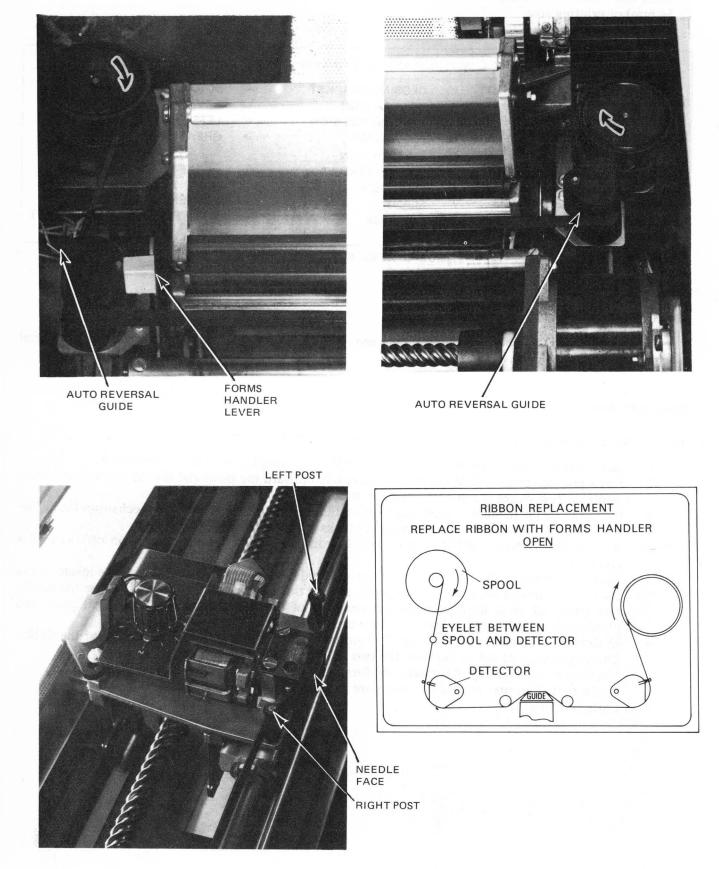

| 3–6    | Ribbon Path                                                       | 3-8   |

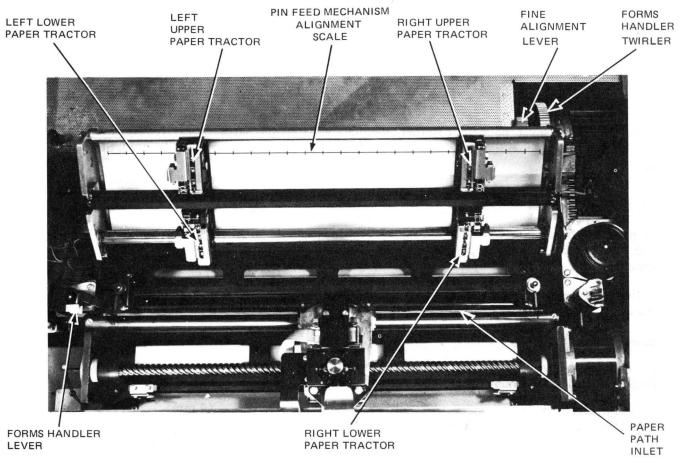

| 3–7    | Forms Handler                                                     | 3–9   |

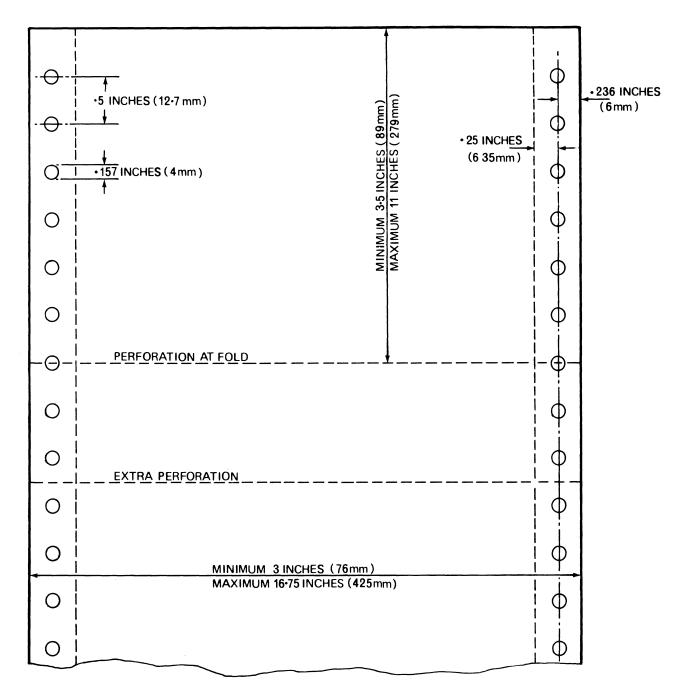

| 3-8    | Pin Feed Form                                                     | 3-11  |

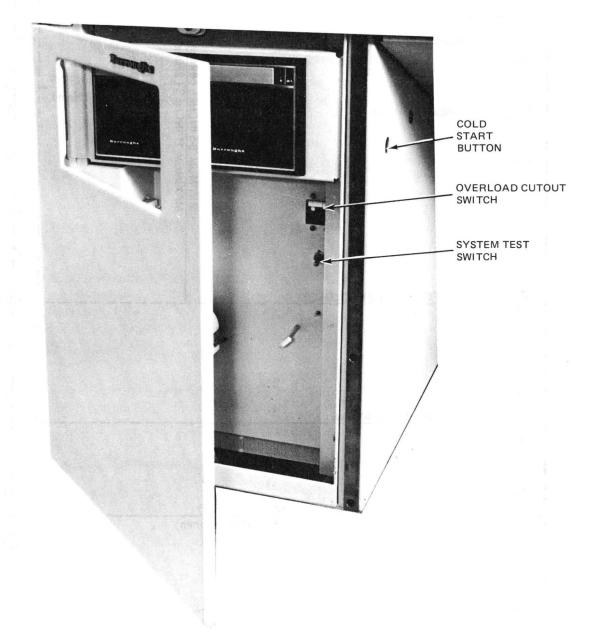

| 39     | Operator Controls.                                                | 3-12  |

| 4–1    | Input/Output Storage Subsystem.                                   | 4-1   |

| 4-2    | Magnetic Tape Cassette                                            | 4-2   |

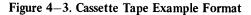

| 4–3    | Cassette Tape Example Format                                      | 43    |

| 4–4    | Cassette Data Record Format                                       | 4-4   |

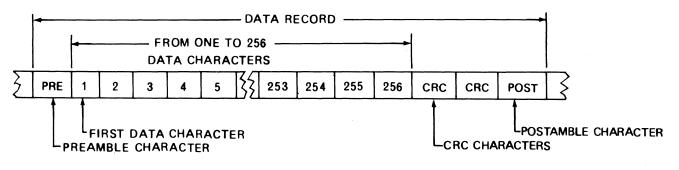

| 4-5    | Cassette Tape Mark Format (Control Record)                        | 4-4   |

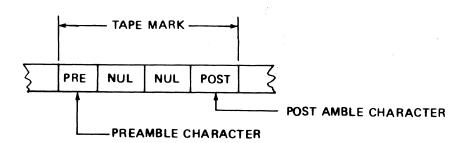

| 4–6    | Cassette Drive Unit                                               | 46    |

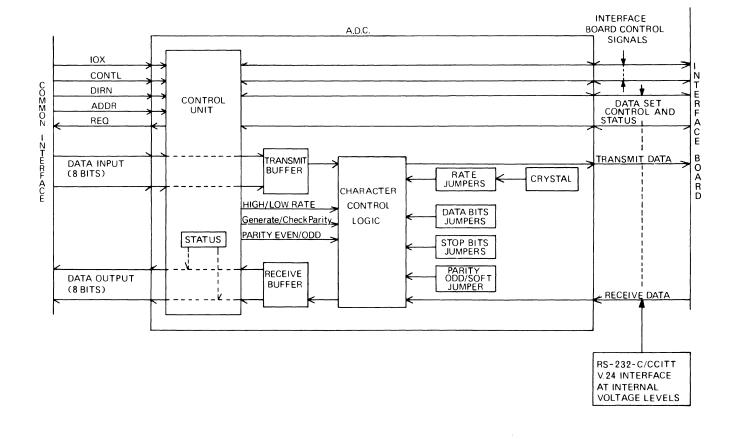

| 5-1    | Asynchronous Data Communications Controller Block Diagram         | 5-3   |

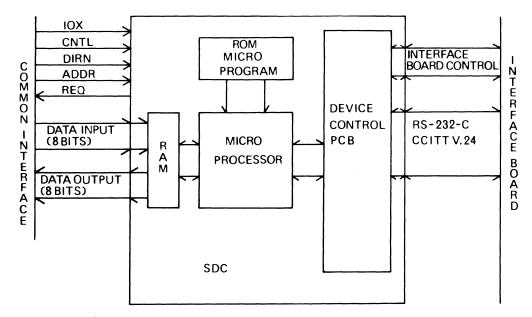

| 5-2    | Synchronous Data Communications Controller (SDC)                  | 5-7   |

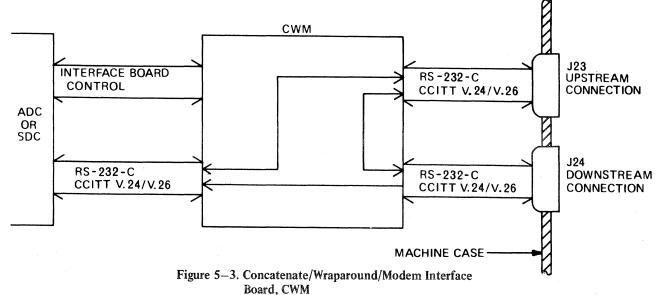

| 5–3    | Concatenate/Wraparound/Modem Interface Board, CWM                 | 5-8   |

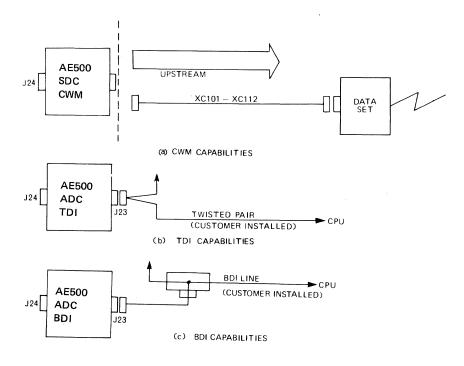

| 5-4    | AE500 Upstream Connections                                        | 5–9   |

| 5-5    | Data Communications Connectors                                    | 5-10  |

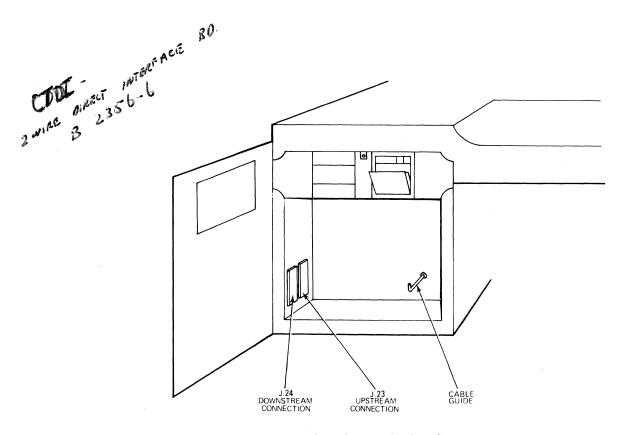

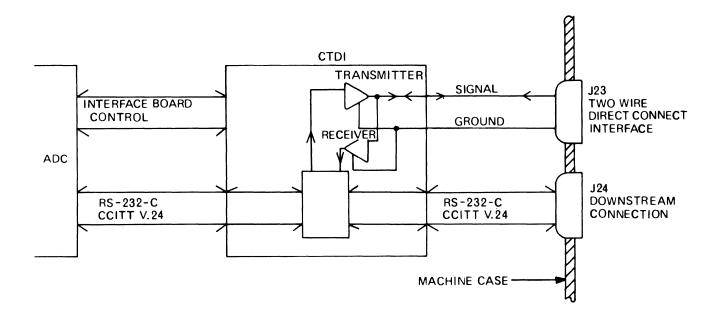

| 5-6    | Two Wire Direct Connect Interface Board, TCI                      | 5-11  |

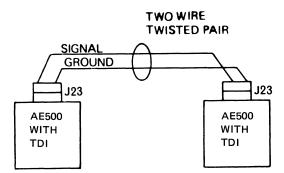

| 5-7    | Example TDI Configurations                                        | 5-11  |

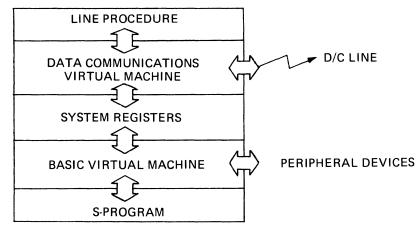

| 6–1    | Virtual System Communication                                      | 6-1   |

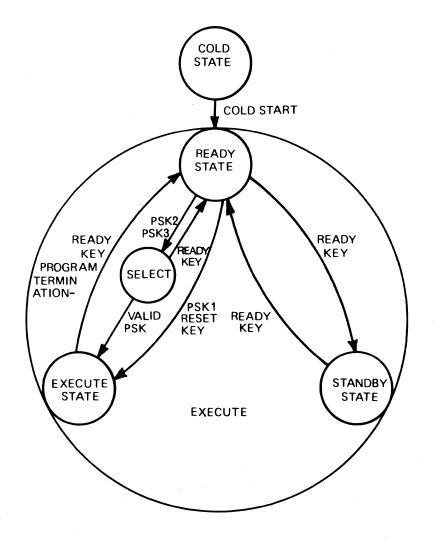

| 6–2    | Virtual System States                                             | 6-2   |

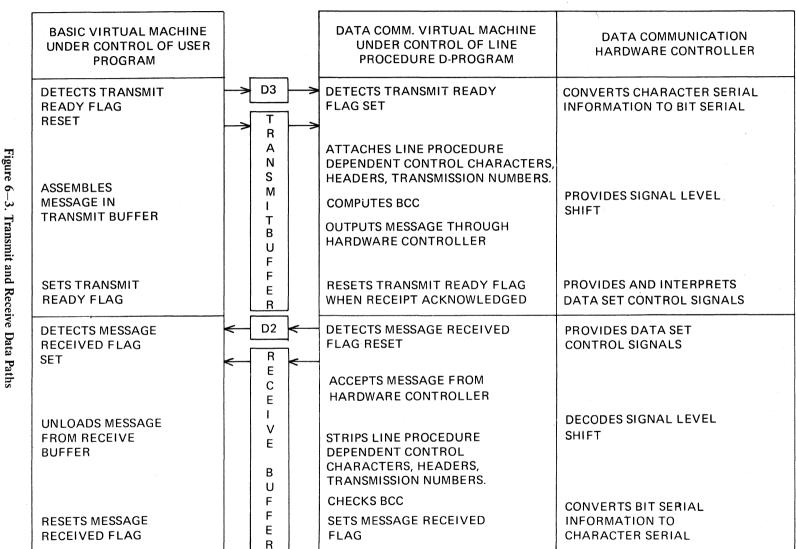

| 6–3    | Transmit and Receive Data Paths.                                  | 6–6   |

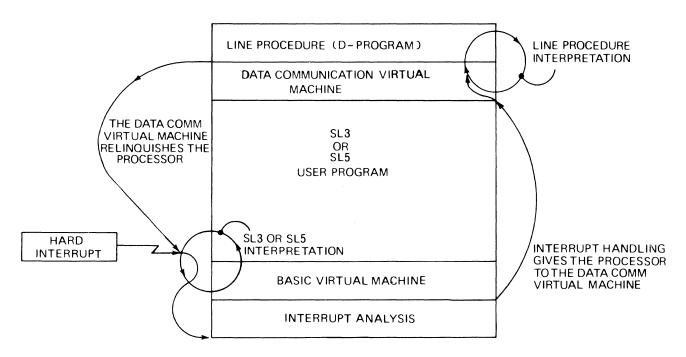

| 6–4    | Sharing of Processor by the Two Virtual Machines                  | 6–7   |

| 6–5    | SL3/SL5 Memory Division                                           | 6-8   |

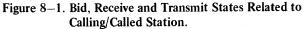

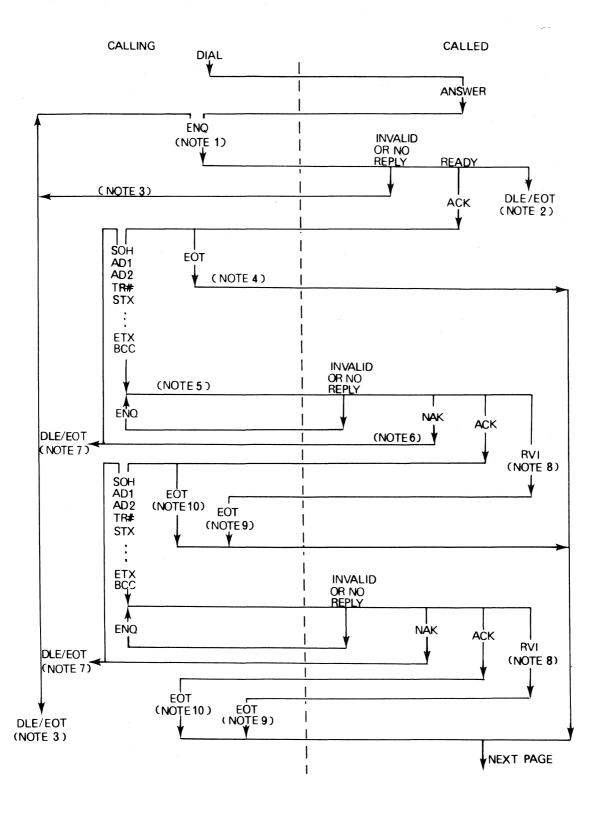

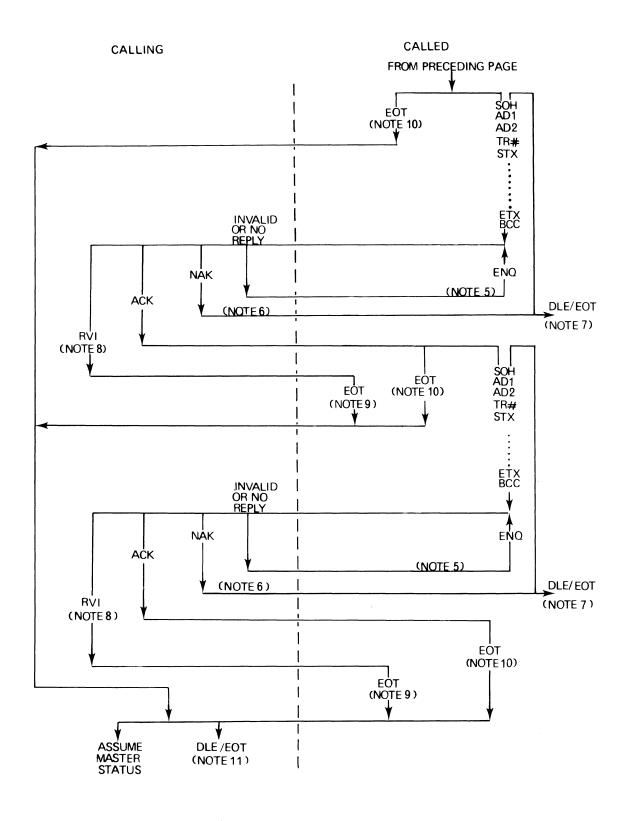

| 8-1    | Bid, Receive and Transmit State Related to Calling/Called Station | 8-3   |

| 8-2    | Point-to-Point Switched Batch Procedure                           | 8-6   |

| 8-2    | Continued                                                         | 8–7   |

| 10–1   | Temperature and Humidity Operating Range                          | 10–3  |

|        | LIST OF TABLES                                                    |       |

| Table  |                                                                   |       |

| 5-1 | Asynchronous Controller Variable Characteristics         | 5–4  |

|-----|----------------------------------------------------------|------|

| 5-2 | Asynchronous Data Communications Parity Control          | 5-5  |

| 5–3 | Transmit/Receive Rates Available using Asynchronous Data |      |

|     | Communications Controller                                | 5-6  |

| 54  | AE500 Data Set Interface.                                | 5-12 |

| 5-5 | Data Communications Cables                               | 5-13 |

## SECTION SECTION

#### INTRODUCTION

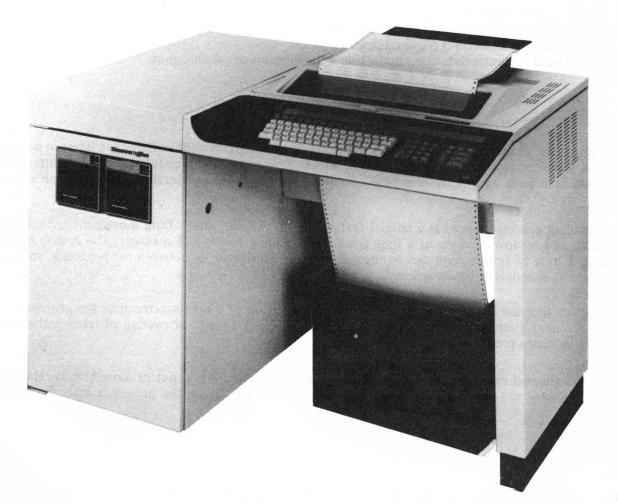

The AE500 is a new product series (figure 1-1) designed to complement and increase the throughput capability of Burroughs' line of intelligent terminal systems. The series includes four styles to provide the following:

Up to 28K Bytes of high speed memory (1 MHz) 60 CPS matrix printer 15" forms handler with pin feed 1 asynchronous or synchronous data communications line 1 or 2 magnetic tape cassette drive

Figure 1-1. AE500 Intelligent Terminal System

#### MACHINE DESCRIPTION

The AE500 series is a free-standing, operator attended, intelligent terminal system designed to provide on-line as well as off-line data processing. The following features are provided:

A serial matrix impact printer which provides 60 character-per-second printing and a 150 print-position pin-feed forms handler.