# MEM-BRAIN FILE FOUR VERSIONS FOR DCA

Angil X3431

1

1

1

l

l

1

l

U

U

T5-1435/33

Autonetics a division of North American Aviation, INC., ANAHEIM, CALIFORNIA

. 14 4

T5-1435/33 COPY <sub>68</sub>

# **MEM-BRAIN FILE** FOUR VERSIONS FOR DCA

24 AUGUST 1965

Approved By:

Mr. Pollast

M. Pollack Asst. Chief Engineer Data Systems Division

Autonetics a division of north American Aviation, Inc., ANAHEIM, CALIFORNIA

This data shall not be disclosed outside the Government or be duplicated, used or disclosed in whole or in part for any purpose other than to evaluate the proposal; provided, that if a contract is awarded to this offeror as a result of or in connection with the submission of such data, the Government shall have the right to duplicate, use, or disclose this data to the extent provided in the contract. This restriction does not limit the Government's right to use information contained in such data if it is obtained from another source.

## ABSTRACT

A large capacity, completely self-contained rotating disk file is currently being developed by Autonetics as a result of a direct continuation of thirteen years of experience in the design, development, and manufacture of disk memory systems for military markets. This new file, known as MEM-BRAIN, embodies a new disk form, a new head positioning principle, a different data buffering concept, and a larger data storage in a smaller package than any presently announced file. This unit, or one of three alternate lower capacity units based on the same principles, is proposed as a solution to the auxiliary storage problems recently discussed with DCA.

#### GLOSSARY

#### Access Time:

Read: The time between the instant at which information is called for and the instant at which it is delivered from storage.

Write: The time between the instant at which information is ready for storage and the instant at which it is stored.

Activity Ratio: The fraction of records with file activity in a given time period.

Address: A name or number which designates a register or a memory location. That part of an instruction which specifies the location of an operand.

Alpha-Numerics: Characters representing letters, numbers, or special symbols.

Auxiliary Storage: A storage, other than main memory, usually capable of holding larger amounts of information than the main memory, although with slower access.

Bit: One element of a binary code.

Block: A group of bytes, characters or words considered or transported as a unit. Block Sort: A sort in which the file is "broken down" according to the characters of the key, and the separated parts are then sorted one at a

Block Transfer: The movement a data block from one area of storage to another.

Branch:

(noun): A point in a program at which one of two or more alternatives is chosen under control of the routine.

(verb): Jump.

Break Point: A point in a program at which special action is taken, such as a stop or a jump, often as the result of the setting of a switch. Buffer Storage: Any device which stores information temporarily.

Byte: A group of bits taken together.

Cell: = Memory cell - Space allocated in memory for storage of one bit.

Channel: A circuit or route in a computer system through which data travels.

Characters: Elementry symbols (groups of bits) which in ordered groups express information.

Clear: To replace information in a storage device by zero or blank.

Clock: Equally spaced pulses used for master synchronization.

Code: A grouping of bits with a specific meaning.

Collate: To merge items from two or more similarly sequenced files into one.

Compare: Determining identity or relative magnitude.

Control Unit: Hardware which directs a sequence of automatic operations.

Core Storage: Storage with information held in the magnitization of magnetic cores.

Counter: A device in which numbers are altered by a unit increment or decrement.

Data: Information handled by a computer, as distinguished from instructions.

Data Processing: A generic term for the operations carried out on data.

Debugging: Determining, locating, and correcting errors of operation.

Decision: The operation of determining if certain relationships exist between words in memory or registers, and taking alternative courses of action

Digit: One of the symbols 0, 1....9, or others used to designate each of the n quantities of the base n of the number.

Echo Check: Information is sent out, returned, and compared to ensure accuracy.

Erase: In magnetic recording, the removal of all information content.

Execution: Producing the result specified by the operation code of an instruction.

Extract: To read parts of a word as determined by a control pattern.

Field: A set of characters which is treated as a whole.

File: An organized collection of information directed toward some purpose.

File Activity: Any action upon the information in a file.

File Maintenance: The processing of a file required to handle the changes in it.

Format: The arrangement of lines, columns, fields, punctuation marks, etc.

Gas Bearing: A bearing in which gas is used as the lubricant.

Autolubricated: (Hydrodynamic) The support is derived from the relative motion.

Hydrostatic: The lubricant is supplied under pressure from an external source.

Hardware: Machine or mechanism, including electronics. Contrasted with software.

Housekeeping: Parts of a program which are not directly in the solution of the problem but are made necessary by the method of operation of the machine.

Index Register: A device which holds data addresses offset from their callout.

Information: A collection of facts, data, records, characters, bits, etc.

Instruction: A set of characters which, as a unit, causes a machine to perform one of its operations. (Preferred to "command" and "order".)

Interrecord Gap: An interval in a sequential store which contains no data. Separates records.

Item Advance: A technique for operating successively on records in memory.

Iteration: The techniques of repeating a group of instructions; one repetition.

Jump: (noun): A jump instruction.

(verb): To break out of the one-after-the-other sequence of instructions.

Key: The field(s) by which a record is identified and/or controlled.

Label: A part of a record used to identify the record's contents.

Linkage: A technique for providing a re-entry to a storage location.

Location: A place in which information may be stored; identified by an address.

Logical Operations: Operations which are Boolean in nature, such as "and", "or", extract, and decision. Contrasted to arithmetic operations.

Magnetic Disk: A storage device or system in which information is recorded on the magnetizable surface of a rotating disk.

Mask: The coding used for extract.

MCP: (Master Control Program) (Executive Routine): A routine which "directs" the operation of other routines.

Memory: Storage associated with a computation center.

Memory Dump: A listing of the contents of storage.

Merge: To combine items from two or more similarly sequenced files into one sequenced file, including all items from the original files.

Multiplex: To carry out two or more functions time shared.

Nonvolatile Memory: Storage which retains information when power is removed.

Off-Line: Operation of I/O and other devices not under direct computer control.

On-Line: Operation of peripherals under computer control.

Origin: The absolute memory address to which addresses in a region are referenced.

Parallel Transfer: Simultaneous data transfer of elements of information.

Parity Digit, Parity Bit: A bit (0 or 1) added to a group of data bits to produce a chosen "evenness" or "oddness" of the number of one's in the total group.

Peripheral: Refers to parts used with but not in the "main frame" of a computer.

Program: A complete plan of attack on a problem (may include flow charts and routines).

Random Access Storage: A store with access time independent of the address.

Rapid Access Loop: (recirculating loop, revolver). A small section of a sequential access memory in which data is reviewed often. Read: To transcribe from storage.

Read Head: An electromagnetic device which produces a voltage output in response to a change in the state of magnetization of the record passing under it.

Recirculating Loop: See "Rapid Access Loop."

Record: (noun): Item; a collection of fields.

(verb): To transcribe into storage.

Register: The hardware for temporarily storing information.

Reset: (Clear). To return a location or device to an initial condition.

Revolver: See "Rapid Access Loop."

Search: To locate a desired word or record in a set of words or records.

Sequential Access Storage: A storage in a one-after-the-other sequence.

Serial Storage: See "Sequential Access Storage."

Signal: The output of a circuit, used for control and/or timing,

Software: A term applied to programs and logic (contrasted to hardware).

Storage (Memory): A device which holds information and returns it unaltered.

Store: (noun) A storage device,

(verb) To transfer information to storage.

String: A set of records which is in ascending (or descending) sequence.

Synchronous: All operations are controlled by a clock.

Systems Approach: Looking at the overall situation rather than the narrow implications of the task at hand; looking for interrelationships between the task at hand and the other functions.

Track: The region reviewed by a stationary head in a disk memory.

Volatile Memory: A storage in which information is lost when power is removed.

Word: A set of characters or bits which is treated by the machine as a unit.

Word Length: The number of bits in a word.

Write: To transfer into storage.

Write Head: An electromagnetic device which produces a change in the state of magnetization of the medium passing under it in response to an input current.

## CONTENTS

|       |          |                          |          |       |       |               |        |       |     |     |       |     | Page          |

|-------|----------|--------------------------|----------|-------|-------|---------------|--------|-------|-----|-----|-------|-----|---------------|

| Abstı | act      |                          | • •      | •     | •     | •             | •      | •     | •   | •   | •     | •   | iii           |

| Gloss | sary     | • • • •                  | • •      | •     | •     | •             | •      | •     | •   | •   | •     | •   | iv            |

| I.    | Intr     | oduction $\cdot$ $\cdot$ | • •      | •     | •     | •             | •      | •     | •   | •   | •     | •   | I-1           |

|       | А.       | Purpose · ·              | • •      | •     | •     | •             | •      | •     | •   | •   | •     | •   | I-1           |

|       | в.       | MEM-BRAIN F              | Tile Con | ncep  | ots   | •             | •      | • • • | •   | •   | •     | •   | I-1           |

|       | C.       | Quantitative Ex          | xamples  | 5 •   | • *   | •             | •      | •     | •   | •   | •     | • • | I-4           |

| II.   | Pro      | gram Descripti           | on ·     | •     | •     | •             | •      | •     | •   | • . | •.    | •   | II-1          |

|       | Α.       | Autonetics ME            | M-BRA    | IN I  | File  | $\mathbf{Pr}$ | ogr    | am    | •   | ٠   | •     | •   | II-1          |

|       | в.       | Outline of Adap          | otations | •     | •     | •             | •      | •     | •   | •   | •     | •   | II-2          |

|       | с.       | Airborne Appli           | cation   | •     | ٠     | ٠             | •      | • *   | •   | •   | •     | •   | II-2          |

|       | D.       | Multiple Comp            |          | •     | •     | ٠             | •      | •     | •   | •   | •     | •   | II-4          |

|       | E.       | Utility Exampl           |          | •     | •     | •             | •      | •     | •   | •   | • , • | ٠   | II <b>-</b> 5 |

|       | F.       | Correlation of           |          | BRA   | .IN a | and           | DC.    | A N   | eec | ls  | •     | •   | II <b>-</b> 5 |

|       | G.       | Plan of Attack           | • •      | •     | •     | •             | •      | •     | •   | •   | •     | •   | II-6          |

| III.  | Des      | cription of MEN          | M-BRAI   | IN    | • .   | •             | •      | •     | •   | •   | •     | •   | III-l         |

|       | Α.       | Fundamental C            | Consider | ratio | ons   | •             |        | •     | •   | •   | •     | ٠   | III-l         |

|       | в.       | Mechanical Fe            |          | •     |       | •             | •      | •     | •   | •   | •     | •   | III-2         |

|       | C.       | Electronic Des           |          |       |       |               | с.<br> | •     | •   | •   | •     |     | III-4         |

|       | D.       | Size Adaptation          | 0        |       |       | •             | •      | •     | •   | •   | •     | •   | III-5         |

| IV.   | Log      | ical Organizatio         | on .     | •     | •     | •             | •      | •     | •   | •   | •     | •   | IV-1          |

|       | Α.       | Basic <b>C</b> apabili   | ties .   |       | •     |               |        | •     | •   | •   | •     | •   | IV-1          |

|       | в.       | Additional Cap           |          | s of  |       |               | - ar   | d     |     |     |       |     |               |

|       |          | 60- Arm Units            |          |       |       |               |        |       |     | •   |       |     | IV-2          |

|       | C.       | Example                  |          |       |       |               |        |       |     |     |       |     | IV-3          |

|       | <u> </u> |                          |          | -     |       |               |        |       |     |     |       |     | J             |

| V.    | Inte     | rface With Othe          | er Units | · ·   | •     | •             | •      | •     | •   | •   | •     | • , | V-1           |

|       | А.       | Hardware .               | •        |       |       |               |        |       | •   | •   | •     | •   | V-1           |

|       | -        | Software · ·             |          | •     |       | •             |        |       |     |     |       |     |               |

|       | ъ.       | Soltware -               | •        | Ť ,   | -     |               | -      |       |     |     |       |     | ¥ — Т         |

## CONTENTS (Cont)

|       |              |        |        |       |      |      |       |       |      |      |                  |   |   |   |   | Page         |

|-------|--------------|--------|--------|-------|------|------|-------|-------|------|------|------------------|---|---|---|---|--------------|

| VI.   | Reli         | abilit | ÷y ·   | •     | •    | •    | •     | ٠     | •    | •    | •                | • | • | • | • | VI-1         |

|       | Α.           | Stand  | lard   | Doci  | ıme  | nts  |       |       | •    |      | •                |   | • | • |   | <b>VI-</b> 1 |

|       | в.           | Desi   |        |       |      |      |       |       |      |      |                  |   | • |   |   | VI-1         |

|       | C.           | Prev   | 0      |       |      |      |       |       |      |      |                  |   |   |   |   | VI-2         |

|       | D.           | Relia  |        |       |      |      |       |       | •    |      |                  | • | • | • | • | VI-2         |

| VII.  | Res          | istanc | ce to  | Mili  | tar  | y Eı | nvir  | onn   | nent | -    | •                | • | • | • | • | VII-l        |

|       | А.           | Vibr   | ation  | and   | Sho  | ock  | •     |       | •    | •    | •                |   | • | • | • | VII-l        |

|       | в.           | Radi   | ation  | and   | Ext  | tern | al I  | Fiel  | ds   | ٠    | •                | • | • | • | • | VII-2        |

| VIII. | M <b>a</b> n | agem   | ent    | •     | •    | •    | •     | •     | •    | •    | ٠                | • | • | • | • | VIII-1       |

|       | А.           | Orga   | niza   | tion  | and  | Ma   | nago  | eme   | ent  | ٠    | •                | • | • | • |   | VIII-1       |

|       | В.           | Curr   | ent I  | Relat | ed 1 | Res  | eard  | ch    | •    | •    | •                | • | • | • | ٠ | VIII-3       |

|       | С.           | Faci   | lities | · 8   | •    | •    | •     | •     | •    | •    | •                | • | • | • | • | VIII-4       |

|       | D.           | Key    | Pers   | onne  | 1.   | •    | •     | •     | •    | ٠    | •                | • | • | • | ٠ | VIII-8       |

| Appe  | ndix         | I.     | Auto   | netio | cs C | com  | pute  | er N  | 1em  | ory  | J                |   |   |   |   |              |

|       |              |        | Expe   | erier | ice  | •    | •     | •     | •    | •    | •                | • | • | • | • | AI-l         |

| Appe  | ndix         | II.    | Pres   | sent  | Stat | us   | of Ir | h-Ho  | ous  | е    |                  |   |   |   |   |              |

|       |              |        | Prog   | gram  | ı •  | •    | •     | •     | •    | •    | •                | • | • | • | • | AII-1        |

| Appe  | ndix         | III.   | Fixe   |       |      |      |       |       | -    | •    |                  |   |   |   |   |              |

|       |              |        | Opeı   | atio  | n ar | nd U | tilit | ty    | •    | •    | •                | • | • | • | • | AIII-1       |

| Appe  | ndix         | IV.    | MEN    |       |      |      | lles  | $\Pr$ | elin | nina | ary <sub>.</sub> |   |   |   |   |              |

|       |              |        | Spec   | ifica | tior | ıs   | •     | •     | •    | •    | •                | • | • | • | • | AIV-l        |

## **ILLUSTRATIONS**

| Figur | Pag                                                       | ge |

|-------|-----------------------------------------------------------|----|

| 1.    | MEM-BRAIN File - Physical                                 |    |

|       | Configuration · · · · · · · · · · · · · · · · · III-      | .3 |

| 2.    | Functional Schematic of 6 Arm                             |    |

|       | Storage Unit · · · · · · · · · · · · · · · · · · ·        | 2  |

| 3.    | Functional Schematic of 60 Arm                            |    |

|       | Storage Unit · · · · · · · · · · · · · · · · · · ·        | .3 |

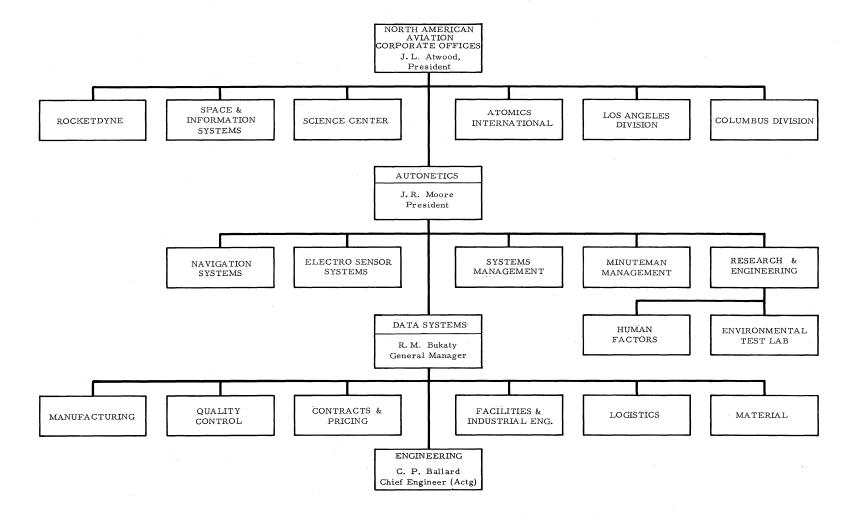

| 4.    | Corporate Structure · · · · · · · · · · · · · · · · · · · | -2 |

|       |                                                           |    |

## TABLES

| Т | able |                                     |     |      |      |     |   | Page |     |    |     |   |   |   |      |

|---|------|-------------------------------------|-----|------|------|-----|---|------|-----|----|-----|---|---|---|------|

|   |      | and the second second second second |     |      |      |     |   |      |     |    |     |   |   |   |      |

|   | 1.   | Data Capacities                     | ٠   | •    | •    | •   | • | •    | •   | •  | • . | • | • | • | I-3  |

|   | 2.   | MEM-BRAIN Ch                        | ara | cter | rist | ics | • | •    | • • | •, | •   | • | • | • | II-3 |

## I. INTRODUCTION

#### A. PURPOSE

This document describes how Autonetics proposes to adapt the company-funded (in-house) 2 gigabit MEM-BRAIN File development to the mass storage problems which have been discussed informally with DCA. Units of four different sizes have been considered. The two smaller units (200 million and 400 million bits) are basic storage for use under detail control of the system computation center(s). The two larger units (one and two billion bits) have the complete internal operational capability of the basic MEM-BRAIN design. They can do much of the internal file organization and management under their own internal stored program control. Therefore, the system computation center(s) will be freed from detail file control. Simple "generic" commands from the computer will serve to control storage or retrieval, after initially loading the unit with the desired program.

A hypothetical civilian problem is described, which Autonetics understands from the referenced discussions to approximate the actual DCA problem. The proposed units are well adapted in speed, capacity, and data organization to the auxiliary storage requirements associated with processing such problems.

## B. MEM-BRAIN FILE CONCEPTS

1. Mechanical

The mechanical design of MEM-BRAIN depends on the high stiffness to mass ratio of a pretensioned membrane. This property is employed both in the disk form and in the principal support structure for the rotating mass (the disk stack). This leads to an inside-out structure relative to conventional disk files. Each disk is a thin annular sheet of magnetically plated foil stretched over a tensioning hoop to provide a rigid surface of uniform flatness. A unique feature of this structure is its tolerance to extreme thermal variations without distortion. The principal support structure of the rotating disk stack is formed of pretensioned pairs of conical sheets. This provides extremely high rigidity in both axial and radial directions. The opposite end of the disk stack is located by a flat membrane-type support to complete the kinematic mounting. The main memory is accessed by internally mounted arms which provide simultaneous radial motion of groups of 8 magnetic read-write heads across the two facing surfaces of adjacent disks. At one end of the disk stack a group of fixed heads is provided to handle internal control and bookkeeping.

The entire disk stack and head assembly is enclosed in the hermetically sealed portion of the frame.

#### 2. Electrical

The basic (two gigabit) MEM-BRAIN unit has sixty-four I/O data channels, each capable of transmitting data to or from storage. Associated with these are four I/O control registers to direct these data. Sufficient electronics, logic, and control is included to permit simultaneous motion of four arms. The arm servos are capable of transferring heads from one set of tracks to any other in less time than one disk revolution. Data organization requirements are very flexible (fixed or variable word, parallel by byte, serial by byte, parallel by bit, serial by bit, etc.). The only fundamental restriction is associated with the relationship between sector length in main memory and short loop length in the fixed head section of the unit.

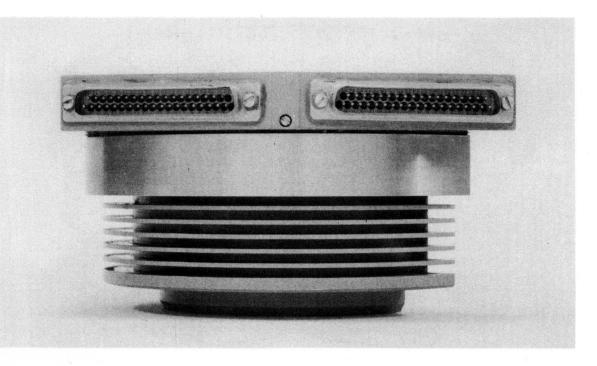

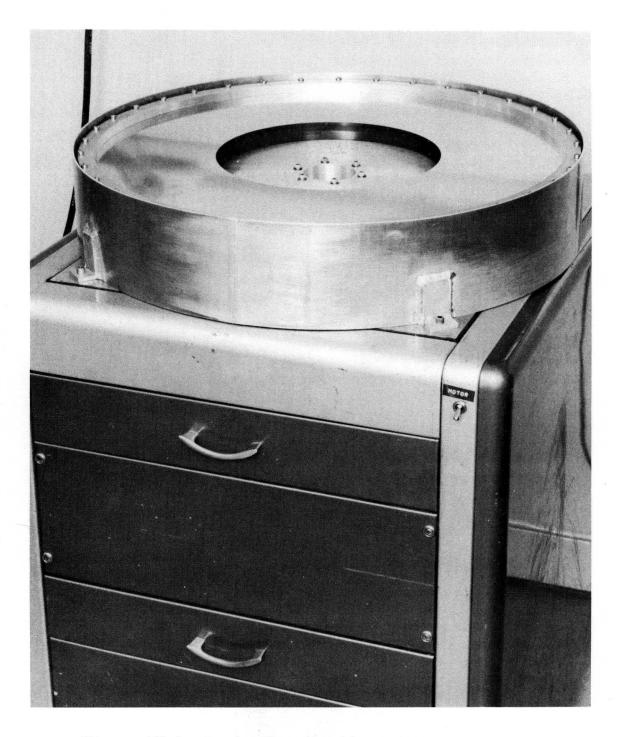

The electronic elements of the file are located at one end of the main frame accessible for service, in an enclosure which is dustand drip-proof but not hermetically sealed.

#### 3. Adaptations to Smaller Units

The only mechanical changes required to adapt the MEM-BRAIN principle to smaller capacity requirements are the reduction in the number of memory disks and the corresponding shortening of the overall structure. Electrical changes are more numerous. For all smaller sizes, the number of I/O control registers is reduced to two. For the smallest units, the internal electronics, logic, and control are minimized.

#### 4. Capacities

Table 1 tabulates the capacity of each of the four proposed units, not only in total but in various groupings which indicate data accessible without servo action.

| Total File Capacity   |                                  | 3x2 <sup>26</sup> bits<br>(201, 326, 592) | $3x2^{27}$ bits (402,653,184)   | 15x2 <sup>26</sup> bits<br>(1,006,632,960) | $15 \times 2^{27}$ bits (2,013,265,920) |

|-----------------------|----------------------------------|-------------------------------------------|---------------------------------|--------------------------------------------|-----------------------------------------|

| bit/track             |                                  | 2 <sup>14</sup> (16, 384)                 |                                 |                                            |                                         |

| 128-bit records/track |                                  | 2 <sup>7</sup> (128)                      |                                 |                                            |                                         |

| 32-bit words/track    |                                  | 2 <sup>9</sup> (512)                      |                                 | <u>-</u>                                   |                                         |

| bits/arm              |                                  | 2 <sup>17</sup> (131, 072)                |                                 |                                            |                                         |

| 128-bit records/arm   | , p                              | 2 <sup>10</sup> (1024)                    |                                 |                                            |                                         |

| 32-bit words/arm      | with all heads<br>in fixed posi- | 2 <sup>12</sup> (4096)                    |                                 |                                            |                                         |

| bits/file             | tions (all<br>head trans-        | 3x2 <sup>18</sup> (786, 432)              | 3x2 <sup>19</sup> (1, 572, 864) | 15x <b>2<sup>18</sup> (3, 932, 216)</b>    | 15x2 <sup>19</sup> (7, 864, 432)        |

| 128-bit records/file  | ports at rest)                   | $3x2^{11}$ (6, 144)                       | 3x2 <sup>12</sup> (12, 288)     | 15x2 <sup>11</sup> (30, 720)               | 15x2 <sup>12</sup> (61, 440)            |

| 32-bit words/file     |                                  | 3x2 <sup>13</sup> (24, 576)               | 3x2 <sup>14</sup> (49, 152)     | 15x2 <sup>13</sup> (122, 880)              | 15x2 <sup>14</sup> (245, 760)           |

## Table 1. Data Capacities

NOTE: Data on the first six lines are common to all four units.

T5-1435/33

## 5. Reliability

The basic MEM-BRAIN concept was aimed at military applications. Therefore, both it and the adaptations proposed herein have used as criteria for design decisions the extensive background in military computer memory work accumulated by Autonetics. These criteria include methods of design for high reliability, for ease of service of elements requiring preventive maintenance, and techniques necessary to insure high tolerance to adverse environmental conditions. Designs are based on MIL E 5400G; GED STD 222 and MIL Q 9858A.

## C. QUANTITATIVE EXAMPLES

A few specific numbers may clarify the foregoing qualitative discussion:

- 1. Assuming 8 bits are used for each alpha-numeric, the smallest unit can store the equivalent of some 1300 pages of standard telephone directory. This is approximately the size of the Los Angeles Central Section directory. The largest unit has ten times this capacity, sufficient to store the telephone directory for a city requiring 7,000,000 entries.

- All units can store or deliver data at a rate in excess of 10,000,000 bits/sec. Any bit in the file is accessible in less than 0.1 sec. A total memory readout of the 2 x 10<sup>9</sup> bit unit can be completed in 100 sec.

- 3. A useful content search of the entire  $2 \times 10^9$  bit file can be accomplished in 16 seconds, if the data has been properly structured for such a search (records of approximately 1000 characters each, search based on 32-bit fields in these records, for example). This is based on the adjacent track access time of .004 seconds.

4. Mechanical stiffness of the end bell is least in the axial direction, where the spring rate may be expressed as .025 in/ ton. Torsional stiffness of the longest disk pack will limit relative deflection from end to end to less than 10% of a data cell.

I-4

- 5. Reliability of the complete units as proposed is conservatively predicted\* to range from 3200 hours MTBF for the largest unit to 6800 hours for the smallest. If a full reliability program (of MINUTEMAN class) were undertaken, these figures would rise to 6700 hours and 10, 300 hours, respectively.

- 6. Maintenance is expected to require an average of approximately 1 hr. per month, total of scheduled and unscheduled.

<sup>\*</sup>Corresponding predictions on the MINUTEMAN program <u>underestimated</u> MTBF relative to subsequent experience by a factor of at least 3 for the memory unit.

## II. PROGRAM DESCRIPTION

## A. AUTONETICS MEM-BRAIN FILE PROGRAM

In 1960 Autonetics became aware of an almost total lack of militarily fieldable peripheral equipment for data processing systems. A highly successful background in militarized disk memories utilizing air bearings for stability and magnetic surface recording for information storage and retrieval led to the decision to concentrate on a rotating disk auxiliary storage unit for military applications. Exhaustive studies were made to determine the requirements of such a mass storage element for military electronic data processing systems. Concurrent studies showed the poor chance of meeting these requirements by upgrading equipment presently available or about to be offered by the industry, and led to the conclusion that a very drastic change in characteristics was essential if this problem was to be reasonably solved. A completely new attack on such characteristics as form, shape, logical flow, and maintenance philosophy appeared necessary. Based on these studies, the MEM-BRAIN file concept was evolved. The concept included a capacity of two gigabits and considerable internal operational capability to allow for foreseeable military growth within reasonable (state-of-the-art) size and weight.

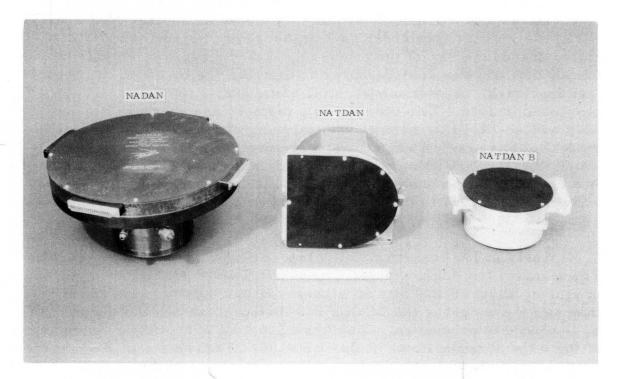

Based on this concept, as embodied in a preliminary design, a company-funded development program began late in 1963. The initial phase of this program included computer simulations, model tests and material investigations, and demonstrated the feasibility of the concept and of a reduction in disk size from 42" to 23". Subsequent work has been directed toward development and construction of a design proofing model with 33 million bits capacity. Concurrent studies of the software aspects of the MEM-BRAIN concept have elucidated the simplifications and increased flexibility of use resulting from provision of some fixed head operational capacity. Many alternate internal capabilities are possible without upsetting the primary advantage of the electromechanical design of this unit.

Emphasis in the Autonetics MEM-BRAIN File program has been placed on the following factors, deemed necessary or desirable in an auxiliary store for military data processing systems:

- 1. Tolerance to military environments:

- a. Extremes of shock and vibration

- b. High and low temperatures and temperature changes

- c. Humidity and other weather factors

2. High MTBF

- 3. Internal data manipulation to unload the system computation center(s).

- 4. Reduction in size, weight and power required

- 5. Large capacity (number of bits)

6. Maintainability

## B. OUTLINE OF ADAPTATIONS

This document describes design adaptations of the MEM-BRAIN File to the data storage requirements of DCA as Autonetics understands them. Two smaller units, being as simple as possible, are direct fetch-put stores. They can be viewed at the interface as equivalent to a number of drum files. These smaller units provide only the controls necessary for directly accessing any portion of the file with reasonable rapidity and high veracity. Two larger units include electronics and logic for stored program control to improve efficiency (from a maintenance, MTBF, and data throughout standpoint).

This choice of unit capabilities results from Autonetics' estimate that storage capacities less than one gigabit probably would not justify the cost of internal program control which would be reasonable for larger units. As can be seen from Table 2, capacity in bits per unit of size, weight and power increases with the size of the unit. The magnitude of these changes would be much more drastic if the same internal control capability had been included in all units.

## C. AIRBORNE APPLICATION

The shake, rattle and roll environment to which equipment is subjected in military aircraft, dictates a design which has a stiffness to mass ratio that is as high as possible and extreme damping (high logarithmic decrement or low Q). The design must give the recording heads sufficient mechanical fidelity to follow the recording surface without undue signal modulation. Phase (jitter) modulation is more critical than amplitude modulation. This has been a major consideration in the selection of MEM-BRAIN parameters.

| Description | Total Data<br>Bit Capacity                 | Number<br>of Disks | Size<br>(Inches) | weight<br>( <u>Pounds</u> ) |      | Bits/cu ft<br>_(x10 <sup>6</sup> ) | Bits/lb<br>(x10 <sup>6</sup> ) | Bits/watt<br>(x10 <sup>6</sup> ) |

|-------------|--------------------------------------------|--------------------|------------------|-----------------------------|------|------------------------------------|--------------------------------|----------------------------------|

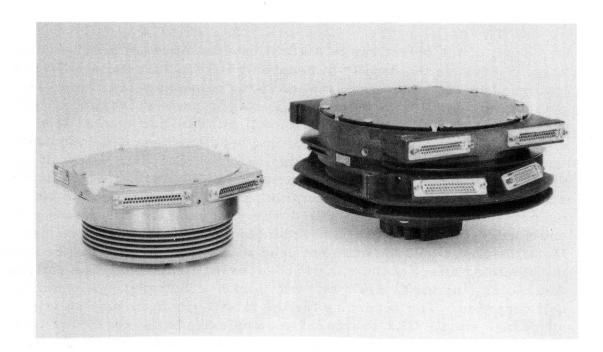

| 6-arm Unit  | 3x2 <sup>26</sup> bits<br>(201, 326, 592)  | 7                  | 23x23x11         | 90                          | 700  | 66                                 | 2.2                            | . 3                              |

| 12-arm Unit | 3x2 <sup>27</sup> bits<br>(402,653,184)    | 13                 | 23x23x14         | 150                         | 800  | 110                                | 2.7                            | . 5                              |

| 30-arm Unit | 15x2 <sup>26</sup> bits<br>(1,006,632,960) | 31                 | 23x23x23         | 250                         | 1200 | 170                                | 4                              | . 8                              |

| 60-arm Unit | 15x2 <sup>27</sup> bits<br>(2,013,265,920) | 61                 | 23x23x38         | 400                         | 1500 | 210                                | 5                              | 1.3                              |

## Table 2. MEM-BRAIN Characteristics

II **-** 3

# T5-1435/33

The external shaft design gives the disks of the file an unexcelled torsional stiffness to mass ratio for a given volume. The relatively great shrinkage-expansion spring stiffness of the external shaft, combined with lightweight preloaded disks, gives a resultant recording surface stiffness far higher than that of any thick disk, center shaft design. The mass of the thin foil disk structure is orders of magnitude less than that of any thick disk design. The integral motor minimizes injection of vibration modes from drive power by eliminating flutter and wow due to such drive train elements as gears and belts. Mounting the rotating element on a preloaded double disk diaphragm at one end and a single diaphragm at the other gives a minimum mass kinematic support which is tolerant of construction, assembly and installation misalinements and low frequency elastic deflections. The small physical size and low total weight of the complete unit allow it to be mounted and demounted, through normal access hatches without special equipment, in many different vehicles.

### D. MULTIPLE COMPUTERS

The multiplicity of I/O control registers and I/O data channels permits direct connection to two computation centers (four in the largest unit). These centers can operate as independent controls over and upon the data in the storage units. Neither of the computation center's control programs need be aware of the other's existence in most normal problem handling. Two conditions do exist, however, in which one of the computation centers can get in another's way. The first of these occurs when the machines command an individual head positioner to two separate locations. Under this condition one or the other must wait its turn, and so a basis of priority must be established, tested, and operated upon. The other condition exists when, in a large program, the two computation centers are both working on the same data. If one is altering the data and the other is using the data, it is possible that the data being used will not correlate because some of it will come from old (not updated) storage and some will come from new (just updated) storage. A special security interlock is used to flag this problem. Tags are placed on data blocks indicating the signature of the last writer in that file. If a computation center wishes to be certain that its data are not being modified, it writes its signature in this block before using the data, and each time it uses the data, it inspects this block to ascertain if its signature is still there. If so, no write entries have been made.

## E. UTILITY EXAMPLE

To avoid need for classified information, a civilian problem is cited as an example of MEM-BRAIN File utility in this proposal to DCA. This problem is the maintenance of a comprehensive directory for a medium-sized city. The entries in this directory are more complex than name, address, and telephone number. Each consists of about 1,000 characters of data, reasonably well structured and organized. The data include such items as number of members in the family, profession and interest of these members, facilities in the house, and activity numbers on the phone. Further, it is assumed that a firregular but frequent intervals, unchanged family units move to another house which has different facility characteristics with a different address and a different phone number, that entire groups of families such as the occupants of a "company town" covering an area of two or three blocks move out and other families move into the same quarters, sometimes picking up the old telephone numbers and sometimes not. Furthermore, at irregular but frequent intervals whole street names may be changed or the addressing scheme of the entire city or a portion thereof is altered by executive fiat. Besides the file maintenance to keep these data correct, assume that queries will be made rather frequently, and in fact, the main purpose of the file is to answer these queries which are analogous to, "If baseball became extremely popular, what would be the utilization of baseball fields located at various places if they were to have Little League players come from five blocks away, high school intramural players come from three miles away, and collegiate teams come from half the city?" Or, if the emergency demanded it, what distribution would be possible for the doctors in the city so that a minimum distance would exist between the location of any probable injury and the nearest doctor?

All proposed MEM-BRAIN File units have the speed and capacity needed for auxiliary storage in data systems required to handle this class of problem. The two larger units, by virtue of increased capacity and internal data organizational capability, could handle materially larger "cities" than the smaller units. Specifically, the capacities of the four units at 1000 characters per entry will handle maximum populations of about 25,000, 50,000, 125,000 and 250,000 respectively.

## F. CORRELATION OF MEM-BRAIN AND DCA NEEDS

As Autonetics understands the mass storage problem with which DCA is concerned, it appears to correlate closely with the reasoning which led to development of the MEM-BRAIN concept. Militarization has been a fundamental criterion in the establishment of MEM-BRAIN principles. So also have minimum size and weight to permit airborne

use. The basic MEM-BRAIN capacity target is at the upper end of the range of values in which DCA has expressed an interest.

The MEM-BRAIN file concept has electromechanical advantages for military use in the three areas of cost, reliability and ruggedness. Cost per bit is expressed in terms of size, weight and power as well as in cents per bit. The design emphasizes fundamental simplicity for the required task in order to provide the maximum potential for overall reliability. In combination with the requirements for compactness and light weight, the design contemplates optimum use of material properties to provide a rugged unit capable of withstanding the military shock and vibration environment. Fundamental knowledge which led to the development of a disk memory which survived a missile crash \* with data still readable, has been applied to the task of developing a rugged and reliable large-scale storage unit.

The basic two gigabit concept is particularly adaptable to the use of internal stored program control and data manipulation. This enhances its capability for working with numerous data channels associated with multiple computers or other peripheral equipment. It also reduces the time demands on the associated computer for detailed control of the data store. It obviously is adapted to handling problems which require the use of a very large data base.

The chief features of the MEM-BRAIN concept are readily adaptable to smaller units such as have been discussed with DCA. Problems appropriate to such smaller units can probably afford the use of more computer time for detailed control so that less internal control capacity is required. Since internal control capability is a relatively expensive portion of the entire device, such a reduction can keep the cost per bit to a reasonable value. However, the main storage techniques used for the large unit are directly adaptable to the smaller units by a mere reduction in number of disks.

From Autonetics' point of view, development of units explicitly directed at DCA's problem provides a definite target for the design stage of the program and would, therefore, be a natural effort to undertake in the overall MEM-BRAIN development.

## G. PLAN OF ATTACK

The development and construction of these units will be as engineering models. The design of the units will conform to all applicable portions of Military specifications, but there is neither time nor money provided in the proposed development, manufacture, assembly \*See Appendix I

and test effort to run a complete environmental assurance program. All of the units defined are electromechanically as similar as possible to the present two gigabit unit (under development). This commonality makes all but the electrical-information interface a direct result of the present development. One reason for this choice of program is to gain experience of maximum utility to the basic Autonetics two gigabit program without jeopardizing the specific DCA objectives.

## T5/1435/33

## III. DESCRIPTION OF MEM-BRAIN

## A. FUNDAMENTAL CONSIDERATIONS

Selection of the storage medium for a large-scale auxiliary file is extremely important because the whole electronic data processing system organization can depend upon its characteristics.

In selecting the storage medium, many types were considered. A prime requirement of a high reliability memory is nondestructive readout (NDRO) to eliminate possibility of system malfunction due to improper rewriting of information. Lumped element storage media such as cores, spots, biaxes, bouncers, etc., are undesirable in mass storage systems because their individuality leads to an ensemble of characteristics (probability of failure, unit cost, unit volume, assembly manpower, etc.) which is detrimental to the overall design. Magnetic recording on a surface which rotates under a magnetic head provides NDRO and time-cyclic review. A cyclic (rotating) memory usually is considered to have a disadvantage in access time due to the sequential nature of its access along a track. In a large storage system properly organized, this can be more of an attribute than a deficit. The control for data location along a given track or series of tracks can be greatly simplified and completely hardware implemented. Trackto-track transfer is random, with an access time which is a function of the relative addresses of the old and new tracks. There are three forms of magnetic recording currently in use---magnetic tape loops, magnetic drums and magnetic disks. Of these, the magnetic disk can be smaller, lighter, and more tolerant of high packing densities under the extremes of vibration, shock, and humidity than tapes or drums. Head-per-track systems, head-per-zone systems, head-per-disk-surface systems, and head-per-disk-stack systems with various controls on the head-track selection scheme exist.

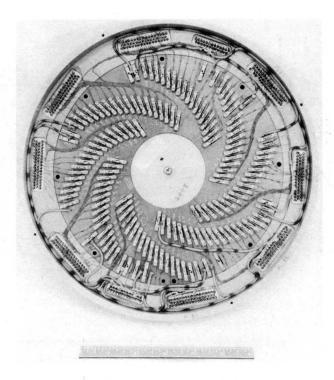

Autonetics chose head-per-zone synchronous recording with four zones at the same angular cell density (same bit rate) as a compromise between cost, reliability, access time, latency time, and master control program time. Eight tracks (one head per track) on two facing disk surfaces are accessed simultaneously by a single arm. The number of arms is equal to the number of facing disk surface pairs for each unit, and each can be positioned to access the various tracks independently. The MEM-BRAIN file includes a modest amount of I/O scheduling, formatting, and controlling capability to enhance the average throughput data rate possible, with minimum

attention from the master control program of the data processing system. This random sequential data storage form costs less and has higher reliability than a true random access file, because the addressing and bookkeeping equipment is much simpler.

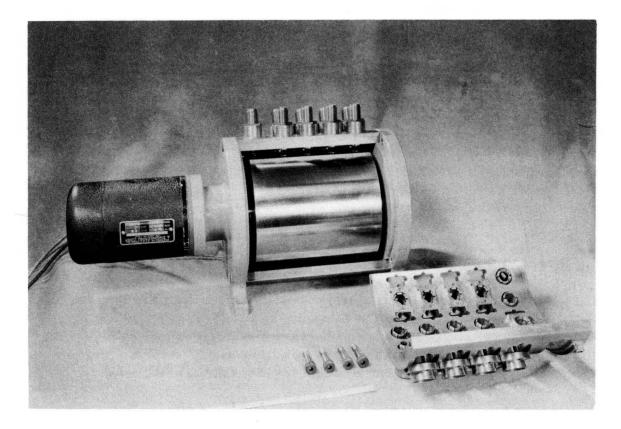

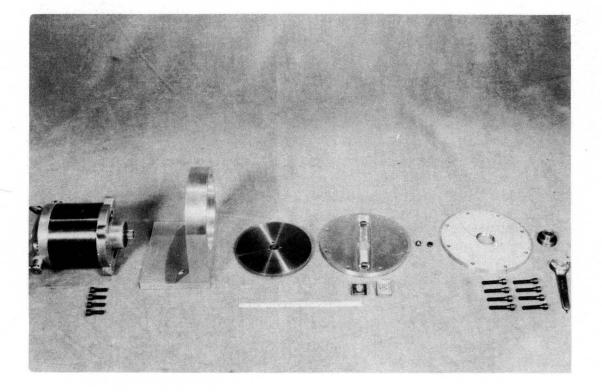

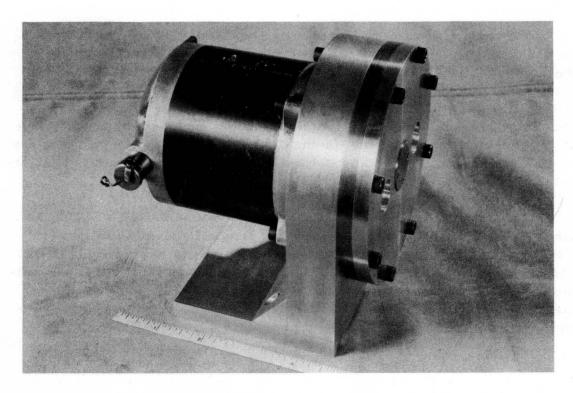

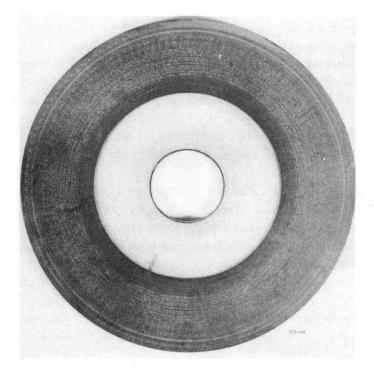

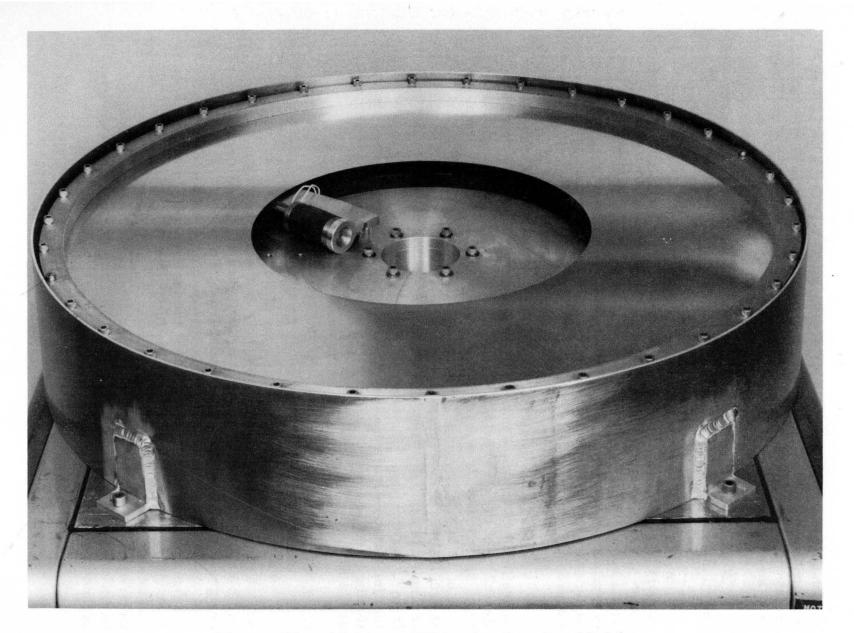

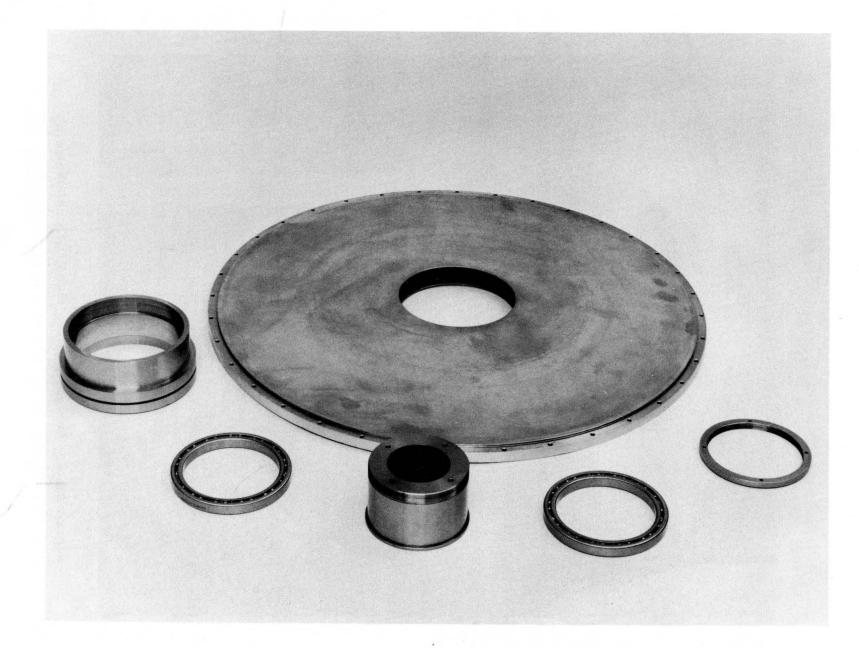

## B. MECHANICAL FEATURES

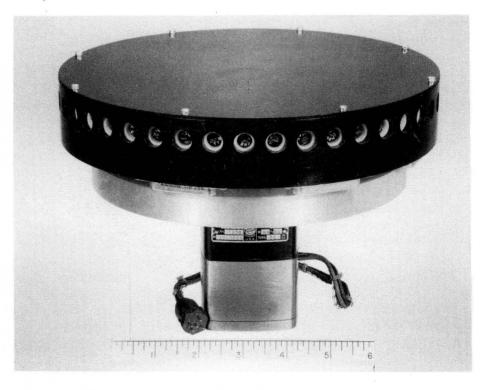

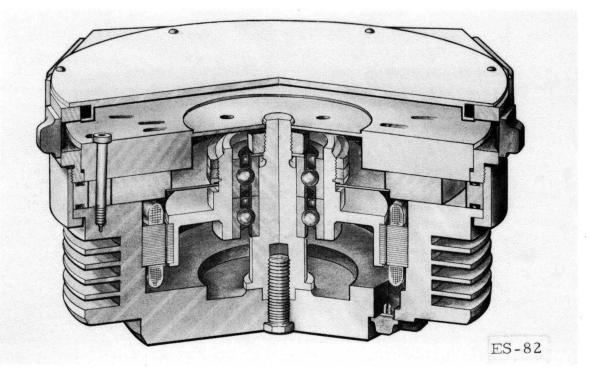

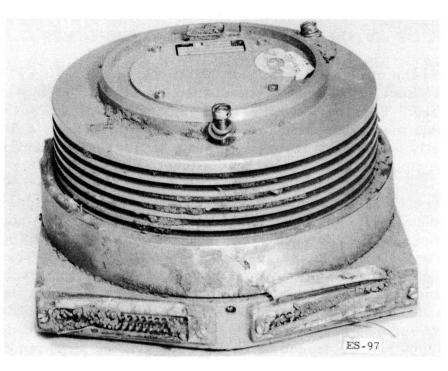

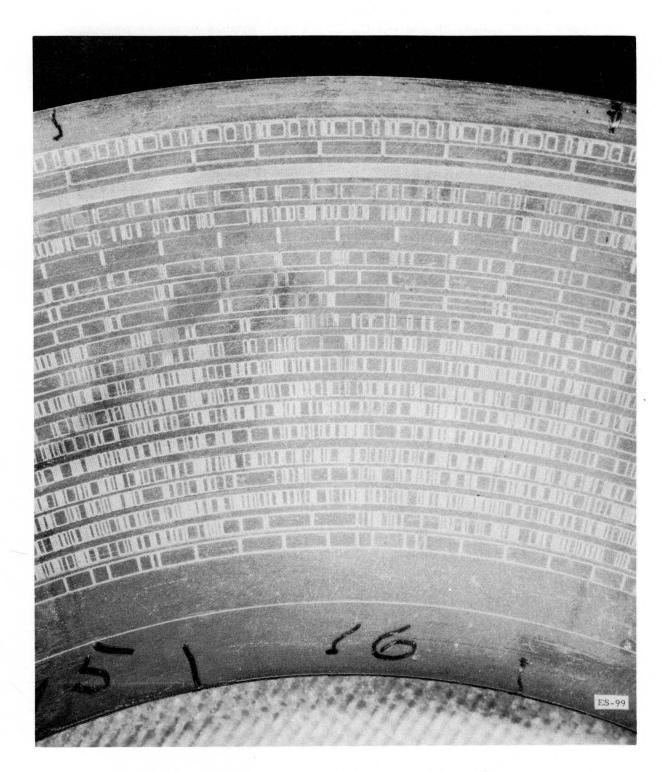

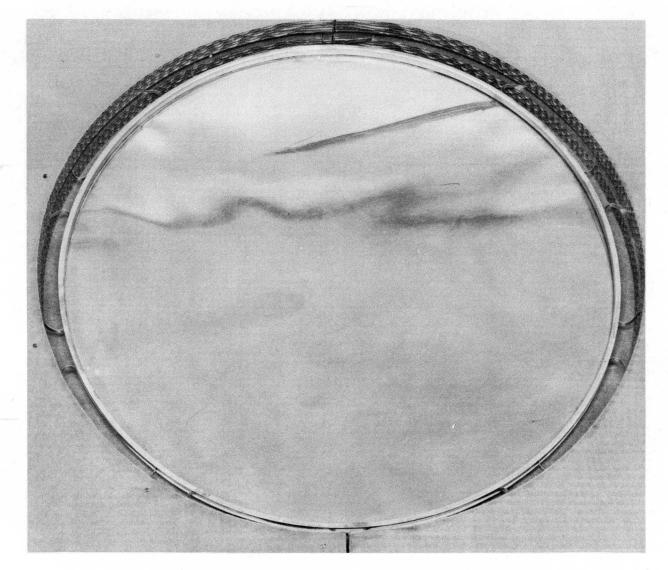

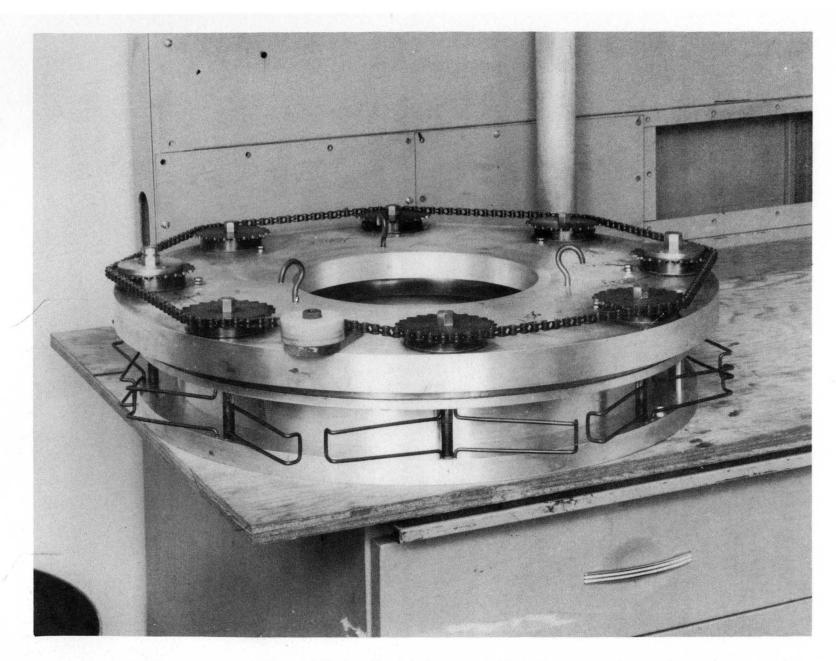

The mechanical design of MEM-BRAIN depends on the high stiffness to mass ratio of a pretensioned membrane both for the disks and for the principle support structure for the rotating mass (the disk stack). This principle leads to an inside-out form for the disk. The disk is mounted and rotated from the periphery and accessed from the center, as shown in Figure 3. The disks are thin annular sheets of magnetically plated foil, each stretched taut over a tensioning hoop. The tensile preload established by this process causes the plated membrane to act as a rigid surface of uniform flatness. This eliminates surface finishing operations. Such a membrane has tolerance to extreme thermal variations without distortion out of plane. This property and the minimum mass of the disk (approximately two orders of magnitude less than a standard disk) lead to the militarized qualities of the MEM-BRAIN File.

The disk stack forms a cylinder which is closed around the periphery. Radial air flow is thus minimized and the usual siren effect of a standard disk stack is virtually eliminated. This disk stack is driven by a synchronous motor which combines with the high moment of inertia to mass ratio of the disk stack to provide a highly uniform rate of rotation.

One end of the disk stack is constructed of a pretensioned pair of shallow coned metal sheets. This forms a light end bell which provides extremely high rigidity in both axial and radial planes. This end bell is carried by a bearing supported by a similar conical pair. The two units are oppositely configured, one having maximum separation at the periphery, the other at the hub. Three degrees of freedom are thus constrained. The other end of the disk stack is supported by a bearing attached to a flat membrane, to complete a five degree of freedom kinematic mount. The sixth degree of freedom is the desired rotation.

The low mass and high stiffness of the dynamic element just described provides a mechanism having high natural frequency and low vibration amplitude. By judicious application of viscoelastic coatings, the mechanical Q of the structure is kept well below the critical

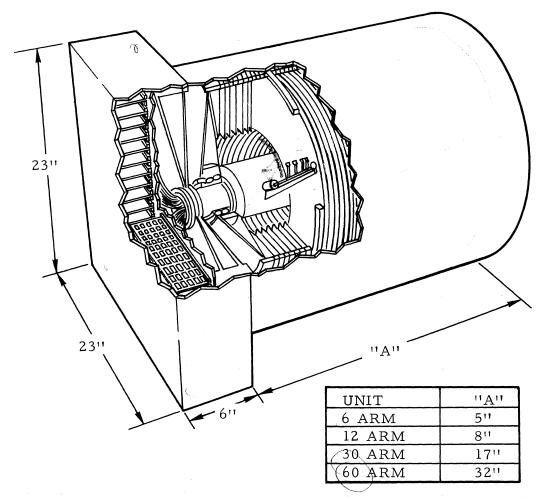

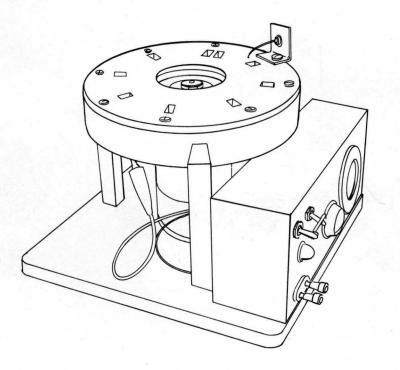

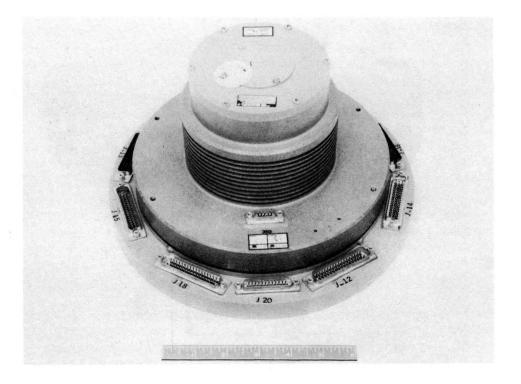

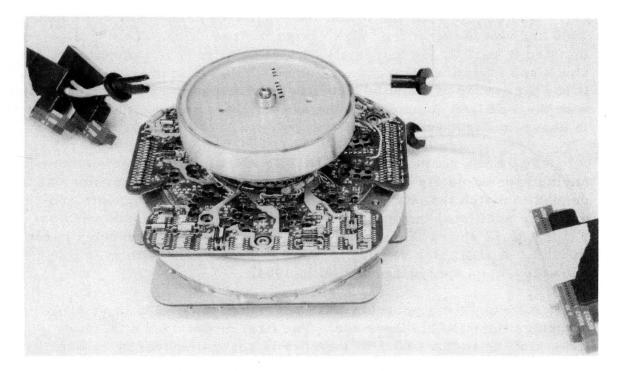

Figure 1. MEM-BRAIN File - Physical Configuration

damping value. The four units proposed all use the same electromechanical and magnetic elements. All are similarly packaged with the electronic elements in a rectangular box 23" x 23" x 6" and the electromechanical portion contained in a 23" diameter cylindrical extension whose length varies from 5" to 32" in accordance with the required disk stack length. All use the same head positioning servo, using track-seeking and track-centering for servo control. All are provided with fixed heads associated with one rotating disk surface. Clock, sector, origin and the short loops utilized in the head servos are included in all four units. The two larger units also have a number of fixed head rapid access loops which are used for formatting, editing, bookkeeping, and other I/O control functions.

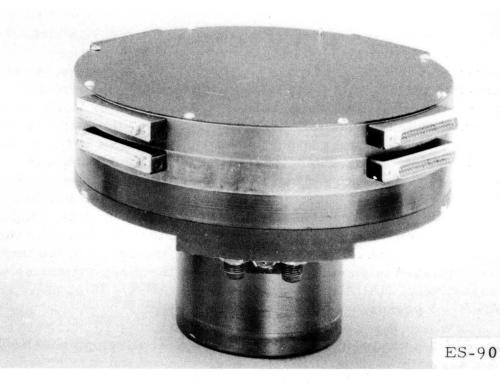

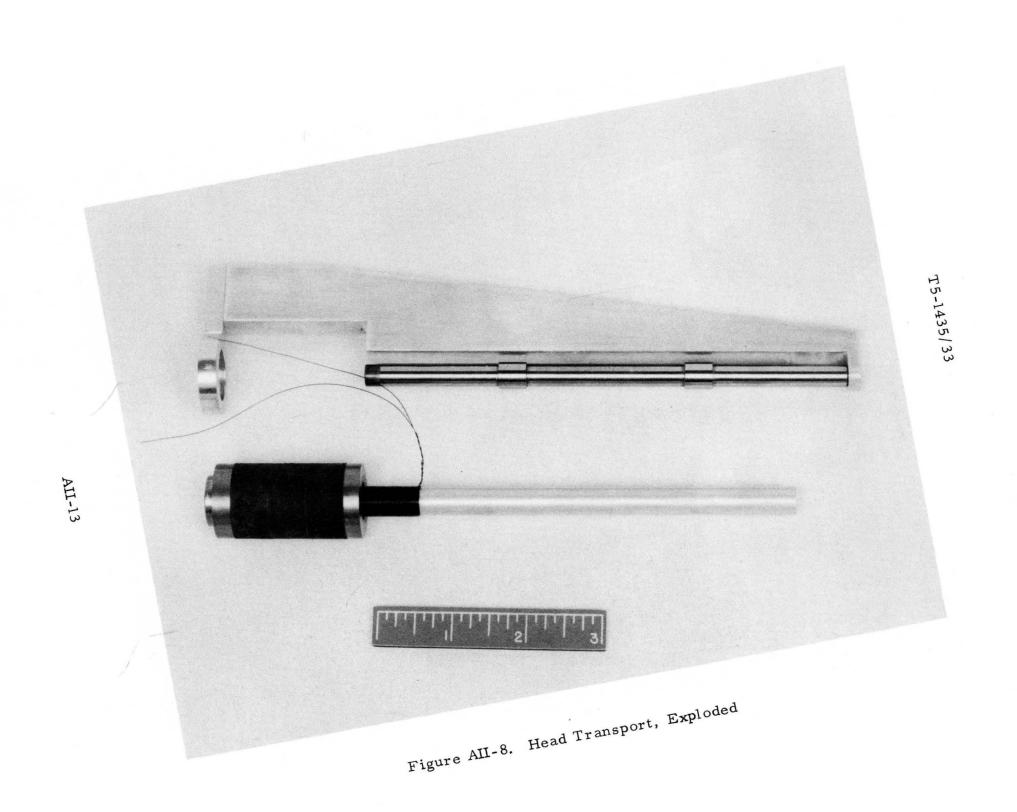

Each of the movable head arms comprises a light tubular member supported on an internal gas bearing and driven by a "voice coil" servo motor. Each of these tubular arms carries eight read-write heads

on flexible support drag links with suitable means for forcing them toward the facing surfaces of two adjacent disks (four heads per disk surface). The heads are attached to pads which furnish an air bearing support to maintain accurate head spacing from the rotating disk surfaces. The entire assemblage is supported by a rigid structural member attached to the central structural frame of the disk pack unit. The four heads facing one disk surface are equally spaced at a separation corresponding to the zone width of the record pattern. Therefore, the distance through which the servo motor must drive the heads is one zone width.

A unique NRZ phase recording technique was developed for this unit to permit the servo positioning signals to be derived from the output of the heads. This involves effectively displacing the bit pattern of some tracks by 90 electrical degrees relative to other tracks. Suitable processing and rectification of the signals from a plurality of heads serve to give both error signal and sense for the final trackseeking operation of the servo. For gross movements a trackcounting technique is used and the servo motor is driven at maximum input to accelerate the arm for approximately one-half the total number of tracks following which it is reversed to decelerate the arm to essentially zero velocity as the desired track is approached. At this point the track-seeking function takes over.

Each arm is equipped with a brake which serves to hold it in position once the servo has attained the proper location. By this means the electronic elements of the servo can be released and switched under I/O register control to position a different arm.

At one end of the disk stack a group of fixed heads are located. These are gas bearing supported on flexible drag links against the exterior surface of the end disk. These head units are supported by a plurality of rigid structural members attached to the central structure and are located and spaced to provide rapid access and buffer loop capability as required for the respective units. In function the support for these fixed heads is equivalent to a solid headplate such as has been used in Autonetics computer memories, but it is structurally segmented to permit removal and replacement for service from the center of the undisturbed disk stack.

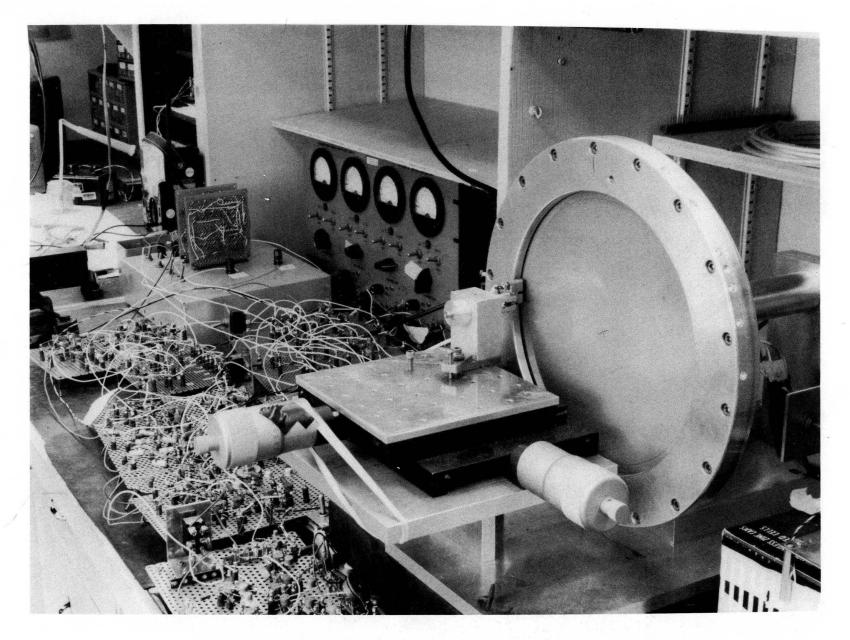

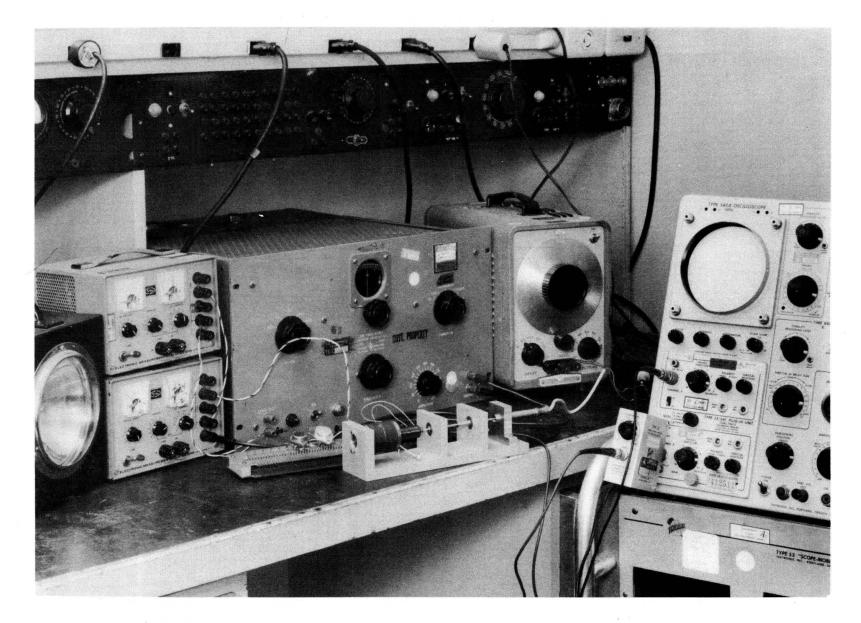

## C. ELECTRONIC DESIGN

The basic storage function of all units is accomplished on the disks accessed by movable heads. All built-in control functions are

provided by the fixed head elements and associated electronics. Clock, sector and origin are provided by (permanent) records on fixed head tracks (read only).

In the basic 60-arm unit the combination of the fixed head elements with other electronics provides capability for bookkeeping, formatting, and other functions and for storage of an internal program to control these operations. Additional electronics includes the necessary read and write amplifiers, together with a small amount of core buffer and logic and switching networks. These provide the I/O control registers as well as the necessary means for transfer and handling of data between fixed head storage elements and between fixed head and moveable head storage. The electronic package also includes the elements of the arm servos which are switched from arm to arm. A program stored in the fixed head area may be inserted and changed at will by the central processor(s) with which the unit is associated. These facilities are capable of performing automatic and continuous on-line file maintenance, record manipulation, data formatting and editing, sorting, merging, collating and other list processing operations and permit direct interfacing with other peripheral units without need for detail action on the part of the central processor. All circuitry uses advanced state-of-the-art techniques in microminiaturization and replaceable circuit board assemblies to maximize MTBF and minimize service time.

The electronics of each head transport servo automatically inspects the I/O control registers for further instructions as soon as it completes positioning one arm. The maximum time required for movement of an arm from one position to any other is less than required for one disk revolution. Thus the maximum rate of execution of discrete position changes is greater than 40 per second. By the nature of these units all of the data from all of the I/O channels and all of the read-write stations is in synchronism. This allows for the parallel transport of data to and from the files if desired and properly called for.

## D. SIZE ADAPTATION FEATURES

In adapting the two gigabit file to smaller sizes, nearly all of the electromechanical, data recording, servo manipulation, integrated circuit, code conversion, environmental integrity, and other design features remain unchanged. The various units utilize the same recording scheme, the same recording density, the same recording code, the same data layout, the same disks, the same heads, the same arms, and essentially the same mounting, stacking, and

holding provisions. In this manner the units, which vary in size from  $3x2^{26}$  bits to  $15x2^{27}$  bits, vary mainly in the number of independent head arms and magnetic recording disks in the stack.

The 6-arm and 12-arm units are proposed as put-fetch stores only. The 30-arm and 60-arm units will have a considerable capability for data manipulation, data format, and data scheduling included as an integral part of the system. These storage units all operate as synchronous, sequential access units for any given channel, and the synchronous, sequential nature of the data permits its manipulation and control without undue hardware complications when the control and temporary storage is handled and manipulated in like manner. The kinematics of arms and disks is such as to include two disk surfaces in each file which are inaccessible to the roving arm heads of the basic storage unit. A small portion of one of these disks is used for timing and storage and manipulation of servoing data. This surface has a total capacity of 17 million bits which permits its economic use for temporary recirculating and manipulating storage in addition. This capability, which is included in the two larger units, comes at comparatively low equipment cost due to the extreme simplicity of data manipulation in sequential strings when the data is synchronized.

All units are capable of storing or delivering data at a rate in excess of 10,000,000 bits/sec. Any bit in the entire data store is accessible in less than 0.1 second.

## IV. LOGICAL ORGANIZATION

#### A. BASIC CAPABILITIES

The internal organization of these four proposed units is identical in its basic memory area and different in its I/O interface and bookkeeping area. The number of head arms varies from 6 to 60, but the method of directing and controlling the head positioners is identical inside the machine. The form, fit and function of data and format in the basic storage is the same in all models. Signal levels involved are identical in all models and all I/O channels. However, the I/O interface for each of these units is distinctly different. The I/O interface consists of I/O control registers and I/O data channels.

The I/O control registers serve as buffers for address information, to assure that the proper head(s) is positioned on the proper track(s) and connected to the proper I/O channel(s). In the two larger units they also alternatively control the routing of data to and from the internal manipulative elements.

Each I/O data channel consists of two input lines and one output line. The read signal on the output line is either at 0 volts to signify a "0" or at -6 volts to signify a "1." A signal of -6 volts on either input line calls for writing a bit of information, while a 0 volt level is a non-write condition. When activated, one line causes the unit to write a "0"; the other line causes a "1." Associated with each I/O channel (or, in some cases, groups of channels) is a signal line which is activated whenever some internal action is taking place which would render data from that channel invalid. Such conditions include head transport in motion or channel being used by another control element. External connections are provided to supply clock, sector counter and sector strobe signals for use of the central processor (or other peripherals).

In the two larger units a core buffer proposed as having a capacity of 256 16-bit words is provided for use with each I/O control register and its data I/O circuits to permit direct connection between the synchronous internal organization of the MEM-BRAIN unit and external elements of the system, which may be asynchronous or synchronized to a different clock.

In the basic storage region each arm has access to 256 groups of 8 tracks on the facing surfaces of two disks. Each track is currently

thought of as divided into 128 sectors, each sector containing space for 128 bits of information with four-bit gaps between sectors. The number of sectors and bits per sector is controlled by the sector track pre-recorded on the fixed head disk and, therefore, this sector and record length organization can be modified by different recording in the initial fabrication of the machine or by a subsequent "factory type" service operation. As this organization must be compatible with the short loop structure and sector counter capacity of the "fixed head" elements, such later modification is more restricted than in the initial design. Any change in the sector number and length may modify the total number of useful bits of information available to each arm. In the current plan, this number is  $2^{25} = 33,554,432$ .

## B. ADDITIONAL CAPABILITIES OF THE 30- AND 60-ARM UNITS

The provision of additional fixed heads and short loop segments on the two larger units provides capabilities for internal data manipulation. Rapid review of the data in a portion of the basic storage is simply accomplished by copying the data in question into the fixed head storage element where it can be reread by additional heads circumferentially distributed along the corresponding tracks. Data may be reordered in sequence or position by appropriate recirculation of the data from one of these additional read heads to another write head with appropriate recirculation control By proper control of this type of operation, any desired record intermix can be obtained. As a specific example, segments of two records of suitable format may be combined in alternating order in the time required for two disk revolutions. A short recirculation loop can be used to make a given record (of length no greater than the length of the loop) available for serial manipulation once during each recirculation interval. The fixed head equipment can also be used as a temporary storage or buffer for information, pending transfer to or from movable arm storage. A more detailed description of some of these operations is given in Appendix III. The use of fixed head equipment for operations of these types is more economical by any measure than any other known method. The primary additional cost is involved in equipment for reading, writing, and controlling the data flow. The controls can effect a great deal of information with comparatively little hardware because of the sequential nature of the operations. In the MEM-BRAIN design the basic recording medium is essentially free because in fabrication of the recording disks, both sides are plated simultaneously and the outside face of an end disk is not otherwise accessed.

## C. EXAMPLE

In terms of the "civilian problem" previously described, these operations of the larger units may be more explicitly exemplified. It is assumed that the directory data is located in the file in order of the social security number of the head of the household. Solution of many facets of the problem therefore requires the limited content search capability which is included in the internally stored program. Suppose that the "baseball field problem" were to arise. Instructions to the MEM-BRAIN file could call for a tally of the number of boys in each of three specified age groups that are located in each of a group of areas defined by street names and address ranges. Such an instruction could be automatically executed within the MEM-BRAIN unit by a search of the entire file. If this particular problem had been anticipated at the time of setting up the stored program, a reduction in search time could be achieved by having the appropriate data located in a subset of the entire file. For example, in the baseball field case, the city might have initially been subdivided into districts and the question might be asked with respect to only one of these districts. The current estimate of the equipment required to perform the content search corresponding to this problem, in addition to the minimal buffering requirements, is five recirculating loops and some logic. The same equipment could be used with only a minor variation in the logic (provided by stored program instruction) to solve other related problems on a time-share basis. Consequently, provision of such capability need not be charged to a single facet of the overall problem. For example, the rearrangement of the file required to handle the movement of groups of families, as mentioned in the problem description, can be covered by essentially the same equipment. In this case, change or alteration of a record can be performed in a systematic search manner without direct supervision by the system's master control program (external to the MEM-BRAIN file). Evidently, any request for data directly correlated with a specific list of social security numbers requires only a simple address access for response.

In the largest unit, a complete serial content search of the file (2 gigabits) can be accomplished in 16 seconds, if the data has been properly structured for optimal access. For the simplest (identity) search criterion on a small field, two tracks of fixed head storage and associated logic will be needed. More complex criteria can be handled by the use of additional fixed head equipment, without affecting search time.

IV-4

## V. INTERFACE WITH OTHER UNITS

## A. HARDWARE

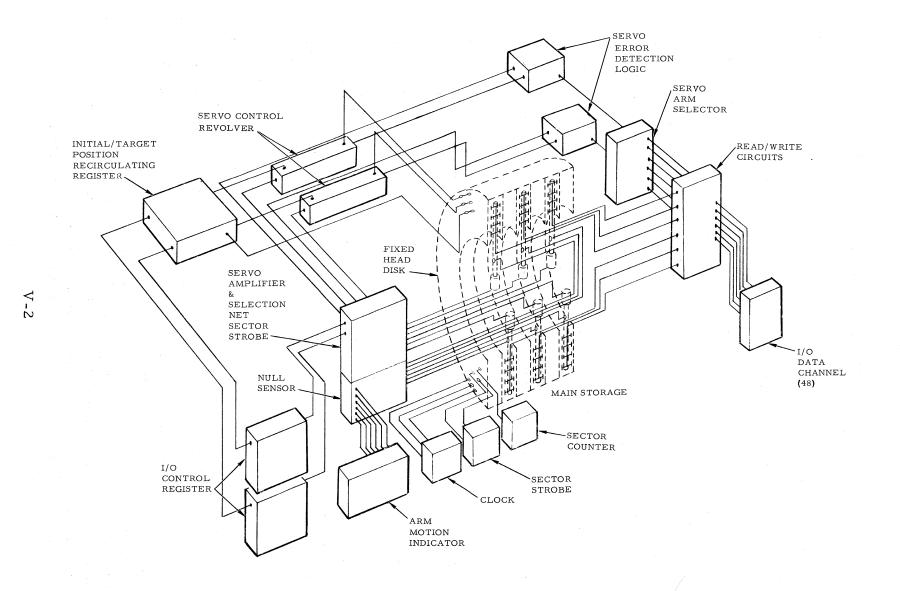

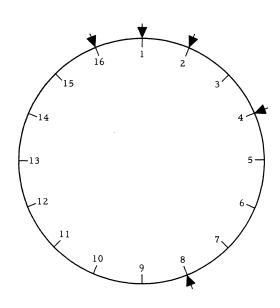

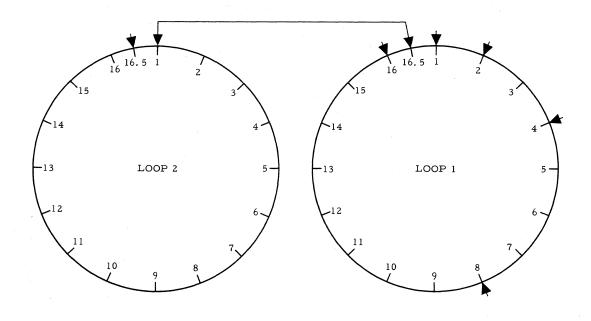

The general internal organization of the MEM-BRAIN File units is indicated in the functional schematics, Figures 2 and 3. These are respectively for the smallest and largest of the four units under consideration. In these figures the blocks which appear closest to the viewer symbolize the interface connectors. The basic data channels are shown at the extreme right of each figure, while the control and external signal blocks are shown at the extreme left and intermediate left, respectively. In the simplest unit there is a one-to-one correspondence between heads and data channels as symbolized by the six lines (one per arm) entering the I/O data channel block. Two I/O control registers are provided for the receipt and interpretation of instructions from the outside source. The arm motion indicator provides a signal to warn the user if invalid data may be appearing, on an output data channel, as a result of action of an arm servo. The signal alternatively will indicate that the unit is not yet ready to receive input data if a write instruction has been called for. In the simplest unit, there is one such indicator per arm. The remaining three boxes indicate connections, which provide the internal clock, sector counter, and sector strobe signals for the information of the external equipment. The sector counter is arranged to change its indication, approximately midway through the sector currently being read, to the designation of the next sector to appear. The sector strobe signals indicate the actual beginning of the sector whose number appears in the sector counter at the time they are produced. Separate strobes are provided for read and write operations. To avoid complication of the figures, the internal connections for use of the clock and sector channels are not shown.

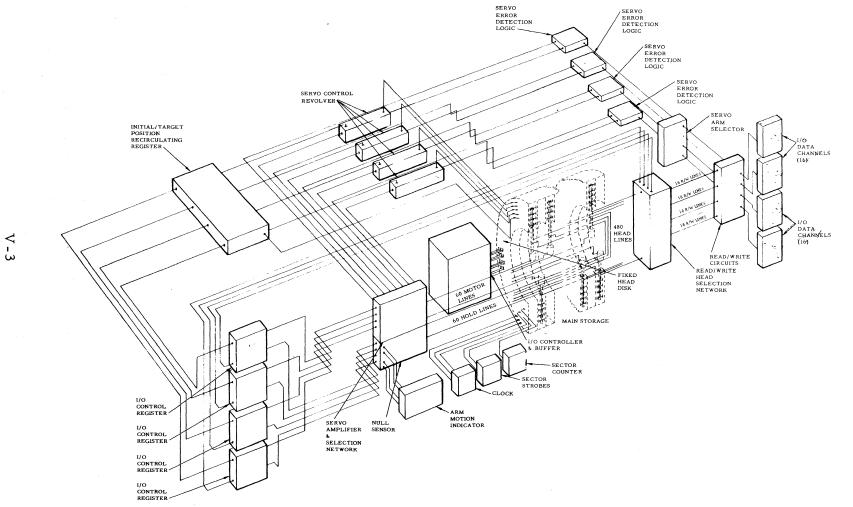

In all except the smallest unit internal switching occurs between heads and external data channels. This is symbolized in the functional schematic of the 60-arm unit by showing four separate I/O data channel blocks. Each block corresponds to 16 I/O channels. In parallel with the data channels, four I/O control registers are provided. Each I/O control register has access to only its corresponding group of 16 I/O data channels but has access to all other internal functions. These registers are capable of controlling not only the positioning of the arms but also the switching of head-to-data-channel connections. They also accept and transmit the necessary instructions to control the internal data manipulation on the fixed head equipment. The external signal blocks (clock, etc.) are the same in all four units.

Figure 2. Functional Schematic of 6 Arm Storage Unit

.

T5-1435/33

T5 - 1435/33

The 30-arm unit is identical in all respects to the 60-arm unit except in length of disk pack and in having only half as many (two each) I/O control registers and corresponding groups of I/O data channels. In both the large units, core buffers are provided (equivalent to one each per I/O control register) to provide synchronous/ asynchronous conversion between the MEM-BRAIN file and other equipment.

The 12-arm unit is similar to the 30-arm unit in number of data channels and control registers, but does not have the fixed head data manipulation capabilities or core buffers. In addition, there is a restriction on the data switching capabilities in that a control register can only define which half of a group of 16 I/O lines corresponds to which arm. The ordering of the interconnection from head to line within a block of eight is fixed in the hardware.

For emphasis it is reiterated that in the two larger units, any head in the main store or any head in the data manipulation section of the fixed head unit can be connected under control of the I/O register to any data line associated with that register. It is also emphasized that the two smallest units are designed only as storage for use under direct process control at synchronous rate by the central processor. By contrast the two larger units can work either under such direct control or under independent control of an internal stored program with only generic instructions from outside---either synchronous or asynchronous.

#### B. SOFTWARE

All four units may be operated in a variety of ways at the option of the user. While the basic operation of any one channel of such a unit is serial by nature, the organization of the complete unit permits some non-serial operation. Because of the multiplicity of heads, characters or words may be recorded and read in parallel from appropriately chosen groups of heads. A natural subdivision for all units is an 8-bit byte parallel mode which can be handled by a single arm. Multiples of this number may be used up to the capacity of the I/O channels provided in each unit. Thus the 6-arm unit can handle 48-bit words in parallel; the 12- and 30-arm units can handle 32-bit words in parallel; and the 60-arm unit can process 64-bit words in parallel. These are maximum capabilities for parallel operation. The two smaller units are designed to be optimal when used with an 8-bit byte parallel or direct serial mode of operation. Because of the internal processing capability, the two larger units may be optimized in other fashions by appropriate program control.

An instruction code is fed into an I/O control register in the form of a binary number which includes segments designating arm number, track number, head number, and (except in the 6-arm unit) an I/O line number. In the two largest units the instruction also contains a sector number and a mode code. Except for the latter item, the functions of these various portions of the instruction code are essentially self-explanatory. They define the necessary arm servo operation, if any, and the internal interconnections required to write or read the data in the proper portion of movable head storage. In the two largest units, when used with non-synchronous external equipment, the core buffers are normally connected in the I/O channels to provide translation services. If the external system is normally synchronized with the MEM-BRAIN unit, these buffers are available for use under control of the mode code in the instruction. This mode code, in general, is provided to control the operation of internal data manipulation or direct the execution of appropriate portions of the internally stored program. If it appears necessary for a particular machine application, the core buffer may be addressed under direction of the mode code (usually by the operation of the internal program) for use in connection with the data manipulation operations in the "fixed head" section. If such operation is called for in a system in which the external elements are not synchronous with MEM-BRAIN, such use of the core buffer will temporarily interrupt the corresponding communication channel between the MEM-BRAIN file and the external system, during the time required to process the portion of the instruction which requires this use of the core buffer. When used with internal stored program control, such interruption is not likely to be of serious consequence because the central processor does not require continuous detailed control of the MEM-BRAIN operations. This function of the core buffer is in addition to that described under "Hardware" above.

In response to an instruction code, an I/O control register addresses the particular head transport called for and designates the target position (track). An available transport servo is included in this operation and compares the target position with the present arm position from the fixed head record to determine control necessary for gross arm motion. When this motion has been completed, the servo switches to target-seek mode and completes the location of the arm to the new track. Simultaneously the necessary logical switching is carried out to connect the heads of this arm to the designated I/O data lines or other elements. A number of independent arm servos equal to the number of I/O control registers may be in operation at any given instant. Any servo may be under control of any I/O

register. The register provides an interface signal when it has accepted the target commands. When this signal is present, an arm may be addressed and a target position may be assigned to it. If less than all servos are operating at that instant, that I/O request will be acted upon by the file. If all servos are active, the I/O register will store the information until a servo is free, and will provide another interface signal showing that it is unavailable for new commands.

Reading or writing on heads associated with any arm while it is in fixed position may occur simultaneously with servoing of another arm to a new location. This capability has advantages in permitting continuous reading of records longer than provided in a single disk revolution by placing successive portions of the record on tracks accessed by different arms and moving the arms, which are not being used for reading or writing, to a position corresponding to a subsequent portion of the continuous record. The file magnetics and electronics uses an interrecord gap of four-bits (the slop-over on stop write is one-bit). Therefore, any change in the word length must be carefully planned to avoid waste of space when grouped into records for storage. A sector counter is included in each storage unit to allow the location of addresses along the track to be fixed with respect to origin. The exact number of sectors is fixed when the hardware is manufactured but is variable in principle (may be changed by a special service operation within the restrictions imposed by hardware, including sector counter capacity). Therefore, in the two smaller units, the simple rewriting of the sector tracks will change the minimum directly alterable record size. In the two larger units, short loops are utilized to manipulate data, and these must be modulo "sector count." Therefore, any change in sector organization after the file is constructed must be taken with the short loop structure in mind.

Because of the flexibility provided in the two larger units, it is possible to optimize the operation of the MEM-BRAIN file on the basis of a variety of criteria in accordance with the needs of the user. Such optimization may be based on the use of content or location address for data or an intermixture of the two. The file may be organized for optimal data access under a variety of contemplated major data manipulation requirements as, for example, to permit the equivalent of alphabetic insertion of new data at the appropriate point in an existing file, etc.

In all cases, it is possible to connect more than one control source to a MEM-BRAIN file unit. However, this capability is primarily an advantage in the two larger units because of the internal techniques available to minimize interference. Specifically, these

units can be connected to a multiplicity of computers and also to direct inquiry stations for appropriate system requirements. Likewise, the outputs of the larger MEM-BRAIN files may be transmitted through the central processing equipment(s) or may be sent direct to display or printer units or other peripheral devices.

Where one of the larger units is used with multiple processing systems, it can either be operated as a unit so that all data storage is available to all processors, or it may be operated with entirely different organization in different parts of machine so that to the external data systems, it looks like a multiplicity of completely independent auxiliary stores.

#### VI. RELIABILITY

#### A. STANDARD DOCUMENTS

The proposed storage units will be designed in accordance with the following Military documents: MIL E5400G; FED STD 222; MIL Q 9858A.

#### B. DESIGN FOR RELIABILITY

Design principles embodied in the MEM-BRAIN File have been selected with the ultimate reliability of the device as a paramount consideration. Simplicity is always of extreme value in eliminating failure modes and enhancing reliability of any system. Consequently, at every point where a choice between simple and complex solutions was available, the simpler technique was chosen.

For any unit intended for military application, it is desirable to assume the need for operation in a hostile environment. Consequently, ruggedness is a necessary feature in such a design. In the MEM-BRAIN development such ruggedness has been sought at every decision point, but not by the brute force method of increasing structural dimensions. Rather, the technique has been one of reducing mass wherever possible and increasing effective stiffness and structural damping to minimize response to shock and vibration.

Furthermore, the electromechanical elements of such a device are known to be sensitive to adverse environments related to humidity, pressure, and temperature. In the MEM-BRAIN file, therefore, the electromechanical package has been designed as a hermetically sealed unit, and care has been taken in the choice of materials and their structural interconnection to minimize disturbance of critical locations due to temperature change or temperature gradient.

The electronic elements of such a system, on the other hand, may be more subject to deterioration in performance by parameter drift or catastrophic failure. Therefore, the electronic package has been designed for ready access to permit maintenance by module replacement. Its enclosure will be dustproof and drip-proof but will not be hermetically sealed.

To minimize the failure potential in the electronic system, the background developed on the MINUTEMAN standard parts will be used wherever applicable but parts will not be subjected to the full "burn-in program" used in the MINUTEMAN itself.

# C. PREVENTIVE MAINTENANCE

In addition to the care taken in selecting design features to improve the inherent reliability of the MEM-BRAIN file, it is contemplated that a preventive maintenance program will be developed to enhance the overall (as used) reliability of the file. Such a program will be based on a philosophy of replace and test which assumes that the serviceman has available a stock of spare modules and a checklist giving an optimum routine for such procedure. It is anticipated that the preventive maintenance program will call for carrying through this operation at scheduled intervals (about once per month). However, if an unscheduled failure were to occur, the replace and test routine would remain the same. It is expected that the entire end of which time the electronic elements of the file will have been brought up to essentially "factory-fresh" performance. It is not anticipated that the hermetically sealed electromechanical package will require maintenance except at extremely long intervals. Such maintenance should not be attempted except under clean-room conditions such as exist at the factory or at major military repair centers.

# D. RELIABILITY PREDICTION

It was found that MINUTEMAN components without full MINUTE-MAN tests were, in general, less expensive than commercial components. Assuming the use of such parts and the methods of predicting reliability which have been so completely successful for MINUTEMAN, the following MTBF and failure rates have been predicted:

#### Failure Rate\* and MTBF