1984 Data Book

ADVANCED MICRO DEVICES

MULTIBUS OEM Products and Microprogrammable Development Tools

MULTIBUS MULTIBUS MULT JS MULTIBUS MULTIBUS MULTIBUS MULTIBUS MULTIBUS MULTIBUS MULTIBUS ILTIBUS MULTIBUS MULTIE MULTIBUS MULTIBUS MUL

MICROPROGRAMMABLE MICROPROGRAMMABLE MICROPROGRAMMABLE MICROPROGRAMMABLE MICROPROGRAMMABLE

# **Advanced Micro Devices**

## Microcomputer Systems Data Book

١

© 1984 Advanced Micro Devices, Inc.

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics. The company assumes no responsibility for the use of any circuits described herein.

> 901 Thompson Place, P.O. Box 3453, Sunnyvale, California 94088 (408) 732-2400 TWX: 910-339-9280 TELEX: 34-6306

> > Printed in U.S.A.

· · · •

GENERAL INFORMATION SALES OFFICES

5

## **Index Section**

Numerical Device Index ..... ...1-1

#### NUMERICAL DEVICE INDEX

1

| AmSYS <sup>™</sup> 29/10B | Microprogram/Bit-Slice Development System     |

|---------------------------|-----------------------------------------------|

| AmSYS29/15                | Microprogram Control Store Emulator3-7        |

| Am29/2065                 | High-Speed Writable Control Store             |

| Am29/6310                 | High-Speed Trace/Trace Expansion              |

| Am29/6312                 | High-Speed Trace/Trace Expansion              |

| Am94/0350                 | Parallel I/O SBX Module2-34                   |

| Am94/0351                 | Serial I/O SBX Module2-39                     |

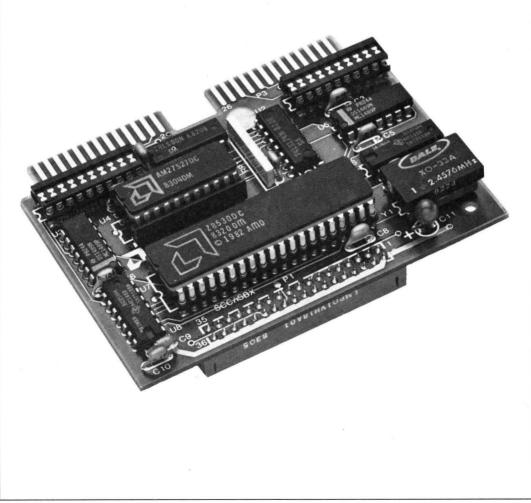

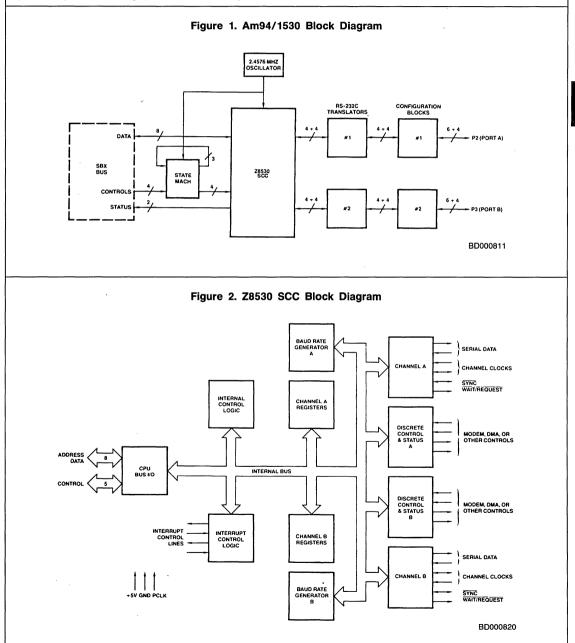

| Am94/1530                 | Dual-Channel Serial Communications Controller |

|                           | SBX Module2-44                                |

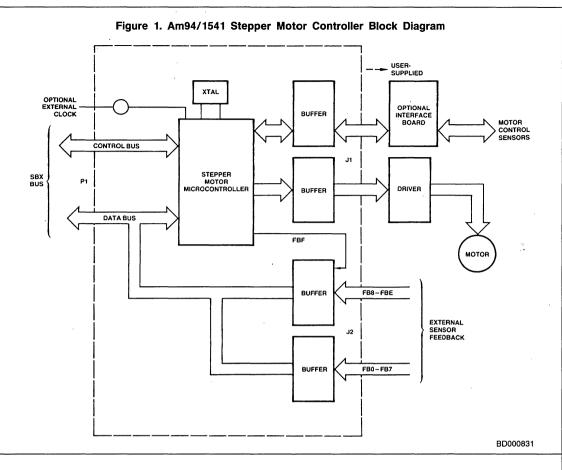

| Am94/1541                 | Stepper Motor Controller SBX Module2-49       |

| Am94/2000                 | SBX Motherboard2-53                           |

| Am95/6120                 | Intelligent Floppy Disk Controller Board      |

| Am95/6440                 | Card Cages and System Chassis2-79             |

| Am95/6448                 | Card Cages and System Chassis2-79             |

| Am95/6450                 | Card Cages and System Chassis2-79             |

| Am95/6452A                | Card Cages and System Chassis2-79             |

| Am96/0000L                | 512K – 4 Megabyte RAM Boards with LBX2-32     |

| Am96/3500                 | Intelligent Serial Interface Board2-76        |

| Am96/5232                 | Programmable RAM/EPROM and I/O Board2-68      |

| Am96/6130                 | Intelligent Floppy Disk Controller Board      |

| Am96/8052                 | Intelligent Color Video Controller Board      |

| Am97/0000                 | Random-Access Memory Boards2-20               |

| Am97/0000B                | 1 Megabyte RAM Boards 768K Bytes, 512K        |

|                           | Bytes RAM Boards2-24                          |

| Am97/0000C                | 512K - 4 Megabyte RAM Boards2-28              |

| Am97/0343                 | Memory Expansion Module for the Am97/86052-14 |

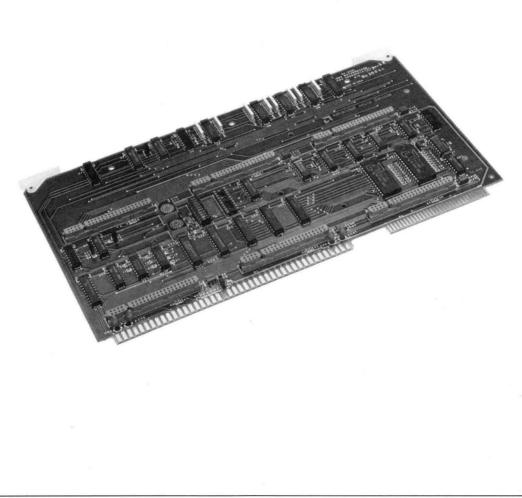

| Am97/8605                 | 16-Bit Single Board Computer2-2               |

| Am97/8605A                | 8086-Based 16-Bit Single Board Computer2-17   |

|                           |                                               |

\ \

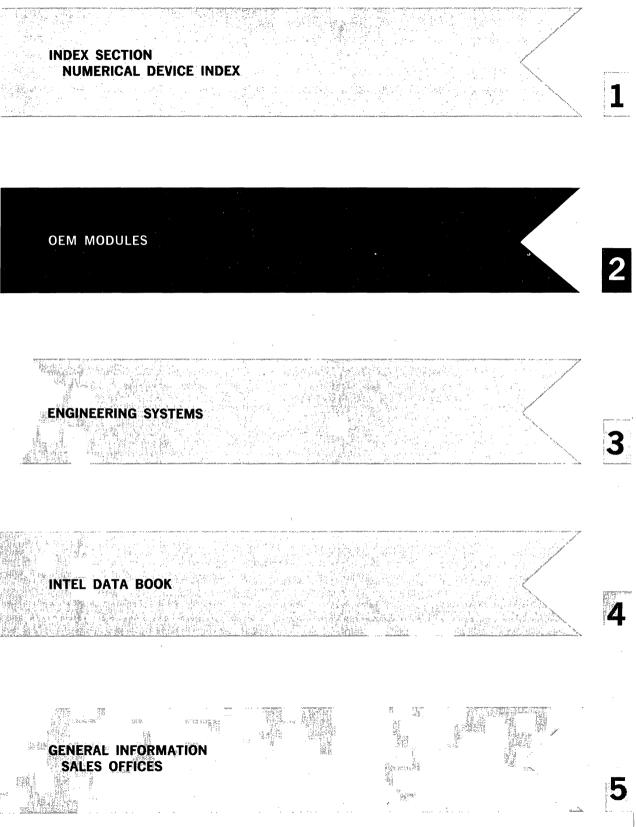

# **OEM Modules**

| Microcomputer Systems Line                                                                      | Card2-1                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8086-Based Single Board C                                                                       | omputers                                                                                                                                                                                                    |

| Am97/8605<br>RMX on the Am97/8605<br>iSBC 86/05 and Am97/8605<br>Jumper Comparison<br>Am97/0343 | 16-Bit Single Board Computer       2-2         Application Note by Bruce Pettner       2-7         Application Note by Bruce Pettner       2-9         Memory Expansion Module for the Am97/8605       2-14 |

| Am97/8605A                                                                                      | 8086-Based 16-Bit Single Board Computer2-17                                                                                                                                                                 |

| High-Speed Dynamic Memo                                                                         | ry Boards                                                                                                                                                                                                   |

| Am97/0000 Series<br>Am97/0000B Series                                                           | Random-Access Memory Boards                                                                                                                                                                                 |

| Am97/0000C Series<br>Am96/0000L Series                                                          | 512K - 4 Megabyte RAM Boards2-28<br>512K - 4 Megabyte RAM Boards with LBX2-32                                                                                                                               |

| SBX Expansion Products                                                                          |                                                                                                                                                                                                             |

| Am94/0350<br>iSBX 350 and Am94/0350                                                             | Parallel I/O SBX Module2-34                                                                                                                                                                                 |

| Jumper Comparison<br>Am94/0351<br>iSBX 351 and Am94/0351                                        | Application Note by Doug Kern                                                                                                                                                                               |

| Jumper Comparison<br>Am94/1530                                                                  | Application Note by Doug Kern                                                                                                                                                                               |

| Am94/1541<br>Am94/2000                                                                          | Stepper Motor Controller SBX Module2-49<br>SBX Motherboard2-53                                                                                                                                              |

| Peripheral Boards                                                                               |                                                                                                                                                                                                             |

| Am95/6120<br>Am95/6110 to Am95/6120                                                             | Intelligent Floppy Disk Controller Board                                                                                                                                                                    |

| Upgrade                                                                                         | Application Note by Bruce Pettner                                                                                                                                                                           |

| Am96/6130<br>Am96/5232<br>USING EEPROMS ON                                                      | Intelligent Floppy Disk Controller Board                                                                                                                                                                    |

| Am96/5232                                                                                       | Application Note by Tom Crawford2-74                                                                                                                                                                        |

| Am96/3500<br>Am96/8052                                                                          | Intelligent Serial Interface Board2-76<br>Intelligent Color Video Controller Board2-78                                                                                                                      |

| Card Cages and System Cl                                                                        | nassis                                                                                                                                                                                                      |

| Am95/6440, 6448,                                                                                |                                                                                                                                                                                                             |

| 6450, 6452A                                                                                     | Card Cages and System Chassis2-79                                                                                                                                                                           |

# **Microcomputer Systems**

Line Card

01702C

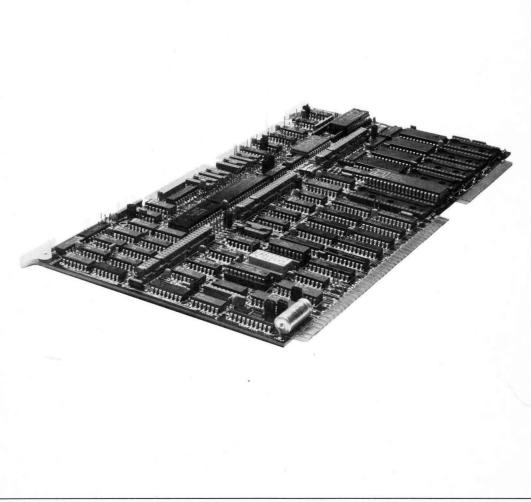

Am97/8605

8086 16-Bit Single Board Computer

#### DISTINCTIVE CHARACTERISTICS

- 8086 microprocessor with 5,8, or 10MHz operation

- Fully software transparent with Intel iSBC\*86/05 and iSBC 86/12

- On-board socket for 8087 Numeric Data Coprocessor

- Two 16-bit timers/event counters

- Two serial ports with optional Z80B-SIO/0

- Sockets for up to 64K bytes EPROM. Expandable onboard to 128K with memory module

- 24 programmable parallel I/O lines

- Nine levels of vectored interrupt control

#### **GENERAL DESCRIPTION**

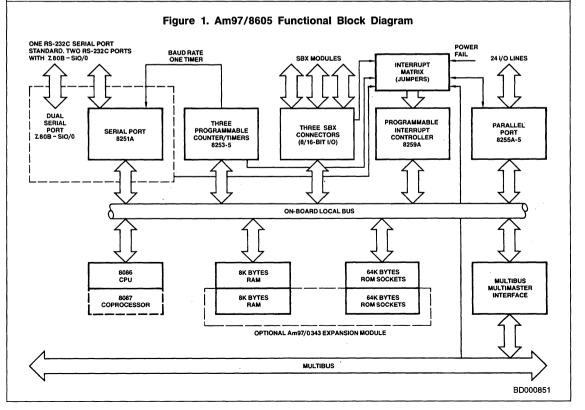

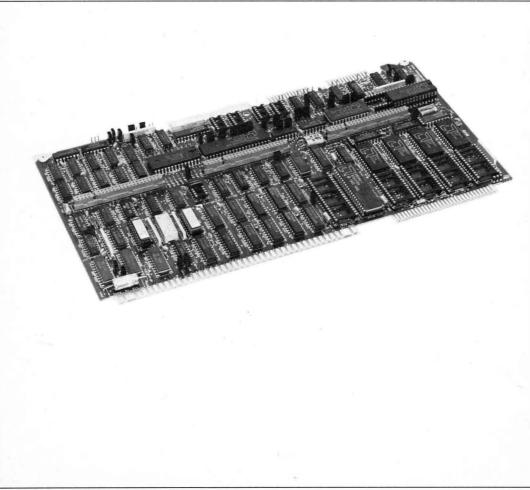

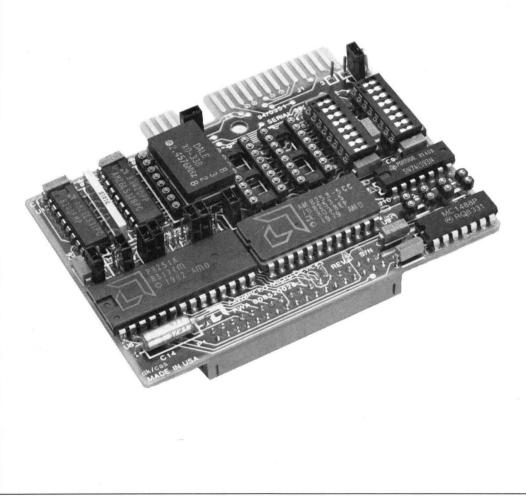

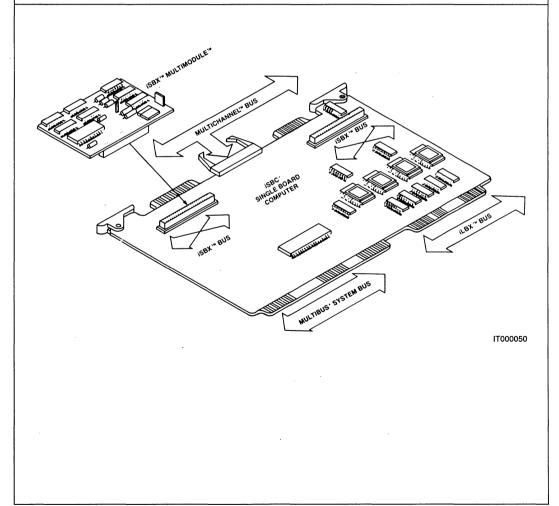

The Am97/8605 is a complete 16-bit computer system on a single MULTIBUS\* board. It includes CPU, 8K static RAM, EPROM sockets, counter/timers, 3 SBX connectors, and both serial and parallel I/O ports. The large EPROM

capacity, extensive I/O, and modular expansion capabilities make the Am97/8605 ideally suited for industrial control and intelligent I/O applications. It is designed to work in both standalone and multiple CPU systems.

#### PRODUCT OVERVIEW

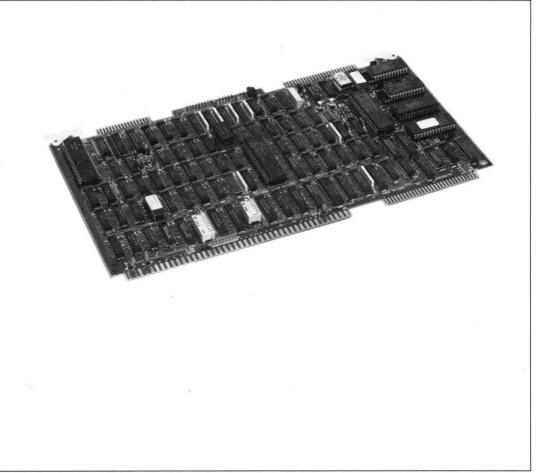

The Am97/8605 is a powerful 16-bit single board computer that is based on the 8086 microprocessor and 8087 coprocessor. The Am97/8605 is a complete computer system on a single MULTIBUS board (see Figure 1). It includes CPU, static RAM, EPROM sockets, counter/timers, 3 SBX connectors, and both serial and parallel I/O ports. In addition, it has full MULTIBUS multimaster capability, interrupt logic, and is fully software compatible with the Intel iSBC 86/05 and iSBC 86/ 12 boards.

The large EPROM capacity, extensive I/O, and modular expansion capabilities make the Am97/8605 ideally suited for ROM-intensive control and I/O applications. It is designed to work as both a standalone CPU and as a slave CPU in a multiple master system.

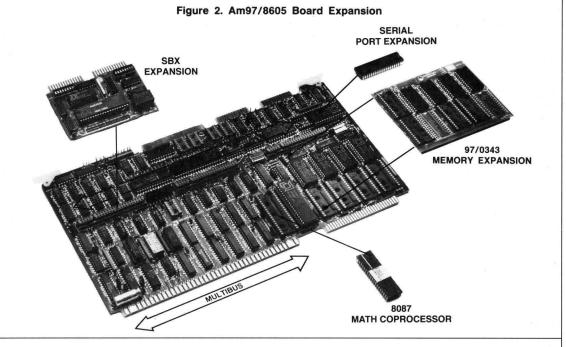

The Am97/8605 is a very versatile CPU board. Custom I/O and special functions can be added with the addition of up to three SBX modules. Memory capacity can be doubled by adding an Am97/0343 Memory Expansion Module, and an additional serial port can be added by using the Z80B-SIO/O Serial I/O chip. The Am97/8605 board comes in three CPU speeds (5,8, or 10MHz) and the 5MHz version can be ordered with or without an 8087 coprocessor.

#### **Central Processing Unit**

The Am97/8605 contains the high-performance, 16-bit 8086 microprocessor. The pipelined architecture of the 8086 incorporates both a bus interface unit and an execution unit. This enables the microprocessor to execute one instruction while at the same time fetching the next, thus greatly improving throughput.

The advanced architecture of the 8086 supports high-level languages and complex application programs. The microprocessor contains four 16-bit data registers, two 16-bit index registers and two 16-bit base pointer registers. It can directly access up to one megabyte of memory. The 8086 has 24 operand addressing modes for comprehensive memory addressing and for support of various data structures. The instruction set includes variable length instruction format, 8 and 16-bit signed and unsigned arithmetic operators for binary, BCD and ASCII data, and iterative word and byte string manipulation functions.

#### **Basic Am97/8605 Components**

| CPU                  | 8086         |

|----------------------|--------------|

| Coprocessor          | 8087         |

| Static RAM           | 9128 or 6116 |

| Counter/Timers       | 8253-5       |

| Serial I/O           | 8251A        |

| Parallel I/O         | 8255A-5      |

| Interrupt Controller | 8259A        |

|                      |              |

#### Numeric Data Coprocessor

The 8087 is a numeric coprocessor that can provide up to 100 times the performance of an 8086 alone for numeric processing. It performs arithmetic, transcendental, and comparison operations on a variety of numeric data types. It supports 32 and 64-bit floating point and 16, 32, and 64-bit integer numbers.

The 8087 works in parallel with the 8086. Both processors share the same data and address lines and communicate with each other through status lines. When the 8087 recognizes an instruction that it must execute, it gains control of the local

bus. In this manner both the 8086 and 8087 can execute their own particular instructions.

The 8087 coprocessor is ideally suited for numerical-based application programs. A socket is provided on-board so that you may add the 8087 when ordering the board, or at a later date.

#### **On-Board Memory**

The Am97/8605 comes with 8K bytes of high-speed static RAM and four 28-pin memory sockets. The four sockets will accept any JEDEC standard 24/28-pin memory device for up to 64K bytes of EPROM memory. If more RAM and less EPROM is desired, two of the sockets may be used for static RAMs.

If additional memory is required, the Am97/0343 Memory Expansion Module can be added to double both RAM and EPROM capacity for a total of 16K bytes of RAM, and 128K bytes of EPROM (see Figure 2).

Full 20-bit addressing is utilized on the Am97/8605, allowing it to control up to one megabyte of memory over the MULTIBUS.

Memory accesses are performed either a word (16 bits) at a time, or a byte (8 bits) at a time, for maximum flexibility.

#### Serial I/O

The Am97/8605 will accommodate either an 8251A or Z80B-SIO/0 Serial I/O device. The 8251A comes with the board and provides a single RS-232C serial port. The 8251A can be replaced by an Z80B-SIO/0 which will provide two serial ports. Both devices feature software-selectable baud rates, synchronous and asynchronous operation, parity, data format and control character format. The serial lines are routed to two 26pin edge connectors on top of the Am97/8605 board.

#### Parallel I/O

An 8255A-5 Programmable Peripheral Interface (PPI) device supplies 24 lines of parallel input/output capability to the Am97/8605. These lines can be programmed and hardware configured as three sets of 8-bit ports with either status-driven, polled, or interrupt-driven protocol. One of the ports is supplied with a bidirectional bus transceiver, while sockets are provided for drivers or terminators for the other two ports. A 50-pin edge connector is provided on top of the board to access the ports.

#### **Programmable Timers**

To handle timing, sequencing, and counting functions, the Am97/8605 board utilizes an 8253-5 Programmable Interval Timer. The 8253-5 has three independent, 16-bit interval timer/event counters. Each counter is capable of operating in either BCD or binary mode. Two counters are available to the systems' designer, while the third is dedicated for generating the baud rate for the serial port.

#### Interrupt Capability

Nine interrupt levels are supported on the Am97/8605. The non-maskable interrupt line is routed directly to the 8086, while an 8259A Programmable Interrupt Controller (PIC) handles eight vectored interrupt levels. The 8259A PIC efficiently

oversees and controls the interface between I/O devices and the CPU. The 8259A features four priority processing modes including auto rotating, fully nested, polled and specific priority. In addition, the interrupt mask register can be programmed to mask a variety of interrupt levels. The number of interrupt levels is expandable to 64 by the addition of slave 8259A PICs on the MULTIBUS.

#### Multimaster Capability

Full MULTIBUS arbitration is provided on the Am97/8605 board through the use of an 8289 Bus Arbiter. The control logic allows up to three masters using serial priority resolution, and sixteen masters using parallel priority resolution. This capability makes the Am97/8605 particularly suited for development and OEM applications requiring multiple master processors.

#### **SBX Expansion**

The Am97/8605 contains three 8/16-bit SBX type connectors for plug-in I/O expansion. These SBX connectors meet the

Intel iSBX\* specifications and can be used to add on-board I/O functions. By mounting modules directly on the Am97/ 8605 CPU board, less interface logic, less power, higher performance, and lower costs result when compared to alternative expansion methods.

#### SPECIFICATIONS

#### CPU

8086 CPU with optional 8087 coprocessor

#### Word Size

Instruction 8, 16, 24, or 32 bits Data 8 or 16 bits

#### System Clock

The Am97/8605 can be ordered with either a 5, 8, or 10MHz system clock.

| System Clock (MHz) | 5    | 8      | 10     |

|--------------------|------|--------|--------|

| CPU                | 8086 | 8086-2 | 8086-1 |

| Coprocessor        | 8087 |        |        |

#### **CPU Cycle Time**

| At 10MHz | 600ns<br>200ns (with instruction in queue)  |

|----------|---------------------------------------------|

| At 8MHz  | 750ns<br>250ns (with instruction in queue)  |

| At 5MHz  | 1200ns<br>400ns (with instruction in queue) |

#### **Memory Cycle Time**

| RAM   | 150ns (no-wait-states)                |

|-------|---------------------------------------|

| EPROM | Jumper selectable from 200ns to 450ns |

|       |                                       |

#### Memory Capacity and Addressing

On-Board RAM: 8K Bytes

0-1FFF H

#### On-Board EPROM:

| Device | Total Capacity | Address Range   |

|--------|----------------|-----------------|

| 2716   | 8K Bytes       | FE000 - FFFFF H |

| 2732   | 16K Bytes      | FC000 – FFFFF H |

| 2764   | 32K Bytes      | F8000 – FFFFF H |

| 27128  | 64K Bytes      | F0000 – FFFFF H |

On-Board RAM with Am97/0343 Expansion Module: 0-3FFF H 16K Bytes

On-Board EPROM with Am97/0343 Expansion Module:

| Device | Total Capacity | Address Range   |

|--------|----------------|-----------------|

| 2716   | 16K Bytes      | FC000 - FFFFF H |

| 2732   | 32K Bytes      | F8000 - FFFFF H |

| 2764   | 64K Bytes      | F0000 - FFFFF H |

| 27128  | 128K Bytes     | E0000 – FFFFF H |

#### Serial I/O

Configured for either one or two ports. The 8251A provides one serial port, while the Z80B-SIO/0 provides two.

Synchronous Baud Rates: 4.800 to 38.400

Asynchronous Baud Rates: 75 to 19,200

Synchronous Modes: 5/8-bit characters with internal or external character synchronization and automatic sync insertion.

Asynchronous Modes: 5/8-bit characters: break character generation; 1, 1-1/2, or 2 stop bits; and false start bit detection.

#### Parallel I/O

24 programmable lines are provided utilizing the 8255A-5 Programmable Peripheral Interface device.

#### Timers

Three independent, fully programmable, 16-bit timers/event counters are provided utilizing the 8253-5. Two of these are user-available, while the third is dedicated for baud rate generation.

#### Interfaces

| MULTIBUS:     | All signals three-state TTL, 32mA sink |

|---------------|----------------------------------------|

| Serial I/O:   | RS-232C to J2A, J2B                    |

| Parallel I/O: | User-selectable                        |

| Interrupt:    | TTL active-LOW, 9 levels               |

| SBX:          | Per Intel iSBX specifications          |

#### Connectors

| Interface                              | Pins           | Centers                         | Mating Connectors                                                                                         |

|----------------------------------------|----------------|---------------------------------|-----------------------------------------------------------------------------------------------------------|

| MULTIBUS<br>Serial I/O<br>Parallel I/O | 86<br>26<br>50 | 0.156 in.<br>0.1 in.<br>0.1 in. | Viking 3KH43/9AMK12<br>3M 3462-0001 Flat or<br>AMP 88106-1 Flat<br>3M 3415-000 Flat or<br>TI H312125 Pins |

#### **Physical Characteristics**

| Width:           | 12.00 in | (30.48 cm.) |

|------------------|----------|-------------|

| Height:          | 6.50 in  | (17.15 cm.) |

| Thickness:       | 0.50 in  | (1.27 cm.)  |

| Weight:          | 15 oz    | (425 gr.)   |

| Shipping Weight: | 2.00 lbs | (907 gr.)   |

#### **Electrical Characteristics**

**DC** Power Requirements

| +5 Volts  | 2.8Amps (Typical) |

|-----------|-------------------|

| +12 Volts | 40mA              |

-12 Volts 40mA

#### **Reference Manual**

0059920036-001-Am97/8605 16-Bit SingleBoard Computer

#### **ORDERING INFORMATION**

| Part Number | Description                          |  |  |  |

|-------------|--------------------------------------|--|--|--|

| 97/8605/005 | 5MHz 8086 CPU Board without an 8087  |  |  |  |

| 97/8605/008 | 8MHz 8086 CPU Board without an 8087  |  |  |  |

| 97/8605/010 | 10MHz 8086 CPU Board without an 8087 |  |  |  |

| 97/8605/105 | 5MHz 8086 CPU Board with an 8087     |  |  |  |

| Options     | Options                              |  |  |  |

| 97/8605/500 | EPROM Monitor for the Am97/8605      |  |  |  |

| 97/0343     | Memory Expansion Module              |  |  |  |

# RMX On The Am97/8605

# **RMX On The Am97/8605**

Application Note by Bruce Pettner AMD Microcomputer Systems Directorate

#### INTRODUCTION

Are customers asking you how to configure the Am97/8605 Single Board Computers to run RMX 86? If so, the following information should help get them started:

The fully configured RMX 86 system is a unique environment that utilizes the special capabilities of its associated hardware and software. Due to this flexibility, there are many possible jumper configurations for the CPU board (designated by the user, based on his application requirements). Keeping this in mind, however, it is possible to provide the customer with a "basic" jumper configuration that allows the iRMX\* 86 Nucleus Demo, version 3.0, to be loaded and run on the Am97/8605 board. The hardware configuration used in our test lab was:

3. Am95/6448 - Standard 6-Slot Card Cage w/power supply

The software used was iRMX 86, version 3.0, and the development tool used for down-loading the software was ICE\* 86A (5MHz pod). Information on version 5.0 of iRMX 86 will be provided as it becomes available.

The following table shows the basic jumper configuration used.

|            | ADD                | DESCRIPTION                                  |

|------------|--------------------|----------------------------------------------|

|            | E1 – E2<br>E6 – E7 | 1 wait states – I/O<br>2 wait states – PROMs |

|            | E10 - E11          | 3 wait states – acknowledge                  |

|            | E14 – E15          | Bus timeout timer enable                     |

|            |                    |                                              |

| 8253–5     | E25 – E27          | Timer 0 gate input                           |

| Timer      | E32 – E33          | Timer 1 gate input                           |

|            | E56 – E57          | Timer 2 clock input                          |

|            | E58 – E59          | Timer 0 clock input                          |

|            | E60 – E61          | Timer 1 clock input                          |

|            | E69 – E70          | Serial port B RX, TX clk (timer 2)           |

|            | E79 – E80          | Serial port A RX clock (timer 2)             |

|            | E83 – E84          | Serial port A TX clock (timer 2)             |

| Serial     | E87 – E88          | Connects CTS to RTS of port A                |

| Port       | E89 – E90          | Connects CTS to RTS of port B                |

|            | E91 – E92          | External DTR port A                          |

| Memory     | E107 – E108        | Enable RAM at 00000H-1FFFFH                  |

|            | E115 – E116        | Enable PROM at E0000H – FFFFFH               |

| 8259       | E120 – E121        | NON-MASKABLE INTERRUPT                       |

| Interrupt  | E123 – E124        | Clock 1 out to IR2                           |

| Controller | E143 – E131        | INT3/ to IR3                                 |

|            | E147 – E130        | INT4/ to IR4                                 |

|            | E146 – E145        | INT5/ to IR5                                 |

|            | E125 – E128        | RXRDY to IR6                                 |

|            | E134 – E127        | TXRDY to IR7                                 |

|            | E170 – E171        | 8086 clock (always installed)                |

| ·          | E177 – E178        | Disable battery backup                       |

|            | E179 – E180        | Allows 97/8605 to be BCLK/ source            |

|            | E186 – E187        | Bus priority out (BPRO/)                     |

#### Am97/8605-iRMX Nucleus Demo Jumper List

\*iRMX and ICE are registered trademarks of Intel Cororation.

RMX On The Am97/8605

| Am97/9605 – iRMX Nucleus Demo Jumper List (cont.) |                                                |                                                                        |                                |

|---------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------|--------------------------------|

|                                                   | ADD                                            |                                                                        | DESCRIPTION                    |

|                                                   | E188 – E189<br>E191 – E192                     | Bus arbitor, resident<br>Allows 97/8605 to b                           |                                |

| Jumper Block<br>X1                                | 1 – 14<br>3 – 12<br>6 – 9                      | PROM Select<br>PROM select<br>PROM select                              | 2732 EPROMs                    |

| Switch 1                                          | 1 ON<br>2 ON<br>3 ON<br>4 OFF<br>5 OFF<br>6 ON | SBX J4<br>SBX J3<br>SBX J5<br>Don't care<br>PROM select<br>PROM select | ON = disabled<br>OFF = enabled |

|                                                   | 7 ON<br>8 ON                                   | PROM select<br>PROM Select                                             |                                |

Note: Intel's iRMX 86 Nucleus Demo, version 3.0 (Part number 143705-001) comes on a single-density diskette as part of the iRMX 86 Software Package.

The Am97/8605 is a complete 16-bit computer system on a single MULTIBUS\* board. It includes CPU, static RAM, EP-ROM sockets, counter/timers, 3 SBX connectors, and both serial and parallel I/O ports. The large EPROM capacity,

#### FEATURES

- 8086 microprocessor with 5,8, or 10MHz operation

- Fully software transparent with Intel iSBC\* 86/05 and iSBC 86/12

- Three SBX bus expansion connectors

- On-board socket for 8087 Numeric Data Coprocessor

- Two 16-bit timers/event counters

- Two serial ports with optional Z8OB-SIO/0

- 8K bytes of static RAM. Expandable on-board to 16K with Am97/0343 Memory Expansion Module

extensive I/O, and modular expansion capabilities make the Am97/8605 ideally suited for industrial control and intelligent I/O applications. It is designed to work in both standalone and multiple CPU systems.

- Sockets for up to 64K bytes EPROM. Expandable on-board to 128K with memory module

- 24 programmable parallel I/O lines

- Nine levels of vectored interrupt control

- MULTIBUS multimaster interface

- One year warranty and Rapid Exchange Service (RES)

- · Extensive burn-in and testing for enhanced reliability

### iSBC 86/05 and Am97/8605 Jumper Comparison

Application Note by Bruce Pettner Microcomputer Systems Directorate

#### INTRODUCTION

The following pages are a "pin-for-pin comparison" of Intel's iSBC\* 86/05 board and our Am97/8605 8086-Based, 16-Bit Single Board Computers (SBC). The intent is to show their functional similarities and to provide a quick reference list for reconfiguring to user requirements.

The following table starts on the left with a consecutive list of numbers from 1 to 219, which represent jumper pin numbers. The next column to the right is a list of jumpers that appear on Intel's iSBC 86/05 board. When a jumper does not exist on-board, the word "none" is written in its place. The next column to the right contains the pin number on the Am97/8605 SBC with the signal that corresponds to that provided by the Intel board jumper. The last column contains the signal description, as specified by the Intel schematic. All discrepancies are noted in the Legend and Tables following the jumper pin list.

| Table | 1.0 | iSBC | 86/05 | and | Am97/8605 | Jumper | Comparison |

|-------|-----|------|-------|-----|-----------|--------|------------|

|       |     |      |       |     |           |        |            |

|          | Intel      | AMD        |                         |

|----------|------------|------------|-------------------------|

| PIN #    | iSBC 86/05 | Am97/8605  | SIGNAL                  |

| 1        | 1          | 1          | 1 WAIT/                 |

| 2        | 2          | 2          | I/O sync ready          |

| 3        | 3          | 3          | 2 WAIT/                 |

| 4        | 4          | 4          | 1 WAIT/                 |

| 5        | 5          | 5          | 0 WAIT/                 |

| 6        | 6          | 6          | PROM sync ready         |

| 7        | 7          | 7 !        | 2 WAIT/                 |

| 8        | 8          | 8 !        | 3 WAIT/                 |

| 9        | 9          | 9          | 2 WAIT/                 |

| 10       | 10         | 10         |                         |

| 11       | 11         | 11 -       | 3 WAIT/                 |

| 12       | none       | 12         | OPT1 J5-28              |

| 13       | 13         | 13         | · ·                     |

| 14       | 14         | 14         |                         |

| 15       | 15         | 15         |                         |

| 16       | none       | 16         |                         |

| 17       | 17         | 17         |                         |

| 18       | 18         | 18         |                         |

| 19       | 19         | 19         | PROM ASYNC              |

| 20       | 20         | 20         | BUSY/ (J6)              |

| 21       | 21         | 21         | READY/ (J6)             |

| 22       | 22         | 22         | STXD                    |

| 23       | 23         | 23         | EXT CLK/                |

| 24       | 24         | 24 !       | OVERRIDE/               |

| 25       | 25         | 33 *       | GATE 1 CNTRL            |

| 26       | 26         | 26         | NMI MASK/               |

| 27       | 27         | 27         | +5 VOLTS                |

| 28<br>29 | 28<br>29   | 28 .<br>29 | 8287 pin 11 (T/R)       |

|          |            |            | GROUND                  |

| 30<br>31 | 30<br>31   | 30<br>31   | PB INTR<br>BUS INTR OUT |

| 31       | 31         | 32         | +5 VOLTS                |

| 32       | 32         | 32<br>25 * | GATE 0 CNTRL            |

| 33       | 33         | 34         | PA INTR                 |

| 34       | 34         | 35         | TEST/                   |

| 35       | 36         | 36 !       | PFSN/                   |

| 30       | none       | 37         | SBX3 INTR 1 (J5-12)     |

| 38       | 38         | 38         | J1-28                   |

| 39       | 39         | 39         | J1-30                   |

| 40       | 40         | 40         | J1-32                   |

| 40       | 40         | 40         | J1-26                   |

| 42       | 42         | 42         | 8255A-5 PC-5            |

| 42       | 43         | 43         | 8255A-5 PC-6            |

|          |            |            |                         |

\*iSBC and iSBX are registered trademarks of Intel Corporation.

197/8605 nparison ~ ~

#### Table 1.0 (cont.)

,

| àğ                |          |            |           |                                       |  |  |

|-------------------|----------|------------|-----------|---------------------------------------|--|--|

| nper Compar       | Intel    |            | AMD       |                                       |  |  |

|                   | PIN #    | iSBC 86/05 | Am97/8605 | SIGNAL                                |  |  |

| /us and<br>Jumper | 44       | 44         | 44        | 8255A-5 PC-7                          |  |  |

|                   | 45       | 45         | 45        | 8255A-5 PC-4                          |  |  |

| ゴ                 | 46       | 46         | 46        | J1-24                                 |  |  |

| 6                 | 47       | 47         | 47        | J1-22                                 |  |  |

| •                 | 48       | 48         | 48        | J1-20                                 |  |  |

| ñ                 | 49       | 49         | 49        | J1-18                                 |  |  |

| טסנו              | 50       | 50         | 50        | 8255A-5 PC-0                          |  |  |

|                   | 51       | 51         | 51        | 8255A-5 PC-1                          |  |  |

|                   | 52       | 52         | 52 !      | 8255A-5 PC-2                          |  |  |

|                   | 53       | 53         | 53        | 8255A-5 PC-3                          |  |  |

|                   | 54       | 54         | -         | 8255A-5 PC-3 (light)                  |  |  |

|                   |          | -          | 54 +      | OVERRIDE/ second serial port          |  |  |

|                   | 55       | 55         | -         | light                                 |  |  |

|                   |          | -          | 55 +      | Z80-SIO/0 RXTXCB second serial port   |  |  |

|                   | 56       | 56         | 56 !      | 8253-5 CLK 2                          |  |  |

|                   | 57       | 57         | 57        |                                       |  |  |

|                   | 58       | 58         | 58        |                                       |  |  |

| 1                 | 59       | 59         | 59        | 8253-5 CLK 0                          |  |  |

|                   | 60       | 60         | 60        |                                       |  |  |

|                   | 61       | 61         | 61        | 8253-5 CLK 1                          |  |  |

|                   | 62       | <b>62</b>  | 62        | EXT CLK/                              |  |  |

|                   | 63       | 63         | 63 .      | 8253-5 OUT 0 (TIMER 0 INTR)           |  |  |

|                   | 64       | 64         | 64        | 8251A CLK                             |  |  |

|                   | 65       | 65         | 65        | 8253-5 OUT 1 (TIMER 1 INTR)           |  |  |

|                   | 66       | 66         | 66        | PLC                                   |  |  |

|                   | 67       | 67         | 67        | 8253-5 OUT 2                          |  |  |

|                   | 68       | 68         | -         | +5 VOLTS (P1-83,84)                   |  |  |

|                   |          | _          | 68 +      | 2XCB J2B-8                            |  |  |

|                   | 69       | 69         | -         | J2-23                                 |  |  |

|                   |          | -          | 69 +      |                                       |  |  |

| - 1               | 70       | 70         | -         | J2-19                                 |  |  |

|                   |          | -          | 70 +      | Z80-SIO/0 RXTXCB                      |  |  |

|                   | 71       | 71         | -         | -12 VOLTS (P1-79,80)                  |  |  |

|                   |          | -          | 71 +      |                                       |  |  |

|                   | 72       | 72         | 72        | 8251 TXC                              |  |  |

|                   | 73       | 73         | 73        | STXD                                  |  |  |

|                   | 74       | 74         | 74        |                                       |  |  |

| 1                 | 75       | 75         | 75        | J2-26                                 |  |  |

|                   | 76       | 76         | 76        |                                       |  |  |

|                   | 77       | 77         | 77        | J2-5                                  |  |  |

|                   | 78       | 78         | 78        | J2-21<br>00514 DXC                    |  |  |

|                   | 79       | 79         | 79        | 8251A RXC                             |  |  |

|                   | 80       | 80         | 80        | 8253-5 OUT 2                          |  |  |

| 1                 | 81       | 81         | 81        | SEC. TRANSMIT CLOCK J2-7              |  |  |

| 1                 | 82       | 82         | 82        | SEC. TRANSMIT CLOCK J2-7<br>8251A TXC |  |  |

|                   | 83<br>84 | 83<br>84   | 83<br>84  | 8253-5 OUT 2                          |  |  |

|                   | 85       | 85         |           | J2-22                                 |  |  |

| ·                 | 00       |            | - 85 +    | 52-22                                 |  |  |

|                   | 96       | -<br>86    |           | + 12 VOLTS (P1-7,8)                   |  |  |

|                   | 86       | -          | -<br>86 + |                                       |  |  |

| - 1               | 87       | 87         | 87        | CLEAR TO SEND J2-10                   |  |  |

|                   | 88       | 88         | 88        | REQUEST TO SEND J2-8                  |  |  |

|                   | 89       | 89         | 89 !      |                                       |  |  |

|                   | 90       | 90         | 90 !      |                                       |  |  |

|                   | 90<br>91 | 90         | 90 1      | 8251A DSR                             |  |  |

|                   | 92       | 92         | 92        | DATA TERMINAL READY J2-13             |  |  |

|                   | 93       | none       | none      |                                       |  |  |

|                   | 93<br>94 | none       | none      |                                       |  |  |

|                   | 94<br>95 | none       | none      |                                       |  |  |

|                   | 95<br>96 | none       | none      |                                       |  |  |

|                   | 98<br>97 | none       | none      |                                       |  |  |

|                   | 98       | none       | none      |                                       |  |  |

|                   |          |            |           | · · · · · · · · · · · · · · · · · · · |  |  |

|            | Intel      | AMD       | {                             |  |

|------------|------------|-----------|-------------------------------|--|

| PIN #      | iSBC 86/05 | Am97/8605 |                               |  |

| 99         | nóne       | none      |                               |  |

| 100        | none       | none      |                               |  |

| 101        | none       | none      |                               |  |

| 102        | none       | none      |                               |  |

| 103        | none       | none      |                               |  |

| 104        | 104        | SWITCH1   | select SBX 302 RAM expansion  |  |

| 105        | 105        | SWITCH1   | Ground                        |  |

| 105        | 105        | SWITCH1   | select SBX 341 PROM expansion |  |

| 100        | 100        | 107       | Page select RAM               |  |

| 107        | 108        | 107       | RAM @ 00000 – 1FFFF           |  |

| 109        | 109        | 109       | RAM @ 40000 - 5FFFF           |  |

| 110        | 110        |           |                               |  |

|            |            | 110       | PROM @ 20000 - 3FFFF          |  |

| 111<br>112 | 111        | 111       | RAM @ 80000 - 9FFFF           |  |

|            | 112        | 112       | PROM @ 60000 - 7FFF           |  |

| 113        | 113        | 113       | RAM @ C0000 - DFFFF           |  |

| 114<br>115 | 114        | 114       | PROM @ A0000 – BFFFF          |  |

| 115        | 115        | 115       | Page select PROM              |  |

| 116        | 116        | 116       | PROM @ E0000 - FFFFF          |  |

| 117        | 117        | 117       | SBX2 INTR 0                   |  |

| 118        | 118        | 118       |                               |  |

| 119        | 119        | 119       | EXT INTRO/ (J1-50)            |  |

| 120        | 120        | 120       | NMI MASK/                     |  |

| 121        | 121        | 121       | GROUND                        |  |

| 122        | 122        | 122       |                               |  |

| 123        | 123        | 123       | TIMER 2 INTR                  |  |

| 124        | 124        | 124       | 8259A IR2                     |  |

| 125        | 125        | 125       | SIRX INTR                     |  |

| 126        | 126        | 126       | SBX2 INTR 1                   |  |

| 127        | 127        | 127       | 8259A IR7                     |  |

| 128        | 128        | 128       | 8259A IR6                     |  |

| 129        | 129        | 129       | EDGE INTR                     |  |

| 130        | 130        | 130       | 8259A IR4                     |  |

| 131        | 131        | 131       | 8259A IR3                     |  |

| 132        | 132        | 132       | 8259A IRO                     |  |

| 133        | 133        | 133       | 8259A IR1                     |  |

| 134        | 134        | 134       | SITX INTR                     |  |

| 135        | none       | none      | · · ·                         |  |

| 136        | 136        | 136       |                               |  |

| 137        | 137        | 137       | SBX1 INTR 0                   |  |

| 138        | 138        | 138       | SBX1 INTR 1                   |  |

| 139        | 139        | 24 *!     | MINT                          |  |

| 140        | 140        | 140       | PB INTR                       |  |

| 141        | 141        | 141       | PA INTR                       |  |

| 142        | 142        | 142       |                               |  |

| 143        | 143        | 143       |                               |  |

| 144        | 144        | 144       |                               |  |

| 145        | 145        | 145       | 8259A IR5                     |  |

| 146        | 146        | 146       |                               |  |

| 147        | 147        | 147       |                               |  |

| 148        | 148        | 148       |                               |  |

| 149        | 149        | 149       |                               |  |

| 150        | 150        | 150       | PLC                           |  |

| 151        | none       | none      |                               |  |

| 152        | 152        | 152       | 8288 AMWTC/ (J6-2)            |  |

| 153        | 153        | 153       | U33 (U73) & U66 (U74) PGM     |  |

| 154        | none       | none      |                               |  |

| 155        | none       | none      |                               |  |

| 156        | none       | none      |                               |  |

| 157        | none       | none      |                               |  |

| 158        | none       | none      |                               |  |

| 159        | none       | none      |                               |  |

| 160        | none       |           | ·                             |  |

.....

| ມ                       |  |

|-------------------------|--|

| Am97/8605<br>Comparison |  |

| 97/<br>1pa              |  |

| E E                     |  |

|                         |  |

| and                     |  |

| /05 and<br>Jumper       |  |

| 86/05<br>Jun            |  |

| SBC                     |  |

| iSi                     |  |

|                   | Table 1.0 (cont.)                                                                                                                                                                                                                                                                                                                                              |              |                                       |  |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------------|--|--|--|--|

| PIN #             | intei                                                                                                                                                                                                                                                                                                                                                          | AMD          |                                       |  |  |  |  |

|                   | iSBC 86/05                                                                                                                                                                                                                                                                                                                                                     | Am97/8605    | SIGNAL                                |  |  |  |  |

| 162<br>163<br>164 | none                                                                                                                                                                                                                                                                                                                                                           | none         |                                       |  |  |  |  |

| 163               | none                                                                                                                                                                                                                                                                                                                                                           | none         |                                       |  |  |  |  |

| 164               | none                                                                                                                                                                                                                                                                                                                                                           | none         |                                       |  |  |  |  |

| 165               | none                                                                                                                                                                                                                                                                                                                                                           | none         |                                       |  |  |  |  |

| 166               | 166                                                                                                                                                                                                                                                                                                                                                            | 166          | OPT 0 (J3-30)                         |  |  |  |  |

| 167               | 167                                                                                                                                                                                                                                                                                                                                                            | 167          | OPT 1 (J3-28)                         |  |  |  |  |

| 168               | 168                                                                                                                                                                                                                                                                                                                                                            | 168          | ON BD ADR/                            |  |  |  |  |

| 169               | 169                                                                                                                                                                                                                                                                                                                                                            | 169          |                                       |  |  |  |  |

| 170               | 170                                                                                                                                                                                                                                                                                                                                                            | 170          | 8284A CLK                             |  |  |  |  |

| 171<br>172        | 171<br>172                                                                                                                                                                                                                                                                                                                                                     | 1,71<br>172  | 8086 CLK                              |  |  |  |  |

| 172               | 172                                                                                                                                                                                                                                                                                                                                                            | 172          | OPT 0 (J4-30)<br>OPT 1 (J4-28)        |  |  |  |  |

| 173               | none                                                                                                                                                                                                                                                                                                                                                           | none         | OFT T (34-28)                         |  |  |  |  |

| 175               | none                                                                                                                                                                                                                                                                                                                                                           | none         |                                       |  |  |  |  |

| 176               | none                                                                                                                                                                                                                                                                                                                                                           | none         |                                       |  |  |  |  |

| 170               | 177                                                                                                                                                                                                                                                                                                                                                            | 177          |                                       |  |  |  |  |

| 178               | 178                                                                                                                                                                                                                                                                                                                                                            | 178          |                                       |  |  |  |  |

| 179               | 179                                                                                                                                                                                                                                                                                                                                                            | 179          | BCLK/ (P1-13)                         |  |  |  |  |

| 180               | 180                                                                                                                                                                                                                                                                                                                                                            | 180          | · · · · · · · · · · · · · · · · · · · |  |  |  |  |

| 181               | 181                                                                                                                                                                                                                                                                                                                                                            | none         | ) Installed = 8 MHz                   |  |  |  |  |

| 182               | 182                                                                                                                                                                                                                                                                                                                                                            | none         | Removed = 5 MHz                       |  |  |  |  |

| 183               | 183                                                                                                                                                                                                                                                                                                                                                            | 183          | CBR0/ (P1-29)                         |  |  |  |  |

| 184               | 184                                                                                                                                                                                                                                                                                                                                                            | 184          | 8289 CBRQ                             |  |  |  |  |

| 185               | 185                                                                                                                                                                                                                                                                                                                                                            | 185          | GROUND                                |  |  |  |  |

| 186               | 186                                                                                                                                                                                                                                                                                                                                                            | 186          | 8289 BPR0                             |  |  |  |  |

| 187               | 187                                                                                                                                                                                                                                                                                                                                                            | 187          | BPR0/ (P1-16)                         |  |  |  |  |

| 188               | 188                                                                                                                                                                                                                                                                                                                                                            | 188          | 8289 CRQCK, RESB, IOB, +5V            |  |  |  |  |

| 189               | 189                                                                                                                                                                                                                                                                                                                                                            | 189          | 8289 ANYREST                          |  |  |  |  |

| 190               | 190                                                                                                                                                                                                                                                                                                                                                            | 190          | GROUND                                |  |  |  |  |

| 191               | 191                                                                                                                                                                                                                                                                                                                                                            | 191          |                                       |  |  |  |  |

| 192               | 192                                                                                                                                                                                                                                                                                                                                                            | 192          | CCLK/ (P1-31)                         |  |  |  |  |

| 193               | 193                                                                                                                                                                                                                                                                                                                                                            | 193          | Bus interrupt output                  |  |  |  |  |

| 194               | 194                                                                                                                                                                                                                                                                                                                                                            | none         | INT4/ P1-37                           |  |  |  |  |

| 195               | 195                                                                                                                                                                                                                                                                                                                                                            | none         | INT2/ P1-39                           |  |  |  |  |

| 196<br>197        | 196<br>197                                                                                                                                                                                                                                                                                                                                                     | none         | INT5/ P1-38<br>  INT3/ P1-40          |  |  |  |  |

| 197               | 197                                                                                                                                                                                                                                                                                                                                                            | none<br>none | INT3/ P1-40<br>INT7/ P1-36            |  |  |  |  |

| 198               | 198                                                                                                                                                                                                                                                                                                                                                            | none         | INT0/ P1-41                           |  |  |  |  |

| 200               | 200                                                                                                                                                                                                                                                                                                                                                            | none         | INT6/ P1-35                           |  |  |  |  |

| 201               | 201                                                                                                                                                                                                                                                                                                                                                            | none         | INT1/ P1-42                           |  |  |  |  |

| 202               | none                                                                                                                                                                                                                                                                                                                                                           | none         |                                       |  |  |  |  |

| 203               | none                                                                                                                                                                                                                                                                                                                                                           | none         |                                       |  |  |  |  |

| 204               | none                                                                                                                                                                                                                                                                                                                                                           | none         |                                       |  |  |  |  |

| 205               | none                                                                                                                                                                                                                                                                                                                                                           | none         |                                       |  |  |  |  |

| 206               | 206                                                                                                                                                                                                                                                                                                                                                            | none         | Jumper in for 16-bit mode J4          |  |  |  |  |

| 207               | 207                                                                                                                                                                                                                                                                                                                                                            | none         | Jumper in for 16-bit mode J4          |  |  |  |  |

| 208               | 208                                                                                                                                                                                                                                                                                                                                                            | none         | Jumper in for 16-bit mode J3          |  |  |  |  |

| 209               | 209                                                                                                                                                                                                                                                                                                                                                            | none         | Jumper in for 16-bit mode J3          |  |  |  |  |

| 210               | 210                                                                                                                                                                                                                                                                                                                                                            | SWITCH1      | PROM select                           |  |  |  |  |

| 211               | 211                                                                                                                                                                                                                                                                                                                                                            | SWITCH1      | PROM select                           |  |  |  |  |

| 212               | 212                                                                                                                                                                                                                                                                                                                                                            | SWITCH1      | PROM select See Table 2.1             |  |  |  |  |

| 213               | 213                                                                                                                                                                                                                                                                                                                                                            | SWITCH1      | PROM select                           |  |  |  |  |

| 214               | 214                                                                                                                                                                                                                                                                                                                                                            | 214          |                                       |  |  |  |  |

| 215               | 215                                                                                                                                                                                                                                                                                                                                                            | 215          | LOCK/ (P1-25)                         |  |  |  |  |

| 216               | none                                                                                                                                                                                                                                                                                                                                                           | 216          |                                       |  |  |  |  |

| 217               | none                                                                                                                                                                                                                                                                                                                                                           | 217          | 4.72MHZ CLOCK                         |  |  |  |  |

| 218               | none                                                                                                                                                                                                                                                                                                                                                           | 218          | Z80B-SIO/0 CLK J2B                    |  |  |  |  |

| 219               | none                                                                                                                                                                                                                                                                                                                                                           | 219          | 8251 CLK J2A                          |  |  |  |  |

| LEGEND:           | LEGEND:<br>! = Jumper number duplicated on this board (see Table 1.1)<br>* = Indicates ''pin number different'' for this signal<br>+ = Indicates ''jumper exists, but has different signal''<br>none = Indicates ''jumper number does not exist on this board'' (see Table 4.0)<br>SWITCH1 = Indicates ''jumper function performed by switch'' (see Table 2.0) |              |                                       |  |  |  |  |

iSBC 86/05 and Am97/8605 Jumper Comparison

#### Table 1.1 Am97/8605 Duplicate Pins

|       | AMD       |                      |

|-------|-----------|----------------------|

| PIN # | Am97/8605 | SIGNAL               |

| 7     | 7         | DTRB on J2B-24       |

| 8     | 8         | To DSR pin on MK3884 |

| 24    | 24        | See Intel jumper 139 |

| 36    | 36        | J5-14 SBX INTO       |

| 52    | 52        | RTS To J2B-9 (CTSB)  |

| 56    | 56        |                      |

| 89    | 89        | To J2B-22            |

| 90    | . 90      | To J2B-25            |

#### Table 2.0 SWITCH1 Jumper Function

SWITCH1-1 SBX J4 select

- -2 SBX J3 select

- -3 SBX J5 select

- -4 not used

- -5 PROM select

- -6 PROM select

- -7 PROM expansion select

- -8 RAM expansion select

#### **Table 2.1 PROM Selection**

|              | Intel                | AMD                     |

|--------------|----------------------|-------------------------|

| PROM         | iSBC 86/05           | Am97/8605               |

| 2716<br>2732 | no jumper<br>210-211 | SW1-5,6 on<br>SW1-5 off |

| 2764         | 212-213              | SW1-6 off               |

| 27128        | 210-211<br>212-213   | SW1-5,6 off             |

Note: Switch 1 uses off active logic.

#### Table 3.0 PROM/IC Sockets Cross Reference

| Intel      | AMD       |                              |  |  |  |

|------------|-----------|------------------------------|--|--|--|

| iSBC 86/05 | Am97/8605 | FUNCTION                     |  |  |  |

| U8         | U11       | Parallel Port C (4-7)        |  |  |  |

| U9         | U12       | Parallel Port C (0-3)        |  |  |  |

| U10        | U13       | Parallel Port B (0-3)        |  |  |  |

| U11        | U14       | Parallel Port B (4-7)        |  |  |  |

| U33        | U72       | Bank 0 High (odd) bytes (0H) |  |  |  |

| U34        | U73       | Bank 1 High (odd) bytes (1H) |  |  |  |

| U66        | U74       | Bank 0 Low (even) bytes (0L) |  |  |  |

| U67        | U75       | Bank 1 Low (even) bytes (1L) |  |  |  |

| U35        | X1        | Jumper block                 |  |  |  |

#### **Table 4.0 Unused Jumper Pin Numbers**

| Intel        | AMD          |

|--------------|--------------|

| iSBC 86/05   | Am97/8605    |

| 12           | 93 thru 106  |

| 16           | 135          |

| 37           | 151          |

| 93 thru 103  | 154 thru 165 |

| . 135        | 174 thru 176 |

| 151          | 181          |

| 154 thru 165 | 182          |

| 174 thru 176 | 193 thru 213 |

| 202 thru 205 |              |

| 216 thru 219 |              |

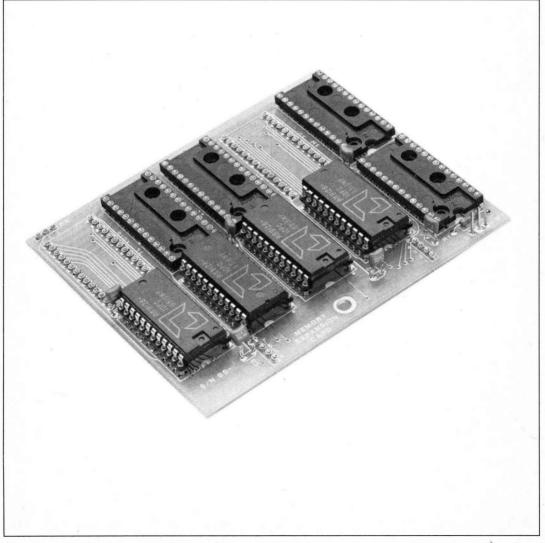

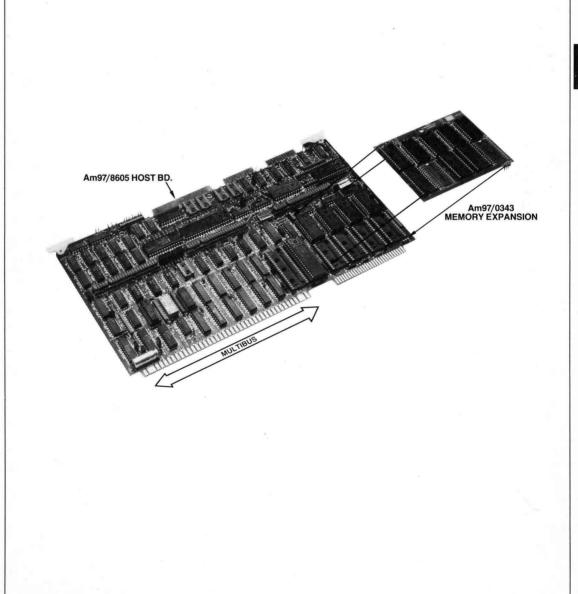

# Am97/0343

Memory Expansion Module for the Am97/8605 Single Board Computer

#### DISTINCTIVE CHARACTERISTICS

- Doubles Am97/8605 on-board memory capacity

- 8K bytes of 150ns static RAM

- Four additional 28-pin JEDEC sockets accommodate up to 64K bytes of EPROM/ROM

- Same access times as memory provided on the Am97/8605

#### **GENERAL DESCRIPTION**

The Am97/0343 Memory Expansion Module doubles the memory capacity of the Am97/8605 Single Board Computer (SBC) by providing an additional 8K bytes of static RAM and four 28-pin JEDEC EPROM sockets. It is designed to

plug directly on-board the Am97/8605 SBC and has the same access time as the memory provided on the host board.

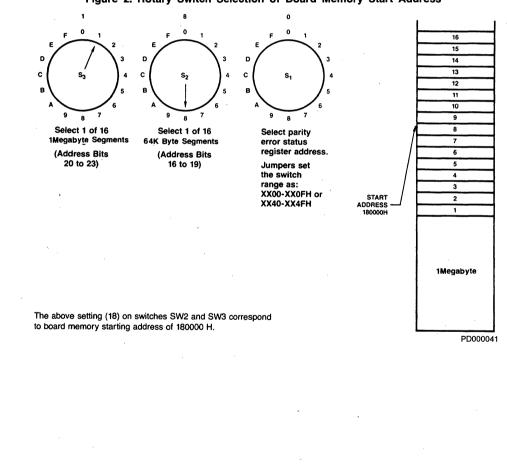

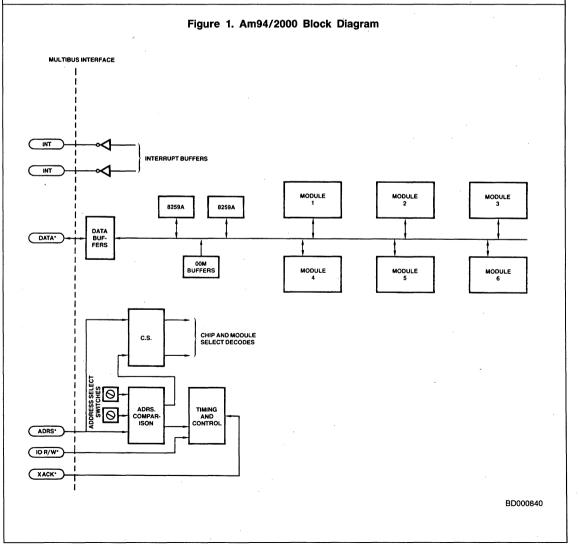

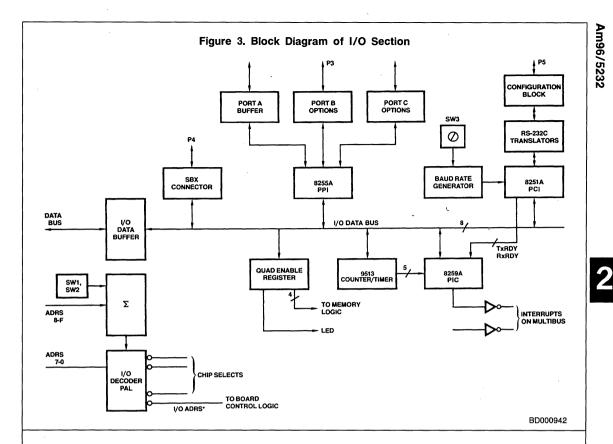

#### FUNCTIONAL DESCRIPTION