## 1086/2086 Maintenance

# Altos Computer Systems

#### **Copyright Notice**

Manual Copyright©1986 Altos Computer Systems

Programs Copyright©1986 Altos Computer Systems

All rights reserved. Printed in U.S.A.

Unless you request and receive written permission from Altos Computer Systems, you may not copy any part of this document or the software you received, except in the normal use of the software or to make a backup copy of each diskette you received.

#### Trademarks

The Altos logo, as it appears in this manual, is a registered trademark of Altos Computer Systems.

UNIX® is a registered trademark of AT&T Bell Laboratories.

UNIX System III™ is a trademark of AT&T Bell Laboratories.

XENIX® is a registered trademark of Microsoft Corporation.

MULTIBUS® is a registered trademark of Intel Corporation.

PC/AT® is a registered trademark of IBM Corporation.

System 34 Double Density  $(MFM)^{\oplus}$  is a registered trademark of IBM Corporation.

Scotch<sup>®</sup> is a registered trademark of 3M Corporation.

3270/SNA is an Altos Implementation of ACCESS/SNA developed by Communications Solutions, Inc.

WorkNet® is a registered trademark of Altos Computer Systems.

#### Limitations

Neither Altos nor its suppliers make any warranty with respect to the accuracy of the information in this manual. Altos Computer Systems reserves the right to make changes to the product described in this manual at any time and without notice.

#### FCC Warning

This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instruction manual, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user, at his own expense, will be required to take whatever measures may be required to correct the interference.

## **ABOUT THIS MANUAL**

This manual contains detailed service information for the technician who is trained in digital electronics, microcomputers, and operating systems.

The purpose of this manual is to describe the operation of the 1086/2086 Computer System and provide specific instructions to enable the technician to effectively service the 1086/2086.

Careful attention to the preventive and corrective maintenance information contained in this manual will ensure maximum trouble-free operation from the Altos 1086/2086 Computer System.

This manual is organized into the following chapters:

#### Chapter 1 System Overview

- describes the features and capabilities of the system

- provides a hardware overview of the major circuits and peripherals

- lists and shows the location of the field replaceable assemblies comprising the system

- describes and shows the dedicated and recommended expansion plug-in printed circuit board (PCB) locations

- describes and shows the locations of the front and rear-panel controls, connectors, and indicators

- discusses the software available for the system

#### Chapter 2 Specifications

lists the pertinent electrical, environmental, and physical specifications for the system shows the overall physical dimensions of the system

#### Chapter 3 Principles of Operation

- explains how the plug-in PCB subsystems interface to the system through the system bus

- describes how the system is initialized or programmed at power-up

- describes the programmed steps performed in the main operational sequences

- lists the addresses for each device that can be accessed

- includes bit definitions for the ports and external registers

- includes pertinent timing diagrams and general programmable array logic (PAL) information

#### Chapter 4 Maintenance

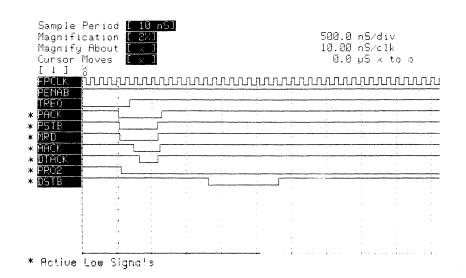

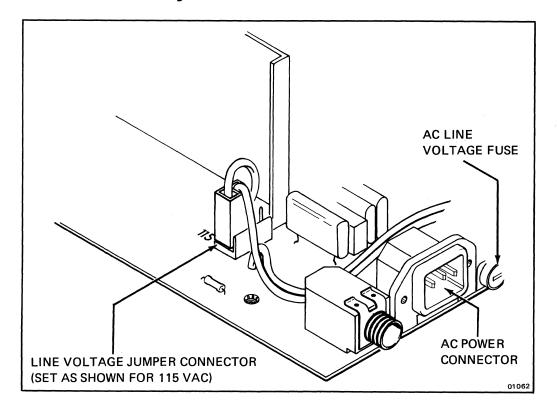

- includes 115/230 VAC conversion instructions

- provides cleaning procedures

- provides removal and replacement procedures.

- provides shipping information

#### Chapter 5 Troubleshooting

- discusses troubleshooting aids and techniques

- includes detailed troubleshooting procedures using power-up, system-confidence, and field-service diagnostics

iv

#### Appendices

Includes jumper pinning, loopback connector assembly, storage device specifications, and utility program information.

#### Glossary

Includes an alphabetical list and definitions of specialized terms and acronyms used in this manual.

#### Index

Includes an alphabetical list of names, subjects, or topics contained in this manual with the page numbers where they occur.

## **RELATED PUBLICATIONS**

The following is a list of publications that contain additional information relating to the 1086/2086 The 1086/2086 Owner's Guide is shipped with system. The remaining publications are optional the system. and are divided into three types: (1) basic (run-time) system manuals that contain information for installing and using the operating system, (2) development system manuals that include reference and tutorial material for programs available in the development system, (3) supplemental information manuals that are referenced in the text of this manual and contain additional information required to understand the operation of the 1086/2086 system. The publications listed here are available through your Altos distributor or directly from integrated circuit manufacturers.

## Shipped with 1086/2086

Altos 1086/2086 Owner's Guide (Altos part no. 690-16447-XXX)

V

## **Basic System**

- Installing XENIX on Your 1086/2086 System (Altos part no. 690-16630-XXX)

- Introduction to XENIX (Altos part no. 690-13449-XXX)

- Directory of XENIX Commands (Altos part no. 690-1664-XXX)

#### **Development System**

Altos Development System Set (Altos part no. 583-13801-XXX)

#### Supplemental Information

- Altos 1086/2086 System Reference Manual (Altos part no. 690-15623-XXX)

- Altos 1086/2086 Illustrated Parts List (Altos part no. 690-15625-XXX)

- Altos 1086/2086 Remote Diagnostics Instructions (Altos part no. 690-17072-001)

- IEEE 796 System Bus Specification (Multibus)

- Intel IAPX 286 Programmer's Reference Manual

- Intel Microsystem Components Handbook

- Intel Microprocessor and Peripheral Handbook

- Intel 8254 Data Book (Mode 2)

- National Semiconductor 58167 Applications Note Data Handbook

- Advanced Micro Devices 9517 Technical Reference Manual

- Zilog Data Handbook/Technical Manual

- Hitachi HD68450 Data Book

- Hitachi Microcomputer Handbook

- National Cash Register 5385 SCSI Protocol Controller Data Sheet

- Archive QIC-Ø2 1/4-Inch Tape Drive Interface Standard

- Archive QIC-24 1/4-Inch Cartridge Tape Drive Format Standard

- Archive QIC-36 Basic 1/4-Inch Cartridge Streaming Tape Drive Interface Standard

- NEC PD765 Data Sheet

- NEC Data Handbook

- ANSI X3T9.2/82-2 SCSI Small Computer System Interface

- National Cash Register Data Handbook

## SPECIAL SYMBOLS AND NOTATIONS

The following is a list of the special symbols and notations used in this manual.

About This Manual

| Symbol/Notation | Description                                                                                                                         |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------|

| * (Asterisk)    | Used following a capitalized<br>mnemonic or signal name to<br>indicate a "not" (complement)<br>function or an active low<br>signal. |

|                 | Example: PERR*                                                                                                                      |

| h               | Used after a number to<br>indicate that the number is a<br>hexadecimal notation.                                                    |

|                 | Example: 25h                                                                                                                        |

| đ               | Used after a number to<br>indicate that the number is a<br>decimal notation.                                                        |

|                 | Example: 16d                                                                                                                        |

| b               | Used after a number to<br>indicate that the number is a<br>binary notation.                                                         |

|                 | Example: Ølb                                                                                                                        |

Altos 1086/2086 Computer System

## TABLE OF CONTENTS

## **1 SYSTEM OVERVIEW**

|                                         | 1-3    |

|-----------------------------------------|--------|

|                                         |        |

|                                         | L-3    |

|                                         | L-3    |

| Configurations                          | L-4    |

|                                         | L-4    |

|                                         | L-5    |

| Diagnostics                             | L-5    |

| Power-Up Tests                          | L-6    |

| User System-Confidence Tests            | L-6    |

| Field-Service Diagnostics               | L-6    |

| Hardware                                | L-7    |

| System Bus                              |        |

|                                         | L-8    |

|                                         | L-8    |

| Communications PCB                      |        |

| File Processor PCB                      | L-9    |

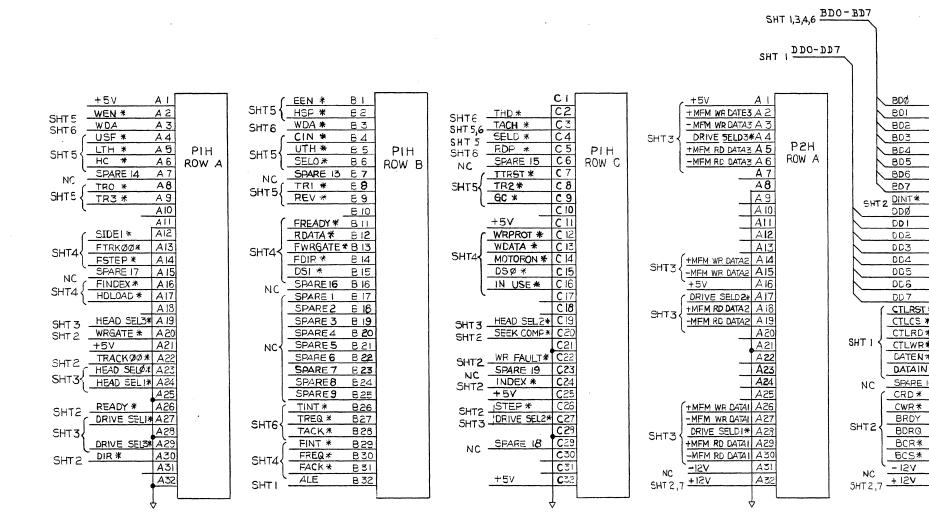

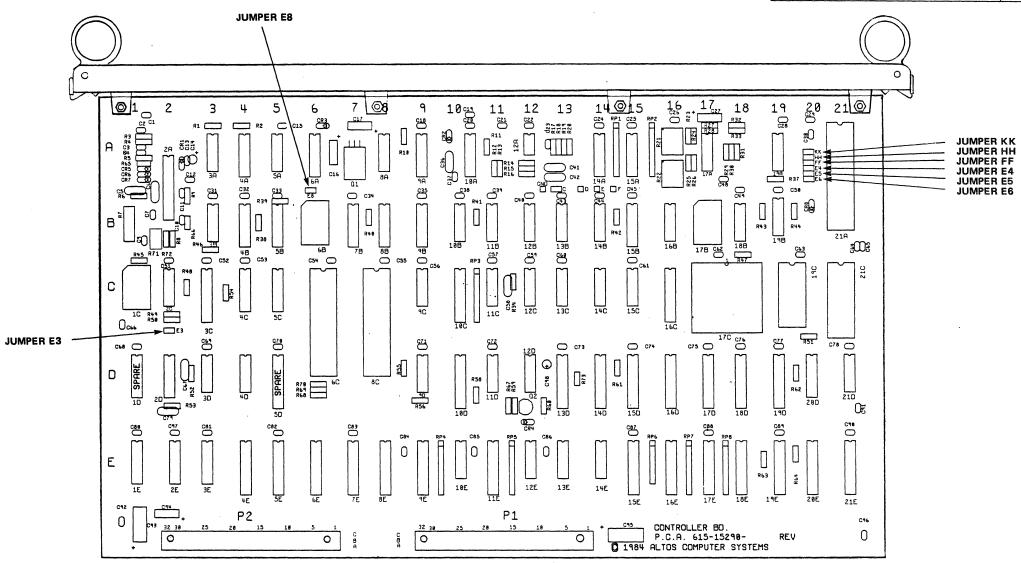

| Controller PCB                          |        |

| FIELD REPLACEABLE UNITS                 |        |

| CONTROLS, CONNECTORS, AND INDICATORS ]  |        |

|                                         | L = 13 |

|                                         |        |

| Rear Panel                              |        |

| PLUG-IN PRINTED CIRCUIT BOARD LOCATIONS |        |

|                                         | L-15   |

| Operating System Programs               |        |

| Address Translation                     |        |

| Disk Performance                        | 1-17   |

| Serial Port Performance                 | 1-17   |

| Compatibility                           |        |

|                                         | L-18   |

## 2 SPECIFICATIONS

| INTRODUCTION                 | • | • | • | • | • | • | • | • | • | 2-3 |

|------------------------------|---|---|---|---|---|---|---|---|---|-----|

| ELECTRICAL SPECIFICATIONS    |   |   |   | • | • | • |   | • | • | 2-3 |

| ENVIRONMENTAL SPECIFICATIONS | • |   |   |   | • | • | • | • |   | 2-8 |

| PHYSICAL SPECIFICATIONS      | • | • |   | • | • | • | • | • |   | 2-8 |

## **3 PRINCIPLES OF OPERATION**

| INTRODUCTION               | • | • | • | • | • | • |   | • | • | • | 3-5 |

|----------------------------|---|---|---|---|---|---|---|---|---|---|-----|

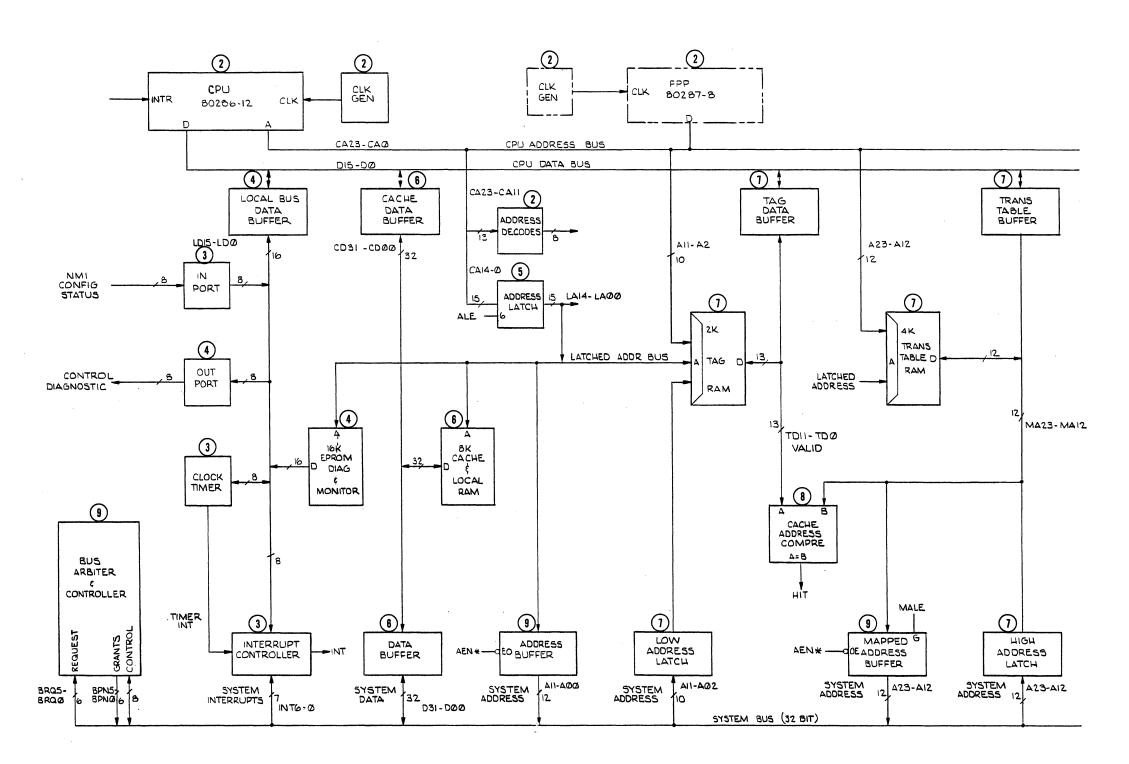

| BLOCK DIAGRAM DESCRIPTION. | • | • | • | • | • | • | • | • | • | • | 3-5 |

| System Bus                 |   |   |   |   |   |   |   |   |   |   |     |

| Central Processing Unit    |   |   |   |   |   |   |   |   |   |   |     |

| System Memory              |   |   |   |   |   |   |   |   |   |   |     |

| Communications             | • | • | • | • | • | • | • | • | • | • | 3-7 |

| File Processor             | • | • | • | • | ٠ | • | • | • | • | • | 3-8 |

| Controller                 |   |   |   |   |   |   |   |   |   |   |     |

| DETAILED CIRCUIT OPERATION | • | • | • | • | • | • | • | • | • | • | 3-9 |

## NOTE

For convenience, each of the following PCB subsystem descriptions have a red locator tab on the right edge of the first page.

| System Bus Interface                     | 3-11   |

|------------------------------------------|--------|

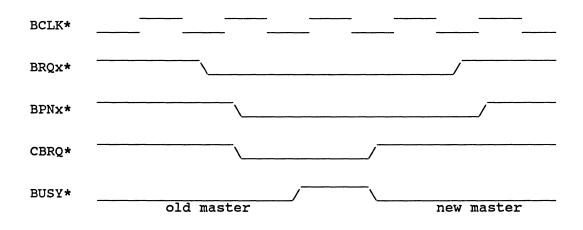

| Bus Masters                              | 3-12   |

| Bus Slaves                               |        |

| Bus Signals                              |        |

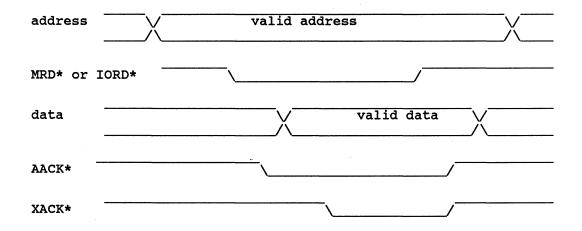

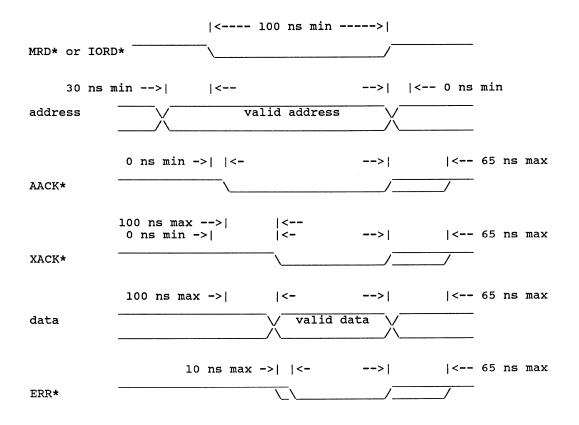

| Data Transfer Operations                 |        |

| Interrupt Operation                      |        |

| Bus Exchange                             |        |

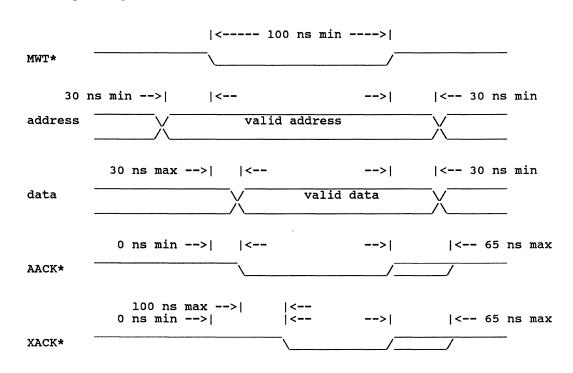

| Lock Operation                           |        |

|                                          |        |

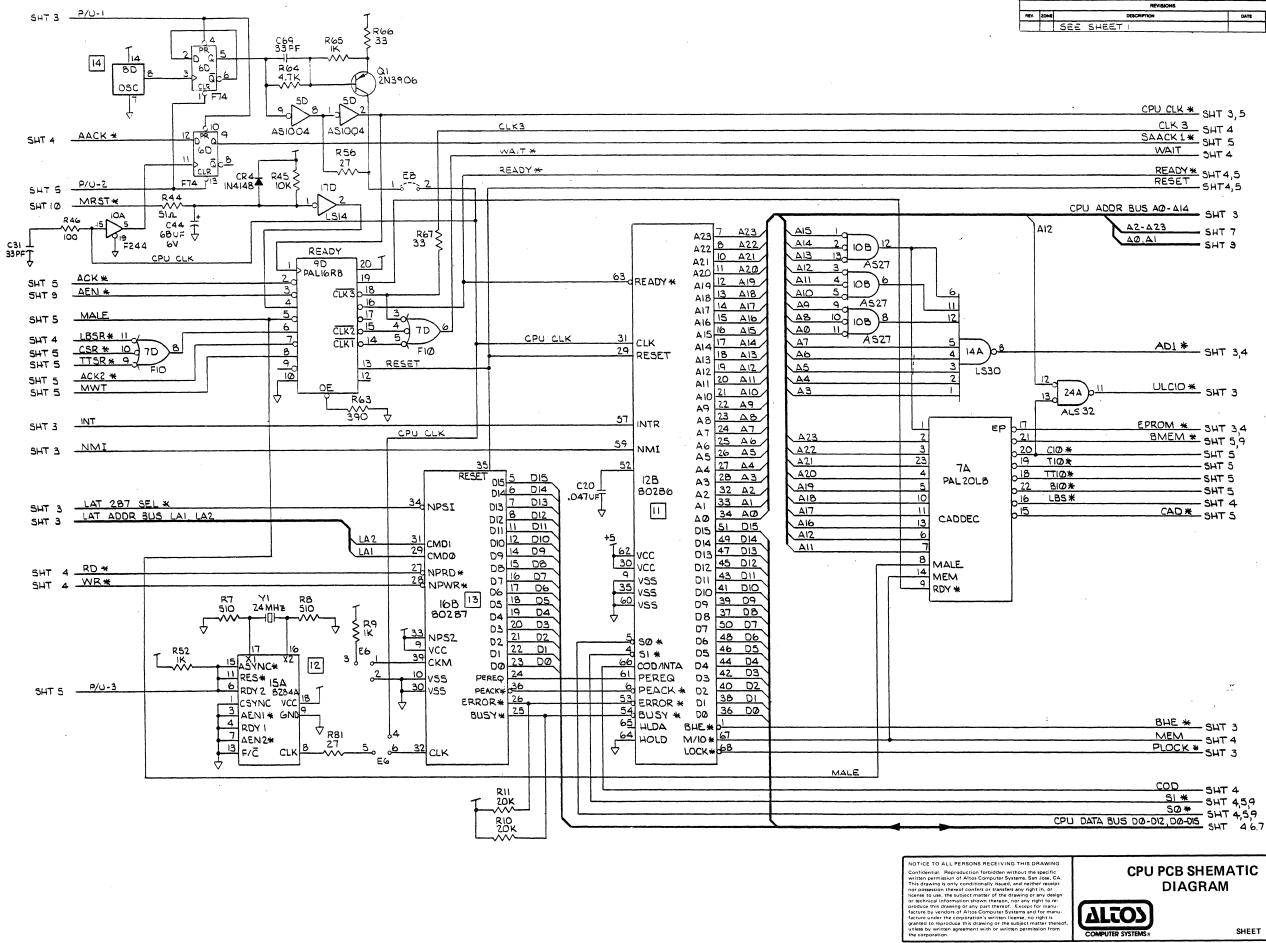

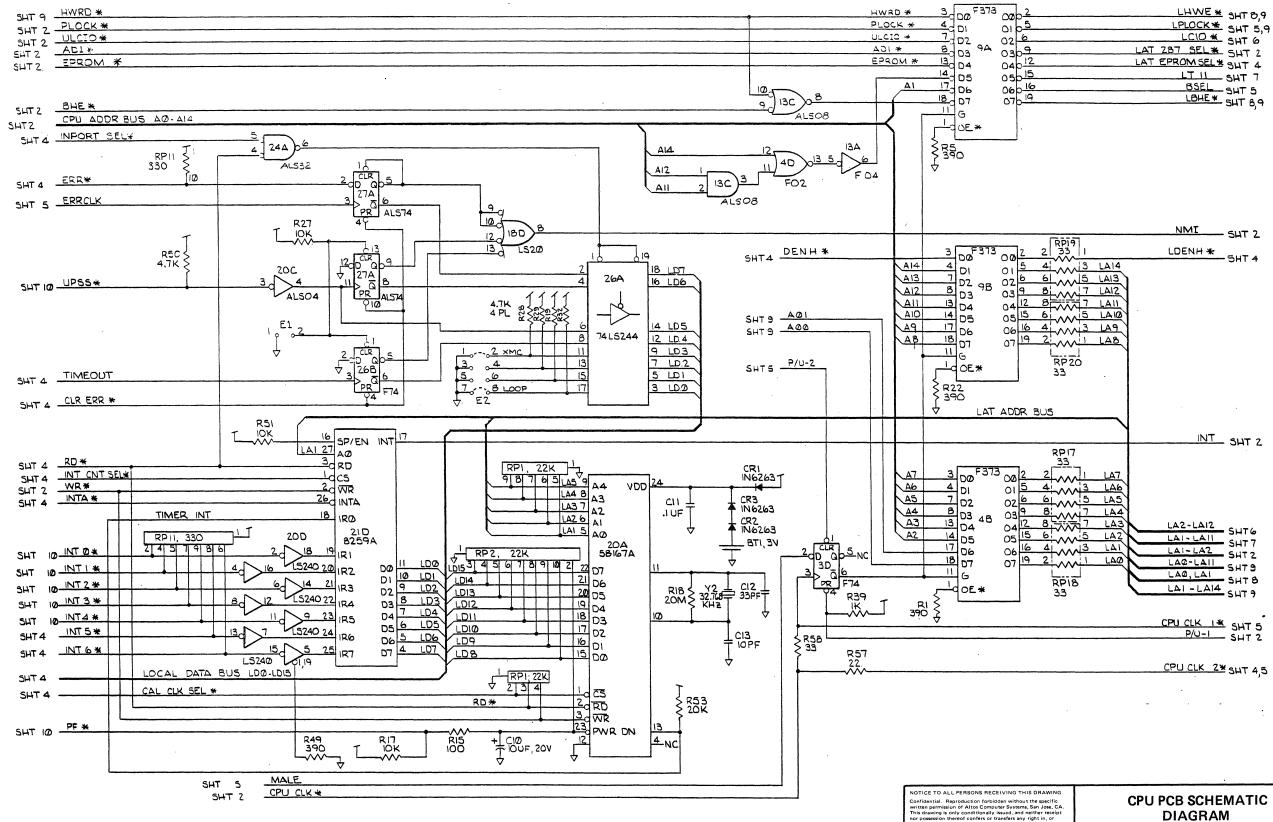

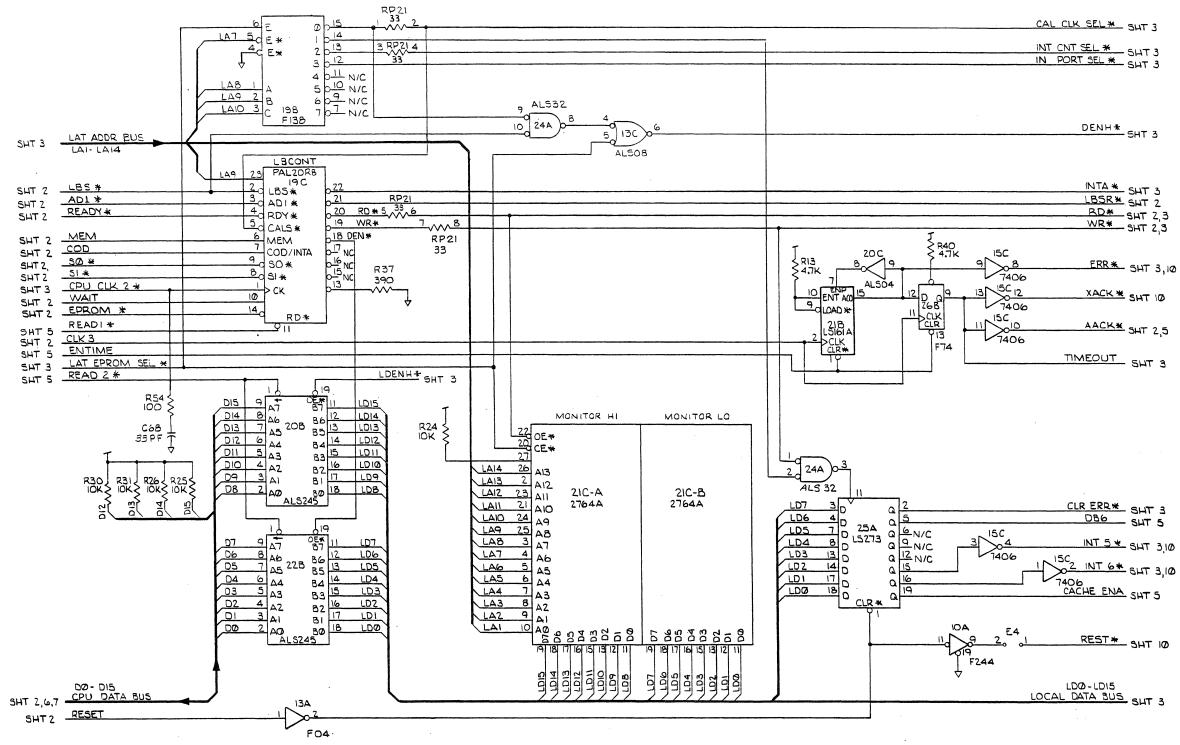

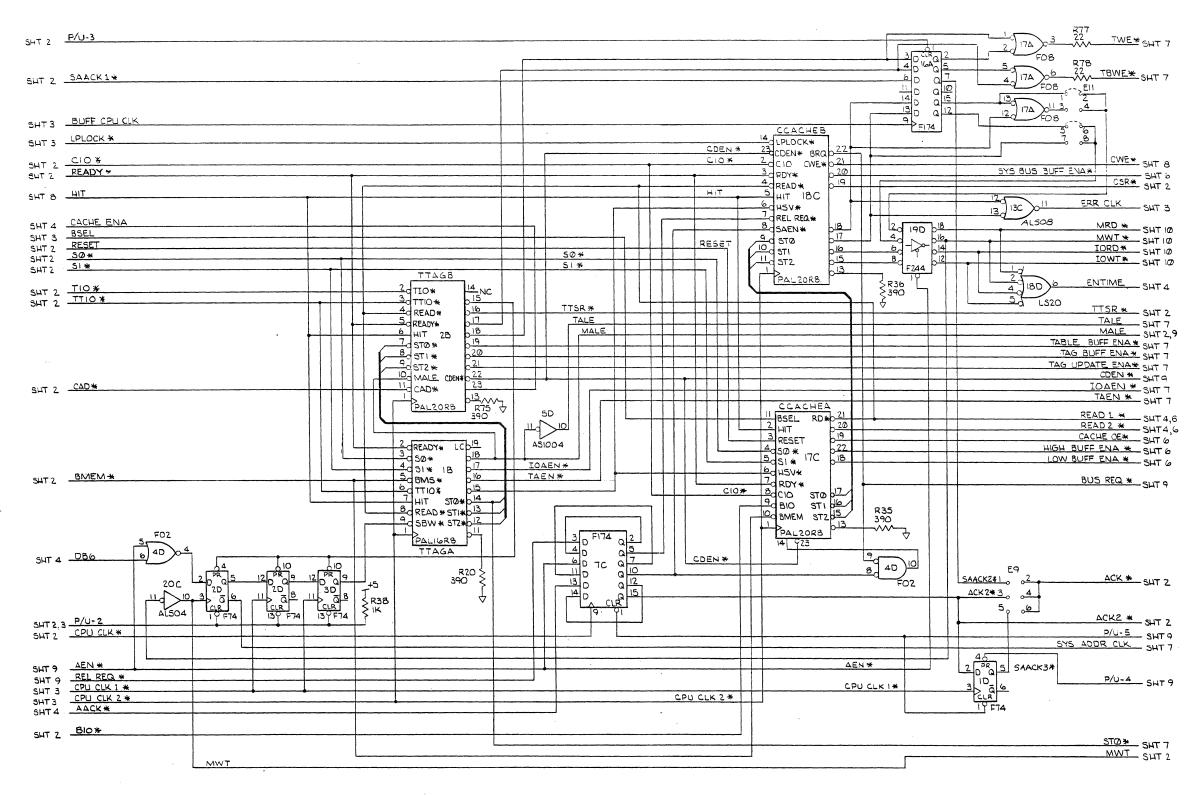

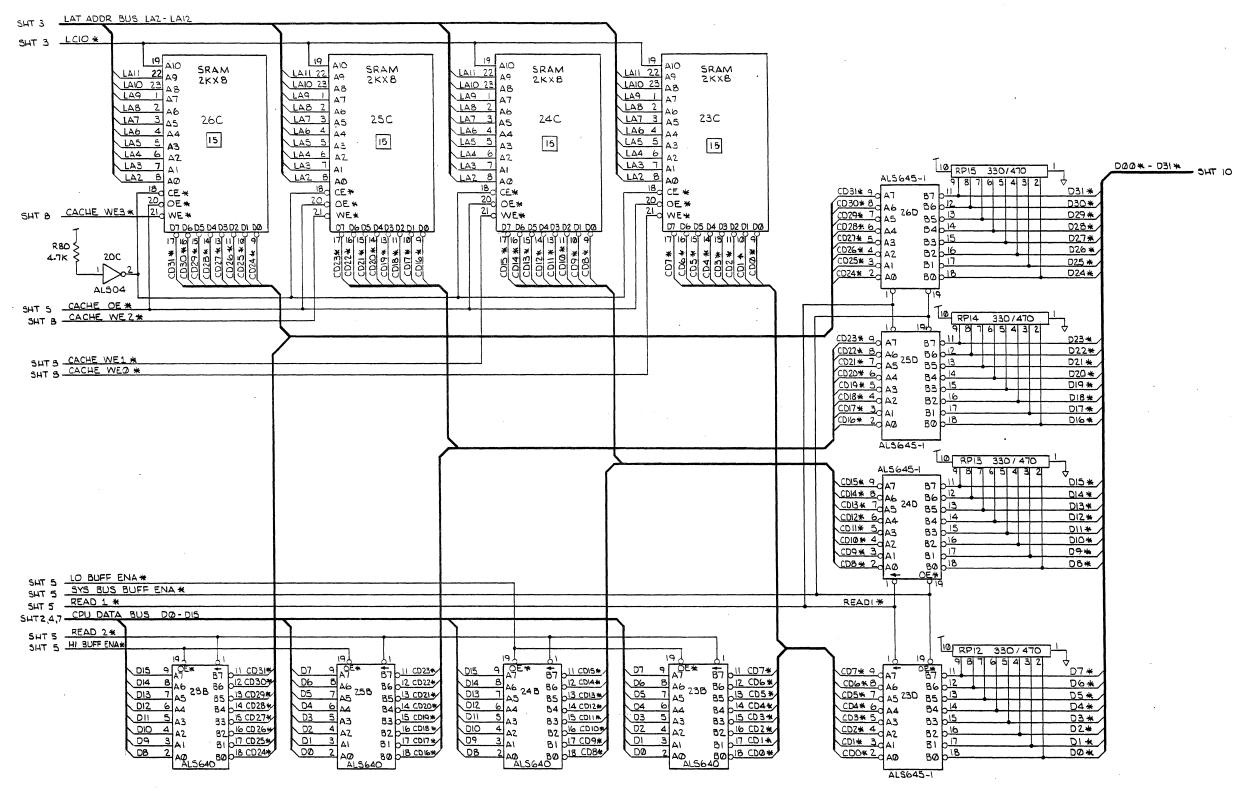

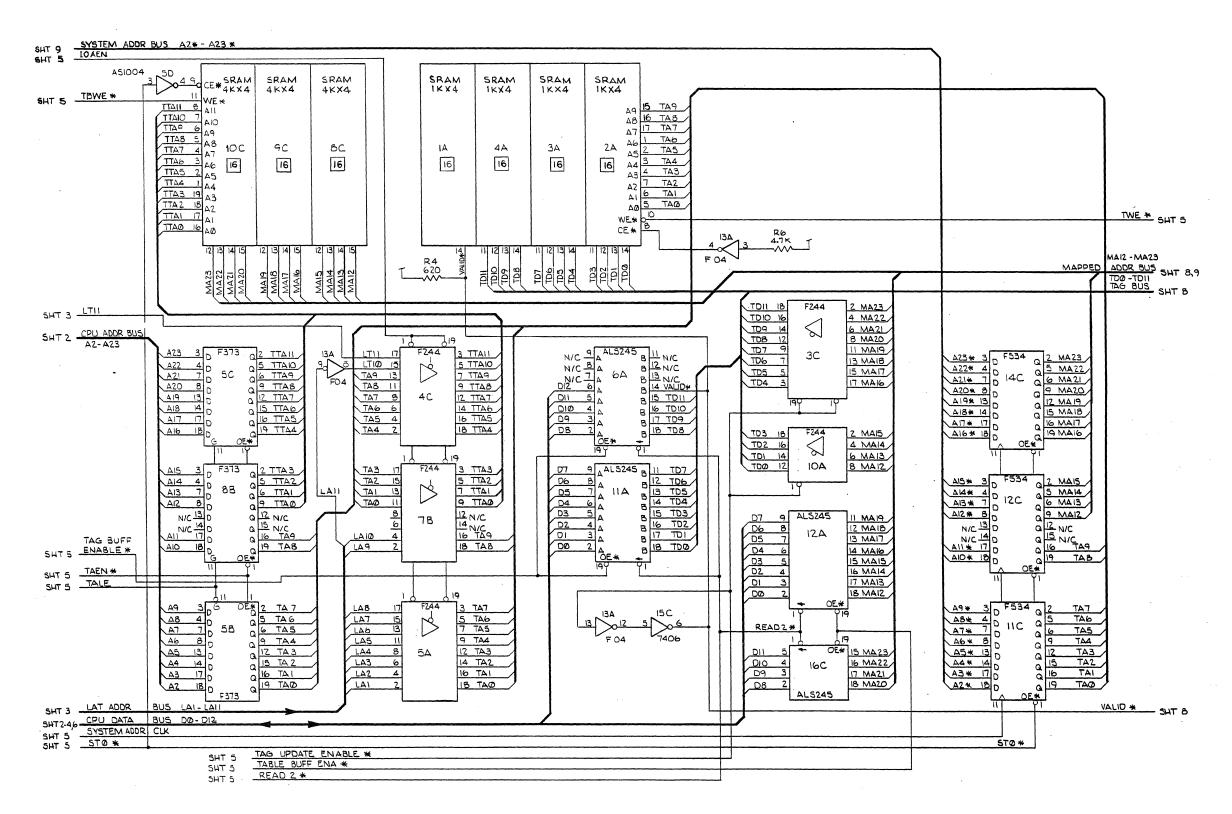

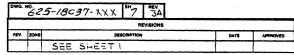

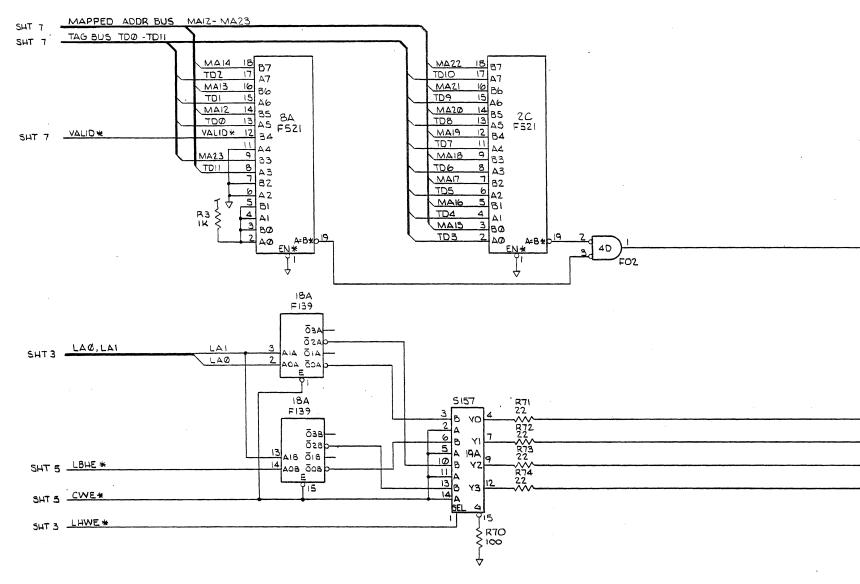

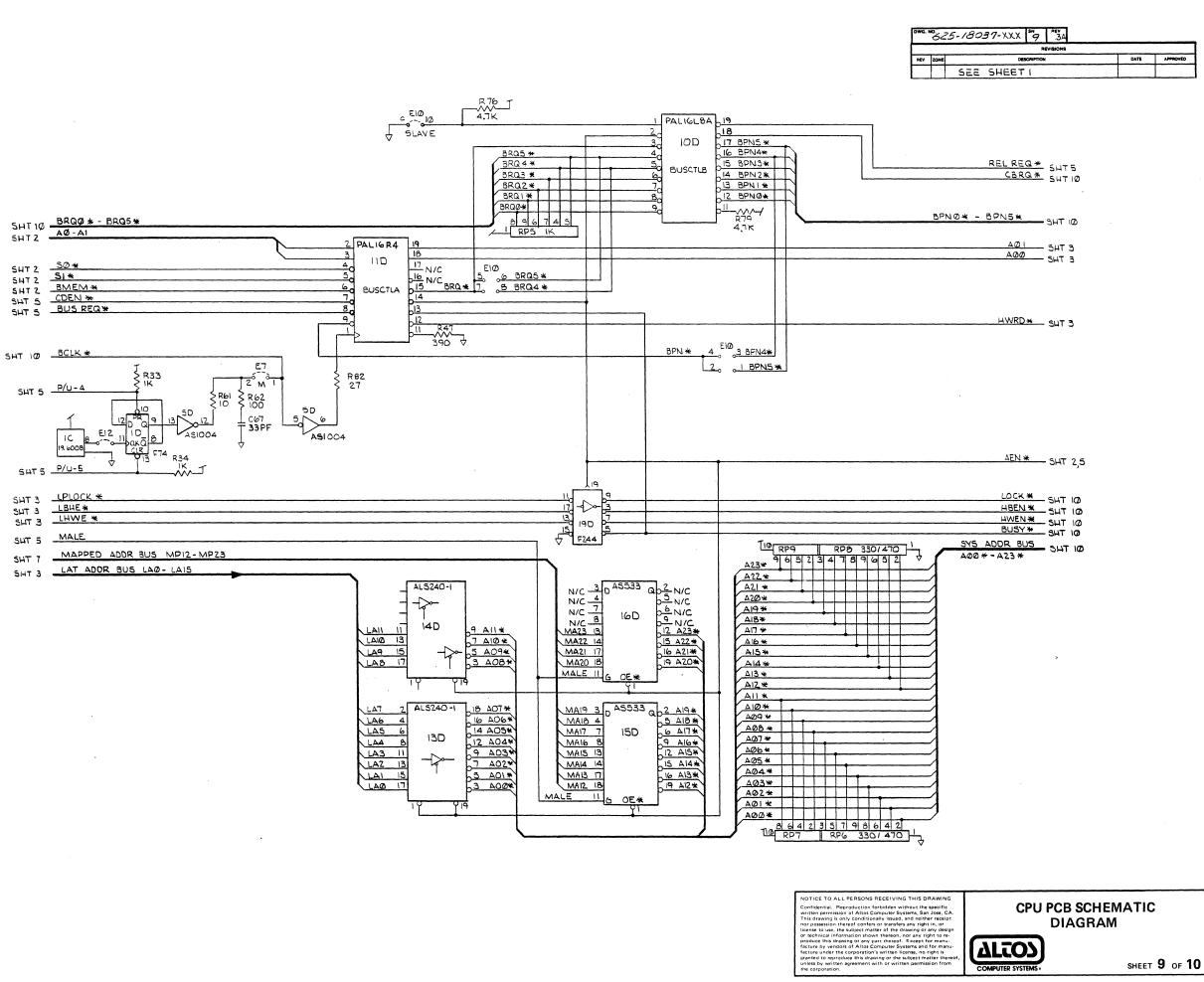

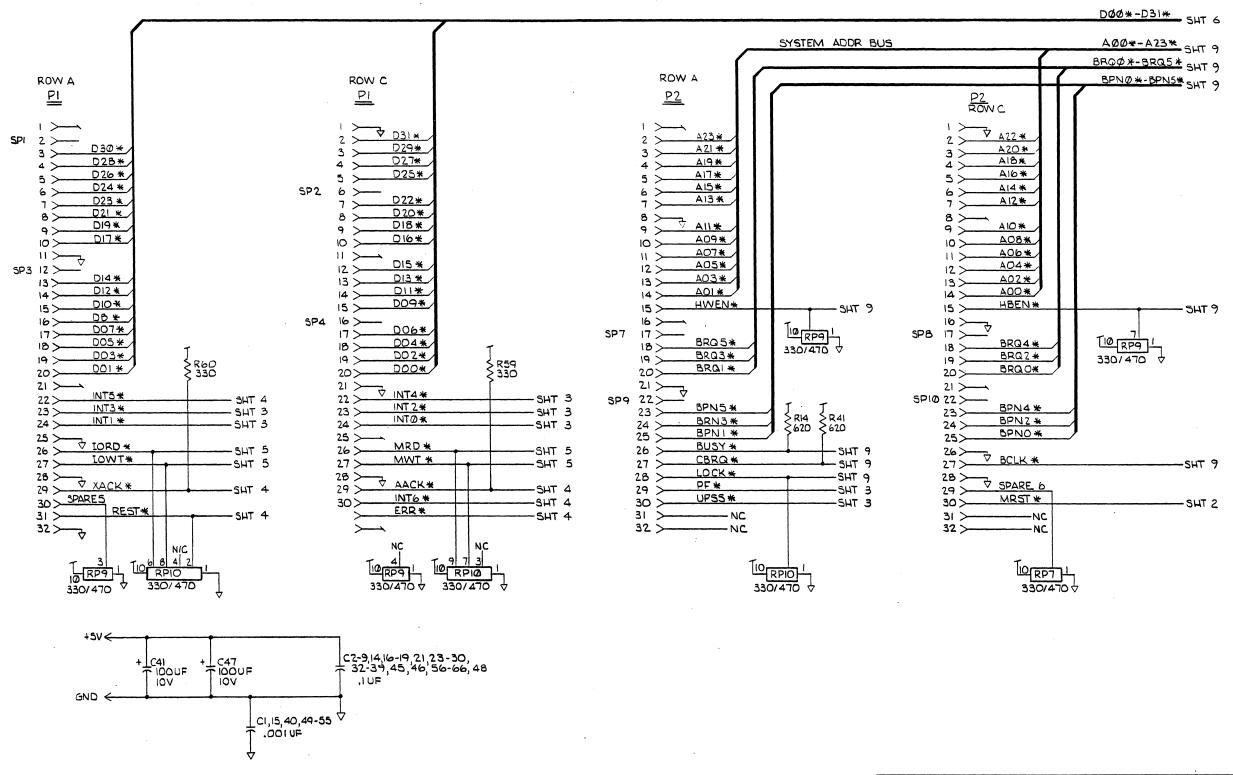

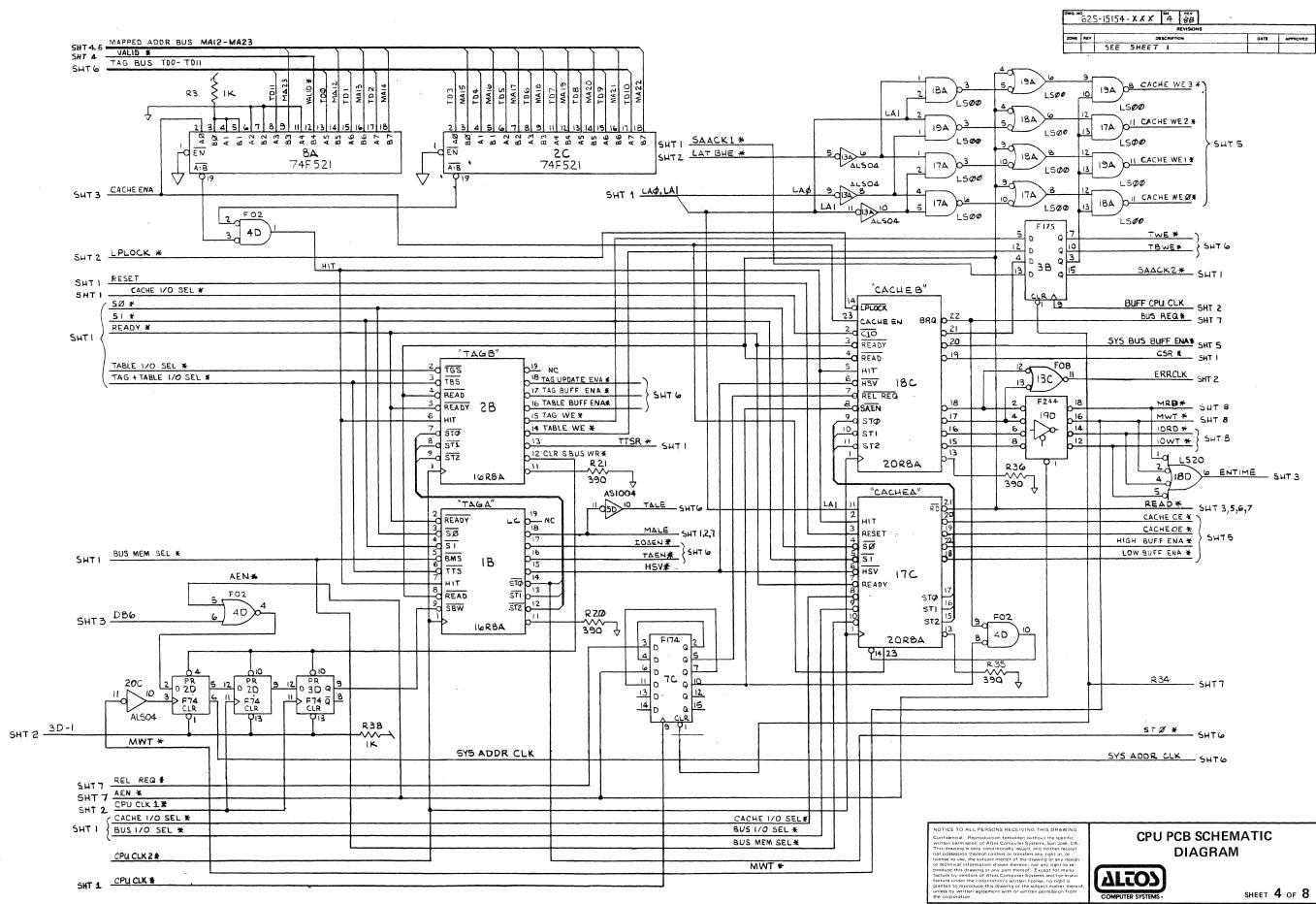

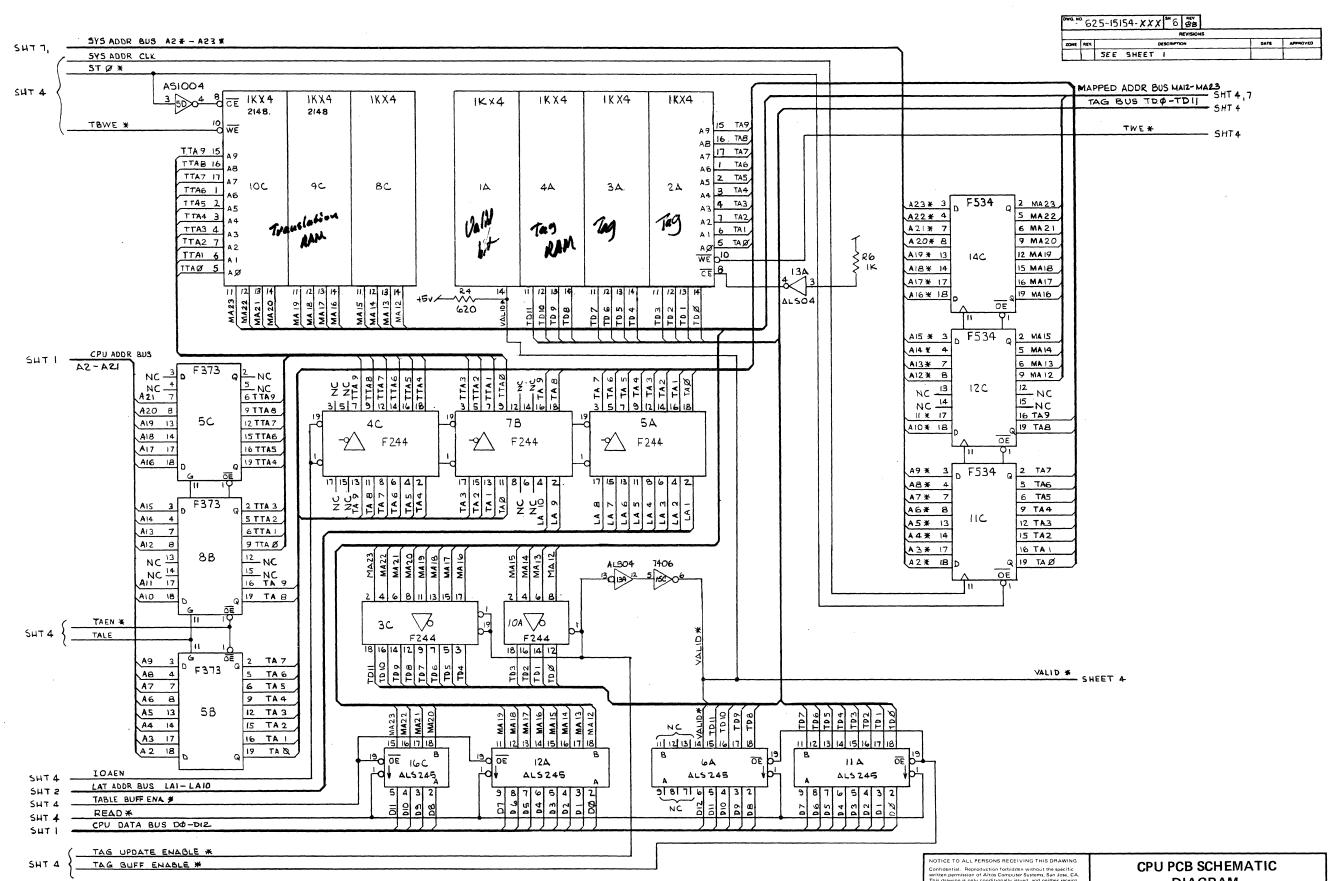

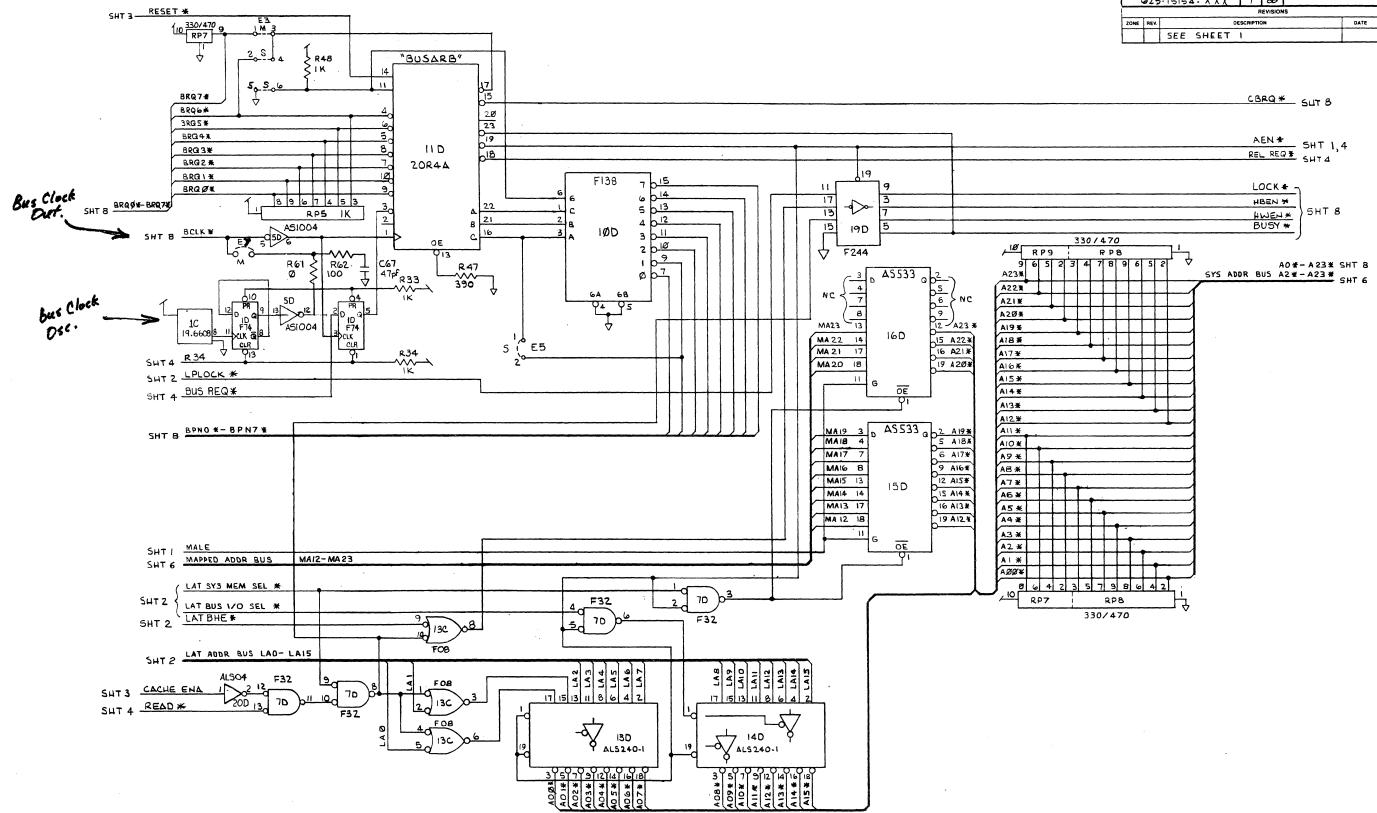

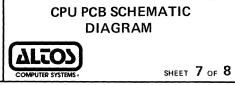

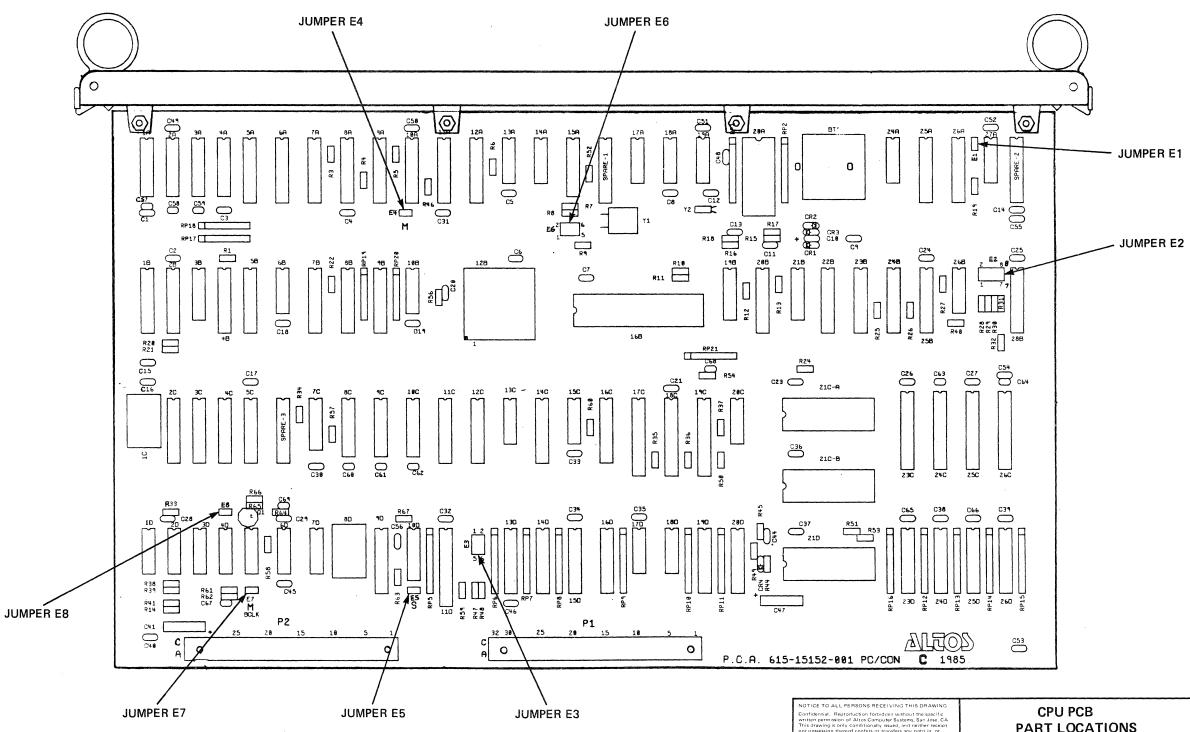

| Central Processing Unit (CPU) PCB        | 3 - 27 |

| CPU Initialization                       |        |

|                                          | 3-28   |

| Microprocessor Address Decoder Logic     |        |

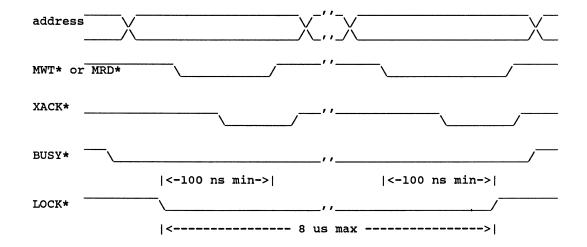

| 80286 Memory Map                         |        |

| Local Bus Control Logic.                 |        |

| Local Bus.                               |        |

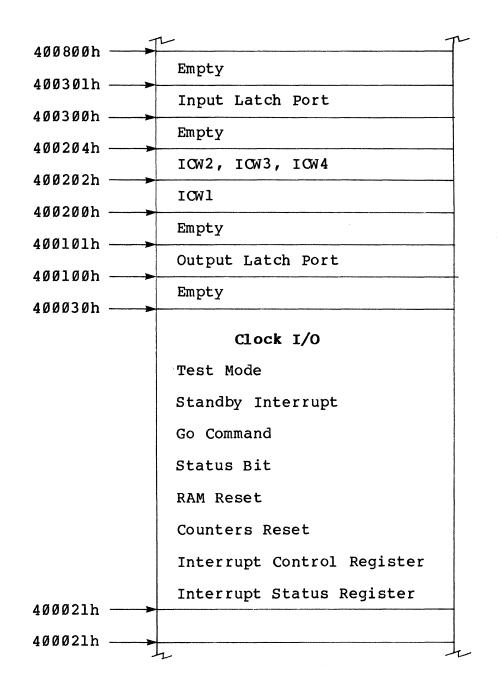

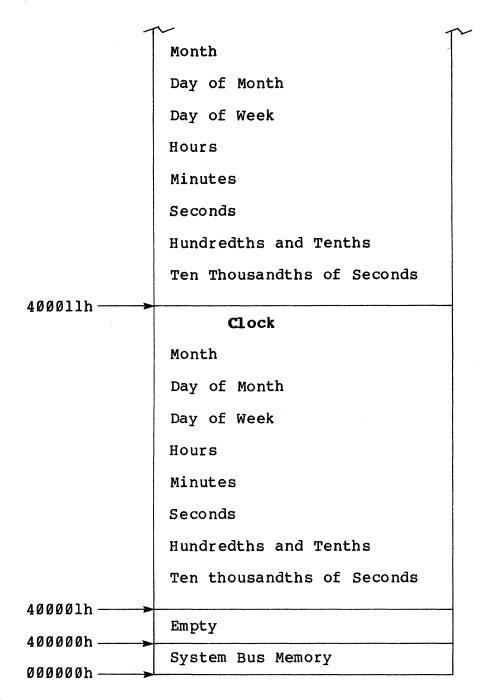

| Calendar Clock                           |        |

|                                          |        |

| Interrupt Controller                     | 3-33   |

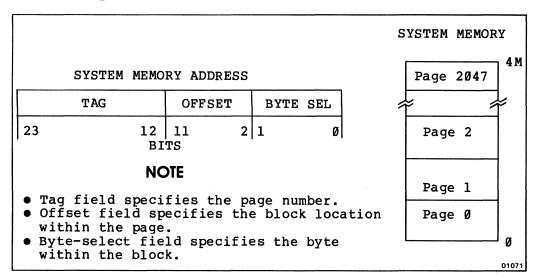

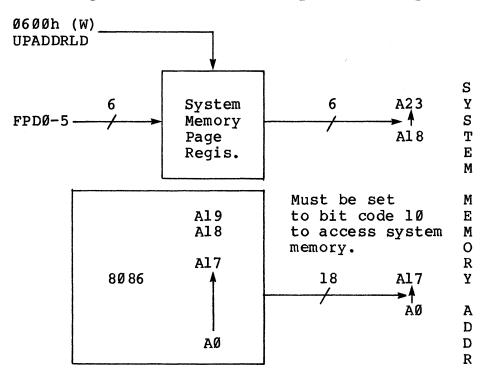

| System Memory Accessing and Address      | 3-35   |

|                                          |        |

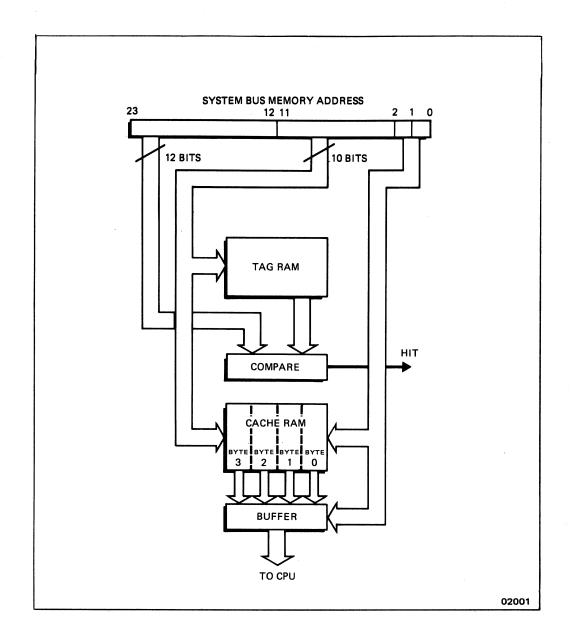

| Tag and Translation RAM Control Logic    |        |

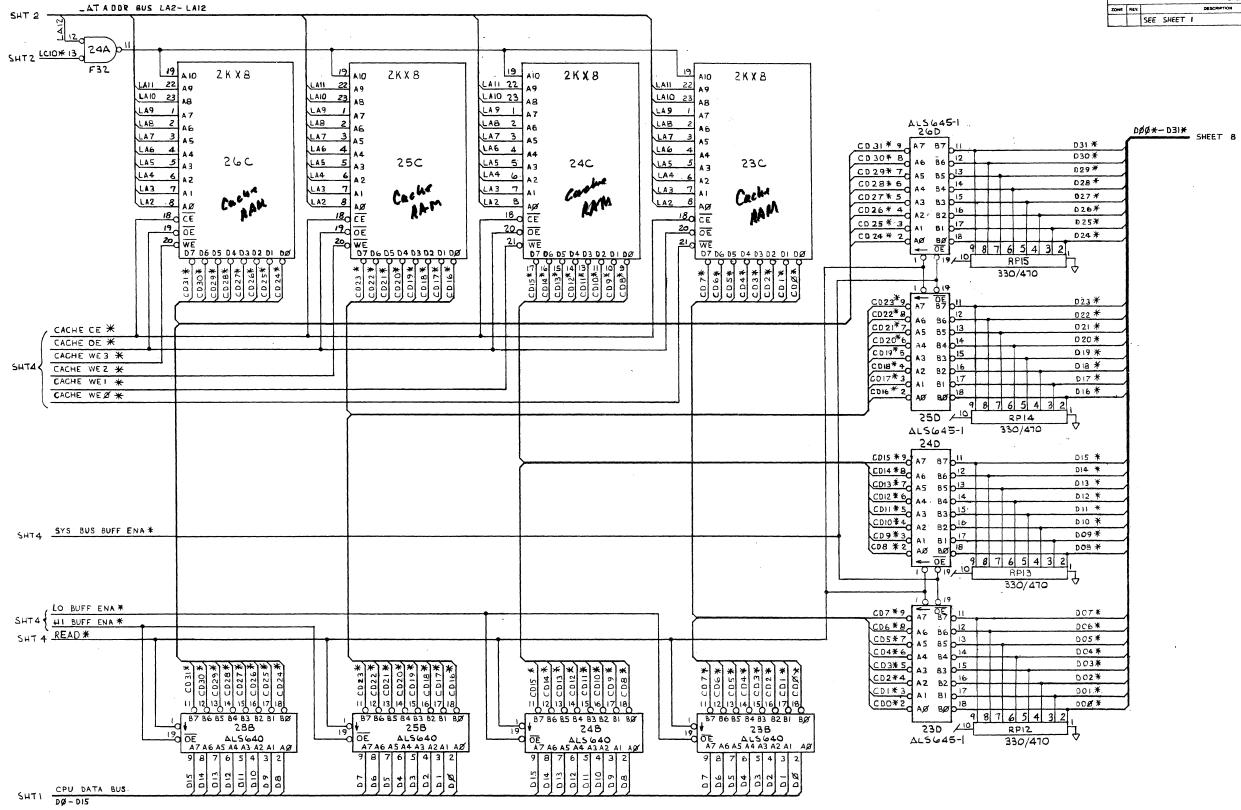

| Cache Memory Organization                |        |

| System Bus Arbiter and Priority Encoding |        |

| Logic                                    | 3-41   |

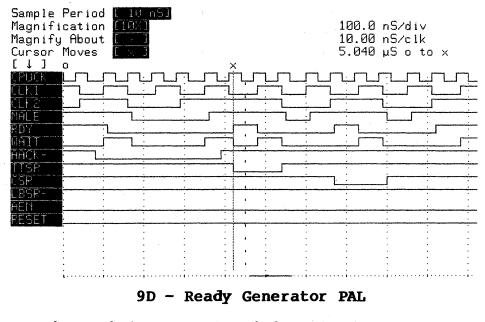

| Microprocessor Ready Generator           |        |

| Jumper Descriptions                      |        |

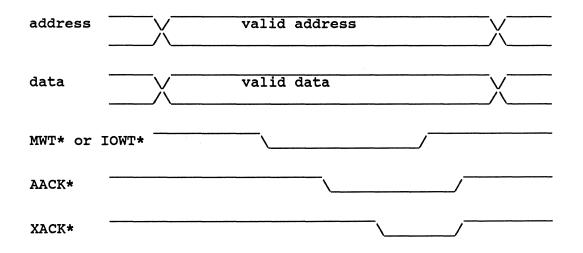

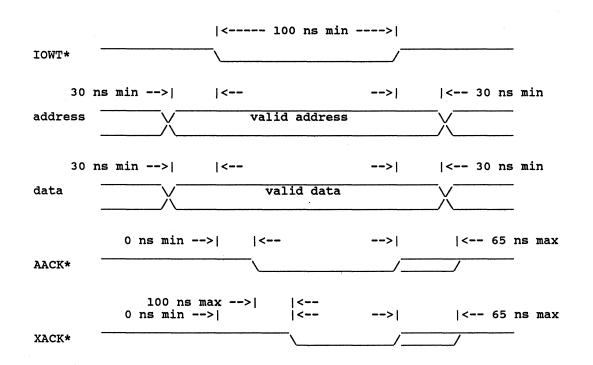

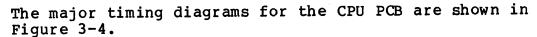

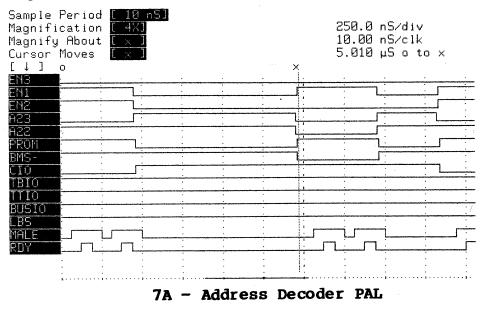

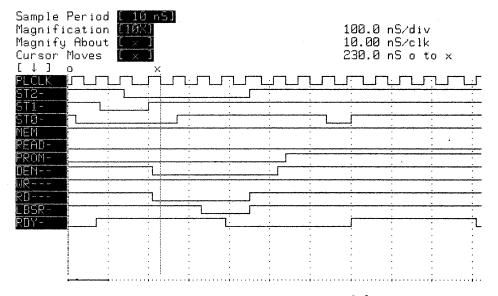

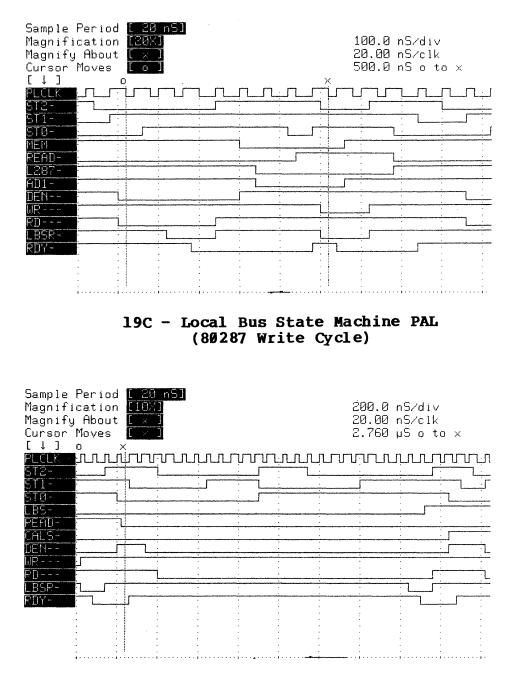

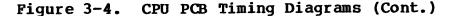

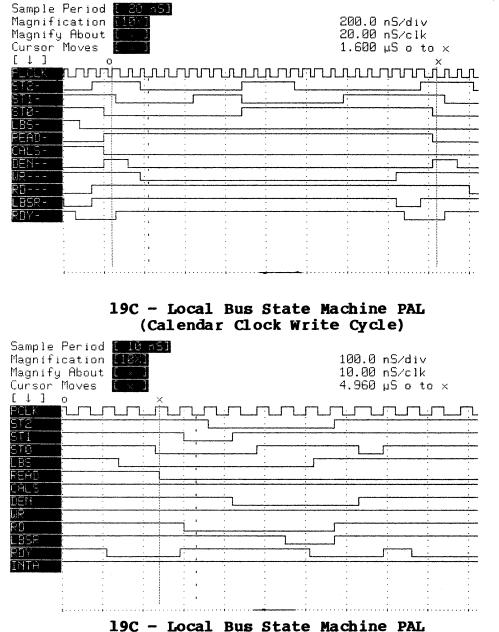

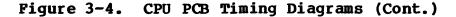

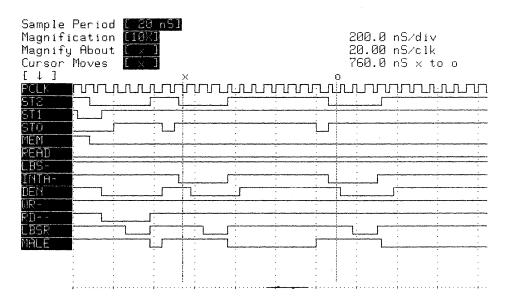

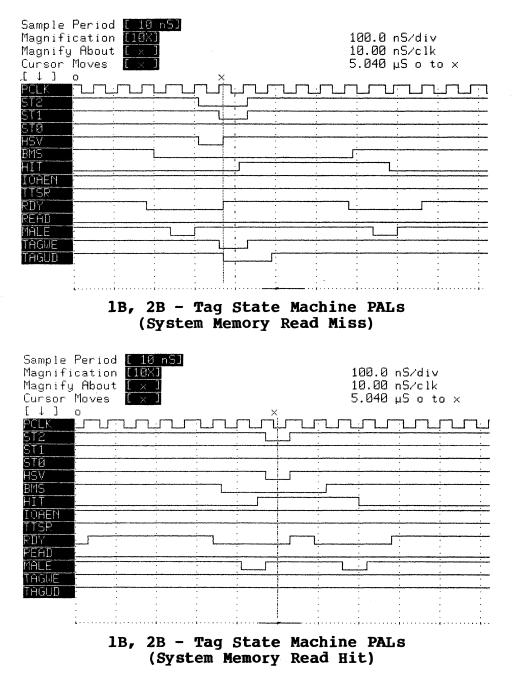

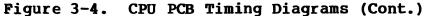

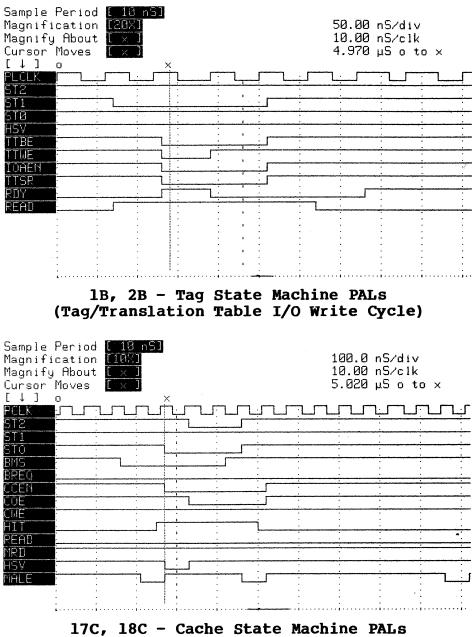

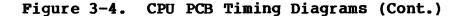

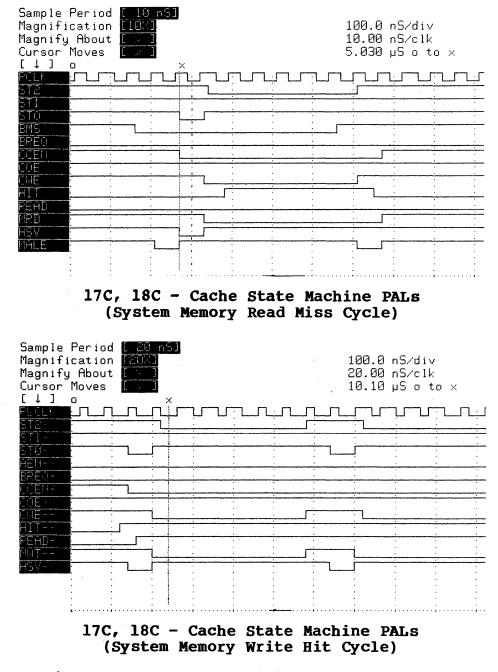

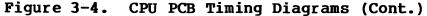

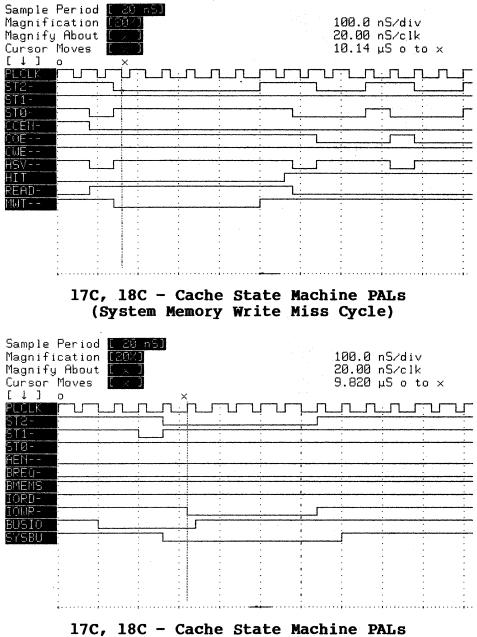

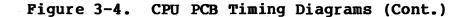

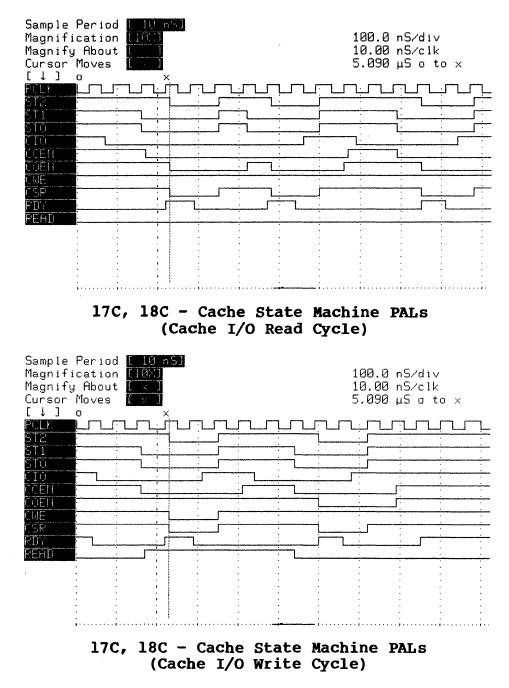

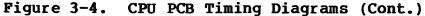

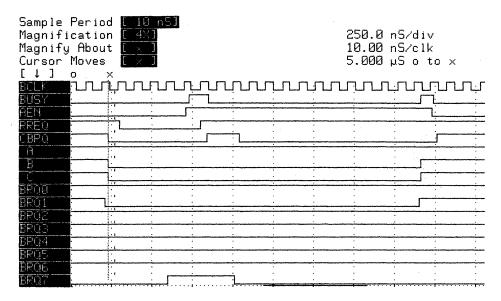

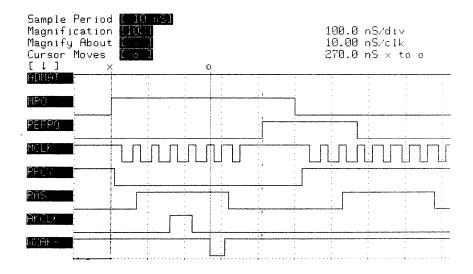

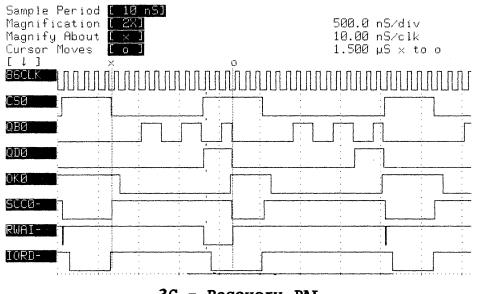

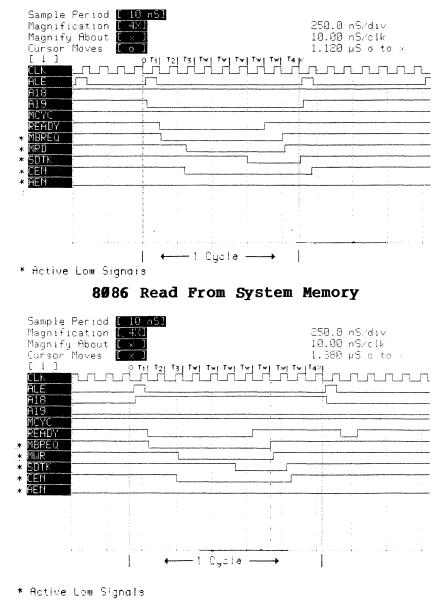

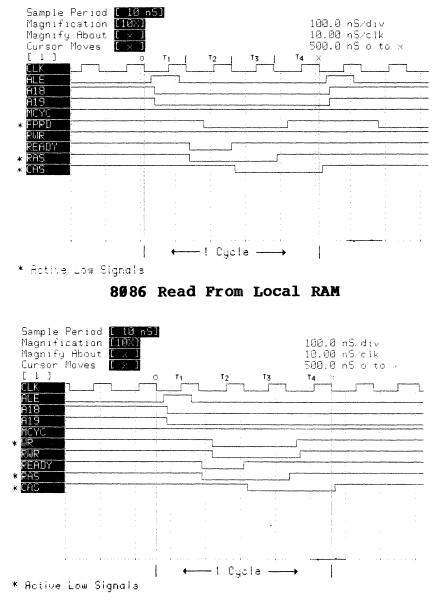

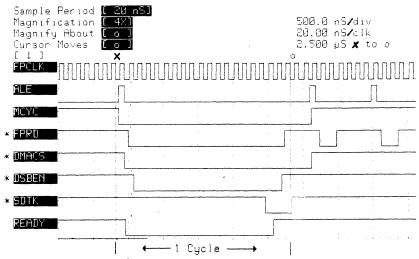

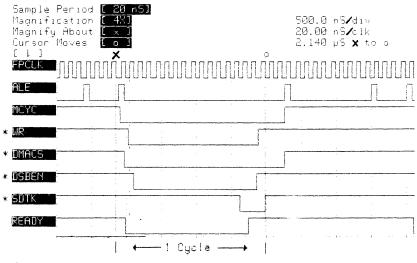

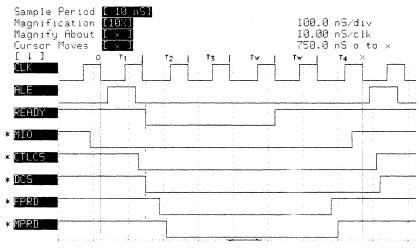

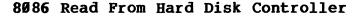

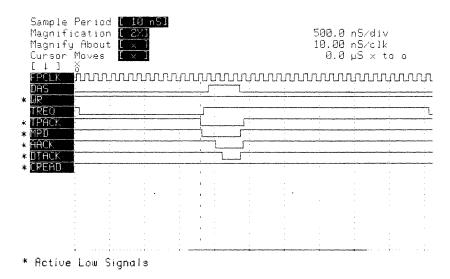

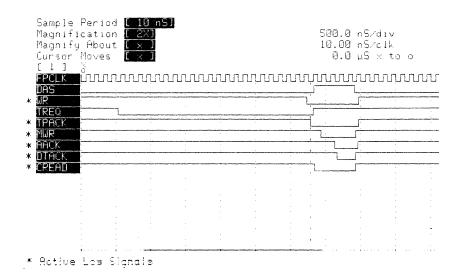

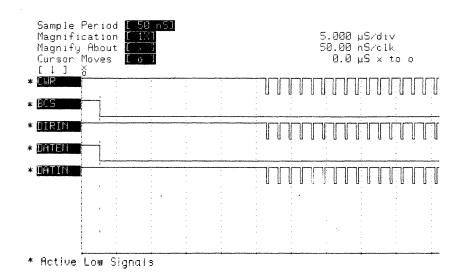

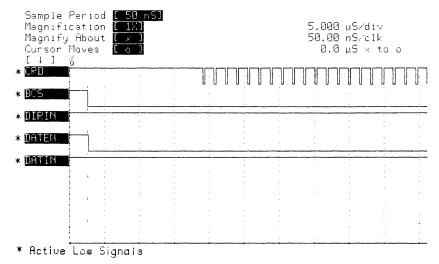

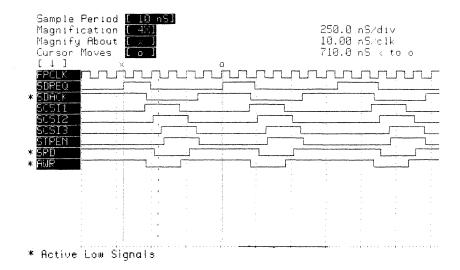

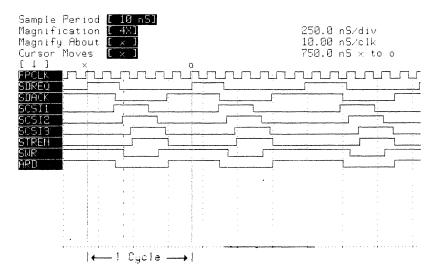

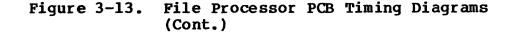

| Timing Diagrams                          | 3-44   |

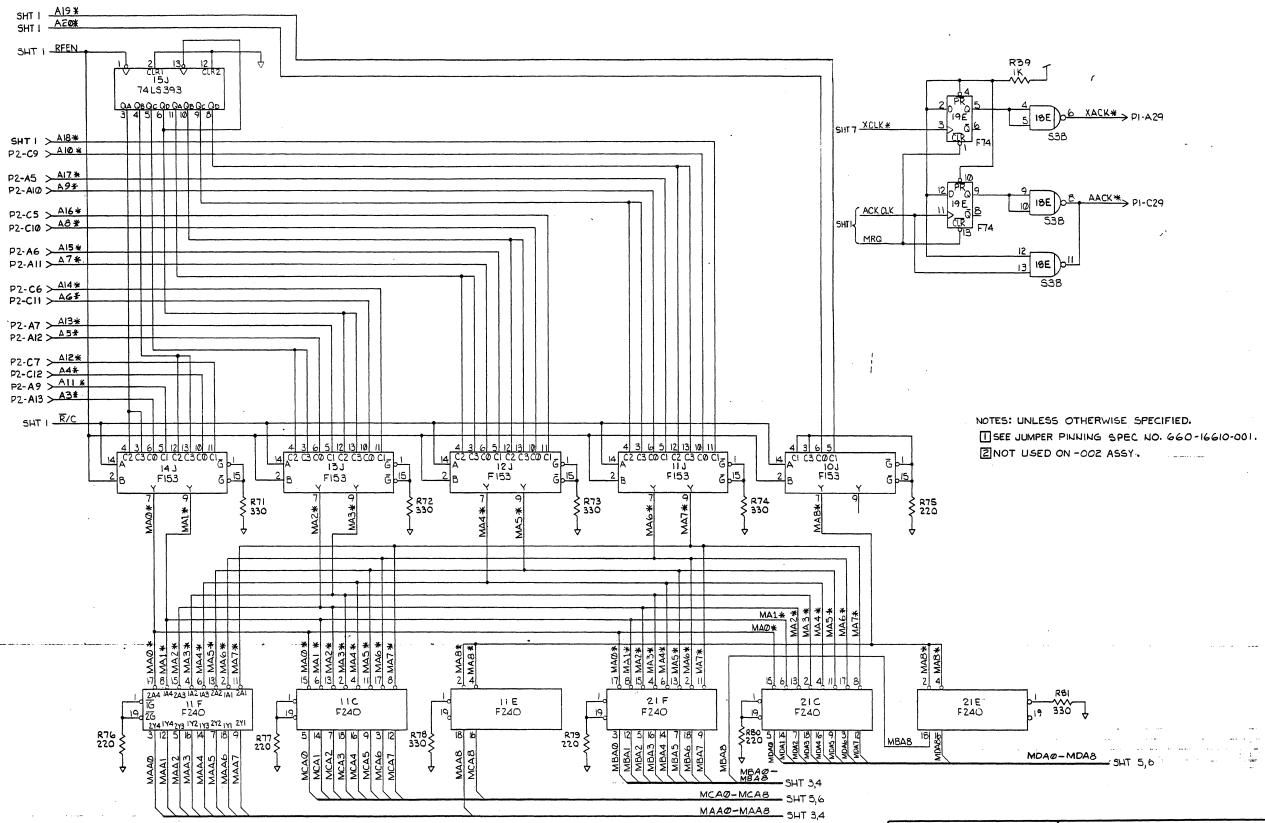

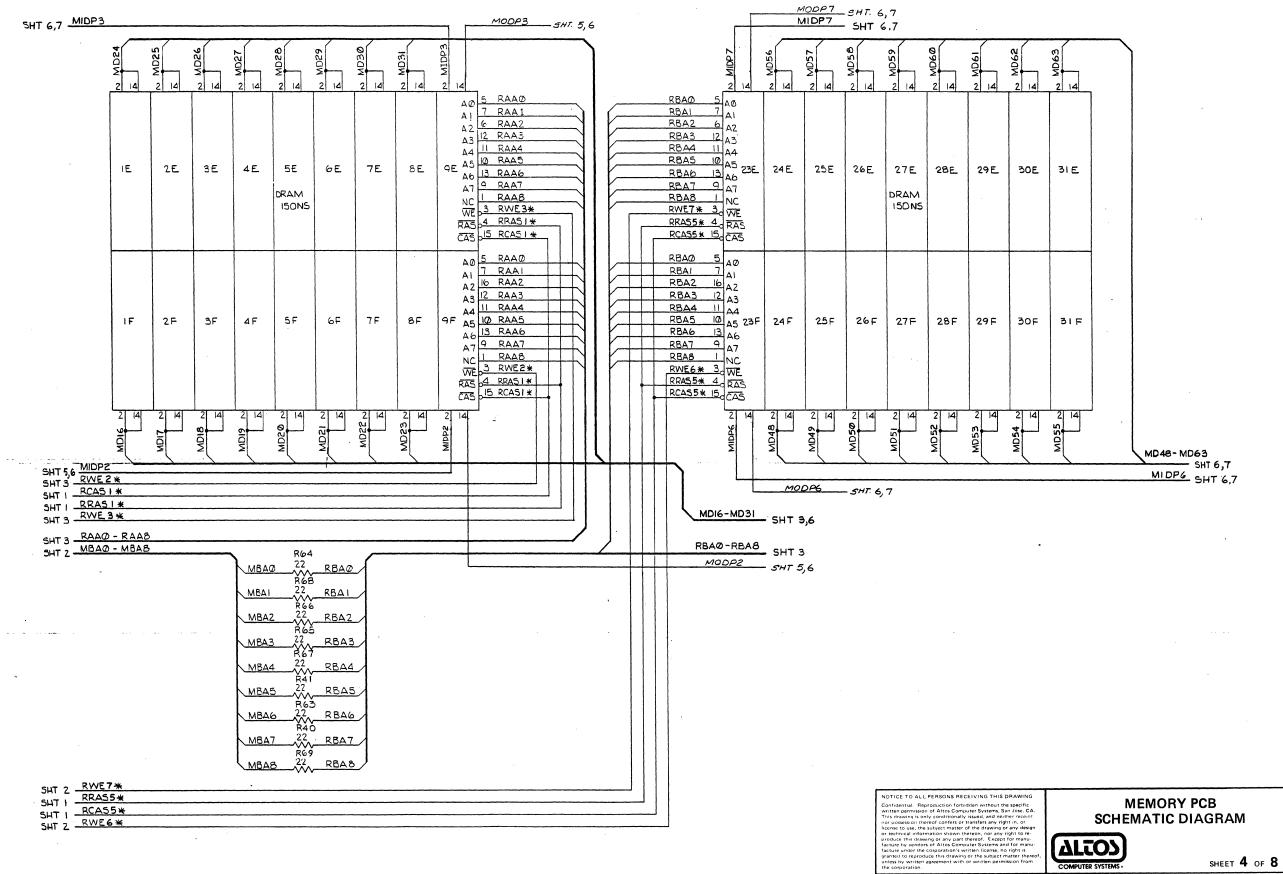

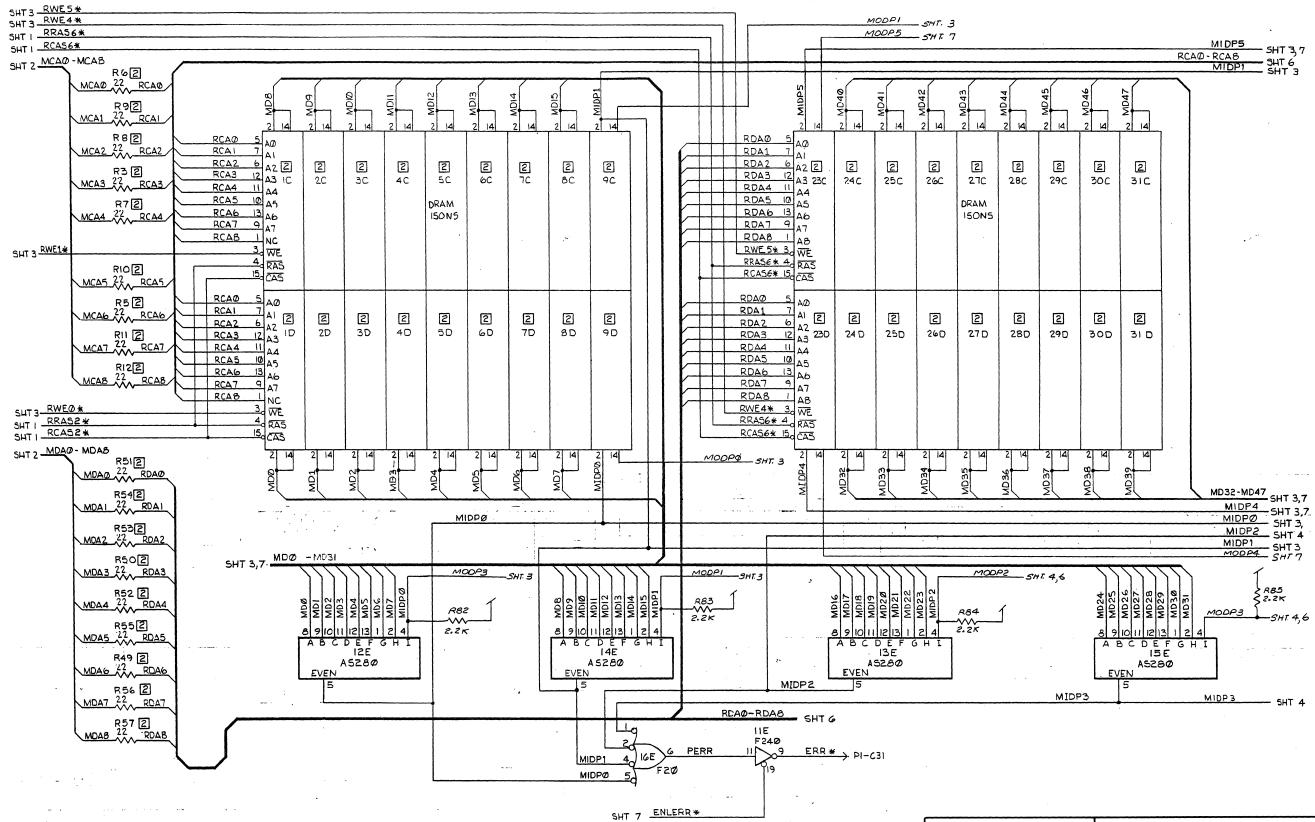

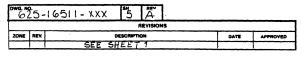

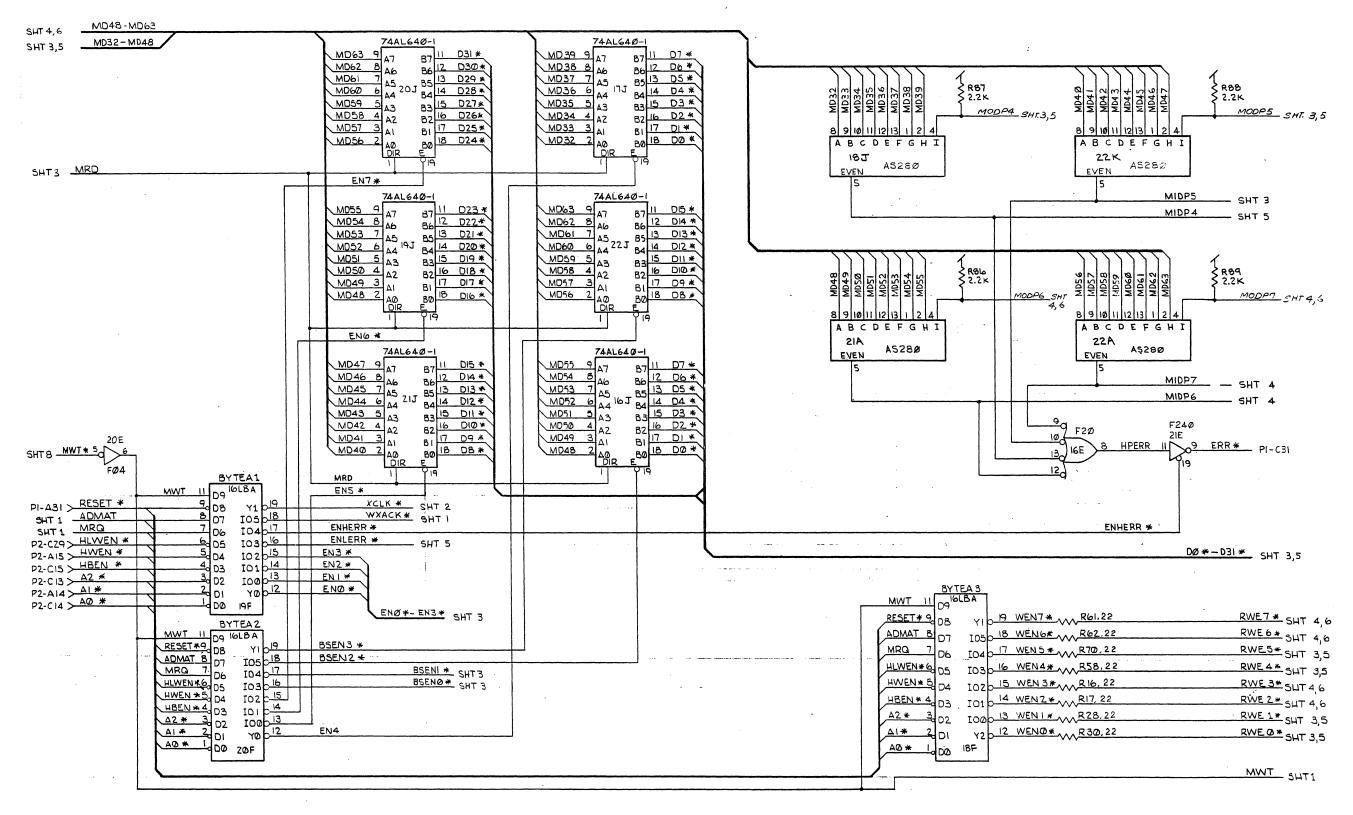

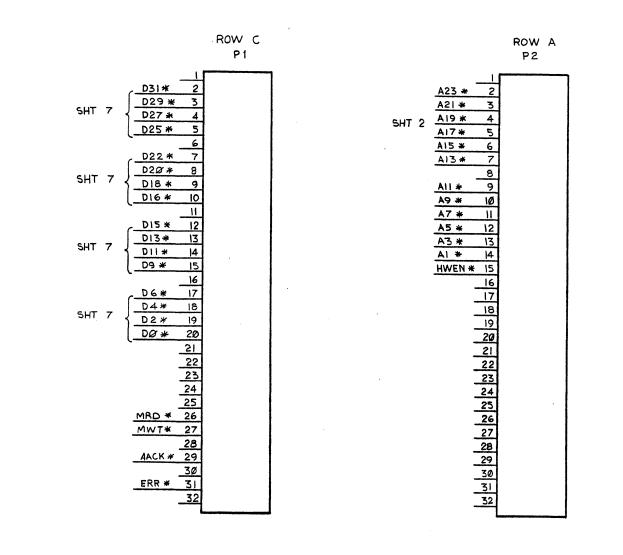

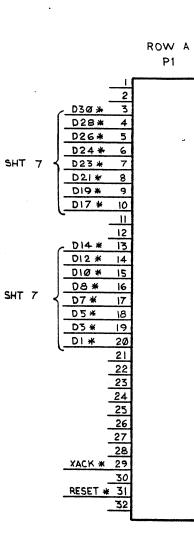

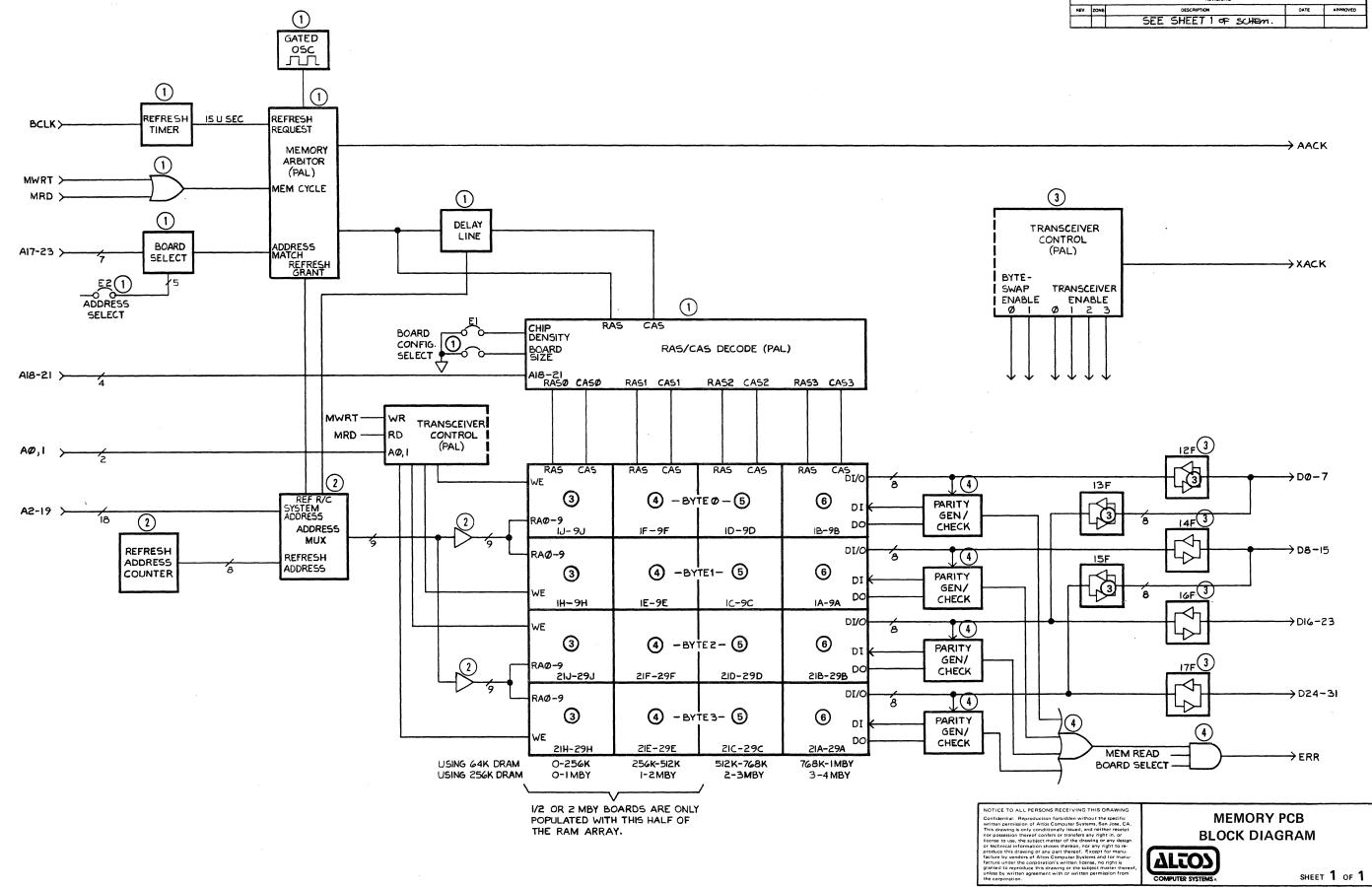

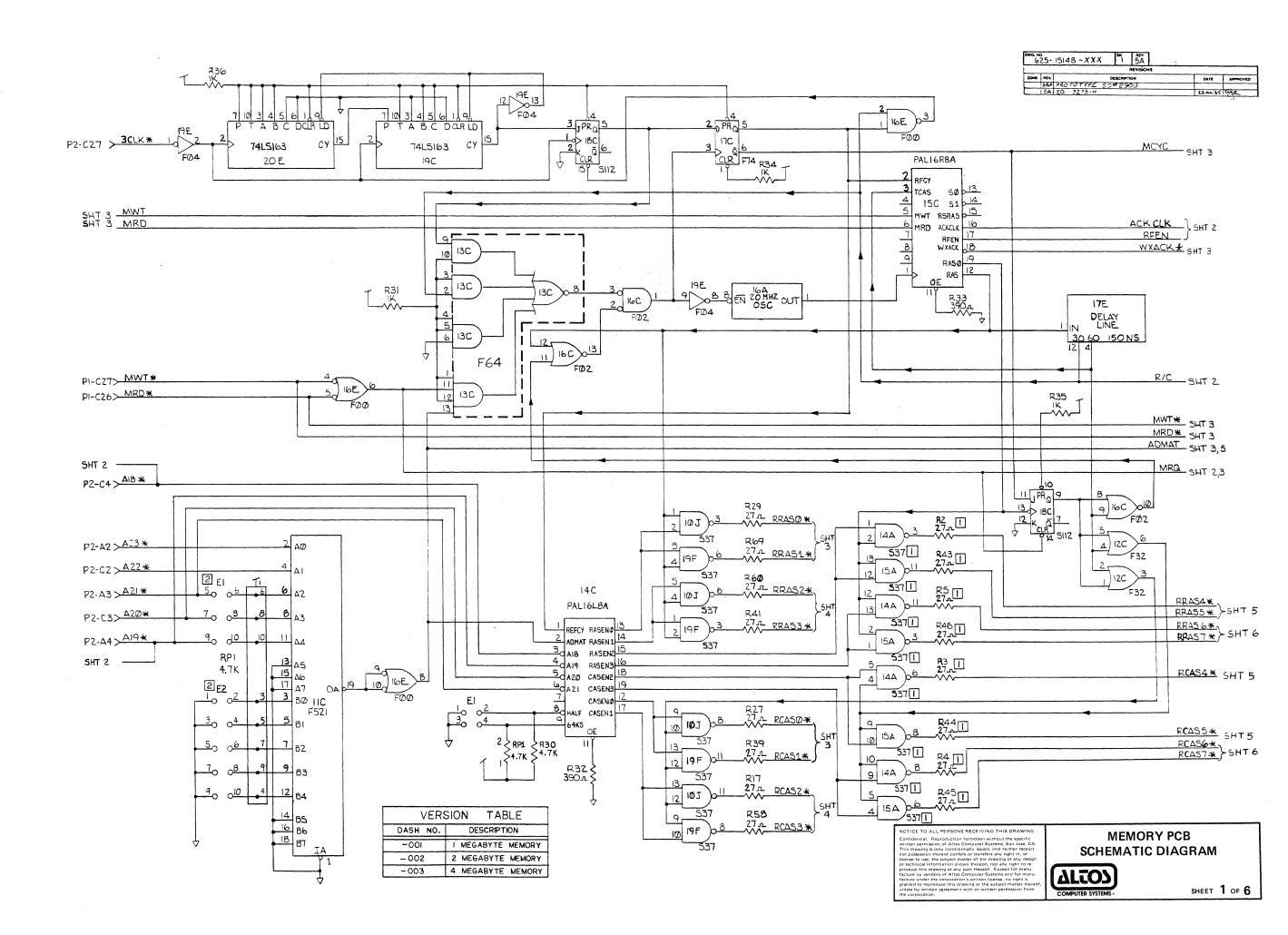

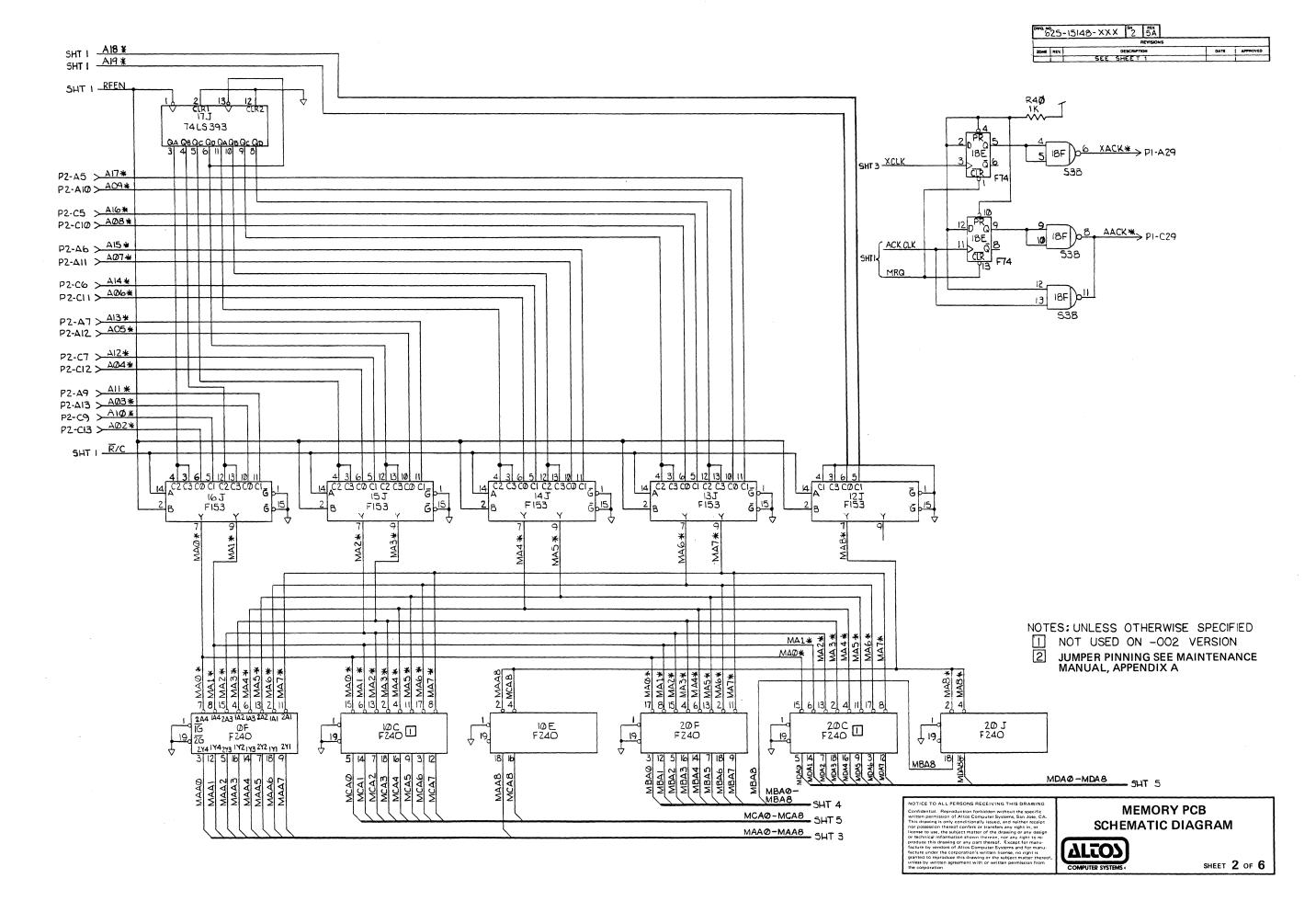

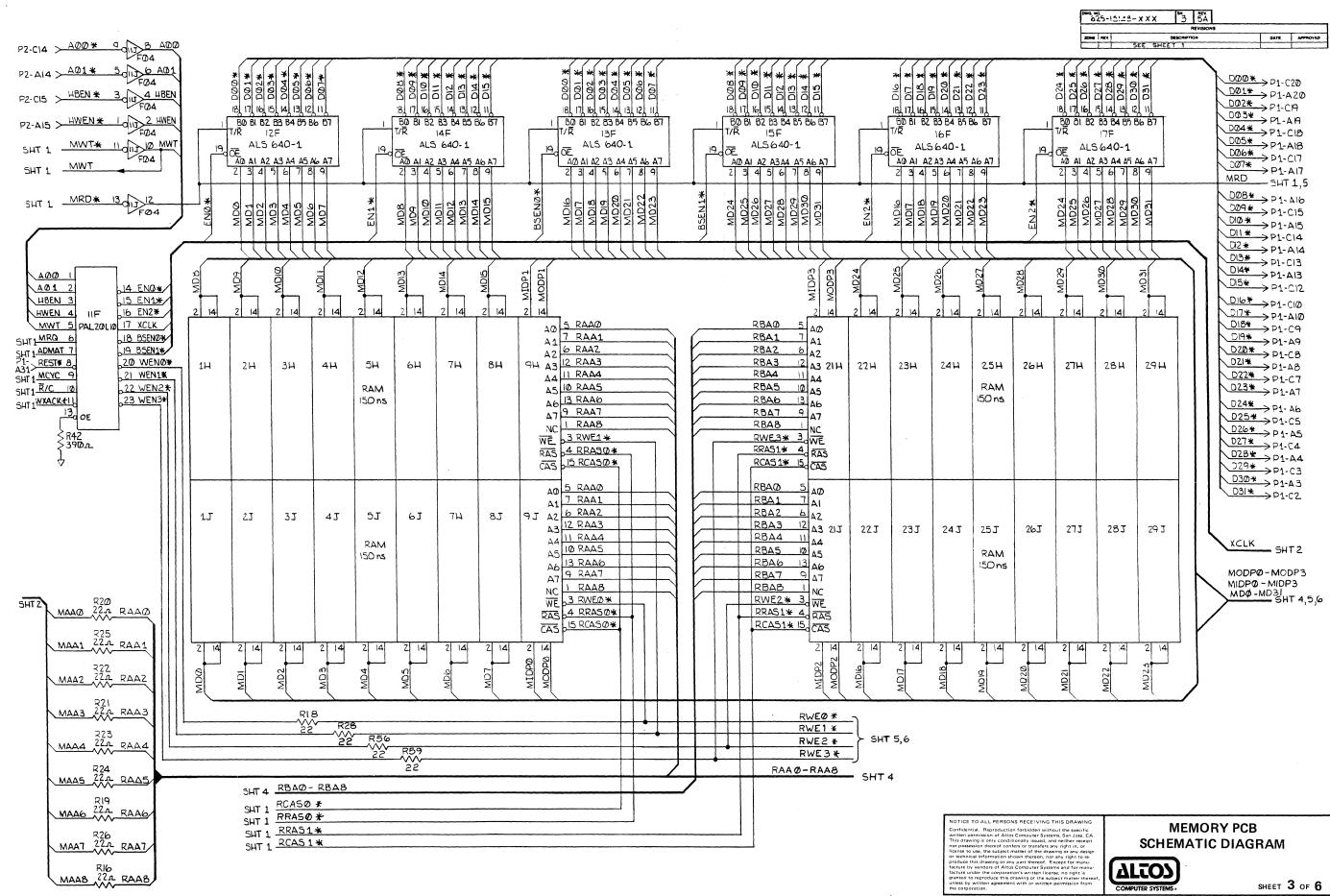

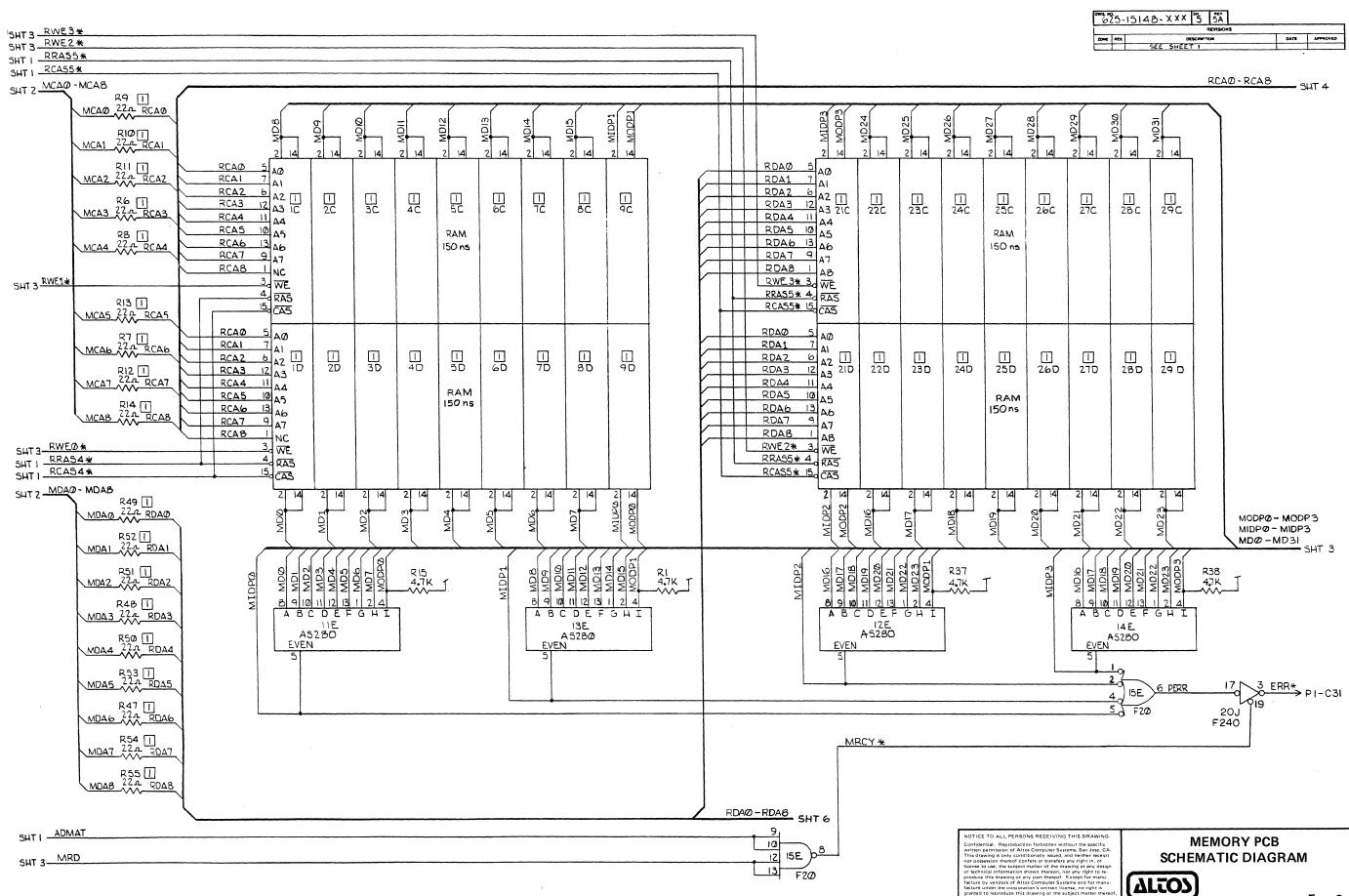

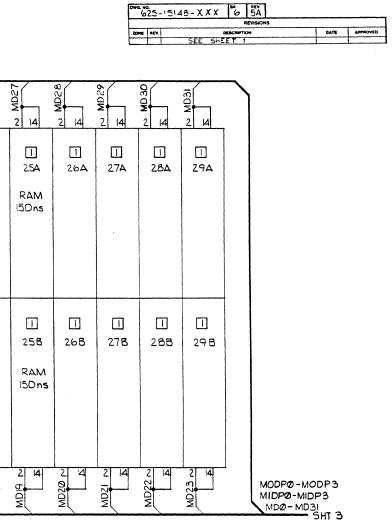

| Memory PCB                       |    | • | • |   | 3-55           |

|----------------------------------|----|---|---|---|----------------|

| System Bus Interface             | •  | • | • |   | 3-55           |

| Row/Column Address Decoder       |    |   |   |   | 3-57           |

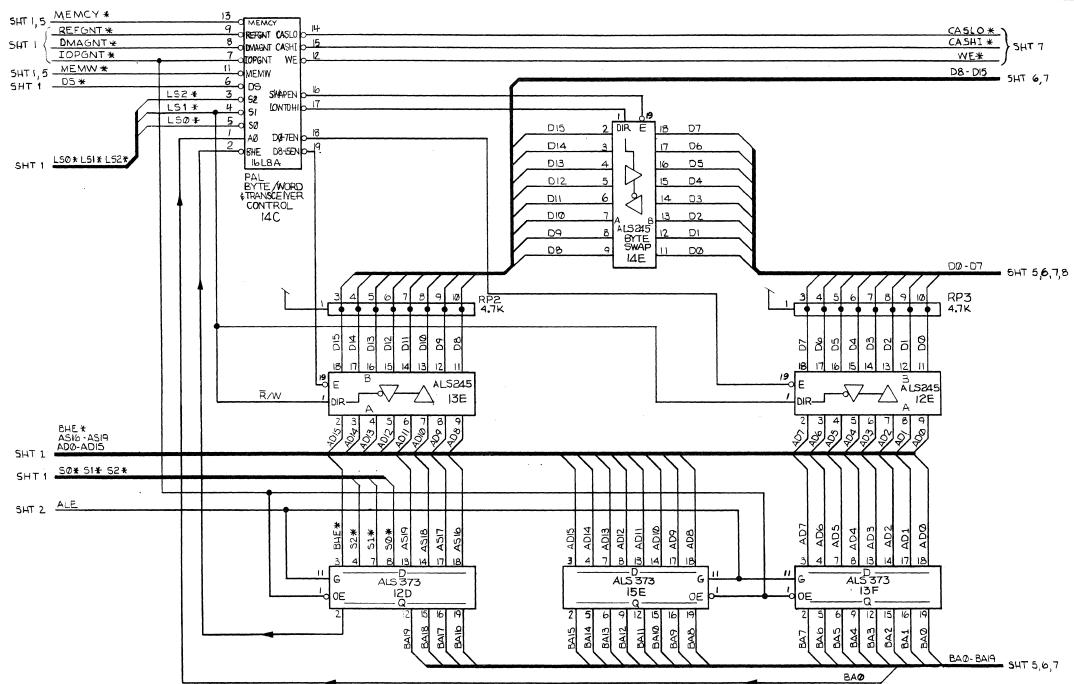

| Memory Transceiver Control       |    | • |   | • | 3-57           |

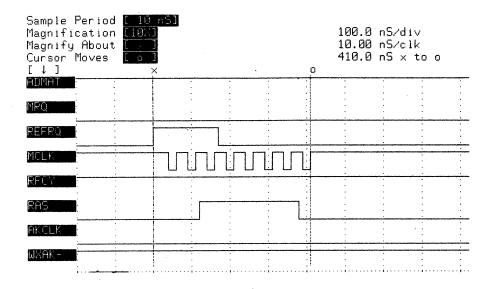

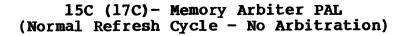

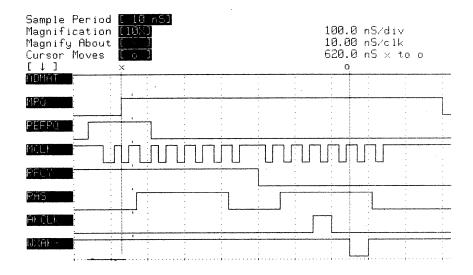

| Memory Arbiter                   |    |   |   |   | 3-58           |

| RAM Refresh                      |    |   | • |   | 3-58           |

| Address Space Allocation         | •  | • |   |   | 3-59           |

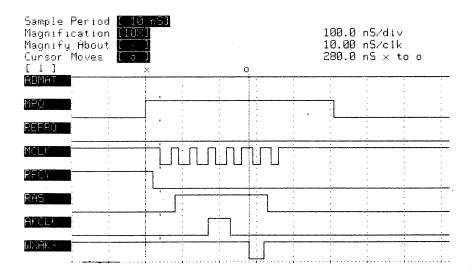

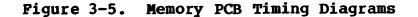

| Timing Diagrams                  |    |   |   |   | 3-59           |

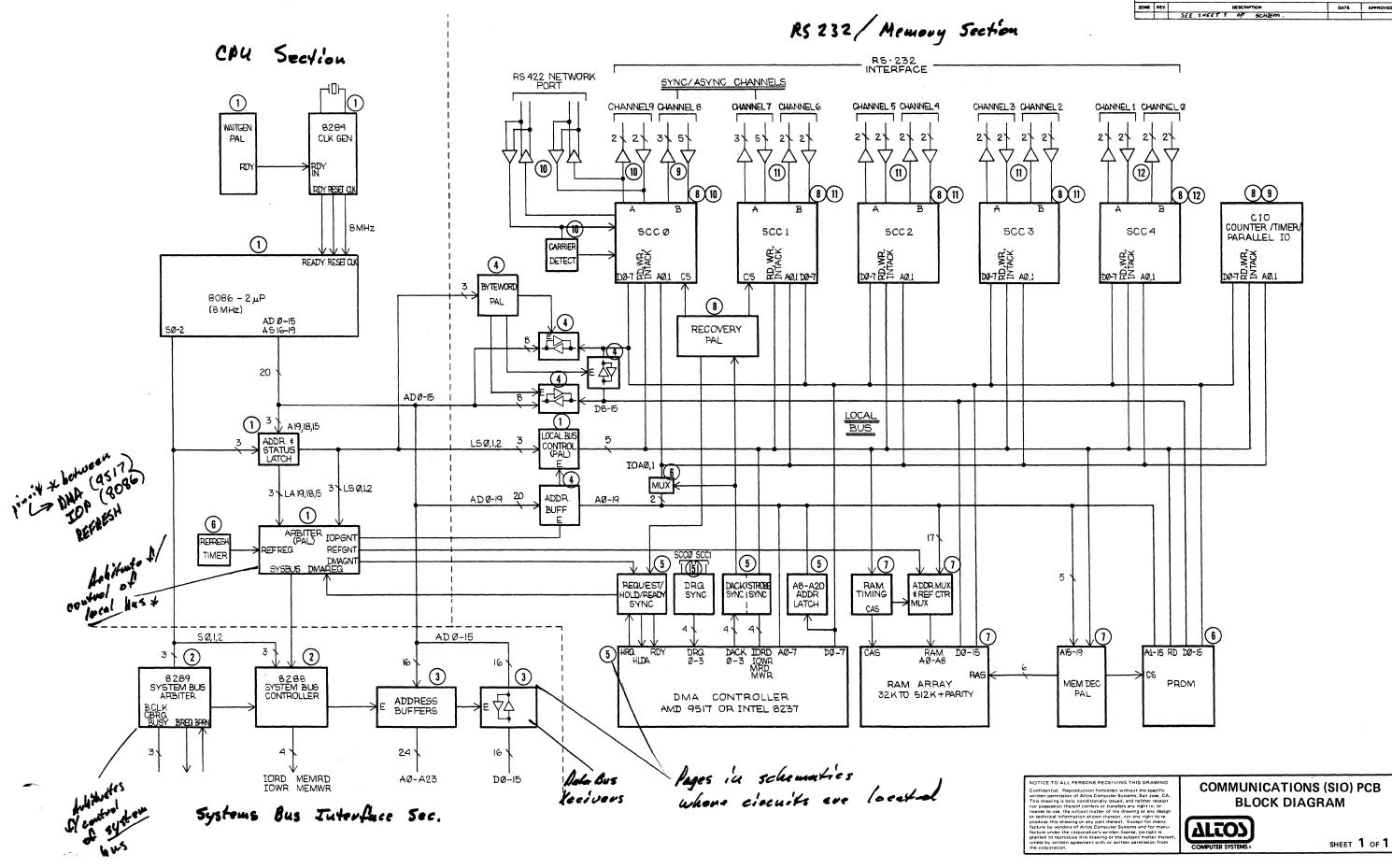

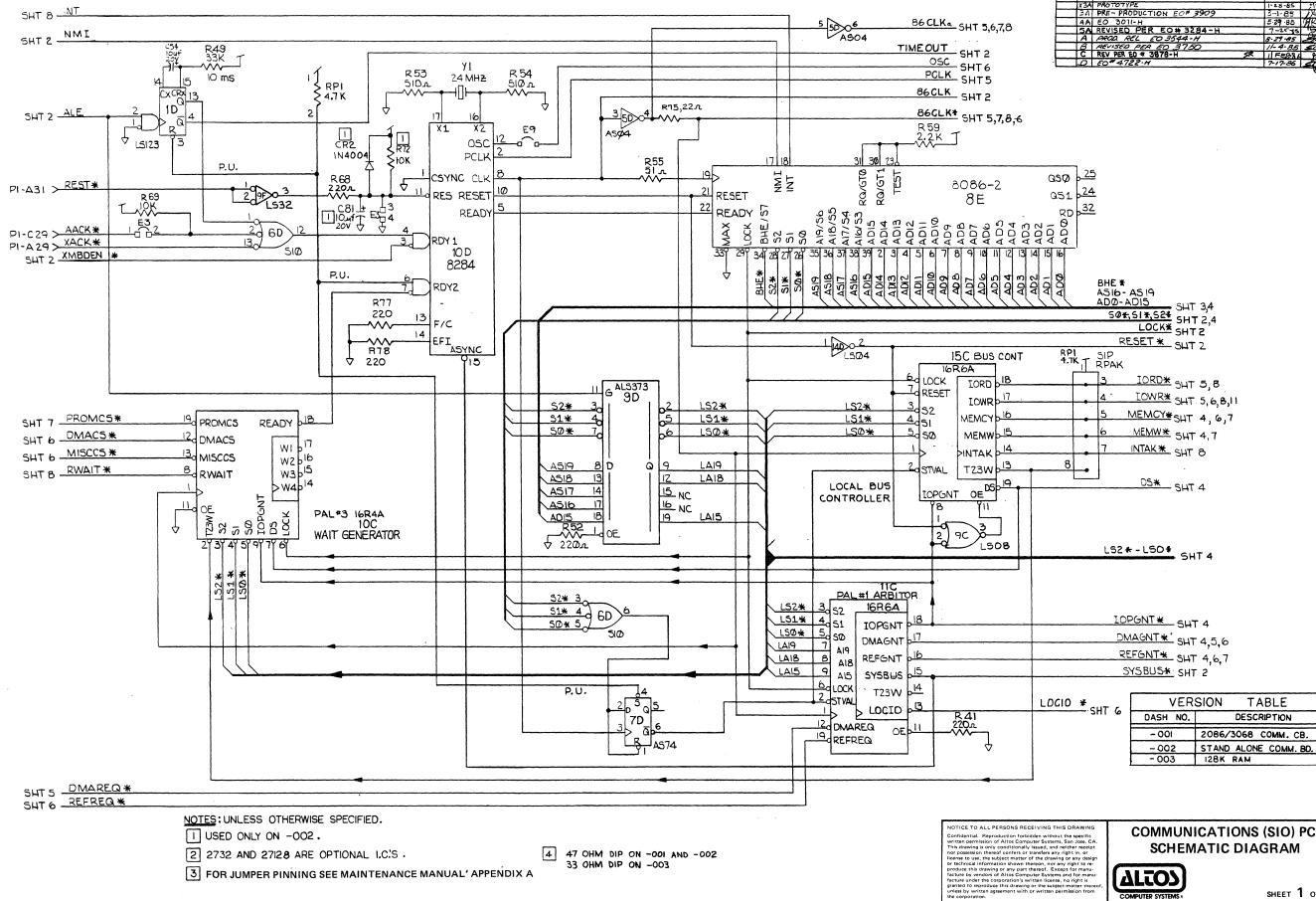

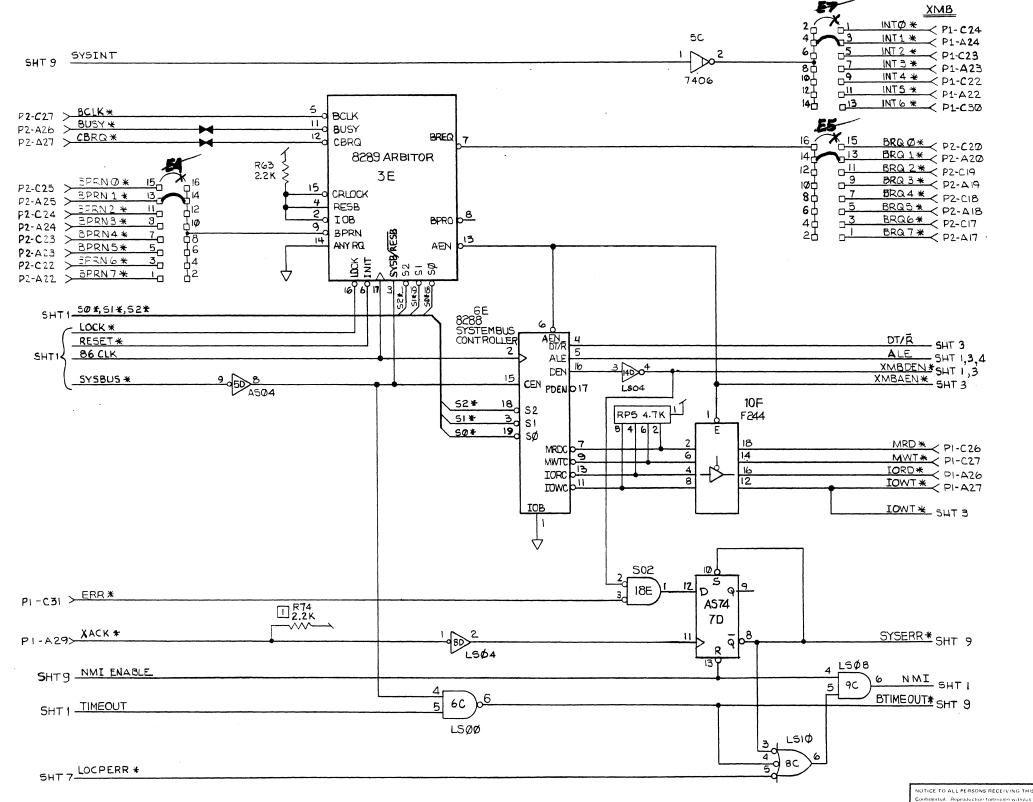

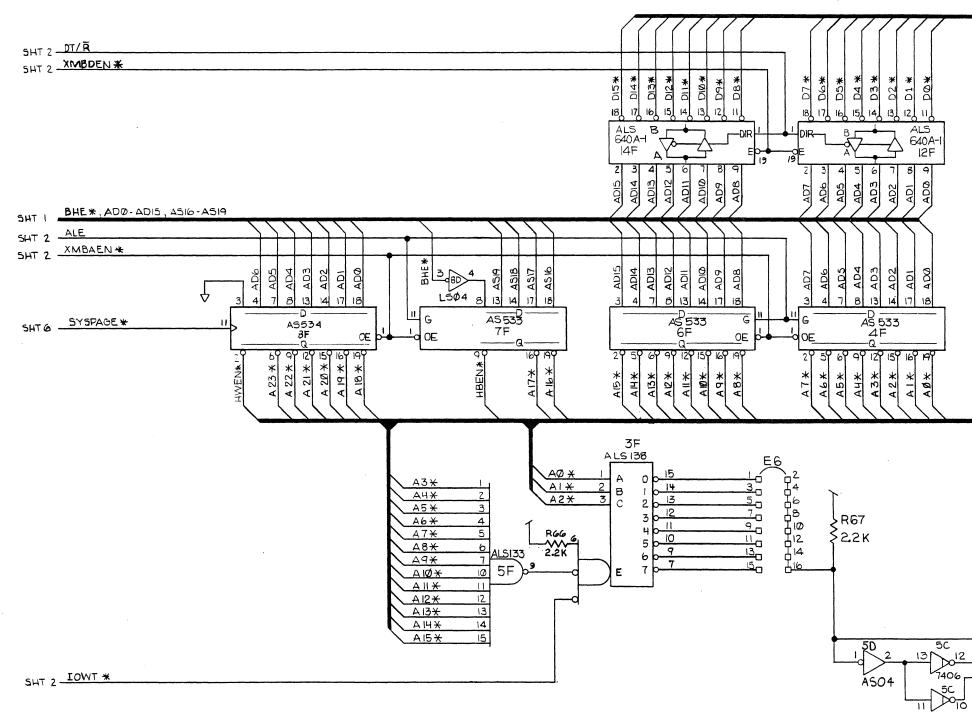

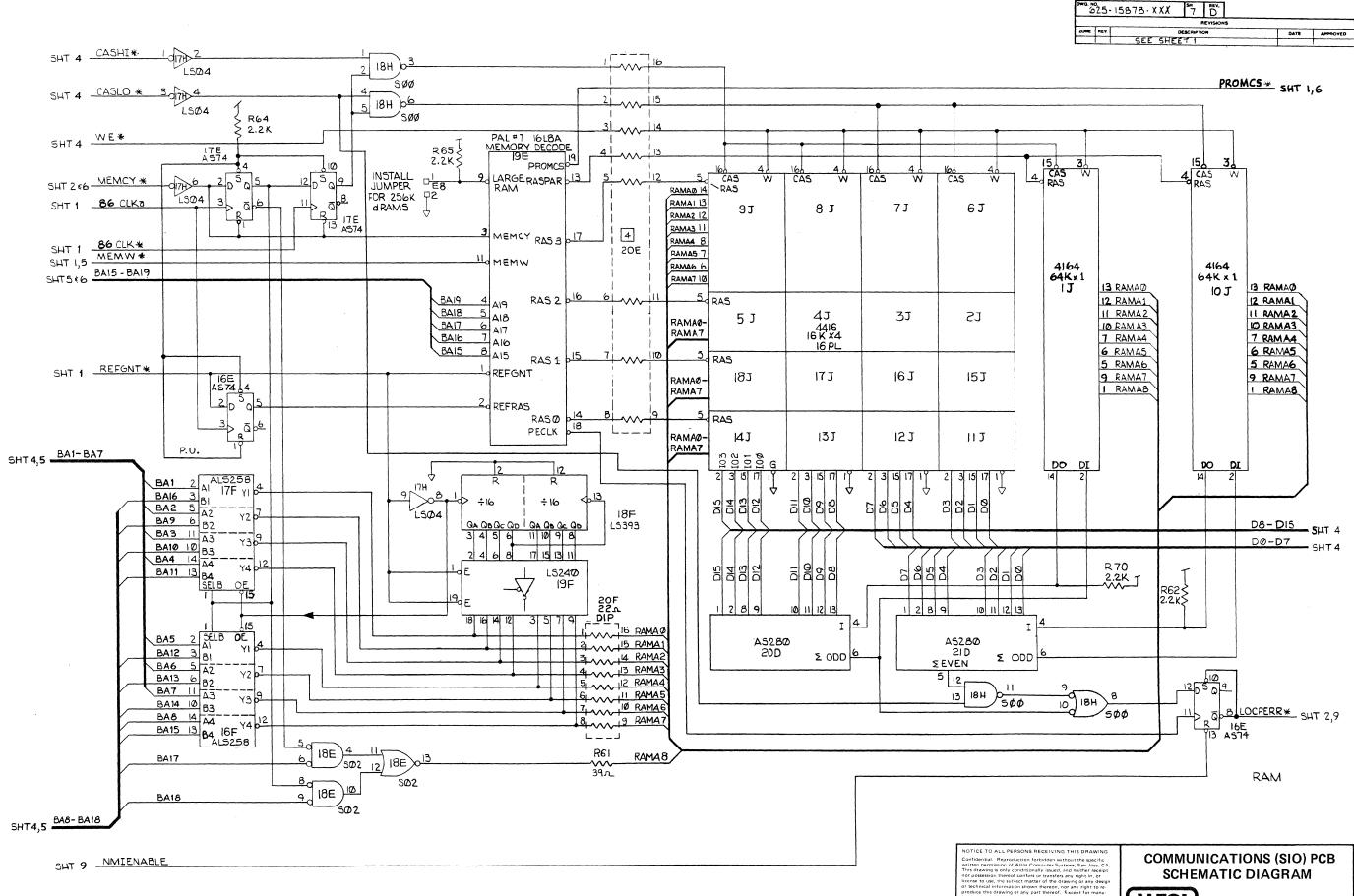

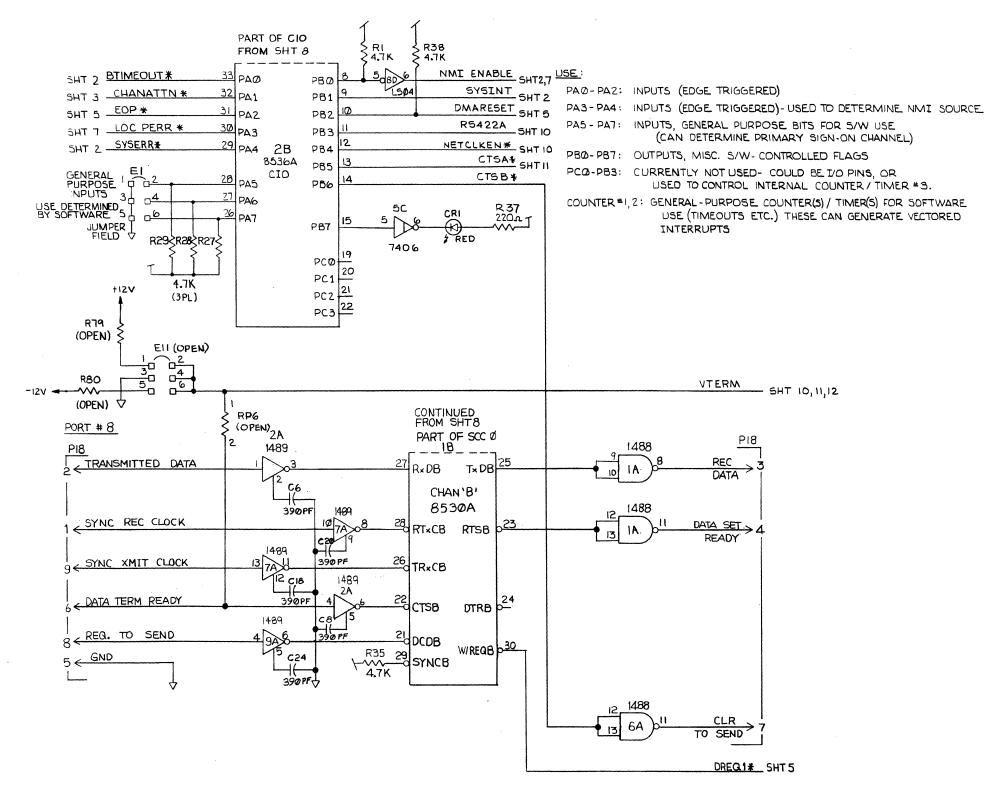

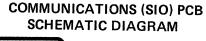

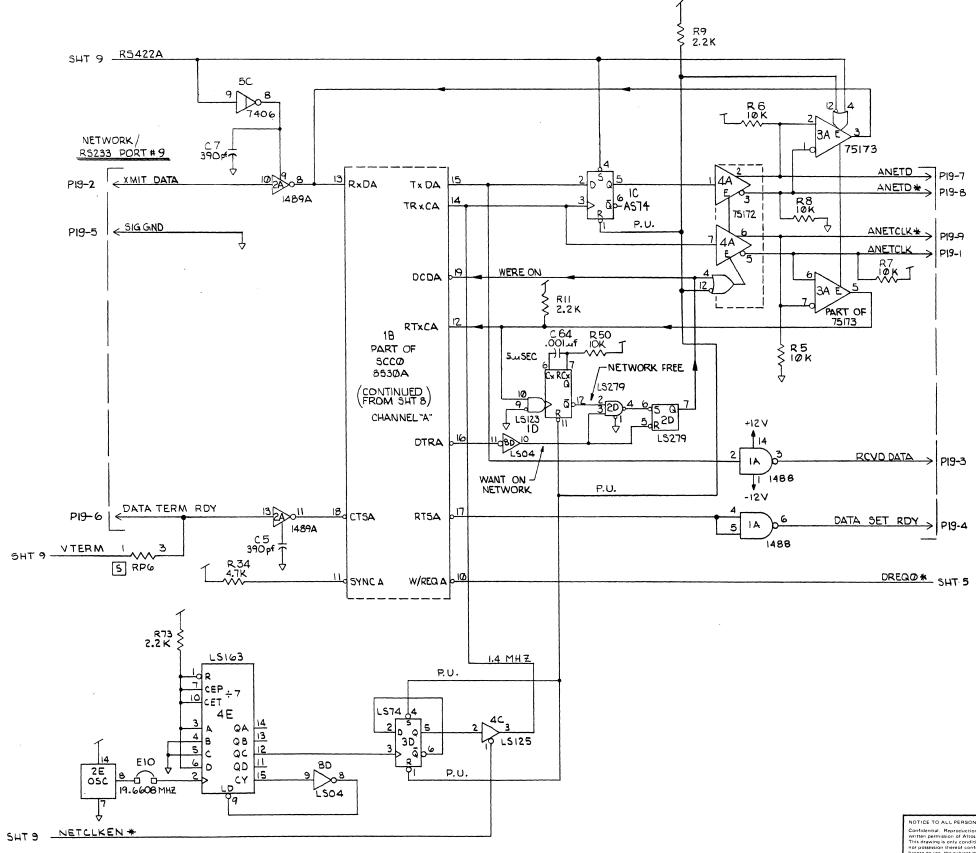

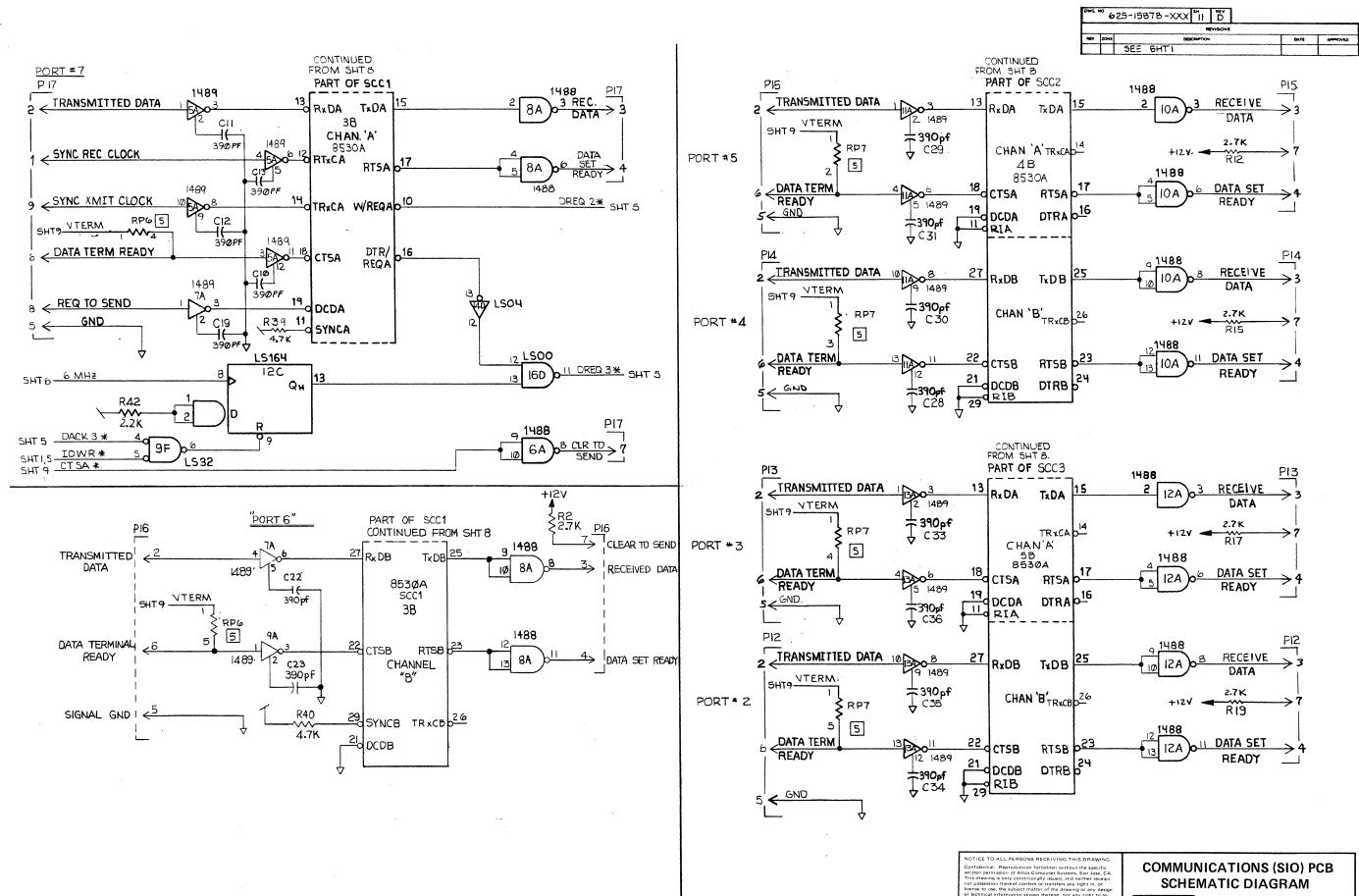

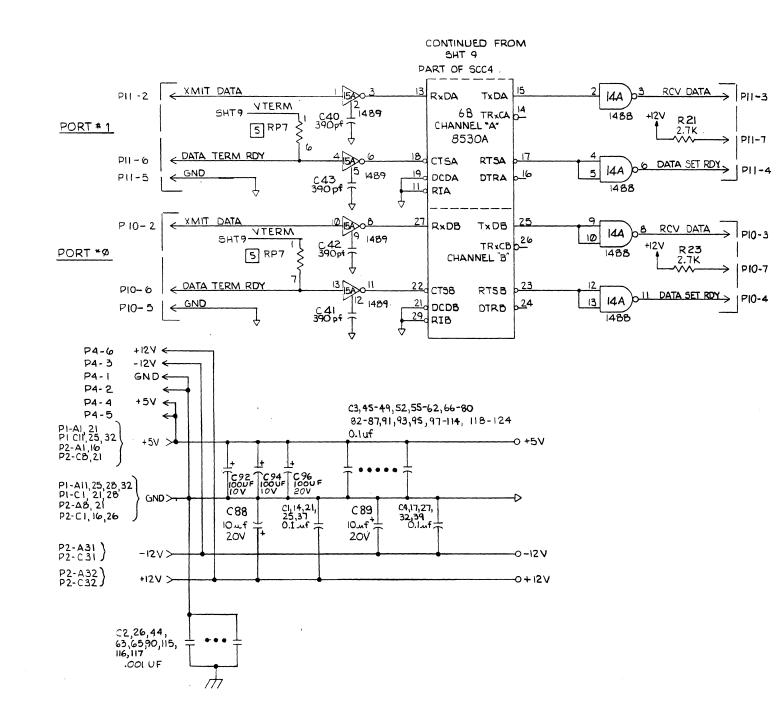

| Communications (SIO) PCB         |    |   |   | • | 3-63           |

| I/O Microprocessor               | •  |   |   |   | 3-63           |

| I/O Microprocessor               |    | • | • |   | 3-63           |

| System Bus Interface             |    | • | • |   | 3-64           |

| Local Bus Controller             |    | • | • |   | 3-65           |

| Local Bus Interface              | •  | • | • |   | 3-65           |

| Local Bus Transceiver Controller |    |   | • |   | 3-66           |

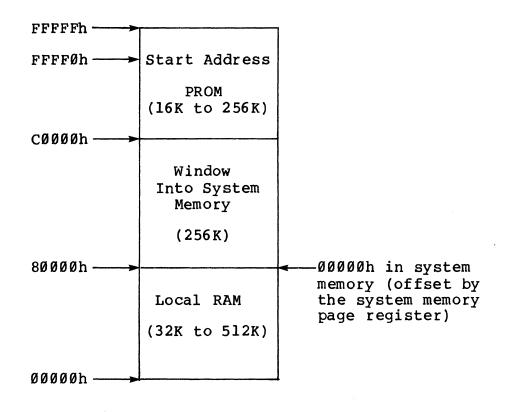

| Local Memory                     |    |   |   | • | 3-66           |

| Local Memory                     | •  | • |   |   | 3-68           |

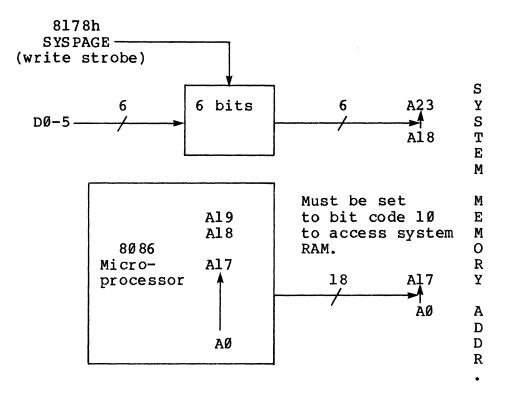

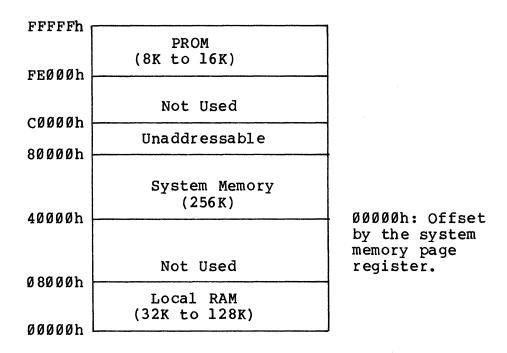

| System Memory Page Register      | •  | • | • |   | 3-68           |

| Accessing System Memory          |    |   |   |   | 3-69           |

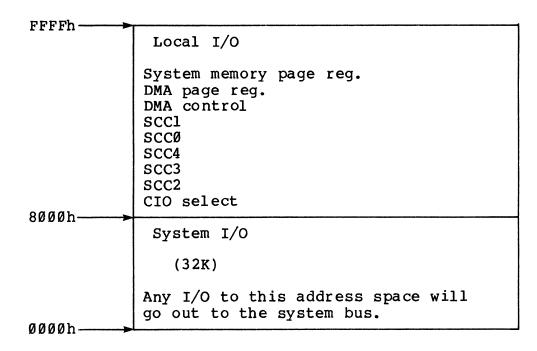

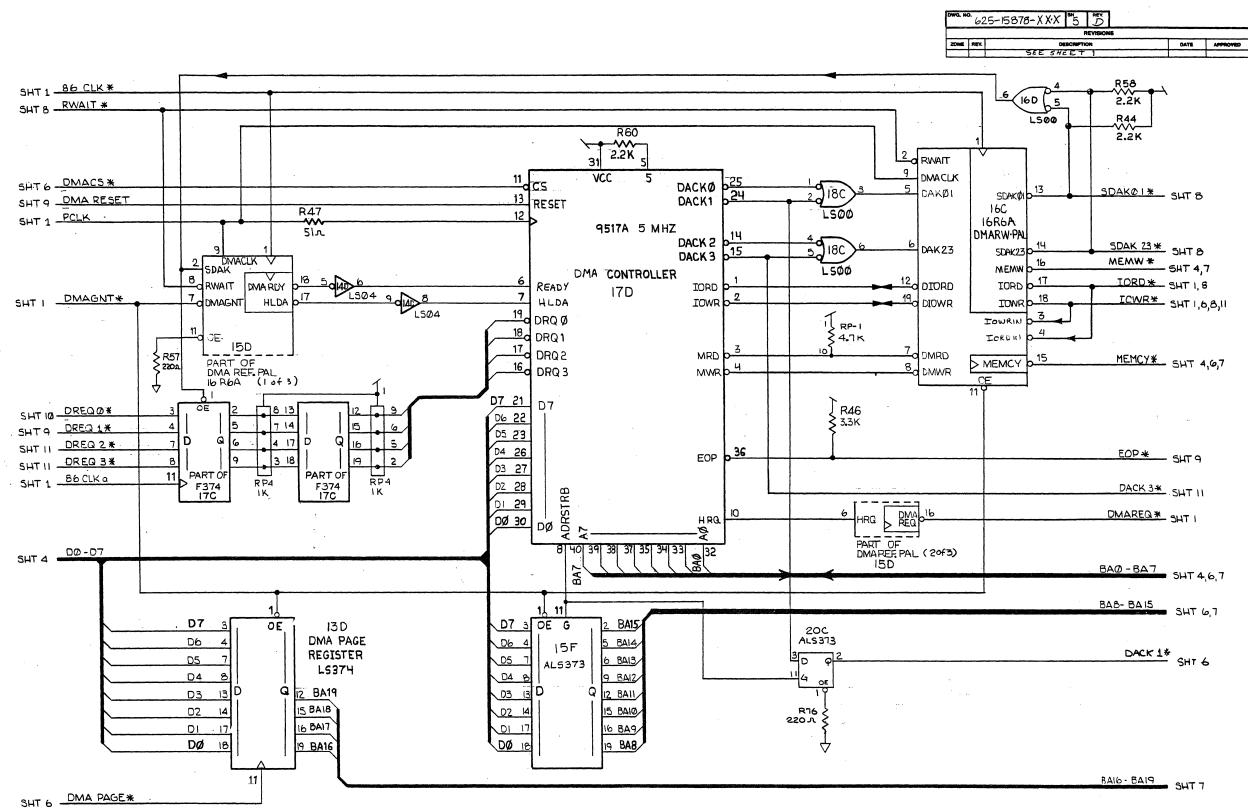

| T/O Port Addressing              |    |   |   |   | 2.70           |

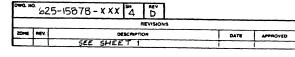

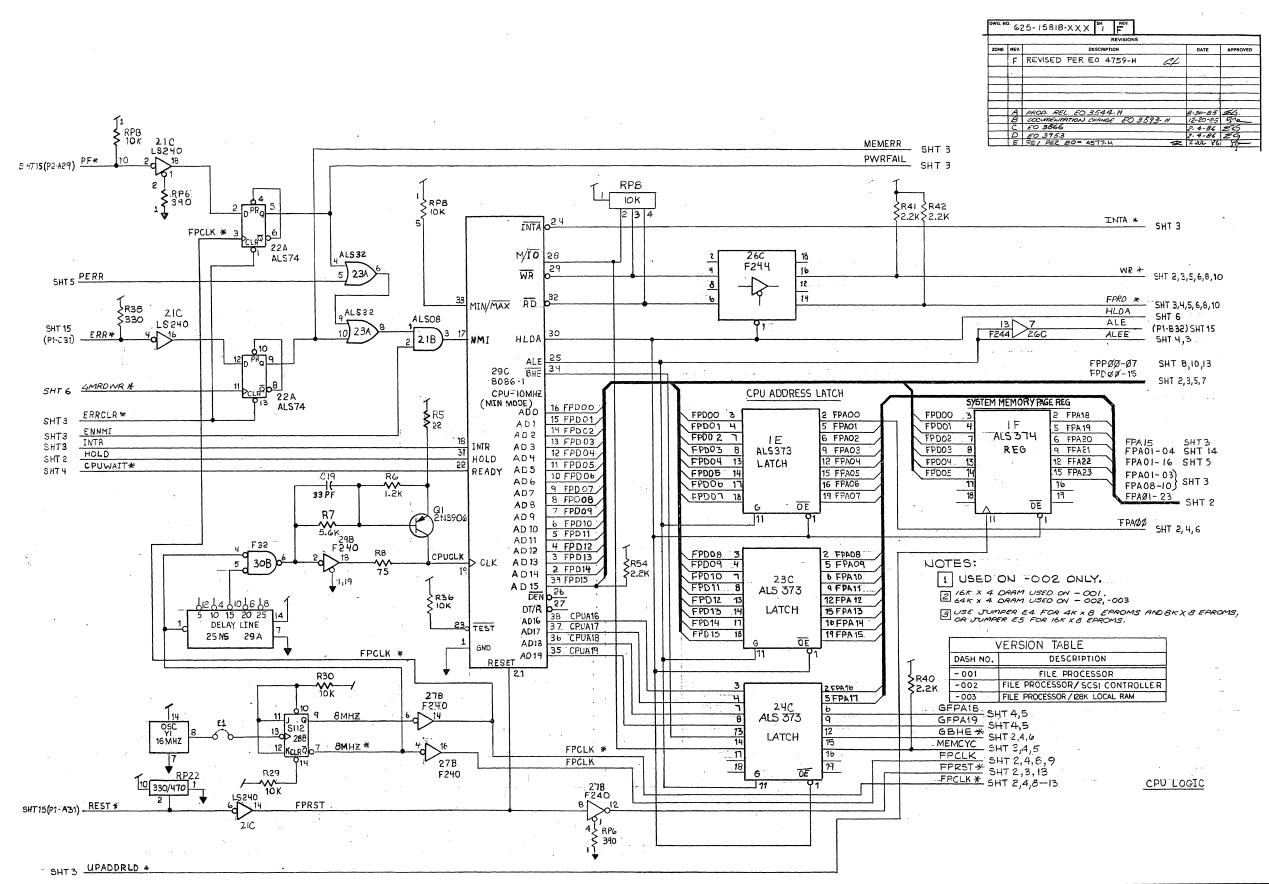

| DMA Controller                   | •  | • | • | • | 3-75           |

| DMA Synch/Refresh Controller     | •  | • | • | • | 3-77           |

| DMA Controller                   | •  | • | • | • | 3-77           |

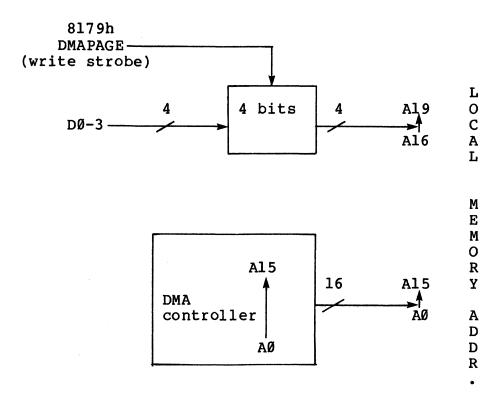

| DMA Page Register                | ٠  | • | • | • | 3-78           |

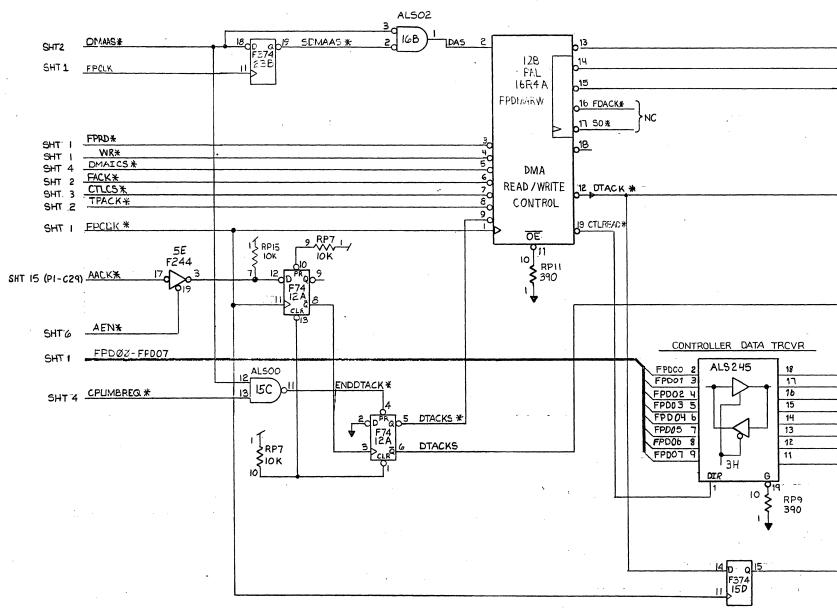

| DMA Read/ Write Controller       | ٠  | ٠ | • | • | 3-79           |

| Network Channel.                 | •  | • | • | • | 3-82           |

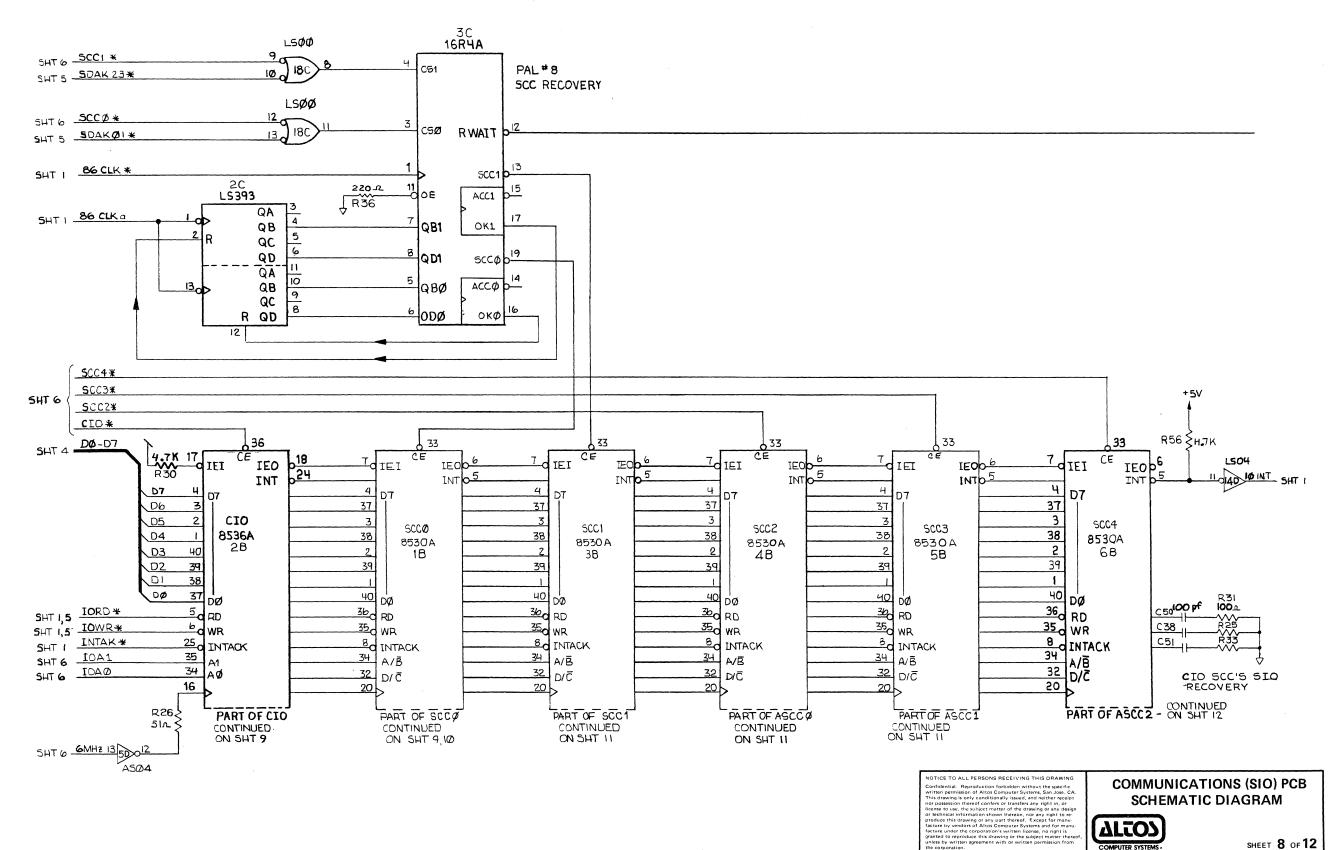

| SCC Recovery                     | ٠  | ٠ | • | • | 3-83           |

| Programming Precautions          | ٠  | ٠ | • | • | 3-83           |

|                                  |    |   |   |   |                |

| CIO Programming Notes.           | •  | • | ٠ | • | 3-88           |

| Interrupt Priorities             | •  | • | • | ٠ | 3-90           |

| Interrupt Priorities             | •  | • | • | • | 3-92           |

| 1/0 Connectors                   | ٠  | ٠ | • | • | 3-93           |

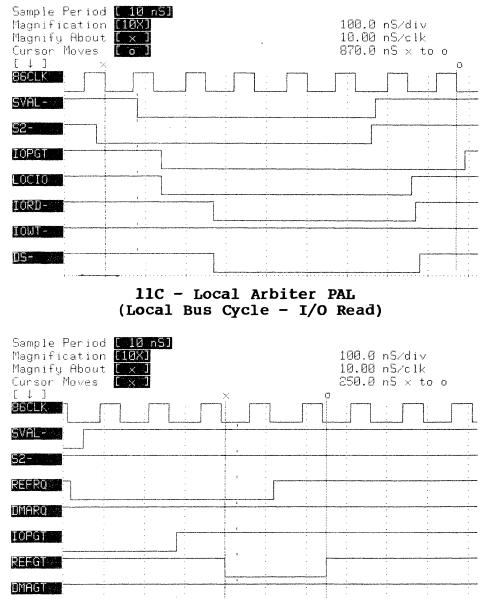

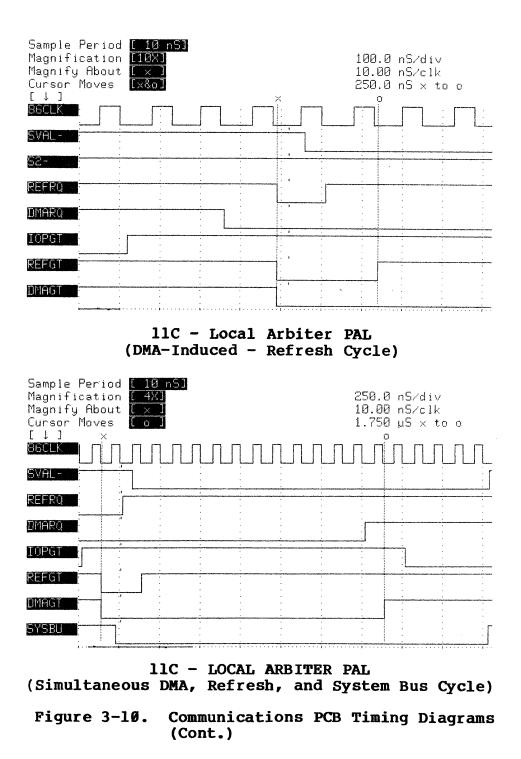

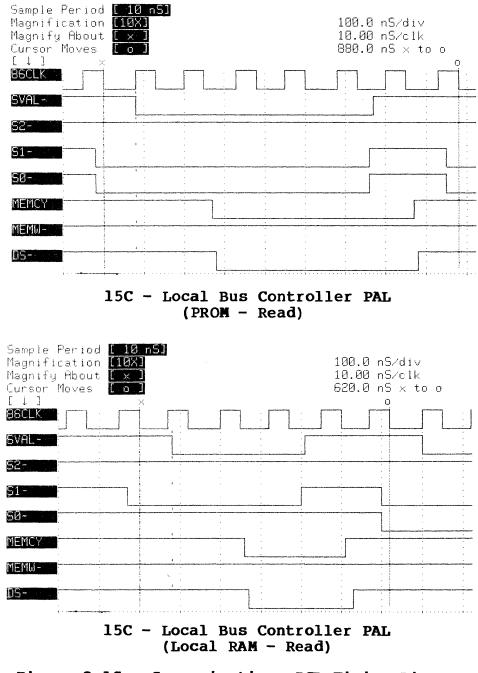

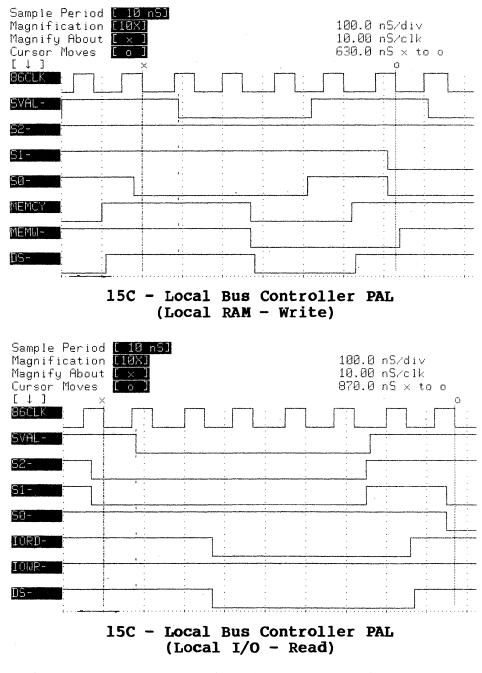

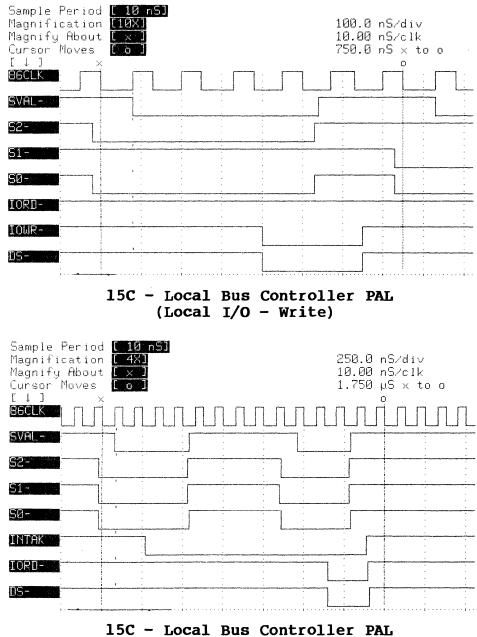

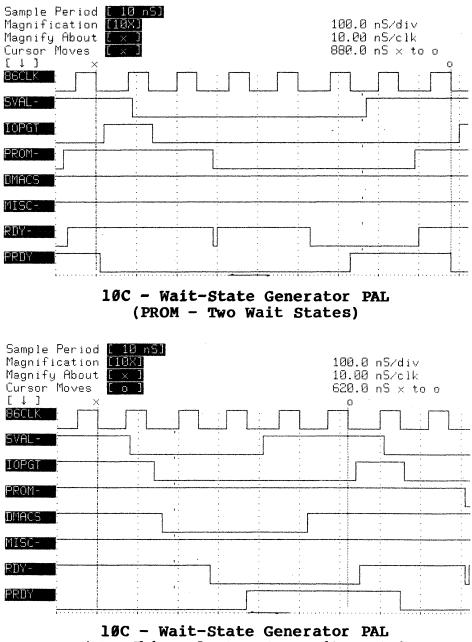

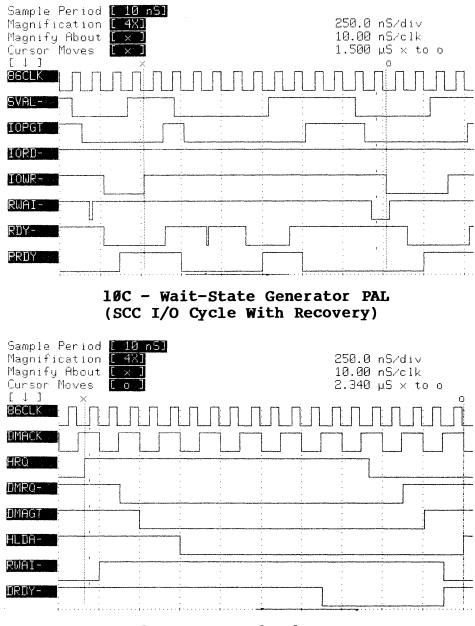

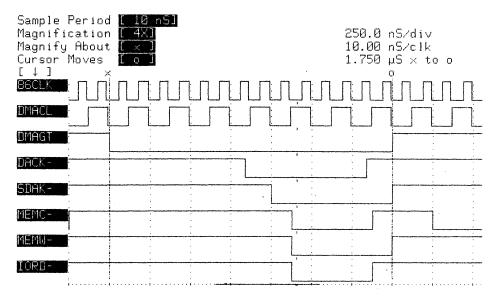

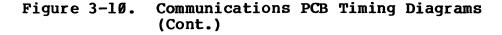

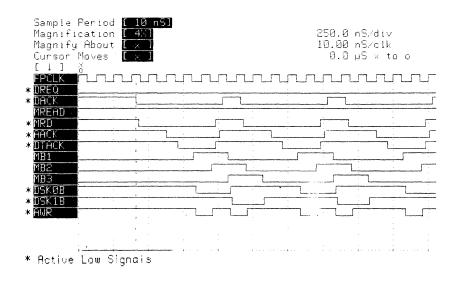

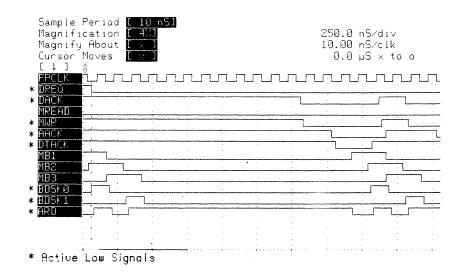

| Timing Diagrams.                 | •  | • | ٠ | • | 3-95           |

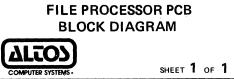

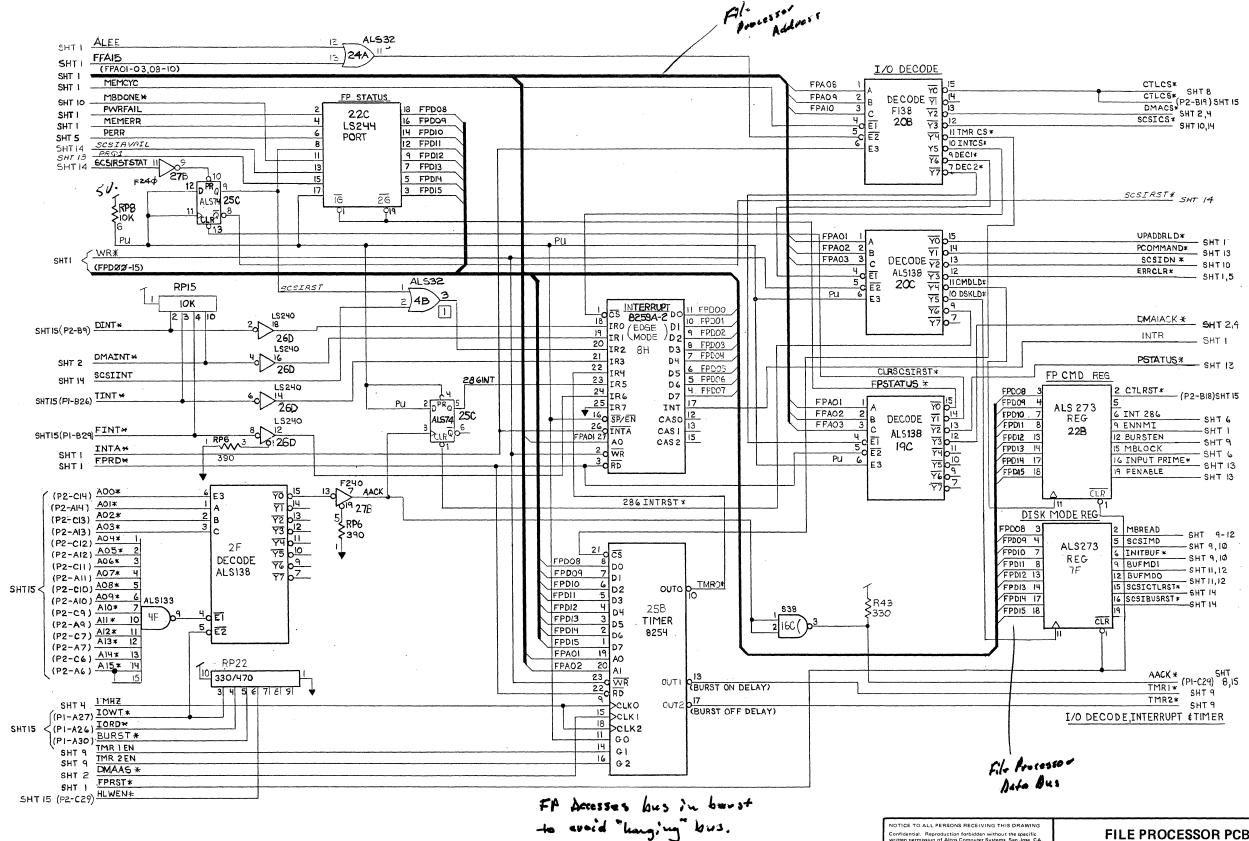

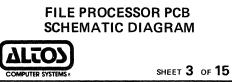

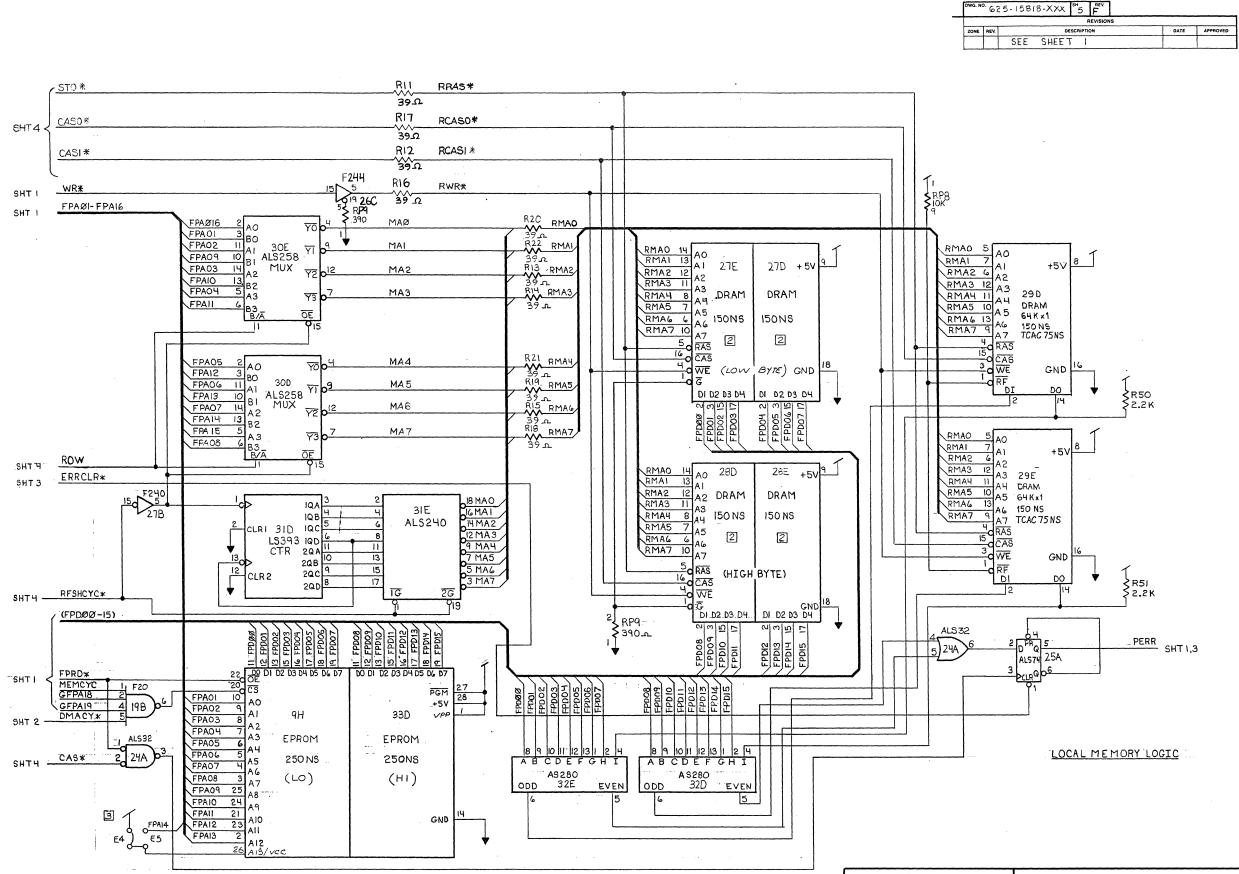

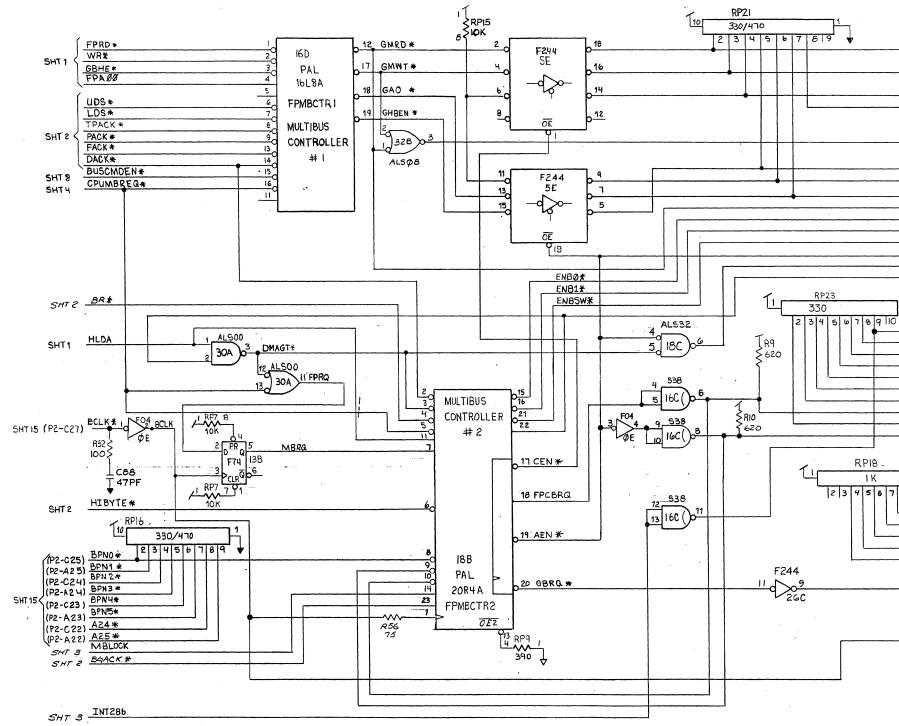

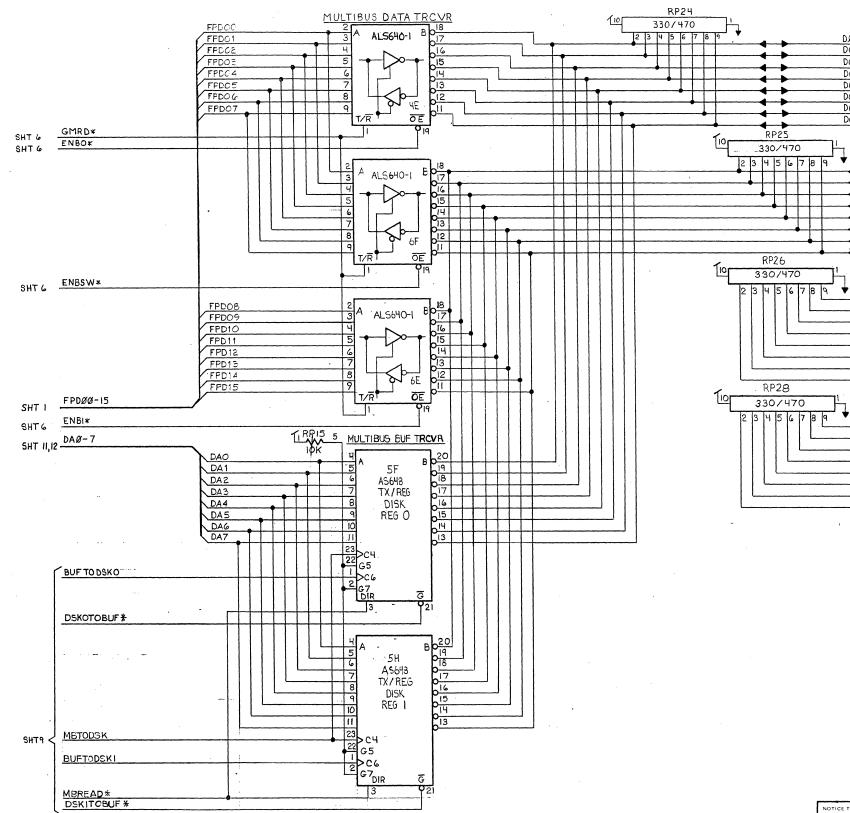

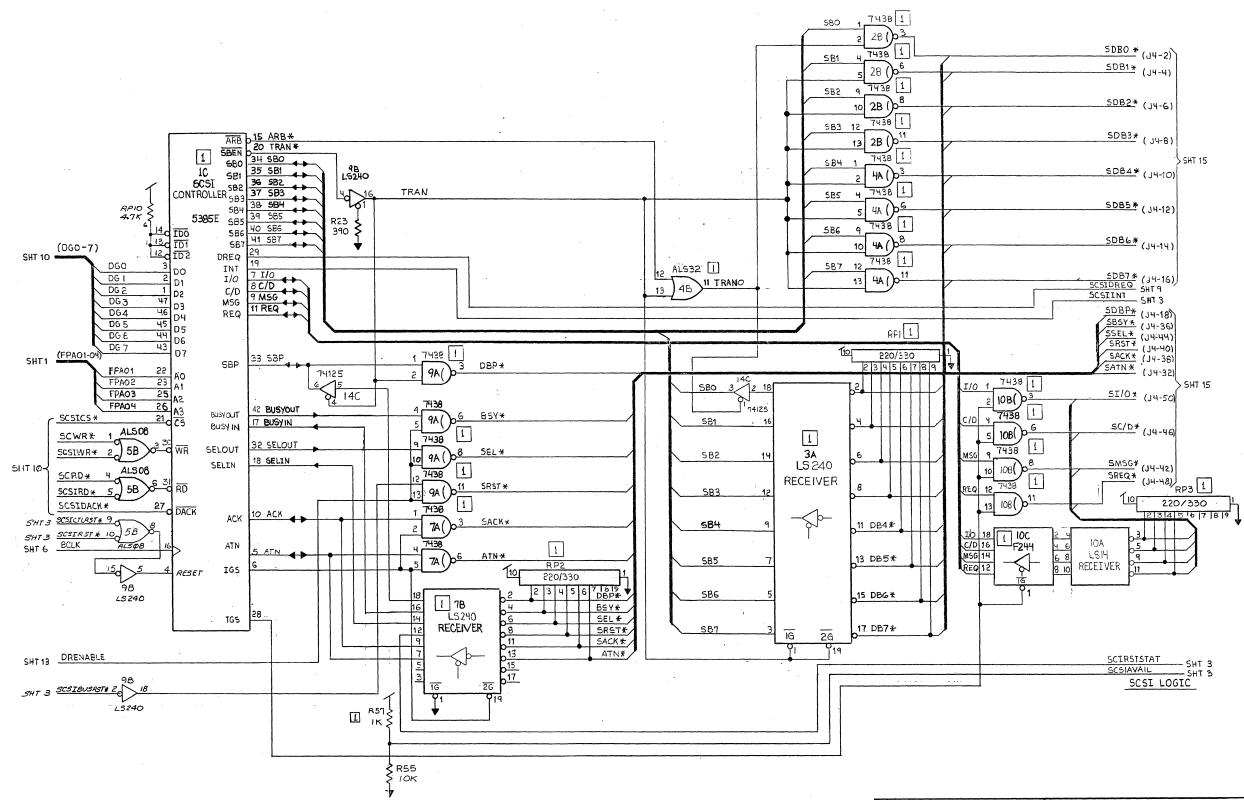

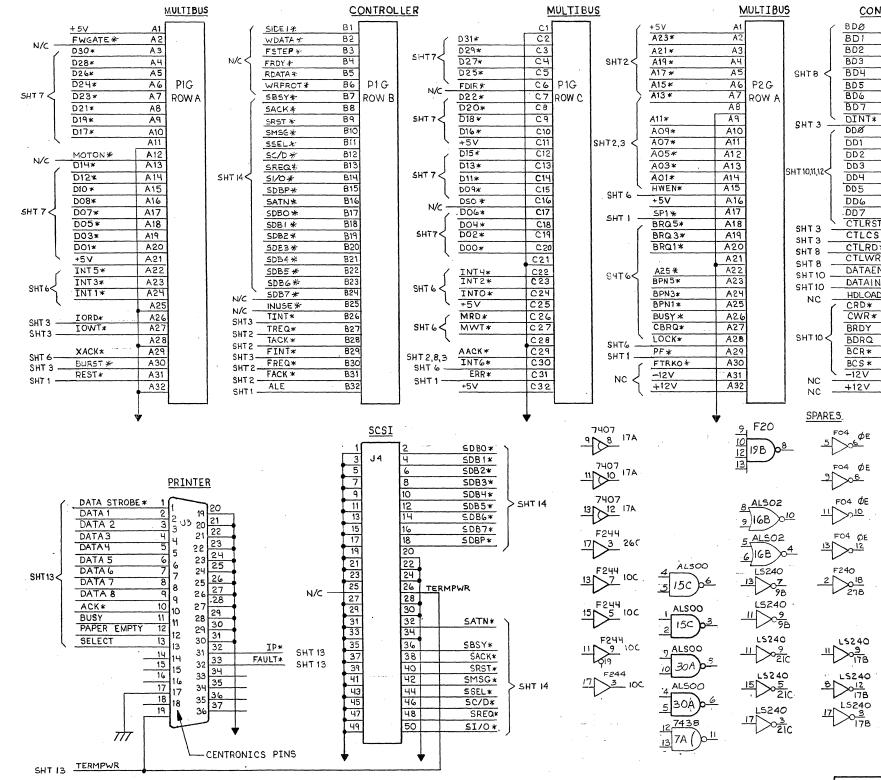

| File Processor PCB.              | •  | • | • | • | 3-105          |

| I/O Connectors                   | •  | • | • | • | 3-105          |

| System Bus Control Logic         | •  | • | • | • | 3-106          |

| Microprocessor                   | •  | ٠ | • | ٠ | 3-106          |

| Interrupts                       | •  | ٠ | • | • | 3-107          |

| Memory Organization              | •  | • | • | • | 3-107          |

| Memory Options                   | •  | ٠ | • | • | 3-109          |

| RAM Control Logic                | •  | ٠ | • | • | 3-109          |

| Parity Errors                    | .• | • | • | • | 3-1Ø9<br>3-1Ø9 |

|                                  | •  | • | • | • | 3-112          |

|                                  | •  | • | • |   | 3-112          |

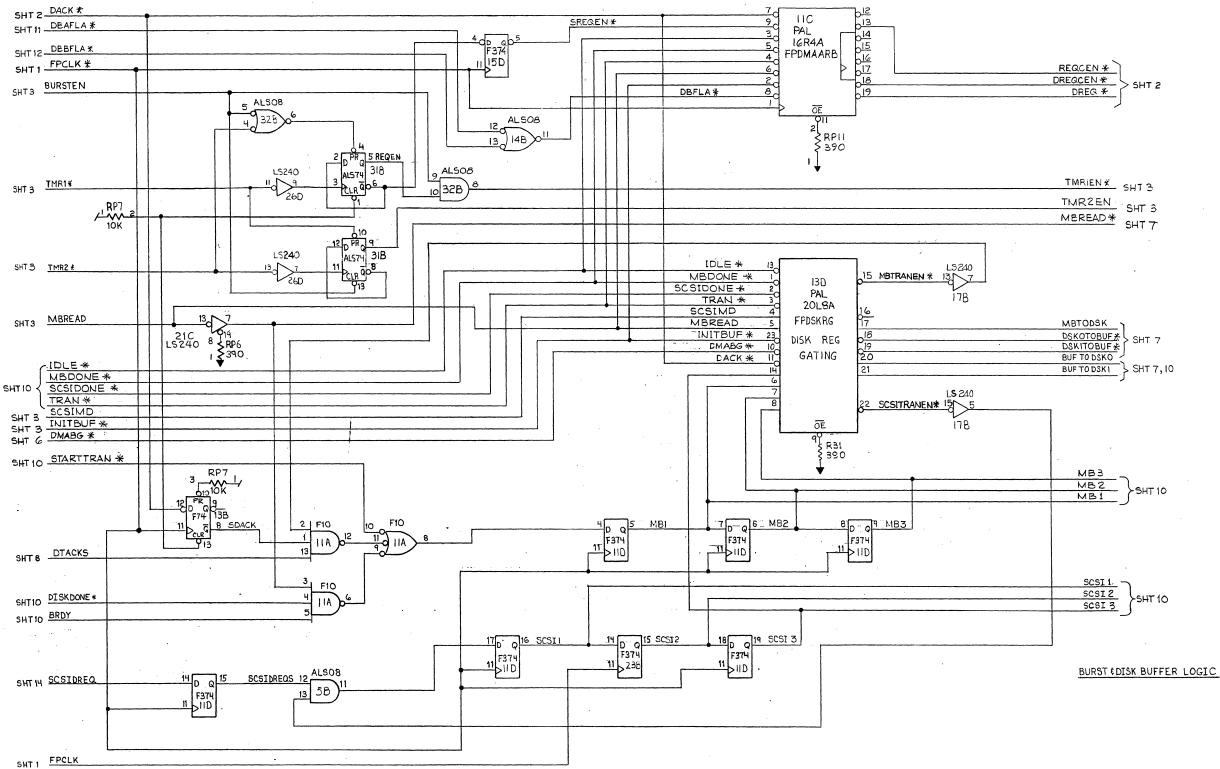

| Burst Logic.                     | •  | • | • | • | 3-117          |

|                                  | •  | • | ٠ |   | J TT /         |

| DMA Controller                      | 3-117 |

|-------------------------------------|-------|

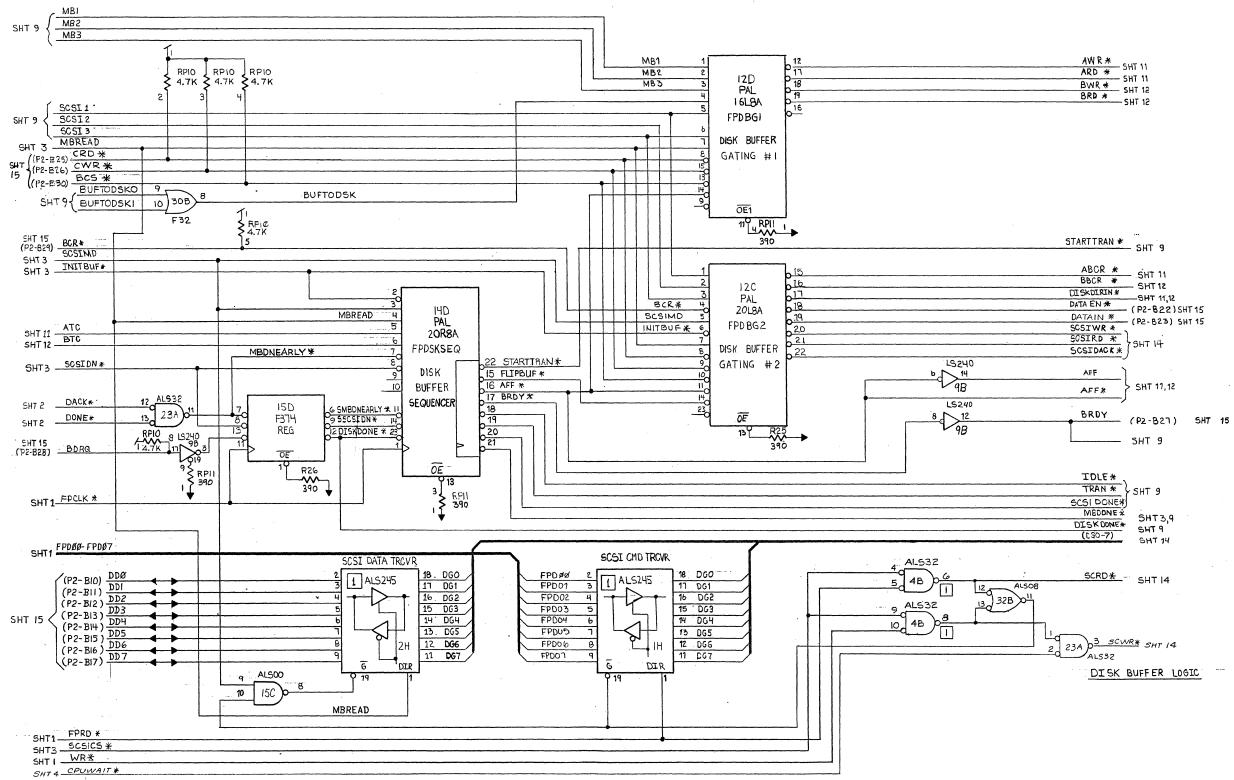

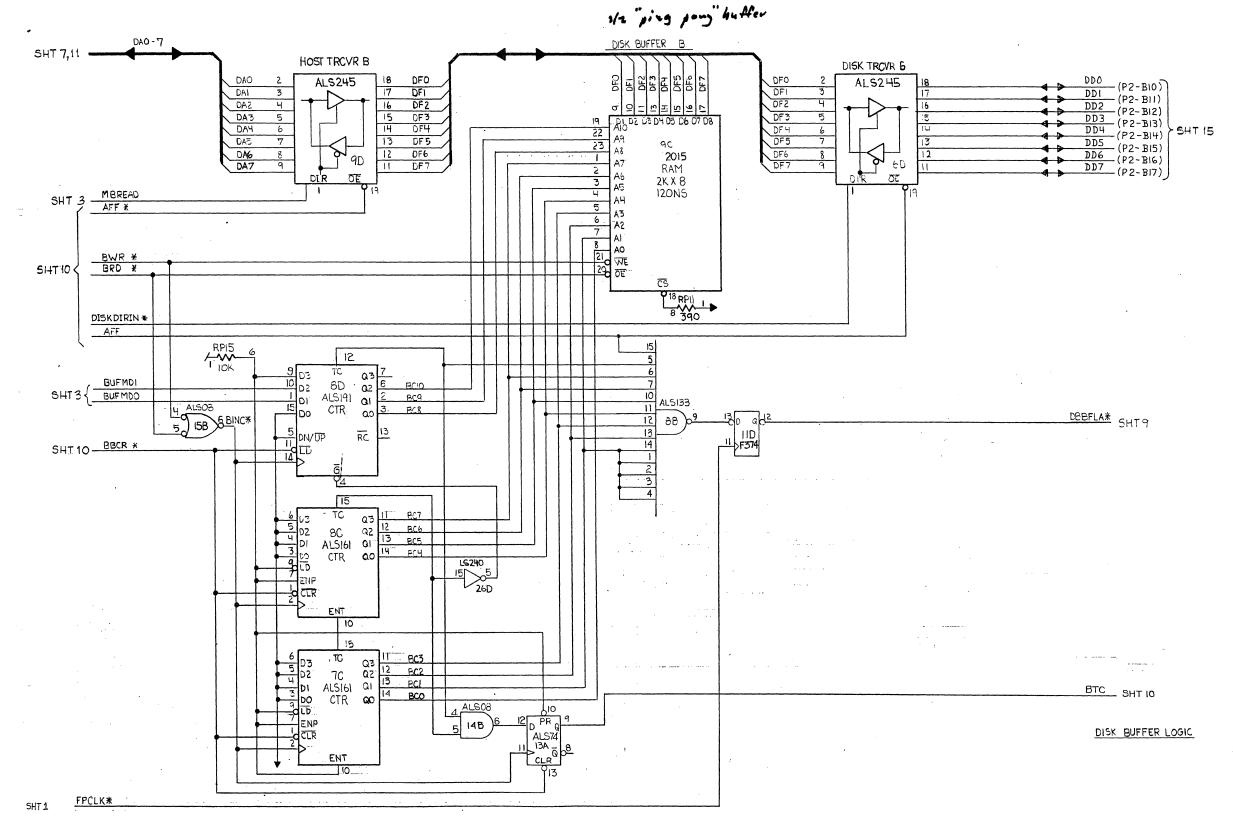

| Ping-Pong Buffer                    | 3-118 |

| Ping-Pong Buffer Control Logic      | 3-120 |

| Controller Interface                |       |

|                                     | 3-122 |

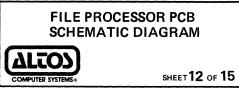

| Printer Controller                  | 3-122 |

| SCSI Controller                     | 3-124 |

| File Processor Initial Program Load |       |

|                                     | 3-126 |

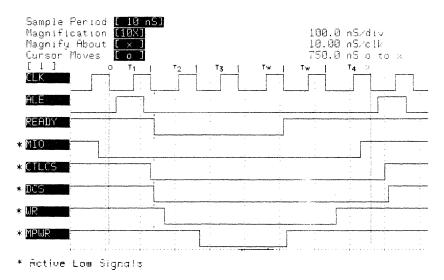

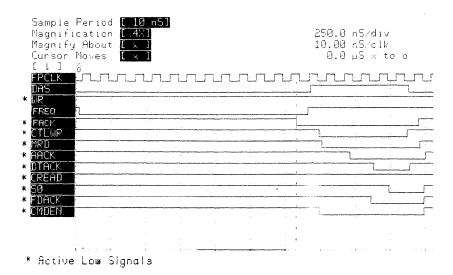

| Timing Diagrams                     |       |

|                                     | 3-137 |

|                                     | 3-137 |

|                                     | 3-137 |

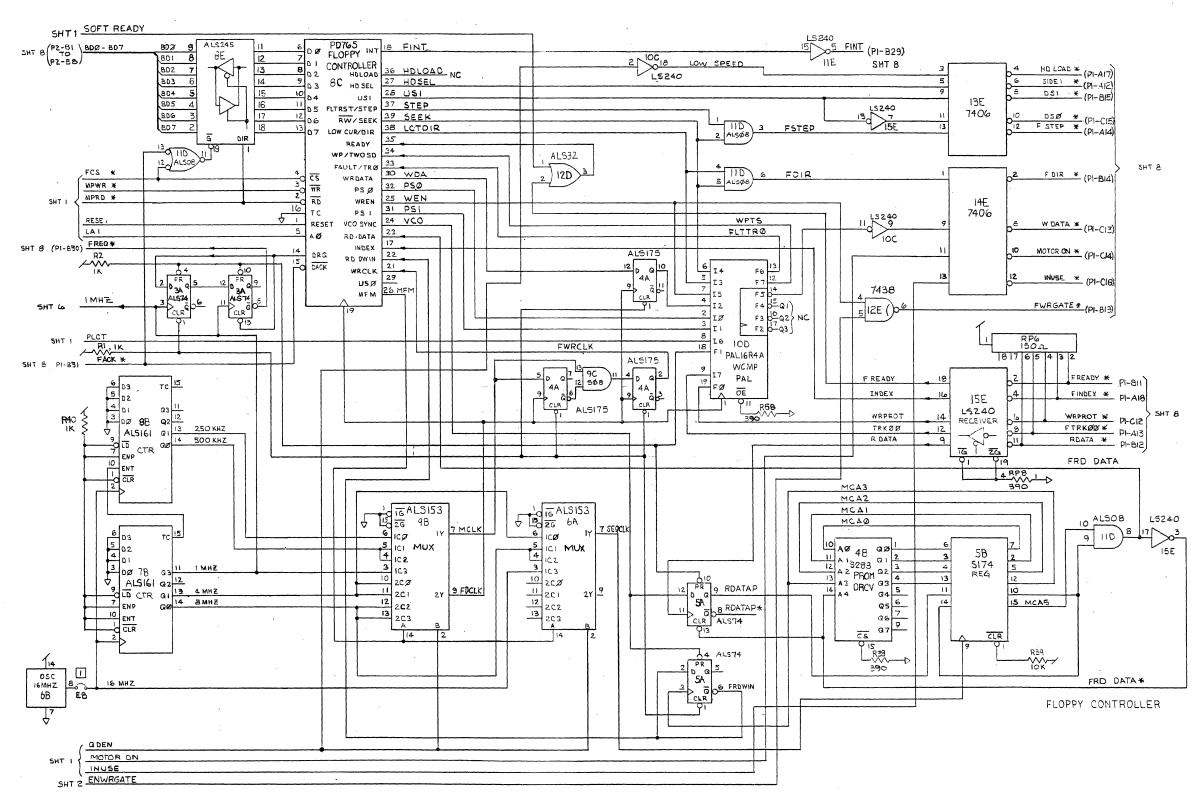

| Floppy Disk Controller              | 3-140 |

| Tape Controller                     | 3-143 |

#### **4 MAINTENANCE**

| INTRODUCTION                                                                    | 3   |

|---------------------------------------------------------------------------------|-----|

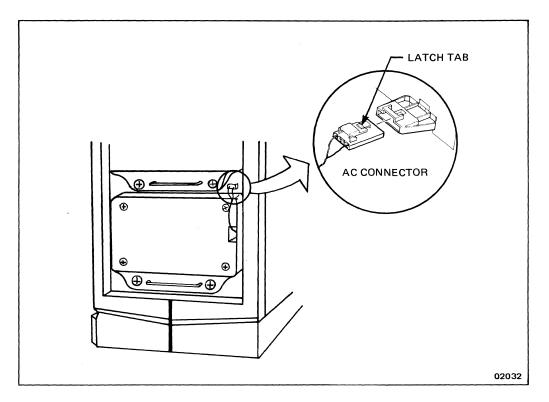

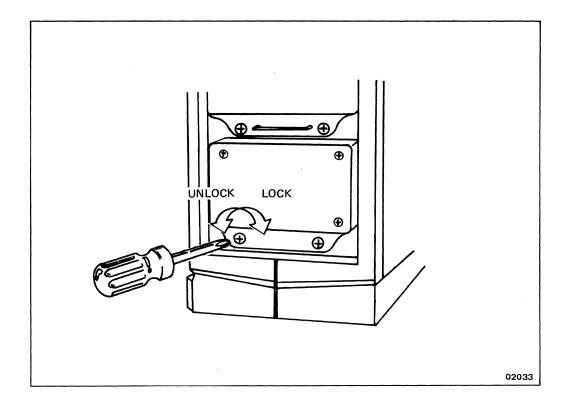

| SELECTING 115/230 VAC OPERATION 4-3                                             | 3   |

| PREVENTIVE MAINTENANCE 4-5                                                      | 5   |

| Cleaning                                                                        | 5   |

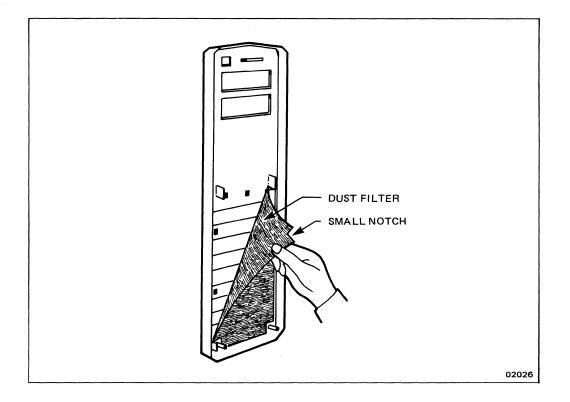

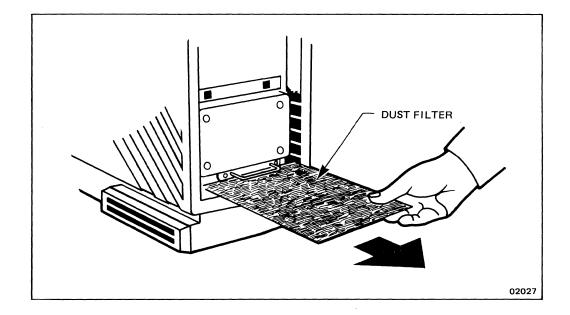

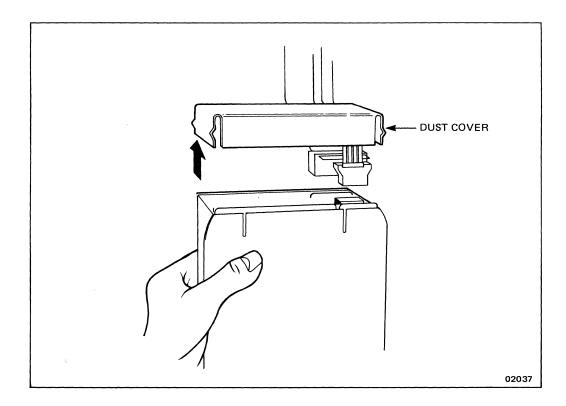

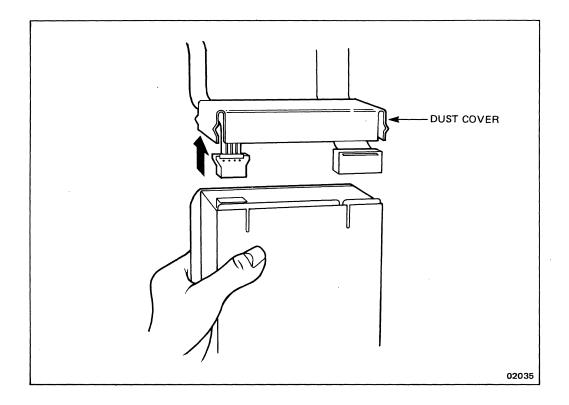

| Dust Filters 4-6                                                                | 5   |

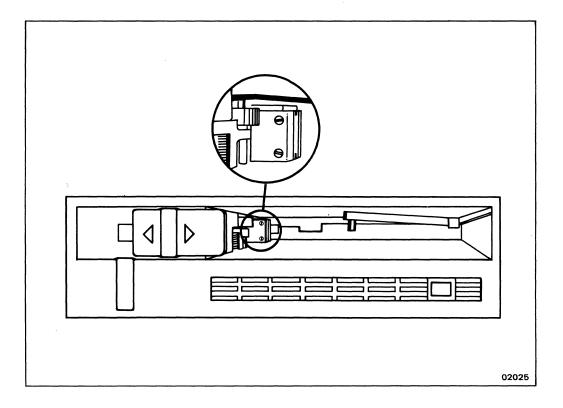

| Tape Heads $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 4-9$ | )   |

| Floppy Disk Drive 4-3                                                           | 11  |

| Exterior                                                                        | 12  |

| Interior                                                                        | 12  |

| CORRECTIVE MAINTENANCE                                                          | 13  |

| Removal and Replacement 4-1                                                     | 13  |

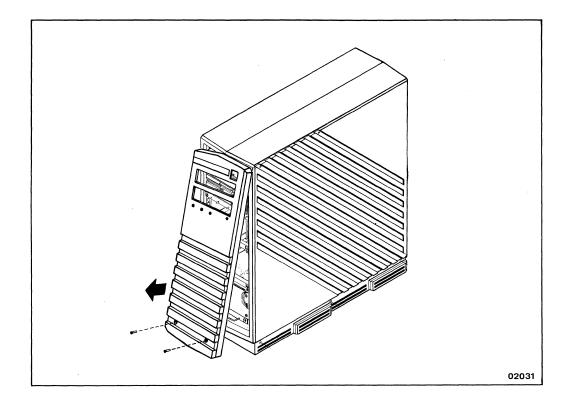

| Removing the Front Panel 4-1                                                    | 13  |

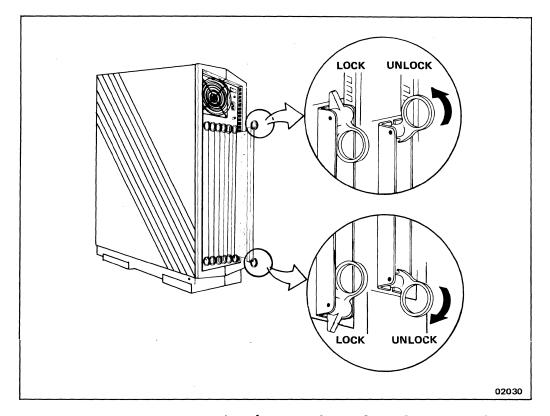

| Removing the Side Panels 4-1                                                    | 15  |

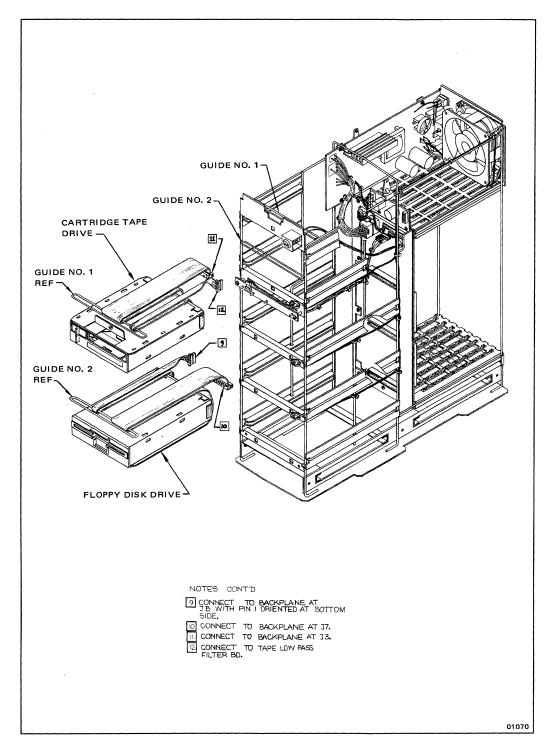

| Removing the Tape Drive 4-1                                                     | 16  |

| Removing the tape brive                                                         |     |

| Replacing the Tape Drive                                                        |     |

| Removing the Floppy Drive                                                       | 23  |

| Replacing the Floppy Drive 4-2                                                  | 5 T |

| Removing the Hard Disk Drive 4-2                                                | 44  |

| Replacing a Hard Disk Drive 4-2                                                 | 24  |

| Removing the Plug-In Printed Circuit                                            | ~   |

| Boards                                                                          |     |

| Removing the Main Power Supply 4-2                                              |     |

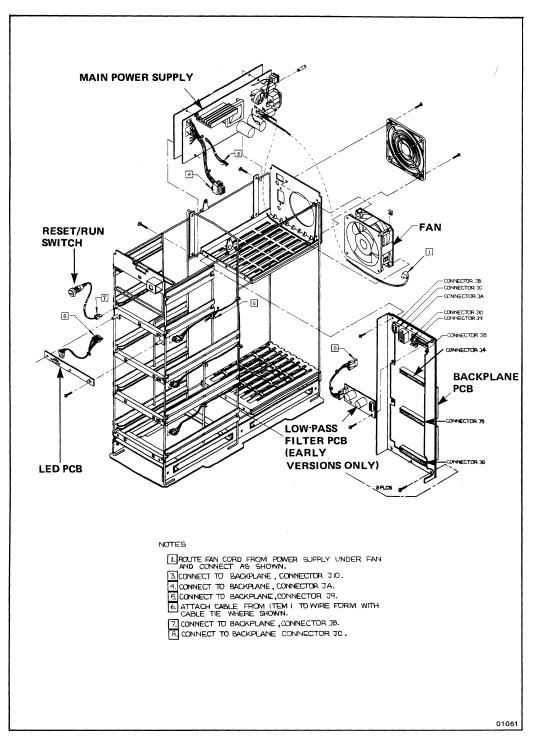

| Removing the Backplane PCB 4-2                                                  | 28  |

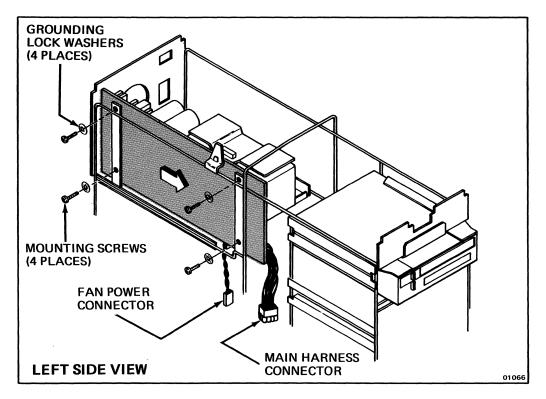

| Removing the Low-Pass Filter PCB                                                |     |

| (Early Version Only)                                                            | 3Ø  |

| Removing the LED PCB 4-3                                                        | 31  |

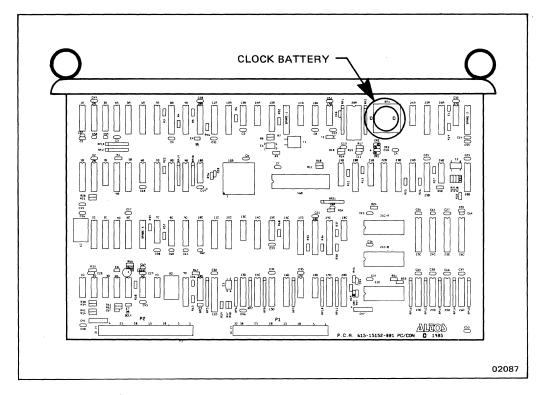

| Removing the Clock Battery 4-3                                                  | 31  |

| Packaging the System Unit                           | 4-35<br>4-35<br>4-36<br>4-36 |

|-----------------------------------------------------|------------------------------|

| TROUBLESHOOTING                                     |                              |

|                                                     | 5-3                          |

|                                                     | 5-3                          |

| System Overview                                     | 5-3                          |

| Principles of Operation                             | 5-4                          |

|                                                     | 5-4                          |

| Diagrams                                            | 5-4                          |

| Field Replaceable Unit Locations                    | 5-5                          |

| TROUBLESHOOTING CONSIDERATIONS                      | 5-5                          |

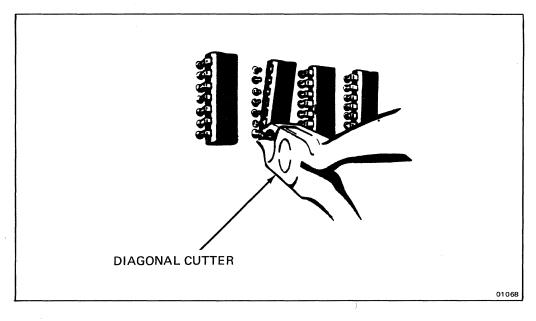

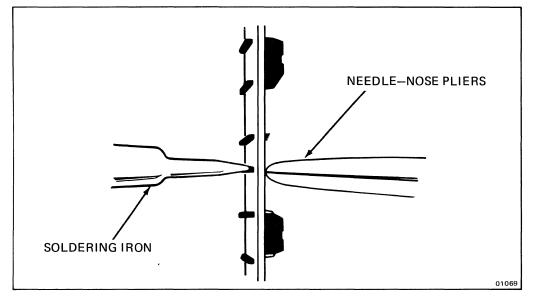

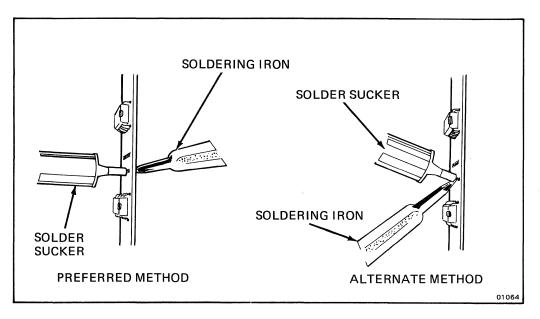

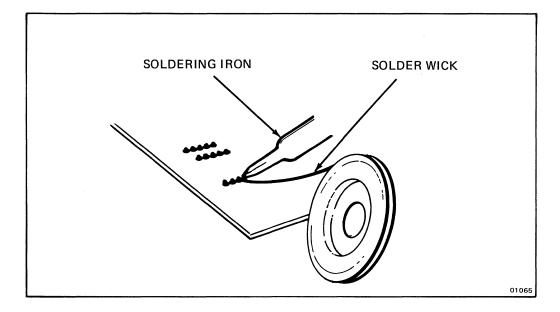

| Soldering Techniques and Equipment                  | 5-6                          |

| Removing Integrated Circuits                        | 5-7                          |

| TROUBLESHOOTING PROCEDURES                          | 5-11                         |

| Low-level Tests                                     | 5-13                         |

| Low-level Tests                                     | 5-15                         |

| System Power-Up Sequence                            | 5-17                         |

| Communications Power-Up Tests                       | 5-18                         |

| CPU Power-Up Tests                                  | 5-19                         |

| File Processor and Controller Power-Up              |                              |

| Tests                                               | 5-37                         |

| CPU and File Processor Communication                | 5-41                         |

| Interrupt Signals                                   | 5-41                         |

| Communication Protocol                              | 5-41                         |

| System-Confidence Tests                             | 5-43                         |

| Booting the SDX Disk                                | 5-43                         |

| Field-Service Tests                                 | 5-47                         |

| SDX Field Service Menu                              | 5-47                         |

| CPU Test Menu                                       | 5-52                         |

| File Processor and Controller Board Test            | ,<br>~                       |

|                                                     | 5-56                         |

|                                                     | 5-61                         |

| File Processor and Controller PCB                   | F (7                         |

| Circuit Level Test Menu                             | 5-6/                         |

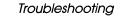

| Debugger Tests.                                     | 5-89                         |

| CPU Debugger Commands                               | 2-09                         |

| Communications Debugger Commands                    | E 07                         |

| (Software Mode)                                     | 5-91                         |

| Communciations Debugger Commands<br>(Hardware Mode) | 5-101                        |

|                                                     | דמדנ                         |

5

Table of Contents

#### **APPENDICES**

#### **A** JUMPERING

| INTRODU | CTIO | N.   | • • | •  | •   | •  | •  | • | • | • | • | • | • | • | • | • | • | A-3  |

|---------|------|------|-----|----|-----|----|----|---|---|---|---|---|---|---|---|---|---|------|

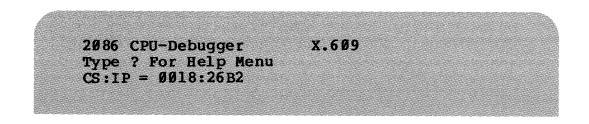

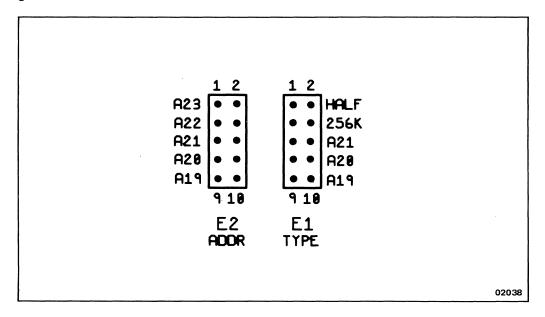

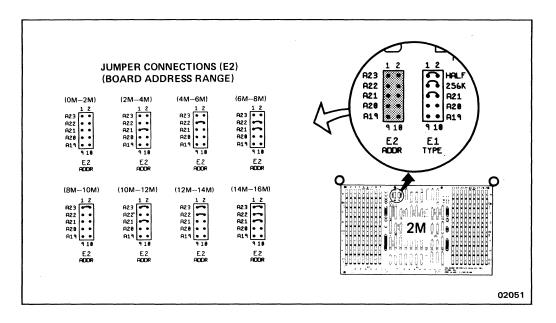

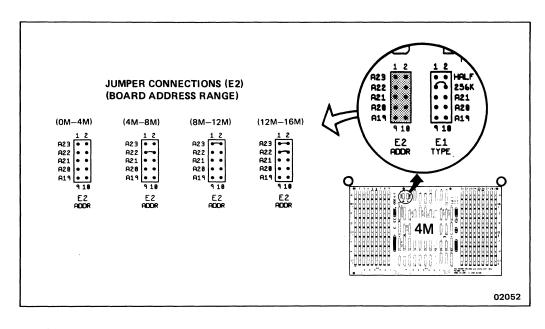

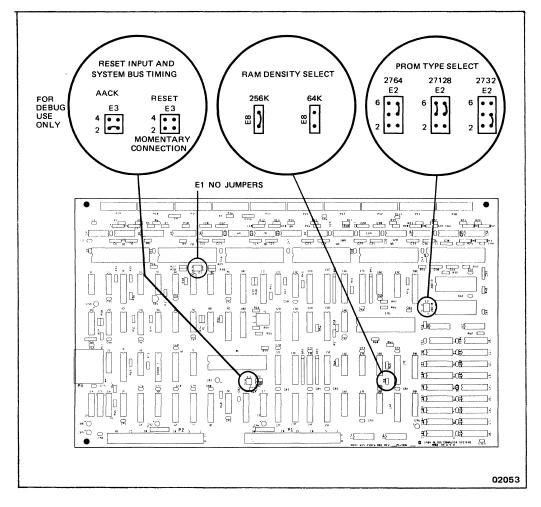

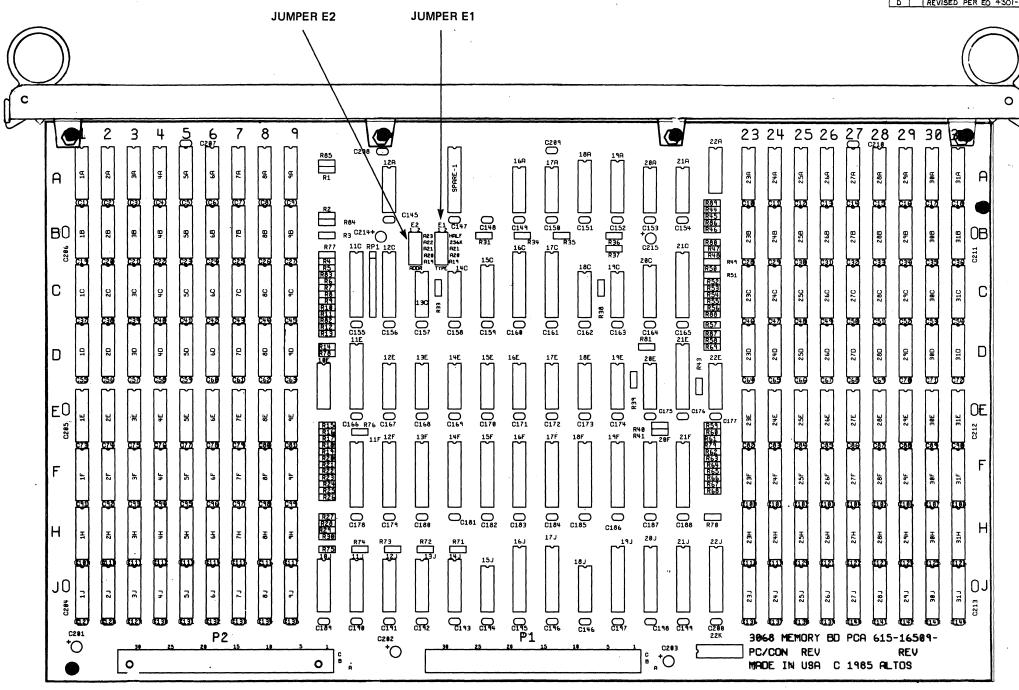

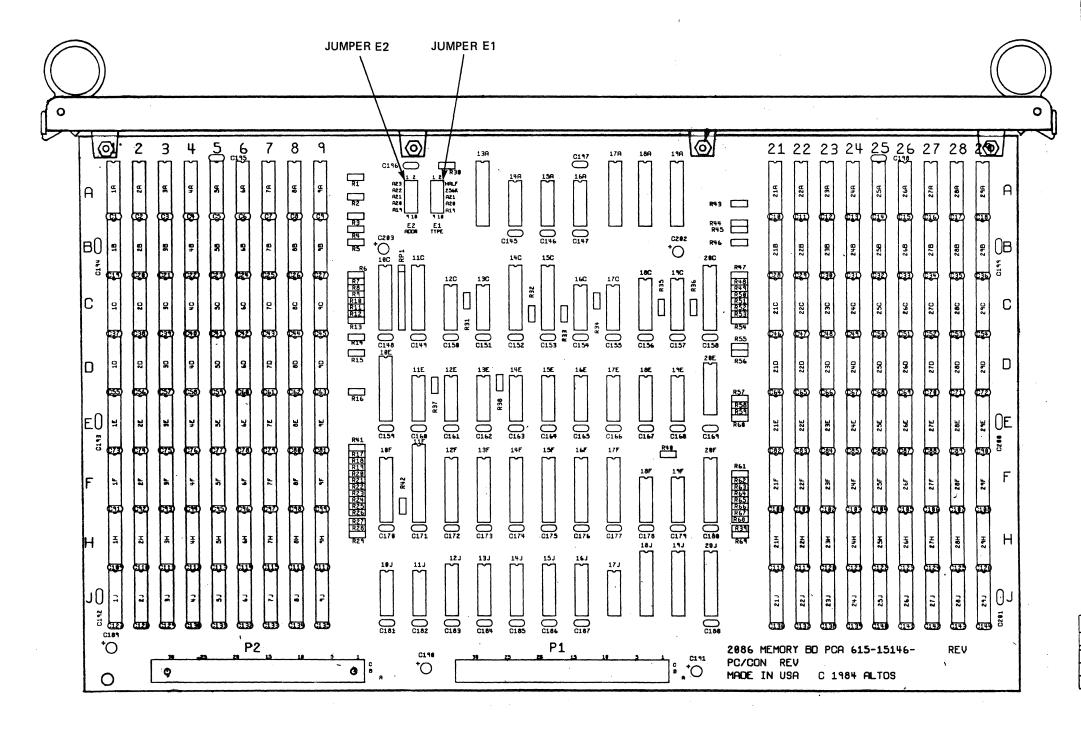

| MEMORY  | PCB  | JUMP | ERI | NG | •   | •  | •  | • | • | • | • | • | • | • |   | • | • | A-3  |

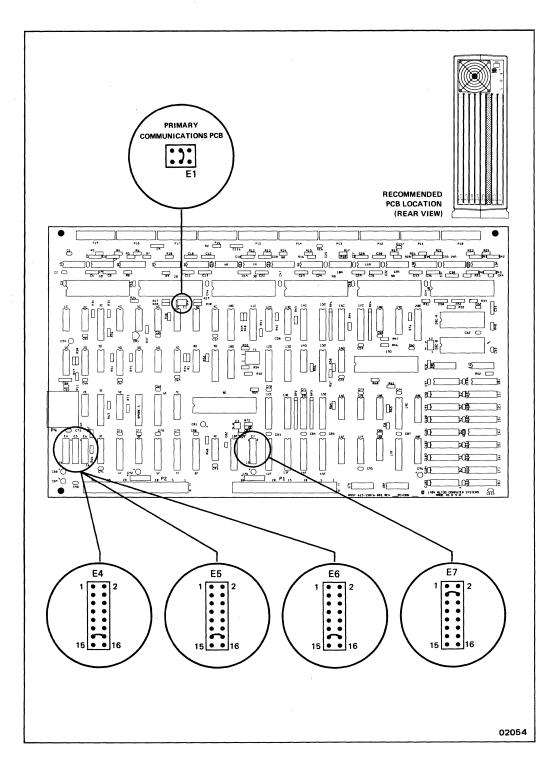

| COMMUNI | CATI | ONS  | PCB | Jl | JMP | ER | IN | G | • | • | • | • | • | • | • | • | • | A-12 |

### **B** STORAGE DEVICE SPECIFICATIONS

| INTRODUCTION              | • | • | • | •   | • | • | • | •   | • | B-3 |

|---------------------------|---|---|---|-----|---|---|---|-----|---|-----|

| CARTRIDGE TAPE DRIVE      | • | • | • | •   | • | • | • | •   | • | B-3 |

| Electrical Specifications | • | • | • | • . | • | • | • | •   | • | B-3 |

| FLOPPY DISK DRIVE         | • | • | • | •   | • | • | • | •   | • | B-4 |

| Electrical Specifications | • | • | • | •   | • | ٠ | • | . • | • | B-4 |

| HARD DISK DRIVE           |   |   |   |     |   |   |   |     |   |     |

| Electrical Specifications | • | • | • | •   | • | • | • | •   | • | B-6 |

### C UTILITY PROGRAMS

| IN            | TRO  | DDU        | CT  | ION | •   | •    | •   | •   | •   | •   | •   | •   | •   | •   | •          | •   | • | •   | • | • | • | C-3  |

|---------------|------|------------|-----|-----|-----|------|-----|-----|-----|-----|-----|-----|-----|-----|------------|-----|---|-----|---|---|---|------|

| BO            | OT   | ING        | T   | ΙE  | SD  | ΚI   |     | SK  | •   | •   | •   | ٠   | •   | •   | •          | •   | • | •   | • | • | • | C-3  |

| $\mathbf{FL}$ | OPI  | ΡY         | FOI | RMA | т.  |      | •   | •   | •   | ٠   | •   | •   | •   | •   | •          | •   | • | •   | • | • | • | C-6  |

| $\mathbf{FL}$ | OPI  | PY.        | COI | PY. | •   | •    | •   | •   | •   | •   | •   | •   |     | •   | •          | •   | • | •   | • | • | • | C-8  |

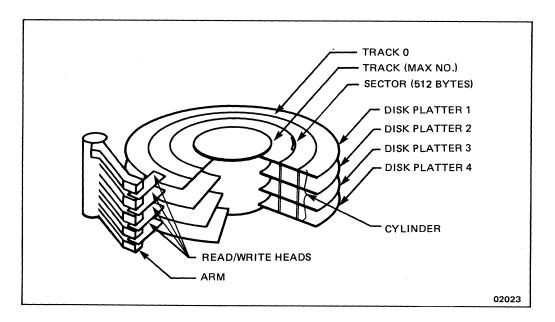

| WO            | RKJ  | ING        | W:  | ITH | ΗZ  | \RI  | וכ  | DIS | 5 K | Bł  | AD  | SI  | ECT | OF  | RS         | •   | • | •   | • | ٠ | • | C-12 |

|               | Te   | erm        | ind | 010 | gy  |      | •   | •   | •   | •   | •   | •   | •   | •   | •          | •   | • | •   | • | • | • | C-12 |

|               | De   | ete        | rm: | ini | ng  | tł   | ne  | Dr  | civ | ve  | Νı  | umb | ber | •   | •          | •   | • | •   | • | • | • | C-14 |

| DI            | S PI | <b>JAY</b> | ΗZ  | ARD | D]  | [S ] | X ( | 100 | NF: | IGI | JR  | AT: | ION | נ ו | <b>CAE</b> | BLE |   | •   | • | • | • | C-14 |

| SC            | AN   | HA         | RD  | DI  | SK  | FC   | )R  | BZ  | ٩D  | SI  | ECI | roi | RS  | •   | •          | •   | • | •   | • | • | • | C-16 |

| $\mathbf{FL}$ | AG   | HA         | RD  | DI  | SK  | Bł   | ٩D  | SE  | EC. | ΓOI | RS  | •   | •   | •   | •          | •   | • | •   | • | • | • | C-19 |

|               | Dr   | iv         | e S | Ser | ial | . 1  | Jur | nbe | er  | •   | •   | •   | •   | •   | •          | •   | • | •   | • | • | • | C-2Ø |

|               | Er   | ntr        | y I | lod | e.  | •    | ٠   | •   | •   | •   | •   | •   | •   | •   | •          | •   | • | •   | • | • | • | C-2Ø |

|               |      |            |     |     |     |      |     |     |     |     |     |     |     |     |            |     |   |     |   |   |   | C-24 |

| HA            | RD   | DI         | SK  | FO  | RMA | ΥT   | •   | •   | •   | •   | •   | •   |     | •   | •          | •   | • | , • | • | • | • | C-24 |

| RE            | CON  | IFI        | GUI | RE  | HAF | RD   | DI  | RIV | 7E  | •   | •   | •   | •   | •   | •          | •   | • | •   | • | • | • | C-26 |

#### D LOOPBACK CONNECTORS

| INTRODUCTION | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | D-3 | 3 |

|--------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|---|

|              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |   |

#### E ADJUSTMENT PROCEDURES

| TAPE PHASE | LOCK LOOP | ADJ USTMENT. | • • | • • | ••• E-3  | 1 |

|------------|-----------|--------------|-----|-----|----------|---|

| GLOSSARY   |           |              | ••  | ••  | •••• G-3 | 1 |

| INDEX      |           |              |     | • • | I-       | 1 |

## List of Illustrations

Figure Title

| 1-1<br>1-2<br>1-3                                                                   | Field Replaceable Units 1-12<br>Controls, Connectors, and Indicators . 1-14<br>Recommended Plug-In PCB Locations 1-16                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2-1                                                                                 | Maximum Overall Dimensions 2-9                                                                                                                                                                                                                                                                             |

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11<br>3-12 | 80286 Memory Map3-30Cache Memory Organization3-38Cache Memory Search3-40CPU PCB Timing Diagrams3-44Memory PCB Timing Diagrams3-60Local Memory Map3-67System Memory Page Register3-69Local I/O Map3-71DMA Page Register Block Diagram3-78Communications PCB Timing Diagrams3-958086 Memory Address Map3-108 |

| 4-1                                                                                 | 115/230 VAC Selection (Main Power                                                                                                                                                                                                                                                                          |

| 4-2<br>4-3                                                                          | Supply)                                                                                                                                                                                                                                                                                                    |

| 4-4<br>4-5<br>4-6<br>4-7                                                            | Removing/Replacing the Bottom Filter . 4-9<br>Cleaning the Tape Head 4-10<br>Removing/Replacing the Front Panel 4-14<br>Removing/Replacing the Side Panels                                                                                                                                                 |

Figure Title

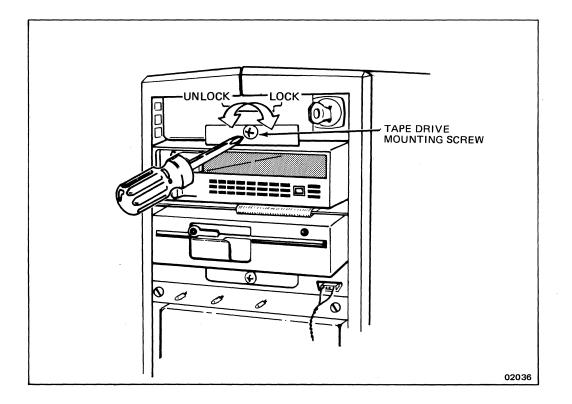

| 4-8          | Locking/Unlocking the Tape Drive                                     |       |

|--------------|----------------------------------------------------------------------|-------|

|              |                                                                      | 4-16  |

| 4-9          |                                                                      | 4-17  |

| 4-10         | Locking/Unlocking the Floppy Drive                                   |       |

|              |                                                                      | 4-19  |

| 4-11         |                                                                      | 4-20  |

| 4-12         | Removing/Replacing the Hard Disk                                     |       |

|              |                                                                      | 4-23  |

| 4-13         | Unlocking/Locking the Hard Disk Drive                                |       |

|              |                                                                      | 4-24  |

| 4-14         |                                                                      | 4-26  |

| 4-15         | Removing/Replacing the Main Power                                    |       |

| 4 10         |                                                                      | 4-28  |

| 4-16         |                                                                      | 4-29  |

| 4-17         | Removing/Replacing the Clock Battery .                               |       |

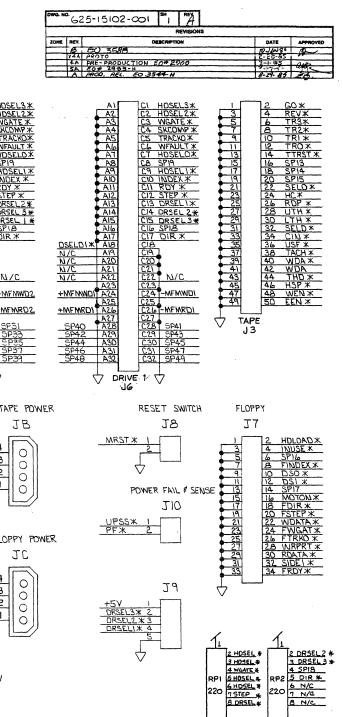

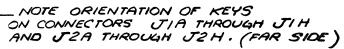

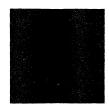

| 4-18         | Cable Interconnections                                               |       |

| 1 10         |                                                                      | 1 00  |

| 5-1          | Removing ICs (Cut Pin Method)                                        | 5-8   |

| 5-2          |                                                                      | 5-9   |

| 5-3          | Removing Solder from Plated-Through                                  | 5 5   |

| 5.5          |                                                                      | 5-1Ø  |

| 5-4          | Removing Solder from Lead Connection                                 | 5 20  |

| 5 1          |                                                                      | 5-11  |

| 5-5          | System Power-Up Test Sequence Block                                  | •     |

|              |                                                                      | 5-16  |

|              |                                                                      | • -•  |

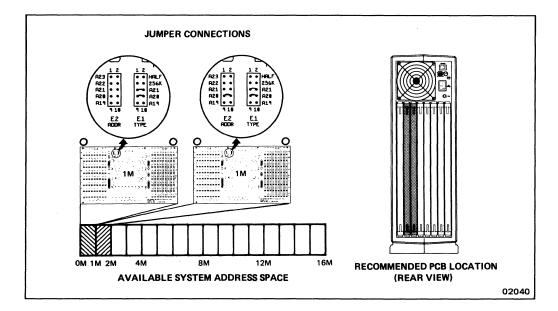

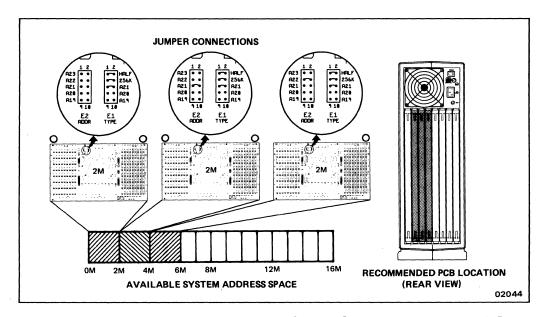

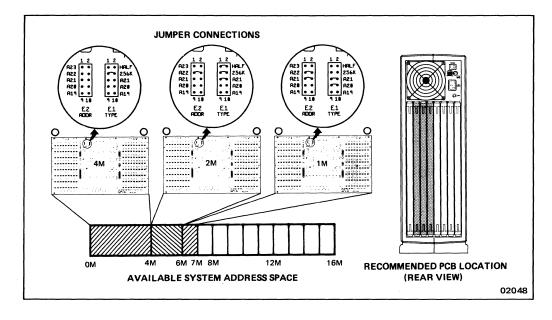

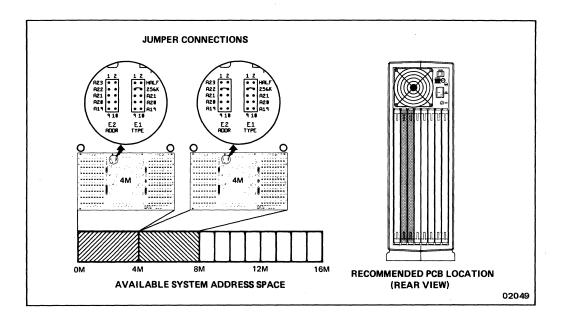

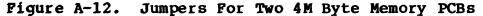

| A-1          | Memory PCB Jumper-Pin Connectors                                     | A-4   |

| A-2          | Jumpers for One 1M Byte Memory PCB                                   |       |

| A-3          | Jumpers for Two 1M Byte Memory PCBs                                  |       |

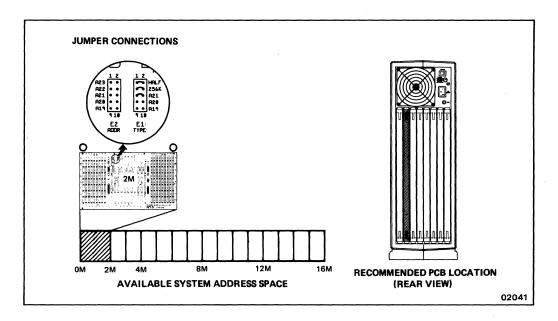

| A-4          | Jumpers for One 2M Byte Memory PCB                                   |       |

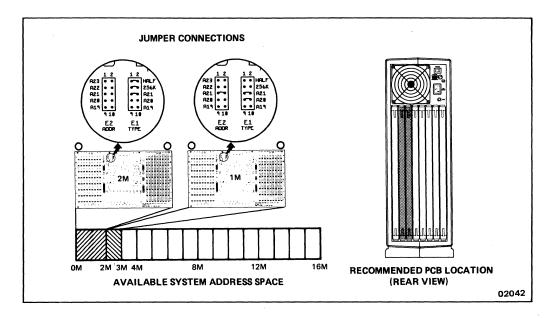

| A-5          | Jumpers for 2M and 1M Byte                                           |       |

|              | Memory PCBs                                                          | A-6   |

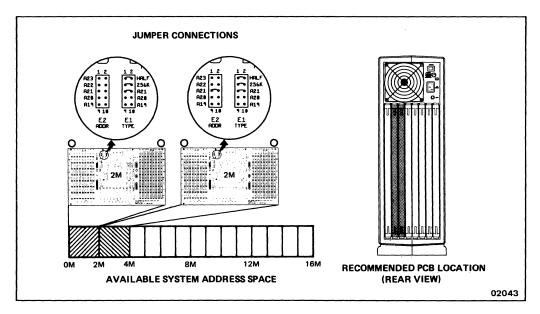

| A-6          | Jumpers for Two 2M Byte Memory PCBs.                                 |       |

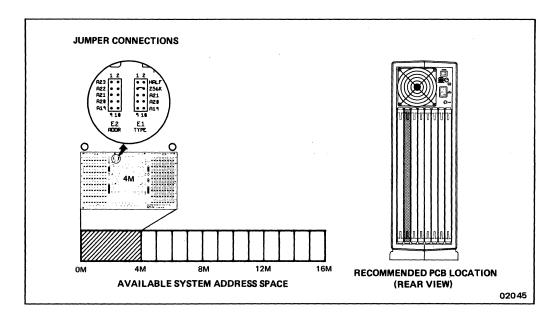

| A-7          | Jumpers for Three 2M Byte Memory PCBs.                               |       |

| A-8          | Jumpers for One 4M Byte Memory PCB                                   | A-8   |

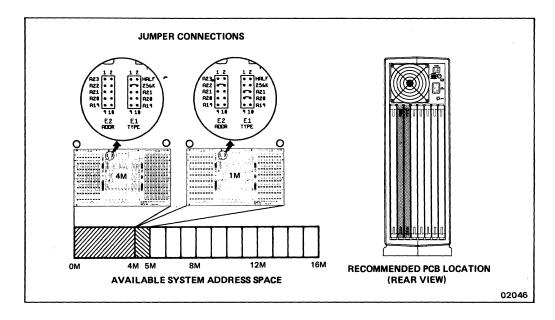

| A-9          | Jumpers for 4M and 1M Byte                                           | no    |

|              | Memory PCBs                                                          | A-8   |

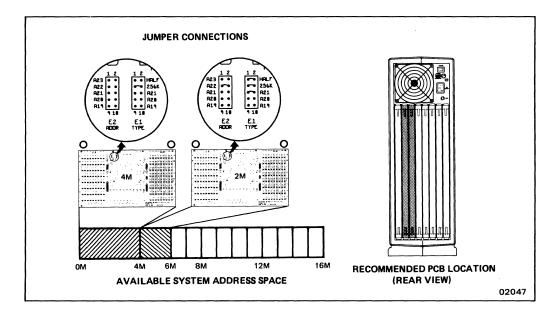

| A-10         | Jumpers for 4M and 2M Byte                                           |       |

| ~ <b>.</b> . | Memory PCBs                                                          | A-9   |

| A-11         | Jumpers for 4M, 2M, and 1M Byte                                      | A 9   |

| ~ ~ ~        | Memory PCBs                                                          | A-9   |

| A-12         |                                                                      |       |

| A-12<br>A-13 | Jumpers for Two 4M Byte Memory PCBs<br>Reference Jumpers for 1M Byte | 4 T.Q |

| M-13         |                                                                      | A-10  |

|              | Memory PCBs                                                          | Y-TN  |

Table of Contents

| Figure | Title |

|--------|-------|

|--------|-------|

| A-14 | Reference Jumpers for 2M Byte            |

|------|------------------------------------------|

|      | Memory PCBs                              |

| A-15 | Reference Jumpers for 4M Byte            |

|      | Memory PCBs                              |

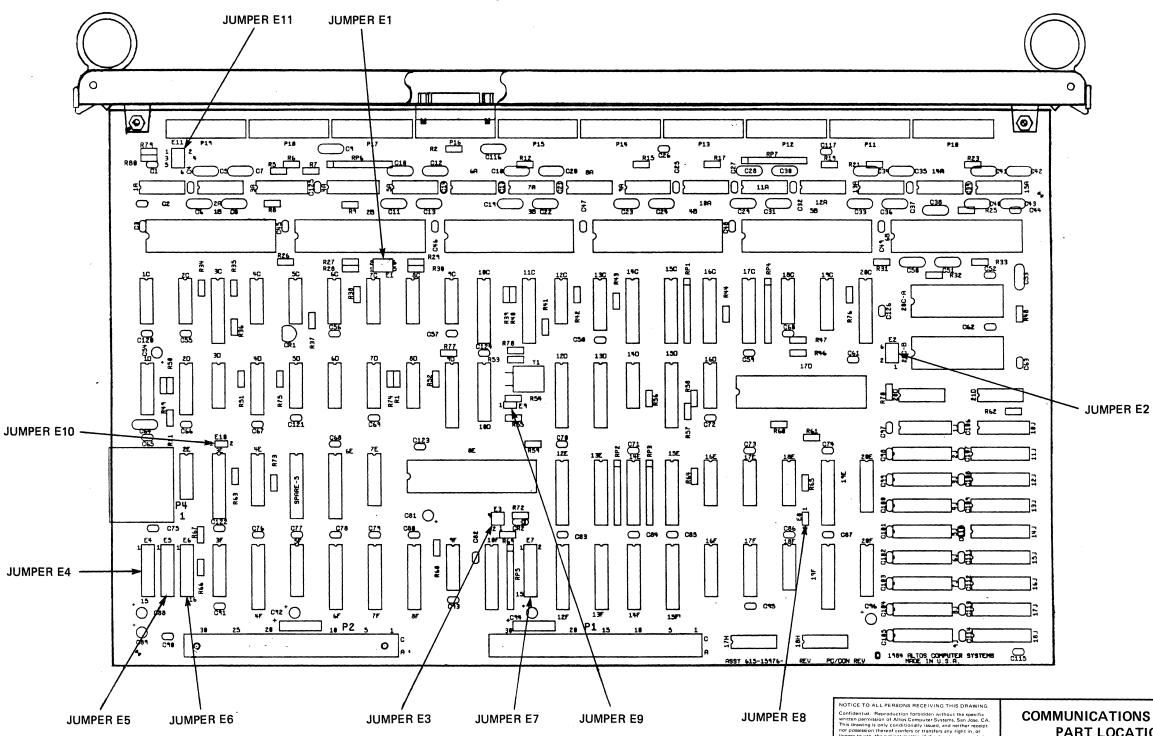

| A-16 | Jumpers for SIO Communications PCBs      |

|      | (Factory Setting)                        |

| A-17 | Jumpers for SIO Communications           |

|      | COMM Ø                                   |

| A-18 | Jumpers for SIO Communications           |

|      | COMM 1                                   |

| A-19 | Jumpers for SIO Communications           |

| A-20 | COMM 2                                   |

| A-20 | Jumpers for SIO Communications<br>COMM 3 |

|      | COMM 5                                   |

| C-1  | Hard-Disk Terminology                    |

| 0 1  |                                          |

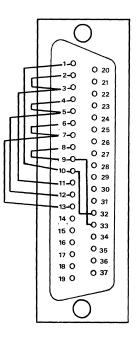

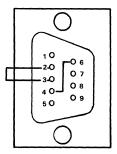

| D-1  | Parallel Printer Port Loopback           |

|      | Connector                                |

| D-2  | Serial Communications (SIO) Loopback     |

|      | Connector                                |

|      |                                          |

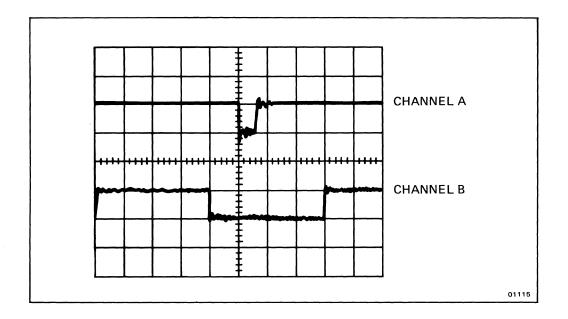

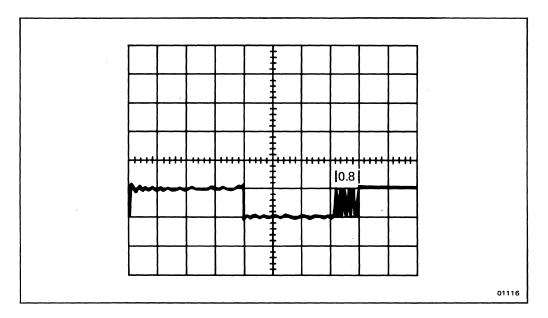

| E-1  | Channel A and B Waveforms E-2            |

| E-2  | Channel B Waveform                       |

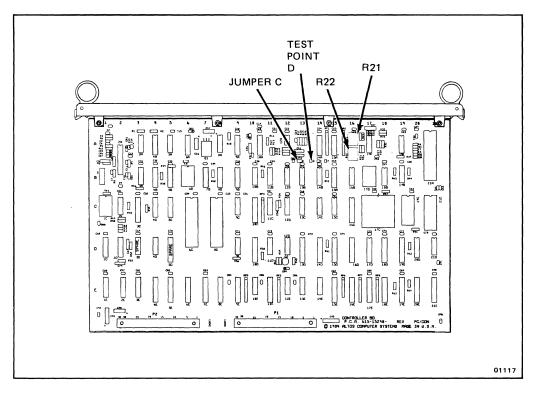

| E-3  | Jumper and Test Point Locations          |

|      | (Controller PCB)                         |

## List of Tables

| Table | Title                                |      |

|-------|--------------------------------------|------|

| 2-1   | Electrical Specifications            |      |

| 2-2   | Environmental Specifications         | 2-8  |

| 2-3   | Physical Specifications              |      |

| 3-1   | Input Status-Port Bit Definitions    | 3-33 |

| 3-2   | Output-Latch Bit Definitions         | 3-34 |

| 3-3   | Interrupt Request Levels             |      |

| 3-4   | Translation-Table Addresses          |      |

| 3-5   | Translation-Table Bit Definitions    |      |

| 3-6   | Tag-Memory Bit Definitions           |      |

| 3-7   | Jumper Descriptions                  |      |

| 3-8   | I/O Port Assignments                 |      |

| 3-9   | Communications Controller References |      |

Table Title

| 3-1Ø | Asynchronous-Channel Handshake Lines . | 3-81  |

|------|----------------------------------------|-------|

| 3-11 | Synchronous-Channel Handshake Lines    | 3-82  |

| 3-12 | CIO Port Descriptions                  | 3-86  |

| 3-13 | Interrupt Daisy Chain                  |       |

| 3-14 | Jumper Descriptions                    |       |

| 3-15 | Connector/Controller Configuration     |       |

| 3-16 | Connector Pin Assignments              | 3-94  |

| 3-17 |                                        | 3-110 |

| 3-18 | Control and Status Bit Assignments     | 3-110 |

| 3-19 | Nonmaskable Interrupts                 | 3-113 |

| 3-20 | Interrupt controller Port Assignments. | 3-114 |

| 3-21 | Maskable Interrupts                    | 3-114 |

| 3-22 | DMA Controller Port Assignments        | 3-118 |

| 3-23 | Printer Port Assignments               | 3-123 |

| 3-24 | Printer Status Port Bit Assignments    | 3-123 |

| 3-25 | SCSI Controller Port Assignments       | 3-126 |

| 3-26 | Hard Disk Controller Port Assignments. |       |

| 3-27 | Hard Disk Controller Bit Assignments . | 3-139 |

| 3-28 | Floppy Disk Controller Port            |       |

|      |                                        | 3-141 |

| 3-29 | Floppy Disk Control-Register Bit       |       |

|      |                                        | 3-141 |

| 3-30 | Tape-Controller Port Assignments       |       |

| 3-31 | Tape-Controller Bit Assignments        | 3-144 |

| 5-1  | Low-Level Trouble Analysis             | 5-13  |

| 5-2  | Power Supply DC Voltages               |       |

| 5-3  | CPU Failure Status at Output Latch     |       |

|      | Port                                   | 5-82  |

| 5-4  | Hard Disk Controller Error             |       |

|      | Register Bit Descriptions              | 5-28  |

| 5-5  | Hard Disk Controller Status            |       |

|      | Register Bit Descriptions              | 5-29  |

| 5-6  | Floppy Disk Controller Status          |       |

|      | Register Ø Bit Descriptions            | 5-32  |

| 5-7  | Floppy Disk Controller Status          |       |

|      | Register 1 Bit Descriptions            | 5-33  |

| 5-8  | Floppy Disk Controller Status          |       |

|      | Register 2 Bit Descriptions            | 5-35  |

| 5-9  | Floppy Disk Controller Status          |       |

|      | Register 3 Bit Descriptions            | 5-36  |

| 5-10 | SDX Trouble Analysis                   | 5-72  |

|      |                                        |       |

| A-1  | SIO PCB Jumper Descriptions            | A-12  |

Table of Contents

Table Title B-1 Cartridge Tape Drive Specifications. . B-4 Floppy Disk Drive Specfications. . . B-5 B-2 50M Byte Hard Disk Drive B-3 B-4 80M Byte Hard Disk Drive Specifications. . . . . . ...B-5 . B-5 190M Byte Hard Disk Drive

## Chapter 1 System Overview

| Characteristics                                                                                                                                                                                                                                                                                                                                                   | SYSTEM | I DES | CRI  | PT                 | ION           | ۱.  | •         | •  | •   | •  | •  | •   | •  | •  | •  | •  | • | • | • | • | • | 1-3  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|------|--------------------|---------------|-----|-----------|----|-----|----|----|-----|----|----|----|----|---|---|---|---|---|------|

| Configurations                                                                                                                                                                                                                                                                                                                                                    | Cha    | iract | eri  | st:                | ics           | 3.  | •         | •  | •   | •  | •  | •   | •  | •  | •  | •  | • | • | • | • | • | 1-3  |

| Configurations                                                                                                                                                                                                                                                                                                                                                    | Arc    | hite  | ctu  | ire                | •             | •   | •         | •  | •   | •  | •  | •   | •  | •  | •  | •  | • | • | • | • | • | 1-3  |

| Communications                                                                                                                                                                                                                                                                                                                                                    |        |       |      |                    |               |     |           |    |     |    |    |     |    |    |    |    |   |   |   |   |   |      |

| Diagnostics                                                                                                                                                                                                                                                                                                                                                       |        |       |      |                    |               |     |           |    |     |    |    |     |    |    |    |    | • | • | • | • | • | 1-4  |

| Power-Up Tests                                                                                                                                                                                                                                                                                                                                                    | Con    | muni  | cat  | io                 | ns            | •   | •         | •  | •   | •  | •  | •   | •  | •  | •  | •  | • | • | • | • | • | 1-5  |

| Power-Up Tests                                                                                                                                                                                                                                                                                                                                                    | Dia    | ignos | tic  | s.                 | •             | •   | •         | •  | •   | •  | •  | •   | •  | •  | •  | •  | • | • | • | • | • | 1-5  |

| Field-Service Diagnostics1-6Hardware1-7System Bus1-7Central Processing Unit (CPU) PCB1-8Memory PCB1-8Communications PCB1-8File Processor PCB1-9Controller PCB1-10FIELD REPLACEABLE UNITS1-11CONTROLS, CONNECTORS, AND INDICATORS1-12Front Panel1-13PLUG-IN PRINTED CIRCUIT BOARD LOCATIONS1-15SYSTEM SOFTWARE1-15Operating System Program1-17Disk Performance1-17 |        | Powe  | r-U  | lp !               | Tes           | sts |           |    | •   | •  | •  | •   | •  | •  | •  | •  | • | • | • | • | • | 1-6  |

| Field-Service Diagnostics1-6Hardware1-7System Bus1-7Central Processing Unit (CPU) PCB1-8Memory PCB1-8Communications PCB1-8File Processor PCB1-9Controller PCB1-10FIELD REPLACEABLE UNITS1-11CONTROLS, CONNECTORS, AND INDICATORS1-12Front Panel1-13PLUG-IN PRINTED CIRCUIT BOARD LOCATIONS1-15SYSTEM SOFTWARE1-15Operating System Program1-17Disk Performance1-17 |        | User  | Sy   | st                 | em-           | -Co | nf        | iċ | len | ce | I  | 'es | ts | •  | •  | •  | • | • | • | • | • | 1-6  |

| Hardware1-7System Bus.1-7Central Processing Unit (CPU) PCB1-8Memory PCB.1-8Communications PCB.1-8File Processor PCB.1-9Controller PCB.1-10FIELD REPLACEABLE UNITS1-11CONTROLS, CONNECTORS, AND INDICATORS.1-12Front Panel.1-13Rear Panel1-13PLUG-IN PRINTED CIRCUIT BOARD LOCATIONS1-15SYSTEM SOFTWARE1-15Operating System Program1-17Disk Performance.1-17       |        | Fiel  | d-S  | ler                | vic           | ce  | Di        | ag | no  | st | ic | S   | •  | •  | •  | •  | • | • | • | • | • | 1-6  |

| System Bus.1-7Central Processing Unit (CPU) PCB1-8Memory PCB.1-8Communications PCB.1-8File Processor PCB.1-9Controller PCB.1-10FIELD REPLACEABLE UNITS1-11CONTROLS, CONNECTORS, AND INDICATORS.1-12Front Panel.1-13Rear Panel1-15SYSTEM SOFTWARE1-15Operating System Program1-15Address Translation1-17Disk Performance.1-17                                      | Har    |       |      |                    |               |     |           |    |     |    |    |     |    |    |    |    |   |   |   |   |   |      |

| Memory PCB.1-8Communications PCB.1-8File Processor PCB.1-9Controller PCB.1-10FIELD REPLACEABLE UNITS1-11CONTROLS, CONNECTORS, AND INDICATORS.1-12Front Panel.1-13Rear Panel1-13PLUG-IN PRINTED CIRCUIT BOARD LOCATIONS1-15SYSTEM SOFTWARE1-15Operating System Program1-17Disk Performance.1-17                                                                    |        | Syst  | em   | Bu                 | s.            | •   | •         | •  | •   | •  | •  | •   | •  | •  | •  | •  | • | • | • | • | • | 1-7  |

| Communications PCB                                                                                                                                                                                                                                                                                                                                                |        | Cent  | ral  | . P:               | roc           | ces | si        | ng | Ū   | ni | t  | (C  | PU | )  | PC | В  | • | • | • | • | • | 1-8  |

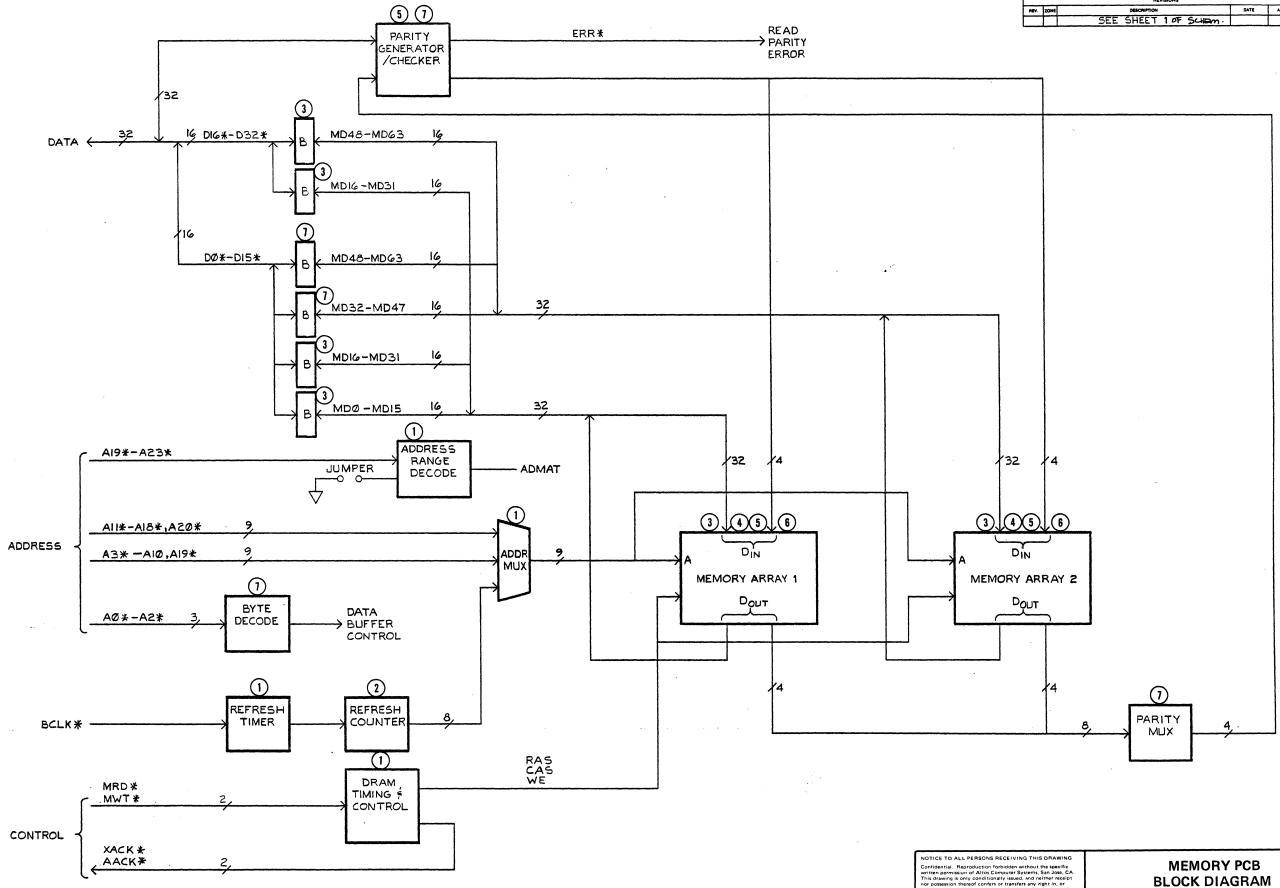

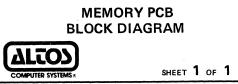

| Communications PCB                                                                                                                                                                                                                                                                                                                                                |        | Memo  | ry   | PC                 | Β.            | •   | •         | •  | •   | •  | •  | •   | •  | •  | •  | •  | • | • | • | • | • | 1-8  |

| Controller PCB                                                                                                                                                                                                                                                                                                                                                    |        | Comm  | uni  | ca                 | tic           | ons | E         | CE |     | •  | •  | •   | •  | •  | •  | •  | • | • | • | • | • | 1-8  |

| FIELD REPLACEABLE UNITS1-11CONTROLS, CONNECTORS, AND INDICATORS1-12Front Panel1-13Rear Panel1-13PLUG-IN PRINTED CIRCUIT BOARD LOCATIONS1-15SYSTEM SOFTWARE1-15Operating System Program1-15Address Translation1-17Disk Performance1-17                                                                                                                             |        | File  | Pr   | 000                | ess           | sor | F         | CE |     | •  | •  | •   | •  | •  | •  | •  | • | • | • | • | • | 1-9  |

| FIELD REPLACEABLE UNITS1-11CONTROLS, CONNECTORS, AND INDICATORS1-12Front Panel1-13Rear Panel1-13PLUG-IN PRINTED CIRCUIT BOARD LOCATIONS1-15SYSTEM SOFTWARE1-15Operating System Program1-15Address Translation1-17Disk Performance1-17                                                                                                                             |        | Cont  | rol  | <b>le</b> :        | r I           | PCB | •         | •  | •   | •  | •  | •   | •  | •  | •  | •  | • | • | • | • | • | 1-1Ø |

| Front Panel.1-13Rear Panel1-13PLUG-IN PRINTED CIRCUIT BOARD LOCATIONS1-15SYSTEM SOFTWARE1-15Operating System Program1-15Address Translation1-17Disk Performance1-17                                                                                                                                                                                               | FIELD  | REPL  | ACE  | AB                 | $\mathbf{LE}$ | UN  | <b>II</b> | S  | •   | •  | •  | •   | •  | •  | •  | •  | • | • | • | • | • | 1-11 |

| Rear Panel1-13PLUG-IN PRINTED CIRCUIT BOARD LOCATIONS1-15SYSTEM SOFTWARE1-15Operating System Program1-15Address Translation1-17Disk Performance1-17                                                                                                                                                                                                               |        |       |      |                    |               |     |           |    |     |    |    |     |    | RS | •  | •  | • | • | • | • | • | 1-12 |

| Rear Panel1-13PLUG-IN PRINTED CIRCUIT BOARD LOCATIONS1-15SYSTEM SOFTWARE1-15Operating System Program1-15Address Translation1-17Disk Performance1-17                                                                                                                                                                                                               | Fro    | ont P | ane  | 1.                 | •             | •   | •         | •  | •   | •  | •  | •   | •  | •  | •  | •  | • | • | • | • | • | 1-13 |

| SYSTEM SOFTWARE                                                                                                                                                                                                                                                                                                                                                   |        |       |      |                    |               |     |           |    |     |    |    |     |    |    |    |    |   |   |   |   | • | 1-13 |

| Operating System Program                                                                                                                                                                                                                                                                                                                                          | PLUG-1 | N PR  | INT  | ED                 | CI            | RC  | UI        | T  | BC  | AR | D  | гo  | CA | TI | ON | IS | • | • | • | • | • | 1-15 |

| Address Translation 1-17<br>Disk Performance                                                                                                                                                                                                                                                                                                                      | SYSTEM | I SOF | TW A | RE                 | •             | •   | •         | •  | •   | •  | •  | •   | •  | •  | •  | •  | • | • | • | • | • | 1-15 |

| Address Translation 1-17<br>Disk Performance                                                                                                                                                                                                                                                                                                                      | Ope    | rati  | ng   | Sya                | ste           | m   | Pr        | og | ra  | m  | •  | •   | •  | •  | •  | •  | • | • | • | • | • | 1-15 |

|                                                                                                                                                                                                                                                                                                                                                                   | _      | Addr  | ess  | $\mathbf{\bar{T}}$ | rar           | nsl | at        | ic | n   | •  | •  | •   | •  | •  | •  | •  | • | • | • | • | • | 1-17 |

| Corial Dart Darformance                                                                                                                                                                                                                                                                                                                                           |        | Disk  | Pe   | rfe                | orn           | nan | ce        | •  | •   | •  | •  | •   | •  | •  | •  | •  | • | • | • | • | • | 1-17 |

| Serial Port Performance 1-17                                                                                                                                                                                                                                                                                                                                      |        | Seri  | al   | Pop                | rt            | Pe  | rf        | or | ma  | nc | e  | •   | •  | •  | •  | •  | • | • | • | • | • | 1-17 |

| Compatibility                                                                                                                                                                                                                                                                                                                                                     |        | Comp  | ati  | bi]                | lit           | y   | •         | •  | •   | •  | •  | •   | •  | •  | •  | •  | • | • | • | • | • | 1-17 |

| Diagnostics                                                                                                                                                                                                                                                                                                                                                       |        | Diag  | nos  | ti                 | CS            | .•  | •         | •  | •   | •  | •  | •   | •  | •  | •  | •  | • | • | • | • | • | 1-18 |

## SYSTEM DESCRIPTION

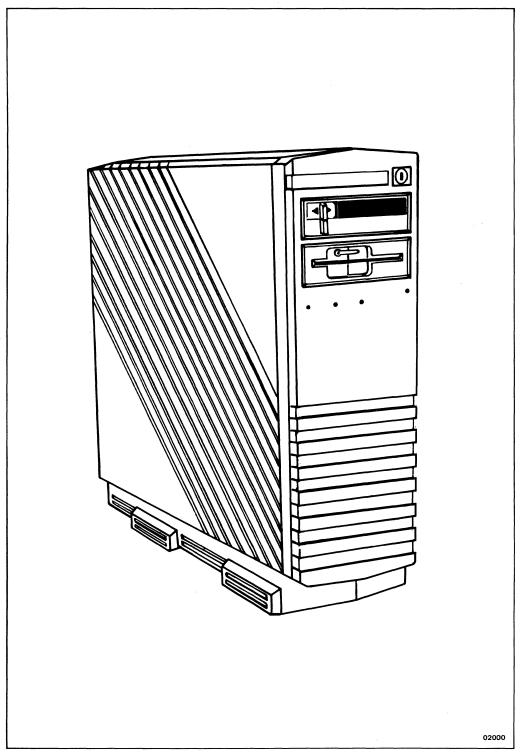

The Altos 1086/2086 Computer System is a floor-standing computer designed for general processing, office automation, and network fileserver applications. The system contains a CPU, system memory, I/O connections, mass storage, streaming tape backup, and a floppy disk drive.

## **Characteristics**

The following are some of the main characteristics of the 1086/2086:

- exceptional modularity for easy system expansion

- 8 MHz Intel 80286 main microprocessor

- optional high-speed Intel 80287 floating-point processor

- up to 451M bytes of formatted internal hard disk storage

- up to 8M bytes of RAM system memory

- 60M byte streaming cartridge tape drive

- storage expansion beyond 451M bytes via a small computer system interface (SCSI) channel. (-002 version of file processor subsystem only.)

- high-speed 32-bit expanded Multibus[tm]

- remote diagnostics (with optional modem) for rapid fault isolation to field replaceable units

## Architecture

The modular system architecture allows for convenient service. The printed circuit boards (PCBs) are easily removed or replaced without disassembling the system.

#### System Overview

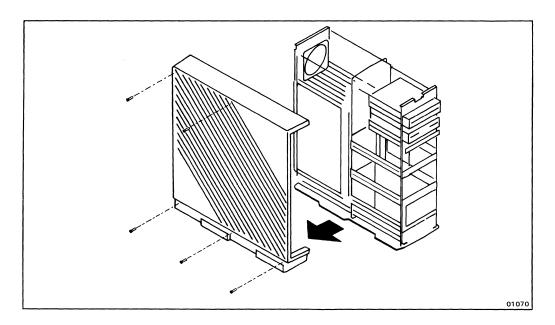

The cartridge tape, floppy disk, and hard disk drive mass storage subassemblies are easily installed or replaced by removing the front panel and sliding the subassemblies in or out of the chassis. The three available hard disk drive subassemblies plug directly into the backplane.

The system can contain up to eight plug-in PCB subsystems (five PCBs are used for a minimum lØ-user system) and five magnetic media storage subassemblies. All of the plug-in PCBs slide into the back of the chassis and connect to the system backplane PCB located in the center of the chassis. The mass storage subassemblies slide into the front of the chassis and also connect to the backplane PCB. The backplane PCB serves as the medium for data interchange between the processors, system memory, and mass storage subassemblies.

## **Configurations**

The 1086/2086 system can be configured in a variety of ways. The smallest possible configuration (or minimum system) could be made with 1M byte of random access memory (RAM), 10 RS-232 ports, a 50M byte hard disk drive, and a 1.6M byte floppy disk drive. More system memory, hard disk capacity, and RS-232 ports can be added.

A larger system configured to support 20 or 30 users could contain a 2M byte or 4M byte memory PCB, two or three 10-port communications PCBs, a 190M byte hard disk drive, a 1.6M byte floppy disk drive, and a 60M byte cartridge streaming tape drive.

## Networking

The 1086/2086 hardware supports local area networking (LAN). The networking hardware runs at two speeds: 750K and 1.4M bits per second. The slower speed allows the 1086/2086 to talk to Altos 186, 486, 586/586T, and 986/986T networks. The higher speed allows the 1086/2086 to talk to other 1086/2086 systems. A simple low-cost, twisted-pair, RS-422 interface is used at the hardware level. The 1086/2086 uses the same type of WorkNet software that runs on most Altos systems. The WorkNet software allows transparent remote file access and remote processor execution.

### Communications

The 1086/2086 system supports several serial communications protocols which are down-loaded to the serial communications PCB. These communications protocols are run by the 8086 microprocessor on the communications PCB, which removes this burden from the main CPU. By using multiple communications PCBs, multiple communications protocols can be run at the same time. The software for running the communications protocols is downloaded into the RAM on the communications PCB.

The software for 3270, 3780, X.25, and SNA protocols will run on the 1086/2086. The system is capable of supporting asynchronous modems for dial-up data base services or offsite communications and bisynchronous modems for IBM 3780 emulation. WorkNet can also be supported through one port via a software command communicating at 1.4M bits per second or 750K bits per second (used to connect compatibles to Altos processors). The optional communications PCB subsystem, configured with 32K bytes of RAM, supports certified X.25 or IBM/SNA software protocols.

#### Diagnostics

The 1086/2086 performs three major categories of diagnostic tests. The first category is the built-in hardware tests contained in the power-up monitor program. (Refer to **System Software** in this chapter for additional diagnostics information.)

The second category of tests is the user systemconfidence tests. The final category is the fieldservice diagnostics (SDX) tests which can be run either from a floppy disk or remotely with the optional communications modem. (Refer to the **1086/2086 Remote Diagnostics** manual for remote diagnostics information.)

#### **Power-Up Tests**

The power-up tests are ROM-based and reside on the CPU, communications, and file processor PCBs. These power-up tests are always performed when power is applied to the system to check the minimum hardware configuration on its particular PCB, identify any missing or failed assemblies, and then confirm communication with the system. These tests are always performed on power-up.

The CPU power-up tests include programmable read-only memory (PROM), cache memory, translation and tag RAM memory, clock, floating-point numeric processor, interrupt, and system bus checks. The file processor power-up tests include local RAM and PROM, interval timer, system bus, DMA controller, and magnetic media controller checks. The communications PCB power-up tests consist of local RAM and PROM, I/O integrated circuits, DMA controller, interrupt, and system bus checks.

#### **User System-Confidence Tests**

The user system-confidence tests allow a system user to test the functionality of the system. These tests are menu driven. A full set of tests can be run with only one or two keystrokes on the system console. More detailed and flexible tests are also available for the service technician. A full set of system utilities for handling system configuration and mass storage devices is included.

#### Field Service Diagnostics

The field-service diagnostics can be run either from the SDX floppy disk supplied with the system or from a remote service depot through the optional communications modem. The principle advantage of the remote method of performing diagnostics is that only one PCB (one of the communications PCBs) needs to be working in order to begin testing. In most multi-board systems, the CPU PCB, system memory PCB, controller PCB, and communications PCB must be working before diagnostic testing can start. In the 1086/2086, the communications (SIO) PCB contains a full 16-bit microprocessor that acts as a diagnostic controller on the system bus.

Thus, each PCB can be called up and tested separately, or the full system can be enabled and exercised to isolate and identify failures for repair or replacement.

Another advantage of the remote diagnostic method is that the tests are run by highly trained technicians at the main Altos facility or at designated service centers. The full expertise of Altos is available on the spot to evaluate a problem without waiting for a service technician to arrive.

The remote facility can call up specific PCB monitors or debuggers, or transmit the latest circuit-level diagnostics, with no interaction required from the user. The failed unit can, upon isolation, be easily replaced by the user or by the system administrator.

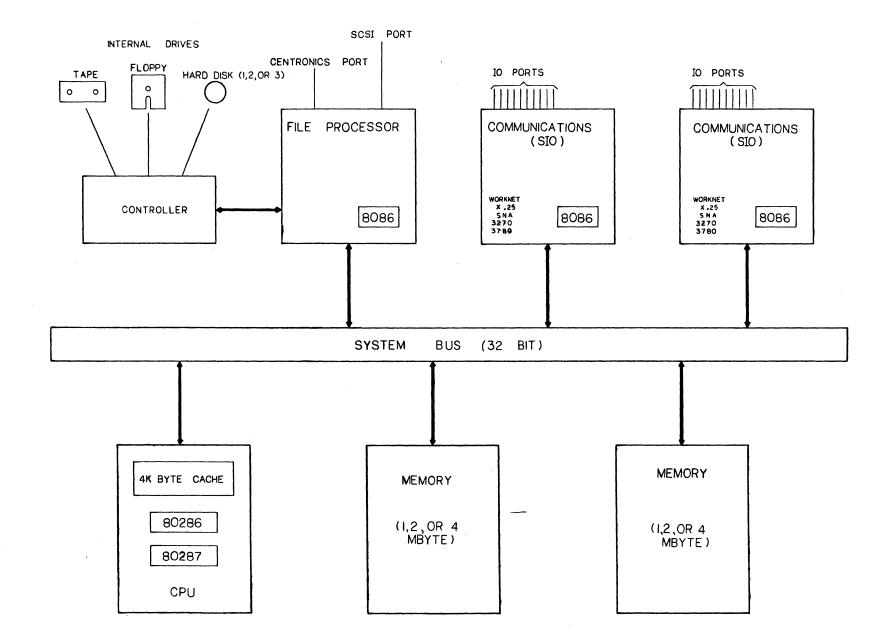

### Hardware

The system hardware is partitioned so that each major function is performed by a single PCB. The five required PCBs for the minimum 10-user system are the CPU, system memory, communications, file processor, and controller. All of these PCBs, except the controller, connect to the 32-bit system bus. Refer to Chapter 3 for a description of the system hardware operation.

#### System Bus

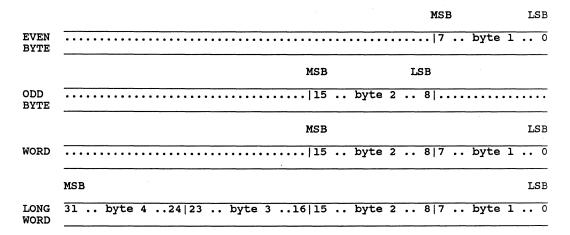

The system bus is asynchronous and has 32 data lines and 24 address lines that can support a maximum data transfer rate of 30M bytes per second. Up to 16M bytes of RAM can be accessed and data transfers can be 8-, 16-, or 32-bits wide. The system bus supports one of up to eight bus masters. All the processors in the system communicate with each other via system memory and I/O channel attentions and interrupts.

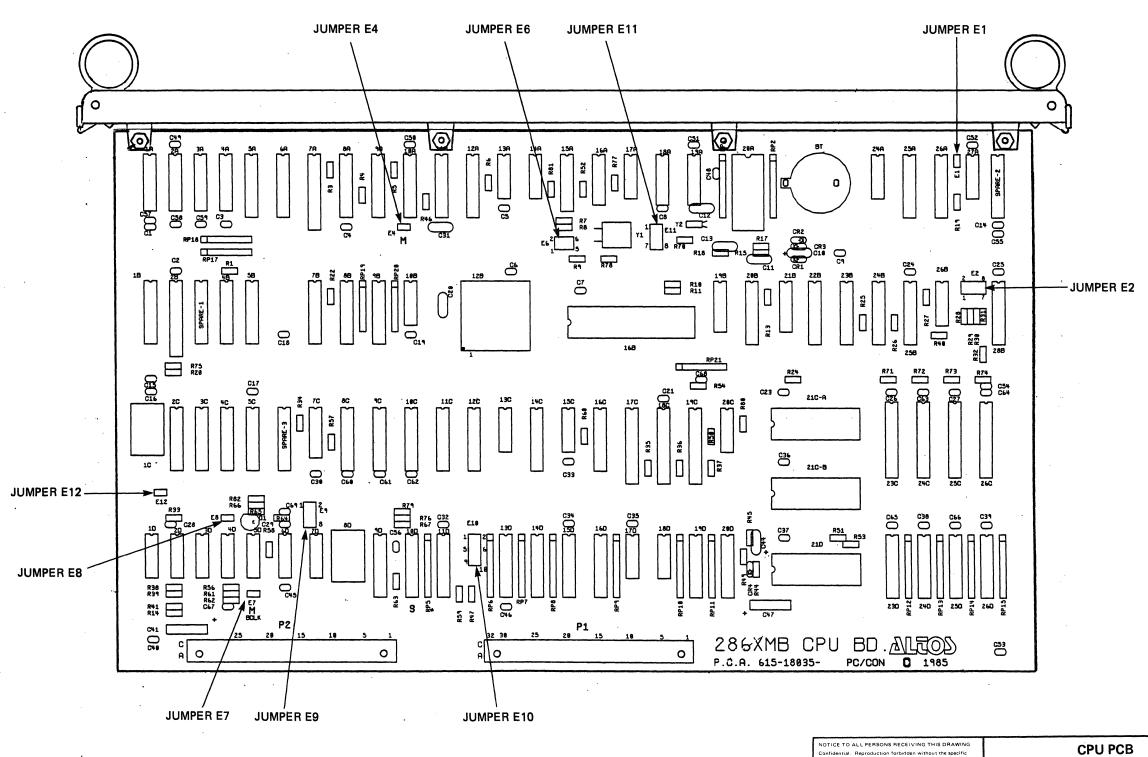

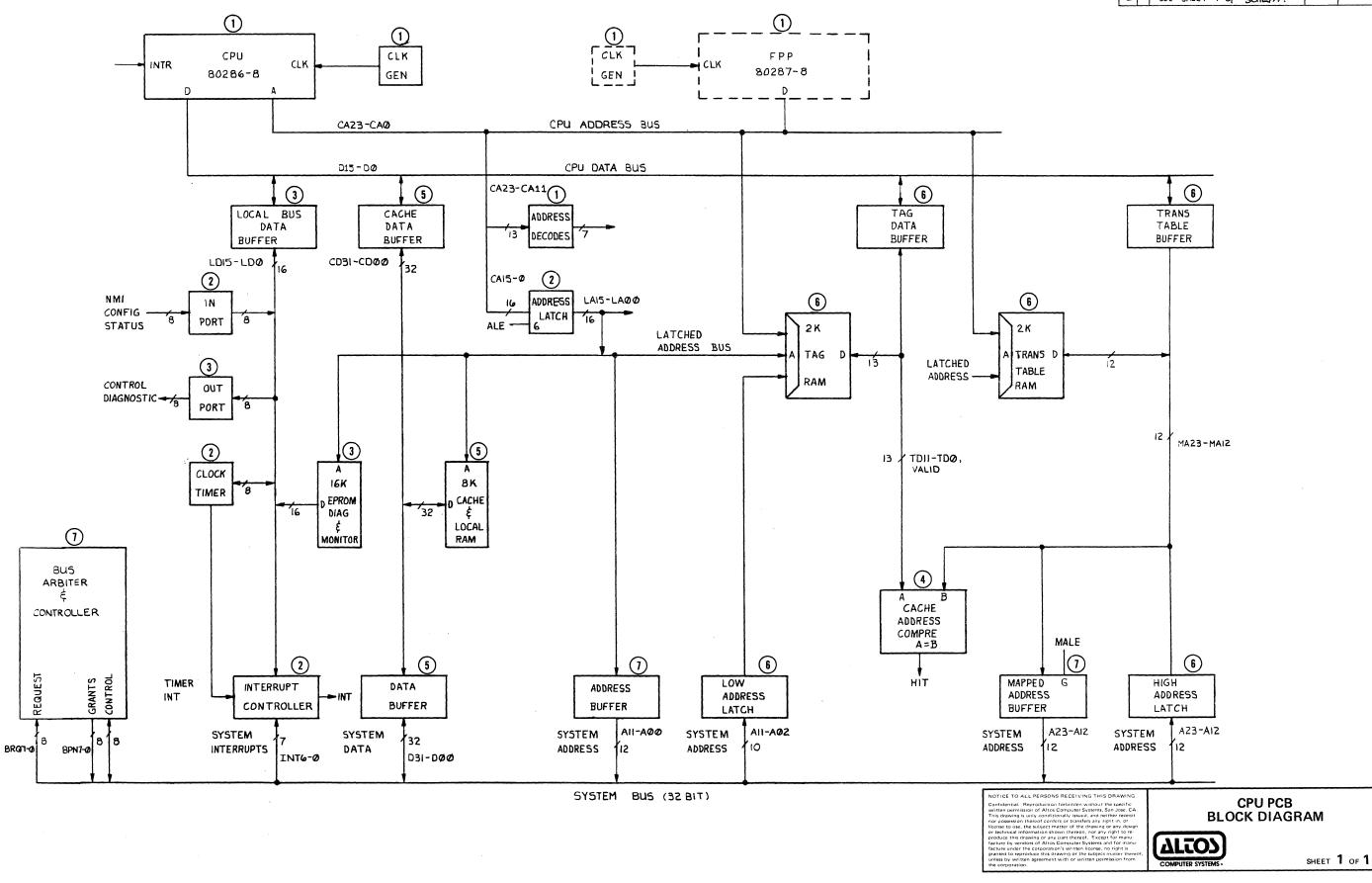

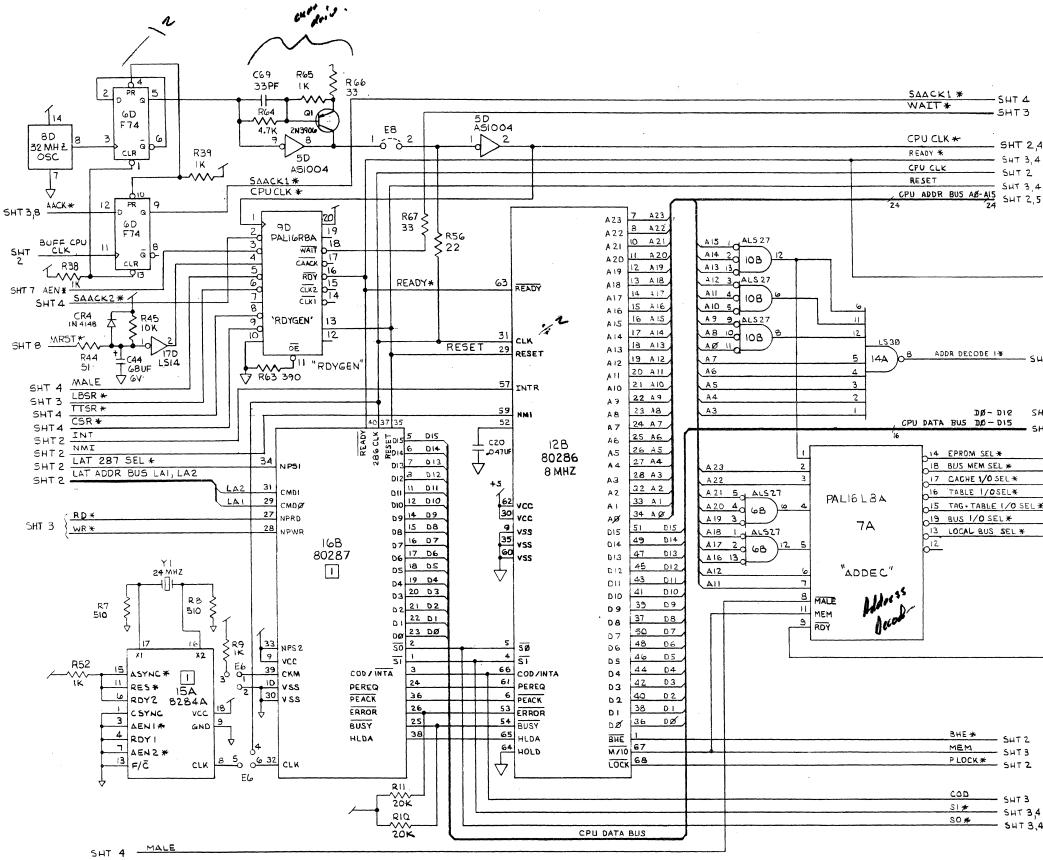

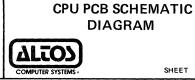

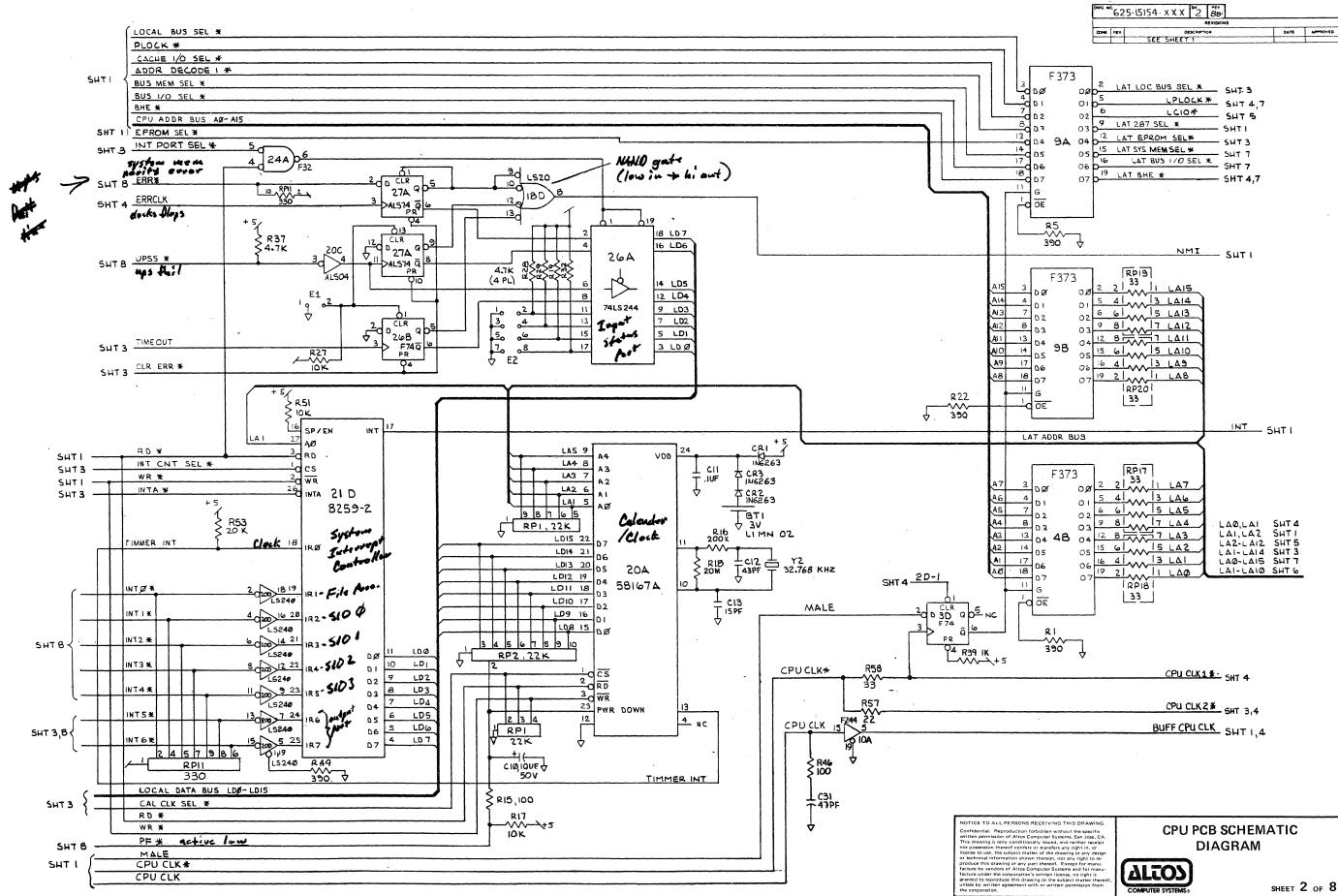

#### Central Processing Unit (CPU) PCB

The CPU PCB contains an 80286 microprocessor (running at 8 MHz), an interrupt controller, and a calendar clock with battery backup.

Also available on the -002 version of the CPU PCB is an optional 80287 floating-point numeric processor. The 80286 is aided by a 4K byte instruction and data cache memory. When operating out of cache memory, the 80286 runs with zero wait states.

When a memory write on the system bus occurs, the cache control hardware searches the cache. If there is a cache hit, then that location in the cache is marked as invalid. This feature of the cache makes it fully coherent with system memory at all times. The cache hit rate has been measured at 88% under typical use environments.

The CPU PCB contains memory mapping hardware that splits up system memory into 4K byte pages to speed up task switching and prevent memory fragmentation problems.

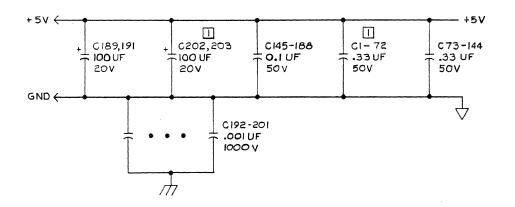

#### Memory PCB

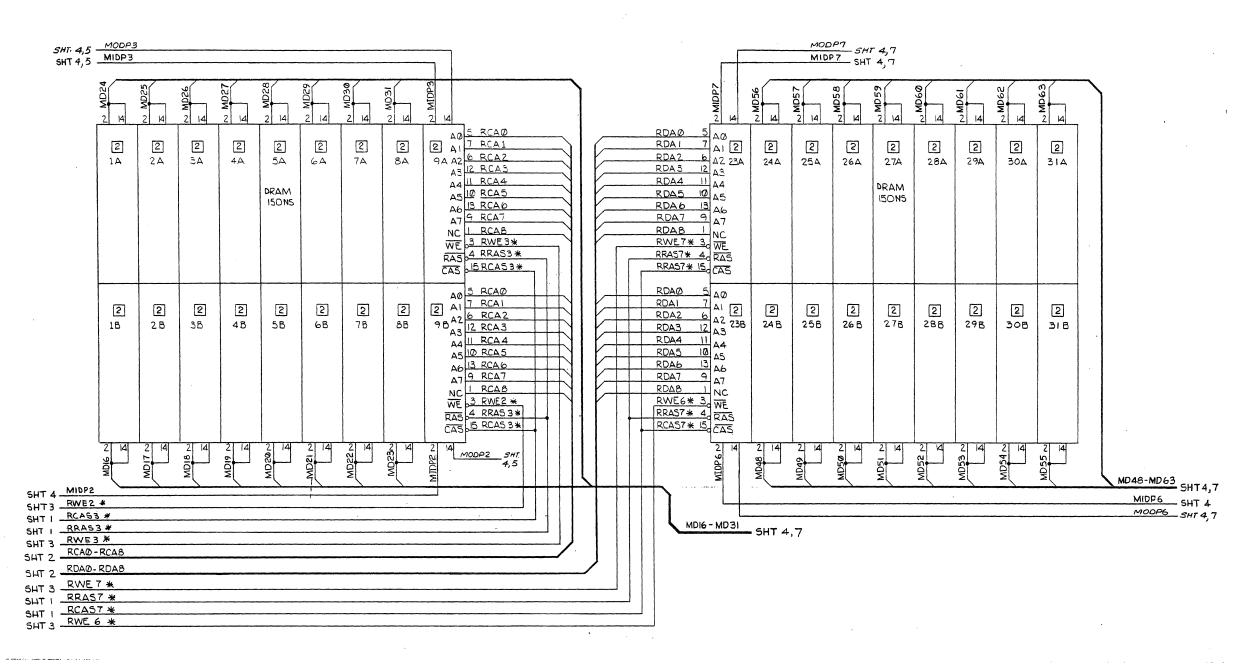

The memory PCB comes in three sizes: 1M, 2M, or 4M bytes. The system memory is organized into long words of 32 bits and memory transfers can be made in 8, 16, or 32-bit quantities.

The memory PCB uses 150 nanosecond dynamic RAM integrated circuits (ICs) and features a typical access time of 240 nanoseconds with a typical cycle time of 400 nanoseconds. Multiple memory PCBs can be installed in the 1086/2086 system.

#### **Communications PCB**

The communications PCB handles all of the serial communications for the 1086/2086 system and supports asynchronous and synchronous RS-232, and RS-422 network communications.

The communications PCB supports up to 10 asynchronous ports; three of which can be software-switchable to support two synchronous channels and one networking port.

The operating software for the communications processor is down-loaded at boot time so that the communications PCB becomes fully programmable.

The networking port is fully compatible with Altos 800K bit WorkNet, 186, 486, 586, and 986 systems and can run at a faster 1.4M bit per second rate when communicating with other 1086/2086 and Altos 3068 systems. Several synchronous communications packages, which include the X.25 and SNA protocols, are available to run on the communications PCB. An Intel 8086 microprocessor (running at 8 MHz) manages all the data flow, I/O interrupts, DMA channels, and communications with the CPU.

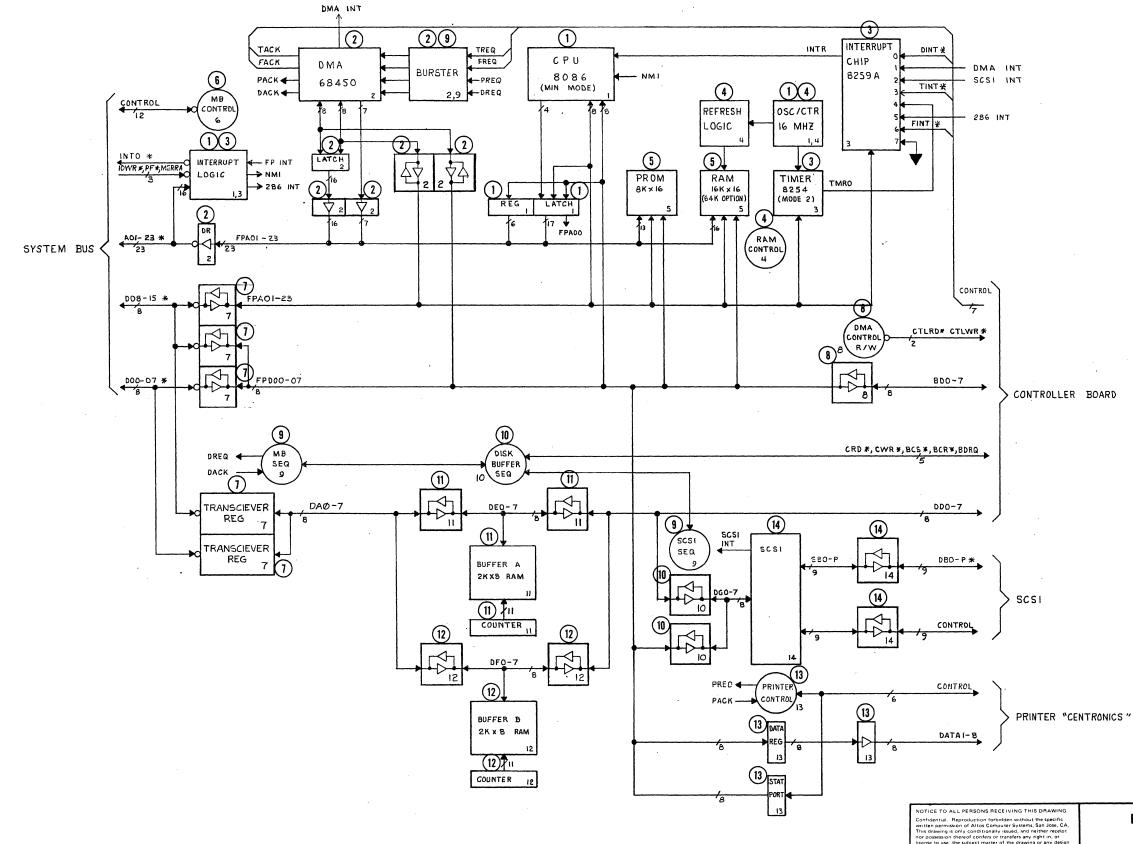

#### File Processor PCB

The file processor PCB manages the data flow to/from the Centronics parallel port and all of the mass storage devices in the system. The mass storage devices include the floppy disk, hard disk, and cartridge streaming tape drives, and all the peripherals connected to the SCSI channel.

#### NOTE

The -ØØl version of the file processor PCB does not support small computer system interface (SCSI) operation. The -ØØ2 version of the file processor PCB includes SCSI.

Some of the main characteristics of the file processor are:

- supports up to three internal hard disk drives and additional drives connected via the SCSI channel

- supports a DMA-driven Centronics parallel port for high-speed line and laser printers

- concurrent transfer of the printer, tape, floppy disk, and hard disk data (only one hard disk at a time)

- performs overlapped seeks when more than one disk drive is connected

- performs reads and writes to consecutive sectors on the hard disk, even though data may be scattered in system memory.

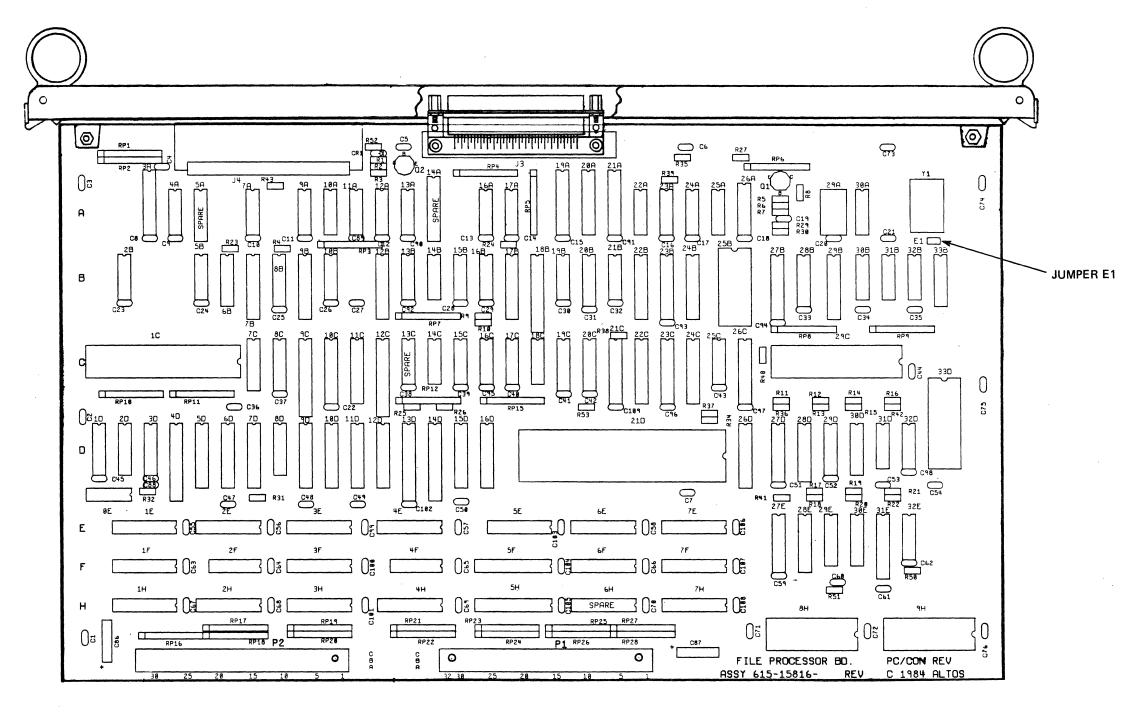

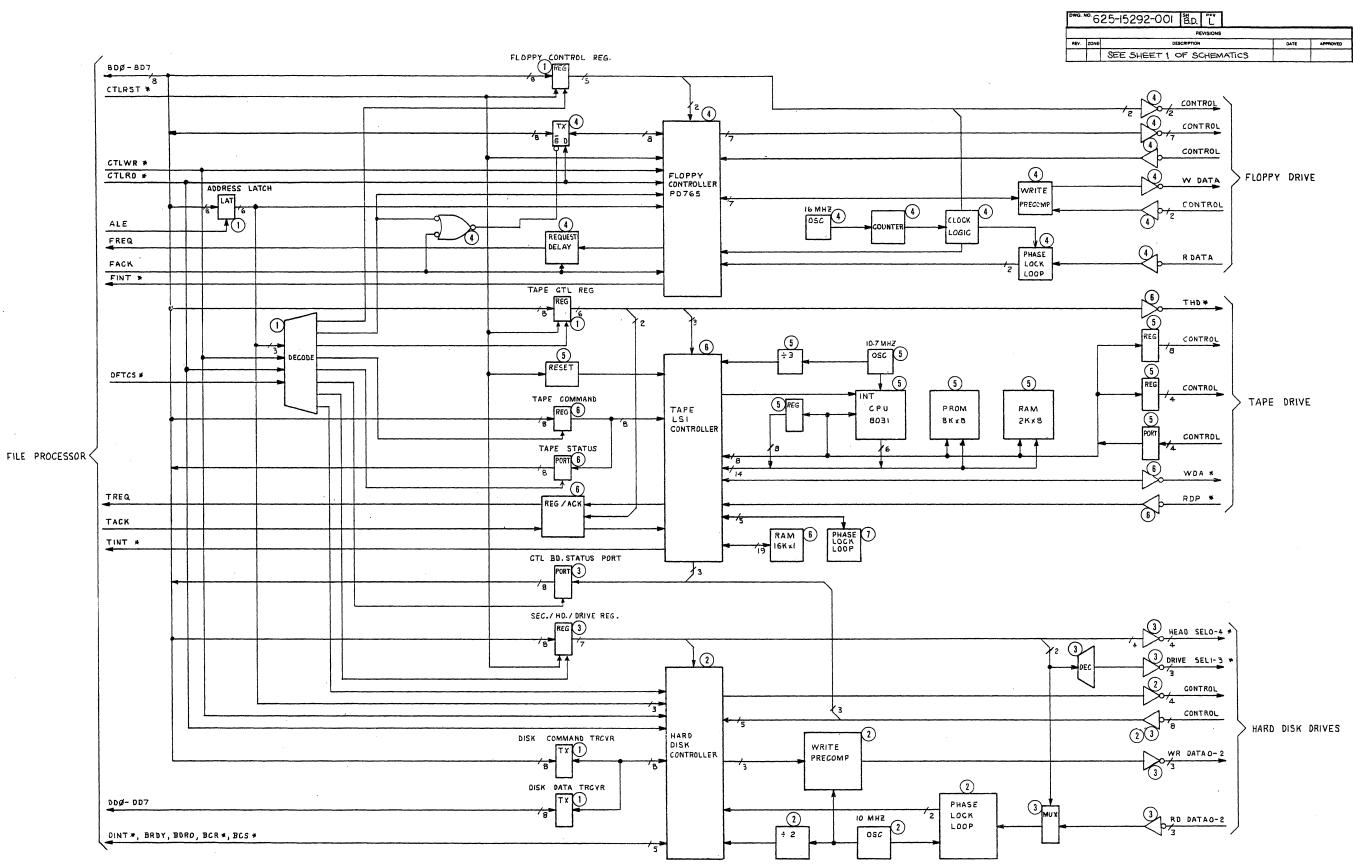

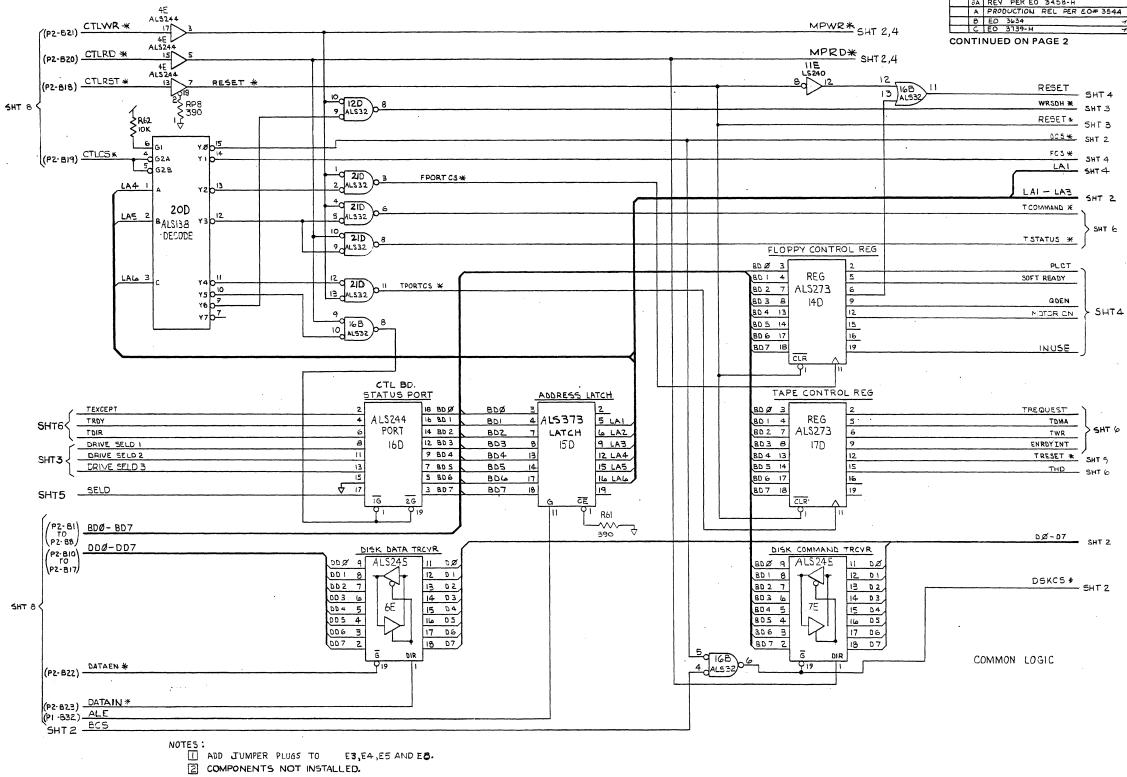

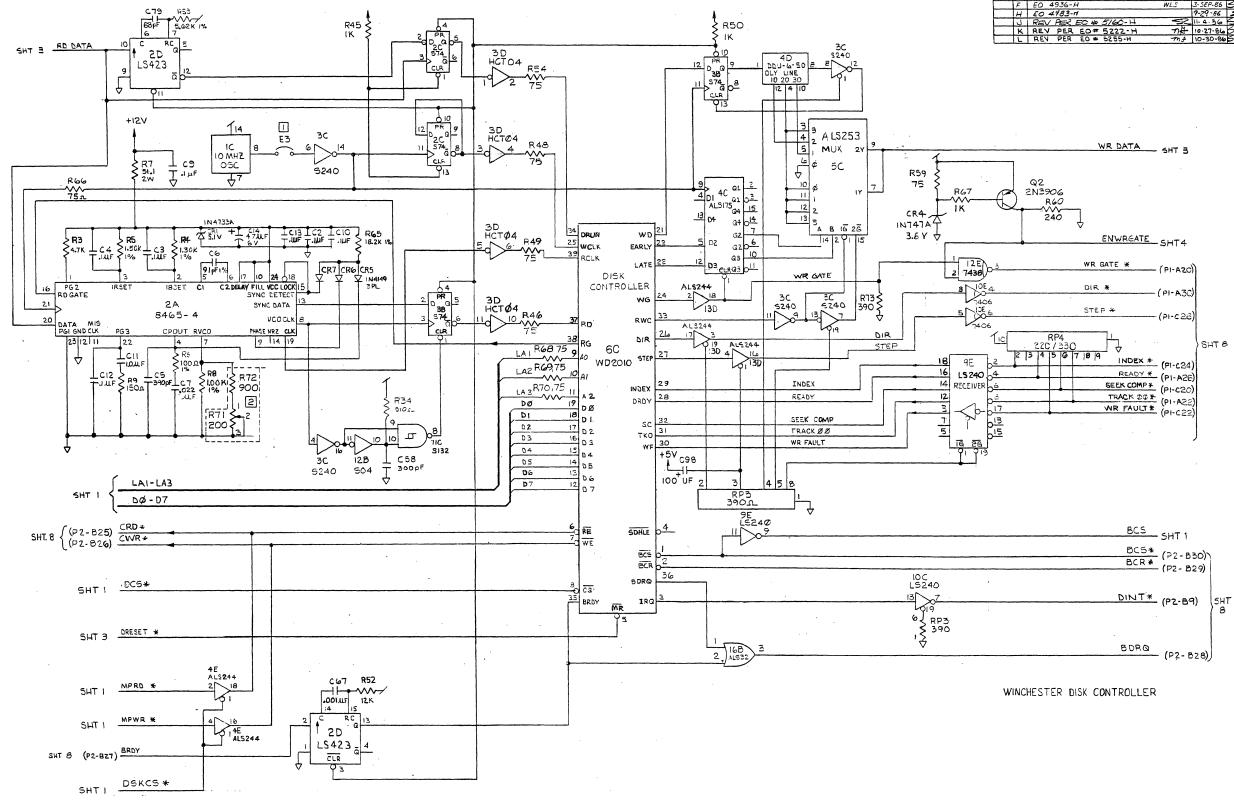

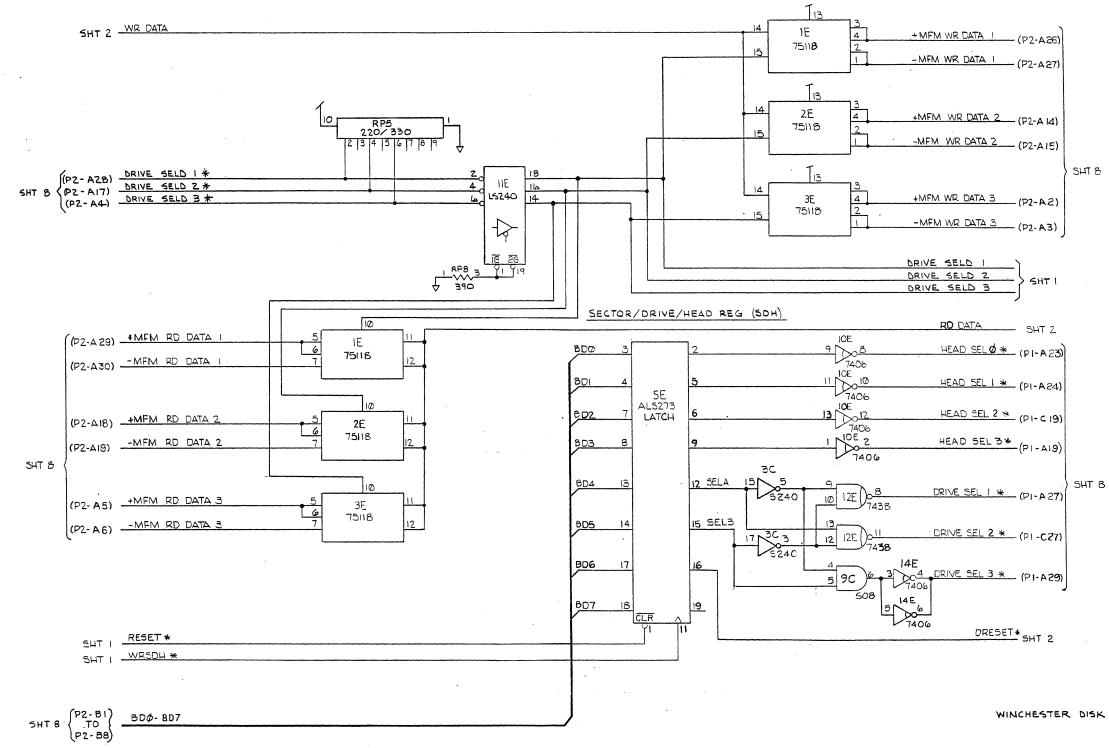

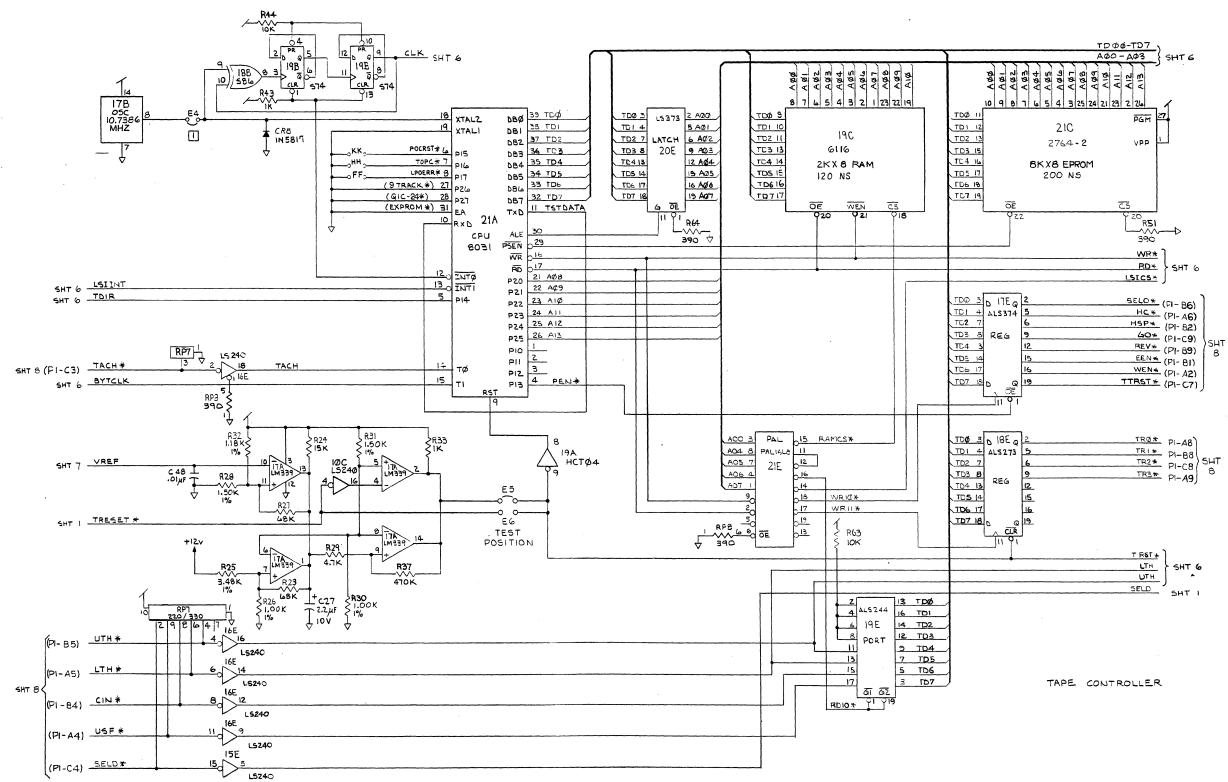

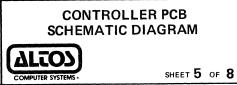

#### **Controller PCB**

The controller PCB contains the device controllers for the floppy disk, hard disk, and streaming tape drives. All of these device controllers take commands from the file processor.

The hard disk controller accommodates disk drives with ST506 or ST412HP interfaces and can handle data transfer rates up to 5M bits per second. The hard disk controller can support up to three internal hard disk drives.

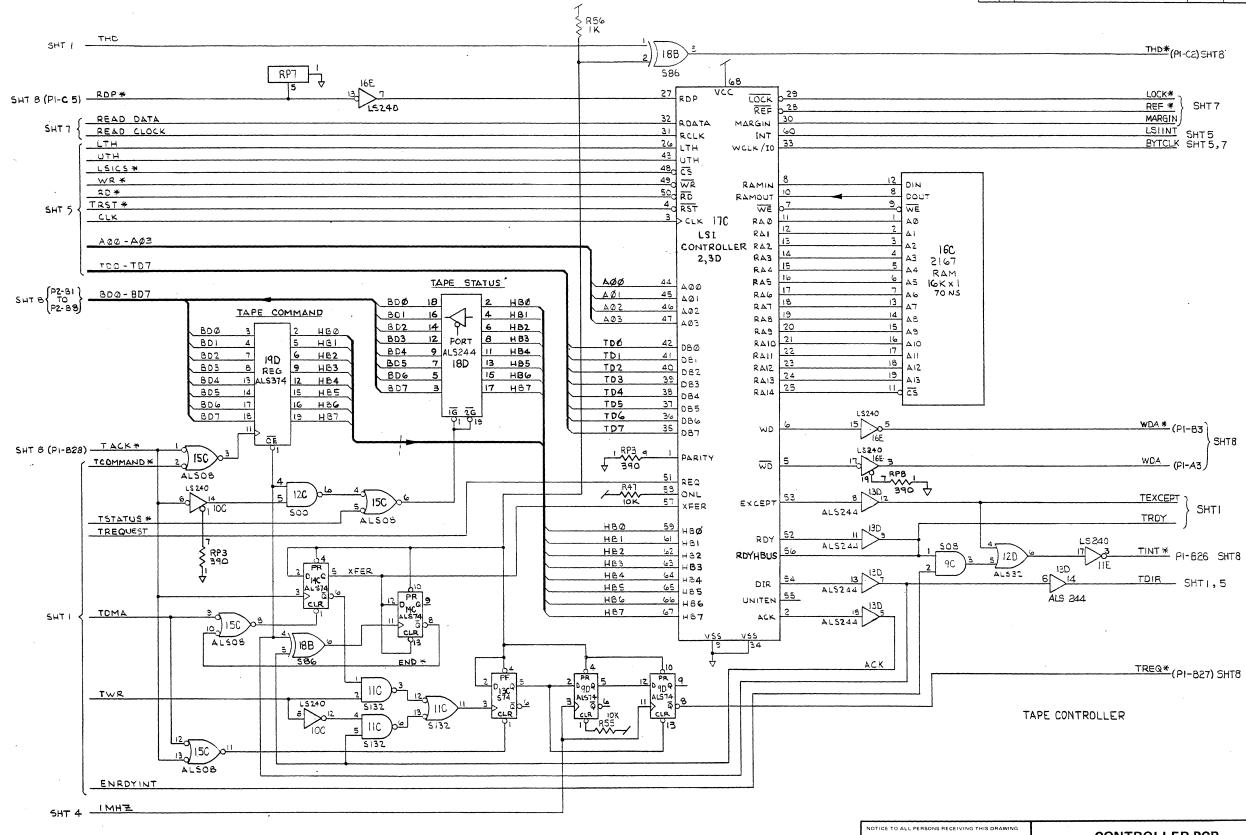

The tape controller can interface with Altos cartridge streaming tape drives with the QIC-36 interface and uses the QIC-24 format for putting data on the tape. The tape streams at 90 inches per second and has a maximum capacity of 60M bytes.

The floppy disk controller interfaces with a dual-speed floppy disk drive which uses either normal or high capacity disks. The normal disks are fully compatible with the floppy disks used on the Altos 186, 486, and 586 systems.

System Overview

2

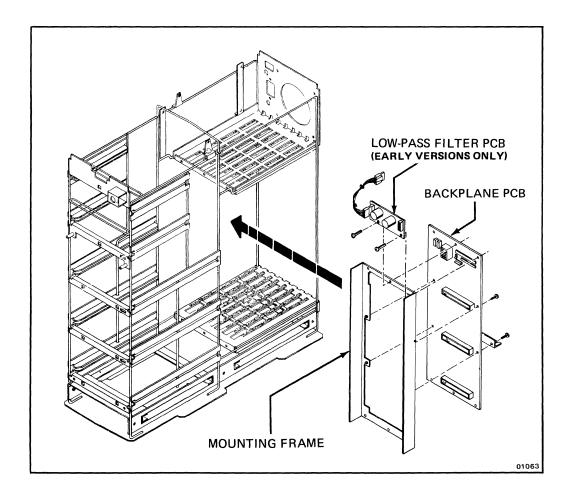

## FIELD REPLACEABLE UNITS

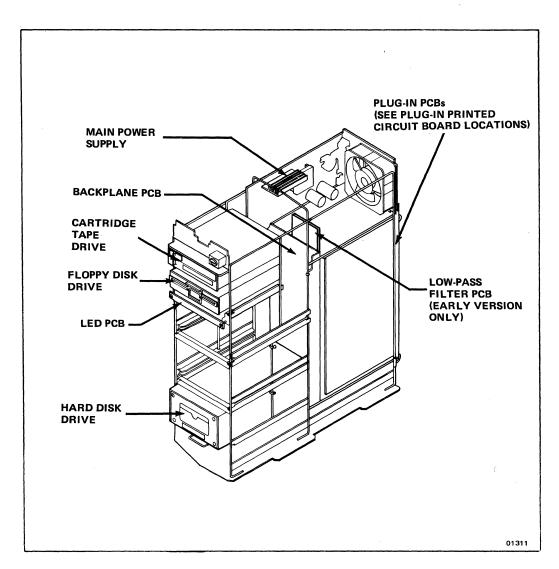

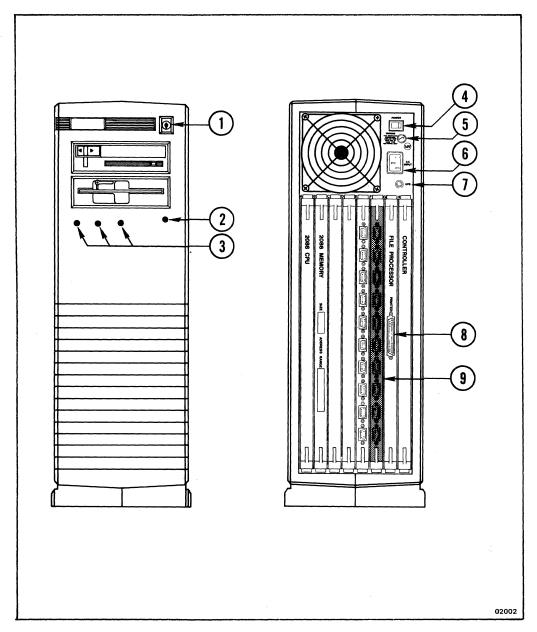

The 1086/2086 Computer System contains the following field replaceable units (FRUs) (see Figure 1-1):

- main power supply

- streaming tape drive

- hard disk drive

- floppy disk drive

- central processing unit (CPU) PCB

- memory PCB

- communications PCB

- file processor PCB

- controller PCB

- backplane PCB

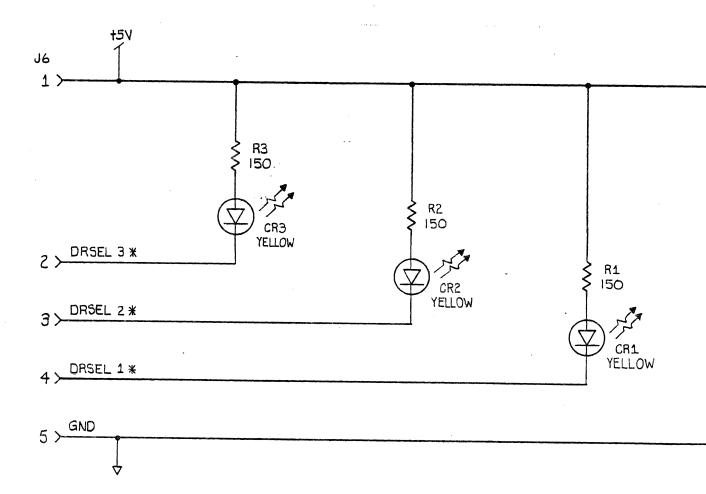

- light-emitting diode (LED) PCB

- low-pass filter PCB (early versions only)

System Overview

Figure 1-1. Field Replaceable Units

## CONTROLS, CONNECTORS, AND INDICATORS

Refer to Figure 1-2 for the locations of the front and rear-panel controls, connectors, and indicators. The following is a description of the controls, connectors, and indicators indexed to the numbers in Figure 1-2:

## Front Panel

- 1 RESET/RUN Switch. Key-operated switch that resets (boots) the system when turned to RESET and back to RUN. Allows normal system operation when set to RUN. If the key is turned to RESET and removed, the system will remain in the reset condition and will not operate.

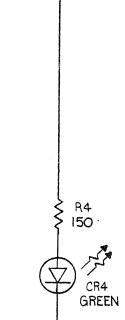

- 2 **POWER Indicator.** Green light-emitting diode (LED) indicator that lights when power is applied to the system (rear panel POWER switch is in the on position).

- 3 HD 1, HD 2, and HD 3. Yellow LED indicators that light to indicate which hard disk drive is selected.

## **Rear Panel**

- 4 **POWER Switch.** Rocker switch that applies power to the system when placed in the on position (green LED indicator 2 on the front panel is lit). The system will boot when the POWER switch is placed in the off, then on, position while the RESET/RUN switch 1 on the front panel is in the RUN position.

- 5 Fuse Holder. Holder that contains the main linevoltage fuse (Refer to Chapter 2 for the proper fuse rating).

- 6 AC INPUT Connector. Three pin AC connector for attaching an AC power cord to the system.

- 7 UPS Jack. Jack for connecting a power fail status signal from an external uninterruptable power source device to the system.

- 8 **PRINTER Connector.** Connector for attaching a printer with a Centronics parallel interface to the system.

9 Serial I/O Ports. Ports Ø through 9 on the communications PCB provide 1Ø asynchronous RS-232 ports for connecting terminals or printers to the system. Refer to the communications PCB description in Chapter 3 for details on the serial I/O port capabilities.

Figure 1-2. Controls, Connectors, and Indicators

System Overview

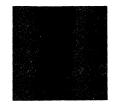

## PLUG-IN PRINTED CIRCUIT BOARD LOCATIONS

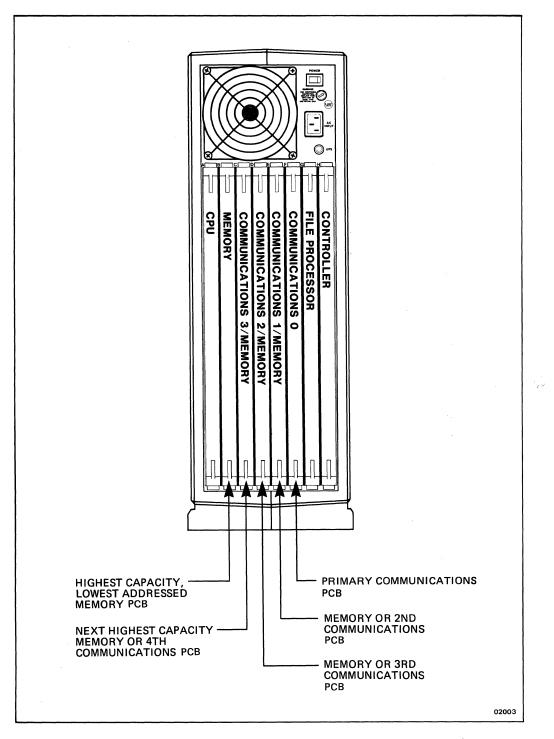

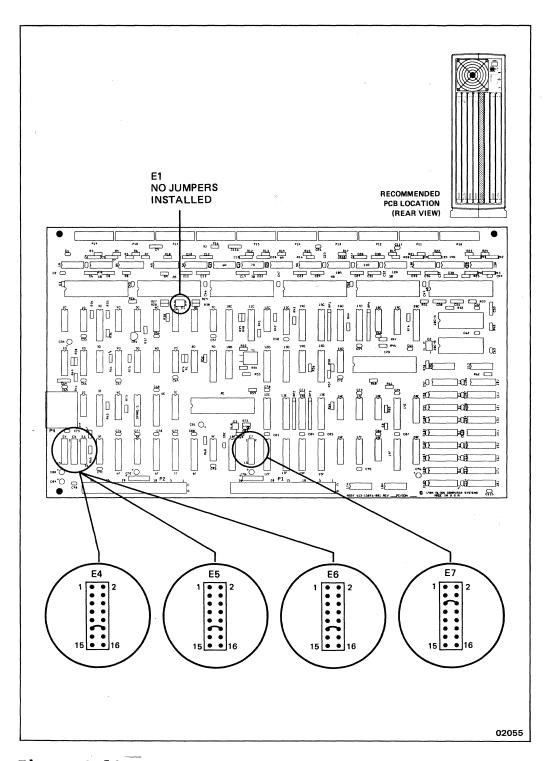

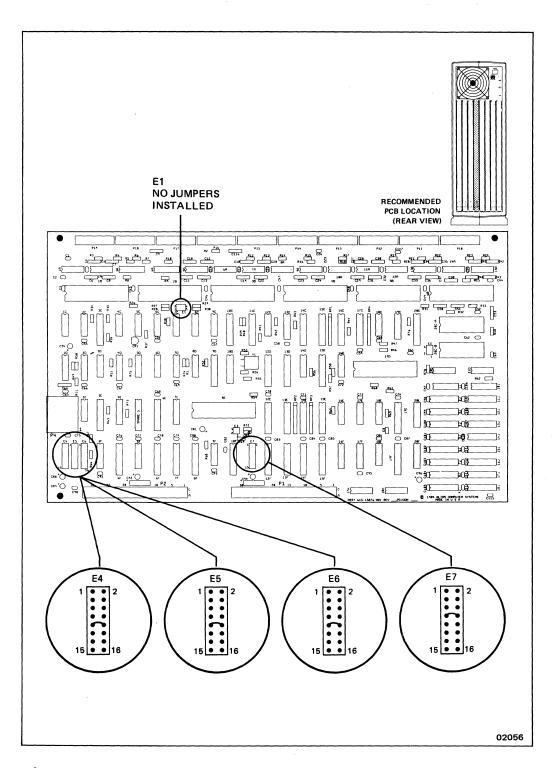

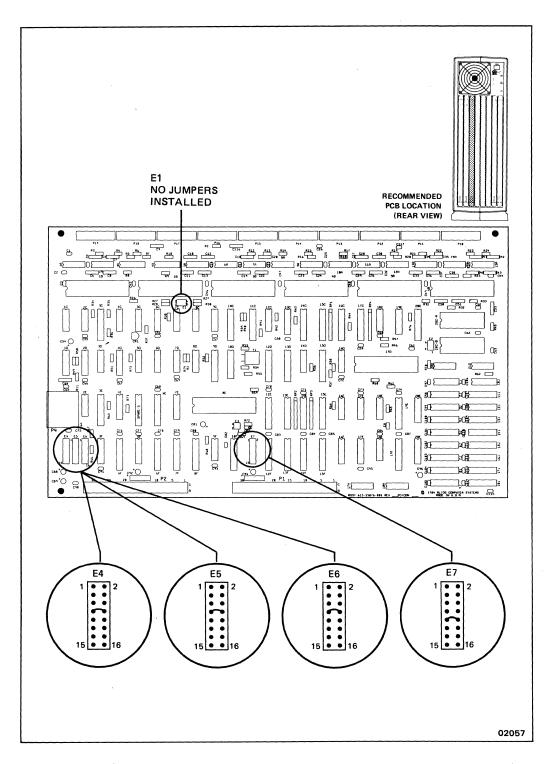

The CPU, file processor, and controller PCBs are dedicated to slots A, G, and H respectively in the back of the 1086/2086. The remaining slots, B through F, are electrically identical which allows memory and communications PCBs to be installed in any order in these five slots. However, software requires that the memory and communications PCBs be jumpered according to their logical assignment in the system (see jumper description information in Chapter 3 and Appendix A).

## SYSTEM SOFTWARE

The system software supplied with the 1086/2086 consists of the operating system, utility, and diagnostic programs.

## **Operating System Program**

The 1086/2086 Computer System is specifically designed for the XENIX 3.2 operating system.

The XENIX operating system supports the following development tools and programming functions:

- large Model C compiler with lM byte of address space per program

- shared data that allows programs to share a common memory space

- semaphores that provide a synchronization tool for cooperating programs

- source code control system for easy program maintenance

- full suite of development tools, such as, vi, csh, nroff, lint, and adb

System Overview

Figure 1-3. Recommended Plug-In PCB Locations

#### **Address Translation**

XENIX uses the sophisticated address translation logic on the 1086/2086 to improve performance as follows:

- Scatter Loading. Loads user programs into noncontiguous 4K byte pages of system memory for more efficient use with less swapping

- Faster Context Switching. When context switching, the per process data area is mapped by loading a table entry instead of copying the data around memory as in standard XENIX

- Dynamic Stack Growth. Programs do not preallocate stack space

#### **Disk Performance**

The 1086/2086 hard and floppy disks are controlled by the file processor PCB which removes much of the processing work from XENIX. The Altos XENIX also supports a 1K byte block file system that maximizes disk throughput.

#### Serial Port Performance

The 1086/2086 serial ports are controlled by the communications PCB which offloads interrupts and processing from XENIX. Each communications PCB is down-loaded with a code that handles the asynchronous ports, WorkNet, and any other communication protocols (SNA, X.25, 3780, and 3270).

#### Compatibility

The XENIX operating system on the 1086/2086 can read and write floppy disks and execute programs that run on the most Altos systems. Tapes created on the Altos 986T can also be read on the 1086/2086.

#### **Diagnostics**

The System Diagnostic Executive (SDX) Program is on a floppy disk included with the 1086/2086 system. The SDX program performs a series of user system-confidence tests. Refer to Chapter 5 for information on the SDX user system-confidence tests.

Field-service diagnostics are also available on the SDX floppy disk. Additional information on the SDX fieldservice diagnostics is provided in Chapter 5. (Refer to the 1086/2086 Remote Diagnostics manual for detailed remote diagnostics procedures.)

# Chapter 2 Specifications

| INTRODUCTION                  | • | • | • | • | • | • | • | • | • | • | 2-3 |

|-------------------------------|---|---|---|---|---|---|---|---|---|---|-----|

| ELECTRICAL SPECIFICATIONS     |   | • | • | • | • |   | • | • | • | • | 2-3 |

| ENVIRONMENTAL SPECIFICATIONS. | • | • | • | • | • |   | • |   | • |   | 2-8 |

| PHYSICAL SPECIFICATIONS       | • | • | • | • | • | • | • | • | • | • | 2-8 |

4

## INTRODUCTION

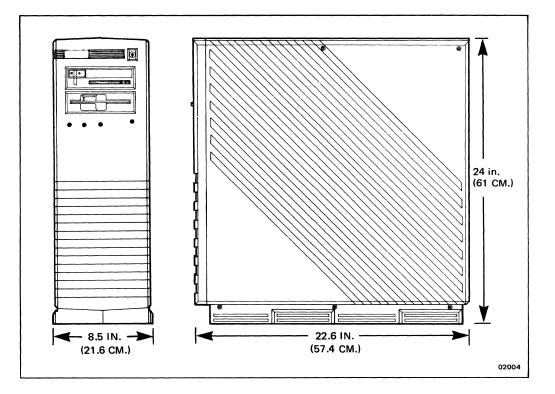

The electrical specifications listed in Table 2-1 apply when the 1086/2086 Computer System has been operating for at least 15 minutes at an ambient temperature between +40 and +95 degrees Fahrenheit (+5 and +35 degrees Celsius). The environmental and physical specifications are listed in Tables 2-2 and 2-3.

## **ELECTRICAL SPECIFICATIONS**

Table 2-1 lists the electrical specifications for the Altos 1086/2086 Computer System.

|                                                                                                                                                                                                                                                                                            | Performance Requirement                                                                    |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Subsystem                                                                                                                                                                                                                                                                                  |                                                                                            |  |  |  |  |  |  |

| Central Processing Unit<br>(CPU)                                                                                                                                                                                                                                                           |                                                                                            |  |  |  |  |  |  |