Publication No. 990004-01 April 1982

> ADVANCED ELECTRONICS DESIGN, INC. WINC-08 OPERATIONS AND MAINTENANCE MANUAL

#### PREFACE

## COPYRIGHT

Copyright 1982 by Advanced Electronics Design, Inc. (AED). All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Advanced Electronics Design, Inc., Sunnyvale, California 94086.

## TRADEMARKS

The various registered trademarks referred to in this manual are identified and acknowledged as follows:

WINC-08, and FLEX-02 are registered trademarks of AED. DEC, PDP-11, LSI-11, RT11, RSX, RL02, RX01/02, RSX11M, UNIBUS, and Q-BUS are registered trademarks of Digital Equipment Corporation.

## WARRANTY

AED Corporation products are warranted against defects in material and workmanship for a period of 90 days. Refer to your AED purchase contract for complete warranty information. Refer to the "Service packages from AED" brochure for complete service information.

#### CHANGES

The material in this manual is for information only and is subject to change without notice.

AED reserves the right to make changes in the product design without reservation and without notification to its users.

i

## TABLE OF CONTENTS

# Section

1

.

| PREFACE |         | ,                                        |     |

|---------|---------|------------------------------------------|-----|

|         | Copyr   | ight                                     | i   |

|         | Trade   | marks                                    | ī   |

|         | Warra   | inty                                     | i   |

|         | Chang   | es                                       | i   |

| 1       | INTRO   | DUCTION                                  | 1-1 |

|         | 1.1     | Scope and Purpose of Manual              | 1-1 |

|         | 1.2     | Reference Documents                      | 1-1 |

|         | 1.3     | Overview of System                       | 1-1 |

|         | 1.4     | Definition of Available Configurations   | 1-4 |

|         | 1.5     | Emulation Characteristics                | 1-4 |

|         |         | 1.5.1 RL02 Emulation                     | 1-4 |

|         |         | 1.5.2 RX02 Emulation                     | 1-6 |

|         | 1.6     | Supplied Software                        | 1-6 |

|         |         | 1.6.1 Initialization                     | 1-7 |

|         |         | 1.6.2 Data Diagnostic (Winchester) RLMFD | 1-7 |

|         |         | 1.6.3 Data Diagnostic (Floppy Disk)      | 1-7 |

|         |         | 1.6.4 ECC Diagnostic (Winchester) RLMFC  | 1-7 |

|         | 1.7     | WINC-08 Specifications                   | 1-7 |

|         | 1.8     | Disk Drive Specifications (Floppy)       | 1-9 |

|         | 1.9     | Disk Drive Specifications (Winchester)   | 1-9 |

|         | 1.10    | Quality Assurance                        | 1-9 |

| 2 IN    | STALLAT | TION                                     | 2-1 |

|         | 2.1     | General                                  | 2-1 |

|         | 2.2     | Site Requirements                        | 2-1 |

|         | 2.3     | Unpacking                                | 2-2 |

|         | 2.4     | Physical Installation                    | 2-4 |

|         |         | 2.4.1 Rack Mounting                      | 2-4 |

11

## TABLE OF CONTENTS (Cont'd)

| Section |               |                                          | Page |

|---------|---------------|------------------------------------------|------|

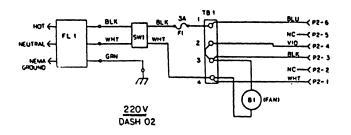

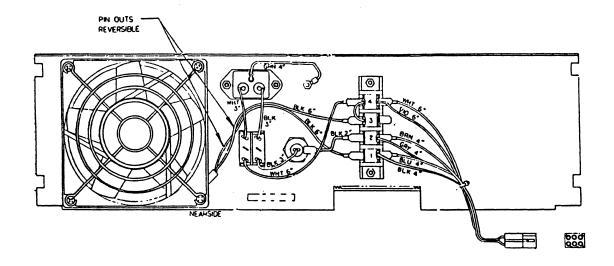

|         | 2.5           | Electrical Installation                  | 2-6  |

|         |               | 2.5.1 AC Power Connection                | 2-6  |

|         |               | 2.5.2 System Ground                      | 2-6  |

|         | 2.6           | Signal Interconnection to Host           | 2-13 |

|         | 2.7           | WINC-08 to PDP-11 Host Installation      | 2-13 |

|         |               | 2.7.1 PDP-11 Interface Card Modification |      |

|         |               | Instruction                              | 2-13 |

|         |               | 2.7.2 PDP-11 (Unibus) Installation       | 2-19 |

|         | 2.8           | WINC-08 to LSI-11 Installation           | 2-20 |

|         |               | 2.8.1 LSI-11 Interface Card Modification |      |

|         |               | Instructions                             | 2-20 |

|         |               | 2.8.2 LSI-11 (Q-Bus) Installation        | 2-22 |

|         | 2.9           | Flex Configuration Jumpering and Flex-02 |      |

|         |               | Installation LSI-11 (Q-Bus)              | 2-25 |

| 3       | 5 <b>0F</b> 1 | 3-1                                      |      |

|         | 3.1           | Introduction                             | 3-1  |

|         | 3.2           | Bootstrap Methods                        | 3-3  |

|         |               | 3.2.1 Example Bootstrap from Unit Zero   | 3-4  |

|         |               | 3.2.2 Example Bootstrap from Unit Two    | 3-5  |

|         |               | 3.2.3 Floppy Disk Bootstrap Methods      | 3-6  |

|         | 3.3           | Initialization (RLMFV)                   | 3-7  |

|         |               | 3.3.1 RLMFV Introduction                 | 3-8  |

|         |               | 3.3.2 RLMFV Description                  | 3-8  |

|         |               | 3.3.3 RLMDV Execution                    | 3-10 |

| 4       | MAIN          | ITENANCE AND TROUBLESHOOTING             | 4-1  |

|         | 4.1           | Maintenance Philosophy                   | 4-1  |

|         | 4.2           | Tools and Test Equipment                 | 4-1  |

## TABLE OF CONTENTS (Cont'd)

## Section

5

6

6-1

| 4.3  | Diagnostics                         | 4-2   |

|------|-------------------------------------|-------|

| 4.4  | Data Diagnostics (Winchester) RLMFD | 4-2   |

|      | 4.4.1 RLMFD Description             | 4-2   |

|      | 4.4.2 RLMFD Execution               | 4-3   |

| 4.5  | ECC Diagnostic RLMFC                | 4 - 4 |

|      | 4.5.1 RLMFC Description             | 4-4   |

|      | 4.5.2 RLMFC Execution               | 4-5   |

| 4.6  | Floppy Disk Data Diagnostics        | 4-6   |

| 4.7  | Power Supply Check                  | 4-6   |

| 4.8  | Troubleshooting Guide               | 4-9   |

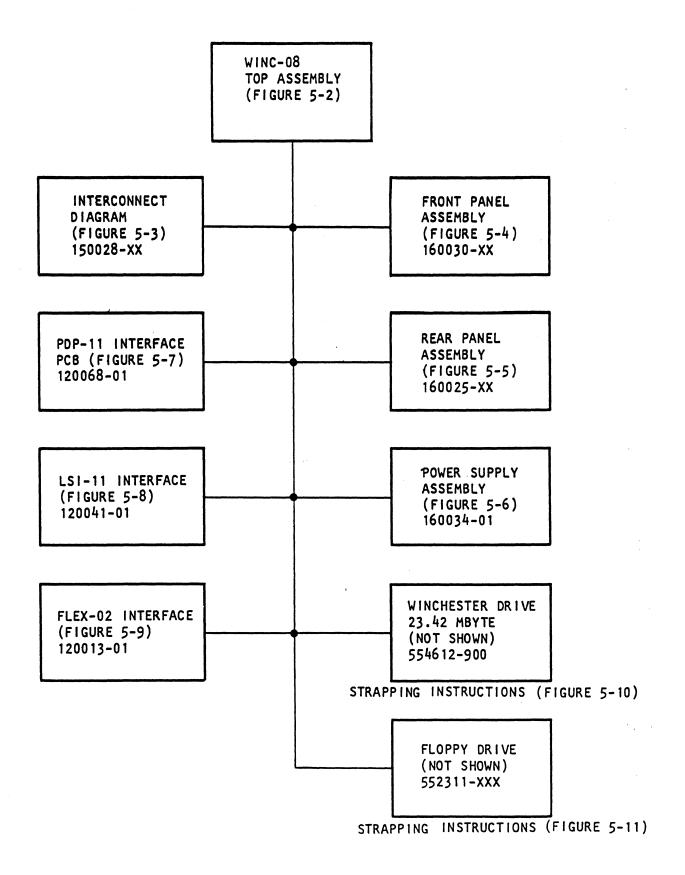

| PART | NUMBERS OF REPLACEABLE ASSEMBLIES   | 5-1   |

| 5.1  | Replaceable Parts                   | 5-1   |

| 5.2  | Ordering Information                | 5-1   |

| PROG | RAMMERS' GUIDE                      |       |

| 6.1  | Winchester RL01/02 Emulation Mode   | 6-1   |

| 6.2  | Winchester Maintenance              | 6-1   |

6.3 Floppy Emulation

iv

## LIST OF TABLES

# TablePage1-1WINC-08 Specifications1-81-2Disk Drive Specifications (Floppy)1-101-3Disk Drive Specifications (Winchester)1-112-1WINC-08 Cable Configuration2-134-1FLEX-02 Dual Head Floppy Data Diagnostics4-75-1Replaceable Parts5-2

## LIST OF ILLUSTRATIONS

# Figure

| 1-1  | Typical WINC-08 Functional Block Diagram  | 1-3           |

|------|-------------------------------------------|---------------|

| 1-2  | WINC-08 Standard Configurations           | 1-5           |

| 2-1a | Removal of Top/Sides Assembly             | 2-7           |

| 2-1b | Winchester Drive Head Lock Mechanism      | 2-8           |

| 2-1c | Rack Installation                         | 2-9           |

| 2-1d | Assembly into Top/Sides                   | 2-10          |

| 2-1e | Top/Sides Installation                    | 2-11          |

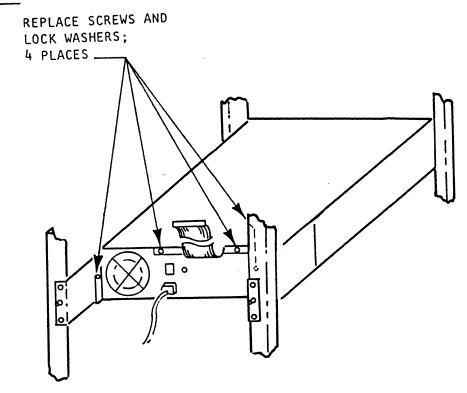

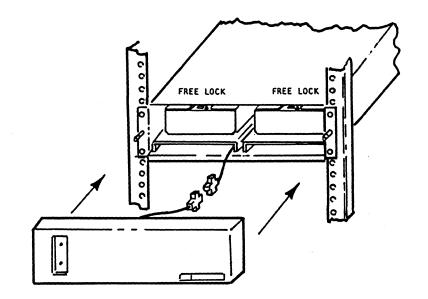

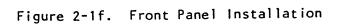

| 2-1f | Front Panel Installation                  | 2-12          |

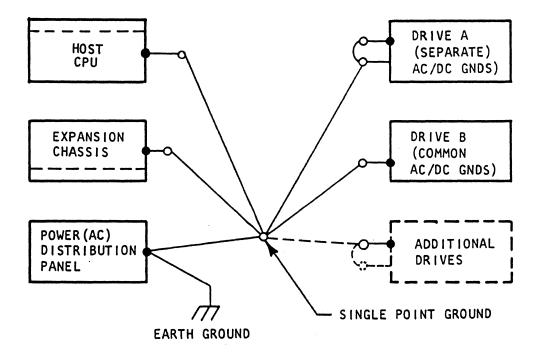

| 2-2  | System Grounding Diagram                  | 2-14          |

| 2-3  | PDP-11 Interface Card                     | 2-15          |

| 2-4  | WINC-08/PDP-11 (Unibus) Interface         | 2-17          |

| 2-5  | PDP-11 Interrupt Priority Level Jumpers   | 2-18          |

| 2-6  | Removal of Nonprocessor Grant Signal      | 2-21          |

| 2-7  | LSI-11 Installation                       | 2 <b>-</b> 23 |

| 2-8  | LSI-11 Interface Card                     | 2-24          |

| 2-9  | FLEX-02 Interface Card                    | 2-27          |

| 2-10 | Interrupt Vector and Bootstrap Inhibit    | 2-28          |

| 3-1  | WINC-08 Controller Board with LED Display | 3-2           |

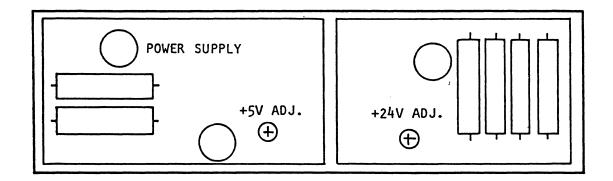

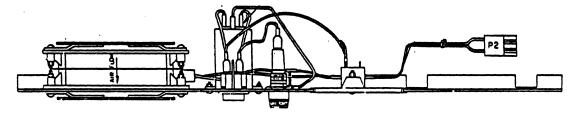

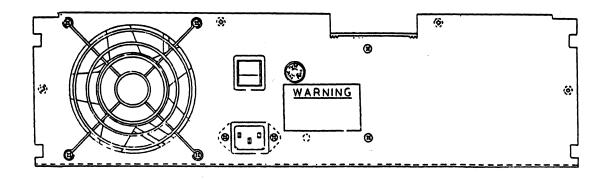

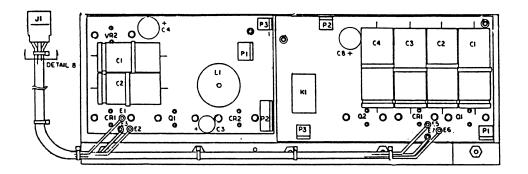

| 4-1  | Top View of WINC-08                       | 4-8           |

| 4-2  | Adjustment Potentiometers                 | 4-9           |

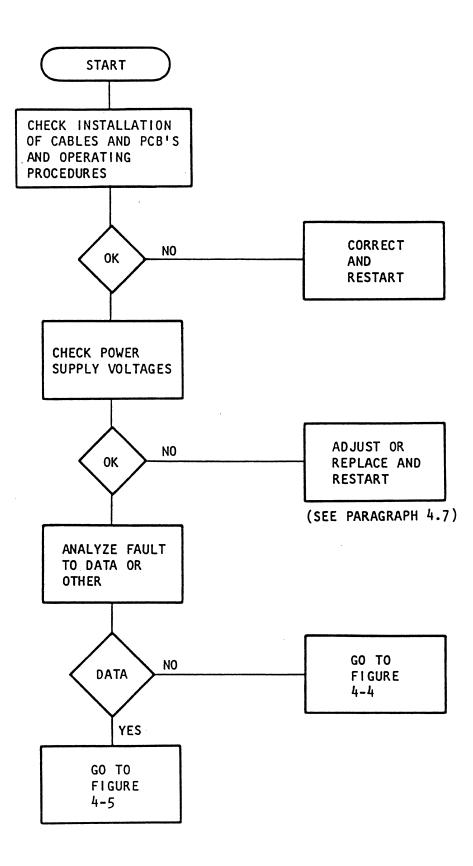

| 4-3  | Basic Checks                              | 4-11          |

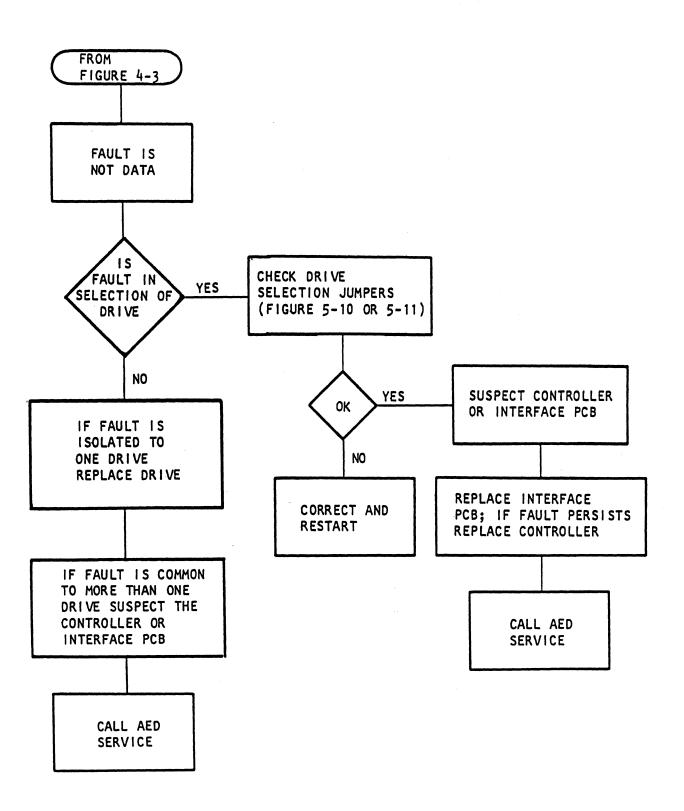

| 4-4  | Other Than Data Related Fault             | 4-12          |

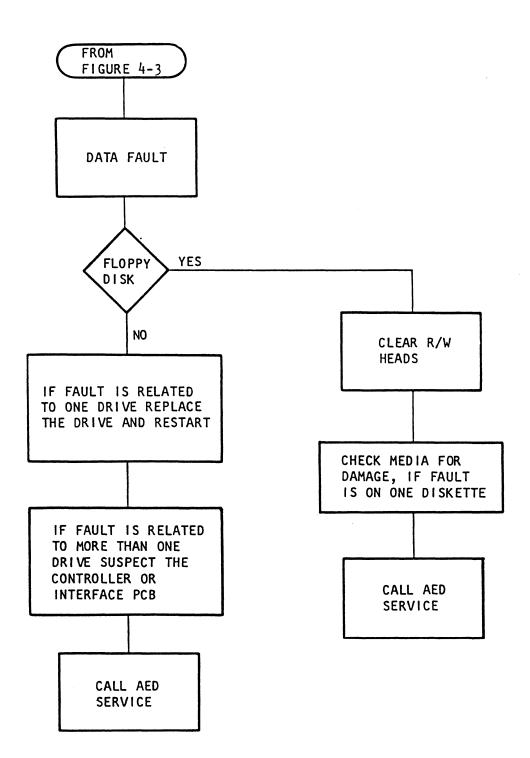

| 4-5  | Data Related Fault                        | 4-13          |

| 4-6  | LED Display Indication                    | 4-14          |

| 5-1  | WINC-08 Subassembly Arrangement           | 5-4           |

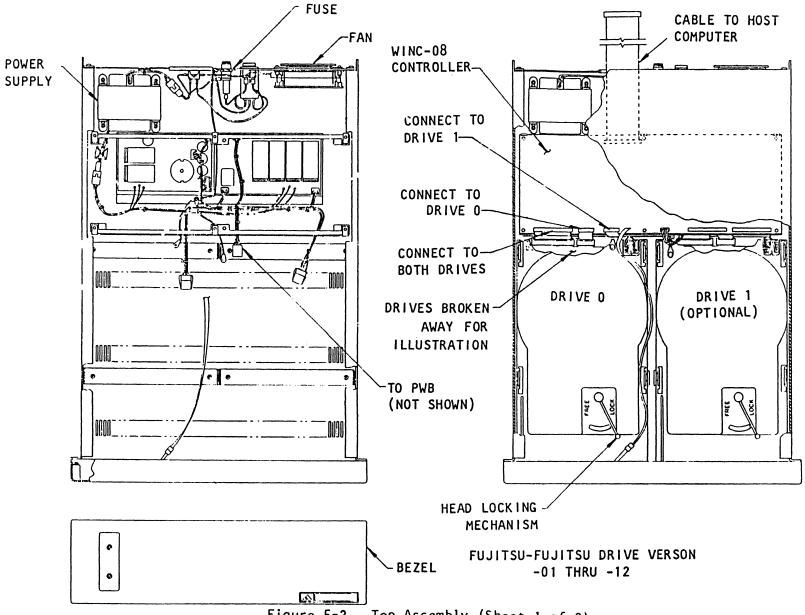

| 5-2  | Top Assembly (Sheet 1 of 2)               | 5-5           |

|      | Top Assembly (Sheet 2 of 2)               | 5 <b>-</b> 6  |

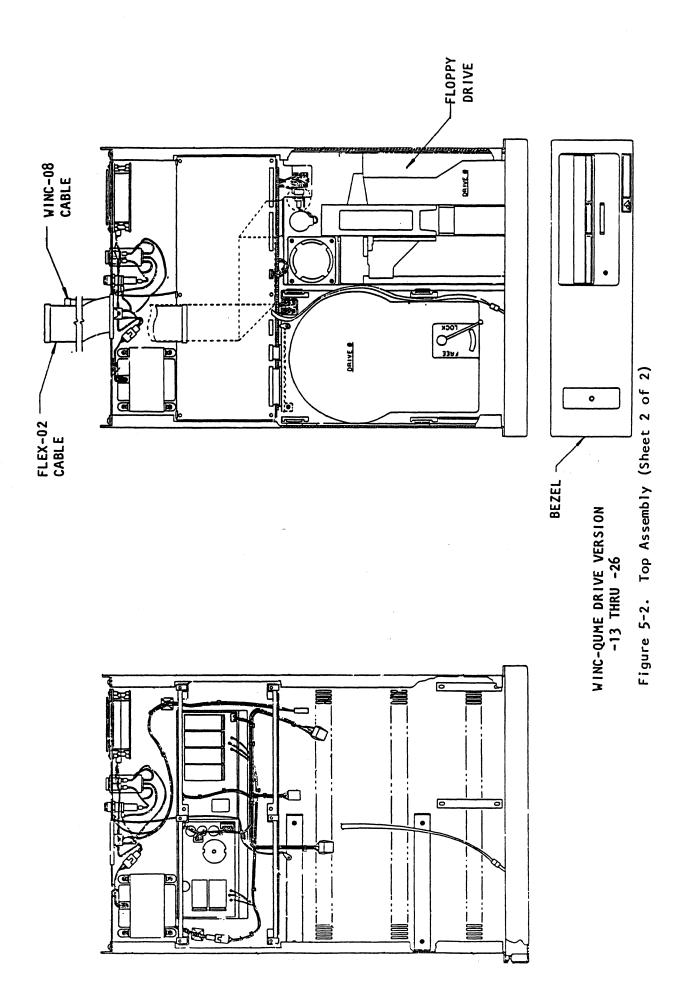

| 5-3  | Interconnection Diagram                   | 5-7           |

| 5-4  | Front Panel Assembly                      | 5-8           |

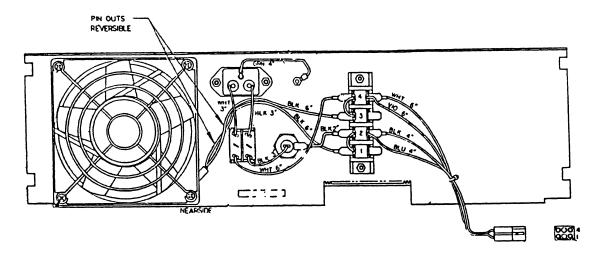

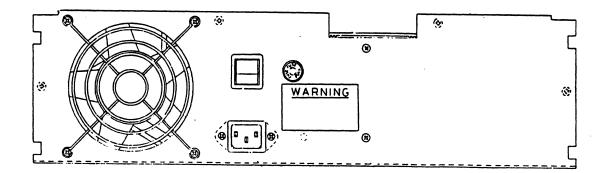

| 5-5  | Rear Panel Assembly                       | 5-9           |

## LIST OF ILLUSTRATIONS (Cont'd)

# Figure

| 5-6  | Power Supply Assembly                 | 5-13 |

|------|---------------------------------------|------|

| 5-7  | PDP-11 Interface Assembly             | 5-14 |

| 5-8  | Interface Assembly                    | 5-15 |

| 5-9  | FLEX-02 Assembly                      | 5-16 |

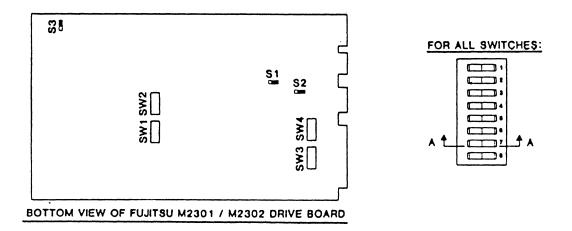

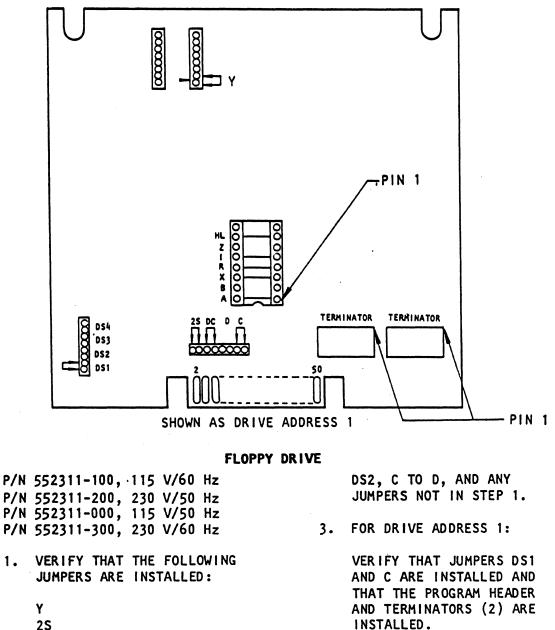

| 5-10 | Drive Strapping Instructions, WINC-08 | 5-17 |

| 5-11 | Drive Strapping Instructions, FLEX-02 | 5-18 |

## Section 1

## INTRODUCTION

## 1.1 SCOPE AND PURPOSE OF MANUAL

This manual contains information on the performance, installation, operation, maintenance, and troubleshooting of the WINC-08 disk drive system. It is intended for operational and maintenance personnel.

## 1.2 REFERENCE DOCUMENTS

Reference documents include the following:

WINC-08 Documentation Package AED -- Part No. 180003-XX FLEX-02 User's Guide AED -- Part No. 990000-01 FUJITSU M2301B/2302B Maintenance Manual -- FUJITSU LTD Microcomputer Processors -- Digital Equipment Corporation Minicomputer Handbook -- Digital Equipment Corporation PDP-11 Peripherals Handbook -- Digital Equipment Corporation Data Trak 8, Maintenance Manual -- Qume Corporation

## 1.3 OVERVIEW OF SYSTEM

The WINC-08 controller is unique in its utilization of single or dual 8inch Winchester drives to emulate DEC RL02 drives; or you can order it with one 8-inch (single or dual head), floppy drive in place of the second Winchester.

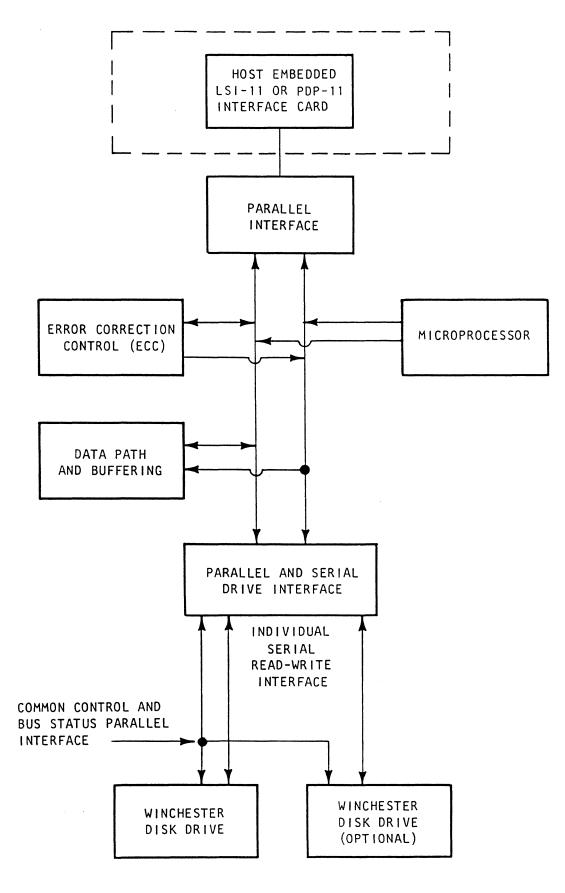

The floppy disk drive option emulates the DEC RX02. Its dual head allows storage on both sides of the diskette, for a total capacity of one megabyte per diskette. Thus, in a single compact configuration, you can emulate both the RL02 and the RX02. A functional block diagram of the WINC-08 is shown in Figure 1-1. Briefly, WINC-08 technology includes these features:

- o Reliability

- o Steel band stepping motor

- o Modular construction

- o No preventive maintenance

- o Easy access to subassemblies

- o Low power consumption

- o Optional floppy disk

- o Error correction code

- o Faster data throughput

- o Software compatibility

- o Unique diagnostic self-test

The WINC-08 controller is a state-sequential machine based on a bipolar microprocessor. The horizontally structured microprocessor improves reliability of the controller by minimizing the component usage and cost.

The WINC-08 controller is functionally equivalent to the DEC RL02, and so it is compatible with DEC software. You can run either RT-11 or RSX-11M without the need or concern for software modifications.

The WINC-08 also offers PDP-11 or LSI-11 users the ability to expand their system to a total storage capacity of 41.6 megabytes -- equal to a fully expanded DEC RL02 system with four disk drives.

Figure 1-1. Typical WINC-08 Functional Block Diagram

## 1.4 DEFINITION OF AVAILABLE CONFIGURATIONS

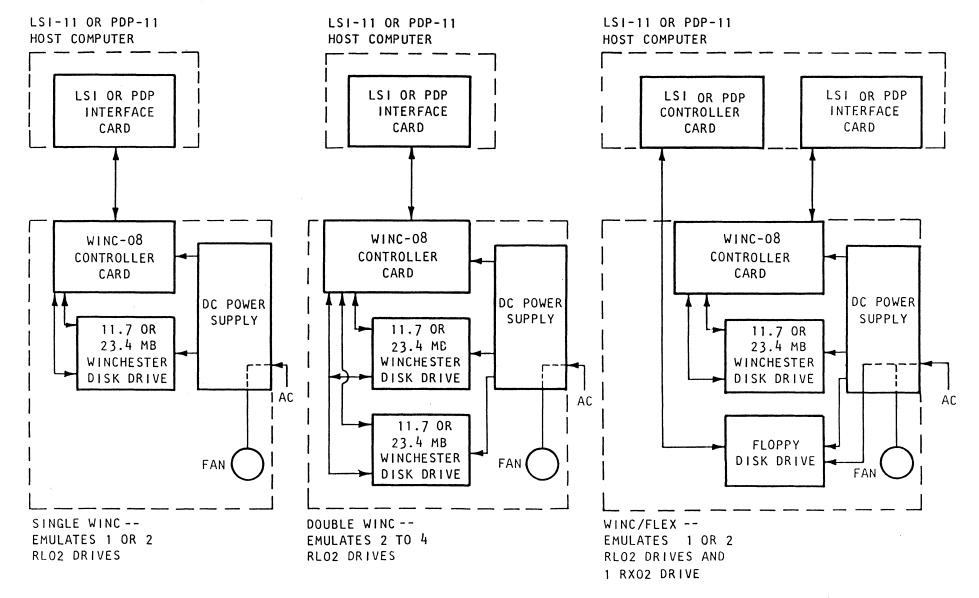

The standard versions of WINC-08 are shown in Figure 1-2 and described below.

- a. Single WINC consists of one WINC-08 controller and one

Winchester disk drive interfaced to either an LSI-11 or a PDP-11; this emulates two RL02 drives.

- b. Double WINC consists of one WINC-08 controller and two

Winchester disk drives interfaced to either an LSI-11 or a PDP-11; this emulates four RL02 drives.

- c. WINC/FLEX consists of one WINC-08 controller with one Winchester disk drive and one FLEX-02 controller with one floppy disk drive; this emulates two RL02 drives and one RX02 drive.

## 1.5 EMULATION CHARACTERISTICS

1.5.1 RL02 EMULATION

RT-11 or RSX-11M software transparency is achieved by two fundamental WINC design features:

- a. The WINC firmware specifically emulates the RLO2 disk system.

- b. The dual 8-inch Winchester drives controlled by the WINC-08 have RL02-compatible formats with individual capacities of 20.8 megabytes per drive (23 megabytes per drive unformatted).

Figure 1-2. WINC-08 Standard Configurations

Note

A 10.4-megabyte Winchester disk drive is also supported by the WINC-08, but this unit is not available through AED.

## 1.5.2 RX02 EMULATION

The substitution of the second 8-inch Winchester drive with an 8-inch floppy disk drive allows DEC RX02 emulation. This floppy disk drive, attached to the AED FLEX-02 controller, emulates the RX02; the dual head of the floppy disk drive allows storage capacity of one megabyte per diskette. The format of the diskette is compatible with that of the RX01, RX02, or RX03 (double sided RX02).

## 1.6 SUPPLIED SOFTWARE

AED diagnostic programs are supplied on the Winchester drive or on a FLEX-02 diskette. If the WINC-08 controller is purchased separately, the diagnostic routines must be purchased separately from AED with RX01 or RX02 format specified. All AED diagnostics operate under the RT11 operating system. The RT11 operating system is not provided.

The diagnostic routines consist of:

- a. Winchester media intitialize

- b. ECC diagnostic

- c. Data diagnostic

## 1.6.1 INITIALIZATION

Before the WINC-08 Winchester drives or the floppy diskettes may be used, they must be initialized with header information and data fields. Winchester drives received from AED will be preinitialized. Winchester drives not received from AED should be initialized using the initialization program described in paragraph 3.3 of this manual.

1.6.2 DATA DIAGNOSTIC (WINCHESTER) -- RLMFD

This diagnostic routine writes and checks data on the disk and is used to verify data integrity of the entire system, including media if desired. Complete information on the data diagnostic routine is presented in paragraph 4.4.

1.6.3 DATA DIAGNOSTIC (FLOPPY DISK)

The DEC diagnostic program (vendor no. #ZRXDAO.BIC) will run without modification on the FLEX-02 controller. Refer to the DEC User's Guide for operating instructions on this program. Additional information on the floppy disk data diagnostic is given in paragraph 4.6.

1.6.4 ECC DIAGNOSTIC (WINCHESTER DISK) -- RLMFC

The WINC-08 error correction code (ECC) diagnostic routine forces the disk sectors to contain data errors such that the ECC logic may be exercised and tested. Complete information on the ECC diagnostic is covered in paragraph 4.5.

1.7 WINC-08 SPECIFICATIONS

WINC-08 specifications are presented in Table 1-1.

## Table 1-1. WINC-08 Specifications

## Physical:

Chassis size: 5.25" H x 17.62" W x 26.5" L Weight: single drive -- 40 lb double drive -- 55 lb Mounting method: desk top or standard 19-inch rack

## Electrical:

|                           | System Configuration |                   |

|---------------------------|----------------------|-------------------|

| Input Voltage Range       | Single Drive         | <u>Dual Drive</u> |

| 100 or 115 VAC            | 157 watts            | 248 watts         |

| 50 or 60 Hz, Single Phase | 1.19 amps            | 1.83 amps         |

| 200 or 230 VAC            | 157 watts            | 248 watts         |

| 50 or 60 Hz, Single Phase | 0.60 amps            | 0.92 amps         |

Environmental:

Temperature

| Operating:     | 41 <sup>0</sup> through 113 <sup>0</sup> F (5 <sup>0</sup> through 45 <sup>0</sup> C)                                                                                                |  |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Non-operating: | Maximum gradient is 10 <sup>°</sup> C/hour<br>-40 <sup>°</sup> through 140 <sup>°</sup> F (-40 <sup>°</sup> through 60 <sup>°</sup> C)<br>Maximum gradient is 50 <sup>°</sup> C/hour |  |  |

| Humidity:      | 20% through 80% R/H                                                                                                                                                                  |  |  |

| Altitude:      |                                                                                                                                                                                      |  |  |

| Operating:     | 12,000 feet (3,700 meters) or below                                                                                                                                                  |  |  |

| Non-operating: | 43,000 feet (12,900 meters)                                                                                                                                                          |  |  |

#### 1.8 DISK DRIVE SPECIFICATIONS (FLOPPY)

Floppy disk drive specifications are presented in Table 1-2.

## 1.9 DISK DRIVE SPECIFICATIONS (WINCHESTER)

Winchester disk drive specifications are presented in Table 1-3.

## 1.10 QUALITY ASSURANCE

At AED, quality and reliability stand as major objectives, supported and promoted throughout all levels of management and production. Quality controls meet or exceed industry and government standards and requirements. AED treats product quality as a matter of policy and of pride.

Product quality is not considered as solely a function of inspection and control; it underlies all policies, procedures, and management responsibilities. The complete quality program encompasses all management systems from product conception and planning through shipment and post-shipment support.

The formal quality assurance policy is documented in AED's Quality Assurance Manual. Additional information on AED's quality standards is available from AED.

| Table 1-2 | . Disk | Drive | Specifications | (Floppy) |

|-----------|--------|-------|----------------|----------|

|-----------|--------|-------|----------------|----------|

| Capacity (formatted)     | 1.0 Mbyte     |

|--------------------------|---------------|

| Heads                    | 2             |

| Tracks                   | 77            |

| Sectors/track            | 26            |

| Bytes/sector             | 256           |

| Avg rotational latency   | 87 ms         |

| Positioning times:       |               |

| minimum                  | 18 ms         |

| average                  | 91 ms         |

| maximum                  | 243 ms        |

| DMA transfer rate (peak) | 64 Kbytes/s   |

| Net throughput           | 18.3 Kbytes/s |

# Table 1-3. Disk Drive Specifications (Winchester)

|                          | 11.7 Mbyte Drive | 23.4 Mbyte Drive |

|--------------------------|------------------|------------------|

| Total formatted capacity | 10.4 Mbyte       | 20.8 Mbyte       |

| Mapping emulation        | 1 ea. RL02       | 2 ea. RL02       |

| Number of platters       | 2                | 4                |

| Number of heads:         |                  |                  |

| R/W                      | 4                | 8                |

| clock                    | 1                | 1                |

| Number of cylinders      | 244              | 244              |

| Tracks/cylinder          | 4                | 8                |

| Sectors/track            | 42               | 42               |

| Bytes/sector             | 256              | 256              |

| Recording density        | 6100 BPI         | 6100 BPI         |

| Recording density        | MFM              | MFM              |

| Transfer rate (peak)     | 593 Kb/sec       | 593 Kb/sec       |

| Net throughput           | 219 Kb/sec       | 219 Kb/sec       |

| Track density            | 195 TPI          | 195 TPI          |

| Rotational speed         | 2964 rpm         | 2964 rpm         |

| Avg rotational latency   | 10.1 ms          | 10.1 ms          |

| Positioning time:        |                  |                  |

| minimum                  | 30 ms            | 30 ms            |

| average                  | 70 ms            | 70 ms            |

| maximum                  | 140 ms           | 140 ms           |

|                          |                  |                  |

## Section 2

## INSTALLATION

## 2.1 GENERAL

Installation of your WINC-08 controller is simple and straightforward. It is designed for either desk-top or standard 19-inch rack mounting. As shipped from the factory, it is supplied with four rubber feet. When the supplied rubber feet are installed on the bottom of the WINC-08, it is ready to be set on a desk for installation.

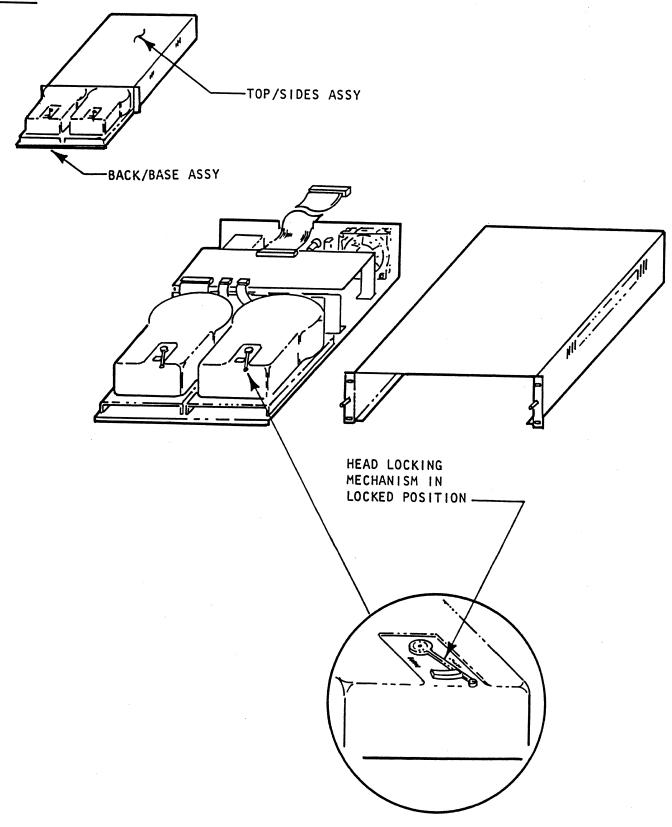

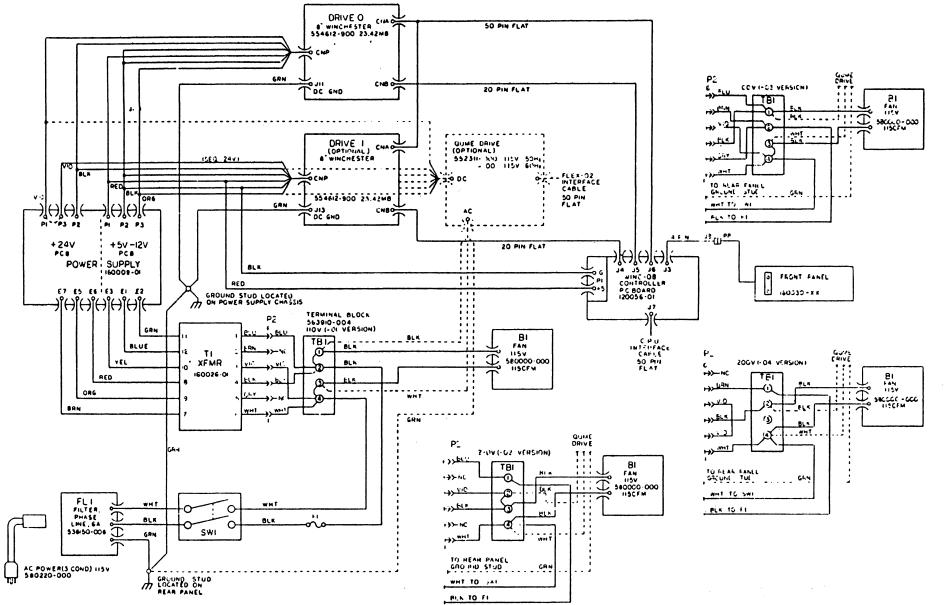

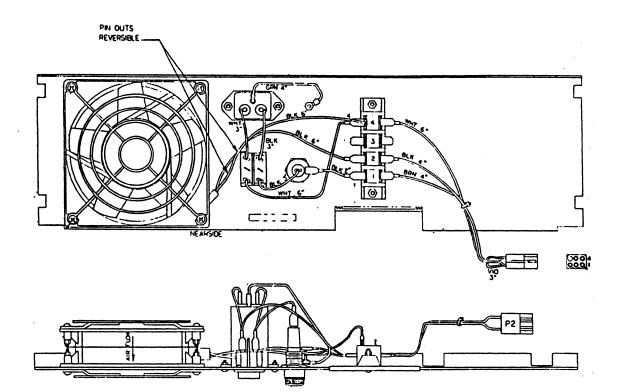

For rack mounting (without chassis slides), the top/sides assembly is fastened to the rack. This forms a shell from which the base/back assembly -- which includes the drives, power supply, and AC wiring -slides in or out of the top/sides assembly for servicing. Step-by-step rack mounting instructions are included in this section.

## 2.2 SITE REQUIREMENTS

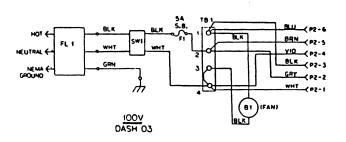

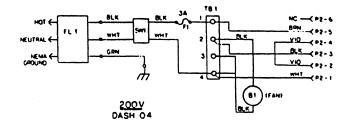

The area intended for operation of your WINC-08 controller should be clean and well ventilated. Ambient temperature during operation should range from  $41^{\circ}$  through  $113^{\circ}F$  (5° through  $45^{\circ}C$ ) and humidity should be 20% through 80% R/H. Altitude operating limits are from zero to 12,000 feet (to 3,700 m). Power to the WINC-08 controller must be singlephase, three-wire AC. The WINC-08 power requirements are as follows:

a. Voltage: 100 VAC or 115 VAC 200 VAC or 230 VAC

b. Frequency: 60 + 3 Hz or 50 + 3 Hz

## c. Current:

|                  | Single<br>Winchester | Double<br>Winchester | Winchester<br>and Floppy |

|------------------|----------------------|----------------------|--------------------------|

| (100 or 115 VAC) | 1.2 A max.           | 1.8 A max.           | 1.7 A max.               |

| (200 or 230 VAC) | 0.6 A max.           | 0.9 A max.           | 1.3 A max.               |

## 2.3 UNPACKING

The carrier is responsible for damage incurred during shipment. In case of damage, have the carrier note the damage on both the delivery receipt and the freight bill, then notify your AED customer service representative so that the necessary insurance claims can be initiated.

After opening the shipping container, use the packing slip to verify receipt of the individual items listed on the slip. Retain the shipping container and packing material for possible later reuse should return of the equipment to the factory be necessary.

Initial inspection of the WINC-08 is as follows:

- a. Located on the rear panel is a black and white foil tag containing the unit configuration number, unit serial number, and unit power requirements. Verify that the power requirements of the unit match those that were ordered.

- b. Set the WINC-08 unit on a flat, nonabrasive work surface.

- c. Remove the ten screws securing the top cover assembly and remove the top cover for inspection of the interior.

d. Grasp the front panel (bezel) and pull it away from its snap-on fasteners.

## CAUTION

Movement of the front panel is limited by the attached wiring cable.

- e. Disconnect the cable connector to free the front panel (bezel) (see Figure 2-1f).

- f. Verify that the WINC-08 drive(s) head locking mechanism is engaged, i.e., that the white nylon arm is in the right most position as shown in Figure 2-1b.

- g. If WINC/FLEX configuration, verify that the cardboard shipping diskette is in place for double-sided floppy drives.

- h. Look for any loose hardware that may have resulted from shipping shock and vibration.

- i. Apply finger pressure to each connector to ensure that the cable connectors are firmly seated.

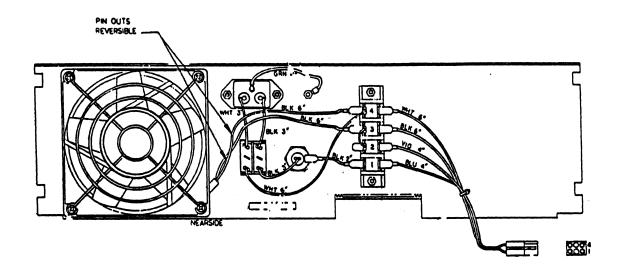

- j. Raise the controller board around its hinged edge to gain access to the power supply board below.

- k. Inspect for loose hardware or connectors on or near the power supply board.

- 1. Replace the top cover and its screws except for the two screws at the top rear, but leave the front panel (bezel) detached.

## 2.4 PHYSICAL INSTALLATION

With the WINC-08 unit unpacked and the initial inspection completed, proceed with the physical installation.

2.4.1 RACK MOUNTING

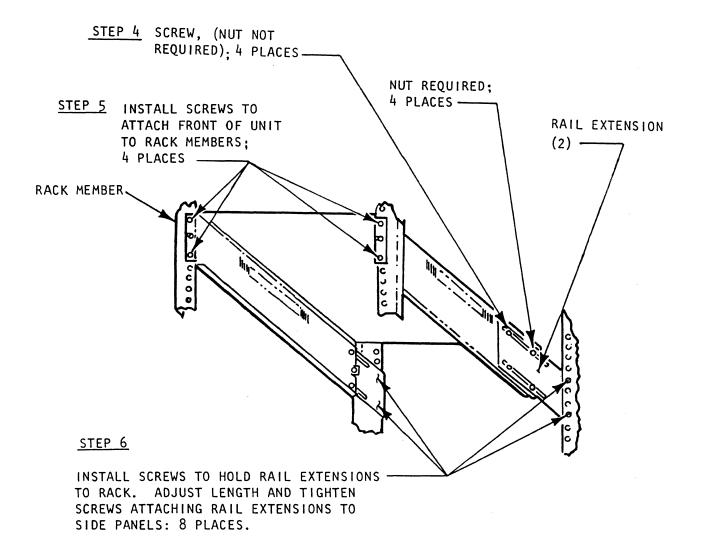

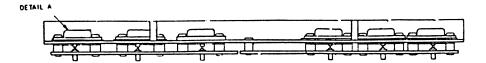

The WINC-08 is designed to mount in a rack that is 19 inches wide, 26 inches deep, and 5-1/4 inches high. Figures 2-1a through 2-1f illustrate the rack mounting procedure.

#### CAUTION

The head locking mechanism should remain in the "LOCKED" position during mechanical and electrical installation.

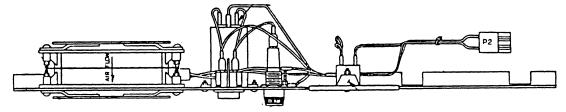

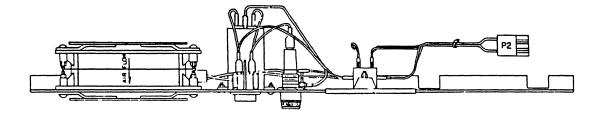

- Step 1. Remove four screws and lock washers from the back panel. Save the screws and lock washers for later use (see Figure 2-1a).

- Step 2. Turn the unit upside down on a nonabrasive surface. Remove the six screws holding the baseplate (see Figure 2-1a).

- Step 3. Turn the unit upright and slide the base/back assembly out of the top/sides assembly (see Figure 2-1b).

- Step 4. Two side rail extensions are provided in the accessory kit. Attach a side rail extension to each side of the top/sides assembly with the eight screws provided, but leave the screws loose (see Figure 2-1c).

- Step 5. Install the top/sides assembly in the rack using four screws each in front of rack (see Figure 2-1c).

- Step 6. Install four screws attaching the rail extensions to the rear of the rack. Adjust the length of the two rail extensions by extending or closing them until the length of the side rails matches the rack (front to rear) as shown in Figure 2-1c. Tighten all rail extension screws.

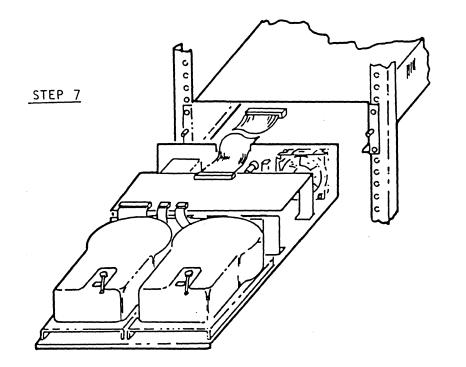

- Step 7. Slide the base/back assembly into the top-sides assembly, making sure that the flat cable(s) is (are) routed over the top edge of the back panel in the groove provided (see Figure 2-1d).

#### Note

The topmost cable should be the WINC-08 cable. The optional bottom cable should be the FLEX-02.

Step 8. Install four screws from the rear of the racks as shown in Figure 2-1e. Attach the AC power cord to the WINC-08.

## Note

DO NOT plug in the power until the Signal Interconnect flat cables have been connected to their associated interface cards as described in Section 2.6.

Step 9. Move the head locking mechanism(s), at the front of the WINC-08, to the "FREE" position (see Figure 2-1f).

Connect the front panel cable and push the front panel (bezel) onto its snap fasteners (see Figure 2-1f).

## CAUTION

The head locking mechanism should be returned to the "LOCKED" position whenever

the system is to be moved. The heads must be at track 0 to allow the locking mechanism to hold the heads from movement. The heads are moved to track 0 by either a SEEK TO ZERO or by issuing a BUS INIT signal. See paragraph 3.2. NEVER move the drive heads when the disk is not spinning.

Step 10. Remove the cardboard "shipping" diskette on units equipped with the double-sided floppy option.

#### CAUTION

Failure to remove this cardboard protector could result in damage to the drive motor after power on.

## 2.5 ELECTRICAL INSTALLATION

2.5.1 AC POWER CONNECTION

The WINC-08 requires a single phase, three-wire AC power source as described in paragraph 2.2. The WINC-08 comes equipped with a detachable AC power cord.

2.5.2 SYSTEM GROUND

A single-point grounding scheme should be used to minimize ground loop problems. Figure 2-2 represents a typical single-point ground for a single-CPU system.

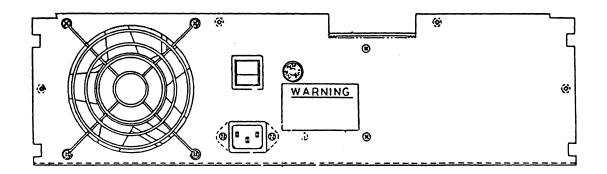

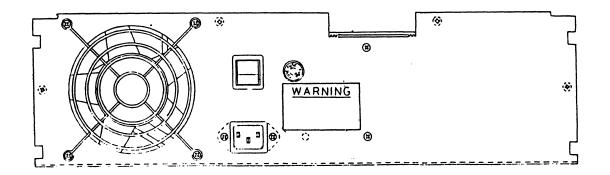

The common ground point, to which individual equipment grounds are connected, should be located electrically close to the building ground, which is typically available at the main power distribution panel. (BOTTOM REAR VIEW)

STEP 1 REMOVE SCREWS AND LOCK WASHERS AND SAVE: 4 PLACES-0 STEP 2 REMOVE SCREWS AND LOCK WASHERS AND SAVE; 6 PLACES-

Figure 2-1a. Removal of Top/Sides Assembly

.

Figure 2-1b. Winchester Drive Head Lock Mechanism

Figure 2-1c. Rack Installation

Figure 2-1d. Assembly into Top/Sides

Figure 2-1e. Top/Sides Installation

<u>STEP 9</u>

If the CPU is rack-mounted and if a good electrical connection between the CPU ground and the rack mount can be ensured, then a support rail attachment point may be used as the single-point ground. In such a system, all grounds (from controllers and drives and power supplies) should be returned to this single-point ground, thereby minimizing ground currents. The same single-point grounding system, shown in Figure 2-2, applies to desk-top system.

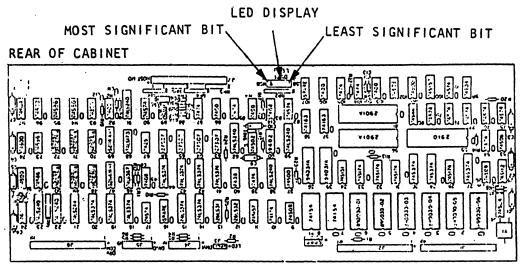

## 2.6 SIGNAL INTERCONNECTION TO HOST

There will be one or two flat cables between the WINC-08 unit and the host computer, depending on the mix of Winchester and floppy disk drives used in the particular configuration. Table 2-1 lists the various connections required for the standard configurations.

Table 2-1. WINC-08 Cable Configuration

| WINC-08 Configuration                        | Number of Cables to Host Computer                                                                                                                                        |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| One or two Winchester drives                 | One cable from WINC-08 to the host-<br>imbedded interface card.                                                                                                          |

| One Winchester drive and one<br>floppy drive | Two cables from WINC-08. The top<br>cable to the host-imbedded interface<br>card and the bottom cable to the<br>floppy drive's host-imbedded FLEX-02<br>controller card. |

## 2.7 WINC-08 TO PDP-11 HOST INSTALLATION

2.7.1 PDP-11 INTERFACE CARD MODIFICATION INSTRUCTION

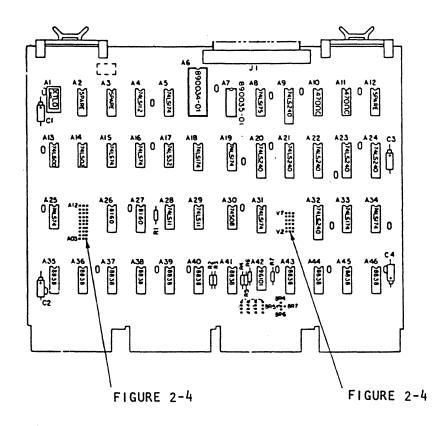

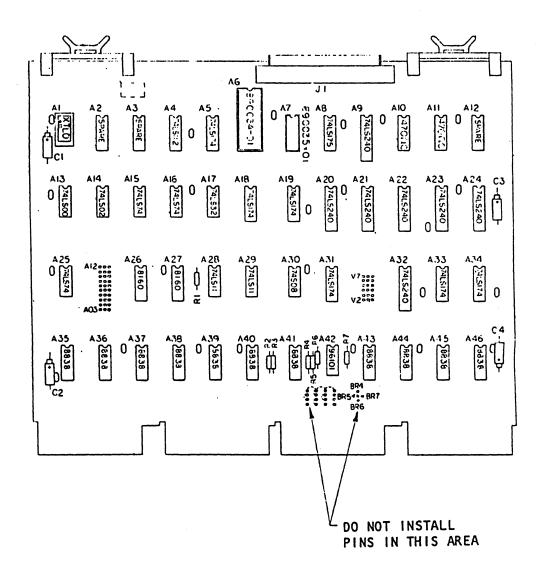

The interface card to connect the WINC-08 to the PDP-11 host computer (AED part no. 120068-01), is shown in Figure 2-3. As supplied, this

Figure 2-2. System Grounding Diagram

Figure 2-3. PDP-11 Interface Card

card is set for the standard Device Address and Interrupt Vector Address and for most applications will be used in this configuration. If the Device and Interrupt Vector Addresses used are not standard, they may be altered as described below. If standard Device and Vector Addresses are used proceed to paragraph 2.7.2.

The standard Device Address bits are A0 through A17; A0, A1, and A2 are factory-set to 0, and bits A13 through A17 are factory-set to 1. Device Address bits A3 through A12 are user-selectable, and are preset at the factory to the standard DEC configuration as shown in Figure 2-4.

interrupt Vector Address bits V0, V1, and V8 are factory-set to 0 and are not user-selectable. Bits V2 through V7 are user-selectable and are preset at the factory to the standard DEC configuration as shown in Figure 2-4.

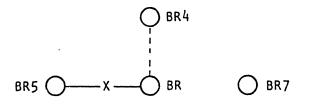

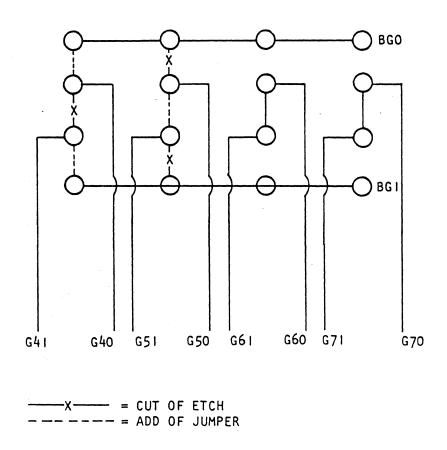

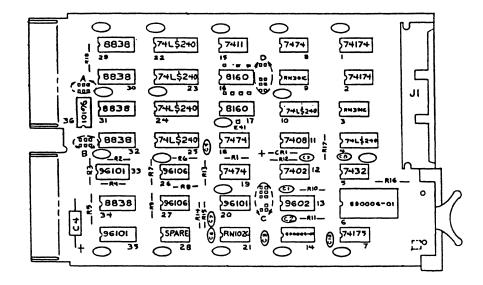

The Interrupt Priority Level is set for level 5 on the PDP-11 Interface board. It is selectable for levels 4 through 7. If the user finds it necessary to change the priority level the following steps must be followed:

- a. Refer to the PDP-11 Interface card and Figure 2-5. On the lower right hand corner of the board, the etch between BR and BR5 must be cut.

- b. Connect a jumper from BR to the desired priority level (BR4 through BR7).

- c. Cut the connection between BGO and G50.

- d. Cut the connection between BGI and G51.

- e. Connect a jumper between BGO and the desired level (G40 through G70).

| DEVICE ADDRESS:                    | PLUG SELECTABLE FROM 760,000 TO 777,777 OCTAL,<br>IN FOUR WORD INCREMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STANDARD OCTAL<br>DEVICE ADDRESS:  | 7 7 4 4 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                    | SET SELECTABLE SET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| STANDARD BINARY<br>DEVICE ADDRESS: | 1 1 1 1 1 1 1 0 0 1 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                    | ~ \u019 \u01 |

| PCB LABELING:                      | A15<br>A15<br>A15<br>A15<br>A15<br>A15<br>A15<br>A15<br>A15<br>A15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SHORTING PLUG<br>PLACEMENT:        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TEACENENT.                         | • • • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                    | 0044044444                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VECTOR ADDRESS:                    | PLUG SELECTABLE FROM 000 TO 377 OCTAL,<br>IN TWO WORD INCREMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| STANDARD OCTAL<br>VECTOR ADDRESS:  | 1 6 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| STANDARD BINARY<br>VECTOR ADDRESS: | SET         SELECTABLE         SET           0         0         1         1         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PCB LABELING:                      | 8 Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SHORTING PLUG<br>PLACEMENT:        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Figure 2-4. WINC-08/PDP-11 (Unibus) Interface

Figure 2-5. PDP-11 Interrupt Priority Level Jumpers

#### Note

Cable connectors are not keyed, therefore, it is necessary to identify the Pin 1 position on both the male and female plug connectors by means of the imprinted arrow on the top edge of each connector. The flat cable also identifies pin 1 by a red stripe. When connecting the plugs, these arrows (pin 1) must be aligned to ensure correct pin and circuit connections.

- e. Connect the WINC-08 cable to its mating interface card connector, observing the arrow alignment requirement as mentioned in the above note.

- f. Slide the PDP-11 chassis back into its rack mount, being careful not to tangle or distort the flat cable excessively.

- g. Turn on the power to the host.

- h. Plug in the WINC-08 AC power cord and place ON/OFF switch in ON position.

### Note

Power to the WINC-08 and host should be applied simultaneously. If power is applied separately the WINC-08 should be the last unit to receive power.

j. Proceed with the software installation (see Section 3).

- f. Connect a jumper between BGI and the desired level (G41 through G71).

- g. Cut the connection between the desired GXO and GXI level (G40 to G41, G50 to G51, G70 to G71).

- h. Connect desired GXO to the desired GXI. Figure 2-5 shows the changes required to change priority to level 4.

2.7.2 PDP-11 (UNIBUS) INSTALLATION

Standard installation instructions for the PDP-11 Unibus are as follows:

- a. Remove power from the system.

- b. Slide the PDP-11 chassis to its outermost position. This exposes the card slots located on the left hand side of the PDP-11 chassis, as viewed from the front.

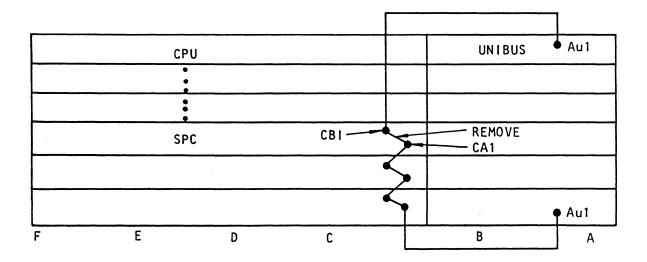

- c. Insert the WINC-08 Unibus interface card into the next available quad-wide small peripheral controller (SPC) slot. The WINC-08 is a DMA device so the Nonprocessor Grant Signal (NPG), wired to the SPC slot, must be broken. Break the connection (using a wire-unwrap tool) between pin CA1 and CB1 on the back panel corresponding to the slot in which the WINC-08 interface card resides (see Figure 2-6).

- d. Route the WINC-08 flat interconnect cable through the chassis and rack members to enable it to be connected to the edge card connector on the Unibus interface card without severe twisting or bending of the flat cable.

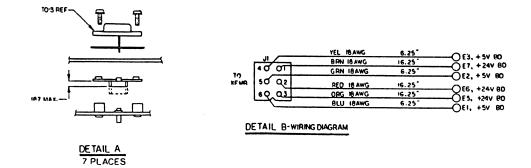

PIN SIDE VIEW

Figure 2-6. Removal of Nonprocessor Grant Signal

# 2.8 WINC-08 TO LSI-11 INSTALLATION

2.8.1 LSI-11 INTERFACE CARD MODIFICATION INSTRUCTIONS

The LSI-11 interface card is supplied with the standard DEC address, vector, and interrupt priority. Contact AED if modifications are required.

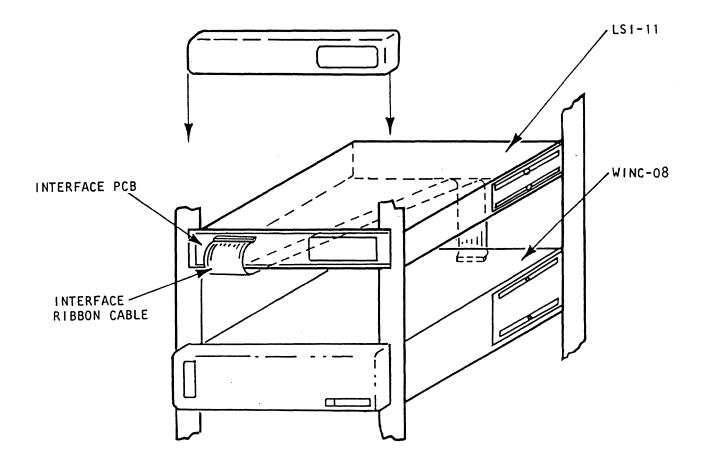

2.8.2 LSI-11 (Q-BUS) INSTALLATION

One WINC-08 flat cable is supplied with its respective LSI-11 interface card for configurations with one or two Winchester disk drives. If a floppy disk is supplied, perform the following installation steps for the Winchester and see paragraph 2.9 for the floppy disk drive installation.

- a. Turn off the host computer (LSI-11) power supply.

- b. Remove the LSI-11 front bezel (pull straight out on bezel). See Figure 2-7.

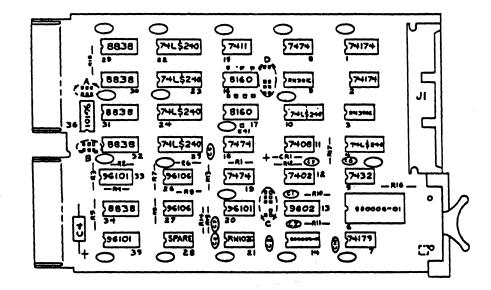

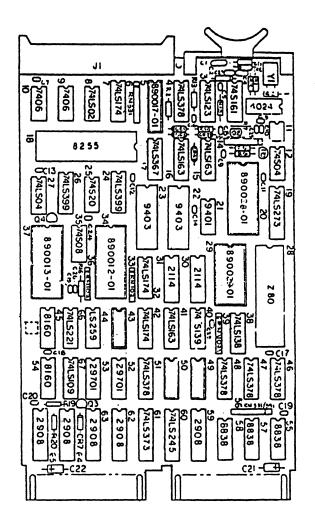

- c. Plug the WINC-08 dual wide interface card (see Figure 2-8) into the next available dual wide slot (either left or right hand).

- d. Connect the Q-bus (flat cable) from the WINC-08 to the edge connector on the Q-bus interface card.

#### Note

Cable connectors are not keyed, therefore, it is necessary to identify the pin 1 position on both the male and female plug connectors by means of the imprinted arrow on the top edge of each connector. The flat cable also identifies pin 1 by a red

Figure 2-7. LSI-11 Installation

Figure 2-8. LSI-11 Interface Card

stripe. When connecting the plugs, these arrows must be aligned to ensure correct pin and circuit connections.

- e. Proceed with paragraph 2.9 (FLEX-02 Installation) if you have a floppy disk drive. If you do not have a floppy proceed to the next step.

- f. Replace the LSI-11 front bezel.

- g. Turn on the LSI-11 power supply.

- h. Plug in the WINC-08 AC power cord and place ON/OFF switch in ON position.

- i. Proceed with the software installation (see Section 3).

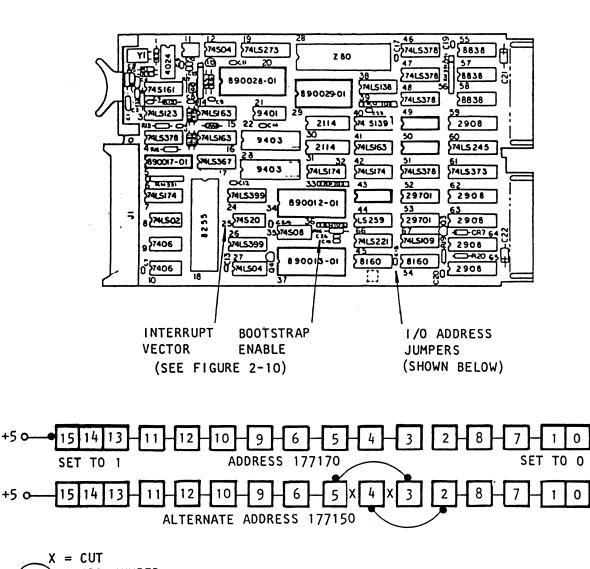

# 2.9 FLEX CONFIGURATION JUMPERING AND FLEX-02 INSTALLATION LSI-11(Q-BUS)

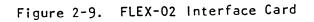

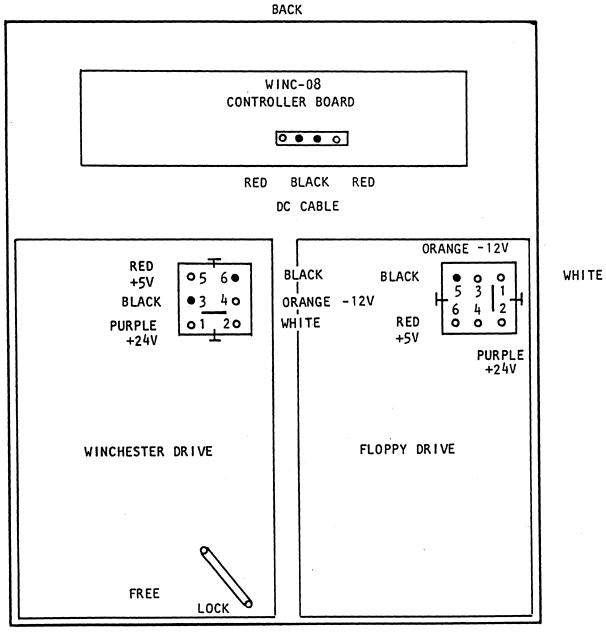

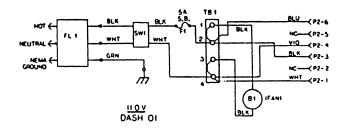

The I/O address of the FLEX can be jumpered within the range of 160000 to 177774 (see Figure 2-9). Bits 15, 14, and 13 are factory set to 1, and bits 1 and 0 are factory set to 0. When shipped from AED, the standard 1/O address of 177170 is set. The alternate address of 177150 is set as shown in Figure 2-9.

The interrupt vector and the bootstrap selection on the FLEX can be selected. The interrupt vector and Auto-bootstrap can be selected from a set of four as shown in Figure 2-10. Other vectors must be special ordered from AED. To inhibit the FLEX bootstrap, install a jumper from E13 to E14. If Auto-bootstrap is selected on the FLEX, then the CPU must be set for the bootstrap mode with power-up. The bootstrap starting address is 173000. The bootstrap program occupies 512 bytes in the address range 173000 to 173776. All other bootstrap devices must be disabled when the FLEX-02 bootstrap is enabled.

The FLEX-02 is compatible with the LSI-11/23 four-level priority interrupt feature. It must be installed in the position-dependent configuration and can only be operated on priority level 4, as described in the LSI-11 microprocessor handbook.

- a. Plug the dual-wide FLEX-02 controller card into the desired dual-wide slot (either left- or right-hand slot).

- b. Connect the FLEX flat cable from the WINC-08 with a FLEX-02 unit to the edge connector of the FLEX-02 controller interface card.

### Note

Cable connectors are not keyed, therefore, it is necessary to identify the pin 1 position on both the male and female plug connectors by means of the imprinted arrow on the top edge of each connector. The flat cable also identifies pin 1 by a red stripe. When connecting the plugs, these arrows must be aligned to ensure correct pin and circuit connections.

- c. Proceed with paragraph 2.9 (FLEX-02 Installation) if you have a floppy disk drive. If you do not have a floppy proceed to the next step.

- d. Replace the LSI-11 front bezel.

- e. Turn on the LSI-11 power supply.

• = ADD JUMPER

- f. Plug in the WINC-08 AC power cord and place ON/OFF switch in ON position.

- g. Proceed with the software installation (see Section 3).

#### Section 3

# SOFTWARE INSTALLATION

#### 3.1 INTRODUCTION

After the WINC-08 is connected and the power is applied, software installation, including media initialization, may be performed. This section explains bootstrap operation and media initialization. Diagnostic operations are explained in Section 4. Media initialization and diagnostics are optional operations if the WINC-08 is received as a complete system, because these tasks have been performed at the factory.

Note

For WINC-08 operation a DEC-supplied DL driver must be a part of the user's Operating System. A SysGen is not needed if a loadable DL driver is used. Refer to DEC's Operating System manual for additional details.

The first phase of software installation is to verify the power-up sequence. When power is applied to the WINC-08, a power-up diagnostic will be executed to check the internal functions.

Microprocessor ALU operations and conditional branches are checked, and verification of the internal buffer follows. The WINC-08 then will attempt to become bus master, after which the controller and drive ready bits will be posted in the interface registers. After power is applied, the LED display for drive 0 should be lit. If no LED's are lit, refer to Section 4 for troubleshooting information. If the LED's for drive 0 and drive 1 are both lit, an error has occured in the unit. If an error is detected, the WINC-08 will trap and accept no other commands, and an error code will be posted in the internal LED display.

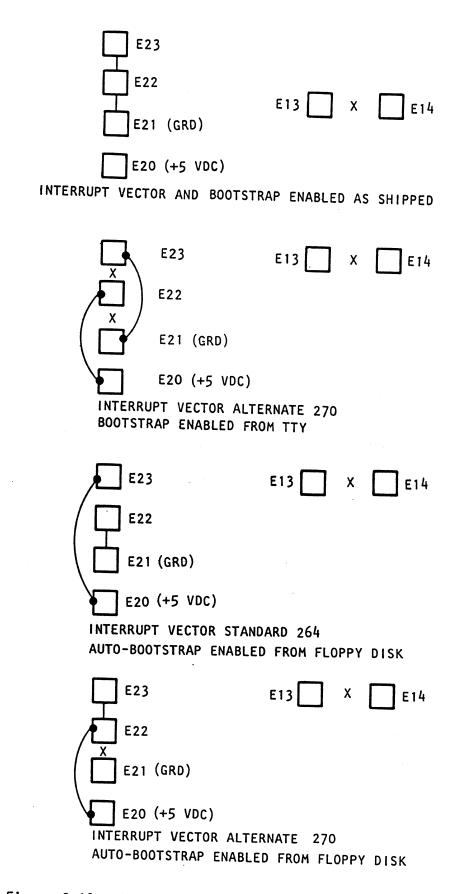

This internal LED display is located on the WINC-08 controller board. See Figure 3-1, which shows the controller board and the LED display.

FRONT OF CABINET

Figure 3-1. WINC-08 Controller Board with LED Display

The error codes, as displayed in the WINC-08 LED display (shown in Figure 3-1), are as follows:

| Error Code | (1 = LED lit)<br>(0 = LED off) | Description                     |

|------------|--------------------------------|---------------------------------|

| 11000001   |                                | ALU or conditional test failure |

| 11000010   |                                | FIFO status error               |

| 11000011   |                                | Buffer data/Address error       |

| 11000100   |                                | FIFO data error                 |

| 11000101   |                                | Bus master error                |

The WINC-08 will remain in an error trap until a BUS INIT signal is received from the CPU, after which it will again attempt the power-up diagnostic tests. Section 4 of this manual contains troubleshooting information.

Following the power-up diagnostics, the WINC-08 will check to determine if the drives are up to speed; if they are, a rezero (restoring the heads to Track 0) will be issued. If the drives are not up to speed, the rezero will be postponed until the first seek command. On power-up, DRIVE ZERO will be selected and, when the drive is ready, the LED on the front panel of the WINC-08 will turn on.

### 3.2 BOOTSTRAP METHODS

The system can now be booted from any bootable device on the bus.

The WINC-08 will operate with any standard bootstrap procedure that is loaded onto the WINC-08. There is no bootstrap resident on the Winchester disk drives when shipped.

The WINC-08 bootstrap may also be performed manually, using direct I/0 commands.

First, generate a BUS INIT signal. With an LSI-11, this is done by storing a HALT instruction into location zero, then executing LOCATION ZERO as follows:

| Ente      | ۲             | Display                     |

|-----------|---------------|-----------------------------|

| BREAK KEY | (BREAK)       | @ (prompt)                  |

| 0/        | (ZERO SLASH)  | @ 0/04000_ <b>0</b>         |

| 0 CR      | (ZERO RETURN) | @ <b>0/</b> 04000_ <b>0</b> |

| OG        | (ZERO G)      | @ 0 <b>G</b>                |

|           |               | <b>@</b> 000002             |

On most PDP-11 (Unibus) systems, a BUS INIT signal can be generated by pressing an INIT switch.

### 3.2.1 EXAMPLE BOOTSTRAP FROM UNIT ZERO

The BUS INIT signal will cause the drives to rezero and the bus address, disk address, and word-count registers to be set to zero. Issuing a READ command will cause 40 sectors, starting with sector zero, from disk drive zero, to be read into memory. The memory is loaded starting from location zero and creates another BUS INIT signal, clearing the CSR ERROR STATUS.

For LSI to load the bootstrap program follow the procedure given below:

|                 | Enter                    | Display                |

|-----------------|--------------------------|------------------------|

| <b>774</b> 400/ | (CSR ADDRESS SLASH)      | @ <b>774400/</b> 00201 |

| 14 CR           | (READ COMMAND)           | @ 774400/00201 14 CR   |

| 0G              | (ZERO G = START AT ZERO) | @ 0 <b>G</b>           |

This will return the title of the booted operating system and a prompt.

Usually, only sectors zero and one are needed (the others are read to avoid the requirement of setting the word-count register). In many systems, execution of an OG (ZERO G) will result in a BUS INIT signal, which will clear the WINC-08 registers.

If a boot to a logical unit other than zero is required, the REGISTER CLEAR must be prevented. This may be done by setting the "PC" register and issuing a PROCEED request.

3.2.2 EXAMPLE BOOTSTRAP FROM UNIT TWO

For LSI Protocol only, generate a bus init signal, then:

|                 | Enter                        | Display                             |

|-----------------|------------------------------|-------------------------------------|

| BREAK KEY       | (BREAK)                      | <b>e</b>                            |

| 0/              | (ZERO SLASH)                 | @ <b>0/</b> 040000                  |

| 0 CR            | (ZERO RETURN)                | @ 0/040000_ <b>0</b> (CR)           |

| OG              | (ZERO G)                     | @ 0G                                |

|                 |                              | <b>@ 000002</b>                     |

| 77440 <b>0/</b> | (CSR ADDRESS SLASH)          | @ <b>774400/</b> 000201             |

| 1014 CR         | (UNIT NO. *256. + 14 RETURN) | @ <b>774400</b> /000201_1014(CR)    |

| 1               | (SLASH)                      | @ <b>/</b> 113215_                  |

| 0 CR            | (ZERO RETURN)                | @ /113215_ <b>0</b> (CR)            |

| \$7/            | (DOLLAR SIGN SEVEN SLASH)    | @ <b>\$7/</b> 000002                |

| 0 CR            | (ZERO RETURN)                | @ <b>\$7</b> /000002 <b>_0</b> (CR) |

| Ρ               | (P)                          | @ P                                 |

This will return the title of the booted operating system and a prompt.

This sequence will read 40 sectors, starting at sector zero of disk drive two, and will then set the program counter to zero and start execution without creating a BUS INIT signal.

# Note

In this sequence the BUS INIT signal, generated by the console "G" command, must be avoided as it will cause the WINC unit register to be reset to zero.

Some processors have a different console monitor or have only front panel switches. In these cases, equivalent sequences should be generated to match the examples given. A typical sequence would be as follows:

For PDP Protocol:

| PRESS: | INIT SWITCH | (GENERATE BUS INIT)     |

|--------|-------------|-------------------------|

|        | L 774400 CR | (LOAD CSR ADDRESS)      |

| ENTER: | D 14 CR     | (ISSUE READ COMMAND)    |

| ENTER: | L 0 .       | (LOAD STARTING ADDRESS) |

| ENTER: | S           | (START BOOTSTRAP)       |

#### Note

If a FLEX-02 is present, a bootable diskette may be used to boot the WINC-08 by entering the desired DY number.

3.2.3 FLOPPY DISK BOOTSTRAP METHODS

The FLEX-02 bootstrap starting address is 173000.

To boot from the FLEX-02, when power is applied and Autoboot is inhibited, perform the following:

| Enter     | Display           |

|-----------|-------------------|

| BREAK KEY | e                 |

| 173000G   | € 1 <b>73000G</b> |

This will return a \$ prompt.

In this case enter the name of the drive where the boot resides.

| Enter | Display |

|-------|---------|

| DY    | \$ DY   |

Note DYO, DY1, DLO, DL1, DL2, DL3, or any other bootable device may be entered.

This will return the title of the operating system.

To boot from the FLEX-02 (after power is applied with Autoboot enabled) place a bootable diskette in Drive 0 and perform the following:

| Enter            | Display            |

|------------------|--------------------|

| BREAK KEY        | e                  |

| 17300 <b>0</b> G | @ 17300 <b>0</b> G |

This will return the title of the operating system.

If the FLEX-02 Autoboot is enabled, the system will boot automatically from the floppy drive upon initial application of power and return the title of the operating system.

### 3.3 INITIALIZATION (RLMFV)

Before the WINC-08 drives may be used, the disk must be initialized by recording header information and data fields. Drives received from AED will be formatted and only an initialization of a directory is needed (i.e., INIT command). Drives not received from AED should be initialized using the program RLMFV.

# 3.3.1 RLMFV INTRODUCTION

The AED WINC-08 initialize-and-format routine (RLMFV) is used to write headers on the disk media and to fill-in and verify the data sectors; it places a record of any bad sectors in the bad block table at the end of the logical disk unit.

#### Note