# AD/FIVE REFERENCE MANUAL

Γ

[

ſ

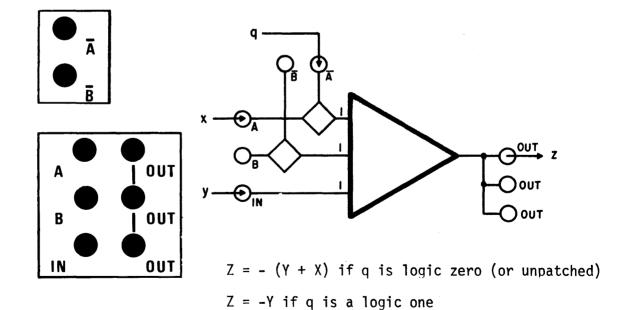

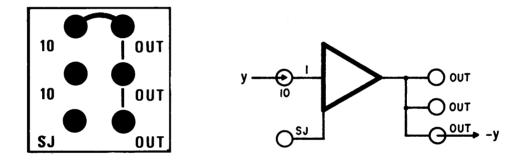

F

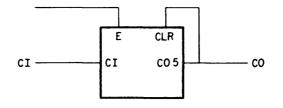

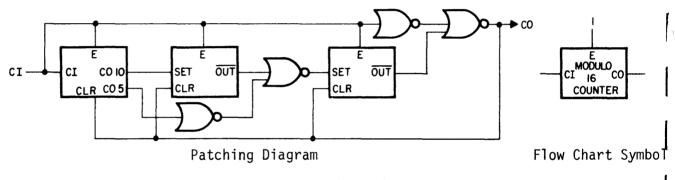

Г

## VOLUME 1 ANALOG

AD APPLIED DYNAMICS INTERNATIONAL

3800 Stone School Road · Ann Arbor, Michigan 48104 · Phone 313-973-1300

## CHAPTER 1 INTRODUCTION

ų'r

## TABLE OF CONTENTS

| 1.0                   | INTRODUCTIONPage                                                                   | 1 |

|-----------------------|------------------------------------------------------------------------------------|---|

| 1.1<br>1.1.1<br>1.1.2 | COMPUTING COMPONENTS<br>Analog Computing Components<br>Logic Computing Components  | 3 |

| 1.2                   | CONTROL AND ADDRESSING SYSTEM                                                      | 4 |

| 1.3                   | HYBRID FEATURES                                                                    | 5 |

| 1.4<br>1.4.1<br>1.4.2 | MAN-MACHINE COMMUNICATIONS<br>Operator Convenience Features<br>Ease of Maintenance |   |

| 1.5                   | MODULARITY AND EXPANSION CAPACITY                                                  | 9 |

## ILLUSTRATIONS

**|**

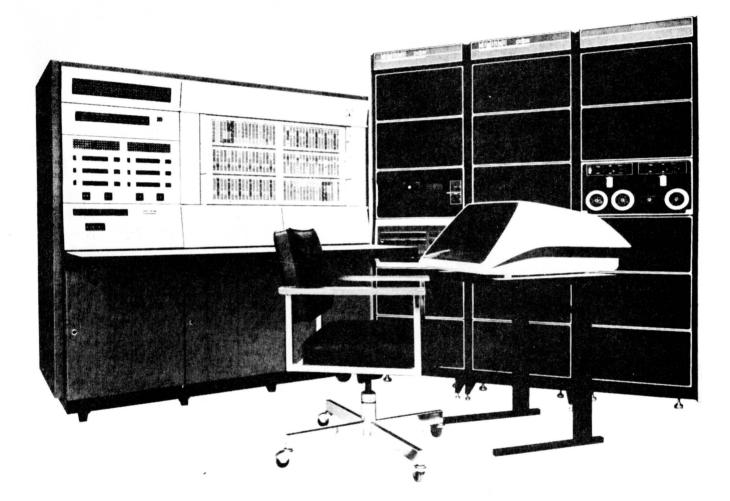

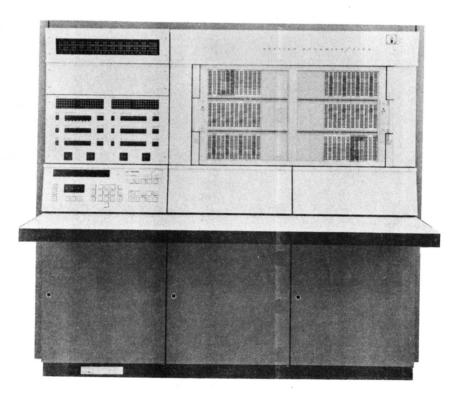

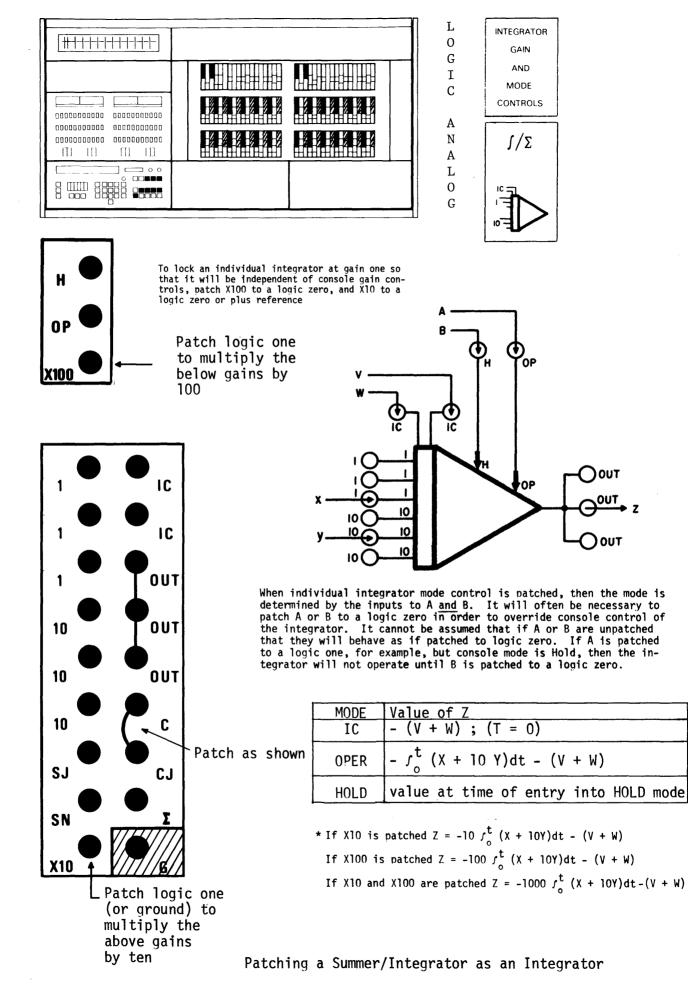

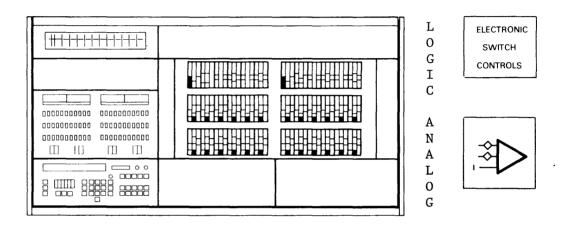

| Figure 1-1 | The AD/FIVE Analog-Hybrid SYSTEM 511                     |   |

|------------|----------------------------------------------------------|---|

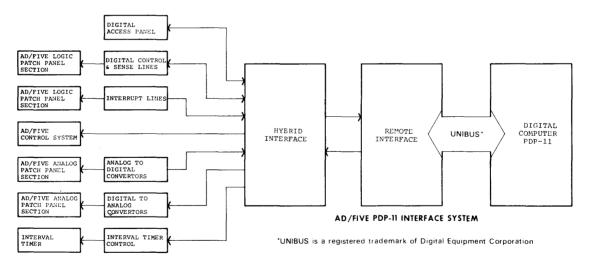

| Figure 1-2 | The AD/FIVE-PDP 11 SYSTEM 511                            | 5 |

| Figure 1-3 | Patchboard Layout and Component Terminations             | 7 |

| Figure 1-4 | Patchboard Module, Patchbay Pin Block, and Circuit Cards | 9 |

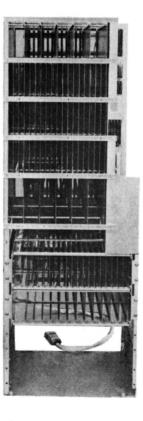

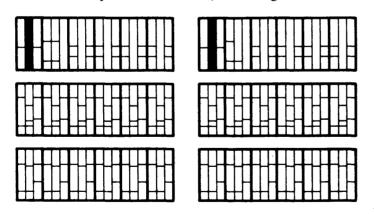

Figure 1-1 The AD/FIVE Analog-Hybrid SYSTEM 511

#### 1.0 INTRODUCTION

The AD/FIVE Reference Manual was written as a comprehensive reference source for the Applied Dynamics AD/FIVE Analog Computer. Chapter 1 introduces the primary features of the AD/FIVE and gives a brief description of the various computing components of the computer. Chapter 2 gives a detailed view of the organization of the AD/FIVE. Chapter 3 discusses the Control System of the AD/FIVE. Chapter 4 gives all directions necessary to achieve proper patching of all patchboard elements of the AD/FIVE. Chapter 5 introduces some essential analog and logic circuits to help the user obtain full benefit of the computing capability of the AD/FIVE computer. Finally, the Arbitrary Function Generator is discussed fully in an appendix to the manual. The primary subject matter is thus logically developed to furnish a working knowledge of the AD/FIVE, and to enable a user unfamiliar with the computer to be able to implement a program and control it as he desires.

The AD/FIVE carries on several new concepts introduced by Applied Dynamics in earlier computers. For those unfamiliar with the design of AD computers, the following discussion should furnish insight into the guiding philosophies of the AD/FIVE Analog Computer.

No significant advance in major computer design would be expected without first making a detailed analysis of the shortcomings and strenghts of present generation equipment and, simultaneously, relating this knowledge to a qualified understanding of the required computational tasks. Applied Dynamics, through its problem-oriented staff, has done this. By building upon a foundation of achievement in scientific computation, AD designers have produced a new state-of-the-art computer system. Advanced concepts in basic configuration, control, component design, patchboard termination, slaving, man-machine communication, and hybrid interfacing all interact to widen the scope of scientific and engineering problems that can be solved.

The predominant philosophy in the development of the AD/FIVE was that it be inherently hybrid in design; this is reflected throughout the control structure, in the patchable logic system, and in an efficient integral hybrid interface. Because hybrid and high speed iterative analog computation places particular demands upon both the dynamic and static performance of the analog computer, emphasis has been placed on overall system performance through component and system design. The result is an optimum balance of static and dynamic accuracy.

In addition to the desirability of having the best computational accuracy obtainable, computer laboratories today place premiums on total system "up-time". This direct measure of return on the invested computer-dollar demands that the manufacturer account for all reliability parameters for each step of design and production. The Applied Dynamics continuous philosophy of conservative circuit design has been incorporated throughout the development of the AD/FIVE to insure compliance with the maximum uptime criterion. A decade of proven product integrity stands behind this assurance of reliability.

1.

The AD/FIVE was designed to provide both simplicity and flexibility of operation. These apparently contradictory goals were met by adopting a philosophy of control by exception. For a small problem, very few patching connections are required to configure the amplifiers, and even on a large problem the number of patching connections is reduced. The control system incorporates this principle to an even greater degree. Designed to be used by both the inexperienced and most sophisticated programmer, the control by exception technique is found throughout the control system. All integrator mode switches and time scale selection switches are internally connected to pushbuttons so that the computer can be operated as a standard analog computer with no logic patchboard patching. However, groups of integrators or individual integrators can be separately controlled by patching. The AD/FIVE control system is as flexible as the operator desires for any specific problem.

The basic design of the AD/FIVE interface was conceived years after the design and application of the initial hybrid computing systems. Consequently, Applied Dynamics was able to incorporate into the AD/FIVE interface its own past knowledge and those innovations resulting from the advance of technology.

The most outstanding feature of the interface is its degree of integration into the AD/FIVE computing system. This was accomplished by assimilation of some of the special purpose devices previously required for hybridization in a basic hybrid system, and also by elimination of the need for other hybrid devices through the design of the control structure. The underlying design assumption was that the AD/FIVE would augment a digital computer.

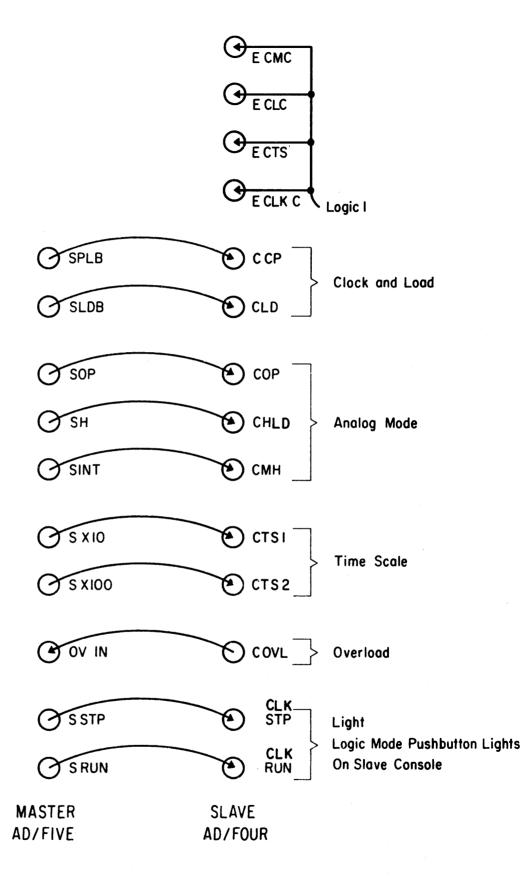

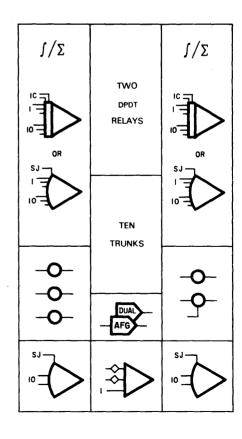

The AD/FIVE control and monitoring structure has been specifically designed for straightforward multiple-console computation in both stand-alone and hybrid system operation. Two of the more obvious advantages inherent in a two-console system over a single computer of equivalent total equipment complement are flexibility and capacity for economical expansion. There is also the corollary benefit of improved overall computing laboratory efficiency from a problem loading standpoint, i.e., simultaneous running of two independent smaller scale problems. An overall reliability increase is also implied because of the system redundance and module-level interchangeability. Full two-console (or more) operation is accomplished through cross-trunking of analog and synchronized logic signals plus analog mode, logic mode, and time-scale control signals. The control functions are easily accomplished by using eight of the interconsole logic trunks. Two-phase clocking of the double-ranked logic elements, and external access to both clocking signal busses at local and console levels insures true synchronous operation between slaved machines. External access to the overriding Master Hold inputs on a console, as well as the ability to inhibit these imputs from the Master Overload bus on the master console, further augments the operational independence of multiple consoles in a system.

The unique modular capability of the AD/FIVE as a system, contrasted to previous computers which have been modularized for components only, introduces a growth capability not previously obtainable. Since the user need not originally invest in complete system wiring at the patchbay, and power and signal wiring to unexpanded areas, he is able to make an original modest investment, and then later he can expand the system as the computing components are expanded. Advanced wiring plane/cabling techniques make this feature possible.

#### 1.1 COMPUTING COMPONENTS

#### 1.1.1 Analog Computing Components

The heart of any analog system is the operational amplifier. The AD/FIVE offers an amplifier of exceptional performance and stability. The solid state amplifier offers the following typical performance features: a voltage range of  $\pm 13$  volts; a gain bandwidth (10K/10K) of 1.5 MHz; noise peak-to-peak (0-800 KHz) of 1.5 Mv; T.I.D.E. at 1.0 KHz of 0.04%; and overload recovery from either voltage or current overload condition of 0.5 Msec. The amplifier is further short circuit proof to any voltage in the range  $\pm 15$  volts.

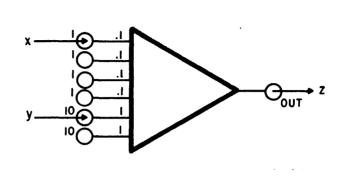

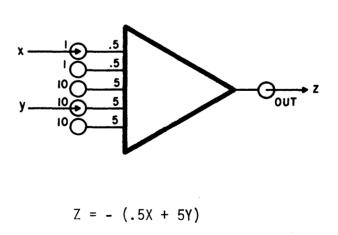

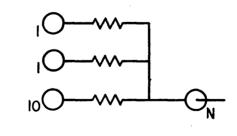

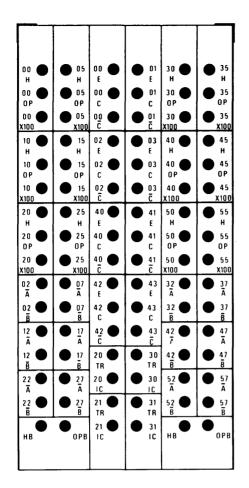

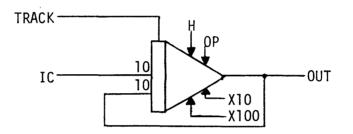

Integrators can be time scaled at X1, X10, X100, and X1000 by individual patched control or by pushbutton operation. Six inputs are available: 3 gains of 1 and 3 gains of 10. Electronic switching of mode control allows operation in IC (Initial Condition), OP (Operate), and H (Hold), whether controlled by pushbuttons or individual patching; switching time is typically 900 nanoseconds between any two modes. Drift in Hold is typically 50 microvolts/sec. at X1 or X10 time scale.

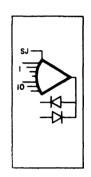

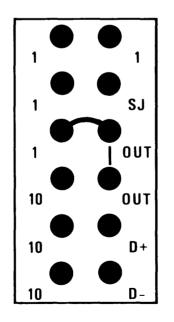

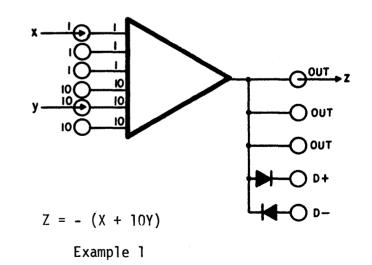

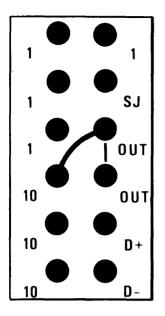

Summer/High Gain amplifiers are available with 3 gain one inputs, 3 gain 10 inputs, 3 outputs, and 2 output diodes. Switch/Summer amplifiers have two electronically switched inputs and one unity gain input. Control of the 900 nanosecond switches is available on the logic patchboard.

Potentiometers are available as servo-set or hand set modules, with a resistance of 5 Kohms, typical resolution of 0.02%, and typical phase shift range at 1.0 KHz of  $\pm 0.1^{\circ}$  for setting greater than 0.1.

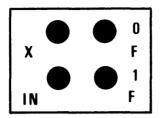

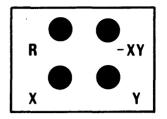

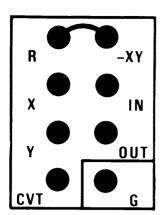

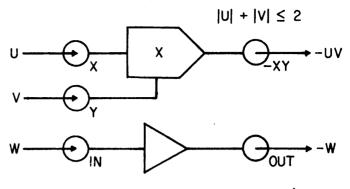

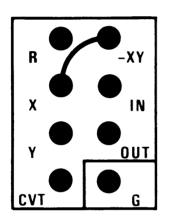

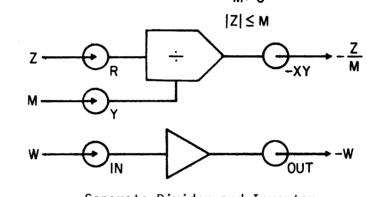

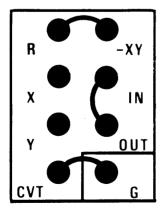

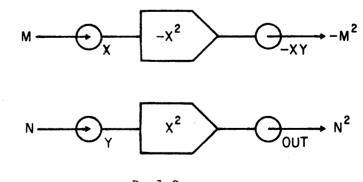

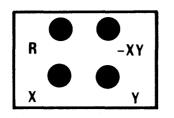

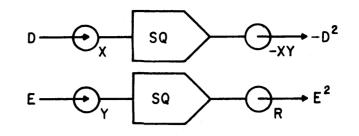

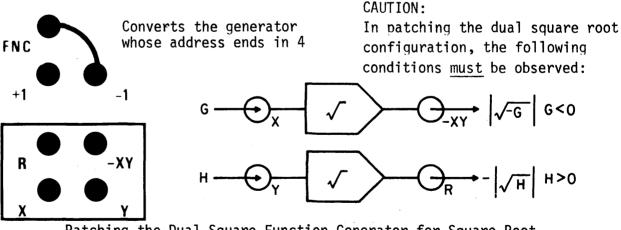

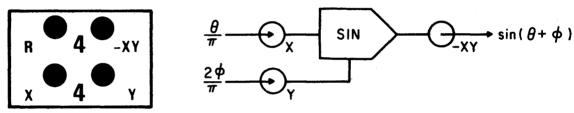

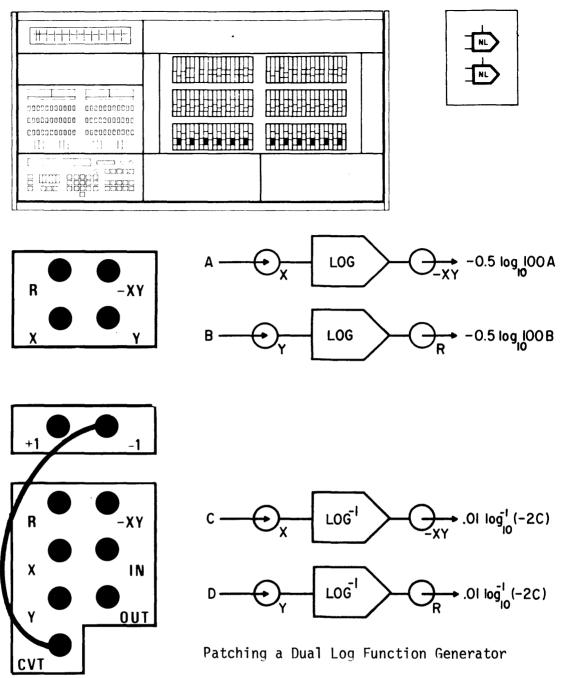

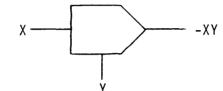

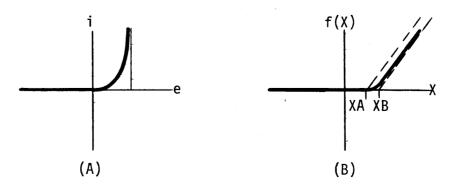

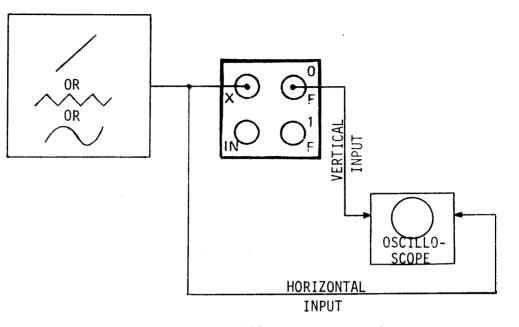

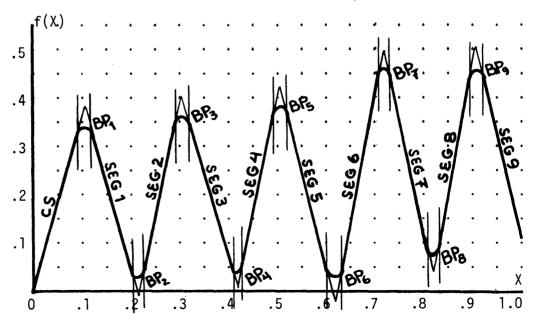

Non-linear computing components available with the AD/FIVE include Dual Square Function Generators, Sin/Cos Function Generators, Log Function Generators, Arbitrary Function Generators, and Multipliers. Precision Multipliers in the AD/FIVE offer typical performance such as: static error (|x| + |y| < 20 volts) of  $\pm 5 \text{ Mv}$ , with zero error (x=y=0) of  $\pm 0.5 \text{ Mv}$ ; bandwidth (x = 10 volts, y = 20 volts) peak-to-peak) of 1.0 MHz; and phase shift of  $0.03^{\circ}$  at 1.0 KHz. T.I.D.E. at 1.0 KHz is typically 0.06%.

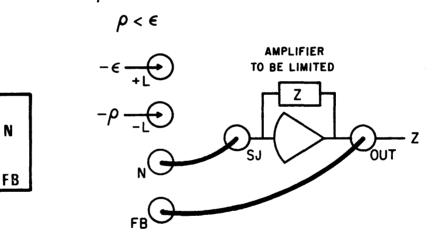

Track Store Networks are available for use with Summer/High Gain amplifiers, Summer/Integrator amplifiers, or Inverter amplifiers. Network switching time is less than 900 nanoseconds. Limiters are available on the AD/FIVE to limit the range of an operational amplifier between -10 volts to +10 volts on both +L and -L, with slope after limit typically 1.0 Mv/volt.

Free Impedance Network circuit cards are also available on the AD/FIVE to allow maximum flexibility to meet all user needs.

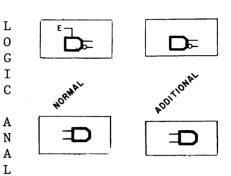

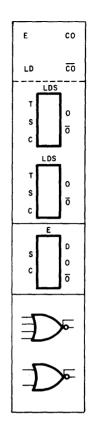

#### 1.1.2 Logic Computing Components

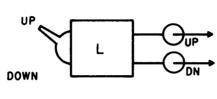

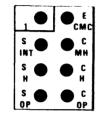

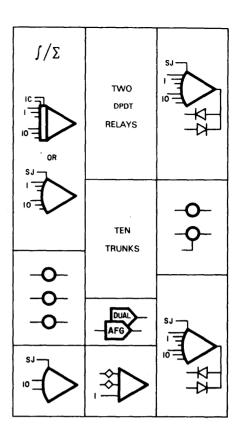

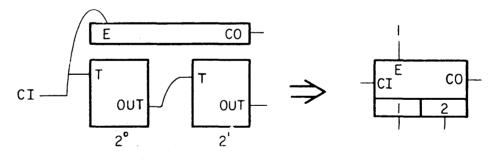

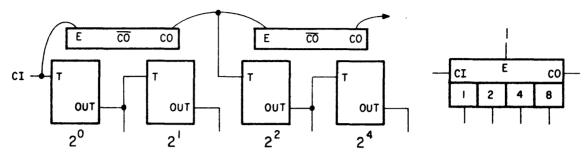

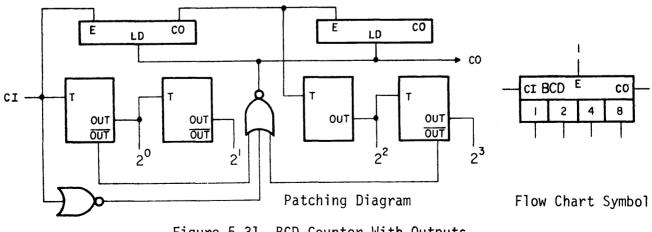

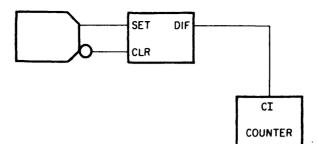

A precision 1 MHz oscillator is the master timing source for the AD/FIVE logic. The full complement logic system includes flip-flops, flip-flop differentiators, two-decade BCD counters, gates with two, four, and six inputs, DPDT relay switches, function and logic switches, trunks, and hybrid lines. Indicators are provided for flip-flops, gates, comparators, and counters. Preset controls are a useful adjunct to BCD counters. In addition, there are trunks and hybrid lines for implementation of full logic control in hybrid usage.

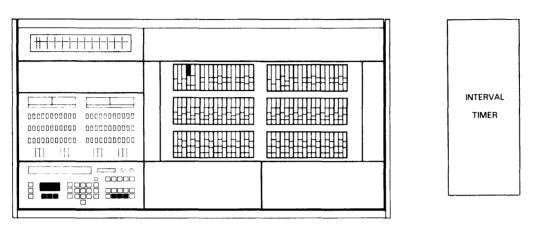

An interval timer with three pre-settable periods with BCD circuitry can also be used as a logic computing component, with a carry-out available with every one of the three intervals.

#### 1.2 CONTROL AND ADDRESSING SYSTEM

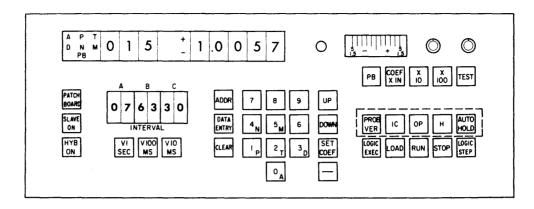

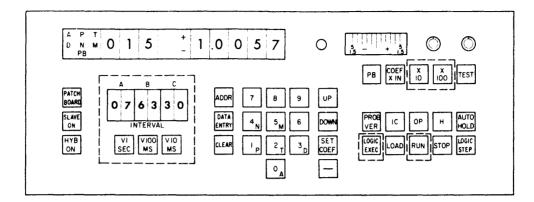

The Control Panel of the AD/FIVE offers numerous features to implement ease and flexibility of control. Pushbutton control is available for analog modes of integrators IC, OP, and H, and for logic modes LOAD, RUN, and STOP. Time scales may be controlled by pushbuttons labelled X10 and X100. Rep-op operation is pushbutton controllable, allowing analog modes to be controlled by the three pre-settable periods of the Interval Timer, which has a counter input derived from the 1.0 MHz logic clock.

Other pushbutton control features include COEF X IN for reading true potentiometer output values; TEST for ascertaining initial values of inputs to integrators; PROB VER for checking IC values of integrators; AUTO HOLD to put all integrators into Hold in case of the occurrence of any component overload; LOGIC STEP to allow logic to run for a programmable number of clock periods; UP and DOWN controls to allow manual slewing of servo-set pots; PB to allow patched inputs to be read via the Digital Ratiometer of the Addressing System; control of the pulses counted by the Interval Timer in decade steps from VISEC to VIOMS; PATCHBOARD to control the patchboard motors; and controls to enable slaving and hybrid operation.

In addition there are a number of useful controls associated with the Control Panel Analog Voltmeter.

The Addressing System is capable of addressing up to 721 addressable elements in a fully expanded AD/FIVE, with circuitry and switches all solid state. The multiplex rate for hybrid operation is 10,000 points/sec. when used with an A-D Converter.

#### 1.3 HYBRID FEATURES

Hybrid usage of the AD/FIVE is discussed in a separate manual. Only the main points of the hybrid system will be mentioned here. The AD/FIVE is joined by interface hardware to the digital computer to allow digital control of the analog and logic modes, repetitive operation, address and data registers, time scale, autohold, problem verify, setting and reading coefficient devices, interval timer, digital ratiometer, analog-to-digital conversion, digital-to-analog conversion, sense lines, control lines, and interrupt lines. The analog-to-digital converter system in the interface is a 100KHz, 14-bit plus sign, 10 volt unit. Sixteen multiplexer channels are supplied with the basic converter, and an additional sixteen channels may be added as desired. The A-to-D converter features random access or sequential modes of operation under computer control.

The Digital-to-Analog Converter (DAC) system includes double-bufferred, 14-bit plus sign multiplying D-to-A converters. Digitally Set Coefficient Units (DCU's) are also available, and are single-bufferred, 14-bit magnitude devices in two versions: two quadrant and four quadrant.

Sixteen control lines and sixteen sense lines, as well as eight interrupt lines, are terminated in the logic section of the AD/FIVE patchboard. The control lines are set and the sense lines read by the digital computer through the interface system, or by manual control from the Digital Access Panel option (DAP).

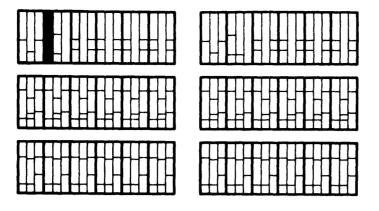

Figure 2 shows a diagram of the organization of the AD/FIVE hybrid system.

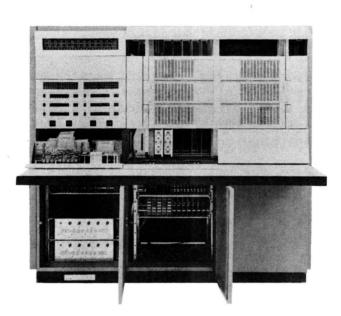

Figure 1-2 The AD/FIVE-PDP 11 SYSTEM 511

#### 1.4 MAN-MACHINE COMMUNICATIONS

In the design of the AD/FIVE a great deal of emphasis was placed on optimizing interrelationships between the operator and the computer. Care was taken to arrange for maximum operator convenience in the placement of controls and arrangement of the patchboard. Ease of maintenance was also a major factor. The features of AD/FIVE manmachine communication are discussed below.

5.

#### 1.4.1 Operator Convenience Features

1. The Control System of the AD/FIVE is all housed in one bay, so that all control functions are available to the operator in one area.

2. Hand-set potentiometers are easily accessible behind a hinged door panel below the patchboard, so that the operator can conveniently set pots.

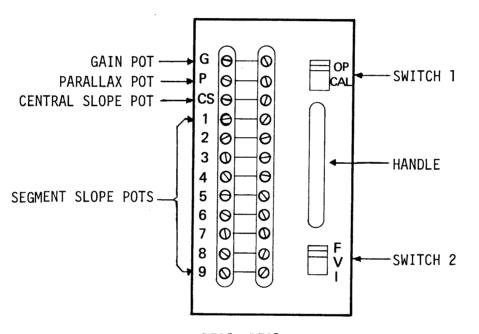

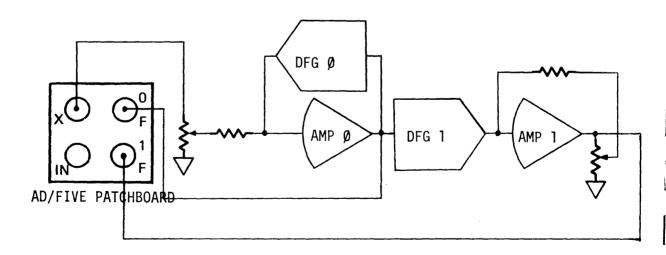

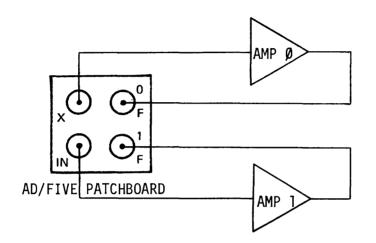

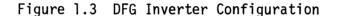

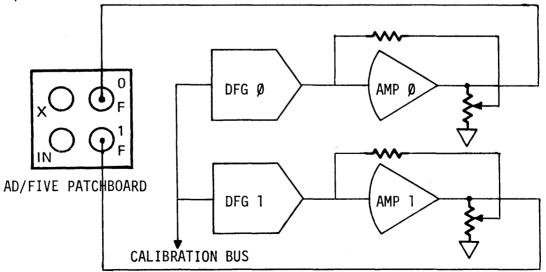

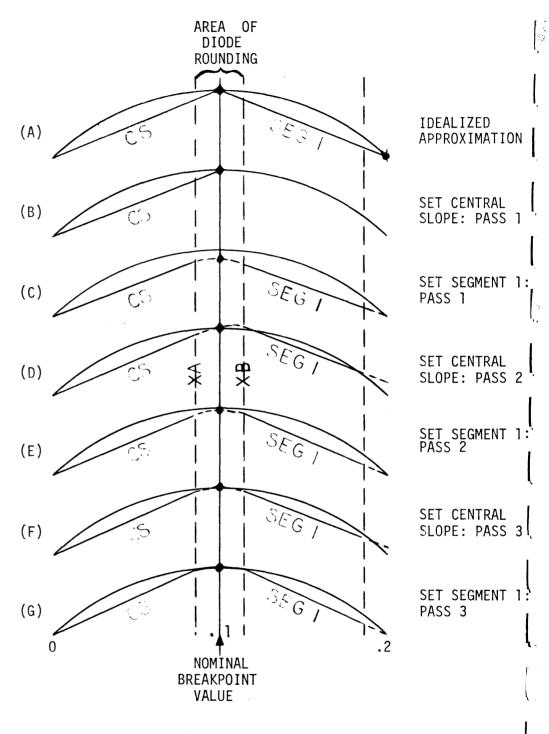

3. Diode Arbitrary Function Generators and Calibration Units are conveniently placed behind a hinged door panel above the patchboard, so that the operator can make all necessary calibrations and settings with ease and comfort.

4. The entire control area is well lighted for visual comfort and ease of reading indicator lights. The overload indicator panel, Digital Access Panel, and logic state indicator lights are all easily readable. Lighted pushbuttons give their information on the state of the computer to the operator quickly and accurately. The address and data register display windows are well lighted and easily readable.

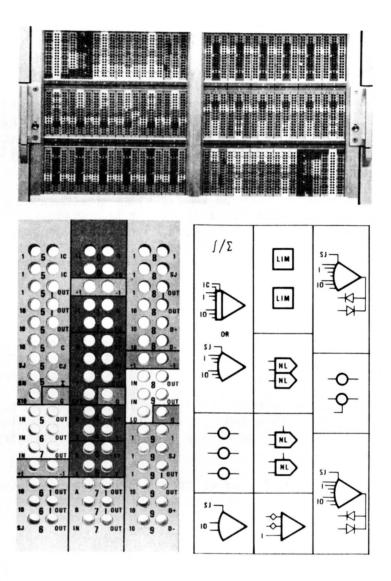

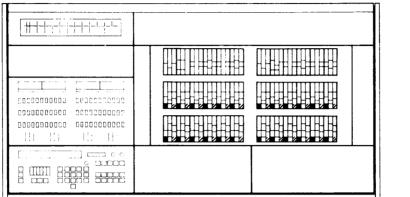

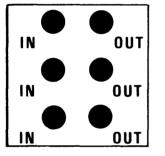

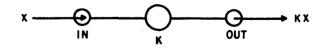

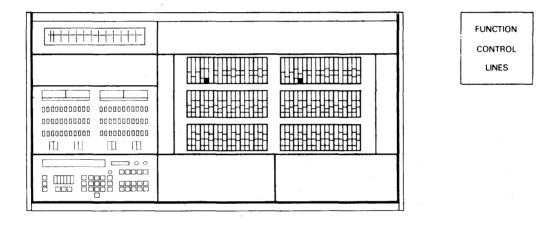

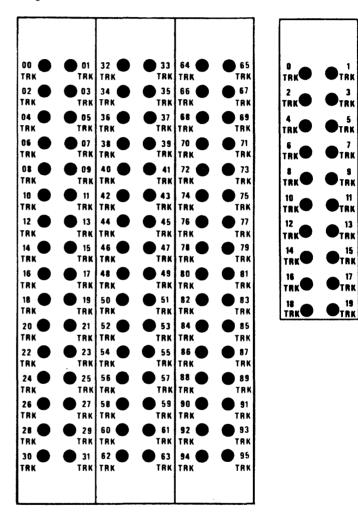

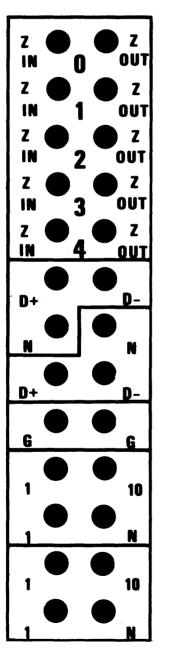

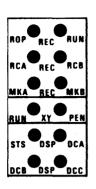

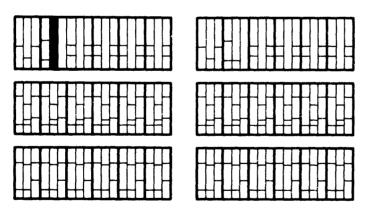

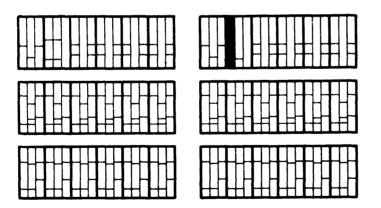

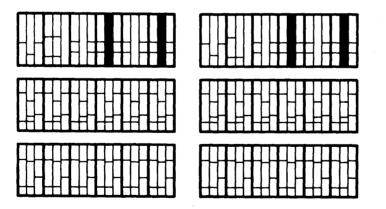

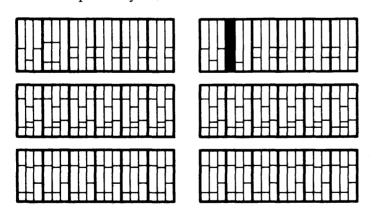

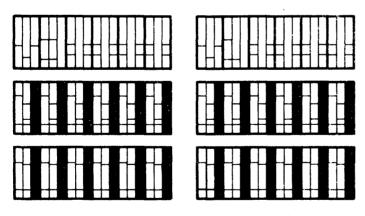

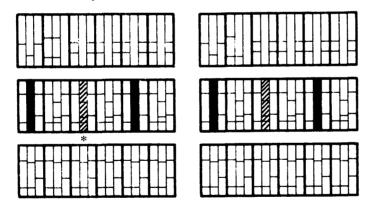

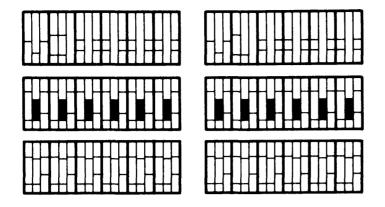

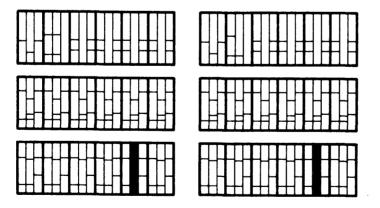

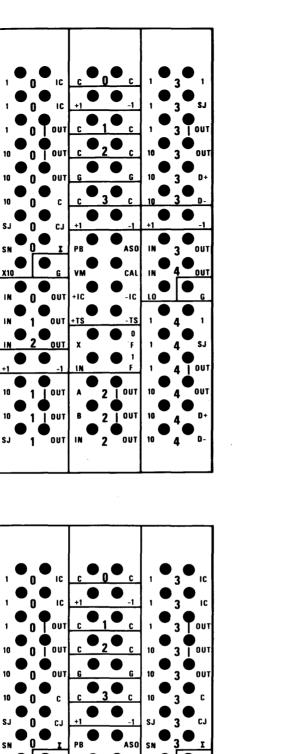

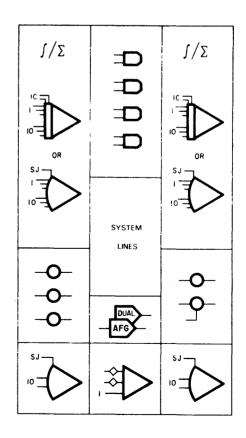

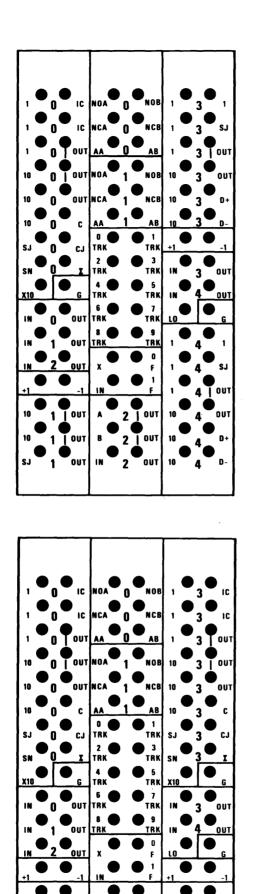

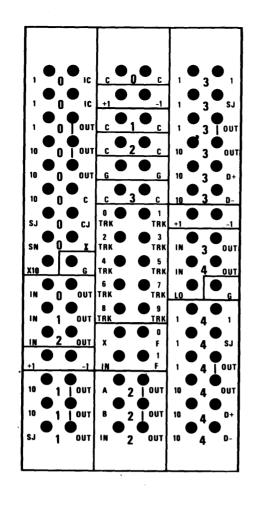

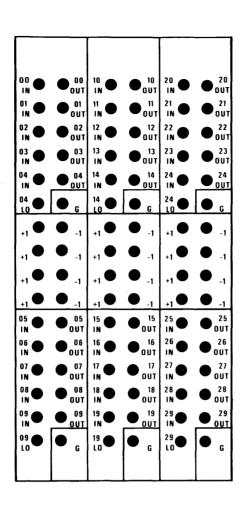

5. The organization of the patchboard is designed to give maximum efficiency to the operator in patching. The patchboard is divided into two fields horizontally, with each field having an upper logic section, and upper and lower analog sections. Each field has six areas which extend horizontally for six patchboard holes per area, and vertically through all three sections of the logic and upper and lower analog. Each area has components clearly labelled and numbered, so that inputs and outputs are easily visible for convenient patching. Every component has an individual number associated with it, so that a component can be given a unique address through the use of its field, area, and individual numbers. A consistent layout of components area by area throughout the patchboard maximizes simplicity and ease of correct patching.

A harmonious, well-balanced, and subdued color scheme which is consistent throughout the patchboard is not only restful to the eye, but greatly facilitates location of components for patching. In the analog sections, integrators and the various summers and inverters are colored green, pots are colored yellow, trunks and hybrid elements in soft blue, non-linear components, free impedance networks, diodes, and limiters in brown, system lines and analog reference in grey. Analog/Logic devices such as comparators and track-store networks are in white on both the analog and logic sections of the patchboard. In the logic section, integrator and amplifier controls are green to match the analog colors, flip-flops and counters are in green, gates and relays in yellow, function lines and logic switches in brown, system controls in brown, peripheral device and hybrid lines and trunks in soft blue, and logic reference in grey.

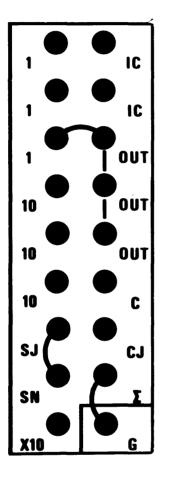

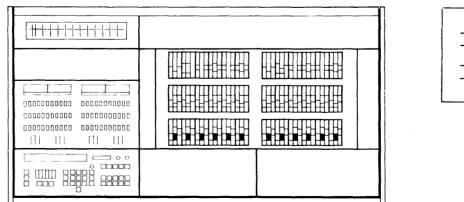

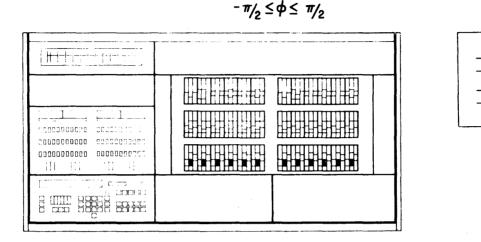

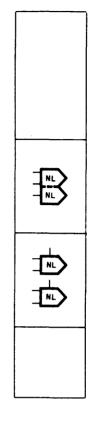

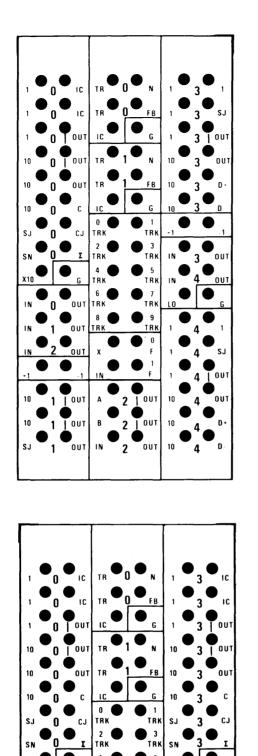

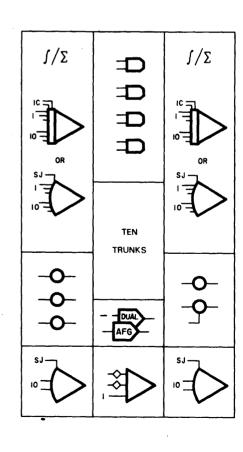

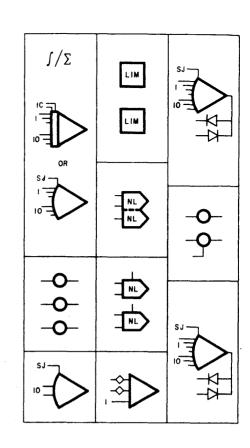

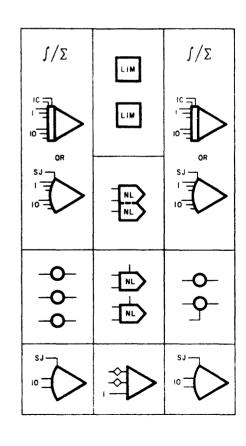

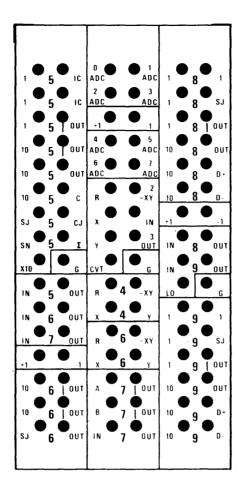

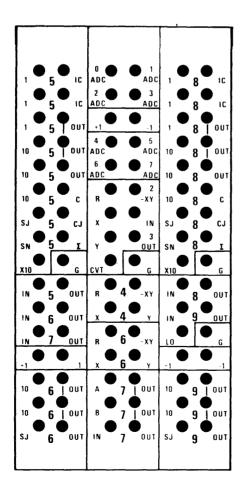

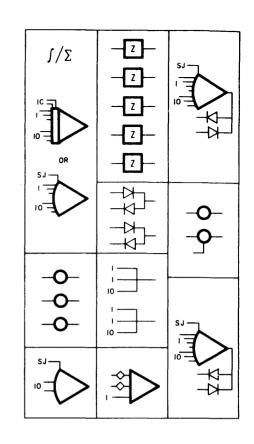

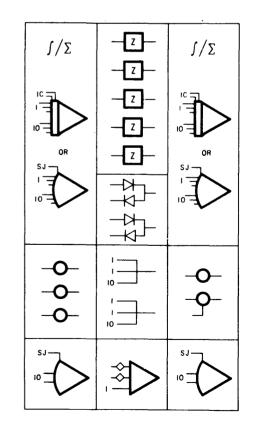

Figure 1-3 shows the AD/FIVE patchboard and a typical patchboard module with the components terminated in it.

Figure 1-3 Patchboard Layout and Component Terminations

6. A workshelf across the entire width of the computer is a great convenience to the operator, giving ample room for comfortable writing and programming, and for supplies of patchcords and tools when needed. In addition, there is ample comfortable leg room for prolonged operator use of the computer.

7. It is virtually impossible to damage any part of the computer or components through improper patching of any terminations at the patchboard.

8. A cost saving convenience on an AD/FIVE up to one field full is the reversible patchboard, which can be rotated 180°, allowing two separate problems to be patched on one board, so that the user needs to pay for only half as many patchboards as if this unique feature were not available.

#### 1.4.2 Ease of Maintenance

1. The AD/FIVE has operational temperature and humidity ranges such that it does not require a controlled atmosphere; thus it may be moved freely about any laboratory or building without affecting its computational ability, provided the broad environmental specifications are complied with.

2. The computer offers unmatched mobility because of its compact size. The front workshelf may be easily removed without the need for any tools, allowing the computer to pass through any standard thirty-inch doorway. The six casters are of a special composition chosen to support the computer without flat spotting while being pliable enough to pass over linoleum without scoring the surface.

3. All trim panels are removable for maintenance purposes without the need for any tools.

4. Non-linear components are located behind doors at the front of the AD/FIVE, so that most normal calibration can be accomplished conveniently from the front of the machine, without the need of removing any panels.

5. Amplifier balance controls are located behind the pot panel, and can be easily used with a small screwdriver, thus removing the danger of accidental alteration of amplifier balance and maintaining ease of necessary servicing.

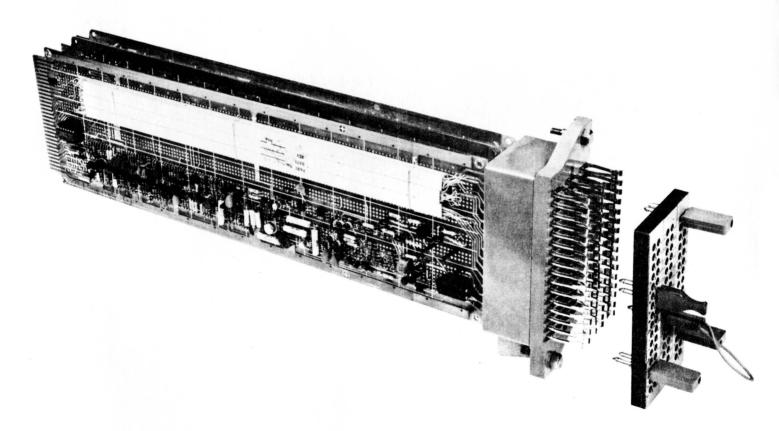

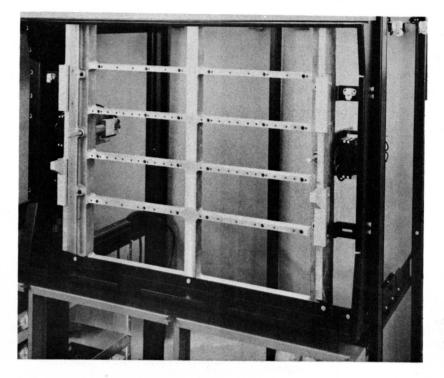

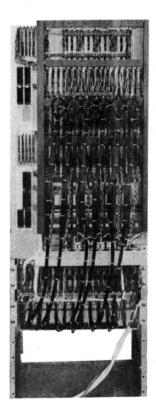

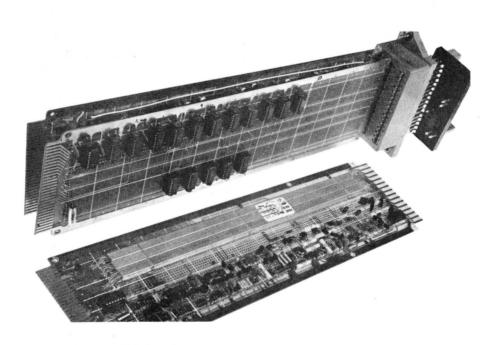

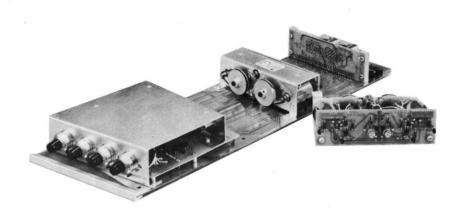

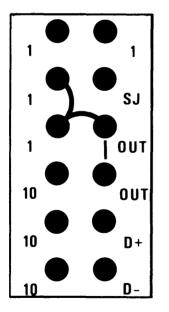

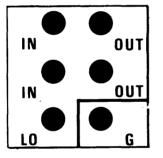

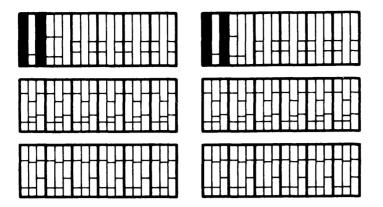

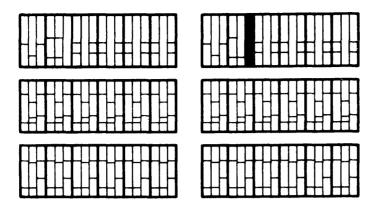

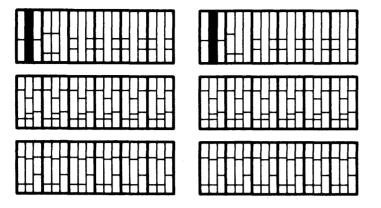

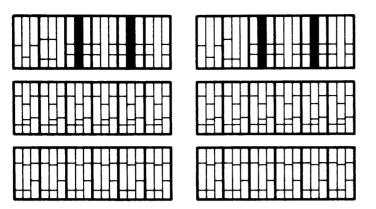

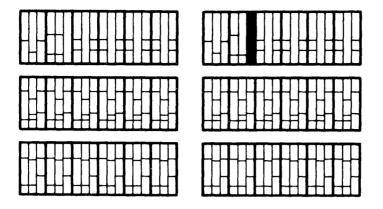

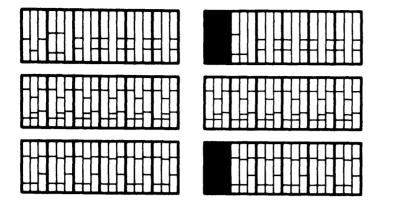

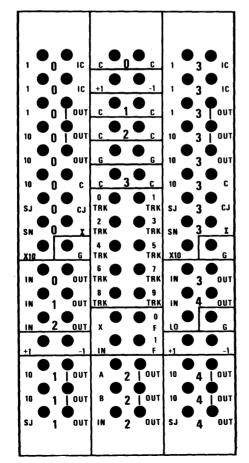

6. Access to circuit cards behind the patchboard is easily gained. Only two bolts fasten each patchbay pin block behind each patch panel module, and removing the patchbay pin block allows access to three component cards at a time.

7. The various sections of the control bay are easily accessible on the AD/FIVE; only four screws need to be removed per section to lift out the overload indicator panel and the logic control panel. The DAP conveniently slides out on a rack for servicing. The control panel is mounted on a hinged door for ease of maintenance.

8. A number of useful maintenance kits are available with the AD/FIVE, and a most useful feature is the Programmable extender, which allows component cards to be physically removed from their computer locations, and yet still be functional as if they were in the computer, allowing diagnostic check-out and calibration to be easily and reliably performed.

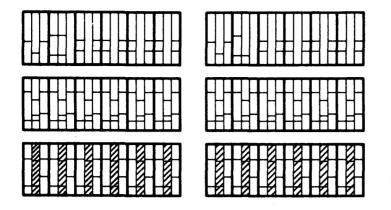

#### 1.5 MODULARITY AND EXPANSION CAPACITY

The AD/FIVE offers exceptional capacity for simple and efficient expansion. The modularity of the AD/FIVE computing components allows numerous variations of the patchboard component layout to suit varying user needs. The computer can be expanded from one to two fields by the addition of a wiring plane and power supply. Patchboard components can be expanded merely by plugging circuit cards to appropriate slots behind the patchboard. Non-linear components can be added beneath and above the patchboard in non-linear slots; non-linear access cards need to be present behind the patchboard, and, as the access feature is sometimes part of another computing card, it is sometimes easily possible to add a non-linear computing element without even removing the patchboard, depending on individual computer configurations.

All expansions of the AD/FIVE can be achieved without the need for soldering or extensive rewiring. Even expansion from a stand-alone analog computer to a hybrid system is easy and straightforward. The modularity of AD/FIVE components and the ease of analog and hybrid expansion, coupled with the precision and ease of use, as well as great flexibility, of the AD/FIVE make it the ideal analog computer for the most modern laboratory and professional or industrial applications.

Figure 1-4 Patchboard Module, Patchbay Pin Block, and Circuit Cards

## CHAPTER 2

## SYSTEM ORGANIZATION

ť,

## TABLE OF CONTENTS

| 2.0                                                       | SYSTEM ORGANIZATIONPAGE                                                                                                                                                                     | E 1                             |

|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 2.1<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6 | PHYSICAL ORGANIZATION.<br>General Description.<br>Modular Construction.<br>Component Locations.<br>Computing Components.<br>Fields and Areas.<br>Power Switch and Patchboard Drive Control. | . 1<br>. 4<br>. 6<br>. 7<br>. 9 |

| 2.2                                                       | FUNCTIONAL ORGANIZATION                                                                                                                                                                     | . 11                            |

| 2.2.1                                                     | General Description                                                                                                                                                                         |                                 |

| 2.2.2                                                     | Computing Components                                                                                                                                                                        |                                 |

| 2.2.3                                                     | Patchable Control Components                                                                                                                                                                | . 12                            |

| 2.2.4                                                     | Overload System                                                                                                                                                                             |                                 |

| 2.2.5                                                     | The Logic Panel                                                                                                                                                                             | . 14                            |

| 2.2.5.1                                                   | Gate State Indicators                                                                                                                                                                       | . 15                            |

| 2.2.5.2                                                   | Flip-flop Status Indicators and Switches                                                                                                                                                    | . 15                            |

| 2.2.5.3                                                   | BCD Counter Indicators and Switches                                                                                                                                                         |                                 |

| 2.2.5.4                                                   | Comparator Indicators and Switches                                                                                                                                                          | . 15                            |

| 2.2.5.5                                                   | Logic Switches                                                                                                                                                                              |                                 |

| 2.2.5.6                                                   | Function Switches                                                                                                                                                                           |                                 |

| 2.2.6                                                     | The Control System                                                                                                                                                                          |                                 |

| 2.2.7                                                     | The Control Panel                                                                                                                                                                           | . 16                            |

| 2.2.7.1                                                   | The Address System Controls and Display                                                                                                                                                     |                                 |

| 2.2.7.2                                                   | Readout System                                                                                                                                                                              | . 18                            |

| 2.2.7.3                                                   | Coefficient Setting System                                                                                                                                                                  |                                 |

| 2.2.7.4                                                   | The Interval Timer Controls                                                                                                                                                                 |                                 |

| 2.2.7.5                                                   | The Analog Voltmeter                                                                                                                                                                        |                                 |

| 2.2.7.6                                                   | Time Scale Controls                                                                                                                                                                         |                                 |

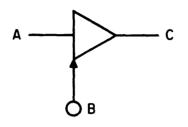

| 2.2.7.7                                                   | Mode Control Pushbuttons                                                                                                                                                                    |                                 |

| 2.2.7.8                                                   | Misce <b>llaneous Controls</b>                                                                                                                                                              | . 23                            |

## ILLUSTRATIONS

| Figure | 2-1  | AD/FIVE ConsolePAGE                                           | 1  |

|--------|------|---------------------------------------------------------------|----|

| Figure | 2-2  | AD/FIVE Frame and Patchbay Casting                            | 2  |

| Figure | 2-3  | AD/FIVE Front Access                                          | 3  |

| Figure | 2-4  | AD/FIVE Rear Access                                           | 3  |

| Figure | 2-5  | AD/FIVE Wiring Plane Assembly                                 | 4  |

| Figure | 2-6  | AD/FIVE Patchboard Expansion Method                           | 5  |

| Figure | 2-7  | AD/FIVE Component Locations                                   | 6  |

| Figure | 2-8  | AD/FIVE Potentiometer Module                                  | 8  |

| Figure | 2-9  | AD/FIVE Logic Panel and Control Panel                         | 9  |

| Figure | 2-10 | AD/FIVE Patchboard Fields and Areas                           | 10 |

| Figure | 2-11 | Functional Diagram for Analog and Analog/Logic Components     | 11 |

| Figure | 2-12 | Functional Diagram for Logic and Patchable Control Components | 11 |

| Figure | 2-13 | Overload Indicator Panel                                      | 13 |

| Figure | 2-14 | State Indicators and Switches                                 | 14 |

| Figure | 2-15 | Address System Controls and Display                           | 17 |

| Figure | 2-16 | Readout System Displays and Controls                          | 18 |

| Figure | 2-17 | Coefficient Setting System Displays and Controls              | 18 |

| Figure | 2-18 | Interval Timer Controls                                       | 20 |

| Figure | 2-19 | The Analog Voltmeter                                          | 21 |

| Figure | 2-20 | Time Scale Controls                                           | 21 |

| Figure | 2-21 | Mode Control Pushbuttons                                      | 22 |

#### 2.0 SYSTEM ORGANIZATION

The AD/FIVE is a sophisticated computer designed to be used either as a self-contained general purpose analog computer or as an integral part of a hybrid computer system. A versatile logic system for control of the computer and potential for considerable expansion of the analog and logic computing components are characteristics of the AD/FIVE. Chapter 2 describes the organization of the AD/Five as a basic analog computer. Hybrid operation of the AD/FIVE in an expanded system is dealt with in Volume 2 of this manual.

- 2.1 PHYSICAL ORGANIZATION

- 2.1.1 General Description

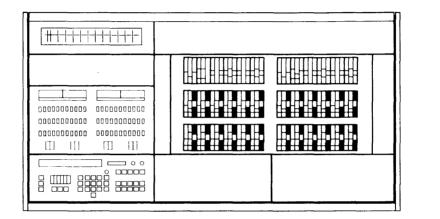

AD/FIVE Console Figure 2-1 The AD/FIVE Console is shown in Figure 2-1.

The cabinetry of the AD/FIVE is carefully designed for strength and efficiency, with rigid steel frame construction and mounted on large, heavy-duty castors which allow ease of movement. A rugged castaluminum patchbay frame provides excellent structural integrity and insures proper alignment of parts in the patchbay area. The front of the cabinet showing the patchbay frame is illustrated in Figure 2-2.

#### AD/FIVE Frame and Patchbay Casting

Figure 2-2

The patchboard connections are vital to the proper operation of an analog computer. The AD/FIVE is equipped with patchboard motor drive mechanisms to insure uniform movement of the patchboard. Regardless of the number of patchbay blocks in the patchbay frame, perfect connections are consistently assured through the action of the drive mechanisms.

A work shelf for the convenience of the operator is mounted across the front of the AD/FIVE. This work shelf can be easily removed to allow the computer to pass through a thirty-inch doorway.

Ease of maintenance is a prime feature in the design of the AD/FIVE. Access to all parts of the computer is easily gained through the side and rear panels which are held in place by snap-in latches. No tools are required for the removal of these panels. The area below the work shelf in the front of the computer is provided with hinged doors for convenient entry. The sloping control panel and the panels above and below the patchbay are all hinged to allow access to the controls and to the components mounted above and below the patchbay.

AD/FIVE Front Access Figure 2-3

AD/FIVE Rear Access Figure 2-4

#### 2.1.2 Modular Construction

It is a feature of analog computation that each class of problems often requires a particular combination of computing elements which may not be well suited to the solution of other classes of problems.

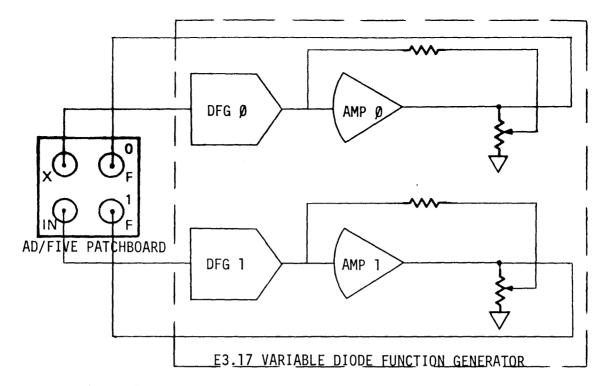

Aerospace applications, for example, require a significant complement of multipliers, sin/cos generators, and variable diode function generators.

Chemical kinetics, however, require an abundance of integrators and log generators, A successful design of an analog computer must take this feature into account in order to provide useful service in a wide range of applications. Flexibility of configuration is therefore of prime importance in the design of the AD/FIVE.

An analog computer must also be able to grow along with the growing needs of its user. In order for a computer to be of maximum service to the user, expansion of its capabilities must be easily and efficiently achieved, without the need for extensive rewiring or soldering.

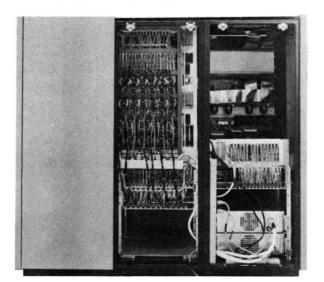

AD/FIVE Wiring Plane Assembly

Front View

Rear View

AD/FIVE Wiring Plane Assembly

These particular needs of analog computation have resulted in the carefully designed modular construction which is a feature of the AD/FIVE. The computing components are all on circuit boards which need merely to be plugged into the wiring plane assembly in order to plan the configuration of computing components, or in order to expand an already existing system. Each AD/FIVE can therefore easily be tailored to meet the specific needs of any customer. Likewise, each AD/FIVE can be easily modified and expanded with a minimum of time and expense to keep up with the changing needs of its user. The basic AD/FIVE contains the cabinetry, control structure, and reference power supply capacity required for a fully expanded system. It also contains the power supplies and wiring plane assembly for expansion of one-half of the computer. Expansion into the second half requires the addition of a power supply unit, a wiring plane assembly, and some miscellaneous hardware and cables. No soldering, cable lacing, or sheet metal modification is required for any expansion.

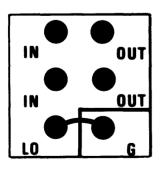

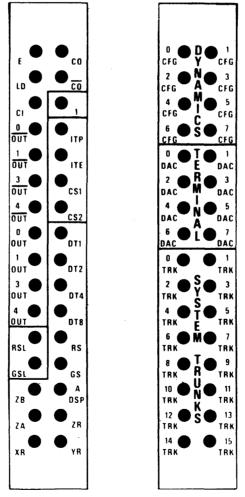

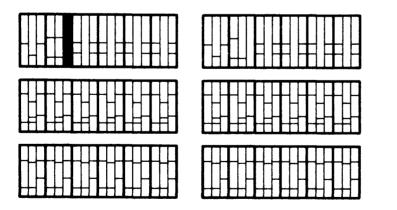

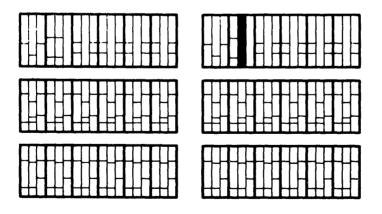

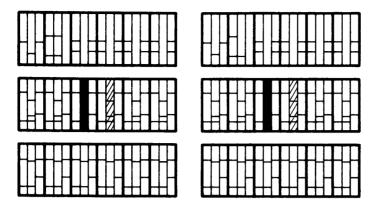

The addition of computing components in areas other than directly behind the patchbay simply involves plugging the appropriate circuit card into the proper area of the wiring plane assembly. The circuit boards for computing components which are located in the patchbay behind the patchboard are plugged into the appropriate place in the wiring plane assembly and terminate directly behind the patchboard in connector blocks which contain the patchbay springs, as illustrated in Figure 2-6.

AD/FIVE Patchboard Expansion Method

Figure 2-6

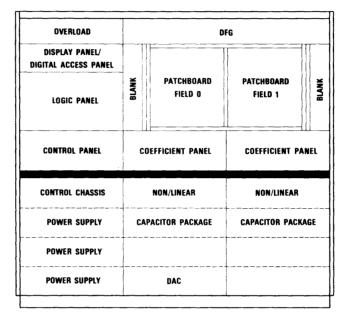

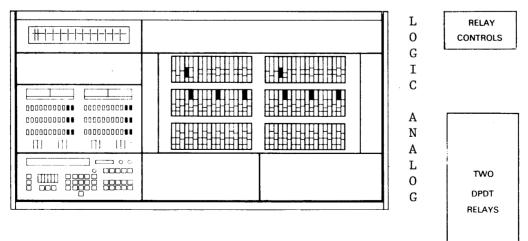

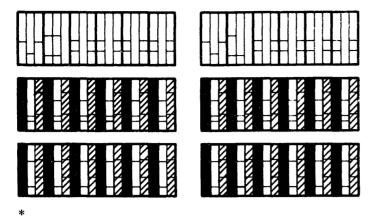

Location assignments for all components are illustrated in Figure 2-7, showing both front and rear views of the AD/FIVE. For the convenience of the operator, as well as ease of maintenance, the controls, indicators, interface hardware (when present), and power supplies are all located in one bay. The other two bays are used exclusively for patchable control (such as interval timer circuitry) and computing elements.

| DFG                | DFG                | OVERLOAD          |

|--------------------|--------------------|-------------------|

| LOGIC              | LOGIC              | HIF               |

| UPPER ANALOG       | UPPER ANALOG       | ADC               |

| LOWER ANALOG       | LOWER ANALOG       |                   |

| COEFFICIENT PANEL  | COEFFICIENT PANEL  |                   |

| POWER DISTRIBUTION | POWER DISTRIBUTION | CONNECTOR CHASSIS |

| NON/LINEAR         | NON/LINEAR         | CONTROL CHASSIS   |

| CAPACITOR PACKAGE  |                    | POWER SUPPLY      |

| 16                 | 08                 | POWER SUPPLY      |

| 19                 | DAC                | POWER SUPPLY      |

AD-FIVE FRONT VIEW

AD-FIVE REAR VIEW

AD/FIVE Component Locations

#### Figure 2-7

Each of the blocks in the AD/FIVE rear-view diagram has a number in the lower right-hand corner. This number is the chassis/ location address. These addresses are used in the maintenance manuals, wiring lists, etc.

2.1.4 Computing Components

Patchable computing components are available in the following types for the AD/FIVE:

Summer/Integrator/High Gain Amplifiers Summer/High Gain Amplifiers Inverter/High Gain Amplifiers Switch Amplifiers Limiter Networks Track-Store Networks Comparators Multipliers Sin/Cos Function Generators Log Function Generators Potentiometers Diode Function Generators (DFG's) Flip-flops Flip-flop Differentiators Gates Counters **Function Switches** Logic Switches

Patching configurations and operation of these elements are described in detail in Chapter 4 of this volume. Patchable controls such as the Interval Timer are described in Chapter 3.

LOGIC computing components and the circuitry for the PATCHABLE CONTROLS are located in the area behind the upper third of the patchboard.

ANALOG and ANALOG/LOGIC computing components are located in the remaining area of the patchbay. (Analog/Logic computing components are those elements which have both analog and logic signal terminations on the patchboard, such as comparators.)

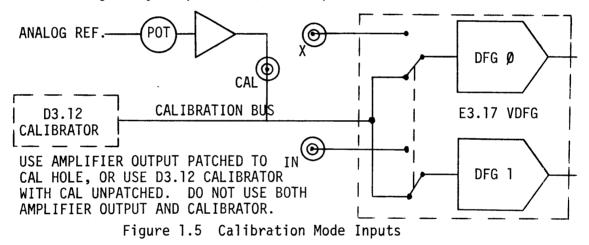

VARIABLE DIODE FUNCTION GENERATORS are located in the area above the patchboard. This area can be used for a variety of other computing components as desired, such as multipliers or other fixed function generators.

COEFFICIENT POTENTIOMETERS and AMPLIFIER BALANCE POTENTIOMETERS are located in the area immediately below the patchboard behind the hinged door. Both hand-set and servo-set potentiometers are available. Each servo-set potentiometer has its own individual drive motor. Figure 2-8 illustrates the coefficient potentiometer assembly.

#### AD/FIVE Potentiometer Module

#### Figure 2-8

The hand-set potentiometer module contains four potentiometers; the servo-set potentiometer module contains two potentiometers. The arm of each coefficient potentiometer is protected by an incandescent lamp which acts as a nonlinear resistance to prevent damage to the potentiometer in the case of a patching error.

TRUNKS, DISPLAY LINES, and other lines used for communication between the patchbay and external devices are terminated in connectors located on the rear of the wiring plane assembly. (See Figure 2-5.)

The CONTROL BAY provides the major communication link between the operator and the AD/FIVE.

The OVERLOAD PANEL at the top of the control bay contains the overload indicators for amplifiers and function generators.

The DISPLAY PANEL is immediately below the overload panel (See Figure 2-7). This area, 5 1/4" high, can be used for any of a variety of functions. In a hybrid system this area is often used for mounting the DIGITAL ACCESS PANEL, which provides for manual monitoring and control of the hybrid interface.

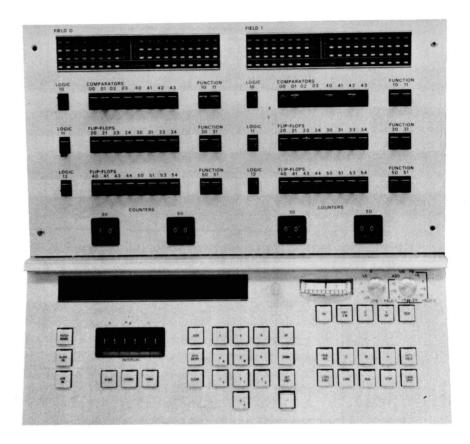

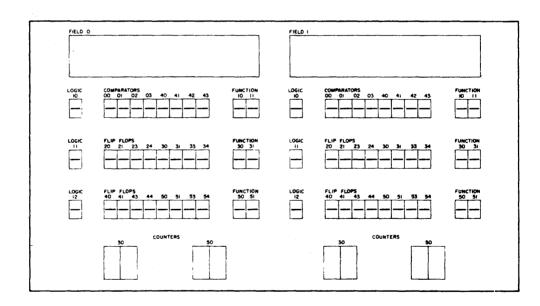

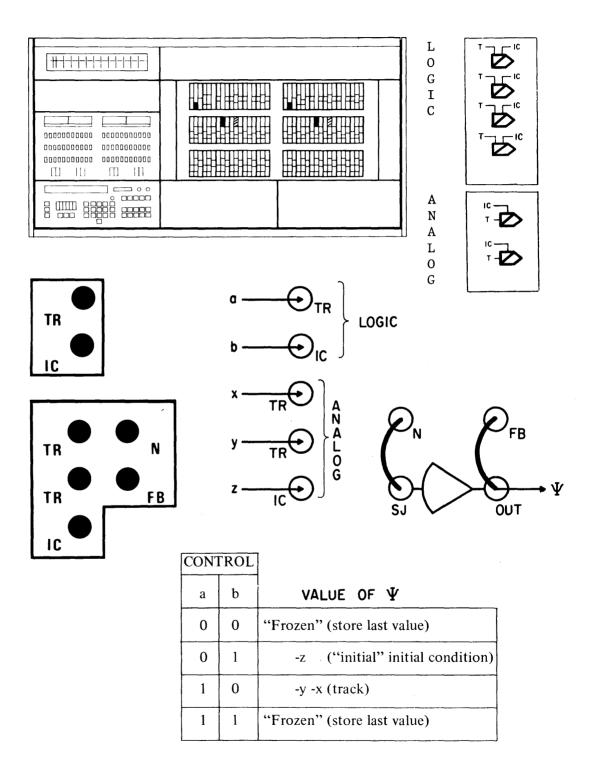

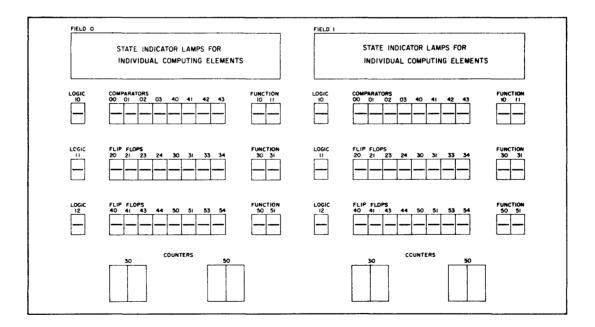

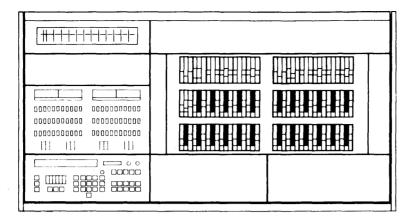

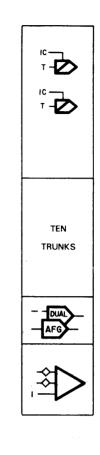

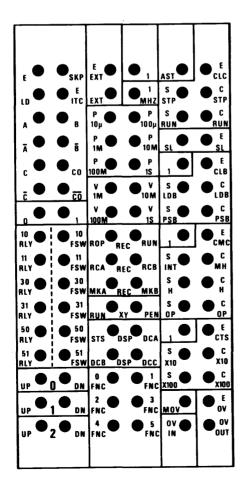

The LOGIC PANEL contains the logic state indicators for the patchable gates, flip-flops, comparators, and counters; the logic and function switches; the control switches for comparators and flipflops; and the precount thumbwheel switches for the counters.

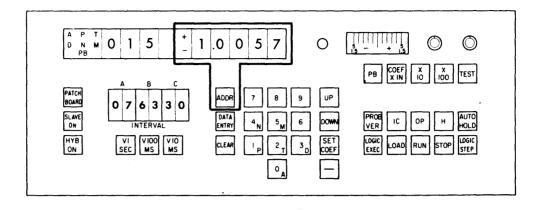

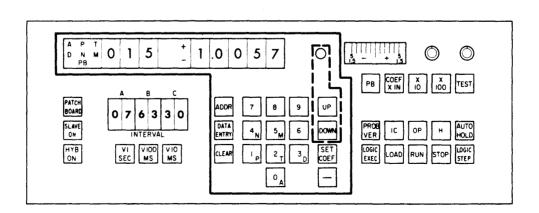

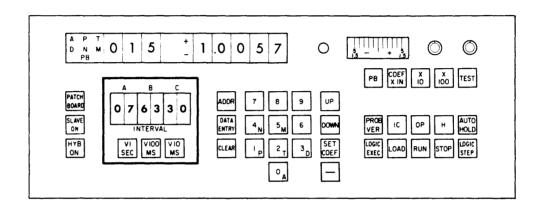

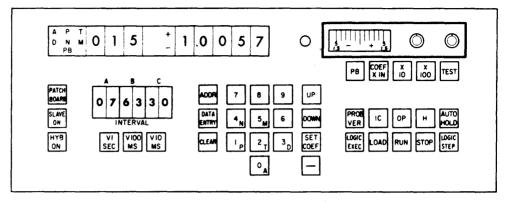

The CONTROL PANEL contains the pushbutton controls and readout indicators for the ADDRESS SELECTOR SYSTEM, the DATA REGISTER, and the DIGITAL RATIOMETER (DRM); the INTERVAL TIMER controls; the ANALOG VOLTMETER; and the various pushbutton controls for analog and logic modes, time scales, etc.

The Logic Panel and Control Panel are shown in Figure 2-9.

#### AD/FIVE Logic Panel and Control Panel

#### Figure 2-9

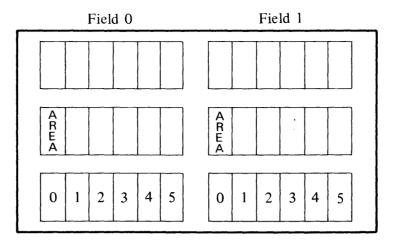

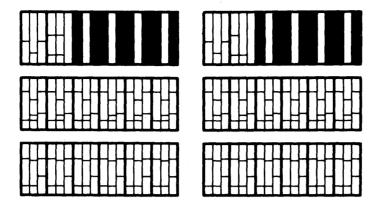

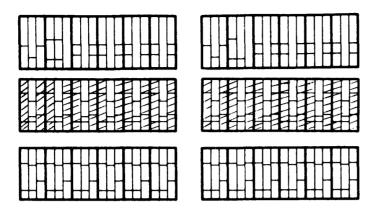

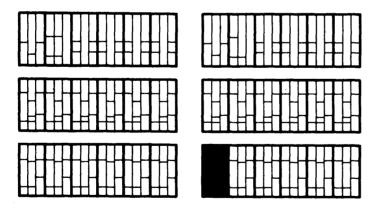

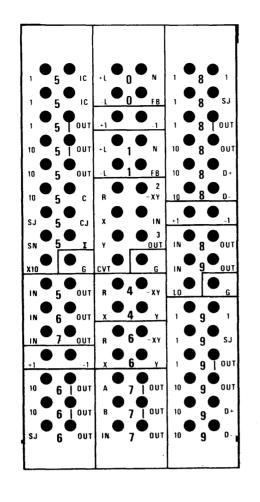

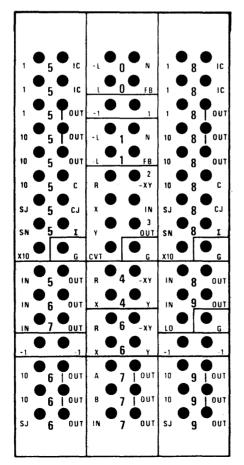

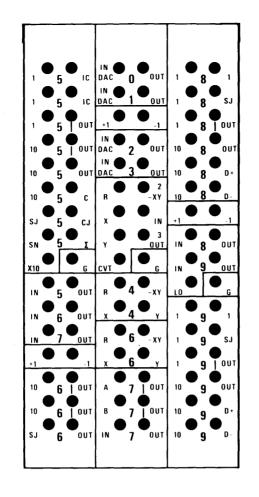

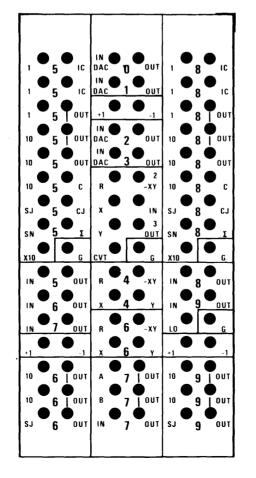

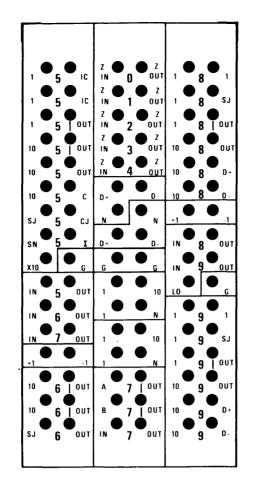

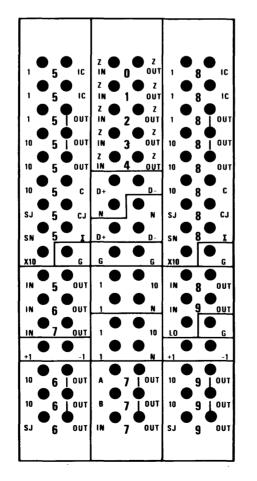

#### 2.1.5 Fields and Areas

The AD/FIVE is divided into three bays. One bay houses the control components and power supplies. The other two bays house the patchable computing components, with a wiring plane assembly and power supply required to incorporate the computing elements into each bay.

Each of these two computing bays is called a "FIELD" as shown in Figure 2-7, and is numbered 0 or 1 from the operator's left to right. The Logic Panel (Figure 2-9) and the Overload Indicator Panel (Figure 2-13) are also divided into two fields to reflect the division of the computing components in the computing bays.

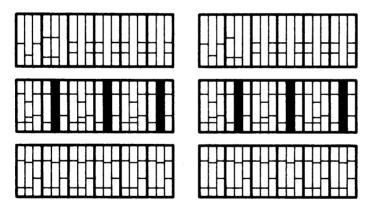

The patchboard is clearly divided into two fields, one in each bay. Each patchboard field is further divided into six "AREAS" numbered O through 5 as illustrated in Figure 2-10. Each area extends from the upper third of the patchboard, which contains the logic computing components, through the lower two thirds of the patchboard

#### Figure 2-10

which contain the upper and lower analog computing components. Each area of the patchboard contains three double vertical rows of patchboard holes from the top to the bottom of the board. Each patchboard block is one area wide.

A patchboard area can contain a maximum of ten components of a given type (i.e., ten addressable amplifiers, ten coefficient devices, etc.). The components are numbered from 0 through 9 for each type of component. The labelling on each patchboard block includes the component number for each computing component which can terminate in that block. Chapter 4 of this manual gives detailed descriptions of each of the various available patchboard blocks for the AD/FIVE.

A component location is specifically defined by a four digit address consisting of its component type (represented by a letter of the alphabet), and of its field, area, and individual component numbers. This is the method of location address used in the operation of the AD/FIVE. A detailed explanation is given in a following section of this chapter (The Address System Controls and Display, 2.2.7.1). By means of this class-field-area-component number designation the operator may rapidly and accurately locate any of the computing components.

2.1.6

Power Switch and Patchboard Drive Control

The power on/off switch and the patchboard motor drive control are two important controls for the operator. The power on/off switch is located behind the hinged door of the pot panel in field O (See Figure 2-7), at the operator's far left. When power is applied to the AD/FIVE various control panel indicators are illuminated. The power supply voltages can be monitored via the analog voltmeter on the control panel.

The patchboard motor drive control is a pushbutton labelled PATCH-BOARD, and is located on the control panel at the operator's far left. This is a momentary contact control: it is only necessary

10.

to depress the pushbutton until the patchboard begins to move. The patchboard motor drive will then complete the cycle initiated by the depressing of the pushbutton, i.e., if the patchboard is disengaged, depressing the pushbutton will cause the motors to engage the patchboard, and if the patchboard is engaged, the pushbutton will cause the motors to disengage the patchboard. The patchboard motor drive mechanism contains limit switches to stop the motors when the patchboard is properly engaged or disengaged.

#### 2.2 FUNCTIONAL ORGANIZATION

#### 2.2.1 General Description

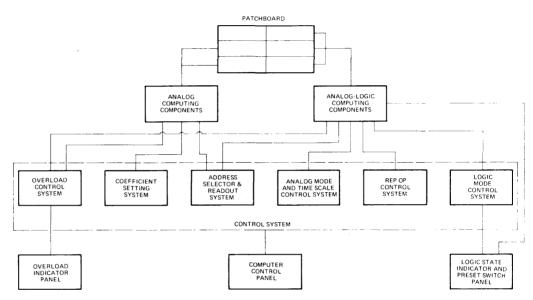

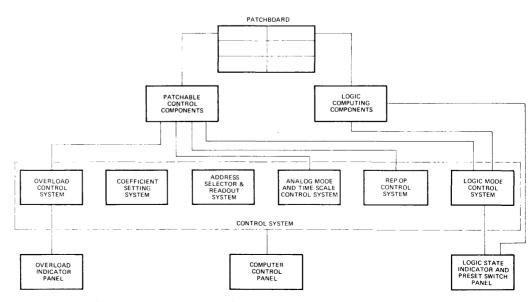

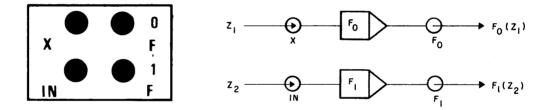

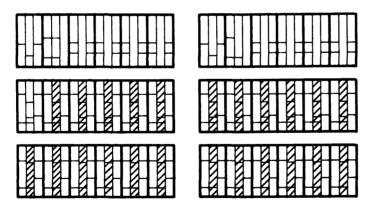

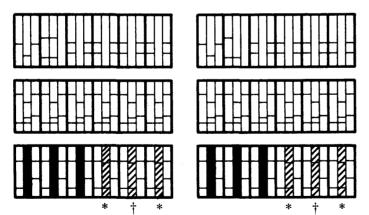

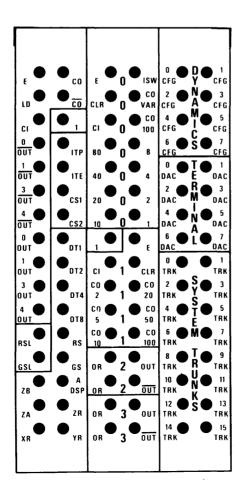

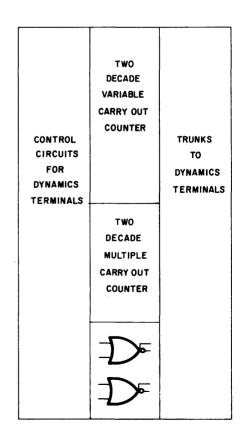

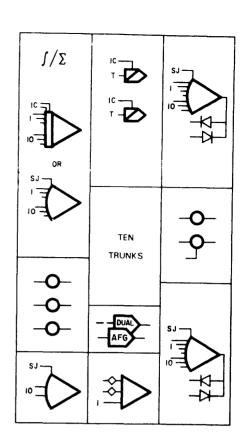

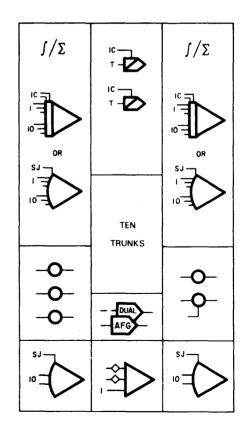

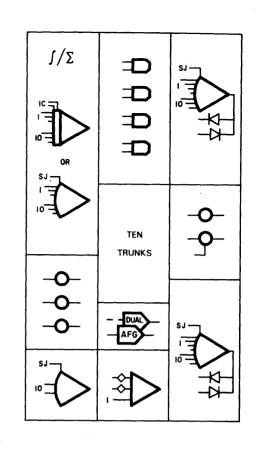

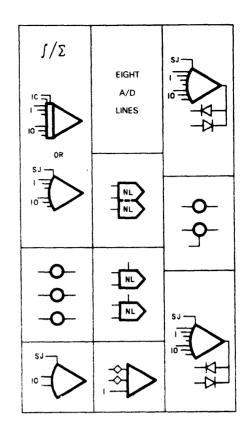

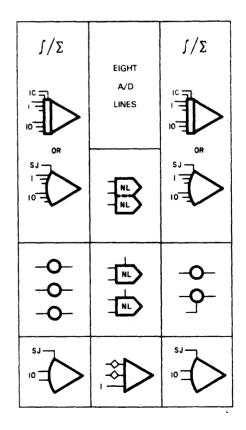

The functional organization of the AD/FIVE is shown in Figure 2-11 and Figure 2-12.

Functional Diagram for Analog and Analog/Logic Components

Figure 2-11

Functional Diagram for Logic and Patchable Control Components

Figure 2-12

2.2.2 Computing Components

The computing components in the AD/FIVE are of three types as indicated in the functional organization diagrams. The ANALOG COMPUTING COMPONENTS have only analog signals as inputs and outputs and have no terminations in the upper one-third of the patchboard. The analog computing components are:

> Summers Inverters Coefficient devices Limiters Diode Function Generators Multipliers Sin/Cos Generators Log Generators

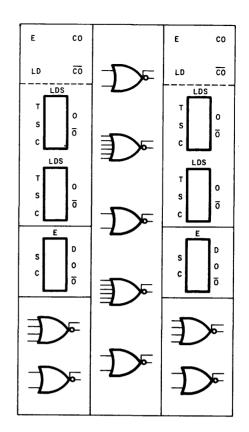

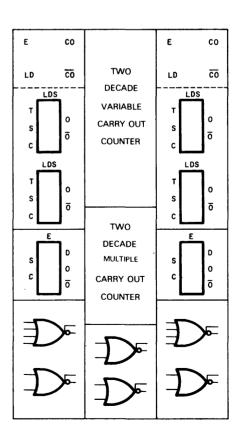

The LOGIC COMPUTING COMPONENTS have only logic signals as inputs and outputs and are terminated exclusively in the upper one-third of the patchboard. The logic computing components are:

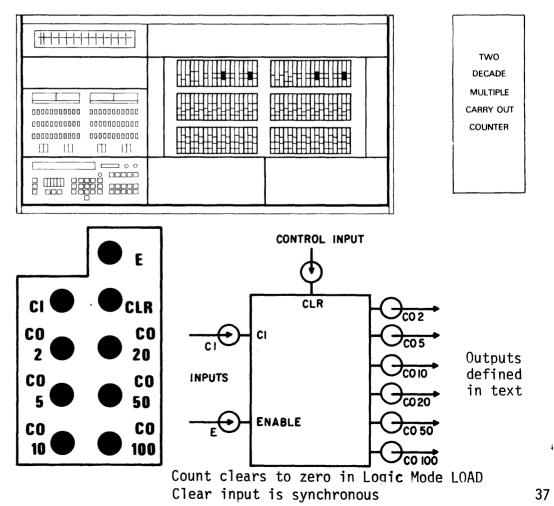

> Gates Flip-flops Flip-flop Differentiators Variable Carry-Out BCD Counters Multiple Carry-Out BCD Counters

The ANALOG/LOGIC COMPUTING COMPONENTS have both analog and logic signal terminations on the patchboard. The analog/logic computing components are:

Integrators Comparators Switch Amplifiers Function Switches Track-Store Networks

The various computing components and their patching configurations are discussed in Chapter 4 of this manual.

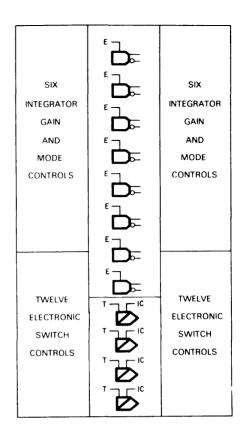

2.2.3 Patchable Control Components

In addition to the computing components listed above, the AD/FIVE contains patchable control components which are terminated in the upper one-third of the patchboard. These are:

Logic Switches Interval Timer, Three Period Reference Timer, Six Decade Console Mode Control Console Time Scale Control Clock Step Control

#### Time Scale Controlled Clock Outputs

These patchable control components are discussed in detail in Chapter 3.

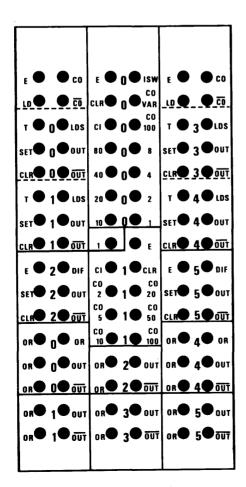

FILD 0 FILD 0

#### 2.2.4 Overload System

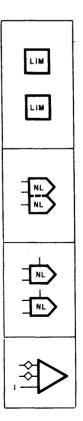

#### Overload Indicator Panel

Figure 2-13

The AD/FIVE contains a high-speed overload detection system which presents both visual and logic signal indication of an overload. The OVERLOAD INDICATOR PANEL, shown in Figure 2-13, is completely wired for a fully expanded system. The indicators in the panel correspond on a one-to-one basis with the amplifiers in the lower two-thirds of the patchboard. An illumined indicator reveals an overload condition in the component to which it is assigned. Individual indicators are provided for the maximum of ten amplifiers (i.e., summer-integrators, summers, inverters, and switch amplifiers) which terminate in each area of each field. Each indicator is labelled with the number of the component to which it is assigned. One indicator, labelled NL, is provided for each area of each field to serve as a common overload indicator for the various nonlinear computing devices (i.e., DFG's, multipliers, etc.) which terminate in that area. In addition, there are indicators on the right-hand side of the panel for the plus and minus reference power supplies (+R and -R), the Servo Amplifier (SA), and the Unloading Amplifier (UA).

The overload indicator drive signals are used to generate a logic signal indicating an overload condition in the computer. This signal is available to the programmer on the upper third of the patchboard in Field 0, Area 1 (See Chapter 4, Section 4.2.3). This logic signal is also used by the Auto Hold circuit for Master Hold (See Chapter 3, Sections 3.1.1.2 and 3.1.1.3).

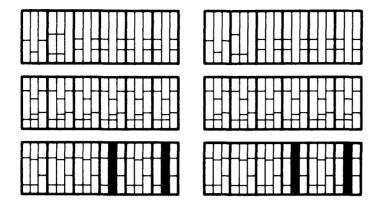

#### 2.2.5 The Logic Panel

State indicators and switches are provided for the logic computing components and for certain of the analog/logic computing components. These indicators and switches are located on the Logic Panel. (See Figures 2-9 and 2-14.) The indicators are illuminated when the true output of the logic computing components and the comparators is logic 1. These status indicators are quite useful to the operator, particularly during problem checkout. The toggle switches for the flip-flops and comparators allow the operator to set initial logic states for these components. In the case of the counters, the thumbwheel switches allow manual precount values to be entered. The logic and function switches provide the operator with a convenient means for controlling various aspects of a problem.

Each of the indicators and switches is labelled with the area and number designators of the corresponding computing component's address. This facilitates rapid and easy correlation of a particular indicator or switch with the patchboard location of the component with which it is associated.

State Indicators and Switches

Figure 2-14

#### 2.2.5.1 Gate State Indicators

Individual indicators are provided for the thirty gates which can terminate in each field. The indicator is illuminated when the gate output is a logic 1.

#### 2.2.5.2 Flip-flop Status Indicators and Switches

The complement of indicators and switches for each field includes sixteen indicators and sixteen single-pole triple throw spring return toggle switches for the eight flip-flop pairs which can be terminated in that field. The individual indicator lamp is illuminated when the corresponding flip-flop output is a logic 1. The toggle switch for each flip-flop serves two purposes. First, it is used to establish the initial state of the flip-flop in the LOAD mode; second, it can also be used when in the logic STOP mode to complement the output of the flip-flop. (See Chapter 4, Section 4.2.2.2 for complete details of flip-flop operation.)

#### 2.2.5.3 BCD Counter Indicators and Switches

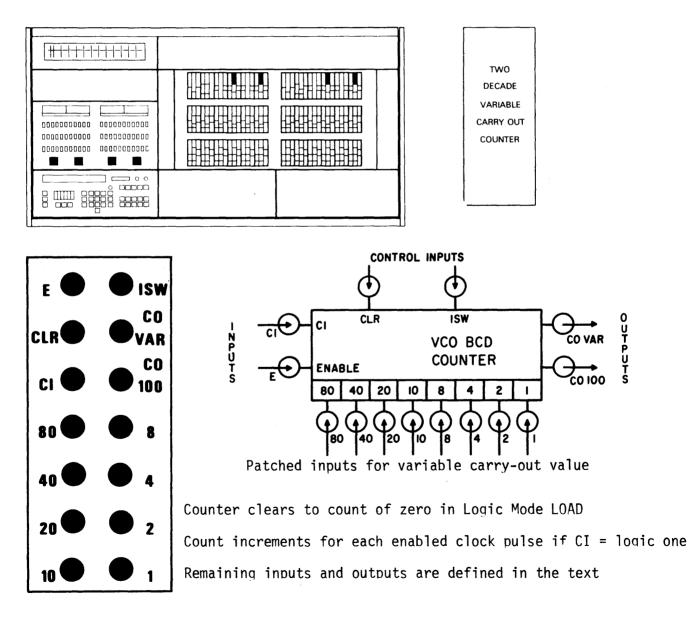

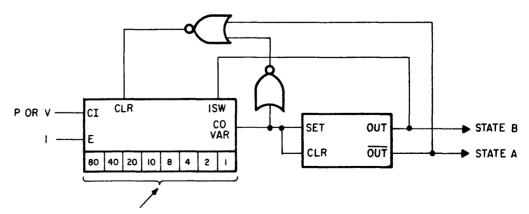

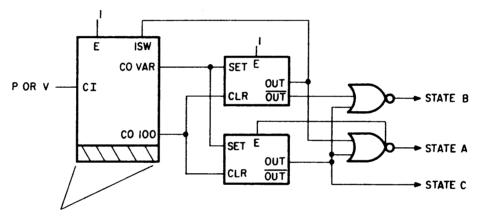

Indicators and thumbwheel switches are provided for the two twodecade Variable Carry-Out BCD Counters which can be terminated in each field. Each counter has eight indicator lamps to indicate the current count of the counter in BCD format. The thumbwheel switches associated with each counter permit the operator to establish a desired count for which the counter will issue a carryout pulse. This two-decade BCD Counter, which is discussed in detail in Chapter 4, Section 4.2.2.4, counts up two decades (100 counts), produces a carry-out pulse, resets itself, and repeats the two-decade up count. The precount feature, determined by the thumbwheel switches, produces a carry-out pulse on a patchboard terminal labelled CO VAR when the desired precount is reached. This precount does not interfere with the normal two-decade counting cycle, but allows an intermediate carry-out pulse to be obtained.

#### 2.2.5.4 Comparator Indicators and Switches

Each of the eight comparators normally contained in a fully expanded field has an indicator and a single-pole triple throw toggle switch associated with it. The indicator lamp is illuminated when the comparator output is a logic 1. The three-position toggle switch allows the operator to preset the comparator output at the beginning of a problem, thus insuring that the comparators start in specified states. See Chapter 4, Section 4.2.1.13 for comparator programming details.

#### 2.2.5.5 Logic Switches

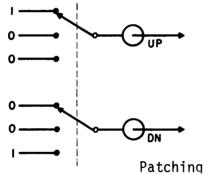

The Logic Panel contains three single-pole triple throw toggle switches labelled LOGIC for each field. These switches terminate in the upper third of the patchboard in area 1 of each field as

the computer is expanded. See Chapter 4, Section 4.2.3.3 for details. Each switch terminates in two patchboard holes, labelled UP or DN. When the switch is in the up position, a logic 1 is available at the UP terminal; when the switch is in the down position, a logic 1 is available at the DN terminal. When the switch is in the center position, logic 0 is present at both the UP and DN terminals.

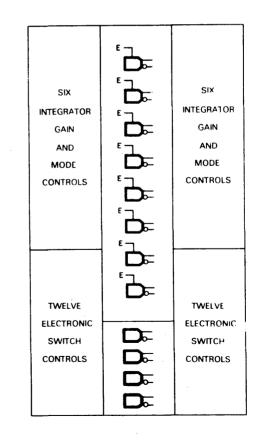

2.2.5.6 Function Switches

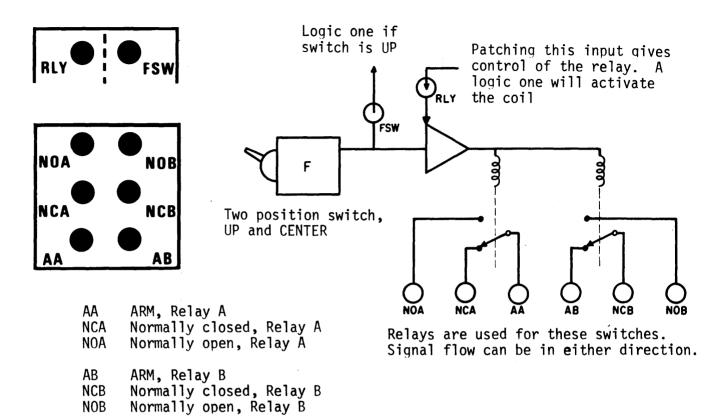

The Logic Panel contains six single-pole double throw toggle switches in each field labelled FUNCTION. Patchboard terminations for these switches are provided as the computer is expanded. (See Chapter 4, Section 4.2.3.3 for details on the operation of the Function switches.) Each of these switches serves a dual purpose: each is a logic switch and each provides manual control for a double-pole, double-throw (DPDT) relay. Two terminations are associated with these switches in logic area 1 of each field of the patchboard. The termination labelled FSW is an output controlled by the switch, and provides a logic 1 when the switch is in the up position. The termination labelled RLY is a logic signal override control input for control of the DPDT relay. Any logic source patched to RLY overrides the toggle switch control of the DPDT relay, and results in direct logic control of the relay. The DPDT relay terminates in areas 1, 3, and 5 of the upper analog section of the patchboard. Details of control of the DPDT relay are to be found in Chapter 4, Section 4.2.3.3.

2.2.6

The Control System

That part of the AD/FIVE denoted as the Control System in Figures 2-11 and 2-12 includes all of the computer internal control circuitry such as the logic clock, the interval and reference timers, the coefficient setting system, etc. Chapter 3 presents a complete discussion of the Control System.

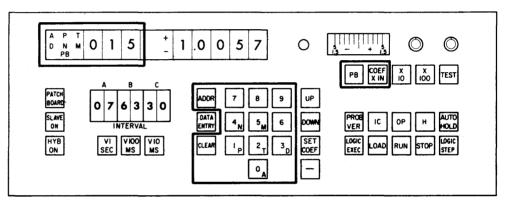

#### 2.2.7 The Control Panel

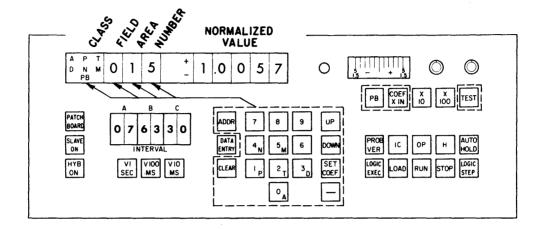

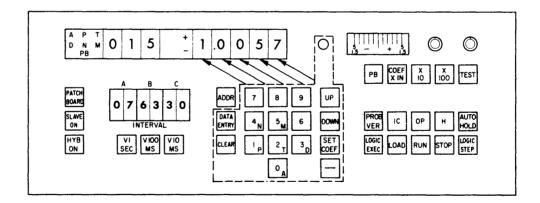

The Control Panel is the central operator interface with the AD/FIVE. This panel contains: the in-line readout display for the ADDRESS SELECTOR SYSTEM, the DIGITAL RATIOMETER (DRM), and the data register for the COEFFICIENT SETTING SYSTEM; the INTERVAL TIMER controls; the pushbutton controls for the ADDRESS SELECTOR SYSTEM, the COEFFI-CIENT SETTING SYSTEM, the LOGIC MODES, the ANALOG MODES and TIME SCALES; and the ANALOG VOLTMETER. A detailed description of the functions of these pushbuttons, thumbwheel switches and displays is included in Chapter 3. Only the general functions of these controls are presented in this chapter. 2.2.7.1

The Address System Controls and Display

The display indicators and pushbutton controls outlined in Figure 2-15 are associated with the Address Selector System. The purpose of the Address Selector System is to select the specific component whose output is to be monitored by the computer's Readout System. The following classes of components are addressable: Amplifiers (A), Potentiometers (P), Trunks (T), Digital-to-Analog Converters (D), Non-Linear (N) (i.e., DFG's, Multipliers, etc.), and Miscellaneous (M) (a class currently held in reserve for possible future use). An address consists of the following four parts: component class, field, area, and individual component number (i.e., PO18 is the potentiometer in field 0, area 1, with the component number 8). When the pushbutton labelled ADDR is illuminated, the numerical entry group of pushbuttons is used to enter an address register are normally displayed in the left-hand half of the in-line display.

Address System Controls and Display

#### Figure 2-15

A different condition exists, however, if the pushbutton labelled PB is depressed and illuminated. In this case, the address portion of the in-line display is not illuminated except for the letters PB, and the input to the Readout System comes from a patchboard input termination labelled PB.

The CLEAR pushbutton, if depressed while the ADDR pushbutton is illuminated, will clear the address register to the address A000, i.e., Amplifier 000. It will also return the hardware pointer for the sequential entry address register to the left-most (class) entry designator, so that the address register is set to accept a new address from the numerical entry pushbuttons. See Section 2.2.7.3 of this chapter for the function of the CLEAR pushbutton when the DATA ENTRY pushbutton is depressed, instead of the ADDR pushbutton.

If a coefficient device is addressed, the input to that device is removed from its patchboard input termination and is connected to the computer reference voltage so that the coefficient setting is monitored. However, if the COEF XIN pushbutton is depressed, then the input to the coefficient device remains connected to its patchboard input termination and the value of the problem variable at the output of the coefficient device is monitored.

Readout System Displays and Controls

#### Figure 2-16

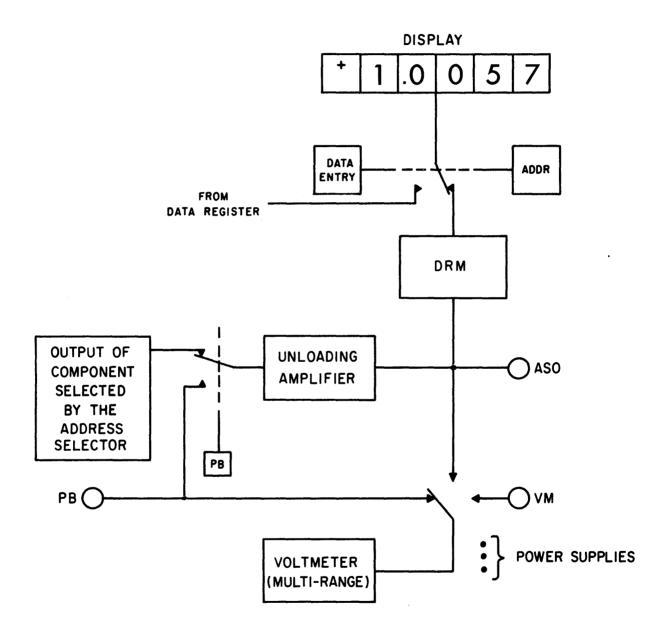

The AD/FIVE Readout System consists of an Unloading Amplifier (UA), a Digital Ratiometer (DRM), and in-line display indicators. The Unloading Amplifier is a very high input impedance device which is used to eliminate errors caused by loading effects that might otherwise occur if a component such as a potentiometer is monitored directly by the DRM. The DRM provides as its output the ratio of the voltage being monitored to the computer reference voltage. This ratio is displayed by the right-hand section of the in-line display whenever the ADDR pushbutton is illuminated.

(

2.2.7.3 Coefficient Setting System

Figure 2-17 illustrates the display indicators and controls which are used in setting or changing a coefficient.

Coefficient Setting System Displays and Controls

Figure 2-17

18.

The procedure for setting a coefficient is as follows: 1. The coefficient device to be set is addressed through the Address Selector System. 2. The DATA ENTRY pushbutton is depressed and illuminated. (Depressing the DATA ENTRY pushbutton accomplishes two things: the right hand group of display indicators is transferred from the DRM output to the data register output so that the operator can monitor the contents of the data register, and the numerical entry group of pushbuttons is transferred from the address register function to the data register function so that the operator can enter the value of the desired coefficient.) 3. The numerical entry pushbuttons are depressed sequentially to enter the value of the desired coefficient from left to right in the data register display windows. If a wrong pushbutton is depressed during data entry, pushing the CLEAR button will clear the data register to 0.0000, and the desired coefficient may be correctly reentered. 4. The SET COEF pushbutton is depressed, and remains illuminated for the time during which the coefficient is being set (approximately 1 second); pushing the SET COEF pushbutton automatically sets the coefficient device to the value entered in the data register. The desired coefficient is now set.

The minus (-) entry pushbutton located beneath the SET COEF pushbutton is used in the setting of DAC's and four-quadrant DCU's. See the hybrid reference manual for details of DAC and DCU setting.

At the end of the setting operation the DATA ENTRY pushbutton light is extinguished and the ADDR button becomes illuminated; the righthand section of the indicator display is automatically returned to the DRM output so that the operator can verify the setting of the coefficient device, and the numerical entry pushbuttons are automatically returned to the address selector function, so that a new address may be selected as desired. Note that the output from a coefficient device must be patched to an appropriate linear load for correct setting of the desired coefficient in the problem; a coefficient device should not be set before patching the output to the desired problem input of a linear computing component.

The two pushbuttons labelled UP and DOWN contained in the section outlined by a dashed line in Figure 2-17 allow the operator to vary the coefficient setting of a servo-set potentiometer in an open loop manner. If a servo-set pot is addressed, depressing the UP pushbutton will increase the value of the coefficient in a continuous manner, and depressing the DOWN pushbutton will decrease the value. The slew rate can be controlled by the potentiometer located above the UP and DOWN pushbuttons on the control panel.

If a potentiometer is addressed, the input to the pot is switched from the patchboard input termination to computer reference, and the indicator display shows the setting of the potentiometer with respect to the computer reference voltage. Depressing the COEF XIN pushbutton, however, causes the input to the coefficient device to remain connected to the patchboard input termination, and the indicator display then reads the value of the coefficient times the input; i.e., the value of the problem variable at the output of the coefficient device is monitored. Using the UP and DOWN pushbuttons with COEF XIN depressed allows the operator to vary the setting of the coefficient device in a continuous manner without removing it from the computational configuration. It should be noted here that, even though COEF XIN is depressed, using the DATA ENTRY and SET COEF pushbuttons will cause the coefficient device to be removed from its patched input for the time during which the coefficient is being set and the SET COEF pushbutton is illuminated, thus in effect removing the device from the computational configuration. This does not occur when the UP and DOWN buttons are used with COEF XIN depressed. This permits the operator to conveniently vary a parameter or coefficient during a problem solution.

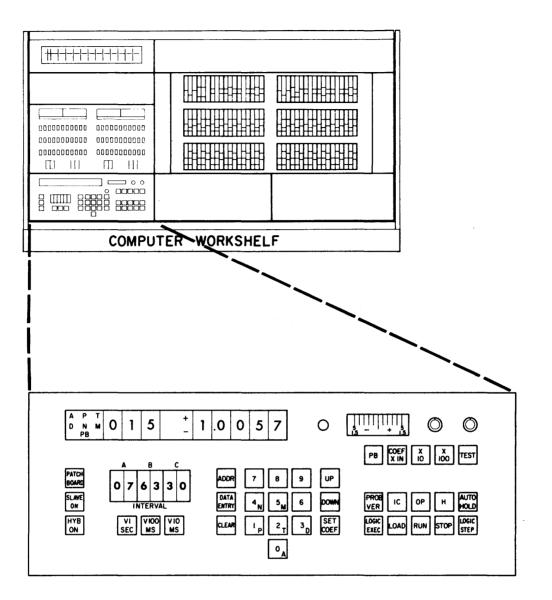

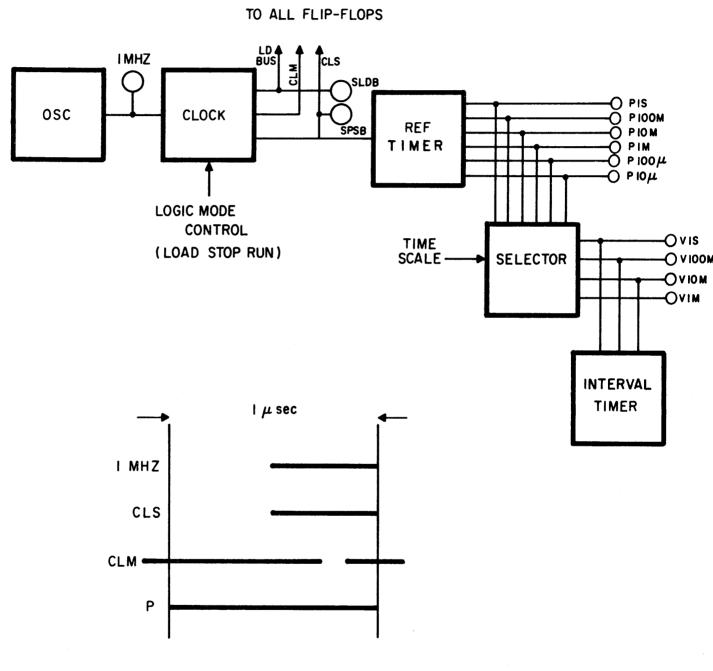

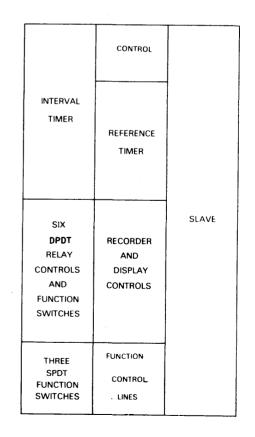

#### 2.2.7.4 The Interval Timer Controls

#### Interval Timer Controls

#### Figure 2-18

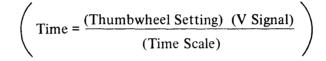

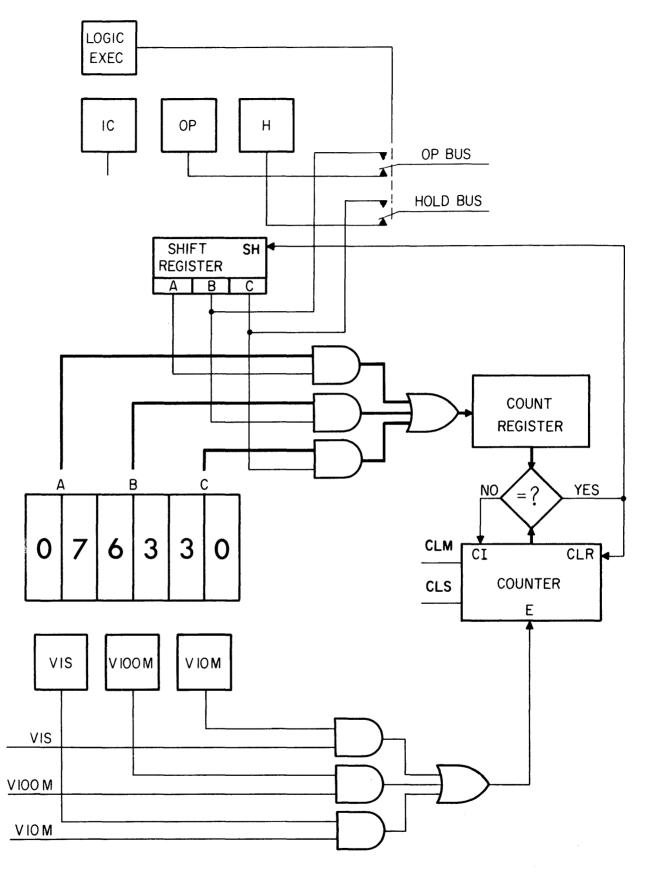

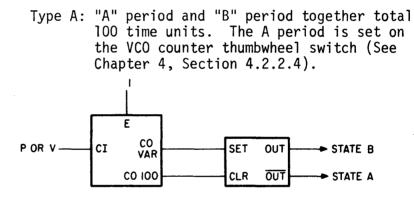

The pushbuttons and thumbwheel switches which are used to control the Interval Timer are illustrated in Figure 2-18. The Interval Timer provides three sequential timing intervals for cyclic control of the computer analog modes when the LOGIC EXEC pushbutton is depressed. Interval A corresponds to initial condition, B to operate, and C to hold. Each interval duration is set with a two-decade thumbwheel switch. The three pushbuttons below the Interval Timer set the decimal point for the three periods by multiplying the setting on the thumbwheel switches by 1.0, 0.1, or 0.01 seconds. The Interval Timer outputs are terminated on the patchboard in field 0, logic area 1, and are accompanied by control terminations. The outputs of the Interval Timer are also internally connected to the computer analog mode control buses, thus allowing repetitive operation if desired. The Interval Timer is also very useful as a ring counter with a carry-out pulse generated every time the timer changes state. Details of the Interval Timer and its operation are presented in Chapter 3, Section 3.1.4, and Chapter 4, Section 4.2.2.6.

The Analog Voltmeter

### Figure 2-19

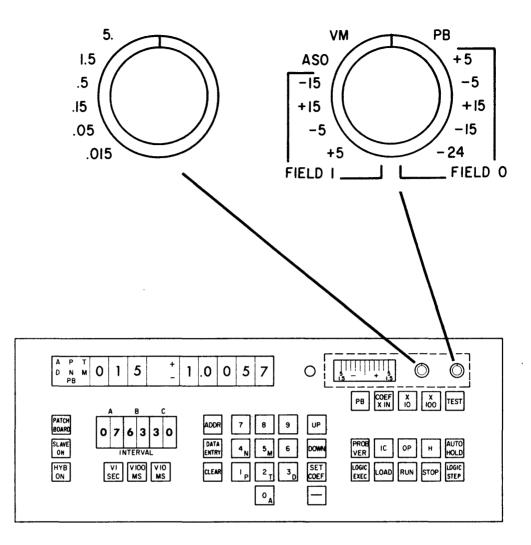

The Analog Voltmeter and its controls are shown in Figure 2-19. One rotary switch allows a variety of scale selections for the voltmeter. The other rotary switch selects the input to the voltmeter. The choice of inputs includes the Address Selector Output (ASO), two patchboard terminations labelled PB and VM, and the outputs of the various power supplies. When ASO is selected, the voltmeter is connected to the output of the Unloading Amplifier and reads the value at the point addressed.

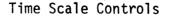

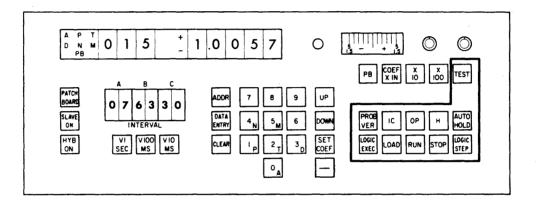

Figure 2-20

The two pushbuttons indicated in Figure 2-20 determine the computer time scale. Four time scales are available with the use of these pushbuttons. These are:

X1 If neither pushbutton is depressed and illuminated; X10 If the X10 pushbutton is depressed and illuminated; X100 If the X100 pushbutton is depressed and illuminated; X1000 If both the X10 and X100 pushbutton are depressed and illuminated.

These pushbuttons control the integrator time constants and allow the operator to speed up or slow down the problem solution. The pushbuttons also control the selection of clock subfrequencies so that the Interval Timer and the logic computing components may also be appropriately time scaled.

2.2.7.7 Mode Control Pushbuttons

Figure 2-21

The group of pushbuttons outlined in Figure 2-21 are associated with the computer mode control. The three pushbuttons labelled IC, OP, and H activate the three normal analog operational modes of Initial Condition, Operate, and Hold. These controls do not affect the logic system. The three pushbuttons just below the analog mode controls labelled LOAD, RUN, and STOP are the logic mode control pushbuttons, and control the clocking signals and the logic. In the LOAD mode, all logic components are set to their initial states or cleared when it is appropriate. In the RUN mode, clocking signals are applied to all logic components as patched. The STOP mode interrupts the clocking signals and freezes the logic in its current state.

The LOGIC EXEC pushbutton completely disables the analog mode pushbuttons and transfers the console analog mode control buses to Interval Timer control. Thus the time in IC, OP, and H is determined by the thumbwheel switches and V pushbuttons of the Interval Timer. The logic mode control pushbuttons can provide complete control of repetitive operation without any special patching while LOGIC EXEC is depressed and illuminated.

22.

The LOGIC STEP pushbutton is operative when the logic mode is STOP, and allows advance of the logic program by a predetermined number of clock pulses. See Chapter 3, Sections 3.1.2.4 and 3.1.2.5 for details on the use of the LOGIC STEP pushbutton.

AUTO HOLD activates automatic hold of all integrators if any analog component overloads. This high-speed feature is most helpful in problem checkout. See Chapter 3, Sections 3.1.1.2 and 3.1.1.3.

The PROB VER pushbutton controls relays that disable certain patchboard reference terminals and activate others, allowing test initial conditions to be applied to integrators for problem verification. See Chapter 3, Section 3.1.1.4.

If the TEST pushbutton is depressed when the analog mode is IC, an addressed integrator is automatically converted to a summer whose output is proportional to the integrator's initial derivative input current. This feature is useful in the static check-out of a problem. See Chapter 3, Section 3.1.6.5 for details.

# 2.2.7.8 Miscellaneous Controls

Three pushbuttons on the left-hand side of the control panel remain. The PATCHBOARD pushbutton activates the patchboard motor drive mechanism. The SLAVE ON pushbutton provides an enable signal to computer control circuits to allow some of the AD/FIVE controls to be operated remotely from another computer. The HYB ON pushbutton provides an enable signal to the hybrid interface to allow control of the AD/FIVE from the digital computer in a hybrid computer system.

# CHAPTER 3

# THE CONTROL SYSTEM

# CHAPTER THREE

# THE CONTROL SYSTEM

|                     | Table of Cor                    | ntents         |          |         |   |   | Page       |

|---------------------|---------------------------------|----------------|----------|---------|---|---|------------|

| 3.0                 | THE CONTROL SYSTEM              |                | • •      | •••     | • | • |            |

| 3.1                 | PUSHBUTTON CONTROL              | • • •          |          | •••     | • | • | . 2        |

| 3.1.1               | Analog Mode Control             |                |          |         | • |   | . 3        |

| 3.1.1.1             | Initial Condition,              |                |          |         |   |   | . 3        |

| 3.1.1.2<br>3.1.1.3  | Master Hold<br>Auto-Hold        | • • •          | • •      | •••     | • | • | .5<br>.5   |

| 3.1.1.4             | Problem Verify .                |                |          |         |   |   | . 5        |

| 3.1.2               | Logic Mode Control              | • • •          |          |         | • | • | . 7        |

| 3.1.2.1             | General                         |                |          |         |   | • | . 7        |

| 3.1.2.2             | Synchronous Logic               | • • •          | •••      | •••     | • | • | . 7        |

| 3.1.2.3<br>3.1.2.4  | Load, Stop, Run .<br>Logic Step |                |          |         |   |   | .8<br>.9   |

| 3.1.2.5             | Advance Step                    | ••••           | •••      | •••     | • | • | . 9        |

| 3.1.3               | Time Scale Control              |                |          | • •     | • | • | . 9        |

| 3.1.3.1             | Analog                          |                |          |         |   | • | . 9        |

| 3.1.3.2             | Logic                           | • • •          | • •      | • • •   | • | • | .10        |

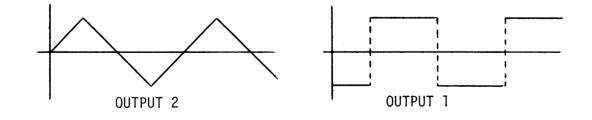

| 3.1.4               | Repetitive Operation .          | •••            | • •      | • •     | • | • | .12        |

| 3.1.5               | Simulation Operation .          | • • •          | • •      | •••     | • | • | .14        |

| 3.1.6               | Addressing                      | • • •          | • •      | •••     | • | • | .15        |

| 3.1.6.1             | Amplifier, Trunk,               |                |          | • •     | • |   | .18        |

| 3.1.6.2             | Miscellaneous.                  |                |          | $\cdot$ | • |   | .18        |

| 3.1.6.3<br>3.1.6.4  | Potentiometer (Coe<br>PB        |                |          |         | • |   | .18<br>.18 |

| 3.1.6.5             | Test                            | • • •          | •••      | •••     | : | • | .19        |

| 3.1.6.6             | Panel Voltmeter .               |                |          |         |   | • | .20        |

| 3.1.7               | Coefficient Setting.            | • • •          | •••      | • •     | • | • | .20        |

| 3.1.7.1             | Hand-set Potention              |                |          |         |   | • | .20        |

| 3.1.7.2             | Servo-set Potentio              | meters .       | • •      | • •     | • | • | .21        |

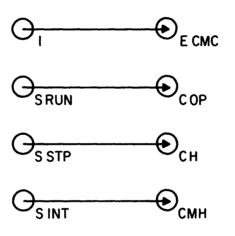

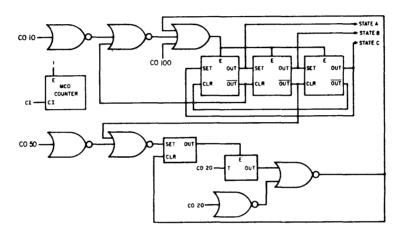

| 3.2                 | LOGIC PROGRAM CONTROL           | • • •          | •••      | •••     | • | • | .22        |

| 3.2.1               | Analog Mode Control             | • • •          | • •      | • •     | • | • | .24        |

| 3.2.2               | Logic Mode Control              | • • •          | •••      | • •     | • | • | .25        |

| 3.2.3               | Time Scale Control              | • • •          | •••      | •••     | • | • | .25        |

| 3.2.4               | Miscellaneous                   |                |          | • •     | • | • | .26        |

| 3.2.4.1             | Clock Selection .               |                |          |         |   |   | .26        |

| 3.2.4.2             | Slaving                         | • • •          | •••      | • •     | • | • | .26        |

| 3.2.4.2.1 3.2.4.2.2 | Ťwo AD/FIVE'<br>An AD/FOUR a    | 5<br>nd an AD/ | <br>FIVF | • •     | • | • | .28        |

| 3.2.4.2.3           | To a Brand X                    |                |          |         |   |   |            |

| 3.2.4.3             | IO Devices                      | • • •          | • •      |         | • |   | .31        |

# CHAPTER THREE

# THE CONTROL SYSTEM

# List of Illustrations

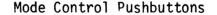

| 3-1  | OR/NOR and AND/NAND Relationships          | . 1 |

|------|--------------------------------------------|-----|

| 3-2  | Emitter-Follower-Override                  | . 2 |

| 3-3  | AD/FIVE Control Panel                      | . 3 |

| 3-4  | Analog Modes                               | . 4 |

| 3-5  | Simplified Flip-Flop                       | 6   |

| 3-6  | Logic Modes                                | . 8 |

| 3-7  | AD/FIVE Timing Signals                     | .11 |

| 3-8  | Interval Timer Operation                   | .12 |

| 3-9  | Interval Timer                             | .13 |

| 3-10 | Simultaneous Logic and Analog Mode Control | .14 |

| 3-11 | Addressing and Coefficient Setting         | 15  |

| 3-12 | Readout System                             | .16 |

| 3-13 | Test Feature                               | .19 |

| 3-14 | Panel Voltmeter Controls                   | .21 |

| 3-15 | Logic Program Control                      | .23 |

| 3-16 | Slaving and Overload Signals               | .27 |

| 3-17 | Slaving Two AD/FIVE's                      | .28 |

| 3-18 | Slaving and AD/FIVE to an AD/FOUR          | .29 |

| 3-19 | Slaving an AD/FOUR to an AD/FIVE           | .30 |

## 3.0 THE CONTROL SYSTEM

The AD/FIVE control system was designed to realize three primary objectives:

- 1. Simplicity and convenience of operation;

- 2. Flexibility in the use of commonents;

- 3. Ease of hybrid integration.

Simplicity and flexibility may appear to be contradictory goals, since an increase in flexibility makes more choices available to the operator, which requires the operator to become familiar with a wider range of possibilities and to be able to make decisions based on this wider range. The Applied Dynamics philosophy of CONTROL BY EXCEPTION resolves this apparent contradiction. Complete control of the AD/FIVE may be exercised from the control panel pushbuttons, without the need for logic patching or a digital computer. The operator thus does not need to consider complex control features until he becomes familiar with them and desires to use them. Sophisticated control features are available and may then be implemented one by one as the problems become more complex and as the operator's familiarity with the potential of the versatile control system increases.

Ease of hybrid integration is achieved through the hybrid interface, which gives the digital computer access to all operator controls, without, however, excluding the operator from the system. The operator thus retains the ability to directly interact with a hybrid problem without having to go through the digital computer. The hybrid interface is described in detail in a separate section of the reference manual.

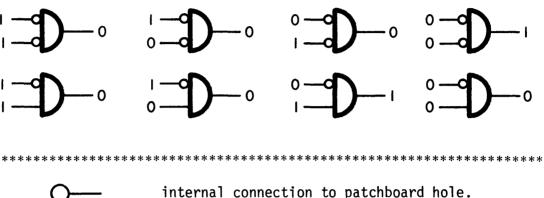

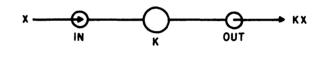

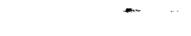

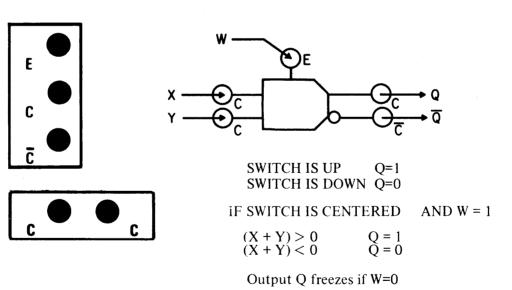

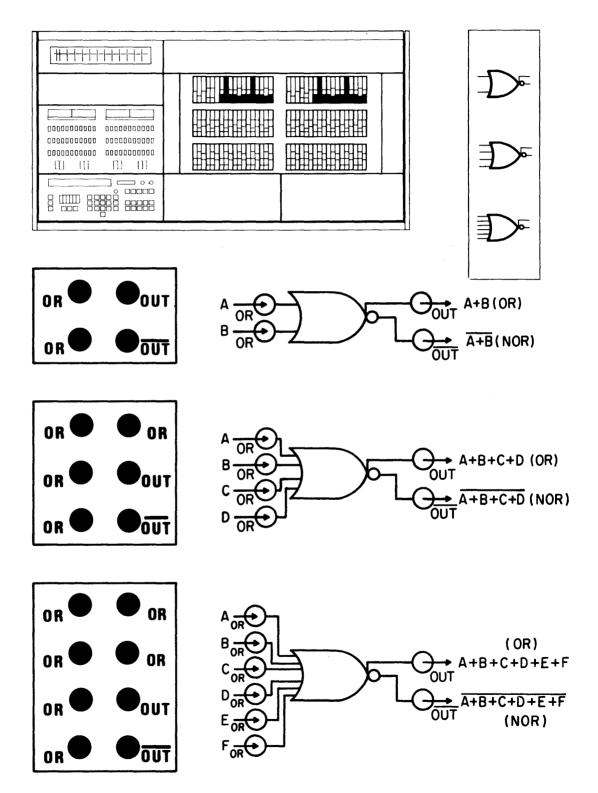

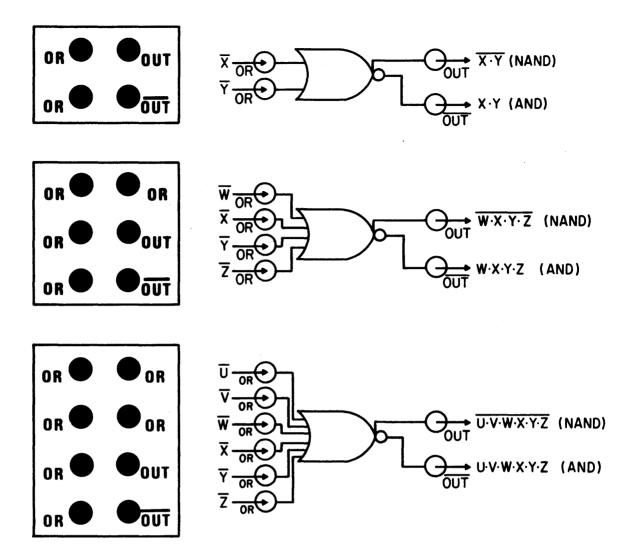

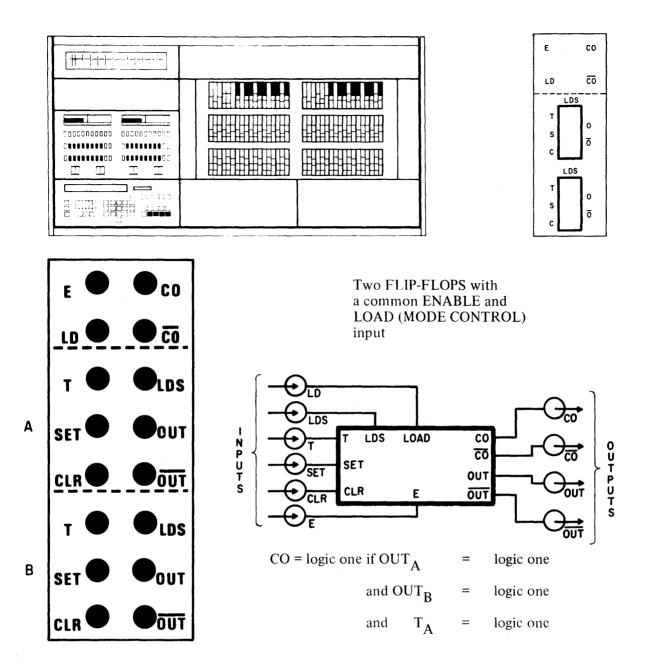

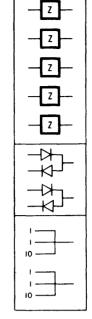

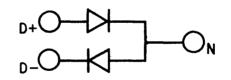

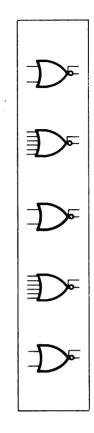

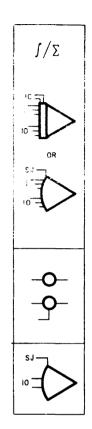

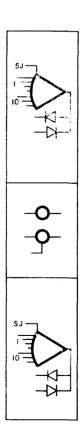

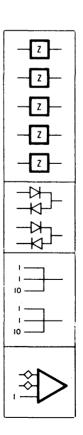

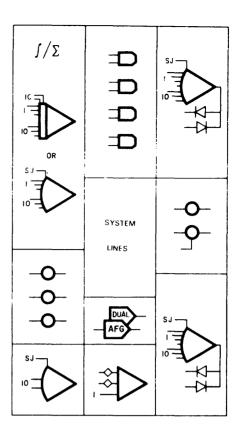

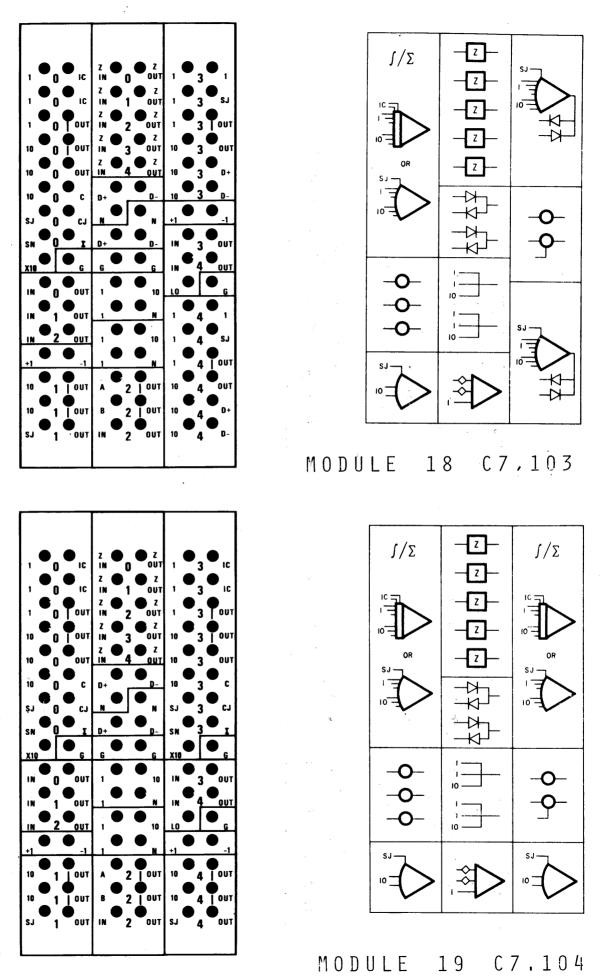

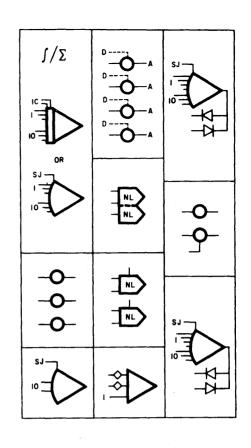

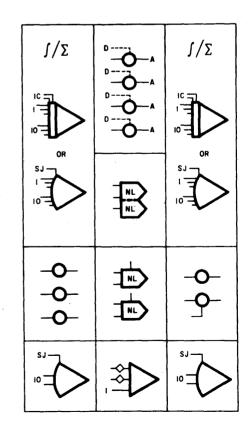

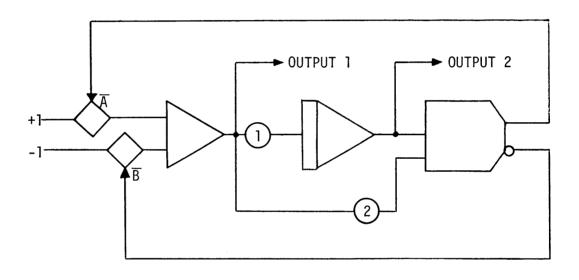

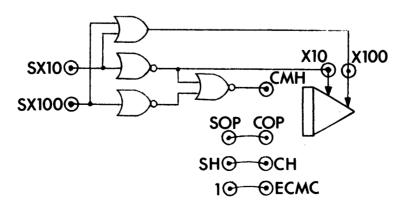

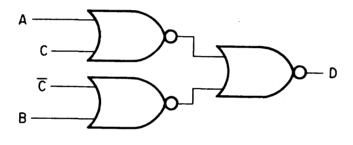

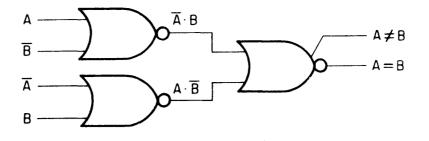

The symbols for OR/NOR and AND/NAND gates are used in this chapter. The reader should be familiar with signal steering through logic gates, and should be thoroughly familiar with the concepts of "logic one" and "logic zero". Figure 3-1 shows the relationships of logic gates and their logic inputs and outputs as used in this manual.

OR/NOR and AND/NAND Relationships

#### Figure 3-1

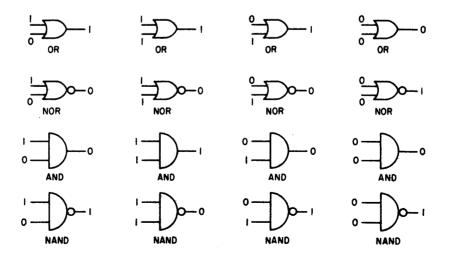

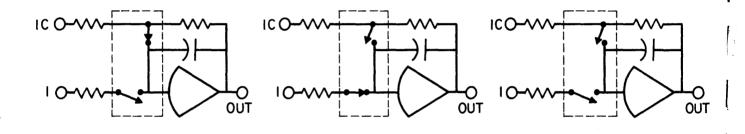

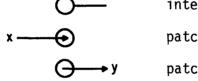

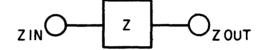

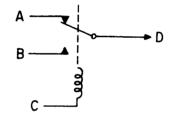

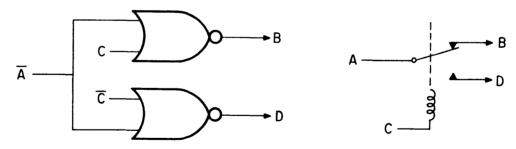

A symbol is also introduced here which is not commonly encountered except in the documentation of Applied Dynamics computers. This is the symbol for the electronic emitter-follower override, which is an improvement in cost and simplicity over the patchbay-pin-switch scheme used on some computers. The symbol is illustrated in Figure 3-2.

Emitter-Follower-Override

Figure 3-2

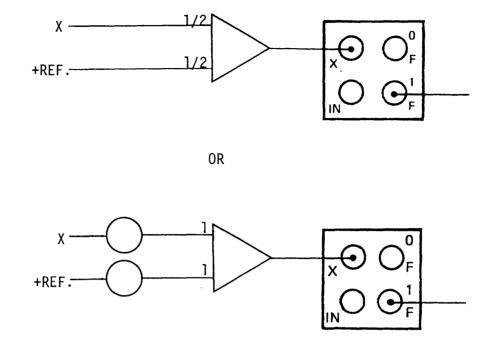

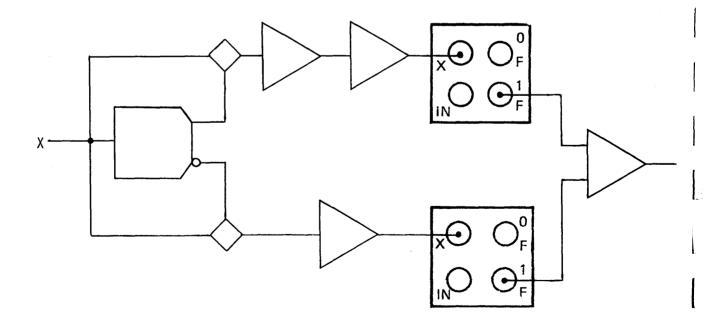

The emitter-follower-override symbol is used to represent the following control scheme; Normally a control signal from source A is delivered to destination C. If, however, a control signal is patched into the patchhole at B (from some logic output), then the signal patched at B will be delivered to destination C and signal A is ignored. The above definition is true regardless of the state (logic one or logic zero) of either A or B.

## 3.1 PUSHBUTTON CONTROL

The AD/FIVE operator can have complete pushbutton control of:

Analog mode Logic mode Time Scale Repetitive Operation Addressing Coefficient Setting Problem Checkout

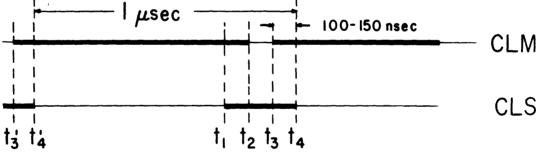

No patchable logic controls are necessary to control the above functions. The control panel and pushbuttons are shown in Figure 3-3. This section describes only these control panel features. Control by exception from the logic patchboard is discussed in Section 3.2.

2

AD-FIVE CONTROL PANEL

Figure 3-3

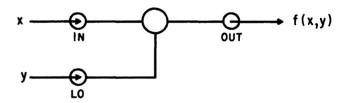

# 3.1.1 Analog Mode Control

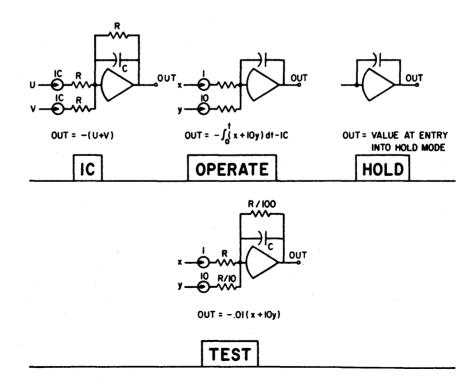

3.1.1.1 Initial Condition, Operate, Hold

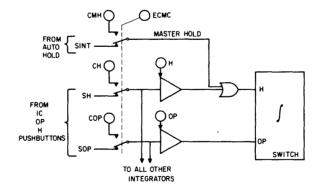

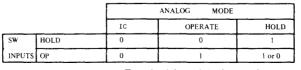

The AD/FIVE has three basic analog modes: Initial Condition (IC), Operate (OP), and Hold (H). These three modes correspond to the states of the integrator mode control switches and are defined schematically in Figure 3-4. Mode switching is actually done with a high speed electronic switch. All integrator mode switches are normally connected to the console mode control bus lines and are controlled by the control panel pushbuttons IC, OP, and H.

3

IC

OP

Η

The mode switches are designed to respond to the control inputs in accordance with this truth table.

#### 3.1.1.2 Master Hold

Master Hold is an analog mode in which all integrator controls are put in hold, and cannot be overridden. Master Hold may be generated in a number of ways, and these are discussed in section 3.2 of this Chapter. Master Hold may be generated by the use of the AUTO HOLD pushbutton as described below.

#### 3.1.1.3 Auto Hold

When the AUTO HOLD pushbutton is depressed, the analog and logic operations will run normally unless an overload occurs in any analog component. When an overload occurs, the Master Hold Bus is automatically activated, and forces all integrator mode switches to the hold position, regardless of any individually patched mode control. Use of the AUTO HOLD pushbutton will cause one of two conditions to occur in the case of an overload in an analog component:

- 1. If LOGIC EXEC is not depressed, then the analog operation only will freeze;

- 2. If LOGIC EXEC is depressed, then both the analog and the logic operations will freeze.

If the AUTO HOLD button is activated, only manual intervention by the operator will release it and deactivate the hold condition. When the AUTO HOLD button is desengaged by the operator, the integrator mode switches will return to the states commanded by the console mode buses before the auto hold feature was activated.

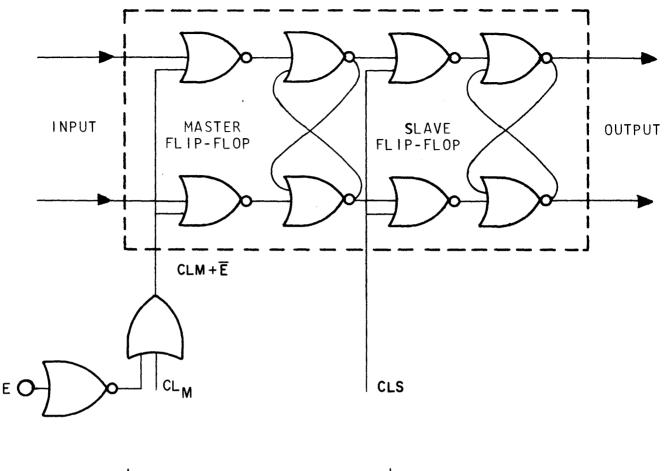

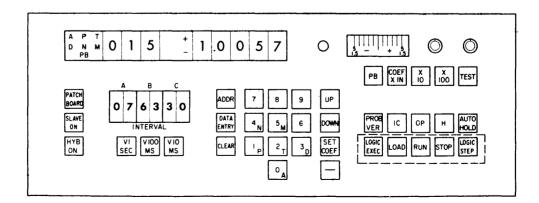

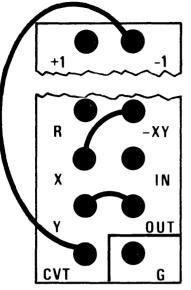

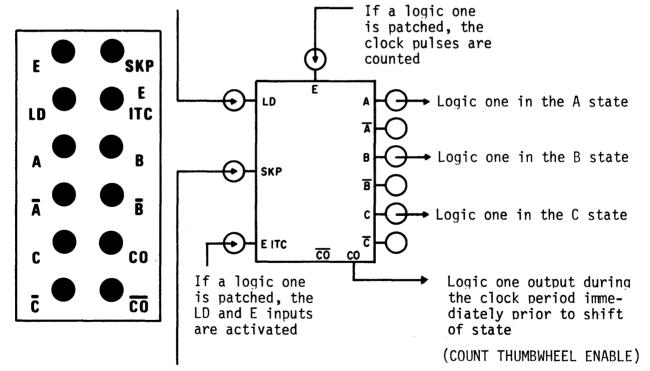

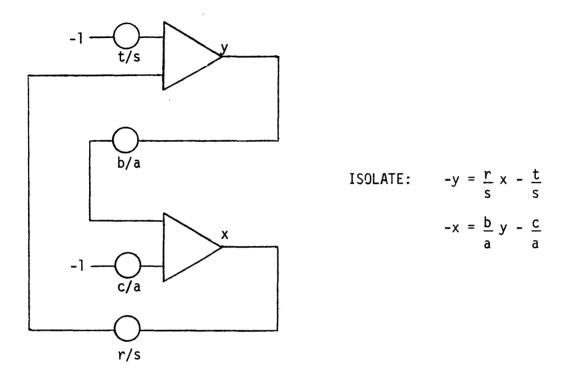

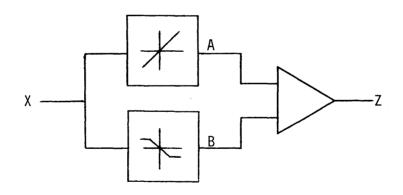

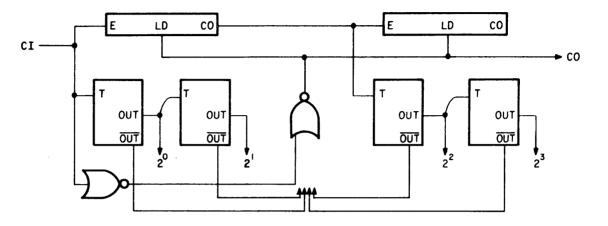

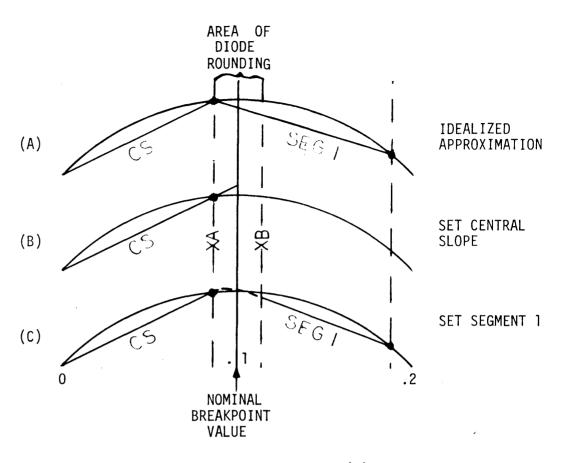

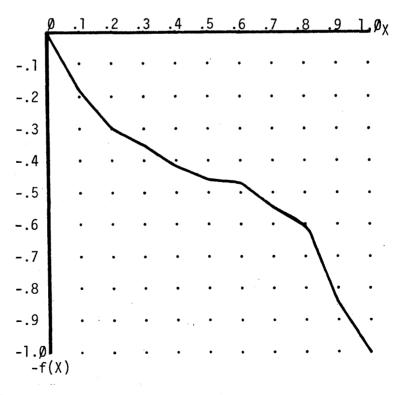

#### 3.1.1.4 Problem Verify