# SIGDA NEWSLETTER

A Quarterly Publication of the Special Interest Group on Design Automation

| VOLUME 20                                                                                   | NUMBER 3                                                                                                                 | DECEMBER 1990                              |

|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| CONTENTS                                                                                    |                                                                                                                          | PAGE                                       |

| SIGDA Advisory Boar                                                                         | d Meeting Minutes (September 90)<br>d Meeting Minutes (November 90)<br>pership Meeting Minutes (ICCAD)<br>Section<br>Pry | 2<br>3<br>10<br>16<br>18<br>21<br>23<br>24 |

| DEPARTMENTS Benchmarks—France Scholarships—Hers DATAPLAN Project                            |                                                                                                                          | 26<br>29<br>30                             |

| ARTICLES ASIC Design in VHI A VHDL Design En                                                | DL—Alford vironment—Martello & Levitan                                                                                   | 32<br>52                                   |

| Conference Reports<br>DA Standards Activiti<br>Conferences & Annou<br>Statement of Publicat | incements                                                                                                                | 68<br>84<br>96<br>114                      |

| ***********                                                                                 | **************************************                                                                                   | *******                                    |

(See page 23)

# SIGDA BOARD OF ADVISORS

# **Nominating Committee Chair**

Richard C. Smith

National Semiconductor, Inc.

2900 Semiconductor Drive, D3677

Santa Clara, California 95051

(408) 721-4794 FAX (408) 773-0978

nsc!parns!ricardo

# **High School Scholarship Program**

Charlotte F. Acken Sandia National Laboratories, Div. 4853 P. O. Box 969 Livermore, California 94551 (415) 294-3248 FAX (415) 294-1539 cacken@sandia.llnl.gov

# **Bibliography & Textbook Projects**

Waldo G. Magnuson, Jr. Lawrence Livermore National Lab. P. O. Box 808, L-153 Livermore, California 94550 (415) 422-9950 FAX (415) 423-5080 magnuson@icdc.llnl.gov

# Workshops/Conferences (except DAC)

Paul B. Weil Nextwave Design Automation, Inc. 5339 Prospect Road, Suite 240 San Jose, California 95129 (408) 255-6458 weilcad@frith.cs.psu.edu

# IEEE/CS DATC Chairman

Joanne E. DeGroat

Department of Electrical Engineering

Ohio State University

2015 Neil Avenue

Columbus, Ohio 43210-1272

(614) 292-2439 FAX (614) 292-7596

degroat@hathi.eng.ohio-state.edu

# **Outstanding Member Recognition**

Charles E. Radke

IBM Corporation, AR1

Route 52

Hopewell Junction, New York 12533

(914) 892-2957 FAX (914) 892-3039

C.RADKE@COMPMAIL.COM

# **European Activities**

H. Gordon Adshead International Computers Ltd. Wenlock Way, West Gorton Manchester M125DR, ENGLAND (011-44-61) 223-1301

# **Asian Activities**

Akihiko Yamada, Chief Engineer Information Processing Group NEC Corporation, Daito Tamachi Bldg. 14-22 Shibaura 4-Chome, Minato-Ku Tokyo 108, JAPAN (011-81-3) 456-5750 FAX (011-81-3) 456-7495 a.yamada@compmail.com

# **Travel Grants and Library Grants**

James P. Cohoon, Ph.D.

Department of Computer Science

University of Virginia, Thornton Hall

Charlottesville, Virginia 22903

(804) 982-2210 FAX (804) 982-2214

csnet: cohoon@virginia.edu

uucp: !uvacs!cohoon

# **Scholarships**

Herschel Loomis, Jr.

Naval Postgraduate School - EE Dept.

Code 62Lm

Monterey, California 93943

(408) 646-3214

loomis@cs.nps.navy.mil

# **University Faculty Activities**

Mary Jane Irwin

Pennsylvania State University

Department of Computer Science

University Park, Pennsylvania 16802

(814) 865-3176

mji@psuvaxl.cs.psu.edu

# University Booth Project (DAC)

Martin Wong

Department of Computer Science

University of Texas

Austin, Texas 78712

(512) 471-7316

wong@cs.utexas.EDU

# SIGDA OFFICERS

# Chairman & ACM DAC Representative

Charles A. Shaw

Cadence Design Systems, Inc.

2455 Augustine Drive

Santa Clara, CA 95054-3082

(408) 987-5321

shaw@cadence.com

# Secretary/Treasurer

Michael J. Lorenzetti Mentor Graphics Corporation 8500 S.W. Creekside Place Beaverton, OR 97005-7191 (503) 626-7000 mikelor@mentor.com

# **EDITOR'S NOTES**

Welcome to the Winter edition of the SIGDA Newsletter. This will be the final edition of 1990, and it is an important one since it contains the slate of officers for SIGDA. There are two candidates for each office. Please be sure to vote. See page 23 for a listing of the candidates and related information.

This edition also contains two articles on VHDL. One is a lucid tutorial on VHDL design techniques by David Alford. David is from industry and has illustrated his article with a very comprehensive set of examples. The other article is a description of the Keystone VHDL Design System developed by the University of Pittsburgh and Penn State University. The authors, Alan Martello and Steven Levitan, are from the academic community, and they too have included design examples in their article. Both articles take a very practical approach to using VHDL in design. I think they will be of particular interest to those just learning about VHDL and needing explicit examples of it use.

Additionally, this edition contains the minutes of two Advisory Board meetings and the Fall (ICCAD) General Membership meeting. These minutes contain good summaries of the state of the various projects of SIGDA. Also, included is the second edition of the SIGDA e-mail directory. It was drawn from the survey responses. If you want to be listed, just send in your survey form. I suspect the e-mail directory will become ever more popular.

One last note: At the recent SIG Board Meeting, a motion was passed (authored by Tom Keller, chairman of SIGMETRICS) that removes the prohibition

# **Vice Chairman & IEEE DATC Newsletter Coordinator**

Bryan T. Preas

CADLAB

Bahnhofstrasse 32

4790 Paderborn, West Germany

011 49 52 51 28 41 02 main

011 49 52 51 60 20 67 secy

preas.@cadlab.cadlab.de

preas%cadlab.uucp@seismo.css.gov

# **ACM SIG Program Director**

Debbie Hall 11 West 42nd Street New York, NY 10036 (212) 869-7440 Hall@ACMVM.Bitnet

against employment advertising in SIGNewsletters. The SIGDA Advisory board has not formally acted on this relative to SIGDA; however, a straw e-mail poll indicates that there is broad support for this idea. If adopted, SIGDA members could submit 'situations wanted' ads (probably for free), and DA companies could submit 'help wanted' (probably for a fee). Please don't send me your ad-copy yet since ACM-HQ must be consulted on fee structures, disclaimers, policies, etc. However, it seems likely that this new service may be added some time in 1991.

Patrick M. Hefferan - SIGDA Editor

1681 Princeton Ave. St. Paul, MN 55105 (612)690-5451 hefferan@frith.entmoot.cs.psu.edu

# LETTER FROM THE CHAIR

SIGDA has an election this Spring. In this issue, you'll find the list of nominations for our elected officers. Put together by Dick Smith, this list presents you, the members, with a selection of the most dedicated and dynamic participants in SIGDA and its activities. Dick drew on his long experience in SIGDA activities, including his position as Chair preceding me. He is uniquely qualified to head up the Nominating Committee, whose role was to put together this slate of candidates.

Should you feel that a strong candidate has been overlooked, it is not difficult to add nominations by petition. The procedure is detailed in the same section of this Newsletter.

I am not running for SIGDA office. I feel that you have had a long enough period under my leadership; it's time for a change. No organization can be healthy for the long pull if its top position isn't open, as a goal to which others in the organization can aspire. California, in the recent election, put a term limit on its state legislators - I don't want SIGDA to feel that it would need to do the same to move me out!

SIGDA has before it many exciting opportunities. It will be a pleasure, not a burden, to be elected an officer of SIGDA. There are few organizations with the financial resources of SIGDA, with such a dedicated and active group of volunteers, with such wholehearted support from its parent organization ACM, and with such a dynamic technical field of CAD as its base. The new

officers will have a rich set of alternatives from which to choose.

Among these are the emergence of an integrated Europe, stretching from the Atlantic to the Soviet Union, and the chance for SIGDA to play a strong role in its conferences, workshops, universities, and industries. In Asia, the Japanese CAD-oriented conferences draw as many attendees as does DAC. Other Asian countries are ripe for a strong expansion in their CAD activities.

ACM continues to examine its structure and the services its members want to have from it. SIGDA is fortunate in having ACM as its parent - ACM has become, during my term of office, a SIG-oriented organization. SIGDA's strength gives it a leading role in ACM deliberations. The SIGDA officers are key players in ACM direction and policy decisions.

There is also the great personal satisfaction of leading an organization doing as many good things as SIGDA does. The officers you elect can feel justly proud to be elected. So choose wisely, and VOTE!

Charles A. Shaw - Chairman SIGDA

December 1990

# SIGDA ADVISORY BOARD MEETING MINUTES

The SIGDA Advisory Board Meeting was called to order at 9 a.m. on <u>September 16, 1990</u> by Chairman Chuck Shaw. In attendance were Board Members Franc Brglez, Jim Cohoon, Patrick Hefferan, Mary Jane Irwin, Michael Lorenzetti, Bryan Preas, Chuck Radke, Ron Waxman, Paul Weil, and Akihiko Yamada. Also in attendance were Joe Deblasi and Debbie Hall, from ACM Headquarters and Mark Mendelbaum, Bill Greener, Meg Tuttle and Bernie Rouse from the ACM Publications Board.

### A. Minutes

**MOTION:** The minutes of the June 23 SIGDA Board Meeting be approved as submitted. (Weil, Irwin, unanimous)

### B. Financial

Secretary/Treasurer Michael Lorenzetti reviewed the financial status of SIGDA. The fund balance is approximately \$1,300,000 as of June 30, 1990. As discussed in our last meeting, our annual recurring expenses are now on the order of the revenues we realize from the Design Automation Conference (~\$800,000). For fiscal year 1990, our expenses exceeded our revenues by \$166,000, which indicates we are beginning to apply our massive fund balance to services for the DA profession.

# C. Newsletter

Pat Hefferan reviewed the sales of proceedings, EDIF and VHDL manuals via the coupons published the Newsletter. This program provides low-cost standards manuals and proceedings to our members. He presented the following summary:

| pro                    |        |            |

|------------------------|--------|------------|

|                        | Number | Cost       |

| EDIF manuals           | 58     | \$3,378    |

| VHDL manual            | 76     | 3,130      |

| 25 years of DA         | 35     | 5,100      |

| 1990 DAC proceedings   | 60     | (w/25 Yrs) |

| 1990 ICCAD proceedings | s 50   | 3,000      |

| Subtotal               |        | 14,608     |

| Postage                |        | 1,012      |

| Labor (@\$20/hr)       |        | 1,000      |

| TOTAL                  |        | \$16,620   |

| ł .                    |        |            |

Hefferan also summarized the administration cost for the Newsletter which totaled \$5,544 for the year so far.

Hefferan requested that SIGDA purchase a PC and laser printer for Newsletter administration. He detailed the request as follows:

| 386SX PC         | \$2,600    |

|------------------|------------|

| HP Laser Printer | 1,800      |

| Modem            | 300        |

| Software         |            |

| Ventura          | 500        |

| Word             | 400        |

| Communications   | <u>100</u> |

| TOTAL            | \$5,700    |

MOTION: Approve Pat Hefferan's request for \$5700 for a PC and laser printer for Newsletter support. (Weil, Cohoon, unanimous)

# D. DA Library (CD-ROM)

Kathy Preas reported that there was a great deal of enthusiasm for the DAL demos at DAC. Evaluators have been invaluable in getting feedback on the system. Many design changes have resulted. She summarized some of these.

DAL will be organized by year rather than by publication. This facilitates updates each year but makes addition of other series more difficult. ICCD proceedings have been added. The SIGDA Newsletter is included, but as page images only (this means only that it will not be searchable). The 1990 proceedings will not be included in the first release because it was not budgeted.

All text will be stored on one CD as a search device. Page images will appear on the remaining seven CDs. They plan to go back and key in tables, algorithms and other similar entries that were previously considered unkeyable. They are putting a QA plan in place. SAZTEC will do 100%

sampling of page images (some were skewed in the prototype). There will be some sampling of keyed text.

The 1989 volumes will be done as an additional pre-production evaluation version within a couple of weeks. The final version will not be available by the DAC in June. Prototype evaluation is taking longer than anticipated and there were more changes than anticipated. They expect to have ROMs pressed by July.

A discussion ensued about whether this process can be speeded up, but no solutions were found. SUN now requires purchase of CD-ROM to get software. This helps us in that drives will be installed (which is difficult).

MOTION: Expand the DA Library budget (by approximately \$110,000) to include 1990 publications, if possible. (Hefferan, Lorenzetti, unanimous)

At this point Mark Mendelbaum introduced the other ACM Publications representatives.

Bernie Rouse asked for a loan from SIGDA to ACM Publications of \$110,000 to cover startup costs for CD-ROMS, to be paid back in the next fiscal year based on revenues from DAL. He reviewed the business plan.

Deblasi pointed out that we are heavily underwriting the cost. Prices can go as high as \$3,500 for such a set if we were not subsidizing it. (The business plan puts the price at \$599 for SIGDA members, \$999 for other ACM/IEEE members and \$1399 for non-members). Although SIGDA views this project as a service to the profession, a price that does not cover costs will make it tough for other SIGs to price their ROMs competitively.

After some discussion, it was agreed to leave the pricing as is, but to put a clear statement in the promotional literature that SIGDA is underwriting the cost and to what extent they are doing so. The business plan presented assumes exclusive distribution rights for ACM because the market is too small to split between them and IEEE. The plan is to pay royalties to IEEE on a per unit sold basis. Weil requested a marketing plan from ACM for DAL.

Brglez suggested we offer a bonus to registrants at DAC and ICCAD (as part of the registration form, perhaps) to order DAL. Preas agreed to take that up with the DAC and ICCAD boards. ACM also presented a proposal for how to handle the excess revenues, should this project be wildly successful (1/3 to publications to build up CD-ROM program, 1/3 for DAL updates and 1/3 back to the SIGDA treasury).

**MOTION:** Accept the tentative business plan as presented by ACM publications, including the loan from SIGDA. (Cohoon, Weil, unanimous)

The question was raised whether the loan should be a grant instead in order to leverage ACM into the CD-ROM business. After a brief discussion, it was agreed to leave it as is (as per Radke's suggestion) since we can always cancel the payback later if we so desire.

# E. Formal Methods Journal

Weil reported that the proposal for a Journal on Formal Methods stands unchanged from the version presented at the DAC meeting.

The SIGDA concerns regarding scope and funding were expressed to the authors of the proposal.

**MOTION:** Refer the Formal Methods Journal to the SIG Discretionary Fund for funding because it appeals to a broad based set of technical interests within ACM, not merely those of SIGDA. (Lorenzetti, Irwin, 10-0-1)

# F. Email System

Mary Jane Irwin summarized costs for the 800 number used for our Email system. Installation was \$341 and the total bill for February through July was \$812.83. Felix Lee (flee@frith.cs.psu.edu) is the system administrator.

### G. DAC Contract

Shaw reported that the three-year contract for DAC management by MPA has finally been signed. It is now time start on the next one (beginning with DAC 95) which will be done by competitive bid.

## H. SIGDA University Booth

Mary Jane Irwin announced that the booth selected for the '91 DAC will be the largest so far (30' by 50'). It will contain six machines (four Suns and two DECs).

The budget is as follows:

| ltem .       | Cost          |

|--------------|---------------|

| Booth Rental | \$25,000      |

| Furniture    | 10,000        |

| Management   | 10,000        |

| Travel       | 4,000         |

| Shipping     | 2,000         |

| Equipment    | <u>20,000</u> |

| Total Cost   | \$71,000      |

Jim Cohoon is the organizer for 1991. It is now time to select an organizer for 1992. Several names were proposed but the decision was left up to Cohoon and Irwin. Irwin suggested that we may need an NEC machine in 1991 to encourage Asian participation.

**MOTION:** Allocate \$20,000 for the equipment grant for the University Booth for the 1991 organizer. (Irwin, Radke, unanimous)

Bryan Preas pointed out the DAC Executive Committee may be willing to help with public service projects such as this (that relate to DAC) and posed the question "what, if any, assistance would be beneficial?" It was pointed out that the University Booth is a high visibility area for SIGDA and is one for which we would like to retain responsibility. On the other hand, the graduate scholarship program is one that is shared with DATC (although SIGDA pays the largest share of the funding) and is generally recognized as associated with DAC. Making that program a part of the DAC budget would make the situation more equitable. Also, we could ask them to waive the registration fee for our travel grant recipients to allow our funds to go further.

Weil informed the committee that EDAC wants a University Booth for their conference. We should also consider expanding it to other areas (possibly Asia).

MOTION: SIGDA set aside \$50,000 to fund a University Booth at EDAC, contingent upon SIGDA formally becoming a sponsor or obtaining "in cooperation with" status for that conference. (Weil, Radke, unanimous)

### I. Asian Activities

Akihiko Yamada reviewed a list of Asian activities related to SIGDA.

IFIP Workshop on Design and Test of ASICs. June 11-12, 1990 Hiroshima, 80 attendees. Co-sponsors IFIP WG 10.5, IPSJ

IPSJ Annual DA Workshop '90. August 30 - September 1, Hakone, Kanagawa, Japan. 108 attendees.

InfoJapan '90. International Conference on Information Technology. Commemorating IPSJ 30th anniversary. October 1-5 Keio Plaza Hotel, Tokyo, 1200 attendees expected.

IPSJ-SIGDA, IEICE-FTS Joint Workshop on Design and Test, October 8-9, Osaka, Japan.

IPSJ-SIGDA, IEICE-VLD Joint Workshop on Synthesis, December 11-12, Tokyo, Japan

Weil suggested a Pacific-Rim DA workshop somewhere between Asia and the U.S. (perhaps in Hawaii or Fiji). Yamada agreed to bring this idea up with IPSJ at their next meeting.

# J. High School Scholarship

Shaw reported for Charlotte Acken. The visit by the scholarship recipients to the DAC went well. No changes in the program are anticipated for next year. We will keep the scholarship in the Bay Area and have MESA help with the screening.

Donna Couch, the current scholarship administrator, is moving from the Bay Area and will resign from her position. Two candidates have been identified to serve as her replacement. Acken proposed that we make the position a fixed fee of \$6,000 per year (rather than hourly). ACM would pay the administrator directly.

The Board saw no problem with the plan and Shaw pointed out that no Board action was required, since this change is within the current scholarship budget.

Acken requested a PC, printer and software for word processing and bookkeeping for the project.

**MOTION:** Approve up to \$7,000 for a computer and printer for administration of the High School Scholarship program. (Weil, Cohoon, 10-1-0)

Debbie Hall of ACM requested that we collect a list of capital equipment, including price and serial number. These are necessary to depreciate the equipment and just to keep track of its location.

Lorenzetti agreed to collect the list and provide it to Hall.

Shaw presented the tentative breakdown of expenses for the fiscal year ASCEE:

| Scholarship Fund\$40,000                                                                    | ,        |

|---------------------------------------------------------------------------------------------|----------|

| Administrator Fee                                                                           |          |

| PC, Printer & Software10,000                                                                |          |

| Two Mentor Meetings1,000                                                                    |          |

| DAC '91 meeting expenses (travel, student luncheon, Mentor registrations at DAC, etc.)2,500 |          |

| Office supplies, phone, mail, misc. expenses                                                | <b>S</b> |

| TOTAL\$60,000                                                                               |          |

# K. Graduate scholarships

Shaw reported for Loomis that no changes are anticipated for this successful program. The current funding level is appropriate.

Waxman appointed Radke to continue as DATC representative on the Graduate Scholarship committee.

### L. Video Tape

Irwin distributed comments from reviewers on Richard Newton's outline for the Introduction to Design Automation video. The comments were very positive. The budget remains at \$43,000 and they hope to start production some time this fall.

Reviewer comments were also distributed on the outline of Introduction to VHDL by Jim Armstrong. This project is to be funded jointly with DATC. The anticipated total cost is approximately \$38,000. They hope to have tapes ready in time for spring courses.

**MOTION:** SIGDA fund 50% of the Introduction to VHDL video, up to a maximum of \$20,000. (Radke, Hefferan, unanimous)

Irwin announced that they may show the video tapes at the SIGDA University Booth at DAC next year.

Irwin announced that two universities have contacted her about distributing videos that they have produced. After some discussion it was agreed that we should refer them to University Video and not get involved with distribution of tapes from other sources.

# M. Discretionary Fund

Lorenzetti summarized the SIG Discretionary Fund and contributions from other SIGs (see SIGDA Newsletter, v20, number 1, page 40). The Discretionary Fund provides a means to support projects which span a wide range of technical interests, rather than those of a single SIG. SIG Board manages the fund and contributions are made by individual SIGs on a voluntary basis. For the past two years, SIGDA has worded their contribution as follows: "Subject to an absolute maximum of \$200,000, SIGDA will contribute an amount equal to the maximum of the following two numbers:

- (1) the largest contribution of any other single SIG,

- (2) half the contribution of all other SIGs combined."

Lorenzetti reported that this wording has served to induce other SIGs to increase their contributions to the fund (most notably SIGPLAN) and prevented SIGDA from being the overwhelming majority contributor.

**MOTION:** For the fiscal year 1992 Discretionary Fund contribution, apply the same conditions and amount as fiscal year 1991. (Cohoon, Irwin, unanimous)

# N. Meeting at Critical Issues Conference

There are several SIG-related meetings to be held at the Critical Issues Conference in November in Washington DC. Shaw asked for suggestions as to who should represent us. Shaw and Irwin will both attend (Irwin also represents SIGARCH). Hefferan volunteered to serve as backup, should one of them be unable to make the trip.

### O. Next Meeting

After some discussion, Shaw announced that the next Board Meeting will be 9 a.m. on the Sunday before ICCAD. The General Membership meeting will be held Sunday evening.

### P. Conferences and Workshops

Weil summarized SIGDA conference and workshop activities. DAC is, of course, our primary conference which we co-sponsor with IEEE-CS. We are currently "in cooperation with" ICCAD, which is sponsored by the IEEE Circuits and Systems Society. They may be interested in having SIGDA as a co-sponsor. ICCAD is not a big moneymaker, but is a strong technical conference and one which we already support indirectly through our Travel Grant Program. We need to be sure, however, that the current sponsors of ICCAD are in favor of such a move, so as not to damage our good working relationship with them.

**MOTION:** If invited, it is the sense of the SIGDA Advisory Board that we support SIGDA co-sponsorship of ICCAD. (Radke, Brglez, 9-0-2)

Weil presented a list of 11 workshops being organized for fiscal year 1991. These included a workshop and tutorial in Leningrad, USSR, but local arrangements may be a problem, which they are now trying to resolve. Weil pointed out that over half the proposals he receives are turned down for lack of planning. There are sometimes problems with ACM organizing fees, particularly for co-sponsored workshops.

**MOTION:** SIGDA will advance an \$8,000 organizing fee to any workshop it sponsors (to be paid to ACM or other organizing agency) which is not included on the TMRF. If there is a surplus from the workshop, they

must pay this amount back to SIGDA before any profit is split among the sponsors (otherwise SIGDA will absorb this cost). (Weil, Cohoon, 10-0-1)

The question was raised whether, as a matter of policy, we should favor having a single sponsor per workshop and allow additional potential sponsors to have "in-cooperation with" status. Sponsorship could alternate between societies each year. Dual sponsorship is a large coordination effort between societies. No action was taken on this matter.

MOTION: SIGDA allocate \$7,000 for a computer for the workshop program. (Cohoon, Hefferan, unanimous)

Last year was the first year for the European Design Automation Conference (EDAC). They have bootstrapped themselves without sponsorship. No formal request for '91 has been made, but they are likely to request "incooperation with" status from SIGDA. There was support among the Board for some kind of association, but several questions must first be resolved including DAC EC's concerns about "look and feel" issues. Is there an actual sponsoring organization (or some legal entity)? Do they have liability insurance? Do they have cooperation of other European professional societies? Weil will be traveling to Europe to meet with them in the near future to discuss possible relationships between EDAC and SIGDA.

# Q. Travel Grants

Cohoon announced that by not paying for meals he has been able to allow more people to participate in the grant program without causing hardship on the part of the recipients. Approximately 50% of the awards are for travel to DAC, and another 20% to ICCAD. He averages about three awards per each SIGDA sponsored workshop. He announced that they are planning on five Eastern European awards for DAC again this

year. He is also trying to encourage more Asian recipients.

### R. Publication Chair Search

Shaw is looking for more recommendations for a Publications Chair to serve on the Board (replacing Waldo Magnuson who recently retired). An International Journal of Design Automation is something this Board Member might consider (in addition to textbook and bibliography projects). Several names were suggested and Shaw agreed to follow up on them.

# S. DATC

Ron Waxman announced that he is approaching the end of his two-year tenure as DATC chair. The new chair will be Joanne DeGroat. Waxman reported that his requested (but not yet approved) budget for the coming year is \$120,000. Last year it was \$45,000 (compared to the \$30,000 cap of previous years).

# T. Outstanding Member Awards

Radke solicited recommendations for the '91 awards. He reminded the group that no more than one of the two recipients can be current Board Members. Paul Weil suggested awards be made to workshop chairs (in addition to the outstanding member awards).

# U. DAC '91

Shaw announced that the conference will take place in San Francisco in June. Relationships with U.S. companies are improving. Dates for future DACs are being pushed to earlier in June (away from end of the fiscal year). The committee is still trying to keep the dates after graduations. MidJune seems to be the best compromise here. Next year, an Industrial Liaison position will be added to the DAC Executive Committee to

help them respond to concerns of the exhibiting companies.

This year DAC is "in cooperation with" the IEEE Circuits and Systems Society. Discussions of possible co-sponsorship are ongoing. Deblasi asked whether SIGDA feels we should encourage such a relationship.

**MOTION:** The SIGDA board would like to see that SIGDA financial interest be protected and that there be a five year transition plan for additional co-sponsorship for DAC. (Radke, Cohoon, DEFEATED 2-5-4)

MOTION: The SIGDA Board favors the inclusion of the IEEE Circuits and Systems Society as a co-sponsor of DAC provided that the distribution of funds and other matters can be worked out to the satisfaction of all parties. (Radke, Lorenzetti, 10-0-1)

# V. Benchmarks

Brglez summarized the Benchmark Program. He reported that a proposal is being drafted for a benchmark session at DAC'91. He requested suggestions for a chairperson, should the session be accepted. The Board requested a report on the preparation of bibliographies of benchmark citations at the next meeting.

### W. Leningrad Workshop

Weil informed us that, for the workshop in Leningrad, hotel rooms must be prepaid in order to reserve them. This money may not be refundable, should the workshop fall through for some reason.

MOTION: Approve the expenditure of up to \$50,000 to make arrangements for the Leningrad Workshop. (Weil, Radke, unanimous)

### X. New Officer Elections

Shaw announced that Dick Smith is soliciting nominations for officers for next year. Recommendations for nominees should be made directly to Smith.

The meeting was adjourned at this point.

Respectfully Submitted,

Michael J. Lorenzetti SIGDA Secretary/Treasurer

# SIGDA ADVISORY BOARD MEETING MINUTES

The SIGDA Advisory Board Meeting was called to order at 9:20 a.m. on November 11, 1990 by Chairman Chuck Shaw. In attendance were Board Members Franc Brglez, Jim Cohoon, Joanne DeGroat, Patrick Hefferan, Mary Jane Irwin, Michael Lorenzetti, Bryan Preas, Chuck Radke, Paul Weil, and Akihiko Yamada. Also in attendance were Debbie Hall from ACM Headquarters and Kathy Preas from the CD-ROM Project.

### A. Minutes

**MOTION:** The minutes of the September 16, 1990 SIGDA Board meeting be approved as submitted. (Weil, Irwin, unanimous)

# B. Financial

Secretary/Treasurer Michael Lorenzetti reviewed the financial status of SIGDA. The fund balance is \$1,078,400 as of September 30, 1990. For fiscal year 1990, our expenses exceeded our revenues by \$166,000, which indicates we are beginning to apply our massive fund balance to services for the DA profession.

Lorenzetti brought up the subject of DAC sponsorship. Negotiations are in progress to add the IEEE Circuits and Systems Society as a co-sponsor of DAC. It is unclear at this point what the division of costs and surpluses will be. In case the result is an even three-way split of surplus, SIGDA should have a contingency plan for adjusting to the decrease in revenues. It was suggested that in this event we request that the DAC take over the funding of both the scholarship programs (High School and Graduate). This would remove a total of \$230,000 in expenditures from our annual budget.

This led to a discussion of the larger issue of multi-sponsorship of conferences. Should we adopt a position requesting compensating influence in other conferences? The conferences of interest to the DA profession include DAC, ICCAD, EDAC, EuroDAC and, to a lesser extent, CICC, ITC and ICCD. After much discussion of the wording of such a position, the following motion was passed.

MOTION: SIGDA requests that the Computer Society, ACM and the Circuits and Systems Society expand the discussion of sponsorship of DAC to include formulating a unified approach to sponsorship of CAD related conferences, such as ICCAD, DAC, EDAC and EuroDAC. (Weil, Brglez, 10-1-0)

The intent is that we have more cooperation among societies in conference activities and avoid an adversarial relationship, as in the case of recent EDAC activities. SIGDA wishes to work toward a unified approach to conference activity among the societies.

### C. EDAC

Paul Weil brought the group up to date on the European Design Automation Conference (EDAC) situation. At this point we still have not received written evidence that the conference organizers are a legal entity. We also need evidence of insurance. EDAC continues to imply close cooperation with DAC (through use of our mail list, and by maintaining a DAC "look-and-feel") although no relationship exists.

There are coordination problems in dealing with conferences and workshops held overseas. Perhaps SIGDA should have a policy specific to such meetings. The following three guidelines for dealing with such meetings were proposed:

- (1) the conference be sponsored by a professional society or government,

- (2) SIGDA must be a co-sponsor (even if this is just a small percentage) with review responsibility, and

- (3) the conference have a cooperative relationship with other professional activities.

(Dick Smith joined the meeting at this point). It was pointed out that the reason for criteria (2) above is to keep us involved in the decision-making process for the conference in order to avoid misunderstandings due to lack of communication. "In co-operation with" status is not adequate to do this when the conference is organized and run overseas.

**MOTION:** Accept the three guidelines (outlined above) in negotiating SIGDA involvement with any international conference. (Radke, Preas, unanimous)

# D. Planning and Future Meetings

Preas suggested a planning meeting like the one held in 1988, in which we would review funding levels for all projects, and discuss new project proposals. Shaw agreed to schedule a two-day meeting in early spring (March), maybe during CSC in San Antonio.

### E. Newsletter

Pat Hefferan reported on the Newsletter, which continues to be published three times per year. The most recent issues were Dececember 1989, June 1990 and October 1990. The next issue (December 1990) will include an invited article on ASIC Design in VHDL. Mary Jane Irwin suggested that we solicit papers from our workshops. We could ask the organizers for the best papers from these workshops (in addition to the summary already submitted).

Hefferan went on to discuss the Membership Benefits Program - about \$9,000 has been spent so far. VHDL manuals, EDIF manuals, 25 years of DAC and DAC and ICCAD proceedings are available to members at \$5 per copy. Members who take advantage of these benefits are mostly students and professors, many from Pacific rim.

MOTION: The SIGDA Board expresses its appreciation to Pat Hefferan for his efforts on the Newsletter and for the membership benefit program. (Radke, Acken, unanimous)

### F. CD-ROM

Kathy Preas reported that contracts have been signed with SAZTEC and RTI. They are currently negotiating license agreements with KSC. Both single-user and multi-user licenses will be offered. Provisions will be offered for multi-users at the same time. Production test has begun. Changes have been made in capture specs and design as a

result of prototype evaluation. Preas reported on delays with getting agreements with the Circuits and Systems Society. We must get their approval for Transactions on CAD. Preas is pursuing this with IEEE Press and Chuck Radke agreed to assist.

The final DA Library will be ready in October. This schedule may be moved up if quality is found to be high during evaluations. A total budget of \$778K has been authorized (plus \$100K for ACM support). So far, \$110,000 has been spent and the remainder will be expended during the coming year. Shaw asked for ways to publicize the project and give recognition to the Preases, perhaps by presenting a paper at a publication conferences. Preas agreed to pursue this.

### G. Elections

Smith reported that there is only one nomination so far. He wants to complete the slate by the end of the week and asked Board Members to come to him with suggestions. If we get it in the next Newsletter, we can avoid a special mailing. Slates must be submitted to ACM by December 3.

# H. ACM HQ Costs Allocations and Budgeting Methods

Debbie Hall announced that there will be major changes in HQ allocation charges. ACM Headquarters took fiscal year 1990 HQ support amounts (\$116,000 for SIGDA) and used them to calculate fees for fiscal year 1992. ACM will have a meeting in March to review and plan how this will be allocated in future years (fiscal year 1993 and beyond). SIG Board Members argued for individual charges instead of a blanket fee. HQ prefers blanket charges so they can budget in advance. SIGs prefer individual charges because they make HQ focus on the services they need most (and are willing to pay for).

Hall recommended bringing these suggestions through the Area Director and insist that he keep us informed. Shaw's motion to scrap this plan was voted down at the meeting in Washington. We could also

work to gain support of the other SIG chairs. It might be productive to propose an alternate plan. One alternative is to sign contracts for services one year in advance. Another is a minimum fee plus additional fees for individual services.

Shaw appointed a subcommittee consisting of Shaw, Lorenzetti, Weil and Irwin to pursue this actively.

### I. EDAC

Jochen Jess, chairman of EDAC'91, joined the meeting at this point. He reviewed the history of the conference. It grew out of a CAVE workshop. The first conference committee consisted of many of the CAVE organizers. One goal was to demonstrate technical know-how developed in Europe. They also wanted to include U.S. papers and tutorials. They had 450 attendees at the first meeting. It was originally planned to be biennial, but changed to annual based on the success of the first one.

The flavor of the conference is a topic of discussion among their committee members. They are weighing vendor participation versus a strictly technical workshop. They want to be international with Japanese and U.S. participation. They have floor space this year for use as vendor exhibit area. EuroDAC is viewed as a competitor because they are not sure that the European market can bear two conferences.

He stated that the EDAC association is a non-profit organization "built around a bank account." Gordon Adshead is president, Jess is vice president. The sole purpose of the organization is to run the conference. There is no European-wide professional organization, which is why EDAC exists. It is considered a nucleus of such activities that may become abandoned if a larger group is formed to subsume this work. He stated that the association is established under English law as a non-profit organization.

Board Members requested a copy of the documents establishing this legal entity. They also requested a copy of the

conference insurance policy and reiterated their concerns about sponsorship, insurance and cooperation among the conferences sponsored. SIGDA must abide by ACM guidelines and procedures. SIGDA is not concerned about whether EDAC has exhibits, whether the merge with EuroDAC or other organizational decisions. Board Members reviewed our position regarding sponsorship (even in as little as 5%) by SIGDA for international conferences in which we are involved. Joanne DeGroat (the DATC Chair) stated that DATC agrees with the position taken by SIGDA.

Jess summarized his understanding of the SIGDA position:

- (1) documentation of non-profit legal status,

- (2) evidence of insurance of the conference (not just of the sponsors),

- (3) prefer sponsorship over "in-cooperation with" status.

He questioned the difference between "sponsorship" and "in-cooperation" and was informed that some participation in conference organizing and decision-making is involved in sponsorship. Jess explained that these terms are not so well defined in Europe and they have used them somewhat loosely in the past. Mary Jane Irwin provided him with a copy of the ACM procedures on "in-cooperation with" status. Cohoon agreed to send him information from the ACM procedures manual on sponsorship.

Smith pointed out the early concerns of ICCAD overlapping with DAC, which proved to be unimportant. Perhaps this will be the same with EDAC and EuroDAC. Jess responded that there are two completely different groups. EuroDAC represents the "big 12" European companies, EDAC has more membership from academia.

It was agreed that mutual cooperation was important to both SIGDA and EDAC. Jess reiterated his concerns about competition from EuroDAC.

### J. Asian Activities

Yamada reviewed the Asian activities, both of IPSJ and in the area of Standards.

IPSJ - SIGDA workshop. He discussed the idea of an Asia-Pacific workshop with both groups. He introduced SIGDA activities to the IPSJ meeting (they are unfamiliar with us). He distributed copies of our brochures and Newsletters to them. There was general support, but no chairman or organization has yet been put in place. Paul Weil agreed to obtain the list of Asian recipients of manuals from Pat Hefferan and send them invitation to participate in organizing such a workshop.

InfoJapan '90 was held October 1-5. It attracted 1335 attendees and was very successful.

IPSJ sponsors several workshops: October 8-9 on Test; December 11-12 on Logic Synthesis. Weil asked whether can we publish papers or abstracts from these workshops in the Newsletter. Yamada will check this out with IPSJ, (perhaps only the abstracts since they are already in English and printing them would not prevent the authors from republishing in other journals).

EDIF - EIAJ EDIF committee met in April 1990. They will hold an EDIF forum in December 1990.

VHDL - preliminary discussions were held September 21. There is a U.S.-Japan meeting to be held here on November 15. They hope to establish a Japanese VHDL group.

# K. University Booth

Cohoon announced that Japanese universities want to participate, but need NEC machines to do so. Cohoon will investigate getting them. International participation in this program would be nice. Steve Levitan has agreed to run the 1992 booth.

# L. High School Scholarship

Acken announced that we have seven students attending school under our

program, including students at Idaho State, UNLV, UCLA, and Berkeley. The new administrator (Susan Wills, formerly of Daisy) is working out very well. She is an excellent coordinator and meeting planner.

# M. Graduate Scholarships

Loomis reported that we are again awarding ten scholarships of \$12,000 each. Foreign applicants have been few, which may indicate we are not getting the word out internationally. It was pointed out that we do support many foreign students in American universities. Approximately 53 proposals were received last year.

There was some discussion of the amounts for scholarships. It was pointed out that stipends for graduate students run closer to \$14,000. It was also pointed out that if we are considering asking DAC to take over funding of this program, decisions on the amount should be left to them.

MOTION: For Chuck Shaw (the SIGDA representative on the DAC Executive Committee) to request the DAC to take over funding of the Graduate Scholarship Program. (Lorenzetti, Radke, unanimous)

Hersch Loomis pointed out that we currently include no statement on the type of DA we support in the announcement. Some proposals specify mechanical DA. Do we want to support them? It was agreed that it is Loomis' responsibility to write up the criteria and the Board suggested "topics covered by the Design Automation Conference" as a possible wording for the announcement.

## N. Discretionary Fund

SIG Board is forming a group to evaluate proposals for the SIG Discretionary Fund. This group would pre-screen the proposals before they were voted on by SIG Chairs and SIG Board. Since we are such a large contributor to the Fund, we have been invited to assign a representative to the group. It is in our best interest to assign such a member to help steer the allocation of these funds, since we contribute one third of them.

MOTION: Chuck Shaw be assigned the task of representing SIGDA on the SIG Discretionary Fund review committee. (Lorenzetti, Weil, unanimous)

# O. ACM Winter Meetings

Debbie Hall reported that the bylaw amendments submitted last March have not yet been approved. She expects they will be approved by conference call in the near future.

Some controversial proposals were voted down by the Conference Board at the last meeting. One was that conference contracts would require approval of all parties (including sponsoring society chairs) and be competitive bids. This was voted down as unworkable and replaced by a simple statement that sound business practice should be employed.

A second proposal was that special discount registration fees be offered to ACM officers and Board Members when they hold a meeting at an ACM-sponsored conference. This was voted down to be only a recommendation and that the amount be large enough to cover real expenses incurred by the conference for each registrant.

# P. University Booth

Weil pointed out that the motion we passed at our last meeting regarding a University Booth was specifically for EDAC and perhaps we should broaden the motion to allow it to be done

**MOTION:** Up to \$50,000 be budgeted for a University Booth at a European conference. **(Cohoon, Weil, unanimous)**

# Q. Brochure

Chuck Radke announced that after the next officer election, he will print a revised version of the SIGDA Membership Brochure. He requested that Board Members send changes and corrections to him.

### R. Travel Grants

Cohoon reported that the program is going well. He requested details on the recent DAC executive committee motion to fund the DAC grants for us. The question was raised whether we should require faculty approval for students to apply. No motion made on this and it was decided that the process should remain informal and requirements be left up to Cohoon.

### S. Publication Chair

Shaw announced that he has several candidates for this new board post. He intends to approach them this week during ICCAD.

### T. DATC

Joanne DeGroat is the new DATC representative to SIGDA. The IEEE Computer Society has changed its operating procedures. Technical Committees now propose budgets each year and the amount is not fixed as in the past. The budgets come up for approval in the next week. DATC is asking for \$127,400. The scope of DATC projects for the coming year depend on the outcome of these budget decisions.

# U. Outstanding Member Award

Radke has placed an announcement in the Newsletter requesting nominations for this year's Outstanding Membership Awards. We award two each year, but try to limit them to one person on the current Board. He is looking for nominations.

Shaw informed us that there are awards within ACM, such as the Turing and Grace Murray Hopper awards. SIGs should propose members from their own field to receive these awards. Radke agreed to send out a list of awards and their criteria to board members.

There has recently been a discussion of an ACM Fellows category similar to that of IEEE. This is particularly important not only to the academic community, but also for the industrial community. This came up a few

years ago but did not come about. There is a lot of support among the SIGs to get this program going. He supports it and will keep the Board informed.

### V. DAC '91

Shaw reported that there is a push toward listening to the DAC exhibitors and trying to address their concerns. For example, they are trying to move away from the end of the fiscal year and DAC '91 will take place earlier in June than in recent years. These actions have been well received by the exhibitors.

The conference starts on Monday this year (instead of Sunday as in the past). The Exhibitor Technical Program will be Monday, June 17. The technical program will be Tuesday, Wednesday and Thursday and the tutorials will be on Friday.

# W. Workshops

Weil reported that we supported eleven workshops this year, half of which were in Europe. He will present details at the general meeting.

# X. Evening Meetings

Shaw reported that he received comments last time that our Membership Meeting was more of a lecture. He would like to make it more interactive.

After a brief discussion it was agreed to not present reports on all projects, but only selected ones with important recent activity. Following this we would solicit questions and proposals to make the meeting more interactive.

# Y. Press Room Computers

Shaw announced his intention to spend \$20K to purchase computers for use in the DAC press room. No action was required since this money was already budgeted for the purchase of hand-held radios for the conference. It was found to be more economical to rent the radios and this money will be used instead for PCs.

## Z. Eastern European Travel Grants

Shaw informed us that we continue to receive congratulations on this program. The program was brought up in the Supreme Soviet of the USSR as an example of the benefits of *glasnost*.

We are looking for candidates for next year. Professor Marek-Sadowska has volunteered to help identify candidates in Poland. Egon worked through the scientific communities there last year, asking them to make nominations. It was agreed that we should let their professional society do the selection again this year.

### a. Benchmarks

Brglez has proposed a special session for DAC to discuss benchmarks. He intends to talk to Dunlop (the DAC program chair) to get early approval of this session. Brglez is looking for nominations for a session moderator.

### b. New Business

Radke has a transcript of Bill Joy's DAC keynote, for anyone who would like to review it. There was a discussion of whether we should publish it in the Newsletter. There are some holes in the transcript which need to be filled in. Radke will pursue getting the missing information from Sun.

The meeting was adjourned at this point.

Respectfully Submitted,

Michael J. Lorenzetti SIGDA Secretary/Treasurer

# SIGDA MEMBERSHIP MEETING MINUTES

The SIGDA Membership Meeting was called to order at 6:00 p.m. on November 11, 1990 by Chairman Chuck Shaw. Thirty-one members were in attendance. He announced that the format would be a brief review of some key projects and then he would solicit input on SIGDA activities. He pointed out that the SIGDA Newsletter is distributed to all ICCAD attendees and that all our activities are summarized therein.

Shaw announced that Chuck Radke is looking for award nominations for service awards from SIGDA, the Turing award and the Grace Murray Hopper award. Please make suggestions to Radke.

Mary Jane Irwin announced that DAC starts on MONDAY this year. The conference has been shifted by one day. Southern Pacific will add extra cars to travel from Silicon Valley to San Francisco.

# A. High School Scholarship

Charlette Acken reviewed the purpose of the program, which is to encourage underrepresented minorities (Black. Hispanic, American Indian and women) to enter the DA profession. We have seven students in school under our program, at several universities including Idaho State, UNLV, UCLA and Berkeley. Charlotte is looking for volunteers to act as mentors for these students. Mentors must be CS or EE professionals and be a member of one of the targeted minorities.

## B. Graduate Scholarships

Hersch Loomis announced we will again award ten scholarships of \$12,000 each, sponsored jointly by DATC and SIGDA. These are awarded based on proposals submitted in the spring. Contact Hersch (or see the Newsletter) for more information.

# C. CD-ROM

Bryan Preas reviewed the CD-ROM project. It will be a seven CD-ROM set, which includes retrieval software, and will contain all of the DAC, ICCAD, ICCD, EDAC, Transactions on CAD and the SIGDA Newsletter. It will run on

the Sun SPARCstation, Mac and the IBM PC and be distributed through ACM. This project is being run in cooperation with IEEE CS DATC.

Preas gave a brief review of the history of the project. The requirements were formulated in July of 1989. Production will begin in January and distribution is scheduled for third quarter, 1991. Thus far, \$110,000 has been invested in the project. The total cost will be near \$750,000.

# D. Workshops

Paul Weil presented list of workshops for the current fiscal year.

Workshop on Timing Issues in Specification and Synthesis (Tau90) Vancouver, August 15, 1990 Chair Rick McGeer Sponsor

Logic Level Modeling for ASICs Monterey, August 12, 1990 Chair Mark Glasser Sponsor

Workshop on EDA Frameworks Charlottesville, November 26, 1990 Chair Ron Waxman In Cooperation

Workshop on Formal Methods in VLSI Design

Miami, January 9, 1991 Chair P.A. Subrahmanyam [Subra] Sponsor

Workshop on High Level Synthesis Black Forest, March 3, 1991 Chair Raul Composano In Cooperation

Symposium on Computer Hardware Description Languages and Applications Marseille, April 22, 1991 Chair Dominique Borrione In Cooperation

# SIGDA MEMBERSHIP MEETING MINUTES (continued)

Workshop on Logic Synthesis

Research Triangle Park, May 7, 1991 Chair Franc Brglez In Cooperation

Physical Design Workshop II Nemacolin Woodlands, PA, May 20-22, 1991 Chair Antun Domic Sponsor

Leningrad: Workshop and Tutorial Leningrad, Russia, USSR, June 1991 Chair Jim Cohoon Sponsor

Workshop on Theory and Practice in Physical Design

Dachstul, Saarland, (Black Forest) Germany, August 25-31, 1991 Chair Thomas Lengauer In Cooperation

First International Workshop on the Economics of Design and Test

MCC, Texas, September 9-11, 1991

Chair Sarma Sastry

Sponsor

1991 Logic Level Modeling for ASICs Monterey, August 11, 1991 Chair Mark Glasser Sponsor

Weil summarized by noting we are involved in eleven workshops within a year's time. SIGDA is interested in fostering development of new workshops and provides a great deal of assistance in planning, as well as funding. Jim Cohoon elaborated on the Leningrad Workshop. It takes place June 3-4 1991. There will be four sessions with five presentations per session, mostly tutorial in nature. The goal is to promote international dissemination of DA information.

### E. Elections

Shaw reported that SIGDA will conduct officer elections in the spring and that Dick Smith (Chairman of the Nominations Committee) is soliciting nominations. The

nominations are due at ACM headquarters by December 3.

# F. New Projects

Shaw requested that members present ideas for new projects. The Board will meet in February to discuss future directions for the organization, so get proposals to us in advance.

### G. New Business

Shaw opened the floor for questions and comments at this point.

The first question was on the criteria for graduate scholarship. Loomis reviewed the criteria (from the announcement). These include quality of student, contribution for DA program at the school, and technical quality of the proposal. There were about 55 proposals last year. Members requested more feedback from the committee, particularly when proposals were turned down.

Bryan Preas asked the group whether they felt that SIGDA should publish a journal. He noted that this topic comes up periodically on the Advisory Board. It was pointed out that Transactions on CAD currently has a year and a half lag time on getting articles published, and competition with them is not a real issue. One person suggested a journal for more theoretical work (papers without practical examples or benchmark results, but strictly on theoretical aspects of DA problems). The Board agreed to consider this matter further.

# H. Adjourn

Since no other topics were brought up, Shaw thanked the members for their input and adjourned the meeting.

Respectfully Submitted,

Michael J. Lorenzetti SIGDA Secretary/Treasurer

# MEMBERSHIP BENEFITS

As a special benefit to SIGDA members, certain standards manuals, proceedings, and other documents of general interest will be made available at a nominal rate. Availability of the documents may vary, so allow several weeks for delivery. Proceedings will only be issued after the conference sales have been satisfied. You must be a member of SIGDA to quality.

|                                           | PERSHIP COUPON - DOC<br>obership Sponsored Manual/Proceedings -                                                                                                                                                                        |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name _<br>Address _                       |                                                                                                                                                                                                                                        |

| ACM Memb                                  | ership Number                                                                                                                                                                                                                          |

| ☐ EDIF 2.0 ☐ VHDL La ☐ 25 Years ☐ 1990 DA | ONS (please check box(es))  0.0 Standards Manual  anguage Reference Manual  s of Electronic Design Automation  C Proceedings  CAD Proceedings                                                                                          |

| for shipping                              | ude a check for \$5.00 (made out to ACM/SIGDA) to cover shipping. (\$5.00 per document). Please allow several weeks and handling. DAC & ICCAD Proceedings mailed only after is over. Also, allow extra time for EIA EDIF Publications. |

Please send coupon to: Patrick M. Hefferan 1681 Princeton Avenue St. Paul, MN 55105

# SIGDA MEMBERSHIP SURVEY

In order to better serve the SIGDA membership, we are taking a survey of your wants and needs. Please take a few minutes to fill out the survey form on the next page and send it in. It has a preprinted address on the back, so just cut it out and fold it up with the address facing outward. Then tape (please do not staple) it shut and mail it in. You will need to provide 25 cents postage, as we cannot use our bulk mailing permit for this.

To make this more interesting and provide an incentive to get the surveys filled out, those who participate will be eligible for a drawing for a portable, electronic address book. We want to hear from you - so take a few minutes and fill it out. THANK YOU!!

| PLEASE FILL OUT AND SEND IN | > |

|-----------------------------|---|

|-----------------------------|---|

THE WINNER OF THE ELECTRONIC ADDRESS BOOK THIS QUARTER IS <u>ELAINE RITCHIE</u> FROM MARLBORO, MASSACHUSETTS!! THERE WILL BE ANOTHER WINNER ANNOUNCED IN THE NEXT SIGDA NEWSLETTER.

# SIGDA SURVEY January, 1990

This is a general membership survey.

Participants will be entered in a drawing for an electronic address book.

| Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | EMAIL Addres                                       |                                            |                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------|----------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                    | (May we publish this                       | address?)                                                      |

| Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Company                                            |                                            |                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Occupation                                         |                                            |                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | La la Para antina                                  |                                            |                                                                |

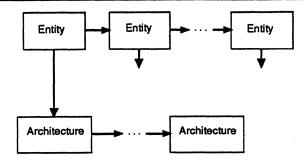

| Phone - Home                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                    |                                            |                                                                |