# SIGDA NEWSLETTER

A Quarterly Publication of the Special Interest Group on Design Automation

• • • • •

. .

| VOLUME 20                                                                                                       | NUMBER 2                                                                                               | OCTOBER 1990                |

|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------|

| CONTENTS                                                                                                        |                                                                                                        | PAGE                        |

| Letter from the Chai<br>SIGDA Advisory Boa<br>SIGDA Membership 1<br>Membership Benefits<br>E-Mail Directory     | rd Minutes<br>Meeting Minutes                                                                          | 2<br>4<br>7<br>10<br>12     |

| Outstanding Memb<br>Benchmark Project                                                                           | erences—Paul B. Weil<br>per Recognition—Chuck Radke<br>t—Franc Brglež<br>–Martin Wong & Mary Jane Irwi | 15<br>16<br>17<br>in 18     |

| 1990 DAC Photos                                                                                                 |                                                                                                        | 20                          |

| ARTICLE<br>A New Placement<br>by Steve Meyer                                                                    | Level Wirability Estimate with                                                                         | Measurements 25             |

| Conference Reports<br>DA Standards Activit<br>Calendar of Events—<br>Conferences & Anno<br>Statement of Publica | -Sunil Das<br>uncements                                                                                | 40<br>88<br>89<br>94<br>  4 |

|                                                                                                                 | PECIAL ICCAD CONFERENCE<br>tend the SIGDA Fall Meeting at                                              |                             |

11

# SIGDA BOARD OF ADVISORS

### Nominating Committee Chair

Richard C. Smith National Semiconductor, Inc. 2900 Semiconductor Drive, D3677 Santa Clara, California 95051 (408) 721-4794 FAX (408) 773-0978 nsc!parns!ricardo

#### **High School Scholarship Program**

Charlotte F. Acken Sandia National Laboratories, Div. 4853 P. O. Box 969 Livermore, California 94551 (415) 294-3248 FAX (415) 294-1539 cacken@sandia.llnl.gov

#### Bibliography & Textbook Projects

Waldo G. Magnuson, Jr. Lawrence Livermore National Lab. P. O. Box 808, L-153 Livermore, California 94550 (415) 422-9950 FAX (415) 423-5080 magnuson@icdc.llnl.gov

## Workshops/Conferences (except DAC)

Paul B. Weil Nextwave Design Automation, Inc. 5339 Prospect Road, Suite 240 San Jose, California 95129 (408) 255-6458 weilcad@frith.cs.psu.edu

## **IEEE/CS DATC Chairman**

Ron Waxman University of Virginia, Thornton Hall Charlottesville, Virginia 22901 (804) 924-6086 FAX (804) 924-8818 waxman@virginia.edu

#### **Outstanding Member Recognition**

Charles E. Radke IBM Corporation, AR1 Route 52 Hopewell Junction, New York 12533 (914) 892-2957 FAX (914) 892-3039 C.RADKE@COMPMAIL.COM

#### **European Activities**

H. Gordon Adshead International Computers Ltd. Wenlock Way, West Gorton Manchester M125DR, ENGLAND (011-44-61) 223-1301

## **Asian Activities**

Akihiko Yamada, Chief Engineer Information Processing Group NEC Corporation, Daito Tamachi Bldg. 14-22 Shibaura 4-Chome, Minato-Ku Tokyo 108, JAPAN (011-81-3) 456-5750 NEFAX (011-81-3) 456-7495

## **Travel Grants**

James P. Cohoon, Ph.D. Department of Computer Science University of Virginia, Thornton Hall Charlottesville, Virginia 22903 (804) 982-2210 FAX (804) 982-2214 csnet: cohoon@virginia.edu uucp: !uvacs!cohoon

#### Scholarships

Herschel Loomis, Jr. Naval Postgraduate School - EE Dept. Code 62Lm Monterey, California 93943 (408) 646-3214 Ioomis@cs.nps.navy.mil

#### **University Faculty Activities**

Mary Jane Irwin Pennsylvania State University Department of Computer Science University Park, Pennsylvania 16802 (814) 865-3176 mji@psuvaxl.cs.psu.edu

#### University Booth Project (DAC)

Martin Wong Department of Computer Science University of Texas Austin, Texas 78712 (512) 471-7316 wong@cs.utexas.EDU

# SIGDA OFFICERS

## Chairman & ACM DAC Representative

Charles A. Shaw Cadence Design Systems, Inc. 2455 Augustine Drive Santa Clara, CA 95054-3082 (408) 987-5321 shaw@cadence.com

## Secretary/Treasurer

Michael J. Lorenzetti Mentor Graphics Corporation 8500 S.W. Creekside Place Beaverton, OR 97005-7191 (503) 626-7000 mikelor@mentor.com

# EDITOR'S NOTES

Welcome to the fall edition of the *SIGDA Newsletter*. This edition contains the minutes of both the Advisory Board meeting and the Summer General Membership meeting. These minutes contain good summaries of the state of the various projects of SIGDA. You should also note Franc Brglez' appointment as manager of the SIGDA Benchmarks project (see the Departments Section). Additionally, this issue contains the first edition of the SIGDA e-mail directory. It was drawn from the survey responses. If you want to be listed, just send in your survey form.

This edition has a collection of photos from the DAC including shots of the summer meeting, the lunch organized for the Eastern European students, Dr. Martin Wong's University Booth, our scholarship winners, and more. We are fortunate to have another article by Steve Meyer in this issue on wirability estimates. This newsletter can be a good place to publish articles and notes that would otherwise wait long periods in the queue for more formal journals. And that problem is likely to be further aggravated (read on).

Another DA publication, *High Performance Systems* (formerly - *VLSI Design*, and before that *Lambda*) folded this summer. You may have also heard that the IEEE's *Design & Test Magazine* will scale back its publishing frequency. Most certainly, this is an unpleasant trend, leaving the DA industry with an ever smaller bandwidth of interchange. We will all miss the feeling of community that *High Performance Systems* provided with its news, interviews, and editorials. And the

## Vice Chairman & IEEE DATC Newslet-

## ter Coordinator

Bryan T. Preas CADLAB Bahnhofstrasse 32 4790 Paderborn, West Germany 011 49 52 51 28 41 02 main 011 49 52 51 60 20 67 secy preas.@cadlab.cadlab.de preas%cadlab.uucp@seismo.css.gov

#### ACM SIG Program Director Debbie Hall 11 West 42nd Street New York, NY 10036 (212) 869-7440 fax (212) 302-5826 Hall@ACMVM.Bitnet

fewer pages available in *D*&*T* will further slowdown the technical paper pipeline. If you have any insights on this problem (or perhaps a solution), please drop me a line. **THANK YOU**...

#### Patrick M. Hefferan - SIGDA Editor

1681 Princeton Ave. St. Paul, MN 55105 (612) 690-5451 hefferan@frith.entmoot.cs.psu.edu 76350.54@compuserve.com

1

# LETTER FROM THE CHAIR

SIGDA's premier event, DAC, came off in steamy Orlando last June in its usual grand style. In the opinion of most, it was the best DAC ever. Nevertheless, DAC cannot stagnate, or it will lose its preeminent position. A somewhat earlier start date, modification of its Sunday-Wednesday schedule, more tutorials, additional tracks of sessions devoted to the interests of groups other than developers are under discussion.

As one of DAC's sponsors, we put a modest amount of money each year into purchasing equipment to support DAC. Our sister organization IEEE-CS this year will purchase a UNIX computer, on which a truly effective email system can be mounted at DAC. SIGDA will purchase PCs for the press room, with different brands of word processing software familiar to the press corps. DAC itself will require the supplier of badgemaking equipment to bring enough equipment on site to provide backup against the equipment failure which produced the long lines at registration this year.

The summer annual SIGDA membership meeting took place, again shared with DATC; see the minutes elsewhere. Your officers and board solicit your opinion on the format of these meetings. The range of SIGDA activities is now so large that meaningful discussions of alternatives and membership votes on directions and budgets isn't feasible. But a negative comment made to me seems valid criticism - the meeting has turned into a presentation by SIGDA's Board of its already made decisions. Give us your opinion how do you want these meetings structured? We meet again at ICCAD - see the announcement elsewhere. Come, but also tell me or other Board members how to improve this meeting!

SIGDA's High School Scholarship program, under Charlotte Acken, draws universal praise. Eight winners are now in the program. Their entire college awards are in escrow, to be paid out as they succeed in their college programs. The program initiated in a suggestion from Pat Pistilli; its current success is due in large measure to the efforts put into it by Regina Pistilli whose salary was a donation from MP Associates. SIGDA is greatly indebted to them! We wish Regina all the success in her PhD studies.

Here is a chance for you to help this great project. Charlotte needs mentors from under-represented groups in our profession - women, hispanics, blacks, native americans, etc. SIGDA pays your expenses, we need your participation.

Bryan and Kathy Preas' CD-ROM project was a roaring success at DAC. Its demo at the University Booth was always crowded, the comments of its prototype evaluators significantly changed its format. This is SIGDA's major project, measured both in expenditure level and in our expectations of its impact on our profession. Get your CD-ROM reader plans ready for its availability next year!

The University Booth itself was thronged. Martin Wong and Mary Jane Irwin scheduled non-stop demos of university software. It was the meeting place for the whole university community. And this year its appearance was the equal of any vendor booth in its increased size, its furnishings and equipment, and of course in the large SIGDA banner. Most importantly, the research results demoed by the students were impressive; our profession shows no signs of stagnating!

To control the wide-ranging SIGDA activities, your Board now meets four times a year. SIGDA's FY91 budget is over three quarters of a million dollars, the equal of many a business. The group which gives up its weekends to control these activities deserves continued recognition. We have a vacancy now, Waldo Magnuson has retired and I am searching for a replacement to run our publications efforts. With talk of a Journal or other regular publication, this can be an important spot. SIGDA will have elections next Spring. Dick Smith, our nominations chair, is now searching for candidates. Call him with your suggestions. Don't be modest, either, you can suggest yourself!

ACM's elections last spring produced a top level in ACM totally supportive of SIGDA and DAC. From John White down, the volunteer heads of ACM come from SIG backgrounds. At the same time, Joe Deblasi joined ACM as its executive director, and Pegotty Cooper hired Debbie Hall to handle SIG activities for the group of SIGs which includes SIGDA. Their assistance has already produced a DAC management contract renewal, breaking a long stalemate. Debbie in particular became immediately indespensible, I don't know how we ever functioned without her.

Paul Weil is a dynamo - look at the list of workshops! These include a number in Europe, and Jim Cohoon is working with Siemen's Egon Hoerbst in helping Eastern Europeans to hold one in Leningrad! Workshops are the cutting edge of technology, they complement the major conferences. Why don't you volunteer to Paul to lead a workshop? It's great for your reputation as well as being a service to our profession.

Pat Hefferan has started a new consulting business, yet he continues to provide us superlative newsletters. Look through this one - they just get better and better!

يسر

Hersh Loomis' graduate scholarship program drew an amazing number of high-quality applicants. A mailing made through Pat Hefferan to ALL graduate schools with possible candidate programs was partly responsible. Picking the winners which were announced at DAC, was a tough job. Library grants were awarded to those just missing the scholarships. One recipient was a Mainland China university. SIGDA is truly becoming world-wide.

Jim Cohoon handles an amazing number of requests for travel grants efficiently and fairly. This year, it included a project to bring potential Asian paper authors to DAC to help them understand the requirements for a paper to be accepted. His piece-de-resistance was the Eastern European project, seven CAD professionals were brought to DAC from Russia, Eastern German, Hungary, Poland and Czechoslovakia, each with a Western European companion to ease the travel and customs problems. I was thrilled to talk with them and find such dedication to a free society. Again Jim had the help of Egon Hoerbst. SIGDA thanks you!

#### Charles A. Shaw - Chairman SIGDA

#### September 1990

# SIGDA ADVISORY BOARD MEETING MINUTES

The SIGDA Advisory Board Meeting was called to order by Chairman Chuck Shaw at 8:00 a.m. on June 23, 1990. Board Members in attendance were Gordon Adshead, Franc Brglez, Jim Cohoon, Pat Hefferan, Mary Jane Irwin, Michael Lorenzetti, Bryan Preas, Dick Smith, Ron Waxman, and Paul Weil. Also present were Debbie Hall (ACM), Kathy Preas (CD-ROM project manager) and Mark Mandelbaum (ACM Publications Board).

#### A. Welcome New Members

Chairman Chuck Shaw introduced Franc Brglez from MCNC, who is the new board member in charge of benchmarks. Chuck also introduced two visitors from ACM: Debbie Hall, who is now our liaison to headquarters and Mark Mandelbaum, who is from ACM publications and has joined the meeting to participate in the CD-ROM discussions.

#### B. CD-ROM

Kathy Preas presented the current status of the CD-ROM project (now called DALibrary). The prototype is now available and evaluation has begun. It runs on the IBM PC, the Apple MAC II and Sun workstation (the first database to run on all three). So far, PC problems are very minor. MAC users have a little problem getting started, but it works fairly well. The Sun version has numerous problems (the UNIX kernel must be rebuilt to use the system). Sun is working on correcting this.

The IEEE Circuits and Systems Society has given us permission to use their copyrighted material. FIZ Karlesruhe (a German interactive database company) is interested in putting our database on-line for their customers. Details are being worked out. Demos will be run in the ACM University Booths during the Design Automation Conference.

There is an evaluation meeting on Tuesday from 6-7:30 p.m. during the Conference, during which beta test users will discuss the system and suggest modifications for the production version. Some distribution issues are yet to be resolved.

The IEEE has been cooperative, receptive and encouraging, but not closely involved and have not yet committed to active involvement in distribution and support. Bryan Preas reminded the Board that he hopes to price DALibrary such that there is no return to SIGDA (this is a service to the profession). All costs, except support, are now fixed. Support costs are being worked out. The following table summarizes the costs for a single (nine CD) volume:

| \$25 |

|------|

| -12  |

| 00   |

| ???  |

| 50   |

|      |

Mark Mandelbaum reported on market forecasts made by ACM. Technical libraries are the biggest customers (rather than individuals). He estimates 1000-1200 sales (75% to libraries). Library grants specifically for CD-ROMs were suggested as a way to get the project going (1200 for ROM and drive). Current grant size is \$1000.

**MOTION** - Budget \$30,000 to support library grants to universities for CD-ROM readers and ROMs, limit to one grant per university, \$1500 maximum per grant. (Weil, Hefferan, 10-0-1).

Bryan brought up the question of whether we can fund a person at ACM to handle support. There are often problems with installation and there are usage questions to be answered. There must be a number to call for assistance. Should this be RTI or ACM? We can fund the start-up of such a service at ACM to leverage them into the CD-ROM business. RTI is quoting \$160,000 for this service. Mark has hired a full-time CD-ROM person at ACM to do marketing and support. Question is what happens if she becomes overloaded? Can we fund part-time backup?

4

# SIGDA ADVISORY BOARD MEETING MINUTES (continued)

**MOTION:** - Grant up to \$100,000 to ACM as seed money for support of CD-ROM customers. (Waxman, Weil, unanimous)

Preas presented a revised budget. Total spent so far is \$696,222 (slightly over the budgeted amount of \$668,000). The cost will grow to \$794,222 if we add the ICCD proceedings.

**MOTION** - The CD-ROM project stick with current budget and scope. (Smith, Waxman, 9-2-0)

The Board expressed appreciation and congratulations to Bryan and Kathy Preas for a job well done.

#### C. DAC

Dick Smith reported that DAC pre-registration is up from last year. Some changes in format are in the works. Practical user track parallel to the regular Conference is one of the suggestions being discussed.

#### D. Travel Grants

Jim Cohoon reported that 110 travel grants were awarded for DAC alone. No food money was provided to recipients this year (registration, lodging and transportation only). This allowed more awards to be granted and doesn't seem to present a hardship to recipients. Jim asked for a budget increase for next year.

MOTION - Increase Travel Grant budget from \$125,000 to \$150,000. (Radke, Preas, unanimous)

Cohoon questioned whether we- should require ACM membership on the part of travel grant recipients (as opposed to only SIGDA membership, as is the current policy).

**MOTION** - That ACM membership be a requirement for travel grant recipients. (Preas, Radke, 10-0-1)

#### E. Conferences

Paul Weil listed conferences and workshops in which SIGDA is involved. There are three conferences and seven workshops that we sponsor, co-sponsor or are "in cooperation with". Weil questioned whether we should require proceedings from our workshops. Does this stifle open interchange of ideas? After some discussion, it was decided to leave this to the discretion of workshop chairmen. However, it was agreed that a summary (for publication in the Newsletter) should include a technical overview and the workshop program.

#### F. New Journal

ACM Journal on Formal Methods wants \$48,000 seed money to start the journal. Long term costs may be \$150,000. This publication would be co-sponsored by SIGDA and SIGPLAN (who is putting in an equal amount of money). Is this too narrow of a topic to be a successful journal? Should we require a broader coverage of DA? Should ACM create a special interest group to cover this? Shaw pointed out that we need a replacement for Waldo Magnuson to manage the Textbook and Bibliography projects (under whose jurisdiction this kind of publication would fall). Shaw requested recommendations and several were made.

**MOTION** - Recommend that Chairman Chuck Shaw find new board member to manage journals (along with textbooks and bibliography) and authorize up to \$50,000 to initiate an ACM Journal which includes Design Automation as a topic. (Weil, Radke, 9-0-2)

#### G. Benchmarks

Franc Brglez reported that FTP from MCNC works well. He presented a profile for benchmark distributions. He proposed a benchmark panel discussions at the next DAC. Franc was referred to Al Dunlop (DAC program chair) to discuss this further. Franc also reported on the MCNC International Workshop on Layout Synthesis, which was held last May. The workshop attracted over attendees and 100 a two-volume proceedings was distributed. The place and route benchmarks were enhanced and redistributed for this workshop. Next year

# SIGDA ADVISORY BOARD MEETING MINUTES (continued)

(1991) the topic is Logic Synthesis, 1992 will be Layout Synthesis again.

#### H. University Booth

Mary Jane Irwin reported that the booth is going well. Twenty universities will be demonstrating software this year, three of which are European. Five machines (three Suns and two DECstations) are in the booth. The total cost is approximately \$71,000. Cohoon will be the organizer for 1991. It is time to designate a person for 1992.

#### I. Video Tape Project

Irwin reported that the first tape will be "An Introduction to DA" targeted at sophomore university students. Professor Richard Newton of UC Berkeley will be the speaker. The schedule calls for August production for fall course use. Adshead recommended that we provide tapes in European-compatible format. Irwin will investigate this through ACM distribution. A VHDL tutorial (joint with DATC) is also in the works. The speaker has not yet been identified. The maximum cost to SIGDA will be \$20,000.

#### J. European Activities

Adshead reviewed the goals and policies of EDAC. They plan to continue to have an annual conference in March. This conference will have a moving European location. It is a non-profit, self-financing activity. They plan steady growth and increasing vendor presence. The intention is to act in harmony with U.S. DAC and emerging global scenario. They started with a \$20,000 loan (which has since been repaid) and have netted a \$35,000 profit from the 1990 conference (total cost for EDAC90 was \$400,000). Paying attendance was 460. EDAC'91 will be in Amsterdam, EDAC'92 in Brussels and EDAC'93 in Paris.

## K. DATC

Ron Waxman reminded the Board that the DATC Executive Committee will meet Monday evening at the Sheraton. Everyone is invited to this open meeting.

#### L. Publicity

Chuck Radke reported that the new brochures are included in the DAC handouts and will be available at all workshops. Shaw extended thanks on behalf of the Board.

#### M. Bulletin Board and Communications

Dick Smith reported that the News system is not being used. SIGDA traffic in the comp.lsi.cad newsgroup is very light How do we increase the interest in this service? DAC has had a DIN network for use by attendees in the past. This year there will also be a Sun network to do this. DAC is discussing installation of a UNIX machine to provide year-round DAC-related communications. Perhaps we can utilize this tool. No action taken.

#### N. DAC Contract

The DAC management contract is still in the works. Yet another final version is now ready for review. IEEE and ACM have agreed to it. It now goes back to the contract negotiation committee. Shaw pointed out that this board may need to become involved in the process if this version is not approved. (NOTE: the contract was approved and signed a few days following the meeting - MJL.)

#### O. Next Board Meeting

After some discussion, it was agreed to hold the next Board Meeting in conjunction with ICCD in September in Cambridge, Mass. Shaw will make arrangements and inform the committee.

At this point Chairman Shaw adjourned the meeting.

Respectfully Submitted,

Michael J. Lorenzetti SIGDA Secretary/Treasurer

6

# SIGDA MEMBERSHIP MEETING MINUTES

The SIGDA Membership Meeting was called to order by Chairman Chuck Shaw on June 24, 1990 at 7:10 p.m. Approximately 150 members were in attendance.

## A. DA Library

Bryan Preas reviewed the project and informed attendees that they could view a prototype version at the ACM and University Booths. The final version will contain 35,000 pages on 8-9 CD-ROMs. This is the first CD-ROM database to support three different platforms (Sun, Mac and IBM PC). The final version will be available from the IEEE and ACM publication departments in early 1991.

#### B. University Booth

Mary Jane Irwin reviewed the University Booth Activities. This year's Booth is 30 X 45 (compared to last year's 20 X 20). Twenty universities are participating (three of which are European). There are five workstations (three Suns and two DECstations) in the booth. Jim Cohoon will be next year's university booth organizer.

#### C. Workshops

Paul Weil reviewed the conference and workshop schedule. The three main conferences are DAC, ICCAD and EDAC. ICCAD (the International Conference on Computer-Aided Design) is in its sixth year. Last year it attracted over 1000 attendees. A total of 124 papers have been accepted for the coming year's conference (in November), which will be in Santa Clara, California (as it has been every year).

EDAC (the European Design Automation Conference) was held "in cooperation with" SIGDA. Jochen J.A. Jess reviewed the conference. EDAC evolved from a CAVE workshop. The first conference was held in Glasgow last March. There were 450 paid attendees, and 600 participants overall. Next year it will be held in Amsterdam and they expect 700-800 participants. Seven workshops are being supported (at least partially) by SIGDA. Weil introduced representatives from each of them to tell the members about the workshops.

Rick McGeer discussed the ACM/IEEE International Workshop on Timing Issues in the Specification and Synthesis of Digital Systems (tau 90). It will be held August 15-17, 1990, in Vancouver. The workshop covers all aspects of timing. Forty-five papers have been submitted, 25 were accepted. Proceedings will be made available for attendees only. Each session will feature twenty-minute presentations followed by a panel discussion of the speakers in that session.

The Workshop on Logic Level Modeling for ASICs was discussed by Rob Mathews. It is attended by people involved in modeling, simulating and using ASICs. The first workshop was held December 3-5, 1989 and had 30 attendees. (See the June 1990 SIGDA Newsletter for the conference summary.) The next one is scheduled for August 12-14, 1990 in Monterey. It will have largely the same format. An announcement for the upcoming workshop also appears in the June 1990 Newsletter.

Ron Waxman discussed the Workshop on EDA Frameworks in Charlottesville, Virginia, November 26, 1990 (SIGDA and DATC are both working "in cooperation with" this IFIP workshop).

Waxman also talked about CHDL '91 (another IFIP workshop), which will be held in April 1991, in Marseille France, and is also "in cooperation with" SIGDA.

The workshop on Formal Methods in VLSI Design to be held January 1991 in Puerto Rico was discussed by P.A. Subrahmanian. The workshop is intended to bridge traditional CAD to those interested in formal methods.

# SIGDA MEMBERSHIP MEETING MINUTES (continued)

The Workshop on High Level Synthesis was discussed by Raul Camposano. It will be held in Black Forest, West Germany, on March 3, 1991.

The International Workshop on Logic Synthesis, was discussed by Franc Brglez of MCNC. A similar workshop is held each year in Research Triangle Park, North Carolina, "in cooperation with" SIGDA (last year's topic was layout synthesis). SIGDA provides funding for benchmark development and distribution support. The next one will be held May 7-10, 1991 and will have special emphasis on sequential logic synthesis. The workshop typically attracts 100+ attendees. Weil summarized the workshop program and the support that SIGDA offers in terms of proposal development, organization (including site selection, budgets and timeline of activities leading up to the meeting). He encouraged those with ideas for other workshops to contact him at the address which appears inside the front cover of the Newsletter.

#### D. Newsletter

Newsletter Editor Pat Hefferan reminded members that one of the membership benefits is the reduced rate for VHDL Manuals, EDIF Manuals, 25 Years of Design Automation, Proceedings of ICCAD and DAC which are available using the coupons printed in the Newsletter. He asked members to participate in the membership survey printed on page 13 of the June issue. Preliminary results say that 81% of the respondents are US citizens, 44% are from industry, and 72% have email addresses.

#### E. High School Scholarship (ASCEE)

Charlotte Acken informed the members that the program is in its second year. ASCEE awards undergraduate scholarships to underepresented minorities in computer science and EE fields. Last year the program was held in Las Vegas (the site of last year's DAC). Four high school juniors were selected as finalists. Two of these (Maria Nolasco and Kim Dinks) were selected as winners of \$4000/year renewable scholarships. Jon Duran received a one-time only \$1000 scholarship. The fourth finalist elected not to pursue a career in the computer science or EE fields, and thereby became ineligible to receive an ASCEE award.

This year the scholarship is being conducted in the San Francisco area. It was decided that having the scholarship follow the DAC each year, as originally planned, is too cumbersome to manage effectively. San Francisco was chosen because it has a large number of DA professionals available to serve as mentors. The program will again award two \$4000 per year renewable scholarships and two \$1000 one-time only scholarships. The winners will be introduced at the keynote address at DAC. Charlotte expressed her thanks to Regina Pistilli for founding program.

#### F. Travel Grant Program

Jim Cohoon reviewed the travel grant program which has an annual budget of \$125,000. This year there were 150 awards made. Roughly half of the budget goes to DAC attendees. A total of 110 students and professors traveled to DAC this year under the program. They represented 15 countries and 49 universities. Six awardees were Eastern Europeans.

#### G. Graduate Scholarships

Chuck Shaw reported for Herschel Loomis. A total of 10 graduate scholarships were awarded during the DAC general sessions. Library grants were awarded to all proposals which were not fully funded.

## H. Awards

Charles Radke presented the SIGDA service awards for this year. The SIGDA service

# SIGDA MEMBERSHIP MEETING MINUTES (continued)

awards were started in 1986 to recognize outstanding efforts of SIGDA volunteers. Two of the \$500 awards are given each year and no more than one can be from the current Advisory Board. This year's recipients were Fred Hinchliffe (for instituting the travel grant program) and Bryan Preas (for the CD-ROM project and serving as vicechairman). Radke also presented plaques to last year's recipients: Michael Lorenzetti and Scott Baeder.

#### I. Video Project

Mary Jane Irwin reported that the first SIGDA funded video will be Introduction to Design Automation by Richard Newton of UC Berkeley. The targeted audience is sophomore college students. The video is expected to be ready for fall distribution.

~

At this point the meeting was adjourned.

Respectfully Submitted,

Michael Lorenzetti SIGDA Secretary/Treasurer

# **MEMBERSHIP BENEFITS**

As a special benefit to SIGDA members, certain standards manuals, proceedings, and other documents of general interest will be made available at a nominal rate. Availability of the documents may vary, so allow several weeks for delivery. Proceedings will only be issued after the conference sales have been satisfied. *You must be a member of SIGDA to quality.*

| \ddress                              |                             |

|--------------------------------------|-----------------------------|

| CM Membershi                         | p Number                    |

| SELECTIONS                           | (please check box(es))      |

| Je Triddele e energie in Deile e Ein | tandards Manual             |

| VHDL Langua                          | ge Reference Manual         |

| 25 Vears of F                        |                             |

| 25 Years of E<br>1990 DAC Pro        | lectronic Design Automation |

Please send coupon to: Patrick M. Hefferan 1681 Princeton Avenue St. Paul, MN 55105

# SIGDA MEMBERSHIP SURVEY

In order to better serve the SIGDA membership, we are taking a survey of your wants and needs. Please take a few minutes to fill out the survey form on the next page and send it in. It has a preprinted address on the back, so just cut it out and fold it up with the address facing outward. Then tape (please do not staple) it shut and mail it in. You will need to provide 25 cents postage, as we cannot use our bulk mailing permit for this.

To make this more interesting and provide an incentive to get the surveys filled out, those who participate will be eligible for a drawing for a portable, electronic address book. We want to hear from you - so take a few minutes and fill it out. THANK YOU!!

## PLEASE FILL OUT AND SEND IN ----->

THE WINNER OF THE ELECTRONIC ADDRESS BOOK THIS QUARTER IS <u>DEBABRATA SARMA</u> FROM CINCINNATI, OHIO!! THERE WILL BE ANOTHER WINNER ANNOUNCED IN THE NEXT SIGDA NEWSLETTER.

#### SIGDA SURVEY January, 1990

#### This is a general membership survey. Participants will be entered in a drawing for an electronic address book.

| \ddress                                             | (May we publish this address?) _ Company Occupation |  |  |  |  |

|-----------------------------------------------------|-----------------------------------------------------|--|--|--|--|

|                                                     |                                                     |  |  |  |  |

|                                                     | Occupation                                          |  |  |  |  |

|                                                     |                                                     |  |  |  |  |

|                                                     | Job Function                                        |  |  |  |  |

| hone - Home                                         | Education                                           |  |  |  |  |

| Work                                                | (Highest attained)                                  |  |  |  |  |

| (Signature)                                         | <del>_</del>                                        |  |  |  |  |

|                                                     | sional?                                             |  |  |  |  |

|                                                     |                                                     |  |  |  |  |

| )o you have a PC at home?                           | If yes, what kind                                   |  |  |  |  |

|                                                     |                                                     |  |  |  |  |

|                                                     | t home? At work? Speed?                             |  |  |  |  |

| Are you connected to a network (Arpa, CIC,          | , INTERNET?)                                        |  |  |  |  |

|                                                     |                                                     |  |  |  |  |

| n what professional societies are you a mer         | mber?                                               |  |  |  |  |

|                                                     |                                                     |  |  |  |  |

| Nhat CAD/CAE functions are you responsib            | ole for?                                            |  |  |  |  |

| Schematic capture                                   | Simulation Layout                                   |  |  |  |  |

| DRC                                                 | Test Management                                     |  |  |  |  |

| Design                                              | Specification Evaluation                            |  |  |  |  |

| Mechanical                                          | Other                                               |  |  |  |  |

| Nhat additional benefits would you like from        | n SIGDA?                                            |  |  |  |  |

| DAC Proceedings                                     | DAC/ICCAD Admissions                                |  |  |  |  |

| ICCAD Proceedings                                   | Network Access for EMAIL/BBS                        |  |  |  |  |

|                                                     | Continuing Education                                |  |  |  |  |

| Standards Manuals                                   |                                                     |  |  |  |  |

| Standards Manuals<br>Tutorial Tapes                 | Other                                               |  |  |  |  |

| Standards Manuals<br>Tutorial Tapes<br>CD-ROM Tapes | Other                                               |  |  |  |  |

| Tutorial Tapes                                      | Other<br>YesNo                                      |  |  |  |  |

Indian. We are requesting that the Mentors be from the target groups. Also, for administrative purposes, the Mentors must be from the San Francisco Bay Area. For further details, contact Charlotte Acken (address on front cover).

Would you like to be a Mentor? \_\_\_\_\_Yes \_\_\_\_\_No

Of which target group are you a member?\_\_\_\_\_

put 25 cent stamp here

÷ ...

SIGDA Membership Survey c/o Patrick M. Hefferan 1681 Princeton Avenue Saint Paul, Minnesota 55105

# SIGDA EMAIL DIRECTORY

Listed below are the EMAIL addresses taken from the Membership Survey. Please check your address and advise us of any changes - either by an EMAIL message<sup>1</sup>, a short note, or simply send us the Survey form with a "revised" notation at the top. Drop us a message if you would like to be included in this directory.

|   | Acken, Charlotte      | cacken@sandia.llnl.gov                   |                                           |

|---|-----------------------|------------------------------------------|-------------------------------------------|

|   | Adshead, H. Gordon    |                                          |                                           |

|   | Benton, Ron           | rrbenton@honeywell.com                   |                                           |

|   | Blackburn, Robert     |                                          |                                           |

|   | Chakravarty, Sreejit  |                                          | ÷ 1                                       |

|   | Chen, Liang-Gee       |                                          |                                           |

|   | Chen, Kuang-Chien W   |                                          |                                           |

|   | Chiang, Charles       |                                          |                                           |

|   | Cohoon, James P.      |                                          |                                           |

|   | Crawford, Robert M    |                                          |                                           |

|   | DeGroat, JoAnne E     | degroat@hathi.eng.ohio-state.edu         |                                           |

|   | Enbody, Richard, Dr.  | enbody@cps.msu.edu                       |                                           |

|   | Gu, Jun               |                                          |                                           |

|   | Gupta, Anurag P       |                                          |                                           |

| 1 |                       | hefferan@frith.entmoot,cs.psu.edu        |                                           |

|   | Hemmendinger, David   |                                          |                                           |

|   | Hughes, J. Gordon     |                                          |                                           |

|   | Irwin, Mary Jane      |                                          |                                           |

|   | Jost, Allan G         |                                          |                                           |

|   | Kaufman, Jerry        |                                          | •                                         |

|   | Kim, Heung-Nam        |                                          |                                           |

|   | Kim, Soohong          |                                          |                                           |

|   |                       | KWANGMI@GONDOR.CS.PSU.EDU                | 1. C. |

|   |                       | DEAN.KUKRAL@WICHITA.NCR.COM              |                                           |

|   | Lin, Youn-Long S      |                                          |                                           |

|   | Loomis, Herschel, Jr  |                                          |                                           |

|   | Lorenzetti, Michael   |                                          |                                           |

|   | Magnuson, Waldo G.,Jr |                                          |                                           |

|   |                       | MARWEDEL@Is12.informatik.uni-dortmund.de |                                           |

|   | Midkiff, Scott F      |                                          |                                           |

|   | Moh, Teng-Sheng       | moht@iris.ucdavis.edu                    |                                           |

|   | Preas, Bryan T        | preas@cadlab.cadlab.de                   |                                           |

|   | Quayle, Michael S     | quayle@ee.cornell.edu                    |                                           |

|   | Radke, Charles E      | C.RADKE@COMPMAIL.COM                     |                                           |

|   | Rajsuman, Rochit      |                                          |                                           |

|   | Ravi, S. S            |                                          |                                           |

|   | Ritchie, Elaine K     | ritchie%hpstek.dec@decwrl.dec.com        |                                           |

|   | Roy, Rabindra K       |                                          |                                           |

|   | Rundensteine, Elke    |                                          |                                           |

|   | Sarma, Debabrata      | sarma@ucecl.ece.uc.edu                   |                                           |

|   | Shaw, Charles A       | shaw@cadence.com                         |                                           |

|   | Smith, Richard C      | nsc!parns!ricardo                        |                                           |

|   | Spillinger, Ilan      | ilan@techunix.bitnet                     |                                           |

|   | Stevenson, Carl R.    | 73065,270@cis.com                        |                                           |

|   | Taylor, Gordon        | gft@genrad                               |                                           |

|   | Tonkin, Bruce         |                                          |                                           |

|   | Tuan, T. C            |                                          |                                           |

# SIGDA EMAIL DIRECTORY (continued)

| Walker, Duncan M. | dmw@ece.cmu.edu          |

|-------------------|--------------------------|

| Waxman, Ron       | waxman@virginia.edu      |

| Weil, Paul B.     | weilcad@frith.cs.psu.edu |

| Wilsey, Philip A  | paw@ueeng.uc.edu         |

| Wong, Martin      | • • •                    |

| Wuu, Tzyh-Yung    | •                        |

÷ . . .

ىسم

SIGDA Newsletter, vol 20, number 2

÷ 2.

# Departments

The following pages contain updates and information about various projects and activities funded by the SIGDA. Contact information (e-mail, phone, and addresses) for the individuals directing the programs can be found on the inside front cover.

## Workshops/Conferences ..... Paul B. Weil

SIGDA sponsors many Workshops and Conferences in the Electronic CAE/CAD arena. During 1990 and 1991, SIGDA will either sponsor cosponsor or work in cooperation with other professional societies on 20 professional meetings. Please watch the newsletter for announcements.

We are always developing new Professional Activities to meet the needs of our 2000 + membership. SIGDA does its utmost to assist the organizing committees through comprehensive support activities. For the smaller meetings, SIGDA funds ACM and others who provide direct assistance with: site selection, budgeting, advertisement, and registration. This leaves the organizers with time to develop a superior technical program.

If you would like to propose a Conference or Workshop,

you need only to prepare a two page summary of: The Meeting's Technical Objectives, Background of this and similar meetings on this Subject, Potential Locations and Dates, Meeting Size and Format, and the Organizing Committee and brief background of Chairpersons. This should be e-mailed to the SIGDA Workshop and Conference Chair Dr. Paul Weil at *weilcad@frith.cs.psu.edu*

#### SIGDA SPONSORED CONFERENCES, SYMPOSIUM, AND WORKSHOPS APPROVAL PROCESS

1. PROPOSAL: Two page Summary of:

The Meeting's Technical Objectives Background of this and similar meetings on this Subject Potential Locations and Dates Meeting Size and Format بر Organizing Committee and brief background of Chairpersons

2. INITIAL ORGANIZATION: ACM will assist the Committee with:

Site Selection Budgets Timeline of Activities leading up to the Meeting

#### 3. MEETING BETWEEN ACM/SIGDA REPRESENTATIVE AND CHAIRPERSON(s)

4. FORMAL APPROVAL BY SIGDA

SIGDA Newsletter, vol 20, number 2

5. SIGDA WILL ARRANGE FOR ACM TO PROVIDE ASSISTANCE IN:

Local Arrangements Call of Papers/Participation Registration Advanced Program Publications Onsite Registration Post Conference Accounting

The ACM/SIGDA encourages the organizers to consider in-cooperation or co-sponsorship with other Professional Societies (ACM/SIGDA has a close working relationship with the IEEE as well as other Electronic Engineering Societies).

#### AFTER THE MEETING

IMMEDIATELY FOLLOWING THE CONF/SYMP/WORKSHOP hold a meeting that will discuss future events and seek volunteers to run these events.

STATUS REPORT: Within a few days of the Meeting transmit to SIGDA a brief status report including the meeting's attendance, financials, how the meeting met its technical objectives and any outstanding problems that may have developed.

MEETING SUMMARY: Within a few Weeks of the Meeting provide a 5 to 10 page Summary (see the June 1990 Newsletter pp 129-135 for a good example) of the meeting's activities for publication in the SIGDA Newsletter along with plans for future events. Emphasize the Technical aspects of the CONF/SYMP/WORKSHOP.

COPIES OF PROCEEDINGS: Any Proceeding or Digest of the material presented at the Meeting should be available to SIGDA Members. Five copies should be mail to SIGDA as soon as they are available. Arrangements must be made to assure that a quantity of proceedings can be purchased by SIGDA Members.

## Outstanding Member Recognition .....Charles A. Radke

Since January of 1971, SIGDA has been in continuous operation, and over these 15 years has steadily increased its influence on the Design Automation profession. It, therefore, appears fitting that SIGDA recognize those members who have given so much of themselves to the SIGDA organization, to the members, to its newsletter, and to the sponsored technical functions (e.g., conferences, workshops, and symposia).

The award is given annually and is presented at the Design Automation Conference. It consists of a plaque plus \$500. No more than two are given in a year, and none are awarded if no appropriate candidate is felt to exist.

A committee of four including the SIGDA Advisory Board Person responsible for Outstanding Member Recognition selects the award winners from nominations received from the SIGDA

membership. The nominations must be in by 3/15 with a decision by 5/15 of that same year.

The awards for the past five years were:

1986 Richard C. Smith & Charles E. Radke

1987 Robert Smith & Waldo G. Magnuson, Jr.

1988 Charles A. Shaw & Luther Abel

1989 Michael J. Lorenzetti & D. Scott Baeder

1990 Frederich Hinchcliffe & Bryan T. Preas

If you have a nomination for the upcoming 1991 year, please send it to me (my address is on the front cover). Please state the reasons for your nomination.

## Benchmark Development & Distribution .....

Mr. Brglez has recently taken over the management of the SIGDA sponsored benchmark series from Michael Lorenzetti. Mr. Brglez is at the Microelectronics Center of North Carolina. His report follows:

An unknown number of benchmarks have been obtained from MCNC anonymously via ftp copies over the Unix network. Also, a total of 46 tapes and printed versions were distributed to 14 foreign countries and the US between January 1 and June of 1990. See the distribution profile below for detail.

| BENCHMARK            | <b>Requests Filled</b> |

|----------------------|------------------------|

| MODGEN89             | 1                      |

| Logic Synthesis 89   | 5                      |

| PNR88                | 2                      |

| COMPACT87            | 0                      |

| ISCAS85              | 7                      |

| ISCAS89 ~            | 7                      |

| High Level Synthesis | 0                      |

| Layout Synthesis90   | 14                     |

| All Benchmarks       | 10                     |

I plan to approach the program chair of next year's DAC about having a panel session on benchmarks. Please contact me at (919) 248-1925 or e-mail at *brglez@mcnc.org* for further details about the SIGDA sponsored benchmark program.

## University Booth Project ...... Martin Wong (Mary Jane Irwin 1989)

This is the third year that the SIGDA has sponsored the University Booth at the DAC. This year's booth was the largest yet, measuring  $30' \times 45'$ , and was equipped with five workstations.

Twenty universities demonstrated their research programs and work of their graduate students. Also, the SIGDA's CD-ROM prototype (running on a Sun workstation) was demonstrated at the University Booth.

James Cohoon will be taking over the University booth project for next year's DAC. Below is a schedule of the demonstrations at the 1990 DAC.

|      | SUNDAY          |                  |                  |                 |                  |      |  |

|------|-----------------|------------------|------------------|-----------------|------------------|------|--|

| TIME | Sun 4/60        | Sun 4/60         | Sun 4/110        | DECstation 3100 | DECstation 3100  | MISC |  |

|      | panda           | uci_cad          | frith            | washoe          | hydrus           |      |  |

| 4:00 | ATPG            | SLAM/LES         | slicer/splicer   | BLIS            | PEW/FABRICS      |      |  |

| to   | test generation | layout synth     | schdl, connctvty | behav to logic  | proc/device sim  |      |  |

| 5:00 | Virginia Tech   | UC Irvine        | Penn State       | UC Berkeley     | CMU              |      |  |

| 5:00 | BTG             | MILO/VSS         | ivf2glue         | SLIP            | COSMOS           |      |  |

| to   | test generation | optmz, synth     | machine synth    | partitioning    | switch level sim |      |  |

| 6:00 | Virginia Tech   | UC Irvine        | Penn State       | UC Berkeley     | CMU              |      |  |

| 6:00 | CHAMP           | BIF/EXEL         | SDE              | VOV             | SAW              |      |  |

| to   | logic fault sim | behavioral synth | o-o design env   | design managmt  | behavioral synth |      |  |

| 7:00 | Illinois        | UC Irvine        | Michigan State   | UC Berkeley     | CMU              |      |  |

|       | MONDAY          |                  |                  |                  |                  |                |  |  |

|-------|-----------------|------------------|------------------|------------------|------------------|----------------|--|--|

| TIME  | Sun 4/60        | Sun 4/60         | Sun 4/110        | DECstation 3100  | DECstation 3100  | MISC           |  |  |

|       | panda           | uci_cad          | frith            | washoe           | hydrus           |                |  |  |

| 10:00 | ATPG            | DSUI             | ivf2glue         | EDIF/CFI         | VLASIC           | GALAXY         |  |  |

| to    | test generation | user interface   | machine synth    | EDIF tools       | yield sim        | design env     |  |  |

| 11:00 | Virginia Tech   | TU Delft         | Penn State       | UC Berkeley      | CMU              | Wisconsin      |  |  |

| 11:00 | CHAMP           | DSUI             | factorII/tvg     | MIS              | HITEC/PROOFS     | GALAXY         |  |  |

| to    | logic fault sim | user interface   | ml logic synth   | multilevel synth | test gen, f sim  | design env     |  |  |

| 12:00 | Illinois        | TU Delft         | Penn State       | UC Berkeley      | Illinois         | Wisconsin      |  |  |

| 12:00 | ICE             | SLAM             | artistII         | SLIP             |                  | GALAXY         |  |  |

| to    | incremental sim | layout synth     | , layout synth   | partitioning     |                  | design env     |  |  |

| 1:00  | Illinois        | UC Irvine        | Penn State       | UC Berkeley      |                  | Wisconsin      |  |  |

| 1:00  | SYLON           | MILO             | SDE              | BOLD             | PEW/FABRICS      |                |  |  |

| to    | logic net synth | logic optm:      | o-o design env   | X win interface  | proc/device sim  |                |  |  |

| 2:00  | Illinois        | UC Irvine        | Michigan State   | Colorado         | CMU              |                |  |  |

| 2:00  | ASYL            | VSS              | a.out            | BLIS             | MICON            |                |  |  |

| to    | std cells synth | behavioral synth | sizer            | behav to logic   | SBC prototyping  |                |  |  |

| 3:00  | INP Grenoble    | UC Irvine        | UC Santa Cruz    | UC Berkeley      | CMU              |                |  |  |

| 3:00  | OESIM           | BIF/EXEL         | a.out            | EDIF/CFI         | HITEC/PROOFS     | Modeler's Asst |  |  |

| to    | high level sim  | behavioral synth | sizer            | EDIF tools       | test gen, f sim  | VHDL generator |  |  |

| 4:00  | Washington      | UC Irvine        | UC Santa Cruz    | UC Berkeley      | Illinois         | Virginia Tech  |  |  |

| 4:00  | WIREC           | UCI Tools        | hdtv             | OLYMPUS          | SAW              | Modeler's Asst |  |  |

| to    | framework       | misc             | timing verifictn | vertical synth   | behavioral synth | VHDL generator |  |  |

| 5:00  | Washington      | UC Irvine        | Pittsburgh       | Stanford         | CMU              | Virginia Tech  |  |  |

| 5:00  | OESIM           | UCI Tools        | TimberWolf       | VOV              | minTC            | Modeler's Asst |  |  |

| to    | high level sim  | misc             | placemt, routing | design managmt   | optimal clock    | VHDL generator |  |  |

| 6:00  | Washington      | UC Irvine        | Yale             | UC Berkeley      | Michigan         | Virginia Tech  |  |  |

The ACM SIGDA CD-ROM Project is also exhibited in the University Booth

|       | TUESDAY         |                  |                  |                  |                  |                  |  |  |

|-------|-----------------|------------------|------------------|------------------|------------------|------------------|--|--|

| TIME  | Sun 4/60        | Sun 4/60         | Sun 4/110        | DECstation 3100  | DECstation 3100  | MISC             |  |  |

|       | panda           | uci_cad          | frith            | washoe           | hydrus           |                  |  |  |

| 10:00 | ASYL            | NELSIS           | hdtv             | SIS              | minTC            | SPARK            |  |  |

| to    | std cells synth | CAD framework    | timing verifictn | seq ckt synth    | optimal clock    | test gen, diagns |  |  |

| 11:00 | INP Grenoble    | TU Delft         | Pittsburgh       | UC Berkeley      | Michigan         | Case Western     |  |  |

| 11:00 | CHAMP           | NELSIS           | slicer/splicer   | OLYMPUS          | SAW              | SPARK            |  |  |

| to    | logic fault sim | CAD framework    | schdl, connctvty | vertical synth   | behavioral synth | test gen, diagns |  |  |

| 12:00 | Illinois        | TU Delft         | Penn State       | Stanford         | CMU              | Case Western     |  |  |

| 12:00 | BTG             | VSS              | ivf2glue         | BLIS             | PEW/FABRICS      | SPARK            |  |  |

| to    | test generation | behavioral synth | machine synth    | behav to logic   | proc/device sim  | test gen, diagns |  |  |

| 1:00  | Virginia Tech   | UC Irvine        | Penn State       | UC Berkeley      | CMU              | Case Western     |  |  |

| 1:00  | ATPG            | BIF/EXEL         | factorII/tvg     | BOLD             | VLASIC           |                  |  |  |

| to    | test generation | behavioral synth | ml logic synth   | X win interface  | yield sim        |                  |  |  |

| 2:00  | Virginia Tech   | UC Irvine        | Penn State       | Colorado         | CMU              |                  |  |  |

| 2:00  | ICE             | SLAM             | artistII         | VOV              | COSMOS           |                  |  |  |

| to    | incremental sim | layout synth     | layout synth     | design managmt   | switch level sim |                  |  |  |

| 3:00  | Illinois        | UC Irvine        | Penn State       | UC Berkeley      | CMU              |                  |  |  |

| 3:00  | BTG             | BIF/EXEL         | TimberWolf       | MIS              | Architectural    | CATHEDRAL-II     |  |  |

| to    | test generation | behavioral synth | placemt, routing | multilevel synth | Synthesis        | DSP Si compiler  |  |  |

| 4:00  | Virginia Tech   | UC Irvine        | Yale             | UC Berkeley      | CMU              | IMEC Leuven      |  |  |

| 4:00  | ASYL            | SPACE            |                  | SIS              | MICON            | CATHEDRAL-II     |  |  |

| to    | std cells synth | 3D verification  |                  | seq ckt synth    | SBC prototyping  | DSP Si compiler  |  |  |

| 5:00  | INP Grenoble    | TU Delft         |                  | UC Berkeley      | CMU              | IMEC Leuven      |  |  |

| 5:00  | SYLON           | SPACE            | a.out            | OLYMPUS          | minTC            | CATHEDRAL-II     |  |  |

| to    | logic net synth | 3D verification  | sizet            | vertical synth   | optimal clock    | DSP Si compiler  |  |  |

| 6:00  | Illinois        | TU Delft         | UC Santa Cruz    | Stanford         | Michigan         | IMEC Leuven      |  |  |

# 27th DAC University Booth

|       | WEDNESDAY       |                  |                  |                 |                 |                |  |  |

|-------|-----------------|------------------|------------------|-----------------|-----------------|----------------|--|--|

| TIME  | Sun 4/60        | Sun 4/60         | Sun 4/110        | DECstation 3100 | DECstation 3100 | MISC           |  |  |

|       | panda           | uci_cad          | frith            | washoe          | hydrus          |                |  |  |

| 10:00 | ICE             | UCI Tools        | TimberWolf       | SLIP            | HITEC/PROOFS    | JUNE           |  |  |

| to    | incremental sim | misc             | placemt, routing | partitioning    | test gen, f sim | placer. router |  |  |

| 11:00 | Illinois        | UC Irvine        | Yale             | UC Berkeley     | Illinois        | Minnesota      |  |  |

| 11:00 | SYLON           | VSS              | ivf2glue         | OLYMPUS         | minTC           | JUNE           |  |  |

| to    | logic net synth | behavioral synth | machine synth    | vertical synth  | optimal clock   | placer, router |  |  |

| 12:00 | Illinois        | UC Irvine        | Penn State       | Stanford        | Michigan        | Minnesota      |  |  |

| 12:00 | WIREC           | BIF/EXEL -       | hdtv             | BOLD            | Architectural   | JUNE           |  |  |

| to    | framework       | behavioral synth | timing verifictn | X win interface | Synthesis       | placer, router |  |  |

| 1:00  | Washington      | UC Irvine        | Pittsburgh       | Colorado        | CMU             | Minnesota      |  |  |

| 1:00  | OESIM           | MILO/SLAM        | factorII/tvg     | EDIF/CFI        | MICON           |                |  |  |

| to    | high level sim  | optmz. synth     | ml logic synth   | EDIF tools      | SBC prototyping |                |  |  |

| 2:00  | Washington      | UC Irvine        | Penn State       | UC Berkeley     | CMU             |                |  |  |

| 2:00  | WIREC           |                  |                  |                 |                 |                |  |  |

| to    | framework       |                  |                  |                 |                 |                |  |  |

| 3:00  | Washington      |                  |                  |                 |                 |                |  |  |

The ACM SIGDA CD-ROM Project is also exhibited in the University Booth

# **DAC** Photos

Following are photographs of the 27th DAC including the Summer SIGDA Meeting and associated activities.

# Entrance to the 27th DAC Exhibit hall and Conference Rooms

Martin Wong, this year's SIGDA University Booth Manager, and Mary Jane Irwin, last year's Booth Manager, stand in front of their creation

A conference attendee talks with an exhibitor from the University of California at Irvine in the SIGDA booth.

## Luncheon for SIGDA-Sponsored Eastern European Students

The SIGDA sponsored travel and DAC attendance for six students from Eastern European countries. They were paired with Western European students who acted as mentors.

Jim Cohoon organized the travel and arrangements for the Eastern Europeans, and set up a luncheon for them and their mentors.

## SIGDA High School Scholarship Program

The SiGDA provides a scholarship to under-represented groups in the engineering field. The recipients were invited to the DAC in Orlando and attended the DAC functions as well as Disney World.

> Charlotte Acken administers the SIGDA High School Scholarship program.

Maria Soledad Ochomongo and Raul Alberto Ortega, Jr.

Christopher Ray Silva and Tessa Helena Wilbert.

## SIGDA Summer Meeting (1990)

The annual general membership meeting of the SIGDA was held at the Orlando Convention Center. Summaries of the major SIGDA projects and workshops were presented.

Chuck Shaw, Chairman of SIGDA, opens the annual summer meeting of the ACM/SIGDA

The crowd mills around the food and refreshment table before the SIGDA meeting.

Rob Matthews reports on the successful ASIC modelling workshop held this Spring.

#### SIGDA Outstanding Member Awards

The SIGDA recognizes outstanding members who have made significant contributions to the society and the DA profession. Charles Radke is the board member in charge of this award. Awards for both 1989 and 1990 were presented at this year's DAC.

Chuck Radke presents the award to Michael Lorenzetti, SIGDA Secretary-Treasurer

Chuck presents awards to Bryan Preas, SIGDA Vice Chairman and director of the CD-ROM Project, and to Fred Hinchcliffe, the former SIGDA Travel Grants Director.

Chuck presents the award to D. Scott Baeder, the former Newsletter Editor.

#### A New Placement Level Wirability Estimate with Measurements

#### Steve Meyer

#### Pragmatic C Software 220 Montgomery Street, Suite 925 San Francisco, CA 94104

Abstract: An extension of the wirability estimate concept to master slice placement is presented. This estimate is usable on individual circuits, produces detailed wire requirement maps, but requires target designs to be at least partially placed. The main innovation is the discovery of an outer rectangle estimate that separates basic wire requirements from routing details. The estimate averages wires within one chip but is inapplicable to chip type wire space modeling. Steiner tree net decomposition, the half perimeter wire length estimate, and potential wire requirement reduction from a third metal layer are evaluated.

#### 1. Introduction

Just as approximate device models are necessary during logic design, approximate wirability estimates assist in layout system development. Once the decision to improve a layout system is made, it is often difficult to identify the part of the system most in need of improvement. This paper describes a new wirability estimate usable during and after placement on master slice based semicustom ICs. A master slice based IC is either a gate array or standard cell circuit organized as fixed length cell rows separated by wiring channels with two perpendicular metal wiring layers. Vertical feed thrus are used for cross row connections [18] [29].

The estimate produces detailed chip maps that can be used to determine if congested regions are caused by the placement or by the routing part of a layout system. It can be used on automatically or manually placed designs at any placement stage. The idea behind this estimate is to compute a very simple global routing. It measures placement wire requirements independent of channel router efficiency and independent of congestion versus wire length trade offs made by global routers (see [14] for example).

Three basic estimate matrices are computed. One measures the number of horizontal wires running along each wiring channel at every wire grid. Another measures the number of vertical feed thru wires crossing every active row at every grid. The third measures the vertical wiring channel crossing wires. The three computed matrices are used to produce wire requirement maps and to compute global statistics. The estimate is called "outer rectangle" because 1/2 wire is added to the value (row or channel wire number) for all four sides of the bounding rectangle determined by each two point connection. Every signal net is decomposed into pin pairs by computing the minimum spanning tree (MST) on the complete graph corresponding to each net. The outer rectangle wire segments are treated as if every channel and every feed thru grid had "infinite" capacity.

Exact chip totals such as total-substrate wiring channel track demand or total row feed thru requirements can be computed. The total is exact because even though fractional wires are used, the totals are exact after division by two. In this paper the estimate results are interchangeably called maps, the output form, arrays, the storage form, or matrices, the conceptual form.

#### **1.1 Relation to Other Wirability Estimates**

The estimate is related to standard wiring capacity demand matrices (see [2] for example) but requires only placement level circuit data base information and produces more detailed (fine grain) measurements for each placement. It is also slightly related to the placement evaluation scheme described by Shiraishi and Hirose[26], but does not use net cut crossing counts and is able to predict feed thru requirements. The outer rectangle estimate is complementary to the standard statistical chip wirability (chip type wiring space requirements) work [3] [5-6] [8] [10-11] [30-31]. It is also related to transistor area evaluation metrics [25]. Measurements from the circuit maps can be used to validate wirability models. The estimate should perhaps be called circuit or even circuit region specific wirability. Statistical validation of this estimate is meaningless since it simply measures important

layout parameters. The simplifying assumptions have proven in practice to balance accuracy against programming ease and resource utilization.

#### **1.2 Relation to Global Routing**

In a sense this estimate is an abstracted global router. However, it can be used on partial placements because data from the routing part of the circuit data base is not required. A real global router needs to know exactly which feed thru grids are blocked, and where to add extra feed thru cells for standard cell layouts. Exact horizontal channel entry points need to be determined before a standard channel router can be used. Papers by Lee [14] and Rose [23] describe global routers that also break nets into pin pairs using an MST calculation and then search for a path connecting the pin pair minimizing some evaluation function. The outer rectangle estimate introduced here uses the best routing path assuming no interference from other connections. If a one bend route is possible, it will cause the least additional congestion. This idealized estimate is preferable for placement evaluation since it is unaffected by router implementation details [20] [17].

#### 2. Estimate Description

#### 2.1 Matrix Dimensions

The vertical row feed thru matrix (called vrow[][] below) has dimension R by G+2 where R is the number of rows and G is the wire grid number per per row. Every wire connecting to or feeding thru a row is added to its grid row location. For the purpose of including signal nets connecting I/O pads to the master slice area, I/O pads are assumed to be located at the real substrate wire grid and row closest to the lower left pad corner in a "virtual" row or grid just outside the master slice area. I/O pads that lie inside the master slice area.

The horizontal channel congestion matrix (called hchan[][] below) has dimension R+1 by G+2. The channel corresponding to a row is by convention immediately above it. This means an extra matrix row is needed immediately below the bottom row. Notice the channel immediately above and the channel immediately below the master slice area are included in the output map. The vertical channel feed thru matrix (called vchan[][] below) has dimension R+1 by G+2 and includes wires crossing a channel. Such wires may cause problems for a channel router.

#### 2.2 Algorithm

To compute the outer rectangle matrices first decompose all nets into N-1 two point connections (assume the size of a net is N). The minimum spanning tree (MST) of the complete graph of N points is the best decomposition. See section 5 for a discussion of the various problems encountered in attempting to use one easy to compute L-shape Steiner tree decomposition method. The distance metric should be the sum of the rectilinear matrix row and column distances. When connecting to a pin from below, the pin should be treated as if it were located on the bottom of its row. When connecting from above, the pin should be treated as if it were on top.

Next add each pin pair to the three arrays in any order. Add one to each array location crossed by the wire segments required to connect the MST pin pair. The outer rectangle estimate assumes a pin pair connection is made with four wires coincident with the four rectangle sides determined by the two points. After all connections have been added to an outer rectangle array, each array value is divided by two because each pin pair is connected twice and because only one wire will actually connect the pin pair.

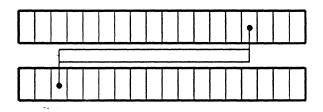

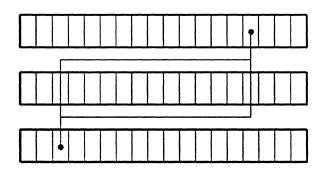

There are three different possible connection configurations: a connection crossing at least two wiring channels, a connection crossing exactly one wiring channel, and a connection extending horizontally along one cell row crossing no wiring channel. For each connection type both the vertical and the horizontal wire matrices must be updated (see figures 1-3). Two aspects of the updating must be treated carefully. For wires crossing at least one channel, the channels closest to the rectangle center must have their counts incremented. When both pins connect to grids along the same vertical line, the rectangle degenerates into two coincident lines. Each crossed grid and channel must be incremented by two.

#### **3. Implementation Details**

#### 3.1 MST Pin Data Structure

Assuming a circuit is stored according to the data structure scheme described in [16], the following C Programming Language [13] pin data structure can be used to decompose one signal net into N, MST pin pairs (one pin element will be the root and have no connecting pin):

```

struct pintab_t { /* place for one MST edge */

struct type_pin_t *ptpin; /* the pin's type data */

struct coord_t pt; /* pin (grid, row) coordinates */

int ndist; /* current ptr to partial MST distance */

struct pintab_t *nrnod; /* current nearest node */

struct coord_t nrpt; /* nearest pin coordinates */

};

struct pintab t pintab[MAXNETSIZE];

```

The MST is stored so that each element points only to the coordinates of its tree parent. This is sufficient to determine pin pairing since tree topology is not needed.

#### 3.2 MST Function

The following in place implementation of Prim's algorithm [21] can be used to compute the MST for one net (pointed to by parameter np). It assumes the pintab[] array is filled and initialized for every pin in the net and assumes the np->npnum field contains the number of pins in the net. The ptp->ndist field must be initialized to the constant FAR\_DIST that is larger than the wire grid size of the chip, and the ptp->nrnod field must be initialized to NULL. The exchange() function exchanges the contents of two pintab[] elements and the wdist() functions computes the rectilinear row and grid distance between pintab[] pin pair entries.

```

cmp nmst(np)

struct net_t *np;

{

register struct pintab t *endp, *ptp, *minp;

int tmp, mind, edges, numtodo;

edges = np - npnum - 1;

for (endp = &pintab[0]; edges > 0; endp++, edges--)

{

mind = FAR DIST;

numtodo = edges;

for (ptp = endp + 1; numtodo > 0; ptp++, numtodo--)

if ((tmp = wdist(&endp->pt, &ptp->pt)) < ptp->ndist)

{ ptp->ndist = tmp; ptp->nrnod = endp; }

if (ptp->ndist < mind) { mind = ptp->ndist; minp = ptp; }

}

/* link in edge pointing to tree parent */

minp->nrpt = minp->nrnod->pt;

/* change pintab[] so new node will be at endp next pass */

exchange(minp, endp + 1);

-

}

}

```

This algorithm runs in  $O(N^2)$  time but makes no assumption that wdist() uses geometric distance. See [7] or [1] for a discussion of MST algorithms. Since the real pin to pin tree edge is not needed and since **pintab**[] entries move, the nearest pin coordinates are used to represent the edge when updating the maps or wire lengths. Notice the part of the circuit data base containing mask level data can be ignored, and once data base coordinates are translated into master slice row and grid values, wire coordinates can be ignored.

#### **3.3 Example Matrix Update Function**

The following C function illustrates map update code for a decomposed MST edge with pin pairs separated by at least one row. This code assumes the points have coordinates (grid1, row1) and (grid2, row2), and that a possible exchange has been made to insure row1 <= row2. vrow[][] in the matrix of vertical row crossing feed thru wires, vchan[][] is the matrix of vertical channel feed thru wires, and

hchan[][] is the horizontal wiring channel matrix. addin\_vert() adds one to the vertical count in the given map from the first row to second row along the given grid. addin\_chan() adds one to every horizontal grid along the channel at hchan[row] from grid1 to grid2.

```

add_dist_conn(grid1, row1, grid2, row2)

int grid1, row1, grid2, row2;

{

/* know at least one row between connecting rows */

addin_vert(vchan, grid1, row1, row2 - 1);

addin_vert(vrow, grid1, row1, row2);

addin_vert(vrow, grid2, row1, row2);

/* channel with same row number is above row */

addin_chan(hchan, grid1, grid2, row1 - 1);

addin_chan(hchan, grid1, grid2, row1);

```

#### **3.4 Output Format**

A good output scheme rotates the maps ninety degrees. Cell rows run from top to bottom in a file or on a printed page. Maps of large circuits will be too wide for one page, but a map file can be separated into vertical segments and then joined after printing. For channel map sections see figure 4 and 5. For over row feed thru map sections see figure 6.

#### 3.5 Run Time