# SIGDA NEWSLETTER

A Quarterly Publication of the Special Interest Group on Design Automation

| VOLUME 20                                                                                                                                                                 | NUMBER I                                                                                           | JUNE 1990                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------|

| CONTENTS                                                                                                                                                                  |                                                                                                    | PAGE                                   |

| Letter from the Chair<br>SIGDA Advisory Board<br>Membership Benefits Se<br>Letters to SIGDA                                                                               |                                                                                                    | 2<br>3<br>12<br>15                     |

| DEPARTMENTS<br>European Activities<br>Workshops/Confere<br>Asian ActivitiesAki<br>CD-ROM ProjectB<br>BylawsMichael J. Lo<br>High School Scholarsl<br>Scholarship Program- | nces—Paul B. Weil<br>hiko Yamada<br>ryan & Kathy Preas<br>orenzetti<br>nip Program—Charlotte Acken | 18<br>19<br>21<br>22<br>26<br>32<br>33 |

| ACM CSC'90 Report-<br>DAC Insider's Guide-F                                                                                                                               | Michael J. Lorenzetti                                                                              | 36<br>42<br>43                         |

| ARTICLES<br>CAD Tool Interchang<br>by Steve Meyer                                                                                                                         | geability through Net List Translation<br>Data Integration by G. Kaufman                           | 5 I<br>60                              |

| Conference Reports<br>DA Standards Activities<br>Calendar of Events—Su<br>Conferences & Announ<br>LATE NEWS: ASIC Mod                                                     | (CFI)<br>nil Das                                                                                   | 82<br>108<br>111<br>13<br>129<br>136   |

| **************************************                                                                                                                                    |                                                                                                    | ************************************** |

$\gamma = \frac{1}{2}$

SPECIAL DESIGN AUTOMATION CONFERENCE ISSUE Attend the SIGDA Annual Meeting at DAC—Sunday 7:00 pm

.

## SIGDA BOARD OF ADVISORS

#### Nominating Committee Chair

Richard C. Smith National Semiconductor, Inc. 2900 Semiconductor Drive, D3677 Santa Clara, California 95051 (408) 721-4794 FAX (408) 773-0978 nsc!parns!ricardo

#### High School Scholarship Program

Charlotte F. Acken Sandia National Laboratories, Div. 4853 P. O. Box 969 Livermore, California 94551 (415) 294-3248 FAX (415) 294-1539 cacken@sandia.llnl.gov

#### **Bibliography & Textbook Projects**

Waldo G. Magnuson, Jr. Lawrence Livermore National Lab. P. O. Box 808, L-153 Livermore, California 94550 (415) 422-9950 FAX (415) 423-5080 magnuson@icdc.llnl.gov

#### Workshops/Conferences (except DAC)

Paul B. Weil Nextwave Design Automation, Inc. 5339 Prospect Road, Suite 240 San Jose, California 95129 (408) 255-6458 pweil@icdc.llnl.gov

### **IEEE/CS DATC Chairman**

Ron Waxman University of Virginia, Thornton Hall Charlottesville, Virginia 22901 (804) 924-6086 FAX (804) 924-8818 waxman@virginia.edu

#### Outstanding Member Recognition

Charles E. Radke IBM Corporation, AR1 Route 52 Hopewell Junction, New York 12533 (914) 892-2957 FAX (914) 892-3039

#### **European Activities**

H. Gordon Adshead International Computers Ltd. Wenlock Way, West Gorton Manchester M125DR, ENGLAND (011-44-61) 223-1301

#### **Asian Activities**

Akihiko Yamada, Chief Engineer Information Processing Group NEC Corporation, Daito Tamachi Bldg. 14-22 Shibaura 4-Chome, Minato-Ku Tokyo 108, JAPAN (011-81-3) 456-5750 NEFAX (011-81-3) 456-7495

#### **Travel Grants**

James P. Cohoon, Ph.D. Department of Computer Science University of Virginia, Thornton Hall Charlottesville, Virginia 22903 (804) 982-2210 FAX (804) 982-2214 csnet: cohoon@virginia.edu uucp: !uvacs!cohoon

#### Scholarships

Herschel Loomis, Jr. Naval Postgraduate School - EE Dept. Code 62Lm Monterey, California 93943 (408) 646-3214 Ioomis@cs.nps.navy.mil

#### University Faculty Activities

Mary Jane Irwin Pennsylvania State University Department of Computer Science University Park, Pennsylvania 16802 (814) 865-3176 mji@psuvaxl.cs.psu.edu

#### University Booth Project (DAC)

Martin Wong Department of Computer Science University of Texas Austin, Texas 78712 (512) 471-7316 wong@cs.utexas.EDU

# SIGDA OFFICERS

#### Chairman & ACM DAC Representative

Charles A. Shaw Cadence Design Systems, Inc. 2455 Augustine Drive Santa Clara, CA 95054-3082 (408) 987-5321 shaw@cadence.com

#### Secretary/Treasurer

Michael J. Lorenzetti Microelec. Center of North Carolina P.O. Box 12889 Research Triangle Park, NC 27709 (919) 248-1915 mikel@mcnc.org

# EDITOR'S NOTES

Welcome to the summer edition of the SIGDA Newsletter, the DAC edition. It contains a real mix of articles from how to get the most from your trip to the DAC to thermal expansion joints (circa 1970). Also, there are summaries of the first-ever European DA conference (EDAC-90) held in Glasgow.

We also have a special feature in this edition courtesy of Chuck Radke. We have reprinted the first *SIGDA Newsletter* (Vol. 1, No. 1). Chuck has archived all the *Newsletters*, and he kindly sent me copies of the early ones.

Everyone seems to have found the new Membership Benefits section, and we are getting a large number of orders for manuals. The ordering is going smoothly, except for EDIF manuals, which have been very difficult to obtain. And of course, conference proceedings will not be available until after the conference date. Thank you for your patience. In contrast to the response for the manuals, there has been a slow response to our membership survey. We have had less than 50 responses. This is out of a membership of over 3000. I hope the tide will turn on this so we can get some meaningful data (for our email directory, etc.).

We are fortunate to have two very good articles in this edition; one on CAD Tool Interchangeability by Steve Meyer, and one on ECAD Data Integration by G. Kaufman. Both focus on CAE/CAD database and tool integration issues (areas I like to call enabling technology). Good enabling technology allows the DA user to mix and match diverse tools for

## Vice Chmn & IEEE DATC Nwsltr Coord

Bryan T. Preas CADLAB Bahnhofstrasse 32 4790 Paderborn, West Germany 011 49 52 51 28 41 02 main 011 49 52 51 60 20 67 secy preas.@cadlab.cadlab.de preas%cadlab.uucp@seismo.css.gov

their special individual attributes. Mr. Meyer takes the somewhat controversial stand that netlist translators running under the basic Unix operating system may be a sufficient framework for integration. Mr. Kaufman suggests a database approach (ultimately object oriented) for linking diverse DA applications. Of course, equal time will be given to any CFI advocate who wishes to comment.

If you have an opinion or article, send it in to the *Newsletter*. And please, send in your survey forms. **THANK YOU.**

Patrick M. Hefferan - SIGDA Editor 1681 Princeton Ave. St. Paul, MN 55105 (612) 690-5451 hefferan@frith.entmoot.cs.psu.edu 76350.54@compuserve.com

1

# LETTER FROM THE CHAIR

Activities are picking up in preparation for the 27th DAC in Orlando. You won't want to miss it! If you aren't convinced already that you need to go, you will be after you've read this issue of the Newsletter!

SIGDA starts out right on opening day. Our ANNUAL MEETING is SUNDAY, June 24, from 7 to 9 p.m., in Room 6 of the Convention Center. The usual beverages and groaning table of finger food will take care of any rumbles in the tummy. The reports of our many activities, and the chance to discuss them and provide your directors with input and authorization to continue, should make this another interesting, stimulating meeting. Come and give your support.

In the meeting, we'll have reports on the first EDAC European Conference, which a number of your officers and directors attended and met with their counterparts in Europe. I -want to congratulate Gordon Adshead, General Chair of EDAC in Glasgow this year on a stellar conference. Hopefully he'll attend our Sunday night session - he misses very few SIGDA events and we can give him our congratulations in person.

While you tour the exhibit floor at DAC, make it a special point to stop by the SIGDA University Booth. Martin Wong has a much expanded and even more dynamic version of Mary Jane Irwin's booth from last year. The enthusiasm and skill of these University students, as they demo their software, should make you feel that our profession will be in good hands in the coming years.

The landmark CD-ROM project will share the University Booth. See what you'll be able to do in literature search when your SIGDA project is completed - the whole world's literature on Design Automation literally at your finger tips, with easyto-use software to help you find the references you really need. Bryan and Kathy Preas are driving the field of literature retrieval!

Our candidates for High School Scholarships will be at DAC, with their mentors. You'll get a chance to meet them Sunday night. Take time during the week to talk with them. See what a great program Charlotte Acken and Regina Pistilli have going it'll make you proud that your SIGDA is doing such good things. Help us honor Regina, as she leaves us to go for her PhD, and welcome Donna Couch in her place.

The awards and scholarships will be announced and presented. We hope you'll agree with the selection committee that these are richly deserved.

I'll conclude with a Chairman's constant plea -GET ACTIVE in SIGDA if you aren't already. We have a rich variety of projects, and an open mind toward ideas for new ones. Dynamic organizations need infusions of ideas, talent and energy. The excitement you see around you in SIGDA's activities at DAC this year should inspire you to want to join in yourself!

SEE YOU AT DAC!

Charles A. Shaw SIGDA Chairman

# SIGDA ADVISORY BOARD MEETING MINUTES

The SIGDA Advisory Board held its meeting on Saturday, January 20, 1990, at the Hyatt Regency at the Dallas-Fort Worth airport. The meeting was called to order by SIGDA Chairman, Chuck Shaw at 9:30 a.m. In attendance were Charlotte Acken, Jim Cohoon, Pat Hefferan, Mary Jane Irwin, Hersch Loomis, Mike Lorenzetti, Bryan Preas, Dick Smith, Ron Waxman and Paul Weil.

Shaw presented the agenda, which was approved. Those agenda items appear as boldface headers in these minutes.

#### A. Approval of Minutes

Minutes from the November 4 Board Meeting were distributed by SIGDA Secretary/Treasurer, Mike Lorenzetti. There were no amendments (the minutes had been distributed earlier via email and Board comments and corrections incorporated).

*MOTION:* The minutes be approved as presented. (*Preas, Weil, unanimous*)

The minutes will be printed in the next issue of the Newsletter (vol 20, no. 1, February 1990).

#### B. Budget

Mike Lorenzetti reported that the FY '91 budget (which covers July 1990 to June 30, 1991) has been submitted. In addition to distributing copies to the Board members, he presented a summary in terms of expenses which recur annually versus those which are one time expenditures. These are summarized in the following tables:

SIGDA Recurring Expenses:

| Travel Grant               | 125,000 |

|----------------------------|---------|

| Officer/Board Travel       | 40,000  |

| Secretarial                | 10,000  |

| Newsletter Help            | 10,000  |

| Office & Printing overhead | 21,400  |

| Mailing                    | 8,000   |

| SIG Discretionary Fund     | 200,000 |

| HQ Allocation              | 10,000  |

| Undergraduate Scholarships | 60,000  |

| Conference Capital Equip   | 30,000  |

| Textbooks             |         |

|-----------------------|---------|

| Graduate Scholarships | 120,000 |

| Library Grants        |         |

| Benchmarks            |         |

| Other Misc. Expenses  |         |

| University Booth      |         |

| TOTAL                 |         |

SIGDA Non-Recurring Expenses

| Communications          |         |

|-------------------------|---------|

| Promotion & Advertising |         |

| Local Support           |         |

| CD-ROM                  |         |

| Video Tape Production   | 100,000 |

| TOTAL                   | 490,000 |

The important point is that due to recent increases in SIGDA Board activity levels, the recurring expenses now total slightly in excess of our annual revenues. Given our current reserves (approximately \$1,500,000) this is not cause for alarm, but indicates we are finally applying our reserves to meaningful ways to further the DA profession.

#### C. Member Address List

Pat Hefferan has a complete address, phone, FAX and email list for the Board, which he updates and publishes on the inside front cover of the Newsletter. The question was raised whether we should expand this listing service to include all members. It was pointed out that mailing labels for members are available from ACM Headquarters, should we need to reach the membership by direct mailing. After some discussion, including concerns about privacy and whether members want us to do this, the issue was tabled without action.

#### D. Newsletter

Hefferan reported on the success of the coupon program, wherein SIGDA members could mail in coupons printed in the Newsletter, along with a \$5 fee and receive

copies of the VHDL and EDIF manuals (with SIGDA picking up the balance of the cost). To date, he has received over 60 responses, mostly for the VHDL manual. The next Newsletter (vol. 20 no. 1) goes to press in 2 weeks. Hefferan asked whether we should reprint coupons.

*MOTION:* Reprint coupons for EDIF and VHDL manuals in the next Newsletter issue and continue offer. (*Preas, Weil, unanimous*)

Should we expand the program to include Proceedings such as DAC or ICCAD? Jim Cohoon checked with ACM about this previously. There is no problem with Proceedings discounts (we buy from ACM at the regular price). Coupons could be an alternative to the two classes of membership proposed by Cohoon at the November Board Meeting. One problem is estimating the number of extra Proceedings to print and passing this information on to DAC in a timely manner. For DAC and ICCAD we need to ask our members in advance so we can give projections to ACM and IEEE and they can adjust the number of copies they print. DAC needs to know by mid-March. Jim Cohoon volunteered to check prices with Fred Aaronson of ACM.

MOTION: SIGDA Newsletter print coupons which allow members to order DAC and ICCAD Proceedings for coming year (1990) at a cost of \$5 per Proceedings. (Hefferan, Lorenzetti, unanimous)

*MOTION:* SIGDA Newsletter print coupons which allow members to order 25-Years of Electronic Design Automation for \$5 per copy. (*Preas, Cohoon, unanimous*)

Hefferan requested more articles for the Newsletter. The Newsletter seems to be a good place to print system overview articles. Such articles are of high interest to the members and are often rejected by conferences and journals as not theoretical enough. Currently, EDIF, VHDL and CFI all submit minutes and reports to our Newsletter. The idea of publishing the tables of contents of CAD-related journals and magazines was suggested. After some discussion it was agreed that this was a good idea and we should restart it.

MOTION: Include the SIGDA Newsletter in the European Design Automation Conference (EDAC) handouts. (Weil, Hefferan, 10,1,0)

#### E. Email System

Mary Jane Irwin announced that the 800 number was installed in mid-December and Board members may now dial into one of the SIGDA University Booth machines to read news and mail. A 2400 baud modem is required and details on how to log in and use the system were distributed. This service will be down during DAC or whenever they use the machine for demos off site (usually only one other show). Announcements will be made in advance of these downtimes.

The costs for this service were \$340 for installation and \$45 per month plus a per-call charge for the phone line. The \$1000 per year budget should be adequate.

The question of whether we should open this service to all SIGDA members was raised. Disk cost could be a problem. Also, it could end up being used for more than DA and SIGDA purposes. There was general agreement not to pursue it at this time.

The question was raised whether we can we link in the Asian representative to this system. This led into a discussion of Asian representation in general. It was pointed out that although Akihiro Yamada is an excellent contact and а hard worker. his responsibilities do not always allow him time to attend SIGDA meetings and perform other volunteer functions. Should we pursue a replacement? Ron Waxman volunteered to contact Yamada regarding both issues. He also agreed to contact Richard Newton about suggesting an Asian representative.

On the subject of Asian activities, it was suggested that we fund translation of the VHDL manual to Japanese. Hefferan reported that translation of technical material costs approximately \$100/page. It was pointed out during the discussion that perhaps Japanese professional societies or DATC should pay for this. However, UHDL is a competing Japanese language so Japanese societies may not be interested. Also, if we do this for Japanese, what about German, French and all the others. The suggestion was tabled without action.

#### F. CD-ROM

Bryan Preas distributed a report from the contractor which included sample screens, and a description of the capabilities. Three contractors are working on the design:

| Data Capture       | Saztec     |

|--------------------|------------|

| Service Bureau     | Reference  |

|                    | Technology |

| Retrieval Software | Knowledge  |

|                    | Set        |

Contractors are yet to be determined for documentation, packaging and CD pressing. They are working on a prototype consisting of the 26th DAC Proceedings. Evaluators should have ROM's in March. Cooperation from societies has been good. Both ACM and IEEE-CS press are excited about it and are planning a large publicity campaign. Our cost is approximately \$11 per page. Adding the Proceedings of the International Test Conference is currently being discussed. There will be six CD-ROMs total (instead of two or three, as originally estimated). All the DAC Proceedings will fit on three ROMs. ICCAD and Transactions on CAD will each be on one ROM.

Preas summarized the approximate costs as follows:

| Design Phase      | 30,000  |

|-------------------|---------|

| Prototype         | 35,000  |

| Production        | 305,000 |

| Press 1100 copies | 15,000  |

| Documentation     | 20,000  |

Administration......97,000

TOTAL ...... 502,000

This works out to about \$11/page, including mark-up, keying in the papers (twice) and QA of the results.

The question of whether the SIGDA Newsletter should be added was raised. Although it is not a reviewed publication like the others, it has much useful information and it is our own publication.

*MOTION:* Establish a budget of \$25,000 for inclusion of the SIGDA Newsletter in the CD-ROM project. (*Weil, Loomis, unanimous*)

The software will run on MAC, PC, some Unix machines. It will require lots of memory and a CD-ROM reader (which cost about \$700-800). Users will be able to order the ROMs from ACM and IEEE. Unit costs will be \$70 for license fee plus (approximately) \$150 for overhead, advertising and profit (this is currently being negotiated). Preas will report in the future on costs to members.

Kathy Preas is administrating the project. She has been paid roughly \$2,000 total so far.

MOTION: SIGDA pay Kathy Preas's expenses to attend future SIGDA Board Meetings to report on the status of the Project. (Loomis, Weil, unanimous)

#### G. DAC Management Contract Status

Dick Smith reported on contract status. The process has been much more prolonged than anticipated, despite great efforts by Dan Schweikert and Smith himself. The final draft has been approved by legal counsel on both sides. It has been sent to ACM and IEEE-CS. The contract covers three years (92, 93 and 94). Subsequent contracts will be put to competitive bid.

#### H. University Booth 1990

Mary Jane Irwin reported on the University Booth for DAC. SIGDA has paid for space and a schedule is being formulated. Professor Martin Wong of The University of Texas is the contact person. He is sending out direct mail invitations to faculty and students who have published at DAC and ICCAD during the last two years. A demonstration of the CD-ROM will be included in the University Booth, if available.

#### I. University Booth 1991

Jim Cohoon will organize the University Booth for the 1991 DAC. There is nothing to report at this time.

•

#### J. High School Scholarship

Charlotte Acken reported that she has been meeting with MESA and High School counselors from the San Francisco area to set up the 1990 program.

The final selections for the 1989 program are about to be made. Mentors are reviewing the progress of their students. They also use the visit to the high school to talk to classes about DA careers. The Mentors will meet in the middle of February for final selection.

The question of how to disburse the money was raised. The winners are awarded \$4000 per year. Should we work through financial department of the school? Since rules vary for different schools it was decided that this should be left up to the Mentors.

Charlotte is looking for Mentors between now and May. She feels it is important to match minorities of Mentor and student. It was suggested that she recruit a pool of Mentors and make selections once the students are chosen.

Charlotte reported that Regina Pistilli is going back to school this fall and may not be able to continue. We may be able to hire MPA staff to replace her, however, staff local to Bay Area may be better. Can MESA do it for a fee? The approximate salary range is \$20 per hour (administrative assistant). The decision was left up to Charlotte.

Charlotte suggested a token of appreciation for Regina. A plaque combined with a small cash award would be appropriate.

*MOTION:* SIGDA award \$500 plus a plaque to Regina Pistilli for her tremendous work on behalf of the High School Scholarship program. (*Loomis, Lorenzetti, unanimous*)

Charlotte volunteered to make the arrangements for the award.

#### K. Graduate Scholarships

Herschel Loomis reported that at the 1989 Design Automation Conference three new scholarships at \$10,000 each, were awarded along with three renewals at \$7000 each. This year there will be ten scholarships total (new and renewal), at \$12,000 each. The Graduate Scholarship Committee consists of Loomis, Shaw, and Radke. Publicity is done by direct mail to ACM student branches, IEEE student branches, SIGDA members and DATC members. Loomis showed a sample of the flier he will mail. It was suggested that he add the list of university people who submitted papers to DAC and ICCAD which is used for University Booth announcements.

The idea of expanding the program further was raised, however, it was pointed out that \$120,000 is a large portion of the budget already. It was agreed that we should leave it as is for now and that library grants can continue to be used as consolation prizes. It was suggested that Loomis send reminders to recipients for Newsletter articles describing their programs.

#### L. Petty Cash Fund

Lorenzetti announced that a SIGDA checking account has been opened for petty cash expenses. The maximum amount in the account is \$10,000. He requested that Board members limit requests to \$5000 and send larger bills to ACM as before.

#### M. Video Tape Plans

Mary Jane Irwin distributed a letter from University Video Communications (UVC) which included a proposal for SIGDA support of CAD video tape production. At Irwin's request, UVC interviewed a list of industry and academic experts in the CAD community regarding the need for CAD related videos. As a result of these interviews, UVC proposed the production of two tapes:

- (1) Introduction to CAD, geared to sophomore/junior university curricula,

- (2) First in a series of in-depth CAD tutorials, geared to the professional community, university and graduate students.

Some of the research and speaker fees contain variable amounts, but the total budget is not to exceed \$96,000. Discussion centered around whether this is in keeping with our goals and a good use of our funds. Should we include a VHDL tutorial? This could also be good for educating management and non-technical people on the importance of CAD. An introduction tape that grabs the interest of a CEO would help the profession. One of the concerns of the Electronic Design Automation Companies (EDAC) is the perception of the industry. Perhaps they are willing to be partners in this project. Smith volunteered to contact EDAC to assess their interest. Tutorials from DAC could be taped at a separate site. Slides of a selected tutorial could be reformatted for video and the filming done at a site with a studio. This sort of project must be done a short time after DAC while the information from the tutorial is still fresh and interest of the speaker is high.

*MOTION:* SIGDA fund one introductory tape targeted at management personnel who are not familiar with CAD. (*Preas, Smith, 10, 1, 0*)

Discussion then turned to a tutorial tape. It was pointed out by Ron Waxman that DATC may be pursuing this in the near future. The

issue was tabled until next meeting. Charlotte Acken volunteered to pursue the matter further and make a proposal at the next meeting.

#### N. SIG Discretionary Fund

Lorenzetti reviewed the ACM SIG Discretionary fund, to which ACM's 30 SIGs donate funds used to support ACM-wide He announced that our interests. contribution is worded the same as last year: "Subject to an absolute ceiling of \$200,000, SIGDA will contribute an amount equal to the higher of the following two numbers: the largest contribution of any other single SIG or half the contribution of all the other SIGs combined." This is only a one-year commitment and can be changed for FY'92. Lorenzetti asked for guidelines from the Board in representing SIGDA at the meeting disbursements to decide for the Discretionary Fund in February. The consensus of the Board was that service directly to members of ACM is a higher. priority than to the profession as a whole.

#### O. CSC Meetings

Lorenzetti, who will be representing SIGDA at the SIG Board and Conference Board meetings at ACM, asked for input on any other issues regarding DAC which are expected to come up. Smith and Shaw reported that no such issues exist in light of recent progress on the DAC management contract.

#### P. University Booth Equipment Purchase

Cohoon brought up the idea of equipment grants to. He reported that we can get a better discount in bulk purchases than in giving individual awards. However, individual faculty members can do better in negotiating matching funds if the grants are cash and we should not endorse a single workstation with these awards. Time is now short for this new project so we should not start until the '91 conference. Cohoon will assemble a detailed proposal, including a committee to administer the awards, and bring it to the

Board. One aspect that needs to be addressed in that proposal is the criteria for the awards (need vs. merit).

#### Q. SIGDA at EDAC

Preas reported on plans for publicizing SIGDA at the upcoming European Design Automation Conference (EDAC). He plans to distribute the following material: overview of ACM (material from ACM headquarters), brochures and membership forms. He will make a presentation giving an overview of SIGDA projects at one of the evening sessions.

#### R. Brochure

Shaw reported for Chuck Radke on the preparation of a SIGDA brochure. He distributed sample brochures to the Board and invited comments/corrections. Preas reminded the group that he needs printed brochures for the March 11 presentation at EDAC.

#### S. Travel Grants

Cohoon reported that he is currently spending his entire budget. \$104,000 has already been expended for this year. Cohoon reviews airfares and per diem charges to insure they are reasonable. It was suggested that he hire a travel agent to help shop for the best airfares. However, this was left to his discretion, as is the monitoring of proposals and funds.

#### T. Proceedings Copies Response

See item D above.

#### U. Modern Journal (Video) Proposal

Preas discussed his idea for a "Video Journal" which features filmed presentations on VCR tape or CD-ROM rather than printed papers. It should have a shorter lead-time than current journals and would be a modern medium not previously utilized for this purpose. The rejection rate at DAC and ICCAD is very high, and there is room for other means of "publishing" good work. Furthermore, system overview papers are no longer published because they are rejected in favor of algorithm papers and this could be an outlet for such papers. The Board agreed that it is an interesting idea that we should keep in mind for later action. It was felt that we should evaluate the response to the Video Tape project (see item M above) before proceeding with this one.

#### V. Future Meeting Plans

Shaw announced that the General Membership Meeting at DAC will be held Sunday night after the close of the technical presentations in the convention center. There will be a Saturday morning Board Meeting at DAC as well. Informal Board discussion will take place Friday night in one of the hotel suites.

Shaw opened a discussion on whether we need to hold another Board Meeting prior to DAC. Weil proposed that we hold one at EDAC. This could help establish our image as international organization and open doors to more European cooperation. He pointed out that the cost is low for a one-week stay in Glasgow. There is a conflict with the Technical Program Meeting for the MCNC workshop on Layout Synthesis which involves two Board members (Cohoon and Lorenzetti). The discussion was tabled while one of the Board members called to check airfares.

#### W. Textbook Report

Since Waldo Magnuson was not able to attend the meeting, the report on textbooks was postponed until next meeting.

#### X. DATC Report

DATC chair, Ron Waxman, brought us up to date on DATC activities. They are holding an Executive Committee meeting January 24 at Scottsdale, Arizona. They are looking for ways to increase circulation of Design & Test Magazine. They plan to increase the number of pages that DATC Newsletter purchases from D&T.

IEEE-CS now has 106,000 members, 34% of IEEE members are CS members.

Waxman distributed copies of the February issue of the DATC Newsletter which summarizes DATC activities. A VHDL video tutorial is in the planning stages and we may wish to make this a cooperative effort with SIGDA (see item M above). The VHDL users group, sponsored by DATC, has agreed to an experiment to plan their 1990 activities as an entity of the Computer Society. DATC is working with DASS to set up a DASS meeting on VHDL maintenance by way of international teleconference between US and France.

For more information on DATC activities, see the DATC Newsletter in the February issue of Design & Test Magazine.

#### Y. Outstanding Member Recognition

Shaw reported for Chuck Radke that Board members should send nominations for this year's award directly to Radke.

#### Z. Benchmarks

Lorenzetti reported that the benchmark distribution program is continuing well within budget. Requests to MCNC for benchmarks occur at a rate of 8-10 per month, with higher rates around the time of workshops.

It was pointed out that Hal Carter is putting together a repository of VHDL benchmarks and we may want to investigate merging those into the SIGDA set.

#### a. Letter of Commendation from ACM

Shaw distributed copies of a letter he received from Jack Esbin, Treasurer of ACM, commending SIGDA on the scope and depth of our programs. He commended both the Executive Committee and advisory Board "for the effort and concern placed on constructive use of your resources to benefit others."

#### b. Workshops

Paul Weil reported a dramatic increase in requests for SIGDA sponsored workshops. He receives about two requests per month and has turned down only three of them. Two could not produce a two-page proposal and were turned down for that reason. Another was not well organized enough to be successful.

Workshops we will be sponsoring in the near future include:

- \* The High Level Synthesis Workshop in Germany (March 3-6, 1991),

- \* A Workshop on Timing Issues in British Columbia (August 1990), and

- \* Formal Methods in VLSI Design organized by Subrahmanyan of AT&T

A workshop on Solid Modeling is being organized by Joshua Turner of Rensselaer and has requested SIGDA co-sponsorship (along with SIGGRAPH). Weil asked if we should pursue this since all our other activities focus on Electronic Design Automation. How many SIGDA members would attend this workshop? After some discussion it was decided to refer them elsewhere (to a mechanical engineering society).

Weil reported that the workshop on Logic Level Modeling had lower than expected attendance, but broke even financially.

Weil asked the Board whether we will be holding a Physical Design Workshop this year. Preas informed him that there may not be one this year because the MCNC workshop on Layout Synthesis (for which we have "in cooperation with" status) is covering physical design this year.

There was a discussion of what happens when workshops are co-sponsored. Division of services between ACM and the other society are negotiated on a per-workshop

9

basis. ACM usually handles registration and other bureaucratic details. This is very helpful to volunteers who organize workshops and are not familiar with organizing such activities.

Weil asked for extra Newsletters to give to workshop organizers for distributions. Hefferan agreed to request 200 extra copies per issue. He also requested two gross of SIGDA brochures, when they become available.

#### c. Bylaws

Lorenzetti reported that the bylaw changes have been sent to ACM for approval and we are awaiting their response.

#### d. Bulletin Board

Smith reported that comp.lsi.cad works well as a bulletin Board medium, but is not heavily used. He asked for ideas on how we can publicize it further. Do our members have access to the network? Smith suggested that we run a survey in the Newsletter to determine who has access. The same survey can ask for email addresses and other information to help us determine the needs of our constituents. Hefferan suggested that we offer some prize or some other inducement to encourage return of the survey, such as a pocket electronic diary. We could either send a small award (such as a SIGDA pen) to all respondents or have a drawing among those who return it for a larger award.

*MOTION:* SIGDA Newsletter publish a survey with a prize awarded by drawing among those who participate. The prize is to be determined at the Newsletter Editor's discretion, but should not exceed a cost of \$500. (Loomis, Smith unanimous)

#### e. Publicity

John Acken has ordered pencils with "SIGDA" printed on them to be distributed at workshops and conferences sponsored by us.

#### f. ACM Regional Representative Candidates

Shaw reminded the Board that, although the ACM council has been reorganized to give more seats to SIGs and less to regions, it is a phased transition and the Nominating Committee is looking for nominations. To place a name in nomination requires a petition signed by some percentage of ACM members. For the North Central Region, 47 signatures are required. For the Pacific, 91 are needed. He asked if SIGDA should consider nominating someone to these posts. No action was taken on this issue.

#### g. New Projects, Suggestions

Cohoon suggested pursuing production of a tutorial or interactive paper. Such a system would run on a PC, or on an X-based system, and allow the user to walk through the information, skipping over parts he was not interested in and viewing very detailed information for parts of high interest. Computer-aided instruction tools currently exist to do this. The CMU Tutor is such a system, another is available from a firm in Minnesota. These systems come with an authoring system.

MOTION: Budget \$5,000 to look into computer-aided instruction kits as a means for publishing CAD papers or tutorials. The money is to be used to get copy of the necessary software. (Waxman, Preas, unanimous)

Preas encouraged project leaders to write a one-two page article at least once per year describing their activities. Smith added that these should also be posted to news.

Lorenzetti requested that money be allocated to allow the Secretary/Treasurer to purchase a portable computer for taking minutes at these meetings, keeping electronic copies of bylaws and other SIGDA functions.

*MOTION:* Budget up to \$5,000 for purchase of a portable computer for use by the SIGDA

Secretary/Treasurer. (Weil, Hefferan, unanimous)

#### h. Next Meeting of the Advisory Board

It was reported that a seven day stay in Glasgow is needed to reduce airfare from \$1400 to \$600. SIGDA could pay for the flight and three nights lodging. A strong presence at EDAC would help to solidify our European ties. ACM is unknown in Europe and we need to make a splash. An information booth at EDAC would help. We could have an Advisory Board Meeting there on Sunday before the conference or just send a subcommittee and hold the meeting at a later date in the US.

*MOTION:* SIGDA send subcommittee (appointed by the Chairman) to EDAC, and hold the Advisory Board Meeting at a later date in the US. (*Lorenzetti, Smith, 10-one-0*)

MOTION: To adjourn. (Cohoon, Loomis, unanimous)

Respectfully submitted,

Michael J. Lorenzetti SIGDA Secretary/Treasurer After the meeting adjourned, it was suggested that a budget of \$5,000 be established to purchase a portable computer for the Newsletter Editor. All present (Shaw, Weil, Waxman, Acken, Hefferan, Loomis, Lorenzetti) agreed.

÷ 1.

11

## MEMBERSHIP BENEFITS

As a special benefit to SIGDA members, certain standards manuals, proceedings, and other documents of general interest will be made available at a nominal rate. Availability of the documents may vary, so allow several weeks for delivery. Proceedings will only be issued after the conference sales have been satisfied. *You must be a member of SIGDA to quality.*

| Name                                                |                                    |

|-----------------------------------------------------|------------------------------------|

| Address                                             |                                    |

|                                                     | Parabia Number                     |

|                                                     | bership Number                     |

| SELECT                                              | TIONS (please check box(es))       |

| 🚛 🕹 (ang) - ang | 0.0 Standards Manual               |

|                                                     | anguage Reference Manual           |

| 25 rea                                              | rs of Electronic Design Automation |

| 🛶 🖌 de de de de de de de la de de la receber        | AC Proceedings                     |

Please send coupon to: Patrick M. Hefferan 1681 Princeton Avenue St. Paul, MN 55105 ŝ

## SIGDA MEMBERSHIP SURVEY

In order to better serve the SIGDA membership, we are taking a survey of your wants and needs. Please take a few minutes to fill out the survey form on the next page and send it in. It has a preprinted address on the back, so just cut it out and fold it up with the address facing outward. Then tape (please do not staple) it shut and mail it in. You will need to provide 25 cents postage, as we cannot use our bulk mailing permit for this.

To make this more interesting and provide an incentive to get the surveys filled out, those who participate will be eligible for a drawing for a portable, electronic address book. We want to hear from you - so take a few minutes and fill it out. THANK YOU!!

PLEASE FILL OUT AND SEND IN ----->

THE WINNER OF THE ELECTRONIC ADDRESS BOOK THIS QUARTER IS <u>DAVID J. ELLIS</u> FROM LONDONDERRY, NEW MEXICO!! THERE WILL BE ANOTHER WINNER ANNOUNCED IN THE NEXT SIGDA NEWSLETTER.

#### SIGDA SURVEY January, 1990

#### This is a general membership survey. Participants will be entered in a drawing for an electronic address book.

| Name                                         | EMAIL Address                                        |                                                      |

|----------------------------------------------|------------------------------------------------------|------------------------------------------------------|

|                                              | (May we publish this address?                        | )                                                    |

| Address                                      | _ Company                                            |                                                      |

|                                              | Occupation                                           |                                                      |

|                                              | Job Function                                         |                                                      |

| Phone - Home                                 |                                                      |                                                      |

| Work                                         | (Highest attained)                                   |                                                      |

| (Signature)                                  |                                                      |                                                      |

| How long have you worked as a DA professi    | onal?                                                |                                                      |

| Computers used in work                       |                                                      |                                                      |

| Do you have a PC at home?                    | If yes, what kind                                    |                                                      |

| Do you have a modem? At                      | home? At work? Speed?                                |                                                      |

| Are you connected to a network (Arpa, CIC,   | INTERNET?)                                           |                                                      |

| In what professional societies are you a men | nber?                                                | ;                                                    |

|                                              |                                                      | · ·                                                  |

| What CAD/CAE functions are you responsib     | le for?                                              |                                                      |

|                                              | Simulation Layout                                    |                                                      |

| DRC                                          | Test Management                                      |                                                      |

| Design                                       | SpecificationEvaluation                              |                                                      |

| Mechanical                                   | Other                                                |                                                      |

| What additional benefits would you like from |                                                      |                                                      |

| DAC Proceedings                              | DAC/ICCAD Admissions                                 |                                                      |

| ICCAD Proceedings<br>Standards Manuals       | Network Access for EMAIL/BBS<br>Continuing Education |                                                      |

| Tutorial Tapes                               | Other                                                |                                                      |

| CD-ROM Tapes                                 |                                                      | ang kadé pina kadé kadé kadé kadé kadé kadé kadé kad |

| Would you pay extra for them?                | YesNo                                                |                                                      |

| The SIGDA High School Student Mentor Pr      | ogram is designed to increase under-represented grou | ups in the D                                         |

The SIGDA High School Student Mentor Program is designed to increase under-represented groups in the DA profession. The target groups for this program are: Hispanic, Black, Women (all races), Disabled, and American Indian. We are requesting that the Mentors be from the target groups. Also, for administrative purposes, the Mentors must be from the San Francisco Bay Area. For further details, contact Charlotte Acken (address on front cover).

Would you like to be a Mentor? \_\_\_\_\_Yes \_\_\_\_No

Of which target group are you a member?\_\_\_\_\_

put 25 cent stamp here

SIGDA Membership Survey c/o Patrick M. Hefferan 1681 Princeton Avenue Saint Paul, Minnesota 55105

## LETTERS TO SIGDA

#### UNIVERSITY OF VIRGINIA CHARLOTTESVILLE

OFFICE OF THE PRESIDENT

March 5, 1990

Mr. Charles A. Shaw Cadence Design Systems, Inc. 2455 Augustine Drive Santa Clara, California 95054-3082

Dear Mr. Shaw:

It was a pleasure to learn of SIGDA's recent grant to the University of Virginia for computer hardware to be used at the Design Automation Conference next year in San Francisco. Our computer scientists find this support deeply gratifying indeed.

The University must rely increasingly on private support to meet many of its special funding needs. The workstations and associated equipment which you will make available to us both before and after the conference will be of great assistance to our researchers as they develop innovative software packages. We are exceedingly appreciative of SIGDA's continued generosity, and we hope that our information processing program continues to merit your confidence.

Very sincerely,

elector point

Robert M. O'Neil President

RMO:slb

MADISON HALL BOX 9011 22906-9011 TELEPHONE 804-924-3337

SIGDA Newsletter, vol 20, number 1

÷ 1.

## LETTERS TO SIGDA (continued)

the society for computing and information processing

March 20, 1990

Ron Oliver (SIG Board Chair) Dept. of CS CAL POLY San Louis Obispo, CA 93407

Stewart Zweben (Chairman, Constitutions & Bylaws Committee) Dept. of Computer & Information Science Ohio State University 2036 Neil Avenue Mall Columbus, OH 43210

#### Dear Sirs:

Enclosed for your approval are proposed changes to the SIGDA Bylaws. I have included both a new draft and an annotated copy of the current bylaws, so you can see where the changes were made. The changes were precipitated by the recent changes to ACM Bylaw 7. The SIGDA Advisory Board has elected to make some additional (minor) changes during the revision process. Namely:

- A more precise formalization for the approval of large expenditures (Article 5.b.iii),

- Increase the suggested size of the Advisory Board to better fit our current operating mode and the magnitude of our ongoing projects (Article 8a). It was also felt that "Board of Directors" was a misnomer for the members-at-large and it was deleted.

- Change the suggested location of the annual membership meeting to the Design Automation Conference, in keeping with current SIGDA practice.

- Minor changes as suggested by Stu Zweben of the Constitutions and Bylaws (a copy of his suggestions is attached)

These changes have been approved by the SIGDA Advisory Board at their March 12th meeting.

Sincerely,

Michael J. Lorenzetti SIGDA Secretary/Treasurer

MJL/myd

Fred Aaronson, (Manager, SIG Activities)

Pat Hefferan, (SIGDA newsletter editor)

Bryan Preas, (SIGDA vice-chairman)

Charles Shaw, (SIGDA chairman)

#### Enclosures

÷ (\*

## ACM Press Database and Electronic Products

A Publication Series of the Association for Computing Machinery • 11 West 42nd St., NY, NY 10036, TELEX 421686 ACM HQ Liason, Bernard Rous, Assoc. Dir. of Pub., 212/869-7440, FAX 212/944-1318, rous-cr@acmvm.bitnet Editor-in-Chief, Edward A. Fox, Dept. of Computer Science, VPI&SU, Blacksburg VA 24061-0106, 703/231-5113 Internet: fox@vtopus.cs.vt.edu, BITNET: foxea@vtcc1, FAX 703/231-7826

Hypertext Editor, Gary Marchionini, 4121C Hornbake, CLIS, Univ. Maryland, College Park MD 20742, 301/454-3235 Multimedia Editor, Scott M. Stevens, Software Eng. Inst., Carnegie-Mellon Univ., Pittsburgh PA 15213, 412/268-7700

## Memorandum

To: All SIG Chairs and SIG Newsletter Editors Date: December 20, 1989 Subject: ACM CSC Meeting, Tuesday 10-12, about Electronic Submissions (tentatively, in Arlington Room at the Sheraton Washington Hotel) From: Edward A. Fox, Editor ACM Press Database and Electronic Products

You are invited to a meeting to hear about and help with planning for ACM allowing electronic submissions of documents sent in for publication. This topic is especially important as we move toward making articles available for hypertext browsing or computer-aided searching. It can also help with re-use of articles, which might be prepared for a conference, reprinted in a Transaction, and also later included in an ACM Press Books manuscript.

This topic relates to SIG methods for: accepting submissions to newsletters, handling of accepted papers for conference proceedings, and possibly also to receiving and distributing notes for tutorials. Therefore we ask that you and/or others in your SIG attend this session if at all possible.

The meeting will include presentations on national and international standards for document markup, discussion of difficult problems dealing with graphics and compatibility between various formatters and WYSIWYG editors, and issues relating to media or network transmission. We hope that you also will consider helping us involve volunteers so that authors and editors can have versatile tools to make electronic submission and subsequent processing be feasible and perhaps even somewhat convenient.

My current suggestion is that we have volunteers prepare "Author Kits" so that someone using troff or LaTex or GML Script or Microsoft Word, etc. will be able to follow a set of guidelines, using some set of macros or electronic style sheets that we provide. Then they can work in their own environment and yet allow us to map their article into the "ACM Internal Document Standard Form" which I believe should be based on SGML (Standard Generalized Markup Language -- ISO 8879-1986) and its application in ANSI/NISO Z39.59-1988, the American National Standard for Electronic Manuscript Preparation and Markup. Meanwhile, I look forward to alternative or additional suggestions, and to discussing realistic plans with you in February!

\* 2/20/90

## DEPARTMENTS

The following pages contain updates and information about various projects and activities funded by the SIGDA. Contact information (email, phone, and addresses) for the individuals directing the programs is available from the front inside cover.

## European Activities ..... H. Gordon Adshead

FROM: Gordon Adshead

SUBJECT: EDAC '90

EDAC '90 is apparently being enthusiastically received. The EDAC committee currently plans EDAC91 on February 25-28 in Amsterdam and EDAC92 in February/March in Brussels. We plan to promote a good series of high quality technical forums for the DA community moving steadily around Europe. As such we respectfully request the support and involvement of DATC, SIGDA, and the DAC Committee.

.

1

An IFIP 10.5 group headed by Gerry Musgrave has some interesting suggestions to extend the scope, size, time and place of a possible "Mega-event" in 1992. Some of the ideas and suggestions make good sense and some seem not. I would like to stress that at this point in time there is unfortunately no agreed position of the European DA Community and most of the EDAC committee demand a lot more discussion.

The current plan is to meet constructively at EDAC in Glasgow on Wednesday, March 14, agree on a policy and get an advance EDAC '92 committee moving.

I look forward to a healthy co-operation between DAC and EDAC and welcome your comments.

DATE: April 2, 1990

FROM: Gordon Adshead

SUBJECT: EDAC - DAC

It was very good to see SIGDA in force at EDAC in Glasgow. Many of us felt that we have at last achieved the basis of a good technical, relevant DA event in Europe - 450 paying attendees and 520 people involved totally!

EDAC '91 will be in Amsterdam in February, and we are pleased to have the cooperation of DATC and SIGDA! GREAT!!

The real problem is EDAC '92. Everybody has ideas. Everybody wants a piece of the action. There was a lot of misunderstanding created when TEN of YOU (our friends from the U.S.) turned up at a meeting in Glasgow and gave some of us the impression that the U.S. DAC Committee was in some sense trying to exert influence or even take over EDAC. I know this is not the case, but the real problem is that there are still

some European views to be reconciled before we are clear on exactly what sort of help and involvement we would like from the U.S. DAC.

I cannot, of course, speak for "Europe" - this is impossible.

However, I would like to make it absolutely clear what the position of the EDAC Association is regarding EDAC '92:

- 1. Significant high quality technical international DA event.

- 2. Held in Europe but fitting the world context.

- 3. Best possible harmonious relationship with the U.S. DAC.

- 4. Target March 1992 in Brussels or Paris.

- 5. 1,000 to 1,500 attendees.

- 6. Significant exhibition with 100 vendors.

- 7. A real DA Conference.

I would greatly appreciate any views, comments or suggestions from SIGDA Board Members on how we can best set out to achieve the best possible relationship between EDAC and DAC in a way that makes real sense when viewed from both sides of the Atlantic.

Workshops/Conferences.....Paul B. Weil

SIGDA sponsors many Workshops and Conferences in the Electronic CAE/CAD arena. During 1989 and 1990, SIGDA will either sponsor, co-sponsor or work in cooperation with other professional societies on a dozen professional meetings, including the Design Automation Conference (DAC), International Conference on CAD (ICCAD), Logic Level Modeling of ASICs WS, Formal Methods WS, Physical Design WS on Model Generation, High Level Synthesis WS, Timing Issues WS, International WS on Logic Synthesis, C Hardware Description Lang & Applications WS, International WS on Layout Synthesis.

We are always developing new Professional Activities to meet the needs of our 2,000+ membership. SIGDA does its utmost to assist the organizing committees through comprehensive support activities. For the smaller meetings, SIGDA funds ACM and others who provide direct assistance with site selection, budgeting, advertisement, and registration. This leaves the organizers with time to develop a superior technical program.

If you would like more information about the SIGDA Workshop and Conference support activities, E-mail or write the Workshop/Conference Chair (see inside the front cover of this Newsletter).

DATE: February 8, 1990

FROM: Paul Weil

SUBJECT: SIGDA Workshops & Conferences

#### SIGDA SPONSORED CONFERENCES SYMPOSIUM AND WORKSHOPS APPROVAL PROCESS

- 1. PROPOSAL: Two page summary of:

- The Meeting's Technical Objectives Background of this and similar meetings on this Subject Potential Locations and Dates Meeting Size and Format Organizing Committee and brief background of Chairs

- 2. INITIAL ORGANIZATION: ACM will assist the Committee with: Site Selection Budgets Timeline of Activities leading up to the Meeting

#### 3. MEETING BETWEEN ACM/SIGDA REPRESENTATIVE AND CHAIRPERSON(s)

-

- 4. FORMAL APPROVAL BY SIGDA

- 5. SIGDA WILL ARRANGE FOR ACM TO PROVIDE ASSISTANCE IN:

Local Arrangements Call of Papers/Participation Registration Advanced Program Publications On-site Registration Post Conference Accounting

ACM/SIGDA encourages the organizers to consider in-cooperation or co-sponsorship with other Professional Societies. (ACM/SIGDA has a close working relationship with the IEEE as well as other Electronic Engineering Societies.)

#### PROFESSIONAL ACTIVITIES DEVELOPMENT

- 1. **PROVIDE ATTENDEES** with copies of the latest SIGDA Newsletter and other handouts including ACM membership information

- 2. SEND SIGDA four copies of any material that is generally published for the attendees. If any portion of the material is not for public release, please indicate that on appropriate section of the material.

į.

Ł

#### AFTER THE MEETING:

- 1. IMMEDIATELY FOLLOWING THE CONFERENCE/SYMPOSIUM/WORKSHOP hold a meeting that will discuss future events and seek volunteers to run these events.

- 2. STATUS REPORT Within a few days of the meeting transmit to SIGDA a brief status report including the meeting's attendance, financials, how the meeting met its technical objectives and any outstanding problems that may have developed.

- 3. MEETING SUMMARY Within a few weeks of the meeting provide a summary (1 to 5 pages) of the meeting's activities for publication in the SIGDA Newsletter along with plans for future events. Emphasize the technical aspects of the CONFERENCE/SYMPOSIUM/WORKSHOP.

Asian Activities ......Akihiko Yamada

#### REPORT OF ASIAN ACTIVITIES March 7, 1990

#### 1. DAC SUBCOMMITTEE

DAC Subcommittee, chaired by T. Kozawa of Hitachi, has been organized for the first time following the recommendation of the DAC Executive Committee. As a result, the acceptance rate of Japanese papers has greatly improved - from 16% (5 papers) in 1989 to 56% (13 papers) in 1990. The Subcommittee is supported by SIGDA of IPSJ (Information Processing Society of Japan).

e É

#### 2. SIGDA OF IPSJ

SIGDA of IPSJ has about 400 members. It holds small workshops every two or three months, mostly one-day sessions. The SIGDA Committee, chaired by K. Hirakawa of Oki Electric, consists of 32 members from industries and universities. It also sponsors a DA Workshop every summer with about 100 attendees. We sometimes invite speakers from the States for panel discussions. This year, it will be held from August 30 to September 1 in Hakone, Kanagawa.

#### 3. AFFILIATE RELATIONSHIP BETWEEN SIGDA OF ACM AND SIGDA OF IPSJ

I am proposing to IPSJ SIG Board to establish an affiliate relationship between SIGDA of ACM and SIGDA of IPSJ. The joint membership agreement between ACM and IPSJ has been established for several years, and they are sister societies. The DAC Subcommittee is supported by the SIGDA of IPSJ. It will be useful to have an affiliate relationship between the two SIGDAs to promote further cooperation.

#### 4. EFIP WORKSHOP ON DESIGN & TEST OF ASICS

This workshop, chaired by Professor Kozo Kinoshita of Osaka University, will be held in Hiroshima, Japan, June 11-12, 1990. It is sponsored by IFIP WG10.5 and IPSJ. Twenty-seven abstracts have been

ł

ч.

accepted: five from the United States and Canada, eleven from Europe, and twelve from Japan. Seventy participants are expected. The topics will include core microcomputer design methodology.

#### 5. INFOJAPAN '90

IPSJ holds InfoJapan '90 international conference on information technology on October 1-5, 1990, in Tokyo, commemorating its 30th anniversary. Steven Jobs will be invited as a keynote speaker. They are expecting 1,200 attendees.

#### 6. ADEE JAPAN '90

In January of this year, ADEE Japan '90, sponsored by Cahners Exposition Japan, was held in Tokyo. Forty-five United States and Japanese EDA vendors exhibited their latest products. There were 14,000 attendees.

# CD-ROM Project......Bryan T. Preas, Director

| DATE: | April 4, 199 | 0 |

|-------|--------------|---|

|-------|--------------|---|

FROM: Kathy Preas

SUBJECT: Report to Board of Directors March 30, 1990

Although we just saw many of you at EDAC and presented a report on the CD-ROM Project at that time, we believe that it is important to keep you informed of the progress of this project. And these days, progress occurs daily. The project requires a lot of time from both of us now.

Ì,

#### 1. PROTOTYPE PROJECT

Data capture is complete for the prototype (the 26th DAC). Our contractors are working well together, and we expect that the Sparc and Mac versions of the prototype will be available for evaluation around the end of April. The Windows version of the retrieval engine is not complete, which will delay prototype evaluation on the IBM. Happily for the prototype evaluation schedule, we have a significant number of evaluators who are working on either Mac or Sparc machines, so we should be able to get enough feedback based on those versions for progress to continue on the final design, even as we await the IBM version. The IBM version will have the same feel, but a slightly different look. (Although KRS has not released the Windows version, they are using our data to demonstrate it at trade shows.) We are confident that we can obtain a good evaluation of the project from the prototype versions for Mac and Sparc stations.

The rapidly approaching date for testing of our prototype means that we must order the evaluation CD-ROM drives immediately. We have gotten very few returned information sheets and evaluation agreements, but Bryan has been personally contacting evaluators to get their system requirements so the evaluation will not be unduly delayed.

IEEE CS and ACM are anxious to evaluate the product in preparation for marketing, sales and distribution. Gene Falken (IEEE CS) will get the editors of various IEEE magazines to review it (in both

prototype and final form), so we are hopeful of some good publicity. Mark Mandelbaum and Bernard Rouse of ACM are also going to act as evaluators.

We will have our prototype on Jim Cohoon's SparcStation at the University Booth at DAC for demos. Thanks, Jim!

The names of those who have agreed orally to act as evaluators, and their machines, are:

| Jim CohoonSparc           |         |

|---------------------------|---------|

| Jonathan RoseSparc        |         |

| Chuck Shaw, CadenceSparc  |         |

| Dick Smith, NationalSparc |         |

| Bryan PreasSparc          |         |

| •                         | ан<br>Х |

| John AckenMac II          | -       |

| Mark MandelbaumMac II     |         |

| (ACM publications)        |         |

| Gene FalkenMac II         |         |

| (IEEE CS publications)    |         |

| Gordon Adshead            | . IBM |

|---------------------------|-------|

| Univ. of Paderborn/CADLAB | .IBM  |

| Kathy Preas               | .IBM  |

| Pat Hefferan              |       |

|                           |       |

Mike Lorenzetti ...... Mac II Rhonda Gaede...... Mac II, Mac+

#### 2. ACM/IEEE

Bryan spent a day at ACM headquarters talking with Mark Mandelbaum, and has had a long telephone conversation with Gene Falken of IEEE CS. Both organizations have "agreed to agree" regarding their positions on the CD-ROM Project. Their enthusiasm for the project is most welcome and encouraging to us - they genuinely seem interested in becoming involved and working to the benefit of the Project. Several issues which have been agreed to in principle relate to marketing, advertising, packaging and cost of the CD-ROMs. It is important that the CD-ROMs, as distributed, look the same to the end user, no matter from which Society they are purchased. Similarly, an identical price structure is necessary. Both ACM & IEEE agree that pricing should not be based on the value of the information; that would make the ROMs so expensive that no one would buy them. Rather, a reasonable price is called for, so as to encourage widest possible distribution of the ROMs. Pricing currently under discussion is \$300 for members and \$600 for non-members. Perhaps we should have a price break for SIGDA/DATC members (\$300 for SIGDA/DATC, \$450 for ACM/IEEE, and \$600 for others).

Both ACM and IEEE will have machines running the prototype at DAC, as well as advertising, flyers, preliminary order forms, etc.

#### 3. DOCUMENTATION

ACM is actively working on the problems of production, advertising, packaging, and distribution of the CD-ROMs. Bryan and Mark have agreed that ACM will take the lead in providing packaging for the product. Kathy will be responsible for writing the documentation and ACM will supply a copy editor to assist her. Kathy will submit camera ready copy to ACM. The documentation will be on paper, as well as being available on each of the ROMs. Kathy will prepare the documentation for data base build (SGML tags). ACM will handle the printing, collating, packaging and shrink wrap.

#### 4. **PRODUCTION**

ACM wants to do several other CD-ROM projects, using this one as a model. They want to establish relationships with disk-pressing houses, and have asked Bryan and Kathy to evaluate the pressing facilities. We will begin this task shortly.

23

ł

ì,

ž

ACM is currently working on the question of how many copies to press. SIGDA should consider the number of copies that we would like to have to distribute for: evaluators, library grants, rewards for those who participated in the project, distribution to magazine editors for review, etc.

#### 5. DISTRIBUTION & USER SUPPORT

ACM and IEEE will stock the CD-ROMs just as they do printed material. They have tentatively decided to have our contractor, Reference Technology, provide user support. Bryan and Kathy concur in this, at least in the beginning. As a topic of discussion for the SIGDA Board, how does this impact our consideration of building up a position at ACM headquarters for our use? Possibly support for this project could be included in that position.

Support can be a big variable in the cost of the product. The CD-ROM Project may have to fund support, at least partially.

#### 6. ON-LINE SERVICES

The SIGDA Board has discussed putting the CD-ROM databases on-line, but the discussion was tabled because of concerns about the impact of such a service on ACM income. It turns out that ACM has an ongoing relationship with three on-line services, STN, Dialog and FIZ Karlsruhe, and earns a royalty from on-line use of its databases. ACM has asked Bryan and Kathy to talk with these services about how our CD-ROM database might be used. Two of these services are based in Germany, so we will be talking with them over the next few months.

#### 7. NEW MATERIAL FOR ROMS

At the Dallas meeting Bryan was authorized to include the SIGDA Newsletter on the CD-ROMs. Many thanks to Chuck Radke, who has collected all of the back issues for us.

We also propose to include the European Design Automation Conference Proceedings on the CD-ROM, so as not to isolate our European friends and colleagues.

We can include the 27th DAC on the first ROM set instead of the update ROM. We assume everyone wants us to do so.

We have direction to include the SIGDA Newsletter from the Dallas meeting. We are proceeding under the assumption that we should include EDAC and the 27th DAC. Like the Newsletter, there will be a cost increase in the project proportional to the page count, as discussed at Dallas. We still don't know the exact figures, so we don't propose to update the budget at this time. At the close of the prototype evaluation we will get hard figures from our contractors, based on all of the information available. At that time the budget can be updated.

#### 8. FOLLOW-ON PROJECTS

We have discussed providing advanced retrieval capabilities beyond those possible with our retrieval engine by using KRS' Open Retrieval Interface. Examples are cite checking, forward and backward referencing, perhaps a key word index if we find that word searching is not powerful enough. (ACM has a program to extract key words from text and would like to be a part of this project.) The potential exists to fund university students to do part of this work. The new capabilities would be put on the first yearly update disk. We need to get Board member reaction now because we have the most leverage for negotiation for the Open Retrieval Interface licenses now.

ł.

We have found a company that can put digital data (pictures and text), as well as audio on the CD-ROMs. We installed a demo on the SIGDA CD-ROM Project computer -- very nice. This seems ideal for courses for undergraduates. Graphics can show slide material, algorithm operation, audio could be lecture/tutorial (maybe even some 'heavy metal' to keep the interest level up!)

#### 9. CURRENT HOT TOPICS

We are, at this very moment, working on the following:

- \* Completion of prototype design, ordering drives, instructions for evaluators, making sure the prototype will work.

- \* Royalty agreement with KnowlegeSet: agreed orally, next need a written version; we are working with the ACM lawyer on this.

- \* Production contracts

- \* Prototype evaluation program

- \* Documentation

#### 10. PROBLEM AREAS

We still have no authorization to include the Transactions on CAD.

The FAX machine at CADLAB is unreliable. This is causing delays in communication.

#### \*\*\*\*\*ACTION ITEMS\*\*\*\*\*

- 1. The Board must decide how many copies of the CD-ROMs are wanted for library grants, Board members, evaluators, etc.

- 2. Consider position at ACM for support, SIGDA business.

- 3. Budget increase proportional to page count for EDAC, 27th DAC: speak up if this is a problem.

- 4. Any input regarding pricing of the CD-ROMs?

- 5. Reaction to follow-on projects (#8 above):

- A. Only the first part is critical. We need to know how hard to push for Open Retrieval Interface?

- B. The Multimedia ROM is not critical to anything we are doing now.

Just something to think about.

1

×,

## Board of Advisors...... Michael J. Lorenzetti, Secretary/Treasurer

DATE: March, 1990

FROM: Michael J. Lorenzetti

SUBJECT: SIGDA Bylaws

I received the following from Stu Zweben, Chairman, Constitution and Bylaws Committee, ACM regarding the SIGDA Bylaws. The SIGDA Advisory Board has been having an email discussion of the bylaw suggestions that were made. There is general agreement that the suggestions are excellent and serve to improve our bylaws. I will enter these changes and have them approved at the Advisory Board Meeting. The Constitution and Bylaws Committee will then be prepared to state that our proposed bylaws are consistent with the ACM Constitution and Bylaws, and that should clear the way for approval by the ACM Executive Committee.

The Constitution and Bylaws Committee has met to discuss the proposed SIGDA bylaws changes. We have the following comments for your consideration.

#### Inconsistencies:

- 1. Article 3. The dissolution of a SIG can take place in a manner other than Council vote (per Bylaw 7). Therefore, we suggest that the phrase "by the Council of the ACM" be deleted from Article 3.

- 2. Article 6. Section b should state that the "SIG Board Chairman" rather than the "SIG Board" fills vacancies if there's no other provision in the SIGDA bylaws.

- 3. Article 11. There are references to both a "nominating" committee and an "election" committee, when it appears that only one committee is in fact intended. We suggest that the references to "an election" committee in section a, and to "the election" committee in section c, be changed to "a nominating" and "the nominating" committee, respectively.

- 4. Article 11. In section a, there is no election of ANY officers if the SIG Board decides to exercise its option to extend the terms of office, according to PPG 17.4.2. Therefore, the middle sentence should be changed to something like "This committee will nominate at least two candidates, who consent to serve, for each elective office."

- 5. Article 12. In section a, there is reference to approval by the SIGDA "Advisory Board" before an amendment of section 1 can go to the SIG Board. However, ACM Bylaw 7 states that the SIG's "Executive Committee" must approve of such an amendment. So we suggest that you change the words "Advisory Committee" to "Executive Committee" in section a (alternatively, you can have both approvals, but you must require that the Executive Committee be in the loop). Also in Article 12, section b, you mention the "Advisory Board" rather than the Executive Committee, in approving amendments to

go to the SIG's membership. This is not in conflict with ACM's Bylaws, but is this what you want, given the change you must make to section a?

6. Use of the word "Chair." The Constitution and Bylaws Committee takes the position that references to ACM positions should be made consistently throughout ACM's documents. ACM refers to its positions using the title "Chairman" and recognizes this use as a non-gender-specific use (you may be interested to know that several years ago Council "cleaned up" its Bylaws to remove the use of gender-specific pronouns, but deliberately chose to keep the word "Chairman" and not use "Chairperson" or "Chair" instead). While we recognize that your executive committee takes a different position, we are still recommending the use of Chairman wherever the word "Chair" appears in the bylaws. Perhaps we will need to let the ACM Executive Committee decide this issue.

Clarifications and wording suggestions:

- 1. There are several examples of the use of future tense in the SIGDA bylaws, where present tense would seem more appropriate. Examples are in Articles 1a, 2a, 2b, 5b, and 8a where "will" or "will be" can be changed. This is, of course, a minor point.

- 2. The use of the phrase "executive committee" should be consistently capitalized or consistently noncapitalized in the document. For example, it is not capitalized in Article 4bi (where we also recommend inserting the modifier "SIGDA" in front of executive committee, since the Executive Committee hasn't yet been defined), Article 7a and Article 8c.

- 3. Use of gender-specific pronouns. In Article 6a, the phrase "offices he has appointed" would be better phrased "positions appointed by the Chair(man)" since the Chairman doesn't appoint offices (as SIGDA has defined its officers) and this would avoid the use of "he (or she)." In Article 8, sections a and b, the word "his" should be "his or her."

- 4. Avoid the use of the word "Group" since it wasn't defined in section 1. Instead, use "SIGDA." Relevant places are Article 8b and Article 14.

- 5. In Article 9, preface the second sentence with "As provided in ACM Bylaw 7," for clarification, since the rest of the first sentence (until the semicolon is verbatim from Bylaw 7); however, the word "voters" should be changed to "votes" to be consistent with Bylaw 7's wording.

- 6. In Article 11, section a, do you really want to state that the report of the nominating committee must be presented "in the SIGDA newsletter"? Perhaps the timing of the publication of the newsletter is such that you can't get it out in order to meet this provision. You might instead want to do a special mailing to all members of SIGDA to announce candidates. To allow such flexibility, the phrase "in the SIGDA newsletter" can be changed to "to the SIGDA membership". However, this is entirely your call.

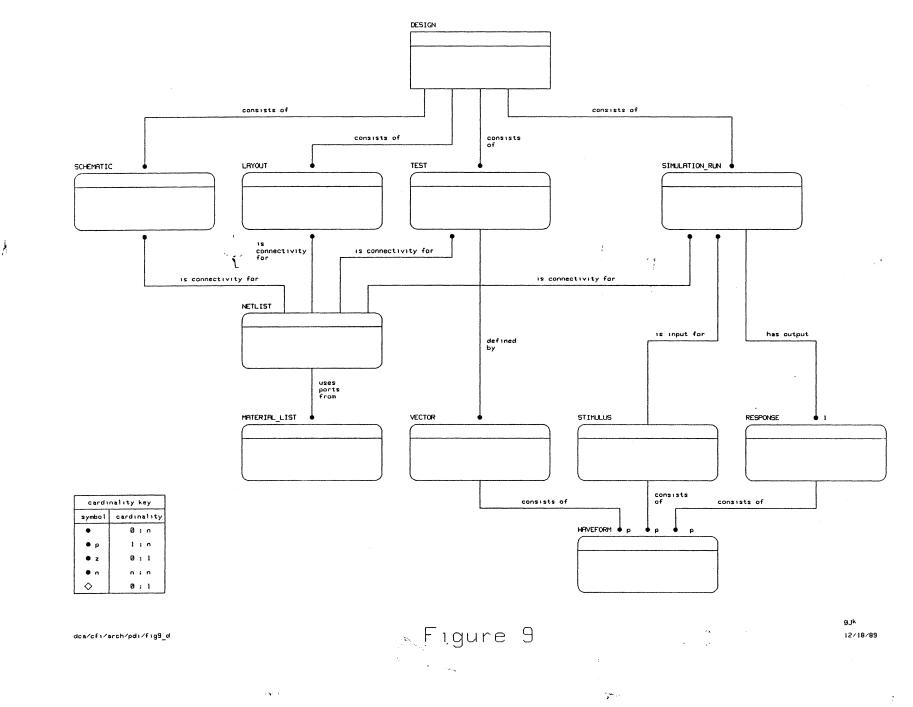

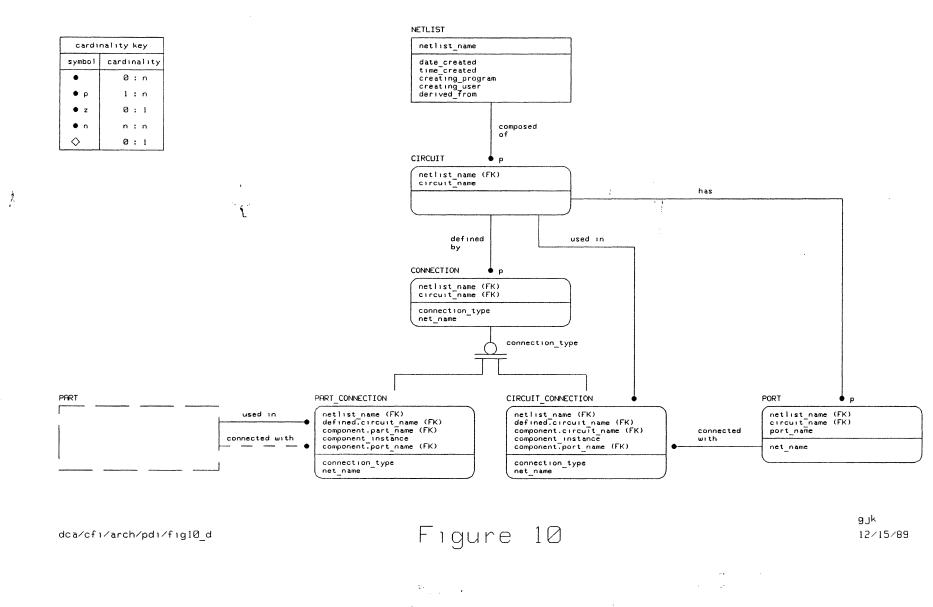

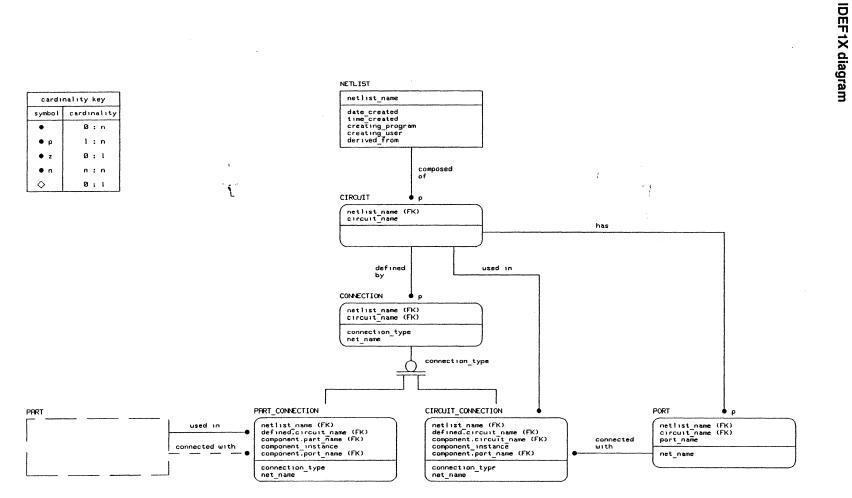

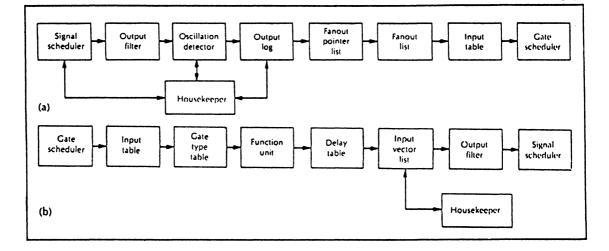

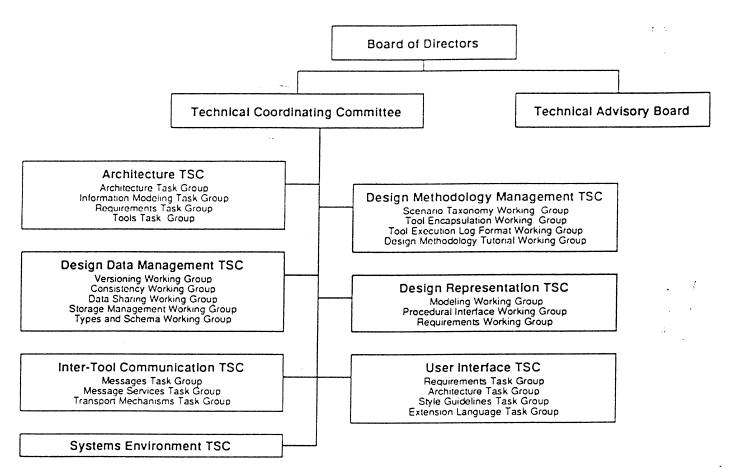

- 7. There are capitalization omissions that, in the final writing, should probably be fixed. Examples are Article 4dii, Article 10 (second sentence), and Article 12c (last sentence). Also, readability would be improved if commas were inserted in i) Article 9b, last sentence, after the word "SIGDA"; ii) Article 14, first sentence, after the word "year".