| acm       | SIGDA NEWSLETT                                                                                                 | ER |

|-----------|----------------------------------------------------------------------------------------------------------------|----|

| Volu      | ume 6 Number 3 September 1976                                                                                  |    |

| Contents: | Chairman's Message                                                                                             | 1  |

|           | From the Editor                                                                                                | 15 |

|           | A Data Structure for the Description and<br>the Handling of Engineering Drawings*,<br>C. Cavagna and U. Cugini | 2  |

|           | CAD for LSIProduction's Interest is in its Economics*, J.G.M. Klomp                                            | 11 |

| . ·       | Clustering Methods as Partial Solutions<br>to the Space Allocation Problem*,<br>R. S. Frew                     | 16 |

|           | CAD 76 Abstracts of Papers on B uilding<br>Design, J. S. Gero                                                  | 22 |

|           | 13th Design Automation Conference Review,<br>D. Hightower                                                      | 24 |

|           | Meeting Announcements and Calls for Papers                                                                     | 26 |

| •         | List of Attendees at the 13th DAC                                                                              | 28 |

|           | Automated PC Board Routing Cleanup<br>Procedures , R. J. Smith and<br>R. N. Castleton                          | 41 |

~

\*Presented at 13th Design Automation Conference

## SIGDA

ACM Special Interest Group on Design Automation

#### ADDRESSES

CHAIRMAN: Charles W. Rose Computing & Information Science Case Western Reserve University Cleveland, Ohio 44106 (216) 368-2800

VICE-CHAIRMAN: Judith G. Brinsfield Bell Laboratories Building 3B-323 Whippany, NY 07981 (201) 386-3169

SECRETARY-TREASURER: Luther C. Abel Digital Equipment Corporation 146 Main Street Maynard, Mass. 01754 (617) 897-5111

EDITOR: Robert J. Smith, II Lawrence Livermore Laboratory, L-156 P.O. Box 808 Livermore, CA 94550 (415) 447-1100, X-8088

TECHNICAL COMMITTEE: Judith G. Brinsfield

MEMBERSHIP COMMITTEE: William M. vanCleemput Digital Systems Laboratory Stanford University Stanford, CA 94305 (415) 497-1270

PUBLICITY COMMITTEE: Lorna Capodanno, Chairman Bell Labs 2C169 Murray Hill, New Jersey 07974 (201) 582-6909

BOARD OF DIRECTORS: Dr. John Grason Department of Electrical Engineering Carnegie Mellon University Pittsburgh, Pennsylvania 15213

Dr. Edwin Hassler Design Automation Department Components Group Texas Instruments, Inc. P.O. Box 5012 Dallas, Texas 75222

Professor James Linders Department of Applied Analysis University of Waterloo Waterloo, Ontario Canada BOARD OF DIRECTORS, cont.'d Dr. Ralph Miller Structures Research Commercial Airplane Group Boeing Company P.O. Box 3707 Seattle, Washington 98124

Dr. Jean-Marie Comeau Bureau of Management Consulting 365, Ave Laurier Ouest Ottowa, Canada KIAOT5

#### MEMBERSHIP

SIGDA dues are \$3.00 for ACM members and \$5.00 for non-ACM members. Checks should be made payable to the ACM and may be mailed to the SIGDA Secretary/ Treasurer listed at left, or to SIGDA, ACM Headquarters, 1133 Avenue of Americas, New York, N.Y. 10036. Please enclose your preferred mailing address and ACM Number (if ACM member).

#### SIG/SIC ACTIVITIES

1) Informal technical meetings at NCC.

- Formal meeting during National ACM meeting + DA Workshop.

- Joint sponsorship of annual Design Automation Workshop.

4) Quarterly newsletter.

Panel and/or technical sessions at other National meetings.

#### FIELD OF INTEREST OF SIGDA MEMBERS

Theoretic, analytic, and heuristic methods for;

1) performing design tasks,

- 2) assisting in design tasks,

- optimizing designs through the use of computer techniques, algorithms and programs to:

- facilitate communications between designers and design tasks,

- 2) provide design documentation,

- 3) evaluate design through simulation,

- 4) control manufacturing processes.

The 13th Design Automation Conference in San Francisco was an outstanding event. The technical program contained a number of significant presentations, the tutorials were very helpful and well presented, and the arrangements, as usual, were top notch. Thanks and congratulations to Don Humcke and the rest of the committe for their hard work and dedication.

SIGDA held a business meeting at the conference which was attended by 18 persons of which 14 were SIGDA members. The meeting was scheduled opposite several "birds of a feather" informal technical sessions, and so I am not disappointed with the turnout.

General discussions revolved around our somewhat loose association with ACM which resulted in a consensus that since our group is strong and enthusiastically supports the Design Automation Conferences, our lack of participation in traditional ACM conferences (ACM National and NCC) while unfortunate, is not a cause for concern.

Luther Abel presented a financial report which indicated that we are financially healthy SIG, and that our surplus derives primarily from conference and proceeding profits. These are soft funds, and with the exception of the Design Automation Conferences, they lose money at least as often as they make it. The discussion then focused on the assessment for non-ACM SIG members.

The issues, as I have discussed in previous chairman's messages are: non-ACM SIGDA members are assessed \$7.50 yearly for "data processing" and \$1.50 head tax. This means that, in addition to the usual costs of newsletter mailing, etc., we are charged \$9.00 for these members while they pay only \$5.00 in dues. ACM SIGDA members office costs amount to approximately \$5.00 yearly while dues are \$3.00. It has been the feeling of your executive committee and board of directors that the degree to which non-ACM members are subsidized is out of line and that their dues should be raised.

This feeling was supported by the meeting attendees.

The next problem discussed dealt with the provisions in the bylaws for charging dues. I outlined this problem to you in my last message and proposed a solution. The attendees felt that while the executive committee with the advice and counsel of the directors should be able to set the dues, removing all limits on dues from the bylaws was not appropriate.

An alternative was proposed and strongly backed which 1) remains responsive to the need for dues revisions in response to ACM Headquarters assessment changes without continued revision of the bylaws, and 2) retains a limiting function to prevent the dues from being increased excessively by an irresponsible administration. Briefly, the proposal is to set the dues floor at \$4.00 for members and \$8.00 for non-members (providing a \$1.00 subsidy for both classes currently) and to allow an increase of not more than \$2.00 per year to be imposed by the executive committee with the advice and counsel of the directors. Under this scheme, the rate of dues increase is controlled and the time constant for substantial increases will allow members to effect the increases by exercising their rights of officer selection and/or bylaw revision if a dues increase pattern is felt to be excessive or unnecessary.

In a straw vote of the attendees the alternative received unanimous support, and it is my intention to submit it to you in the form of an amendment to Article III. Section C of the Bylaws in accordance with Article VIII of the Bylaws and the rules of ACM. Which states that:

- A. An amendment to these bylaws may be proposed by a resolution adopted by the Executive Committee or by a petition signed by at least 10 members.

- Within 60 days after receipt by the Secre-tary-Treasurer of the proposal of an amendment, the Secretary-Treasurer shall Β. conduct a mail vote on the amendment. The proposed amendment shall be reviewed by the Chairman of the Committee on Special Interest Groups and Committees prior to the mail vote on the amendment. Ballots shall be mailed to all members of the Group and shall state the last day for receipt of a voted ballot by the Secretary Treasurer. This date shall be 30 to 60 days after the last ballots are mailed. The amendment shall become effective if it receives a majority vote of one-fourth of the Group membership, with the effective date falling 60 days after the final receipt date stated on the amendment ballots.

SIGDA will <u>hold elections</u> next <u>spring</u> for <u>Chairperson</u>, <u>Vice Chairperson</u>, and <u>Secretary-Trea-</u> <u>surer to take office on 1 July 1977</u>. I will soon be appointing a nominating committee in accordance with ACM rules. The chairperson of this committee will be announced in the December Newsletter. In the meantime, if any of you are interested in running or wish to place another's name in nomination, please call or write me. The jobs require people who care about SIGDA and its future, but the work load is really minimal. Please consider running for an office!

Bill Van Cleempt is doing a great job organizing the <u>Symposium</u> on <u>Design Automation</u> and <u>Microprocessors</u> to be held 24-25 February 1977. Read the call for paper elsewhere in the Newsletter and contribute!

## A DATA STRUCTURF FOR THE DESCRIPTION AND THE HANDLING OF ENGINEERING DRAWINGS

## by

## C.Cavagna and U.Cugini

Politecnico di Milano, Sez. Disegno Macchine P.za Leonardo da Vinci,32 20133 Milano, ITALY

## 1. Introduction

The specifications of a data structure are essentially linked to the model which it is wished to represent, to the functional links which it is wished to obtain amongst the various data and the action which it is wished to take on such structure.  $\begin{bmatrix} 1 & 2 \end{bmatrix}$

An engineering drawing is the two-dimensional representation obtained according to precise accepted standards of three-dimensional objects.

Thus the data structure representing an engineering drawing will surely contain all the connections among the two-dimensional graphic elements of which same is composed and should contain a complete description of the threedimensional object represented, so as to allow action on same at any level whatsoever through its two-dimensional representation.

On the other hand, by analyzing the various phases of the design process which lead to the production of final working drawings, it is to be noted that the three-dimensional model of the mechanical part becomes increasingly detailed and complex, as are the drawings used to illustrate same.

Moreover, the quantity of drawings which accompany the various phases of the design process is ever greater and the types of action to be taken on such drawings refer to an ever greater extent to details which do not substantially alter the piece from a functional point of view, but which complicate its shape to an appreciable degree.

Furthermore, at such a level, the drawing contains a large amount of data of a technological and constructive nature which are also continually changed or amended.

The use of computer aided drafting systems is justified where large numbers of considerably complex drawings are involved. In the field of mechanics, this occurs as may be seen, during the final stage of design where the manner of action taken as to the object represented essentially concerns details (from the point of view of the shape of the piece); it would not therefore seem reasonable at this level to use for the storage of the drawing, a data structure which contains a complete and faithful representation of the illustrated mechanical part given its great complexity. 3

It will therefore be sufficient for the data structure for the handling of the drawings to contain only those functional links which are of interest at the detailing design stage.

## 2. Analysis Of Engineering Drawings

An engineering drawing, as mentioned in the introduction above, is the final document resulting from all the phases of design, and thus constitutes the specifications for production, hence containing a complete series of data which are not limited to a graphic description of the shape of the piece illustrated according to traditional standards, but refer to the technological processing specifications such as dimensions and dimensional tolerances, surface roughness and manufacturing methods.

It may therefore be seen that engineering drawings may be considered as being a graphic structure divided logically and functionally into two parts: the graphic structure representing the shape of the piece and the graphic structure representing all other data.

These two different structures may be thought of as being arranged on two separate sheets, superimposed one over the other, taking into account, however, the fact that there exist certain connections between the said two sheets. More precisely, the graphic structures which represent dimensions or symbols are coupled to points or lines of the graphic structure representing the shape of the piece.

## 2.1 Shape Of The Piece (Sheet 1)

In many kinds of non engineering applications, a drawing is composed of a more or less numerous series of repeated graphic elements (symbols, diagrams, etc.). A typical example is that of electric or electronic circuits, plant drawings, etc..

The data structure of a drawing of this kind may be suitably organized in a hierarchical fashion by establishing basic patterns used as primitives and more complex figures, built up by means of such primitives, which may in turn be appropriately repeated in generating the final drawing. 4

In the case of mechanical engineering drawings, it is not possible to identify any basic primitives which may then be suitably introduced into a hierarchical structure, and hence the drawing will be structured at the lower graphic level namely, that of points, segments and arcs. 5 6

The objects illustrated in engineering drawings are three-dimensional, finite bodies which are thus defined in space by finite and contiguous surfaces.

Each of these projected finite surfaces gives rise to a closed polygonal. From this point of view, an engineering drawing may be thought of as being read in the form of a series of closed polygonals, each of which represents the projection of a surface of the piece.

This would always be true were it not for the fact that for reasons of clarity in the drawing, the hidden lines (that is, those polygonals or parts thereof covered by other surfaces to be found between such polygonals and the projection point) are eliminated.

The visible parts of the partially hidden polygonals, may be seen as open polygonals whose ends are determined and hence coupled to those polygonals which define anteriorly arranged outlines.

An engineering piece, moreover, is not univocally characterized by a pure geometrical form, there being functional links existing between the various surfaces which define same; 11-12-13-14-15; whilst open polygonals may be there exist, that is, Surfaces which are functionally dependent upon others.

This dependency may be maintained in the drawing by having recourse to open polygonals which in fact create a hierarchical link among the polygonals themselves.

Moreover, in such a way it is possible to eliminate all those parts which would be duplicated since they belong to contiguous polygonals.

The coupling points of the open polygonals which will only be those at the beginning and the end, may be at the turning point of other polygonals.

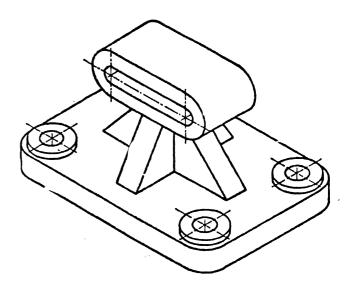

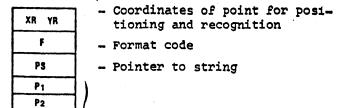

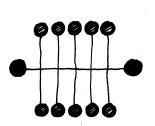

In the case of side coupling, the point will be conventionally referred to with the term "half hinge". In Figure 1, it is possible to identify as closed polygonals, the turning point sequences 1-2-3-4-5, 6-7-8-9-10 and identified in 16-17-18-19, 20-21-22-23, 24-25, 26-27, 28-29 and 30-31.

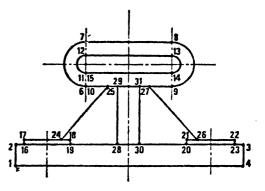

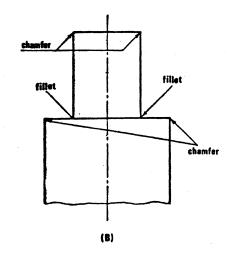

The points 16 and 19, 20 and 23, 24 and 25, 26 and 27, 28 and 29, 30 and 31 are half hinges. Again, by continuing in the analysis of an engineering drawing, it may be seen that there exist local details such as fillets and chamfers, that it would serve no purpose to introduce explicitly into the structure illustrated in the drawing. For example, the end of the shaft shown in Figure 2A is to be taken, and therefore stored, as a perfectly cylindrical section with local variations as indicated schematically in Figure 2B.

Figure 2.

## 2.2 Technological Data (Sheet 2)

As regards the technological and dimensional data, same are indicated in a conven-

tional manner in the drawing, using standardized and therefore ripetitive graphic structures and a series of alphanumerical symbols, varied from time to time.

In this case, the use of graphic primitives may therefore be considered in order to introduce this information into the data structure representing the engineering drawing, which allow the generation of:

- linear dimensions

- circumference dimensions

- arc dimensions

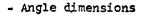

- angle dimensions

- symbols relating to the surface condition

- special notes.

The single technological data could be obtained by characterizing each of these primitives by means of a series of free parameters associated with a string of alphanumerical symbols, containging the relative information.

## 3. Modification

The types of action taken with regard to modifying a drawing, in addition to additions or erasure of parts, are essentially of two kinds:

- change in the shape of the piece

- change in the technological data.

In the former of these cases, the change in shape consequently leads to the adjustment of all the relative technological data. This means cancellation of all the information related to parts which have been taken away and up-dating of the data relating to those parts of the drawing which have been modified.

The second type of action only concerns the

technological data and is therefore limited to merely changing the relative alphanumerical

data, or to modifications as to formats or references. In all events, none of these operations may be such as to affect the representation of the shape of the piece.

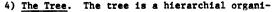

### 4. Proposed Data Structure

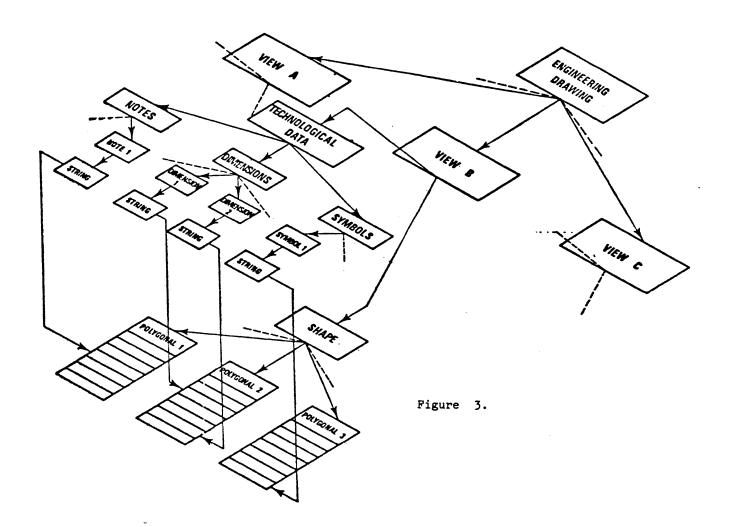

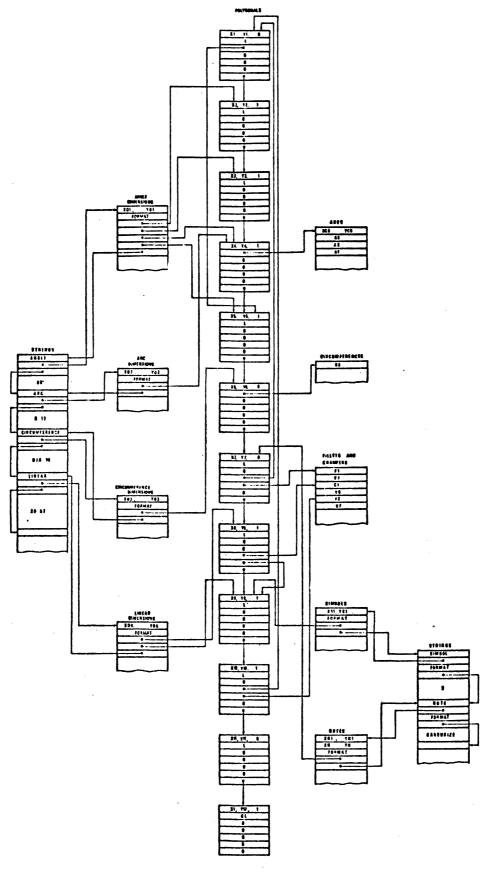

From the analysis of an engineering drawing and the types of action which may be taken as regards same, a schematizable data structure as shown in Figure 3 may be derived. As may be seen, the drawing as a whole is subdivided into various independent "drawings" which represent its various views and sectional views, and thus have no other connection if not that of reciprocal position.

In each of these drawings, it is possible to identify, as has been seen, two different levels of graphic information: one containing only the representation of the piece and the other containing all its technological and dimensional data.

In conformity with the analysis carried out, the level representing the shape alone is composed of a series of open and closed polygonals, and the level representing the technological and dimensional data is composed of three different categories of graphic structures representing, respectively:

- dimensions

- symbols

- notes.

The single technological and dimensional data are stored in the data structure by means of single alphanumerical strings and the free parameters which represent the corresponding primitives.

Between the level of the technological data and that of the shape of the piece, exist, as has been seen, a number of connections in the sense that the technological and dimensional

data are coupled to particular elements of the shape, being dependent upon same.

In the data structure which will be illustrated - pointer at next point of polygonal hereinbelow, reference will be made to a single drawing (that is, to only one view or sectional view) since the only link existing between the single views or sectional views is that of reciprocal position.

4.1 Data Structure Relating To Shape (Level 1)

The shape of the piece is stored by means of a series of lists connected one with the other, each of which represents a polygonal.

Each element of the list is structured in such a way as to contain the following information:

- x, y coordinates of point

- code indicating type of line (blank, solid, dashed)

- function code indicating which kind of curve joins the point

In cases other than that of a straight line, same is replaced by a table pointer

setting forth all the parameters which characterize the sections of the curve:

- pointer at possible points of coincidence

- pointer of connection in the event of point being a half hinge

In such a case, the pointer points to the initial point of the side of the polygonal to which the half hinge is coupled.

- code of local variation used for chamfers and fillets

In the event of there being a chamfer or fillet corresponding to the point, it points to a table containing a code of variation (chamfer or fillet) and the relative numerical value.

chamfer pointer This pointer serves the purpose of connecting up with the other point defining the chamfer (in fact, this point does not necessarily have to be contiguous).

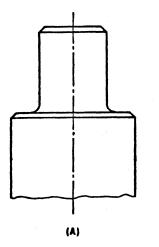

An element of the list will therefore be structured as shown in Figure 4.

- Arc dimensions

- X Y L F PC PH PV PC PN

- coordinates of the point - line code - function code

- coincidence pointer

- half hinge pointer

- local variation pointer

- chamfer pointer

- pointer to next point

Figure 4.

## <u>4.2 Data Structure Relating To Technological</u> Data

The technological data are defined by means of the primitives established from time to time by a series of parameters. In all the primitives, the following types of parameters may be identified:

- coupling pointers to elements of the structure which describe the shape of the piece

- format code

- parameters of position on plane. These parameters are the coordinates of a characteristic point used both for the positioning of the technological data and for the recognition thereof

- string pointer. Since the alphanumerical strings relating to each set of technological data may have very differing lengths, easily put to editing, same are stored in a suitable structure. It therefore becomes necessary to have a pointer to said structure for each set of technological data.

More precisely:

- Linear dimensions

| XR YR      | - Coordinates of point for posi-<br>tioning and recognition                    |  |  |  |

|------------|--------------------------------------------------------------------------------|--|--|--|

| F          | - Format code                                                                  |  |  |  |

| PS         | - Pointer to string                                                            |  |  |  |

| P1 )       | - Coupling pointers to two points                                              |  |  |  |

| · P2       | ) of the structure describing shape.                                           |  |  |  |

| - Circumfe | <pre>} - Coupling pointers to two points     of the structure describing</pre> |  |  |  |

| XR YR | ] |  |  |

|-------|---|--|--|

| F     |   |  |  |

| PS    |   |  |  |

| PC    |   |  |  |

- Coordinates of point for positioning and recognition

- Format code

- Pointer to string

- Coupling pointers to circumference centre.

P3

**P4**

XR YR

F

PS

XS YS

P1

- Notes

# Format code Pointer to string

- Coupling pointer to the second point of the arc.

tioning and recognition

- Coordinates of point for posi-

- Coupling pointers to four points of the structure describing shape.

- Coordinates of point for positioning and recognition

- Format code

- Pointer to string

- Coordinates of point used for positioning string

- Coupling pointer to shape.

- Symbols

P1

| XR YR | - Coordinates of point for posi-<br>tioning and recognition |

|-------|-------------------------------------------------------------|

| F     | - Format code                                               |

| PS    | - Pointer to string                                         |

- Coupling pointer to shape.

Figures 5 and 6 show by way of example, a drawing and its corresponding structure.

Figure 5.

Figure 6.

## 5. Possible Modification Operations

According to the schematization introduced, a distinction will be made between action regarding the graphic structure corresponding to the shape of the piece and action as to the structure corresponding to all the other data. Taking into account the fact that there exists a connection between the two structures and that the graphic data are subject to the shape of the piece and not vice versa.

## 5.1 Modification Of The Shape Of The Piece

Action as to the shape of the piece may be taken at two levels:

- modification which will be termed "dimensional", variation of a centre and/or radius of an which does not involve the sequence of graphic elements making up the polygonals, but merely changes their numerical values (coordinates, length, etc.)

- modification which will be termed "functional" which does affect the sequence of graphic elements (erasure, replacement, insertion of parts).

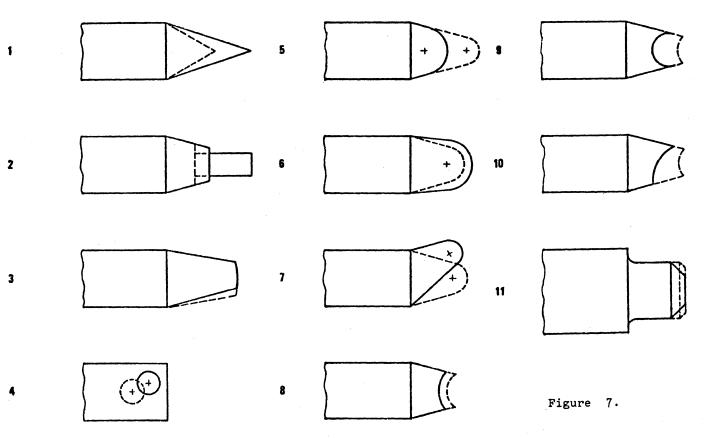

5.1.1 Dimensional Modification. As far as the dimensional modification of the shape is concerned, the following possibilities have been identified:

- change in the coordinates of a point common to two consecutive segments of a straight line (this leads to a variation in the length of the two segments concurrent at such point). See Figure 7/1.

- translation of a segment of a straight line comprised between two other segments (translation occurs in an orthogonal direction to the segment itself and its extremities are bound to lie on the straight lines defined between the previous and following segments). See Figure 7/2.

- rotation of a segment of a straight line around its extreme point (the other point being bound to belong to the polygonal section contiguous at such point). See Figure 7/3.

- variation of the centre and/or radius of a circumference. See Figure 7/4.

- arc of a circumference extending between two segments maintaining the tangency at its extremes. See Figures 7/5, 7/5 and 7/7.

- variation of the centre and/or radius of an arc without the conditions of tangency at its extremes. In this case the initial and end points of the arc are determined by fixing their belonging to the polygonal sections before and after same. See Figures 7/8, 7/9 and 7/10.

- variation in the characteristic value of chamfers and fillets. See Figure 7/11.

In all these cases any information of a technological nature which refers to pieces which have undergone functional modifications is automatically adjusted to the new values.

8

<u>3.1.2 Functional Modification</u>. As regards the functional modification of the shape, the following possibilities have been identified:

- erasure of an entire open or closed polygonal

- append of a new open or closed polygonal

- replacement of a part of a polygonal; that is, erasure of the sides of the polygonal included between two points and insertion between same of a new sequence.

The half hinges which are attached to the sides of the polygonal are cancelled or transformed into the extreme points of an open polygonal which may either be erased or completed.

Any technological information having points of connection with the erased parts is automatically cancelled.

### 3.2 Modification Of Technological Information

The technological information, whilst having points of connection to the shape of the piece, has some degree of freedom as regards its positioning on the plane of the drawing.

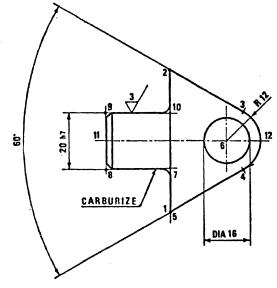

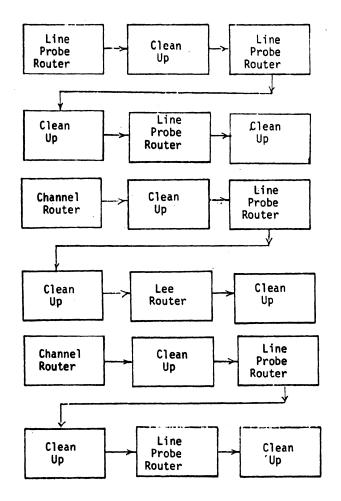

A diagram of the various types of graphic information evidencing these points of connection and their possibilities of displacement, is given in Figure 8.

As regards the modification of these graphic structures, the following possibilities have been identified:

- displacement of the graphic structure according to its degree of freedom

- variation in format of dimensions

- editing of relative alphanumerical string

- erasion of one or more graphic structures

- addition of new graphic structures.

6. Comments And Conclusions

The illustrated data structure centres upon the open and closed polygonal concept: this makes it possible to express in terms of structural links the relations of both a functional and positioning nature relating to the various surfaces defining the illustrated piece.

Moreover, the implicit sequentiality of each single polygonal, in addition to expressing the continuity of the surfaces defining the piece in terms of structural links, also optimizes the efficiency of the data structure. In fact, when used for loading the structure, either entirely by means of digitalization or making use of graphic systems for generation of drawings, same compacts the storage of the points which define the drawing, reducing to a minimum, the duplication of the stored points. This is important because clearly the response time for any action as to the structure, same being based on lists, is proportional to the number of stored points.

It is moreover clear that also the output phases are optimized since blank paths are reduced to a minimum.

> LINEAR DIMENSIONS CIRCUMFERENCE DIMENSIONS ARC DIMENSIONS ANGLE DIMENSIONS NOTES AND SYMBOLS

> > Figure 8.

This type of approach also implicity proposes a description and reading methodology for engineering drawings, given the fact that it makes it possible to identify the links existing between the outlines of the piece based on its relative positioning or on its functional dependancy.

If the data structure is loaded with a sequentiality which does not reflect the continuity of the engineering drawing examined, whilst loosing in efficiency it causes an increase in the number of stored points, but maintains all its possibilities.

The quantitative data relating to overall dimensions and response times as a function of the complexity of the drawing and the loading procedures of the structure will be available upon conclusion of the implementation presently being carried out on a Hewlett-Packand 2100 System, (16K core, disc, magnetic tape) to which are connected a graphic terminal, namely, Tektronix 4010, and a graphic tablet, namely, the Tektronix 4954.

## 7. Acknowledgements

This work has been undertaken with financial aid from CNR under grants number CT 74.01650.07 and CT 74.00845.07.

## 8. References

- R.WILLIAMS: "A survey of Data Structures for Computer Graphics Systems". Computing Surveys Vol.3, No.1, March 1971.

- B.BITTNER and B.WOLF: "A Graphics Database for engineering drawings". CAD'74 Conference Proceedings 25-27, September 1974, Imperial College London.

- C.CAVAGNA and U.CUGINI: "An interactive system for the handling of engineering drawings". EUROCOMP Conference on "Interactive Systems" 23-25, September 1975, London.

- 4. A.Van DAM and D.EVANS: "A compact data structure for storing, retrieving and manipulating line drawings". SJCC 1967, Pages 601-610

- C.CAVAGNA, U.CUGINI and C.LUINI: "Interactive dimensioning of engineering drawings: a general approach". 13th International Automation and Instrumentation Conference. 13-15, November 1974, Milan.

- 6. V.MOREGGIA and R.TAVAN: "FIAT's automated mechanical drafting system". CAD'76 Conference Proceedings, 23-25, March 1976, Imperial College London.

Figure 9. Blocked Access to Edge Connector Pads.

CAD FOR LSI PRODUCTIONS'S INTEREST IS IN ITS ECONOMICS

J.G.M. Klomp N. V. Philips/Elcoma Division Nijmegen, The Netherlands

## System Description

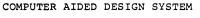

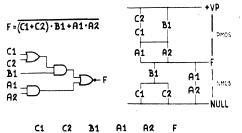

CAD for LSI design means a total package from basic circuit analysis up to programs which generate tapes for numerical controlled pattern generators and testing equipment. The flow of such a system is given in Fig. 1. It shows the usual diagram of circuit analysis, cell library, logic simulation, functional and d.c. parametric test generation and an automatic layout system.

fig. l.

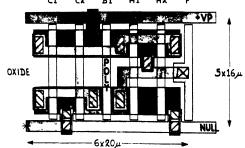

The cells in the cell library range from simple gates and flipflops to more complex functions up to nine input variables; also ROM- and RAM bit cells are available. An example of a cell structure is given in Fig. 2. Each cell has a constant height and variable width. The in- and output signals can be reached both from the top and the bottom of the cell. The library contains about 120 items which are all characterized with respect to layout as well as electrical and logical be-haviour, including time delay factors. Custom designs and LSI's in general often need something special. If a CAD system is not capable of handling these specialties without losing its efficiency or without becoming difficult to handle, users are not willing to accept that system as a tool. To bypass this problem a library is developed which contains so-called "primitives", examples of which are shown in Fig. 3.

## COMPACT LOGIC CELL

fig. 2

fig. 3

With these basic items, which are related to the single process steps, the designer is able to develop all kinds of specials, which will not only satisfy the customer specification but also will fit into the rest of the system.

The first step after the acceptance of the development of a design is to convert it into functions provided by the library. If necessary a special building block is developed. For this purpose the analysis program is used to check the electrical properties. A correlation has been established between the calculated values and the diffusion product with an accuracy of about ten percent.

When all building blocks are available, the network is coded for the computer, where macro facilities, parameter descriptions, etc. are available to reduce the amount of work. (see Fig. 4.)

| ٥  |           | MACHU        |                                                             |                         |          |             |               |         |              |              |

|----|-----------|--------------|-------------------------------------------------------------|-------------------------|----------|-------------|---------------|---------|--------------|--------------|

| ĭ  | • 01 CH-4 |              |                                                             |                         |          |             |               |         | L./0=05=02   | + DF F Q Q ; |

| ż  | 2         | DICUNA       | Ircl.0                                                      | Care Contraction of the | ******** | PLEO NAND   | 0.0.0         | ES. PHL | C. / 0=03=02 | FDFF00       |

| 3  |           |              |                                                             | , LEJ<br>Le UNU, IAN    |          |             | 0 (14, 4      |         |              |              |

| 4  | :         |              |                                                             |                         |          |             |               |         |              | FOFFUOL      |

| 5  | :         |              | 1 (X+12)                                                    | *****11*                | A.L.X.X. | x.12, x, x, | 15 . 1 . 01   | ,×,F(1, | 6,1),        | FOFFUOS      |

|    | 2.61      |              | F(6,15,1),F(4,4,-1),F(4,12,-1))<br>AND 1/2,F4,C1,2,F2) D(0) |                         |          |             |               |         |              | FDFFulle     |

| ?  |           | NA10<br>1000 |                                                             |                         | )        |             | 0(0)          |         |              | FDFF00       |

| á  | 2.82      | NAND         | 1 (                                                         |                         |          |             | 0(0)          |         |              | FOFFUOR      |

| à  |           | VANU         | 112.14                                                      |                         |          |             | 0(0)          |         |              | FDFFUQ       |

| 10 | 2.14      |              | 112.13                                                      |                         |          |             | 0(0)          |         |              | FDFFU10      |

|    | 4.15      | NAM()        | 1(2,+4)                                                     |                         |          |             | u ( 🖓         |         |              | FOFFUL       |

| 11 |           |              | 062,13                                                      |                         |          |             |               |         |              | FOFFOId      |

| 12 | 2.00      | NANO         | 11:12.1                                                     |                         |          |             | C(UN)         |         |              | FDFF01:      |

| 15 | •         |              | Drinde                                                      | 491)                    |          |             |               |         |              | FOFFOID      |

| 14 |           | MENO         |                                                             |                         |          |             |               |         |              | FOFFULS      |

| 15 |           | 44640        |                                                             |                         |          |             |               |         |              | TUUTUUI      |

| 10 | 2         | 10019        | (IAI)                                                       |                         |          |             | 0(+)          |         | 0(00,01)     | TOUTUO       |

| 17 | •         |              | 1180203                                                     |                         | X+X+X)   |             |               |         |              | TOUTOON      |

| 18 | 2.+       | 54 N.C       | 1(41)                                                       |                         |          |             | 0(+)          |         | D(00,01)     | TOUTUOS      |

| 19 |           | 18 N 2       |                                                             |                         |          |             |               |         |              | TUUTUOS      |

| 20 | ****      | ****         | ****                                                        | ****                    | ****     | ****        | ****          | ****    | ****         | ****         |

| 21 |           |              |                                                             | F 1 P                   | CUIT DES | CH1P11UN    |               |         |              |              |

| 22 | ****      | ****         | ****                                                        |                         |          | ****        |               |         | ****         |              |

| 0  |           | NETSTA       |                                                             |                         |          |             |               |         |              | EHSD001      |

| 1  |           | OLCR1A       | 1114,00                                                     | , (H)                   |          |             | 0 ( A , A)    | N 3     |              | EHSDUD       |

| 2  |           |              | -111641                                                     | 10,511                  |          |             |               |         |              | EHSUND       |

| 5  |           | DUCHAA       | 1714,00                                                     | . [4]                   |          |             | C(B,B)        | N )     |              | EHSOUD-      |

| 4  |           |              | 01 91 51                                                    | , 0, 2A)                |          |             |               |         |              | EHSDOOS      |

| 5  | C C       | 01 C 4 + A   | I ( A. A.                                                   | 19)                     |          |             | 040.00        | N 1     |              | EHSDUG       |

| 6  |           |              | 1115.20                                                     | 1, 5, 24)               |          |             |               | .,      |              | EHSUUD.      |

| 7  | U U       | "LLRNA       | 111410                                                      | (*I*)                   |          |             | 010.0         | ~1      |              | EHSDUD       |

| 8  |           |              | 5111.51                                                     | +11+31)                 |          |             |               |         |              | EHSUUDY      |

| 9  | t         | OLCHIA       | 1114, 84                                                    |                         |          |             | ULEVEN        | ~ )     |              | E450010      |

| 10 |           |              | 717,31,                                                     | 17.151                  |          |             |               |         |              | EHSDU11      |

| 11 | ۶         | PLCKYA       | 1110,00                                                     |                         |          |             | OCL.F         |         |              | EHSDU1       |

| 12 |           |              | 0114.11                                                     |                         |          |             |               | .,      |              | EHS0013      |

| 3  | 04        | ··           | 11.5.8                                                      |                         |          |             | (( <b>A</b> ) |         |              | EHSDU14      |

| 14 |           |              | Cra. 191                                                    |                         |          |             |               |         |              | EHSOU1:      |

| 15 | 09        | 141122       | 110.041                                                     |                         |          |             | 0(00)         |         |              | EHSDU1       |

|    |           |              | 114,103                                                     |                         |          |             |               |         |              |              |

| 17 | ũ.C       | 141.22       | 115-5.4                                                     |                         |          |             | 0.003         |         |              | EHSDU1/      |

| 18 |           |              | 110.000                                                     |                         |          |             | erout         |         |              | EH5001a      |

| 9  | un.       | Sec. 12      | 1/0, AND                                                    |                         |          |             | 1. ( D.). A   |         |              | EHSDU14      |

|    |           | 1.1          | U/4.101                                                     |                         |          |             | 0(00)         |         |              | EMSOUL       |

| 21 | DF        | 541-03       | 170946                                                      |                         |          |             |               |         |              | LHSOUZI      |

| 2  |           |              | 011211                                                      |                         |          |             | D(LF)         |         |              | F420155      |

| 55 | F 5 H     | 4 5 R        |                                                             |                         |          |             |               |         |              | FW20053      |

|    |           | e 30         | 115                                                         | NZ.UI.F                 | 5 J      |             | 1(F58)        | )       |              | FHSUNSA      |

## fig. 4

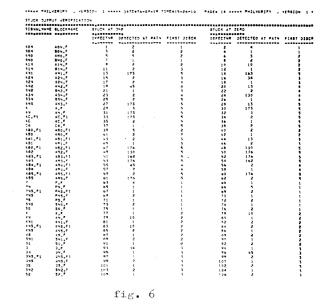

To check the logic behaviour against the original specification a time dependent logic simulator is used. The designer "feeds" his circuits by describing the input pulses and he gets back the response of the circuit as calculated by the computer. (See Fig. 5.)

A loop of checking and changing the logic set-up is started until the specifications are met.

At this moment the description is fixed and this one will be used by each consequent step.

It is very nice to have a functional working circuit, but it is useless if it cannot be tested. One has to make sure that not only testing can be done, but that it can be performed on a production basis, which means on a standard automatic tester in a short time. For this purpose the test engineer works with a logic test verifier which deals with logic stuck at one/zero defects and a program that generates the d.c. parametric tests. With these aids he is informed about the defects which can or cannot be detected, how efficient the test sequence is, etc. (See Fig. 6.). As LSI test equipment is not cheap, this is an important step which, if not carefully handled, will cost a lot of money afterwards.

fig.5

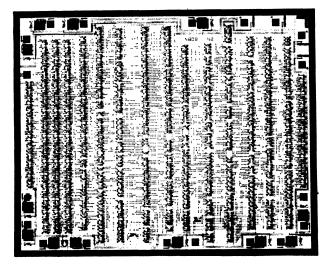

Once the logic has been designed and it has been proven that testing is not a problem, the layout phase can be entered. As all information to generate the layout is available this is not a large problem. Because of the constant height of the cells it is obvious that they are placed in rows. This is in our system done by hand as we have seen sofar that in general the designer can come up with a starting solution which is even as good as one produced by a computer program, but at far less costs. The placement information is added to the original network description and also stored in the computer. As both the interconnection scheme (derived from the net-work and placement) and the cell layout (retrieved from the library) are known, an automatic wiring routine is able to generate a double layer interconnection pattern, The outcome is presented to the designer (see Fig. 7), and as the first shot in placement never is 100 % good as well as the wiring algorithms, which do not take years, are not 100 % optimal a loop starts of iterative and partly interactive man-machine work.

#### fig. 7

The program calculates the contribution of the wiring to the circuit delay and this is fed back into the network. This enables the designer to make a final check of his logic with the actual final layout data. After this is accomplished we end up with two magnetic tapes, one is driving the mask pattern generator and the other is to control the automatic tester.

#### Production requirements

The system as described above is not new in its set-up but several systems like this have never come further than the research buildings although they are only worthwhile to develop if they are used for production purposes because here is where cycle time, hit rate and design efficiency are directly related to money or market position. A CAD system for production purposes has to

cope with several aspects which seem to be contradictory. You have to design faster, but chip area may not grow. You have to be advanced but the failure rate must be lower. You are forced to standardise, but flexibility for specialties and design freedom may not be cut down to zero. The way of operation in the design cycle has changed drastically, but it must be easy to learn for existing designers, etc. So more factors are involved than just that the system produces a good chip. Searching for acceptable compromises the following starting conditions were formulated:

- . Develop the system not in research but in the middle of the users, step by step, not starting from a complete specification, because full specifications of a really new approach tend to contain more wishfull thinking and utopia's than realistic thoughts about tools for daily use. The constant feedback of users gives better information of what is really needed next.

- . Do not use initially high professional programmers because they do not understand the design world nor do designers

- speak programmers slang. . Use a small computer to do the job, so

- one is not invited by the hardware to be wasteful, minicomputers are becoming cheaper, no large system-overhead costs have to be paid and one can schedule the machine without being pushed off by accounting-, salary-, sales- and management programs which have always higher priority. Designers need fast turnaround.

- . Do not try to make the computer "creative" because per definition she is not, and simulating that costs a lot of dollars.

- Do not give a designer more information than he is asking for because either he does not want it or he is not yet susceptible for it; in both cases it is a waste of effort, paper and money.

- Put more emphasis on the fact that the algorithms are 100 % safe rather than 100 % optimal and allow adjustment by the designer.

- A circuit should only be described once during the design cycle, to avoid translation errors, and double checking.

- . Make the system transparent to future users, not a magic black box.

## Hardware and algorithms

Keeping these things in mind the LOCMOS design system is developed on a small 64 K/16 bit word oriented computer, disc and magnetic tape backing store, a tektronix storage display and a plotter. As in the first place the aim was to be safe the algorithms in use are reasonably well

established.

The model in the circuit analysis has been kept simple and the number of nodes that can be calculated in one run has been kept to maximum 100. The reason is that if one has to do circuit analysis in detail on a complete LSI to get the last nano-second

out, the production never will be able to make such a product with reasonable yield. So for the normal applications a cross check between model and production was made. The time delays as function of the fanout were calculated and these factors are automatically produced when the network is entered in the computer.

The simulator/verifier uses a slightly modified version of the look ahead algorithm as described by Ulrich 1). Here a lot of attention has been paid to features which are not absolutely necessary but which make it easier to detect errors, make sure everything has been excercised, warm starts, etc.

In the layout phase the partitioning, if necessary, and the placement of the cells is done by hand. Here the knowledge of the designer who has struggled with his product during the logic set-up is used, rather than to excercise with an algorithm. This has two reasons. In the first place the computerprograms are not yet so extremely clever, that they beat the designers' brains evidently and second, because of the reason just mentioned the man still has to make himself thoroughly acquainted with the computer placement to be able to do the final optimisation and this costs as much time as doing it himself right from the beginning and he is more involved. For the wiring a combination is used of the algorithms described by Lee  $^{2}$ ) and the one mentioned by Schweickert  $^{3}$ ). It is a routine, for two layer wiring, consisting of aluminum and polysilicon. The algorithms used do not give in all cases the optimum solution, as they are also dependent upon the placement. For this reason the possibility has been built for the designer to interact with the machine in front of a storage tube display. He may shift, replace or add cells in a row, as well as change the wiring which is produced between rows. All changes are controlled and checked against the original network.

Although we are rather confident that the existing program is error-free, we still do a cross check at the end. Having the wiring and the cell placement, we generate via a separate procedure a network and compare that with the original one. In this way we are absolutely sure that the circuit on the slice is the circuit we developed.

When special blocks have to be incorporated, like large output stages, a complete ROM, etc., not only the logic connection is checked, but also whether these items and connections, as they have to be brought in by hand, fulfill the process design rules. To generate a ROM we have a special program that produces the layout starting from an adress-content table. The complete ROM is then placed in the reserved area in the total circuit.

To check the layout when cells are generated and when larger portions are glued together a program is available with extensive features on design rule checking and pattern manipulation both in batch and interactive mode.

### System Failures

Up to now about one hundred circuits have been developed with the LOCMOS design system. Their complexity ranges from 700 to 1800 gates, plus ROMs and RAMs with chip areas up to 22 mm<sup>2</sup>. Two of them did not meet the original specification. On the first one it turned out that a part of the function never was correctly simulated and by consequence failed. On the second the program had not given adequate information about the delay added by the wiring. The total amount was given but the long delay line effect that came together with it was not taken into account. So one is to blame the system, for the others the first

## Design Cycle

shot was correct.

Development of the network, special cells, if needed, and logic simulation until checked circuitry takes 2 - 3 man-months depending on the complexity. Generating an adequate and efficient testsequence requires about 4 - 6 weeks. The designer needs 3 - 6 weeks to generate the layout. In this period he is able to change his philosophy regarding the placement a couple of timescompletely and to do optimisation on each of them.

When the specification of an existing design changes, all information is still available and if just a couple of gates have to be changed, only a few computer runs are necessary. When a larger part is altered some weeks may be involved.

#### Hand-versus Machine layout

A couple of designs, made by hand, have been taken and reworked with the help of the machine. It turned out that the designer working with the system, generates the layout on the same chip area with a factor varying from six to nine gaining in time. The most important point was however, that the hand-layouts contained errors which indicate that it is nearly impossible to make a circuit of up to 8000 transistors of mostly wild logic, error-free in the first go.

The reason for this result is that the cells themselves are made without sacrificing area to the fact that they have to fit into a system. That is why they are called COMPACT LOGIC cells. Also the fact that the wiring can approach a cell from both sides has the advantages that the algorithms can be kept simple and that no extra area is lost by going across or around a cell.

## Education and Transfer

Both a company like Philips, which comprises several design centres, and the LSI-design field itself, with its large variety of customers, require that a CAD system can be learned easily.

When it takes half a year or more before a man is able to use CAD, the benefit is already coubtfull and it will be very difficult to get such a system accepted as a tool for

#### day to day use.

Besides, a manufacturer never can have all the knowledge of the different fields of technology as e.g. computer industry, telephone equipment, consumer electronics, military developments etc. So it must be possible to teach a customer how to use the system and to be sure that the product he designs with it works according to specification.

Both for internal and external customers a course is given of one week and in the week following some guidance is offered when they start their designs. After that they work on their own, also outside customers, which may be illustrated by the fact that one customer designed a 15000 gate system divided over 12 chips after following the course by sending carddecks and inspecting the computer outputs which were sent back. We as a manufacturer do not know the contents of the chips with respect to the logic functions but we produce and test the parts and we have seen the final system working.

As several centres must be able to use the system and not all have the same computer equipment, machine language could not be used. This may be considered as a drawback because programs written in high level language tend to take more core and some more run time but the advantages are more important. The programs can be transfered easily, which is impossible when machine code is used. Coding and debugging costs less money and more people are able to understand what is coded so the system does not die when the programmer leaves.

#### Summary

The LOCMOS design system is in use completely in five different centres and partly in another four. A group of 3 programmers is available to maintain an expand the program possibilities.

As testprogram- and layout- generation go in parallel the typical turnaround time for a circuit of 1200 gates from start to tapes for mask and tester is four months. The computer expenses amount to about 3300.--.

So in half a years time it is possible to make parts which are correct in the initial version and that is exactly what the product manager is looking for.

E.G.Ulrich Communications of ACM Vol 12/2

C.Y.Lee IRE Transactions on electronic computers Vol EC-10

3. D.Schweikert e.a. Proceedings of the 10th design automation workshop.

## FROM THE EDITOR

This issue is almost entirely devoted to material from the recent 13th Design Automation Conference held in San Francisco June 28-30. It is being sent (complements of SIGDA) to all attendees, in the hope that nonmembers of SIGDA will decide to join the group. All of the papers included here are ones which were refereed for and presented at the 13th DAC, so the material should be of interest to a wide audience. Hope you benefit from it!

The next (December) issue copy deadline is October 27; once more I encourage your contributions to this Newsletter.

Rob Smith 8/20/76

P.S. Join SIGDA -- if you're not now a member!

Errata for 13th DA Proc. (Jones/Nelsen paper) page 349: Table 5: line 2: change "10,000,000" to read "1,000,000".

## CLUSTERING METHODS AS PARTIAL SOLUTIONS TO THE SPACE ALLOCATION PROBLEM

## Robert Simpson Frew PhD Associate Professor Yale School of Architecture New Haven, Connecticut 06520

#### Abstract

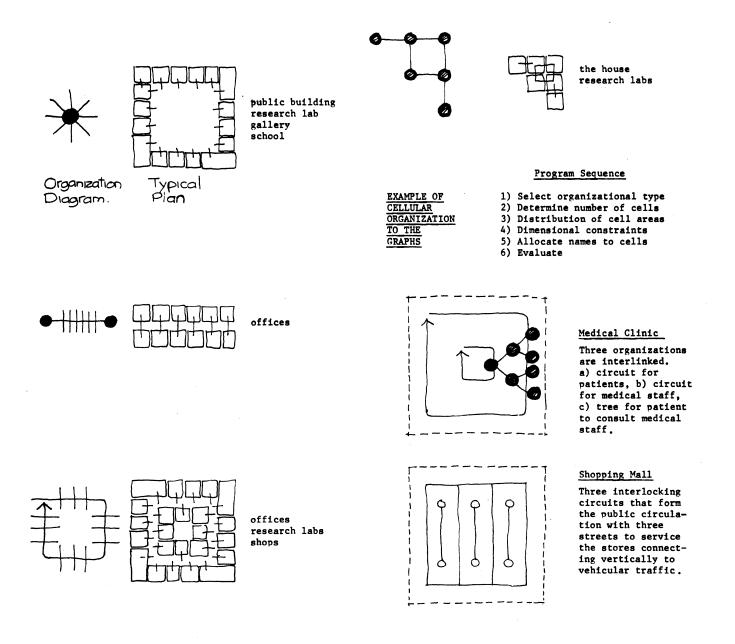

The paper presents a three phase approach to the space allocation problem. The first phase is to identify the activities that can be considered as members of component groups by classification methods. Secondly to find organizational form for each of the groups and to locate the members into the lavout. Thirdly to find organizational form for the whole system and to locate the groups in the system.

#### Introduction

A survey of space allocation procedures will produce many hundred procedures. From early work by Whitehead and Elder and by Buffa and Armour procedures have been generated from many different viewpoints. The problem presented by Whitehead and Elder was to find the optimum layout for an operating floor of a hospital given (a) the activities that had to be located, (b) the personnel and their relative salaries, and (c) the frequency of movement between activities by different personnel groups. The criteria used in this work was to minimize travel cost computed as the distance x frequency x personnel salary (by group). In general the space allocation problem is one of finding the spatial configuration and the allocation

of specific activities to the configuration, given a criterion function.

#### Existing Methods

It is not intended in this paper to cover all of the methods that are available for space allocation, but rather to illustrate a few recent developments. The methods can be considered as (1) heuristic (2) enumerative (3) dissections and (4) classification.

#### Heuristic

Until recently all of the approaches were heuristic. In the majority of cases the procedure is to select an activity, locate it and then select another and locate it in the best location relative to the first, and so on until all activities were located. ALDEP and CRAFT are examples of this approach. The problem of this approach is in the selection of the first activity to place, and to establish the order of the activities. A solution to this problem was presented at the DAC Conference in 1971 in Dallas by the author. The solution used a classification method to find the ordering of the elements, thus increasing the probability that an optimum could be reached.

Enumeration In "The Animals of Architecture" by the author<sup>1</sup>

a list of the enumeration of polyominos (configuration of connected squares) was reported from research carried out by Read<sup>2</sup> and Lunnon<sup>3</sup>. In a further article

by Matela and March entitled "The Animals of Architec-

ture. A Census"<sup>4</sup> the enumerations were analysed to identify coefficients that would reduce the set of polyominos to a manageable size, given different criteria for the coefficient. The advantage of enumeration is that once a complete set of configurations exists, then it is only necessary to look through a catalogue to find the one configuration that is needed in the specific case. The disadvantage is in finding a coefficient that is able to discriminate and also be relevant to the different design problems that are encountered. An interesting offshoot of this work is the enumeration of bridges or cutsets that are possible within a polyomino. This work will be useful in arriving at layouts for houses given that there is a need for a certain number of component groups and a total number of activities. For example, in a house with nine activities in three groups the scanning procedure would simply find all nine cell configurations with two bridges or cutsets. Further analysis would determine which layout to select. Future work in this area will be useful in building design problems when coefficients can be generated to reflect the design criteria.

#### Dissections

Recent work by Steadman<sup>5</sup> and Mitchell<sup>6</sup> is based

on the graph theoretic work of Tutte<sup>7</sup>. The work on dissections is a subset of the general space allocation problem. In dissection enumeration there is the constraint that each configuration must be contained by a simple rectangle. Mitchell<sup>8</sup>, in recent work has a simple rectangle. Mitchell<sup>8</sup>, in recent work has produced a design system using the dissection enumeration; the system searches the catalogue of dissections to find all those that match the graph properties given by the user. By means of a non-linear program the dissection is adapted to specific dimensions. The application of this system would seem to be constrained to the level of complexity of a house. The computation necessary to dimension a configuration greater that three cells in depth becomes unreasonable due to the amount of computation time. The advantages of this enumeration are similar to the enumeration of polyominos; however, the design system by Mitchell<sup>9</sup> shows the usefulness of the theoretic development.

#### Classification

Classification methods were first generated by biologists who needed to separate different animals or cells into classes or families or species. The work in biology developed by Sokal and Sneath<sup>10</sup> has been applied in a design system by Mitchell<sup>11</sup>. The same functional operation of classification can be found in electrical engineering. By the operation of cutset analysis a set of component groups in a system can be found. This work has been applied to design by Tabor<sup>12</sup>; the classification is represented in the form of a dendrogram which illustrates how the system is broken down into its components. Work in the social sciences on factor analysis methods by Horst<sup>13</sup> and Harman<sup>14</sup> can also be considered as a classification method. This

work has been applied to design by the author <sup>15</sup>. In previous work, classification methods have

been used as a partial solution to the allocation problem. Let us consider the allocation of 9 cells. If we classify the data matrix given to relate the 9 cells and find that three groups of 3 cells are formed, then only approximately 200 solutions exist for any one configuration. If on the other hand we had to allocate each cell to a location in any one configuration, then approximately 360,000 solutions would be possible. By classifying the data we are reducing the selection to one in 200 from one in 360,000. For a complete reference to the methods associated with classification and the disciplines from which they

## come refer to Ball<sup>16</sup>.

The development from heuristics to enumerations would seem to have been generated by a need on the part of the researchers to develop a theoretic framework for the subject. This would appear to have been achieved.

Although it is important to develop such a theory it also seems important to find the correct relationship between the environment of the problem and the methods involved. In early work on the subject it was assumed that there was significance in using travel cost as a criteria; however, it is obvious that this is not significant at the building scale. In house design it is possible to use the travel cost criteria indirectly to find the optimal layout to give privacy in the different sections of the house, the objective being to minimize the amount of internal partitions. Outside of these two specific problems, and those that are only economic in nature such as the factory, the space allocation problem is not one of optimization. The problem is to find the level of building organization that is appropriate to the use of the building.

#### The Environment Of The Problem

The type of problem to which this method can be applied is one where there is a large number of different activities. It is increasingly common to find that large organizations have a diversified network of administrative control and that it is difficult to find one person who can identify the needs for a new building. Universities and research facilities are typical of this type. The groups that can be identified in such situations may be classified as follows; a control group consisting of the personnel in administrative control ie. Presidents and Vice-Presidents in a research group or the Dean and Department Chairmen in a university group. The second group is composed of all the personnel who have a particular functional unit in the organization under their control. This could be the director of a lab or an individual who is conducting a specific project. The design analysis that is carried out is based on information collected from the individuals described in the second group and presented to the control group for verification. The process that developes between the designers, control group, and researchers is one that clarifies the needs of all three groups. The method to be described is the method that the designers would use to arrive at the spatial allocations for each itteration of the method.

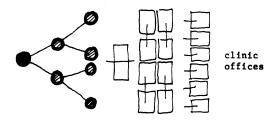

#### The Method

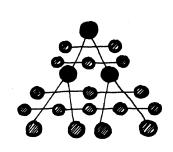

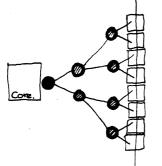

The method of space allocation has three distinct phases. The first phase is to find by classification the component groups of the system. The component group in a research facility could be the group of individual research activities that cluster together because of common service requirements or because of the free exchange of ideas between researchers. The second phase of the method is the analysis of the component groups to find out if there are characteristics of the group that would help in the selection of a spatial organization. The selection of a spatial organization for each of the component groups is also part of this phase. The third phase is to find a spatial organization that will be used to organize the component groups into a total system. As Allen has described "the gatekeeper" in communication terms, we will use the same term to refer to those activities in a building that organizes the component groups and in themselves form a network with other gatekeepers to organize the complete system.

Phase 1

The first phase is to classify the elements, or activities, into their component groups. The information collected for the analysis can vary considerably, refer Frew . In different building

types different criteria will be important. In Allen the criteria has to do with where personnel found their ideas for research. The resultant classification identified the personnel type known as "the gatekeeper." From an operational standpoint, the matrix that is most useful in space allocation is the one where the matrix represents all of the criteria that can be used to determine a physical connection between two elements. or where it is advantageous to minimize the distance between two elements. The information is represented in the form of a matrix D where the elements of the matrix represent the connection or lack of connection of the elements of the system.

For any two rows in the matrix a distinction must be made between  $D_{ij} = D_{ji}$  (direct relation)

and  ${}^{D}_{ij} \neq {}^{D}_{ji}$  (associative relation). Any resultant classification must keep the direct relation  $\geqslant$  the associative relation as the direct relationship is a given condition. Consequently, the comparison of rows will produce an intercorrelation matrix I which, when combined with the distance matrix D, will produce a matrix R which will have the characteristic as follows.

It will have the elements in the same rank order as D and have the further discrimination of the intercorrelation matrix I. The values of the elements of the R matrix indicates the strength of connection between the members represented in the element. To find the component groups, firstly order the elements in R from strongest to weakest, then sort each element of the matrix from the strongest down into different groups, each time checking to make sure that neither member of the element is present in a previous group. If either member is present, then that element becomes part of that group. The process continues until all members of the system have been accounted and the exact composition and number of component groups established.

#### Phase 2

From existing algorythms this phase would be to find the pattern that is the best fit to the data matrix that was originally generated. One weakness of these algorythms is that they use data that is either in distance terms or in terms of required boundaries; consequently, the process used generates patterns that are normally free form and with numerous cells that are completely enclosed by other cells. The determination of the closed packed pattern or the open pattern is a function of the scale used in the original data matrix. Similar problems occur in cellular assembly and rectangular dissection programs. At the level of 10 cells the foregoing programs are adequate. At the level of 100 cells they are not. The 100 cell case is typically a hospital or research facility. In these cases the phase, after finding the component groups, is to find the organization of paths that will be used to connect the cells or activities ie. corridors.

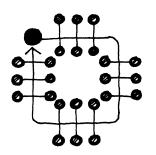

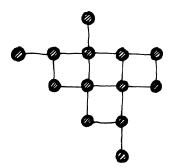

Let us look for a moment at the number of possible organizations of paths that exist. At a fundamental level it is the author's contention that there are not more than five types that can be assembled in combination with other types to create the building form. The types are:

1) Centralized Activity. Where one activity

such as a waiting room is isolated as the activity to organize all other activities in the component group. The qualities that are apparent in this type are:

minimum distance between cells, minimum privacy, greater potential for an informal environment.

2) <u>The Street</u>. Where an additional element is added such as a

corridor or, if expanded in scale, an activity can be a street or meeting place. If the street is only entered from one side, then one is able to design an environment that is controlled and secure.

3) The Circuit or Loop. This type is sometimes

known as a courtyard form due to the negative space created by the circuit form of the layout. It is more common in low rise buildings, although it is found as the top or top two stories of large bulk buildings such as Place Bonaventure in Montreal. This form gives the designer the ability to create a secure environment and

gives maximum distance between cells.

zation of cells where the user is guided to his destination by a sequence of decision points or branches. This form gives the opportunity to clearly identify the levels of authority in an organization if they exist. It is a system where the user must be given information at each branch. Control and security can

be designed as required and each cell will have a different level of privacy depending on the location of the cell in the system.

5) The Cell as a Path. Each cell can be considered as having a path as part of its function. A house is often considered as this especially among the daytime activities. The qualities that one can obtain from such an organization are to minimize any set of distance requirements and also to minimize the degree of privacy that is possible in each cell.

Organization Diagram for Multi-Cellular Structure

Simple tree structure to provide pedestrian access with the private offices organized as a circuit on the

outside face of the building.

Offices

## COMBINATION OF FUNDAMENTAL ORGANIZATIONAL FORMS

Although the subject has been limited to the organization of activities to facilitate human usage, it is also possible to apply the organizational forms to the sub-systems of a building. In applying them to the sub-systems the objective would be to identify the design problems that would arise from the overlap or intersection of the sub-systems.

To select one of the five organizational forms for the component group is not an obvious process. It would seem that the most rational way to do this would be to analyze the original matrix and determine the best fit between pattern and matrix and thereby select consultation with graph theorists. the best. On it would seem that there is not at present a method for making such a selection. Since there can be only five space allocations for each component group, it is suggested that all five be produced or that the obviously unfeasible solutions be dropped and only those that meet the higher level qualities described against each type be continued. For example, a component group that requires maximum privacy for each cell would not consider a centralized activity type as feasible. The selection procedure is one of excluding the unfeasible types and carrying all others to the next phase.

#### Phase 3

The organization of the component groups can be determined by analysis of the qualities of the individual groups. From the original data matrix one can determine a ratio between the number of elements that define the internal cohesion of the group and the number of elements that define the connections of the members of the group to the other members of the system. In a recent study of the requirements for an expansion to a research facility it was found that the chemical group had a very high ratio. Almost 100 percent of the connections were internal, whereas the design group had a very low ratio indicating a need for central location and easy access to other groups. In this particular example the existing facility determined the allocation at this level. If this had not been the case, then the ratio could be used as a simple gravity measure. In addition, the summation of the values of the connections between the groups can be used to locate the groups relative to each other.

On closer analysis of the component groups, one may find that there are one or two cells that have greater connection to the whole system than to the particular group. Such cells are known as "gatekeepers" and can be used to represent the group in arriving at the space layout for the whole system. The method of finding the layout at this level is the same as previously described ie. by carrying out a space layout for each of the organizational types. As can be seen in the clinic example there is a need for exploration of overlaping types which puts a demand on the computer system for greater user input which can be provided through interactive graphics with large computation and storage ability.

#### Conclusion

As Eastman<sup>18</sup>has described in data base design for building design problems, there are three levels of information that must be stored. They are:

- a) topological information of the elements

- b) dimensions

- c) location in the particular instance

In this paper it is also recommended that the computerized process of considering the arrangement of rooms in a building be as follows:

- a) identify the component groups

- b) select topological organization types for groups

- c) locate groups and identify system organization.

- d) give dimension to the elements

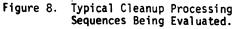

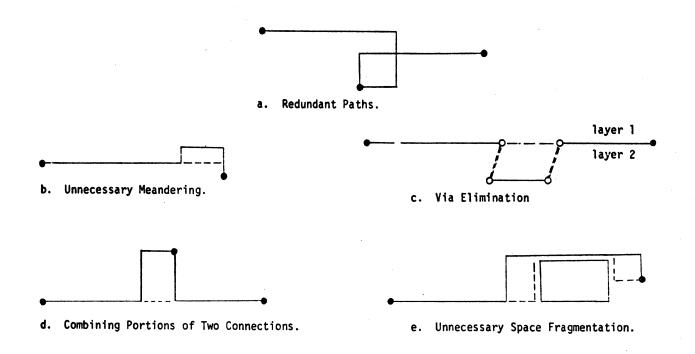

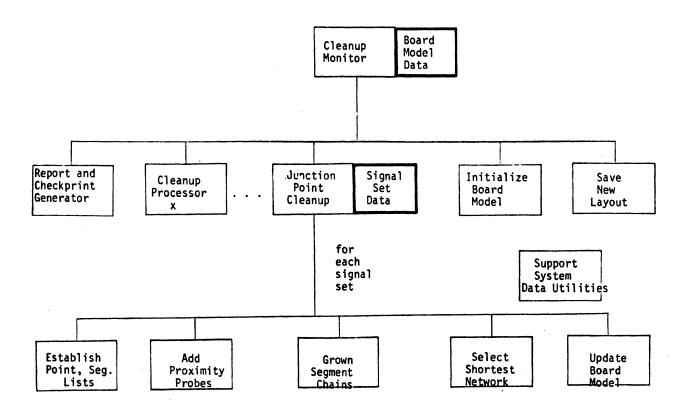

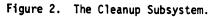

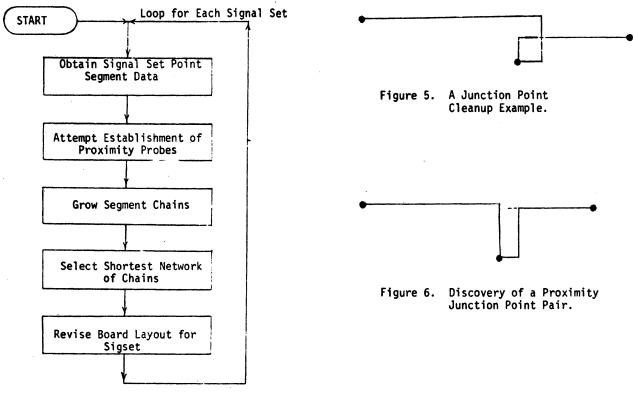

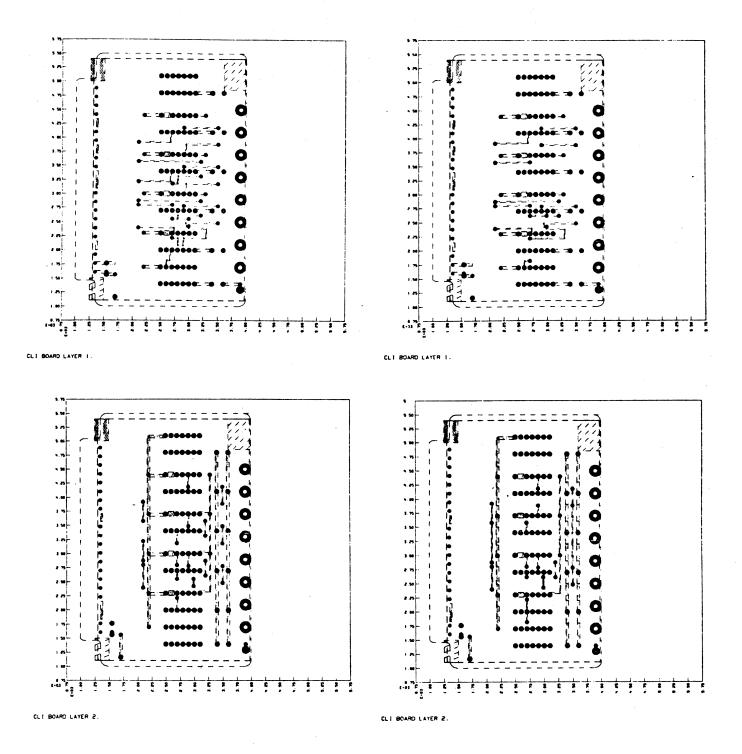

In conclusion, it would appear that too much attention has been given to establishing theoretical framework to look at the space allocation problem which has now developed to the point where application in computer aided design is unlikely, although contributions have been made to the original graph theoretic issues raised by Read, Tutte, and Harary. It is the environment of the problem, ie. the nature of the design process and existing buildings, that create the criteria for generation of computer aided design systems. The system described in this paper is in a preliminary stage; computer programs are not complete but will be developed in the next year.