# CM SIGDA NEWSLETTER

# SPECIAL INTEREST GROUP ON DESIGN AUTOMATION

# VOLUME 4 NUMBER 2 JUNE 1974

# **Contents:**

| Editor's Message                                                                                                                                      | 1  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Chairman's Message                                                                                                                                    | 2  |

| Call For Papers                                                                                                                                       | 3  |

| Program for the 1974 Design Automation Workshop,<br>June 17-19, W. M. Hall, General Chairman                                                          | 7  |

| Working Papers:                                                                                                                                       |    |

| "GazelleAn Interactive Graphic Logic Design System"<br>W. H. Sass, International Business Machines Corp.                                              | 10 |

| "Bibliography on Algorithms for Shortest Path,<br>Shortest Spanning Tree, and Related Circuit Routing<br>Problems"<br>A. R. Pierce, Bell Laboratories | 29 |

| A, R, FIELCE, DELL LADULALULLES                                                                                                                       |    |

## ADDRESSES

CHAIRMAN: Charles E. Radke IBM Corporation (B99/951) P. O. Box 390 Poughkeepsie, New York 12602 (914) 485-7775 VICE-CHAIRMAN: David W. Hightower Bell Labs 2B312A Holmdel, New Jersey 07733 (201) 949-6549 SECRETARY/TREASURER: Lorna Capodanno Bell Labs 2C169 Murray Hill, New Jersey 07974 (201) 582-6909 CO-EDITOR: Robert J. Smith, II Southern Methodist Univ. Dept. of Computer Science Dallas, Texas 75275 (214) 692-2859 CO-EDITOR: Stephen P. Krosner IBM Corporation (96N/002) P. 0. Box 1328 Boca Raton, Florida 33432 (305) 391-0500 (4052) TECHNICAL COMMITTEE: David W. Hightower, Chairman MEMBERSHIP COMMITTEE: Lorna Capodanno, Chairman PUBLICITY COMMITTEE: Lorna Capodanno, Chairman BOARD OF DIRECTORS: John R. Hanne Texas Instruments P. O. Box 5012 (MS 907) Dallas, Texas 75222 (214) 238-3554 Steven A. Szygenda Department of Elec. Eng. University of Texas Austin, Texas 78712 (512) 471-7365 Donald J. Humcke Bell Labs 2C-318 Holmdel, New Jersey 07733 (201) 949-6253 Larry Margol Micro Electronics Division Rockwell Instruments D/734-057 Box 3669 Anaheim, California 92803 (714) 632-8565

> Charles W. Rose Computing & Information Sci. Case Western Reserve Univ. Cleveland, Ohio 44106 (216) 368-2800

#### MEMBERSHIP

SIGDA dues are \$3.00 for ACM members and \$5.00 for non-ACM members. Checks should be made payable to the ACM and may be mailed to the SIGDA Secretary/ Treasurer listed above, or to SIGDA, ACM Headquarters, 1133 Avenue of Americas, New York, N. Y. 10036. Please enclose your preferred mailing address and ACM Number (if ACM member).

#### SIG/SIC FUNCTIONS

Information processing comprises many fields, and continually evolves new subsectors. Within ACM these receive appropriate attention through Special Interest Groups (SIGs) and Special Interest Committees (SICs) that function as centralizing bodies for those of like technical interests ... arranging meetings, issuing bulletins, and acting . as both repositories and clearing houses. The SIGs and SICs operate cohesively for the development and advancement of the group purposes, and optimal coordination with other activities. ACM members may, of course, join more than one special interest body. The existence of SIGs and SICs offers the individual member all the advantages of a homogeneous narrower-purpose group within a large cross-field society.

#### ACTIVITIES

- Informal technical meetings at SJSS and FJCC.

- 2) Formal meeting during National ACM meeting + DA Workshop.

- Joint sponsorship of annual Design Automation Workshop.

- 4) Quarterly newsletter.

- 5) Panel and/or technical sessions at other National meetings.

FIELD OF INTEREST OF SIGDA MEMBERS

Theoretic, analytic, and heuristic methods for:

- 1) performing design tasks,

- 2) assisting in design tasks,

- 3) optimizing designs through

the use of computer techniques,

algorithms and programs to: 1) facilitate communications

- facilitate communications between designers and design tasks,

- 2) provide design documentation,

- evaluate design through simulation,

- 4) control manufacturing processes.

# EDITORS MESSAGE

It is with great pleasure that I welcome Bob Smith from SMU as co-editor of the SIGDA Newsletter. It is our intent to increase the technical content of the Newsletter. With Bob's excellent contacts in academia we hope to increase the number of items available for publication.

This issue has another fine bibliography as well as an article from last years ACM conference that didn't get published there.

Future plans include publication of more bibliographies covering all aspects of design automation. Bill Van Cleemputt from the University of Waterloo has sent me an extremely comprehensive (1500 item) bibliography. We hope to publish sections of it in the near future.

This years Design Automation Workshop has a fantastic technical program. There are over 50 papers being presented including 4 tutorials. The concept of an entry level tutorial preceding the technical presentation in major areas should be a great help to people wanting to hear papers out of their specialty. I hope to see you all in Denver on June 17th.

Steve Krosner

# CHAIRMAN'S MESSAGE

As I peer northward out my window and watch the traffic move across the Mid-Hudson Bridge, I see a full range of products of man's creation and design.

The suspension bridge which gracefully spans the Hudson River is unique and when designed probably used established technology and structural design techniques. One builds such a bridge "right" the first time. There is no early build and test.

Then there is the automobile, designed out of some standard and some specially designed parts, designed for appearance, comfort, and performance. The individual components are tested to assure that they meet specifications and then the assembly is built, tested, and as required changed to meet certain economic, market, and technical objectives.

On the other hand, the fence outside was designed to the extent that its intended placement was roughly staked out, visualized in the contractor's mind, the cost was quickly estimated, then it was built out of readily available parts.

One can easily visualize the use of computer resources to specify the fencing objectives against a plot plan and even to provide a 3-dimensional view on a graphic display so that the esthetics can be judged. An accurate cost estimate and a complete bill of material can then be outputted. To stake the fence out and erect it would still be left to the contractor.

However, to some it may be a little more difficult to visualize providing vehicle designs directly through the use of computer resources and against supplied technical and economic objectives, as it may also be to visualize the complete design of a suspension bridge which must be correct the first time.

But what was not visualized yesterday is often reality today. May I suggest that you attend the DA Workshop in Denver, June 17-18-19 to be brought up to date.

I'll see you there.

international conference and exhibition-computers in engineering and building design

Imperial College, London 24-27 September 1974

The success of the 1972 and 1973 conferences on computer-aided design has shown the need for a meeting that will bring together industrial users and research workers in all branches of c.a.d. CAD 74 will meet this need.

The dominant theme will be <u>engineering users</u> of c.a.d. - mechanical, civil, architectural, structural, chemical, electrical and control. Recent advances in computer-aided techniques and design methods, either already proven or under development, will be emphasized. Examples can be found in drawing offices, in stress analysis, in project management and in manufacture.

<u>Special c.a.d.</u> topics will be grouped into separate sessions. Examples are optimization, surface and shape description, and graphics. These special-topic sessions will concern themselves with developments in c.a.d. which will affect engineering in 2 - 5 years' time.

Apart from cost and time savings, computer methods have a considerable effect on organizations and people. The conference will, therefore, include sessions on the social implications of c.a.d., the teaching of c.a.d., and the design process itself.

Each session will comprise an invited survey of the state of application or research, followed by submitted papers on particular systems. Sessions are being planned so as to accommodate 100 papers.

#### CALL FOR PAPERS

Authors are invited to submit synopses of papers. Final date fo synopses is 31st May 1974 but early submissions will be given priority in arranging the conference sessions.

rapers should be sent to the Conference Organizers.

Conference Organisers

M. I. Dawes and G. W. Jones

Exhibition Manager

T. McGowran

Computer Aided Design IPC House 32, High Street Guildford, Surrey, England. Telephone: Guildford (0483) 71661 Telex: Scitechpress Press Gd 85556

# Needed - ADDITIONAL BOOK REVIEWERS

We have received a copy of COMPUTER-AIDED DESIGN for review. We are looking for two additional reviewers. Please contact Dave Hightower (address inside front cover) directly.

The book is the Proceedings of the IFIP Working Conference in Principles of Computer Aided Design, Findhoven, October 16-18, 1972, and edited by J. Vlietstra and R. F. Wielinga.

The Papers included in the Proceedings are:

- 1. The Scope of Computer-Aided Design.

- 2. Foundations of the many manifestations of computer augmented design.

- 3. Total technology Integrating design with production.

- 4. New Concepts in interactive Computing and their relationship to Computer-Aided Design.

- 5. The engineer's creative activity in a CAD environment.

- 6. Computer aids in system building.

- 7. Computer aided design an extension of man.

- 8. Methodical design, the basis of computer-aided design.

- 9. Software methods in developing CAD programs.

- 10. Program and information structures in computer-aided design.

- 11. Lifetime and evolutionary properties of applications software.

- Computer generation of symbolic network functions an overview.

- 13. Computer-aided system reliability analysis and optimization.

- 14. A system for computer-aided design in architecture.

- 15. Non-numerical problem solving methods in computer-aided design.

16. Computer-aided design in aircraft industry.

17. Computer-aided design using SYSFAP.

18. A plant and buildings draughting and scheduling system.

19. The application of computer aids to hospital building.

Reduced rates for SIGDA members: The publishers are offering the book at a discount to SIGDA individual members for their personal use. The book is offered at US \$19 if prepaid (list around \$23.20). Send orders to North-Holland Publishing Co., P.O. Box 211, Amsterdam or American Elseiver Publishing Co. 52 Vanderbilt Ave., New York, N.Y. 10017.

# BOOK AND JOURNAL REVIEWS

The SIGDA Technical Committee intends to review selected books and journal articles and publish the reviews within the SIGDA Newsletters; however, we are in need of additional reviewers. Send your name, address and area of interest to Dave Hightower (address inside front cover). More literature on Design Automation is being published and we feel this is one service we can provide for the DA profession.

#### JOURNAL - COMPUTER-AIDED DESIGN

A journal which we will start reviewing on a trial basis is "Computer-Aided Design" published by IPC Science and Technology Press Ltd. (IPC House, 32 High St., Guildford, Surrey, England). The journal is published four times a year and is devoted exclusively to the design-aided application areas.

Again we request those interested in reviewing articles to contact Dave Hightower.

The tables of contents for the last two issues are:

Vol 5, No. 4 October 1973

Computer-aided design in electron optics, P. W. Hawkes.

Computer aids in experimental nuclear plant design, R. K. Hilton.

The application of a computer to hopper design, N. Bundalli.

The balanced approach to process design by computers, H. P. Hutchinson and M. E. Leesley.

An analogue approach to surface definition, J. P. Bloomer, M. M. Sadeghi and G. N. Fedbring.

From words to wires by computer-aided design, A. H. Evans and P. Edmonds.

Vol 6, No. 1 January 1974

Cubic Spline fitting with controlled end conditions, J. D. Adans.

Graphics facilities for computer-aided architectural design, H. Sussock.

The BERSAFE finite element system, T. K. Hellen and S. J. Protheroe.

An integrated c.a.d. system for an architects department, J. W. Paterson.

The inefficiency of the adjoint network approach to the calculation of first order sensitivity coefficients, T.B. M. Neill

Computer simulation of a submersible vehicle, C. Wo and J. O. Geremia.

ELEVENTH ANNUAL DESIGN AUTOMATION WORKSHOP DENVER HOLIDAY INN, JUNE 17-19, 1974 H.M. WALL, GENERAL CHAIRMAN

II.II. WALL, GENEIVAL CHALMA

## MONDAY, JUNE 17

| 8:00 AM | PARTITIONING TUTORI | AL M. HANAN<br>IBM CORPORATION      |

|---------|---------------------|-------------------------------------|

|         | YOR                 | KTOWN HEIGHTS, N. Y.                |

| 9:00 AM | WELCOME TO DENVER   | P. O. PISTILLI<br>NGEMENTS CHAIRMAN |

| 9:05 AM | INTRODUCTION        | H. M. WALL                          |

GENERAL CHAIRMAN

9:20 AM KEYNOTE SPEECH STEPHEN J. LUKASIK

DIRECTOR OF ADVANCED RESEARCH PROJECTS AGENCY

DEPT. OF DEFENSE

#### 10:20 AM ANNOUNCEMENTS

#### 11:00 AM

"DATA BASE DESIGN FOR DESIGN AUTOMATION – A TUTORIAL" E. HASSLER, TEXAS INSTRUMENTS, DALLAS, TEXAS

# SESSION 1: LSI

CHAIRMAN: W. CREWS, MOTOROLA, MESA, ARIZ.

CHAINMAN. W. CREWS, MOTOHOLA, MESA, AMZ.

#### 1:30 PM

- "CRITIC: AN INTEGRATED CIRCUIT DESIGN RULE CHECKING PROGRAM"

- L. M. ROSENBERG AND C. BENBASSAT, RCA CORP., SOMERVILLE, N. J.

A production proven IC design rule checking program, CRITIC, which can berform prescribed or user specified physical description checks is described.

#### 2:00 PM

"MASTER SLICE LSI COMPUTER AIDED DESIGN SYSTEM"

Y. OZAWA, M. MURAKAMI AND K. SUZUKI, OKI ELECTRIC INDUSTRY CO. LTD., TOKYO, JAPAN

This paper presents an LSI-CAD system which is intended for practical use in masteristice LSI design and testing including five sub-systems, a common data file, and an on-line graphic display.

#### 2:30 PM

"ADVANCED LILAC – AN AUTOMATED LAYOUT GENERATION SYSTEM FOR MOS/LSI"

T. KOZAWA, H. HORINO, T. ISHIGA AND J. SAKEMI, TOKYO, JAPAN

An advanced automated layout design system with Celi, ROM SR, and PLA models for MOS\_LSI. The program can generate composite patterns for single chip micro computer MOS/LSI arrays from logic descriptions.

# SESSION 2: GRAPHICS I

CHAIRMAN: J. LOURIE, IBM CORP. NEW YORK, N. Y.

1:30 PM

"COMPUTER AIDED PROCESS DESIGN AND SIMULA-TION FOR FORGELS OF TUBBINE BLADES" N. AKGERMAN AND D. J. KASIK, BATTELLE COLUM-

N. AKGERMAN AND D. J. KASIK, BATTELLE COLUM-BUS LABORATORIES, COLUMBUS, OHIO

A system of computer programs, which utilizes interactive graphics and computer animation, for the design of the forging process for turbine blades, is the subject of this paper.

#### 2:00 PM

# "METASYSTEM: A HIERARCHICALLY STRUCTURED GRAPHIC TOOL"

N. P. DOONER, J. R. LOURIE, P. VELDERMAN, A. C. GUBIOTTI, AND A. KAUFMAN, *IBM CORP., YORK-TOWN HEIGHTS, N. Y.*

This paper explores an interactive graphic system built from a set of hierarchically structured functions. The one weres of each modiee and migimal infertace of modules is provided.

#### 2:30 PM

"AN INTEGER ARITHMETIC PATH EXPANSION ALGORITHM"

T. A. WEBER AND D. G. SCHWEIKERT BELL LABS, MURBAY HILL, N. J

Several algorithms essential to the plotting of an expanded slant-line path, for low resolution graphical displays, such as CRT's, have been combined and imbiemented.

# SESSION 3: PARTITIONING

CHAIRMAN: M. HANAN, IBM CORP., YORKTOWN HEIGHTS, N. Y.

3:30 PM

"AN INTERACTIVE MAN MACHINE APPROACH TO THE COMPUTER LOGIC PARTITIONING PROBLEM"

M. HANAN, A. MENNONE AND P. K. WOLFF, *iBM* CORP., YORKTOWN HEIGHTS, N. Y.

An interactive approach to the problem of partitioning computer logic which combines aspects of manual and automated approaches and creates results which are better than those obtainable by either approach independently is described.

#### 4:00 PM

"THE USE OF TOPOLOGICAL MODELS FOR THE CIRCUIT LAYOUT PROBLEM"

W. M. VANCLEEMPUT, UNIVERSITY OF WATERLOO, ONTARIO, CANADA

A state-of-the-art survey of topological methods for solving the circuit layout problem, including one model, which allows pin and gate assignment as a function of layout, is presented.

4:30 PM

"A PARTITIONING TECHNIQUE FOR LSI CHIPS IN-CLUDING A BUNCHING ALGORITHM"

P. T. WANG, IBM CORP., MANASSAS, VA.

This paper discusses a partitioning technique which initially orders circuits according to a scoring mechanism, and thus uses a two-stage interchange technique to arrive at a final partition.

# SESSION 4: GRAPHICS II

CHAIRMAN: N. P. DOONER, IBM CORP., YORKTOWN HEIGHTS, N. Y.

#### 3:30 PM

"A SIMPLE COMPUTER-AIDED ARTWORK SYSTEM THAT WORKS"

D. G. RESSLER, RCA CORP., SOMERVILLE, N. J.

A complete computerized artwork processing system for integrated circuits and printed circuit boards is described. The system includes digitizers, plotters, a design rule checker, and a pattern generator command program.

#### 4:00 PM

#### "AUTOMATED INSPECTION OF ELECTRONIC ASSEM-BLIES"

C. A. HARLOW, S. E. HENDERSON, D. A. RAYFIELD, AND S. J. DWYER, III, UNIVERSITY OF MISSOURI, COLUMBIA, MISSOURI

Automatic Visual Inspection Systems for electronic assemblies have been investigated. Three major phases have been researched: scanning devices, software algorithms, and possible computer systems.

#### 4:30 PM

"MAP: A USER CONTROLLED AUTOMATED MASK ANALYSIS PROGRAM"

GOULD, NASA, HUNTSVILLE, ALA.

A general program for mask analysis is presented. The command language including operational, list processing and dimensional processing commands is described.

6:00 PM COMMON INTEREST GROUP MEETINGS

PARTITIONING DATA BASE DESIGN ACM SIGDA IEEE DA TECH COMM

# TUESDAY, JUNE 18

#### 8:00 AM

SIMULATION AND TEST GENERATION TUTORIAL S. A. SZYGENDA, UNIVERSITY OF TEXAS, AUSTIN, TEXAS

# SESSION 5: DOCUMENTATION SYSTEMS

CHAIRMAN: C. E. RADKE, IBM CORP., POUGHKEEPSIE, N.Y. 9:00 AM

"AUTOMATED DESIGN AND MANUFACTURE OF PRINTED CIRCUIT BOARDS"

D. L. PETERSON, LEAR SIEGLER, INC., GRAND RAPIDS, MICH.

The reasons behind one company automating the design of priors a circuit boards are exposed. The resultant accomplishments, the economic benefits and the reduction in calendar days for development as a result of automation are detailed.

# SESSION 5: DOCUMENTATION SYSTEMS

9:30 AM

"A SIMPLE, EFFICIENT DESIGN AUTOMATION PRO-CESSOR"

L. E. DRUFFEL, D. C. SCHMIDT AND R. A. WAGNER, VANDERBILT UNIVERSITY, MASHVILLE, TENN.

A base system which processes, provides simulation, allows physical description of small logical switching systems (e.g., controllers, mini-computers) is described. The system was developed as a design, education, and research tool.

10:00 AM

"MICROPROGRAMMING DESIGN SUPPORT SYSTEM" A. YAMADA, NIPPON ELECTRIC CO., LTD., TOKYO. JAPAN

A microprogramming design support system addressing require-ments for central processors, perioheral controls and terminals is described. The total system is described from the design language to the post-processing of bit patterns.

11:00 AM

"COMPUTER AIDED SCHEMATICS"

G. G. HAYS, WESTINGHOUSE ELECTRIC CORP., BALT-IMORE, MARYLAND

A proton is described which aids in the generation of support publications for digital hardware. Besides an indicated 33% cost savings, shorter publication time and earlier start of the publication effort is achieved.

11:30 AM PANEL DISCUSSION - DOCUMENTATION SYSTEMS

# SESSION 6: TEST DATA GENERATION

CHAIRMAN: S. A. SZYGENDA, UNIVERSITY OF TEXAS, AUSTIN, TEXAS

9:00 AM

"AUTOMATIC TEST GENERATION AND TEST VERIFI-

CATION OF DIGITAL SYSTEMS" J. P. VERMA, B. M. SELOVE AND J. N. TESSIER, BURROUGHS CORP., CITY OF INDUSTRY, CALIF.

A series of programs were developed over the yeas to completely automate the test cycle – using DA files as input. The output is a test deck in the language of card test equipment and a list of detected or undetected failures.

9:30 AM

"MSI/LSI IMPACT ON DIGITAL SYSTEM TESTING" H. H. HUANG, NCR CORP., SAN DIEGO, CALIF.

10:00 AM

"A SYSTEM OF COMPUTER PROGRAMS FOR EFFI-CIENT TEST GENERATION FOR COMBINATIONAL SWITCHING CIRCUITS"

E. KJELKERUD, THE ROYAL INSTITUTE OF TECH-

E. KJELKEROD, THE HOTAL INSTITUTE OF TECH-NOLOGY, STOCKHOLM, SWEDEN Programs for test generation, fault simulation and test minimization for combinational switching circuits form a special strategy directing the choice of a test set. The object is to minimize the number of tests required for the detection of logical faults.

11:00 AM

"A HEURISTIC TEST GENERATION ALGORITHM FOR SEQUENTIAL CIRCUITS" T. ARIMA, J. OKUDA,

G. AMAMIYA AND M. TSUEOYA, NIPPON ELECTRIC CO., LTD., TOKYO, JAPAN

A new algorithm for test generation for a sequential circuit with at least one thousand logic blocks is discussed. It is based on special values expressed in boolean vectors, their logical operations, and three basic theorems.

11:30 AM PANEL DISCUSSION - TEST GENERATION

SESSION 7: FUNCTION DESIGN TECHNIQUES CHAIRMAN: D. J. HUMCKE, BELL LAES, HOLMDEL, N. J.

9:00 AM

"A PROGRAMMABLE CONFIGURATOR"

T. W. SIDLE, F. BEUGER, L. W. LEYKING AND A. G. LIVITSANOS, BURROUGHS CORP., CITY OF INDUS-TRY, CALIF

A program definition language is used to specify rules for translating a purchase order into the required set of hardware and software components.

9:30 AM

#### "SPECULATIONS ON THE FUTURE OF DESIGN AUTO-MATION"

S. Y. H. SU, CITY UNIVERSITY OF NEW YORK, NEW YORK, N. Y.

The future direction of the use of design automation for designing and developing disital data processing systems and hards use is highlighted. Some of the unresolved problems are indicated and some thoughts toward resolving them are suggested.

10:00AM

"AN EXPERIMENTAL COMPARISON OF FORCE DI-

RECTED FLACEMENTAL COMPARISON OF FORCE DI-RECTED FLACEMENT TECHNIQUES" D. C. WILSON AND R. J. SMITH, II, SOUTHERN METHODIST UNIVERSITY, DALLAS, TEXAS Significant differences are noted in the computational efficiency of the alterithms screece 1 and to the computational efficiency of solution to the routability of a board.

# SESSION 7: FUNCTION DESIGN TECHNIQUES

11:00 AM

"A TOOL FOR COMPUTER DESIGN"

H. WEBER, IBM, BOBLINGEN, GERMANY

This paper critically analyzes the development process, it covers methods which keep the function of the system being developed invariant.

11:30 AM "TRANSMISSION LINE MODELS FOR TRANSIENT ANALYSIS"

S. J. GARRETT, UNIVERSITY OF SOUTH FLORIDA, TAMPA, FLORIDA

A method of incorporating a model of any two conductor transmission line in terms of a SCEPTRE transient analysis problem is described. Several examples are used, and their computer response is compared with actual results.

# SESSION 8: ARCHITECTURE

CHAIRMAN: E. E. DUDNIK, UNIVERSITY OF ILLINOIS, CHICAGO, ILL.

1:30 PM

#### "PROGRAM PLANNING FOR NEW TOWN DESIGN PROBLEMS"

M. LOS, UNIVERSITY OF PENNSYLVANIA, PHILA-DELPHIA, PA.

This paper formalizes the new town design problem as a problem in combinatorial programming, describes computer algorithms designed to solve it and reports computational experience.

2:00 PM

"OPTIMAL POLYOMINO MAPS" H. B. SHAPIRA, AND R. S. FREW, YALE UNIVERSITY, NEW HAVEN, CONN.

The procedure for generating an optimal polyomino from a given set of preferences and the creation of a variably proportioned rectiline-ar map from that n-celled animal is described.

3:00 PM "A COMPUTER AIDED LAND USE STUDY TECH-NIQUE"

E. E. DUDNIK AND W. SCHACHTEL, UNIVERSITY OF ILLINOIS, CHICAGO, ILL.

This paper describes a computer-aided decision-making technique by which site evaluation with respect to land use can be made.

3:30 PM

"INTERACTION, INTERFACES, AND DESIGN"

J. S. GERO, UNIVERSITY OF CALIFORNIA, BERKE-LEY, CALIF.

Many design processes are iterative in nature and require extensive designer/computer interaction. As an experiment in interactive architectural design, four basic interactive functions were imple-mented in APL. These functions are described and their conversa-tional use linkustrated.

#### SESSION 9: SIMULATION

CHAIRMAN: S. Y. H. SU, CITY UNIVERSITY OF NEW YORK, NEW YORK, N. Y.

#### 1:30 PM

"A MINICOMPUTER-BASED LOGIC-FAULT SIMULA-TOR"

M. FLOMENHOFT AND B. M. CSENCSITS, BELL LABS, ALLENTOWN, PENNSYLVANIA

A unit-gate-delay three-valued-logic parallel fault simulator handles up to 1500 gates on a minicomputer with 16K core. Capabilities, programming novelties, and performance statistics will be presented.

#### 2:00 PM

"FUNCTIONAL TESTING OF LSI GATE ARRAYS"

G. VAUGHN, MOTOROLA INC., MESA, ARIZ.

This report is a description of the problems encountered while functionality testing LSI gate arrays in a production environment and some solutions we are implementing for these problems.

## 3:00 PM

"TIMING ANALYSIS FOR DIGITAL FAULT SIMULA-

E. W. THOMPSON, S. A. SZYGENDA, N. BILLAWALA, AND R. PIERCE, UNIVERSITY OF TEXAS, AUSTIN, TEXAS

This paper presents implemented techniques for timing analysis, and termination of fault induced activity, within an assignable delay digital fault simulation environment.

3:30 PM PANEL DISCUSSION - SIMULATION

# SESSION 10: GENERAL APPLICATIONS

CHAIRMAN: J.G.BRINSFIELD, BELL LABS, WHIPPANY, N. J. 1:30 PM

'A COMPUTER AIDED SYSTEM FOR THE DESIGN, MANUFACTURE AND TEST OF DIGITAL PRINTED CIRCUIT BOARDS"

R. J. SUMMERS, WESTINGHOUSE ELECTRIC CORP., BALTIMORE, MD.

A Computer Aided System (CAS) for the design, manufacture, and test of printed boards containing digital circuits is described. Along with a walk through of the system, the cost savings and production increases obtained are indicated.

# SESSION 10: GENERAL APPLICATIONS

2:00 PM

"COMPUTER AIDED SHIP DESIGN AT THE MARITIME ADMINISTRATION"

A. H. WOODYARD, U. S. DEPT. OF COMMERCE, WASHINGTON, D. C.

Organization of the computer aided ship design process is detailed, illustrating input and output with a sample design. Design verification of certain phases of the design process is treated using graphical aids.

3:00 PM

"RTL - THE FIRMWARE DESIGN AUTOMATION SYSTEM"

R. L. HASTERLIK, HONEYWELL INFORMATION SYSTEMS INC., BELLERICA, MASS.

A system to control design and development of a microprogrammed device is summarized. Documentation of the design, simulation of the firmware, and assembly of the firmware are system facilities.

3:30 PM

"AUTOMATED SIGN DESIGN AND STENCIL CUTTING SYSTEM"

W. M. BARNES, COMPUTER TALK, INC., IDLEDALE, COLO.

A real-time minicomputer system for sign design, stencil making, payroll and time keeping, file management, font design, maintenance and hardware diagnostics is presented.

5:00 PM COMMON INTEREST GROUP MEETINGS INTERCONNECTION SOFTWARE DA SIMULATION AND TEST GENERATION ARCHITECTURE

# WEDNESDAY, JUNE 19

8:00 AM

INTERCONNECTION TUTORIAL

D. W. HIGHTOWER, BELL LABS, HOLMDEL, N. J.

#### SESSION 11: INTERCONNECTION

CHAIRMAN: D. W. HIGHTOWER, BELL LABS, HOLMDEL, N. J.

9:00 AM

# "AN ITERATIVE TECHNIQUE FOR PRINTED WIRE ROUTING"

F. RUBIN, IBM CORP., POUGHKEEPSIE, N. Y.

This paper describes an iterative method of routing which tries to avoid crossings and path adjacency while simultaneously controlling path length.

9:30 AM

"A PROGRAMMABLE PRINTED WIRING ROUTER" C. S. SLEMAKER, R. C. MOSTELLER, L. W. LEYKING AND A. G. LIVITSANOS, *BURROUGHS CORP., CITY OF INDUSTRY, CALIF.*

This paper describes a cost function which halos a Moore-Lee router avoid finding paths that block unwired access pins.

#### 10:00 AM

"A SYSTEM FOR MULTI-LAYER PRINTED WIRING LAYOUT"

J. C. FOSTER AND R. L. CALAFIORE, BELL LABS, WHIPPANY, N. J.

An interactive design station for routing multi-layer backplanes is described. The system uses a digitizer/plottor, storage scope and standalone computer. The overall philosophy and goals are explained.

# SESSION 12: LARGE SCALE SYSTEMS

CHAIEMAN: R. TAYLOR, NICD, WASHINGTON, D. C.

9:00 AM "IPAD 1" C. GARROCO, GENERAL DYNAMICS

9:30 AM "IPAD 2" R. MILLER, BOEING CORP.

The IPAD 1 and IPAD 2 presentations concern NASA's activities in Design Automation for aerospace vehicle design.

10:00 AM "DESIGN AUTOMATION IN PRELIMINARY DESIGN" D. E. TIPPING, MARTIN MARIETTA, ORLANDO, FLA. Preliminary design of tactical weapons systems using interdisciplinary computer aids provides insight into any automated preliminary design activity. The necessary attributes of these design automation tools is discussed.

# SESSION 13: SOFTWARE

CHAIRMAN: J. SHERMAN, *IBM CORP., SAN JOSE, CALIF.* 11:00 AM

"GERMINAL: TOWARDS A GENERAL AND INTE-GRATED SYSTEM FOR COMPUTER AIDED DESIGN" R. JACQUART, P. REGNIER AND F. R. VALETTE, CERT/DERI COMPLEX AEROSPATIAL, TOULOUSE CE-DEX, FRANCE

GERMINAL is a system of tools for a project from conception to the finished product. Standard procedures, adding devices and management of the devices are discussed.

11:30 AM

"USING SIMULATION TO EVALUATE SYSTEM PER-FORMANCE"

E. K. BOWDON SR., UNIVERSITY OF ILLINOIS, URBANA, ILL.

Effects of job scheduling algorithms on computer system performance and resources are demonstrated and evaluated by a simulation model of a hypothetical, graphically distributed network computer.

# SESSION 14: DESIGN SYSTEM NEEDS

CHAIRMAN: C. E. RADKE, *IBM CORP., POUGHKEEPSIE, N.Y.* 11:00 AM

"INITIAL DESIGN OF AN ADVANCED DA SYSTEM" M. A. BREUER, AND A. D. FRIEDMAN, UNIVERSITY OF SOUTHERN CALIFORNIA, LOS ANGELES, CALIF. This advanced DA system is intended to be capable of highly interactive design. It has several unique features which will greatly enhance the possibilities of automatic design which is superior to that of the design engineer.

11:30 AM

"ENGINEERING DATA MANAGEMENT SYSTEM (EDMS) FOR COMPUTER AIDED DESIGN OF DIGITAL COMPUTERS"

M. SOGA, C. TANAKA, K. TABUCHI, K. SEO, M. KUNIOKA, AND H. TSUJI, *MITSUBISHI ELECTRIC* CORP., KANAGUWA, JAPAN

This paper describes an automated design system with a data base constructed by the general data base system capable of handling network structure and its DA programs.

#### 1:30 PM

PANEL DISCUSSION – "THE FUTURE AND HISTORY OF DESIGN AUTOMATION" PANELISTS: DA WORKSHOP COMMITTEE AND SES-

SION ORGANIZERS

3:30 PM

"CRITIQUE OF THE ELEVENTH ANNUAL DESIGN AUTOMATION WORKSHOP"

## AN INTERACTIVE GRAPHIC LOGIC DESIGN SYSTEM

As presented at ACM '73, Atlanta, Ga., on August 29, 1973 by:

W. H. Sass, Advisory Engineer International Business Machines Corp., Kingston, New York 12401

## INTRODUCTION

The "Gazelle" system is composed of a group of programs developed as tools\* to aid the design engineer in the creation, simulation, analysis and test generation of digital logic. Gazelle is designed for use on an IBM 1130 computing system running under the "GLEAM" (Reference #1) multitask operating system. An IBM 2250 display console provides the engineer with the ability to interface with the computer in his development and simulation of a logic circuit.

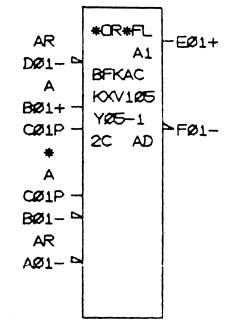

The Gazelle system presents the same general format that has been used on machine printed logic sheets; one that the user is already familiar with. The logic page may be composed of from one to ninety-one logic blocks, from one to ninety-one left-edge connectors, from one to ninety-one right edge connectors, and wires to join the connectors and logic blocks to perform specific logic functions. The logic blocks are actually "macro" blocks, which represent circuits composed of the logic functions AND, OR, NOT, and DELAY.

The display light pen is used to perform operations upon logic circuits displayed on the screen. Information may also be added to the display by typing at the display console keyboard.

Gazelle is composed of many individual program phases which perform functions of the system. The selection of a phase is accomplished via the display and light pen. Each phase provides one or more functions which may be chosen by selecting the name of the function on the screen with the light pen.

\*NOTE: This application program is an IBM internal tool and is not available for outside distribution.

## PHASES

The major phases of GAZELLE are:

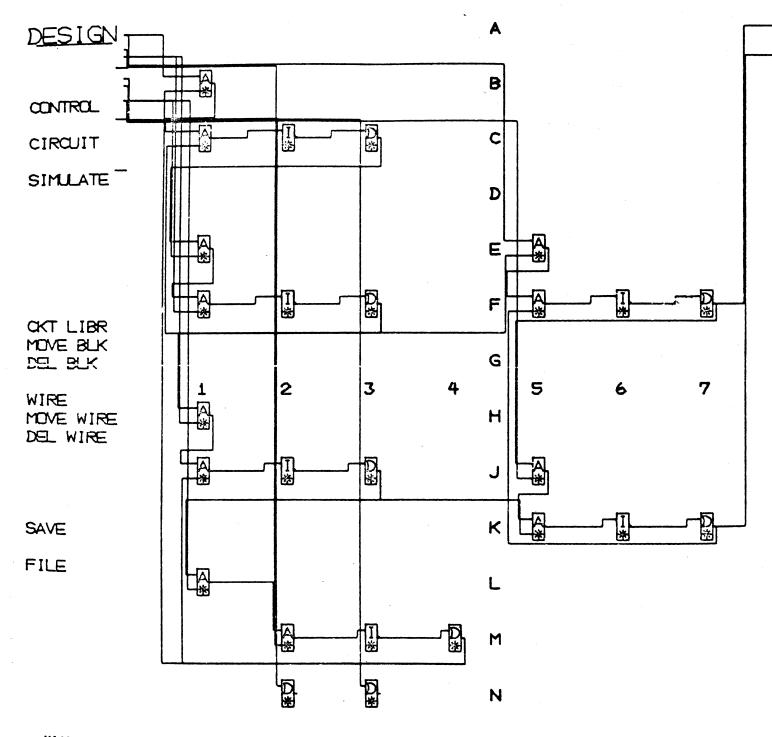

Control is the prime hub of the GAZELLE program and is the initial display panel which the user sees (refer to Figure #1). In this phase the design number is determined and the next phase is selected.

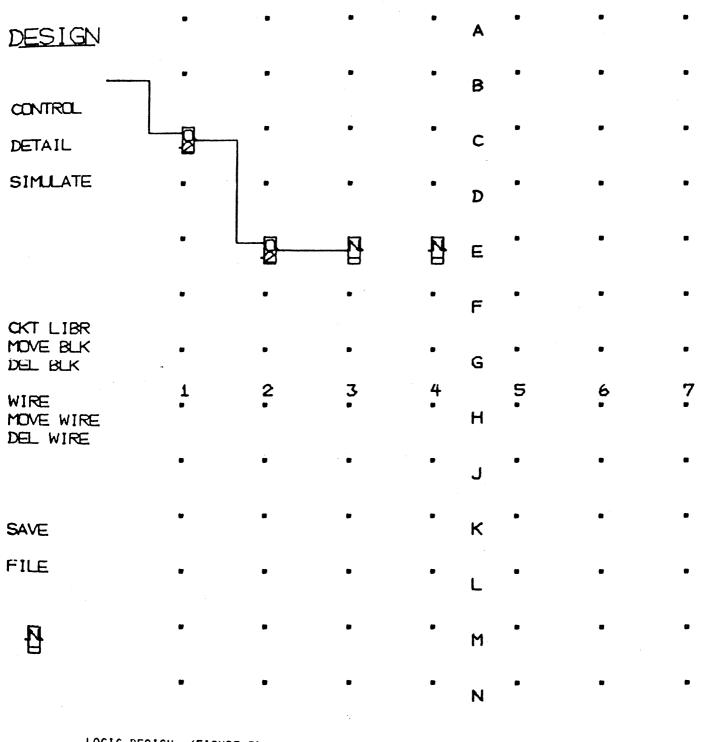

<u>Circuit</u> is selected by the design engineer (see Figure #2) for designing "macro" logic blocks from the basic logic functions (AND, OR, NOT, DELAY, ETC.) or from combinations of existing macro logic blocks (see Figures #3 and #4). These circuits are retained in a special circuit library file for subsequent reuse.

Design is selected to design or alter logic pages using the same basic format as the machine printed logic sheets see Figure #5). These pages are composed of (macro) logic blocks, left-edge and right-edge connectors, and wires connecting these blocks and edge connectors.

Detail may 's selected from the Design phase. It provides a means for entering title, logic block, (see Figure #6) left-edge and right-edge connector textual information via the display's alphameric keyboard.

New Page operation permits creating a new logic page and page number for an existing design.

COPY operation is used to create new logic pages from pages which already exist in the Gazelle logic files.

File is an operation which saves the circuit and detail information for the in-process logic page. This page becomes the "latest level" for this design.

DA-LINK is a means of interfacing with a central computer system (S/360 or S/370) via RJE/RJP or the SBCU. This phase includes a JCL compiler that generates a customized job control deck from user-supplied variables (see Figure #7).

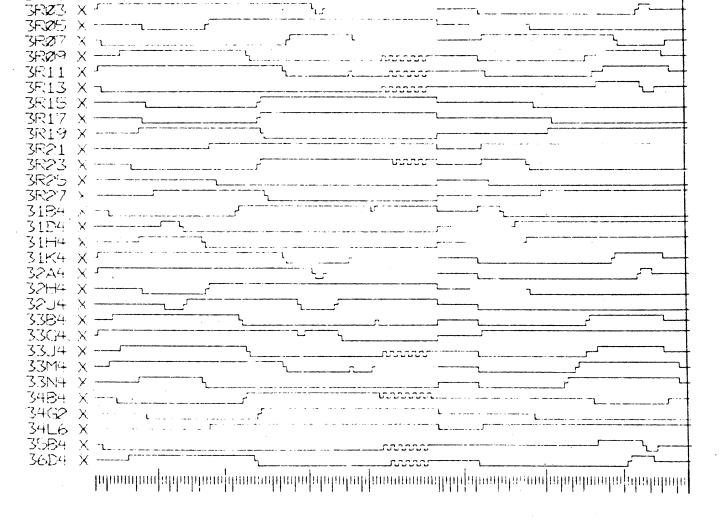

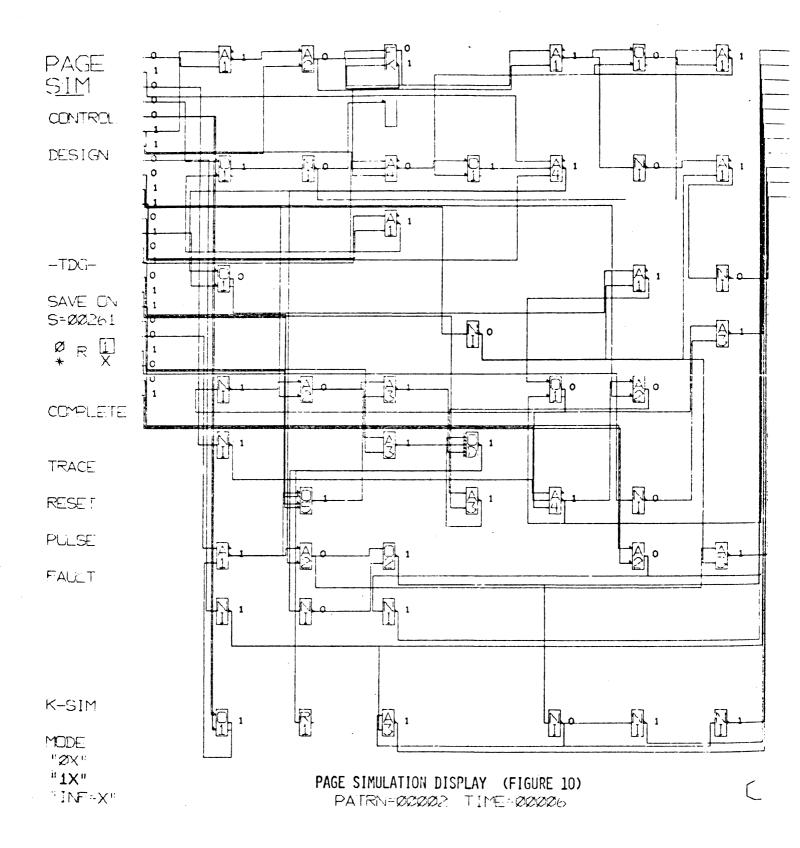

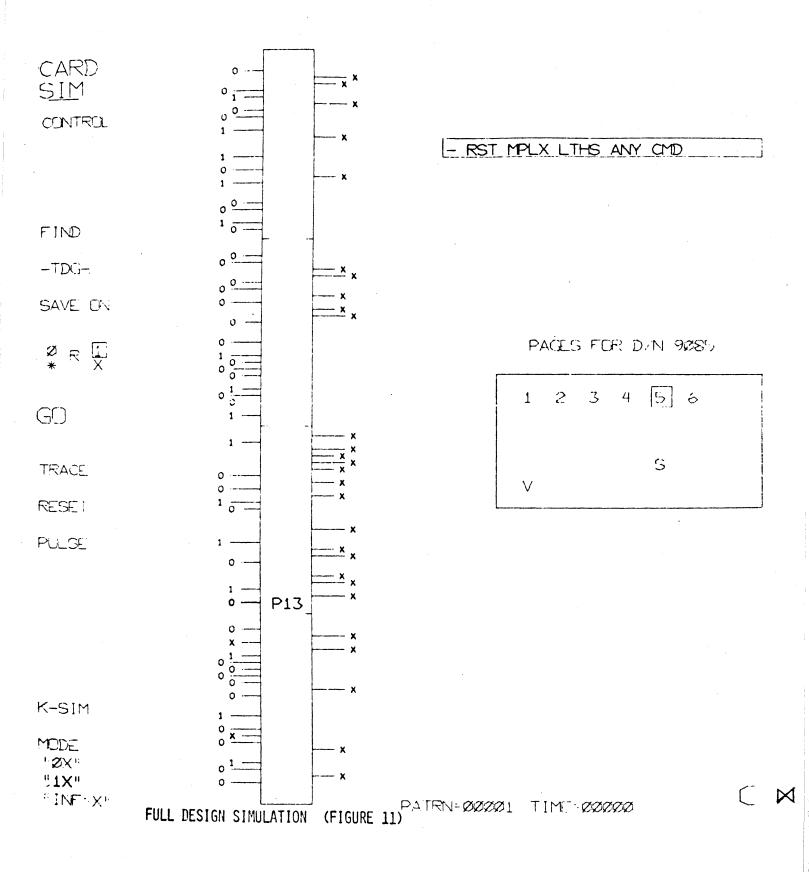

-TDG- or Test Data Generation provides various features that enhance the basic simulation capabilities, and interface with the host system's test generation facilities (see Figure #8). Simulation allows the designer to exercise the circuit functions on a logic page (see Figure #10) or card (see Figure #11). Values of "0", "1", "X" and "\*" may be applied to the input pins (left-edge connectors) of the logic and the resultant value of each line will appear at the output pin of the logic block which is the source of that line. The resultant values are determined by Gazelle according to the mode of simulation the designer has selected. One of these enchancements is the "scope" feature which provides multibeam oscilloscope images of the simulation output (see Figure #9).

Activate will activate the circuits used in the selected Design and will list any circuits not defined in the Circuit Library.

<u>Ckt-List</u> will list all circuits used in the selected Design and provide a "where used" cross-reference table.

#### FEATURES

This logic layout and evaluation system is designed to operate on the IBM 1130 computing system. The purpose of this family of programs is to provide a design engineer with a means of evaluating his design, via the 2250 display, prior to committing it to hardware. The system takes care of the many control and bookkeeping tasks that an overworked designer often resents and sometimes disregards:

The major features of this system are:

- <u>Graphic Access</u>: The designer may have immediate access to his design files via the 2250 display console. He may display, plot or edit the file content. He may also reference various shared files in the same manner.

- 2. <u>Multitasking</u>: The application utilizes the GLEAM/1130 Multitask Control Program which permits the concurrent execution of several task programs. This feature allows natural interaction between man and machine for the creation and analysis of a design, yet provides a reasonably steady workload for the system.

- 3. <u>Macro Facility</u>: The designer can group collections of elemental (or micro) blocks (AND, OR, NOT, ETC.) and define a macro (for example a register stage), then design logic using both macro and micro blocks. The design may be saved on a disk file for later recall.

- 4. <u>Design Control</u>: Design files are maintained and updated by the file management routines within the 1130 system. The logic design data will be automatically reformatted for input to the existing Design Automation processors.

- 5. Logic Simulation: An interactive ternary timing simulator is available for establishing "good machine responses". Using this system, it is possible for the designer to sit at a 2250 display and determine if the logic does indeed perform the desired function. It is also possible to examine the performance of a logical network when variable delays are encountered on "parallel" lines. An option is provided to operate in binary mode (as a two-valued simulator) for improving run time.

- 6. <u>Fault Simulation</u>: A ternary fault simulator is also available for examining the effect of "stuck at 1" or "stuck at 0" faults in the logic.

- 7. Logical to Physical Transformation: The logic diagram is automatically converted to a physical form showing the logical point to point nets. This display is used to layout components with an eye toward simplification of wiring patterns. After component placement has been optimized the nets are formed into the actual wire paths.

- 8. Artwork Generation: The wire file is interpreted by a task which drives on-line plotting devices to produce artwork masters or numerical control tapes for device fabrication.

- 9. <u>Remote Job Entry</u>: Information is transmitted-to (and received-from) S/360 or S/370 via "RJE/RJP" over switched, voice-grade telephone lines, allowing the S/360 to also serve the designer. A high-speed coaxial line may also be used to interconnect the 1130 to an on-site S/360, S/370 via a Sensor Based Control Unit (SBCU).

The advent of medium and large scale integration has increased the cost of change. It is now imperative that the hardware function correctly the first time, or else the design costs and attendant delays become unbearable.

The designer can now create, evaluate and initiate the release procedures on a small system which has desirable facilities, capabilities, and cost attributes.

# MODES OF SIMULATION

Three modes of simulation exist within the GAZELLE simulator. With each of the modes, the delay blocks (D\*) used to define higher level macros are taken into consideration. This means that if no delay blocks are used in a definition, a zero-delay simulation will occur. If one delay block is used in each function, unit-delay simulation will occur. When different number of delay blocks have been used in different functions, a variable delay simulation will occur. The more realistically the delays have been assigned to the function, the more realistic the simulation will become.

Also, for each of the modes, any of the four values of 0, 1, X or \* can be applied to an input and simulated. 0 and 1 are binary values; X is the "unknown" or transition state between 0 and 1; \* is "don't care" and acts as if the line doesn't exist at all.

Upon initial entry to the simulator and after reset, the active logic is set to the -X- or uninitialized state. The untied lines are set to the pre-selected untied line state, which can be any of the four values indicated above.

# 0-X Mode:

The significant characteristic of this mode is that state change within a function is assumed to occur instantaneously. Delay is considered if delay blocks have been used to define the function. The change from one state to another is assumed to always be known. Therefore, an -X- is not inserted during the change.

## 1-X Mode:

During simulation in the 1-X mode, a state change is assumed to go through a transition period of one unit of time (one unit of delay). The propagation of this unknown or transition state will cause certain loops to be set to the -X- state indicating a potential race or hazard condition.

#### INF-X Mode:

For this mode, the transition from one state to another is assumed to take an infinite period of time. In actual usage, when a transition occurs, an -X- is applied to a line and allowed to propagate until stabilization occurs. This causes all "feedback" loops to be set to -X- before propagation of the intended signal. Wherever the -X- state would control a latch, the -X- will remain, indicating a potential race, hazard or oscillatory condition.

In general, the "0/X" mode is optimistic in that it will not indicate race or hazard conditions and "INF/X" is very pessimistic, indicating possible problem areas that in reality will not be problem areas. The "1/X" mode will be found to be the most useful and closely approximate actual hardware operation. This is the default mode upon initial entry to the simulator.

# FAULT SIMULATION

The Fault Simulator provides the user with a tool for applying a "stuck" condition on any line within the logic, simulating that "stuck condition and holding the value at the "stuck" level while other simulations are progressing.

To apply a value to a line, select FAULT (the option -FAULTappears on the Page panel). FAULT will change to STICK, indicating that the option is active. The next line selected will be stuck at the level currently indicated by the "boxed" value. (The left edge lines of the page cannot be "stuck".) When a line has been "stuck" a diamond () will appear around the line value and the option STICK will change to STUCK. If a simulation is performed at this point, the "stuck" value will be actively propagated and the results allowed to stabilize.

To "un-stick" a line, select STUCK. The word STUCK will change to FAULT and the diamond around the "stuck" value will be removed. If a simulation has not been performed so that the "stuck" condition has not been propagated, selecting STUCK will cause the previous line value to re-appear on the line. Selecting STICK will also cause a return to the FAULT word.

It should be recognized that application of the Fault feature can produce logic states that have not been caused by changes to P/I's. Care must be taken to recognize what effects, if any, the application of the Fault has had and not to confuse these changes with those that occur as a result of normal pattern propagation. Note also that RESET will not remove the "stuck" condition unless the option STUCK has been changed to FAULT.

The Fault Simulator is used to evaluate the effectiveness of the test patterns that have been generated, by observing the difference in the simulation results between the "good machine" and the "fault machine".

## SCOPE

SCOPE is an option on the test data generation (TDG) panel which converts the users simulation patterns into a thirty-one beam oscilloscope pattern on the display (see Figure #9). This option makes it possible for the user to immediately inspect any selected area of his simulation run. The user selects the lines to be "scoped" by having the scope line selector display the desired page, then selecting the desired net with the light pen. A flag (\*) will be displayed on the chosen set. To deselect a previously chosen net, the user triggers the light pen on the flag (\*). A pattern/time scale is provided on the display for the users convenience. He can use this scale to check values on one line against the values on any other line for the same pattern/ time frame. In a situation where there is an unusually great amount of activity, it may not be possible to display the entire simulation run at one time. SCOPE will however display as much as it possibly can, and the user can scroll the display as he desires. All four simulation values are displayed; "0", "1", "X" (unknown), and "\*" (don't care).

#### CONCLUSIONS

A relatively small computing system can assist the engineer in performing logic design, simulation and test data generation.

Graphic computer-aided design methods improve the man-machine relationship. The combination of a small computer, disk storage units, high performance display, low cost on-line plotter and unit record I/O devices offer significant benefits to the user.

Even the small-sized system is enhanced by a multitasking operating system. The major benefit realized is accessability for the user. Any nonbusy facility can be immediately accessed by the designer; he doesn't need to wait for the current computer job to complete. The multitasking program attempts to keep all devices operating full time, thereby offering better system utilization.

Remote Job Entry (RJE) to a larger computer system via the telephone network or at higher speeds over dedicated coaxial cables allows the small system to handle extremely large designs for the user. The graphic system operates as a satellite to the larger system, providing the user with a power input/output facility, as well as performing some local computation; and the larger host system provides the main data base and performs the heavy computation which might be required. This distributed computing philosophy appears to be an optimum way to support computer aided design.

REFERENCES

- 1. GLEAM/1130 A Production System Base for Computer-aided Design. Fifth Annual Design Automation Workshop, 1968.

- An 1130 Logic, Layout and Evaluation System Seventh Annual Design Automation Workshop, 1970.

- 3. Revisiting an Operational Graphic Design System Eighth Annual Design Automation Workshop, 1971.

# GAZELLE LOGIC CONTROL

25ø9 2497 2513 2953 9831

CKT LIST ACTIVATE

IN-PROCESS 9115-3

-FILE GAZELLE CONTROL PANEL (FIGURE 1) CIRCUIT

DESIGN NEW PAGE COPY PRINT PLACE WIRE LINK SIM -TDG- C X

| CIRCUIT<br>L <u>IBRARY</u> | *F3 *U<br>*F4 *P<br>*F5 *Ff              | R#FL BFKAC<br>H BFKAD<br>F BFKAE |

|----------------------------|------------------------------------------|----------------------------------|

| CONTROL                    | *F6 *Ff<br>*F7 A<br>*F8 *A               | BFKAG<br>BFKAH                   |

| I-P PAGE                   | *F9 *A<br>*FØ *Ff<br>*FA *Ff             | = BFKAL                          |

| PUNCH                      | *FB *Ff<br>*FC *Ff<br>*FE *A1<br>*FF *Ff | F BFKAQ<br>FOR BFKAU             |

| PRINT                      | *FG *Ff<br>*A1 A<br>*O1 OR               |                                  |

|                            | *01 UK<br>*A2 A<br>*02 DR<br>*A3 A       | BLKAB<br>BLKAB<br>BLKAC          |

| NEW OKT                    | <b>#03 OR</b><br><b>#</b> A4 A           | BLKAC<br>BLKAF<br>BLKAF          |

| LOGIC                      | #04 OR<br>#A5 A<br>#05 OR                | BLAAF<br>BLKAG<br>BLKAG          |

| MACRO                      | #A6 A<br>#06 OR                          | BLKAH<br>BLKAH                   |

| MOVE OKT                   | *A7 A<br>*07 OR<br>*A8 *A1               | BLKAJ<br>BLKAJ<br>FOR BLKAK      |

|                            | *A9 *A                                   | HOR BLKAL<br>HOR BLKAM           |

| DELETE                     | *AB A<br>*AC A<br>*OC OR                 | BLKAN<br>BLKAO<br>BLKAO          |

|                            | *N- N<br>*N1 N<br>*DA A                  | BLKAD<br>BLKAE<br>DOT            |

| CHG ACTV                   | *DO OR<br>U1 A                           | DOT<br>BUKAA                     |

|                            | U3 0E<br>14 +01<br>U5 +A                 | BUKAC<br>BUKAD<br>BUKAE          |

|                            | U6 +01<br>U7 +A                          | D BUKAF<br>FOR BUKAG             |

|                            | U8 *A1<br>58 *M<br>W3 *SF                | REG BSKAB                        |

|                            | W7 DE<br>#EN #E1                         | BWKBJ                            |

|                            |                                          | MS# CCCAQ                        |

| *PHYS* | CCCAD                                                                |

|--------|----------------------------------------------------------------------|

|        | · · · · ·                                                            |

|        | • • • • •                                                            |

|        | · · · · ·                                                            |

| ••     |                                                                      |

|        |                                                                      |

|        |                                                                      |

| AAAAAA | AAAAAA                                                               |

|        | *PHYS*<br>PHYS*<br>*PHYS*<br>SERV*<br>R<br>*SPEC<br>BBBBBB<br>AAAAAA |

CIRCUIT LIBRARY SELECTION (FIGURE 2)

D

MICRO-LOGIC CONSTRUCTION OF MACRO (FIGURE 3)

CP

RESTART

MACRO

CONTROL DESIGN CIRCUIT

FILE

.

CIRC FUNC (ALD | \*OR\*FL

CIRC TYPE (ALD L BFKAC

> GAZELLE NAME F3

ALTERNATE BLOCK 1 2 3 4

# MACRO LOGIC BLOCK (FIGURE 4)

LOGIC DESIGN (FIGURE 5)

LISTED BLK

RESTART

CV

# DETAIL

BIT 2

CONTROL

DESIGN

FILE

CIRCUIT

LOGIC

\*CANCEL\*= NEXT ONE

# DETAIL OF LOGIC BLOCK (FIGURE 6)

# \*\*\*\* UPDATE LMT FROM GAZELLE \*\*\*\*

JOB NAME ACEGD6 USER NAME WG SMITH PROBLEM NUMBER 123456 DEPT 720 BLDG 005 TODAY 'S DATE MONTH 06 DAY 08 YEAR 73

A2 TAPE NUMBER K1234 DA RUN NO 123 DA CYCLE NO 321

RUN TYPE C 'C' = CHANGE 'N' = NEW DESIGN

INTERFACE TO CENTRAL DA SYSTEM (FIGURE 7)

CONTROL RESTART LIST-PROTO QUE PRINT PUNCH RUE

# -TDG- D/N 9085

CONTROL SIMULATE DESIGN ALL EVENTS STORE SAVED PATTERNS MYDAS

SCOPE

TEST PATTERNS

GIF/BUGLIST

TITES CONTROL

RELEASE SAVED PATTERNS

SELECT

LIST

STORE FILE

EDIT FILE

REPLAY

EDIT

SAVE SIM

RESET SIM

# TEST DATA GENERATION CONTROL (FIGURE 8)

TDG

# SCALE - 5.

26

SCOPE PRESENTATION OF SIMULATOR OUTPUT (FIGURE 9)

RESELECT PATTERNS

JRØI X

PATTERNS FOR D/N 9085 PG 3

TIME 22/2

PATN 2. 2

#### Ribliography on Algorithms for Shortest Path, Shortest Spanning Tree, and Related Circuit Routing Proplems. (1957-1973)

by

#### A. R. Pierce

#### Bell Laboratories Murray Hill, N. J.

This bibliography contains over 300 references on algorithms and machine calculation techiques for solving the shortest path, k-th shortest path, and shortest spanning tree problems. Chapter 1 - Paths and Circuits - is divided into 4 sections, dealing respectively with shortest path, optimal path, Traveling Salesman and other related algorithms. Chapter 2 deals with spanning trees and chapter 3 covers the CAD of electronic systems that utilize minimum path or shortest tree al-gorithms.

These minimum cost problems enjoy a wide application in many different areas. Kruskal and Prim gave early methods for calculating shortest spanning trees. Other algorithms and numerous applications were soon to follow. For example, Lee's algorithm is frequently used to route printed circuit boards. Other best path calculations are used in highway research and planning. It is to be noted that wide applicability results because other variables such as "reliability", "flow", and "cost" can be used instead of "distance".

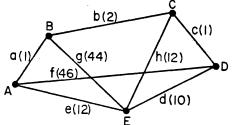

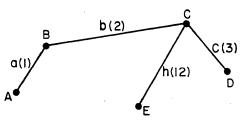

We now give some examples of the terms used. The length of a graph G, having edges of length l(i,j) between vertices i and j, is  $L(G) = \Sigma l(i,j)$ , where the summation is over all edges. Consider the graph G below:

A <u>path</u> (A,D) is any of the subgraphs {abc} or {ed} or {f} or ... The path {abc} is the "shortest" path, {ed} is the 2nd shortest path, ..., kth shortest path.

A subgraph <u>spans</u> a graph if it includes all the vertices of the graph. A subgraph is a <u>tree</u> if it is connected, and if removal of any edge makes it disconnected. Thus a <u>spanning tree</u> is a connected subgraph which includes all the verticies of the graph, and which is disconnected by removal of any edge. The tree t - pictured above - is the shortest spanning if the length l(t) is the minimum length of all spanning trees T of G. Frequently shortest or "minimum" (length) trees are referred to as mimimal trees.

A <u>circuit</u> is a path whose initial and final vertices are the same, but which otherwise never goes through the same vertex twice. The <u>Traveling Salesman Problem</u> is to determine a minimum spanning circuit of a graph.

Illuminating discussions with J. B. Kruskal, who provided some of the above examples, D. W. Hightower, and C. J. McCallum are gratefully acknowledged. Reviews and bibliographies by Dreyfus (1969), Frank and Frisch (1971), Pape (1969), and Wilson and Smith (1973) provided many useful references.

SECTION 1.1 SHORTEST PATH. KTH SHORTEST PATH.

DETERMINATION OF MINIMAL PATHS IN FINITE, DIRECTED, WEIGHTED GRAPHS.

ALBRECHT R; COMPUTING 3 (3): 184-93 (1968) (IN GERMAN)

- ALGORITHM 9: ALGOL PROCEDURES FOR THE MODIFIED ALGORITHMS OF MINTY AND MOORE. ALBRECHT R, VISOTSCHNIG E; COMPUTING 4(1): 76-81 (1969)

- (IN GERMAN)

- AN ALGORITHM FOR FINDING THE SHORTEST PATH IN A NETWORK GRAPH.

- ALEKSEEVA SM, ALEKSEEV OG; USSR COMPUT MATH MATH PHYS 11(4): 336-45 (1971)

- FINDING THE SHORTEST PATH IN A NETWORK WITH K EDGES HAVING THEIR LENGTH MADE EQUAL TO ZERO. ARINAL JC; REV FR RECH OPER 9(37): 323-31 (1965) (IN FRENCH)

- ALGORITHM FOR DETERMINING THE SHORTEST ROUTES THROUGH A CONNECTING NETWORK. (ALGORITHM DOES NOT REQUIRE THE FINDING OF ALL POSSIPLE ROUTES)

- ASTAFEVA NA: MEKH AVTOM UPR 4: 6-8 (1971) (IN RUSSIAN)

- SOME CONSTRAINED SHORTEST FOUTE PROBLEMS. BAJAJ CP: UNTERNEHMENSFORSCHUNG 15(4): 287-301 (1971) (IN GERMAN)

- THE SHORTEST PATH THROUGH MANY POINTS. BEARDWOOD J, HALTON JH, HAMMERSLEY JM; PROC CAMBRIDGE PHILOS SOC 55; 299-327 (1959)

- A COMPUTATIONAL MATRIX ALGORITHM FOR SHORTEST ROUTE PROBLEM. BEHARA EN; CAN MATH BULL 12(5): 697 (1969)

- A MODIFIED CASCADE ALGORITHM FOF SHORTEST PATHS. BILDE O, KRARUP J; METRA (FRANCE) 8(2): 231-41 (JUN 1969)

- AN ALGORITHM (THE P-TH BEST PATH ALGORITHM) FOR FINDING AND RANKING PATHS THPOUGH A NETWORK. BOCK F, KANTNER H, HAYNES J; ARMOUR RES FOUND, TECHNOLOGY CENTER, CHICAGO, 1957

- ALGORITHM 22: SHORTEST PATH BETWEEN START NODE AND END NODE OF A NETWORK. BOOTHPOYD J: COMPUT J 10: 306-7 (1967)

- ALGORITHM 23: SHORTEST PATH BETWEEN START NODE AND ALL OTHER NOLES OF A NETWORK. BOOTHROYD J; COMPUT J 10: 307-8 (1967)

- ALGORITHM 24; THE LIST OF NODES ON THE SHORTEST PATH FROM START NODE TO END NCDE OF A NETWORK. BOOTHROYD J: COMPUT J 10: 308 (1967)

- REMARKS ON THE DETERMINATION OF THE OPTIMAL ALGORITHM TO FIND THE SHORTEST PATH IN CIRCUITLESS GPAPH. BORILLE M; P66-9 OF CAIANEIELLO ER (ED), AUTOMATA THEORY, ACADEMIC, 1966

- THE COMPUTATION OF THE SHOPTEST PATH IN GRAPHS AND APPROPRIATE DATA STRUCTURES. BRAESS D; COMPUTING 8 (1-2): 171-81 (1971)

- R-NETWORKS AND MATPIX ALGORITHMS. (ALL SHORTEST PATHS IN A NETWORK)

- BRUCKER P; COMPUTING 10 (3): 271-83 (1972)

- ESTIMATION OF TRAVEL TIMES IN MULTIPLE MODE SYSTEMS. (SHORTEST DISTANCES, LEAST COST ROUTES) BURT JM, DYER JS; OPER RES QUART 22(2): 155-63 (JUN 1971)

- A DIRECTIONALLY ORIENTED SHORTEST PATH ALGORITHM. BUTAS LF: TRANSP RES 2(3): 253-68 (1968)

- SEARCHING FOR THE SHORTEST PATHS ALONG GRAPH DURING VARIATIONS IN IT. BUTRIMENKO AV; ENG CYBERN (6): 50-3 (NOV/DEC 1964)

- REMARKS ON THE DETERMINATION OF THE OPTIMAL ALGORITHM TO FIND THE SHOPTEST PATH IN A CIRCUITLESS GRAPH. CAIANIELLO ER (ED); P66-9 OF HIS AUTOMATA THEORY, ACADEMIC, 1966

- ON FINDING MINIMUM FOUTES IN A NETWORK WITH TURN PENALTIES. CALDWELL T: COMMUN ACM 4: 107-8 (1961)

- COMPUTING THE N BEST LOOPLESS PATHS IN A NETWORK. CLARKE S, KRIKORIAN A, RAUSEN J; J SOC INDUS APPL MATH APPL MATH 11: 1096-1102 (1963)

- THE SHORTEST ROUTE THROUGH A NETWORK WITH TIME DEPENDENT INTERNODAL TRANSIT TIMES. COOKE KL, HALSEY E: J MATH ANAL APPL 14: 493-8 (1966)

- PATH FINDING WITH ASSOCIATIVE MEMORY. (HIGHLY PARALLEL SEARCH, GRAPHS HAVING EDGES OF UNEQUAL LENGTHS, MIMIMAL MACHINE STORAGE REQUIREMENTS) CRANE BA: IEEE TRANS COMPUT C-17: 691-3 (JUL 1968)

- DISCRETE VARIABLE EXTREMUN PROBLEMS. (INCLUDING SHORTEST PATH AND TRAVELING SALESMAN) DANTZIG GB; OPER FES 5: 266-70 (1957)

- AN APPRAISAL OF SOME SHORTEST PATH ALGORITHMS. (37 REFS) DREYFUS SE; OPER RES 17: 395 (1969)

- AN APPRAISAL OF SOME SHOFTEST PATH ALGORITHMS. DREYFUS SE; RAND CORP, OCT 1967, 42P. MEMO RM-5433-PR

- THE CASCADE ALGORITHM FOR FINDING THE MINIMUM DISTANCES ON A GRAPH.

- FARBEY BA, LAND AH, MURCHLAND JD; MANAGE SCI A 14(1): 19-28 (SEP 1967); LONDON SCHOOL OF ECONOMICS, TRANSPORT NETWORK THEORY UNIT, 1965, REP LSE-TNT-19

- ALGORITHM 97, SHORTEST PATH. FLOYD RW: COMMUN ACM 5: 345 (1962)

- SHORTEST ROUTE PROBELM: ALGOL PROGRAMS, AND DISCUSSION OF COMPUTATIONAL PROBLEMS IN LARGE TRANSPORT NETWORK APPLICATIONS. FOOT DHS: DEP OF ECONOMICS. UNIV OF BRISTOL. 1965.

- DISCUSSION PAPER NO 10

- CALCULATING K-TH SHORTEST PATHS. FOX FL; RAND CORP, APR 1971, 4P. P-4638

- SHORTEST PATHS IN PROBABILISTIC GRAPHS. FRANK H; OPER RES 17(4): 593-99 (1969)

- COMMUNICATION, TRANSMISSION, AND TRANSPORTATION NETWORKS. (BEST PATH, TREES, MINIMUY COST PROBLEMS) FRANK H, FRISCH IT: ADDISON-WESLEY, 1971

- MINIMAL K ARC CONNECTED GRAPHS. FULKERSON DR, SHAPLEY LS; NETWORKS 1(1): 91-8 (1971); RAND CORP, 12 JUL 1961, P-2371

- NOTE ON FINDING ALL SHORTEST PATHS. GLOVER F AND OTHERS; AUSTIN CENTER FOR CYBERNETIC STUDIES, TEXAS UNIV, MAY 1972, 17P. AD749713

- SHORTEST PATHS IN GRAPHS-A PEVIEW. (FOPD'S, DANTZIG'S AND FLOYD'S ALGORITHMS WEIGHTED DIPECTED GRAPH) HAKIMI SL; P368-9 OF IEEE INT SYMP CIRCUIT THEORY, 1972

- THE METHOD OF COMPUTING LINKS. (SHORTEST ROUTES THROUGH A NETWORK)

- HALDER A: TRANSP SCI 4(1): 36-51 (FEB 1970)

- TRIPLE ALGORITHM FOR DETERMINATION OF SHORTEST PATHS IN A GRAPH.

- HAMMER G; Z WAHPSCHEINLICHKEITSTHEOR VERWANDTE GEB 12(2): 153 (1969) (IN GERMAN)

- EFFICIENT ALGORITHMS FOR DETERMINING SHORTEST PATH IN TRANSPORTATION NETWORKS. (21 REFS) HARTUNG HH; ANGEW INFORM 13(12): 573-7 (1971) (IN GERMAN)

- REVISED MATRIX ALGORITHMS FOR SHOFTEST PATHS. (AND EPRATA) HU TC: SIAM J APPL MATH 15(1): 207-18 (1967); IBID 15(6): 1517 (1967)

- A DECOMPOSITION ALGORITHM FOR SHORTEST PATHS IN A NETWORK. HU TC; OPER RES 16(1): 91-102 (JAN/FEB 1968); UNIV WISCONSIN, SEP 1967, 20P. AD662730; IBM WATSON RESEARCH CENTER, YORKTOWN HEIGHTS, NY, 1966, RES PAPER RC-1562

- A SHORT CUT IN THE DECOMPOSITION ALGORITHM FOR SHORTEST PATHS IN A NETWORK. HU TC; UNIV WISCONSIN, JUL 1968, US ARMY, MATHEMATICS RESEARCH CENTER, MADISON, REPT NO 882

- SHORT CUT IN DECOMPOSITION ALGORITHM FOR SHORTEST PATHS IN A NETWORK. HU TC, TORRES WT; IBM J RES DEVELOP 13(4): 387 (1969)

- SHORTEST PATH PROBLEMS VISITING SPECIFIED NODES. IBARAKI T; TRANS INST ELECTRON COMMUN ENG JAP PT A 53(12): 639-46 (1970) (IN JAPANESE)

- ALGORITHMS FOR OBTAINING SHORTEST PATHS VISITING SPECIFIED NODES.

- IBARAKI T: SIAM REV 15(I) PT 1: 309-17 (APR 1973)

- THE SHORTEST ROUTE PROBLEM WITH CONSTRAINTS. JOKSCH HC; J MATH ANAL APPL 14: 191-7 (1966)

- THE MINIMUM POUTE PROBLEM FOR NETWORKS WITH TURN PENALTIES AND PROHIBITIONS.

- KIRBY RF, POTTS RB; TRANSP RES 3(3): 397-408 (SEP 1969)

- A STRING ALGORITHM FOR SHORTEST PATH IN DIRECTED NETWORKS. KLEE VL; OPER RES 12: 428-32 (1964)

- ALGEBRAIC TECHNIQUES OF PATH FINDING AND MINIMUM PATH FINDING IN GRAPHS. KOLKER R, LISS D, OKADA S; MITRE CORP, BEDFORD, MASS, MAY 1963, 36P.

- EXTENSION OF THE CASCADE ALGORITHM TO LARGE GRAPHS. LAND AH, STAIRS SW; MANAGE SCI THEORY SER 14(1): 29-33 (SEP 1967)

- SHORTEST PATH COMPUTATIONS. LAWLER EL; IN FOUNDATIONS OF INFORMATION SYSTEMS ENG, UNIV MICH 1970

- PROCEDURE FOR COMPUTING THE K BEST SOLUTIONS TO DISCRETE OPTIMIZATION PROBLEMS AND ITS APPLICATION TO THE SHORTEST PATH PROBLEM.

- LAWLER EL: MANAGE SCI THEORY SER 18(7): 401-5 (MAR 1972)

- A NOTE ON THE N-TH SHORTEST PATH PROBLEM. LEE CY; IRE TRANS ELECTRON COMPUT EC-11: 572-3 (AUG 19621

- ON LAWLER'S K BEST SOLUTIONS TO DISCRETE OPTIMIZATION PROBLEMS: AND FEPLY. MARSHALL J: MANAGE SCI, THEORY SER 19(7): 834-5 (MAR 1973); 19(7): 835-7 (MAR 1973)

- MINIMUM FATH ALGORITHMS FOR TRANSPORTATION PLANNING. MARTIN EV; DEP CIVIL ENG, MIT, 1963, RES REP R63-52

- MULTI PATH SYSTEM TRAFFIC ASSIGNMENT ALGORITHM. (PATH FINDING ALGORITHM, 40 REFS) MCLAUGHLIN WA: WATERLOO UNIV, CANADA (ONTARIO DEP HIGHWAYS JOINT HIGHWAY RES PROGRAM), MAR 1966, 83P. REP NO RE108

- SHORTEST ROUTE PROBLEM WITE ADDITIONAL PROBLEMS. (EXPENDITURES, BRANCH AND BOUND) MEYL H; HEBEZEUGE FORDERMITTEL 12(2): 41-5 (FEB 1972)

- A DECOMPOSITION ALGORITHM FOR THE SHORTEST ROUTE PROBLEM. MILLS G; OPER RES 14(2): 279-91 (1966)

- A COMMENT ON THE SHORTEST ROUTE PROBLEM. MINTY GJ: OPER RES 5: 724 (1957)

- A VARIANT ON THE SHORTEST ROUTE PROBLEM. MINTY GJ; OPER RES 6: 882 (1958)

- SOLUTION OF THE ROUTING PROBLEM THROUGH A NETWORK BY MATRIX METHOD WITH AUXILIARY MODES.

- MORI M, NISHIMURA T; TRANSP RES 1(2): 165-80 (AUG 1967)

- THE ONCE THROUGH METHOD OF FINDING ALL SHORTEST DISTANCES IN A GRAPH FROM A SINGLE ORIGIN. MURCHLAND JD: TRANSPORT NETWORK THEORY UNIT, LONDON GRAD SCHOOL OF BUS STUDIES, 28 NORTHUMBERLAND AVE, LONDON WC2, AUG 1967, LBS-TNT-56

- THE NUMBER OF OPERATIONS IN FIXED MATRIX METHODS FOR FINDING ALL SHORTEST DISTANCES IN A GRAPH. MURCHLAND JD; TRANSPORT NETWORK THEORY UNIT, LONDON GRAD SCHOOL OF BUS STUDIES, 28 NORTHUMBERLAND AVE, LONDON WC2, 1967, LBS-TNT-59

- A NEW METHOD FOR FINDING ALL ELEMENTARY PATHS IN A COMPLETE

- DIRECTED GRAPH. MURCHLAND JD: TPANSPORT NETWORK THEORY UNIT, LONDON SCHOOL OF ECONOMICS, 28 NORTHUMBERLAND AVE, LONDON WC2, OCT 1965, LSE-TNT-22

- AN INDUCTIVE MATRIX METHOD FOR FINDING ALL SHORTEST PATHS IN A DIRECTED GRAPH. MURCHLAND JD; TRANSPORT NETWORK THEORY UNIT, LONDON

- SCHOOL OF ECONOMICS, 28 NORTHUMBERLAND AVE, LONDON WC2, 1966, LSE-TNT-25

- A NOTE ON THE OPTIMALITY OF SOME ALL-SHORTEST-PATH ALGORITHMS. NAKAMORI M: J OPER RES SOC JAP 15(4): 201-4 (DEC 1972)

- (IN JAPANESE)

- THE SHORTEST ROUTE PROBLEM. (AND ADDENDUM) NARAHARI PANDIT SN; OPER RES 9(1): 129-32 (1961)

- GENERALIZED PERMANENT LABEL SETTING ALGORITHM FOR SHORTEST PATH BETWEEN SPECIFIED NODES.

- NEMHAUSER GL; J MATH ANAL APPL 38(2): 328-34 (1972)

- FINDING THE SHORTEST ROUTE BETWEEN TWO POINTS IN & NETWOPK. (AND COMMENT)

- NICHOLSON TAJ, CHARTES BA; COMPUT J 9: 275-80 (1966); 10: 118-19 (1967)

FINDING THE SHORTEST ROUTE BETWEEN TWO POINTS IN A NETWOPK. (SHORTEST ROUTE FOUND BY INVESTIGATING SELECTION OF ROUTES FROM BOTH STARTING POINT AND TERMINAL POINT) NICHOLSON TAJ; COMPUT J 9: 275-80 (NOV 1966)

- SHORTEST PATHS FROM A FIXED VERTEX TO ANY OTHER VEPTEX IN DIRECTED NETWORKS. PAPE U; ELEKTRONISCHE DATENVERARBEITUNG 11(3): 105-15 (1969) (IN GERMAN)

- A BIBLIOGRAPHY ON SHORTEST PATH LENGTHS AND PATHS IN GRAPHS AND NETWORKS. PAPE U: ELEKTRONISCHE DATENVERARBEITUNG 11: 271-4 (JUN

- 1969) (IN GERMAN)

NETWORK MODEL FOR TRANSPORTATION SYSTEM. (SHORTEST CHAINS IN A DIRECTED, MULTITERMINAL NETWORK) PAYNE EE: BULL OPER PES SOC AMER 19 (SUP 2): B292-3

- (1971)

- THE SHORTEST ROUTE PROBLEM. PEART RM, RANDOLPH RH, BARTLETT TE: OPER RES 8(6): 866-8 (1960)

- SOME COMPUTATIONAL NOTES ON THE SHORTEST ROUTE PROPLEM. PERKO A; COMPUT J 8: 19-20 (1965/66)

- THE K-TH EEST ROUTE THROUGH A NETWORK. POLLACK M; OPER RES 9: 578-80 (1961); J MATH ANAL APPL 3: 547-59 (1961)

- SOLUTIONS OF THE SHORTEST ROUTE PROBLEM; A REVIEW. POLLACK M, WIEBENSON W; OPER RES 8: 224-30 (1960)

- TRANSPORTATION PLANNING MODELS. (MINIMUM PATH ALGOFITHMS) POTTS RE, KIRBY RF; MATH CEP, ADELAIDE UNIV, AUSTRALIA, (IN PROGRESS) (SEE KIRBY RF, "MINIMUM PATH ALGORITHM" FOR REPORT)

- COMMENTS ON A PAPER BY ROMESH SAIGAL: A CONSTRAINED SHORTEST ROUTE PROBLEM. ROSSEEL M; OPER RES 16(6): 1232-4 (NOV/DEC 1968)

- A CONSTRAINED SHORTEST ROUTE PROBLEM. SAIGAL R; BULL OPER RES SOC AMER 17(2): B264 (1969)

- THE K SHORTEST ROUTES AND K SHORTEST CHAINS IN A GRAPH. (PARTIAL GRAPH IS DEFINED BY SHORT CHAINS) SAKAROVITCH M; TRANSP RES 2(1): 1-11 (MAR 1968), OPER RES CENTER, UNIV OF CALIF, BERKELEY, OCT 1966, 24P. REP NO ORC-66-32

A PUBLIC TRANSPORTATION SIMULATION ALGORITHM. (MINIMAL PATHS, TREE BUILDING PROCESS, COST FUNCTION) SCHAERF B, SHAHAM J; P439-47 OF ISRAEL CONF ON OPERATIONS RESEARCH, 3RD, 1969, TEL-AVIV, PROC (DEVELOPMENTS IN OPERATIONS RESEARCH, VOL 1, AVI-ITZHAK B (ED), GORDON, 1971

SHORTEST ROUTE METHODS FOR LIMITED STATE SPACE, DETERMINISTIC DYNAMIC PROGRAMMING PROBLEMS.

- SHAPIRO JF; MIT, OPER RES CENTER, 1967 TECH REP 31

- BIBLIOGRAPHY ON THE SHORTEST ROUTE PROBLEMS. STAIRS SW; TRANSPORT NETWORK THEORY UNIT, LONDON GRAD SCHOOL BUS STUDIES, 28 NORTHUMEERLAND AVE, LONDON WC2, LSE-TNT-6

- A METHOD FOR SOLVING ARBITRARY WALL MAZES BY COMPUTER. (MOORE'S AND LEE'S ALGORITHMS) SUTHERLAND IE; IEEE TRANS COMPUT C-18: 1092-7 (1969)

- AN ALGORITHM FOR FINDING THE SHORTEST PATH. (REQUIRES ONLY THREE INDICES (1,2,3) FOR NUMBERING THE NODES) TYURENKOV VA: VYCHISL SISTEMY 6: 41-4 (1963) (IN RUSSIAN)

- A SERIAL TECHNIQUES TO DETERMINE MINIMUM PATHS. WEIMER DL; COMMUN ACM 6(11): 664-6 (1963)

- THE ASSIGNMENT AND THE SHORTEST ROUTE PROBLEMS. WEINTRAUB AF; OPERATIONS RES CENTER, CALIF UNIV, AUG 1972, 24P. PB-212299

- A METHOD FOR FINDING THE SHORTEST ROUTE THROUGH A ROAD NETWORK.

- WHITING PD, HILLIER JA; OPER RES QUART 11(1-2): 37-40 (1960)

- AN ALGORITHM FOR FINDING SHORTEST ROUTES FROM ALL SOURCE NODES TO A GIVEN DESTINATION IN GENERAL NETWORKS. (15 REFS) YEN JY; QUART APPL MATH 27: 526-30 (1970)

- HU'S DECOMPOSITION ALGORITHM FOR SHORTEST PATHS IN A NETWORK.

- YEN JY; OPER RES 19 (3) : 983-5 (MAY/JUN 1971)

- FINDING THE K SHOPTEST LOOPLESS PATHS IN A NETWORK. (COMPUTATIONAL UPPER BOUND INCREASES ONLY LINEARLY WITH THE

- VALUE OF K) YEN JY: MANAGE SCI THEORY SER 17(11): 711-15 (JUL 1971)

- FINDING LENGTHS OF ALL SHORTEST PATHS IN N NODE NONNEGATIVE DISTANCE COMPLETE NETWORKS USING 1/2\* (N-3) ADDITIONS AND N-3 COMPARISONS.

YEN JY; J ASSOC COMPUT MACH 19(3): 423 (1972)

- SOME ALGORITHMS FOR FINDING THE SHORTEST ROUTES THROUGH THE GENERAL NETWORKS.

- VEN JV: P377-88 OF INT CONF ON COMPUTING METHODS IN OPTIMIZATION PROBLEMS, 2ND, 1968, SAN REMO, ITALY

SECTION 1.2 OPTIMAL PATHS.

ON KTH BEST POLICIES. (OPTIMAL ROUTING) BELLMAN R, KALABA R; SOC INDUS APPL MATH, APPL MATH 8(4): 582-8 (1960)

ON OPTIMAL ROUTING THROUGH COMMUNICATION NETS. CEDERBAUM I; IN NATO ADVANCED STUDY INST ON NETWORK AND SIGNAL THEORY, PETER PEREGINUS, LONDON, 1973

- OPTIMUM SYNTHESIS OF STATISTICAL COMMUNICATION NETWORKS -PSEUDO PARAMETRIC TECHNIQUES.

- FRANK H, HAKIMI SL; J FRANKLIN INST 284: 407-16 (1967)

- OPTIMUM ROUTES IN COMMUNICATION SYSTEMS WITH CHANNEL CAPACITIES AND CHANNEL RELIABILITIES.

FRISCH IT: IEEE TRANS COMMUN SYST CS-11: 241-4 (1963)

AN ALGORITHM FOR CONSTRUCTION OF THE LEAST VULNERABLE COMMUNICATION NETWORK OR THE GRAPH WITH MAXIMUM CONNECTIVITY.

- HAKIMI SL; IEEE TRANS CIRCUIT THEORY CT-16(2): 229-30 (MAY 1969)

- A FORMAL BASIS FOR THE HEURISTIC DETERMINATION OF MINIMUM COST PATHS.

HART PE, NILSSON NJ, RAPHAEL B; IEEE TRANS SYST SCI CYBERN SSC-4: 100-7 (JUL 1968) CPA 1968: 2534

MOST RELIABLE ROUTES IN A NETWORK. HU TC; SIAM REV 8(2): 261 (1966)

- A SYSTEMATIC METHOD OF FINDING ALL DIRECTED CIRCUITS AND ENUMERATING ALL DIRECTED PATHS. (ALGORITHM) KAMAE T; IEEE TRANS CIRCUIT THEORY CT-14(2): 166-71 (JUN 1967)

- OPTIMAL PATH IN NETWORKS WITH TIME VARYING TRAVERSE TIME AND EXPENSES BRANCHES. LING ST, FURUNO K, TEZUKA Y; TECHNOL REP OSAKA UNIV 22(1053-1089): 335-43 (OCT 1972)

- ON THE SEARCH FOR STRONGLY CONNECTED DIGRAPHS BASED ON ONE SUCH SUPPORTING GRAPH OF GENERALIZED MINIMUM OR MAXIMUM LENGTH.

- MANCA P; CALCOLO 8: 139-47 (JAN/JUN 1971) (IN ITALIAN)

- MINADDITION AND AN ALGORITHM TO FIND THE MOST RELIABLE PATH IN NETWORK. NARAHARI PANDIT SN; IRE TRANS CIRCUIT THEORY CT-9(2):

- 190-1 (1962)

- THEOREMS AND ALGORITHMS FOR FINDING OPTIMAL PATHS OVER GRAPHS WITH ENGINEERING APPLICATIONS. PARIKH AC; PHD THESIS, PURDUE UNIV, 1960, 94P

- FINDING THE MOST RELIABLE ROUTES IN A COMMUNICATION SYSTEM. PARIKH SC, FRISCH IT; IEEE TRANS COMMUN SYST CS-11: 402-7 (1963)

- ANALOG COMPUTER FOR FINDING AN OPTIMUM ROUTE THROUGH A COMMUNICATIONS NETWORK. RAPAPOFT H, ABRAMSON P; IRE TRANS COMMUN SYST CS-7: 37-42 (MAY 1959)

- ALGORITHMS AND ANALOG COMPUTERS FOR THE MOST RELIABLE ROUTE THROUGH A NETWORK. SHARAK GR; OPER RES 12: 632 (1964)

- ALGORITHMS TO FIND THE MOST RELIABLE PATH IN A NETWORK. WING 0: IRE TRANS CIRCUIT THEORY CT-8(1): 78-9 (1961)

SECTION 1.3 TRAVELING SALESMAN PROBLEM.

- THE TRAVELING SALESMAN PROBLEM. ARNOFF EL, SENGUPTA SS; IN VOL 1 P150-7 OF PROGRESS IN OPERATIONS RESEARCH, ACKOFF RL(ED). WILEY, 1961 (658.54 P96) 132304

- HEURISTIC ALGORITHM FOR TRAVELING SALESMAN PROBLEMS. (22 REFS)

- ASHOUR S, VEGA JF, PARKER RG; TRANSP RES 6(2): 187 (1972)

- DYNAMIC PROGRAMMING TREATMENT OF THE TRAVELING SALESMAN PROBLEM

- BELLMAN R: J ASSOC COMPUT MACH 9: 61-3 (1962)

- THE TRAVELING SALESMAN PROBLEM: A SURVEY. BELLMOPE M, NEMHAUSER GL; OPER RES 16(3): 538-58 (MAY/JUN 1968)

- MATHEMATICAL PROGRAMMING SOLUTION OF TRAVELING SALESMAN EXAMPLES. BOCK F; P339-41 OF GRAVES RL AND WOLFE P (EDS), RECENT

- ADVANCES IN MATHEMATICAL PROGRAMMING. MCGRAW-HILL, 1963

- A METHOD FOR SOLVING TRAVELING SALESMAN PROBLEMS. CROES GA; OPER RES 6: 791-812 (1958)

SELECTION OF AN INITIAL SOLUTION FOR THE TRAVELING SALESMAN PROBLEM. DACEY MF; OPER RES 8: 133-4 (1960)

- ON THE SHORTEST ROUTE THROUGH A NETWORK. DANTZIG GB; MANAGEMENT SCI 6(2): 187-190 (1960)

- ON A LINEAR PROGRAMMING, COMBINATIONAL APPROACH TO THE TRAVELING SALESMAN PROBLEM. DANTZIG GB, FULKERSON DR, JOHNSON SM; OPER RES 7: 58-66 (1959)

- NEW METHOD OF SOLUTION OF THE TRAVELING SALESMAN PROBLEM. DAVIDSON ES: DEPT OF COMPUTER SCI, UNIV OF ILLINOIS, MAR 1966, REP NO 201

SEQUENCING A ONE-STATE VARIABLE MACHINE: A SOLVABLE CASE OF THE TRAVELING SALESMAN PROBLEM.

- GILMORE PC, GOMARY RE; OPER RES 12(5): 655-79 (1964)

- SOLUTION TO THE TRAVELING SALESMAN PROBLEM BY DYNAMIC PROGRAMMING ON THE HYPERCUBE. GONZALES RH: MIT, OR CENTER, 1962, TECH REP NO 13

- TRAVELING SALESMAN PROBLEM A SURVEY OF THEORETICAL DEVELOPMENTS AND APPLICATIONS.

- GUPTA JND; OPSEARCH 5(4): 181-92 (DEC 1968)

- TRIP ON A GRAPH. (SHORTEST LENGTH TRIP, TRAVELING SALESMAN PROBLEM) HANSEN P, MAES JM; CAH CENTRE ETUD RECH OPER 11(3):

- 139-50 (NOV 1969)

- ON THE RELATION BETWEEN THE TRAVELING SALESMAN AND THE LONGEST PATH PROBLEM. HARDGRAVE WW, NEMHAUSER GL; OPER RES 10: 647-57 (1962)

- REVISED VERSION OF ALGORITHM 7: SHORTEST ROUND TRIP BETWEEN

- N POINTS. (TRAVELING SALESMAN PROBLEM) HAUSCH E, KNODEL W; COMPUT, ARCH ELEKTRON RECHNEN, ARCH ELECTRON COMPUT 5(4): 385-92 (1970) (IN GERMAN)

- A DYNAMIC PROGRAMMING APPROACH TO SEQUENCING PROBLEMS. HELD M, KARP R; J SIAM 10(1): 196-210 (MAR 1962)

- THE RECORD BALANCING PROBLEM: A DYNAMIC PROGRAMMING SOLUTION OF A GENERALIZED TRAVELING SALESMAN PROBLEM. HENPY-LAFORDERE AL; REV FFANCE INFORM OPER 3(B2): 43-9 (AUG 1969)

- A HEURISTIC APPROACH TO SOLVING TRAVELING SALESMAN PROELEMS. KARG LL, THEMPSON GL; MANAGE SCI 10: 225-48 (1964)

- ALGORITHM 7: SHORTEST POUND TRIP BETWEEN N POINTS. (TRAVELING SALESMAN PROBLEM, ALGOL PROCEDURE) KNODEL W; COMPUT APCH ELEKTRON RECHNEN, ARCH ELECTRON COMPUT 3(2): 151-6 (1966) (IN GERMAN)

- MAN-MACHINE APPROACH TOWARD SOLVING THE TRAVELING SALESMAN PROBLEM.

- KROLAK P, MARBLE G; P250-64 OF SHAPE/ACM/IEEE DESIGN AUTOMATION WORFSHOP, 7TH PROC, 1970, SAN FRANCISCO

- COMPUTER SOLUTIONS OF THE TRAVELING SALESMAN PROBLEM. LIN 5; BELL SYST TECH J 44(10); 2245-69 (1965)

- AN ALGORITHM FOR THE TRAVELING SALESMAN PROBLEM. (BRANCH AND BOUND)

- LITTLE JDC, MURTY VKG, SWEENEY DW, KAREL C: OPER RES 11(6): 972-89 (NOV/DEC 1963)

- SOLVING THE TRAVELING SALESMAN PROBLEM BY INTEGER LINEAR FROGRAMMING. MARTIN GT; CORPORATION FOR ECONOMIC AND INDUSTRIAL

- RESEARCH, NY, 1966

- INTEGER PROGPAMMING FORMULATIONS AND TRAVELING SALESMAN PROBLEMS.

- MILLER CE, TUCKER AW, ZEMLIN RA; J ASSOC COMPUT MACH 7: 326-9 (1960)

METHOD OF SOLUTION OF THE TRAVELING SALESMAN PROBLEM BY MEANS OF INTEGER LINEAR PROGRAMMING. (THE PROBLEM OF FINDING THE HAMILTON PATHS OF SHORTEST LENGTH IN A COMPLETE GRAPH) MUDROV VI: 2H VYCHISL MAT MAT FIZ 3(6): 1137-9 (1963) (IN RUSSIAN)

- THREE NEW METHODS FOR SOLVING THE TRAVELING SALESMAN PROBLEM PARTS 1 AND 2. MUELLER-MERBACH H; ABLAUF- UND PLANUNGSFORSCHUNG 7 (1):

- 32-46 (JAN/MAR 1966); IBID 7 (2): 78-91 (APR/JUN 1966) (IN GERMAN)

- AN ALGORITHM TO FIND ELEMENTARY NEGATIVE COST CIRCUITS WITH A GIVEN NUMBER OF ARCS - THE TRAVELING SALESMAN PROBLEM. NETTER JP; OPER RES 19(1): 234-7 (JAN/FEB 1971)

- A SEQUENTIAL METHOD FOR DISCRETE OPTIMIZATION PROBLEMS AND ITS APPLICATION TO THE ASSIGNMENT, TRAVELING SALESMAN, AND THREE MACHINE SCHEDULING PROBLEMS. NICHOLSON TAJ; J INST MATH APPL 3: 362-75 (1967)

- SOME OBSERVATIONS ON THE LONGEST PATH PROBLEM.

- PANDIT SNN; OPER RES 12: 361-4 (1964)

- AN EMJINEERING APPPOACH TO THE TRAVELING SALESMAN PROBLEM. ROBEPTS SM, FLORES B; MANAGE SCI SER & 13: 269-88 (1966)

- ROUTING PROBLEM WITH K SPECIFIED NODES. (TRAVELING SALESMAN PROBLEM, VERSIONS OF THE CROSSING PUZZLE) SAKSENA JP, KUMAR S; OPER RES 14(5): 909-13 (SEP/OCT 1966)

- ALGORITHMS FOR THE SOLUTION OF THE OPTIMAL COST TRAVELING SALESMAN PROBLEM. SHAPIRO D; SC D THESIS, WASHINGTON UNIV, 1966

- A SUFFICIENCY SOLUTION OF THE TRAVELING SALESMAN PROBLEM. STAUDHAMMER J, ASH M; SYSTEM DEVELOP CORP, SANTA MONICA, CALIF, AUG 1966, 66P. REP NO SP-2514/000/00

- SOME IMPROVED ALGORITHMS FOR COMPUTER SOLUTION OF THE TRAVELING SALESMAN PROBLEM. STEIGLITZ K, WEINER P: P814-21 OF ALLERTON CONF ON CIRCUIT AND SYSTEM THEORY, 6TH PROC, 1968,

- A TRAVELING SALESMAN ALGORITHM. (FIVE TOWNS, TREE DIAGRAM) WOOTTON J; METRA (FRANCE) 8(4): 535-42 (DEC 1969)

SECTION 1.4 RELATED TOPICS AND METHODS.

- EFFICIENT ALGOPITHM FOR COMPUTING FREE DISTANCE. BAHL LR; IEEE TRANS INFORM THEORY IT-18: 437 (1972)

- ENUMERATION OF ALL CIRCUITS OF GRAPH. BAPESWARAO VV, MURTI VGK; IEEE PROC 57(4): 700-1 (APR 1969)

- RESULTS IN USING GOMORY'S ALL-INTEGER INTEGER ALGORITHM TO DESIGN OPTIMUM LOGIC NETWORKS.

- BAUGH CR, IBARAKI T, MUROGA S; OPER RES 19(4): 1090-6 (1971)

- ON MAXIMAL CHAINS. (ALGORITHM, COMPLETE SUBGPAPHS) BEDMAREK A, TAULBEE O; REV ROUM MATH PURES APPL 11: 23-5 (1966)

- NETWORK CESIGN WITH FIXED AND VARIABLE COST ELEMENTS. (GLOBALLY OPTIMUM SOLUTION) BILLHEIMER JW; TRANSP SCI 7(1): 49-74 (FEB 1973)

- BILLHEIMER JW; TRANSP SCI 7(1): 49-74 (PEB 1973)

- FINITE GRAPHS AND NETWORKS: AN INTRODUCTION WITH APPLICATIONS.

- BUSACKER R, SAATY T; MCGRAW-HILL, 1965 (513.83 B95) 104339

- NUMBER OF PATHS AND CYCLES IN A DIGRAPH. (ALGORITHM,

- MATRICES) CARTWRIGHT D, GLEASON T; PSYCHOMETRIKA 31: 179-99 (1966)

- AN ADMISSIBLE AND OPTIMAL ALGORITHM FOR SEARCHING AND/OR GRAPHS.

- GRAPHS. CHANG CL, SLAGLE JR; ARTIF INTELL 2(2): 117-28 (FALL 1971) (IN DUTCH)

- ON FINDING THE SIMPLE PATHS AND CIRCUITS IN A GRAPH. DANIELSON GH; IEEE TRANS CIRCUIT THEORY CT-15: 294-5 (1968)

- ALL SHORTEST ROUTES FROM A FIXED ORIGIN IN A GRAPH. DANTZIG GB, FLATTNER WO, RAO MP; P85-92 OF THEORY OF GRAPHS, ROSENSTIEHL P(ED), GORDON AND BREACH, NY, 1967

- TRANSIT PATHFINDER ALGORITHM. (IBM 7090, MINIMUM TIME PATHS) DIAL RB; HIGHWAY RES REC, HIGHWAY RES BOARD NO 205: 67-85 (1967)

- TWO ALGORITHMS FOR BIPARTITE GRAPHS. (MAXIMUM TRANSVERSALS) DULMAGE AL, MENDELSON NS; J SOC INDUS APPL MATH, J APPL MATH 11: 183-94 (1963)

- THEORETICAL IMPROVEMENTS IN ALGORITHMIC EFFICIENCY FOR NETWORK FLOW PROBLEMS. (GENERAL MINIMUM COST FLOW PROBLEM) EDMONDS J, KARP RM; J ASSOC COMPUT MACH 19(2): 248-64 (APR 1972)

SOME NETWORK MODELS IN MANAGEMENT SCIENCE. (SHORTEST PATH PROBLEMS, NETWORKS OF FLOWS, SIGNAL FLOW GRAPHS AND ACTIVITY NETWORKS AND THEIP GENERALIZATIONS) ELMAGHRABY SE; SFRINGER VERLAG, NY, 1970, 176P

A SIMPLE ALGOPITHM FOR FINDING MAXIMAL NETWORK FLOWS AND AN APPLICATION TO THE HITCHCOCK PROPLEM. FORD LR, FULKEFSON DR; CAN J MATH 9(2): 210-18 (1957)

FLOWS IN NETWORKS. FORD LR, FULKERSON DR: PRINCETON UNIV PRESS, 1962