181

SET VENVERE

5.0

OC

S

MOULTON

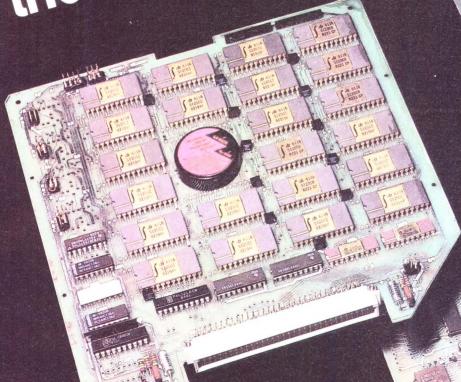

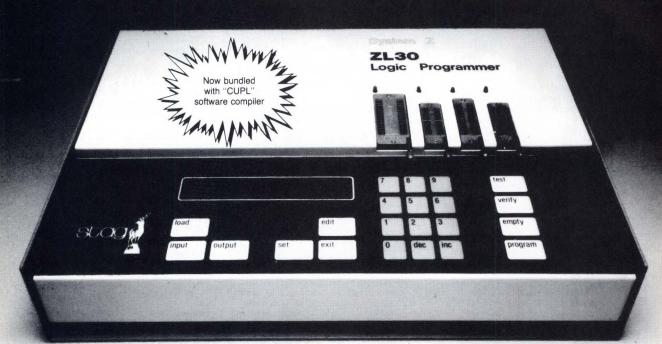

# Silicon compiler customizes VLSI designs with turnkey simplicity

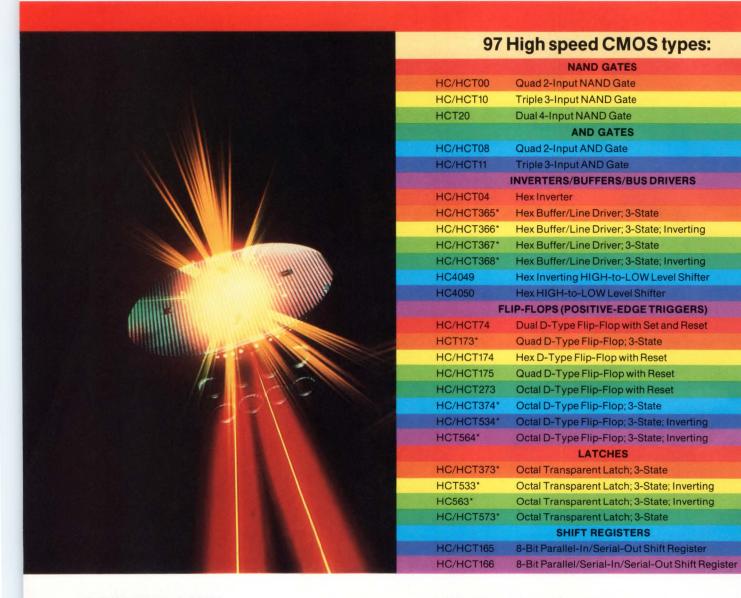

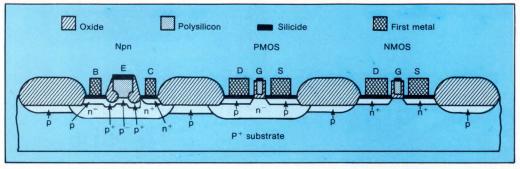

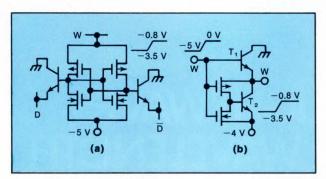

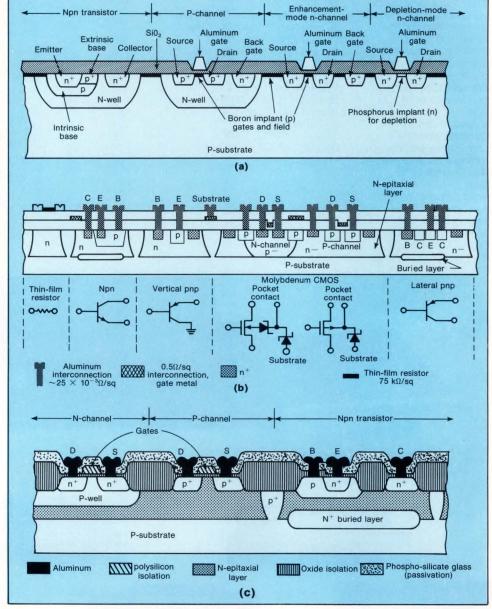

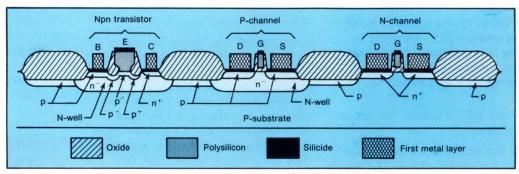

### **CMOS TECHNOLOGY**

Technology Report: CMOS seeks to dominate the digital world

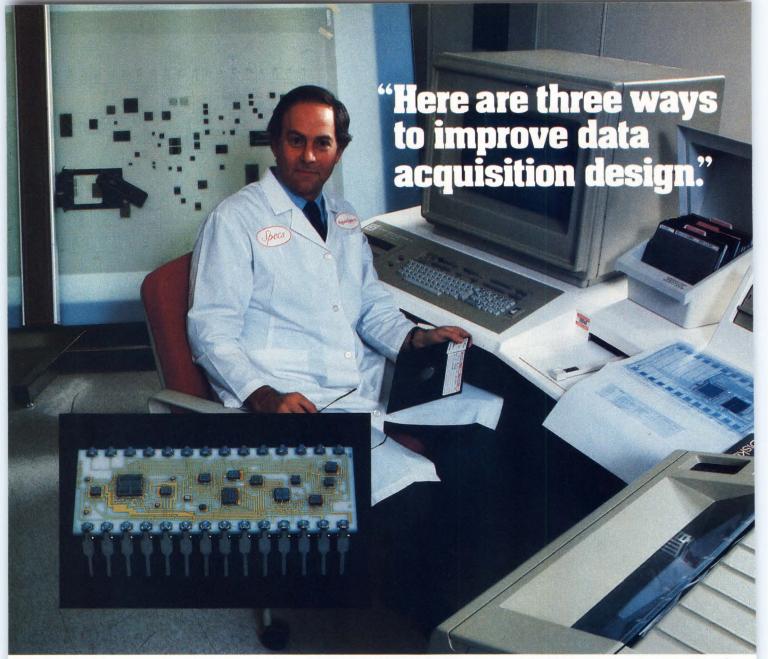

Technology Report: Analog CMOS driven by need for mixed circuitry

The future of CMOS: Twelve experts tell how CMOS will blossom

Six leading-edge CMOS ICs bring new sparkle to system design

PG 50-

PO PO 53-

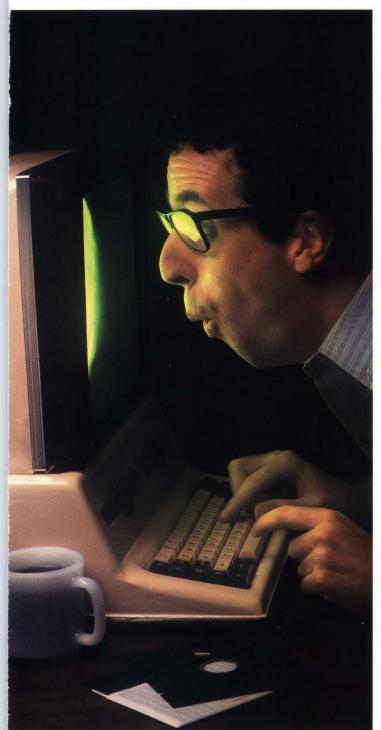

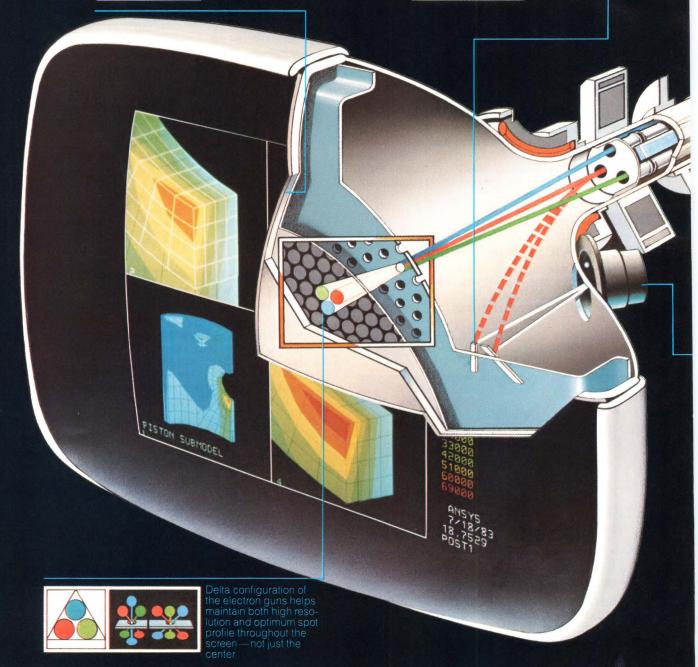

# AMD YOUR CRT.

AMD's CRT controller family wrings every last drop of performance out of your video screen.

You get a dazzling, attractive display your customers will find irresistible.

# The Am8052. You'll wonder where the flicker went.

Thanks to on-board DMA and triple row buffers, you get vertical and horizontal split screens, with smooth-scrolling windows. All flicker-free.

You even get double-height and doublewidth characters, superscripts and subscripts.

# The Am8152A/53A. Make your display look its sparkling best.

You get cleaner, crispier characters with the 100MHz video system controller. And proportional spacing down to two pixels.

No other VLSI chip set gives you as much. And to top it off, the chips even take over many of the functions of the CPU. Like linked list manipulation for easier editing. Your CPU has better things to do.

# We'll put you as far ahead of the competition as we are.

Controllers. Bipolar and MOS microprocessors. Communication circuits. Signal processors. Nobody makes as many peripherals for as many microprocessors as AMD.

And every single chip meets or exceeds the International Standard of Quality.

The International Standard of Quality guarantees a 0.1% AQL on all electrical parameters, AC and DC, over the entire operating range.

If you want the most out of your tube, put the squeeze on AMD. We'll show

you several ways to put the sparkle in your customer's smile.

# Advanced Micro Devices 27

901 Thompson Place, P.O. Box 3453 Sunnyvale, CA 94088 (408) 749-5000, outside California, call toll-free (800) 538-8450, Ext.5000.

# Squeeze more out of the tube.

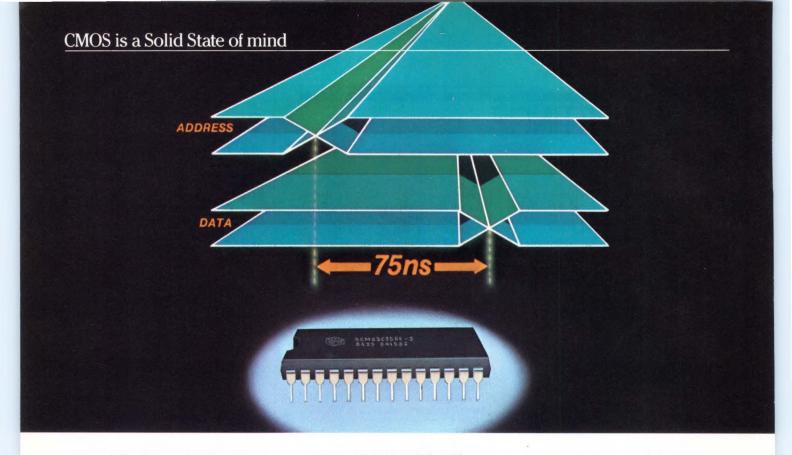

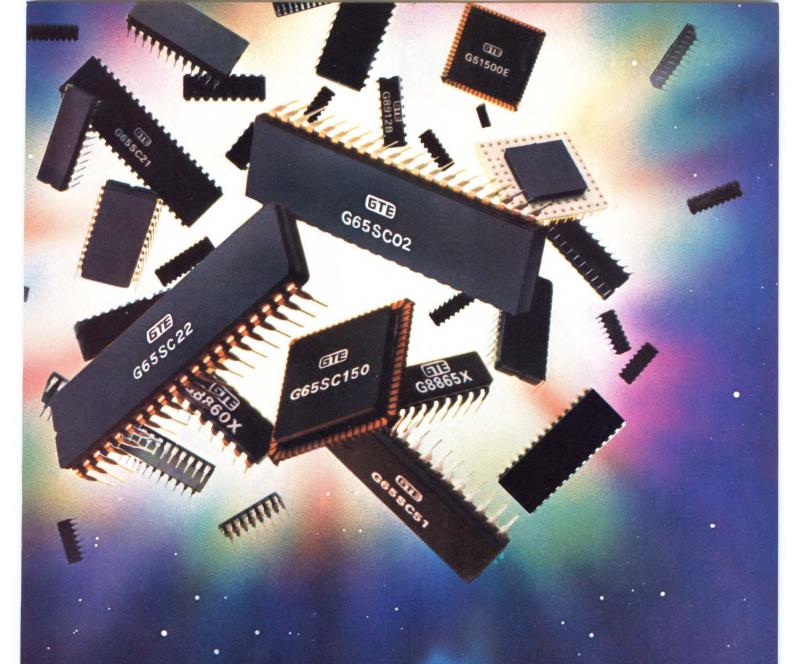

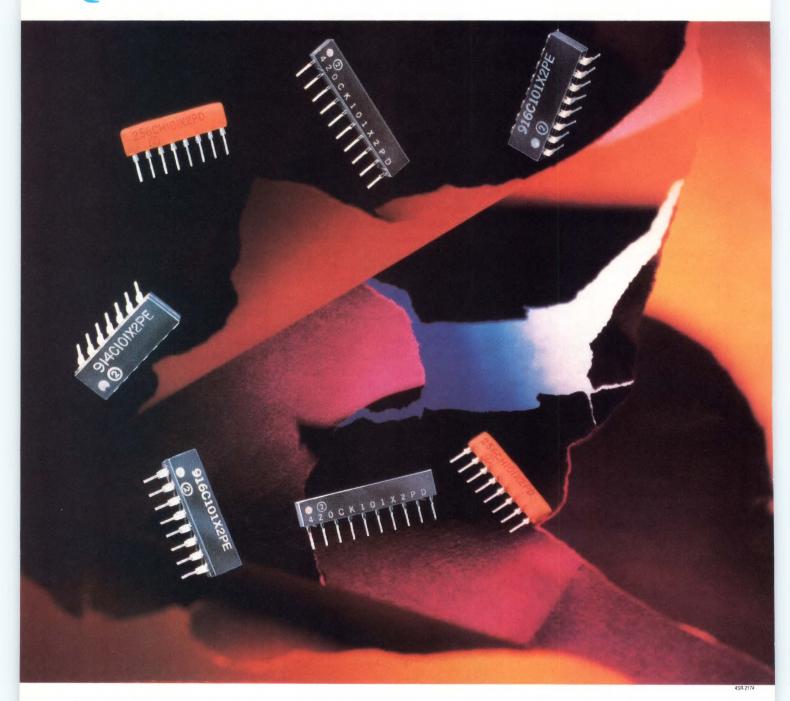

# ROCKWELL SEMICONDUCTOR TECHNOLOGY BREAKS THE CMOS SPEED BARRIER.

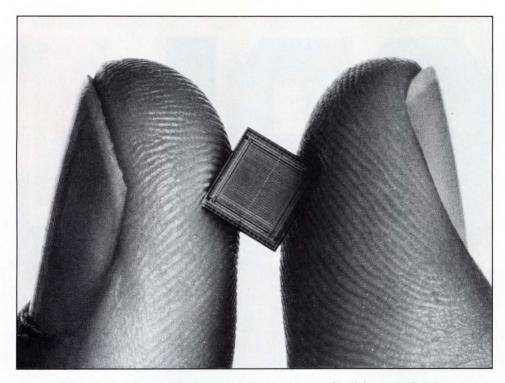

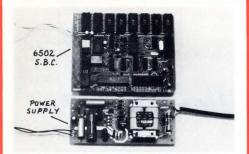

Led by the R65C02 microprocessor, Rockwell's R65C21, R65C24, R65C51 and R23C64 are the latest members of our high-speed, lowpower CMOS family.

500 ns instruction time is our CMOS microprocessors' recordbreaking speed—two times faster than NMOS—with power consumption of only 80mW. And now Rockwell International offers peripheral devices such as the R65C21 (PIA), R65C24 (PIAT) and the R65C51 (ACIA) for your system design.

Our low-power, high-speed combination is not all you get from Rockwell's CMOS; you also get latch-up immunity, a bit manipulation and byte operation instruction set, power and temperature variance toleration, low noise generation, high noise immunity and a small die size. All these features combine to save you design time, lower your costs and improve system performance.

If all that doesn't convince you, write on your letterhead for a free sample of our R65CO2 CPU.

(It's pin-and bus-compatible with the popular R6502). Using is believing.

For your high-speed CMOS storage, we're accepting codes **now** for our R23C64 CMOS Static ROM. This 64K ROM has an access time of 150 ns and consumes only 10mW active, 50µW passive. With 24-hour code approval and competitive lead times, too, you won't find CMOS any faster.

Find out how our breakthrough CMOS family can perform for you. Contact your local Rockwell distributor or sales representative today.

# Rockwell Semiconductor Products Division

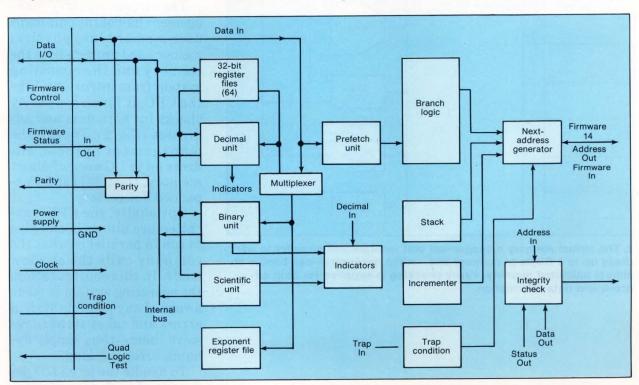

Rockwell International, P.O. Box C, MS 501-300, Newport Beach, CA 92660. Call Toll Free (800) 854-8099. In California, (800) 422-4230.

**Rockwell International**

...where science gets down to business

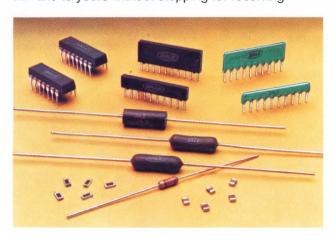

# PUT MORE AP INTO YOUR BUYING POWER

Dale's ZIP<sup>™</sup> program is more than a promise. It's a guarantee that we can save you time and eliminate many of the headaches involved with component specification, procurement and evaluation.

And, now ZIP is more comprehensive than ever:

# **GUARANTEED DELIVERY**

When we confirm a shipping date for any product you order under the ZIP program, we guarantee shipment will be made on or before that date or we will pay the shipping costs for the delinquent portion.

# **GUARANTEED QUALITY**

ZIP moves the products you need from our production line to yours without stopping for receiving

inspection. We guarantee they will perform as specified without costly in-plant verification.

# AT NO EXTRA COST

Dale's ZIP components are competitively priced and most are available from comprehensive factory stocking programs. All you have to do to get these extra advantages is to specify that you want ZIP products at the time the order is placed.

# COVERING MORE PRODUCTS THAN EVER

**Thick film resistor networks:** Molded DIP and SIP (MSP/MDP), coated SIP (CSC) 01, 03 schematics, 2% tolerance. Phone 915-592-3253, El<sub>2</sub>Paso, TX.

Thick film chip resistors: CRCW-1206, 1%, 5% tolerance. **Metal film resistors:** 1/4 watt commercial (CCF-55); Hybrid chip thermistors (Type "H"). Phone 402-371-0080, Norfolk, NE.

**Wirewound resistors:** Commercial/industrial, 3 watt, (CW-2B, RS-2B); Low value, .005-.1 ohm (LVR-3). Phone 402-564-3131, Columbus, NE.

# CALL FOR ADDITIONAL INFORMATION

For additional information on products covered by the ZIP program, contact your Dale representative or one of the factory locations noted above. ZIP—it's your assurance of continued Dale leadership in component quality and service.

# Dale makes your basics better.

DALE ELECTRONICS, INC., 2064 12th Avenue, Columbus, NE 68601 • Phone 402-564-3131

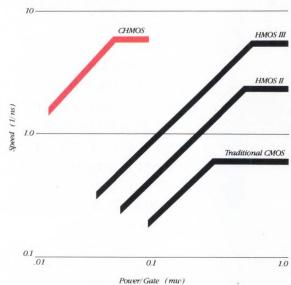

But not lately. Intel's 256K DRAM in CHMOS will set new industry standards. Redefine high performance. And change the direction of VLSI technology.

Our revolutionary new chip provides four times the storage capacity, a high data bandwidth

mode and a drastically lower power consumption than NMOS DRAMs.

It combines the best benefits of CMOS static RAMs, low power and high bandwidth, with the traditional high density and cost effectiveness of DRAMs.

Making the 256K CHMOS DRAM the perfect building block to a smaller, faster, low-power portable system with the same For a spical IXX IX display, intels (cHMOS DRAMS outperform NMOS better than two to one. high performance

For the first time, you can design your truly portable system to run the most powerful spreadsheet software on the market. Without costly CMOS SRAMs. Even work-

High speed. High bandwidth. Onetwentieth the standby power requirement of NMOS DRAMs. Intel offers an entire and 64K DRAMs in The low power advantage: Intel's CHMOS Dynamic RAMs require only 5% of conventional NMOS. CHMOS. The breakthrough combination of our own high performance technology, HMOS, with the low power advantages of CMOS.

On the performance side, high data bandwidth is the result of two new

© 1984 Intel Corporation

methods of data access. Both Ripplemode™ and Static column mode provide the ability to randomly read or write

> any series of bits within a single row at a minimum cycle time of 65ns. This incredible speed makes the **CHMOS DRAM** family the ideal solution for graphics, array processors and other high speed

digital signal processing

applications.

In addition, their resistance to soft errors provides the extremely high reliability critical to medical instrumentation, financial transaction sys-

tems and other failsafe applications.

Low power. High density. Unbeatable performance. Available now for your system design.

Call Intel today, toll-free at (800) \_\_51C256L 538-1876. In California, (800)

672-1833.

Because there have been innovations as important. But none as important to you.

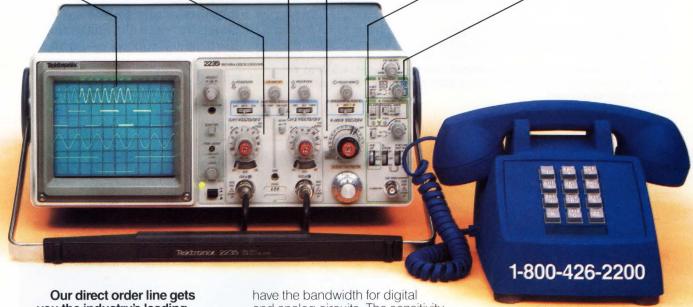

In your system or on the bench...

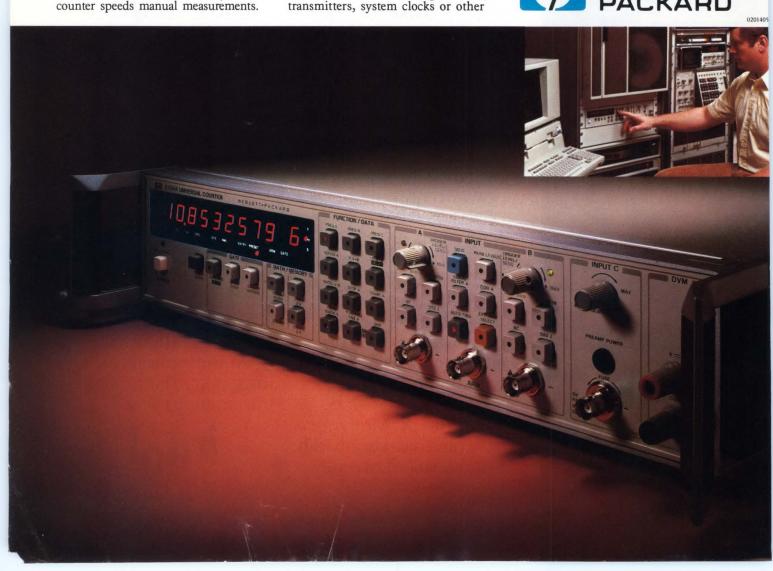

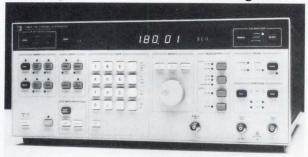

# the latest HP counter delivers all the right numbers. At the right price.

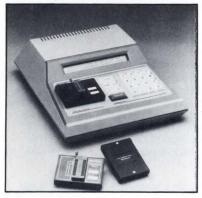

# A new standard for your system.

The HP 5334A is quickly becoming the new system standard. And for good reason: Full HP-IB programmability is included in our low price of \$2,800\*. That means it's a natural for fully automatic systems. Add to that automatic peak amplitude measurements and our exclusive auto attenuation for a real counter breakthrough in this price range. Plus easy interfacing to computers, such as the HP Series 200. And the HP 5334A can even help boost your overall system performance. That's because its internal processor performs math functions and automatic measurements, which lower your system overhead.

# Fast and easy measurements on your bench.

Bench users will like the way this counter speeds manual measurements.

At the push of a button, you'll make waveform measurements such as peak, pulse width, rise and fall...automatically and fast. And its ability to store up to ten front-panel setups in its non-volatile memory will save you setup time and trouble.

# Measure for measure, you get more for less.

You get a lot of performance in this counter bargain. Single-shot resolution of 2 ns, 100 MHz frequency operation is standard or 1.3 GHz C-channel optional. Fast, unformatted throughput of 150 measurements/second. There's even an optional 4-digit, autoranging, auto-polarity DVM. And naturally, it's fully compatible with the IEEE Recommended Practice for Code and Format Conventions of IEEE-728.

Whether you need precise measurements of oscillators, generators, transmitters, system clocks or other

frequency or time-related applications, the HP 5334A comes up with the right numbers.

# The quickest way to get our number.

For more information on the HP 5334A Universal Counter or the full range of solutions to your time interval or frequency measurement problems, request our data sheet and our complete counter brochure. Call your local HP sales office listed in the telephone directory white pages. Ask for the electronic instruments department.

\*U.S.A. list price only.

CIRCLE 9

# **Electronic Design**

Editor-in-Chief: Lucinda Mattera

Executive Editor: Stanley Runyon

Managing Editors:

Michael Riezenman, Technology Report Margaret Eastman, Design Entries Warren Andrews, Technology News Michael Robinson, New Products

Editor-at-large: Martin Gold

Associate Managing Editors:

David Bursky, West Coast

Roger Allan, Special Features

Executive Art Director: Thomas Phon

Senior Editor: Max Schindler

**Technology Editors:**

Analog & Power: Frank Goodenough Communications & Industrial: Roger Allan

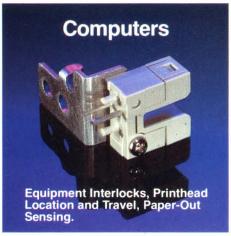

Computers: Mark Brownstein

Computer Peripherals: Stephan Ohr (Sunnyvale)

Instruments: Robert Milne

Semiconductors: David Bursky (Sunnyvale)

Software: Max Schindler

Field Editors:

East Coast: Carole Patton (Hasbrouck Heights);

Gary Elinoff (Boston)

West Coast: Curtis Panasuk (Sunnyvale);

Ray Weiss (Los Angeles)

Midwest: Terry Costlow (Chicago)

South: Heather Bryce (Dallas)

Europe: Mitch Beedie (England)

Design Solutions Editor: Harold Winard New Products Editor: Susan Nordyk Contributing Editor: Gil Bassak

Chief Copy Editor: Diane Tunick-Smith

Copy Editors: Aaron Fischer, Ellen Muraskin, Rachel Maizes

Editorial Production Manager: Anne Gilio Turtoro Assistants: Donna A. Carullo, Catherine Wolf Assistant Art Director: Joanne M. Goodfellow

Graphic Designers: Nancy Hajeski, Mary Van Bodegon

Illustrator: Alice Topf-Cirica

Editorial Secretaries: Mary James, Ruth Ottenheimer, Audrey Naumburg Editorial Administrator: Camille Metzler

Editorial Administrator: Camille Metzle

**Editorial Offices:**

Headquarters: 10 Mulholland Dr., Hasbrouck Heights, N.J. 07604 (201) 393-6000, TWX—710-990-5071 (HAYDENPUB HBHT), Cable Haydenpubs. Boston: Hillcrest Office Park, 260 Bear Hill Rd., Suite 100, Waltham, Mass. 02154, (617) 890-8050. Sunnyvale: 1307 South Mary Ave., Suite 212, Sunnyvale, Calif. 94087, (408) 736-6667. Los Angeles: 8939 South Sepulveda Blvd., Suite 260, Los Angeles, Calif. 90045, (213) 641-6544. Chicago: 200 East Ontario, Chicago, III. 60611, (312) 337-0588. Dallas: 9451 LBJ Freeway, Suite 220, Dallas, Texas 75243, (214) 234-0508. England: Avalon House, Cranston Road, East Grinstead, West Sussex RH19 3HG, 0342-314111.

National Sales Manager: Paul C. Mazzacano Director of Marketing: Stephen E. Scrupski Business Manager: Thomas E. Vachon

Promotion Manager: Jay McSherry Assistant: Evelyn Schmidt Copy Writer: James Keane

Research Manager: Kenneth J. Turtoro

Assistant: Betsy Tapp

**Advertising Production Manager:** Marjorie Duffy Assistants: Roseanne Erickson, Brenda Sauter

Circulation Director: Barbara Freundlich Fulfillment Manager: Lori Shulman Reader Service: Paula Greenleaf

Reprints: Jim Dysert

#### Vice President and Publisher:

Laurence Altman

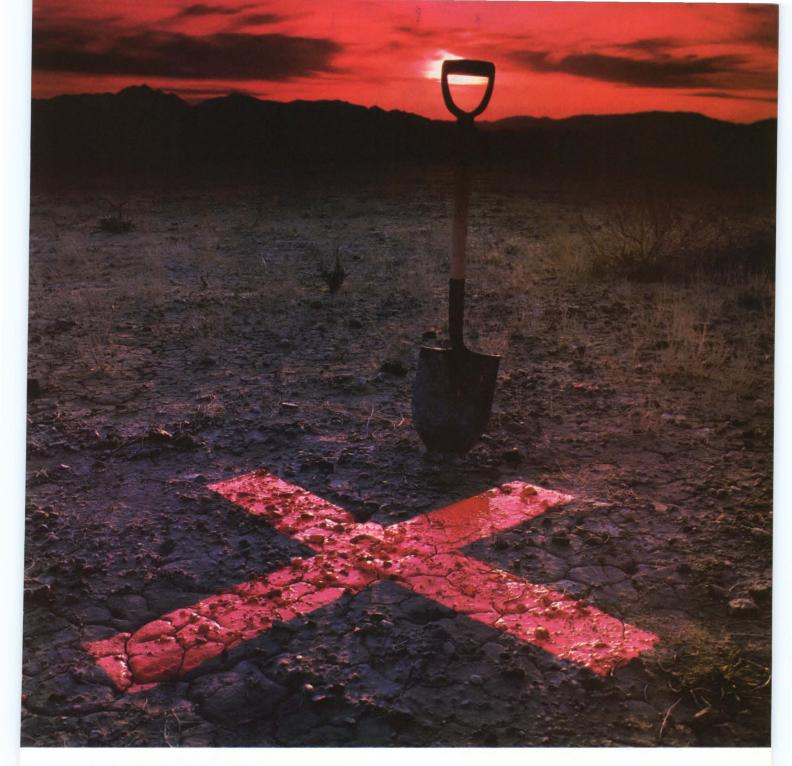

# **BEHIND THE COVER**

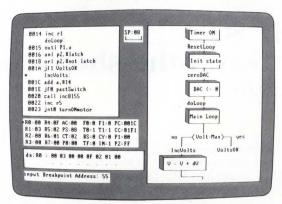

ut it in writing" could be Stephen Johnson's battle cry. For that was exactly what he did on becoming Silicon Compilers' new vice president of engineering a year ago. With the position came the assignment to produce the company's—and the world's—first commercial turnkey silicon compilation system.

The massive software project meant distilling the company's two years of success in producing fully laid-out VLSI chips from only their architectural descriptions. And that entailed being "as systematic about developing the software as the system is about designing chips," says Johnson.

So, before letting designers write a single line of code, he and others first produced a corporate specification that set rigid and detailed programming standards for structuring the software. And since the software was written in C, a language that, as Johnson puts it, "lets you hang yourself," the standards went so far as to outlaw certain constructs.

Enter vice president Dave Johannson, silicon-compiler veteran and protégé of VLSI pioneer Carver Mead (Johannson and Mead were two of the company's three founders). He and Johnson next condensed all the ideas and concepts of the company's past two years into a 455-page functional system specification. It even included a chapter-and-verse description of how the system would look to the user. This specification, Johnson points out, "had a tremendous leveling effect" on the design team, bringing everyone's ideas into harmony. That, however, was only the beginning.

There followed a marathon effort to come up with a top-down design of the actual system. In a few weeks, a 3000-page document was produced, describing every software routine, its role, and its interfaces. About 2600 separate functions, in all, had to be coded into routines. Next came the equally meticulous and exhaustive scheduling sessions and the bottom line on development time: one year.

Is this any way to develop software? Johnson thinks so. And he's not alone: the company met its schedule to within a week. Exactly what it produced is the subject of this issue's three-part cover story (p. 167) written by Stan Mazor and, of course, Stephen Johnson.

# ElectronicDesign

October 4, 1984 • Vol. 32 No. 20

#### **DEPARTMENTS**

- 3 Behind the Cover

- 6 Contents Spotlight

- 11 On Reflection

- 15 Reader Feedback

- 23 U.S. Meetings

- 27 Personally Speaking

- 95 International Meetings

- 345 Index of Advertisers

- 346 Reader Service Card

# CMOS TECHNOLOGY

#### 102 Introduction

# **Technology Report**

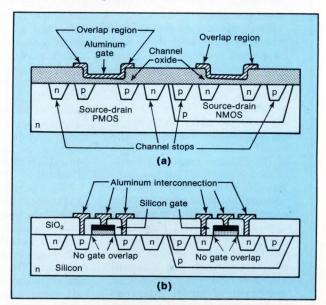

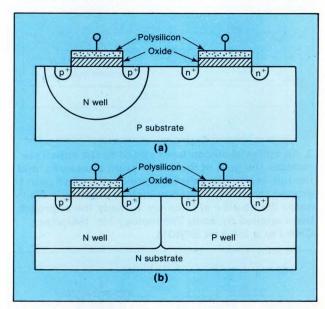

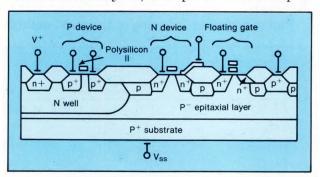

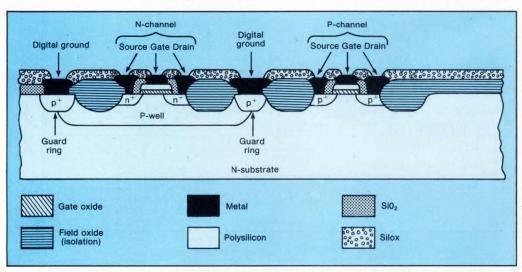

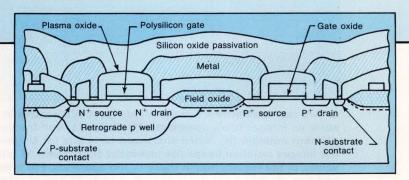

# 104 Before reaching its potential, CMOS faces some thorny problems

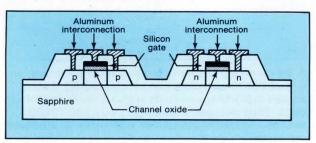

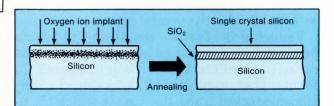

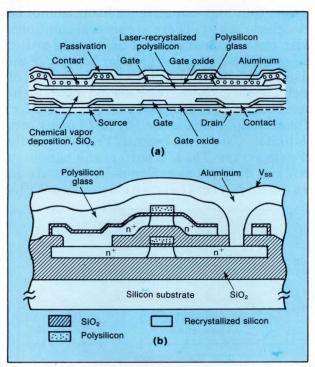

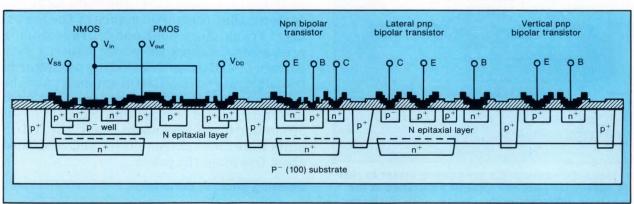

How well CMOS can strengthen its foothold depends on solutions to latch-up, device isolation, and limited interconnections.

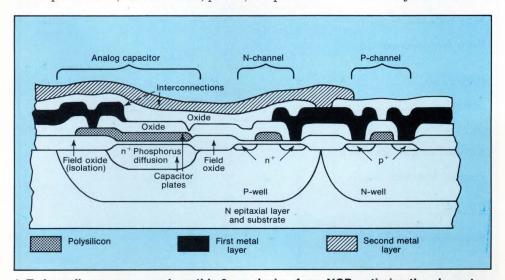

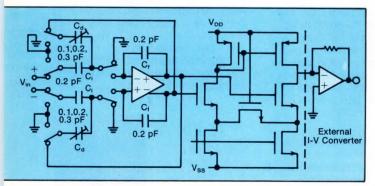

# 121 Analog CMOS marches on, but it steps to the beat of a different drummer

First because it makes excellent switches and input devices, then because it allows the easy addition of digital functions, and always because it dissipates little power, CMOS takes over the analog world.

# 135 A dozen experts see CMOS in your future

# **Design Entries**

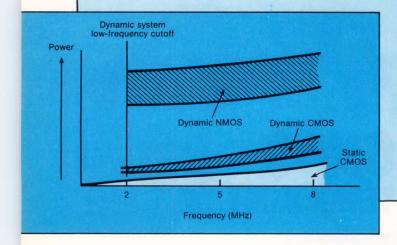

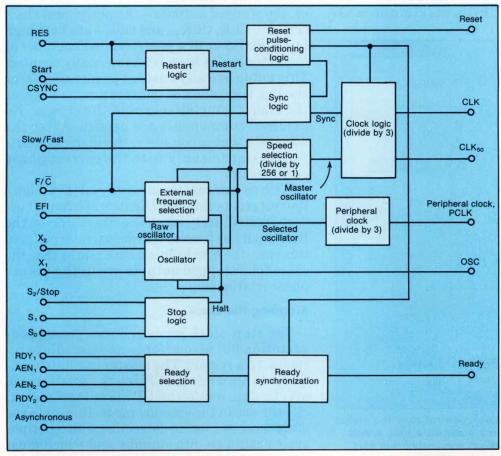

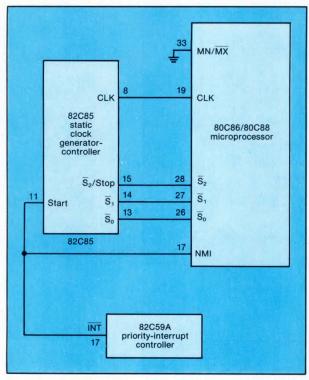

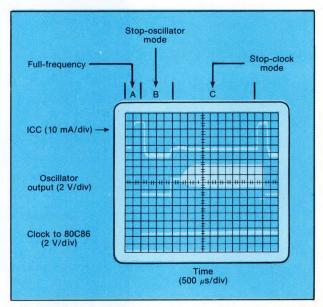

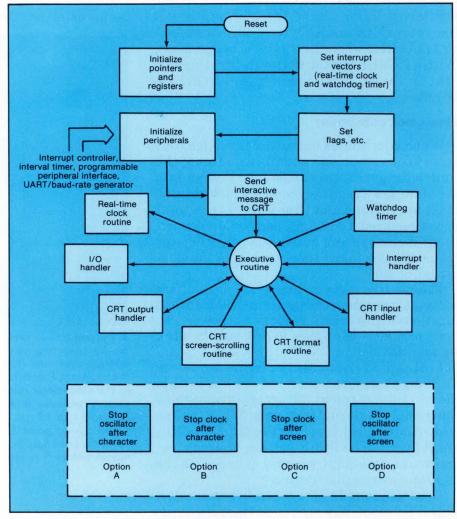

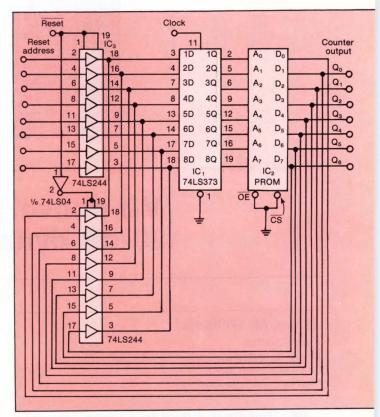

# 185 Advanced clock controller cuts power needs, size of static CMOS systems

With a one-chip controller-generator running a static CMOS system in three minimal-frequency modes, power consumption plummets.

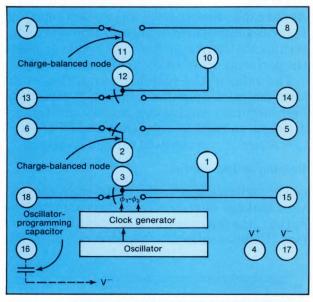

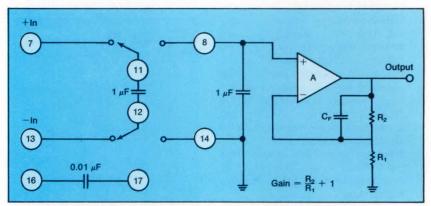

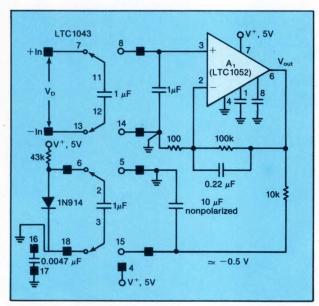

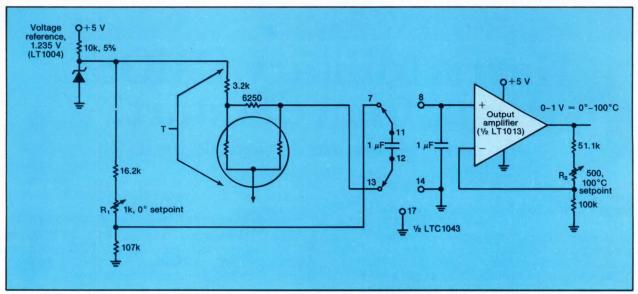

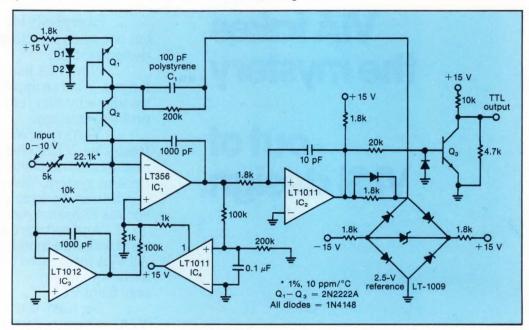

# 195 Charge-nulled CMOS switch lets op amps tackle precision analog tasks

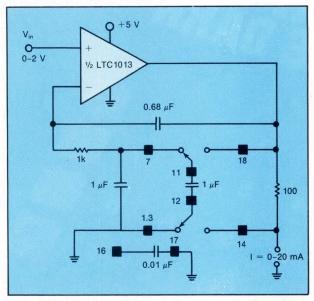

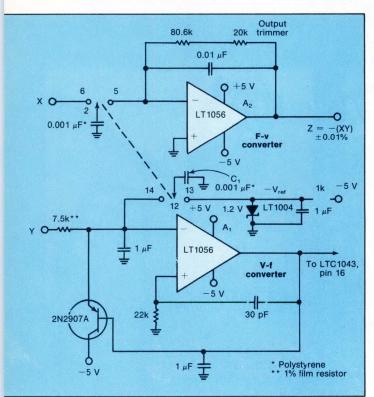

A dual DPDT switch aimed at switched-capacitor designs ushers in new instrumentation amps, analog multipliers, and v-f converters.

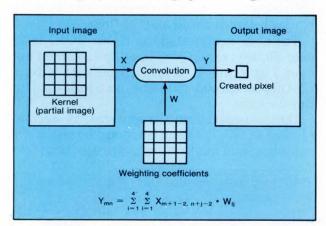

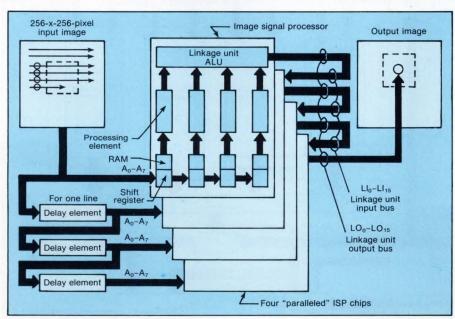

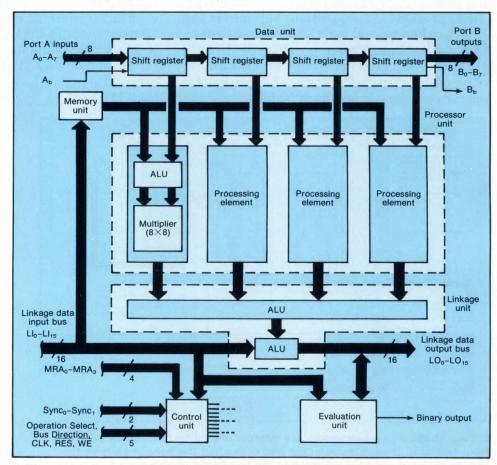

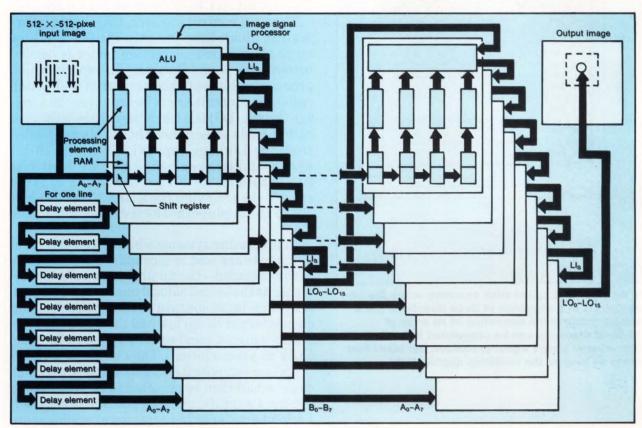

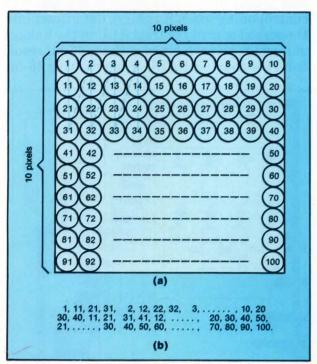

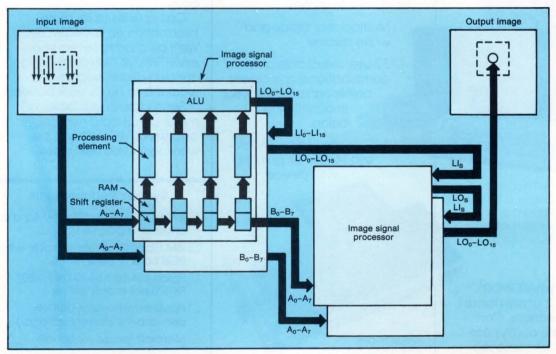

# 209 Image signal processor computes fast enough for grav-scale video

Handling millions of computations per video frame, a pipelined chip attains system speeds 1000 times those of 16-bit processors.

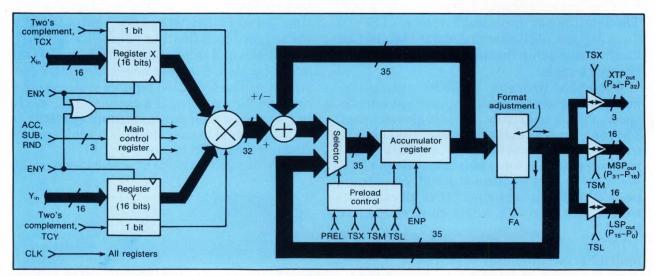

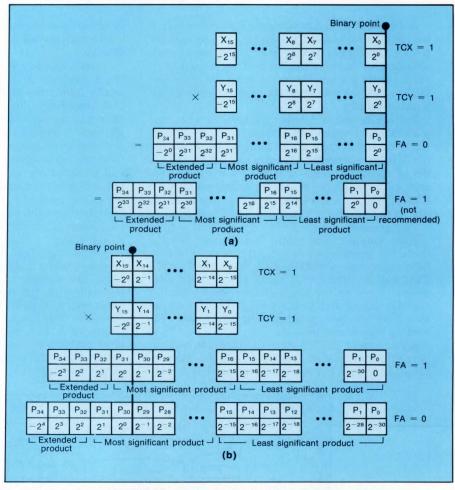

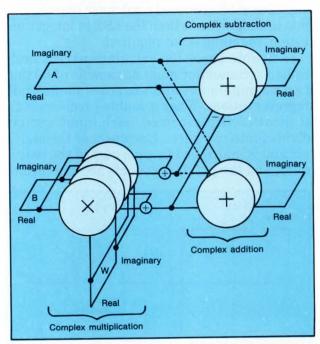

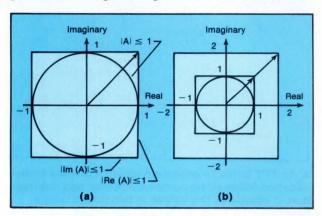

# 217 Multiplier-accumulator derives high performance from 1-μm CMOS

With a 1- $\mu$ m effective channel length, a chip fits in a pin-grid array with enough pins for nonmultiplexed outputs—an asset for many digital signal-processing tasks.

# **TECHNOLOGY NEWS**

## 31 Newspulse Newsfront

- 41 32-bit chip set follows 250 instructions, uses static NMOS circuits

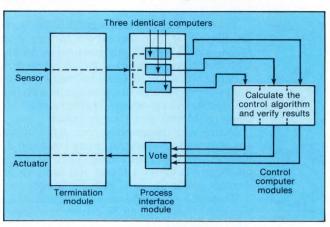

- 44 Computer's voting architecture protects industrial process control

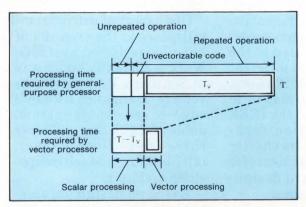

- 46 Parallel-processing mainframe welcomes Unix to a new home

- 48 Serial bus carries multiple-channel or fast data Conference Preview

- 55 GaAs, superconducting, optical ICs spearhead government conference

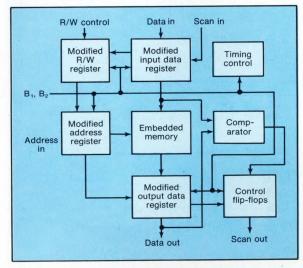

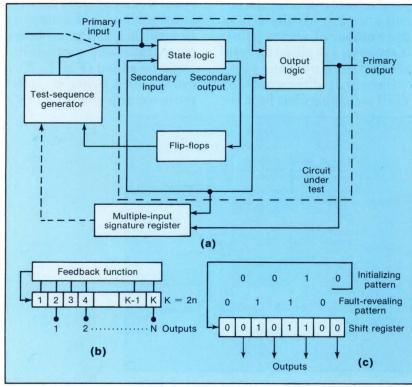

- 67 Ever more complex, VLSI chips spur testing from within and without

- 75 ICCD will heat up with gallium arsenide, AI, and supercomputers

#### **Viewpoint**

- 81 Digital scopes will emerge as the standard tools for hardware designers

- 82 Testing and servicing suffer at the hands of throwaway design methods

- 92 International Newsfront

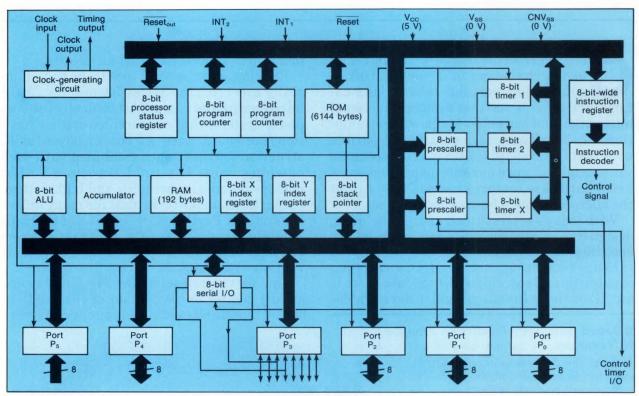

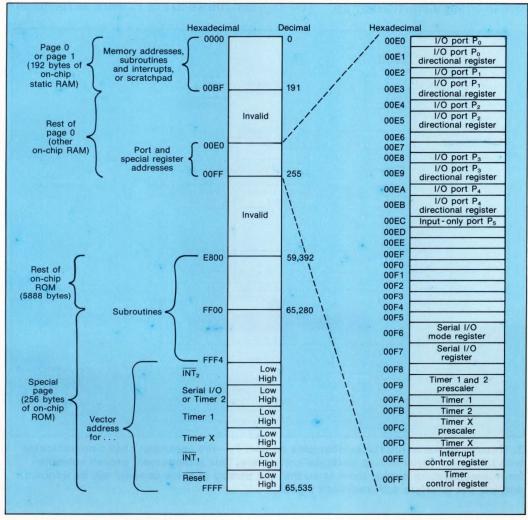

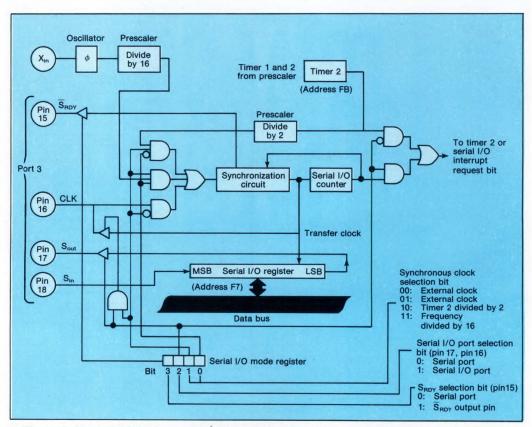

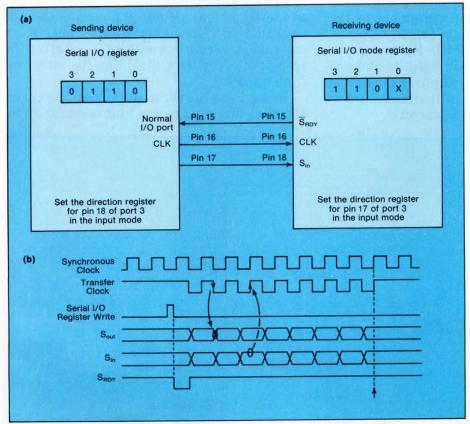

# 229 With built-in specialties, CMOS microcontrollers take aim at diverse tasks

Designers need not add extra devices to their systems. A microcontroller family may well incorporate most of the necessary circuits.

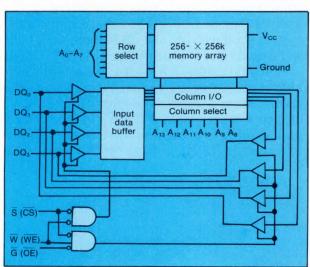

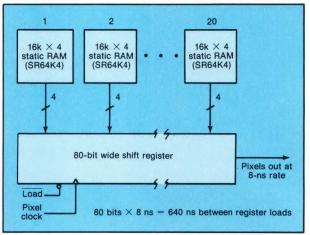

# 245 Dense static RAM speeds data access in memory-intensive systems

Because slow RAM will not do in graphics and other fast signal-processing jobs, dense static devices are making a bid to replace sluggish dynamic parts.

# **DESIGN ENTRIES**

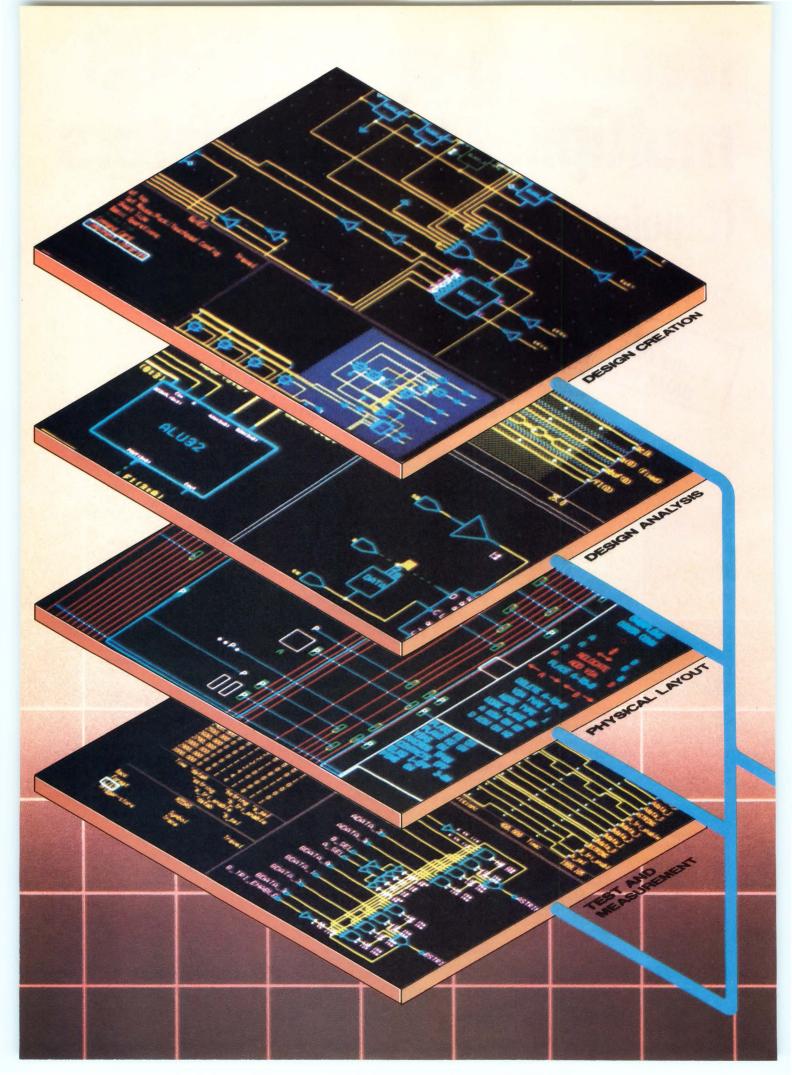

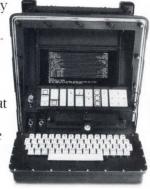

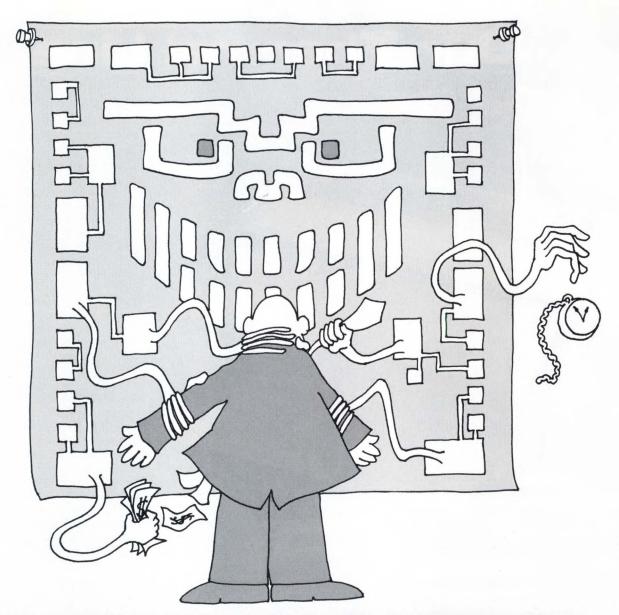

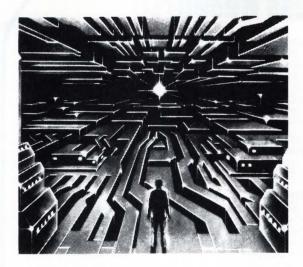

# 167 Cover: Silicon compiler lets system makers design their own VLSI chips

Despite powerful tools, designing custom VLSI circuits is slow and inefficient. A turnkey silicon compiler now streamlines the job, making the task a comparative snap.

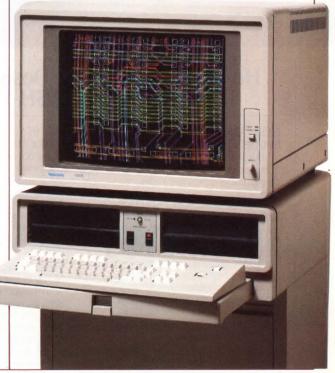

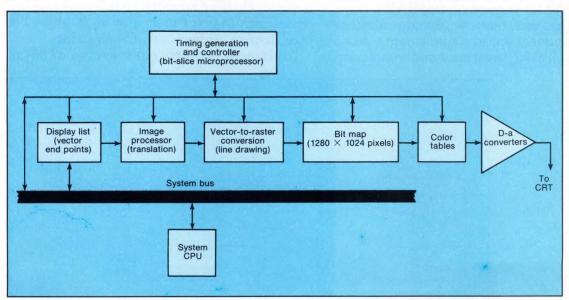

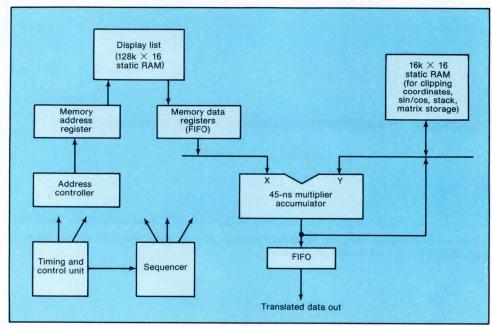

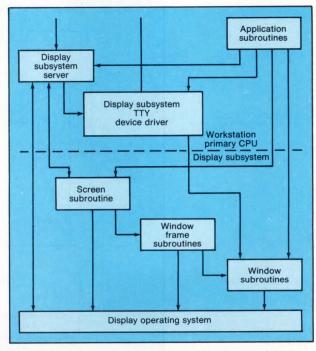

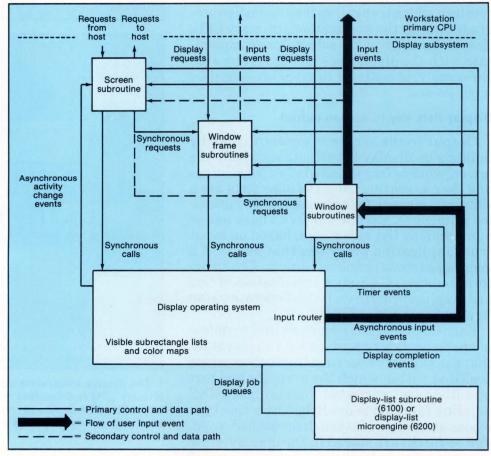

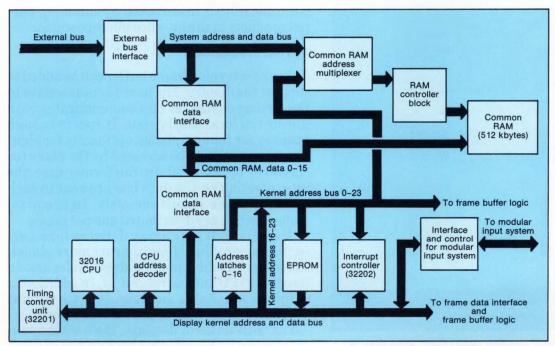

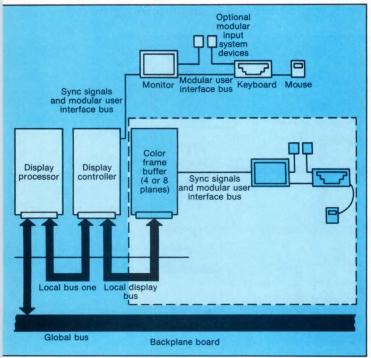

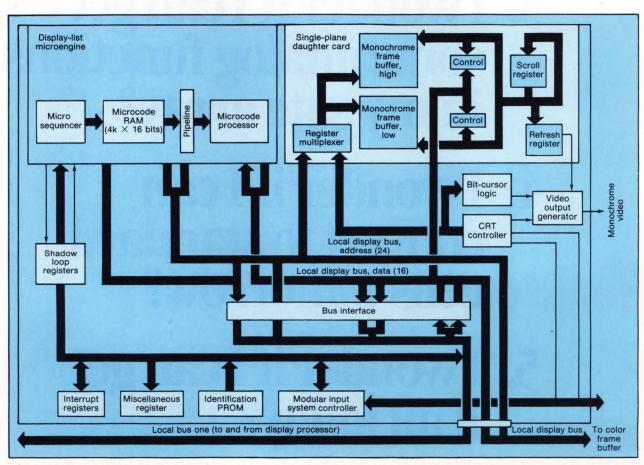

## 259 Multiple display schemes make their mark on smart graphics stations

With attention paid to command structures and windowing, a series of workstations affords speed, high-level drawings, and interactivity.

# 275 Design Solutions

#### IN THE NEXT ISSUE

Instruments Technology: an indepth examination of emulators ... An advanced view of what's coming at Wescon plus a look at products to be introduced at the conference ... Progress in oscilloscopes, logic testing, checking out mass-storage devices.

# Cover photograph by Steve Eisenberg 135,040 copies of this issue printed

ELECTRONIC DESIGN (USPS 172-080; ISSN 0013-4872) is published biweekly with one additional issue in February, May, October and December and two additional issues in August by Hayden Publishing Company, Inc., 10 Mulholland Dr., Hasbrouck Heights, N.J. 07604. Subscription rates are \$45 per year U.S. (foreign rates available upon request), James S. Mulholland Jr., President, Printed at Brown Printing Co., Waseca, Minn., Somerset Publishing Co., Somerset, N.J., and Wisconsin Cuneo Press, Milmaukee, Wis. Second-class postage paid at Hackensack, N.J. 07602 and at additional mailing offices. Copyright © 1984, Hayden Publishing Company, Inc. All rights reserved. POSTMASTER: Please send change of address to ELECTRONIC DESIGN, PO BOX 1418, Riverton, N.J. 08077.

# **NEW PRODUCTS**

#### Analog

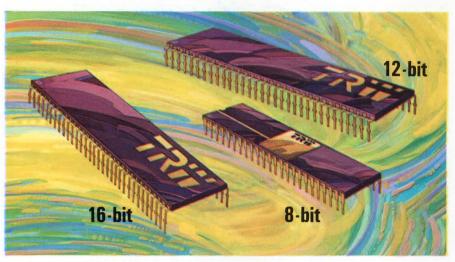

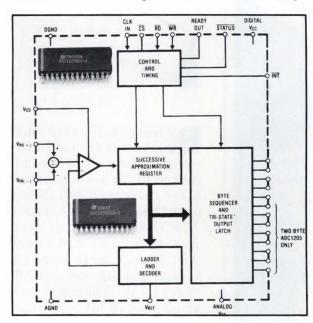

- 291 Monolithic 12-bit ADCs need only 5 V and convert in 100 μs

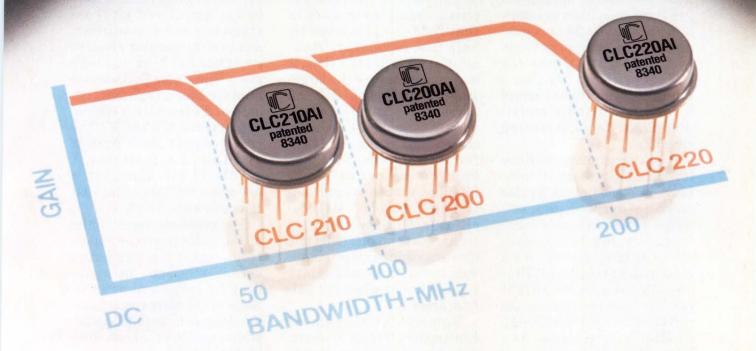

- 294 Op amp chips remain stable at a 40-MHz unitygain bandwidth

- 296 Sense-and-hold hybrid captures pulse peaks as narrow as 100 ns

#### **Computer Systems**

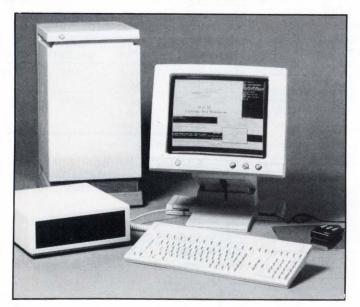

298 Compact Lisp machine fits under a desk; develops and runs Al programs

#### Instruments

**302** Frequency standard holds drift to 10<sup>-11</sup>/day, can use 2 external references

#### **Power**

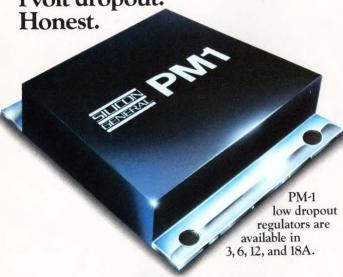

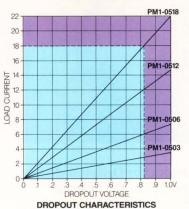

- 306 Switching power supplies occupy 6 in.<sup>3</sup> yet deliver 7.5 W

- 315 Components

- 318 Packaging & Production 3

- 327 Product News 330 Application Notes

- 325 Communications

- 331 New Literature

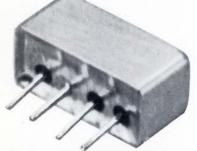

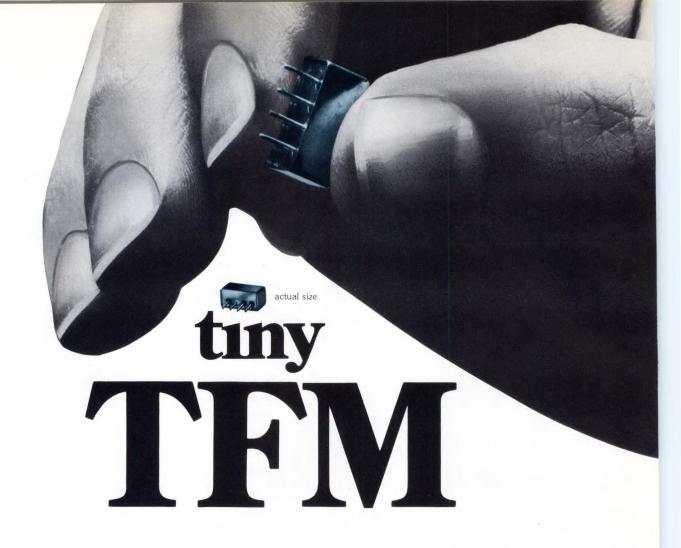

# 1 to 100 MHz only \$1895

IN STOCK...IMMEDIATE DELIVERY

- highest figure-of-merit, 129: (DC output, mV/RF power, dBm) 1000 mV typ. output, with +7 dBm input at L,R ports

- very low DC offset only 0.2 mV typ.

- hermetically sealed to MIL-STD 202

- MIL-M-28837 performance\*

- miniature size, qnly 0.2 x 0.5 x 0.25 in.

- one-year guarantee

\*Units are not QPL listed

#### MPD-1 SPECIFICATIONS

**FREQUENCY RANGE** 1-100 MHz Land R ports Output ports DC-60 MHz SCALE FACTOR 8 mV/Degree **IMPEDANCE** 50 ohms Land R ports 500 ohms port LAND R SIGNAL LEVELS +7 dBm ISOLATION, L-R 40 dB min. MAXIMUM DC OUTPUT, mV 1000 mV typ. DC OUTPUT POLARITY Negative DC OUTPUT OFFSET 0.2 mV typ.

Call or write for 64-page RF Designers Guide, or see guide in EEM, EBG, Gold Book or Microwaves Directory

finding new ways ... setting higher standards

# Mini-Circuits A Division of Scientific Components Corporation

A Division of Scientific Components Corporation World's largest manufacturer of Double Balanced Mixers P.O. Box 166, B'klyn, N.Y. 11235 (718) 934-4500

C101-3 REV. ORIG.

CIRCLE 5

# **C**ONTENTS SPOTLIGHT

# CMOS Technology 102

he impact that CMOS has had on all areas of electronics defies quantification. Besides the well-known advantage of low power consumption, it opens doors to higher density and performance. Digital CMOS circuitry, the subject of our first Technology Report (p. 104), typifies some of the stubborn problems encountered with the technology—latch-up, inadequate device isolation, limited interconnections. The analog world, too, is shifting toward CMOS, pushed by the frequent mixing of digital and analog circuitry on one chip. Naturally, analog circuits cannot sacrifice quality or speed, forcing designers to consider extremely different factors, as our second Technology Report explores (p. 121).

Following the reports, a dozen industry leaders present their views on CMOS and predict its future (p. 135). Not surprisingly, all agree that CMOS is quickly becoming the technology of the 1980s.

# Cover: Silicon compiler 167

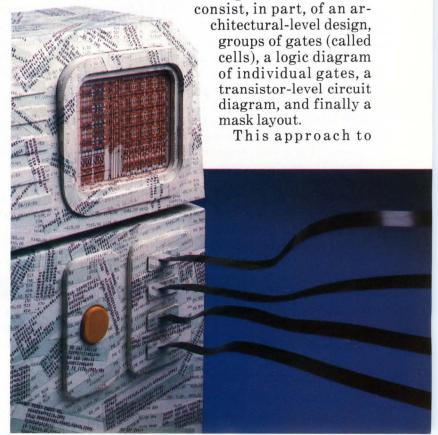

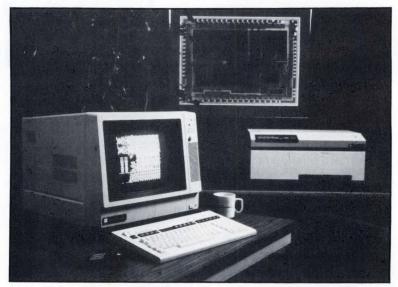

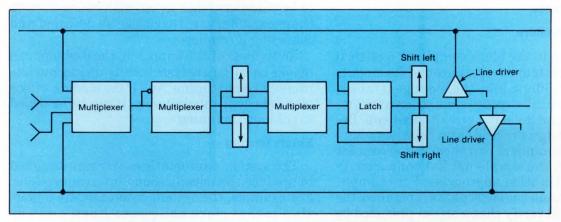

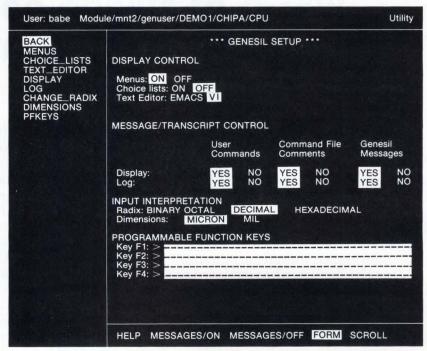

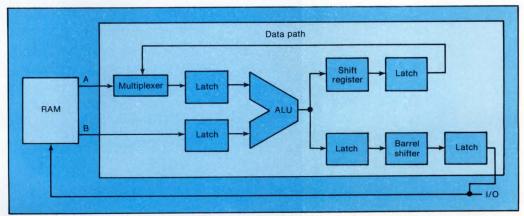

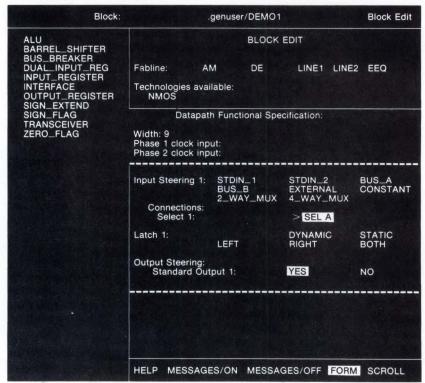

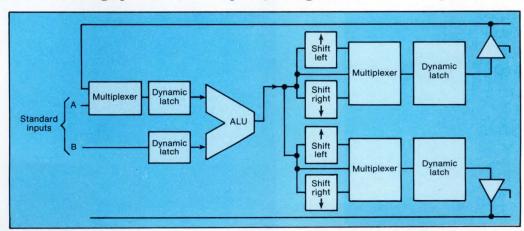

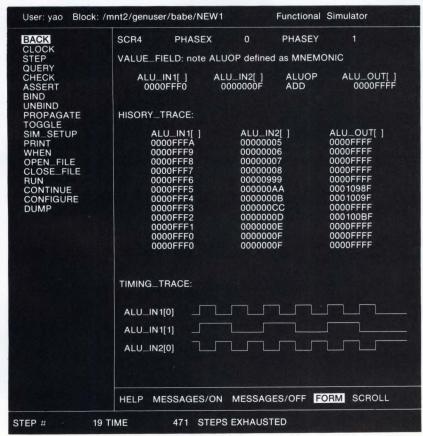

grammers of the minute details of a computer's native instructions, the silicon compiler promises not only to lift a pile of details from IC designers' shoulders but also to turn system designers into VLSI chip makers. A powerful silicon compiler is the first development tool that lets designers translate a VLSI block diagram into a chip and then test the design before committing it to silicon. Our coverage of the silicon compiler, presented here in three parts, explores the general principles behind it, the specifics of the actual system, and a detailed application.

# Preview: International Test Conference 67

t today's extremely high level of integration, device testing becomes a critical matter. The International Test Conference, to be held later this month in Philadelphia, tackles testability in general, through self-testing facilities or through sophisticated testers. Even expert systems are making an entrance, diagnosing the problems of the testers.

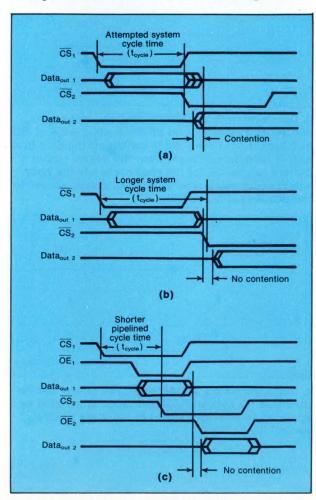

# amplifyor isolate? it does both.

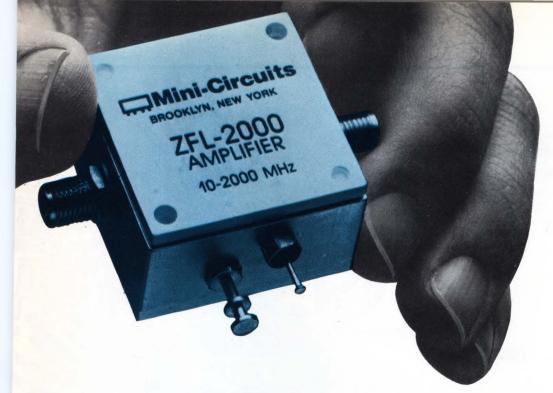

# 22 dB gain and 40 dB isolation, 10-2000 MHz...only \$179

Either way, the ZFL-2000 miniature wideband amplifier is an engineer's problem solver. Some examples of solutions offered by the ZFL-2000 are

- Boosting signal/sweep/synthesizer outputs to 50 mW.

- Achieving broadband isolation, especially when combining 2 signal generators for a two-tone intermodulation measurement.

- Increasing the dynamic range of spectrum analyzers.

- Driver for power amplifiers, such as Mini-Circuits' 1 and 2 watt ZHL series.

- Extending the frequency range of signal generators when using a frequency doubler, filter and then amplifying.

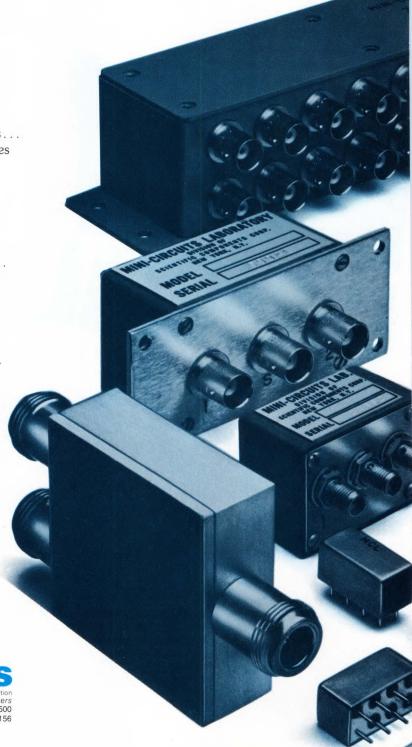

- Creating multiple output ports for one signal generator when amplifying and then adding a Mini-Circuits power splitter or divider.

These unconditionally stable wideband amplifiers are available with SMA connectors and are housed with an internal heat sink in a rugged 1.25 in. sq. by 0.75 in. high RFI shielded case.

Meets MIL-STD 202, these units operate from  $-55^{\circ}$ C to  $+100^{\circ}$ C.

One week delivery and a one-year guarantee, of course.

For complete specifications and performance curves refer to the Goldbook, EEM, EBG, or Mini-Circuits catalog

CIRCLE 4

finding new ways...

setting higher standards

# **Mini-Circuits**

A Division of Scientific Components Corporation

World's largest manufacturer of Double Balanced Mixers

P.O. Box 166, Brooklyn, New York 11235 (718) 934-4500

Domestic and International Telex 125460 International Telex 620156

#### **ZFL-2000 SPECIFICATIONS**

| FREQUENCY                          | 10-2000 MHz                         |

|------------------------------------|-------------------------------------|

| GAIN                               | 20 dB                               |

| <b>GAIN FLATNESS</b>               | $\pm 1.5 \text{ dB}$                |

| OUTPUT POWER<br>(1 dB compression) | +17 dBm                             |

| NOISE FIGURE                       | 7.0 dB                              |

| INTERCEPT POINT (3rd order)        | 25 dBm                              |

| VSWR, 50 OHMS                      | 2:1                                 |

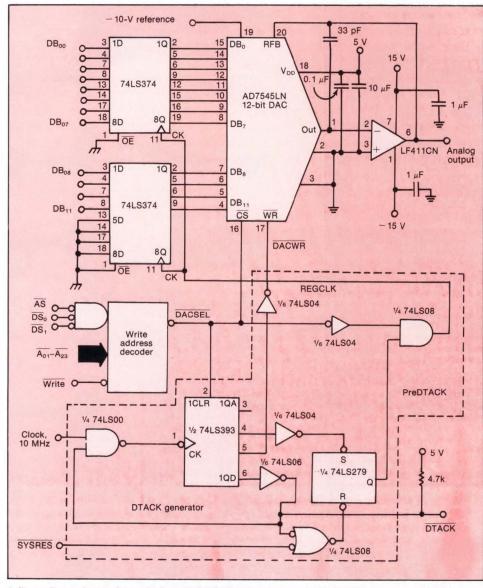

| DC POWER volt, current             | +15 V, 100 mA                       |

| HEAT SINK                          | Internal                            |

| OPERATING TEMP                     | $-55^{\circ}$ C to $+100^{\circ}$ C |

|                                    |                                     |

C98 REV. A

# Everybody talks CMOS gate arrays.

But only National goes beyond talk to bring you low power, one nanosecond gate arrays in production quantities.

You know how it is.

Everybody's *heard* about the benefits of CMOS: High density gate arrays with Schottky speeds. Low CMOS power levels with latch-up immunity and ESD protection. All in production quantities.

"Great idea" they say.

"But it can't be done."

Obviously they haven't talked to National. Because we're doing it!

Using our proven micro-CMOS process technology, we've produced the SCX-Series of high-speed/low-power dual-layer metal gate arrays. Look at the benefits: National's SCX-Series offers a full family of gate array solutions. Including both  $3 \mu m/2$  ns arrays and the first  $2 \mu m/1$  ns internal tpd CMOS gate array in

production. Ranging from 600 to 6000 gates, they all drive 50 pF loads.

And we don't stop there.

National offers a fully

integrated CAD system. With

comprehensive training and

logic simulation. Plus fault

grading for design checking

and testing. And 100% autoplace and route capabilities.

So next time the talk turns to CMOS gate arrays, remember National. We're not just talking about it. We're doing it.

For a copy of our micro-CMOS brochure, contact us at 2900 Semiconductor Drive, MS 23200, Santa Clara, California 95051.

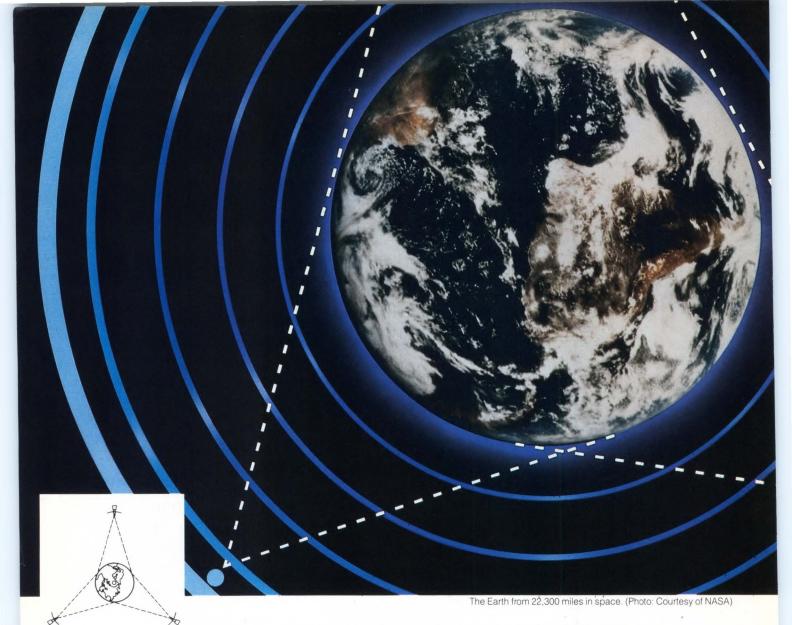

Clarke's proposed 3-satellite system.

# FINDING NEW WAYS...

In 1945, Arthur C. Clarke—a British mathematician, wireless operator and creative science fiction writer found a better way to beam communications signals around the world. He theorized that an artificial satellite, carried by a rocket to an orbit 22,300 miles above the earth's equator and traveling at 6879 mph (the speed at which the earth rotates on its axis), would appear motionless to an observer on earth. From that height, Clarke reasoned, a radio relay station could cover one-third of the earth's surface; three such satellites, placed in geosynchronous orbit around the equator could provide worldwide communications. In 20 years, advances in electronics, miniaturization and rocketry made Clarke's dream a reality and gave the world improved communications capability.

Likewise, in 1969, Mini-Circuits made its total commitment to serve the emerging communications market... by replacing expensive, custom RF signal-processing components with low-cost, catalog units with unparalleled reliability.

Our dream, like Clarke's, has come true. Over 1,000 catalog items available with such Mini-Circuits innovations as our exclusive HTRB burn-in testing, the world's only 3-year guaranteed mixers, computer-automated performance data (CAPD) to eliminate design guesswork . . . just to name a few.

Mini-Circuits' products have become the industry standard. We are actively dedicated to the pursuit of further improvements in product cost/performance, quality and reliability for more effective worldwide communications.

finding new ways...

setting higher standards

# Mini-Circuits

World's largest manufacturer of Double Balanced Mixers

P.O. Box 166, Brooklyn, New York 11235 (718) 934-4500

Domestic and International Telex 125460 International Telex 620156

# **ON REFLECTION**

# Making the most of optical disks depends on accurate retrieval

ne of our dreams is to replace all the clutter and paper on our desks and in our files with a system that easily stores the information in a compact chassis. Rather than shuffling through stacks of paper, we could pull out a page of information merely with the touch of a key and then display it in a window on a screen.

With gigabyte optical disks, we at last have the vast memory we would need to do that. For instance, one system can practically replace 800 standard filing cabinets. Another optical disk can hold 1 terabyte—at an amazing 80¢ a megabyte. Optical disks rely on a laser beam to burn holes into a tellurium alloy; each hole represents one bit. In that way, the disks can hold billions of bits of permanent data, none of which is affected by light, magnetic fields, or

Having so much memory at hand is an ideal situation for a system designer. Yet one question remains: Has the technological advance actually preceded practical use? The problem revolves around organization, not capacity. Consider how desks and files are organized: Some filing is alphabetical, some chronological, some topical; others are arranged by priority or by guess. In fact, with the fairly random nature of the typical filing system it is a miracle that we can find a piece of paper at all. Nevertheless, we seem able to reach into the right file or drawer and retrieve the correct document—if not immediately, then within one or two tries. Conventional computers can-

Perhaps the solution lies in artificial intelligence. Because human beings think through association, AI machines are programmed to "think" that way, too. The similarity stops

there, however: Human beings can think in a disorganized manner, computers do not have that facility. However, the presence of hugecapacity optical memories virtually mandates that computers be able to retrieve randomly organized information.

A good definition of goals and techniques especially in terms of artificial intelligence would go a long way toward structuring data retrieval for the coming generation of optical disks. Otherwise, those devices may end up collecting reams of paperwork—with no way of calling up the information easily. Unless we pay closer attention to ways of organizing information, we may resort to using a nice iconthe wastebasket—for all data.

Heather Dyce

Heather Bryce

Gould AMI... Innovation and Quality in Semiconductors

# The double-metal answer to sluggish gate arrays.

What are you waiting for? Move into the world of 1 to 3 ns gate delays.

Gould AMI  $3\mu$  double-metal HCMOS technology opens up applications once considered too fast for CMOS gate arrays. Now, you can have low cost and power consumption without giving up speed.

# Fast circuit design and delivery.

These double-metal arrays don't just work faster—they're designed faster. One reason is

Gould AMI's growing library of macro cells. Over 100 popular functions—predefined and pretested—allow you to avoid wasting time and money reinventing the wheel.

Also, Gould AMI's fully integrated CAD software places and routes each programmable level automatically. More than fast, it can utilize over 98% of available gates!

Gould AMI offers  $3\mu$  double-metal arrays from 1100 to 4000 gates. (Later this year, our  $2\mu$  family will provide up to 10,000 gates.) Delivery in production quantities takes just 5 to 7 weeks from prototype approval.

# Service just as fast and flexible.

We can do everything from design through fabrication—or any part of the job you wish. Gould AMI CAD software runs on Prime<sup>®</sup> and VAX™ computers. Our macro cells are available on major workstations. We can train your designers. And there's second sourcing, of course.

You're invited to find out more about the Gould AMI gate array program. Call us at 408-554-2311, or return the coupon. Because if the job is making CMOS gate arrays faster, Gould AMI is right for the job.

Prime® is a registered trademark of Prime Computer, Inc.  $VAX^{\infty}$  is a trademark of Digital Equipment Corporation.

| ☐ Complete gate array line.        | ☐ Macro cell libraries.                                                    |

|------------------------------------|----------------------------------------------------------------------------|

| ☐ Complete standard cell           | <ul><li>☐ CAD training program.</li><li>☐ Send your enlightening</li></ul> |

| line.  ☐ CAD software programs.    | case history, "Gate Arrays – The Hidden Cost Savings."                     |

| Name                               |                                                                            |

| Title                              | 7                                                                          |

| Company                            | M/S                                                                        |

| Address                            |                                                                            |

| City/State/Zip                     |                                                                            |

| ( )<br>Phone No:                   |                                                                            |

| Mail to: Gould AMI Semi            | conductors                                                                 |

| Gate Arrays Mark<br>3800 Homestead |                                                                            |

# Q. Whose Magnetic Sensors Are The Big Companies Turning To? A. Aleph International, That's Who!

The top "Fortune 500" companies like IBM, Xerox, AT&T, Toyota, and Honda, just to namedrop a few, are turning to Aleph International for innovative magnetic sensors in all sizes and shapes.

And for good reasons. Aleph has packaged a reliable magnetic technology to interface with the microprocessor world. They offer important advantages over mechanical and Hall Effect devices

Our MagneSensors are hermetically sealed for high reliability and long life. They are low in cost. They can handle a wide range of switching voltages, including low levels. They can withstand transients without surge protection. They aren't affected by heat. Polarization isn't necessary. No offset voltages are present. And no power supply is required.

necessary. No offset voltages are present. And no power supply is required.

We're set up to respond to your needs quickly. And to produce a high volume of Magne-Sensors in a short time. Built to your exacting specifications.

Call us today and find out why the big companies are turning to Aleph International for innovative MagneSensors.

# **R**EADER FEEDBACK

#### Where's the info?

looked forward to reading your July 12 cover article, "Low-Voltage FETs Slash On-Resistance to Boost Power Density" [p. 125]. In five pages the only concrete information concerns decreasing the die size and therefore the cost of manufacture. At the least the authors could have given data on one particular unit of the series. No one could design from this article, and there isn't even a reference for further information.

The article should have given capacitances, which determine driving current; input breakdown voltage; input voltage for minimum forward resistance; thermal resistance with actual numbers; and an output family from which to determine how closely the devices approach the ideal pentode curves with horizontal and vertical output lines and how sharp the transition is from vertical to horizontal.

The fact that this information is omitted makes me wonder whether it's because it isn't too good.

Name witheld

#### **Even faster**

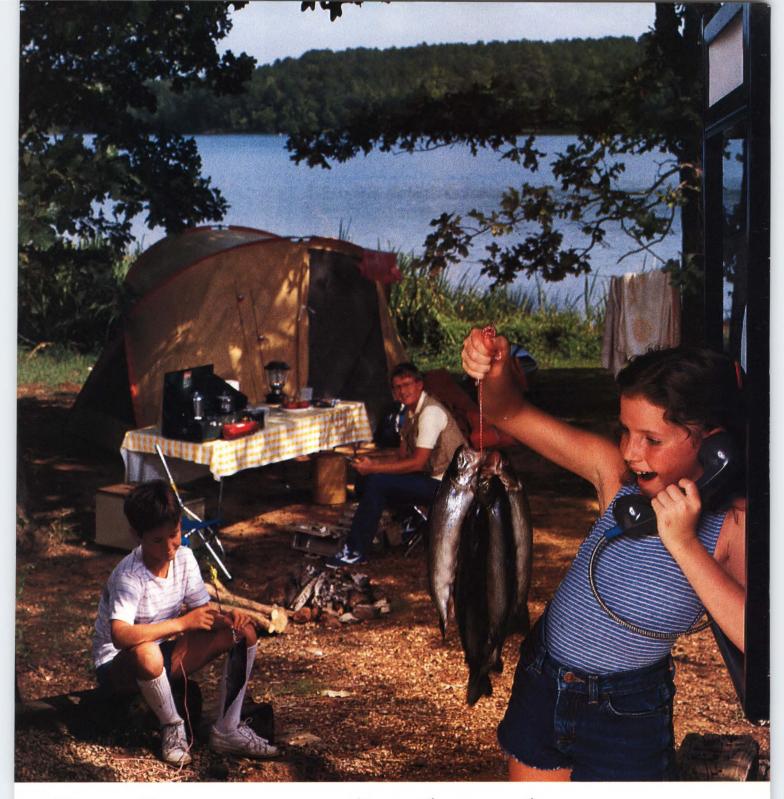

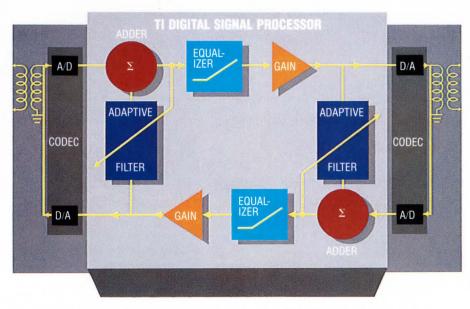

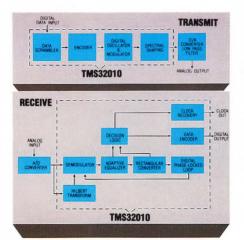

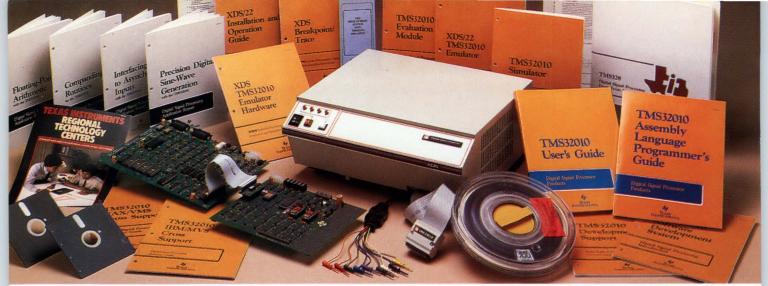

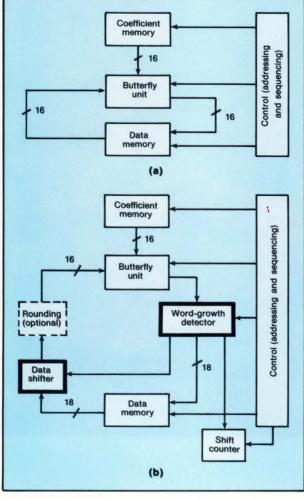

eader R. E. Pickvance is mistaken in stating that Texas Instruments' TMS 320 digital signal-processing chip requires 1.9 ms for a 64-complex-point FFT [July 12, p. 15].

Indeed, TI did list that time for a radix-2, looped 64-complex-point transform (ELECTRONIC DESIGN, Aug. 19, 1982, p. 154). But it also noted in the article that an in-line code version would take  $783 \,\mu\text{s}$ , the unacceptable penalty being that 3722 of the 4906 program memory locations are required.

However, DSPS Inc. has been offering a 580-µs 64complex-point FFT for the TMS 320 since December 1982. The key to the speed and the reasonable memory requirements (2700 locations. leaving more than twice the total memory of the competing NEC 7720 for nontime-critical control) is a superior algorithm architecture (radix 4). The program was created through automated code generation techniques.

DSPS's latest benchmarks for standard TMS 320s (with 4 kbytes of ROM) are 535 µs, 2.4 ms, and 6.2 ms for 64-, 128-, and 256-complex-point FFTs, respectively—including bit reversal. The latter two are program—memory-to-program—memory times and allow for double buffering. That is, data is collected into one buffer while the other is transformed.

The TMS 320 has a deceptively simple architecture and is capable of some relatively astonishing results.

L. Robert Morris President DSPS Inc. Ottawa, Canada

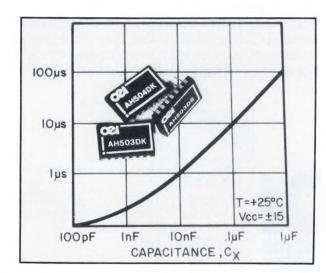

# **Analog Solutions**

# Life too unsettled?

AH103/AH104: 160nsec to 0.1% FET op amps

- ► 160nsec max to 0.1% (AH104)

- ➤ 280V/µsec min (AH104)

- Internally compensated for unity gain (AH103)

- ► 1mV max VOS, 5µV/°C max drift (CL grades)

- 30ma min out at ±10V

- ▶ \$38.60 in 100's

P.O. Box 11140, Tucson, Arizona 85734 Phone 602-624-8358, Telex 910-952-1283

See us at Wescon (Booth 2246) and Electronica (Booth 21-B41)

**CIRCLE 8**

# LONGEST LASTING LCD.

Even in heat, humidity and stress situations, this liquid crystal display stays bright and sharp longer than other LCDs, longer than other types of displays. Literally years longer. Exceeds JEDEC

Class 4 (automotive and outdoor) environmental requirements. Low power, good readability at any angle. Inquire about our long life display. LXD Inc., 24500 Highpoint Road,

Beachwood, Ohio, 44122. (216) 292-3300.

### READER FEEDBACK

#### Left out

readers to know that the directory of manufacturers you published in your June 28 Focus on Switching Power Supplies [p. 301] is incomplete. For one, it omitted our company.

Scotty Wallace

Vice President, Sales

and Marketing

Teapo Electronic Corp.

of America

Norcross, Ga.

# Add the smallest to the list

have just come across your very interesting Focus on Subminiature Switches in the Aug. 23 issue [p. 301]. Since our company was not mentioned, I feel that your readers might be interested to know that Schurter offers the smallest pushbutton switch family (alternate and momentary action) with built-in LED and mechanical indicator in the world.

Bruno H. Schurter President Schurter Inc. Petaluma, Calif.

#### Correction

he Aug. 23 New Products story on Western Digital's WD2400 chip set for tape control and formatting (p. 283) should have referred to the SASI throughout (rather than to the SCSI). Also, the present schedule calls for the chip set to be available early in 1985.

# Win Exciting Prizes!

enter Mini-Circuits'

# Design Contest

# IBM® PC Personal Computer,

dual disk-drives, printer, software (word processing, spreadsheet and planner). A complete system ... a \$4,000 VALUE!

2-4-6 hr. VHS Videocassette Recorder 3 speed, remote control, timer, electronic tuning . . . including 6 tapes . . . a \$500 VALUE!

IBM is a registered trademark of International Business Machines Corporation.

\*Value at time of press. All applicable taxes and duties are the sole responsibility of the winner.

F 93-A REV. ORIG.

# **Design Contest**

# It's Easy to Enter

Do you have a clever design idea or application involving IF/RF/microwave signal-processing components—mixers, power splitter/ combiners, attenuators, RF transformers, directional couplers, amplifiers or RF switches? Or perhaps a versatile setup for testing them or a novel approach to enhance their performance.

If you have an original idea, enter Mini-Circuits Design Contest now. Type or legibly print your submissions. Start with a brief abstract describing the key point of your idea (cost saving, improved performance, simplified testing, etc.). List RF signal processing components used. Then proceed with the detailed explanation. Make schematics and block diagrams clear; include values of circuit components. Be sure to include performance data and curves; judges' scores will be based on content, multiplicity of products involved and thoroughness.

# **Contest Rules**

- 1. Submit as many entries as you wish.

- 2. Ideas should be original and non-proprietary.†

- 3. Entries will be judged by the editorial staff of Microwave Journal and their decisions will be final. The top 25 winning entries will be published in Microwave Journal.

- 4. All entries become the property of Mini-Circuits Laboratory 8. Send your entries to: and must be received by December 31, 1984. †Winners may be asked to sign affidavit of eligibility & release.

- 5. Employees of Mini-Circuits Laboratory, Microwave Journal and their sales representatives, are not eligible.

- 6. Contest void where prohibited by law.

- 7. Make sure to include your business address and phone number. In addition, for non-U.S. entries, indicate AC power line voltage and frequency.

- Mini-Circuits' Design Contest P.O. Box 137 Brooklyn, NY 11235

# Good Luck, and Thanks.

The Mini-Circuits Design Contest, with its competitive excitement and fabulous prizes, is our way of thanking all of the designers worldwide whose staunch customer support has been responsible for our continuing growth.

## Free 64-page RF/IF Signal **Processing Components Guide**

For an up-to-date review of Mini-Circuits' IF/RF/Microwave product line, refer to EEM, EBG, Gold Book or Microwaves Directory. Or call/write our factory or any of our 45 worldwide sales offices for our 64-page RF Signal-Processing Components Guide.

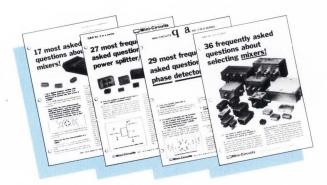

### Free fact-filled Question/Answer Series on RF Signal-Processing Components

Since Mini-Circuits is the world's largest manufacturer of mixers and RF signal-processing components, it's natural for us to receive hundreds of questions from engineers on these products. How to test them, how to make the right selection, how to optimize a circuit design ... questions with answers not found in textbooks or reference manuals.

So we've put together a series of Q & A (question/answer) booklets on most-frequently asked questions on mixers, phase detectors and power splitter/combiners. They are loaded with application-oriented tips, ready to solve a problem you may be facing. The set is free ... just call or write us or any of our 45 worldwide sales representatives.

# **EXAMPLE 1:**

send your entries to:

Mini-Circuits' Design Contest P.O. Box 137, Brooklyn, New York 11235

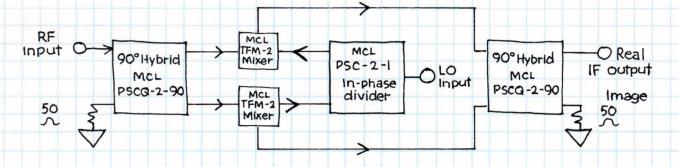

Low-cost, high performance Image-Rejection Mixer.

KEY COMPONENTS; mixers, power splitters.

Many telecommunications systems require a mixer arrangement that delivers the desired IF and sharply rejects the other image frequency.

An effective, low-cost solution makes use of Mini-Circuits' TFM-2 mixers and it's 2-way, 0° PSC-2 and 2-way, 90° PSCQ-2-90 power splitter/combiners as shown in the diagram.

The key to an efficient image-rejection, such as shown in the block diagram, is the use of double-balanced mixers with well-matched amplitude and phase characteristics and high isolation. However, poor hybrid phase characteristics, differences in the output amplitudes of the hybrids and non-symmetrical external circuits will also reduce image-rejection performance. The effects on sideband suppression caused by unequal mixer amplitude and phase shift are shown in Tables 1 and 2.

| Table 1     |               | Table 2                |                   |

|-------------|---------------|------------------------|-------------------|

| Amplitude U | nbalance<br>3 | Phase Unbalan<br>A, dB | ce                |

| Unbal, dB   | A, dB<br>35   | Phase Unbal, degree    | A, dB<br>33<br>22 |

| 0.3         | 35            | 3                      | 33                |

| 0.9         | 27            | 9                      | 22                |

| 1.5         | 22            | 15                     | 18                |

| 2           | 13            | 20                     | 15                |

| 3           | 15            | 20<br>30               | 12                |

JOSEPH CANTORE, Engineering Dept., Alphaomega Corp., II Madison Street Key Biscayne, Florida 33149

finding new ways ... setting higher standards

Mini-Circuits

A Division of Scientific Components Components

Organism

Org

World's largest manufacturer of Double Balanced Mixers

P.O. Box 166, Brooklyn, New York 11235 (718) 934-4500

Domestic and International Telex 125460 International Telex 620156

# **EXAMPLE 2:**

# send your entries to:

Mini-Circuits' Design Contest P.O. Box 137, Brooklyn, New York 11235

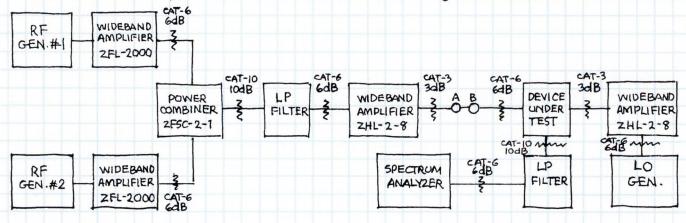

# Improving two-tone, third-order IM measurements.

KEY COMPONENTS; power splitters, attenuators, amplifiers

Two-tone, third-order intermodulation (IM) expresses the degree of non-linearity of an amplifier or mixer. This parameter is generally not included on data sheets because it is dependent upon operating frequencies, terminating impedance and input levels; it must be measured under specific design performance conditions.

Two common errors in these measurements are (1) failure to provide adequate isolation between input signal generators and proper impedance matching and (2) insufficient filtering of the two

input test signals.

Aproper test setup for measuring two-tone, third order IM distortion is shown. Note the use of two amplifiers and 6dB pads for input generator isolation and proper 50 hm matching. A practice of simply using a Tee-connector between generators developes mismatches, producing undesired harmonics which dramatically affect accuracy.

Two-tone, third-order IM distortion is only meaningful when the input levels to the

device-under-test are defined.

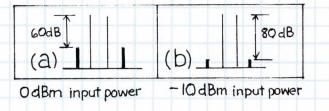

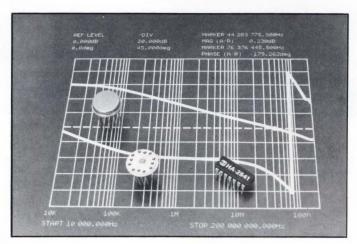

Examine the spectrum analyzer display for a ZAY-I double-balanced mixer. Notice the significant difference in two-tone, third-order component with an input level of -lodBm for each tone (b) compared with 0 dBm input level for each tone (a).

Also, the amount of two-tone, third-order must be specified relative to either the RF input or desired IF output; the desired IF output is more meaningful.

#### GENERAL NOTES

- 1) All Mini-Circuits products have model numbers shown.

- 2) OdBm input, A-B connected as shown

- -10dBm input, insert CAT-10, 10dB between A-B

JOSEPH CANTORE, Engineering Dept., Alphaomega Corp., Il Madison Street Key Biscayne, Florida 33149

finding new ways ...

setting higher standards

Mini-Circuits

A Division of Scientific Components Corporation

P.O. Box 166, Brooklyn, New York 11235 (718) 934-4500

Domestic and International Telex 125460 International Telex 620156

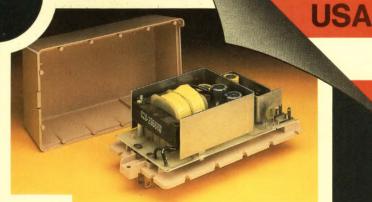

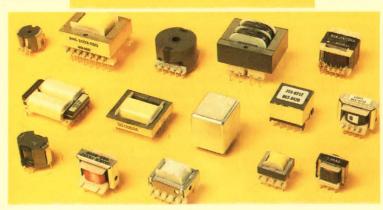

# Why James is the leader

in telecommunication transformers and power supplies.

James advanced CAD/CAM designed transformers and power supplies have become the standard for quality and performance in the telecommunications industry. Here's why James is most often specified . . .

- We're a U.S. equipment manufacturer. That means on-time deliveries without the hassle of letters-of-credit, off-shore expediting or expensive shipments.

- We know what "telephone" quality means. We build it into every product... and inspect for it in every shipment.

- Innovative engineering has kept our product lines competitively priced . . . with performance assured to rigid industry and MILgrade QC standards!

James supplies telecommunications transformers for all signal and power applications. Our power supply line includes plug-in, wall-mount and floor models... both linears and high efficiency switchers in the 2-100 watt range. They're all designed to meet FCC (Part 68) and UL requirements.

Write for complete technical specifications. You'll find our engineering consulting services for custom designs very price-competitive, too!

CIRCLE 10

TELEX/TWX 910 221 5034 JAMES EIEG CGO

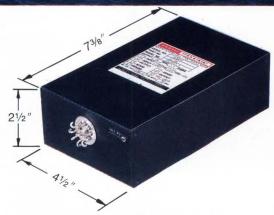

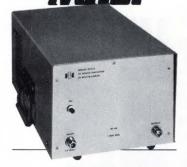

# NEW! 3-phase, 400 Hz, Mil-Spec Linear Power Supply

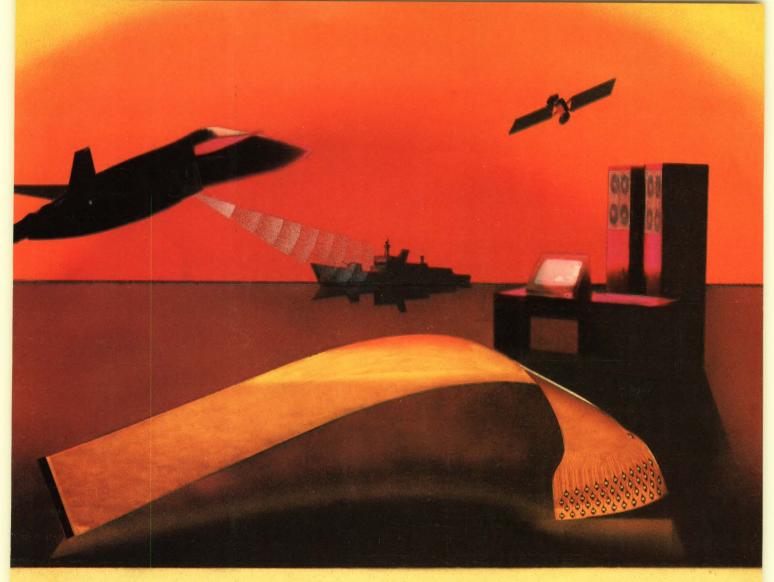

For demanding airborne applications, such as acoustic data processing, electronic surveillance and countermeasures equipment, Abbott's new WL Series of compact power supplies deliver:

MORE POWER IN LESS SPACE. WL Models provide power densities of up to 3.67 watts per cubic inch, with a maximum case height of just 2.5 or 2.75 inches, depending on output power. This permits a space savings of up to 60%, since a balanced ac power distribution system can now be maintained without resorting to three single-phase supplies or costly custom designs.

ENVIRONMENTAL PERFORMANCE. Ruggedly built WL Models are fully encapsulated and hermetically sealed to protect against salt spray, high humidity, shock, vibration and other applicable environmental conditions defined in MIL-STD-810C

**ELECTRICAL PERFORMANCE.** The low EMI of these power supplies ensures compatibility with sophisticated electronics. All units meet applicable requirements of MIL-STD-461B for emissions and susceptibility. They are also protected against input transients of up to 180 Vrms for 100 ms, in accordance with MIL-STD-704.

ABBOTT RELIABILITY. Design engineers have been specifying Abbott power supplies for 23 years...whenever reliability is imperative. The consistent performance that has made the Abbott single-phase Model W the most popular 400 Hz power supply in airborne applications is now available in our new 3-phase WL and WWL Series. Please contact Abbott Transistor Laboratories, Inc., Power Supply Division.

Eastern Office: (201) 461-4411. Southwest Office: (214)

437-0697. Western Office: (213) 936-8185.

Call or send for Specs and Full Line Catalog

- Input: 105-125 Vrms, 380-420 Hz, 3-phase "delta" std. 3-phase "Wye" input optional

Single and dual outputs, 5-28 Vdc

- Output power 48 to 420 Watts

- · Low ripple of 5 mVrms, peak-to-peak 25 mV

- High 55% efficiency

- · Load regulation: 0.1% from no-load to full-load

- Operating temperature range − 55°C to + 100°C

# **HIGH RELIABILITY:**

MTBF CALCULATED PER MIL-HDBK-217D Standard **ER Version**

| Ground benign | 164,406 hours | 883,580 hours |

|---------------|---------------|---------------|

| Air-inhabited | 25,633 hours  | 94,956 hours  |

MILITARY POWER SUPPLIES

# NATIONALANTHEM

**Technology News From National Semiconductor**

54

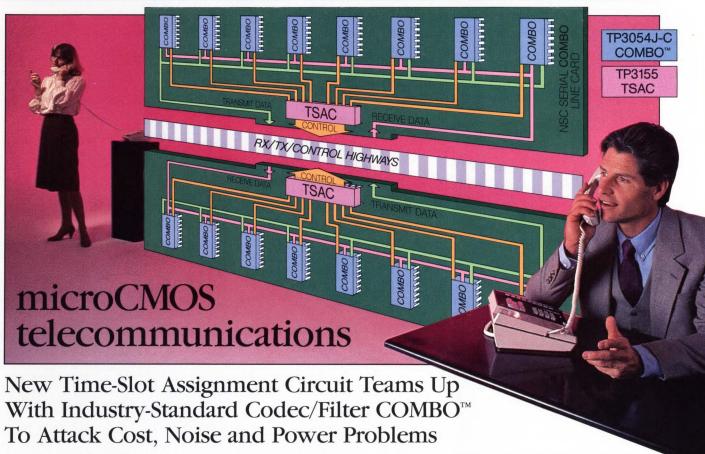

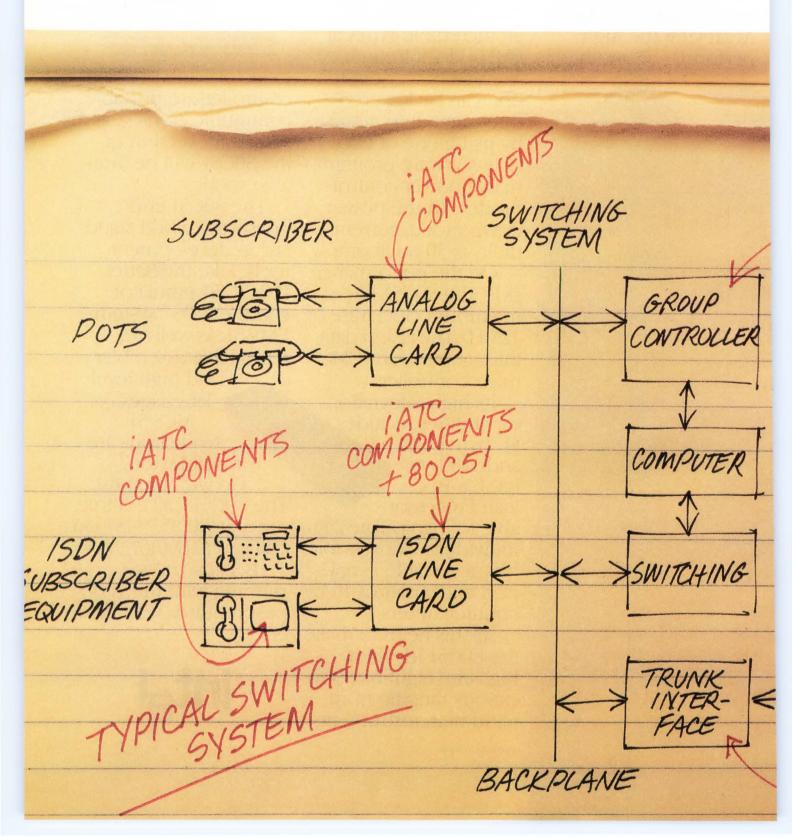

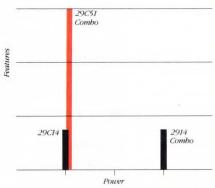

#### Per-line cost reduced

National's TP3155 TSAC takes advantage of microCMOS density to provide a low-cost, single-chip replacement for expensive, conventional discrete logic and software.

One TSAC can be shared over four COMBO lines in a bidirectional system, and eight COMBO lines in a unidirectional format. This spreads the alreadylow TSAC cost over a large number of subscriber lines.

In addition to lowering per-line costs, the TP3155 offers design-in ease and flexibility, by providing a serial control interface compatible with the popular TP3020/2910 codecs. The new circuit features a 4.096MHz clock rate, independent transmit and receive time slots, and up to 64 time slots per frame.

# Noise problems silenced by TP3054/57J-C COMBOs

Noise, the most important consideration in designing a line card, is effectively reduced by National's workhorse TP3054/57J-C COMBOs, which use microCMOS technology to deliver ex-

tremely low idle-channel noise, plus high power-supply rejection ratios and high stability.

These COMBOs perform the complete range of codec/filter functions, including those of transmit highpass/lowpass filters with prefiltering, and receive lowpass filters with post filtering. This capability further ensures low noise characteristics and maximum cost effectiveness.

#### Low power requirements

With PBX and Central-Office systems tending to provide higher and higher line capacities, both the TP3155 TSAC and TP3054/57J-C fully utilize the ultralow power supply current offered by microCMOS technology.

Specifications in the low 'milliwatt' area guarantee minimal line-card and system current drain, expanding cost benefits still further.

Lower line costs, less noise, lower power needs—these features and more make the team of National's TSAC/COMBO a very difficult act to follow.

For complete information, check box **\$7** on the back page of this Anthem.

# **Inside News**

#### CMOS

2-Micron gate array software. New display drivers handle all technologies – LED, LCD, VF.

### NS32000

The ultimate UNIX machine.

#### **New Products**

Serial communications at no extra cost. Programmable logic analysis software for Apple-DOS

Hard-disk design gets cost-effective separator/ synchronizer chips.

Advanced FM IF circuits for low-distortion stereo. 5V-Only EEPROM offers fast read access. New bipolar gate arrays replace low power

National's 15ns PALS – industry's fastest!

Tape-and-Reel. National's new industry standard.

#### Quality

Ship-to-Stock program reflects customer confidence.

Versatile New Additions

To the 'First Family'

Of CMOS

Display Drivers

National's broad-based family of popular display drivers now strengthens its leadership position by adding its newest VF and LCD drivers—the MM58241/8, MM58341/8 and the MM58538/9, MM58540/8 respectively.

#### **Unrivaled** compatibility

Each driver in this comprehensive 22-member family offers function-similar features – a simple serial data-input channel, a 31- to 35-bit shift register, latches, and buffer/drivers for direct interface to respective LED, LCD or VF displays. This compatibility provides users with true design flexibility in selecting display technology.

# VF products: direct microprocessor interface plus full features

High-voltage MM58241/8 (up to 60V) and MM58341/8 (up to 35V) VF drivers furnish a direct, simple interface from microprocessor to display. In addition, they offer on-chip pull-down resistors, direct serial data and clock interface,

on-chip brightness and blanking control, and data-out for easy cascading. Each is ideal for driving multiplexed VF displays such as  $5 \times 7$  dot-matrix character arrays.

Equally important, the new VF drivers fit a wide scope of customer applications, from sophisticated instrumentation to automotive dashboard readouts and word-processor text displays.

With industry-first metal gate CMOS and full software compatibility, National's VF display drivers become instant favorites with both hardware and software engineers.

# Unique flexibility in multiplexed 32/34-bit LCD drivers

Socket-equivalent to the HLCD0538

series, National's innovative MM58538 family provides full TTL compatibility plus alphanumeric, dot-matrix, and bar graph display capabilities.

Advanced features like these bring engineers of microprocessor-based systems the true flexibility necessary to maintain their competitive edge.

#### Traditional quality and performance

The new VF and LCD driver family members are carrying on an all-important National tradition of high-performance, first-quality drivers offered at a reasonable cost—for all popular display technologies.

Check box **\$3** on the back page of this Anthem to receive National's display driver family brochure.

# Now, 2-Micron Gate Array Software For Daisy, Mentor

# Semicustom technology on the move

National continues to set the pace in semicustom technology with its gate array workstation support package.

This advanced software permits development of National's 2-micron microCMOS ICs on such leading computer-aided engineering workstations as Daisy and Mentor.

Now, for the first time, design engineers can take advantage of National's advanced gate array design tools—plus its industry-leading 2-micron processing technology—without ever having to leave their home facility.

#### Facilitates fast, accurate design

Designers simply breadboard a circuit on the workstation screen by

using the new software package—then interface with National's mainframe to develop semicustom ICs. Circuit design time is reduced, while design accuracy and reliability sharply improve.

Fully supporting Daisy and Mentor, the software provides the complete range of semicustom development functions, including schematic capture, design verification, and auto-place-androute.

# Powerful design verification tools—graphically built in

With the new software, basic and complex logic building blocks, in addition to critical timing data, are built into the workstation and displayed graphically.

Timing parameters—including worstcase intrinsic gate delays, wiring capacitance delays, fanout, loading, etc.—let designers quickly simulate logic functions, and accurately estimate circuit performance. As a final check, actual delay calculations can be back-annotated after placement and routing is completed.

#### Complete IC design control

With National's workstation support software, users have total start-to-finish design control—control that dramatically improves designer productivity and reduces system costs.

For more information, check box **S6** in coupon on the back page of this month's Anthem.

# National's Series 32000 – The Ultimate UNIX Machine

#### The Best UNIX micro

If your system design calls for UNIX™, industry experts have called the Series 32000™ "the best for UNIX".

National's GENIX, featuring optimized Demand Paged Virtual Memory support, is available today in source form for OEM adaption. The next generation of GENIX, with Ethernet support, is in test now. National has also delivered the Series 32000 version of UNIX System V (release 2.0) to AT&T for validation.

National's Series 32000 software catalog gives OEMs an opportunity to select from a wide variety of software, including offerings from independent software vendors.

#### True 32-bit architecture with Demand Paged Virtual Memory and Floating Point support

The word "complete" just took on new meaning in the world of 32-bit performance. National's Series 32000 microprocessor family includes the only commercially available 32-bit microprocessors offering it all—Demand Paged Virtual Memory, fast Floating Point, and efficient High Level Language support.

The Series 32000 is the only microprocessor family to offer true two address architecture. A detail which is a must when it comes to efficient high level language support. The Series 32000 is the most complete family of 32-bit CPUs, slave processors, peripherals, development systems and software on the market. Second place isn't even close.

# Fast, compact compiler cuts code costs

National's CPU instruction set supports fast, highly compact C compiler code which, in turn, requires less RAM – significantly improving performance and lowering system costs. As the implementation language for UNIX, efficient C compiler support directly contributes to efficient system performance. National's C compiler fully supports all the architectural features of the Series 32000 family.

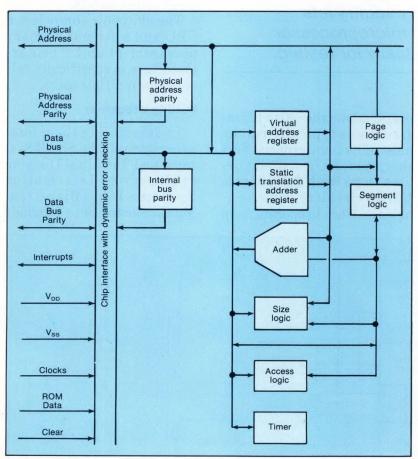

#### Powerful NS32082 MMU provides Demand Paged Virtual Memory

Thanks to National's advanced Memory Management Unit (MMU), the NS32082, Series 32000 micros are the only  $\mu$ Ps in use today offering Demand Paged Virtual Memory.

This industry first not only brings you fast on-chip address translation, but full UNIX operating system support – making the Series 32000 the perfect choice for UNIX design environments.

# Floating Point Unit heightens performance

The Floating Point Unit (FPU), the NS32081, allows operating speed up to 100 times faster than software emulation only, is easily designed into any 32- or 16-bit system.

FPU instructions can be used with any addressing mode, any operand length – and use any general purpose register. In addition, memory-to-memory operations are performed automatically.

#### **Total Compatibility**

Series 32000 CPUs offer total compatibility across the entire line, making it possible to develop a variety of systems with all the benefits of 32-bit software performance.

The same software can be incorporated in all systems within the family – a unique and all-important benefit for programmers and system designers.

# Full 32-bit architecture – a systems solution approach

An elegant 32-bit architecture is the cornerstone of the Series 32000, and is implemented in all Series 32000 CPUs. This is 32-bit architecture from the top down.

Collectively, the features of the innovative Series 32000 – fast, space-saving compiler code, hardware floating point support, the only Demand Paged Virtual Memory offered in a microprocessor, total software compatibility, and immediate availability – assure you the speed, flexibility and cost-efficient performance you need for your system, particularly if your work centers around UNIX.

For more information on Series 32000, check box **R7** in this Anthem's coupon.

# National's 15ns PAL Devices

Industry's fastest offer programmability at advanced Schottky speeds

With the introduction of the industry's fastest PAL® devices, National now offers design engineers an economical,

high-performance replacement for costly Schottky logic.

The set of four high-density chips—the PAL16L8B with active low output, and the PAL16R8B, PAL16R6B and PAL16R4B with registered outputs—are manufactured with National's advanced OXISS™ bipolar process. This process produces logic devices with ultra-fast 15ns maximum access time.

#### Multiple, customized applications

Full programmability at advanced Schottky speeds gives systems engineers the design flexibility necessary for a broad range of customized logic applications without sacrificing performance. These include address coding, multiplexing, microprogrammed control store, arbitration, high-speed random gating, and many more.

#### Lower system costs

Complete integration and spacesaving 20-pin ceramic or plastic dual-inline packaging permit significant chipcount reduction and a corresponding cut in system cost.

Additionally, the new logic devices feature TRI-STATE™ outputs (which can be acted upon by input variables), and typical power dissipation of just 600mw.

No need for additional power combined with programmable design and the fastest access time available, make National's new 15ns PAL devices the cost-effective choice over any of the advanced Schottky logic families.

For more information, check box **R9** on the back page of this Anthem.

# PLAN Software Now Available For Apple-DOS

# Create disk files for multiple hardware options

PLAN™ (Programmable Logic Analysis by National) software gives systems designers using programmable logic devices a set of powerful interactive design and development tools.

Available for CP/M®-80, and MS®-DOS operating systems, PLAN software is now also available for Apple®-DOS.

#### Automatic device selection

Three PLAN programs—PLUS, SERV, and PROG—permit the creation and editing of disk files to provide a broad scope of hardware solutions.

PLUS, a Boolean equation entry/ editing program, features algorithmic programmable device selection that includes pin-out assignment. The program automatically chooses the most efficient device—the one with the fewest fuses and registers.

With PLUS, systems designers can quickly find the most cost-effective hardware solutions. All error and timewaste associated with determining hardware requirements are eliminated.

#### Flexible design-in

SERV offers optional device selection and pin-out editing as well as a documentation utility. In the edit mode, the SERV program allows editing of the pin-out assignment within the limits of the given equations and the selected device. In the documentation mode, SERV permits users to output equations, pin-out diagrams and fuse maps.

Taking the equation file created by PLUS and altered by SERV, the PROG routine generates the formatted programming data for the device. The program directs the formatted data, including optional user-defined test vectors, to a data file disk, system printer port, or CRT.

### **Broad logic applications**

Designed expressly for 64K microcomputers, PLAN software has widerange applications wherever logic is used—especially in computer processing, control systems and copiers. And with the new Apple-DOS version of PLAN software, even more systems engineers can take advantage of National's comprehensive logic design software.

For more information on PLAN software, check box **S4** on the back page of this Anthem.

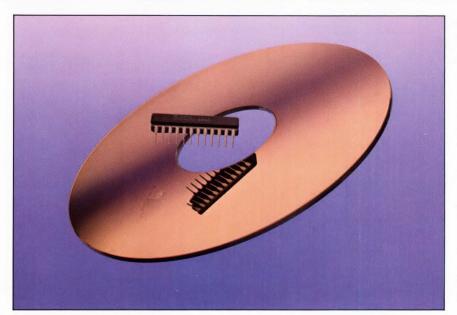

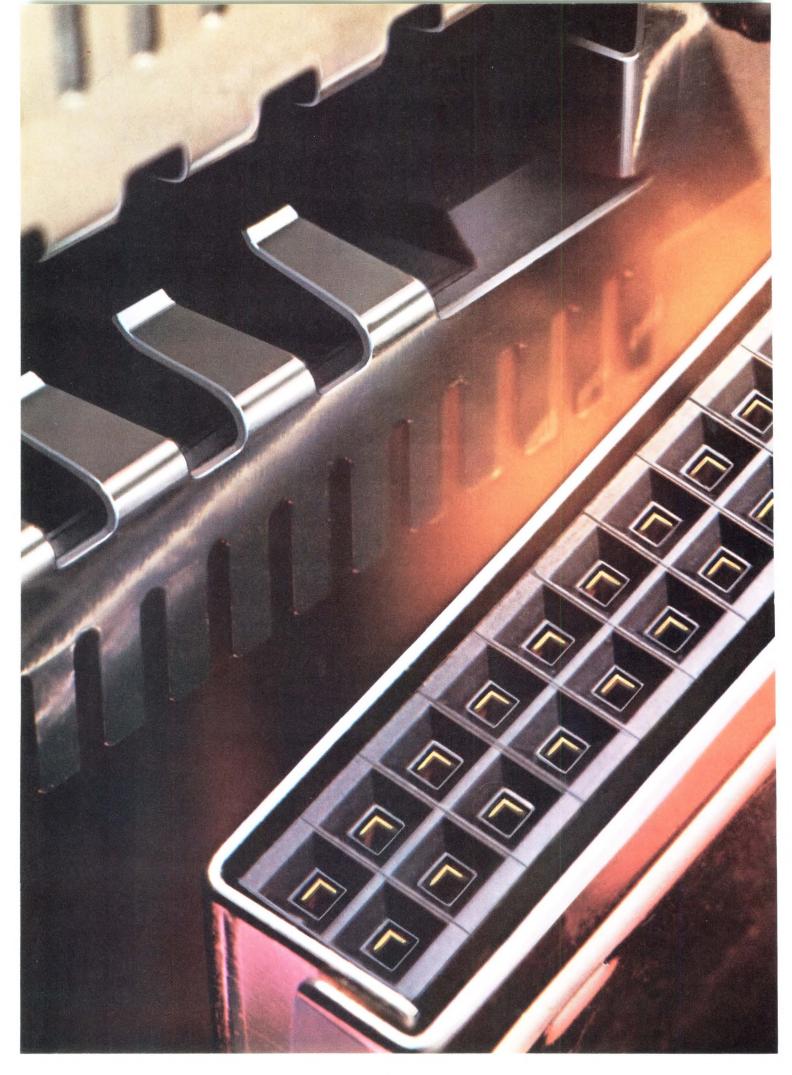

# The DP8460/8450 Data Separator/ Synchronizer ICs: Low-Cost Solutions to Disk Controller Design

With the introduction of the DP8460/8450 data separator/synchronizer chips, National continues its tradition of providing the disk industry with innovative, cost-effective design solutions.

The advanced LSI/VLSI circuits are user-programmable, making them design-appropriate for hard disks and high-density floppies that employ a host of codes and data rates.

#### No more external potentiometers

Performing the read-data synchronization PLL function, the DP8460 also features on-chip decoding circuitry for separating NRZ data and clock from MFM encoded data.

Additionally, the on-chip design frees board space for additional disk data path electronics.

Equally important, the DP8460 Data Separator offers an improved error rate by reducing window error and simplifying production testing with fixed external Rs and Cs.

#### DP8450 with synchronization only

Like the DP8460, the DP8450 Data Synchronizer chip performs basic PLL/ synchronization—but produces only synchronized data and VCO Clock waveforms derived from the incoming encoded bit stream.

With a small pin-count of 20 (the DP8460 has 24), the DP8450 is quite cost effective. The high performance and high reliability characteristics, of course, are the same for both devices.

Applicable to workstations, communications networks and computers of all sizes, National's industry-first LSI/VLSI separator/synchronizer chips offer the disk controller designer an unrivaled pair of cost-lowering, space-saving design tools.

For additional information on these bigh-economy separator/synchronizer circuits, check box **\$5** on the back page of this Anthem.

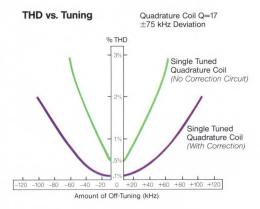

# Advanced FM IF System With Low-Distortion, Single-Tuned Quadrature Coil

#### LM1865/1965

Market pressure for improved FM performance has paralleled the trend toward electronic tuning in car and home stereo systems.

National's new generation of FM intermediate frequency (IF) circuits, the LM1865/1965, gives radio/stereo

designers the tools to ensure high performance while substantially reducing system cost.

# Multi-feature ICs for quality receivers

The LM1865/1965 system contains all active circuitry—from RF tuner output to stereo decoder input. The LM1865 provides sophisticated stop-detection circuitry for electronic tuning, while mechanical tuning is served by the deviation and signal-level mute function in the LM1965 version.

A new-design quadrature detector in both versions compensates for non-linearity, allowing high performance with a single-tuned coil. This compensation eliminates production adjustments of double-tuned coils, and guarantees low distortion.

# First to incorporate ultrasonic noise detection

The LM1865/1965 is the first integrated-circuit implementation of ultrasonic noise detection for determining valid stop (or mute) conditions.

This feature, in conjunction with signal-strength detection and automatic fine tuning, means that a receiver will not stop on a noisy station, or between two strong adjacent signals.

Additionally, the system is the first FM IF to provide a dual-threshold, automatic gain control (AGC). The AGC automatically detects the presence or absence of strong adjacent signals—and selects a high or low AGC threshold, allowing the best possible reception in all conditions.

These versatile FM IF circuits are appropriate in a broad range of design applications—from car, home and TV stereo receivers to satellite sound systems.

For more information, check box **T1** in this Anthem's coupon.

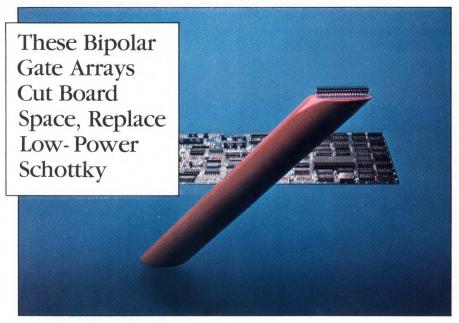

#### Available now

National's newest additions to its bipolar gate array family—the MCA500ALS and MCA1300ALS—provide design engineers with two more cost-cutting tools for custom LSI and VLSI circuit development.

Available now, the new macrocell arrays replace hard-to-find low-power Schottky while significantly reducing board space. And smaller boards mean smaller, less costly systems.

#### High performance, low power

Both MCA500ALS and MCA1300ALS are fabricated with National's advanced OXISS™ process. They internally employ emitter-coupled logic macrocell circuit technology and are TTL compatible to the outside world. Typical gate delay is 2.5 ns and power dissipation is approximately 1 watt per package.

#### Simple design-in

Producing LSI and VLSI designs with the new array devices is easy. Designers simply select the appropriate macrofunctions from the library, then define how to interconnect these functions to realize their design. Samples are delivered six weeks after the design has been completed. National also offers a design service converting circuit diagrams into fully functioning parts (turnkey design).

The MCA1300ALS uses the same macrocell concept as the MCA500ALS

array. Each macrocell contains 54 transistors and ample resistors to create the necessary logic functions. The MCA500ALS has 77 macrocells equivalent to 533 gates. The MCA1300ALS offers 140 macrocells equalling 1280 gates.

National's macro library presently contains more than 80 logic functions. Designers can create these arrays on a workstation, or by accessing National's mainframe through user terminals.

# Low power consumption, high reliability

Replacing low-power Schottky components with bipolar gate arrays reduces power consumption, allowing a smaller power supply, smaller system size and lower system cost.

Gate arrays pack many components into one piece of silicon, allowing systems with fewer soldering pins and less connectors—substantially increasing system reliability.

### Many applications

National's new MCA500ALS and MCA1300ALS have broad-range applications in minicomputers, instrumentation, test and control equipment, and telecommunications. Wherever design engineers need a cost-reducing, high-performance replacement for low-power Schottky, National's new bipolar gate arrays are ready to fit the bill.

For additional information, check box **\$8** on the back page of this Anthem.

# National's NMC9817 EEPROM Reacts Fast For Home Alarm Systems

National's high-performance NMC9817 complements its full line of EEPROMs. Fast read-access time of 200 ns and fast write time of 10 ms maximum make these 16k EEPROMs compatible with high-performance microprocessor applications, such as home security/intrusion and fire alarm systems.

# Dedicated microprocessor operation eliminated

Complete self-timing and AUTO ERASE before WRITE allows an efficient RAM-like write cycle. This frees the microprocessor to tend to other I/Os. The READY/BUSY signal on pin 1 notifies the microprocessor when the programming cycle is complete. During the 10-ms ERASE/WRITE operation, the CPU is freed.

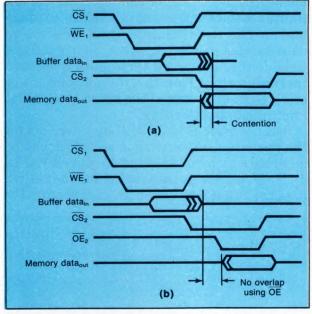

#### **Bus contention eliminated**

Two-line control architecture eliminates bus contention in your system environment.

#### Parts count reduced

On-chip V<sub>pp</sub> generation during ERASE/WRITE allows 5V-only operation in all modes, while on-board addresses and on-board latches completely eliminate the requirement for external circuitry.

#### Easier application design

The NMC9817 offers ease-of-design. It's ideal for storage of user-defined functions, calibration constants, configuration parameters, and accumulated totals.

For more information, check box **P7** on the coupon shown on the last page.

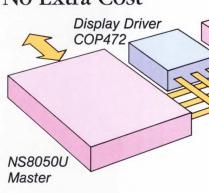

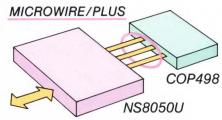

National's New NS8050U Microcontroller—Now Serial Communication at No Extra Cost

National's new NS8050U microcontroller offers multiprocessing and distributed processing capabilities via MICROWIRE/PLUS™ serial communications.

MICROWIRE/PLUS is an advanced three-wire serial communications protocol that makes it easy to communicate between two or more CPUs and to such MICROWIRE™ peripherals as A/Ds, EEROMs, display drivers, frequency generators and more.

#### Saves I/O lines

With MICROWIRE/PLUS, the lines needed by typical eight-bit controllers for data exchange with other processors and peripherals, are reduced from eight to three. This frees up I/O lines so designers can add more features and functions to their systems.

Serial communications reduces necessary pc board space, and markedly lowers system cost. Nicest of all, the NS8050U costs no more than a standard 8050.

#### Straightforward design-in

Design-in is simple. The 8050U utilizes the familiar 8048 instruction set, plus two new instructions (XCHM and XCHS) required for serial communications.

Code generation and device emulation are fast and easy using National's MOLE™ development system. And, after

Slave St. T. T. MICROWIRE/PLUS As el

NS8050U

CMOS Performance at NMOS Prices

By turning off the CPU at noncritical

times, power can be reduced (400mW,+4mW)

with no loss of memory.

developing the appropriate code, designers can use the NS8040U (ROMless version) controller to substantiate their design.

# Rich feature mix allows multiple uses

Features like 256 x 8 RAM, programmable master/slave functions, and piggy-back emulation allow the new controller a diverse range of applications in such fields as automotive, telecommunications, home security systems, and more.

MICROWIRE/PLUS

Serial communication between two CPUs or multiple National MICROWIRE peripherals.

For any applications where eight-bit microcomputer systems require several peripherals—or where design engineers wish to upgrade an 8050-based system at no extra cost—the I/O-efficient 8050U microcontroller outshines the field.

Check box **S9** on the back page of this Anthem for complete information.

National Sets Standard For Surface-Mount Tape-and-Reel

As electronics manufacturers automate production lines and adopt surface-mount technology to lower manufacturing costs, a better way is needed to handle the high volume of chips used in surface-mount assembly.

National's new Surface-Mount Tapeand-Reel offers the perfect componenthandling complement to these advanced manufacturing operations.

#### Less handling, more savings

With Tape-and-Reel, the assembly process is streamlined. Surface-mount components are held, during shipment and machine loading, in cavities of conductive plastic tape. Pick-and-place equipment automatically removes the components in sequence, placing them on the pc board quickly and accurately.

Because a Tape-and-Reel package holds 10 to 25 times as many components as a rail, the result is simplified device handling and sharply reduced labor costs

#### Packaging technology of the future

Made from conductive PVC material, the tape resists static charge buildup, and each Tape-and-Reel carries a barcode label for automated, error-free inventory management.

National's Tape-and-Reel is compatible with all surface-mount devices. These include small-outline transistors, small-outline ICs, plastic chip carrier ICs, and (coming soon) ceramic leadless chip carriers.

In addition, Tape-and-Reel specifications fully meet proposed EIA standard RS-481 (Taping of Surface-Mounted Components for Automatic Placing) to guarantee compatibility with all surface-mount pick-and-place systems in use today.

For more information on the industry's leading Tape-and-Reel packaging, check box **T2** in this Anthem's coupon.

Quality/Reliability is a matter of policy

# National's Ship-to-Stock Program Reflects Customer Confidence