CCCIONNAL State of First Quarter 2009 SOLUTIONS FOR A PROGRAMMABLE WORLD

> FPGAs Command Center Stage in Next-Gen Wired Networks

#### INSIDE

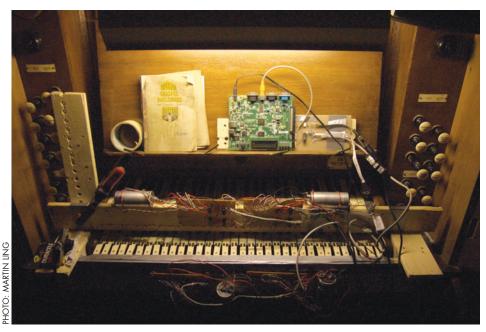

Dorkbot uses Xilinx Spartan-3E Starter Kit to Make 19th-Century Pipe Organ Rock!

Satellite-Based Computing **Flies Flexible Virtex Platform**

Tools and Techniques to Tame FPGA Power Budgets

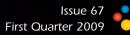

### Xilinx<sup>®</sup> Spartan<sup>®</sup>-3A **Evaluation Kit**

The Xilinx® Spartan®-3A Evaluation Kit provides an easy-to-use, low-cost platform for experimenting and prototyping applications based on the Xilinx Spartan-3A FPGA family. Designed as an entry-level kit, first-time FPGA designers will find the board's functionality to be straightforward and practical, while advanced users will appreciate the board's unique features.

Get Behind the Wheel of the Xilinx Spartan-3A Evaluation Kit and take a quick video tour to see the kit in action (Run time: 7 minutes).

#### **Ordering Information**

Part Number AES-SP3A-EVAL400-G Hardware

Resale Xilinx Spartan-3A Evaluation Kit \$39.00\* USD

Limit 5 per customer

Take the quick video tour or purchase this kit at: www.em.avnet.com/spartan3a-evl

#### **Target Applications**

- » General FPGA prototyping

- >> MicroBlaze<sup>™</sup> systems

- Configuration development

- >> USB-powered controller

- >> Cypress<sup>®</sup> PSoC<sup>®</sup> evaluation

#### **Key Features**

- >> Xilinx XC3S400A-4FTG256C Spartan-3A FPGA

- >> Four LEDs

- >> Four CapSense switches

- >> I<sup>2</sup>C temperature sensor

- >> Two 6-pin expansion headers

- >> 20 x 2, 0.1-inch user I/O header

- >> 32 Mb Spansion<sup>®</sup> MirrorBit<sup>®</sup> NOR GL Parallel Flash

- >> 128 Mb Spansion MirrorBit SPI FL Serial Flash

- >> USB-UART bridge

- >> I<sup>2</sup>C port

- » SPI and BPI configuration

- >> Xilinx JTAG interface

- » FPGA configuration via PSoC<sup>®</sup>

#### **Kit Includes**

- » Xilinx Spartan-3A evaluation board

- >> ISE<sup>®</sup> WebPACK<sup>™</sup> 10.1 DVD

- >> USB cable

- » Windows<sup>®</sup> programming application

- » Cypress MiniProg Programming Unit

- >> Downloadable documentation and reference designs

Accelerating Your Success<sup>™</sup>

1.800.332.8638 www.em.avnet.com

Copyright@ 2008, Avnet, Inc. All rights reserved. AVNET and the AV logo are registered trademarks of Avnet, Inc. All other brands are the property of their respective owners Prices and kit configurations shown are subject to change

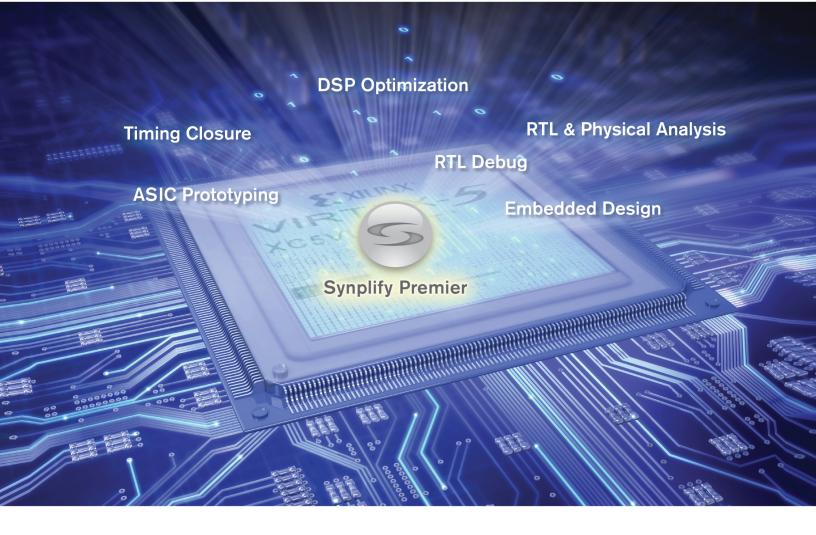

### IS YOUR CURRENT FPGA DESIGN SOLUTION HOLDING YOU BACK?

FPGA Design Ever feel tied down because your tools didn't support the FPGAs you needed? Ever spend your weekend learning yet another design tool? Maybe it's time you switch to a truly vendor independent FPGA design flow. One that enables you to create the best designs in any FPGA. Mentor's full-featured solution combines design creation, verification, and synthesis into a vendor-neutral, front-to-back FPGA design environment. Only Mentor can offer a comprehensive flow that improves productivity, reduces cost and allows for complete flexibility, enabling you to always choose the right technology for your design. To learn more go to mentor.com/techpapers or call us at 800.547.3000.

DESIGN FOR MANUFACTURING + INTEGRATED SYSTEM DESIGN ELECTRONIC SYSTEM LEVEL DESIGN + FUNCTIONAL VERIFICATION

### Xcell journal

| PUBLISHER         | Mike Santarini<br>mike.santarini@xilinx.com<br>408-626-5981                      |

|-------------------|----------------------------------------------------------------------------------|

| EDITOR            | Jacqueline Damian                                                                |

| ART DIRECTOR      | Scott Blair                                                                      |

| DESIGN/PRODUCTION | Teie, Gelwicks & Associates<br>1-800-493-5551                                    |

| ADVERTISING SALES | Dan Teie<br>1-800-493-5551<br>xcelladsales@aol.com                               |

| INTERNATIONAL     | Melissa Zhang, Asia Pacific<br>melissa.zhang@xilinx.com                          |

|                   | Christelle Moraga, Europe/<br>Middle East/Africa<br>christelle.moraga@xilinx.com |

|                   | Yumi Homura, Japan<br>yumi.homura@xilinx.com                                     |

| SUBSCRIPTIONS     | All Inquiries<br>www.xcellpublications.com                                       |

| REPRINT ORDERS    | 1-800-493-5551                                                                   |

|                   |                                                                                  |

www.xilinx.com/xcell/

Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124-3400 Phone: 408-559-7778 FAX: 408-879-4780 www.xilinx.com/xcell/

© 2009 Xilinx, Inc. All rights reserved. XILINX, the Xilinx Logo, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

The articles, information, and other materials included in this issue are provided solely for the convenience of our readers. Xilinx makes no warranties, express, implied, statutory, or otherwise, and accepts no liability with respect to any such articles, information, or other materials or their use, and any use thereof is solely at the risk of the user. Any person or entity using such information in any way releases and waives any claim it might have against Xilinx for any loss, damage, or expense caused thereby.

# Will FPGAs Lead Semiconductors out of the Economic Doldrums?

Programmable logic's 'forgiveness factor' should not be overlooked.

ver the last couple of months, I've read opinion pieces in the electronics trade press predicting FPGAs could very well lead the semiconductor industry's recovery from the economic down-turn. I'm no financial guru, but I have to think this could well be the case.

In my 14 years covering the electronic-design space (EDA, ASIC, FPGA, PCB and memory industries), I've witnessed firsthand the maturation of the FPGA industry in its seemingly relentless quest to grab market share from the ASIC business. As FPGAs leveraged new process technologies to increase logic-cell counts in line with Moore's Law, they grew faster and lower in power with each new node and became ever more affordable. At the same time, FPGA vendors have added a slew of advanced functionality, hardwiring MPU cores into their devices and offering the latest soft IP.

Tools for FPGAs have kept pace with this complexity, allowing engineers to invent novel designs and implement them in FPGAs. What's more impressive is that most FPGAs are forgiving—if your design doesn't come out quite the way you want it, simply make a few tweaks and reprogram the FPGA until you have the functionality you need. If you need to accommodate a particular standard that is not quite fully defined, you can quickly add that new functionality once the standard has firmed up. You can even adjust your design and reprogram your FPGA after it has been deployed in the field. You don't have to be afraid to try something risky—something innovative.

This forgiveness factor, I believe, will become a much more powerful selling point for FPGAs over ASICs as system companies look at their budgets and examine the cost and risks of implementing designs in application-specific ICs. It certainly is no secret that the mask costs for designs in the latest process technologies have grown exponentially, making ASIC starts viable only for extremely high-volume applications. At the same time, the cost of ASIC tools to deal with new process complexity is skyrocketing.

Today, for example, most ASIC design teams must acquire design-for-manufacturing tools, sophisticated power-analysis tools to manage leakage and perhaps very soon (or already, in some cases) statistical analysis tools just to produce viable silicon. Chances are, to become proficient in these new tools will require a training ramp-up and a bit of troubleshooting. Then you have to deploy all these new tools optimally to make sure your multimillion-gate ASIC is right the first time and doesn't require a mask respin or 30. ASIC prospects are especially scary when you consider that during the last economic downturn, the dot-com bust, ASIC design starts plunged, from roughly 9,000 in 1999 to 4,000 in 2003, according to research firm Gartner Dataquest. And they have been steadily declining ever since. Considering that ASICs back in 2000 and 2003 were nowhere near as complex as they are today and mask costs were far less, one has to wonder how much lower ASIC starts may go.

Some may argue that application-specific standard products could step in to replace ASICs. You could indeed buy an ASSP that generally handles your specific task, and then modify the software running on it to do the job you want it to. But your competitors can buy the same part and implement similar, or even better, software in their product. In short, with an ASSP you no longer have the advantage of differentiating your hardware, just the software. Gartner Dataquest predicts a steady, albeit gentle, erosion in ASSP starts, from roughly 4,200 in 2008 to 4,000 in 2011. Meanwhile, FPGA starts are expected to grow from 90,000 to around 105,000 over that time frame.

Can you take innovative risks with ASICs and ASSPs? Can you afford to? These are questions that I think will resonate with greater frequency throughout the remainder of this economic down-turn and likely afterward.

Does all this mean that FPGAs will, in fact, lead the semiconductor industry in the recovery? No one can say for sure, but the arguments ring true to me.

Mike Santarini Publisher

See for Yourself at www.xilinx.com/spartan

#### GET UP TO 50% LOWER COST

- Integrated features and only two power rails minimize need for external components

- Save up to 70% in logic cell resources with dedicated DSP blocks

- Run cool with 11mW static power, 0µW in hibernate mode

In the highly competitive high-volume market, cost is king. Our latest Extended Spartan®-3A FPGAs deliver the integrated features, low static power, complex computation and embedded processing capabilities you need to achieve the absolute lowest total cost. Period.

Combine these advantages with the industry's largest selection of IP cores, reference designs and I/O standards and you have the most complete low-cost programmable solution available for your next high-volume design.

Visit us at **www.xilinx.com** to download our free ISE<sup>®</sup> WebPACK<sup>™</sup> design tools and start saving money today.

©2009 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners

#### CONTENTS

#### VIEWPOINTS

Letter from the Publisher Will FPGAs Lead Semiconductors out of the Economic Doldrums?...4

**Xpectations** Xilinx's Support Network: Our Success Is Your Success...**66**

#### XCELLENCE BY DESIGN APPLICATION FEATURES

Xcellence in Wireless Communications Baseband Development for 3GPP-LTE Just Got Easier...14

Xcellence in Automotive & ISM Updated Starter Kit Speeds Video Development...18

**Xcellence in Aerospace & Defense** A Flexible Platform for Satellite-Based High-Performance Computing...**22**

Virtex-5 Powers Reconfigurable, Rugged PC...**28**

#### XCELLENCE IN WIRED COMMUNICATIONS

Cover Story FPGAs Take Central Role in Wired Networks

#### FIRST QUARTER 2009, ISSUE 67

#### THE XILINX XPERIENCE FEATURES

**Xperts Corner** Floating Point: Have it Your Way with FPGA Embedded Processors...**32**

Xplanation: FPGA 101 Optimizing Xilinx FPGAs for Power...36

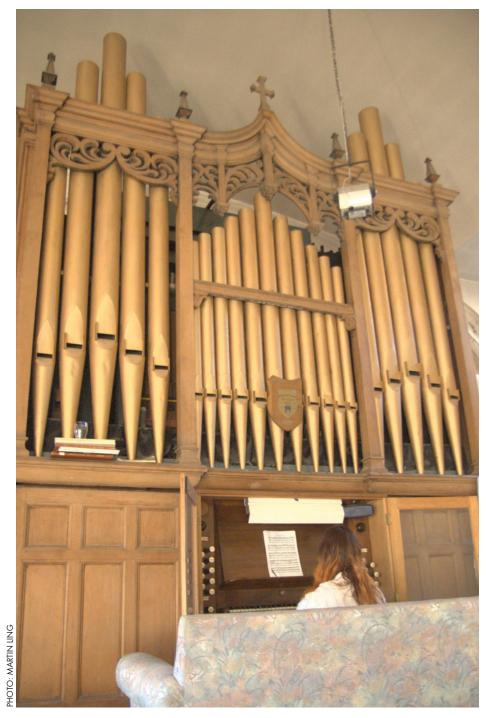

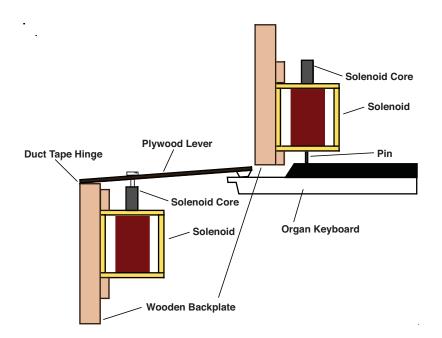

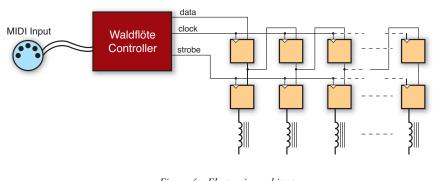

**Xperiment** Computer Interface Makes 19th-Century Pipe Organ Rock...44

Ask FAE-X Hidden in Plain View...50

Profiles of Xcellence Mark Moshayedi Drives STEC Enterprise Storage to Greener Pastures....58

#### XTRA READING

Are You Xperienced? Xilinx, Partners Offer Free Seminar on High-Performance System Design...55

Xamples A mix of new and popular application notes...56

Tools of Xcellence A bit of news about our partners and their latest offerings...62

#### COVER STORY

# FPGAs Take Central Role in Wired Communications

A demand for speed and the advent of multimedia fuel a need for advanced programmable devices in next-generation networks.

#### COVER STORY

by Mike Santarini Publisher, Xcell Journal Xilinx, Inc. mike.santarini@xilinx.com

The wired communications business has an insatiable need for speed. Fifteen years ago, data transport rates (aka bandwidth) were typically in the hundreds of thousands of bits per second (bps). Today's networks can hurl data across the globe at 10 Gbps, and at some points in the network transmission reaches terabit speeds. FPGAs have played a part in this evolution, and as FPGA technologies advance with Moore's Law they will likely take a more central role in nextgeneration wired networks.

In a bid to attract customers willing to pay more for new, high-bandwidth networks delivering multimedia content, telecommunication companies such as AT&T and Verizon are pressuring network equipment manufacturers to build faster systems that will speed the delivery of several types of data, not just voice. Steve Rago, principal analyst of broadband and Internet Protocol TV at market research firm iSuppli Corp., notes that telephone companies are urgently trying to transition their businesses from voice-only networks (see sidebar, page 12). Similarly, big corporations are also demanding faster network equipment that will allow employees to communicate more effectively worldwide. In the financial sector, for example, a speedy network can allow traders in farflung locations to place trades quicklyhere, faster communications translates literally into increased revenue.

Network equipment manufacturers such as Cisco Systems, Alcatel-Lucent, Nokia-Siemens Networks and Juniper Networks are among the many companies vying to be first to market with equipment that can offer carriers and enterprises 40-Gbps and 100-Gbps data transport speeds. To do so, they must first create a new generation of routers and switches powered by the latest generation of bleeding-edge ICs. What's more, they must accomplish this feat while standards for next-generation networks—namely, 40G and 100G—are still evolving.

#### Wired Network Basics

Today's wired communication networks are like a series of roads, highways and superhighways linking one destination to another. Each type of road has a speed limit, and the pokiest byways slow the overall traffic, increasing the time it takes for information to reach its destination.

When a typical user accesses an Internet site from a home PC and downloads a file, the request for data leaves the computer in a data packet at a maximum 1 Gbps—the copper wire connecting your PC to the carrier's access network limits the speed. The access network reads the data packet for, among other things, destination and size, and then forwards it to what's called a metro network—a faster series of electrical routers and switches that reads the packet and forwards the data to the next router along the line. The data ricochets from router to router in the metro network at 10 Gbps.

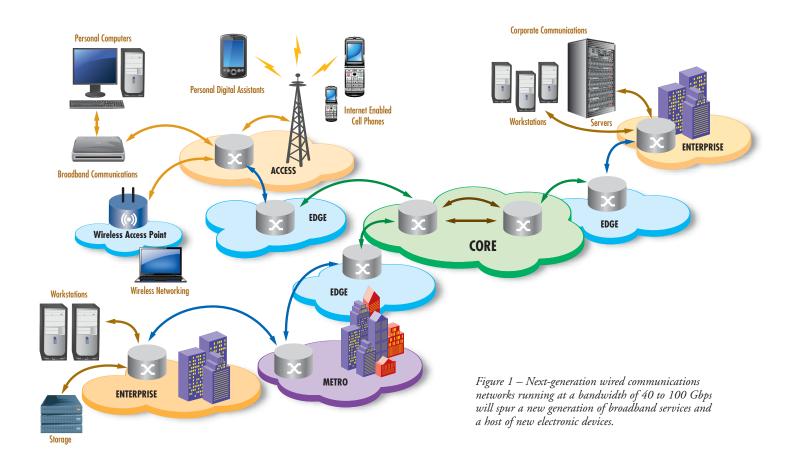

For long-distance routes, the metro network may ultimately connect to a data superhighway called the core, an optical network that shoots the information at the speed of light to a series of metro networks near the data server that contains the Internet file—be it Web page, video clip or music—you are trying to access. The data server then sends the requested data files back, sometimes the same way, through the network (Figure 1).

At each intersection or hub, a router must read the data packet for such information as destination and size, and determine the fastest route given network traffic conditions, before forwarding that data to its next stop. When negotiating longer routes onto the optical network, a router on the front of the optical network must translate that data from the digital signal suited for electronic routers to a pattern of light in the optical domain. Finally, at the end of the core network, another router must do the opposite, retranslating that data from light back to the format for an electrical packet. Then it must read the network traffic conditions for the fastest route and ship the data to the next electrical router or data server.

Access or download typically occurs in a matter of minutes to a matter of seconds,

9

#### COVER STORY

depending on the size and location of the file. But tomorrow's networks will hum along even faster, thanks in part to everadvancing FPGA technology.

#### **Telecom and Datacom Convergence**

Today there are two types of wired networks-one for computing and the second for telecommunications. Traditionally, these networks have been separate, each with its own set of unique protocols, routing equipment, bandwidth requirements and rate of bandwidth growth. For example, the telecom industry has typically increased bandwidth in increments of roughly four (2.5 Gbps to 10 Gbps, now moving to 40 Gbps), while computer networking has done the job in leaps of 10x (100M, 10G, 100G). However, Xilinx distinguished engineer Gordon Brebner notes that during the last wired-network retooling a few years ago, a convergence of sorts took place at 10 Gbps, where physical signaling for Ethernet converged with signaling for telecom as both network types independently increased their top bandwidth rates. While

those networks still remain independent, the network industry has been doing its best over the past few years to merge them, specifically around Ethernet.

"Ethernet used to be the technology that simply connected you to your IT department," said Brebner. "Now there is Ethernet everywhere, and it has developed into carrier Ethernet, in which the telecom industry is using this Ethernet technology internally in their network." The 10-Gbps Ethernet (10GE) technology "has been standardized for a few years now," Brebner said, "and currently, 40GE and 100GE are being drafted together as IEEE 802.03ba.The final standard is expected to be completed in late 2009."

Brebner explained that 40GE would have been the next step for telecom, but the industry expects that rate will initially best suit enterprise networking. For longer transmissions, carriers will use the 100GE standard. It would not be surprising, however, if competition spurs some equipment companies to drive enterprise networking, too, to 100GE.

#### Inside the Router

To transport data at these speeds, network equipment makers will need to create very sophisticated equipment—routers, switches and transport systems—that employ extremely advanced circuitry.

For example, at the heart of a metro router is a series of line cards. Each line card receives data packets in a wide range of protocols, examines the packets for origin, size, destination and information regarding the rest of the network, and then forwards the packet to a switch. The switch, in its turn, shuttles the packet to its next destination along the network. The line card must accomplish all these computations in nanoseconds.

Traditionally, a line card consists of a CPU, a series of dedicated network processor units (NPUs) and a number of the highest-speed FPGAs available. As a packet enters a line card, an FPGA translates the raw data into formats that a given router can read. The processor coordinates the NPUs to read and route data, while the FPGAs facilitate some of the communication between the CPU and the NPUs.

#### Some equipment makers expect FPGAs to start playing a more-central role in the router, integrating the functionality of an NPU into the programmable logic fabric.

To handle packets properly, routers must understand multiple protocols. Indeed, said Brebner, they must support a variety of legacy and new protocols that are layered together in a single packet. Of course, if the entire world converged on one protocol or set of protocols, the network might be able to really speed up. But much of the differentiation that makes one network superior to its competitors lies in the protocols the routers use, Brebner noted. Carriers are not about to relinquish this competitive edge.

Next-generation wired networks will be transferring voice, Internet data and video simultaneously. This so-called triple play requires the development of new protocols and, inevitably, a series of refinements and modifications as carriers race to transfer this data more efficiently and safely.

That's why the ability to modify hardware and change functionality is becoming so important—it allows telecommunications equipment to take advantage of the new protocols and in so doing, delivers a huge advantage to OEMs. Many companies are shunning ASICs and ASSPs in their communications systems because those ICs offer the ability to modify only their own software. FPGAs, by contrast, let you modify the hardware, test software functionality in the software domain and then speed it up by creating a hardware implementation of algorithms in an FPGA.

Still other equipment makers expect FPGAs to start playing a more-central role in the router, integrating the functionality of an NPU into the programmable logic fabric. FPGA vendors tend to be the first silicon developers to use new IC processes. This trait has given them the full doublingof-capacity benefits of Moore's Law, with the payoff of more real estate on each die for additional functionality. With each new generation of FPGA, the likelihood increases that customers can add functions usually reserved for NPUs. Integrating the translation and interface functionality on a single chip ultimately speeds processing, reduces the overall bill of materials and lowers the power consumption of the router—and with it, the operating expenditures for the overall network. Moreover, because FPGAs offer hardware as well as software reconfigurability and can be modified in the field, network equipment vendors have an opportunity to upgrade their equipment while it's in use—indeed, even while it's still running.

With FPGAs evolving rapidly in ways that particularly suit wired communica-

tions applications, network equipment designers are making even greater use of these versatile devices in next-generation routers. Each new generation of FPGA technology includes a greater number of high-speed transceivers to match the increasing overall bandwidth of the network, even as the overall speed of each transceiver continues to climb. For example, the recently released Virtex®-5 TXT devices (Table 1) contain up to 48 RocketIO<sup>TM</sup> multirate transceivers running at 6.5 Gbps. They allow the device to deliver the 312 Gbps total bandwidth required for building network bridges.

| Virtex-5 TXT FPGA Platform                                        |                |            |            |

|-------------------------------------------------------------------|----------------|------------|------------|

| Part Number                                                       |                | XC5VTX150T | XC5VTX240T |

| Slices                                                            |                | 23,200     | 37,440     |

| Logic Cells                                                       |                | 148,480    | 239,616    |

| CLB Flip-Flops                                                    | 92,800         | 149,760    |            |

| Maximum Distributed RAM (kb                                       | 1,500          | 2,400      |            |

| Block RAM/FIFO w/ECC (36 kbits each)                              |                | 228        | 324        |

| Total Block RAM (kbits)                                           |                | 8,208      | 11,664     |

| Digital Clock Manager (DCM)                                       |                | 12         | 12         |

| Phase-Locked Loop                                                 |                | 6          | 6          |

| Maximum Single-Ended Pins (4)                                     |                | 680        | 680        |

| DSP48E Slices                                                     |                | 80         | 96         |

| PCI Express Endpoint Blocks                                       |                | 1          | 1          |

| 10/100/1000 Ethernet MAC Blocks                                   |                | 4          | 4          |

| Rocket10™ GTX High-Speed Transceivers                             |                | 40         | 48         |

| Package (7,8)                                                     | Area           |            |            |

| FFA Packages (FF): flip-chip fine-pitch BGA (1.0 mm ball spacing) |                |            |            |

| FF1156                                                            | 35 x 35 mm     | 360 (40)   |            |

| FF1759                                                            | 42.5 x 42.5 mm | 680 (40)   | 680 (48)   |

Table 1 – Xilinx's serdes-heavy Virtex-5 TXT provides developers of next-generation wired communications equipment with a programmable platform for innovation.

In addition to the high-speed transceivers, the number of logic cells roughly doubles with each new generation of FPGA, in keeping with Moore's Law. These additional logic cells allow equipment manufacturers to place greater functionality within each FPGA, perhaps functionality that was previously assigned to NPUs.

Developing NPUs for each generation of equipment, or deciding which NPU is right for the job, is one of the most trying issues equipment manufacturers confront, Brebner said. The choice is complicated by the fact that with each generation of router, a new batch of startups arises to build the NPUs to power them. "NPUs are about the most fractious area in the market," said Brebner. "Each NPU is designed in a particular way for various niches and functions." The vendor landscape is volatile:

NPU design companies have come and gone, leading some big vendors, such as Cisco Systems, to develop their own.

However, as FPGA technology advances in each generation, there is a greater opportunity for customers to integrate NPU intellectual property (IP) into FPGAs themselves. OEMs can also leverage the devices' reconfigurability so that, as data packets come in with different protocols, the FPGA can

#### **Battle for the Broadband Bundle**

F acing declining revenue as cable competitors poach their voice customers, telephone companies are rapidly bulking up their networks to offer multimedia services, potentially driving new growth in next-generation broadband equipment.

"For the last several years, traditional telephone companies have been losing their subscriber base at an alarming rate," said iSuppli analyst Steve Rago. "Roughly 4 to 10 percent of their subscribers are disappearing every year."

The erosion is occurring for several reasons. "Number one is that many folks are using mobile phones as their only phone line," said Rago. "The second reason is that the need for a second line for the Internet and in some cases even a fax is disappearing—with broadband you don't need a second line for the Internet." In addition, he said, cable multiple-service operators (MSOs) have been successfully snatching away traditional voice services, bundling voice with cable TV and the Internet. In last year's fourth quarter, said Rago, "cable added 1 million voice subscribers in the United States alone." The same transition is going on worldwide, he noted, even in mainland China, where the voice networks are only a dozen or so years old.

Telcos, for their part, are enjoying increased revenue from the broadband services they currently offer, Rago said. However, it hasn't offset the loss of revenue from voice. "The net result is that they are either holding steady [in terms of] revenue growth or growth is declining, which is not a very good position for Wall Street," he said. "If the telcos don't change the way they do business, they are going to become extinct—there won't be a need for them anymore."

Meanwhile, their competitors in the wired space, the MSOs, are not experiencing huge growth either, said Rago. "Actually, they are seeing revenues hold steady or even decline, with more competition from satellite companies and the telcos," he said.

To get back on a growth path, telephone companies worldwide have collectively decided to deliver video as a value-added service to voice, along with other offerings, Rago said. They are banking on one of these Internet-based services in particular: time-shifting TV, which will allow you to watch whatever program you want to see whenever you want to see it. "It will be a paradigm shift from the way you watch TV today," said Rago. "It's one of the advantages telecom companies have with IPTV over the MSOs." Further, Rago said that instead of charging consumers for bits per second, the telcos have decided to do what MSOs do today: have users pay for the services they want. "You pay for your video service [IPTV, for example], you pay for your voice and your other services—you'll pay more depending on what services you add to your plan." Rago said that most telephone companies are already offering these new services or plan to soon do so.

#### **Multibillion-Dollar Question**

Meanwhile, MSOs will continue to attempt to lure traditional voice subscribers to their multimedia mix and will likely come up with their own value-added services.

But the multibillion-dollar question for all these companies, telephone and MSO alike, is not simply how to establish growth, but how to establish sustainable growth.

One challenge is "getting a fat enough pipe to the home to offer all of these new services," Rago said. DSL worldwide, and ADSL in particular, is still the biggest, he said, "but we've seen growth in broadband DSL and fiber to the home; or fiber near to the home and BDSL near to the curb. Fiber to the home is second now in terms of new services. It even surpasses cable modems."

Upgrading the access equipment to handle these new services will, of course, be key to making all this possible. "We're looking at equipment that can handle speeds anywhere from 30 Mbps to 100 Mbps," he said. New services such as timeshifting TV and video-on-demand will put tremendous pressure on bandwidth in the network. "It will drive a major need for innovations and enhancements in long-haul and the metro networking space," said Rago. It will also give rise to a new crop of high-speed-data consumer devices that will in turn shape the feature requirements for next-generation services.

Indeed, Rago said that "the battle for the broadband bundle" should result in novel technologies and services that ultimately drive innovations in related fields. But who will win that battle is anyone's guess at this point.

To read more about the competitive landscape, contact iSuppli for its latest report on consumer communications.

— Mike Santarini

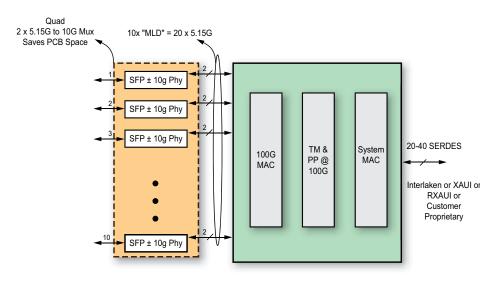

Figure 2 – Sarance Technologies' 100GE MAC solution implemented with Virtex-5 FPGAs

instantiate or implement an NPU architecture on the fly that is best suited to read the data, even run a security check in it, negotiate the fastest route to its destination and then forward the data there.

"FPGAs have traditionally performed embedded RISC and control plane functions," said Loring Wirbel, longtime communications watcher and moderator of *EDN* Magazine's new FPGA Gurus Web site. "Today's FPGAs can now handle a lot of datapath functions, so now seemingly a single FPGA—depending on how it's partitioned—can serve as an aggregation box in an enterprise or one of the blades in a big switching center. So you don't need coprocessing if you have partitioned things correctly. One of the stories of the death of the network processor is that slowly but surely, FPGAs started taking over the NPU's function."

Wirbel notes that traditionally, as each new generation of equipment has rolled out, there is a very brief opportunity for NPU vendors to field specialized packetforwarding engines. But in the wink of an eye the opportunity passes, he said, and the engines get replaced with FPGAs.

"As we start moving to 40G and 100G networks, there will be a temporary place for very fast engines that just do the packet forwarding, just as there was for 1G and 10G [technology]," Wirbel said. "But the thing is, as you move to the new feature sizes, that is only going to be a narrow window and they may very likely just skip looking over the ASSPs and go directly with an FPGA. Every generation has had that brief window where they use ASSPs, but with each generation that window is becoming more narrow—eventually it will stay closed."

#### Advancing FPGA Technologies for Wired Comms

Today, Xilinx's largest Virtex-5 TXT XC5VTX240T device contains 37,440 logic slices with a total of 239,616 logic cells. This architecture has afforded design teams and IP vendors great opportunities to innovate solutions that support XAUI, RXAUI, Interlaken, Sonet, ODN and many other wired standards with the most advanced FPGA silicon to date.

For example, Xilinx worked closely with Sarance Technologies to provide the industry's first 100GE media-access controller, a full-featured, IEEE 802.3ba-compliant solution implemented with Virtex-5 FPGAs (Figure 2).

Sarance announced in mid-2008 that its 100GE MAC solution was up and running on tier-one vendor hardware prototypes using two Virtex-5 FXT FPGAs, 10 external 10-Gbps physical-layer devices and a variety of system-side interfaces.

The 100GE MAC-to-Interlaken bridge solution that the new Virtex-5 TXT FPGA platform supports is a low-risk way to condense functionality into a single FPGA and three external quad serdes muxes. In this implementation, Xilinx's 64/66 and 64/67 encode/decode gearboxes are built into the GTX transceiver, saving nearly one-fifth of the logic count and power consumption of the design.

In June 2008, telecommunications giant Comcast Corp. announced it had successfully completed a 100GE technology test over its existing backbone infrastructure between Philadelphia and McLean, Va., using the industry's first 100GE router interface. The system used the same Sarance Technologies' High Speed Ethernet IP Core (HSEC) running on a Virtex-5 FXT FPGA that is supported by the Virtex-5 TXT platform today.

The demonstrations follow up on early achievements in the 100GE domain. In November 2006, Xilinx FPGAs were the vehicle used to showcase the world's first successful 100GE transmission through a live production network demonstrated at the SC06 International Conference, the confab of high-performance computing, networking, storage and analysis.

Finisar teamed with Level 3 Communications, Internet2 and the University of California at Santa Cruz to demonstrate the transmission of 100GE traffic over Level 3's DWDM network from the show site in Tampa, Fla., to Houston and back—a total of 4,000 miles.

The Xilinx FPGA electrically transmitted all ten signals to ten 10-Gbps XFP optical transceivers, which converted the signals into the optical domain. From there, the signals traveled to Infinera's commercially available DTN Switched WDM System, which handed them off to the Level 3 network.

Overall, FPGA technologies are advancing fast. With each turn of Moore's Law, FPGAs offer communications designers the ability to create higher-bandwidth, next-generation networks. In the not-so-distant future, network designers will give FPGAs a more-central place in their designs. How big that role turns out to be will depend not only on the silicon, but on the IP and hardware and software tools customers have at their disposal. Xilinx remains committed to creating innovations for the wired communications market, with an aim not just to maintain its leadership but to build on it with new programmable solutions. 🍨

#### XCELLENCE IN WIRELESS COMMS

# Baseband Development for 3GPP-LTE Just Got Easier

With the release of LTE-Channel Encoder and Decoder, Xilinx helps customers speed Layer-1 subsystem development and address the performance and latency challenges of 4G wireless.

by David Nicklin Senior Manager, Wireless Product Marketing Xilinx, Inc.

"MATTERNA

The baseband processing signal chain presents both the greatest challenge and the best opportunity for innovation in the base transceiver station. No wonder, then, that it has become a key area for product differentiation among OEMs. Competition in baseband architecture designs has intensified with the realization that many of the techniques used for earlier 2G and 3G systems simply will not scale to meet the performance and latency requirements of the 3GPP Long Term Evolution (LTE) technology, wireless' fourth generation

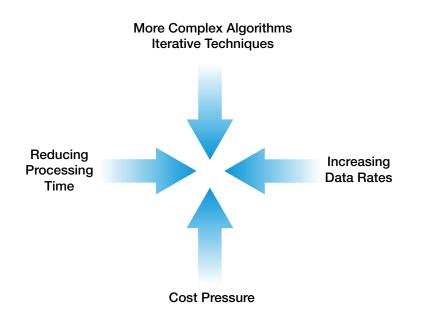

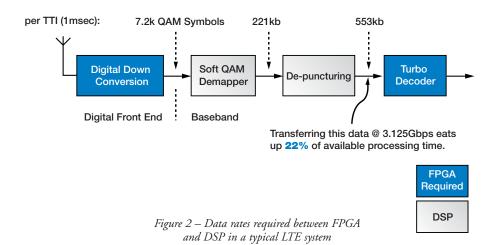

Not only does the processing chain have to contend with far more processing than previously, but also, all the functions must be completed in much less time. Rounding out the set of challenges facing system architects is the need to develop a system that can meet the operators' aggressive capital- and operational-expenditure reduction targets. These major pressures on the baseband processing system design are illustrated in Figure 1.

Xcell Journal

Figure 1 - Challenges in evolving baseband processing needs

An FPGA-based solution can meet all of these demands, while sidestepping the usual performance issues and bottlenecks. Initiatives such as Xilinx's newly released LTE Uplink Channel Decoder and LTE Downlink Channel Encoder LogiCOREs<sup>™</sup> seek to remove the barriers to FPGA adoption by incorporating many of the critical Layer-1 functions in a single IP solution.

Advances in silicon technology have been a key enabler in the success of wireless communications by facilitating the rollout of ever-more-complex algorithmic techniques from the research labs into products. One such example was the deployment of iterative turbo error-correction techniques in 3G networks, a scheme that migrated from discovery to commercial release inside of 10 years. The pace of innovation has continued to accelerate, most notably with the exploitation of the spatial dimension in wireless communication through various multiple-input, multiple-output (MIMO) antenna techniques.

With the advent of 4G air interfaces however, the pressures have built to the point where traditional programmable DSP-centric channel card architectures are struggling to cope. The traditional partitioning between FPGA and DSP is constrained by performance bottlenecks that come into play due to the enormous amount of data that has to pass to-and-fro between them.

So, how can we remove such bottlenecks? The key lies in simplifying the Layer-1 system architecture and eliminating all unnecessary chip-to-chip data transfers. This simplification process raises some uncomfortable questions about the scalability of architectures based on digital signal processors. Designers need a strong portfolio of intellectual property (IP), software and support to aid them with the transition to a Layer-1 system architecture in which most functions are implemented in programmable hardware rather than DSPs.

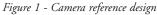

#### Simplifying Layer-1 Design

Let us look more closely at the problems that can occur when the FPGA is solely employed as a coprocessor to offload turbo decoding functions from the DSP processor. In analyzing the effectiveness of such a partitioning in a typical LTE baseband design (see Figure 2), Xilinx system architects have discovered that more than 20 percent of the available latency-timing budget can go into just shifting the data from a DSP processor to an FPGA and back again via SRIO connections. Shockingly, this is far from a worst-case scenario. Add to the mix data that is coded with higher-order modulation schemes, such as 64-QAM, two MIMO code words at a 1/3 code rate, over a full 20-MHz LTE band, and the numbers rapidly get much, much worse.

One response is simply to add bigger "pipes" to move the data around by deploying more high-speed multigigabit-transceiver connections. While it is certainly possible to construct a system this way, it leads to an unnecessary increase in system power dissipation, as the relatively powerhungry high-speed serial connections transport the data back and forth and bridging functions are replicated, leading to the need for more hardware resources.

There is a better, more-optimal solution. By incorporating most of the Layer-1 functionality within the FPGA, a designer can free up this unnecessary overhead and

#### XCELLENCE IN WIRELESS COMMS

pass on the savings in improved system throughput and latency, while at the same time lowering power requirements. The power saving alone translates directly into improved reliability, reduced system cost and opex savings.

Such an architectural approach avoids the need for DSPs altogether-although they can be incorporated, if desired, to perform lower-rate functions. With this kind of a partitioning, the FPGA implements the entire Layer-1 baseband processing, leaving the other higher-layer functions, such as media-access control and HARQ processing, to a more cost-effective general-purpose processor or a network processor, which can also handle additional backhaul connectivity functions. Integrating all the high-performance and time-critical functions on a single platform FPGA effectively circumvents delay and bandwidth limitations, and partitioning becomes a much simpler task.

The key stumbling block to date in adopting such an approach has been the need to simplify the process, from design concept to hardware. Also, designers accustomed to a DSP-centric design flow need IP and development tools that make it easier to unlock the capabilities of the FPGA, and quickly and effectively develop baseband functionality within it. Xilinx's LTE Uplink Channel Decoder and LTE Downlink Channel Encoder LogiCOREs remove such barriers to adoption by folding many of the critical Layer-1 functions in a single IP solution that can be customized via a GUI in the Xilinx CORE Generator<sup>TM</sup> tool. This design flow enables engineers with limited FPGA experience to concentrate on the wider system design, saving significant development and integration effort.

#### The Shape of Things to Come

The drive to ever-faster connectivity and low-latency connections is a key requirement of LTE and will remain so for future systems beyond 4G. As these newer datacentric wireless systems evolve, many companies that have adopted the traditional partitioning between DSP and FPGA will find the overhead involved in shifting data between separate chips has become unacceptable. An FPGA-based solution is now much more accessible to designers looking for that extra edge in their product design. Those who move past their ties to a legacy system design approach will deliver a product that surmounts the performance issues and bottlenecks their competition will continue to experience. 🔹

#### Inside the LogiCOREs

Xilinx's recently released LTE Channel Encoder and Decoder LogiCOREs, designed for 3GPP rel8 E-UTRA eNB baseband processing, comply with specifications 3GPP TS 36.211 v8.2.0 and TS 36.212 v8.2.0 (2008-03). They support different configurations up to 20 MHz in bandwidth with normal (short) CP, 64-QAM modulation and two MIMO code words. Both can also handle FDD and TDD frame structures, suiting them for systems that have evolved from the TD-SCDMA standard.

Both the encoder and the decoder are supplied as standalone, parameterized IP blocks that can be easily incorporated into a customer's design using the Coregen software tool. Supporting them is a comprehensive set of tests, simulations and C models for system simulation in order to aid design integration.

More details on the new LogiCORES are available at the Xilinx IPcenter (*www.xilinx.com/ipcenter*). Designers can access additional wireless reference designs and solutions via the Wireless End-Market page (*www.xilinx.com/esp/wireless*).

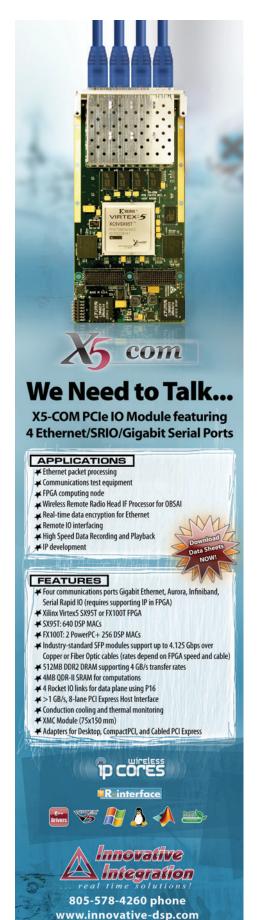

X5-TX, Virtex 5-based Transmitter Module with Integrated Wireless IP Cores!

#### Features

- (4) 500 MSPS or (2) 1 GSPS 16-bit DACs

- +/-1V, 50 ohm, DC or AC coupled inputs

- · External or internal sample clock & trigger

- Xilinx Virtex5, SX95T or LX155T FPGA

- 512MB DDR2 DRAM

- 4MB QDR-II SRAM

- 8 Rocket IO private links, 2.5 Gbps each

- >1 GB/s, 8-lane PCI Express Host Interface

- Power Management features

- XMC Module (75x150 mm)

- PCI Express (VITA 42.3)

#### Applications

- Wireless Transmitter

- RADAR pulse generation

- High Speed Arbitrary Waveform Generation

- Electronic Warfare

- IP development

### More of the same — WAY more

More gates, more speed, more versatility, and of course, less cost — it's what you expect from The Dini Group. This new linx Virtex-5 LX 330s (-1 or -2 speed grades). With over 32 Million ASIC

TEX:5

board features 16 Xilinx Virtex-5 LX 330s (-1 or -2 speed grades). With over 32 Million ASIC gates (not counting memories or multipliers) the DN9000K10 is the biggest, fastest, ASIC prototyping platform in production.

.

User-friendly features include:

VIRTEX-5

in in the second se

VIRTEX-5

VIRTEX-5

-

In Minut

\$ NUN

VIRTEX-5

FPGA F12

DIMM3

The

Group

.

0

VIRTEX-5

ALC: NOTE OF

STATE OF THE

VIRTEX-

D. HER D. HE HERE

n . Jain

FPGA F1

ALL NI

- 9 clock networks, balanced and distributed to all FPGAs

- 6 DDR2 SODIMM modules with options for FLASH, SSRAM, QDR SSRAM, Mictor(s), DDR3, RLDRAM, and other memories

- USB and multiple RS 232 ports for user interface

- 1500 I/O pins for the most demanding expansion requirements

nat e Nati

IRTEX-

Software for board operation includes reference designs to get you up and running quickly. The board is available "off-the-shelf" with lead times of 2-3 weeks. For more gates and more speed, call The Dini Group and get your product to market faster.

XCELLENCE IN AUTOMOTIVE & ISM

# Updated Starter Kit Speeds Video Development

The XtremeDSP Video Starter Kit, Spartan-3A DSP FPGA Edition 2, provides a high-performance development platform for complex high-definition systems.

by Joe Mallett Senior Product Line Manager Xilinx, Inc. jmallett@xilinx.com

The video industry's shift to more-complex and integrated processing solutions along with demanding, next-generation video compression standards is driving system requirements for video performance that exceeds what standalone DSPs can deliver. No wonder, then, that many companies designing state-of-the-art video equipment are turning to FPGA platforms. In particular, many of them are joining companies in sensitive military, automotive, medical, consumer, industrial and security applications in choosing the Xilinx® Spartan®-3A DSP, which supplies more than 20 GMACs of DSP performance for less than \$30.

In addition to performance, this FPGA provides an integrated solution supporting DSP and embedded processing using MicroBlaze<sup>TM</sup> processors in the system. Those features enable OS support and drivers for specific market segments.

Xilinx recently updated the XtremeDSPTM Video Starter Kit-Spartan-3A Edition to help design groups get started with these kinds of advanced designs, and to accelerate development times. This kit can help you create advanced video systems for whatever application you are targeting.

| Reference Design    | Functionality Description                                                                                                                                                                                                                                                       |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DVI Pass-Through    | <ul> <li>Capture a video stream input port</li> <li>Perform real-time image processing on the video stream</li> <li>Display the processed video</li> </ul>                                                                                                                      |

| DVI Frame Buffer    | <ul> <li>Capture a video stream from a camera</li> <li>Perform processing on the video stream</li> <li>Buffer the video stream in external memory</li> <li>Report memory bandwidth utilization data</li> </ul>                                                                  |

| Camera Frame Buffer | <ul> <li>Capture a video stream from a camera</li> <li>Perform processing on the video stream</li> <li>Buffer the video stream in external memory</li> <li>Display the processed video at a different rate</li> <li>Use a MicroBlaze to configure the video pipeline</li> </ul> |

| Video Processing    | <ul> <li>Capture video stream from an S-video interface</li> <li>Support weave and de-weave access to video memory</li> <li>Perform gamma processing and 2D FIR filtering</li> </ul>                                                                                            |

| Hardware Co-SIM     | <ul> <li>Initialize a point-to-point connection to the platform</li> <li>Any design within System Generator can add a HW-CoSIM token</li> <li>Validation acceleration with hardware in-the-loop</li> </ul>                                                                      |

#### Table 1 – Reference designs

#### Video Starter Kit Version 2.0

The latest version of the XtremeDSP Video Starter Kit (VSK) for the Spartan-3A provides a comprehensive platform that accelerates the development of video applications on Xilinx FPGAs. Designed to leverage the cost/performance advantages of the Spartan-3A DSP FPGA device family, the kit offers an updated set of video reference designs based on an embedded design framework that allows customers to focus on their unique valueadded development.

The VSK provides multiple reference designs that can accelerate the development of video applications running on Xilinx FPGAs. Each reference design is built upon a common framework and uses multiple interfaces for the I/O of video data to the FPGA. Table 1 lists each reference design and the video processing and connectivity capability it illustrates.

#### Starting with the camera reference design, a software developer can, from day one, begin implementing an operating system and programming the application layer using the EDK software development tools.

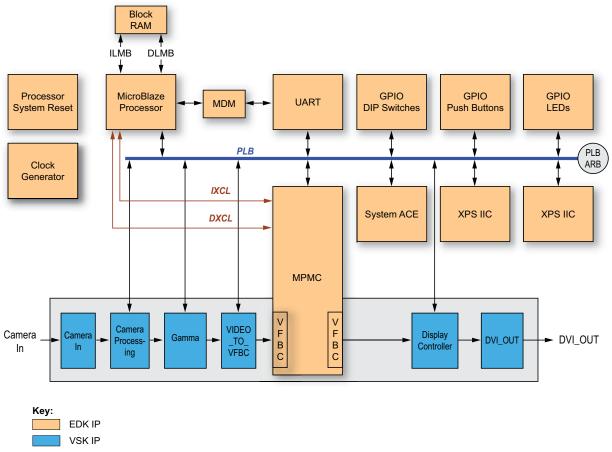

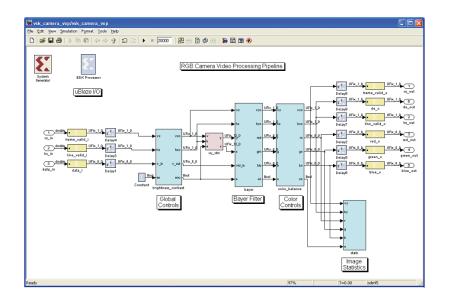

The reference designs help accelerate development by implementing specific data flows that are common to video systems. One such example is having a camera provide RAW image data to the FPGA for processing and display, as seen in the camera reference design shown in Figure 1.

The VSK provides all necessary source and project files for the reference designs, which developers use as a starting point. In the camera reference design, the camera processing block is a design developed in System Generator and integrated as a dedicated hardware peripheral with the EDK embedded system. This allows hardware designers to easily remove the example image processing, replace it with new or existing designs and integrate it within the system without having to design the supporting hardware peripherals.

#### **Embedded Processing**

The migration to a complex hardware acceleration processing system is stepping up the need for embedded processing to handle all the real-time control, configuration and system interaction.

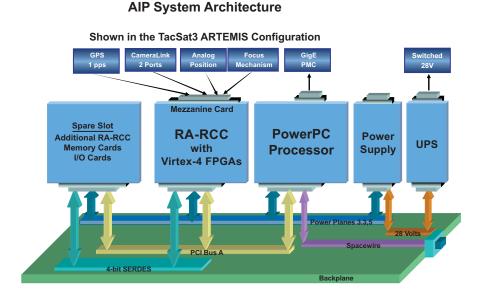

The tight integration means designers can convert DSP designs captured in System Generator into custom peripherals for Platform Studio, and connect them to the base system using the PLB bus. This allows a system designer to easily enable the system control and migration of existing system software with the adoption of a MicroBlaze v7 soft-core processor. Designers gain performance and achieve system integration by exploiting the flexibility of the device to configure a hardware architecture optimized for a particular application. Starting with the camera reference design, for example, a software developer can, from day one, begin implementing an operating system and programming the application layer using the EDK software development tools (see Figure 2).

This flexibility adds a degree of freedom to the development process that also reduces the design complexity. The XtremeDSP Video Starter Kit gives a hardware or software developer a complete and easy-to-use design environment with example applications and full sup-

Figure 2 – Application programming on the VSK

Figure 3 – System Generator diagram for a camera reference design

port for the standard Xilinx tool flows. That combination can help to accelerate the design process and allows for end product differentiation.

System Generator supports hardwarein-the-loop co-simulation using the Spartan-3A DSP 3400A development platform, which can accelerate the performance of Simulink® simulations up to 100x. This acceleration enables video algorithm development and debug using real-time video streams read into Simulink using The Mathworks' Data Acquisition Toolbox<sup>TM</sup>.

#### **Hardware Acceleration**

Now that the required processing bandwidth is outpacing the current capabilities of standalone DSP processors, hardware acceleration is becoming a necessity in many video applications. FPGAs enable this hardware acceleration while delivering the additional benefits of system integration and architecture repartitioning.

The migration from a standalone system processor to the integration of a coprocessor requires some design exploration as the hardware designer is looking at the various functions to accelerate. The first challenge is the need to have a variety of design flows that enable abstract model programming using MATLAB<sup>TM</sup> and Simulink, and the easy integration of any existing VHDL/Verilog designs. Designers can first implement video algorithm designs as a MATLAB or Simulink model using the optional Video and Image Processing Blockset. As the development moves to the next stage, hardware implementation is easily enabled through System Generator for DSP, which provides a rich set of DSP building blocks, optimized for Xilinx devices, for use within the Simulink modeling environment (see Figure 3).

Once the hardware design is completed in System Generator, the HW-CoSIM functionality accelerates the validation time by placing hardware in the loop. For complex systems, this can greatly improve the testing run-time and thereby increase the number of iterations completed within a given amount of time.

The XtremeDSP Video Starter Kit–Spartan-3A DSP Edition coupled with the integrated reference designs provides the ideal platform for video developers by enabling various modes for processing data from streaming to frame buffer based. Video developers can quickly design and validate hardware peripherals (HW-CoSim) using System Generator. Integration of hardware peripherals and embedded processing accelerates the development of complex video systems within industrial imaging, broadcast, consumer, medical and automotive applications.

FPGA

128Mbytes DDR Memory

CameraLink connection

VHDL Imaging Library

USB 2 or Standalone

Programmable hardware with cables, device drivers, loading tools, examples and Power Supply. Systems can be used connected to a PC using USB, or can function standalone (without USB) using the initialisation PROMs.

> sales@hunteng.co.uk +44 (0)1278 760188

www.hunt-rtg.com

## A Flexible Platform for Satellite-Based High-Performance Computing

Space-grade Virtex FPGAs and a reconfigurable system architecture satisfy demanding size, weight and power requirements and accelerate design cycles.

by Ian Troxel Future Systems Architect SEAKR Engineering, Inc. Ian.Troxel@seakr.com

Greg Lara Marketing Manager Xilinx, Inc. greg.lara@xilinx.com

Developers of space-based electronic systems face increasing pressure to deliver higher levels of performance while working within more-aggressive project schedules and tighter budgets. Many space-based systems now under development call for advanced video equipment that will capture images with extremely high resolution and then relay those images instantaneously back to earth. To do this, new systems need to include advanced processing circuitry, greater storage capacity and the ability to transfer large data files quickly over long distances. However space-based systems have a unique set of size, weight and power (SWAP) constraints that can prove taxing for designers.

Requirements to do more for less are driving the adoption of commercial, off-theshelf (COTS) devices, such as FPGAs. The flexibility inherent in reconfigurable FPGAs offers tremendous benefits for developers of space-based systems in terms of SWAP constraints, cost and productivity.

One way to get the maximum leverage from available engineering and budget resources is to create a flexible payload that can be deployed in multiple missions. Our company, SEAKR Engineering, Inc., employed reconfigurable Xilinx® Virtex® FPGAs to create a flexible high-performance computing platform that serves as the heart of a variety of space-based systems. This reconfigurable computing (RCC) methodology has enabled our engineers to achieve demanding performance targets within SWAP, cost and time constraints for a number of missions, most notably our onboard processor for Raytheon's Advanced Responsive Tactically Effective Military Imaging Spectrometer (Artemis), our Programmable Space Transceiver, our Programmable Space IP Modem and the Orion Vision Processing Unit, currently under development.

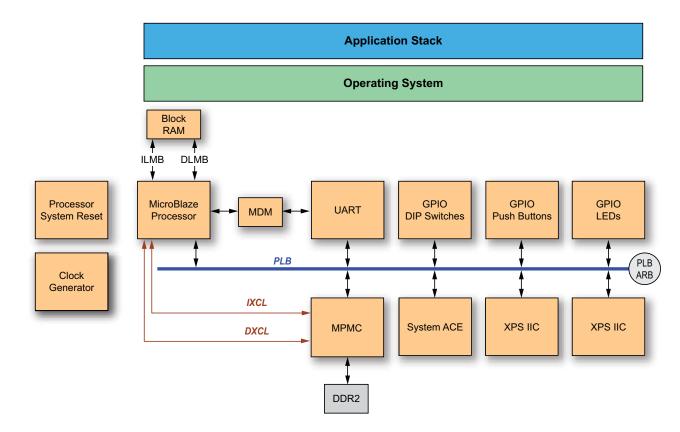

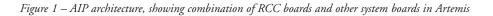

#### Application-Independent Processor Architecture

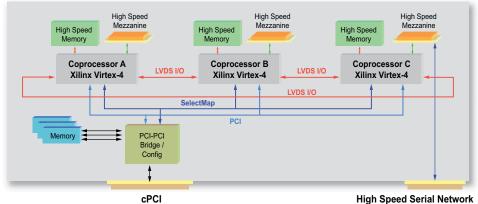

This new platform we developed, called the Application Independent Processor (AIP), comprises a mix of scalar processors and RCCs in a flexible, scalable architecture that supports open standards (Figure 1). Its flexible I/O architecture allows us to mix and match boards to create different configurations that best suit our application requirements, delivering what we call mission-unique functionality. The AIP leverages the unique capabilities of Xilinx's SRAM-based FPGAs to enable in-orbit reconfigurability for additional flexibility and SWAP benefits. The AIP also supports a variety of single-event effect (SEE) radiation-mitigation techniques to ensure reliable operation in different orbits.

The heart of the AIP system architecture is a reconfigurable computer board hosting a trio of Virtex®-4 FPGAs (Figure 2). Our investigation of available components concluded that Virtex FPGAs were the only devices that could achieve our performance targets and provide the characteristics required for spaceflight. For the most demanding applications, Xilinx offers Virtex-4QV space-grade devices. These FPGAs incorporate the same architecture as their commercial-grade counterparts (enabling low-cost system development, prototyping and evaluation), but undergo special processing and screening to Class-Q and Class-V requirements.

Working in concert with sequential processors, the Virtex-4 FPGAs serve as a coprocessor for accelerating key processingintensive tasks. The three-FPGA board architecture offers flexibility for addressing the unique requirements of different missions. In some applications we use the three FPGAs for SEE mitigation techniques that require component-level redundancy. In others, we partition a large coprocessor across multiple devices and use the ring bus connecting the three FPGAs via an LVDS interface for high-speed communication among the devices. Employing an extended 6U form factor, the card has two connectors for interboard communication: one for a CompactPCI backplane and another for a high-speed serial network.

Each FPGA has direct access to dedicated high-speed memory on the RCC board and to a connector supporting expansion and customization via a highspeed mezzanine card. This architecture enables us to expand the capabilities of the RCC board with mission-specific I/O, memory, analog circuitry and even additional logic. The mezzanine card, which also plays a part in SEE mitigation in certain applications, joins the RCC board through a set of three connectors, each providing 170 LVDS I/Os.

Moving mission-specific functionality to the mezzanine card has enabled us to use the same FPGA-based processing card for multiple unique applications. The common architecture has reduced project risk, costs and schedules.

#### **Mitigating Radiation Effects in FPGAs**

Flying reconfigurable FPGA-based systems in space requires special considerations to ensure reliable operation in a high-radiation environment, because the SRAM-based configuration circuitry is susceptible to radiation-induced upset. The first consideration is the choice of component. In addition to industrial and military temperature-grade options, Xilinx offers V-grade Virtex-4 and Virtex-5 FPGAs that undergo special processing to make them immune to radiationinduced latch-up and deliver guaranteed performance for total-dose effects. These devices also undergo extensive characterization in neutron and proton beams to

#### XCELLENCE IN AEROSPACE & DEFENSE

**RCC Board Architecture**

Figure 2 – RCC board architecture diagram and photo

generate reliable predictions of singleevent upset (SEU) and single-event functional interrupt rates for particular orbits. This data guides engineers in selecting an upset-mitigation scheme appropriate for the application and orbit.

Upset mitigation for reconfigurable FPGAs generally involves some combination of hardware triple redundancy and configuration memory scrubbing. Hardware triple redundancy involves tripling critical circuits to ensure uninterrupted operation even if one element experiences a radiationinduced upset. It also adds a voter circuit that compares signals arriving from the triplicated logic branches and rejects an invalid signal resulting from an upset.

Designers can choose from among a number of approaches to satisfy the performance and availability requirements of their system. One technique involves redundant FPGAs and an external radiation-hardened voter circuit. Another approach is device-level mitigation, which involves triplicating mission-critical logic inside a single FPGA, along with the associated voter circuits. Traditionally, engineers have tackled this triple-modular redundancy (TMR) design technique by hand. Xilinx now offers special design tools that automate TMR implementation within an FPGA. Factors influencing the choice of mitigation scheme include the size of the target circuit, the level of radiation in the selected orbit and uptime requirements of the circuit.

The basic concept behind memory scrubbing is to rewrite the configuration memory more frequently than upsets accumulate. Designers can choose from among a number of memory-scrubbing techniques to suit different upset rates and uptime requirements. At one extreme, the simplest technique involves reloading a complete bitstream into the configuration memory. This method involves low overhead but requires that the circuit be inactive for a period at least as long as a configuration cycle. More-advanced techniques exist for applications with stricter uptime requirements, higher upset rates or both. Leveraging the partial-reconfiguration capability of Virtex FPGAs, these methods involve circuits that detect memory upsets and then initiate reconfiguration of only a selected subset of the memory array.

#### **AIP in Action**

We have already used the AIP architecture in four separate missions. The combination of the FPGA-based RCC board and flexible mezzanine card has enabled our engineers to build a variety of processing and communications systems rapidly and to implement mitigation schemes suitable for the unique requirements of each mission.

The first incarnation of the AIP was Artemis—the Advanced Responsive Tactically Effective Military Imaging Spectrometer-which will be flying on the TacSat-3 satellite, scheduled for launch in the second quarter. Designed to provide situational awareness on the battlefield, Artemis performs advanced image processing on data the satellite collects and delivers it to soldiers in the field via a narrowband downlink. Our engineers realized that an RCC approach would be required to meet the spacecraft's size, weight and power goals: dimensions of 7.8 x 11.41 x 10 inches; a weight of 18 pounds; and power of 40 watts (with a hard limit of 50 W).

Two Virtex-4 FPGAs perform sensor data acquisition along with preprocessing functions such as calibration. An embedded processing system based on the MicroBlaze<sup>TM</sup> soft-processor core coordinates memory

access and processor coordination, while a PowerPC<sup>®</sup> single-board computer handles image generation and target cueing. Figure 1 shows the Artemis system architecture.

Because the image data path is not mission critical, configuration memory scrubbing provides suitable mitigation for Artemis. That is, the designers were able to satisfy the availability requirements without resorting to logic triplication or redundant devices. Furthermore, we determined that we could use commercial-grade FPGAs to flash memory; each bitstream configures the FPGAs to process a specific waveform and frequency. In this way the system is able to support multiple waveforms using a minimum amount of hardware (see Table 1).

The flexibility of the RCC board provides benefits that start with initial system development. The delay between requesting and receiving a spectrum slot can be greater than one year. Reconfigurable hardware allows designers to initiate development before receiving

| Receiver/Uplink          | L-Band: 1,760 to 1,840 MHz                     |  |

|--------------------------|------------------------------------------------|--|

|                          | S-Band: 2,025 to 2,120 MHz                     |  |

| Transmitter/Downlink     | S-Band: 2,200 to 3,200 MHz                     |  |

| Space Ground Link System | FSK-AM Command Uplink (1 kbps, 2 kbps)         |  |

|                          | Subcarrier BPSK Telemetry Downlink (256 kpbs)  |  |

| Universal S-Band         | Subcarrier BPSK Command Uplink ( = 4 kbps)</td |  |

|                          | Subcarrier BPSK Telemetry Downlink (256 kbps)  |  |

Table 1 – Programmable Satellite Transceiver communications details

reduce the system cost. Two Virtex-4 FPGAs share the image-processing work-load, while the third socket remains unpopulated to minimize power.

The AIP methodology delivered huge productivity dividends after its first application, enabling us to save roughly one year of development time on each subsequent project thanks to a substantial reduction in nonrecurring-engineering costs.

#### **RCC Enables a Flexible Transceiver**

The second mission for the AIP was in the Programmable Satellite Transceiver. The PST system provides frequency-agile satellite communications on multiple radio bands. SEAKR engineers concluded that even highend PowerPC processors could not provide the necessary heavy lifting within the SWAP requirements of 3.86 x 6.85 x 7 inches, 10 pounds and Rx power of 10 W (Tx, 45 W).

To meet these requirements, our designers exploited the in-system reconfiguration capability of Virtex FPGAs. The system stores multiple configuration bitstreams in the spectrum assignment and then implement the required frequency later. This capability also enables developers to adapt the system to the requirements of subsequent missions. SEAKR is currently developing additional waveforms for future deployment.

The nature of the PST mission simplified the radiation-mitigation requirements. The communication system maintains end-to-end control of the channel and is tolerant of data errors: in the event of corrupted data, the system responds by retransmitting the affected packets. This inherent error tolerance means that configuration memory scrubbing provides suitable SEU mitigation for the control path. To protect intermediate processing results, we triplicated the memory on the mezzanine card.

To complete the system, the AIP board joins RF modules and a power module in an extended 6U form factor chassis that's designed to withstand shock and other stresses of launch.

#### Internet in Space

Packet-based networking in space promises to provide the same flexibility and robustness available in terrestrial networks. Long a mainstay of wireline networking equipment, reconfigurable FPGAs lend the same benefits of performance, flexibility and design acceleration to space-based applications, as demonstrated by our Programmable Satellite Internet Protocol Modem. PSIM extracts Ethernet frames from standard satellite communications waveforms and facilitates IP routing on the spacecraft. Packet-based satellite communication enables beam- and waveform-independent routing of data through virtual circuits. Compared with standard bent-pipe satellite communication channels, packet-based networking improves scalability and throughput, enables decentralized multicast and is flexible enough to offer fine-grained quality-of-service.

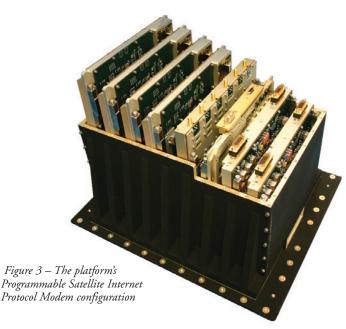

The PSIM comprises 12 Virtex-4V FPGAs mounted on four RCC cards, along with two sequential processors and an analog switch card in a ruggedized chassis (Figure 3). The FPGAs perform waveform processing, while the sequential processors provide Ethernet interfaces and packet switching.

The availability requirements for this mission called for a more-aggressive mitigation scheme than the ones we used in Artemis or the PST. The system must provide uninterrupted end-to-end control, as recovery from an error would take too much time and reduce availability below target requirements. As a result, SEAKR engineers implemented a mitigation scheme that enables on-the-fly correction of errors while providing uninterrupted service.

We triplicated the FPGA logic in three devices on each RCC board. A radiationhardened logic device on the mezzanine card serves as a majority voter. Memory scrubbing takes place in the background, transparent to the operation of the network. The mezzanine card also provides the physical interfaces to the router.

The mission on which the PSIM is to fly is scheduled for launch in the second quarter.

#### High-Performance Video for Manned Spaceflight

The most recent application of the AIP architecture is the Visual Processing Unit (VPU) for the Orion Crew Exploration Vehicle. The VPU provides a reconfigurable platform for processing image algorithms driving pose estimation, optical navigation and compression/decompression. The system receives image data from a variety of sensors: star tracker, vision navigation sensor, docking camera and situational-awareness camera.

To process this volume of data takes a combination of sequential processors and FGPA-based RCC cards. Virtex-4 FPGAs implement video-processing algorithms such as feature recognition, graphical overlay, tiling and video compression. They also incorporate a MicroBlaze soft-processor core to coordinate algorithm cores and processor communication. A LEON faulttolerant processor-based single-board computer is dedicated to system coordination, error handling, RCC configuration and oversight, and interconnect control.

A mezzanine card provides the sensor interfaces, implementing LVDS links to all three FPGAs for maximum flexibility in video stream selection and mitigation schemes.

Because of the "human-critical" nature of the tasks the VPU carries out, SEAKR engineers selected Virtex-4QV spacegrade FPGAs and implemented an aggressive mitigation scheme. Combining TMR methodology and configuration memory scrubbing ensures transparent correction of control path corruptions.

In conclusion, leveraging the capabilities of Virtex FPGAs, SEAKR engineers have developed an application-independent processor for space applications and demonstrated its flexibility on several missions. The RCC serves as a key component in satellite-based image processing and communications, flexible radio communications, space-based networking and navigation for human spaceflight.

Space-grade Virtex FPGAs are COTS components that offer the performance required for demanding data-processing and communications systems. These reconfigurable FPGAs enable a flexible, scalable architecture that reduces development cost and accelerates design cycles. In addition to supporting rapid development and flexible manufacturing on the ground, Virtex FPGAs offer the ability to reconfigure on-orbit for additional, significant SWAP benefits.

Future generations of V-grade reconfigurable FPGAs promise to offer greater size, weight and power benefits by delivering higher logic capacity, greater integration of hardened IP blocks, higher performance and lower power consumption. Radiation-hardened reconfigurable Virtex FPGAs will simplify the designers' task and extend SWAP benefits further by eliminating the need to implement logic- or device-level redundancy.

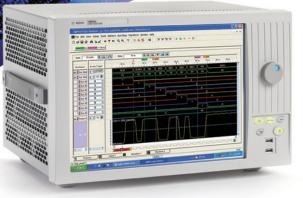

# Save days to weeks on your next FPGA debug cycle

Agilent Logic Analyzers Up to 1.2 GHz timing, 667 MHz state, and 256 M deep memory OR

Agilent Mixed Signal Oscilloscopes 4 scope channels + 16 timing channels

**Agilent FPGA Dynamic Probe**

Application software to increase visibility inside your FPGA

### Fastest FPGA Debug Available

- · Perform real-time functional and parametric debug that time-correlates internal FPGA activity with the surrounding system

- · Change internal FPGA probe points in seconds without design changes

- · Get fast serial bus decode for I<sup>2</sup>C, SPI, CAN/LIN and RS-232/UART

Start saving time now. Download FREE application information. www.agilent.com/find/fpgatools

#### XCELLENCE IN AEROSPACE & DEFENSE

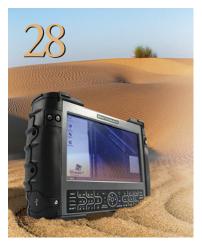

Virtex-5 Powers Reconfigurable, Rugged PC

SWITCHBACK

3

Windows

RMT's SwitchBack uses Xilinx Virtex-5 FPGA in a PC that users can customize in the field and upgrade on the fly.

by Shane Lewis Director of Technology Development RMT, Inc. slewis@ropermobile.com

The U.S. military and companies in heavy industries such as mining, transportation, warehousing, logistics and public safety all have strict requirements for personal computers. First and foremost, their PCs must be ruggedized to endure physical abuse, extreme heat and cold, and exposure to moisture, even submersion. At the same time, these rugged PCs need computing functionality that's on par with the latest commercial PCs, but surpasses them in security and global communications capabilities. Customers looking for this type of computer also require very specific peripheral features targeted at missioncritical tasks. But up until recently, these buyers have been forced to use standard, off-the-shelf PCs that often don't fully meet their needs.

This deficiency presented our design group at RMT, Inc., with the enormous challenge of designing a modular and customizable computing solution-a "common platform" that truly executed the customers' strictest requirements and met their expectations. Savvy R&D teams know the pitfalls of trying to build a "onesize-fits-all" device, which too often results in a kluge of difficult compromises. Our design team set out to defy the odds and engineer a truly adaptable computer platform that would be field-reconfigurable and customizable at the circuit level, while at the same time remaining an elegant, rugged and user-friendly system.

The result of this effort is the SwitchBack. This computer is truly different at every level, and redefines PC architecture through its innovative use of the Xilinx<sup>®</sup> Virtex<sup>®</sup>-5 FPGA. The difference between the traditional PC and the SwitchBack architecture is quite extraordinary.

#### **Traditional Open PC Architecture**

The base of any modern legacy PC is an x86 processor and associated chip set for either Linux or Windows, namely Windows XP or Vista. It's the legacy support behind this code set that has enabled it to dominate the PC world and subsequently, to constrain the embedded computer space, where operating systems and processor technologies tend to be more fragmented. If you open any desktop, laptop or tablet PC designed to run Windows XP or Vista, you will find a chip set/CPU circuit topology.

This architecture, which has been the de facto standard for all PCs, both rugged and commercial, for many years, has one fundamental limitation. Task execution must either be written for a specific processor or must be plugged into one of the many available expansion ports as external hardware. The boundaries of what can be done are closely defined around the wiring of the dedicated ASICs that make up the chip set itself.

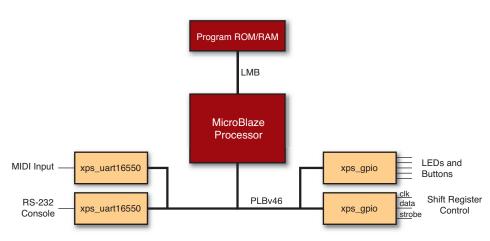

#### SwitchBack Architecture

To get a different outcome, the RMT team knew that we had to rethink this design. We crafted SwitchBack's patent-pending architecture to be both field-reconfigurable as well as compatible with Windows-based applications. The concept of field reconfiguration is widely utilized today in embedded computing, a trend that FPGAs have enabled.

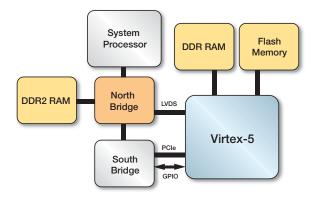

While programmable logic may play various supporting roles on some x86 PCbased motherboards, the FPGA is the hero in the SwitchBack, directing the computer's functions (Figure 1). The Virtex-5 is the primary controller of all major subsystems. From the moment the user presses the power button, the FPGA controls all peripherals, including the display itself, as well as the flow of most data. This scheme

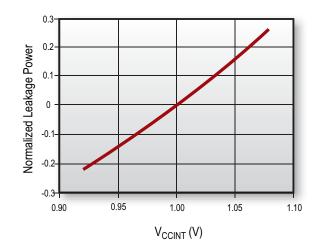

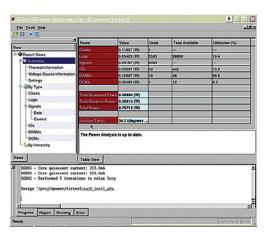

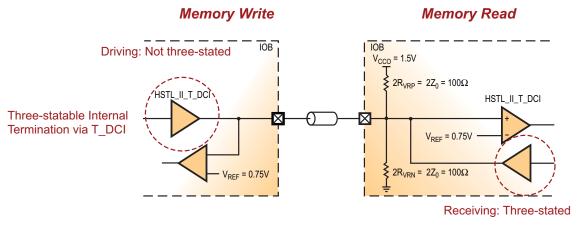

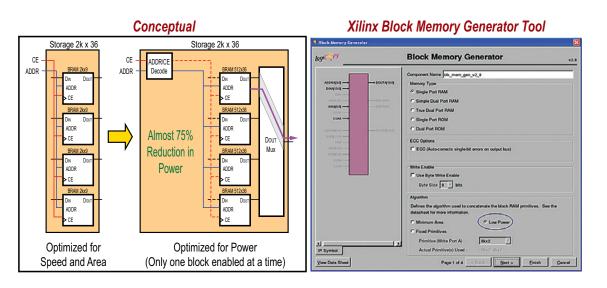

Figure 1 – The difference between a traditional PC architecture (left) and the revolutionary SwitchBack is that in the latter, the FPGA is the primary controller. This improves processing time and makes the SwitchBack reconfigurable and customizable.