XCOR SOFTWARE

SOFTWARE SOLUTIONS FOR A PROGRAMMABLE WORLD

ISSUE 2 FOURTH QUARTER 2015

Use C/C++ to Offload Image Processing to Programmable Logic

Leverage SDSoC to Accelerate AES Encryption on Zynq

SDNet Helps NTT Hatch Lagopus FPGA Reprogrammable Platform

NI, Vivado Tools Take Machine Vision from Concept to Deployment

PLDA's QuickPlay High-level Workflow Builds Efficient FPGA Apps

**EXILINX** ALL PROGRAMMABLE. www.xilinx.com/xcell

## Design it or Buy it?

Shorten your development cycle with Avnet's SoC Modules

Quick time-to-market demands are forcing you to rethink how you design, build and deploy your products. Sometimes it's faster, less costly and lower risk to incorporate an off-the-shelf solution instead of designing from the beginning. Avnet's system-on module and motherboard solutions for the Xilinx Zyng®-7000 All Programmable SoC can reduce development times by more than four months, allowing you to focus your efforts on adding differentiating features and unique capabilities.

Find out which Zynq SOM is right for you http://zedboard.org/content/design-it-or-buy-it

| PUBLISHER          | Mike Santarini<br>mike.santarini@xilinx.com<br>1-408-626-5981                   |

|--------------------|---------------------------------------------------------------------------------|

| EDITOR             | Diana Scheben                                                                   |

| ART DIRECTOR       | Scott Blair                                                                     |

| DESIGN/PRODUCTION  | Teie, Gelwicks & Assoc.<br>1-408-842-2627                                       |

| ADVERTISING SALES  | Judy Gelwicks<br>1-408-842-2627<br>xcelladsales@aol.com                         |

| INTERNATIONAL      | Melissa Zhang,<br>Asia Pacific<br>melissa.zhang@xilinx.com                      |

|                    | Christelle Moraga,<br>Europe/Middle East/Africa<br>christelle.moraga@xilinx.com |

|                    | Tomoko Suto,<br>Japan<br>tomoko@xilinx.com                                      |

| REPRINT ORDERS     | 1-408-842-2627                                                                  |

| EDITORIAL ADVISERS | Tomas Evensen<br>Lawrence Getman<br>Mark Jensen                                 |

Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124-3400 Phone: 408-559-7778 FAX: 408-879-4780 www.xilinx.com/xcell/

© 2015 Xilinx, Inc. All rights reserved. XILINX, the Xilinx Logo, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

The articles, information, and other materials included in this issue are provided solely for the convenience of our readers. Xilinx makes no warranties, express, implied, statutory, or otherwise, and accepts no liability with respect to any such articles, information, or other materials or their use, and any use thereof is solely at the risk of the user. Any person or entity using such information in any way releases and waives any claim it might have against Xilinx for any loss, damage, or expense caused thereby.

## Letter from the Publisher

#### **Xciting Times Ahead with the Zynq MPSoC**

For those of you doing embedded software development, it's imperative to know what system hardware resources are available to you to create optimized embedded systems. For those of you specializing in developing application software, knowing the nitty gritty details about the system resources isn't so important, but knowing you have silicon that can give you options for improving code performance is certainly a plus.

To this end, Xilinx<sup>®</sup> last quarter achieved a significant silicon milestone. In late September, Xilinx announced it had shipped to customers the first samples of its Zynq<sup>®</sup> UltraScale+<sup>TM</sup> MPSoC (see video), the follow-up to its award-winning Zynq-7000 All Programmable SoC. Whereas the Zynq SoC featured an ARM<sup>®</sup> dual Cortex<sup>TM</sup> A-9 processing system connected to programmable logic and on-board peripheral controllers on a single system-on-chip, the Zynq UltraScale+ MPSoC ups the processing power available on an SoC to a total of seven processors (64-bit, quad-core ARM Cortex-A53 and dual-core ARM Cortex-R5 real-time processors, and an ARM Mali<sup>TM</sup>-400 MP GPU), an H.265/264 video codec, an advanced dynamic power management unit to optimize system power efficiency, a configuration security unit, DDR4/LPDDR4 memory interface support, and loads of on-chip programmable logic.

Since the release of the Zynq SoC in 2011, the innovations that Xilinx customers have been able to develop with the device have been truly remarkable. Without delving too deeply into the silicon details, what makes the Zynq SoC device unique are the more than 3,000 connections between the processor and the on-chip programmable logic. Those connections enable the processor and functions implemented in FPGA logic to communicate far faster than would be achievable with any two-chip or even system-in-package configuration. Customers thus have been able to create systems that simply weren't possible before. And since the Zynq SoC's launch, we have seen Zynq SoC-based innovations in just about every market Xilinx serves, from wireless communications to aerospace and defense.

Many of those innovations were created by FPGA engineering teams using the Xilinx Vivado<sup>®</sup> Design Suite of hardware design tools. Earlier this year, Xilinx took a bold leap forward by introducing the C, C++ and OpenCL<sup>TM</sup>-based SDx<sup>TM</sup> development environments: SDSoC<sup>TM</sup> for Zynq SoC design, SDAccel<sup>TM</sup> for FPGA-accelerated processing and SDNet<sup>TM</sup> for software-defined networking system development. While relatively new, the SDSoC development environment is already opening up new possibilities to new users—embedded software developers—as well as traditional FPGA experts. Further opportunities for innovation arise from the ability to create a system-level representation of a system in C or C++ and then use the SDSoC environment to identify slower-running code segments and offload them to the FPGA logic for acceleration.

Now, with the combination of the SDSoC environment and the silicon foundation of the Zynq UltraScale+ MPSoC, I'm betting that we will see even more truly remarkable system innovations created by an expanding number of Xilinx users.

In this second issue of *Xcell Software Journal*, you will read how the SDSoC and SDNet environments are enabling new levels of innovation. I hope you enjoy reading the articles and are inspired to begin using the new development environments—and, of course, sharing your experiences with your peers by contributing technical articles to *Xcell Software Journal*.

— Mike Santarini Publisher

#### CONTENTS

FOURTH QUARTER 2015 ISSUE 2

## VIEWPOINT

Letter from the Publisher Xciting Times Ahead with the Zyng MPSoC...3

## COVER STORY

Use C/C++ to Offload Image Processing to Programmable Logic

6

### XCELLENCE WITH SDSOC FOR EMBEDDED DEVELOPMENT

Accelerate AES Encryption with SDSoC...16

### XCELLENCE WITH SDNET FOR SDN DEVELOPMENT

Innovating a Reprogrammable Network with SDNet...24

### XCELLENT ALLIANCE FEATURES

Delivering FPGA Vision to the Masses...30

A Novel Approach to Software-Defined FPGA Computing...38

### XTRA READING

IDE Updates and Extra Resources for Developers . . . 46

## Use C/C++ to Offload Image Processing to Programmable Logic

Heightofin

for (j=0; jeWidthOffmage,

Some Code

SDSoC lets programmers build complete hardware-software systems without sacrificing performance.

by Olivier Tremois DSP Specialist FAE Xilinx, Inc. olivier.tremois@xilinx.com

The "standard" image processing systems found today in medical, industrial and a growing number of other applications are becoming ever more advanced. In many cases, the imaging processing complexity has already exceeded the processing capabilities of PCs with GPU acceleration. Even as design teams raise their standards for image processing quality and add product features, they must meet customer demand for more-compact, mobile, battery-powered end products.

Many existing platforms are struggling to meet such complex requirements. Luckily, design teams can leverage Xilinx<sup>®</sup> Zynq<sup>®</sup>-7000 All Programmable SoCs and the new Xilinx SDSoC<sup>TM</sup> development environment to create compact, low-power, feature-rich products with advanced imaging systems using C/C++. Let's examine how to do this by using the SDSoC environment to accelerate an image pipeline processing system. I completed this project in less than a week and was able to accelerate the system example by orders of magnitude. Our batch image processing system will read images stored in an SD card and process them using different parameters for the noise level and for the shape used as a structuring element.

#### **BATCH IMAGE PROCESSING**

Our example system acquires images using a specific camera and then processes the images in batch mode. The image size can be up to 3,000 x 2,000 pixels (6 megapixels). Although the processed image is not live video, the intent is to send the images through the image pipeline as quickly as possible. The pipeline here is pretty simple: transform an RGB image into grayscale; add salt-and-pepper noise; and filter the noisy image with three filters (dilate, median and erode).

Dilation, median and erosion filters belong to the family of rank filters, which are primarily but not exclusively applied to remove impulse noise for image enhancement. These are nonlinear filters that involve absolutely no arithmetic operations and restrict their functions to data sorting and picking. Although the algorithms are not highly complex, they consume considerable processing time when they are applied to large images because of the sequential nature of the processor, which will process 1 pixel in a given time period.

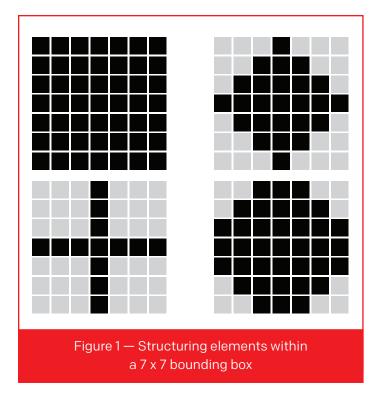

A rank filter is a nonlinear filter that computes the output image pixel by pixel. It does so by taking the neighboring pixels of the input image pixel within a specified shape called a structuring element, sorting them and picking the one that is at the pth rank. The erosion filter selects the minimum value (p = 1). Dilation selects the maximum value (p = N, where N is the number of pixels of the structuring element). Median filtering selects the median value (p = [N/2]). Classically, the structuring element is a square, a diamond or a cross (Figure 1).

Our batch image processing system will read images stored in an SD card and process them using different parameters for the noise level and for the shape used as a structuring element. The dual ARM<sup>®</sup> Cortex<sup>TM</sup>-A9 cores of a Zynq-7000 SoC running at 667 MHz will perform the computations.

#### SOFTWARE IMPLEMENTATION

As a starting point, we write the complete application in C++ so that we can estimate the performance of the computations on the Cortex-A9. The application contains a number of functions to read and write BMP images on the SD card, compute luminance, add noise and perform the

|        | #Size         | #Shape       | SW Latency |

|--------|---------------|--------------|------------|

| Test 1 | 1,920 x 1,080 | 49 (square)  | 29 s       |

| Test 2 | 1,920 x 1,080 | 25 (diamond) | 8.5 s      |

| Test 3 | 3,000 x 2,000 | 25 (diamond) | 8.5 s      |

Figure 2 — Runtime for Zynq processing system only

various filter functions. Working within the SD-SoC development environment's SDDebug configuration will enable rapid implementation on the Xilinx ZC702 evaluation platform under the Linux operating system.

To generate a truly operational executable file, we select option -O3 to turn on all compiler optimization. The shape of the structuring element is a parameter of the application such that we can apply any kind of structuring element that fits within a 7 x 7-pixel bounding box. The parameters that have an impact on the pipeline latency (Figure 2) are the size of the image (#Size) and the number of active pixels in the structuring element (#Shape). Minimizing those latencies will improve system performance. FPGAs perform incredibly well on signal processing algorithms involving numerous additions and multiplications. Our system example will show that programmable logic is good not only at brute-force computations, but also at more standard data processing.

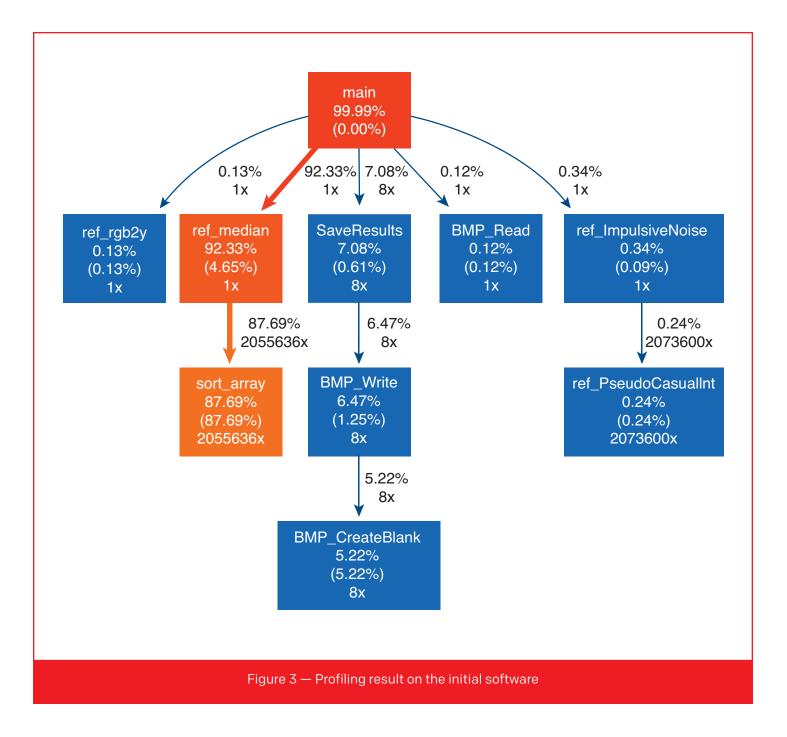

A basic profiling (Figure 3) shows that computing luminance from RGB values (0.13 percent) and adding noise to the pixel (0.34 percent) run pretty fast in software. The main contributor to total time is the median filter (92.33 percent). Other functions contributing to total time are file reads and saves.

#### **MOVING A FUNCTION TO HARDWARE**

The first goal for this acceleration is to be able to process one new sample every clock cycle. Some code rewriting and a rethinking of the interface can yield greater acceleration. Even if the clock rate of the on-chip programmable logic (PL) is much lower than that of the processing system (PS), being able to process one input pixel per clock should provide great acceleration.

The median filter is the only function that will shift to the hardware. Although the SDSoC environment makes it easy to shift functions into the PL with a simple right click in the environment's Project Explorer, it will not add any directive (except at the interface) or change a single line of code for performance purposes. Those modifications are the embedded programmer's responsibility, which explains why the initial acceleration generally will not be that dramatic.

The function specified above contains two nested loops to go through the entire image. It also contains subloops that go through the structuring element and sort all the elements. In this example, we use a standard bubble sort algorithm. Other reduced-complexity algorithms exist for microprocessor implementation, but the regularity of this one is more adapted to hardware implementation:

```

for ( i=0; i<HeightOfImage; i++)

for ( j=0; j<WidthOfImage; j++)

{

Some Code

for ( s=0; s<NumberOfStages; s++)

for ( k=0; k<HeightOfStructElem; k++)

for ( 1=0; 1<WidthOfStructElem; 1++)

{

Swap pixels if not correctly ordered

}

}

}</pre>

```

Because we want to be able to process 1 pixel of the output image per clock cycle, we must add a directive to start a pixel vector sort with every clock tick. We pipeline the second loop that goes over the columns of the image with an initiation interval (II) of 1. (The II is the number of clock cycles required before a new iteration of the loop can launch.) Using this single directive, the SDSoC environment will automatically unroll the remaining inner loops,

### The first goal for this acceleration is to be able to process one new sample every clock cycle. Some code rewriting and a rethinking of the interface can yield greater acceleration.

allowing the hardware to process all the iterations in parallel.

Image processing algorithms implemented in single-core processors are fairly easy to code because various processor features allow smooth data movement between external memory and the processor itself. Memory caches L1 and L2 will temporarily store data that may be reused later, improving data access latency.

Such a mechanism does not exist by default in FPGAs. Although this prevents us from using the same C/C++ source code to create a hardware accelerator, it is a chance for us to design a memory cache that will have the right performance and size for our application. This is a good example of an instance in which we have to change the C/C++ source code not to keep the same functionality, but to improve the performance to a level that suits our requirements. Xilinx's Vivado<sup>®</sup> High-Level Synthesis (HLS), which is the SDSoC engine that generates register transfer level (RTL) IP from C/C++ code, will generate a hardware architecture that is adapted to our code, taking into account our directives. That's why line buffers and analysis windows are not automatically generated when analyzing the image processing code; Vivado HLS adheres to the code as written, which prevents the tool from hiding optimizations that could be done without the developer's consent.

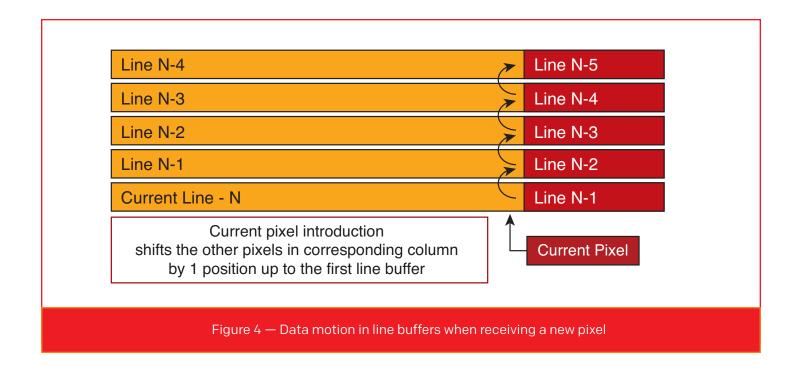

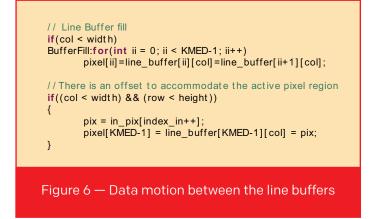

Designers who are familiar with image processing in hardware know all about line buffers and analysis windows. In order to avoid multiple reads of the same pixel from the external memory, pixels are temporarily stored in internal memory (block RAM) and then overwritten when they are no longer useful for the remaining execution. The block RAMs have two ports that can be used as memory reads, memory writes or both. When the accelerator accepts the pixel corresponding to line L and column C, all the pixels corresponding to column C and line (L-1 ... L-6) are read from the line buffer and rewritten to another location, as Figure 4 illustrates. In order to

achieve this 1-pixel/clock objective, all data movement must be performed with a throughput of one clock cycle.

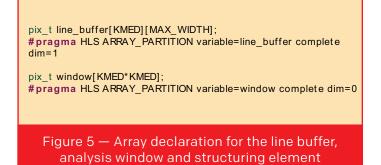

Moreover, all the pixels belonging to the pixel neighborhood and the structuring element must likewise be accessed in one clock cycle. That is why we also define an analysis window that contains the specific pixels in question (and which varies from pixel to pixel). In the SDSoC environment and VHLS, the code is not timed in any way; the tool will parallelize anything that can be parallelized with respect to the resource used and our directives. In our sample batch image processing system code, we add the line buffer and analysis window to the code just by declaring two arrays with the right

partitioning directives (Figure 5). We then describe data motion as read/write accesses to those arrays (Figure 6).

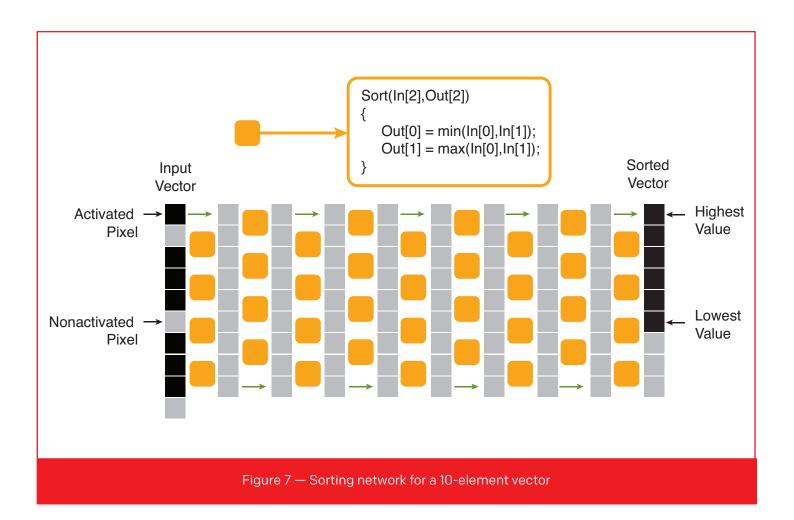

Because it relies on data access in an array, the pixel-value sorting procedure can be complex to implement in the hardware architecture. The C code for software implementation takes the vector of the pixel that has been validated through the structuring element and sorts it using a standard bubble sort. More-efficient algorithms exist but provide a significant benefit only on larger vectors. The complexity of this algorithm is proportional to the square of the number of pixels of the structuring element—up to  $(7 \times 7)^2$  for our sample design.

In hardware, the architecture must be dimensioned for the worst case. If we want to achieve our 1-pixel/clock goal, we need to implement a very regular structure. To this aim, we specify that the input vector will always have the maximum size  $(7 \times 7)$  and that all nonvalidated pixels will

have the value 0 so that they will be at the bottom of the sorted vector. We also dimension the number of stages for the worst case, even if the number of stages could be lower for a structuring element with fewer active pixels. Parallelization of the different stages can occur only if the same vector is not reused at each stage. The result is an array into which the initial vector enters at column index 0 and exits at column index 7 x 7 = 49 (Figures 7 and 8).

#### SDSOC SYSTEM COMPILER

SDSoC is not a simple full-system compiler. It performs an extensive code analysis in order to decide what kind of data mover would best suit the functions that are required to be in hardware, and to which port to connect the data mover. For each parameter of the function, we must determine whether it is best to use an ARM<sup>®</sup> AMBA<sup>®</sup> AXI4-Lite, AXI4-Full memory-mapped or AXI4-Stream data mover. SDSoC is not a simple full-system compiler. It performs an extensive code analysis in order to decide what kind of data mover would best suit the functions that are required to be in hardware, and to which port to connect the data mover.

```

void sorting_network(pix t window[KMED*KMED],mask t shape[KMED*KMED],

kmed2 t NShape,kmed2_t CompNShape,

pix_t *pixmin,pix_t *pixmed,pix_t *pixmax)

static const int N = KMED*KMED;

pix t tmin,tmax,t0,t1;

static pix_t z[N][N+1]; // Array that contains the sorting network

#pragma HLS ARRAY PARTITION variable=z complete dim=0

unsigned int i, k, stage;

// Initialization of the first row of the network

// pixels that do not belong to the mask are set to 0

L1:for (i=0; i<N; i++)

if(shape[i]) z[i][0] = window[i];

else z[i][0] = 0;

//sorting_network: This description is correct for KMED odd

L2:for (stage = 1; stage <= N; stage++)

k = (stage \& 1)^{1}; // stage odd -> k=0 stage even -> k=1

L3:for (i = k; i<N-1; i=i+2)

{

t0 = z[(i)][stage-1];

t1 = z[(i+1)][stage-1];

tmin = MIN(t0,t1);

tmax = MAX(t0,t1);

z[(i )][stage] = tmin;

z[(i+1)][stage] = tmax;

// Copy the value that has not been sorted to the next stage

if(k==0) z[N-1][stage] = z[N-1][stage-1];

else z[0][stage] = z[0][stage-1];

*pixmin = z[CompNShape][N];

*pixmed = z[CompNShape+NShape/2][N];

*pixmax = z[N-1][N];

return;

```

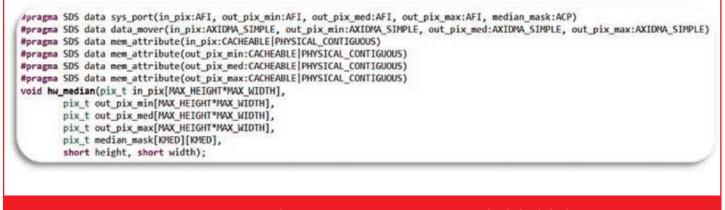

Figure 9 — Directives in the SDSoC environment to override default behavior

We also have to determine which connector to use: the AXI4 High Performance (HP), General Purpose (GP) or Accelerator Coherency Port (ACP), or even ports from other accelerators, either built from within the SDSoC environment or contained in the board support package (BSP).

The SDSoC environment will then create a design, adding all necessary IP to make a fully functional

system—a direct memory access (DMA) for AXI4 Stream data movers, for example—and will modify the C source code (instead of the initial C++ code) in order to call the hardware. In our case, the interface is pretty simple: Two input arrays and three output arrays will be accessed through AXI4-Stream and DMAs, and a few scalars will be set through AXI4-Lite. We don't have to think about setting the DMAs or look at the address at which the scalar registers are accessible; the SDSoC environment manages everything automatically, under the hood.

When I built the sample system, I first verified that the source code was Vivado HLS compliant and then added the VHLS directives. Using specific SDSoC directives, I specified that the data would be stored contiguously in the physical space (with memory allocated using the function sds\_alloc) and that I wanted a DMA to access it (Figure 9).

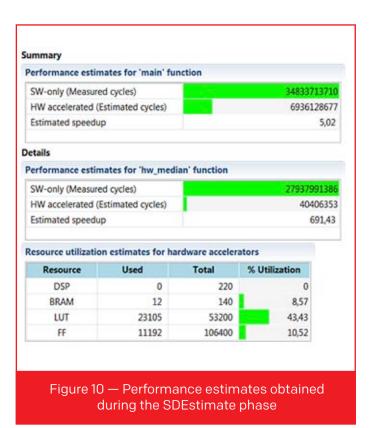

I then switched the build configuration to SDEstimate in order to have a first rough estimate of the acceleration that was achievable (Figure 10). I did not have to wait a long time for this step, because at this point no hardware had been built.

The SDSoC environment computes the speedup estimate from the processor runtime (computed using the hardware-adapted code, which is slower than the original, processor-adapted code, and with compiler optimization set to –O0) and the number of clock cycles (computed by VHLS as the latency of the hardware accelerator). This latency is the maximum latency of the hardware accelerator, so this estimation should be taken for what it is—a rough At this stage, we are able to have an exact value of the acceleration obtained using the hardware accelerators, taking into account all the data transfers to and from DDR.

|        | #Size         | #Shape          | Pure SW<br>Latency | SW + HW<br>Latency | Acceleration |

|--------|---------------|-----------------|--------------------|--------------------|--------------|

| Test 1 | 1,920 x 1,080 | 49<br>(square)  | 29.2 s             | 154.8 ms           | 189x         |

| Test 2 | 1,920 x 1,080 | 25<br>(diamond) | 8.6 s              | 154.7 ms           | 56x          |

| Test 3 | 3,000 x 2,000 | 25<br>(diamond) | 25 s               | 447 ms             | 56x          |

Figure 11 — Runtime for Zynq Processing System with accelerated function in Programmable Logic

estimate. This acceleration is almost 700x for the hardware accelerator itself. There are many file accesses that take time at the "main" level; that's why the overall acceleration is "only" 5x. In practice, we can choose the top-level function at which the global acceleration is computed so that we can obtain a more meaningful acceleration value.

The final step of the flow is to build the entire system. In this phase, all the accelerators are built and connected to the processor. The C++ source code is then modified in order to start and control these accelerators (instead of calling the original C function). At this stage, we are able to have an exact value of the acceleration obtained using the hardware accelerators, taking into account all the data transfers to and from DDR. This acceleration value also takes into account the time it takes to flush the cache, as our data is in a cacheable part of the memory.

The time taken by the hardware accelerator is proportional to the size of the image and not to the size of the structuring element. That's why the higher the number of active pixels in the structuring element, the higher the acceleration ratio will be. The latency referred to in Figure 11 is that of the full image pipeline, containing the software and hardware elements.

When I undertook this project, building the software application proved to be the longest phase. From there, it took less than 2 hours to modify the code so that I had fully compliant Vivado HLS code with the right directives in place to optimize the throughput. Given the size of the hardware part of this design (half the lookup table of the chip), the last stage—synthesis, place and route, bitstream, SD card—took more than 2 hours to complete.

The SDSoC environment's integrated tools for system-level profiling, automated software acceleration in programmable logic and full-system-optimizing compilation—automatically generating the right connectivity to minimize memory access bottlenecks—allowed me to go through this example project in less than a week.

That short time frame wouldn't have been possible using a standard RTL flow for the creation of the accelerator and my own programming abilities to take advantage of the different drivers to modify the C code. ■

# Accelerate AES Encryption with SDSoC

**by Adam Taylor** Chief Engineer e2v *aptaylor@theiet.org*

## Describe the AES256 crypto algorithm in C, then speed performance in hardware.

he Advanced Encryption Standard (AES) has become an increasingly popular cryptographic specification in many applications, including those within embedded systems. Since the National Institute of Standards and Technology (NIST) selected the specification as a standard in 2002,

developers of processor, microcontroller, FPGA and SoC applications have turned to AES to secure data entering, leaving and residing within their systems. The algorithm is described very efficiently at a higher abstraction level, as is used in traditional software development; but because of the operations involved, it is most efficiently implemented in an FPGA. Indeed, developers can even get some operations "for free" in the routing.

For those reasons, AES is an excellent example of how developers can benefit from the Xilinx<sup>®</sup> SDSoC<sup>™</sup> development environment by describing the algorithm in C and then accelerating the implementation in hardware. In this article we will do just that, first gaining familiarity with the AES algorithm and then implementing AES256 (256-bit key length) on the processing system (PS) side of a Xilinx Zynq<sup>®</sup>-7000 All Programmable SoC to establish a baseline of software performance before accelerating it in the on-chip programmable logic (PL). To gain a thorough understanding of the benefits to be gained, we will perform the steps in all three operating systems the SDSoC environment supports: Linux, FreeRTOS and BareMetal.

#### **THE ALGORITHM**

AES is a symmetric block cipher that can be used with varying key lengths of 128, 192 and 256 bits. The key length determines the number of processing steps required to encrypt or decrypt data. As their name implies, block cipher algorithms work on blocks of data. The AES algorithm operates on a fixed block size of 16 bytes at a time. Thus, if we wish to encrypt fewer than 16 bytes, we must pad out the unused bytes. Because AES is a symmetric cipher, the same actions and key are used to encrypt and decrypt information. In contrast, asymmetric algorithms such as RSA use different keys for data encryption and decryption.

Each of the four stages in the AES algorithm is applied to what is called the state. The combination of the four AES stages is called a round. The number of rounds required depends on the key length.

Quite simply, the AES state starts out as the 16 bytes we wish to encrypt. Each new step updates the state. Before processing the state, we need to format the input byte string correctly into the initial state as a  $4 \ge 4$ matrix (Figure 1).

Now that we have rearranged the initial 16 bytes into the initial state as a  $4 \ge 4$  grid, we can explore how each step manipulates its input state.

AddRoundKey: This is the only step that uses the encryption key. As we have already noted, the number of encryption algorithm rounds required depends on the key size (128, 192 or 256 bits). The encryption key must undergo key expansion to ensure that the bytes in the key are not reused during each round before use. Not surprisingly, the expanded key length is different for each key size. The expanded key size will be:

#### Expanded Key Size (bytes) = 16 \* (Rounds + 1)

The operation within this step is simple. The input state bytes are exclusive-ORed with 16 bytes of the expanded key. Each round uses a different section of the expanded key; round 0 uses bytes 0 to 15, round 1 uses bytes 16 to 31 and so on. For each round, byte 1 of the state is exclusive-ORed with the least significant byte of the expanded key, byte 2 is exclusive-ORed with least significant byte + 1 and so on.

**SubBytes:** This step uses byte substitution to swap out state values with another value. The values within the substitution box are predefined and have been designed to have low correlation between input bits and output bits. The substitution box (S-box) is a 16 x 16 matrix. We use the

| B1            | B2                         | B3 | B4   | B5       | B6       | B7       | B8      | B9      | B10     | B11     | B12     | B13     | B14 | B15 | B16 |

|---------------|----------------------------|----|------|----------|----------|----------|---------|---------|---------|---------|---------|---------|-----|-----|-----|

| 16-byte Input |                            |    |      |          |          |          |         |         |         |         |         |         |     |     |     |

|               |                            |    |      |          | В        | 1        | B5      | B9      | B1      | 3       |         |         |     |     |     |

|               |                            |    |      |          | В        | 2        | B6      | B10     | B1      | 4       |         |         |     |     |     |

|               |                            |    |      |          | В        | 3        | B7      | B11     | B1      | 5       |         |         |     |     |     |

|               |                            |    |      |          | В        | 4        | B8      | B12     | B1      | 6       |         |         |     |     |     |

|               | Initial State – 4 x 4 Grid |    |      |          |          |          |         |         |         |         |         |         |     |     |     |

|               |                            |    | Figu | e 1 — II | nitial s | tate tra | anslati | on of t | he 16 b | ytes ir | nto a 4 | x 4 gri | d   |     |     |

upper and lower nibbles of the byte being substituted to index into the substitution table. For example, using the S-box encryption in Figure 2, if the first initial state byte is 0 x 69, then the substitution value 0 x F9 will replace it. The upper nibble of the state byte selects the row in the substitution box; the lower nibble selects

| 0<br>1<br>2<br>3<br>4<br>5<br>6      | 0<br>63<br>CA<br>B7<br>04<br>09<br>53<br>D0  | 1<br>7C<br>82<br>FD<br>C7<br>83<br>D1<br>EF  | 2<br>77<br>C9<br>93<br>23<br>2C<br>00<br>AA  | 3<br>7B<br>7D<br>26<br>C3<br>1A<br>ED<br>FB  | <b>4</b><br>F2<br>FA<br>36<br>18<br>1B<br>20<br>43 | 5<br>6B<br>59<br>3F<br>96<br>6E<br>FC<br>4D  | 6<br>6F<br>47<br>F7<br>05<br>5A<br>B1<br>33  | 7<br>C5<br>F0<br>CC<br>9A<br>A0<br>5B<br>85  | 8<br>30<br>AD<br>34<br>07<br>52<br>6A<br>45  | 9<br>01<br>D4<br>A5<br>12<br>3B<br>CB<br>F9  | A<br>67<br>A2<br>E5<br>80<br>D6<br>BE<br>02  | <b>B</b><br>2B<br>AF<br>F1<br>E2<br>B3<br>39<br>7F | <b>C</b><br>FE<br>9C<br>71<br>EB<br>29<br>4A<br>50 | D7<br>A4<br>D8<br>27<br>E3<br>4C<br>3C       | <b>E</b><br>AB<br>72<br>31<br>B2<br>2F<br>58<br>9F | <b>F</b><br>76<br>C0<br>15<br>75<br>84<br>CF<br>A8 |

|--------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------|----------------------------------------------------|----------------------------------------------------|

| 7<br>8<br>9<br>A<br>B<br>C<br>D<br>E | 51<br>CD<br>60<br>E0<br>E7<br>BA<br>70<br>E1 | A3<br>0C<br>81<br>32<br>CB<br>78<br>3E<br>F8 | 40<br>13<br>4F<br>3A<br>37<br>25<br>B5<br>98 | 8F<br>EC<br>DC<br>0A<br>6D<br>2E<br>66<br>11 | 92<br>5F<br>22<br>49<br>8D<br>1C<br>48<br>69       | 9D<br>97<br>2A<br>06<br>D5<br>A6<br>03<br>D9 | 38<br>44<br>90<br>24<br>4E<br>B4<br>F6<br>8E | F5<br>17<br>88<br>5C<br>A9<br>C6<br>0E<br>94 | BC<br>C4<br>46<br>C2<br>6C<br>E8<br>61<br>9B | B6<br>A7<br>EE<br>D3<br>56<br>DD<br>35<br>1E | DA<br>7E<br>B8<br>AC<br>F4<br>74<br>57<br>87 | 21<br>3D<br>14<br>62<br>EA<br>1F<br>B9<br>E9       | 10<br>64<br>DE<br>91<br>65<br>4B<br>86<br>CE       | FF<br>5D<br>5E<br>95<br>7A<br>BD<br>C1<br>55 | F3<br>19<br>0B<br>E4<br>AE<br>8B<br>1D<br>28       | D2<br>73<br>DB<br>79<br>08<br>8A<br>9E<br>DF       |

| F                                    | 8C                                           | A1                                           | 98<br>89                                     | 0D                                           | BF                                                 | E6                                           | 42                                           | 68                                           | 41                                           | 99<br>yptio                                  | 2D                                           | 0F                                                 | B0                                                 | 54                                           | BB                                                 | 16                                                 |

| 0<br>1                               | <b>0</b><br>52<br>7C                         | <b>1</b><br>09<br>E3                         | <b>2</b><br>6A<br>39                         | <b>3</b><br>D5<br>82                         | <b>4</b><br>30<br>9B                               | <b>5</b><br>36<br>2F                         | <b>6</b><br>A5<br>FF                         | <b>7</b><br>38<br>87                         | <b>8</b><br>BF<br>34                         | <b>9</b><br>40<br>8E                         | <b>A</b><br>A3<br>43                         | <b>B</b><br>9E<br>44                               | <b>C</b><br>81<br>C4                               | D<br>F3<br>DE                                | <b>E</b><br>D7<br>E9                               | F<br>FB<br>CB                                      |

| 1<br>2<br>3<br>4<br>5<br>6<br>7      | 52<br>7C<br>54<br>08<br>72<br>6C<br>90<br>D0 | 09<br>E3<br>7B<br>2E<br>F8<br>70<br>D8<br>2C | 6A<br>39<br>94<br>A1<br>F6<br>48<br>AB<br>1E | D5<br>82<br>32<br>66<br>64<br>50<br>00<br>8F | 30<br>9B<br>A6<br>28<br>86<br>FD<br>8C<br>CA       | 36<br>2F<br>C2<br>D9<br>68<br>ED<br>BC<br>3F | A5<br>FF<br>23<br>24<br>98<br>B9<br>D3<br>0F | 38<br>87<br>3D<br>B2<br>16<br>DA<br>0A<br>02 | BF<br>34<br>EE<br>76<br>D4<br>5E<br>F7<br>C1 | 40<br>8E<br>4C<br>5B<br>A4<br>15<br>E4<br>AF | A3<br>43<br>95<br>A2<br>5C<br>46<br>58<br>BD | 9E<br>44<br>0B<br>49<br>CC<br>57<br>05<br>03       | 81<br>C4<br>42<br>6D<br>5D<br>A7<br>B8<br>01       | F3<br>DE<br>FA<br>8B<br>65<br>8D<br>B3<br>13 | D7<br>E9<br>23<br>D1<br>B6<br>9D<br>45<br>8A       | FB<br>CB<br>4E<br>25<br>92<br>84<br>06<br>6B       |

| 1<br>2<br>3<br>4<br>5<br>6           | 52<br>7C<br>54<br>08<br>72<br>6C<br>90       | 09<br>E3<br>7B<br>2E<br>F8<br>70<br>D8       | 6A<br>39<br>94<br>A1<br>F6<br>48<br>AB       | D5<br>82<br>32<br>66<br>64<br>50<br>00       | 30<br>9B<br>A6<br>28<br>86<br>FD<br>8C             | 36<br>2F<br>C2<br>D9<br>68<br>ED<br>BC       | A5<br>FF<br>23<br>24<br>98<br>B9<br>D3       | 38<br>87<br>3D<br>B2<br>16<br>DA<br>0A       | BF<br>34<br>EE<br>76<br>D4<br>5E<br>F7       | 40<br>8E<br>4C<br>5B<br>A4<br>15<br>E4       | A3<br>43<br>95<br>A2<br>5C<br>46<br>58       | 9E<br>44<br>0B<br>49<br>CC<br>57<br>05             | 81<br>C4<br>42<br>6D<br>5D<br>A7<br>B8             | F3<br>DE<br>FA<br>8B<br>65<br>8D<br>B3       | D7<br>E9<br>23<br>D1<br>B6<br>9D<br>45             | FB<br>CB<br>4E<br>25<br>92<br>84<br>06             |

Figure 2 — AES S-box contents

the column. Note in Figure 2 that there are separate substitution boxes for encryption and decryption and that their content differs.

**ShiftRows:** This step rearranges the input state matrix by performing a circular byte shift for each row. We rotate each row right by a different factor (Figure 3). We leave row 1 unchanged. We rotate row 2 by 1 byte, row 3 by 2 bytes and row 4 by 3 bytes. When we decrypt, we perform the same operations, but we rotate left instead of right.

**MixColumns:** This is the most complicated step within a round, requiring 16 multiplications and 12 exclusive-OR operations. The operations are performed column by column on the input state matrix, which is multiplied against a fixed matrix to create a new state column (Figure 4). Each entry in the column is multiplied by a row in the matrix. The results of each multiplication are XORed together to form the new state value. The first column and row to be multiplied are highlighted in Figure 4.

Here are the MixColumns equations for the first column:

$\begin{array}{l} B1' = (B1 * 2) \; XOR \; (B2 * 3) \; XOR \; (B3 * 1) \; XOR \; (B4 * 1) \\ B2' = (B1 * 1) \; XOR \; (B2 * 2) \; XOR \; (B3 * 3) \; XOR \; (B4 * 1) \\ B3' = (B1 * 1) \; XOR \; (B2 * 1) \; XOR \; (B3 * 2) \; XOR \; (B4 * 3) \\ B4' = (B1 * 3) \; XOR \; (B2 * 1) \; XOR \; (B3 * 1) \; XOR \; (B4 * 2) \end{array}$

This process is then repeated against the same multiplication matrix for the next column in the input state until all of the input state columns have been addressed.

Now that we understand the detailed steps needed for the AES encryption and decryption algorithms, we need to know the order in which to apply the steps in a round and whether we must apply all of AES is described efficiently at a higher abstraction level, as in traditional software development, but is most efficiently implemented in an FPGA. Developers can even get some operations "for free" in the routing.

the steps for each round. Each AES encryption round comprises all four steps, in the following order:

- 1. SubBytes;

- 2. ShiftRows;

- 3. MixColumns (for rounds 1 to N 1 only);

- 4. AddRoundKey (using the expanded key).

Of course, we need to be able to reverse the process and turn the unreadable cipher text back into plain text so that the encrypted information will be useful. To do so, we order the steps as follows:

- 1. Invert ShiftRows;

- 2. Invert SubBytes;

- 3. AddRoundKey (using the expanded key);

- 4. Invert MixColumns (for rounds 1 to N 1 only).

Before executing the first round of encryption, we need to perform an initial AddRoundKey operation for both encryption and decryption.

| _ |    |    |     |     |

|---|----|----|-----|-----|

|   | B1 | B5 | B9  | B13 |

|   | B2 | B6 | B10 | B14 |

|   | B3 | B7 | B11 | B15 |

|   | B4 | B8 | B12 | B16 |

ShiftRows Input State

| B1  | B5  | B9  | B13 |

|-----|-----|-----|-----|

| B6  | B10 | B14 | B2  |

| B11 | B15 | B3  | B7  |

| B16 | B4  | B8  | B12 |

**Resultant Output State**

Figure 3 — ShiftRows operation

| <mark>B1</mark> | B5 | B9  | B13 |

|-----------------|----|-----|-----|

| B2              | B6 | B10 | B14 |

| B3              | B7 | B11 | B15 |

| <mark>B4</mark> | B8 | B12 | B16 |

Input State First Column to be Multiplied

| 2 | 3 | 1 | 1 |

|---|---|---|---|

| 1 | 2 | 3 | 1 |

| 1 | 1 | 2 | 3 |

| 3 | 1 | 1 | 2 |

**Constant Multiplication Matrix**

| Е | В | D | 9 |

|---|---|---|---|

| 9 | Е | В | D |

| D | 9 | Е | В |

| В | D | 9 | E |

**Decryption Constant Multiplication Matrix**

Figure 4 — MixColumns function for encryption and decryption

Let's look at the algorithm we must use for expanding the key so that we provide sufficient key bits for the number of AddRoundKey steps to be performed (Figure 5). Key sizes of 16, 24 or 32 bytes will respectively require 44, 52, or 60 rounds for key expansion. The first bytes of the expanded key are equal to the initial key. This means that for our AES256 example, the first 32 bytes of the expanded key are the key itself. Key expansion generates the 32 additional bits for the expanded key in each iteration.

The following are the key expansion steps.

**RotateWord:** Similar to ShiftRows, this step reorganizes a 32-bit word such that the most significant byte becomes the least significant byte.

## The first bytes of the expanded key are equal to the initial key. This means that for our AES256 example, the first 32 bytes of the expanded key are the key itself.

**SubWord:** This step uses the same substitution box used to make byte substitutions in the encryption.

**rcon:** This stage performs the exponentiation of 2 to a user-defined value. As in the MixColumns stage, rcon is performed over the Galois field (28); therefore it is common to use a precalculated lookup table for this step.

**EK:** This returns 4 bytes from the expanded key.

K: Like EK, this returns 4 bytes from the key.

How will we know that we have correctly implemented the encryption and key expansion algorithms? The NIST specification for AES helpfully contains a number of worked examples that we can use for checking our own implementations.

#### **CREATING THE CODE**

To ensure we can accelerate the encryption part of the AES code within the PL side of the Zynq SoC, we must develop the code from day one with this objective in mind (see the coding rules <u>here</u>). The first thing to consider is the architecture of the algorithm; we need to segment it properly. AES lends itself well to this approach because we can write functions for each of the stages and then call them as required. We must also write the function to be accelerated within its own file. Our software architecture will include the following.

**main.c:** This file contains the key expansion algorithm, the encryption key and the plain-text input, along with the call to the AES encryption function.

```

KeyExpansion(byte key[4*Nk], word w[Nb*(Nr+1)], Nk)

begin

word temp

i = 0

while (i < Nk)

w[i] = word(key[4*i], key[4*i+1], key[4*i+2], key[4*i+3])

i = i+1

end while

i = Nk

while (i < Nb * (Nr+1))

temp = w[i-1]

if (i mod Nk = 0)

temp = SubWord(RotWord(temp)) xor Rcon[i/Nk]

else if (Nk > 6 \text{ and } i \mod Nk = 4)

temp = SubWord(temp)

end if

w[i] = w[i-Nk] xor temp

i = i + 1

end while

end

```

```

void aes_enc(uint8_t state[4][4],uint8_t cipher[4][4],uint8_t ekey[240])

{

uint8 t iteration = 0;

//uint8 t x,y;

uint8 t sub[4][4];

uint8 t shift[4][4];

uint8_t mis[4][4];

uint8_t round[4][4];

addroundkey(state,Ø,sub,ekey);

loop main : for(iteration = 1; iteration < nr; iteration++)</pre>

{

subbytes(sub,shift);

shift row enc(shift,mix);

mixcolumn(mix,round);

addroundkey(round,iteration,sub,ekey);

}

subbytes(sub,shift);

shift_row_enc(shift,round);

addroundkey(round, nr, cipher, ekey);

}

```

**aes\_enc.c:** This file performs the encryption. We will code each of the stages as its own function so that it can be called as required for the AES round. To ensure the design is common to those implemented on processors, we use lookup tables for the mixed step's multiplications.

**aes\_enc.h:** This file houses the definition of the aes\_function and the parameters used to determine the size (e.g., mk, nb and nr).

**sbox.h:** This includes the substitution box used for the substitute bytes, the lookup table for the rcon function that performs key expansion, and the multiplication lookup tables for the MixColumns multiplications.

Within this structure, we can select the AES encryption function (Figure 6) as the one we wish to accelerate simply by right clicking on the function and selecting Toggle HW/SW.

To ensure that we are able to determine the baseline performance and the savings we get from the accelerating the function, we must be able to time the execution of the function. To do this, we'll use sds\_clock\_counter in sds\_lib.h.

After I had written the source code (available on the <u>github</u>), I recorded a time of 36,662 processor cycles when executing the AES algorithm in software running on a single ARM<sup>®</sup> Cortex<sup>TM</sup>-A9 processor core in the Zynq SoC.

#### **OPTIMIZATION FOR ACCELERATION**

Accelerating the AES algorithm is slightly more complicated than the matrix multiplication algorithm we examined in the <u>previous issue</u>. This is because the main loop of the AES algorithm consists of interdependent stages.

I accelerated the AES algorithm by examining the loops to see where I could unroll them, optimizing the memory bandwidth, selecting the correct frequency for the data motion clock frequency and selecting the correct frequency for the hardware functions.

The main loop of the AES encryption function comprises the functions that perform each AES step. Each function in the AES algorithm must be completed and the result computed before the next function can run. This interdependency requires us to focus our efforts

| Data Motion Network |          |              |           |                      |         |                         |

|---------------------|----------|--------------|-----------|----------------------|---------|-------------------------|

| Accelerator         | Argument | IP Port      | Direction | Declared Size(bytes) | Pragmas | Connection              |

| aes_enc_0           | state    | state_PORTA  | IN        | 16*1                 |         | S_AXI_ACP:AXIDMA_SIMPLE |

|                     | cipher   | cipher_PORTA | OUT       | 16*1                 |         | S_AXI_ACP:AXIDMA_SIMPLE |

|                     | ekey     | ekey_PORTA   | IN        | 240*1                |         | S_AXI_ACP:AXIDMA_SIMPLE |

Figure 7 — The data motion network between the PS and PL

on the AES steps created as separate functions. There is plenty of potential for optimization within these steps.

We can pipeline the AddRoundKey, SubBytes and MixColumns steps for increased performance. Within these functions, we execute the HLS Pipeline command by putting pragmas within the first loop. We should unroll the inner loop. Several of these functions read from lookup tables normally built from block RAM. We need to increase the memory bandwidth, so for this example I have specified the pragma parameter "complete," which implements the memory contents as discrete registers as opposed to BRAM.

The ability to transfer the data between the PS and the PL on the Zynq SoC is also of key importance in boosting performance. My first step was to set the data motion clock network at its highest possible clock frequency: 200 MHz. My second approach was to ensure that direct memory access was used for data transfer between the PS and PL. To do this, I had to rewrite the interface slightly and use the sds\_alloc function to ensure that the data was contiguous in memory, as DMA transfer requires (Figure 7).

My third and final optimization step was to set the hardware function's clock rate at the highest frequency supported for this application: 166.67 MHz.

## RESULTS ON THE SUPPORTED OPERATING SYSTEMS

When I finally put these all together and built the example, the PL-accelerated AES code ran on Linux in 16,544 processor clock cycles, or 45 percent (16,544 / 36,662) of the cycles needed when running the AES code in software alone. That's a massive 55 percent reduction in execution time for a fairly complex and interdependent algorithm.

Of course, we can select the BareMetal or FreeRTOS operating system within the SDSoC environment as well. Creating BareMetal and FreeRTOS projects and reusing the code allows a comparison of performance among the three supported operating systems. For a given project, the OS selection will depend on the mission requirements, performance budgets and response times.

Figure 8 reveals the three operating systems' performance in the Zynq SoC's PS and PL (Figure 8).

It is not surprising that FreeRTOS and BareMetal provide similar reductions, as both are much simpler implementations than the full Linux OS.

As our results show, using the SDSoC development environment to accelerate AES encryption provides a real performance improvement and is easy to achieve without in-depth FPGA design experience.

| Operating System | PS Only | PS with PL Acceleration | Reduction |

|------------------|---------|-------------------------|-----------|

| BareMetal        | 28574   | 7102                    | 75%       |

| FreeRTOS         | 28368   | 7104                    | 75%       |

| Linux            | 36662   | 16544                   | 54.8%     |

Figure 8 — OS performance in the Zynq PS and PL. FreeRTOS and BareMetal provide similar reductions.

## create something different

## Zynq<sup>®</sup>. Wi-Fi<sup>®</sup>. Bluetooth<sup>®</sup>. <sup>\$</sup>55. Any questions?

# order yours today at **snickerdoodle.io**

© krtkl inc. 2015. All rights reserved. krtkl is a registered trademark of krtkl inc. Zynq is a registered trademark of Xilinx, Inc. Wi-Fi is a registered trademark of Wi-Fi Alliance. Bluetooth is a registered trademark of Bluetooth SIG.

## Innovating a Reprogrammable Network with SDNet

by Koji Yamazaki Researcher NTT Labs yamazaki.k@lab.ntt.co.jp

**Yoshihiro Nakajima** Researcher NTT Labs

**Takahiro Hatano** Researcher NTT Labs

**Hirokazu Takahashi** Researcher NTT Labs

**Akihiko Miyazaki** Researcher NTT Labs

**Katsuhiro Shimano** Researcher NTT Labs Lagopus FPGA maximizes SDN/ NFV capability for telecom and the cloud.

ippon Telegraph and Telephone Corp (NTT) is the holding company for a global telecommunications group that formulates management strategies and promotes research and development. We are researchers in NTT's R&D division and are

leading two innovative projects for software-defined networking (SDN) and network function virtualization (NFV). For one project, we have developed a high-performance software SDN/OpenFlow switch called Lagopus [1], which we believe to be the best OpenFlow 1.3-compliant switch to have been released to date as open-source software. For our second project, we have developed a software-packet-processing-aware, 40-Gbit/second (Gbps) FPGA network interface card (NIC) called Lagopus FPGA.

Our early adoption of the Xilinx<sup>®</sup> SDNet<sup>™</sup> Software Defined Specification Environment for Networking was key to our ability to develop these technologies. Here's how we used SDNet to meet our goals for the projects.

#### LAGOPUS FPGA FOR SDN/NFV EXCELLENCE

Cloud service providers and network service operators are turning to SDN as a key enabling technology for automated provisioning systems. NFV has a critical role in letting telecom operators reduce capex and opex by changing network systems from proprietary-hardware-based equipment to commodity-hardware-based systems that leverage PC servers, merchant silicon-based switches and software appliances. Many cloud service providers and telecom operators will deploy SDN and NFV for their next-generation commercial networks.

NTT Group is a leader in SDN and NFV in both the commercial-services and research spheres. NTT has

launched an advanced SDN/NFV-related reearch endeavor called the O3 Project with funding from Japan's Ministry of Internal Affairs and Communications. Lagopus is major deliverable of the O3 Project to achieve high-performance software-packet processing and flexible flow control using the Open Networking Foundation's OpenFlow 1.3 protocol with commodity Intel x86 servers and a commodity NIC. The key benefits with Lagopus are high-performance software-packet processing at more than 10 Gbps on commodity servers; elastic network flow control for up to 1 million flow entries; and a scalable flow dispatcher for NFV applications such as virtual Provider Edge (vPE), virtual Customer Premises Equipment (vCPE) and virtual Evolved Packet Core (vEPC) frameworks.

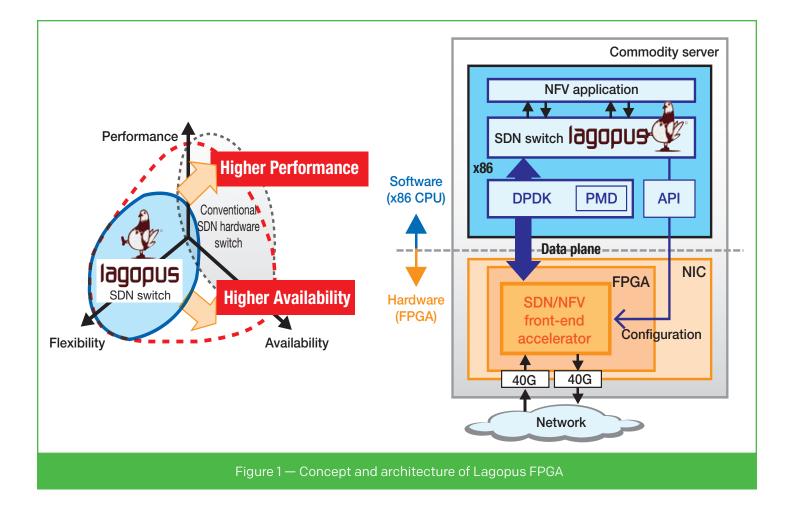

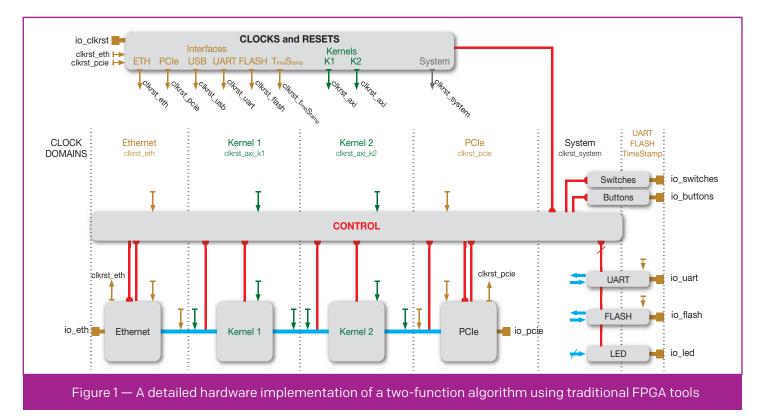

The Lagopus FPGA project aims to explore 40/100-Gbps-capable, high-performance packet processing with flexible partitioning between software and hardware-accelerated functions on an FPGA running on commodity servers. Figure 1 shows the concept and architecture of Lagopus FPGA. The

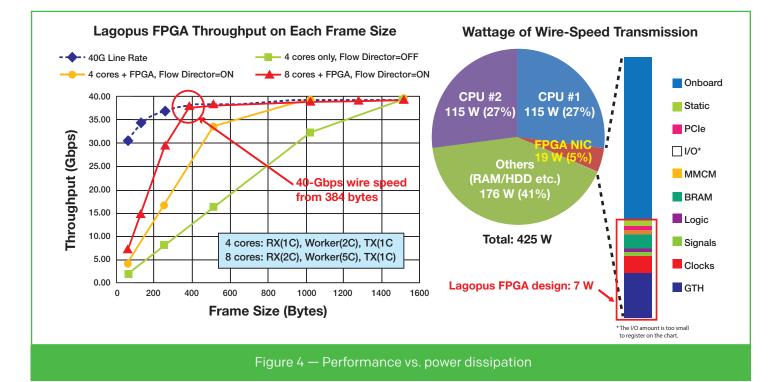

flexible architecture increases the Lagopus switch's 10-Gbps line rate as a pure software implementation to a 40-Gbps line rate via FPGA acceleration. This performance improvement comes at a cost of less than 10 percent of the x86 CPU's power dissipation. The architecture also greatly enhances our network troubleshooting ability, which is essential in a truly virtualized network.

Currently, we are co-designing an advanced software-programmable data plane for Lagopus and original hardware intellectual property (IP) for network carriers using a leading-edge FPGA and design tools, in expectation not only of gaining higher system performance, but also of reducing power and cost. In collaboration with a Xilinx team, we have successfully integrated Lagopus and our IP within 80-Gbps NIC demo boards based on Xilinx Virtex<sup>®</sup>-7 All Programmable FPGAs. We demonstrated Lagopus FPGA for the first time in February at NTT R&D Forum 2015 (Tokyo). We also presented our achievements [2] in August at Hot Chips 27 (Cupertino Calif.).

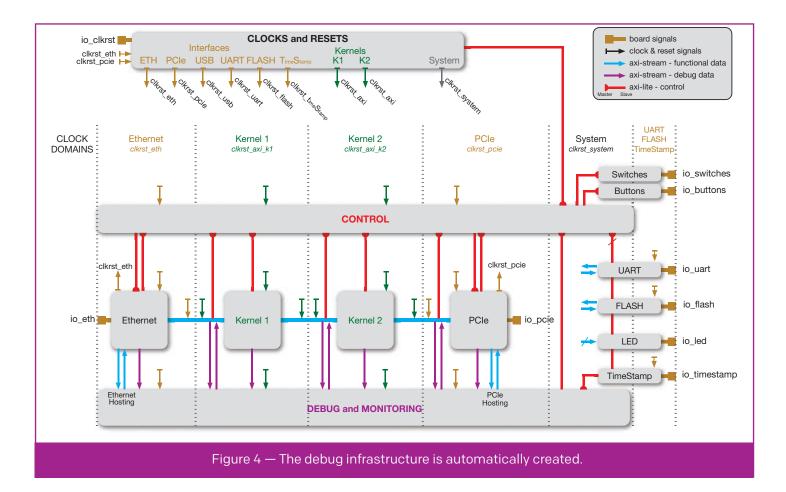

We leveraged the SDNet development environment to create the Lagopus FPGA system. The novel,

# SDNet broadens Lagopus FPGA's potential utilization: The flexible, software-defined hardware design technology enables agile deployment of differentiated network services.

dynamically reprogrammable data plane packet-processing tool chain let us accelerate Lagopus and NFV applications by offloading high-intensity data plane operations such as packet classification, editing, search, load balancing and statics metering—all realized over various multigigabit Ethernet line rates (10/40/100 GbE)—to the FPGA NIC without compromising performance. We believe this is the best solution for our project to enforce the classification IP, a key component for SDN/NFV technology. The environment's quick, reconfigurable packet pipeline capability lets us quickly and easily update protocols and features for networking.

The SDNet environment broadens Lagopus FPGA's potential utilization by covering a broad range of use

cases in both cloud computing data centers and wide area networks. For NTT, the flexible, software-defined hardware design technology enables agile deployment of differentiated network services.

#### DESIGN BASICS WITH THE SDNET ENVIRONMENT

With competition on the rise in the emerging market for SDN/NFV technology, one design challenge for the Lagopus FPGA project was to work within a tight development window in order to achieve timely deployment and promotion. We started designing the Lagopus FPGA system in October 2014 and completed our first integration just three months later, in January 2015.

That was quite an accomplishment, given the complexity of the system design. Figure 1 shows the top-level architecture of the Lagopus FPGA system, which comprises four technical software layers, including a soft FPGA IP bundle: (1) NFV applications; (2) the Lagopus software switch; (3) a hardware abstraction layer, such as an application programming interface (API) and Intel's Data Plane Development Kit (DPDK), a set of libraries and drivers for x86 fast packet processing; and (4) the FPGA NIC IP core suite. The multiple technical layers can make it difficult to trace the source of issues such as dropped packets and performance degradation, hampering the ability to debug and immediately isolate faults; indeed, this is a key challenge for all SDN/NFV architectures. To overcome these difficulties, we leveraged the SDNet environment and Xilinx's Vivado® Design Suite.

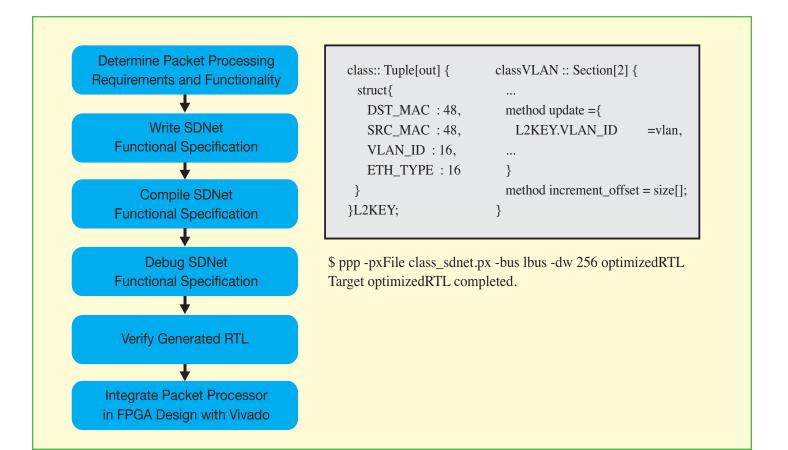

We started the design of Lagopus FPGA by determining our requirements for packet-processing functionality and mapping out a development flow. Figure 2 shows a general description of the development flow and an example code snippet of the SDNet specification. We decided to create a perfect-match filter that uses key information from a virtual LAN. With this, we can accelerate Lagopus' software data plane on the x86 by offloading hardware classification to the FPGA NIC. We can configure the filter entries via a DPDK flow director API by injecting flow entries with the OpenFlow protocol between Lagopus and the SDN controller.

To implement this strategy, we created a corresponding SDNet functional description as shown in the Figure 2 code snippet. We then fed the code into the SDNet compiler, specifying options such as bus type, bus width and generated RTL type. The compilation completed within a few seconds. The actual code size of the SDNet functional description was about 250 lines of code. In contrast, the RTL equivalent comprised several tens of thousands of code lines. Considering that we were working under an intense schedule, we very much appreciated the simplicity of the SDNet specification. It would have been impossible to design

## We achieved 40-Gbps wire-speed software packet processing with Lagopus FPGA, at a cost of less than 10 percent of x86 power dissipation.

and verify such a complicated module in RTL from scratch given our development time constraints.

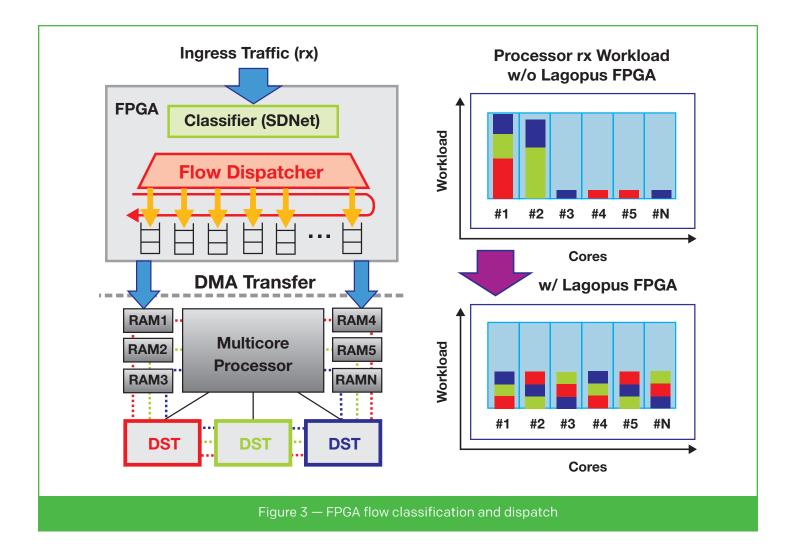

For the next step, we integrated the generated RTL with other peripheral IP on the Vivado Design Suite by employing a Tool Command Language (Tcl) shell. Figure 3 shows the integrated SDNet classifier and our customized flow dispatcher, which we targeted to program a Xilinx Virtex-7 XC7VX690T FPGA.

Since the classified packet flow (targeting 32 receive [rx] DMA queues) can be dispatched efficiently with Lagopus' software data plane on an x86 multicore CPU, the integrated FPGA design enables the system not only to reduce the CPU cycles of the OpenFlow worker threads of Lagopus, but also to balance the workload on each core (Figure 3). As a result, we achieved higher-performance, 40-Gbps wire-speed software packet processing with Lagopus FPGA, at a cost of less than 10 percent of the x86 CPU's power dissipation, as Figure 4 shows.

The SDNet environment and the Vivado Design Suite facilitated our project launch, letting us maximize the feature set, optimize the performance and lower the power consumption of the Lagopus FPGA system. NTT R&D's leadership in SDN/ NFV and our use of Xilinx's SDNet development environment will enable us to bring revolutionary changes to the telecom and cloud infrastructure. Toward that end, we continue to refine our design technique by leveraging a softly defined, reprogrammable SDNet load module. Dynamic and rapid modification of the SDNet specification, including the API, will provide further benefit for us when we define future platforms. ■

#### REFERENCES

#### [1] http://lagopus.github.io/

[2] K. Yamazaki, Y. Nakajima, T. Hatano and A. Miyazaki, "Lagopus FPGA: A reprogrammable data plane for high-performance software SDN switches." Presented at Hot Chips 27, August 2015.

## Delivering FPGA Vision to the Masses

NI's Vision Development Module and Vision Assistant take machine vision from idea to prototype to application deployment.

#### **by Kiran Nagaraj** Senior Software Engineer National Instruments Corp. *kiran.nagaraj@ni.com*

Christophe Caltagirone Senior Software Engineer National Instruments Corp. christophe.caltagirone@ni.com

Dinesh Nair Chief Architect National Instruments Corp. *dinesh.nair@ni.com*

ision systems are going mainstream. The cost/benefit analysis and possible application of technology are now at a point where engineers are designing vision into everything from autonomous vehicles to consumer-electronics quality inspec-

tion systems. This mass adoption is driving vision out of the lab, into embedded systems and onto the factory floor. The deployed systems often require advanced synchronization with I/O, many widely distributed cameras or vision in the control loop. As processes and applications become more complex, vision systems are requiring faster and more advanced processing as well as tighter timing and synchronization.

To meet those requirements, vision system designers are increasingly relying on heterogeneous processing platforms comprising a combination of real-time processors and FPGA, GPU or DSP processing elements that can handle specialized tasks, I/O requirements and processing performance needs. Smart cameras, frame grabbers and vision systems are all leveraging heterogeneous architectures to meet application requirements.

The parallel processing capability of FPGAs, such as those in the Xilinx<sup>®</sup> All Programmable FPGA lineup, is a natural fit for implementing many image processing algorithms. FPGAs can be used for performing both data-intensive processing and high-speed sensor measurements. The devices also have incredibly low latency, which is critical for vision applications because latency accounts for the time that elapses until a decision is made based on the image data. FPGAs can help avoid jitter and thus serve as highly deterministic processing units.

Building a heterogeneous system that includes an FPGA, however, introduces serious programming challenges for system designers. As time-to-market pressures mount, vision system designers need the ability to prototype a solution with complex features quickly. Programming on heterogeneous

systems requires a tool that can help the domain expert design intellectual property (IP) functions on multiple platforms and test the vision algorithm before compiling and running the algorithm on the target hardware. The tool should allow easy access to throughput and resource usage information throughout the prototyping process.

NI refers to this as algorithm engineering: the process by which you, the domain expert, can focus on solving the problem at hand without being preoccupied with the underlying hardware technology. NI's Vision Development Module (VDM) with Vision Assistant arms you with that capability.

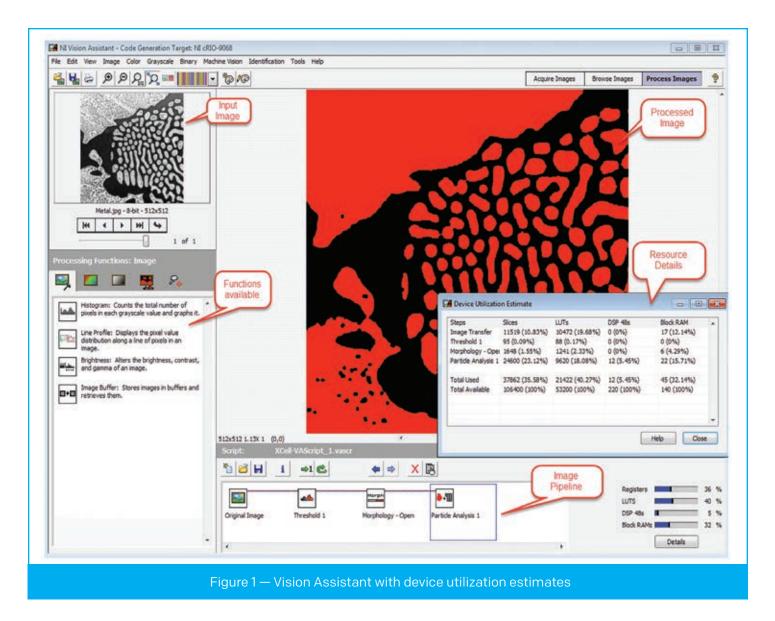

VDM with Vision Assistant helps in fast prototyping and code generation, FPGA resources estimation, automatic code parallelization, and synchronization of parallel streams (for such tasks as latency balancing). VDM includes more than 50 FPGA image processing functions as well as functions to transfer images efficiently between the processor and the FPGA. You can use Vision Assistant within VDM to rapidly prototype and develop FPGA vision applications.

#### **CONFIGURATION-BASED PROTOTYPING**

Vision Assistant is a configuration-based prototyping tool that empowers you to iterate on image processing algorithms and see how changes in parameters affect the image. With Vision Assistant, you can visualize the output (processed image) after every vision block in an image pipeline (Figure 1). You can use the tool to test different algorithms and parameters on different sets of images without having to compile

### You can use Vision Assistant to test the results of algorithms in the prototyping environment and the deployed code to ensure that your implementation yields the same results.

your IP, thereby greatly reducing the time required to design your vision algorithm.

NI has customized the tool to handle FPGA programmers' requirements. The key concerns when building any algorithm on an FPGA are resource consumption on the FPGA fabric, the latency of the pipeline and the maximum frequency the algorithm can achieve on a specific fabric. Vision Assistant helps by providing an estimate of the resources consumed for each block in the image pipeline. You can use the tool to test the results of algorithms in the prototyping environment and the deployed code to ensure that your implementation yields the same results.

One consideration is which kernel size to use for an image filtering operation. The choice of kernel size affects resource usage and latency in the pipeline, with a larger kernel usually requiring more resources than a smaller one.

To select the most appropriate kernel size for your application, you can use Vision Assistant to experiment until you achieve the best performance in terms of minimal resource consumption and maximum performance. A real-time estimate of

The vision FPGA IP of the Vision Development Module lets developers use massively parallel processing and the Vivado High-Level Synthesis tool to achieve fully pipelined, low-latency, architectureoptimized vision functions on the FPGA.

vision IP functions, as in Figure 1, is a useful feature to have during prototyping.

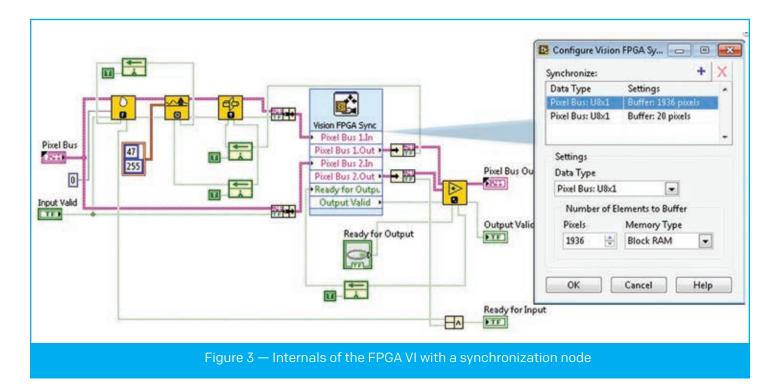

Running multiple image pipelines in parallel is a common requirement. Such scenarios dictate that at the time the pipelines merge into a single pipeline, the latency of the parallel pipelines must be balanced. NI provides a synchronization buffer as part of its vision FPGA IP toolset. Vision Assistant automatically computes the latencies in the pipeline and ensures balanced latency at the time that the parallel pipelines merge to configure the synchronization buffer for you. This guarantees that the FIFOs in the synchronization buffers have sufficient depth based on the maximum latency of the pipelines.

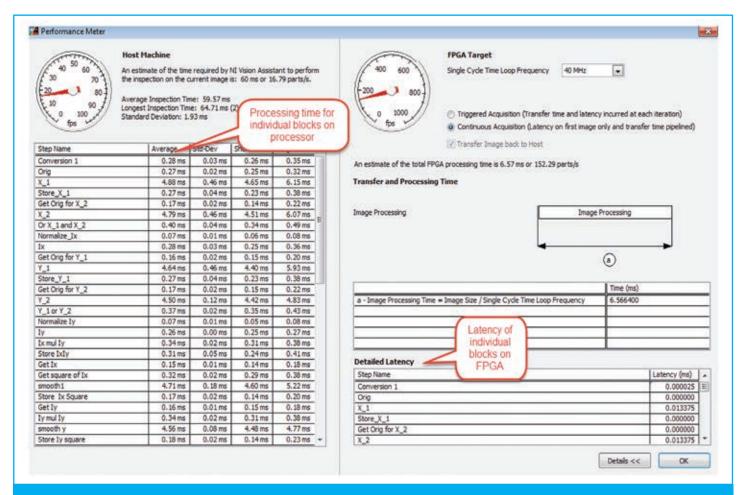

The performance meter utility in Vision Assistant estimates the maximum time taken for processing each frame (Figure 2), letting you know the collective latency of all the blocks in the pipeline. Most of the processors in NI's hardware portfolio have a real-time operating system running on them, so using Vision Assistant makes it easy to estimate the time required to execute a vision function.

For those who are new to LabVIEW, it should be noted that Vision Assistant ensures the creation of a fully functional project, including all dependencies, such as transfer virtual instruments (VIs) and DMA FIFOs, and the image acquisition logic. A VI is similar to a function or subroutine in other programming languages. Transfer VIs are required to transfer the image data between the host/acquisition logic and the FPGA. DMA FIFOs do not involve the host processor; therefore, they are the fastest available method for transferring large amounts of data between the FPGA target and the host. The acquisition logic depends on whether the vision system is based on inline processing or coprocessing. Vision Assistant also helps you create other VIs, such as the Host VI, which runs on the processor, and the FPGA VI. You would then compile the FPGA VI using Xilinx Vivado<sup>®</sup> tools to generate a bitstream for deployment on the FPGA.

It is important to note that the system that houses the image processing pipeline can be broadly categorized as inline processing or coprocessing, depending on where the acquisition logic resides. In inline processing, the acquisition logic resides on the FPGA; the camera is configured using the acquisition logic and the image is processed on the FPGA. The results and the processed image are then sent back to the host for evaluation and further analysis. In coprocessing, the acquisition logic for the camera resides on the FPGA and then sending the processed image from the processor to the FPGA to the processor require a finite amount of time. You also can partition the processor and the FPGA.

As a developer of a vision system that uses an FPGA, you need to be aware of the throughput that the FPGA can achieve. You can use throughput information and real-time resource estimation to determine how many functions (IP blocks) you can deploy to the FPGA. In a coprocessing scenario, the processor performance determines the final throughput. This is true when using the FPGA IP functions that NI ships with the Vision Development Module because those functions are fully pipelined and yield better performance than most processors.

#### **PROTOTYPE TO DEPLOYMENT**

The vision FPGA IP of the Vision Development Module lets developers use massively parallel processing and the Xilinx Vivado High-Level Synthesis (HLS) tool to achieve fully pipelined, low-latency, architecture-optimized vision IP on the FPGA. Vision FPGA IP from NI currently targets three Xilinx FPGA families— Kintex<sup>®</sup>-7, Virtex<sup>®</sup>-5 and Spartan<sup>®</sup>-6—as well as the Xilinx Zynq<sup>®</sup>-7000 All Programmable SoCs. An image can be viewed as a two-dimensional array, and operation on an image is mostly matrix-based. FPGAs' inherent parallelism enables their high-speed performance. You can achieve the matrix operations on the image using loops; you can unroll the loops and take advantage of the parallelism feature of the FPGA to perform several tasks after unrolling. LabVIEW FPGA and the LabVIEW FPGA IP Builder are the primary tools developers use to create vision IP on FPGAs.

Vision FPGA IP functions are single-pixel processing, so they accept 1 pixel from a pixel stream and then output 1 pixel. The IP functions interact with one another using enable-based handshaking or a four-wire handshaking protocol. The primary reason for this implementation is that the complexity of the control path increases with the number of functions in the image pipeline, thus requiring a seamless handover of data between the functions. The four-wire protocol ensures lossless data transfer between vision FPGA IP functions placed in a single-cycle timed loop (SCTL); using the SCTL ensures that the modules in the loop clock at a user-specified frequency.

Figure 3 shows an FPGA VI that depicts the fourwire protocol and the synchronization buffer to merge the pixel. The four-wire protocol is designed for algorithms that run in parallel; it improves throughput by ensuring that the data is processed in a producer-consumer architecture. Further, the four-wire handshake consumes minimal resources on the FPGA. This is critical because the protocol constitutes overhead for the underlying vision functionality.

Vision FPGA IP also gives you the flexibility of adding custom code within the pipeline to provide an open environment. The custom code requires a wrapper VI that has the four-wire handshake implementation. You can then insert custom code in the image pipeline. You must ensure that the custom code is fully pipelined; otherwise it might affect the integrity of the pipeline. You can implement your custom

code using LabVIEW, or you can use existing code in VHDL through an HDL integration node in Lab-VIEW FPGA.

The vision FPGA IP toolset provides preprocessing functions such as edge detection filters, convolution filters, lowpass filters, gray morphology, binary morphology and threshold. It also includes vision IP functions that perform arithmetic and logical operations, as well as functions that output results such as the centroid. Another function, the Simple Edge Tool, finds edges along a line and is useful for caliper applications. The Quantify function accepts a masked image as well as the image stream to be processed and returns a report that has information about the area, mean and standard deviation of the regions defined by the masked image. Linear Average computes the average pixel intensity (mean line profile) on all or part of the image.

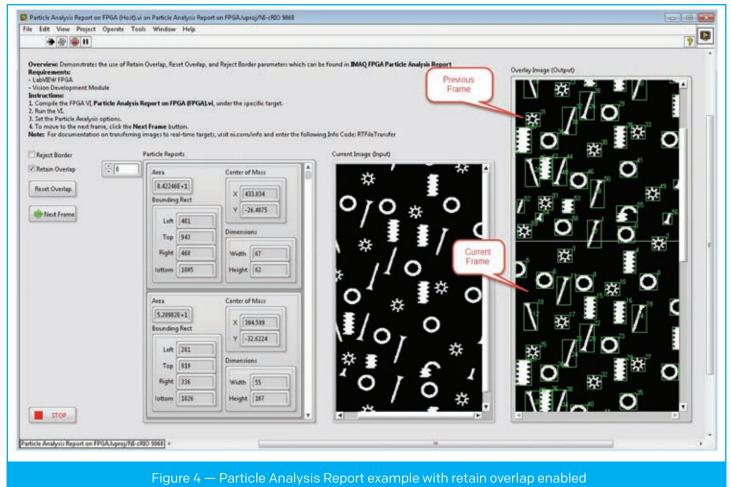

The latest addition to NI's vision FPGA IP list is the Particle Analysis Report. You can perform particle analysis, or blob analysis, to detect connected regions or groupings of pixels in an image and then make selected measurements of those regions. With this information, you can detect flaws on silicon wafers, detect soldering defects on electronic boards or locate objects in motion control applications.

A unique feature of this IP is that it can detect particles when the particle information is spread across two frames. NI ships a Particle Analysis Report example with VDM; Figure 4 shows the Host VI with the image display. This capability is needed in inspection systems, where you cannot always ensure that the objects under inspection are captured in a single frame.

Nearly 70 percent of NI's vision FPGA IP functions were developed using the IP Builder, a utility in LabVIEW FPGA that allows you to code in graphical code using LabVIEW and then output RTL code using Vivado HLS. The major advantage of this approach is that users familiar with graphical coding can develop the application along with a directive file that states their frequency and latency

#### Vivado HLS is a good fit for vision development because it helps abstract algorithmic descriptions and data-type specifications from the generated C code of the IP Builder.

requirements. Using LabVIEW IP Builder with Vivado HLS generates the appropriate VHDL code. You can use array-based operations on images, and Vivado HLS ensures that, based on the directives set, the VI will achieve the required frequency of operation and minimum latency.

Vivado HLS is a good fit for vision development because it helps abstract algorithmic descriptions and data-type specifications (integer, fixed-point) from the generated C code of the IP Builder. It also generates the necessary simulation models for early testing of functionality. The generated architecture-aware VHDL code yields high-quality, highly repeatable results.

NI is committed to the concept of providing open, flexible systems with the right software tools to leverage them. Developers are designing vision systems based on heterogeneous architectures into a growing range of applications. The next frontier for the software design of these heterogeneous systems could be for the compiler or application development engine to decide intelligently where to deploy the components of an algorithm, using the capabilities and resources of the various system components (CPU, GPU and FPGA) to make that determination.

As more-advanced products and processes push the limits of what vision systems are asked to do, application developers will require an effective prototyping and algorithm development environment for vision functionality. Providing the right tools to developers and domain experts will fuel the next wave of innovation in vision system design for the masses.

If you are interested in trying out NI's vision FPGA IPs, you need to install LabVIEW FPGA and VDM. You can do so initially for a 30-day evaluation period and then extend or purchase the license at *ni.com/vision*.

### **A Novel Approach** to Software-Defined **FPGA Computing**

by Stephane Monboisset Director, QuickPlay Marketing and Business Development PI DA smo@quickplay.io

011

0

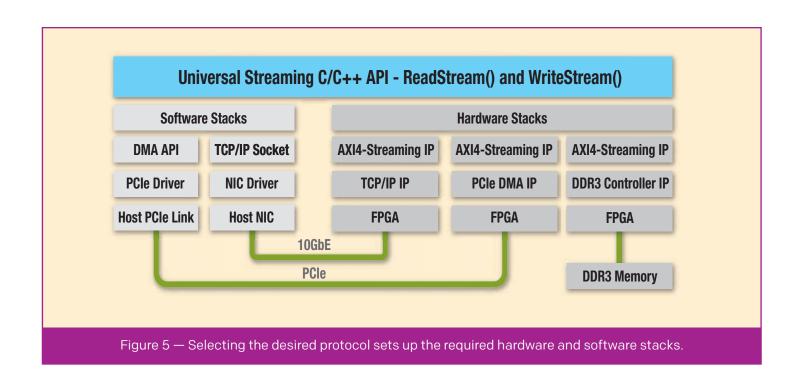

QuickPlay's high-level workflow lets software developers build efficient FPGA-based applications in no time.

$t_{max} = \frac{m_{max}}{MAX(t0,t1)}$

)][stage] = tmin (i+1)][stage] = tmax

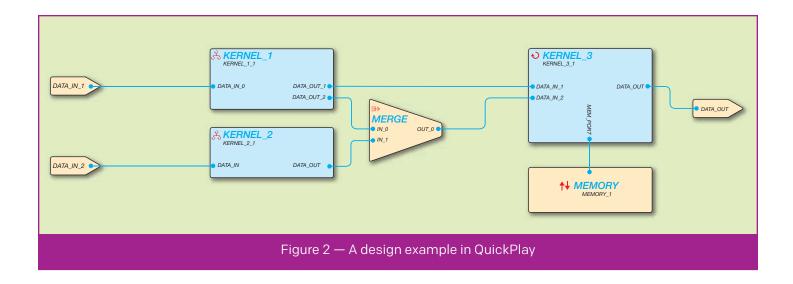

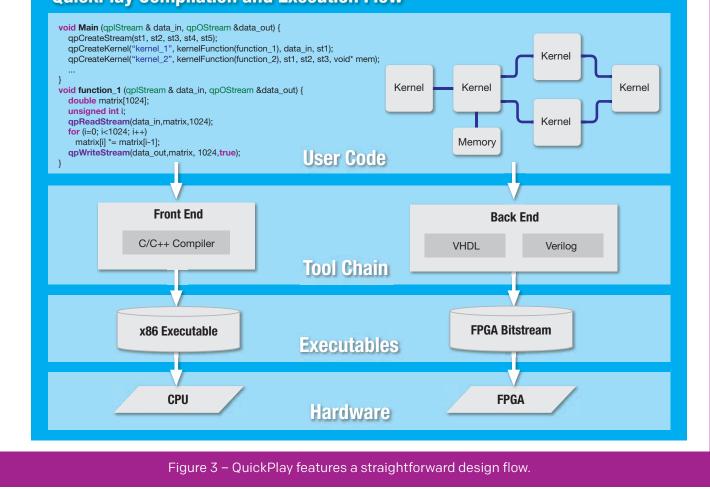

With the rise of the Internet of Things and Big Data processing, the need for transferring and processing data has skyrocketed, and CPUs alone can no longer address the exponential increase. Adding more processors and more virtual machines to run a given application just doesn't cut it, as there is only so much that can be parallelized on multiple CPUs for a given application. Field-programmable gate arrays, on the other hand, have the requisite I/O bandwidth and processing power, not only from a pure processing standpoint but, equally important, from a power standpoint. For data-center equipment manufacturers, the use of FPGAs has long been an appealing prospect. Intel's recent acquisition of the second-largest FPGA vendor is further testament that a CPU-only solution no longer suffices.

The major roadblock to more-widespread FPGA adoption has been the complexity of implementing them. Until now, the only way to develop an application on an FPGA-based platform has been to deal with some of the lowest levels of hardware implementation. This has kept a large potential customer base—software developers—away from the devices and has made life increasingly complicated for traditional FPGA designers.