WD6022

Address or Data

Buffer Device

## **TABLE OF CONTENTS**

| Section<br>1.0                                                   | Title INTRODUCTION  1.1 Description  1.2 Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14-1                                                                                                                             |

|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| 2.0                                                              | ADDRESS AND DATA BUFFER DEVICES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 14-5                                                                                                                             |

| 3.0                                                              | TECHNICAL SPECIFICATIONS  3.1 Absolute Maximum Ratings  3.2 Normal Operating Conditions  3.3 DC Characteristics  3.4 AC Load Specifications  TIMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 14-19<br>. 14-19<br>. 14-19<br>. 14-20                                                                                         |

| 4.0                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 14-21                                                                                                                            |

|                                                                  | LIST OF ILLUSTRATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                  |

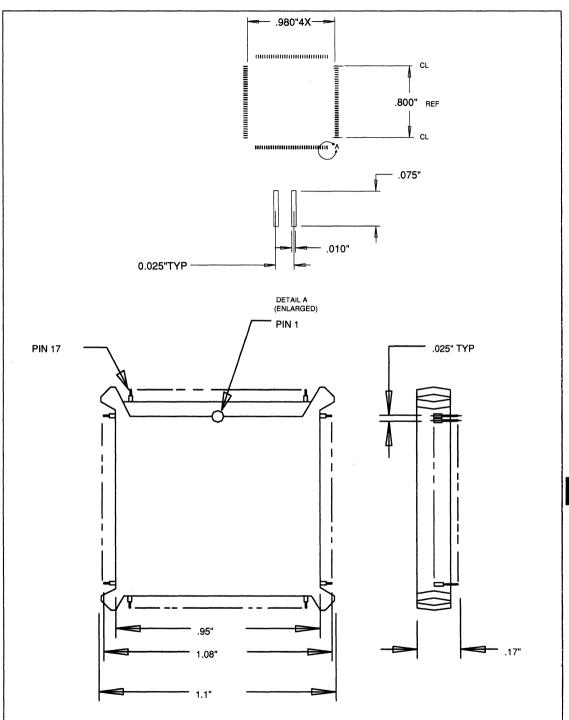

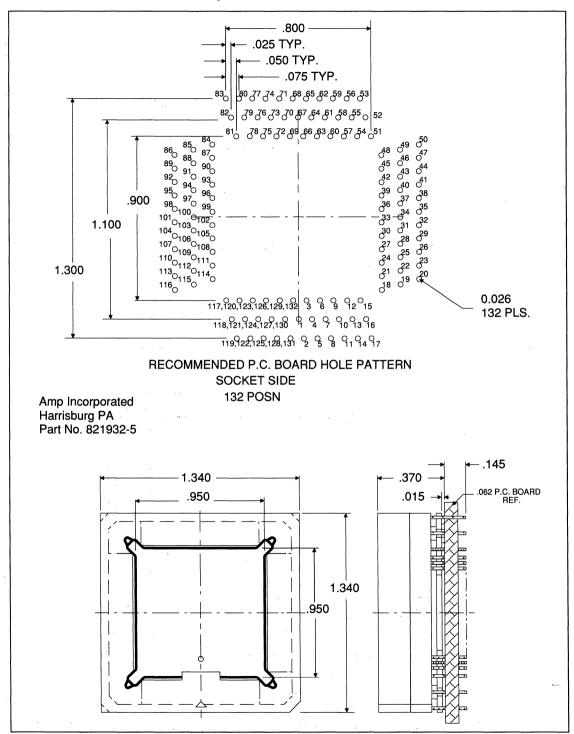

| Figure  1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 | Title  System Block Diagram  Address Buffer Mode Block Diagram  Address Buffer Mode Pin Diagram  Data Buffer Mode Pin Diagram  Data Buffer Mode Pin Diagram  Address Mode: Channel Master Accesses Translate Function  Address Mode: Channel Master Accesses  Address Mode: 80386/DMA Channel Accesses  Data Mode: 80386/Bodes Modes From the Channel  Data Mode: 80386/Bodes Modes | 14-3<br>14-4<br>14-9<br>14-15<br>14-15<br>14-16<br>14-16<br>14-17<br>14-18<br>14-22<br>14-23<br>14-25<br>14-25<br>14-26<br>14-26 |

|                                                                  | LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                  |

| <b>Table</b> 1 2 3 4                                             | Title  Address Buffer Mode Pinout  Data Buffer Mode Pinout  Address Buffer Mode Timings (ns)  Data Buffer Mode Timings (ns)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 14-10<br>. 14-21                                                                                                               |

### 1.0 INTRODUCTION

#### 1.1 DESCRIPTION

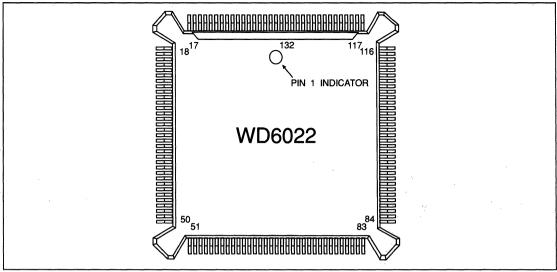

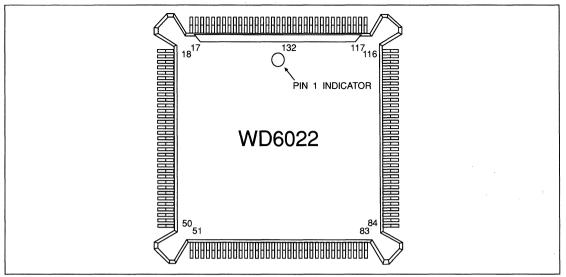

The WD6022 devices form part of Western Digital's® innovative WD6500 chip set, which facilitates the design and implementation of 32-bit Micro Channel system boards. It decreases design complexity and saves space by combining the functions of many discrete arrays and components, also reducing system cost and increasing system reliability.

The chip set contains two WD6022 devices, one configured as an Address Buffer Device, and the other as a Data Buffer Device. Configuration is determined by a Mode pin. When this is zero, the device is configured as an address buffer; when it is one, the device is configured as a data buffer.

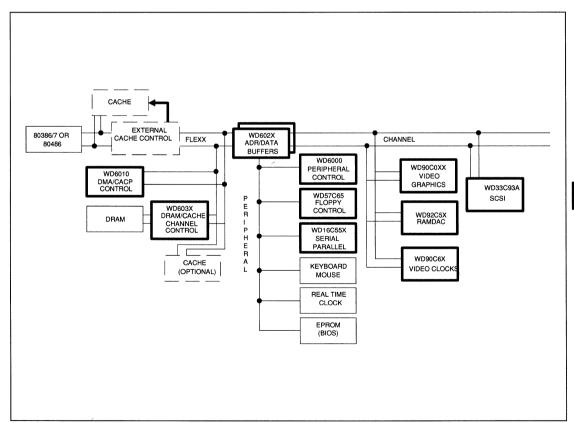

The block diagram in Figure 1 illustrates a typical system using the WD6500 chip set, and shows the two WD6022 devices. Devices with bold outlines are available from Western Digital Corporation.

#### 1.2 FEATURES

- Provides Address and Data Buffers that interface

- to the Micro Channel

- □ Meets Micro Channel AC/DC Specifications

- Contains Peripheral Bus Address and Data Buffers

- □ Low Power 1.25 Micron CMOS Technology

- 132-Lead JEDEC Plastic Quad Flat Pack

Figure 1. System Block Diagram

#### 2.0 ADDRESS AND DATA BUFFER DEVICES

The WD6500 chip set contains two WD6022 Address and Data Buffer Devices, one configured as an Address Buffer Device, and the second as a Data Buffer Device.

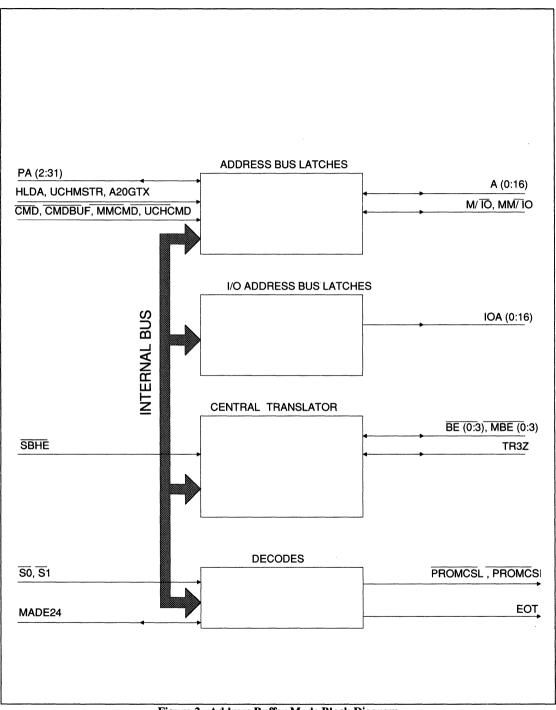

## **Address Buffer Configuration**

To configure the WD6022 as an address buffer, the MODE signal (pin 66) is tied to ground. When configured as an address buffer, the WD6022 performs address bus latches, implements the Central

Translator function for the Micro Channel and provides decodes for the BIOS EPROMs.

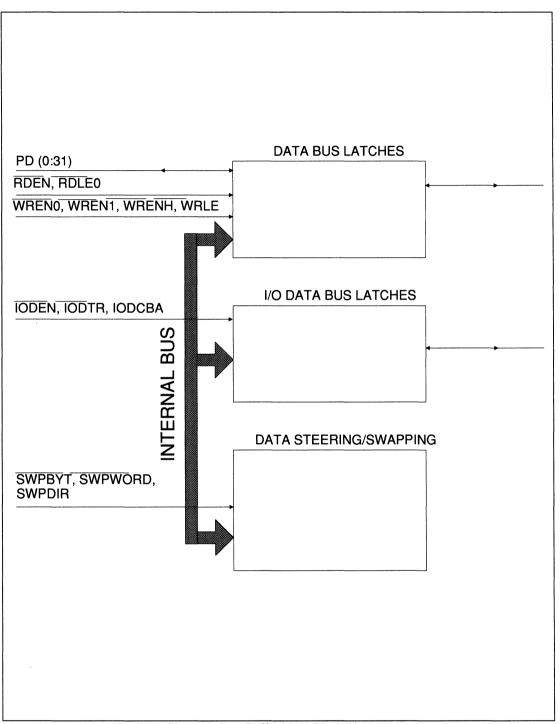

## **Data Buffer Configuration**

To configure the WD6022 as a data buffer, the MODE signal is tied to power. In this mode, the WD6022 performs data bus latches, Micro Channel data steering and data swaps for 80386/80486 and DMA operations.

Figure 2. Address Buffer Mode Block Diagram

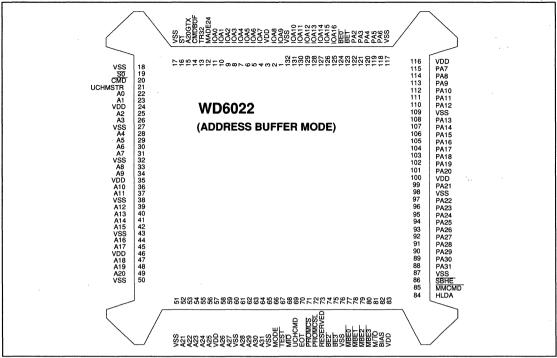

Figure 3. Address Buffer Mode Pin Diagram

| PIN | _ | NAME           | PIN | _ | NAME       | PIN | _ | NAME                | PIN | _ | NAME       |

|-----|---|----------------|-----|---|------------|-----|---|---------------------|-----|---|------------|

| 1   | _ | 1OA9           | 34  | _ | <b>A</b> 9 | 67  | _ | TEST                | 100 | _ | $V_{DD}$   |

| 2   | - | IOA8           | 35  | - | $V_{DD}$   | 68  | _ | MM/ĪŌ               | 101 | _ | PA20       |

| 3   | _ | $V_{DD}$       | 36  | _ | A10        | 69  | _ | UCHCMD <sup>®</sup> | 102 | _ | PA19       |

| 4   | - | IOA7           | 37  | _ | A11        | 70  | _ | EOT                 | 103 | - | PA18       |

| 5   | - | IOA6           | 38  | _ | $V_{SS}$   | 71  | _ | PROMOSL             | 104 | - | PA17       |

| 6   | - | IOA5           | 39  | _ | A12        | 72  | _ | PROMOSH             | 105 | - | PA16       |

| 7   | - | IOA4           | 40  | - | A13        | 73  | _ | RESERVED            | 106 | _ | PA15       |

| 8   | - | IOA3           | 41  | - | A14        | 74  | _ | BE2                 | 107 | _ | PA14       |

| 9   | - | IOA2           | 42  | - | A15        | 75  | - | BE3                 | 108 | _ | PA13       |

| 10  | - | IOA1           | 43  | - | $V_{SS}$   | 76  | _ | Vss                 | 109 | _ | $V_{SS}$   |

| 11  | - | IOA0           | 44  | - | A16        | 77  | _ | MBE0                | 110 | _ | PA12       |

| 12  | - | MADE24         | 45  | - | A17        | 78  | - | MBE1                | 111 | - | PA11       |

| 13  | - | TR32           | 46  | - | $V_{DD}$   | 79  | _ | MBE2                | 112 | _ | PA10       |

| 14  | - | CMDBUF         | 47  | - | A18        | 80  | _ | MBE3                | 113 | - | PA9        |

| 15  | - | <u>A2</u> 0GTX | 48  | - | A19        | 81  | _ | M/IO                | 114 | _ | PA8        |

| 16  | _ | S1             | 49  | - | A20        | 82  | _ | BIAS                | 115 | _ | PA7        |

| 17  | _ | $V_{SS}$       | 50  | - | $V_{SS}$   | 83  | _ | $V_{DD}$            | 116 | _ | $V_{DD}$   |

| 18  | - | <u>Vs</u> s    | 51  | - | $V_{SS}$   | 84  | _ | <u>HLDA</u>         | 117 | _ | $V_{SS}$   |

| 19  | - | <u>S0</u>      | 52  | - | A21        | 85  | _ | MMCMD               | 118 | _ | PA6        |

| 20  | - | CMD            | 53  | - | A22        | 86  | - | SBHE                | 119 | _ | PA5        |

| 21  | - | UCHMSTR        | 54  | _ | A23        | 87  | _ | Vss                 | 120 | - | PA4        |

| 22  | - | <b>A</b> 0     | 55  | - | A24        | 88  | - | PA31                | 121 | - | PA3        |

| 23  | - | A1             | 56  | _ | A25        | 89  | _ | PA30                | 122 | _ | PA2        |

| 24  | - | $V_{DD}$       | 57  | - | $V_{DD}$   | 90  | _ | PA29                | 123 | _ | <u>BE1</u> |

| 25  | _ | A2             | 58  | - | A26        | 91  | _ | PA28                | 124 | _ | BE0        |

| 26  | - | A3             | 59  | - | A27        | 92  | - | PA27                | 125 | _ | IOA16      |

| 27  | - | $V_{SS}$       | 60  | - | Vss        | 93  | _ | PA26                | 126 | - | IOA15      |

| 28  | - | A4             | 61  | - | A28        | 94  | - | PA25                | 127 | _ | IOA14      |

| 29  | - | A5             | 62  | - | A29        | 95  | _ | PA24                | 128 | - | IOA13      |

| 30  | - | A6             | 63  | - | A30        | 96  | - | PA23                | 129 | - | IOA12      |

| 31  | - | <b>A</b> 7     | 64  | - | A31        | 97  | _ | PA22                | 130 | - | IOA11      |

| 32  | - | $V_{SS}$       | 65  | - | Vss        | 98  | - | $V_{SS}$            | 131 | - | IOA10      |

| 33  | - | A8             | 66  | - | MODE       | 99  | - | PA21                | 132 | - | $V_{SS}$   |

Table 1. Address Buffer Mode (Mode = 0) Pinout

# 2.1 ADDRESS BUFFER MODE PIN DESCRIPTIONS

| PIN NO.                                                                                                                                                  | NAME                                                                                                               | TYPE | FUNCTION                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                          |                                                                                                                    |      | ADDRESS BUS LATCHES                                                                                                                                                                                               |

| 22<br>23<br>25<br>26<br>28<br>29<br>31<br>33<br>34<br>36<br>37<br>39<br>41<br>44<br>45<br>47<br>48<br>49<br>55<br>55<br>55<br>55<br>56<br>66<br>66<br>64 | A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 A16 A17 A18 A19 A20 A21 A22 A23 A34 A25 A26 A27 A28 A30 A31  |      | CHANNEL ADDRESS BUS This Channel address bus interfaces directly to the Channel. It is an input during 80386/DMA cycles. Note that A0 is always an input, and is generated by the WD6030 during 80386/DMA cycles. |

| 124<br>123<br>122<br>121<br>120<br>119<br>118<br>115<br>114<br>113<br>112<br>111<br>110<br>108<br>107<br>106                                             | PA0<br>PA1<br>PA2<br>PA3<br>PA4<br>PA5<br>PA6<br>PA7<br>PA8<br>PA9<br>PA10<br>PA11<br>PA12<br>PA13<br>PA14<br>PA15 | I/O  | PROCESSOR ADDRESS BUS This is the local processor address bus on the motherboard, and interfaces directly with the processor address bus. It is an input for 80386/80486/DMA cycles and output for master cycles. |

| PIN NO.                                                                                           | NAME                                                                                                                                        | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 105<br>104<br>103<br>102<br>101<br>99<br>97<br>96<br>95<br>94<br>93<br>92<br>91<br>90<br>89<br>88 | PA16<br>PA17<br>PA18<br>PA19<br>PA20<br>PA21<br>PA22<br>PA23<br>PA24<br>PA25<br>PA26<br>PA27<br>PA28<br>PA29<br>PA30<br>PA31                | VO   | PROCESSOR ADDRESS BUS (CONT)                                                                                                                                                                                                                                                                                                                 |

| 11<br>10<br>9<br>8<br>7<br>6<br>5<br>4<br>2<br>1<br>131<br>130<br>129<br>128<br>127<br>126<br>125 | IOA0<br>IOA1<br>IOA2<br>IOA3<br>IOA4<br>IOA5<br>IOA6<br>IOA7<br>IOA8<br>IOA9<br>IOA10<br>IOA11<br>IOA12<br>IOA13<br>IOA14<br>IOA15<br>IOA16 | 0    | I/O ADDRESS BUS This is the I/O address bus on the system board. It is the latched version of the addresses on the Channel. The I/O address bus supplies the addresses to all the Channel peripherals on the system board, such as the video, floppy, serial port, parallel port, timer and interrupt controllers, and EPROM.                |

| 84                                                                                                | HLDA<br>80386/<br>80486                                                                                                                     | I    | HOLD ACKNOWLEDGE The CPU generates this signal in response to a HOLD signal from the DMA controller. When active, it indicates that the CPU has relinquished control of the local bus.                                                                                                                                                       |

| 21                                                                                                | UCHMSTR                                                                                                                                     | I    | CHANNEL MASTER This signal is generated by the CXACP in the WD6010. When active, it indicates that a Channel master has control ofthe bus. It is used to control the direction of the address buffers.                                                                                                                                       |

| 15                                                                                                | A20GTX                                                                                                                                      | l    | ADDRESS BIT 20 GATE SIGNAL This signal is generated by the WD6010, and has no effect on the address when the DMA or Micrh Channel master is generating the addresses. It is encoded in the following manner:  HLDA UCHMSTR A20GTX A20 SOURCE DEVICE 0 0 0 0 80386/80486 0 0 1 PA20 80386/80486 1 0 x PA20 DMA 1 1 x A20 Micro Channel Master |

| PIN NO.                | NAME                         | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|------------------------|------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 20                     | CMD                          | I    | COMMAND The Command signal generates the latch signal that latches the Channel addresses when a Channel master has the bus.                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 14                     | CMDBUF                       | l    | BUFFERED CHANNEL COMMAND This signal latches the Channel addresses for the IOA (16:0) address the input to this signal is the CMD signal which is generated by the WD6030.                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 85                     | MMCMD                        | 1    | CHANNEL MATCHED MEMORY COMMAND This is the Matched Memory Command signal on the Channel. This signal is pulled-up as MMC is not supported.                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 69                     | UCHCMD                       | 0    | CHANNEL COMMAND This signal is the logical OR of the CMD and MMCMD signals, and indicates that a command is present on the Channel. It is used in the WD6010 diagnostic interface.                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 81                     | M/IO                         | I/O  | LOCAL BUS M/IO The M/IO signal is on the local bus, and interfaces directly with the M/IO signal on the CPU. When a Channel master accesses the system board DRAM, this signal is a latched version of the MM/IO signal.                                                                                                                                                                                                                                              |  |  |  |  |

| 68                     | MM/ <del>IO</del>            | I/O  | CHANNEL M/IO This signal interfaces directly with the Channel M/IO signal, a delayed version of the CMD signal generated by the WD6000. When the 80386 or the DMA accesses the Channel, this signal is the same as M/IO.                                                                                                                                                                                                                                              |  |  |  |  |

|                        | CENTRAL TRANSLATOR           |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 86                     | SBHE                         | 1    | SYSTEM BYTE HIGH ENABLE  The System Byte High Enable signal on the Channel interfaces directly to SBHE on the Channel. When the address flow is from the processor bus to the Channel bus, the WD6030 generates this signal as a decode of BE (0:3). When the address flow goes from the Channel bus to the processor bus, this signal is used in the central translator function.                                                                                    |  |  |  |  |

| 13                     | TR32                         | I/O  | TRANSLATE 32 The Translate 32 signal on the Channel is used in the central translator logic. When it is active, the central translator translates A0, A1, and SBHE to BE (0:3). TR32 is used for a 16-bit master communicating with a 32-bit slave.                                                                                                                                                                                                                   |  |  |  |  |

| 124<br>123<br>74<br>75 | BEO<br>BE1<br>BE2<br>BE3     | I/O  | BYTE ENABLES These byte enables on the local bus interface directly with the 80386/80486 byte enables. When the address flow is from the processor address bus to the Channel address bus, these signals generate Address Bit 1 (A1). A0 is generated by the WD6030. When the address flow is from the Channel address bus to the processor address bus, these signals are generated by a 32-bit master on the Channel or the central translator for a 16-bit master. |  |  |  |  |

| 77<br>78<br>79<br>80   | MBE0<br>MBE1<br>MBE2<br>MBE3 | I/O  | CHANNEL BYTE ENABLES These Channel byte enable signals interface directly to the BE (0:3) on the Micro Channel. During an 80386/80486/DMA cycle, these signals are outputs. For a master cycle they are not input signals.                                                                                                                                                                                                                                            |  |  |  |  |

|                        |                              | 1    | DECODES                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 19<br>16               | <u>S0</u><br>S <u>1</u>      |      | CHANNEL CONTROL SIGNALS These two signals interface directly to the Channel S(0:1) signals. Together with MADE24, MM/IO, and the Channel address, it generates the PROM chip selects.                                                                                                                                                                                                                                                                                 |  |  |  |  |

| PIN NO.                                                                                | NAME               | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------------------------|--------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12                                                                                     | MADE24             | I/O  | CHANNEL MADE24 SIGNAL This signal directly interfaces with the Channel MADE24 signal. In combination with S(0:1) and MM/IO, it generates the PROM chip selects. During 80386/80486/DMA cycles, this signal is an output signal.  ADDRESSES MADE24 0-16 MBytes 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 71<br>72                                                                               | PROMCSL<br>PROMCSH | 0    | PROM CHIP SELECT (Low) PROM CHIP SELECT (High) These signals select the two 64K by 8 (27512) PROMs which together form the 128K of PROM on the system board. The two PROMs are organized into even and odd banks, providing a 16-bit wide interface. PROMCSL selects the even banks and PROMCSH selects the odd banks. Configurations with 8-bit wide, 1 M bit PROMs (27010) are also possible. In such a case, PROM Chip Select is generated by executing a logical OR of PROMCSL and PROMCSH. To get the BIOS to execute faster, the PROM can be mapped to the DRAM and executed from there. The PROMs are located at 000E0000H - 000FFFFFH and at FFFE0000 - FFFFFFFFH. An access to either of these locations generates the chip selects for the PROM. However, a Channel cycle to access the PROM will only be run if an access is made to FFFE0000 - FFFFFFFFH, or if a read access is made to E0000 -FFFFF, and the PROM is not mapped to RAM. Writes to these addresses are ignored. |

| 70                                                                                     | EOT                | 0    | END-OF-TRANSFER This signal is activated when CMD and S(1:0) are inactive. The CACP controller inside the WD6010 uses this signal and BURST to detect an End-of-Transfer condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                        |                    |      | MISCELLANEOUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 66                                                                                     | MODE               | I    | MODE PIN This pin determines the mode of operation for the WD6022 device. When tied to $V_{DD}$ , it puts the WD6022 into the data buffer mode; when it is tied to ground, it puts it into the address buffer mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 67                                                                                     | TEST               | I    | TEST PIN This is an active low pin to facilitate board-level testing. When low, this signal tristates all outputs and bi-directional signal lines so that an ATE tester can drive these signals instead.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 82                                                                                     | BIAS               | 1    | BIAS PIN This pin controls the biasing of the internal buffers, and should be pulled low with a 1.25K $\pm 1\%$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3, 24,<br>35,<br>46,57,<br>83, 100,<br>116                                             | V <sub>DD</sub>    | 1    | +5 V Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 17, 18,<br>27, 32,<br>38, 43,<br>50, 51,<br>60, 65,<br>76, 87,<br>98, 109,<br>117, 132 | V <sub>SS</sub>    | I    | O V Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Figure 4. Data Buffer Mode Block Diagram

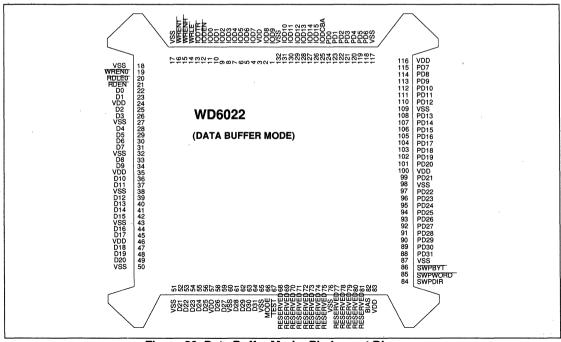

Figure 5. Data Buffer Mode Pin Diagram

| PIN | _ | NAME            | PIN | _ | NAME     | P | IN | _ | NAME     | PIN  | _ | NAME     |

|-----|---|-----------------|-----|---|----------|---|----|---|----------|------|---|----------|

| 1   | _ | IOD9            | 34  | _ | D9       |   | 67 | _ | TEST     | 100  | _ | $V_{DD}$ |

| 2   | _ | IOD8            | 35  | _ | $V_{DD}$ |   | 68 | - | RESERVED | 101  | _ | PD20     |

| 3   | _ | $V_{DD}$        | 36  | _ | D10      |   | 69 | _ | RESERVED | 102  | _ | PD19     |

| 4   | _ | IOD7            | 37  | _ | D11      |   | 70 | - | RESERVED | 103  | _ | PD18     |

| 5   | - | IOD6            | 38  | _ | $V_{SS}$ |   | 71 | - | RESERVED | 104  | _ | PD17     |

| 6   | _ | IOD5            | 39  | - | D12      |   | 72 | - | RESERVED | 105  | _ | PD16     |

| 7   | - | IOD4            | 40  | _ | D13      |   | 73 | - | RESERVED | 106  | _ | PD15     |

| 8   | - | IOD3            | 41  | - | D14      |   | 74 | - | RESERVED | 107  | - | PD14     |

| 9   | _ | IOD2            | 42  | _ | D15      |   | 75 | - | RESERVED | 108  | _ | PD13     |

| 10  | - | IOD1            | 43  | - | $V_{SS}$ |   | 76 | _ | $V_{SS}$ | 109  | _ | $V_{SS}$ |

| 11  | - | IOD0            | 44  | _ | D16      |   | 77 | _ | RESERVED | 110  | _ | PD12     |

| 12  | _ | IODEN           | 45  | _ | D17      |   | 78 | _ | RESERVED | 111  | _ | PD11     |

| 13  | - | IODTR           | 46  | - | $V_{DD}$ |   | 79 | - | RESERVED | 112  | - | PD10     |

| 14  | _ | WRLE            | 47  | - | D18      |   | 80 | - | RESERVED | 113  | - | PD9      |

| 15  | - | WRENH           | 48  | - | D19      |   | 81 | - | RESERVED | 114  | - | PD8      |

| 16  | _ | WREN1           | 49  | _ | D20      |   | 82 | _ | BIAS     | 115  | _ | PD7      |

| 17  | _ | $V_{SS}$        | 50  | - | $V_{SS}$ |   | 83 | - | $V_{DD}$ | 116  | _ | $V_{DD}$ |

| 18  | - | V <sub>SS</sub> | 51  | - | $V_{SS}$ |   | 84 |   | SWPDIR   | 117  | - | $V_{SS}$ |

| 19  | _ | WREN0           | 52  | - | D21      |   | 85 | _ | SWPWORD  | 118  | - | PD6      |

| 20  | _ | RDLE0           | 53  | - | D22      |   | 86 | - | SWPBYT   | 119  | _ | PD5      |

| 21  | - | RDEN            | 54  | - | D23      |   | 87 | - | Vss      | 120  | - | PD4      |

| 22  | _ | D0              | 55  | _ | D24      |   | 88 | _ | PD31     | 121  | _ | PD3      |

| 23  | - | D1              | 56  | _ | D25      |   | 89 | - | PD30     | 122  | _ | PD2      |

| 24  | - | $V_{DD}$        | 57  | _ | $V_{DD}$ |   | 90 | - | PD29     | 123  | _ | PD1      |

| 25  | _ | D2              | 58  | _ | D26      |   | 91 | - | PD28     | 124  | - | PD0      |

| 26  | _ | D3              | 59  | _ | D27      |   | 92 | _ | PD27     | 125  | _ | IODCBA   |

| 27  | _ | $V_{SS}$        | 60  | _ | $V_{SS}$ |   | 93 | _ | PD26     | 126  | _ | IOD15    |

| 28  | _ | D4              | 61  | _ | D28      |   | 94 | _ | PD25     | 127  | _ | IOD14    |

| 29  | _ | D5              | 62  | _ | D29      |   | 95 | - | PD24     | 128  | _ | IOD13    |

| 30  | _ | D6              | 63  | _ | D30      |   | 96 | - | PD23     | 129  | - | IOD12    |

| 31  | - | D7              | 64  | _ | D31      |   | 97 | - | PD22     | 130  | _ | IOD11    |

| 32  | _ | $V_{SS}$        | 65  | _ | $V_{SS}$ |   | 98 | - | $V_{SS}$ | ,131 | _ | IOD10    |

| 33  | - | D8              | 66  | _ | MODE     |   | 99 | _ | PD21     | 132  | _ | $V_{SS}$ |

**Table 2. Data Buffer Mode (Mode = 1) Pinout**

# 2.2 DATA BUFFER MODE PIN DESCRIPTIONS

| PIN NO.                                                                                                      | NAME                                                                                                                  | TYPE | FUNCTION                                                                                         |

|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------|

|                                                                                                              |                                                                                                                       |      | DATA BUS LATCHES                                                                                 |

| 22 23 5 6 8 9 0 1 3 3 4 6 7 9 0 1 2 4 4 5 7 8 9 2 3 4 5 5 5 5 5 5 5 6 6 6 6 6 6 6 6 6 6 6 6                  | D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15 D16 D17 D18 D19 D20 D21 D22 D23 D24 D25 D26 D27 D28 D29 D30 D31 | I/O  | CHANNEL DATA BUS These Channel data bus signal lines connect directly to the Channel data bus.   |

| 124<br>123<br>122<br>121<br>120<br>119<br>118<br>115<br>114<br>113<br>112<br>111<br>110<br>108<br>107<br>106 | PD0<br>PD1<br>PD2<br>PD3<br>PD4<br>PD5<br>PD6<br>PD7<br>PD8<br>PD10<br>PD11<br>PD12<br>PD13<br>PD13<br>PD14<br>PD15   | VO   | PROCESSOR DATA BUS These processor data bus signal lines connect directly to the 80386 data bus. |

| PIN NO.                                                                                           | NAME                                                                                                                                 | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 105<br>104<br>103<br>102<br>101<br>99<br>97<br>96<br>95<br>94<br>93<br>92<br>91<br>90<br>89<br>88 | PD16<br>PD17<br>PD18<br>PD19<br>PD20<br>PD21<br>PD22<br>PD23<br>PD24<br>PD25<br>PD26<br>PD27<br>PD28<br>PD29<br>PD30<br>PD30<br>PD31 | I/O  | PROCESSOR DATA BUS (CONT)                                                                                                                                                                                                                                                                                                                                                                                   |

| 11, 9-4,<br>3-1,<br>13-125                                                                        | IOD (0:15)<br>to IOD (0:0)                                                                                                           | 1/0  | 16-BIT I/O DATA BUS This is the 16-bit I/O data bus, which provides support for devices eight bits or sixteen bits wide.                                                                                                                                                                                                                                                                                    |

| 21                                                                                                | RDEN                                                                                                                                 | l    | READ ENABLE This read-enable signal enables for the processor data bus (PD (0:31)) when data flows from the Channel data bus to the processor data bus. This signal is active when the CPU or the DMA performs a read from the Channel, or when a Channel master writes to the system board DRAM.                                                                                                           |

| 20                                                                                                | RDLE0                                                                                                                                | I    | READ LATCH ENABLE 0 This signal is the latch enable signal for Byte 0 (0:7). When the CPU or the DMA performs a cycle to an 8-bit device on the Channel, the cycle is split in two. This signal latches the first 8 bits (0:7) during the first cycle, reads the next 8 bits (8:15) during the second cycle, and this presents the 16 bits to the CPU.                                                      |

| 19<br>16<br>15                                                                                    | WRENO<br>WREN1<br>WRENH                                                                                                              | 1    | WRITE ENABLE (HIGH, 0:1) This signal enables the buffer during data flow from the processor data bus to the Channel data bus D (0:31). These signals control Byte 0 (0:7) (WRENO), byte 1 (8:15) (WREN1), and the upper word (16:31) (WRENH). These signals are valid when the CPU or the DMA performs a write operation to the Channel or when a Channel master performs a read from the motherboard DRAM. |

| 14                                                                                                | WRLE                                                                                                                                 | I    | WRITE LATCH ENABLE This write latch enable signal latches the write data during a CPU or DMA write operation to the Channel. It also provides the write-data-hold time required by the Channel during these operations. This signal also latches the data when the CPU or DMA writes to an 8-bit port and the cycle has to be split in two.                                                                 |

| 12                                                                                                | IODEN                                                                                                                                | l    | I/O DATA ENABLE The I/O Data Enable signal enables the I/O data buffers and is generated by the WD6000. When it is active, the WD6022 drives either D(0:15) or IOD(0:15), depending on the direction set by the IODTR signal.                                                                                                                                                                               |

| 13                                                                                                | IODTR                                                                                                                                |      | I/O DATA TRANSMIT/RECEIVE The I/O Data Transmit/Receive signal controls the direction of the I/O data buffers inside the WD6022. The signal itself is generated by the WD6000 device.    IODTR   DIRECTION   D(0:15) to IOD(0:15)                                                                                                                                                                           |

| PIN NO.                                                                                | NAME               | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------------------------------------------------|--------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 125                                                                                    | IODCBA             |      | I/O DATA CLOCK The I/O Data Clock signal is used to latch the data during reads from the Channel peripherals on the I/O bus. The MEMRD, MEMWR, IORD, and IOWR commands to the peripherals are shorter than the Channel CMD signal. This signal ensures that the                                                                                                                                                                                     |

|                                                                                        |                    |      | data being read meets the timings of the Channel CMD signal.  DATA STEERING/SWAPPING                                                                                                                                                                                                                                                                                                                                                                |

| 86                                                                                     | SWPBYT             | I    | BYTE SWAP When the CPU or DMA accesses an 8-bit port the cycle is split into two. This signal is used to swap the data to the correct byte: D(0:7) are swapped to D(8:15) for a read operation; D(8:15) are swapped to D(0:7) for a write operation.                                                                                                                                                                                                |

| 85                                                                                     | SWPWORD            |      | WORD SWAP This signal swaps words when a 16-bit Channel master communicates with a 32-bit slave. The cycle is split into two and SWPWORD is used to swap data to the correct word: D(16:31) is swapped to D(0:15) for a Channel master read operation and D(0:15) is swapped to D(16:31) for a Channel master write operation. This function is known as data steering.                                                                             |

| 84                                                                                     | SWPDIR<br>(COPRES) | l    | SWAP DIRECTION At power-up, the state of this signal is latched by the WD6030 to determine the presence of the numeric coprocessor. At all other times, SWPDIR determines the direction of the byte and word swap buffers. A low on SWPDIR indicates a read operation (byte swap D(0:7) to D(8:15) or a Channel master write operation (word swap D(0:15) to D(16:31)). A high on SWPDIR indicates a write operation (byte swap D(8:15) to D(0:7)). |

|                                                                                        |                    |      | MISCELLANEOUS                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 66                                                                                     | MODE               | I    | MODE PIN This pin determines the mode of operation for the WD6022 device. When tied to $V_{\rm DD}$ , it puts the WD6022 into the data buffer mode; when it is tied to ground, it puts it into the address buffer mode                                                                                                                                                                                                                              |

| 67                                                                                     | TEST               | I    | TEST PIN This is an active low pin to facilitate board-level testing. When low, this signal tristates all outputs and bi-directional signal lines so that an ATE tester can drive these signals instead.                                                                                                                                                                                                                                            |

| 82                                                                                     | BIAS               | I    | BIAS PIN This pin controls the biasing of the internal buffers, and should be pulled low with a 1.25K ±1% resistor.                                                                                                                                                                                                                                                                                                                                 |

| 3, 24,<br>35,<br>46,57,<br>83, 100,<br>116                                             | V <sub>DD</sub>    | -    | +5 V Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 17, 18,<br>27, 32,<br>38, 43,<br>50, 51,<br>60, 65,<br>76, 87,<br>98, 109,<br>117, 132 | V <sub>SS</sub>    | I    | 0 V Ground                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PIN NO.                                                              | NAME     | TYPE | FUNCTION                                          |

|----------------------------------------------------------------------|----------|------|---------------------------------------------------|

| 68, 69,<br>70, 71,<br>72, 73,<br>74, 75,<br>77, 78,<br>79, 80,<br>81 | Reserved | -    | RESERVED PINS These pins should not be connected. |

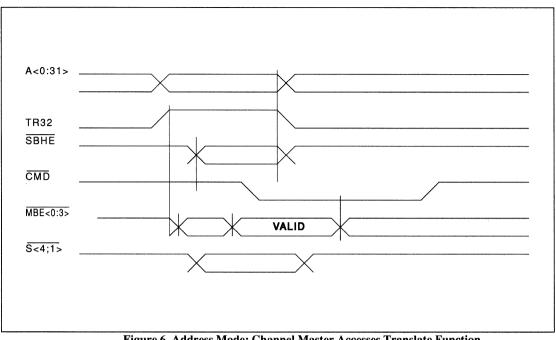

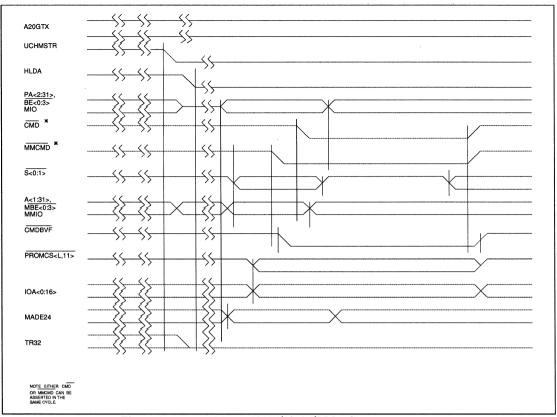

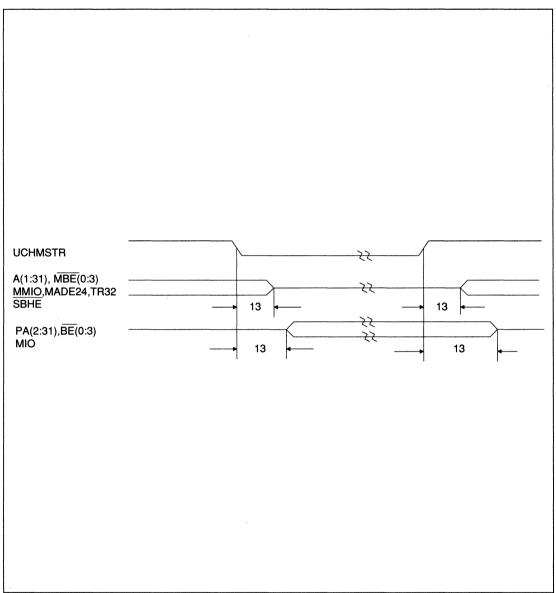

Figure 6. Address Mode: Channel Master Accesses Translate Function

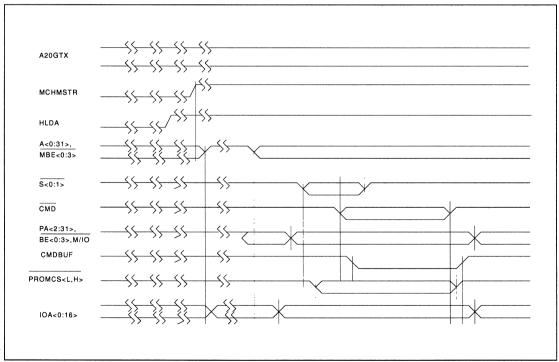

Figure 7. Address Mode: Channel Master Accesses

Figure 8. Address Mode: 80386/80486/DMA Channel Accesses

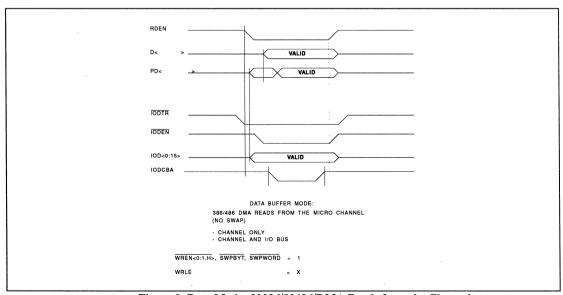

Figure 9. Data Mode: 80386/80486/DMA Reads from the Channel

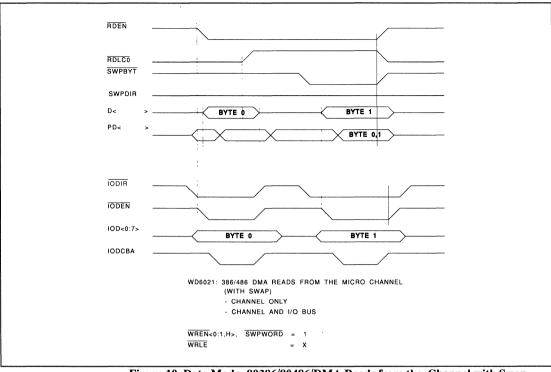

Figure 10. Data Mode: 80386/80486/DMA Reads from the Channel with Swap

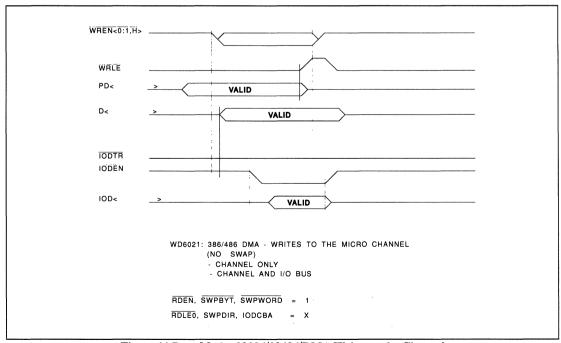

Figure 11.Data Mode: 80386/80486/DMA Writes to the Channel

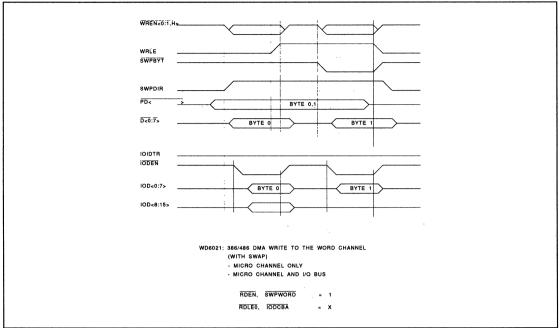

Figure 12. Data Mode: 80386/80486/DMA Writes to the Channel with Swap

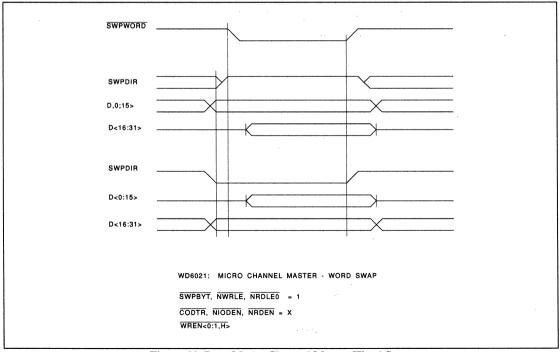

Figure 13. Data Mode: Channel Master Word Swap

PINITS

### 3.0 TECHNICAL SPECIFICATIONS

#### 3.1 ABSOLUTE MAXIMUM RATINGS

The absolute maximum stress ratings for the WD6022 devices are tabulated below. Permanent damage to the devices could result from exposing it to conditions exceeding these ratings.

| PARAMETER           | SYMBOL                            | MIN                   | MAX                   | UNITS      |

|---------------------|-----------------------------------|-----------------------|-----------------------|------------|

| Supply Voltage      | V <sub>DD</sub> - V <sub>SS</sub> | 0                     | 7                     | · <b>V</b> |

| Input Voltage       | VIABS                             | VSS - 0.3             | V <sub>DD</sub> + 0.3 | V          |

| Bias on Output Pin  | VOABS                             | V <sub>SS</sub> - 0.3 | V <sub>DD</sub> + 0.3 | ٧          |

| Storage Temperature | Ts                                | -40                   | 125                   | °C         |

#### 3.2 NORMAL OPERATING CONDITIONS

Exposing the WD6022 to conditions exceeding the normal operating conditions for extended periods of time can affect the long-term reliability of the device. VSS = 0 V

| PARAMETER            | SYMBOL          | MIN  | MAX       | UNITS |

|----------------------|-----------------|------|-----------|-------|

| Power Supply Voltage | V <sub>DD</sub> | 4.75 | 5.25      | V     |

| Ambient Temperature  | T <sub>A</sub>  | 0    | 70        | °C    |

| Input Voltage        | V <sub>IN</sub> | -0.3 | VDD + 0.3 | V     |

| Power Dissipation    | Pw              | -    | TBD       | mW    |

| Supply Current       | Ipp             | -    | TBD       | mA    |

MIN

MAY

## 3.3 DC CHARACTERISTICS (UNDER NORMAL OPERATING CONDITIONS)

SYMBOL

| PARAMETER                                | STWBUL          | IVIIN                     | WAX          | UNITS      |  |  |  |

|------------------------------------------|-----------------|---------------------------|--------------|------------|--|--|--|

| Input Capacitance @ fc = 1 MHz           | Cı              | -                         | 5            | pF         |  |  |  |

| I/O Capacitance                          | C <sub>IO</sub> | -                         | 10           | pF         |  |  |  |

| Logic High Input Voltage                 | ViH             | 2.0                       | -            | V          |  |  |  |

| Logic Low Input Voltage                  | V <sub>IL</sub> | -                         | 0.8          | V          |  |  |  |

| Input Leakage                            | l <sub>IL</sub> |                           | +-10         | μA         |  |  |  |

| Tristate Output Leakage                  | loL             | <del>-</del>              | +-30         | μ <b>A</b> |  |  |  |

| I/O Pin Leakage                          | liol            | -                         | +-40         | μΑ         |  |  |  |

| WD6022 ADDRESS BUFFER MODE (MODE = 0)    |                 |                           |              |            |  |  |  |

| OUTPUTS P                                | ROMCSL, PROMC   | SH, EOT, UCHCM            | D, PA(2:31)* |            |  |  |  |

| Source Current @ V <sub>OH</sub> = 2.4 V | Іон             | -                         | -            | mA         |  |  |  |

| Sink Current @ V <sub>OL</sub> = 0.4 V   | loL             | 4                         | -            | mA         |  |  |  |

|                                          | OUTPUTS BI      | E(0:3), M/ <del>IO*</del> |              |            |  |  |  |

| Source Current @ V <sub>OH</sub> = 2.4 V | Іон             | -                         | -            | mA         |  |  |  |

| Sink Current @ V <sub>OL</sub> = 0.4 V   | loL             | 6                         | -            | mA         |  |  |  |

| OUTPUT IOA(0:16)                         |                 |                           |              |            |  |  |  |

| Source Current @ V <sub>OH</sub> = 2.4 V | Іон             | -                         | -            | mA.        |  |  |  |

| Sink Current @ V <sub>OL</sub> = 0.4 V   | loL             | 8                         | -            | mA         |  |  |  |

| ALL OTHER OUTPUTS*                       |                 |                           |              |            |  |  |  |

| Source Current @ V <sub>OH</sub> = 2.4 V | Іон             | -                         | -            | mA         |  |  |  |

| Sink Current @ V <sub>OL</sub> = 0.4 V   | l <sub>OL</sub> | 24                        | -            | mA         |  |  |  |

PARAMETER

| PARAMETER                                | SYMBOL            | MIN | МАХ | UNITS |  |  |  |

|------------------------------------------|-------------------|-----|-----|-------|--|--|--|

| WD6022 DATA BUFFER MODE (MODE = 1)       |                   |     |     |       |  |  |  |

| OUTPUTS PD(0:31)*                        |                   |     |     |       |  |  |  |

| Source Current @ V <sub>OH</sub> = 2.4 V | . I <sub>ОН</sub> |     | -   | mA    |  |  |  |

| Sink Current @ V <sub>OL</sub> = 0.4 V   | loL               | 4   | -   | mA    |  |  |  |

| OUTPUTS IOD(0:15)*                       |                   |     |     |       |  |  |  |

| Source Current @ VoH = 2.4 V             | Іон               | -   | -   | mA    |  |  |  |

| Sink Current @ VoL = 0.4 V               | loL               | 6   | -   | mA    |  |  |  |

| OUTPUT D(0:31)                           |                   |     |     |       |  |  |  |

| Source Current @ V <sub>OH</sub> = 2.4 V | Юн                | -   | -   | mA    |  |  |  |

| Sink Current @ V <sub>OL</sub> = 0.4 V   | loL               | 24  | -   | mA    |  |  |  |

<sup>\*</sup>The following signals are bi-directional: PA(31:2),  $\overline{\text{BE}}$ (3:0), M/IO, MADE24, TR32, MM/IO,  $\overline{\text{MBE}}$ (3:0), A(31:1), SBHE, PD(31:0), IOD(15:0), and D(31:0).

#### NOTE

- 1. The input pin "BIAS" is connected externally to ground through a 1% 1.25 K ohm resistor, and is part of an internal biasing circuit. Capicitance, leakage, and threshold measurements on this pin do not apply.

- 2. The following signals have internal pullups of 20K: BE(3:2), MBE(3:0), MM/IO, M/IO.

- 3. When TEST = 0, all outputs and bi-directional signal lines are tristated.

| PARAMETER                                                     | SYMBOL | MIN | MAX | UNITS |  |  |

|---------------------------------------------------------------|--------|-----|-----|-------|--|--|

| WD6022 ADDRESS BUFFER MODE (MODE = 0)                         |        |     |     |       |  |  |

| PROMCSL, PROMCSH, EOT, UCHCMD                                 | CL     | 50  | -   | , pF  |  |  |

| BE(0:3), M/IO*                                                | CL     | 120 |     | pF    |  |  |

| PA(2:31), IOA(0:16)*                                          | CL     | 120 | -   | pF    |  |  |

| MADE24, TR32, MM/ <u>IO, MMC,</u><br>MBE(0:3), A(1:31), SBHE* | CL     | 240 | - ` | pF    |  |  |

| WD6022 DATA BUFFER MODE (MODE = 1)                            |        |     |     |       |  |  |

| PD(0:31), IOD(0:15)*                                          | CL     | 120 | -   | pF    |  |  |

| D(0:31)*                                                      | CL     | 240 | _   | pF    |  |  |

#### 3.4 A.C. LOAD SPECIFICATIONS

\*The following signals are bi-directional: PA(31:2),  $\overline{\text{BE}}$ (3:0), M/ $\overline{\text{IO}}$ , MADE24, TR32, MM/ $\overline{\text{IO}}$ ,  $\overline{\text{MBE}}$ (3:0), A(31:1), SBHE, PD(31:0), IOD(15:0), and D(31:0).

#### NOTE

1. The following signals have internal pullups of 20K: BE(3:2), MBE(3:0), MM/IO, M/IO.

## 4.0 TIMING

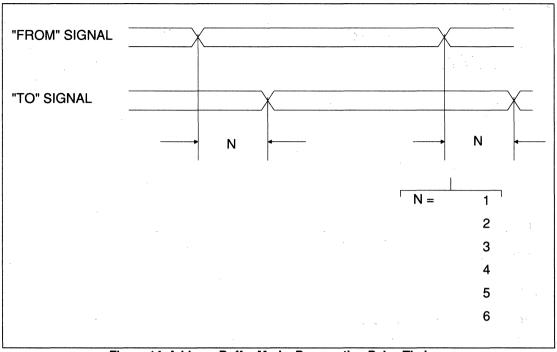

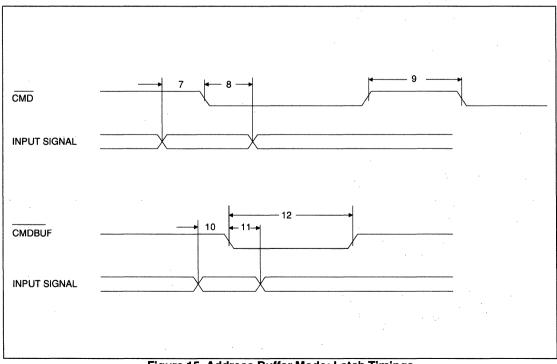

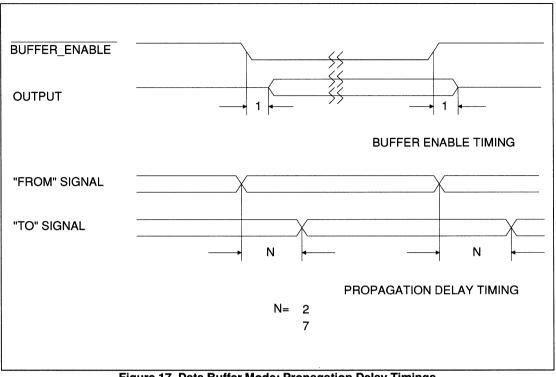

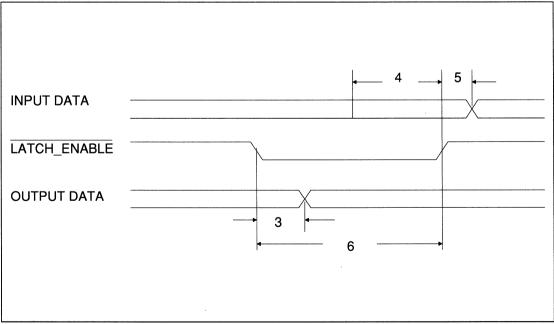

| PARAM | DESCRIPTION                                       | MIN | MAX   | UNITS |