# The proLogic<sup>™</sup> Compiler

# User's Guide

je.

1989

# The proLogic<sup>™</sup> Compiler User's Guide

#### **IMPORTANT NOTICE**

Texas Instruments (TI) provides this software **AS IS** without warranty of any kind, either expressed or implied, including but not limited to the implied warranties of merchantability and fitness for a particular purpose. TI may discontinue, make improvements to and or change the program(s) described herein at any time and without notice. TI does not warrant that this software package will function properly in every software/hardware environment.

Users are authorized to copy, duplicate, and distribute this product for internal use only without further permission from TI provided that the copyright is maintained on each copy. Selling of this product without prior consent in writing from TI is prohibited.

proLogic™ Development Software, Release 1.97

This logic compiler was prepared for distribution by Texas Instruments, Incorporated, expressly to support devices manufactured by them. A complete universal compiler, including Texas Instruments devices, is also available directly from Inlab, Inc. Contact Inlab Customer Service at (303) 460–0103 and ask for information or assistance regarding proLogic.

Assistance on programming Texas Instruments Programmable Logic is also available, upon request, from the nearest TI field sales office, local authorized TI distributor, or by calling the Texas Instruments PLD Hotline (214) 997–5666.

Copyright © 1988, Inlab, Inc.

All Rights reserved.

#### TRADEMARKS

**IBM** is a registered trademark of International Business Machines Corporation.

**IMPACT** is a trademark of Texas Instruments Incorporated. **proLogic** is a trademark of Inlab Incorporated.

### Preface

\*\*\*\*\*

## **Read This First**

This Preface contains a brief description of the contents of *The proLogic Compiler User's Guide*.

How to Use this Manual

| Section 1  | How to Begin<br>Description of the package contents along with installation procedures.                                                                                                   | 1  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Section 2  | Programmable Logic                                                                                                                                                                        | 3  |

| Section 3  | PLD Design Implementation                                                                                                                                                                 | 7  |

| Section 4  | proLogic diagrams<br>Introduction to the proLogic diagrams utilized in the guide.                                                                                                         | 13 |

| Section 5  | Symbols                                                                                                                                                                                   | 15 |

| Section 6  | Expressions                                                                                                                                                                               | 19 |

| Section 7  | The Title Block                                                                                                                                                                           | 23 |

| Section 8  | Truth Table Blocks                                                                                                                                                                        | 25 |

| Section 9  | State Diagrams                                                                                                                                                                            | 29 |

| Section 10 | Test Vector Blocks                                                                                                                                                                        | 37 |

| Section 11 | Include Files                                                                                                                                                                             | 41 |

| Section 12 | Signal Specifications<br>Explanation of how to assign the proper signal name to a Boolean expression.<br>(ie., active high or low, internal or external, set or reset, or output enable.) | 43 |

| Appendix A | Designer's Guide to TIBPSG507                                                                                                                                                             | A1 |

| Appendix B | Device Cross Reference List                                                                                                                                                               | B1 |

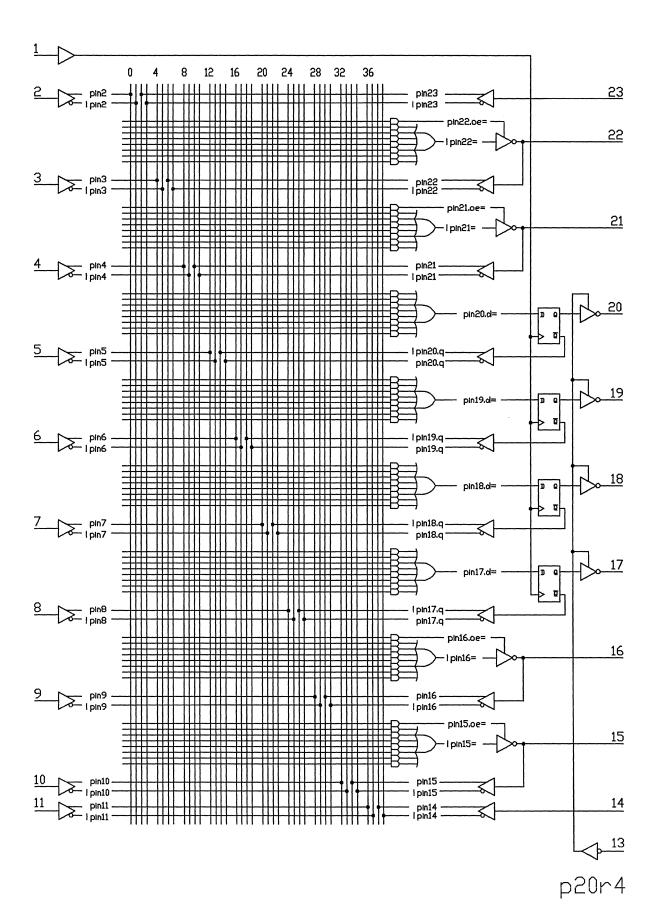

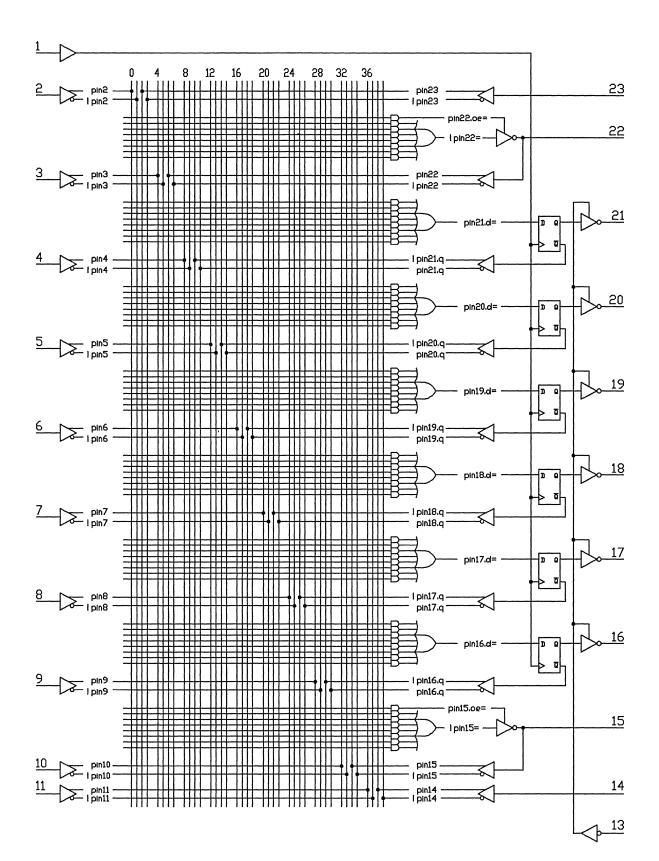

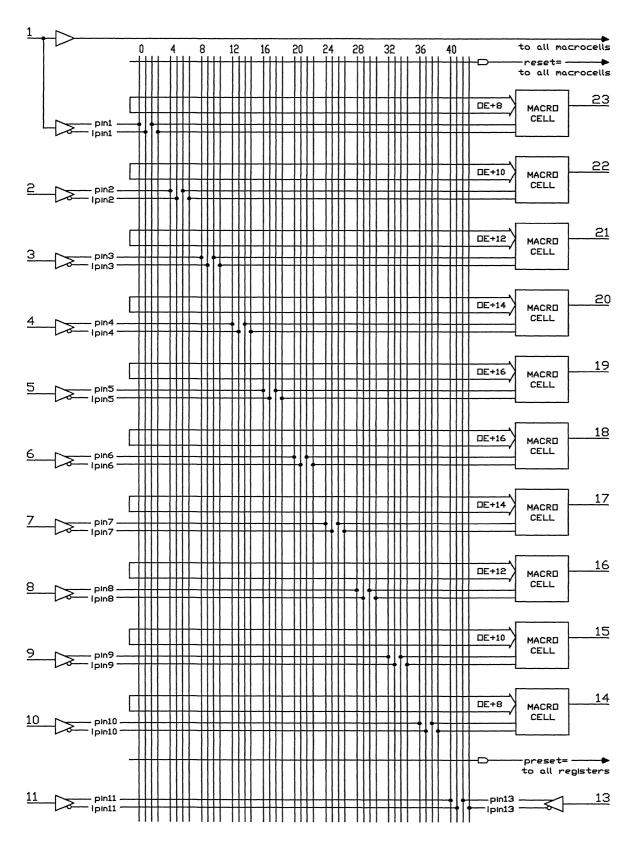

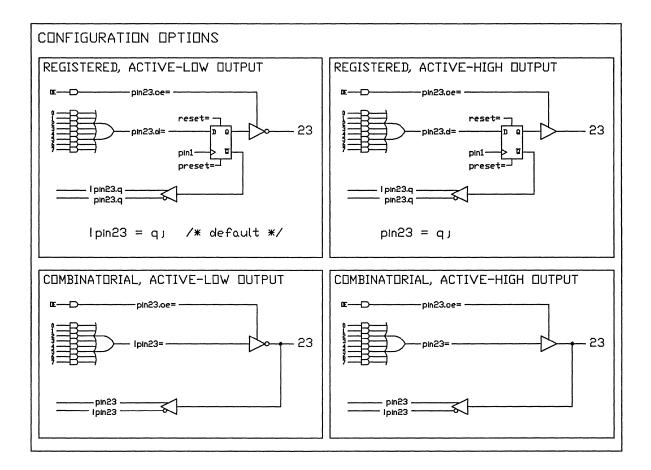

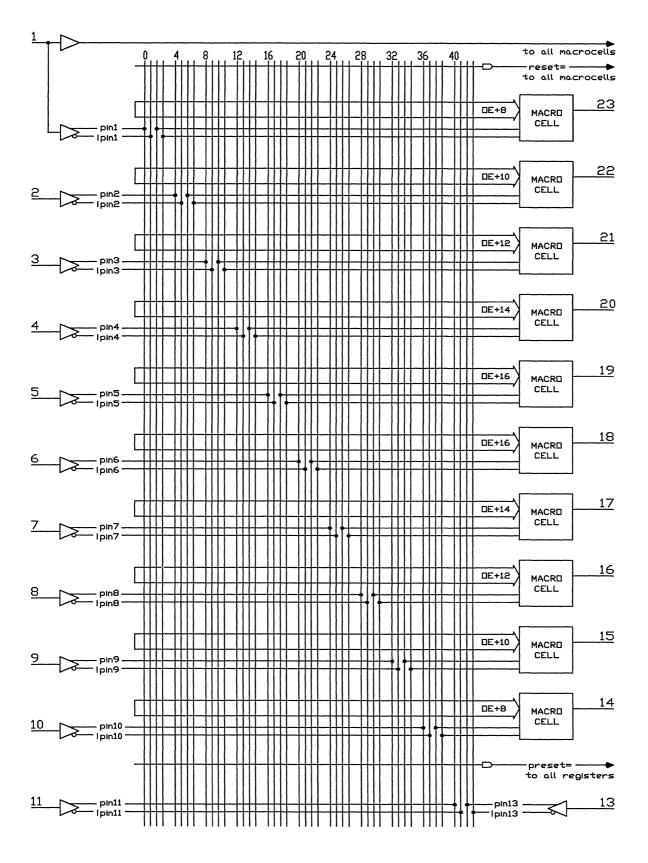

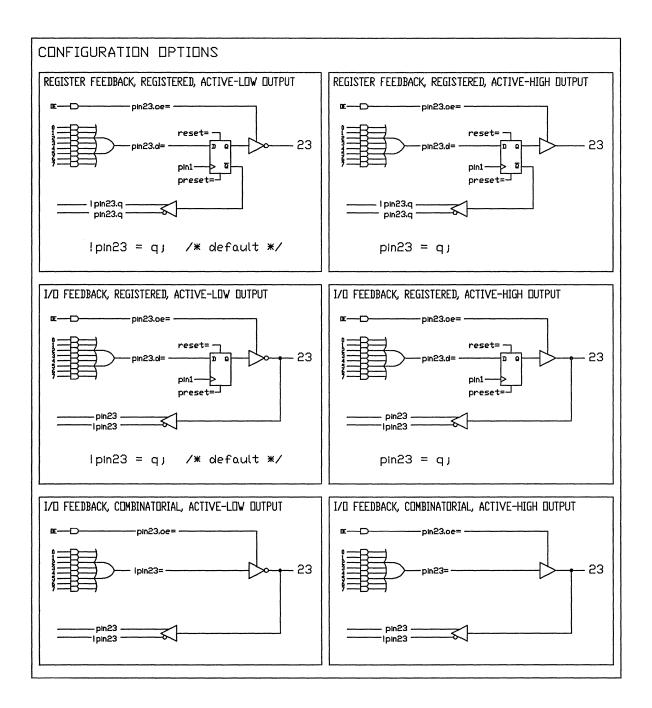

| Appendix C | Logic Diagrams                                                                                                                                                                            | C1 |

#### Preface

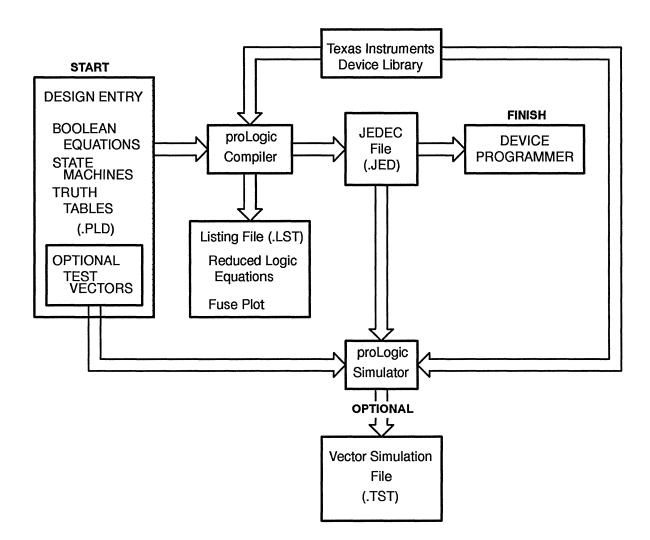

The proLogic compiler is a software development design tool used to program Texas Instrument Programmable Logic Devices (PLD). This development software package quickly converts your logic design to a JEDEC fuse map that can be downloaded to a device programmer. proLogic allows you to describe your logic design in any of the following formats:

- **Truth Table**

- Boolean Equations

- **G** State Diagrams

From your logic design, the proLogic compiler will create a standard JEDEC fuse map. The JEDEC file can be downloaded to a device programmer to produce a functional programmed device. Many Texas Instruments authorized distributors provide these programming services.

The proLogic compiler also serves as a functional test vector simulator. The simulator uses the fuse list portion from the JEDEC file to create a functional device model. It can then execute the simulation vectors against this model. The results are automatically placed in a file for evaluation.

The proLogic compiler, when combined with a device programmer, will allow you to create integrated circuits to your own specifications. The advantages to this new design methodology are numerous:

- Lower chip count

- Reduced board space

- Lower power requirements

- Higher reliability (fewer interconnects)

- Proprietary design protection (fuse protection)

- Fewer parts in inventory

- Greater design flexibility

The proLogic compiler is complete and ready for installation on your IBM<sup>®</sup> compatible PC. The following block diagram shows the steps from design to proLogic to a programmed device.

proLogic Block Diagram

vi

### **How To Begin**

### The proLogic Compiler Package contains:

- a proLogic Compiler User's Guide

- three proLogic Diskettes

### The proLogic Diskette contains:

- the executable files

- a README file

- Header files (.H) which apply to multiple Programmable Logic Devices

- the Texas Instruments PLD Architecture files

### Installation

- Step 1: On your IBM or IBM compatible PC, make a new directory on the hard disk and call it PROLOGIC.

- **Step 2:** Change directories into your new PROLOGIC directory and copy all of the files on the diskettes into the new directory.

- Step 3: The file, NAND3.PLD is a sample Application PLD (sample program source file) needed to describe the PLDs.

Compile the sample device specification by entering the command.

IC NAND3

Compiling NAND3 produces the output files NAND3.JED and NAND3.LST. The JEDEC file can be downloaded to your device programmer. The listing file is a fuse plot showing the programmed device. Step 4: Simulate device programming and testing by entering the command

LS NAND3

Logic Simulation uses NAND3.JED to produce the output file NAND3.TST. All of these files including the source file, are text files so you can print, type, or edit them to see the results.

The files on the Architecture Description diskettes may all be copied to your PRO-LOGIC directory if you have enough disk space. If not, you can selectively copy the files needed for your programmable devices.

This is the time to look at the README file on the Installation Diskette. This file contains last-minute information that may not be in the User's Guide.

### **Programmable Logic**

A Programmable Logic Device (PLD) is a type of integrated circuit whose function is field—configured. These devices allow you to create integrated circuits to your own specifications at a reasonable cost, thus reducing the chip count.

Programmable Logic Devices have the same basic kinds of digital building blocks that Small Scale Integration (SSI) devices have. The difference between SSI devices and PLDs is primarily the higher levels of integration in PLDs.

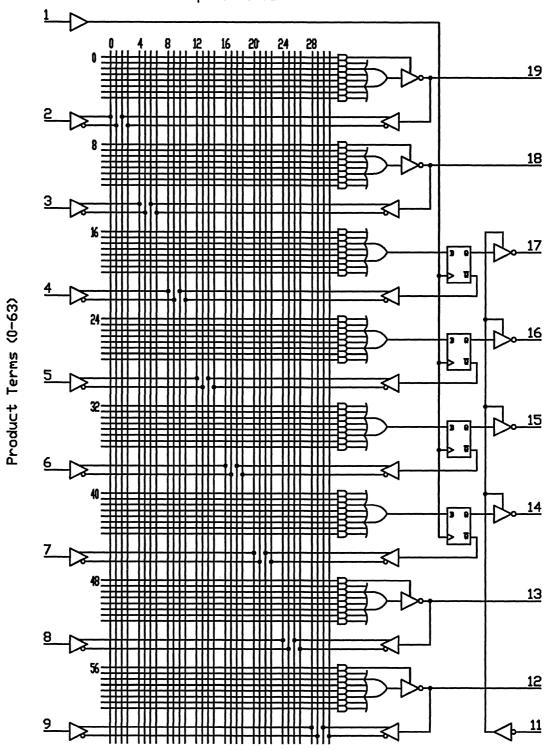

There are more input signals per gate. Even a common PLD like the TIBPAL6R4 has 32-input AND gates.

There are more gates per device. The 16R4 has sixty-four 32-input AND gates. The size of these devices has required a new form of logic notation. This notation permits the semiconductor manufacturer to specify the function of a PLD in a concise, tabular format.

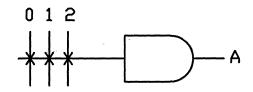

Conventional schematics tend to flow from left to right, with input signals on the left and output signals on the right. Thus a three input AND gate is drawn.

Figure 1. SSI Three Input AND Gate

The new PLD logic notation retains the convention that output signals are on the right. The change is that the input signals flow into a gate vertically from the top or bottom. A PLD AND gate is drawn

Figure 2. PLD Three Input AND Gate

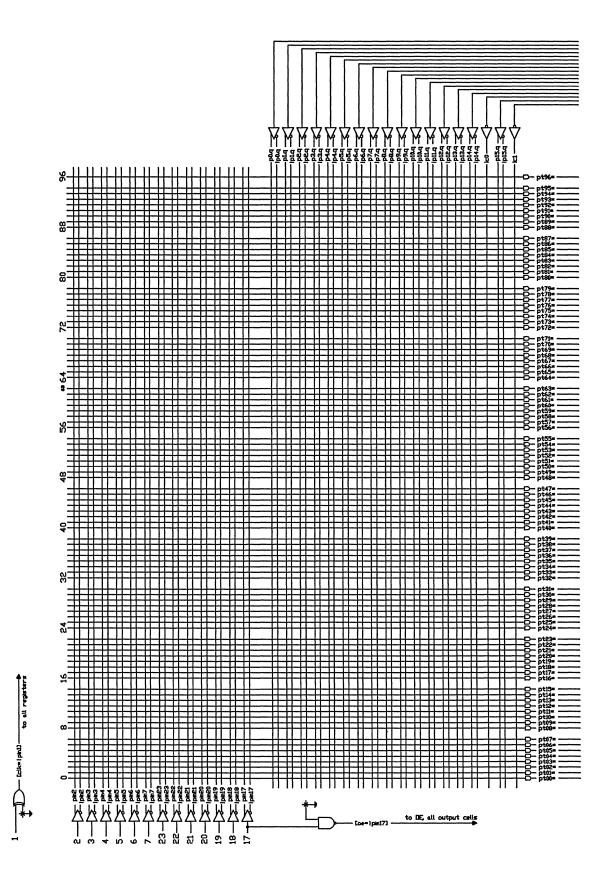

These PLD AND gates are also called product terms. A product term refers to any n-input AND gate. The main reason for vertical inputs is that PLDs have a very regular structure. In the 16R4, all 32 of the input signals are input to each of the 64 AND

gates. This permits the whole logic structure of the device to be concisely noted in tabular format.

|   | U | 1            | C |   | 3  |   | 4  |    | ו  | D  | 1          |          | 1 | Ø | 3 |          | U  | ш  |     |     | Ľ  | 1  | 21 | 1 | IJ | ) | 10 | ) [      | /  | lÖ | 1 | 2  | 6 | U. | ۲  | Ć        | 5  | ٢J | 1 | - 1 | 2   | ) (      | :0 | 21 | C | Ö.               | ۲) | J            | 13 | L        |          |           |        |  |

|---|---|--------------|---|---|----|---|----|----|----|----|------------|----------|---|---|---|----------|----|----|-----|-----|----|----|----|---|----|---|----|----------|----|----|---|----|---|----|----|----------|----|----|---|-----|-----|----------|----|----|---|------------------|----|--------------|----|----------|----------|-----------|--------|--|

|   | 1 | T            | T |   |    | , | L  | J  | ~  | L  | T          | ,        |   | L | J |          | L  | L  | ,   | ,   | L  | J  |    | L | L  | , | J  |          | ١. | L  |   |    |   | L  | J  | ~        | ١. | L  |   | T   | 1   | 6        | ١. | L  |   | L                | L  | T            | J  | ,        |          | <b>`</b>  | <br>۸n |  |

| _ | C | $\mathbf{v}$ | 4 | ~ | 1  |   | C  |    |    |    |            |          |   | T |   |          |    |    |     |     | J. | S  | ò  |   |    |   | T  | <u> </u> | 1  | J  | 5 | 1  |   | J. | S. | ċŚ       | 1  |    |   | Ś   | 5   | $\Sigma$ |    |    |   | $\mathbb{T}$     | J. | V            |    | <i>.</i> | ]—       | $\subset$ |        |  |

| _ | C | <u>بلا</u>   | 4 | 5 | Ż. | • | L  | اد | ذغ | Ŀ. | 4          | <u> </u> | _ | T | ~ | -        | L  | Ś  | i_  |     | 1  | J  | Ż  |   | J. |   |    | 1        | 1  | 4  | 5 | 1  |   |    | N. | <u> </u> | 1  |    |   | Ś   | 5   | 2        |    | J. |   | $\mathbb{C}^{:}$ | 4  | V            | 5  | -        | <u> </u> | $\subset$ | 25     |  |

| _ | T | J.           | 1 |   | 1  |   | L  | 5  | ä  | Ŀ  | 4          | Ĺ        |   | T | 5 | <u> </u> | L  | Ś  | è.  |     | J. | S. | ò  | È | Ý  |   | 1  | 1        | 1  | ┛  | 5 | 1  |   |    | N  | 2        | 1  |    |   | J.  | 5   | 25       |    |    |   | $\mathfrak{D}$   | 1  | J.           |    | ·        |          |           | 43     |  |

| _ | ¢ | $\mathbf{v}$ | 4 |   | 1  |   | Ţ. | Ś  | ä  | Ŀ  | J.         | Ĺ        |   | T | 5 | ~        | Ŀ  | 5  | i_  |     | J  | 5  | ò  | C | Ý  |   | 1  | 1        | 1  | J  |   | 1  |   |    | Ś  | ۵        | 1  | T  |   | Š.  | ~   | 3        |    | J. |   | $\mathbf{T}$     | 1  | $\mathbf{v}$ | 5  | 1        |          |           | 24     |  |

| _ | Ŷ | ¥            | 4 |   | 1  |   | P  | 5  | 2  | 1  | 4          | <u> </u> |   | T | 5 |          | 6  | S. | ė.  |     | J. | Ś  | ٤Ś | È | J. |   | 1  | 1        | ~  | J  | 5 | 1  |   | 4  | >  | 2        | 1  | Ţ. |   | Y   | • • | 25       | 2  |    |   | $\mathfrak{T}$   | 4  | V            | 5  | į        |          | <u>۲</u>  | 45     |  |

| _ | Ŷ |              |   |   |    |   | P  | N. | 2  | 4  | <u>ل</u> د | <u> </u> |   | T | 5 | 1        | J  | Š. | į., | , i | J. | Ś  | ذع | È | 4  |   | 1  | <u> </u> | 1  | J  | 5 | i. |   | 1  | Ś  | ذع       |    |    |   | 4   | 5   | 2S       |    |    | • | $\mathbf{T}$     | 1  | 4            | 1  | 1        |          | <u>`</u>  | ÅĞ     |  |

| _ | T |              |   |   |    |   | Ţ. | S. | 25 | 6  | 4          | /        |   | T | 5 | 1        | J. | Š. | į., |     | 4  | 5  | 2  | 2 | Y  |   | 1  | 1        | 2  | L  | 5 | 1  |   | 4  | >  | 2        |    | T. |   | 4   | 2   | ž        | 2  | 1  |   | T.               | 1  | 4            | 5  |          |          | <u> </u>  | ÅŽ     |  |

|   | Τ | T            | T | 1 | r  |   | T  | 1  | `  | r  | T          | •        | • | T | 1 |          | r  | T  |     | •   | T  | 1  | ~  | Γ | T  | • | T  | 1        | Ľ  | T  | 1 | ľ  |   | T  | 1  | ~        | Ľ  | T  |   | T   | 1   | ٢1       | Ľ  | T  | • | T                | T  | T            | 1  | •        | <b>.</b> |           |        |  |

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

Figure 3. Eight 32–Input AND Gates

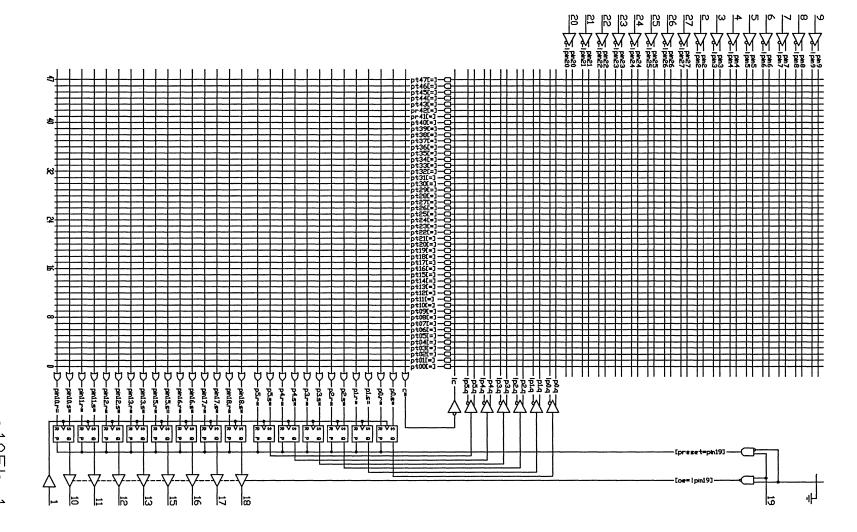

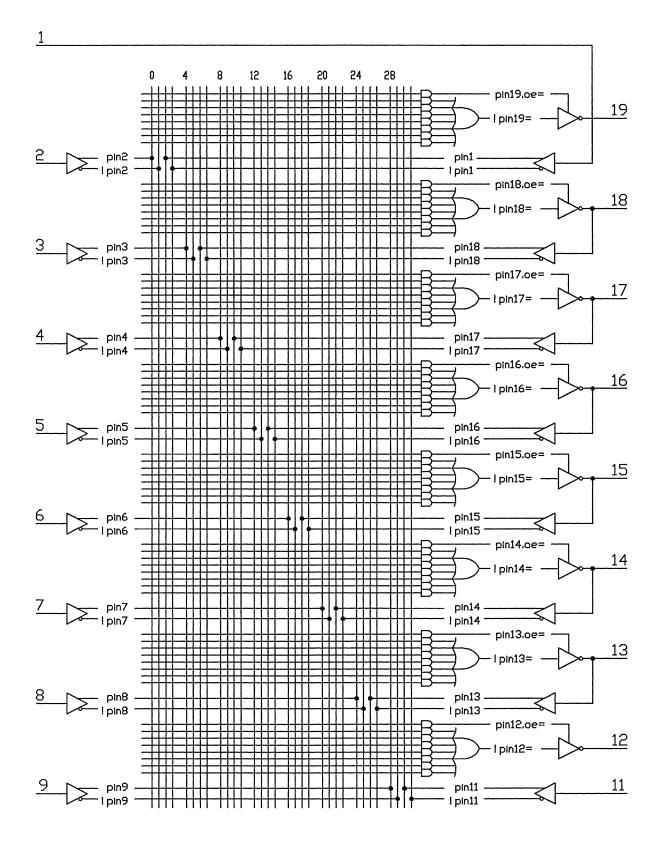

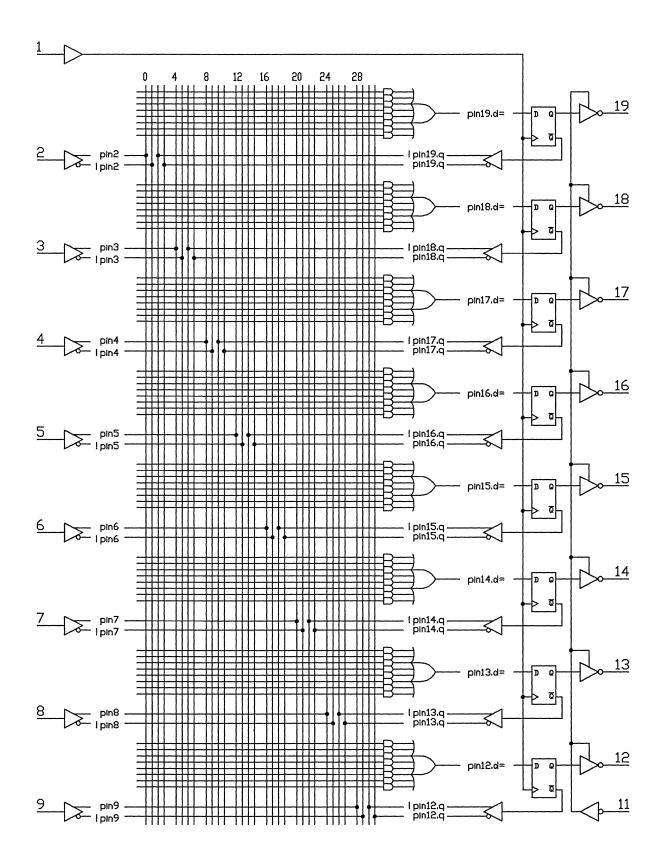

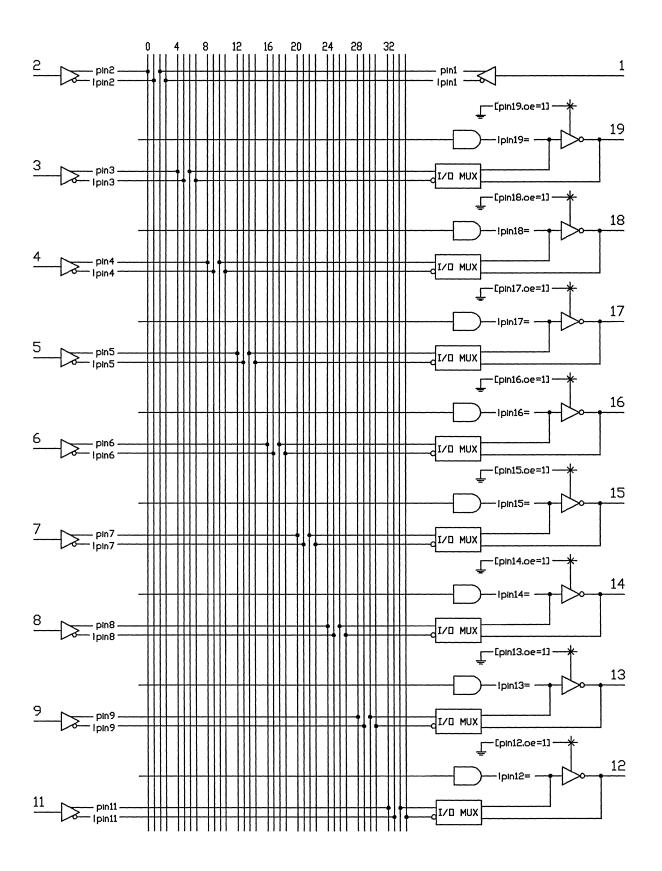

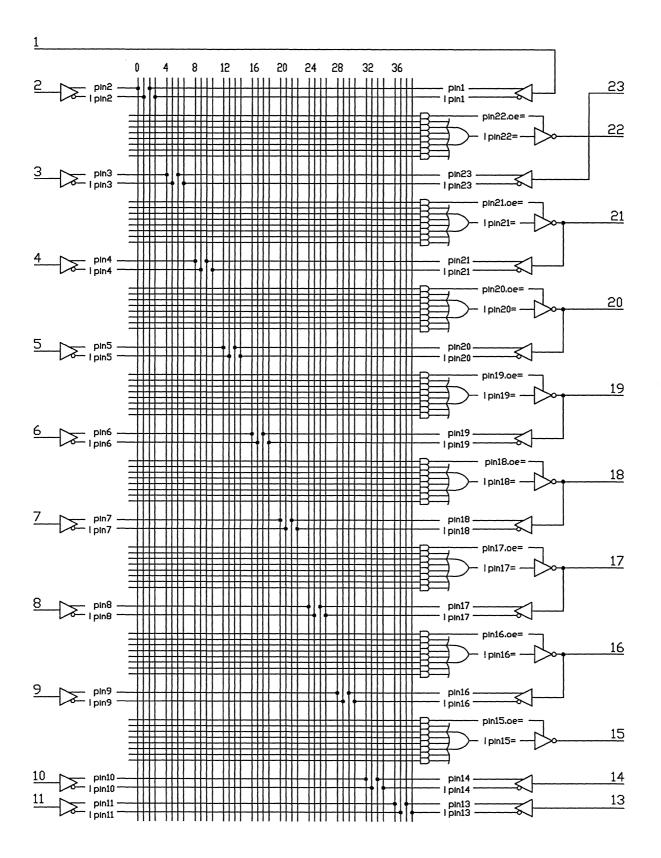

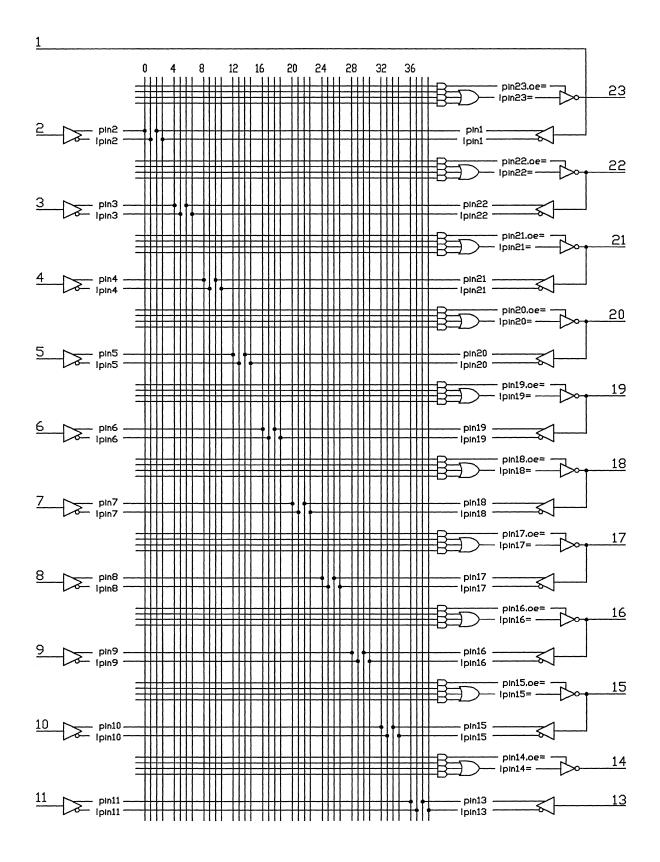

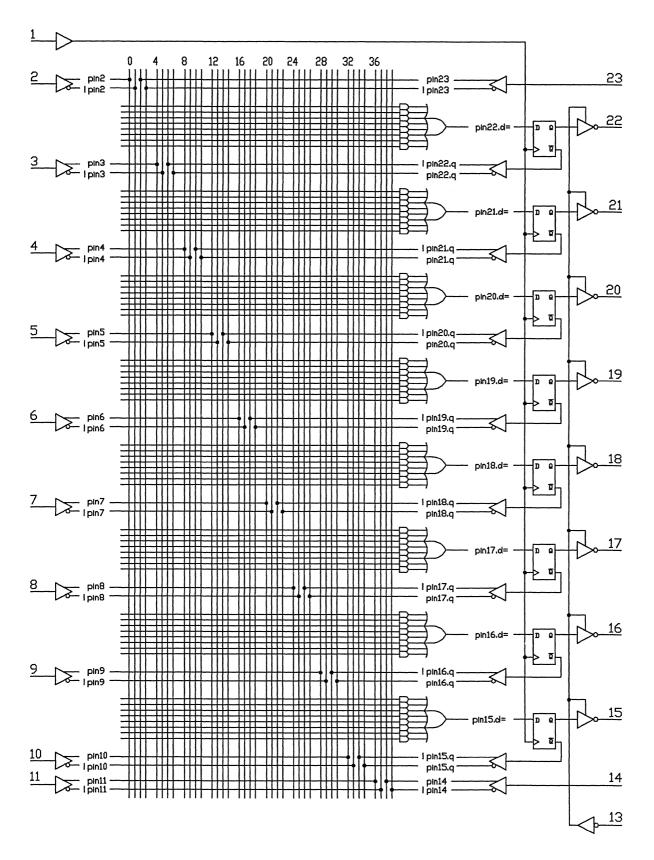

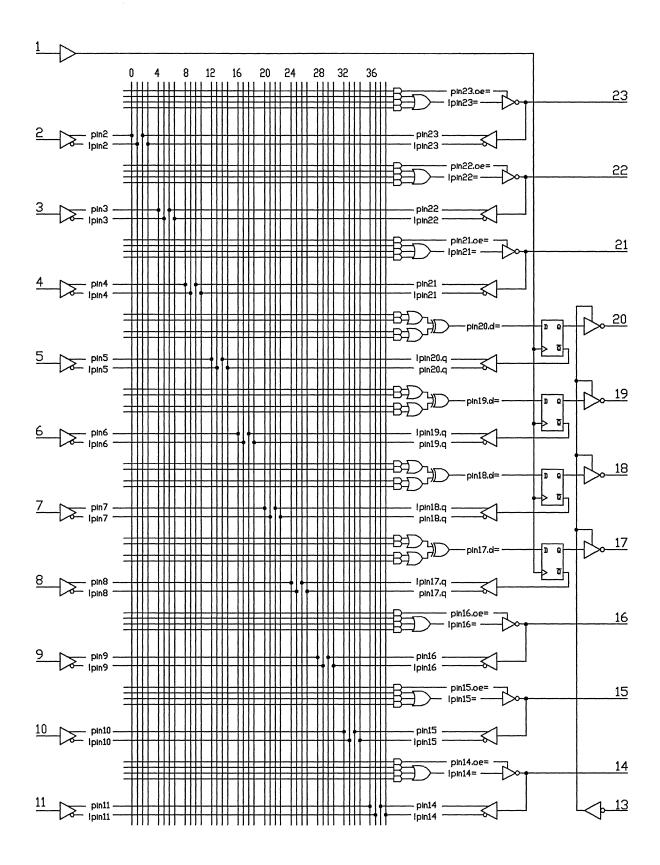

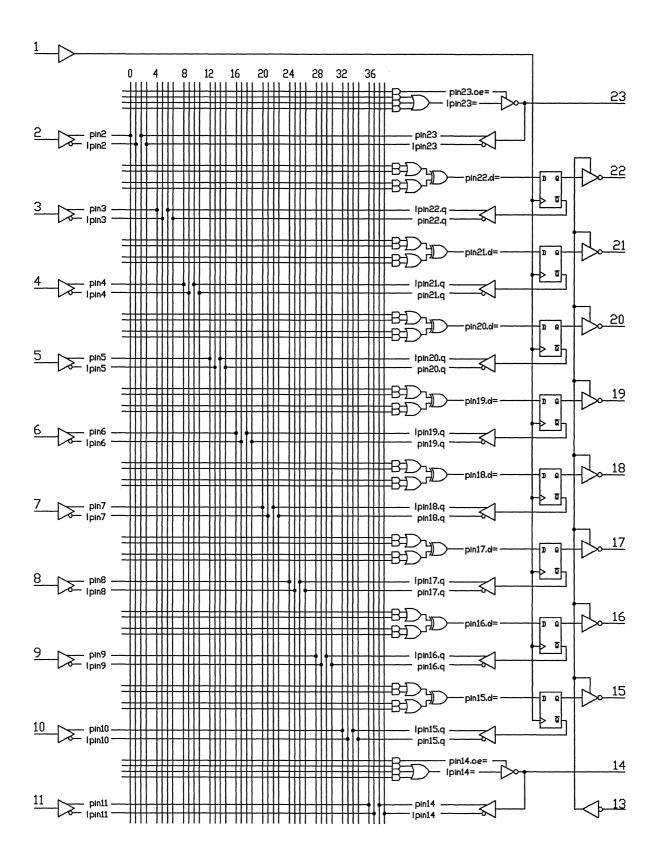

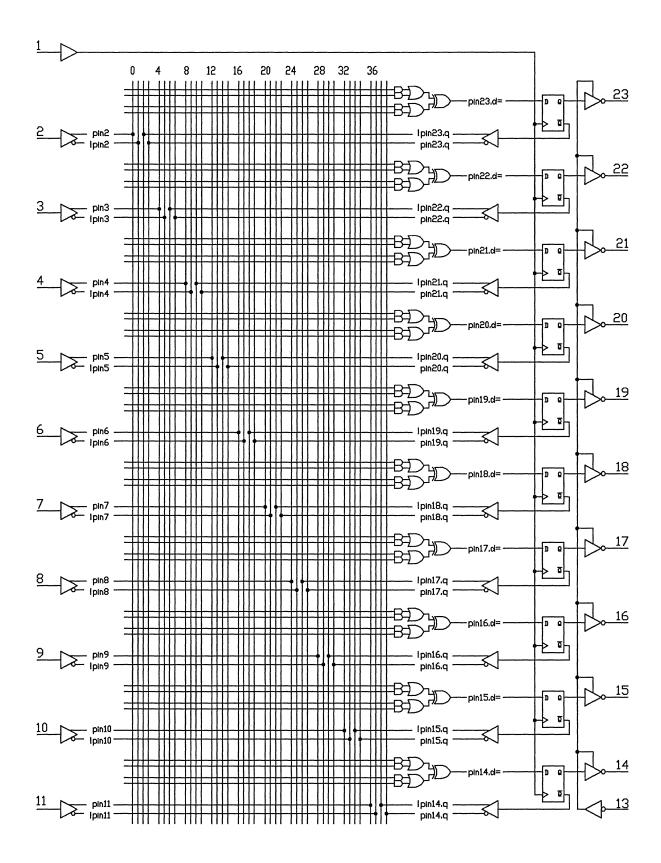

The 16R4 PLD is a 20 pin device. When the power, ground, clock, and output enable pins are substracted, the total I/O pin count is 16. Figure 4 shows how the sixty–four 32–input AND gates are interfaced to the I/O pins.

Figure 4 shows that the device in its unprogrammed state doesn't do anything. The output of all 64 AND gates is logic LOW because the input buffers feed both the true and the complement of all inputs into all the AND gates. In Boolean Logic notation:

a & !a = 0

for all AND gate output.

The basic difference between building a circuit using SSI devices and building a circuit with PLDs is the way in which the gates form a circuit. With SSI devices the gates are connected with wires or traces. Within a PLD, the gates are connected by a process called programming.

A circuit is built within a PLD by disconnecting inputs from gates. In this respect, building a PLD circuit is the exact opposite of building an SSI circuit. A PLD in its initial state has all possible gate connections already made. Programming consists of removing the connections that are not needed for your design. The connections that remain define function of the programmed device.

The notation used to show a programmed device is to draw Xs where connections remain, and draw nothing where connections have been removed. (In most programmed PLDs the number of connections remaining after programming is a lot less than the ones removed, so this convention results in a less cluttered diagram.) To further reduce the number of Xs, a gate with all connections intact is drawn with an X in the gate symbol itself rather than drawing individual Xs at each gate input.

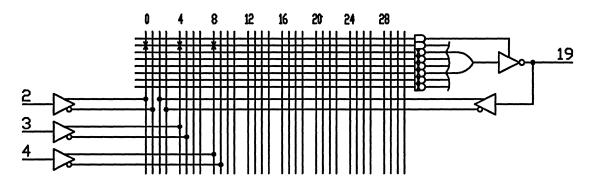

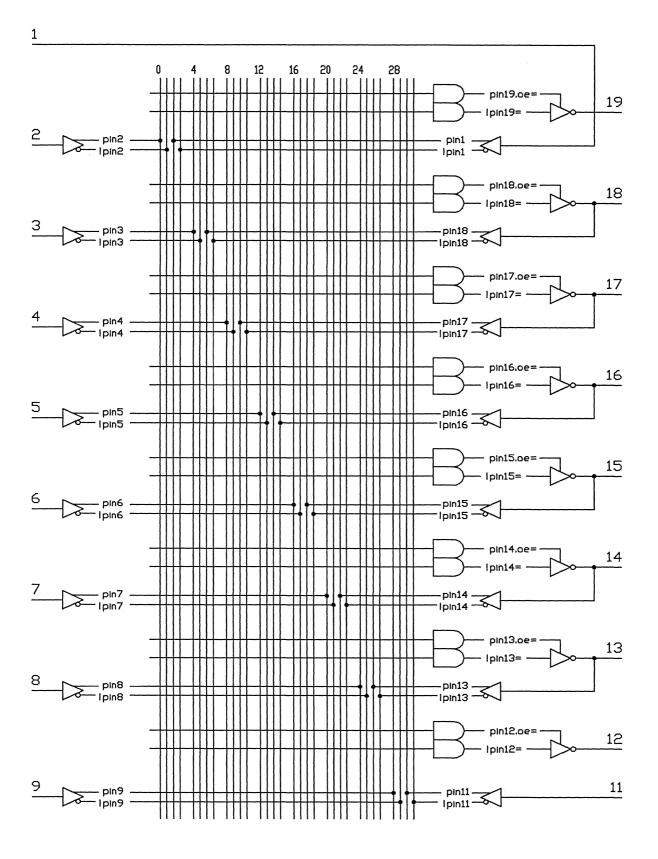

Semiconductor manufacturers ignore this convention when printing the logic diagrams in PLD data books. It is assumed you know that an X is implied at all intersections. Figure 5 shows the part of a 16R4 which has been programmed to implement a 3-input NAND gate. The output is on pin19. The inputs are on pin2, pin3, and pin4.

Inputs (0-31)

Figure 4. 16R4 Logic Diagram

Figure 5 also illustrates one other PLD feature which you should know. The PLD gates are implemented so that when all gate inputs are disconnected, the gate output is asserted. Figure 5 shows the output buffer for pin 19 as always enabled.

Figure 5. A 3-input NAND Gate

### **PLD Design Implementation**

Implementing a digital logic design using PLDs is about the same as implementing a design with SSI devices except you need a development tool called a device programmer to remove the unwanted connections from the internal gates of the PLD.

#### **Device Programmers**

A device programmer is an electronic machine which programs the specified cells of a programmable device. PLDs are available in many technologies. A programming algorithm is defined for each type of device. These algorithms involve voltages and currents not used during normal device operation. As might be expected, the number of different programming algorithms is relatively large because algorithms can vary by both product technology and manufacturer.

Texas Instruments continually evaluates new programming equipment. TI Programmable Logic data books are a good reference source for device programmer vendors.

### **JEDEC Files**

The device programmer vendors have made it as easy as possible for you to specify your requirements. All device programmers accept an input file in a standard format. This file is called a JEDEC file because its format was developed by the Joint Electron Device Engineering Council (JEDEC). JEDEC files, being comprised of ASCII characters, are also readable as text files. This example of a fuse list line of a JEDEC– standard file

L040 100110010101011111\*

is interpreted by the device programmer to mean:

1. program cell 40. The string of 1s and 0s which follow the L040 define the value of consecutive cells after programming. 1 means program the cell. The L040 gives the decimal address of the first cell in the string defined by the line.

2. do not program cell 41. The second digit in the string is a 0 which means do not program the cell.

3. program cells 43, 44, 47, 49, 51, 53, 54 and 56 through 59.

Another kind of JEDEC-standard line is this example of a test vector:

#### V01 NNN010110N10LLLHHNNN\*

These lines are used by the device programmer to functionally test the programmed device. The V01 is a sequence number. The other characters are called test conditions. The first applies to device pin 1, the second to pin2, and so forth. This sample shows a 20-pin device. Test condition N means do nothing, so the first 0 means apply logic low voltage to pin 4. 1 applies logic high and L and H test for output level low and high.

### The proLogic Compiler

The proLogic Compiler is an interface to a device programmer. It accepts your specifications in symbolic form, manages the task of specifying each of the thousands of cell states, and produces a JEDEC file to instruct the device programmer.

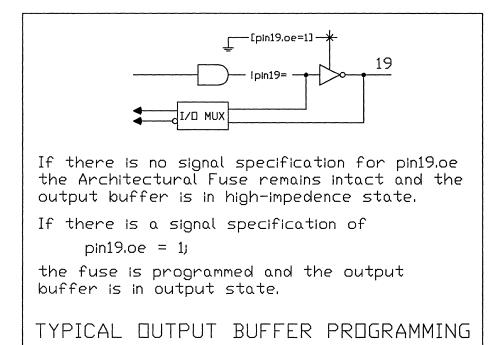

To see how it works, let's take the example at the end of Section 2. It shows a 16R4 programmed to implement a 3-input NAND gate. The output is to be pin19. The inputs are on pin2, pin3 and pin4. To make the JEDEC file control the device programmer, we must prepare a PLD specification file.

The PLD specification is a simple text file which tells proLogic which cells to program in the PLD. proLogic takes its input from a source file in the same way that a compiler for microprocessors does. In order to program a 16R4 so that pin19 is a 3-input NAND gate, we need a source file called NAND3.PLD which has the following three lines:

```

include p16r4;

!pin19 = pin2 & pin3 & pin4;

pin19.0e = 1;

```

The first line specifies the PLD to be programmed. The other lines specify the two signals required to implement the circuit.

Once NAND3.PLD is available, entering the DOS command

LC NAND3

executes the proLogic Compiler. The execution result is a JEDEC file named NAND3.JED which specifies the 61 unwanted connections to be programed by the device programmer. The following is the part of the file which has the fuse list lines.

While preparing the JEDEC file, the compiler may find errors in your program. When it does, it describes what seems to be wrong on the computer display. The error text completely describes the problem, so there is no need for you to look up error codes in the manual. Another file called NAND.LST is also created which allows you to read the NAND3.JED file. The part of the file which describes pin19 of the 16R4 looks like this:

```

proLogic Compiler (Fuse Plot A100) V2.00

Serial bxaw0

Copyright (C) 1988 INLAB, Inc.

p16r4 revision 89.2.11

11 1111 1111 2222 2222 2233

0123 4567 8901 2345 6789 0123 4567 8901

0 ---- ---- ---- ---- ----

OE

1 X--- X--- X--- ---- ----

+

+

+

!pin19

+

+

+

+

4

5

6

7

8

9

pin2

3

pin1

18

17

16

15

14

13

11

Legend:

: Cell intact

х

(JEDEC 0)

: Cell programmed (JEDEC 1)

X- : True input term

-X : Complement input term

XX : Any XX pair in a product term yields product term

LOW.

-- : No input term (don't care).

A product term com-

prised

entirely of -- yields product term HIGH.

```

Compare the NAND3.LST file to Figure 5. This format, called a fuse plot, is just a printer oriented version of the logic diagram. It has some new words in it – an input term is another word for a signal; a product term is another word for AND gate. Other than that, the fuse plot is about the same as a logic diagram.

#### The proLogic Simulator

The proLogic Simulator is a software version of a device programmer. To load it, enter the DOS command

LS NAND3

The simulator uses the fuse list lines from the JEDEC file (NAND3.JED) to create a functional device model. It then executes the test vectors against this model. The test results are placed in file NAND3.TST:

proLogic Simulator V2.00 Copyright (C) 1988 INLAB, Inc. Architecture Description: p16r4.lxa JEDEC Fuse Information: nand3.jed JEDEC Test Vectors: nand3.jed V1 NOOO NNNN NNNN NNNN NNHN V2 NOO1 NNNN NNNN NNNN NNHN V3 NO10 NNNN NNNN NNNN NNHN V4 NO11 NNNN NNNN NNNN NNHN V5 N100 NNNN NNNN NNNN NNHN V6 N101 NNNN NNNN NNNN NNHN V7 N110 NNNN NNNN NNNN NNHN V8 N111 NNNN NNNN NNNN NNLN

No errors detected with 8 Test Vectors.

You will find the same test vectors in NAND3.JED. The more readable source which created them is in NAND3.PLD.

In the example, no errors were found by the simulator. When errors exist, the simulator notes them with a single character code. At the end of the test listing, it appends a legend to explain the meaning of the error codes. This puts all the information you need in one place. There is no need to refer to the manual for a description of the error codes.

### proLogic Simulator Input Files

When you run the simulator, you will need to supply the name of the Test Vectors file. It is a text file in JEDEC 3–A format which contains the test vectors (JEDEC field V) to be executed against the compiled device model. The DOS path name of the test vector file is the first parameter of the DOS command as shown in these examples:

> LS VECTORS LS TEST.JED LS \TEST\VECTORS.VF1

When no file extension is specified, proLogic defaults to (.JED).

If your Test Vectors were created by the proLogic Compiler, that's the only parameter required. If not, the following are other options which can be used.

#### The -j Option

This option specifies the DOS path name of the Fuse Information file. It is also a text file in JEDEC 3–A format. It contains the programming information (JEDEC field F) which specifies the device function. Example:

LS VECTORS -JFUSES.JED

When no file extension is specified, proLogic defaults to (.JED). When the –j option is not supplied, proLogic assumes the fuse information is contained in the Test Vectors file.

The -a Option

This option specifies the DOS path name of the Architecture Description file. This file contains a description of the programmable device to be simulated. proLogic uses this file and the Fuse Information file to compile an optimized device model prior to beginning actual simulation. Example:

LS NAND3 -A\LXA\P16R4

Architecture Description files always have a (.LXA) file extension. When the –a option is not specified, proLogic examines the Fuse Information file for a field beginning with the characters N\_csid. If found, the remainder of the field characters identify the Architecture Description file.

### The proLogic Simulation Algorithm

The simulator behaves just like an electronic device tester. The next few paragraphs describes the device tester as a piece of hardware. These are the details you need to know to test your program.

Before executing any test vectors, the simulator removes voltage from all device pins. It next applies test condition 0 to the device ground pin and 1 to the device  $V_{CC}$  pin to simulate power-on. All memory elements power-on clear unless the device manufacturer specifies that they power-on set. Note that power-on or -off may be simulated by a test vector which applies test conditions to the power and ground pins.

After power–on, the simulator executes each test vector in the order encountered in the Test Vectors file. Execution consists of performing these four steps in order:

- 1. Remove voltage from test pins (L,H,Z) in pin number sequence.

- Apply input and I/O pin voltage (0..9,F,X) in pin number sequence excepting clock (C,K).

- 3. Apply clock pin voltage (C,K) in pin number sequence.

- 4. Read test pin voltage (L,H,Z).

Input pins with no voltage applied are assumed to float logic high. Applied voltages persist from test vector to test vector when neither driven nor tested (N).

The proLogic Compiler

### proLogic Diagrams

### A 3-input NAND Gate

The source file NAND3.PLD which programs 16R4 pin 19 to be a 3-input NAND gate has these three lines:

```

include p16r4;

!pin19 = pin2 & pin3 & pin4;

pin19.0e = 1;

```

The first line names the the header file (.H) for the PLD. The other two lines are called assignment statements.

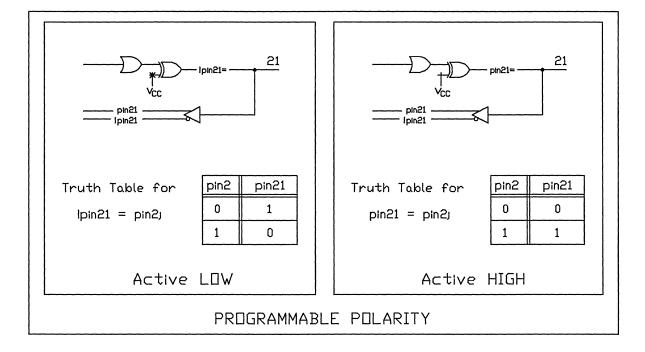

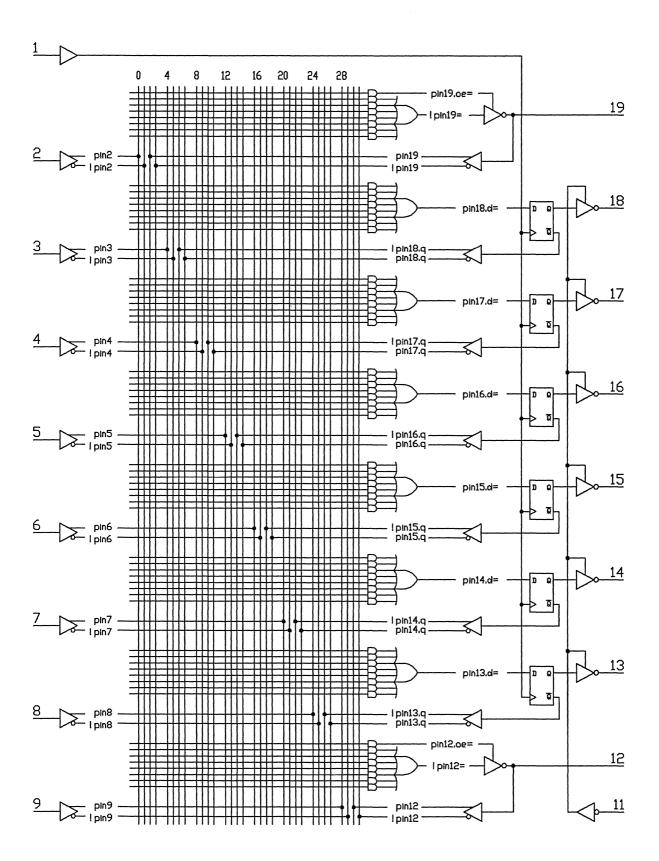

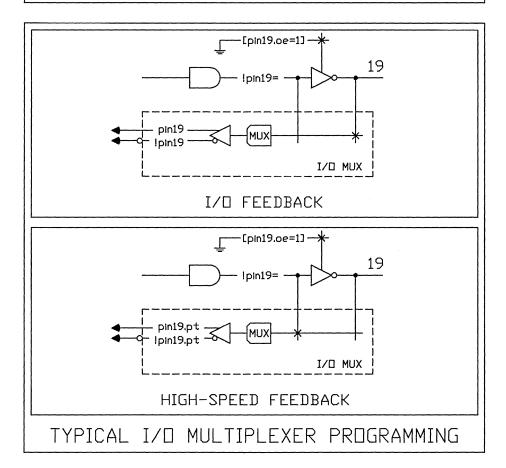

An assignment has an expression made up of signal names and gate operators. Signal names identify signals internal to the PLD to be programmed. The gate operators define signal relationships. Because each PLD is different, the signal names and gate operators also are different from one PLD to another. For example, a 24-pin PLD might have a signal named pin23, but a 20-pin PLD would not. The signal names for each PLD are documented by the prologic diagrams.

Look at the proLogic diagram for the 16R4. You'll find it in the Logic Diagram section. Each signal is labeled with its proLogic signal name.

When you write an assignment statement, it must begin with an output signal name. Output signal names always end with the "=" character. They name gate output signals.

The remainder of the assignment is an expression comprised of any of the signal names which you want as circuit inputs. The signal names which directly feed an AND gate are written using an "&" gate operator as a separator, as in the expression

pin2 & pin3 & pin4

Similarly, signal names directly feeding an OR gate are written using the "|" gate operator as a separator.

pt47 | pt46 /\* device a167 \*/

When there's no signal name on a gate output, use the gate's input expression in place of the missing signal name. The expression

!pin19 = ( pin2 & pin3 & pin4 )

represents an OR gate which has an output signal name in terms of one of it's unnamed AND gate inputs. To program pin19 as an AND instead of a NAND, write

! pin19 = ( ! pin2 ) | ( ! pin3 ) | ( ! pin4 )

where the parenthesized expressions denote the outputs of three of the AND gates feeding the OR gate. The parenthesis aren't required. The expression

! pin19 = ! pin2 | ! pin3 | ! pin4

means the same thing.

Assignments allow a separation of the punctuation parts of a signal name from the rest using spaces, tabs or even new lines. Also, pairs of parenthesis can be used to group expressions. You can also use the symbols "0" and "1" as fixed gate inputs, as in

pin19 . oe = 1

### **Brackets**

When you find a name like

[!]pin16=

in the prologic diagrams, the brackets indicate an optional part. In this case, either

pin16=

or

!pin16=

may be used as the output signal name.

### **Symbols**

### **Signal Names**

The prologic diagrams for each Programmable Logic Device specify the signal names you are required to use in your programs. These names are the ones used in the examples in the earlier sections.

If you've looked at the Texas Instruments application briefs, or at the sample Application PLD files, you've probably noticed that it's standard practice to assign application specific names to the various signals. There are a number of good reasons for doing this:

- PLD specifications can be complex. Appropriate mnemonics are a big help to comprehension, not only during initial PLD specification writing, but also when trying to comprehend an existing specification.

- Certain signal names have conventional meaning, OE for Output Enable, CS for Chip Select, A7 for address line seven, and so forth. Also, some stan dard circuits have conventional names. To illustrate, if part of your PLD circuit is an SR latch, the inputs should be named R and S.

- It saves extra documentation. If your PLD specification file uses the pin17.d signal name, then somewhere you must document that signal's function. On the other hand, if you call it D3 and the programmed PLD is titled "An Up-down Counter", the name itself implies counter output bit three.

- Your programmed PLD is part of a circuit. It's convenient if the names used in the PLD specification are similar to those used by your schematic capture package.

Application signal names are specified by define statements. The statement looks like this

define cs = pin2; /\* chip select \*/

The define replaces the symbol to the left of the = with the symbols to the right of the = (except the ;). This example means "wherever cs is found, replace it with pin2". Thus the expression

!pin19=cs

becomes

!pin19=pin2

after define replacement.

The define is a powerful tool. With it you can create application specific signal names such as

```

define STATE2 = (!pin17 & pin16 & !pin15);

define STATE3 = (!pin17 & pin16 & pin15);

define ERROR = ! pin19;

```

so that an expression for PLD pin 19 can be written as

```

ERROR = STATE2 | STATE3

```

Define statements don't take effect until they are encountered. For this reason, it's a good idea to group them all together near the start of the program.

### Symbols

proLogic recognizes three kinds of symbols:

1. A group of alphanumeric characters, such as

| CS   | define  |

|------|---------|

| pin2 | DEFINE  |

| 3725 | 8259_CS |

2. A group of characters, such as

= == &! ; % =!

except that

() { }

are always single character symbols and

/\*

always begins a comment.

3. Any characters within quotation marks

"this is an unusual symbol" "/\* and so is this \*/"

A comment is any text enclosed by /\* and \*/. Since characters like newline are text, you can write very large comment blocks. Comments can be written anywhere you can use a space or a tab, that is, they are symbol separators.

Do not use any of these reserved symbols as signal names.

| define  | else          | if           |

|---------|---------------|--------------|

| include | repeat        | signal       |

| state   | state_diagram | test_vectors |

| title   | truth_table   |              |

Do not use any symbol beginning with an underscore \_ character as a signal name.

Upper and lower case letters are different. That is, "define" is not the same as "DE-FINE", which is different from "Define". The define statement does not replace a variable's extension (a symbol after the dot). That is, if one of your variables is

define d = pin19;

the expression

pin17.d = d

becomes

pin17.d = pin19

The define statement can be used to tailor the operator symbols to your preference. proLogic uses the "&" for AND, " | " for OR and "!" as the negation attribute. But they can be changed to \*, + and / by these defines:

define \* = & ; define + = | ; define / = ! ;

Notice that the spaces between the symbols are required. If we had written

```

define *=&;

```

proLogic would see this as the symbol "define" followed by the symbol "\*=&;". If you want to change the operator symbols you also need

define =/ = = ! ;

define \*/ = & ! ;

define +/ = | ! ;

to be able to write a natural expression such as

a=/b\*/c+/d

without being forced to put in spaces to separate symbols formed from punctuation characters, as in

a = /b\* /c+ /d

The define statement rescans after it does a replacement. For instance, if you just finished inputing a program and realized you had the polarity of one of the signals wrong, you might be tempted to make a "temporary" fix with a define like

define cs = (!cs); /\* wrong \*/

This define might find an expression such as

x=cs

and replace it with

x=(!cs)

but then it rescans yielding

```

x=(!(!cs))

x=(!(!(!cs)))

x=(!(!(!(!cs))))

.

.

.

.

and so forth...

```

Things like

define a=b; define b=a;

present similar opportunities.

In practice, these don't come up very often. When they do, you'll find that proLogic tells you what symbol it is seeing. A number of instances can be fixed just by adding parentheses. As a further aid, the first part of the listing (.LST) file shows you the signal specifications after everything's completed.

### **Expressions**

### **Operators**

In Section 4 we wrote a 3-input AND gate as

```

! pin19 = ! pin2 | ! pin3 | ! pin4

```

to make the point that an AND gate on an active low output cell requires the consumption of three product terms. That's also the form required to map onto the proLogic Diagram. We loosened up the strict version of signal names by writing

!pin19=

as

! pin19 =

Now we're going to take the next step away from the proLogic Diagram and write

! pin19 = !(pin2 & pin3 & pin4)

When proLogic sees this kind of an expression, it uses arithmetic rules to transform it internally back into the sum–of–products form which maps to the diagram. If you compile

! pin19 = !(pin2 & pin3 & pin4)

and look at the (.LST) file, you'll see that it has become

!pin19= !pin2 | !pin3 | !pin4

Expressions are evaluated according to priority. The "|" operator has a lower priority than the "&" operator. Both "|" and "&" have a lower priority than the "!" attribute. In the expression

la b & c

the highest priority things get evaluated first: first the "!"

(!a) & b | c

then the "&"

((!) & b) c

leaving the " | " for last.

When the normal priorities work against you, there's another rule which says that parenthetical expressions have a higher priority than operators and attributes so that the expression

!((a | b) & c)

becomes

!a & !b | !c

Similarly,

(a b) & (c d)

becomes

a&c | a&d | b&c | b&d

You can even write expressions like

!(a = b & ! c)

which turns out to be

!a = !b | c

The assignment operator = has a lower priority than most, so that in the expression

a = b & c

the

b & c

expression is evaluated before it is assigned to a. Conversely the . (dot) operator has a very high priority so that it applies even before the "!" as in

! pin27 . D = 1

which proLogic sees as

! (pin27 .d) = 1

The dot operator changes upper case letters in the extension to lower case. The equality operators "=="""" and ""!=""" provide a way of writing the equivalent of the logical Exclusive NOR/OR functions. That is,

a == b

is the same as the expression

a & b | !a & !b

The "!=" operator is defined to be the inverse. This means

a != b

is the same as

! ( a == b )

or

a&!b | !a&b

As a general note, all operators are binary. They require an expression both before and after the operator. For example a attributes like "!" apply to a single expression.

### Statements

An assignment expression such as

a = b & c

becomes a statement when it is followed by a semicolon, as in

a = b & c;

You've already seen the define statement. It is also terminated by the semicolon. Syntactically, your program is a sequence of statements.

There is another kind of statement called a block which is terminated by a " ". The title block is the subject of the next section.

The proLogic Compiler

### **The Title Block**

### A title block

title { Function: Special Barrel Shifter. Designer: Acme Products. Date: 4 July 1988. . }

defines text to be copied to the JEDEC output file as documentation. The title block is a statement. It may appear almost anywhere in your program, but you can only have one. The text enclosed by the braces { and } is copied to the JEDEC output file. Because the JEDEC file format uses an \* character to delimit the documentation, your text may not contain this character.

The semicolon is not required to terminate the title block (or any other block). Note that our style of block which has a separate line for the closing } and begins the text on the same line as the opening { may not be to your taste. Feel free to experiment to find a style that suits you.

The text is also copied to the fuse map portion of the (.LST) file.

The proLogic Compiler

### **Truth Table Blocks**

### The Classic Seven–Segment Display

The following is the truth table to program a PLD as a hex decoder driver for a seven-segment display.

~~~~~~

| truth | truth_table { /* aa ++ |    |    |    |    |              |    |             |    |    |    |    |    |     |  |

|-------|------------------------|----|----|----|----|--------------|----|-------------|----|----|----|----|----|-----|--|

|       |                        |    |    |    | b  | +<br>b <br>+ | gg |             | ff |    |    |    |    |     |  |

|       |                        |    |    |    | с  | c <br> <br>+ | dd | <br> <br> + | ee |    |    |    |    |     |  |

|       | */                     |    |    |    |    |              |    |             |    |    |    |    |    |     |  |

|       |                        |    | q3 | q2 | q1 | q0           | :  | aa          | bb | cc | dd | ee | ff | gg; |  |

| /*    | 0                      | */ | 0  | 0  | 0  | 0            | :  | 0           | 0  | 0  | 0  | 0  | 0  | 1;  |  |

| /*    | 1                      | */ | 0  | 0  | 0  | 1            | :  | 1           | 0  | 0  | 1  | 1  | 1  | 1;  |  |

| /*    | 2                      | */ | 0  | 0  | 1  | 0            | :  | 0           | 1  | 0  | 0  | 1  | 0  | 0;  |  |

| /*    | 3                      | */ | 0  | 0  | 1  | 1            | :  | 0           | 1  | 1  | 0  | 0  | 0  | 0;  |  |

| /*    | 4                      | */ | 0  | 1  | 0  | 0            | :  | 1           | 0  | 1  | 1  | 0  | 0  | 0;  |  |

| /*    | 5                      | */ | 0  | 1  | 0  | 1            | :  | 0           | 0  | 1  | 0  | 0  | 1  | 0;  |  |

| /*    | 6                      | */ | 0  | 1  | 1  | 0            | :  | 0           | 0  | 0  | 0  | 0  | 1  | 0;  |  |

| /*    | 7                      | */ | 0  | 1  | 1  | 1            | :  | 0           | 1  | 1  | 1  | 0  | 0  | 1;  |  |

| /*    | 8                      | */ | 1  | 0  | 0  | 0            | :  | 0           | 0  | 0  | 0  | 0  | 0  | 0;  |  |

| /*    | 9                      | */ | 1  | 0  | 0  | 1            | :. | 0           | 0  | 1  | 1  | 0  | 0  | 0;  |  |

| /*    | А                      | */ | 1  | 0  | 1  | 0            | :  | 0           | 0  | 0  | 1  | 0  | 0  | 0;  |  |

| /*    | в                      | */ | 1  | 0  | 1  | 1            | :  | 1           | 0  | 0  | 0  | 0  | 1  | 0;  |  |

| /*    | С                      | */ | 1  | 1  | 0  | 0            | :  | 0           | 0  | 0  | 0  | 1  | 1  | 1;  |  |

| /*    | D                      | */ | 1  | 1  | 0  | 1            | :  | 1           | 1  | 0  | 0  | 0  | 0  | 0;  |  |

| /*    | E                      | */ | 1  | 1  | 1  | 0            | :  | 0           | 0  | 0  | 0  | 1  | 1  | 0;  |  |

| /*    | F                      | */ | 1  | 1  | 1  | 1            | :  | 0           | 0  | 0  | 1  | 1  | 1  | 0   |  |

| }     |                        |    |    |    |    |              |    |             |    |    |    |    |    |     |  |

Each truth\_table block creates a block of assignment statements, but is set up in tabular form to save you writing time and to help you visualize all the cases. The table heading line

q3 q2 q1 q0 : aa bb cc dd ee ff gg ;

lists the input and output expressions. The input expressions are listed first and are separated from the output expressions by the colon. The semicolon ends the heading line.

Each other line of the table is a detail line. Detail lines follow the format set up by the heading line with respect to number of input and output expressions. These lines create assignment statements. If your truth table had only this single detail line

/\* 0 \*/ 0 0 0 0 : 0 0 0 0 0 1;

then only this one assignment statement would be created:

gg = q3 = 0 & q2 = 0 & q1 = 0 & q0 = 0;

These two detail lines

/\* 0 \*/ 0 0 0 0 0 0 0 0 0 0 1; : 0 0 1 1 0 0 1 1; /\* 1 \*/ 0 : 1 1

would create all these:

And these three

| /* | 0 | */ | 0 | 0 | 0 | 0 | : | 0 | 0 | 0 | 0 | 0 | 0 | 1 | ; |

|----|---|----|---|---|---|---|---|---|---|---|---|---|---|---|---|

| /* | 1 | */ | 0 | 0 | 0 | 1 | : | 1 | 0 | 0 | 1 | 1 | 1 | 1 | ; |

| /* | 2 | */ | 0 | 0 | 1 | 0 | : | 0 | 1 | 0 | 0 | 1 | 0 | 0 | ; |

would create these:

All 16 of the detail lines would produce seven assignments and the aa assignment would be the sum of four products — one for each 1 in the aa column. Even though the final signal specifications which show up in the listing file can be reduced to their minimum logical equivalents, a truth table is certainly a way to generate a lot of logic with minimal work on your part.

The reason inputs use the equality operator == is so that you can have more complicated things than 0s and 1s. In

the assignment is

z = a = c & b = d;

You'll notice that we used the phrase input expression at the start of this section. This means that not only can you negate inputs, as in

which creates the assignment

z = (!a == 1) & (!b == !d);

You can also write almost any valid expression, such as

which is

z = (!(a & b)) == c & c == (d | e);

The only expression that you have to stay away from in the detail lines is a signal named X (in either upper or lower case). That's because we picked this signal name to mean don't care. If you have to use it, put it in parenthesis. This table:

yields

```

x = a==1;

y = b==x;

```

The output side of the truth tables is easier because there are only three characters permitted -0, 1 and X (or x). These make menu selections from the output expressions in the header.

The X is again a don't care. It means that this detail line doesn't affect the assignment for the output. The 1 (0) specifies that the output is logic high (low) for the case defined by the input. The output characters can be written together. That is,

0x01

is the same as

0 X 0 1

### **Output Polarity**

You should think of the polarity problem in exactly the same way that you do when you are about to write an assignment statement. Logic high (the 1s) produce assignments which are true relative to the signal specification names. If we remove the abstraction and show some real signal specification names for the 16R4 on this table:

|    | truth_table | { pin2 | pin3 | pin4 | : !p | in19 | ; /* 3 | -input | NAND |

|----|-------------|--------|------|------|------|------|--------|--------|------|

| */ |             |        |      |      |      |      |        |        |      |

|    |             | 0      | х    | х    | :    | 1    | ;      |        |      |

|    |             | 1      | 0    | х    | :    | 1    | ;      |        |      |

|    |             | 1      | 1    | 0    | :    | 1    | ;      |        |      |

|    |             | 1      | 1    | 1    | :    | 0    | ;      |        |      |

|    | }           |        |      |      |      |      |        |        |      |

it becomes clear that we've got it right.

### State Diagrams

### A Module–3 Counter

proLogic can help you implement programmable logic state machines. Other names used for this general subject are finite state machines, sequencers, sequential circuits, counters, Mealy model/machine/circuit, Moore model/machine/circuit, state diagram, ect..

If you want to create a circuit using clocked flip–flops with feedback, then you can use state blocks instead of assignments.

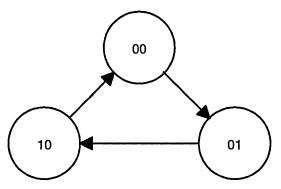

Let's take a modulo–3 counter for an example. It uses two flip–flops as state variables. Each of the three permitted combinations of Os and 1s in the state variables is called a state. On power up it is in one of the states and on each clock a next state is established which depends, in part, on the current state. Figure 6 illustrates a modulo–3 counter.

FIGURE 6. Modulo-3 Counter

The assignments for a D flip-flop implementation are determined by inspection to be

v1.d = v0.q; v0.d = !v1.q & !v0.q; The same counter written as a state diagram appears as follows:

```

state_diagram v1,v0 {

/* modulo-3 counter */

state s0=00

s1;

state s1=01

s2;

state s2=10

s0;

}

```

A state diagram appears different from the assignments. This is because each assignment is a single statement but the state diagram has a hierarchical structure.

First while the outermost state\_diagram statement.

```

state_diagram v1,v0 {

. . .

}

```

It declares v1 and v0 to be state variables. Their values are defined in the body of the diagram. The body is all of the statements enclosed by the braces { and }.

In our counter example, the body consists of a state statement for each of the three states.

The first state statement.

It declares the state name s0 and its value combination (v1.q,v0.q)=(0,0). The state statement also has a body. The body can be a single statement without braces, as written above or it can be one or more statements enclosed by braces, as in

The transition statement

s1;

consists of a state name, as it appears in one of the state statements of this state diagram, followed by a semicolon. It specifies what state occurs on the next clock.

### **IF-ELSE**

The if-else statement is used to condition other statements. The general form is

```

if (expression)

statement-1 /* then part */

else

statement-2 /* else part */

```

where the else part is optional.

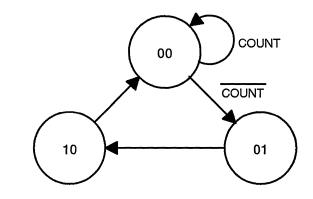

To show its use, let's make our modulo–3 counter stay low (in state s0) until triggered by an external signal (count) as shown in Figure 7.

Figure 7. Modulo-3 Counter

This is coded

```

state_diagram v1,v0 {

state s0=00

if (count)

s0;

else

s1;

state s1=01

s2;

state s2=10

s0;

}

```

The if-else statement conditions its then part with the expression in parenthesis and its else part with the expression's complement. Because its then part (or else part) can be another if-else statement or a block (one or more statements enclosed by braces { and }), things can get as complex as necessary.

The if-else and state statements can also condition assignments.

You can add an output to state s2 by writing

```

state s2=10 {

overflow=1;

s0;

}

```

or make it an up-down counter with

```

state s2=10

if (up) {

overflow=1;

s0;

}

else

s1;

```

Note that the style of one statement per line is Texas Instruments style. State statements can also be written as follows:

```

state s2=10 if (up) {overflow=1; s0;}

else s1;

```

Choose a style that suits you. Also, an if-else can be used anywhere in your program- not just within a state diagram.

### **Global Transitions**

Extend our modulo-3 counter so that instead of being triggered to count, it stays in state 00 unless enabled.

```

state_diagram v1,v0 {

state s0=00

if (count)

s0;

else

s1;

state s1=01

if (count)

s0;

else

s2;

state s2=10

s0;

}

```

State machines often have some condition such as this which applies to every state. These global transitions can be factored out and written before the first state.

#### The diagram

```

state_diagram v1,v0 {

if (count)

s0;

state s0=00

s1;

state s1=01

s2;

state s2=10

s0;

}

```

looks more like what it really is - a modulo-3 counter with an active high reset.

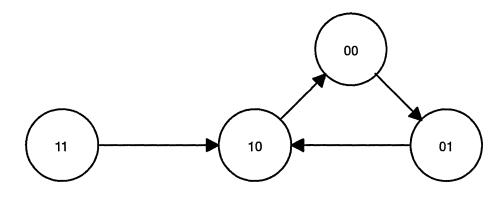

#### **Illegal States**

If the modulo-3 counter (shown in Figure 8) is implemented on flip-flops which power up to a random state the counter may be in trouble. It counts

FIGURE 8. Modulo-3 Counter

This may be acceptable. If it isn't, you can bring it into line by adding an additional

state s3=11 /\* illegal \*/

s0;

If your machine is something other than a counter you can also specify that a state has don't cares for some, but not all, of its values. Instead of adding a new state, the existing state s2 could be redefined as

```

state s2=1x

s0;

```

The x, which can be either upper or lower case, means that either a 10 or a 11 identifies state s2.

#### **State Variables**

The state variables declared by the state\_diagram statement must name a flip-flop with internal feedback. The extension may be omitted. For example

```

state_diagram pin17,pin16 {

. . .

}

```

declares that the pin17.q signal holds the most significant state value for a 16R4 implementation. On this PLD, proLogic synthesizes assignment statements for pin17.d= and pin16.d=.

You can also precede a state variable with a "!" which inverts all logic for that flipflop. The modulo-3 counter example, if written for a 16R4 with active low outputs would be

```

state_diagram !v1.q, !v0.q {

/* p16r4 modulo-3 counter */

state s0=00

s1;

state s1=01

s2;

state s2=1x

s0;

}

which is equivalent to

state diagram (v1,v0) {

/* modulo-3 counter */

state s0=11

s1;

state s1=10

s2;

state s2=0x

s0;

```

}

## Conditioning

The statements which form the body of the state block are conditioned by the state. The following is a state which is the highest state of a modulo–5 counter

```

state s4=1XX {

Y=1;

s0;

}

```

Because the expression Y=1 is contained within the body of state s4, it is conditioned by s4. This means the resulting expression is extended to be true only when state variable v2 (the most significant variable) is logic high and yields

Y = v2.q;

If Y is a combinatorial output, it becomes high shortly after clocking a 1 into v2. If Y is a registered output, it becomes high on the next clock which simultaneously causes v2 to go low as it transitions to state s0. What happens to Y after that depends on what is written in the state s0 block. Conversely, if you wanted register Y high on the clock of 1 into v2 to enter state s4, Y would need to be set up in the prior state. For an up–counter,

```

state s3=000 {

Y=1;

s4;

}

```

would do it, but in an up-down counter, both preceding states are required to set up Y.

```

state s0=000

if (up)

s1;

else {

Y=1;

s4;

}

state s3=011

if (up) {

Y=1;

s4;

}

else

s2;

```

## **Default Transitions**

An unconditioned transition statement is called a default transition. In

state s0=00

s1;

the s1 is a default transition because it is not conditioned by an if-else statement. The state

```

state s0=00

if (count)

s0;

else

s1;

```

could also have been written

```

state s0=00 {

if (count)

s0;

s1;

}

```

because the default transition specifies the state change when none of the other transitions apply.

States which have no default transition remain in their current state when none of the other transitions apply. Thus

```

state s0=00

if (!count)

s1;

```

also holds in s0 while count is logic high.

Each state block can have only one default transition statement.

## Section 10

# **Test Vector Blocks**

Test vectors are used by device programmers or logic simulators to verify that the logic functions defined for a PLD are correct. These vectors describe the inputs to the programmed PLD and specify the outputs expected after applying each set of inputs.

Each test\_vectors block defines a sequence of vectors to be applied to a set of test condition variables. These blocks are written in tabular form with semicolons separating each line of the table.

test\_vectors {

|   | pin3 | !pin1 | pin18        | pin19; |

|---|------|-------|--------------|--------|

|   | 1    | 1     | H            | L;     |

|   | 1    | 0     | $\mathbf{L}$ | L;     |

|   | 0    | 0     | $\mathbf{L}$ | H;     |

| } |      |       |              |        |

The first line of the table

pin3 !pin1 pin18 pin19;

names the test condition variables. In your program you probably have some define statements to make the names more meaningful. Because test conditions are applied to the pins of the device, not internal signals, you don't necessarily need to adhere strictly to the proLogic Diagram signal names. Anything close will usually work.

Each other line of the table is a test vector. The first vector

1 1 H L;

specifies the test conditions 1, 1, H and L to be applied respectively to the test condition variables pin3, !pin1, pin18 and pin19. Spaces aren't required. You can write

1 1 H H;

or

11HH;

as long as there is one test condition for each test condition variable. Lower case letters can be used if you prefer. This table lists the allowable test conditions.

| 0  | - | drive input LOW                         | - | 1  |

|----|---|-----------------------------------------|---|----|

| 1  | - | drive input HIGH                        | - | 0  |

| 29 | - | drive input to supervoltage #2-9        | - | 29 |

| С  | - | drive input LOW-HIGH-LOW                | - | ĸ  |

| F  | - | float input or output                   | - | F  |

| н  | - | test output HIGH                        | - | L  |

| К  | - | drive input HIGH-LOW-HIGH               | - | С  |

| L  | - | test output LOW                         | - | н  |

| N  | - | power pins and outputs not tested       | - | N  |

| Р  | - | preload registers                       | - | Р  |

| х  | - | output not tested, input default level  | - | х  |

| Z  | - | test input or output for high impedance | - | Z  |

The last column lists the inverse condition which is used when a test condition variable is negated. The block

}

```

test_vectors { pin1;

0;

1;

N

```

There is also a special kind of a test vector which is used to create one or more JE-DEC buried register vectors. This one begins with the symbol internal and is followed by as many 0s, 1s, Ls and Hs as there are internal registers in the PLD.

}

#### Note:

If you're new to PLD design, be aware that we've left out some very important practical considerations. When a device programmer executes preload vectors, or vectors which have supervoltages, it may apply high voltages to pins. Refer to the data sheets for your exact PLD. Your device programmer manual also provides important cautions to observe when testing.

### **The Repeat Block**

A repeat block, written

repeat N {

. . .

}

can be used anywhere in your program. Its function is to create N copies of the symbols contained in the body. The following is a sample application.

| <pre>test_vectors {     /* 4-bit counter partial test */</pre>       |               |       |       |       |                   |    |                   |

|----------------------------------------------------------------------|---------------|-------|-------|-------|-------------------|----|-------------------|

| p                                                                    | in1           | pin17 | pin16 | pin15 | <pre>pin14;</pre> |    |                   |

| 1                                                                    | P             | 0     | 0     | 0     | 0;                | /* | preload */        |

| -                                                                    | eat 15 {<br>C | x     | x     | x     | х;                | /* | clock 15 times */ |

| )                                                                    | 0             | н     | н     | н     | Н;                | /* | OK if all high */ |

| (                                                                    | C             | L     | г     | L     | L;                | /* | wraparound */     |

| }                                                                    |               |       |       |       |                   |    |                   |

| The } which terminates the repeat block was placed on the line after |               |       |       |       |                   |    |                   |

C X X X X; /\* clock 15 times \*/

but could also have been placed on the same line after the semicolon.

Repeat blocks are not statements. This means they can be used almost anywhere. Nesting is permitted, such as

repeat 15 { C repeat 4 { X }; }

The proLogic Compiler

## Section 11

# **Include Files**

Exactly one

include file-name;

which identifies the Architecture Description file (.LXA) for the target device must be present somewhere in each program. file-name is a symbol string such as

P16R4.LXA

or

\prologic\p22v10.lxa

When you don't specify a file extension of .LXA, the include has a different function. In this case, the include and its symbols are replaced by the contents of the identified file.

You might want to use include files to define commonly used symbols like

define LOW = 0;

to save time and assure consistency over all of your PLD programs.

Even though a semicolon terminates the file-name, the include is not a statement. Like the repeat block, it can be used almost anywhere. Included files may themselves have includes. A repeat block may contain includes (and vice versa).

When no file extension is supplied, the default is .H (for header). But if your file has spaces as an extension, make this clear.

```

include myfile. ;

include myfile." ";

include "myfile. ";

```

#### **Header Files**

proLogic provides a library of header files (.H). These provide extra levels of information about each device to make it easier for you to write a program. You might think of them as a subroutine library. Header files answer questions like:

```

how many pins?

is register preload available?

what pins have registers?

how do states map to D flip-flops?

to SR flip-flops?

does if (c) x=a; mean x= (c & a)?

does it mean x = (c & a) | (!c & x.q)?

does the compiler drive output enables when you don't?

what about logic minimization?

.

```

The only logical operators which the compiler recognizes are the AND and OR. Header files may offer other operators such as XOR.

When you select a header file such as

include p16r4;

at the beginning of your program, you do not need an

include p16r4.lxa;

because the header file will bring the Architecture Description in as part of itself.

If your preference is for as little "help" as possible, use an include such as

include p16r4.lxa;

at the start of your program. This requires you to be very explicit when you write the program. Most of the higher level statements can't be used in this mode. We recommend you include the STDSYN.H file in addition to the LXA file. It has define statements which relax the operator symbols to make your expressions more natural.

# Section 12

# **Signal Specifications**

Although proLogic has the ability to manipulate, optimize, and even synthesize Boolean equations. Everything gets put into the form which will map onto the proLogic Diagram signal names and gate operators. This form is called a signal specification.

In the example

!pin19 = pin2 & pin3 & pin4

The signal specification is

"!pin19=" pin2 & pin3 & pin4

Quotes are used to write the seven-character symbol

!pin19=

because that is the exact name on the proLogic Diagram. Names such as

!pin2

would also need to be quoted.

The rules for writing a signal specification are as follows:

- 1. A signal specification always begins with an output signal name. These names always end with an = (equal) character.

- 2. An input signal name must follow the output signal name. These names never end with an = character.

- 3. After the first input signal name, more input signal names can be listed if they are separated by gate operators.

#### **Gate Operators**

The prologic diagrams implicitly use these operators:

| & | Logical | AND Gate  |    |      |

|---|---------|-----------|----|------|

|   | Logical | OR Gate   |    |      |

| 8 | Logical | Exclusive | OR | Gate |

Other operators unique to the PLD may be specified by individual diagrams.

The characters

- ! Logical Negation

- = Assignment

- Dot

are not gate operators. They are required to "spell" some signal names.

#### Gate Operators Function

There is always a conceptual "current gate". The importance of the current gate concept is that it provides the environment for interpreting the meaning of the input signal names. Input names always identify signals with respect to the current gate.

The current gate becomes important in multi-level logic. The output name usually identifies a hierarchical logic structure of one, two, or more levels. For example, in a 16R4, the output name pin19.oe= identifies a one level product term. The output name !pin19= identifies a two level sum of product terms. The current gate is always one of the gates at the lowest level of the hierarchy. In both of these examples, the current gates are AND gates.

The initial current gate is identified by the output name. It is always the first (or topmost) of all of the possible current gates. The operator which identifies the current gate (in these examples, the "&"), has no effect on the current gate. It serves only as a separator between input names. An operator which identifies a gate at a higher level in the PLD logic structure (in these examples, the "|") changes the current gate to be the next of all possible current gates.

In a one level structure such as the 16R4 pin19.oe=, there is only one possible current gate – the 32–input AND which drives the output enable for pin 19. It is the initial current gate identified by the pin19.oe= output name. In the signal specification for this signal only "&" operators may appear.

In the two level structure identified by the !pin19= output name, there are seven AND gates at the lowest level. The output name identifies the first of these as the current gate. All input names identify connections to this AND gate until an " | " operator is encountered. After the " | ", all input names identify connections to the second AND gate, until the next " | " when they apply to the third, and so forth.

#### 0 And 1

There are two special signal names which apply to the current gate of all devices. They are 1, which means the output of the current gate is logically true, and 0, which means the the output of the current gate is logically false. Since these names apply to the gate output, no other input names may apply to that gate. For example,

"pin19.0e=" 1 & pin2

is improper.

The 0 and 1 signal names used in the signal specification are different from the 0 and 1 symbols used in expressions. In an expression, they are gate input signals. That is,

```

(pin19.oe = 1 \& pin2)

```

is transformed into

(pin19.oe = pin2)

In the first matrix of a 16R4 there are 256 programmable cells. These two signal specifications cause only the last cell to remain connected, while the first 255 are disconnected (programmed).

```

"pin19.0e=" 1

"!pin19=" 1 | 1 | 1 | 1 | 1 | 1 | "!pin12"

```

#### **The Signal Statement**

Most PLD programs for most devices can be expressed entirely in terms of boolean equations using logical AND, OR and NOT. That's why the assignment statement such as

a = b & !c;

requires you to do the minimum amount of typing on your keyboard. But some PLDs have XOR gates or signature words.

For these instances the signal statement always provides the ability to program at the signal specification level. Another way of writing

a = b & !c;

is

signal "a=" b & "!c";

In this statement, everything between signal and the semicolon must be a signal specification.

You also have the option of letting proLogic do most of the work for you. In the signal statement, anything enclosed by parenthesis is an expression. Thus

```

signal "a=" b & (!c);

signal "a=" (b & !c);

signal (a = b & !c);

```

are all equivalent.

To make it even easier, you can also write the =, ., and ! symbols separately.

proLogic will translate

signal a = ! b . c;

into

signal "a=" "!b.c" ;

because it knows the rules for forming a signal name.

Appendix A

# A Designer's Guide to the TIBPSG507

Robert K. Breuninger and Loren Schiele with Contributions by Joshua K. Peprah

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to or to discontinue any semiconductor product or service identified in this publication without notice. TI advises its customers to obtain the latest version of the relevant information to verify, before placing orders, that the information being relied upon is current.

TI warrants performance of its semiconductor products to current specifications in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Unless mandated by government requirements, specific testing of all parameters of each device is not necessarily performed.

TI assumes no liability for TI applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1987, Texas Instruments Incorporated

# Contents

| -     |

|-------|

| Title |

| Title                                                | Page |

|------------------------------------------------------|------|

| INTRODUCTION                                         | A-7  |

| FUNCTIONAL DESCRIPTION                               | A-7  |

| THEORY OF OPERATION                                  | A-7  |

| Example 1: Waveform Generator                        | A-9  |

| Example 2: Refresh Timer                             | A-12 |

| Example 3: Dynamic Memory Timing Controller          | A-15 |

| DESIGNER NOTES                                       | A-21 |

| Obtaining Maximum Counter Performance                | A-21 |

| Expanding the 6-Bit Counter                          | A-21 |

| Software Support                                     | A-21 |

| 'PSG-507 Example 1: Waveform Generator               | A-27 |

| 'PSG-507 Example 2: Refresh Timer                    | A-29 |

| 'PSG-507 Example 3: Dynamic Memory Timing Controller | A-31 |

# List of Illustrations

| Figure | Title                                        | Page |

|--------|----------------------------------------------|------|

| 1      | PSG Architecture                             | A-8  |

| 2      | Clock Generator Timing Requirements          | A-9  |

| 3      | SCLR at COUNT 11                             | A-10 |

| 4      | Waveform Generator                           | A-11 |

| 5      | Refresh Timer Requirements                   | A-12 |

| 6      | Expanding to 7-Bit Binary Counter            | A-13 |

| 7      | Refresh Timer                                | A-14 |

| 8      | Memory Timing Controller                     | A-15 |

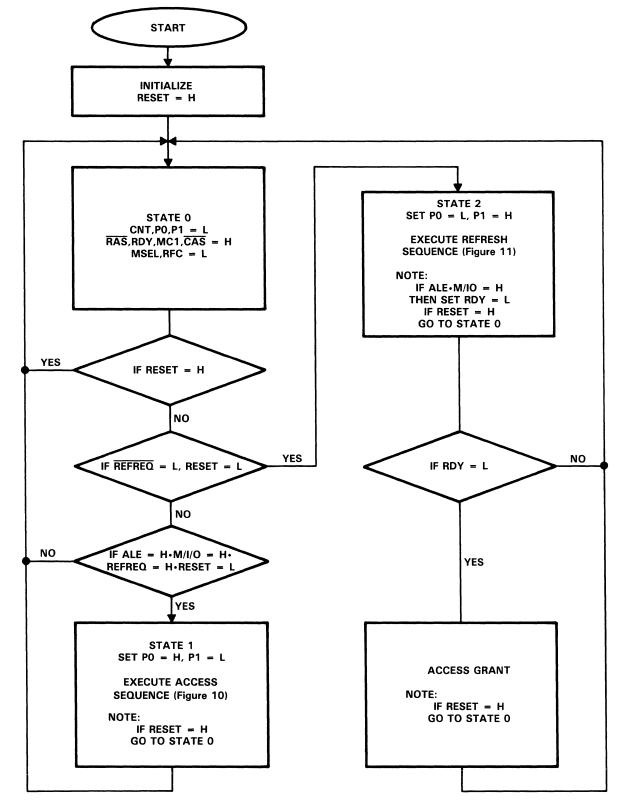

| 9      | Flow Chart: Dynamic Memory Timing Controller | A-16 |

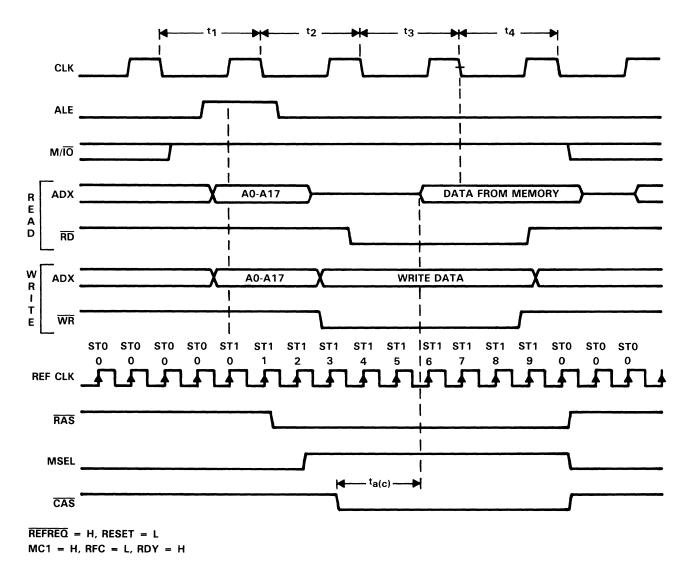

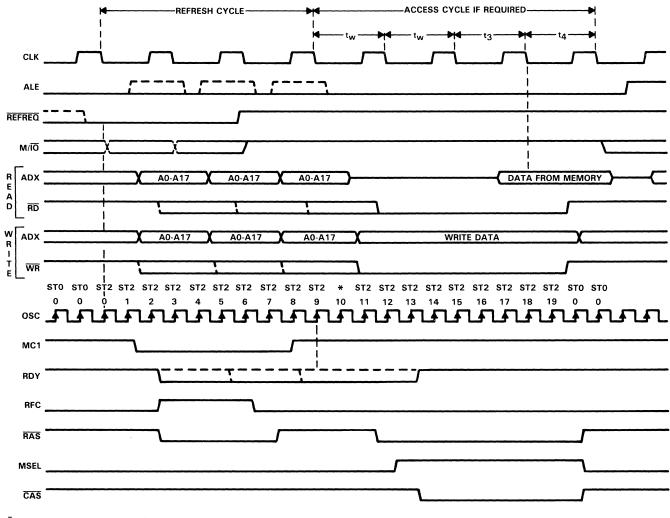

| 10     | Access Cycle                                 | A-17 |

| 11     | Refresh/Access Grant Cycle                   | A-18 |

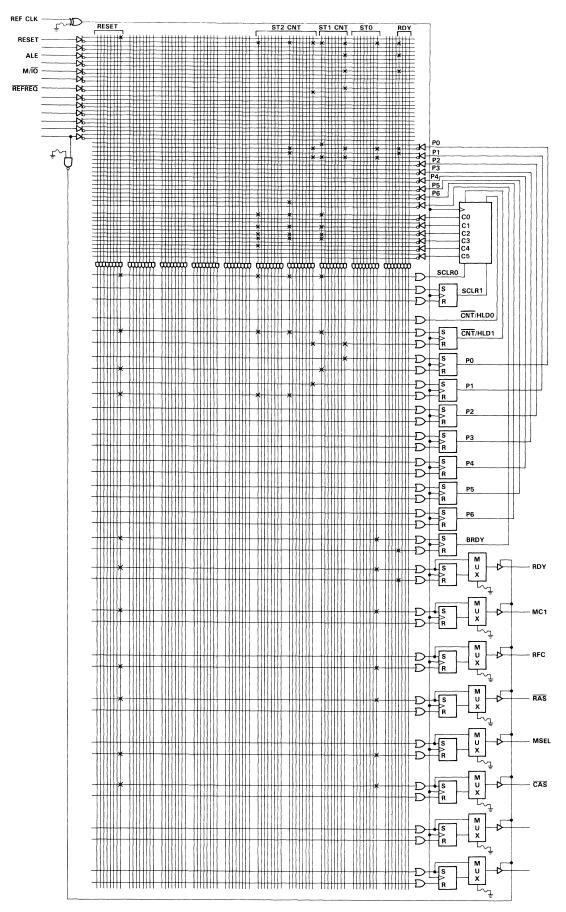

| 12     | Counter Control Logic                        | A-19 |

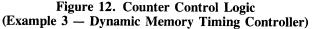

| 13     | Memory Timing Controller                     | A-20 |

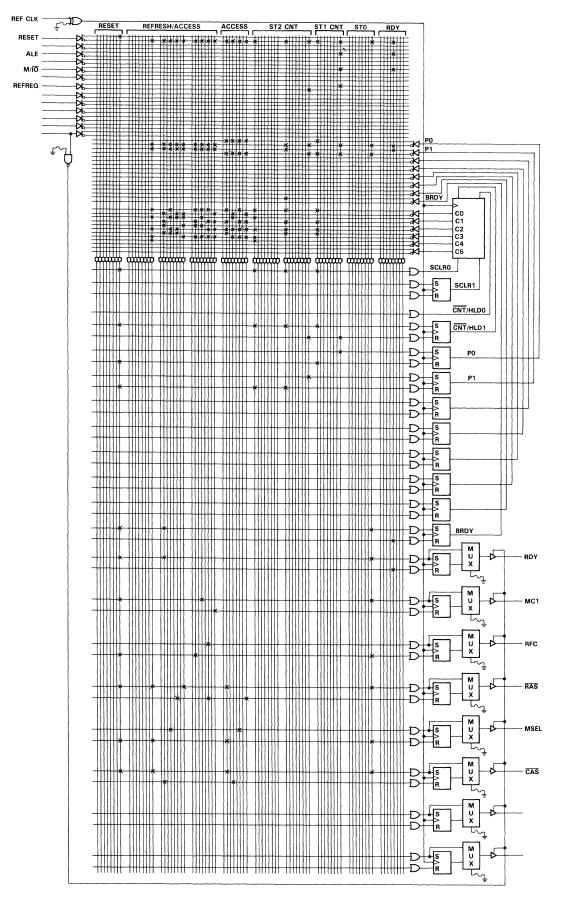

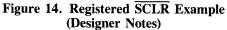

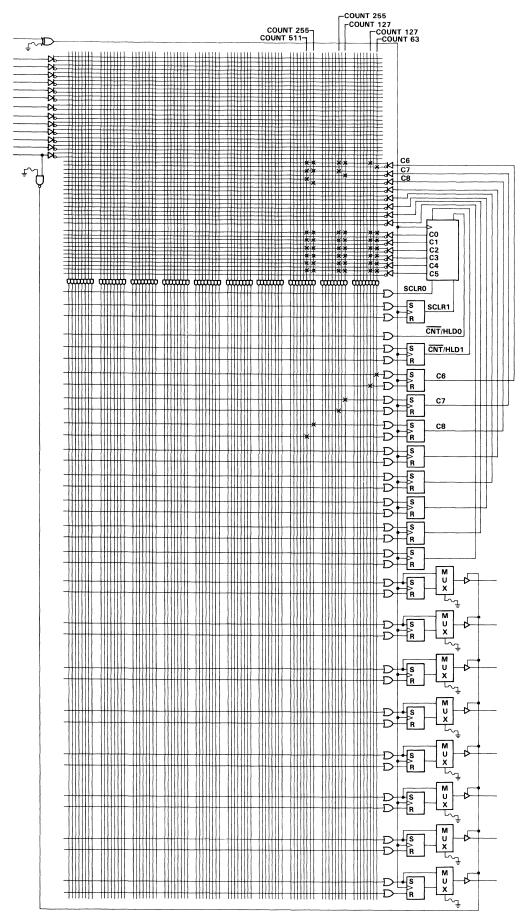

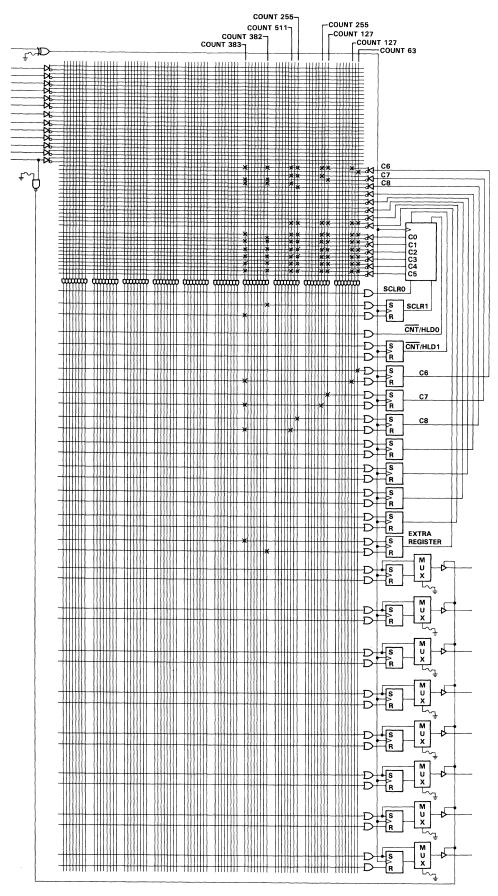

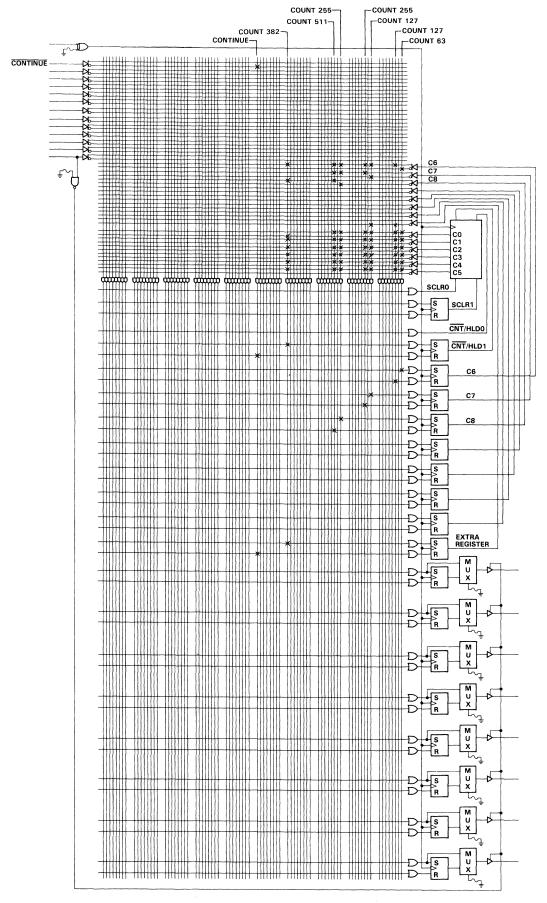

| 14     | Registered SCLR Example                      | A-22 |

| 15     | Expanding the 9-Bit Counter                  | A-23 |

| 16     | Resetting after COUNT 383                    | A-24 |

| 17     | Holding the 9-Bit Counter at COUNT 383       | A-25 |

A-6

#### INTRODUCTION

The term PSG stands for Programmable Sequence Generator. The PSG is the newest member of the programmable logic family. It combines the powerful benefits of programmable array logic (PALs) with the specialized world of Field Programmable Logic Sequencers (FPLSs).

Applications such as waveform generators, state machines, timers, and simple logic reduction are all possible with a PSG. By utilizing the built-in binary counter, the PSG is capable of generating complex timing controllers. In short, the PSG offers the system designer an extremely powerful building block.

The purpose of this application report is to describe the functional operation of the PSG507 and demonstrate how it can be applied in real-world applications. Three design examples that highlight the features and flexibility of the PSG will be discussed.

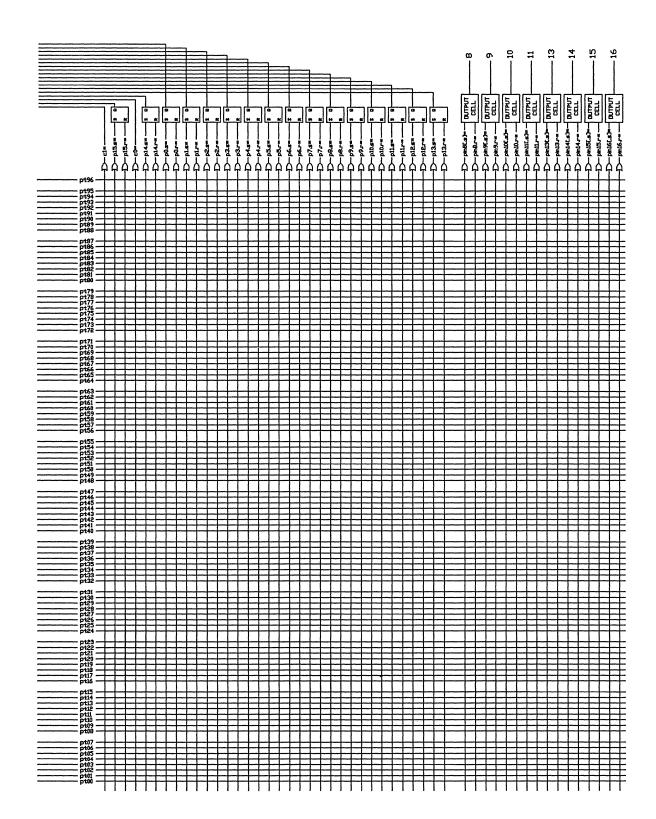

#### FUNCTIONAL DESCRIPTION

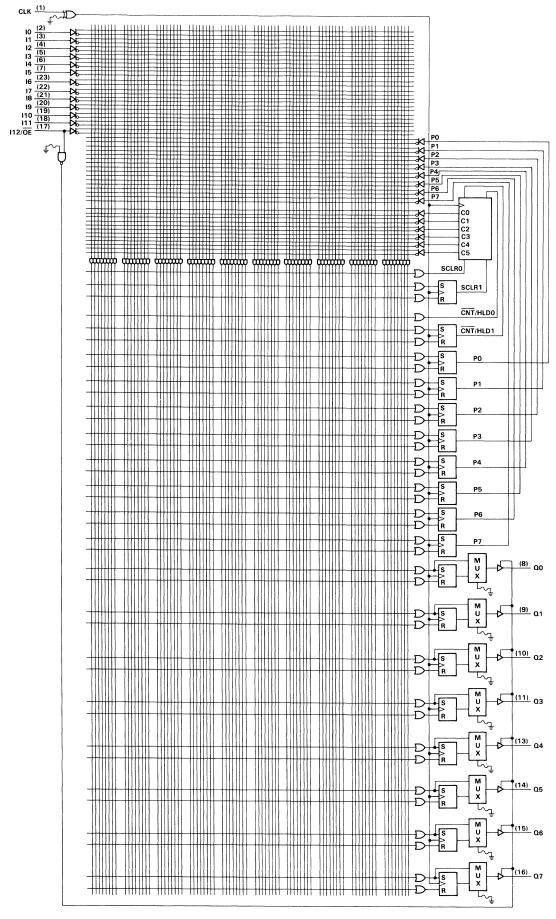

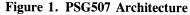

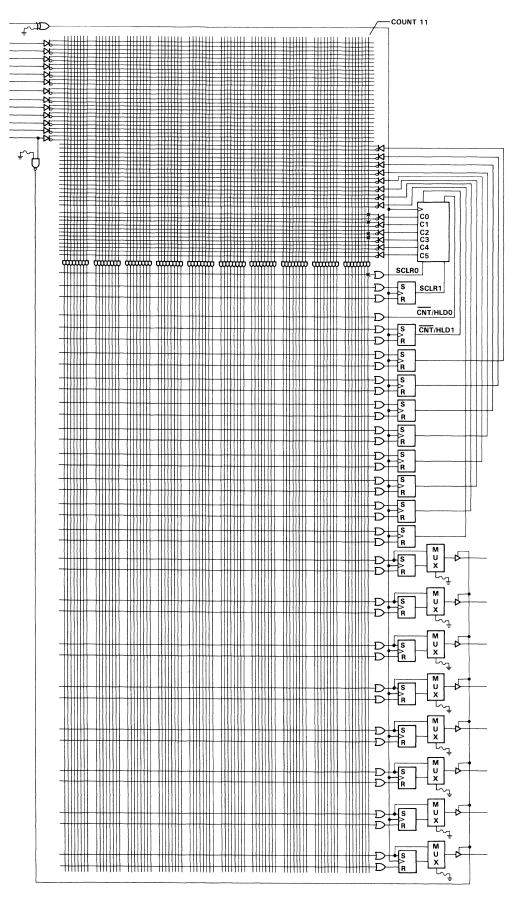

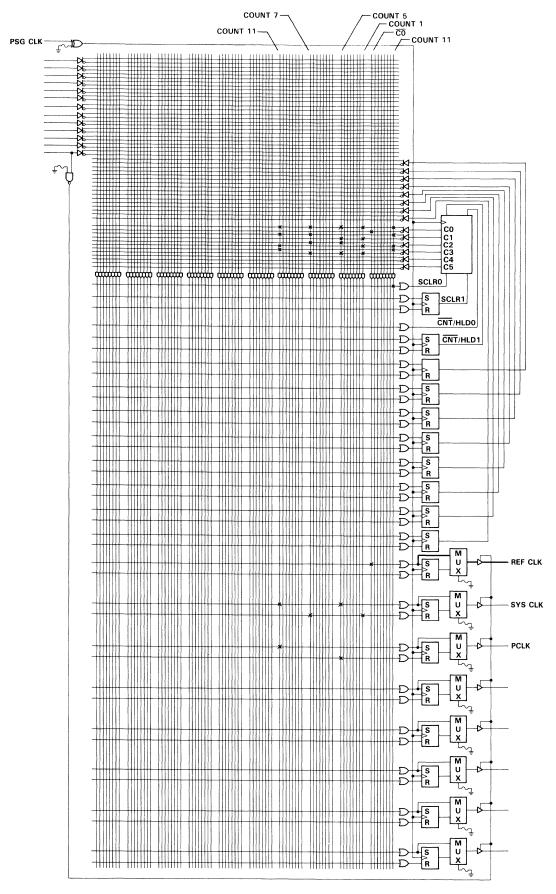

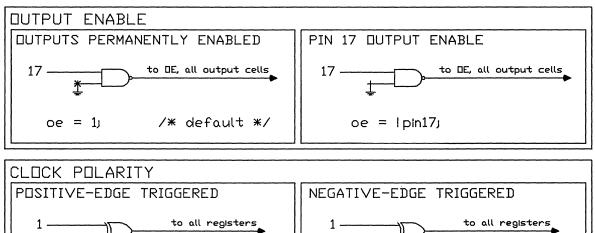

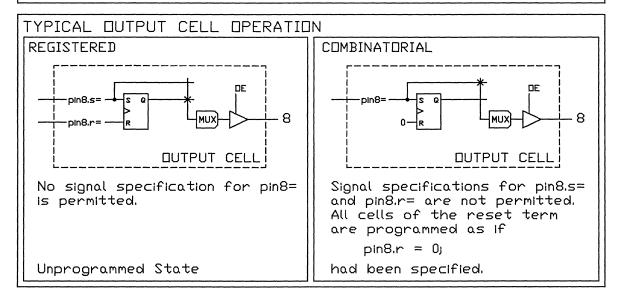

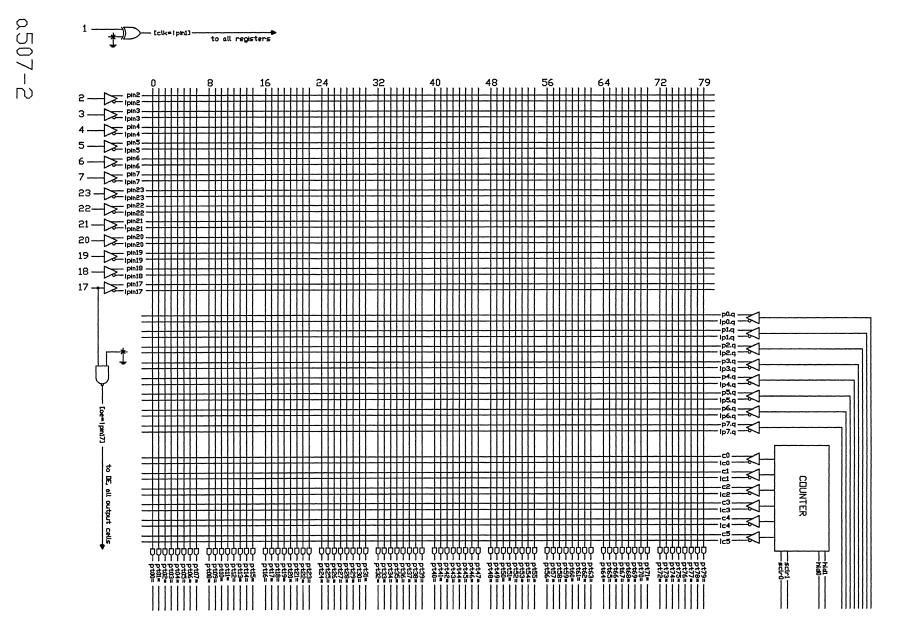

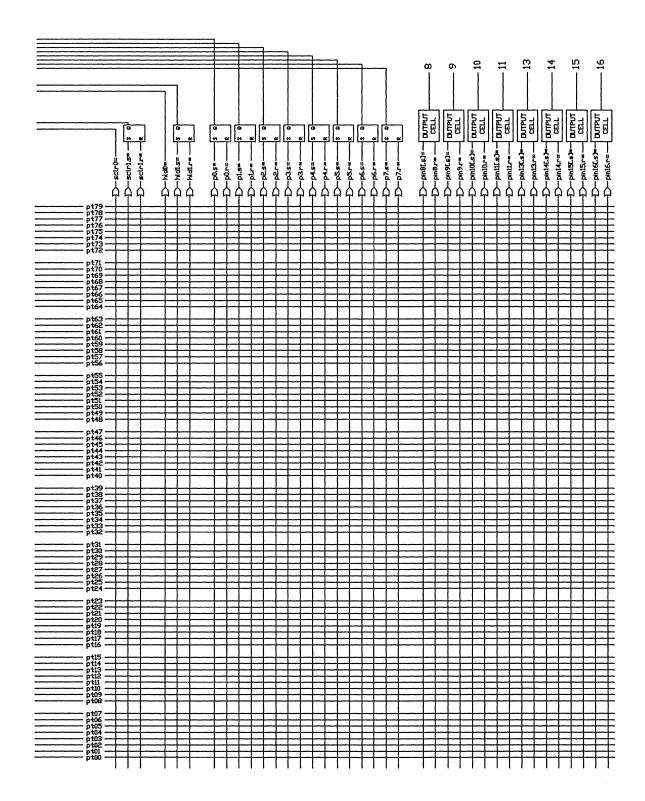

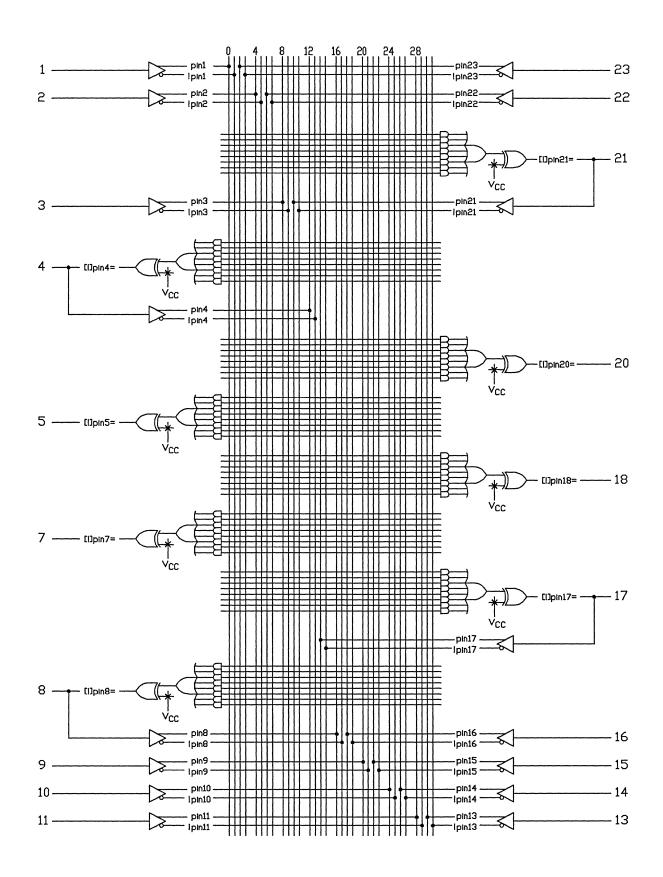

Figure 1 shows the architecture of the PSG507. Major features include 13 inputs, eight programmable registered or nonregistered outputs, eight S/R state registers, and a 6-bit binary counter with control logic. The clock input is fuse-programmable for selection of positive or negative edge triggering.

The binary counter, state registers, and output cells are synchronously clocked by the fuse-programmable clock input. The clock polarity fuse selects either positive or negative edge triggering. Negative edge triggering is selected by blowing the clock polarity fuse. Leaving this fuse intact selects positive edge triggering.

Each output cell on the PSG can be configured for registered or nonregistered operation through the output multiplexer fuse. Nonregistered operation is selected by blowing the output multiplexer fuse. Leaving this fuse intact selects registered operation.

The PSG507 has 13 inputs, each providing a true and complement input to the AND array. Pin 17 functions as either an input and/or an output enable. Blowing the output enable fuse lets pin 17 function as an output enable but does not disconnect pin 17 from the input array. When the output enable fuse is intact, pin 17 functions only as an input with the outputs being permanently enabled.

The 6-bit binary counter is controlled by a synchronous clear and a count/hold function. Each control function has a nonregistered and registered option. When either SCLR0 or SCLR1 is taken active high, the counter resets to zero on the next active clock edge. When either  $\overline{CNT}/HLD0$  or  $\overline{CNT}/HLD1$  is taken active high, the counter is held at the present count and is not allowed to advance on each active clock edge. The SCLR feature overrides the  $\overline{CNT}/HLD$  feature when both functions are simultaneously active high. The functional benefit of both these features will be further clarified in the examples shown later in this application report.

The eight internal state registers feed back into the AND array. These registers can be used to store input data, to keep track of binary count sequences, or they can be used as output registers when connected to a nonregistered output cell. The state registers differ from the output registers in that they feed back into the input array. They can also be used to override an operating sequence such as demonstrated in the designer notes located at the end of this application report. By using extra state registers, the 6-bit counter can be expanded as shown in the second example. Other uses of the internal state registers will become apparent upon reading the examples shown.

#### THEORY OF OPERATION

The PSG architecture is capable of operating in many different modes. When comparing the operation of a PSG to a PAL, the outputs in both devices can be configured as an AND/OR function of the inputs. One major difference between a PSG and a PAL is that a programmable OR array is used in the PSG. This allows a selected number of AND terms to be connected to each output as compared to a fixed number of AND terms assigned to each output on a PAL. The programmable OR array is the more efficient in that it lets the user assign the exact number of AND terms to each output as required by the application.

Another major difference between the PAL architecture and that of a PSG is that the output cells on a PSG are not fed back into the input array. Typically, output feedback is used for building a counter or for holding state information. Since the architecture of the PSG already includes state registers and a binary counter, the requirement for output feedback is eliminated in most applications. This is a benefit to the user because valuable output cells and AND terms are not wasted when generating these functions.

When a Field Programmable Logic Sequencer is compared to a PSG, the most obvious difference is the addition of a binary counter. Most state machine designs can be simplified by referencing all or part of each sequence to a binary count. This technique is highlighted in the third example shown in this application note. A comparison will also reveal that the output cells on a PSG can be configured

for nonregistered operation. This permits the outputs to be directly fed from the counter, AND/OR array, or state registers. Example 1 highlights this feature.

In short, the outputs of a PSG can be controlled by any or all of the following conditions:

- Present state of the inputs

- Present state of the binary counter

- Present state of the state holding registers

The key to understanding state machine design when using a PSG is to realize that different states can be assigned for each sequence. In other words, the assigned state determines which sequence is in operation. The length of each sequence is controlled by the SCLR function. Once the count sequence has been programmed to the desired length, each output can be easily decoded from the present state of the binary counter. The user will soon discover that complex state machines are easily developed when using this technique. This technique is demonstrated in Example 3.

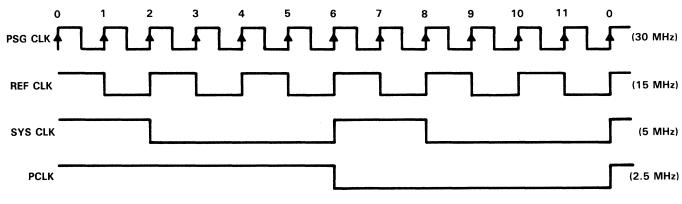

#### **Example 1: Waveform Generator**

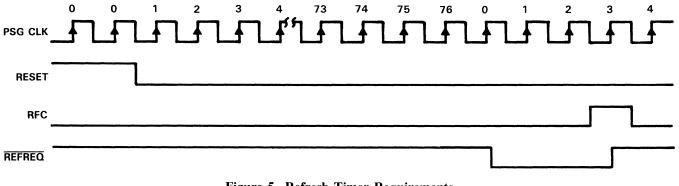

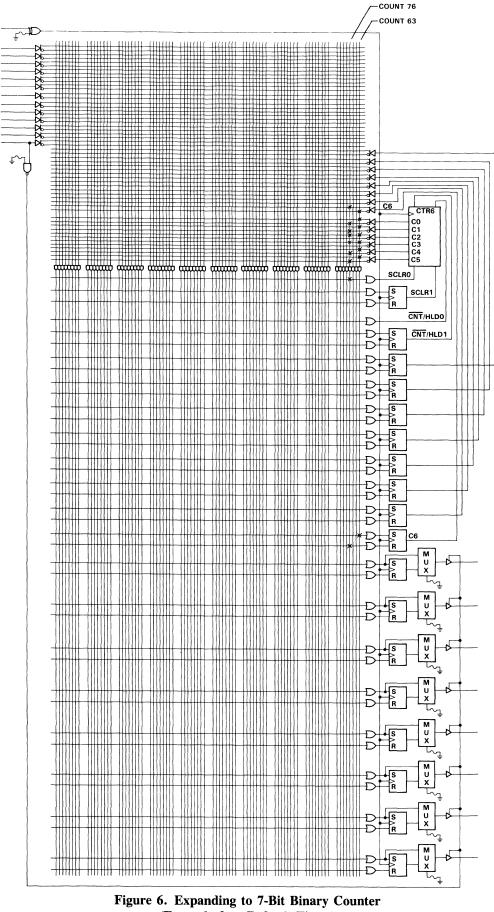

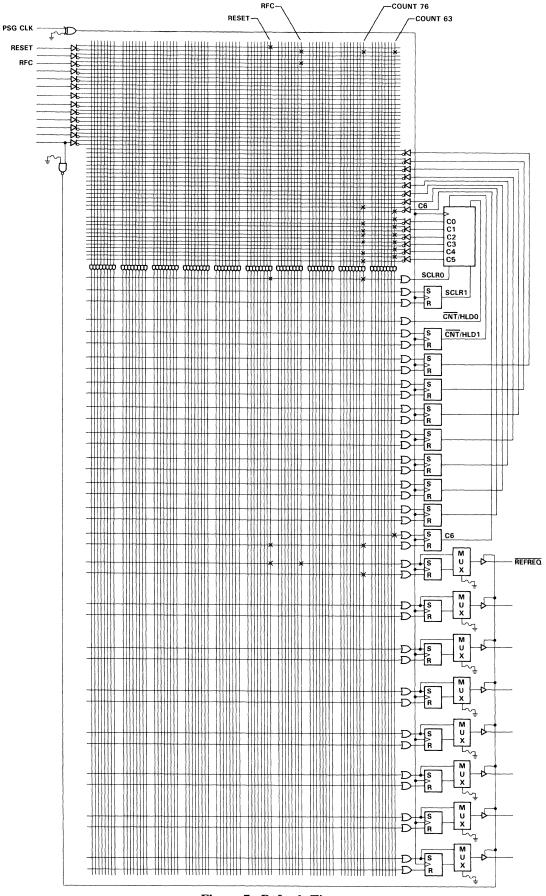

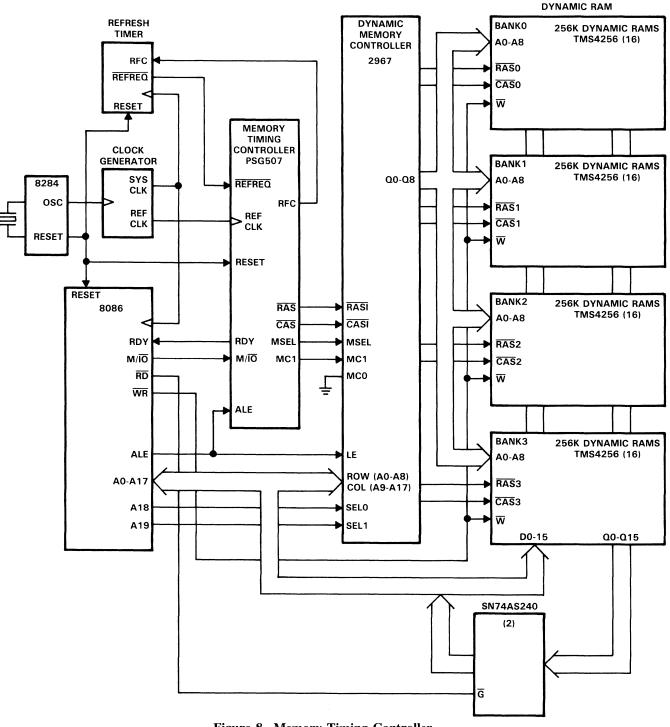

The first example demonstrates a design for a simple clock generator used for driving a microprocessor operating at 5 MHz (required duty cycle of 33.5% high, 66.5% low). In addition to the 5 MHz system clock (SYS CLK), a reference clock (REF CLK) operating at 15 MHz (50% duty cycle) and a peripheral clock (PCLK) operating at 2.5 MHz (50% duty cycle) are required for other timing controllers and peripherals throughout the system. Both clocks must be in close phase with the SYS CLK to guarantee synchronous operation within the system.