# **TMS370C16 Central Processing Unit,** System, and Instruction Set

**PRISM Module Library**

cMCU370<sup>™</sup> Products

### TMS370C16 Central Processing Unit, System, and Instruction Set Reference Guide

**PRISM Module Library**

March 1994

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to current specifications in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Please be aware that TI products are not intended for use in life-support appliances, devices, or systems. Use of TI product in such applications requires the written approval of the appropriate TI officer. Certain applications using semiconductor devices may involve potential risks of personal injury, property damage, or loss of life. In order to minimize these risks, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards. Inclusion of TI products in such applications is understood to be fully at the risk of the customer using TI devices or systems.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1994, Texas Instruments Incorporated

### Preface

### **Read This First**

#### Overview

Texas Instruments uses PRISM methodology, with its modular fabrication processes, to integrate analog and digital functions on a single chip. The process technologies currently include VLSI CMOS, nonvolatile memories (EPROM/EEPROM), lateral DMOS, high-voltage analog CMOS, and high-density analog CMOS

The 16-bit TMS370C16 CPU is part of the cMCU370<sup>™</sup> family of microcontroller devices. This manual provides information about the TMS370C16 CPU architecture, features, operation, and assembly language instruction set; it also includes helpful information about implementing a TMS370C16-based microcontroller design.

Related documentation is listed on page v.

#### Manual Organization

- Chapter 1 gives a brief overview of the TMS370C16 microcontroller device.

- Chapter 2 describes the components and operation of the TMS370C16 CPU architecture, including CPU registers and memory organization.

- Chapter 3 describes the TMS370C16 system configuration, registers, device interrupts, and reset.

- Chapter 4 describes the different addressing modes used by the instruction set.

- □ Chapter 5 lists and describes the TMS370C16 assembly language instructions, execution sequence, effects, and examples.

- Appendix A, Glossary, explains and defines terms and abbreviations used in this manual.

#### Style, Symbols, and Definitions

This document uses the following conventions.

- Abbreviations:

- 'C16: TMS370C16 CPU-based devices

- **LSB, MSB**: Least significant and most significant *bits*

- **LSbyte, MSbyte**: Least and most significant *bytes*

- Register and bit names: SCR1.7, for example

The register name (located to the left of the period) is an alpha abbreviation (e.g., SSR = system status register, and SCR1 = system control register 1). The bit number is to the right of the period (e.g., SCR1.7 is bit 7 of register SCR1 as shown in Figure 3–3 on page 3-7).

Definitions of *device* and *module* as used in this manual:

- Device: The cMCU370 microcontroller; includes the TMS370C16 CPU along with all selected modules integrated on a single chip.

- Module: An element that provides a specific function (such as a serial interface, memory, analog-to-digital conversion, timing, I/0, etc.). A list of modules is provided in the documentation-title list on page v (in this preface).

Program listings and program examples are shown in a special typeface similar to a typewriter's.

#### Note: Assembler Statements Are Not Case Sensitive

TMS370C16 assembly language statements are not case sensitive. You can enter them in lowercase, uppercase, or a combination. To emphasize this, assembly language statements are shown throughout this user's guide in both uppercase and lowercase.

| Related Docur | mentation From Texas Instruments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Literature<br>Number |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|               | TMS370C8 CPU, System, and Instruction Set Reference Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SPNU042              |

|               | TMS370C16 CPU, System, and Instruction Set Reference Guide<br>PRISM Module Library Reference Set, Volume 1<br>Volume 1 includes the following module reference guides.                                                                                                                                                                                                                                                                                                                                            | SPNU043<br>SPNU031   |

|               | <ul> <li>cMCU370 Microcontroller Products Introduction</li> <li>Clock Modules Reference Guide</li> <li>Watchdog and Real-Time Interrupt Module Reference Guide</li> <li>EEPROM/EPROM Modules Reference Guide</li> <li>TMS370C8 Timer Modules Reference Guide</li> <li>Serial Communications Interface Module Reference Guide</li> <li>Serial Peripheral Interface Module Reference Guide</li> <li>Analog-to-Digital Converter Module Reference Guide</li> </ul>                                                   |                      |

|               | <ul> <li>PRISM Module Library Reference Set, Volume 2</li> <li>Volume 2 includes the following module reference guides.</li> <li>TMS370C16 Timer Modules Reference Guide</li> <li>Voltage Regulator Modules Reference Guide</li> <li>Gage Driver Modules Reference Guide</li> <li>Power Driver Modules Reference Guide</li> <li>Switch Interface Module Reference Guide</li> <li>Variable Reluctance Sensor Module Reference Guide</li> <li>Some books on this list will be available at a later date.</li> </ul> | SPNU032              |

#### If You Need Assistance. . .

| If you want to                                                            | Do this                                                                                                                                          |

|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Ask questions about product<br>operation, or report suspected<br>problems | Call the TI microcontroller hotline:<br>(713) 274–2370<br>FAX: (713) 274–4203                                                                    |

| Request more information about<br>Texas Instruments products              | Write to:<br>Texas Instruments Incorporated<br>Market Communications Manager, MS 6101<br>P.O. Box 1443<br>Houston, Texas 77251–1443              |

| Order Texas Instruments<br>documentation                                  | Call the TI Literature Response Center: (800) 477-8924                                                                                           |

| Bulletin board number                                                     | (713) 274–3700                                                                                                                                   |

| Report mistakes in this document<br>or any other TI documentation         | Send your comments to:<br>Texas Instruments Incorporated<br>Technical Publications Manager, MS 702<br>P.O. Box 1443<br>Houston, Texas 77251–1443 |

|                                                                           | or call the TI microcontroller hotline (phone number at top of this table)                                                                       |

#### Information About Cautions

The information in a caution is provided for your protection. Please read each caution carefully.

#### Trademarks

cMCU370 is a registered trademark of Texas Instruments Incorporated.

# Contents

| - |      |          |                                                                 |

|---|------|----------|-----------------------------------------------------------------|

| 1 |      |          |                                                                 |

|   | 1.1  |          | 70C16 CPU — Device-Specific Operation 1-2                       |

|   | 1.2  |          | System, and Instruction Set Features 1-3                        |

|   | 1.3  | TMS37    | 70C16 Control Registers 1-4                                     |

| 2 | Arch | itecture |                                                                 |

|   | 2.1  | -        | mmer's Model                                                    |

|   | 2.2  | CPU R    | legister File (R0 – R15) 2-4                                    |

|   |      | 2.2.1    | Frame Pointer, FP (R0) 2-5                                      |

|   |      | 2.2.2    | Implied Register, IM (R1) 2-5                                   |

|   |      | 2.2.3    | Stack Pointer, SP (R13) 2-6                                     |

|   |      | 2.2.4    | Status Register, ST (R14) 2-6                                   |

|   |      | 2.2.5    | Zero Register, ZR (R15) 2-7                                     |

|   | 2.3  | Progra   | m Counter (PC) and Address Bus 2-8                              |

|   | 2.4  | Instruc  | tion Organization                                               |

|   | 2.5  | System   | n Stack                                                         |

|   |      | 2.5.1    | Stack Operation During Interrupts 2-12                          |

|   |      | 2.5.2    | Stack Use with a Call                                           |

|   | 2.6  | Data O   | Organization and Memory Mapping 2-14                            |

| 3 | TMS  | 370C16   | System Configuration                                            |

|   | 3.1  | System   | n Configuration Overview                                        |

|   | 3.2  | System   | n Reset Operation                                               |

|   | 3.3  | CLKOU    | JT Pin Function Selection                                       |

|   | 3.4  | Paralle  | I Signature Analysis Operation (CRC Generator)                  |

|   | 3.5  | System   | n Configuration Registers                                       |

|   |      | 3.5.1    | System Control Register 0 (SCR0) 3-8                            |

|   |      | 3.5.2    | System Control Register 1 (SCR1) 3-9                            |

|   |      | 3.5.3    | System Reset Status Register (SRSR) 3-10                        |

|   |      | 3.5.4    | System Status Register (SSR) 3-12                               |

|   |      | 3.5.5    | Parallel Signature Analysis Registers (PSARn)                   |

|   | 3.6  | Genera   | al-Purpose Digital Pin Functions                                |

|   |      | 3.6.1    | Digital Output/Control Registers (OCRn)                         |

|   |      | 3.6.2    | Digital Input/Status Registers (ISRn)                           |

|   |      | 3.6.3    | Digital Port Direction and Port Data Registers (xDIR and xDATA) |

|   | 3.7  | Interru  | pt and Exception Handling                                       |

|   |       | 3.7.1    | Interrupt/Exception Sources                               | 9 |

|---|-------|----------|-----------------------------------------------------------|---|

|   |       | 3.7.2    | Vector Table                                              | 1 |

|   |       | 3.7.3    | Reset and Interrupt Operation 3-2                         | 1 |

|   |       | 3.7.4    | Nonmaskable Interrupt (NMI) Processing 3-2                | 3 |

|   |       | 3.7.5    | Peripheral Module Interrupt Processing 3-24               | 4 |

|   |       | 3.7.6    | Software Exception (TRAPs, etc.) Processing 3-24          | 4 |

|   | 3.8   | Externa  | al and Power Module Interrupts 3-2                        | 5 |

|   |       | 3.8.1    | External Interrupt Pins 3-2                               | 5 |

|   |       | 3.8.2    | Power Module Interrupts 3-3                               | 5 |

|   |       | 3.8.3    | Phantom Interrupt Vector                                  | 7 |

|   | 3.9   | Multiple | e Interrupt Servicing                                     | B |

|   | 3.10  | TMS37    | 0C16 Interrupt Configurability Options                    | 9 |

|   | 3.11  | Low-Po   | ower and Idle Modes                                       | D |

|   |       | 3.11.1   | Overview                                                  | 0 |

|   |       | 3.11.2   | Low-Power Wakeup Interrupt 3-4                            | 0 |

| 4 | ۵ddr  | eeina I  | Aodes                                                     | 1 |

| • | 4.1   | -        | Summary                                                   |   |

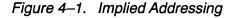

|   | 4.2   |          | Addressing                                                |   |

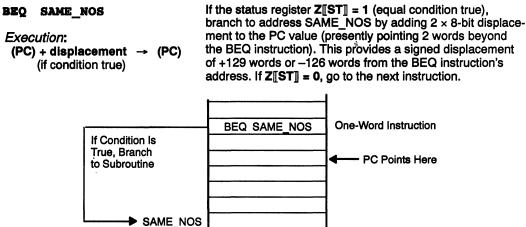

|   | 4.3   | •        | ative Addressing                                          |   |

|   | 4.4   |          | y-Direct Addressing                                       |   |

|   | 4.5   |          | iate Values                                               |   |

|   | 4.6   |          | er-Direct Addressing                                      |   |

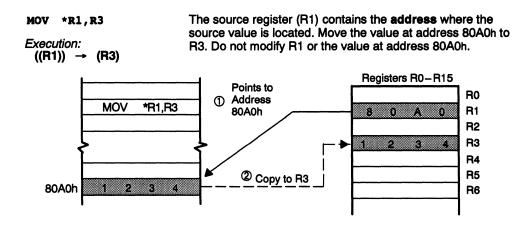

|   | 4.7   | -        | er-Indirect Addressing                                    |   |

|   |       | 4.7.1    | Register-Indirect Addressing, No Displacement             |   |

|   |       |          | (Register Contents = Effective Address) 4-1               | 0 |

|   |       | 4.7.2    | Register Indirect With Displacement (Offset) 4-13         | 3 |

|   | 4.8   | Setting  | the Word Address for CALL, JMP, and FMOV Instructions 4-1 | 6 |

| 5 | Asse  | mbiv La  | nguage instructions                                       | 1 |

| - | 5.1   | -        | tion Set Summary                                          |   |

|   | 5.2   |          | tion Set Summary Table                                    |   |

|   | 5.3   |          | tion Descriptions in Alphabetical Order                   |   |

| Α | Glose | arv      |                                                           | 1 |

|   |       |          |                                                           |   |

# Figures

| 2–1  | Programmer's Model                                                                    | 2-3  |

|------|---------------------------------------------------------------------------------------|------|

| 2–2  | Registers R0 to R15                                                                   | 2-4  |

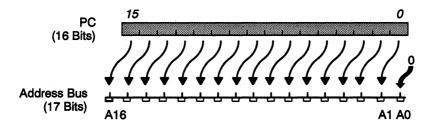

| 2–3  | Program Counter to Address Bus Transition                                             | 2-8  |

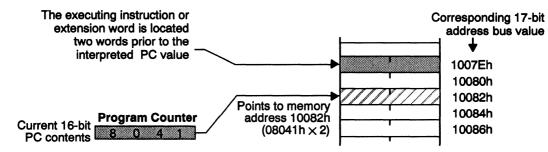

| 2–4  | Relationship Between the PC and Memory Address                                        | 2-9  |

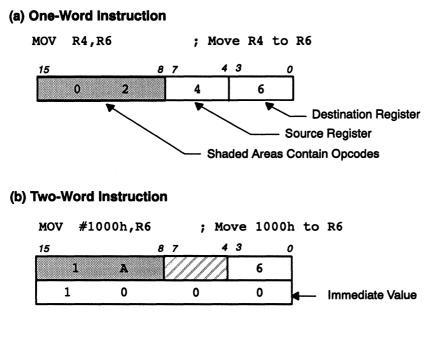

| 2–5  | One-, Two-, and Three-Word Instruction Examples                                       | 2-10 |

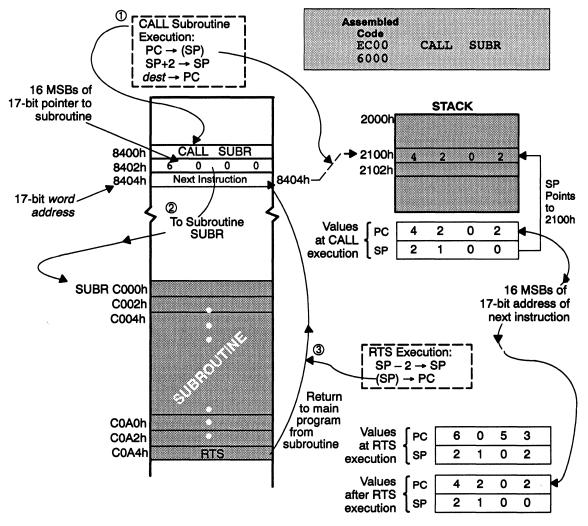

| 2–6  | Example of Stack Use to and From a Subroutine                                         | 2-13 |

| 2–7  | Bit and Byte Numbering for Instructions, Registers, and Words                         | 2-14 |

| 2–8  | Differences in Memory and Register Byte Destinations                                  | 2-16 |

| 2–9  | Data Organization Examples in Registers and Memory                                    | 2-17 |

| 2–10 | Typical 16-Bit Memory Map 2                                                           | 2-18 |

| 2–11 | Location and Names of Control Registers 2                                             | 2-19 |

| 3–1  | System Block Diagram                                                                  | 3-2  |

| 3–2  | Reset State Diagram — Normal Run Mode                                                 | 3-4  |

| 3–3  | System Configuration Registers                                                        | 3-7  |

| 34   | Digital I/O Control and Status Registers                                              | -15  |

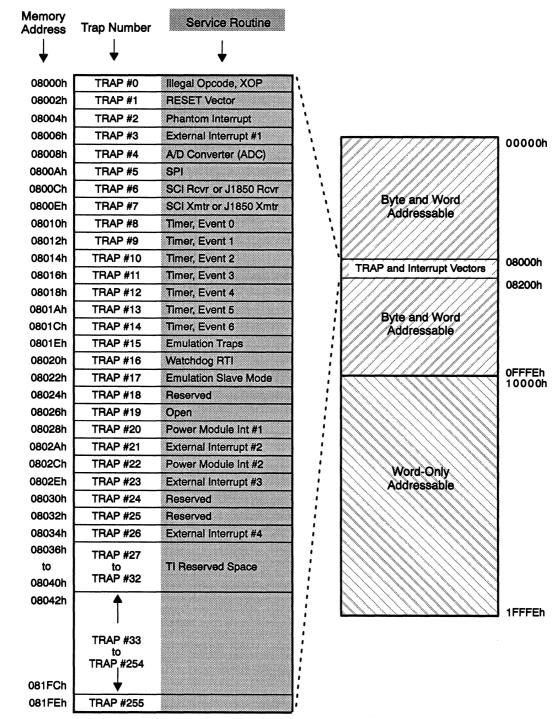

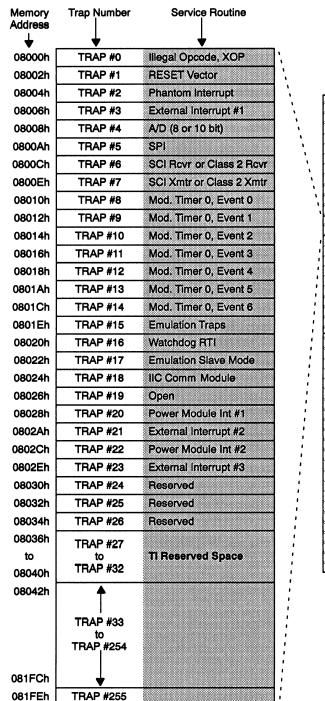

| 35   | Vector Table Organization in Memory                                                   | -20  |

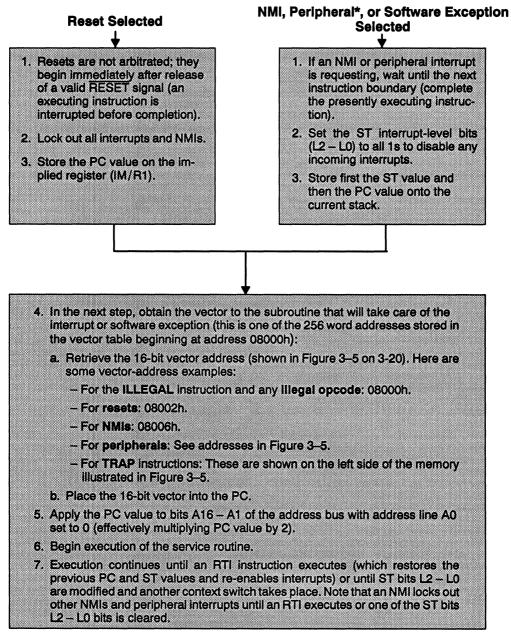

| 36   | Summary of Reset, NMI, Peripheral Interrupts, and Software Exception Operations 3     | 3-22 |

| 3–7  | Interrupt-Frame Typical Configurations                                                | 8-27 |

| 38   | Typical Interrupt Frame                                                               | 8-28 |

| 4–1  | Implied Addressing                                                                    | 4-3  |

| 4–2  | PC-Relative Addressing                                                                |      |

| 4–3  | Memory-Direct Addressing (& Operator)                                                 | 4-5  |

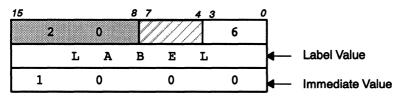

| 44   | Operand Is Immediate Value (# Operator)                                               |      |

| 45   | Register-Direct Addressing                                                            |      |

| 46   | Register Direct With CALL or JMP Instructions Addresses 128K Bytes                    | 4-8  |

| 4–7  | Register Indirect (Operand: *Rn) 4                                                    | -10  |

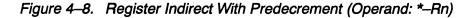

| 48   | Register Indirect With Predecrement (Operand: *-Rn)                                   | I-11 |

| 49   | Register Indirect with Postincrement (Operand: *Rn+) and Predecrement (Operand: *–Rn) | -12  |

| 4–10 | Offset + Register in Word Format (Operand: *disp16[Rn]) 4                             |      |

| 4–11 | Offset + Register in Byte Format (Operand: *disp16[Rn]) 4                             | -14  |

| 4–12 | Offset + Register for JMP and CALL Instructions (Operand: *disp16[Rn]) 4              | -15  |

| 4–13 | Using the ? Operator to Set the Word Address for a CALL or JMP, Direct Register 4     |      |

| 4–14 | Use the ? Operator to Set the Word Address for an FMOV, Indirect Register 4           |      |

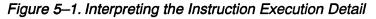

| 5–1  | Interpreting the Instruction Execution Detail                                         | 5-16 |

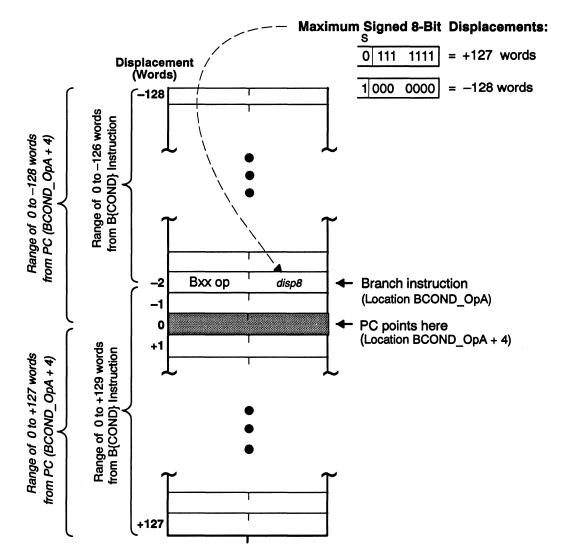

| 5–2  | B{COND} Instruction Displacements                                                     | 5-29 |

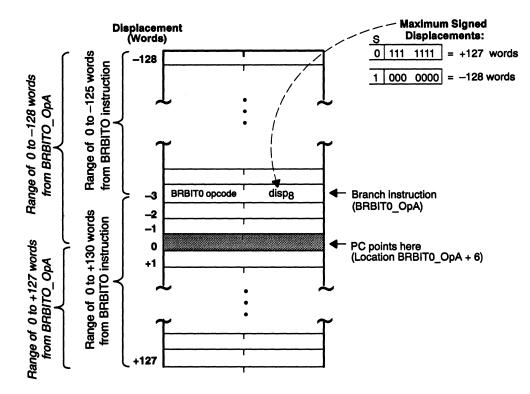

| 5–3 | BRBIT0 and BRBIT1 Instruction Displacements | 5-31  |

|-----|---------------------------------------------|-------|

| 5-4 | CALL and RTS Instruction Example            | 5-35  |

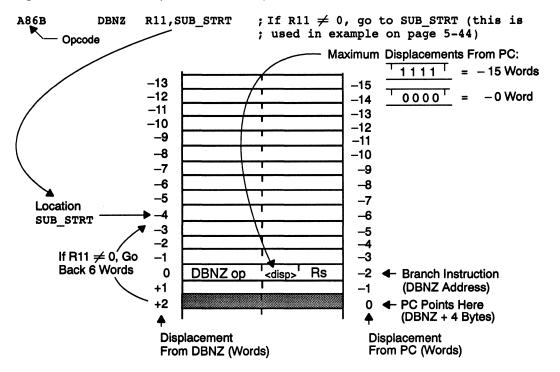

|     | DBNZ Displacement Computation               |       |

| 56  | Vector Table for TRAP Instruction           | 5-113 |

# **Tables**

| 1—1 | TMS370C16 System Configuration Control Registers | 1-4  |

|-----|--------------------------------------------------|------|

| 1–2 | TMS370C16 Digital Pin Function Control Registers | 1-4  |

| 1–3 | TMS370C16 Typical Interrupt Control Registers    | 1-5  |

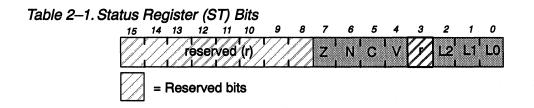

| 2–1 | Status Register (ST) Bits                        | 2-6  |

| 2–2 | Instructions That Use a 17-Bit Address           | 2-9  |

| 2–3 | Instructions That Use The Stack                  | 2-11 |

| 3–1 | CLKOUT Pin Function Options                      | 3-6  |

| 3–2 | External Interrupt Types                         | 3-26 |

| 3–3 | External Interrupt Pin Functions                 | 3-26 |

| 34  | Type A Interrupt Control Bit Freeze Options      | 3-39 |

| 4–1 | Addressing Mode Summary                          | 4-2  |

| 4–2 | Register Indirect Addressing Summary             | 4-9  |

| 5–1 | Abbreviations Used to Describe Instructions      | 5-2  |

| 5–2 | Symbols Used to Describe Instructions            | 5-3  |

| 5–3 | Branches Listed by Opcode 5                      | 5-28 |

|     |                                                  |      |

# **Notes and Cautions**

| Definitions of Device and Module Used In This Manual               | 1-2  |

|--------------------------------------------------------------------|------|

| Register Considerations                                            | 2-7  |

| Word Address Definition                                            | 2-8  |

| The SP Must Contain an Even Value                                  | 2-12 |

| Word Address Definition                                            | 2-14 |

| Avoid Interrupting a Reset With an NMI                             |      |

| INTx Used to Represent INT1 – INT6                                 |      |

| Derivation of Memory-Direct Format (& Operator)                    | 4-6  |

| *Rn Can Be Used If *disp[Rn] Is Assembled                          |      |

| Decrement/Increment Considerations                                 |      |

| Assembler Statements Are Not Case Sensitive                        | 5-16 |

| The wbfd Column Values                                             | 5-18 |

| PC's 16-Bit Word Address Translates to 17-Bit Address Bus          |      |

| Do Not Use Operand Rs,IM:Rs                                        |      |

| 16-Bit Word Address Translates to 17-Bit Address Bus               |      |

| Use FMOV to Address 0–1FFFFh (Up to 128K Bytes)                    |      |

| Considerations for >64K Bytes and Effect of Byte Size on Registers |      |

| Five Trap Words Are Reserved                                       |      |

| TRAP Enumerator Source                                             |      |

|                                                                    |      |

### Chapter 1

### Introduction

The TMS370C16 microcontroller core is part of the PRISM Modular Library. With reusable engineering techniques, it can be combined with other building blocks from the modular library to generate a diversified family of highly integrated devices.

This chapter gives a brief overview of the 'C16 CPU — its device-specific operation, its features, and its registers.

This chapter covers the following topics:

#### Topic

### Page

|   |                                               | 8   |

|---|-----------------------------------------------|-----|

|   | 1.1 TMS370C16 CPU — Device-Specific Operation | 8   |

|   | 11 TMS370C16 CPI — Device-Specific Operation  | 8   |

|   |                                               | 8   |

|   |                                               | 8   |

|   |                                               | 8   |

|   | 1.2 CPU, System, and instruction Set Features | 8   |

|   | 12 LPU System and instruction Set Features    | 8 - |

|   |                                               | 8   |

|   |                                               | 8   |

|   |                                               | 8   |

|   | 1.3 TMS370C16 Control Registers 1-4           | 8   |

| 1 |                                               | 8   |

| 1 | 110                                           | 8   |

| 1 |                                               | 8   |

|   |                                               |     |

#### 1.1 TMS370C16 CPU — Device-Specific Operation

The total integration concept of the cMCU microcontroller family makes multiple configurations possible. Because of this flexibility, certain module features are device specific and therefore cannot be presented as an absolute in this document. You should refer to the specific device data sheet to determine the features and functions available on your particular device. Here is a partial list of these indefinable areas:

- Memory array size and memory map location for RAM, ROM/EPROM, EEPROM, and peripheral file

- System clock (SYSCLK) operation

- Digital I/O pin functionality

- Interrupts (The number of available external and internal interrupts and their associated vectors.)

- Low-power mode availability and interrupt exit capability.

#### Note: Definitions of Device and Module Used In This Manual

**Device:** The core microcontroller. It includes the CPU (TMS370C16), along with all selected modules, integrated on a single chip.

**Module:** An element that provides a specific function (such as a serial interface, memory, analog-to-digital conversion, timing, I/0, etc.) A list of modules is provided on page v of the preface.

#### 1.2 CPU, System, and Instruction Set Features

The TMS370C16 CPU module consists of the following:

- □ 16-bit CPU containing the associated registers:

- Frame pointer

- Implied register

- Stack pointer

- Status register

- Zero register

- 16-bit program counter

- 17-bit address space

- □ Various memory types supported by the 'C16 architecture

- RAM

- Peripheral file control registers

- Data EEPROM

- Program memory (ROM or EPROM)

- Seven possible reset sources

- Interrupt structure

- Software-selectable priority levels

- Nonmaskable Interrupt (NMI) options

- Variable number of interrupts, depending on the device configurations

- Individual interrupt vectors

- Two low-power modes

- Set of 126 instructions including byte, word, and long-word formats.

#### 1.3 TMS370C16 Control Registers

The CPU and system functions are controlled by registers in three separate frames as illustrated in the following three tables.

Table 1–1. TMS370C16 System Configuration Control Registers

|         | Register | Register                                            |         | oed in |

|---------|----------|-----------------------------------------------------|---------|--------|

| Address | Symbol   | Register Name                                       | Section | Page   |

| 0010h   |          | Reserved                                            |         |        |

|         |          |                                                     |         |        |

| to      |          | State of the state of the state of the state of the |         |        |

|         |          | •                                                   |         |        |

| 0017h   |          | Reserved                                            |         |        |

| 0018h   | SCR0     | System Control Register 0                           | 3.5.1   | 3-8    |

| 0019h   | SCR1     | System Control Register 1                           | 3.5.2   | 3-9    |

| 001Ah   | SRSR     | System Reset Status Register                        | 3.5.3   | 3-10   |

| 001Bh   | SSR      | System Status Register                              | 3.5.4   | 3-12   |

| 001Ch   |          | Reserved                                            |         |        |

| 001Dh   |          | Reserved                                            |         |        |

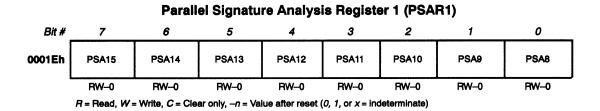

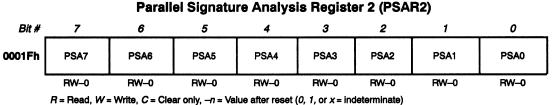

| 001Eh   | PSAR1    | Parallel Signature Analysis Register 1              | 3.5.5   | 3-13   |

| 001Fh   | PSAR2    | Parallel Signature Analysis Register 2              | 3.5.5   | 3-13   |

Table 1–2. TMS370C16 Digital Pin Function Control Registers

| Register |        | Register                      |         | Described in |  |

|----------|--------|-------------------------------|---------|--------------|--|

| Address  | Symbol | Register Name                 | Section | Page         |  |

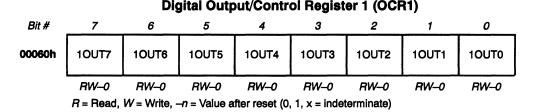

| 0060h    | OCR1   | Output/Control Register 1     | 3.6.1   | 3-16         |  |

| 0061h    | OCR2   | Output/Control Register 2     | 3.6.1   | 3-16         |  |

| 0062h    | OCR3   | Output/Control Register 3     | 3.6.1   | 3-16         |  |

| 0063h    | OCR4   | Output/Control Register 4     | 3.6.1   | 3-16         |  |

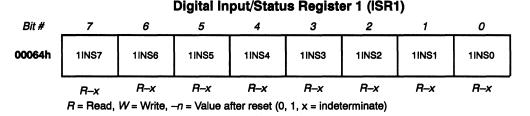

| 0064h    | ISR1   | Input/Status Register 1       | 3.6.2   | 3-16         |  |

| 0065h    | ISR2   | Input/Status Register 2       | 3.6.2   | 3-16         |  |

| 0066h    | ISR3   | Input/Status Register 2       | 3.6.2   | 3-16         |  |

| 0067h    | ISR4   | Input/Status Register 2       | 3.6.2   | 3-16         |  |

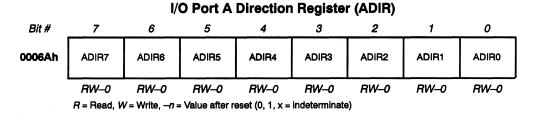

| 0068h    | ADIR   | I/O Port A Direction Register | 3.6.3   | 3-17         |  |

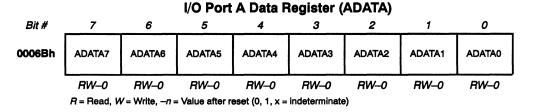

| 0069h    | ADATA  | I/O Port A Data Register      | 3.6.3   | 3-17         |  |

| 006Ah    | BDIR   | I/O Port B Direction Register | 3.6.3   | 3-17         |  |

| 006Bh    | BDATA  | I/O Port B Data Register      | 3.6.3   | 3-17         |  |

| 006Ch    | CDIR   | I/O Port C Direction Register | 3.6.3   | 3-17         |  |

| 006Dh    | CDATA  | I/O Port C Data Register      | 3.6.3   | 3-17         |  |

| 006Eh    | DDIR   | I/O Port D Direction Register | 3.6.3   | 3-17         |  |

| 006Fh    | DDATA  | I/O Port D Data Register      | 3.6.3   | 3-17         |  |

|         | Register   |                                          | Described in |      |

|---------|------------|------------------------------------------|--------------|------|

| Address | Symbol     | Register Name                            | Section      | Page |

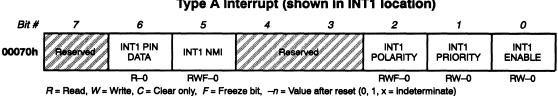

| 0070h   | INT1       | Type A Interrupt                         | 3.8.1.1      | 3-29 |

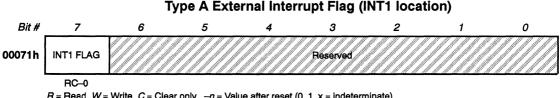

| 0071h   | INT1 FLG   | Type A Interrupt Flag                    | 3.8.1.1      | 3-29 |

| 0072h   | INT2       | Type B Interrupt                         | 3.8.1.3      | 3-31 |

| 0073h   | INT2 FLG   | Type B Interrupt Flag                    | 3.8.1.3      | 3-31 |

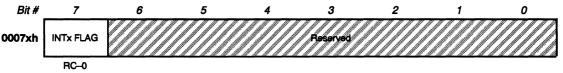

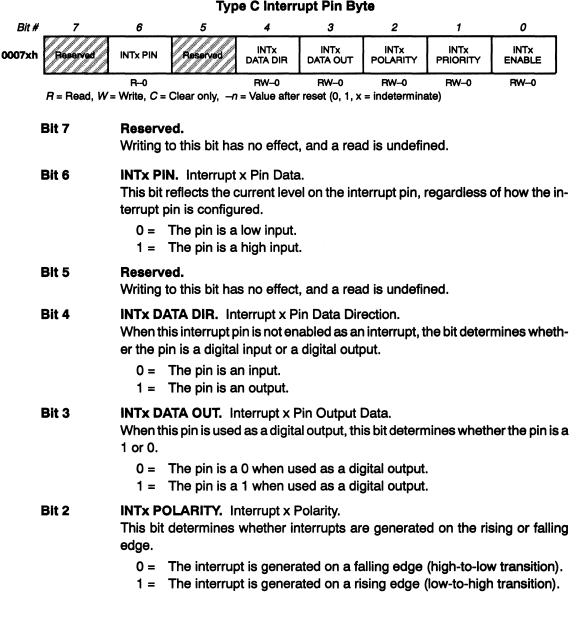

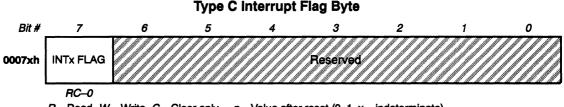

| 0074h   | INT3       | Type C Interrupt                         | 3.8.1.5      | 3-33 |

| 0075h   | INT3 FLG   | Type C Interrupt Flag                    | 3.8.1.5      | 3-33 |

| 0076h   |            | Reserved                                 |              |      |

| 0077h   |            | Reserved                                 |              |      |

| 0078h   |            | Reserved                                 |              |      |

| 0079h   |            | Reserved                                 |              |      |

| 007Ah   |            | Reserved                                 |              |      |

| 007Bh   |            | Reserved                                 |              |      |

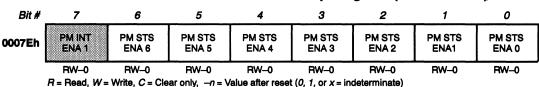

| 007Ch   | PM2 ENABLE | Power Module Interrupt Enable Register 2 | 3.8.2.1      | 3-35 |

| 007Dh   | PM2 FLAGS  | Power Module Interrupt Flag Register 2   | 3.8.2.2      | 3-36 |

| 007Eh   | PM1 ENABLE | Power Module Interrupt Enable Register 1 | 3.8.2.1      | 3-35 |

| 007Fh   | PM1 FLAGS  | Power Module Interrupt Flag Register 1   | 3.8.2.2      | 3-36 |

#### Table 1–3. TMS370C16 Typical Interrupt Control Registers

1-6 TMS370C16 CPU

### Chapter 2

### Architecture

This chapter describes the programmer's model registers and how the 128Kbyte memory is organized and addressed. Topics in this chapter include:

#### Topic

#### Page

| 2.1 | Programmer's Model                      |

|-----|-----------------------------------------|

| 2.2 | CPU Register File (R0–R15)              |

|     | 2.2.1 Frame Pointer (FP, R0) 2-5        |

|     | 2.2.2 Implied Register (IM, R1) 2-5     |

|     | 2.2.3 Stack Pointer (SP, R13) 2-6       |

|     | 2.2.4 Status Register (ST, R14) 2-6     |

|     | 2.2.5 Zero Register (ZR, R15)           |

| 2.3 | Program Counter (PC) and Address Bus    |

| 2.4 | instruction Organization 2-10           |

| 2.5 | System Stack                            |

|     | 2.5.1 Stack Operation During Interrupts |

|     | 2.5.2 Stack Use with a Call 2-12        |

| 2.6 | Data Organization and Memory Mapping    |

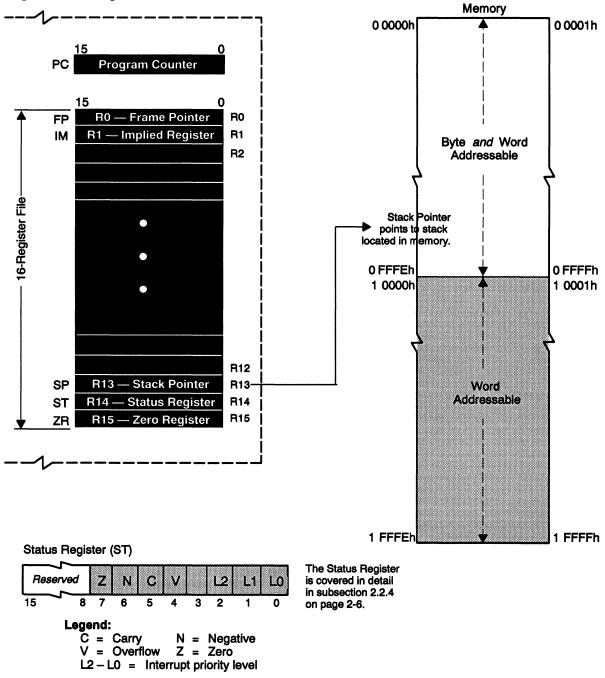

#### 2.1 Programmer's Model

The TMS370C16 programmer's model consists of a 16-bit program counter and a 16-register file, which contains 11 general-purpose registers as well as the frame pointer, implied register, stack pointer, status register, and zero register. These are shown in Figure 2–1. The 'C16 may access RAM, EEPROM, EPROM, or ROM modules internally, depending on your device configuration. The 'C16 may also access the system module (further described in Section 3.1) that controls device operations such as stack location, reset, interrupts, I/O configurations, and the CLKOUT pin initialization. The 'C16 CPU and system module interface through the system address, data, and control buses to other modules such as the SPI, SCI, ADC, and gage drivers, depending upon your specific device configuration.

Figure 2–1 shows the register file and the memory accessible by the TMS370C16 CPU. The 16-register file is located in the CPU and includes five preassigned registers (R0, R1, R13, R14, and R15). This register file is discussed in further detail in Section 2.2, starting on page 2-4, and the status register (R14) and its bits, shown in the bottom of Figure 2–1, are described in more detail in subsection 2.2.4, page 2-6.

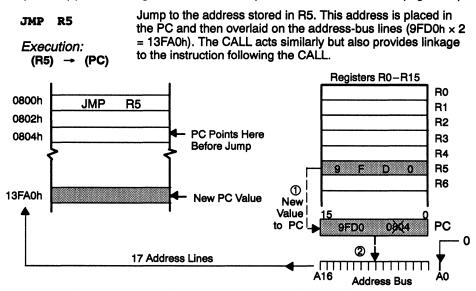

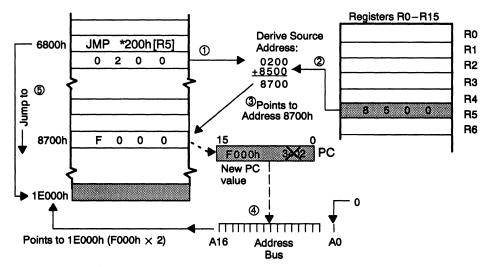

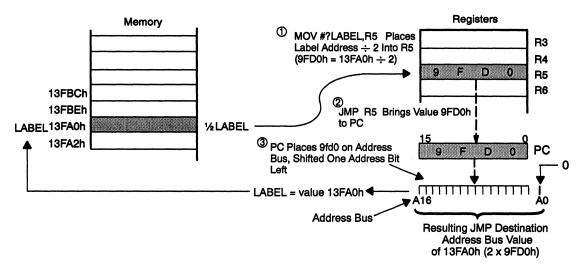

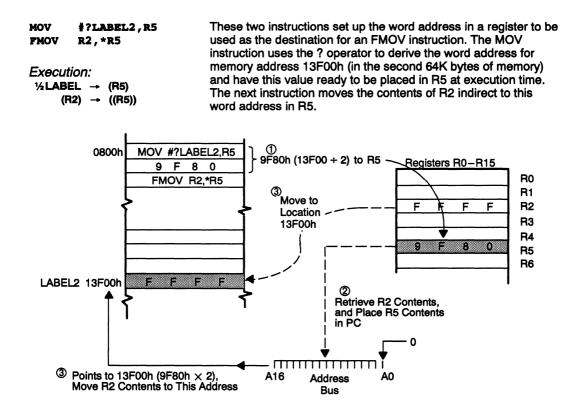

The program counter (PC), not part of the register file, contains the *word address* of an opcode or operand. The word address is applied to address lines A16–A1, with line A0 set to 0 (effectively multiplying the actual byte address by 2). This allows accessing data and executing code in a full 128K bytes of memory. The word address is further described in Section 2.3 on page 2-8, which includes a list of instructions using a 17-bit address (see Table 2–2 on page 2-9).

2-2

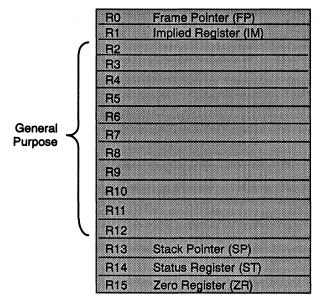

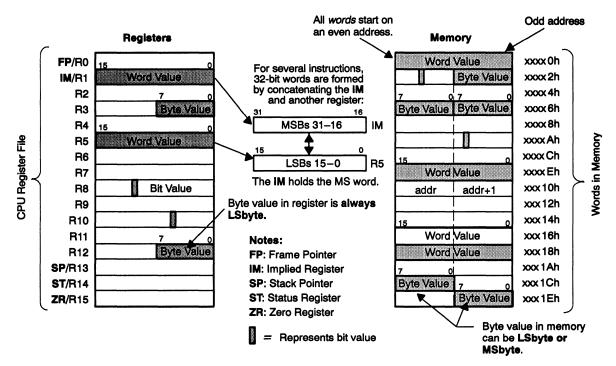

#### 2.2 CPU Register File (R0 - R15)

The TMS370C16 CPU contains 16 registers, R0 - R15, that are not part of the memory map. Of the 16 registers, five can be used for the specialized functions listed in Figure 2–2 (registers R0, R1, R13, R14, and R15) or for general purposes.

R2-R12, the 11 nonspecialized registers of the CPU register file, can be used for data manipulation for bit, byte (least significant byte), or word values. Take care when attempting to use any of the five specialized registers as generalpurpose registers. The zero register (R15) reads as a zero value at all times, *and write values will be ignored.* Of the other specialized registers, R0 and R1 can be used conditionally, but R13 (stack pointer) and R14 (status) should not be used as general purpose at any time.

The values of the register file *are not* initialized by a reset. Your system software should initialize these registers during a startup procedure.

Figure 2–2. Registers R0 to R15

#### 2.2.1 Frame Pointer, FP (R0)

The frame pointer can be used by high-level languages to allocate and deallocate procedure stack frames from the system stack. This register is implicitly used in the following instructions:

- LINK Link the FP to the current frame of the current SP (stack pointer) by pushing the FP onto the stack, setting the FP to the SP value, and then allocating designated words of stack.

- **UNLINK** Deallocate the current system stack frame by placing the FP contents in the SP and then retrieving the previous FP value from the system stack.

- **RTDU** Unlink and deallocate the current system stack frame by placing the FP value in the SP, retrieving the previous FP and PC contents from the stack (to return from a subroutine), and then subtracting a displacement from the SP.

#### 2.2.2 Implied Register, IM (R1)

The implied register assists in dealing with 32-bit objects by serving as the most significant word of the two-word value. Also, in division operations, the IM holds the remainder.

The IM is used implicitly by the following instructions:

- ASRL Arithmetic shift right, longword (32-bit value)

- ASR0L Arithmetic shift right and round to 0, longword (32-bit value); add 1 if N[[ST]] and C[[ST]] are both 1

- SHLL Arithmetic shift left, longword (32-bit value)

- DIVS Division, signed (16- and 32-bit)

- **DIVU** Division, unsigned (16- and 32-bit)

- EXTS Sign-extend word to 32 bits

- LSRL Logically right-shift, longword (32-bit value)

- MPYS Signed word multiplication

- MPYU Unsigned word multiplication

- **TRUNCSL** Test to see if register can be truncated from 32 to 16 bits

#### 2.2.3 Stack Pointer, SP (R13)

The stack pointer identifies the top of the stack — the location within the system stack to be used next (e.g., for storage of the current environment during interrupt processing). The stack also holds the return address for subroutine calls and provides a means of allocating procedure stack frames.

The SP is implicitly declared by the following instructions:

| CALL   | Jump to subroutine (return address on stack)                                                                                                                          |  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LINK   | Link to current stack frame (FP to stack, SP to FP, and allo-<br>cate requested words of space to the stack)                                                          |  |

| POP    | Pull values from top of stack to register(s)                                                                                                                          |  |

| PUSH   | Push values on top of stack from register(s)                                                                                                                          |  |

| RTDU   | Unlink and deallocate current stack frame (return to former PC and new stack address)                                                                                 |  |

| RTI    | Return from interrupt (retrieve PC and ST values from stack)                                                                                                          |  |

| RTS    | Return from subroutine (retrieve PC from stack)                                                                                                                       |  |

| TRAP   | Generate one of 256 trap exceptions (push ST and PC + 1<br>onto stack, use vector offset and TRAP vector table to set PC,<br>and set interrupt level at ST to all 1s) |  |

| UNLINK | Deallocate current stack frame (retrieve previous SP contents from FP register and retrieve old FP contents from stack)                                               |  |

Section 2.5 on page 2-11 contains a detailed discussion of the system stack.

#### 2.2.4 Status Register, ST (R14)

The status register contains CPU status information from operations performed by the Arithmetic Logical Unit (ALU). The condition code bits Z (zero), N (negative), C (carry), and V (overflow) are typically altered during instruction execution. Status is based on the data object size — byte (8), word (16), or longword (32 bits) — of the just-executed instruction. The ST also contains the interrupt mask level bits L2 - L0.

ST bit definitions:

- Reserved (r): Bits reserved for future use. Data written to them are not retained.

- Z: Zero bit. Set to 1 when an instruction generates a zero-value byte, word, or longword.

- N: Negative bit. Generally set to the value of the most significant bit (e.g., sign bit) of an instruction's result. This is bit b7 for byte, b15 for word, and b31 for longword operations.

- C: Carry bit. Set to 1 to indicate whether an unsigned overflow or underflow (carry/borrow) occurred during an arithmetic operation. Testing occurs as appropriate for the size of the data being operated on (byte, word, or longword). Some shift instructions use the C bit as a destination for the bit shifted. Bit load/store instructions treat the C bit as a bit accumulator.

- V: Overflow bit. Generally set to 1 if a signed twos-complement overflow or underflow occurred during an arithmetic operation. Testing occurs as appropriate for the size of the data being operated on (byte, word, or longword).

- L<sub>n</sub>: *Interrupt-mask level bits (L2–L0)*. Coded to specify interrupt levels of 000<sub>2</sub> 111<sub>2</sub> (0-7) with level **7 the highest** priority and level **0 the lowest**. Chapter 3 covers interrupt handling in detail (see Sections 3.7, 3.8, 3.9, and 3.10, beginning on page 3-19).

#### 2.2.5 Zero Register, ZR (R15)

The zero register's contents are *always* 0000h. Thus, it is useful when a zero constant value is required.

This register can be used with indexed addressing (format \*disp[Rn]) to generate a direct address. When Rn is declared to be ZR (disp[ZR]), displacement disp becomes the operand's address (disp + 0). Thus, operands \*disp[ZR] and &disp are equivalent; use of the ampersand (&) operator for direct addressing is further explained in Section 4.4 on page 4-5.

#### Note: Register Considerations

- 1. Do not use R14 (status register) as a general-purpose register.

- 2. R15 (zero register) will always be read as a zero value; writing operations are ignored.

#### 2.3 Program Counter (PC) and Address Bus

The PC is a 16-bit register, *not* included in the register file, that contains the *word* address of the instruction or instruction extension word that the CPU will fetch next. Because the PC uses the word-address data type, the instruction and the instruction extension words can be located at any **even** address in the entire 128K-byte memory address space of the 'C16. The term *word address* is defined in the note below.

#### Note: Word Address Definition

A **word address** is a 16-bit pointer that maps into a 128K-byte address space. Note that 17 bits are needed to fully address a 128K-byte space. Because the 'C16 requires that words begin on an even-byte boundary, the least significant bit of the word's address must be 0 with only the upper 16 bits of an address are required to access the word. A *word address* contains these 16 bits.

The PC holds the 16 *most significant bits* of the 17-bit memory address space. All instructions are word aligned; thus, *the least significant address bit* (bit 0) of all program references **always contains the value 0** (illustrated in Figure 2–3).

Because of a pipeline architecture, the PC typically points to a memory address *two words beyond the currently executing instruction or to its extension word.* This relationship is graphically shown in Figure 2–4.

#### Figure 2-4. Relationship Between the PC and Memory Address

Figure 2–6 on page 2-13 describes execution flow during a jump to a subroutine. It also shows PC values and their corresponding address bus values. The note at the bottom of the figure explains the relationships.

The instructions in Table 2–2 use the PC register (thus generating a 17-bit address).

Table 2–2. Instructions That Use a 17-Bit Address

| Instruction   | Description                                                                          |

|---------------|--------------------------------------------------------------------------------------|

| Bcond         | Branch conditionally                                                                 |

| <b>BRBIT0</b> | Branch if bit equals 0                                                               |

| BRBIT1        | Branch if bit is a 1                                                                 |

| CALL          | Jump to (call) a subroutine (linkage provided)                                       |

| DBNZ          | Decrement register; branch only if result is 0                                       |

| FMOV          | Move (far) data to or from an address of up to 128K bytes                            |

| JMP           | Jump unconditionally                                                                 |

| RTDU          | Return from subroutine and deallocate                                                |

| RTI           | Return from interrupt                                                                |

| RTS           | Return from subroutine                                                               |

| TRAP          | Generate one of 256 trap software interrupts; trap locations begin at address 08000h |

The PC is also involved in the processing of reset, peripheral interrupts, and illegal opcode exceptions.

#### 2.4 Instruction Organization

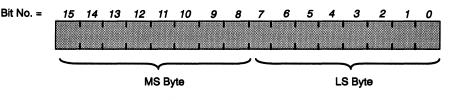

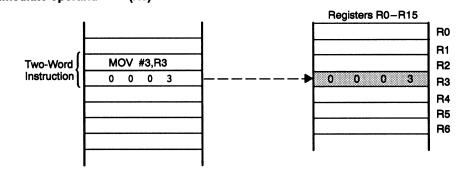

Bits are organized as shown in Figure 2–7. Instructions utilize one-, two-, or three-word formats as illustrated in Figure 2–5 for three different move instructions.

#### (c) Three-Word Instruction

MOV #1000h,\*LABEL[R6] ; Move 1000h to LABEL + R6

#### 2.5 System Stack

The stack is a dedicated area of last-in/first-out RAM that is:

- Located in the first 64K bytes of memory

- Used for the storage of data that can describe an operating environment about to be exited or re-entered (such as the PC and ST values)

- Accessed by instructions that place data (PUSH instruction) into it from registers or retrieve data (POP instruction) from it into registers

- Used during a peripheral interrupt to store the operating environment that is to be exited (current ST and PC contents) before the address of the interrupt service routine is fetched

- Pointed to by the stack pointer (SP)

Table 2–3 lists instructions that use the stack:

Table 2-3. Instructions That Use The Stack

| Instruction | Description                                                                                                                                                  | Detail                                                                                                                       |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| CALL        | Jump to subroutine; provide return<br>linkage                                                                                                                | Push address of next instruction onto stack,<br>then place destination value in PC (shown in<br>Figure 2–6, page 2-13)       |

| LINK        | Link frame pointer (FP) to current stack; allocate stack space                                                                                               | Push FP onto stack, copy SP (old) to FP, then<br>add displacement to SP for <i>new</i> SP value                              |

| POP         | Copy stack words into specified reg-<br>isters                                                                                                               | Specify range of registers affected                                                                                          |

| PUSH        | Copy specified register words onto the stack                                                                                                                 | Specify range of registers affected                                                                                          |

| RTI         | Return from interrupt                                                                                                                                        | Pop PC and ST values from stack                                                                                              |

| RTS         | Return from subroutine                                                                                                                                       | Pop PC from stack (shown in Figure 2–6,<br>page 2-13; RTS is at step 3 in the figure)                                        |

| RTDU        | Return from subroutine and deallocate current stack space                                                                                                    | Can be a return from a CALL <i>but only if</i> sub-<br>routine executed a LINK instruction without an<br>UNLINK instruction  |

| TRAP        | Generate one of 256 trap exceptions                                                                                                                          | Push ST and address of next instruction onto stack. Retrieve trap subroutine address from trap vector table and place in PC. |

| UNLINK      | Unlink and deallocate stack frame                                                                                                                            | Place FP value in SP, then pop previous FP value from stack                                                                  |

| ILLEGAL     | Generate trap exception; this is<br>caused when the instruction's illegal<br>code of 0000h is decoded (one of<br>several illegal opcodes that cause<br>this) | Push ST and address of next instruction onto stack; place subroutine address from first trap location in PC                  |

#### 2.5.1 Stack Operation During Interrupts

A major use of the stack is to provide return linkage for a context switch. Steps of a typical context switch are as follows:

- 1) Context switch (e.g., interrupt) is recognized. Complete presently executing instruction.

- 2) Store present status register (ST) contents on the stack. Increment the stack pointer (SP) by two to the next memory address.

- Store the present program counter value (PC) at the SP value (next address after the location where the ST is stored). Increment the SP by two.

- 4) Enter and execute the service routine for the context switch. When the routine is complete, reverse the process in steps 1 through 3 above to return to the environment present when the context switch was requested. This return is usually through an RTI (return from interrupt) instruction.

- Decrement the SP by two. Retrieve the previous PC value at that address, and place it in the PC. Decrement the PC by two (this is explained in the RTI instruction description).

- 6) Decrement the SP by two. Retrieve the previous ST value at that address, and place it in the ST.

#### 2.5.2 Stack Use with a Call

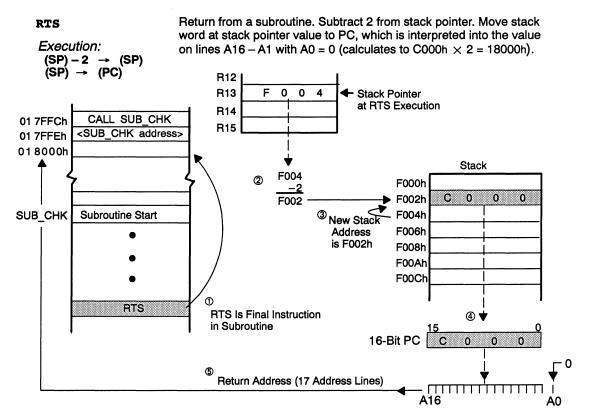

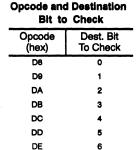

Figure 2–6 depicts how a stack is used when calling a subroutine with the CALL (jump to subroutine) instruction and then later returning to the calling environment. Numbered steps at the bottom of the figure correspond to circled numbers in the figure to explain execution sequence.

The stack increments by two after each *push* of a word value onto the stack. Conversely, the stack is decremented by two before each word is *pulled* (*popped*) from a stack.

#### Note: The SP Must Contain an Even Value

Make sure that the value stored in the SP (R13) is an *even* value (a 0 in address line A0). An odd value causes an illegal-access reset when the stack is addressed.

All implicit stack references by these instructions generate *word* read/write cycles to memory and thus are restricted to **even** addresses. The SP contents are used for address lines A0 - A15; thus, they should always be an even value. A nonaligned memory access generates a reset.

Figure 2-6. Example of Stack Use to and From a Subroutine

The CALL sequence:

- ① The CALL SUBR instruction causes a branch to subroutine SUBR with return values stored in the stack. Before the entry address of SUBR is placed in the PC:

- 1) The present PC value (now pointing four bytes past the address containing the CALL opcode) is stored at the present contents in the stack pointer (SP).

- 2) The SP is incremented by two.

- ② The value of SUBR is placed in the PC. Execution begins at address C000h and continuesdown to address C0A4h, which contains the last instruction in the subroutine — RTS (return from subroutine).

- ③ RTS returns the program back to the environment at the time of the CALL instruction by:

- 1) Decrementing the SP by two to point to the address containing the PC value at the time of the CALL instruction.

- 2) Placing the contents at the SP value into the PC. Execution begins at the next instruction after CALL.

#### 2.6 Data Organization and Memory Mapping

Data resides in memory and on-chip registers with the most significant bit in the left-most position. Figure 2–7 shows the significance of bits and bytes.

Figure 2–7. Bit and Byte Numbering for Instructions, Registers, and Words

A word comprises two bytes:

- the most significant byte is on an even boundary, and

- the *least significant* byte occupies the next higher (*odd*) byte address.

#### Note: Word Address Definition

A word address is a 16-bit pointer that maps into a 128K-byte address space. Note that 17 bits are needed to fully address a 128K-byte space. Because the 'C16 requires that words begin on an even-byte boundary, the least significant bit of the word's address must be a 0; only the upper 16 bits of an address are required to access the word. A *word address* contains these 16 bits.

All word data in memory must be aligned on an even address.

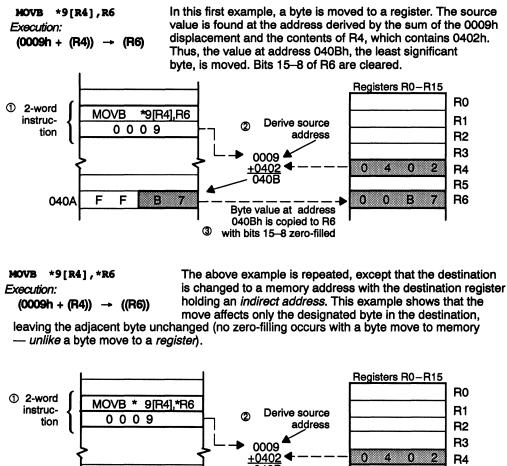

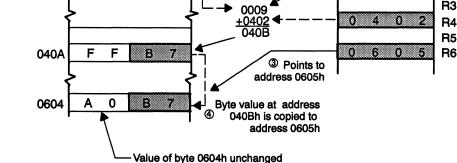

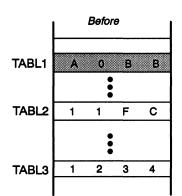

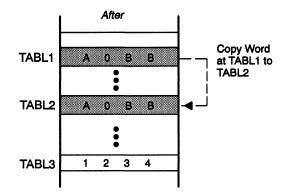

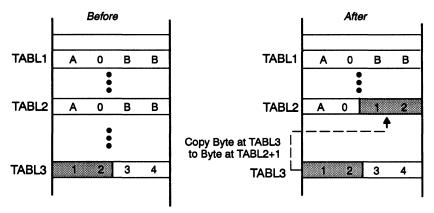

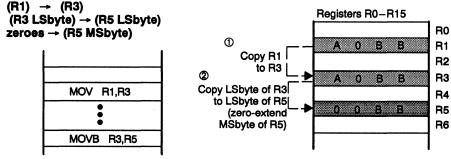

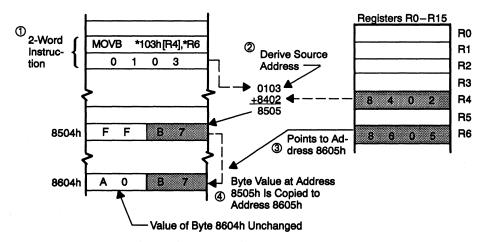

For **byte** operations, the byte operand values are zero-extended to word length, are operated on as words, and produce a word result. *Register destinations* receive the entire word (the MSbyte zero-extended), but *memory destinations* receive only the LSbyte of the result. Thus, a byte moved to a register via the MOVB instruction zeroes the MSbyte of the register with the moved byte in the LSbyte. The same byte moved to a memory address affects only the destination byte addressed. This is illustrated in Figure 2–8 on page 2-16.

Figure 2–9 on page 2-17 shows how bits, bytes, and words are organized in memory and in the register file. Shown in the figure are the least and most significant bits and bytes. The accompanying explanations below the figure complete the description.

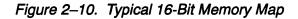

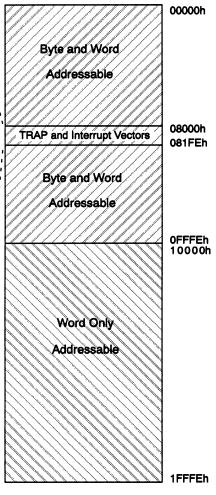

Figure 2–10 on page 2-18 shows a *typical* memory configuration and how the first and second 64K bytes of memory are divided into blocks for 1) **byte and word** access in the lower 64K bytes of memory and 2) **word-only** access in the higher 64K bytes.

For purposes of this manual, these symbols have these meanings:

| Symbol | Meaning                                              | Example                                                                                                        |

|--------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| (x)    | Contents of register x or of memory at address x     | (Rn) = the contents of Rn                                                                                      |

| ((×))  | Contents of memory<br>designated by contents<br>of x | (disp + (Rn)) = the contents within the value found by adding the contents of Rn with the displacement amount. |

#### Figure 2–8. Differences in Memory and Register ByteDestinations

#### Figure 2–9. Data Organization Examples in Registers and Memory

Data restrictions depend upon their location in a register or in memory (as shown in Figure 2–9 above):

| Data Size              | Register                                                                                                   | Memory                                                                                                                                                                     |

|------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Single Bit             | Can be any bit in any register in the register file.                                                       | Can be any bit in any byte in the first 64K bytes of memory.                                                                                                               |

| Byte<br>(8 bits)       | The least significant byte of any register in the register file.                                           | Can be any byte in the first<br>64K bytes of memory. Any<br>adjacent byte is not affected.                                                                                 |

| Word<br>(16 bits)      | Can be any register in the register file.                                                                  | Can be any byte pair where<br>the most significant byte of<br>the word is at an even<br>address and the least signifi-<br>cant byte is at the next<br>higher byte address. |

| Long Word<br>(32 bits) | Uses a register pair in the register file with the most significant word in the IM (implied register, R1). | Not applicable.                                                                                                                                                            |

As shown in Figure 2–10, two 64K-byte areas concatenate to form 128K bytes of addressable memory. The generic view on the left shows that the lower-address half can be accessed as either byte or word, and the higher-address half is accessible as word-only by such instructions as FMOV and CALL. The right side of the figure is an *example* of possible code and data utilization. The actual size of the memory module is device specific. See your specific device data sheet to determine the size of the memory modules for your particular device. The lowest memory addresses contain the control registers, which are expanded in Figure 2–11 (next page).

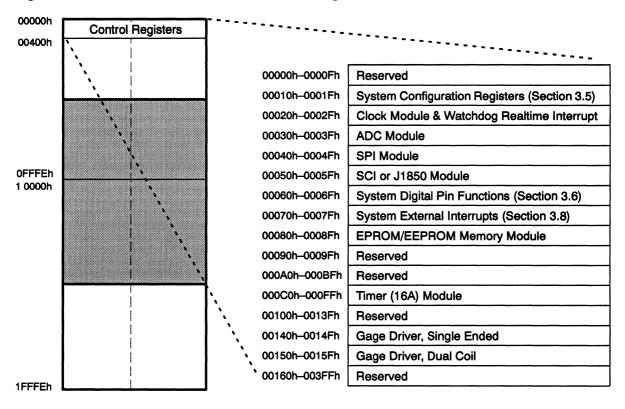

Figure 2–11. Location and Names of Control Registers

Figure 2–11 lists the 16 control-register groups in the lowest 1K bytes of memory. Each register group is 16 bytes and contains the working registers for each module or for the system configuration. These registers are further described in Section 3.5 on page 3-7.

# **TMS370C16 System Configuration**

This chapter discusses system configuration requirements, I/O, interrupts, reset, and low-power modes of the TMS370C16 CPU. Features and options are described, including the registers that control the configuration. This chapter covers the following topics:

#### Topic

#### Page

| 3.1  | System Configuration Overview                         |

|------|-------------------------------------------------------|

| 3.2  | System Reset Operation 3-3                            |

| 3.3  | CLKOUT Pin Function Selection 3-6                     |

| 3.4  | Parallel Signature Analysis Operation (CRC Generator) |

| 3.5  | System Configuration Registers 3-7                    |

| 3.6  | General-Purpose Digital Functions                     |

| 3.7  | Interrupt and Exception Handling                      |

| 3.8  | External and Power Module Interrupts 3-25             |

| 3.9  | Multiple Interrupt Servicing                          |

| 3.10 | TMS370C16 Interrupt Configurability Options           |

| 3.11 | Low-Power and Idle Modes 3-40                         |

# 3.1 System Configuration Overview

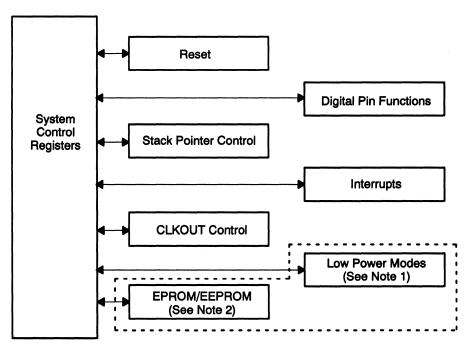

The system module controls device operations such as clock source, stack location, reset, interrupts, and I/O. The actual number of external interrupts and I/O pins is device specific; consult the data sheet for a particular device. Certain device status information is also contained within the system module. The system module block diagram is shown in Figure 3–1.

Figure 3–1. System Block Diagram

Notes:

1. See the Clock Modules Reference Guide.

2. See the EEPROM/EPROM Modules Reference Guide.

## 3.2 System Reset Operation

The system reset operation ensures an orderly start-up sequence for the TMS370C16 CPU-based device. Seven actions can cause a system reset to the device; six of these are internally generated, while the RESET-pin interrupt is controlled externally.

- RESET Pin. A negative edge can trigger a signal on this external pin.

- Watchdog (WD) Timer Overflow. A watchdog-generated reset occurs if the WD timer overflows or an improper value is written to either the WD key register or the WD control register. (See your Watchdog Timer and Real-Time Interrupt Reference Guide for details on these registers.)

- Software-Generated Reset. Writing a 0 to the RESET0 bit (SCR0.6) or a 1 to the RESET1 bit (SCR0.7) causes a reset (SCR0 is the system control register 0, as shown in Figure 3–3 on page 3-7.)

- Illegal Address Access. Attempting to access a nonmemory (not implemented) address causes a reset. (This action is device specific, relative to the memory configuration.)

- Oscillator Reset. Operation of the oscillator outside of the recommended operating range, as indicated by the OSCRST bit of the system reset status register (subsection 3.5.3, page 3-10), causes the clock module to issue a reset. See the *Clock Modules Reference Guide* for more information.

- □ V<sub>CC</sub> Out-of-Range. Operation with V<sub>CC</sub> outside of the recommended operating range may also act as a brownout indicator in addition to ensuring proper operation on power-up sequences.

- Illegal Access. Attempting to access a word by using an odd address causes a reset.

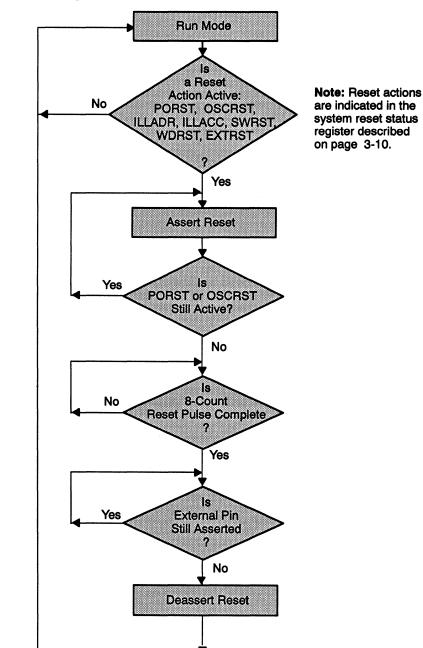

Once a reset source is activated, the external  $\overrightarrow{\text{RESET}}$  pin is driven active low for a minimum of eight SYSCLK cycles. This allows the 'C16 CPU-based device to reset any external devices connected to the  $\overrightarrow{\text{RESET}}$  pin. Normally, the reset logic holds the 'C16 device in a reset state for eight SYSCLK cycles; however, if a V<sub>CC</sub> out-of-range condition or oscillator failure occurs (or the  $\overrightarrow{\text{RESET}}$  external pin is held low), then the reset logic holds the device in a reset state for as long as these conditions exist. Figure 3–2 shows the reset state diagram for the 'C16 device in the normal run mode.

Figure 3–2. Reset State Diagram — Normal Run Mode

After a reset, the program determines the source of the reset by reading the contents of the system reset status register (SRSR, shown in Figure 3–3 on page 3-7). There is one status bit for each of the seven sources that can cause a reset.

Once a reset is activated, the following sequence of events occurs in the 'C16:

- The CPU registers and module control registers are initialized to their reset state. The ST interrupt mask bits are set to all 1s to prevent any interrupt request, including nonmaskable interrupts (NMIs).

- 2) The correct index value to the trap table base address is computed.

- 3) The service-routine address is read from address 8002h.

- 4) The prefetch pipeline is reloaded.

The reset sequence takes six cycles from the time the reset is released until the first opcode fetch begins. During a reset, RAM contents remain unchanged, and the module control register bits are initialized to their reset state.

To generate an external reset pulse on the  $\overrightarrow{\text{RESET}}$  pin, a low-level pulse duration of as little as a few nanoseconds is usually effective; however, pulses of one SYSCLK cycle are recommended to guarantee that the device acknowledges the reset. A typical reset circuit required for the 'C16 CPU-based device consists of a 10-kilohm pullup resistor from the  $\overrightarrow{\text{RESET}}$  pin to V<sub>CC</sub>. Only this single resistor is needed if a primary voltage regulator or brownout detection circuit is on your device. See the specific device data sheet to determine whether additional circuitry is required.

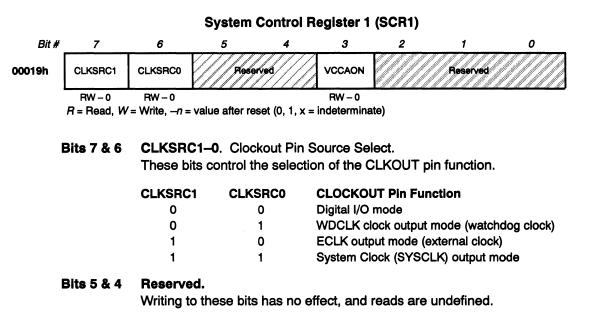

# 3.3 CLKOUT Pin Function Selection

You can select the CLKOUT pin to operate as one of four different functions:

- Digital I/O

- Watchdog clock (WDCLK) output

- External clock (ECLK) output

- System clock (SYSCLK) output

The function is determined by two clock source control bits, CLKSRC1 and CLKSRC0 (SCR1.7 and SCR1.6 respectively, shown in Figure 3–3 on page 3-7). Table 3–1 illustrates the CLKOUT pin function selection options.

Table 3–1. CLKOUT Pin Function Options

|             | CLKSRC1 | CLKSRC0 |

|-------------|---------|---------|

| Digital I/O | 0       | 0       |

| WDCLK       | 0       | 1       |

| ECLK        | 1       | 0       |

| SYSCLK      | 1       | 1       |

For more information, see subsection 3.5.2 on system control register 1 on page 3-9, the specific device data sheet, or the *Clock Modules Reference Guide*.

# 3.4 Parallel Signature Analysis Operation (CRC Generator)

The TMS370C16 device contains an internal 16-bit parallel signature analysis (PSA) circuit that provides a continuous cyclic redundancy check (CRC) function. Two associated registers, PSAR1 and PSAR2 (located at addresses 0001Eh and 0001Fh in the system configuration register), determine a unique 16-bit signature. (The system configuration register is further described in Section 3.5 and in Figure 3–3 on the next page.)

When any memory location (RAM, EEPROM, ROM, EPROM, or control register) is read, the contents of the PSA registers are updated (register bits are described in subsection 3.5.5 on page 3-13). You can create a predetermined signature by initializing the PSA registers to a known value and then reading all memory locations. It is suggested that you read both PSA registers as a single word (*avoid multiple reads such as reading each byte individually*).

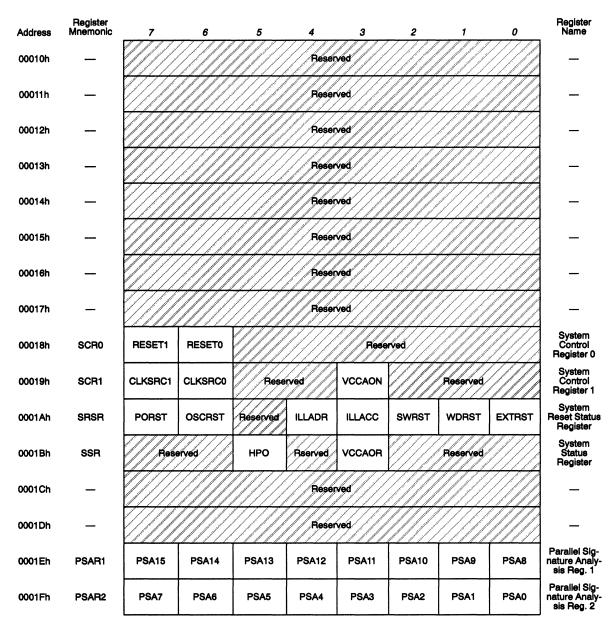

# 3.5 System Configuration Registers

The TMS370C16 system configuration registers are shown in Figure 3–3 and are discussed in detail in the following sections. These registers can be accessed in either byte or word mode.

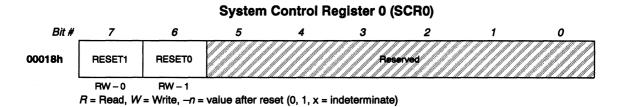

# 3.5.1 System Control Register 0 (SCR0)

The system control register 0 (SCR0) controls the software reset capability of TMS370C16 CPU-based devices.

#### Bits 7 & 6 RESET1/RESET0. Software Reset.

These bits, which control the software reset function of the device, must be written to at the same time. Writing a 1 to RESET1 *or* a 0 to RESET0 causes a global reset to occur as shown in the following table:

| RESET1 | RESET0 | <b>Resulting Action</b> |

|--------|--------|-------------------------|

| 0      | 0      | Global reset            |

| 0      | 1      |                         |

| 1      | 0      | Global reset            |

| 1      | 1      | Global reset            |

#### Bits 5 – 0 Reserved.

Writing to these bits has no effect, and reads are undefined.

# 3.5.2 System Control Register 1 (SCR1)

The system control register 1 (SCR1) controls the CLKOUT pin function and the analog power supply enable.

#### Bit 3 VCCAON. V<sub>CCA</sub> (Analog Power Supply) Enable.

This bit controls the ability of the primary voltage regulator or the brown-out detect circuit to turn the analog power supply ( $V_{CCA}$ ) on and off.

- 0 = Analog power supply is disabled.

- 1 = Analog power supply is enabled.

#### Bits 2–0 Reserved.

Writing to these bits has no effect, and reads are undefined.

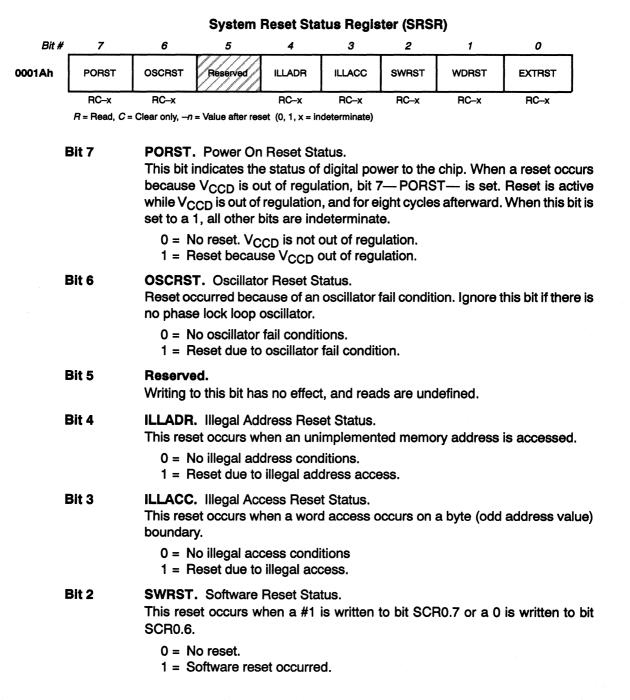

## 3.5.3 System Reset Status Register (SRSR)

The system reset status register (SRSR) contains system-reset history status information. These bits should be cleared after being read.

#### Bit 1 WDRST. Watchdog Reset Status.

See your *Watchdog Timer and Real-Time Interrupt Module Reference Guide* to determine whether this bit applies to your device.

0 = No reset.

1 = Reset due to watchdog timer overflow.

#### Bit 0 EXTRST. External Reset Status.

0 = No reset.

1 = This bit is set when the external RESET pin is pulled low by any source, including an internal reset.

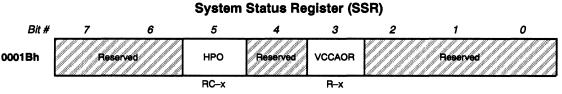

# 3.5.4 System Status Register (SSR)

The system status register (SSR) contains status information about the operational modes of the device.

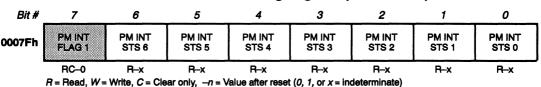

R = Read, C = Clear only, -n = Value after reset (0, 1, x = indeterminate)

Bits 7 & 6 Reserved.

Writing to these bits has no effect, and reads are undefined.

#### Bit 5 HPO. Hardware Protect Override.

The hardware protect override function allows protected EEPROM bits to be written to and enables EPROM programming. To set this bit, external pin INT1 must be at 12 V on the rising edge of RESET. If INT1 is less than 12 V, the bit is a 0. You can disable this function by writing a 0 to it.

- 0 = Normal mode.

- 1 = HPO mode.

#### Bits 4 Reserved.

Writing to this bit has no effect, and reads are undefined.

# Bit 3VCCAOR. V<sub>CCA</sub> (Analog Power Supply) Out of Regulation.This bit shows the status of the internal V<sub>CCA</sub> signal.

$0 = V_{CCA}$  is within regulated range.

$1 = V_{CCA}$  is out of regulated range.

#### Bits 2–0 Reserved.

Writing to these bits has no effect, and reads are undefined.

# 3.5.5 Parallel Signature Analysis Registers (PSARn)

The parallel signature analysis register 1 (PSAR1) contains the MSbyte of the PSA, and the parallel signature analysis register 2 (PSAR2) contains the LSbyte of the PSA.

Bits 7 – 0 PSA15–PSA8. Parallel Signature Analysis Data Bits 15 – 8. The value read from this register is the MSbyte of the most recent PSA routine.

**Bits 7 – 0 PSA7–PSA0.** Parallel Signature Analysis Data Bits 7 – 0. The value read from this register is the LSbyte of the most recent PSA routine.

# 3.6 General-Purpose Digital Pin Functions

Device pins can be configured for general-purpose digital pin functions *except* for those pins:

- That are device operation pins (V<sub>CC</sub>, V<sub>SS</sub>, RESET, INT1, etc.).

- That are *required* for module-specific operation (for the SPI, ADC, gage drivers, etc.)

The total number of digital pins available is device specific. Refer to the specific device data sheet to determine the exact number of digital pins available, pin locations, naming conventions, and control registers. This section describes the different types of digital pin functions available and how they are controlled.

The digital I/O control and status register (Figure 3–4) allows a maximum of 32 output/control functions, 32 input/status functions, and 32 bidirectional I/O pin functions. The output pin functions are also referred to as *control* pins — they can be used to turn particular internal modules on or off and are not actually tied to an external pin. The input pin functions are also referred to as *status* pins because they can be used to determine the status of internal signals on the device as well as to serve as general-purpose input pins. For example, you could use these configurations to tie an input/status function to the low-side driver over-current detection circuitry, or to tie an output/control function internally to the V<sub>CCA</sub> analog voltage output to control the primary voltage regulator during on and off V<sub>CCA</sub>.

The control registers for digital I/O (DIO) pins are located at addresses 0060h to 006Fh and are shown in Figure 3-4.

| Address       | Ports             | Functions                                                                                                                |

|---------------|-------------------|--------------------------------------------------------------------------------------------------------------------------|

| 0060h - 0063h | Output 1, 2, 3, 4 | Output/control only. Pins for output/control ports 1, 2, 3, and 4                                                        |

| 0064h – 0067h | Input 1, 2, 3, 4  | Input/status only. Pins for Input/status ports 1, 2, 3, and 4                                                            |

| 0068h 006Fh   | I/O A, B, C, D    | Pins for I/O ports A, B, C, and D, with each<br>port using one byte for I/O configuration and<br>one byte for pin value. |

The following sections explain the operation of the DIO control registers. The number of DIO control registers available depends on the 'C16 device. Usually, all digital pins available are configured as bidirectional I/O pins, and not output or input only. This configuration selection is determined during the manufacture cycle and cannot be changed by software. See the specific device data sheet for more information.

| •               | -           |        |        |        | •      |        |        |        |        |                                     |

|-----------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|-------------------------------------|

| Addr            | Reg<br>Mnem | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      | Reg<br>Name                         |

| 0 <b>006</b> 0h | OCR1        | 10UT7  | 10UT6  | 10UT5  | 10UT4  | 10UT3  | 10UT2  | 10UT1  | 10UT0  | Output/<br>Control<br>Register 1    |

| 00061h          | OCR2        | 20UT7  | 2OUT6  | 20UT5  | 20UT4  | 20UT3  | 20UT2  | 20UT1  | 20UT0  | Output/<br>Control<br>Register 2    |

| 00062h          | OCR3        | 30UT7  | 3OUT6  | 30UT5  | 3OUT4  | 30UT3  | 30UT2  | 30UT1  | 3OUT0  | Output/<br>Control<br>Register 3    |

| 00063h          | OCR4        | 40UT7  | 4OUT6  | 40UT5  | 40UT4  | 4OUT3  | 40UT2  | 40UT1  | 4OUT0  | Output/<br>Control<br>Register 4    |

| 00064h          | ISR1        | 11NS7  | 1INS6  | 1INS5  | 1INS4  | 11NS3  | 1INS2  | 1INS1  | 1INS0  | Input/<br>Status<br>Register 1      |

| 00065h          | ISR2        | 2INS7  | 2INS6  | 21NS5  | 2INS4  | 2INS3  | 2INS2  | 2INS1  | 2INS0  | Input/<br>Status<br>Register 2      |

| 00066h          | ISR3        | 3INS7  | 3INS6  | 3INS5  | 3INS4  | 3INS3  | 3INS2  | 3INS1  | 3INS0  | Input/<br>Status<br>Register 3      |

| 00067h          | ISR4        | 4INS7  | 4INS6  | 4INS5  | 4INS4  | 4INS3  | 4INS2  | 4INS1  | 4INS0  | Input/<br>Status<br>Register 4      |

| 00 <b>068</b> h | ADIR        | ADIR7  | ADIR6  | ADIR5  | ADIR4  | ADIR3  | ADIR2  | ADIR1  | ADIR0  | I/O Port A<br>Direction<br>Register |

| 00069h          | ADATA       | ADATA7 | ADATA6 | ADATA5 | ADATA4 | ADATA3 | ADATA2 | ADATA1 | ADATA0 | I/O Port A<br>Data<br>Register      |

| 0006Ah          | BDIR        | BDIR7  | BDIR6  | BDIR5  | BDIR4  | BDIR3  | BDIR2  | BDIR1  | BDIR0  | I/O Port B<br>Direction<br>Register |

| 0006Bh          | BDATA       | BDATA7 | BDATA6 | BDATA5 | BDATA4 | BDATA3 | BDATA2 | BDATA1 | BDATA0 | I/O Port B<br>Data<br>Register      |

| 0006Ch          | CDIR        | CDIR7  | CDIR6  | CDIR5  | CDIR4  | CDIR3  | CDIR2  | CDIR1  | CDIR0  | I/O Port C<br>Direction<br>Register |

| 00 <b>06Dh</b>  | CDATA       | CDATA7 | CDATA6 | CDATA5 | CDATA4 | CDATA3 | CDATA2 | CDATA1 | CDATA0 | I/O Port C<br>Data<br>Register      |

| 00 <b>06</b> Eh | DDIR        | DDIR7  | DDIR6  | DDIR5  | DDIR4  | DDIR3  | DDIR2  | DDIR1  | DDIR0  | I/O Port D<br>Direction<br>Register |

| 0006Fh          | DDATA       | DDATA7 | DDATA6 | DDATA5 | DDATA4 | DDATA3 | DDATA2 | DDATA1 | DDATA0 | I/O Port D<br>Data<br>Register      |

|                 |             |        |        |        |        |        |        |        |        |                                     |

Figure 3–4. Digital I/O Control and Status Registers

Note: See the specific device data sheet for the actual digital pin implementation.

# 3.6.1 Digital Output/Control Registers (OCRn)

Writing to bit(s) in the digital output/control registers (OCR1, OCR2, OCR3, and OCR4) outputs values to the bit's corresponding function(s) — such as communication to an internal module or an external pin. OCR1 is illustrated below. OCR2. OCR3, and OCR4 operate identically to OCR1 but are not shown.

- Bits 7–0 10UT7 10UT0. Digital outputs to corresponding functions. The values written to any of selected bit(s) 10UT7 to 10UT0 control the state output of the corresponding function(s).

- 0 =Output a 0 (V<sub>OL</sub>) value to the selected function.

- 1 =Output a 1 (V<sub>OH</sub>) value to the selected function.

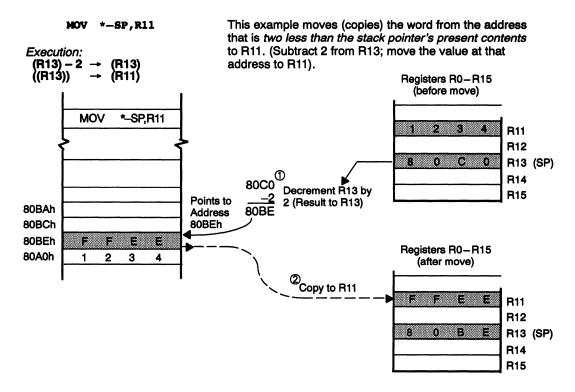

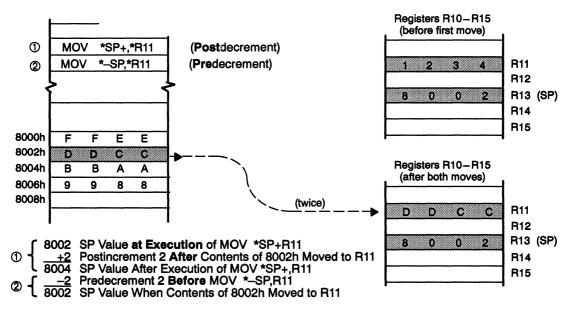

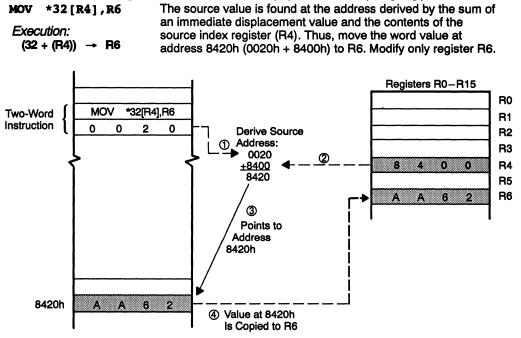

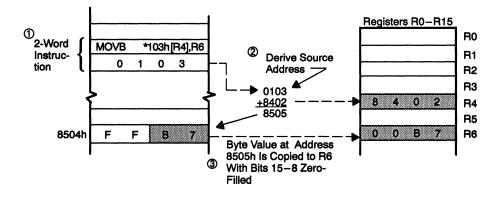

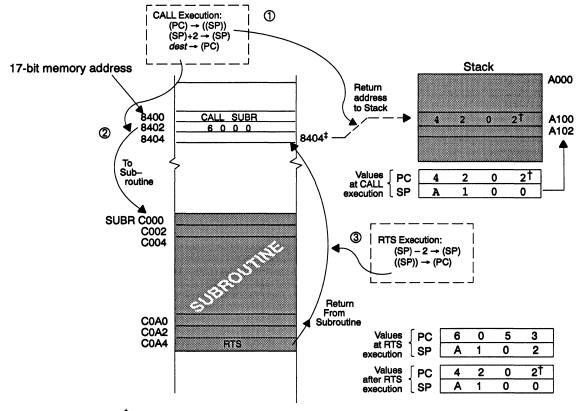

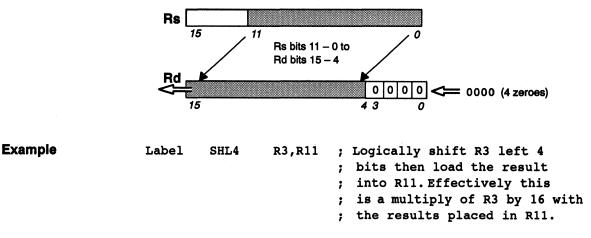

#### 3.6.2 Digital Input/Status Registers (ISRn)