# Digital Signal Processing Applications with the TMS320 Family

**Application Book**Volume 2

# Theory, Algorithms, and Implementations

Digital Signal Processing Applications with the TMS320 Family

1990

1990 Digital Signal Processor Products

# Digital Signal Processing Applications with the TMS320 Family

# Volume 2

Edited by

Panos Papamichalis, Ph.D.

Digital Signal Processing

Semiconductor Group

Texas Instruments

#### IMPORTANT NOTICE

Texas Instruments (TI) reserves the right to make changes to or to discontinue any semiconductor product or service identified in this publication without notice. TI advises its customers to obtain the latest version of the relevant information to verify, before placing orders, that the information being relied upon is current.

TI warrants performance of its semiconductor products to current specifications in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Unless mandated by government requirements, specific testing of all parameters of each device is not necessarily performed.

TI assumes no liability for TI applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

#### **TRADEMARKS**

ADI and AutoCAD are trademarks of Autodesk, Inc.

Apollo and Domain are trademarks of Apollo Computer, Inc.

ATVista is a trademark of Truevision, Inc.

CodeView, MS-Windows, MS, and MS-DOS are trademarks of Microsoft Corp.

DEC, Digital DX, VAX, VMS, and Ultrix are trademarks of Digital Equipment Corp.

DGIS is a trademark of Graphic Software Systems, Inc.

EPIC, XDS, TIGA, and TIGA-340 are trademarks of Texas Instruments, Inc.

GEM is a trademark of Digital Research, Inc.

GSS\*CGI is a trademark of Graphic Software Systems, Inc.

HPGL is a registered trademark of Hewlett-Packard Co.

Macintosh and MPW are trademarks of Apple Computer Corp.

NEC is a trademark of NEC Corp.

PC-DOS, PGA, and Micro Channel are trademarks of IBM Corp.

PEPPER is a registered trademark of Number Nine Computer Corp.

PM is a trademark of Microsoft Corp.

PostScript is a trademark of Adobe Systems, Inc.

RTF is a trademark of Microsoft Corp.

Sony is a trademark of Sony Corp.

Sun 3, Sun Workstation, SunView, SunWindows, and SPARC are trademarks of Sun Microsystems. Inc.

UNIX is a registered trademark of AT&T Bell Laboratories.

# **CONTENTS**

| FOREWORD                                                                                                                                                                                                            | . <b>v</b> |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| PREFACE                                                                                                                                                                                                             | vii        |

| PART I. INTRODUCTION                                                                                                                                                                                                |            |

| 1. The TMS320 Family and Book Overview                                                                                                                                                                              | . 3        |

| <ol> <li>The TMS320 Family of Digital Signal Processors         (Kun-Shan Lin, Gene A. Frantz, and Ray Simar, Jr., reprinted from <i>PROCEEDINGS OF THE IEEE</i>,         Vol. 75, No. 9, September 1987)</li></ol> | . 11       |

| 3. The Texas Instruments TMS320C25 Digital Signal Microcomputer (Gene A. Frantz, Kun-Shan Lin, Jay B. Reimer, and Jon Bradley, reprinted from <i>IEEE Micro Magazine</i> Vol. 6, No. 6, December 1986)              |            |

| PART II. DIGITAL SIGNAL PROCESSING INTERFACE TECHNIQUES                                                                                                                                                             |            |

| 4. Hardware Interfacing to the TMS320C2x (George Troullinos and Jon Bradley)                                                                                                                                        | 53         |

| 5. Interfacing the TMS320 Family to the TLC32040 Family (Linear Products — Texas Instruments)                                                                                                                       | 107        |

| 6. I <sub>CC</sub> Requirements of a TMS320C25 (Dave Zalac)                                                                                                                                                         | 153        |

| 7. An Implementation of a Software UART Using the TMS320C25 (Dave Zalac)                                                                                                                                            | . 167      |

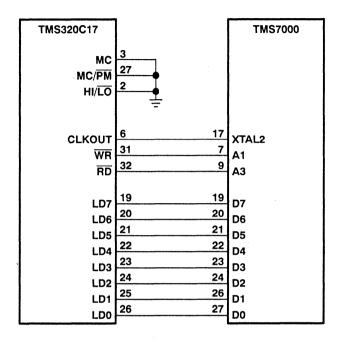

| 8. TMS320C17 and TMS370C010 Serial Interface (Peter Robinson)                                                                                                                                                       | 189        |

| PART III. DATA COMMUNICATIONS                                                                                                                                                                                       |            |

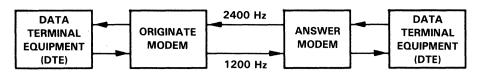

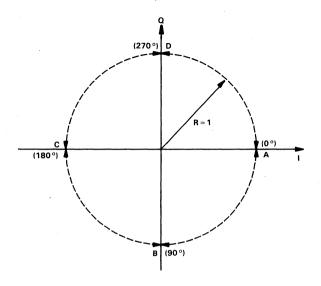

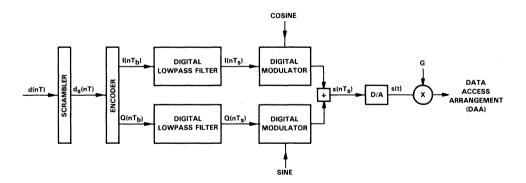

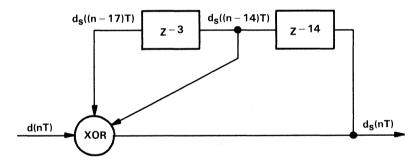

| 9. Theory and Implementation of a Splitband Modem Using the TMS32010 (George Troullinos, Peter Ehlig, Raj Chirayil, Jon Bradley, and Domingo Garcia)                                                                | . 221      |

| 10. Implementation of an FSK Modem Using the TMS320C17 (Phil Evans and Al Lovrich)                                                                                                                                  | 331        |

| 11. An All-Digital Automatic Gain Control (Al Lovrich and Raj Chirayil)                                                                                                                                             | 389        |

| PART IV. TELECOMMUNICATIONS                                                                                                                                                                                         |            |

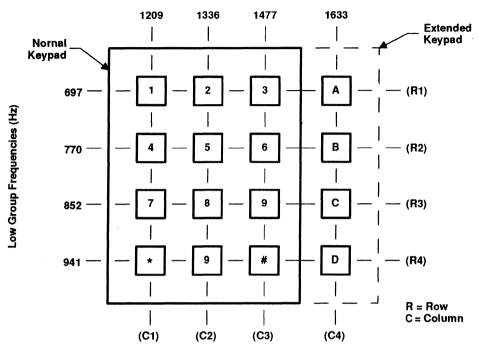

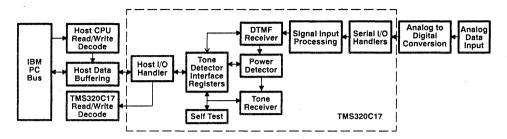

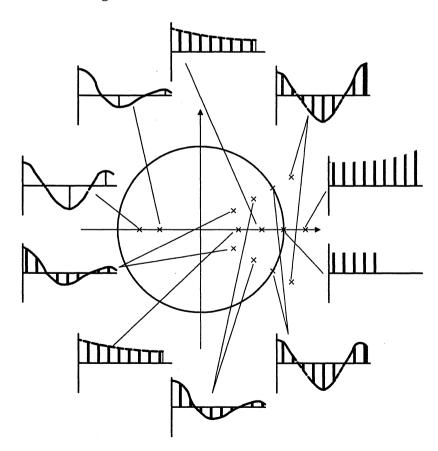

| 12. General-Purpose Tone Decoding and DTMF Detection (Craig Marven)                                                                                                                                                 | . 423      |

| PART V. CONTROL                                                                                                                                                                                                     |            |

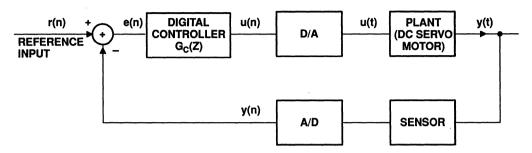

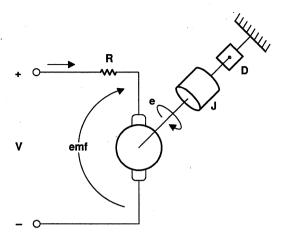

| 13. Implementation of PID and Deadbeat Controllers with the TMS320 Family (Irfan Ahmed)                                                                                                                             | . 529      |

# PART VI. TOOLS

| 14. TMS320 Algorithm Debugging Techniques |     |

|-------------------------------------------|-----|

| (Peter Robinson)                          | 585 |

| TMS320 BIBLIOGRAPHY                       | 597 |

| INDEX                                     | 615 |

### Foreword

Much has happened in the TMS320 Family since Volume 1 of *Digital Signal Processing Applications with the TMS320 Family* was published, and Volumes 2 and 3 are a timely update to the family history.

The DSP microcomputers keep changing the perspective of the systems designers by offering more computational power and better interfacing capabilities. The steps of change are coming more quickly, and the potential impact is greater and greater. Because things change so rapidly in this area, there is a pressing need for ways to quickly learn how to utilize the new technology. These new volumes respond to that need.

As with Volume 1, the purpose of these books is to teach us about the issues and techniques that are important in implementing digital signal processing systems using microprocessors in the TMS320 Family. Volume 2 highlights the TMS320C25; and Volume 3, the TMS320C30 chip. A large part of the books is devoted to such matters as characteristics of the TMS320C25 and TMS320C30 chips, useful program code for implementing special DSP functions, and details on interfacing the new chips to external devices. The remainder of the books illustrates how these chips can be used in communications, control, and computer graphics applications.

What these two volumes make clear is how remarkably fast the field of DSP microcomputing is evolving. IC technologists and designers are simply packing more and more of the right kind of computing power into affordable microprocessor chips. The high-speed floating-point computing power and huge address spaces of chips like the TMS320C30 open the door to a whole new class of applications that were difficult or impractical with earlier generations of fixed-point DSP chips. The signal processing theorists and system designers are clearly being challenged to match the creativity of the chip designers.

The present books differ from Volume 1 in the inclusion of a small section on tools. This is a hopeful sign, because it is progress in this area that is likely to have the greatest impact on speeding the widespread application of DSP microprocessors. While useful design tools are beginning to emerge, much more can be done to help system designers manage the complexity of sophisticated DSP systems, which often involve a unique combination of theory, numerical and symbolic processing algorithms, real-time programming, and multiprocessing. No doubt future volumes of *Digital Signal Processing Applications with the TMS320 Family* will have more to say about this important topic. Until then, Volumes 2 and 3 have much useful information to help system designers keep up with the TMS320 Family.

Ronald W. Schafer Atlanta, Georgia November 14, 1989

## **Preface**

With the advancement of DSP devices, the application of Digital Signal Processing has become more widespread. Areas that were considered outside the domain of DSP devices because of cost, processing power, or peripheral capabilities (such as graphics, control, and consumer products) have seen applications using digital signal processors. On the other hand, the diverse needs of the designer have been addressed in the architectures and the performance of the newer devices.

Volume 2 of Digital Signal Processing Applications with the TMS320 Family contains applications on the first and second generations of the TMS320 Family (fixed-point devices). It is a continuation of Volume 1 in the sense that it addresses the same needs of the designer. The designer still has the task of selecting the DSP device with the appropriate cost, performance, and support, developing the DSP algorithm that will solve his problem, and implementing the algorithm on the processor. This volume tries to help the designer by bringing him up to date in the applications of newer processors or in different applications of earlier processors.

The objectives remain the same as in Volume 1. First, the application reports can be used as examples of device use. They can also serve as tutorials in programming the devices. Of course, the same purpose is served on a more elementary basis by the software and hardware applications sections of the corresponding user's guides. Second, since the source code of each application is provided with the report, the designer can take it intact (or extract a portion of it) and place it in his application.

It is assumed that the reader has exposure to the TMS320 devices or, at least, has the necessary manuals (such as the appropriate TMS320 user's guides) that will help him understand the explanations in the reports. The reports themselves include as references the necessary background material. Additionally, the Introduction gives a brief overview of the available devices at the time of the writing, and points to sources of more information.

The reports are grouped by application area. The term *report* is used here in a broad sense, since some articles from technical publications are also included. The authors of the reports are either the digital signal processing engineering staff of the Texas Instruments Semiconductor Group (including both field and factory personnel, and summer students) or third parties.

The source code associated with the reports is also available in electronic form, and the reader can download it from the TI DSP Electronic Bulletin Board (telephone (713) 274–2323). If more information is needed, the DSP Hotline can be called at (713) 274–2320.

The editor wishes to thank all the authors and the reviewers for their contribution to this volume of application reports.

Panos E. Papamichalis, Ph.D. Senior Member of Technical Staff

# Part I. Introduction

- 1. The TMS320 Family and Book Overview

- 2. The TMS320 Family of Digital Signal Processors (Kun-Shan Lin, Gene A. Frantz, and Ray Simar, Jr., reprinted from *PROCEEDINGS OF THE IEEE*, Vol. 75, No. 9, September 1987)

- 3. The Texas Instruments TMS320C25 Digital Signal Microcomputer (Gene A. Frantz, Kun-Shan Lin, Jay B. Reimer, and Jon Bradley, reprinted from *IEEE Micro Magazine*, Vol. 6, No. 6, December 1986)

# TMS320 Family and Book Overview

Digital signal processors have found applications in areas where they were not even considered a few years earlier. The two major reasons for such proliferation are an increase in processor performance and a reduction in cost. Volume 2 of Digital Signal Processing Applications with the TMS320 Family presents a set of application reports on the first- and second-generation TMS320 devices.

# Organization of the Book

The application reports in this book are grouped by subject area:

- Introduction

- DSP Interface Techniques

- Data Communications

- Telecommunications

- Control

- Tools

- Bibliography

The **Introduction** contains this overview and two review articles. The first article gives a general description of the TMS320 family and is reprinted from a special issue of the *IEEE Proceedings*, while the second article discusses the TMS320C25 device and is reprinted from the *IEEE MicroMagazine*. The overview points out how the TMS320 family has grown since the two articles were published and also introduces newer devices.

The section on **DSP Interface Techniques** contains articles on interfacing first- and second-generation devices with external hardware, such as memories, A/D and D/A converters, or microcontroller devices like the TMS370 series. Other articles cover the implementation of a UART on the TMS320C25 and the power dissipation of the TMS320C25.

The three articles in the **Data Communications** section deal with different aspects of modem implementations. A V.22 design is presented in the first article, a 300-bps FSK modem in the second, and an Automatic Gain Control (AGC) in the third. In all cases, first-generation devices are considered.

The following three sections contain one article each. In the **Telecommunications** section, a generalized tone decoding and DTMF detection method is presented. The **Control** section article gives insight into the relatively new application of digital signal processors in digital control. In the **Tools** section, the article describes ways to debug the algorithms with the aid of spreadsheets and other packages.

The **Bibliography** section contains a list of articles mentioning DSP implementations using TMS320 devices. The different titles are listed chronologically and are grouped by subject. The list is not exhaustive, but it gives enough pointers for pursuing practical implementations in representative application areas.

# The TMS320 Family of Processors

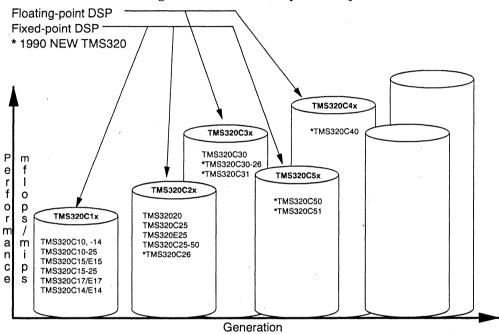

The TMS320 Family of digital signal processors started with the TMS32010 in 1982, but it has been expanded to encompass five generations (at the time of this writing) with devices in each generation. Figure 1 shows this progression through the generations. The TMS320 devices can be grouped in two broad categories: fixed-point and floating-point devices. As implied by Figure 1, the first, second, and fifth generations are the fixed-point devices, while the third and the fourth generations (the last one under development) support floating-point arithmetic.

Figure 1. TMS320 Family Roadmap

The following article, "The TMS320 Family of Digital Signal Processors," by Lin, et. al., is reprinted from the proceedings of the IEEE and gives an overview of the TMS320 family. Since additional devices have been developed from the time the article was written, this section highlights these newer devices. Table 1 shows a comprehensive list of the currently available TMS320 devices and their salient characteristics.

Table 1. TMS320 Family Overview

|       |                                                                                                                |                                                                                                 |                                                                    |                                                                           | Me                                     | mory                 |                                                    |                                                                              | I/O              |                  |                       |                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------|----------------------|----------------------------------------------------|------------------------------------------------------------------------------|------------------|------------------|-----------------------|----------------------------------------------------------------------------------------------------------------|

| . Gen | Device                                                                                                         | Data<br>Type                                                                                    | Cycle<br>Time<br>(ns)                                              | RAM                                                                       | On-<br>Chip<br>ROM                     | EPROM                | Off-<br>Chip                                       | Parallel                                                                     | Serial           | DMA              | On-<br>Chip<br>Timers | Package                                                                                                        |

| 1st   | TMS320C10 ¶ TMS320C10-25 TMS320C10-14 TMS320E14 TMS320C15 ¶ TMS320C15-25 ¶ TMS320E15-25 TMS320E15-25 TMS320E17 | Integer | 200<br>160<br>280<br>160<br>200<br>160<br>200<br>160<br>200<br>200 | 144<br>144<br>144<br>256<br>256<br>256<br>256<br>256<br>256<br>256<br>256 | 1.5K<br>1.5K<br>1.5K<br>4K<br>4K<br>4K | 4K<br>4K<br>4K<br>4K | 4K<br>4K<br>4K<br>4K<br>4K<br>4K<br>4K<br>4K<br>4K | 8x16<br>8x16<br>8x16<br>7x16<br>8x16<br>8x16<br>8x16<br>8x16<br>6x16<br>6x16 | 1 2 2 2          |                  | 1 1                   | DIP/PLCC DIP/PLCC DIP/PLCC DIP/PLCC DIP/PLCC DIP/PLCC DIP/PLCC DIP/CERQUAD DIP/CERQUAD DIP/CERQUAD DIP/CERQUAD |

| 2nd   | TMS32020 ¶ TMS320C25 ¶ TMS320C25-50 ¶ TMS320E25 ¶ TMS320C26                                                    | Integer<br>Integer<br>Integer<br>Integer<br>Integer                                             | 200<br>100<br>80<br>100<br>100                                     | 544<br>544<br>544<br>544<br>1.5K                                          | 4K<br>4K<br>256                        | 4K                   | 128K<br>128K<br>128K<br>128K<br>128K<br>128K       | 16×16<br>16×16<br>16×16<br>16×16                                             | 1<br>1<br>1<br>1 | †<br>†<br>†<br>† | 1<br>1<br>1<br>1      | PGA<br>PGA/PLCC<br>PGA/PLCC<br>CERQUAD<br>PLCC                                                                 |

| 3rd   | TMS320C30 ¶                                                                                                    | Float Pt                                                                                        | 60                                                                 | 2K                                                                        | 4K                                     |                      | 16M                                                | 16Mx32                                                                       | 2                | ‡                | 2                     | PGA                                                                                                            |

| 5th   | TMS320C50 ¶                                                                                                    | Integer                                                                                         | 50                                                                 | 8.5K                                                                      | 2K                                     |                      | 128K                                               | 16x16                                                                        | 1                | †                | 1                     | Crcc                                                                                                           |

<sup>†</sup> External DMA

External/Internal DMA

<sup>¶</sup> For information on military versions of these devices, contact your local TI sales office.

The additions to the first generation are the TMS320C14 and the TMS320E14; the latter is identical with the former, except that the latter's on-chip program memory is EPROM. The TMS320C14/E14 devices have features that make them suitable for control applications. Figure 2 shows the components of these devices. The memory and the CPU are identical to those of the TMS320C15/E15, while the peripherals reflect the orientation of the devices toward control.

MEMORY DATA RAM PROGRAM ROM/EPROM 256×16 bits 4K×16 bits **CPU** PERIPHERALS 16-bit 16-bit T-Reg Timer/Counter 1 Barrel Shifter 16×16-bit Timer/Counter 2 32-bit ALU Multiply Watchdog Timer 32-bit ACC 32-bit P-Reg 16 bit I/O 0,1,4-bit Shift SERIAL PORT 2 Auxiliary Registers **Event Manager** 4 level H/W Stack Status Register

Figure 2. TMS320C14/E14 Key Features

Some of the key features of the TMS320C14/E14 are:

- 160-ns instruction cycle time

- Object-code-compatible with the TMS320C15

- Four 16-bit timers

- Two general-purpose timers

- One watchdog timer

- One baud-rate generator

- 16 individual bit-selectable I/O pins

- Serial port/USART with codec-compatible mode

- Event manager with 6-channel PWM D/A

- CMOS technology, 68-pin CERQUAD

The additions to the second generation are the TMS320E25, the TMS320C25-50, and the TMS320C26. The TMS320E25 is identical to the TMS320C25, except that the 4K-word on-chip

program memory is EPROM. Since increased speed is very important for the real-time implementation of certain applications, the TMS320C25-50 was designed as a faster version of the TMS320C25 and has a clock frequency of 50 MHz instead of 40 MHz.

The TMS320C26 is a modification of the TMS320C25 in which the program ROM has been exchanged for RAM. The memory space of the TMS320C26 has 1.5K words of on-chip RAM and 256 words of on-chip ROM, making it ideal for applications requiring larger RAM but minimal external memory.

A new generation of higher-performance fixed-point processors has been introduced in the TMS320 Family: the TMS320C5X devices. This generation shares many features with the first and the second generations, but it also encompasses significant new features. Figure 3 shows the basic components of the first device in the fifth generation, the TMS320C50.

MEMORY PROG/DATA RAM DATA/PROG RAM **BOOT ROM** 8K×16 bits 544×16 bits 2K×16 bits e e u PERIPHERALS 0-16B Preshift 16b T-Reg Memory Mapped 32b Accumulator 16×16 bit 32b Acc Buffer Serial Port Multiply 32b ALU 32b P-Rea Timer 0-16b Rightshift 0,1,4, -6b shift S/W Waitsts 0-7b Postshift Parallel 16×16 Inputs Mem Mapped Regs Logic Unit -8 Auxiliary 16×16 12 Context -2 Status Outputs -20 Prog Cntl Switch Regs

Figure 3. TMS320C50 Key Features

Some of the important features of the TMS320C50 are listed below:

- Source code is upward compatible with the TMS320C1x/C2x devices

- 50/35-ns instruction cycle time

- 8K words of on-chip program/data RAM

- 2K words boot ROM

- 544 words of data/program RAM

- 128K words addressable total memory

- Enhanced general-purpose and DSP-specific instructions

- Static CMOS, 84-pin CERQUAD

- JTAG serial scan path

The software and hardware development tools available for the TMS320 family make the development of applications easy. Such tools include assemblers, linkers, simulators, and C compilers for software and evaluation modules, software development boards, and extended development systems for hardware. These tools are mentioned in the following paper by Lin, et. al. The interested reader can find much more information in additional literature that is published by Texas Instruments and mentioned in the next section. In particular, the TMS320 Family Development Support Reference Guide is an excellent source.

One important addition to the list of tools is the SPOX operating system, developed by Spectron Microsystems. SPOX permits you to write an application in a high-level language (C) and run it on actual DSP hardware. The operating-system of SPOX hides the details of the interface from you and lets you concentrate on your algorithm while running it at supercomputer speeds on the TMS320C30.

#### References

Texas Instruments publishes an extensive bibliography to help designers use the TMS320 devices effectively. Besides user's guides for corresponding generations, there are manuals for the software and the hardware tools. The Development Support Reference Guide is particularly useful because it provides information not only on development tools offered by TI, but also on those produced by third parties. Here is a partial list of the literature available (the literature number is in parentheses):

- TMS320 Family Development Support Reference Guide (SPRU011A)

- TMS320C1x User's Guide (SPRU013A)

- TMS320C2x User's Guide (SPRU014)

- TMS320C3x User's Guide (SPRU031)

- TMS320C1x/TMS320C2x Assembly Language Tools User's Guide (SPRU018)

- TMS320C30 Assembly Language Tools User's Guide (SPRU035)

- TMS320C25 C Compiler Reference Guide (SPRU024)

- TMS320C30 C Compiler Reference Guide (SPRU034)

- Digital Signal Processing Applications with the TMS320 Family, Volume 1 (SPRA012)

- Digital Signal Processing Applications with the TMS320 Family, Volume 3 (SPRA017)

You can request this literature by calling the Customer Response Center at 1–800–232–3200, or the DSP Hotline at 1–713–274–2320.

# Contents of Other Volumes of the Application Book

#### Volume 1

Part I. Digital Signal Processing and the TMS320 Family

- Introduction

- The TMS320 Family

Part II. Fundamental Digital Signal Processing Operations

• Digital Signal Processing Routines

- Implementation of FIR/IIR Filters with the TMS32010/TMS32020

- Implementation of Fast Fourier Transform Algorithms with the TMS32020

- Companding Routines for the TMS32010/TMS32020

- Floating-Point Arithmetic with the TMS32010

- Floating-Point Arithmetic with the TMS32020

- Precision Digital Sine-Wave Generation with the TMS32010

- Matrix Multiplication with the TMS32010 and TMS32020

- DSP Interface Techniques

- Interfacing to Asynchronous Inputs with the TMS32010

- Interfacing External Memory to the TMS32010

- Hardware Interfacing to the TMS32020

- TMS32020 and MC68000 Interface

### Part III. Digital Signal Processing Applications

- · Telecommunications

- Telecommunications Interfacing to the TMS32010

- Digital Voice Echo Canceller with a TMS32020

- Implementation of the Data Encryption Standard Using the TMS32010

- 32K-bit/s ADPCM with the TMS32010

- A Real-Time Speech Subband Coder Using the TMS32010

- Add DTMF Generation and Decoding to DSP-μP Designs

- Computers and Peripherals

- Speech Coding/Recognition

- A single-Processor LPC Vocoder

- The Design of an Adaptive Predictive Coder Using a Single-Chip

- Digital Signal Processor

- Firmware-Programmable C Aids Speech Recognition

- Image/Graphics

- A Graphics Implementation Using the TMS32020 and TMS34061

- Digital Control

- Control System Compensation and Implementation with the TMS32010

#### Volume 3

#### Part I. Introduction

- Book Overview

- The TMS320 Family of DSP

- The TMS320C30 Floating-Point DSP

# Part II. Digital Signal Processing Routines

- Implementation of FFT, DCT, and other Transforms on the TMS320C30

- Doublelength Floating-Point Arithmetic on the TMS320C30

- An 8 x 8 Discrete Cosine Transform Implementation on the TMS320C25 and the TMS320C30

- Implementation of Adaptive Filters with the TMS320C25 and TMS320C30

- A Collection of Functions for the TMS320C30

# Part III. DSP Interface Techniques

- Hardware Interfacing to the TMS320C30

- TMS320C30 IEEE Floating-Point Format Converter

# Part IV. Telecommunications

• Implementation of a CELP Speech Coder for the TMS320C30 Using SPOX

# Part V. Computers

• A Digital Signal Processor Based 3-D Graphics System

# Part VI. Tools

• TMS320C30 Applications Board Functional Description

# The TMS320 Family of Digital Signal Processors

Kun-Shan Lin Gene A. Frantz Ray Simar, Jr.

Digital Signal Processor Products — Semiconductor Group Texas Instruments

> Reprinted from PROCEEDINGS OF THE IEEE Vol. 75, No. 9, September 1987

# The TMS320 Family of Digital Signal Processors

KUN-SHAN LIN, MEMBER, IEEE, GENE A. FRANTZ, SENIOR MEMBER, IEEE, AND RAY SIMAR. IR.

This paper begins with a discussion of the characteristics of digital signal processing, which are the driving force behind the designal processors. The remainder of the paper describes the three generations of the TMS320 family of digital signal processors available from Texas Instruments. The evolution in architectural design of these processors and key features of each generation of processors are discussed. More detailed information is provided for the TMS320C25 and TMS320C30, the newest members in the family. The benefits and cost-performance tradeoffs of these processors become obvious when applied to digital signal processing applications, such as telecommunications, data communications, graphics/image processing, etc.

#### DIGITAL SIGNAL PROCESSING CHARACTERISTICS

Digital signal processing (DSP) encompasses a broad spectrum of applications. Some application examples include digital filtering, speech vocoding, image processing, fast Fourier transforms, and digital audio [1]–[10]. These applications and those considered digital signal processing have several characteristics in common:

- · mathematically intensive algorithms,

- · real-time operation,

- · sampled data implementation,

- · system flexibility.

To illustrate these characteristics in this section, we will use the digital filter as an example. Specifically, we will use the Finite Impulse Response (FIR) filter which in the time domain takes the general form of

$$y(n) = \sum_{i=1}^{N} a(i) * x(n-i)$$

(1)

where y(n) is the output sample at time n, a(i) is the ith coefficient or weighting factor, and x(n-i) is the (n-i)th input sample

With this example in mind, we can discuss the various characteristics of digital signal processing: mathematically intensive algorithms, real-time processing, sampled data implementation, and system flexibility. First, let us look at the concept of mathematically intensive algorithms.

Manuscript received October 6, 1986; revised March 27, 1987. The authors are with the Semiconductor Group, Texas Instruments Inc., Houston, TX 77521-1445, USA.

IEEE Log Number 8716214.

#### Mathematically Intensive Algorithms

From (1), we can see that to generate every y(n), we have to compute N multiplications and additions or sums of products. This computation makes it mathematically intensive, especially when N is large.

At this point it is worthwhile to give the FIR filter some physical significance. An FIR filter is a common technique used to eliminate the erratic nature of stock market prices. When the day-to-day closing prices are plotted, it is sometimes difficult to obtain the desired information, such as the trend of the stock, because of the large variations. A simple way of smoothing the data is to calculate the average closing values of the previous five days. For the new average value each day, the oldest value is dropped and the newest value added. Each daily average value (average (n)) would be the sum of the weighted value of the latest five days, where the weighting factors (a(i)'s) are 1/5. In equation form, the average is determined by

average

$$(n) = \frac{1}{5} * d(n-1) + \frac{1}{5} * d(n-2)$$

$+ \frac{1}{5} * d(n-3) + \frac{1}{5} * d(n-4)$

$+ \frac{1}{5} * d(n-5)$  (2)

where d(n-i) is the daily stock closing price for the (n-i)th day. Equation (2) assumes the same form as (1). This is also the general form of the convolution of two sequences of numbers, a(i) and x(i) [5], [6]. Both FIR filtering and convolution are fundamental to digital signal processing.

#### Real-Time Processing

In addition to being mathematically intensive, DSP algorithms must be performed in real time. Real time can be defined as a process that is accomplished by the DSP without creating a delay noticeable to the user. In the stock market example, as long as the new average value can be computed prior to the next day when it is needed, it is considered to be completed in real time. In digital signal processing applications, processes happen faster than on a daily basis. In the FIR filter example in (1), the sum of products must

©1989-IEEE. Reprinted, with permission, from *PROCEEDINGS OF THE IEEE*; Vol. 75, No. 9, pp. 1143-1159; September 1989.

be computed usually within hundreds of microseconds before the next sample comes into the system. A second example is in a speech recognition system where a notice-able delay between a word being spoken and being recognized would be unacceptable and not considered real-time. Another example is in image processing, where it is considered real-time if the processor finishes the processing within the frame update period. If the pixel information cannot be updated within the frame update period, problems such as flicker, smearing, or missing information will occur.

#### Sampled Data Implementation

The application must be capable of being handled as a sampled data system in order to be processed by digital processors, such as digital signal processors. The stock market is an example of a sampled data system. That is, a specific value (closing value) is assigned to each sample period or day. Other periods may be chosen such as hourly prices or weekly prices. In an FIR filter as shown in (1), the output y(n) is calculated to be the weighted sum of the previous N inputs. In other words, the input signal is sampled at periodic intervals (1 over the sample rate), multiplied by weighting factor a(i), and then added together to give the output result of y(n). Examples of sample rates for some typical sampled data applications [2], [4] are shown in Table 1.

Table 1 Sample Rates versus Applications

| Application        | Nominal<br>Sample Rate |

|--------------------|------------------------|

| Control            | 1 kHz                  |

| Telecommunications | 8 kHz                  |

| Speech processing  | 8-10 kHz               |

| Audio processing   | 40-48 kHz              |

| Video frame rate   | 30 Hz                  |

| Video pixel rate   | 14 MHz                 |

In a typical DSP application, the processor must be able to effectively handle sampled data in large quantity and also perform arithmetic computations in real time.

#### System Flexibility

The design of the digital signal processing system must be flexible enough to allow improvements in the state of the art. We may find out after several weeks of using the average stock price as a means of measuring a particular stock's value that a different method of obtaining the daily information is more suited to our needs, e.g., using different daily weightings, a different number of periods over which to average, or a different procedure for calculating the result. Enough flexibility in the system must be available to allow for these variations. In many of the DSP applications, techniques are still in the developmental phase, and therefore the algorithms tend to change over time. As an example, speech recognition is presently an inexact technique requiring continual algorithmic modification. From this example we can see the need for system flexibility so that the DSP algorithm can be updated. A programmable DSP system can provide this flexibility to the user.

#### HISTORICAL DSP SOLUTIONS

Over the past several decades, digital signal processing machines have taken on several evolutions in order to incorporate these characteristics. Large mainframe computers were initially used to process signals in the digital domain. Typically, because of state-of-the-art limitations, this was done in nonreal time. As the state of the art advanced, array processors were added to the processing task. Because of their flexibility and speed, array processors have become the accepted solution for the research laboratory, and have been extended to end-applications in many instances. However, integrated circuit technology has matured, thus allowing for the design of faster microprocessors and microcomputers. As a result, many digital signal processing applications have migrated from the array processor to microprocessor subsystems (i.e., bit-slice machines) to single-chip integrated circuit solutions. This migration has brought the cost of the DSP solution down to a point that allows pervasive use of the technology. The increased performance of these highly integrated circuits has also expanded DSP applications from traditional telecommunications to graphics/image processing, then to consumer audio processing.

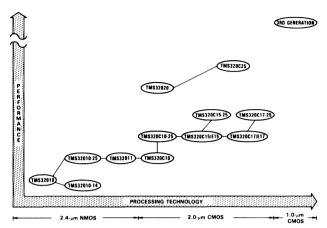

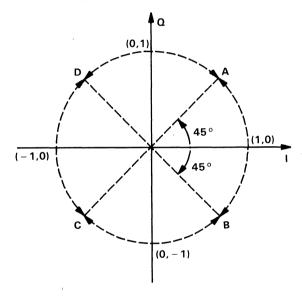

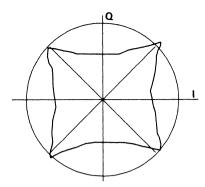

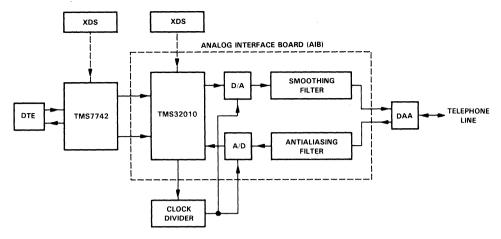

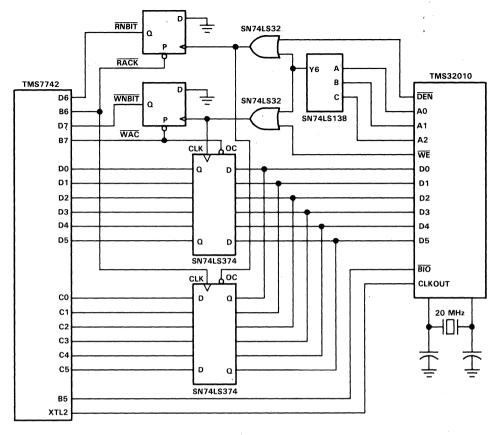

A recent development in DSP technology is the singlechip digital signal processor, such as the TMS320 family of processors. These processors give the designer a DSP solution with its performance attainable only by the array processors a few years ago. Fig. 1 shows the TMS320 family in graphical form with the y-axis indicating the hypothetical performance and the x-axis being the evolution of the semiconductor processing technology. The first member of the family, the TMS32010, was disclosed to the market in 1982 [11], [12]. It gave the system designer the first microcomputer capable of performing five million DSP operations per second (5 MIPS), including the add and multiply functions [13] required in (1). Today there are a dozen spinoffs from the TMS32010 in the first generation of the TMS320 family. Some of these devices are the TMS320C10, TMS320C15, and TMS320C17 [14]. The second generation of devices include the TMS32020 [15] and TMS320C25 [16]. The TMS320C25 can perform 10 MIPS [16]. In addition, expanded memory space, combined single-cycle multiply/ accumulate operation, multiprocessing capabilities, and expanded I/O functions have given the TMS320C25 a 2 to 4 times performance improvement over its predecessors. The third generation of the TMS320 family of processors, the TMS320C30 [26], [27], has a computational rate of 33 million DSP floating-point operations per second (33 MFLOPS). Its performance (speed, throughput, and precision) has far exceeded the digital signal processors available today and has reached the level of a supercomputer.

It we look closely at the TMS320 family as shown in Fig. 1, we can see that devices in the same generation, such as the TMS320C10, TMS320C15, and TMS320C17, are assembly object-code compatible. Devices across generations, such as the TMS320C10 and TMS320C25, are assembly source-code compatible. Software investment on DSP algorithms therefore can be maintained during the system upgrade. Another point is that since the introduction of the TMS32010, semiconductor processing technology has emerged from 3-µm NMOS to 2-µm CMOS to 1-µm CMOS.

Fig. 1. The TMS320 family of digital signal processors.

The TMS320 generations of processors have also taken the same evolution in processing technology. Low power consumption, high performance, and high-density circuit integration are some of the direct benefits of this semiconductor processing evolution.

From Fig. 1, it can be observed that various DSP building blocks, such as the CPU, RAM, ROM, I/O configurations, and processor speeds, have been designed as individual modules and can be rearranged or combined with other standard cells to meet the needs of specific applications. Each of the three generations (and future generations) will evolve in the same manner. As applications become more sophisticated, semicustom solutions based on the core CPU will become the solution of choice. An example of this approach is the TMS320C17/E17, which consists of the TMS320C10 core CPU, expanded 4K-word program ROM (TMS320C17) or EPROM (TMS320E17), enlarged data RAM of 256 words, dual serial ports, companding hardware, and a coprocessor interface. Furthermore, as integrated circuit layout rules move into smaller geometry (now at 2 µm, rapidly going to  $1 \mu m$ ), not only will the TMS320 devices become smaller in size, but also multiple CPUs will be incorporated on the same device along with application-specific I/O to achieve low-cost integrated system solutions.

#### BASIC TMS320 ARCHITECTURE

As noted previously, the underlying assumption regarding a digital signal processor is fast arithmetic operations and high throughput to handle mathematically intensive algorithms in real time. In the TMS320 family [11]–[17], [26], [27], this is accomplished by using the following basic concepts:

- · Harvard architecture,

- · extensive pipelining,

- · dedicated hardware multiplier,

- · special DSP instructions,

- · fast instruction cycle.

These concepts were designed into the TMS320 digital signal processors to handle the vast amount of data characteristic of DSP operations, and to allow most DSP operations to be executed in a single-cycle instruction. Furthermore, the TMS320 processors are programmable devices, providing the flexibility and ease of use of general-purpose microprocessors. The following paragraphs discuss how each of the above concepts is used in the TMS320 family of devices to make them useful in digital signal processing applications.

#### Harvard Architecture

The TMS320 utilizes a modified Harvard architecture for speed and flexibility. In a strict Harvard architecture [18], [19], the program and data memories lie in two separate spaces, permitting a full overlap of instruction fetch and execution. The TMS320 family's modification of the Harvard architecture further allows transfer between program and data spaces, thereby increasing the flexibility of the device. This architectural modification eliminates the need for a separate coefficient ROM and also maximizes the processing power by maintaining two separate bus structures (program and data) for full-speed execution.

#### **Extensive Pipelining**

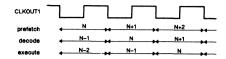

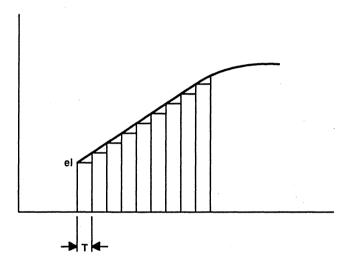

In conjunction with the Harvard architecture, pipelining is used extensively to reduce the instruction cycle time to its absolute minimum, and to increase the throughput of the processor. The pipeline can be anywhere from two to four levels deep, depending on which processor in the family is used. The TMS320 family architecture uses a two-level pipeline for its first generation, a three-level pipeline for its second generation, and a four-level pipeline for its third generation of processors. This means that the device is processing from two to four instructions in parallel, and each instruction is at a different stage in its execution. Fig. 2 shows an example of a three-level pipeline operation.

Fig. 2. Three-level pipeline operation.

In pipeline operation, the prefetch, decode, and execute operations can be handled independently, thus allowing the execution of instructions to overlap. During any instruction cycle, three different instructions are active, each at a different stage of completion. For example, as the Nth instruction is being prefetched, the previous (N-1)th instruction is being decoded, and the previous (N-2)th instruction is being executed. In general, the pipeline is transparent to the user.

#### Dedicated Hardware Multiplier

As we saw in the general form of an FIR filter, multiplication is an important part of digital signal processing. For each filter tap (denoted by i), a multiplication and an addition must take place. The faster a multiplication can be performed, the higher the performance of the digital signal processor. In general-purpose microprocessors, the multiplication instruction is constructed by a series of additions, therefore taking many instruction cycles. In comparison, the characteristic of every DSP device is a dedicated multiplier. In the TMS320 family, multiplication is a single-cycle instruction as a result of the dedicated hardware multiplier. If we look at the arithmetic for each tap of the Filter to be performed by the TMS32010, we see that each tap of the filter requires a multiplication (MPY) instruction.

LT ;LOAD MULTIPLICAND INTO T REGISTER DMOV ;MOVE DATA IN MEMORY TO DO DELAY MPY ;MULTIPLY APAC ;ADD MULTIPLICATION RESULT TO ACC

The other three instructions are used to load the multiplier circuit with the multiplicand (LT), move the data through the filter tap (DMOV), and add the result of the multiplication (stored in the product register) to the accumulator (APAC). Specifically, the multiply instruction (MPY) loads the multiplier into the dedicated multiplier and performs the multiplication, placing the result in a product register. Therefore, if a 256-tap FIR filter is used, these four instructions are repeated 256 times. At each sample period, 256 multiplications must be performed. In a typical general-purpose microprocessor, this requires each tap to be 30 to 40 instruction cycles long, whereas in the TMS320C10, it is only four instruction cycles. We will see in the next section how special DSP instructions reduce the time required for each FIR tap even further.

#### Special DSP Instructions

Another characteristic of DSP devices is the use of special instructions. We were introduced to one of them in the previous example, the DMOV (data move) instruction. In digital signal processing, the delay operator ( $z^{-1}$ ) is very important. Recalling the stock market example, during each new sample period (i.e., each new day), the oldest piece of data

(the closing price five days ago) was dropped and a new one (today's closing price) was added. Or, each piece of the old data is delayed or moved one sample period to make room for the incoming most current sample. This delay is the function of the DMOV instruction. Another special instruction in the TMS32010 is the LTD instruction. It executes the LT, DMOV, and APAC instructions in a single cycle. The LTD and MPY instruction then reduce the number of instruction cycles per FIR filter tap from four to two. In the second-generation TMS320, such as the TMS320C25, two more special instructions have been included (the RPT and MACD instructions) to reduce the number of cycles per tap to one, as shown in the following:

RPTK 255 ;REPEAT THE NEXT INSTRUCTION 256 TIMES (N + 1)

MACD :LT, DMOV, MPY, AND APAC

#### Fast Instruction Cycle

The real-time processing capability is further enhanced by the raw speed of the processor in executing instructions. The characteristics which we have discussed, combined with optimization of the integrated circuit design for speed, give the DSP devices instruction cycle times less than 200 ns. The specific instruction cycle times for the TMS320 family are given in Table 2. These fast cycle times have made

Table 2 TMS320 Cycle Times

| Device     | Cycle Time<br>(ns) |

|------------|--------------------|

| TMS320C10* | 160-200            |

| TMS32020   | 160-200            |

| TMS320C25  | 100-125            |

| TMS320C30  | 60-75              |

<sup>\*</sup>The same cycle time applies to all of the first-generation processors.

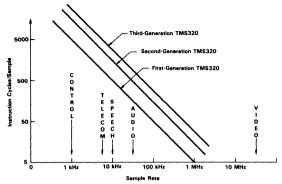

the TMS320 family of processors highly suited for many realtime DSP applications. Table 1 showed the sample rates for some typical DSP applications. This table can be combined with the cycle times indicated in Table 2 to show how many instruction cycles per sample can be achieved by the various generations of the TMS320 for real-time applications (see Fig. 3).

As we can see from Fig. 3, many instruction cycles are available to process the signal or to generate commands for real-time control applications. Therefore, for simple control applications, the general-purpose microprocessors or controllers would be adequate. However, for more mathematically intensive control applications, such as robotics and adaptive control, digital signal processors are much better suited [24]. The number of available instruction cycles is reduced as we increase the sample rate from 8 kHz for typical telecommunication applications to 40-48 kHz for audio processing. Since most of these real-time applications require only a few hundreds of instructions per sample (such as ADPCM [4], and echo cancelation [4]), this is within the reach of the TMS320. For higher sample rate applications, such as video/image processing, digital signal processors available today are not capable of handling the processing of the real-time video data. Therefore, for these

Fig. 3. Number of instruction cycles/sample versus sample rate for the TMS320 family.

types of applications, multiple digital signal processors and frame buffers are usually required. From Fig. 3, it can also be seen that for slower speed applications, such as control, the first-generation TMS320 provides better cost-performance tradeoffs than the other processors. For high sample rate applications, such as video/image processing, the second and third generations of the TMS320 with their multiprocessing capabilities and high throughput are better suited.

Now that we have discussed the basic characteristics of digital signal processors, we can concentrate on specific details of each of the three generations of the TMS320 family devices.

#### THE FIRST GENERATION OF THE TMS320 FAMILY

The first generation of the TMS320 family includes the TMS32010 [13], and TMS32011 [17], which are processed in 2.4-µm NMOS technology, and the TMS320C10 [13], TMS320C15/E15 [14], and TMS320C17/E17 [14], processed in 1.8-µm CMOS technology. Some of the key features of these devices are [14] as follows:

- · Instruction cycle timing:

- -160 ns

- -200 ns

- -280 ns.

- · On-chip data RAM:

- -144 words

- -256 words (TMS320C15/E15, TMS320C17/E17).

- · On-chip program ROM:

- 1.5K words

- -4K words (TMS320C15, TMS320C17).

- 4K words of on-chip program EPROM (TMS320E15, TMS320E17).

- External memory expansion up to 4K words at full speed.

- \* 16  $\times$  16-bit parallel multiplier with 32-bit result.

- Barrel shifter for shifting data memory words into the ALU.

- · Parallel shifter.

- · 4 × 12-bit stack that allows context switching.

- · Two auxiliary registers for indirect addressing.

- Dual-channel serial port (TMS32011, TMS320C17, TMS320E17).

- On-chip companding hardware (TMS32011, TMS320C17, TMS320E17).

- · Coprocessor interface (TMS320C17, TMS320E17).

- Device packaging

- -40-pin DIP

- -44-pin PLCC.

#### TMS320C10

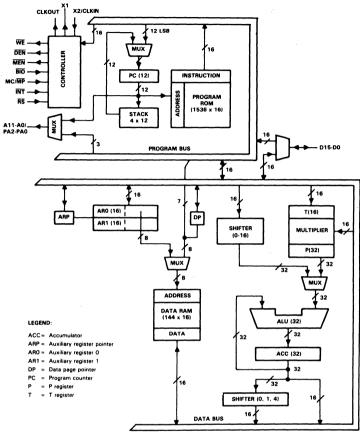

The first generation of the TMS320 processors is based on the architecture of the TMS32010 and its CMOS replica, the TMS320C10. The TMS32010 was introduced in 1982 and was the first microcomputer capable of performing 5 MIPS. Since the TMS32010 has been covered extensively in the literature [4], [11]–[14], we will only provide a cursory review here. A functional block diagram of the TMS320C10 is shown in Fig. 4.

As shown in Fig. 4, the TMS320C10 utilizes the modified Harvard architecture in which program memory and data memory lie in two separate spaces. Program memory can reside both on-chip (1.5K words) or off-chip (4K words). Data memory is the 144  $\times$  16-bit on-chip data RAM. There are four basic arithmetic elements: the ALU, the accumulator, the multiplier, and the shifters. All arithmetic operations are performed using two's-complement arithmetic.

ALU: The ALU is a general-purpose arithmetic logic unit that operates with a 32-bit data word. The unit can add, subtract, and perform logical operations.

Accumulator: The accumulator stores the output from the ALU and is also often an input to the ALU. It operates with a 32-bit word length. The accumulator is divided into a high-order word (bits 31 through 16) and a low-order word (bits 15 through 0). Instructions are provided for storing the high-and low-order accumulator words in data memory (SACH for store accumulator high and SACL for store accumulator low).

Multiplier: The 16  $\times$  16-bit parallel multiplier consists of three units: the T register, the P register, and the multipler array. The T register is a 16-bit register that stores the multiplicand, while the P register is a 32-bit register that stores the product. In order to use the multiplier, the multiplicand

Fig. 4. TMS320C10 functional block diagram.

must first be loaded into the T register from the data RAM by using one of the following instructions: LT, LTA, or LTD. Then the MPY (multiply) or the MPYK (multiply immediate) instruction is executed. The multiply and accumulate operations can be accomplished in two instruction cycles with the LTA/LTD and MPY/MPYK instructions.

Shifters: Two shifters are available for manipulating data: a barrel shifter and a parallel shifter. The barrel shifter performs a left-shift of 0 to 16 bits on all data memory words that are to be loaded into, subtracted from, or added to the accumulator. The parallel shifter, activated by the SACH instruction, can execute a shift of 0, 1, or 4 bits to take care of the sign bits in two's-complement arithmetic calculations.

Based on the architecture of the TMS32010/C10, several spinoffs have been generated offering different processor speeds, expanded memory, and various I/O integration. Currently, the newest members in this generation are the TMS320C15/E15 and the TMS320C17/E17 [14].

#### TMS320C15/E15

The TMS320C15 and TMS320E15 are fully object-code and pin-for-pin compatible with the TMS32010 and offer expanded on-chip RAM of 256 words and on-chip program ROM (TMS320C15) or EPROM (TMS320E15) of 4K words. The TMS320C15 is available in either a 200-ns version or a 160-ns version (TMS320C15-25).

#### TMS320C17/E17

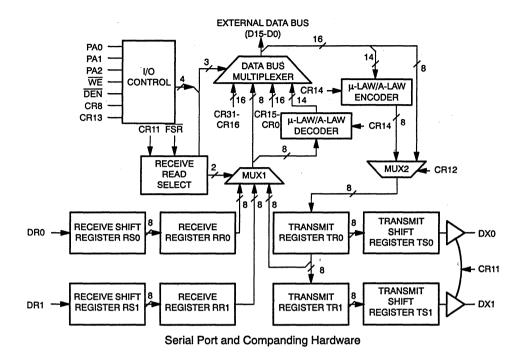

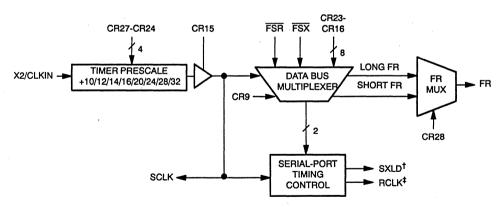

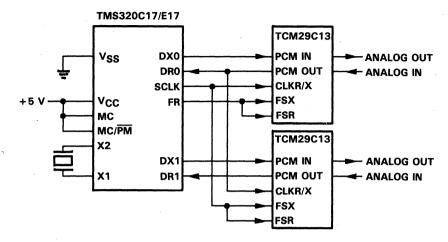

The TMS320C17/E17 is a dedicated microcomputer with 4K words of on-chip program ROM (TMS320C17) or EPROM (TMS320E17), a dual-channel serial port for full-duplex serial communication, on-chip companding hardware (u-law/ A-law), a serial port timer for stand-alone serial communication, and a coprocessor interface for zero glue interface between the processor and any 4/8/16-bit microprocessor. The TMS320C17/E17 is also object-code compatible with the TMS32010 and can use the same development tools. The

Table 3 TMS320 First-Generation Processors

| TMS320<br>Devices | Instruction<br>Cycle Time<br>(ns) | Process | On-Chip<br>Prog ROM<br>(words) | On-Chip<br>Prog EPROM<br>(words) | On-Chip<br>Data RAM<br>(words) | Off-Chip<br>Prog<br>(words) | Ref  |

|-------------------|-----------------------------------|---------|--------------------------------|----------------------------------|--------------------------------|-----------------------------|------|

| TMS32010          | 200                               | NMOS    | 1.5K                           |                                  | 144                            | 4K                          | [13] |

| TMS32010-25       | 160                               | NMOS    | 1.5K                           |                                  | 144                            | 4K                          | [13] |

| TMS32010-14       | 280                               | NMOS    | 1.5K                           |                                  | 144                            | 4K                          | [13] |

| TMS32011          | 200                               | NMOS    | 1.5K                           |                                  | 144                            |                             | [17] |

| TMS320C10         | 200                               | CMOS    | 1.5K                           |                                  | 144                            | 4K                          | [13] |

| TMS320C10-25      | 160                               | CMOS    | 1.5K                           |                                  | 144                            | 4K                          | [13] |

| TMS320C15         | 200                               | CMOS    | 4.0K                           |                                  | 256                            | 4K                          | [13] |

| TMS320C15-25      | 160                               | CMOS    | 4.0K                           |                                  | 256                            | 4K                          | [14] |

| TMS320E15         | 200                               | CMOS    |                                | 4.0K                             | 256                            | 4K                          | [14] |

| TMS320C17         | 200                               | CMOS    | 4.0K                           |                                  | 256                            |                             | [14] |

| TMS320C17-25      | 160                               | CMOS    | 4.0K                           |                                  | 256                            |                             | [14] |

| TMS320E17         | 200                               | CMOS    |                                | 4.0K                             | 256                            |                             | [14] |

device is based on the TMS320C10 core CPU with added peripheral memory and I/O modules added on-chip. The TMS320C17/E17 can be regarded as a semicustom DSP solution suited for high-volume telecommunication and consumer applications.

Table 3 provides a feature comparison of all members of the first-generation TMS320 processors. References to more detailed information on these processors are also provided.

#### THE SECOND GENERATION OF THE TMS320 FAMILY

The second-generation TMS320 digital signal processors includes two members, the TMS320020 [15] and the TMS320C25 [16]. The architecture of these devices has been evolved from the TMS32010, the first member of the TMS320 family. Key features of the second-generation TMS320 are as follows:

- Instruction cycle timing: -100 ns (TMS320C25)

- -100 HS (TM15320C25)

- -200 ns (TMS32020).

- 4K words of on-chip masked ROM (TMS320C25).

- · 544 words of on-chip data RAM.

- 128K words of total program data memory space.

- Eight auxiliary registers with a dedicated arithmetic unit.

- · Eight-level hardware stack.

- · Fully static double-buffered serial port.

- Wait states for communication to slower off-chip memories.

- · Serial port for multiprocessing or interfacing to codecs.

- Concurrent DMA using an extended hold operation (TMS320C25).

- Bit-reversed addressing modes for fast Fourier transforms (TMS320C25).

- Extended-precision arithmetic and adaptive filtering support (TMS320C25).

- Full-speed operation of MAC/MACD instructions from external memory (TMS320C25).

- Accumulator carry bit and related instructions

The consecutions

- (TMS320C25).

1.8-μm CMOS technology (TMS320C25):

-68-pin grid array (PGA) package.

- -68-pin lead chip carrier (PLCC) package.

- 2.4 μm NMOS technology (TMS32020): -68-pin PGA package.

#### TMS320C25 Architecture

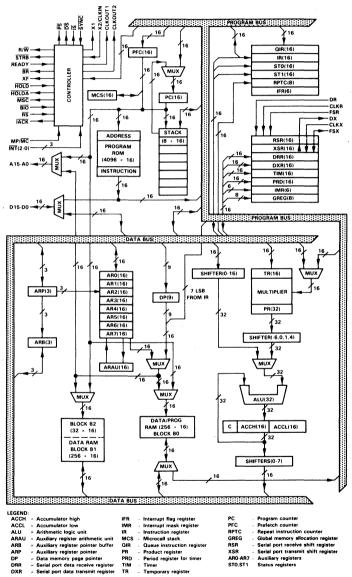

The TMS320C25 is the latest member in the second generation of TMS320 digital signal processors. It is a pin-compatible CMOS version of the TMS32020 microprocessor, but with an instruction cycle time twice as fast and the inclusion of additional hardware and software features. The instruction set is a superset of both the TMS32010 and TMS32020, maintaining source-code compatibility. In addition, it is completely object-code compatible with the TMS32020 so that TMS32020 programs run unmodified on the TMS320C25.

The 100-ns instruction cycle time provides a significant throughput advantage for many existing applications. Since most instructions are capable of executing in a single cycle, the processor is capable of executing ten million instructions per second (10 MIPS). Increased throughput on the TMS320C25 for many DSP applications is attained by means of single-cycle multiply/accumulate instructions with a data move option (MAC/MACD), eight auxiliary registers with a dedicated arithmetic unit, instruction set support for adaptive filtering and extended-precision arithmetic, bit-reversal addressing, and faster I/O necessary for data-intensive signal processing.

Instructions are included to provide data transfers between the two memory spaces. Externally, the program and data memory spaces are multiplexed over the same bus so as to maximize the address range for both spaces while minimizing the pin count of the device. Internally, the TMS320C25 architecture maximizes processing power by maintaining two separate bus structures, program and data, for full-speed execution.

Program execution in the device takes the form of a three-level instruction fetch-decode-execute pipeline (see Fig. 2). The pipeline is essentially invisible to the user, except in some cases where it must be broken (such as for branch instructions). In this case, the instruction timing takes into account the fact that the pipeline must be emptied and refilled. Two large on-chip data RAM blocks (a total of 544 words), one of which is configurable either as program of data memory, provide increased flexibility in system design. An off-chip 64K-word directly addressable data memory address space is included to facilitate implementations of DSP algorithms. The large on-chip 4K-word masked ROM can be used for cost-reduced systems, thus providing for a true single-chip DSP solution. The remainder of the 64K-word program memory space is located externally. Large

programs can execute at full speed from this memory space. Programs may also be downloaded from slow external memory to on-chip RAM for full-speed operation. The VLSI implementation of the TMS320C25 incorporates all of these

features as well as many others such as a hardware timer, serial port, and block data transfer capabilities.

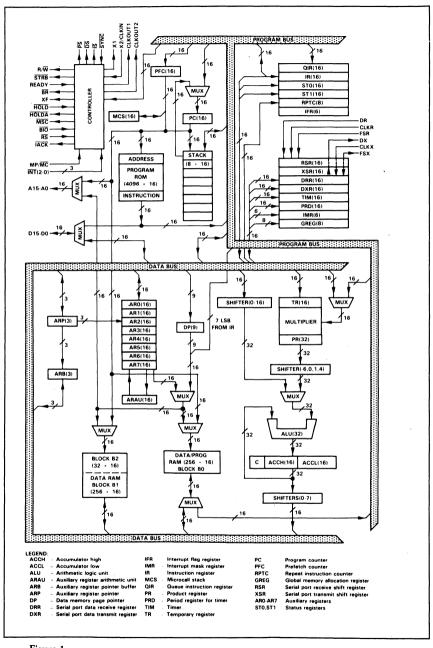

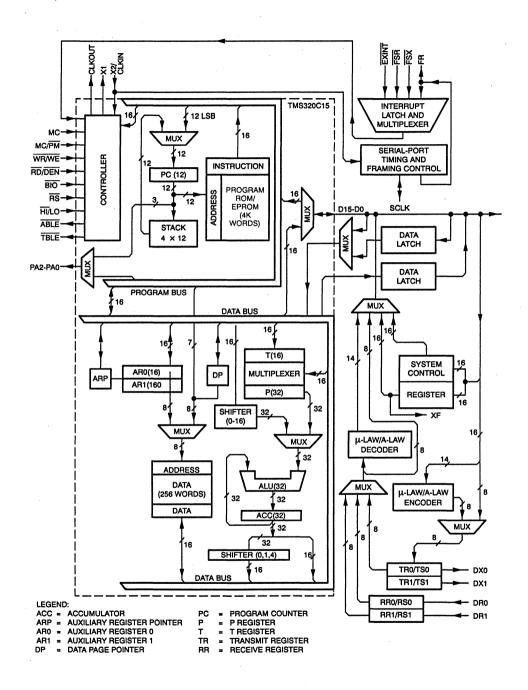

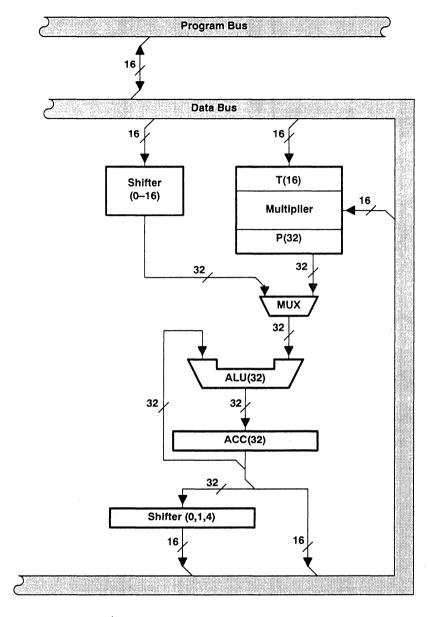

A functional block diagram of the TMS320C25, shown in Fig. 5, outlines the principal blocks and data paths within

Fig. 5. TMS320C25 functional block diagram.

the processor. The diagram also shows all of the TMS320C25 interface pins.

In the following architectural discussions on the memory, central arithmetic logic unit, hardware multiplier, control operations, serial port, and I/O interface, please refer to the block diagram shown in Fig. 5.

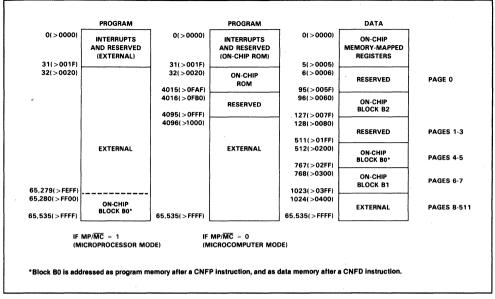

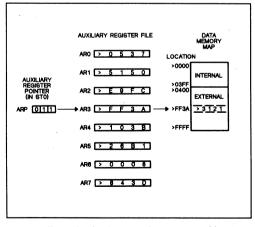

Memory Allocation: The TMS32\(\tilde{O}\)C25 provides a total of 4K 16-bit words of on-chip program ROM and 544 16-bit words of on-chip program ROM and 544 16-bit words of on-chip data RAM. The RAM is divided into three separate Blocks (B0, B1, and B2). Of the 544 words, 256 words (block B0) are configurable as either data or program memory by CNFD (configure data memory) or CNFP (configure program memory) instructions provided for that purpose; 288 words (blocks B1 and B2) are always data memory. A data memory size of 544 words allows the TMS320C25 to handle a data array of 512 words while still leaving 32 locations for intermediate storage. The TMS320C25 provides 64K words of off-chip directly addressable data memory space as well as a 64K-word off-chip program memory space.

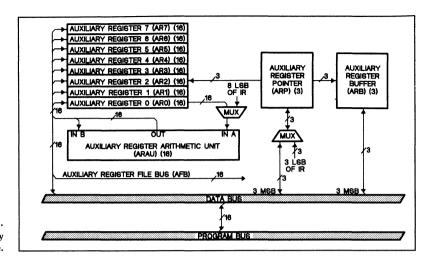

A register file containing eight Auxiliary Registers (ARO-AR7), which are used for indirect addressing of data memory and for temporary storage, increase the flexibility and efficiency of the device. These registers may be either directly addressed by an instruction or indirectly addressed by a 3-bit Auxiliary Register Pointer (ARP). The auxiliary registers and the ARP may be loaded from either data memory or by an immediate operand defined in the instruction. The contents of these registers may also be stored into data memory. The auxiliary register file is connected to the Auxiliary Register Arithmetic Unit (ARAU). Using the ARAU accessing tables of information does not require the CALU for address manipulation, thus freeing it for other operations.

Central Arithmetic Logic Unit (CALU): The CALU contains a 16-bit scaling shifter, a 16  $\times$  16-bit parallel multiplier, a 32-bit Arithmetic Logic Unit (ALU), and a 32-bit accumulator. The scaling shifter has a 16-bit input connected to the data bus and a 32-bit output connected to the ALU. This shifter produces a left-shift of 0 to 16 bits on the input data, as programmed in the instruction. Additional shifters at the outputs of both the accumulator and the multiplier are suitable for numerical scaling, bit extraction, extended-precision arithmetic, and overflow prevention.

The following steps occur in the implementation of a typical ALU instruction:

- 1) Data are fetched from the RAM on the data bus.

- 2) Data are passed through the scaling shifter and the ALU where the arithmetic is performed.

- 3) The result is moved into the accumulator.

The 32-bit accumulator is split into two 16-bit segments for storage in data memory: ACCH (accumulator high) and ACCL (accumulator low). The accumulator has a carry bit to facilitate multiple-precision arithmetic for both addition and subtract instructions.

Hardware Multiplier: The TMS320C25 utilizes a 16  $\times$  16-bit hardware multiplier, which is capable of computing a 32-bit product during every machine cycle. Two registers are associated with the multiplier:

- a 16-bit Temporary Register (TR) that holds one of the operands for the multiplier, and

- a 32-bit Product Register (PR) that holds the product.

The output of the product register can be left-shifted 1 or 4 bits. This is useful for implementing fractional arithmetic or justifying fractional products. The output of the PR can also be right-shifted 6 bits to enable the execution of up to 128 consecutive multiple/accumulates without overflow. An unsigned multiply (MPYU) instruction facilitates extended-precision multiplication.

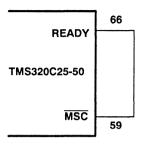

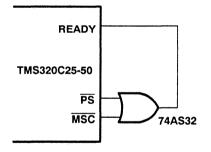

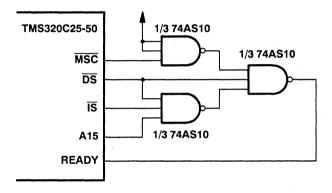

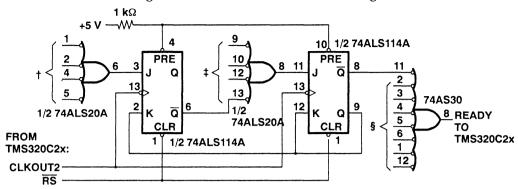

I/O Interface: The TMS320C25 I/O space consists of 16 input and 16 output ports. These ports provide the full 16-bit parallel I/O interface via the data bus on the device. A single input (IN) or output (OUT) operation typically takes two cycles; however, when used with the repeat counter, the operation becomes single-cycle. I/O devices are mapped into the I/O address space using the processor's external address and data buses in the same manner as memory-mapped devices. Interfacing to memory and I/O devices of varying speeds is accomplished by using the READY line.

A Direct Memory Access (DMA) to external program/data memory is also supported. Another processor can take complete control of the TMS320C25's external memory by asserting HOLD low, causing the TMS320C25 to place its address, data, and control lines in the high-impedance state. Signaling between the external processor and the TMS320C25 can be performed using interrupts. Two modes of DMA are available on the device. In the first, execution is suspended during assertion of HOLD. In the second "concurrent DMA" mode, the TMS320C25 continues to execute its program while operating from internal RAM or ROM, thus greatly increasing throughput in data-intensive applications.

#### TMS320C25 Software

The majority of the TMS320C25 instructions (97 out of 133) are executed in a single instruction cycle. Of the 36 instructions that require additional cycles of execution, 21 involve branches, calls, and returns that result in a reload of the program counter and a break in the execution pipeline. Another seven of the instructions are two-word, longimmediate instructions. The remaining eight instructions support I/O, transfers of data between memory spaces, or provide for additional parallel operation in the processor. Furthermore, these eight instructions (IN, OUT, BLKD, BLKP, TBLR, TBLW, MAC, and MACD) become single-cycle when used in conjunction with the repeat counter. The functional performance of the instructions exploits the parallelism of the processor, allowing complex and/or numerically intensive computations to be implemented in relatively few instructions.

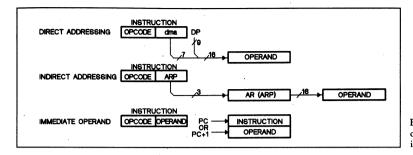

Addressing Modes: Since most of the instructions are coded in a single 16-bit word, most instructions can be executed in a single cycle. Three memory addressing modes are available with the instruction set: direct, indirect, and immediate addressing. Both direct and indirect addressing are used to access data memory. Immediate addressing uses the contents of the memory addressed by the program counter.

When using direct addressing, 7 bits of the instruction word are concatenated with the 9 bits of the data memory page pointer (DP) to form the 16-bit data memory address. With a 128-word page length, the DP register points to one of 512 possible data memory pages to obtain a 64K total data memory space. Indirect addressing is provided by the aux-

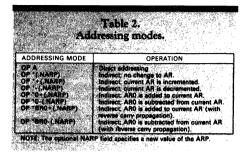

iliary registers (AR0-AR7). The seven types of indirect addressing are shown in Table 4. Bit-reversed indexed addressing modes allow efficient I/O to be performed for the resequencing of data points in a radix-2 FFT program.

Table 4 Addressing Modes of the TMS320C25

| Addressing Mode | Operation                                                                           |

|-----------------|-------------------------------------------------------------------------------------|

| OP A            | direct addressing                                                                   |

| OP * (,NARP)    | indirect; no change to AR.                                                          |

| OP *+(,NARP)    | indirect; current AR is incremented.                                                |

| OP *-(,NARP)    | indirect; current AR is decremented.                                                |

| OP *0+(,NARP)   | indirect; AR0 is added to current AR.                                               |

| OP *0-(,NARP)   | indirect; AR0 is subtracted from<br>current AR.                                     |

| OP *BR0+(,NARP) | indirect; AR0 is added to current AR (with reverse carry propagation).              |

| OP *BR0→(,NARP) | indirect; AR0 is subtracted from<br>current AR (with reverse carry<br>propagation). |

Note: The optional NARP field specifies a new value of the ARP.

#### TMS320C25 System Configurations

The flexibility of the TMS320C25 allows systems configurations to satisfy a wide range of application requirements [16]. The TMS320C25 can be used in the following configurations:

- a stand-alone system (a single processor using 4K words of on-chip ROM and 544 words of on-chip RAM),

- parallel multiprocessing systems with shared global data memory, or

- host/peripheral coprocessing using interface control signals.

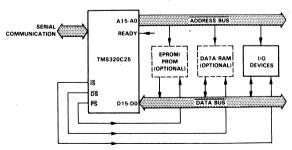

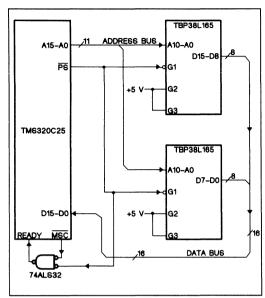

A minimal processing system is shown in Fig. 6 using external data RAM and PROM/EPROM. Parallel multiprocessing and host/peripheral coprocessing systems can be designed by taking advantage of the TMS320C25's direct memory access and global memory configuration capabilities.

In some digital processing tasks, the algorithm being implemented can be divided into sections with a distinct processor dedicated to each section. In this case, the first and second processors may share global data memory, as well as the second and third, the third and fourth, etc. Arbitration logic may be required to determine which section of the algorithm is executing and which processor has access to the global memory. With multiple processors ded-

icated to distinct sections of the algorithm, throughput can be increased via pipelined execution. The TMS320C25 is capable of allocating up to 32K words of data memory as global memory for multiprocessing applications.

#### THE THIRD GENERATION OF THE TMS320 FAMILY

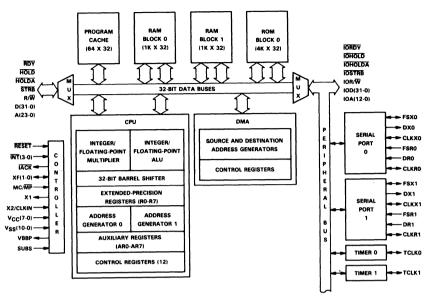

The TMS320C30 [26]-[27] is Texas Instruments third-generation member of the TMS320 family of compatible digital signal processors. With a computational rate of 33 MFLOPS (million floating-point operations per second), the TMS320C30 far exceeds the performance of any programmable DSP available today. Total system performance has been maximized through internal parallelism, more than twenty-four thousand bytes of on-chip memory, single-cycle floating-point operations, and concurrent I/O. The total system cost is minimized with on-chip memory and on-chip peripherals such as timers and serial ports. Finally, the user's system design time is dramatically reduced with the availability of the floating-point operations, general-purpose instructions and features, and quality development tools.

The TMS320C30 provides the user with a level of performance that, at one time, was the exclusive domain of supercomputers. The strong architectural emphasis of providing a low-cost system solution to demanding arithmetic algorithms has resulted in the architecture shown in Fig. 7.

The key features of the TMS320C30 [26], [27] are as follows:

- 60-ns single-cycle execution time, 1-μm CMOS.

- Two 1K × 32-bit single-cycle dual-access RAM blocks.

- One 4K × 32-bit single-cycle dual-access ROM block.

- 64 × 32-bit instruction cache.

- 32-bit instruction and data words, 24-bit addresses.

- 32/40-bit floating-point and integer multiplier.

- 32/40-bit floating-point, integer, and logical ALU.

- · 32-bit barrel shifter.

- · Eight extended-precision registers.

- Two address-generators with eight auxiliary registers.

- On-chip Direct Memory Access (DMA) controller for concurrent I/O and CPU operation.

- · Peripheral bus and modules for easy customization.

- · High-level language support.

- · Interlocked instructions for multiprocessing support.

- · Zero overhead loops and single-cycle branches.

The architecture of the TMS320C30 is targeted at 60-ns and faster cycle times. To achieve such high-performance

Fig. 6. Minimal processing system with external data RAM and PROM/EPROM.

Fig. 7. TMS320C30 functional block diagram.

goals while still providing low-cost system solutions, the TMS320C30 is designed using Texas Instruments state-of-the-art 1-µm CMOS process. The TMS320C30's high system performance is achieved through a high degree of parallelism, the accuracy and precision of its floating-point units, its on-chip DMA controller that supports concurrent I/O, and its general-purpose features. At the heart of the architecture is the Central Processing Unit (CPU).

#### The CPU

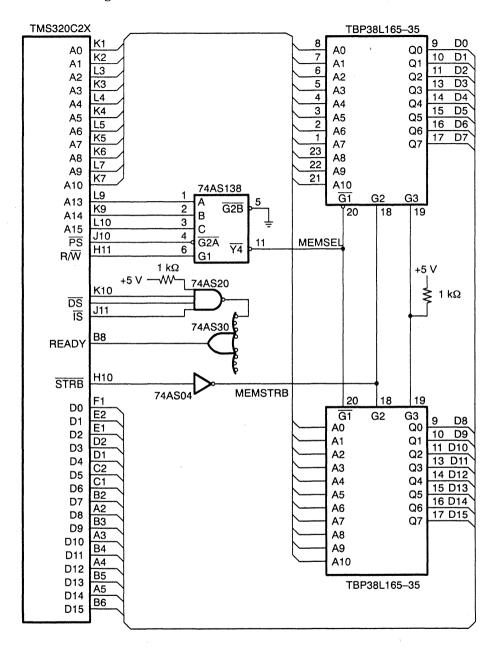

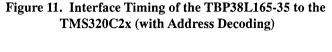

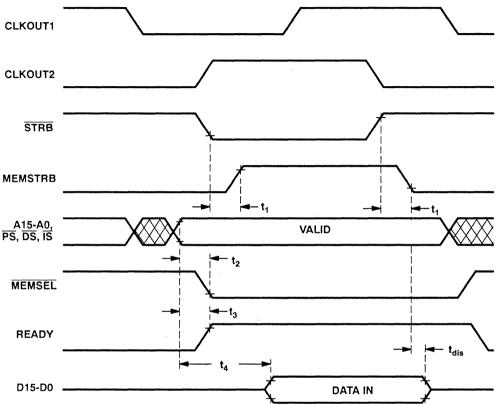

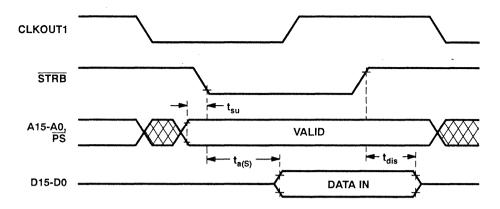

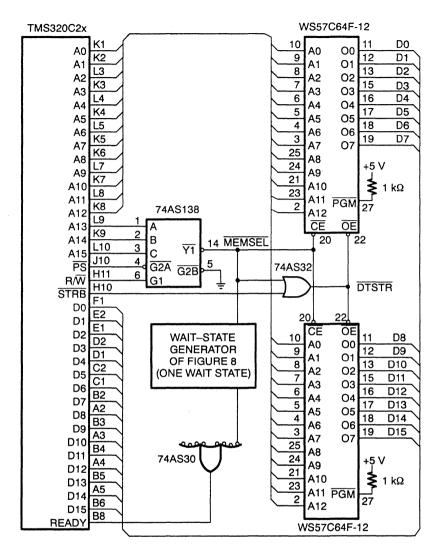

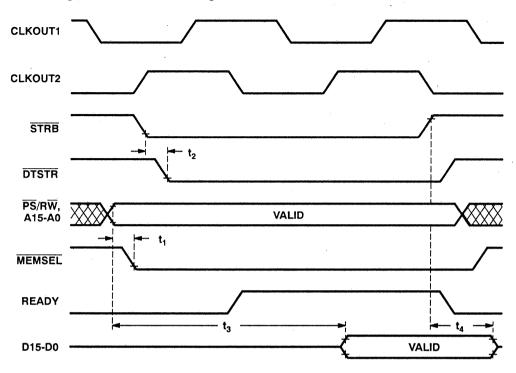

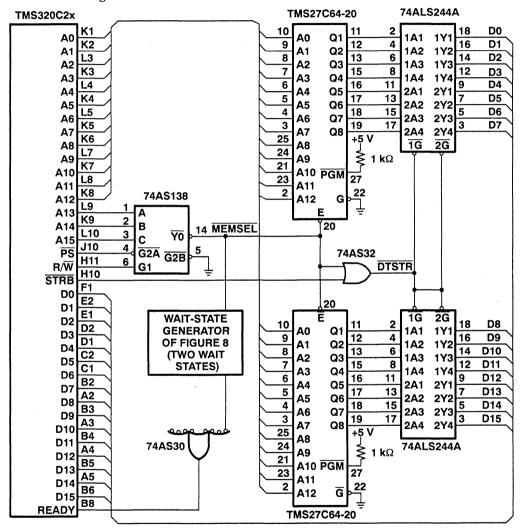

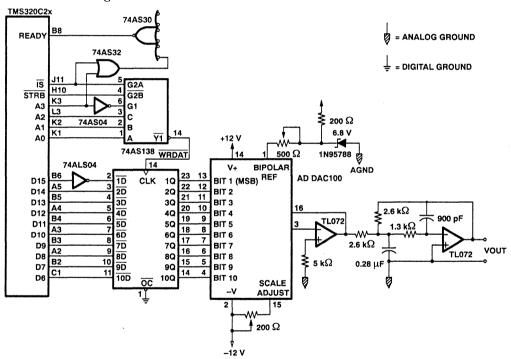

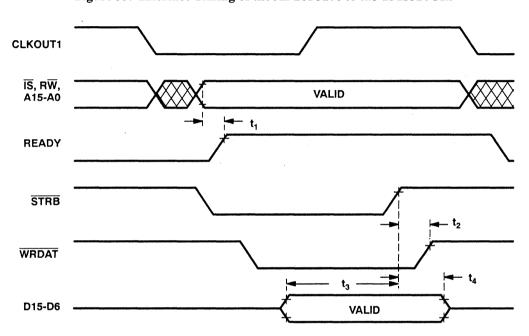

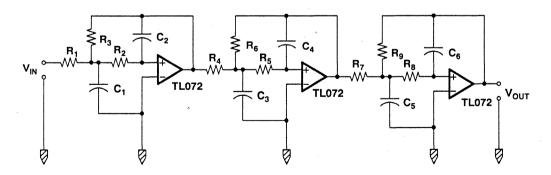

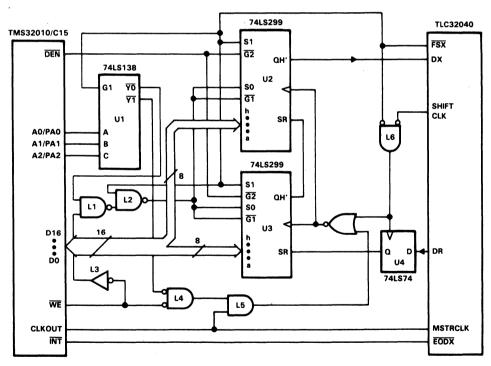

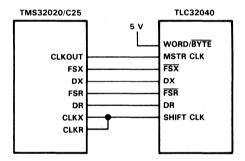

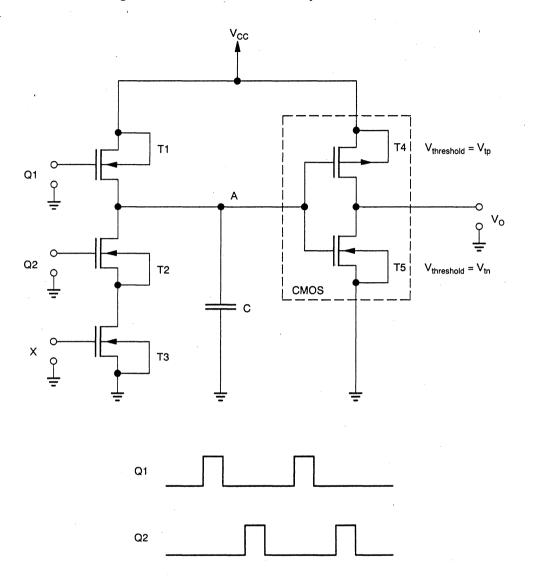

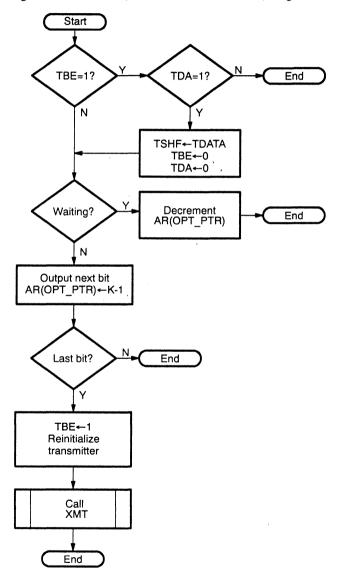

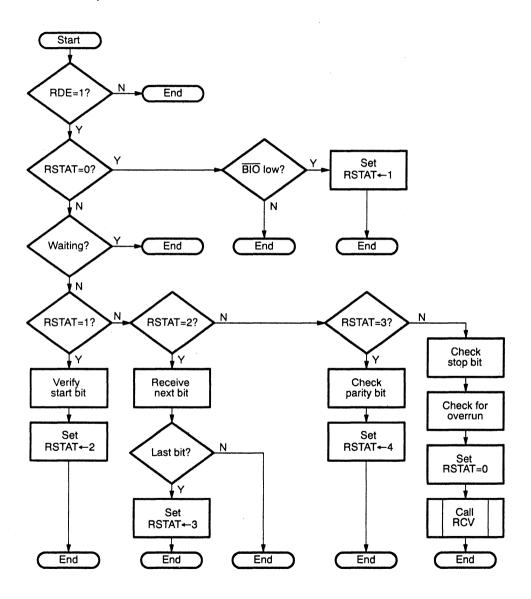

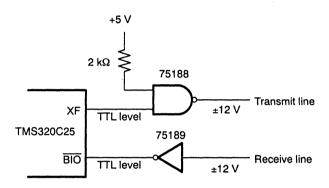

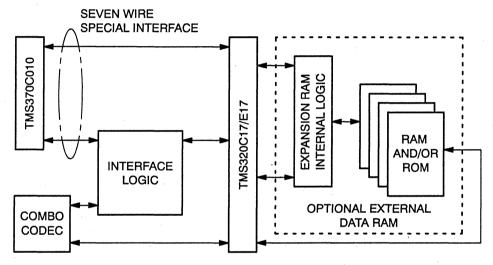

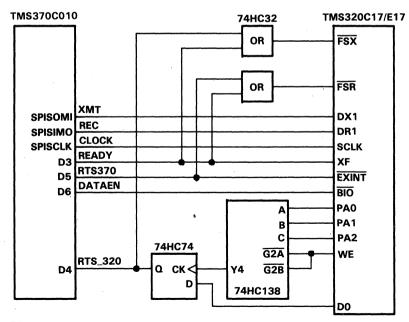

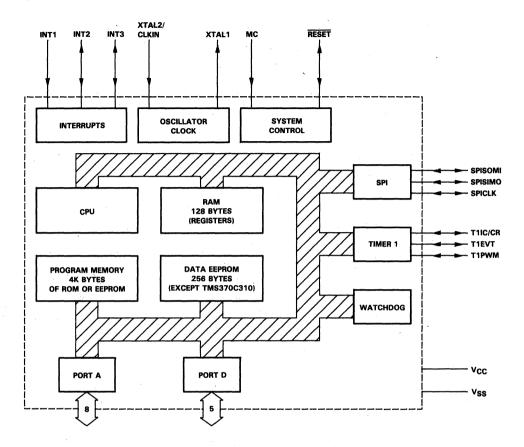

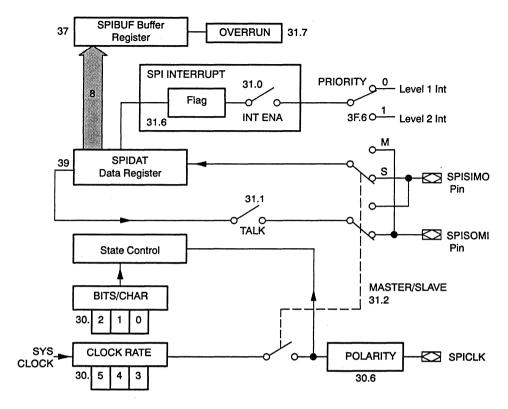

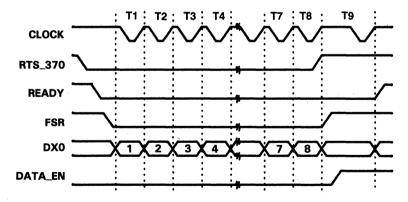

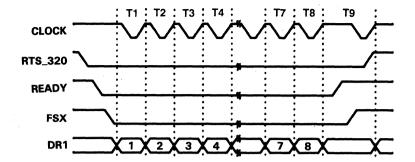

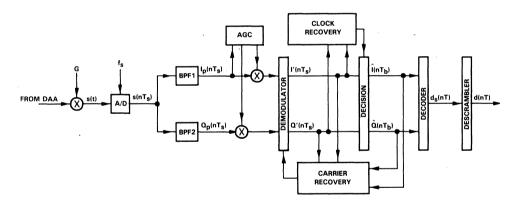

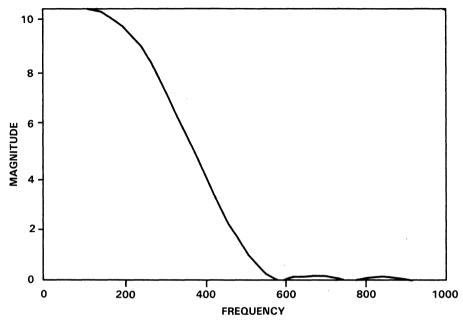

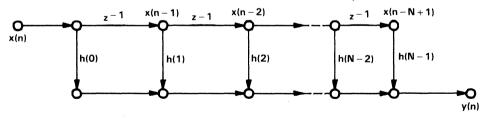

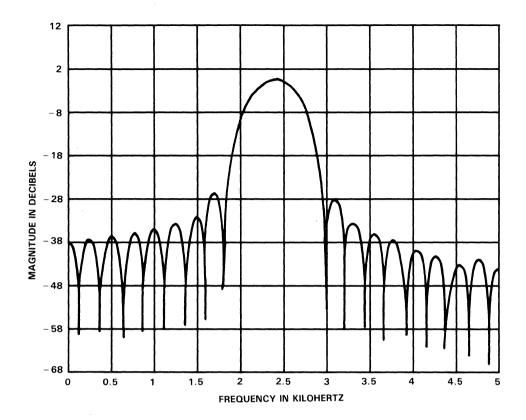

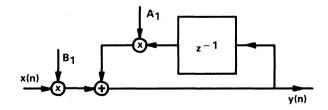

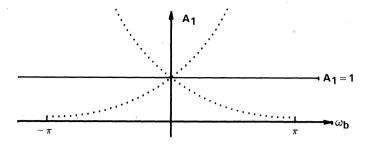

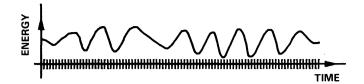

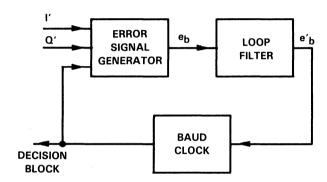

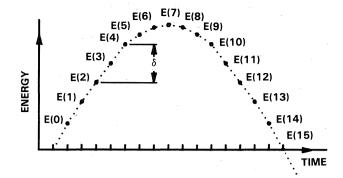

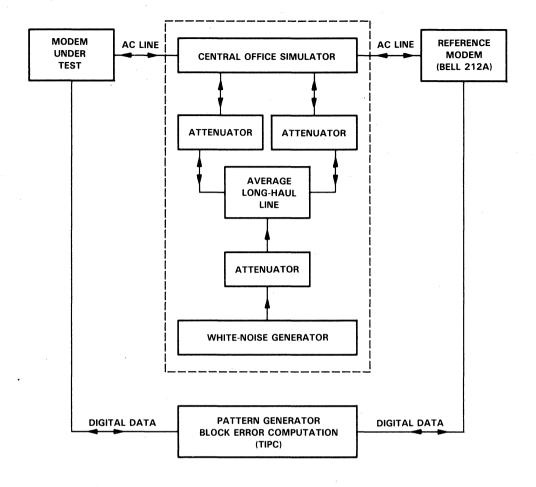

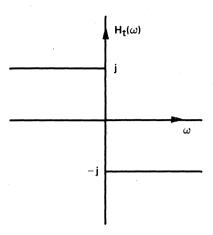

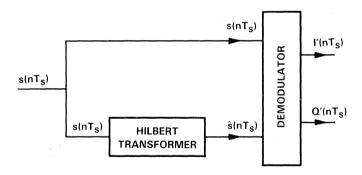

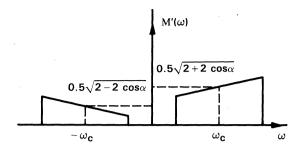

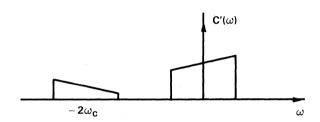

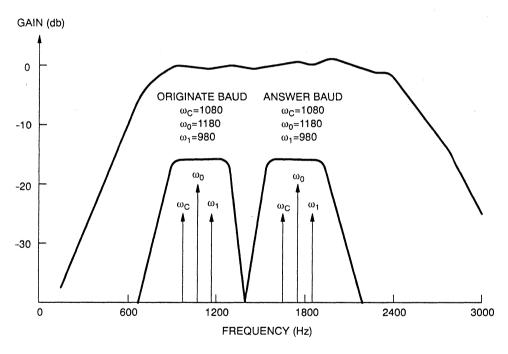

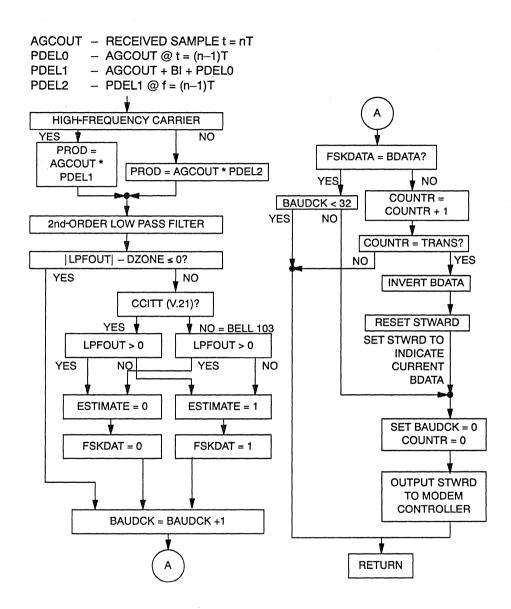

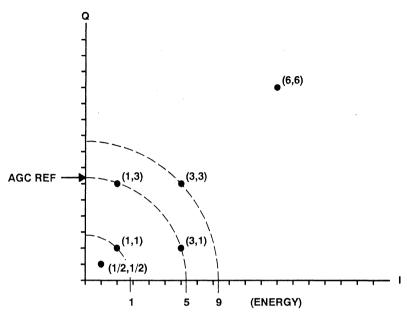

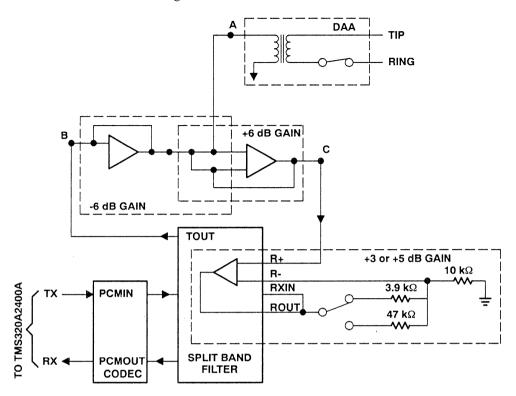

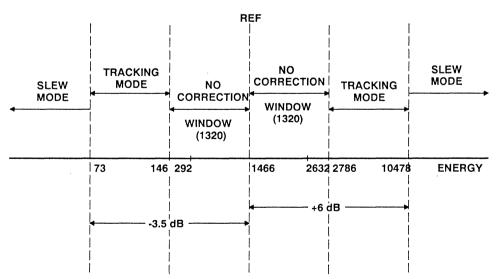

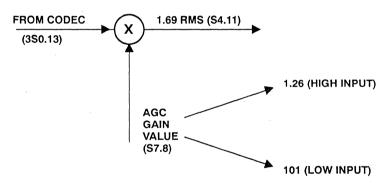

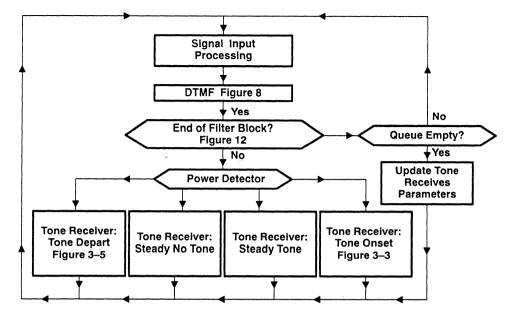

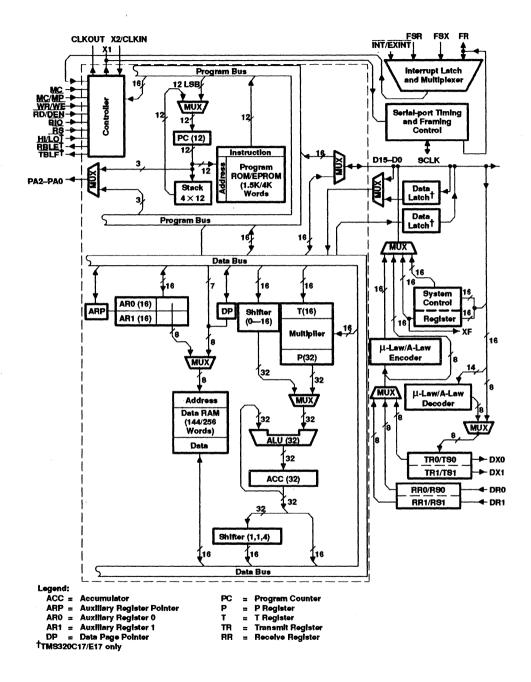

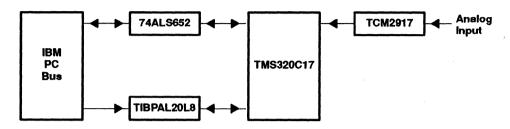

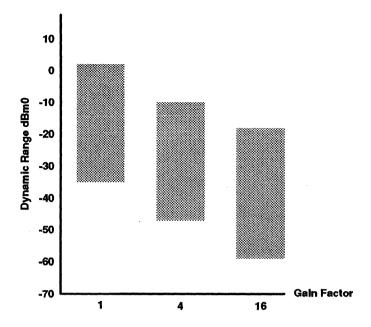

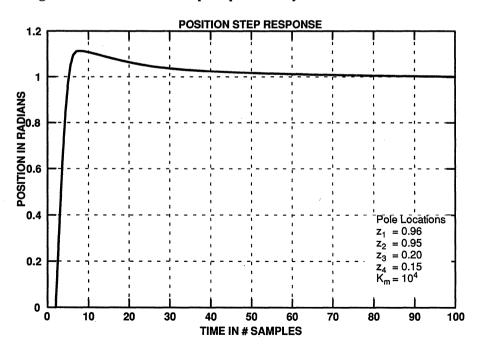

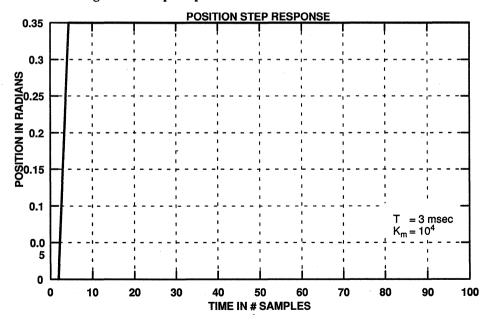

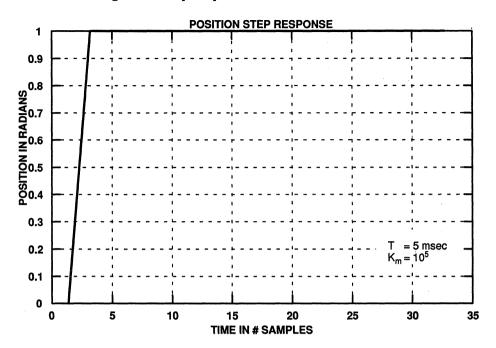

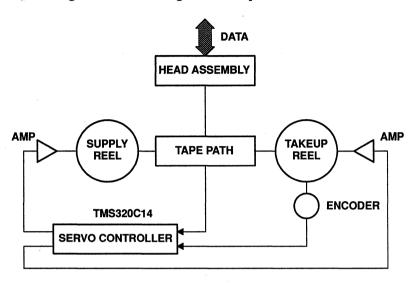

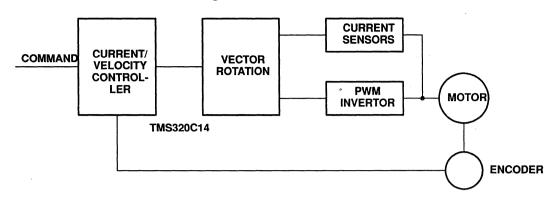

The CPU consists of the following elements: floatingpoint/integer multiplier; ALU for performing floating-point, integer, and logical operations; auxiliary register arithmetic units; supporting register file, and associated buses. The multiplier of the CPU performs floating-point and integer multiplication. When performing floating-point multiplication, the inputs are 32-bit floating-point numbers, and the result is a 40-bit floating-point number. When performing integer multiplication, the input data is 24 bits and yields a 32-bit result. The ALU performs 32-bit integer, 32-bit logical, and 40-bit floating-point operations. Results of the multiplier and the ALU are always maintained in 32-bit integer or 40-bit floating-point formats. The TMS320C30 has the ability to perform, in a single cycle, parallel multiplies and adds (subtracts) on integer or floating-point data. It is this ability to perform floating-point multiplies and adds (subtracts) in a single cycle which give the TMS320C30 its peak computational rate of 33 MFLOPS.