# TMS320C25 User's Guide Preliminary

## Digital Signal Processor Products

## TMS320C25 User's Guide

## **Digital Signal Processor Products**

Preliminary

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes in the devices or the device specifications identified in this publication without notice. TI advises its customers to obtain the latest version of device specifications to verify, before placing orders, that the information being relied upon by the customer is current.

In the absence of written agreement to the contrary, TI assumes no liability for TI applications assistance, customer's product design, or infringement of patents or copyrights of third parties by or arising from use of semiconductor devices described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor devices might be or are used.

Copyright © 1986, Texas Instruments Incorporated

## Contents

| Sect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | tion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>1</b><br>1.1<br>1.2<br>1.3<br>1.4<br>1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Introduction         General Description         Typical Applications         Key Features         How To Use This Manual         References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>1-1</b><br>1-2<br>1-4<br>1-5<br>1-6<br>1-7                                                                                                                              |

| <b>2</b><br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Architectural Overview         Functional Block Diagram         Pinout and Signal Descriptions         Memory         Central Arithmetic Logic Unit (CALU)         System Control         I/O Interface         System Configurations         Addressing Modes and Instructions         Development Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>2-1</b><br>2-3<br>2-7<br>2-10<br>2-11<br>2-12<br>2-12<br>2-15<br>2-22                                                                                                   |

| <b>3</b><br>3.1<br>3.2.1<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>3.3.1<br>3.3.4<br>3.4.5<br>3.5.1<br>3.5.4<br>3.5.1<br>3.5.3<br>3.5.4<br>3.6.2<br>3.5.4<br>3.6.2<br>3.7.1<br>3.7.1<br>3.7.1<br>3.7.1<br>3.7.1<br>3.7.1<br>3.7.1<br>3.7.1<br>3.7.1<br>3.7.1<br>3.7.1<br>3.7.1<br>3.7.1<br>3.7.1<br>3.7.1<br>3.7.1<br>3.7.1<br>3.7.1<br>3.7.1<br>3.7.5<br>3.7.1<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5<br>3.7.5 | On-Chip Data RAM Blocks         Memory Maps         Memory-Mapped Registers         Auxiliary Registers         Auxiliary Registers         Addressing Modes         Memory-to-Memory Moves         Central Arithmetic Logic Unit (CALU)         Scaling Shifter         ALU and Accumulator         Multiplier, T and P Registers         System Control         Program Counter and Related Hardware         Reset         Status Registers         Timer Operation         Repeat Counter         Powerdown Mode         External Memory and I/O Interface         Memory Combinations         Internal Clock Timing Relationships         External Read Cycle         External Write Cycle         Interrupt Operation         External Interrupt Interface         Serial Port         Burst-Mode Operation | 3-7<br>3-9<br>3-12<br>3-13<br>3-14<br>3-15<br>3-16<br>3-16<br>3-18<br>3-21<br>3-26<br>3-26<br>3-26<br>3-26<br>3-27<br>3-28<br>3-28<br>3-31<br>3-31<br>3-31<br>3-35<br>3-38 |

| 3.7.2<br>3.7.3<br>3.7.4<br>3.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Continuous-Mode Operation Without Frame Sync Pulses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-40<br>3-41<br>3-43<br>3-44                                                                                                                                               |

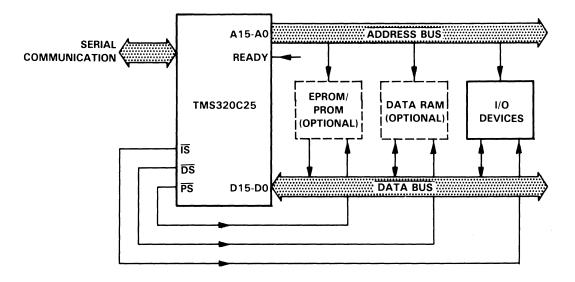

| 3.8.1<br>3.8.2<br>3.8.3 | 2 Global Memory                               |           | 3-45<br>3-45<br>3-47 |

|-------------------------|-----------------------------------------------|-----------|----------------------|

| 3.9<br>3.9.1            |                                               | • • • •   | 3-49<br>3-49         |

| 3.9.2                   | 2 External Flag Output                        |           | 3-50                 |

| 4                       | Assembly Language Instructions                |           | 4-1                  |

| 4.1                     | Memory Addressing Modes                       |           | 4-2                  |

| 4.1.1                   |                                               |           | 4-2                  |

| 4.1.2                   | 2 Indirect Addressing Mode                    |           | 4-3                  |

| 4.1.3                   | 3 Immediate Addressing Mode                   |           | 4-7                  |

| 4.2                     | Instruction Set                               | • • • • · | 4-8                  |

| 4.2.1                   | Symbols and Abbreviations                     |           | 4-8                  |

| 4.2.2                   |                                               |           | 4-9                  |

| 4.3                     | Individual Instruction Descriptions           |           | 4-13                 |

| 5                       | Software Applications                         |           | 5-1                  |

| 5.1                     | Processor Initialization                      |           | 5-2                  |

| 5.2                     | Program Control                               |           | 5-4                  |

| 5.2.1                   | Subroutines                                   |           | 5-4                  |

| 5.2.2                   | 2 Software Stack                              |           | 5-6                  |

| 5.2.3                   | 3 Timer Operation                             |           | 5-7                  |

| 5.2.4                   |                                               |           | 5-8                  |

| 5.2.5                   |                                               |           | 5-9                  |

| 5.3                     | Interrupt Service Routine                     |           | 5-11                 |

| 5.3.1                   |                                               |           | 5-11                 |

| 5.3.2                   |                                               |           | 5-14                 |

| 5.4                     | Memory Management                             |           | 5-15                 |

| 5.4.1                   |                                               |           | 5-15                 |

| 5.4.2                   |                                               |           | 5-17                 |

| 5.4.3                   |                                               |           | 5-20                 |

| 5.5                     | Fundamental Logical and Arithmetic Operations |           | 5-23                 |

| 5.5.1                   |                                               |           | 5-23                 |

| 5.5.2                   |                                               |           | 5-24                 |

|                         | Advanced Arithmetic Operations                |           | 5-25                 |

| 5.6.1                   | •                                             |           | 5-25                 |

| 5.6.2                   |                                               |           | 5-26                 |

| 5.6.3                   |                                               |           | 5-26                 |

| 5.6.4                   | •                                             |           |                      |

|                         |                                               |           | 5-28                 |

| 5.6.5                   |                                               |           | 5-32                 |

| 5.6.6                   |                                               |           | 5-35                 |

| 5.6.7                   | $\mathbf{O}$                                  |           | 5-37                 |

| 5.6.8                   |                                               |           | 5-38                 |

| 5.7                     | Application-Oriented Operations               |           | 5-42                 |

| 5.7.1                   |                                               |           | 5-42                 |

| 5.7.2                   |                                               |           | 5-43                 |

| 5.7.3                   | 3 Fast Fourier Transforms (FFT)               |           | 5-46                 |

| 6                       | Hardware Applications                         |           | 6-1                  |

| 6.1                     | External Local Memory Interface               |           | 6-2                  |

| 6.2                     | Wait States                                   |           | 6-3                  |

| 6.3                     | Direct Memory Access                          |           | 6-4                  |

| 6.4                     | Global Memory                                 |           | 6-6                  |

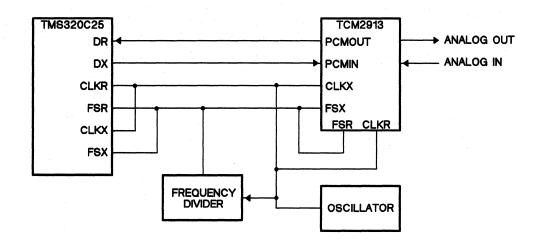

| 6.5                     | Codec Interface                               |           | 6-7                  |

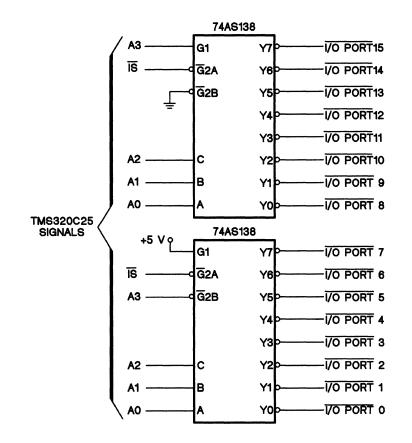

| 6.6                     | I/O Ports                                     |           | 6-8                  |

÷

|       | Assembler Directives                             |

|-------|--------------------------------------------------|

| 7.1   | Creation of TMS320C25 Source Code                |

| 7.1.1 | Label Field                                      |

| 7.1.2 | Command Field                                    |

| 7.1.3 | Operand Field                                    |

| 7.1.4 | Comment Field                                    |

| 7.2   | Symbols                                          |

| 7.2.1 | Predefined Symbols                               |

| 7.3   | Constants                                        |

| 7.3.1 | Decimal Integer Constants                        |

| 7.3.2 | Binary Integer Constants                         |

| 7.3.3 | Hexadecimal Integer Constants                    |

| 7.3.4 | Character Constants                              |

| 7.3.5 | Assembly-Time Constants                          |

|       | Character Strings                                |

|       |                                                  |

| 7.5.1 | Arithmetic Operators in Expressions              |

| 7.5.2 | Parentheses in Expressions                       |

| 7.5.3 | Well-Defined Expressions                         |

| 7.5.4 | Absolute and Relocatable Symbols in Expressions  |

| 7.5.5 | Externally Referenced Symbols in Expressions     |

|       | Assembler Directives                             |

| 7.6.1 | Directives That Affect the Location Counter      |

| 7.6.2 | Directives That Affect Assembler Output          |

| 7.6.3 | Directives That Initialize Constants             |

| 7.6.4 | Directives That Provide Linkage Between Programs |

| 7.6.5 |                                                  |

|       |                                                  |

|       | Individual Directive Descriptions                |

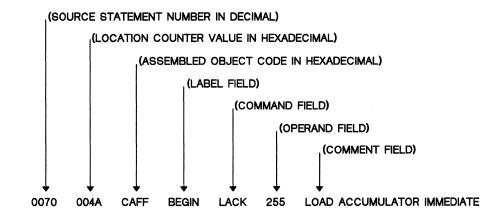

| 7.8   | Source Listing Format                            |

|       | Object Code                                      |

| 7.9.1 | Object Code Format                               |

| 7.9.2 | Changing Object Code                             |

| 7.10  | Cross-Reference Listing                          |

| 7.11  | Assembler Error Messages                         |

| 8     | Assembler Macros                                 |

|       | Macro Definitions                                |

| 8.1.1 | Sample Macros                                    |

|       |                                                  |

|       | Strings                                          |

|       | Constants                                        |

|       | Variables                                        |

| 8.5.1 | Parameters                                       |

| 8.5.2 | Macro Symbol Table (MST)                         |

|       |                                                  |

| 8.5.3 |                                                  |

|       |                                                  |

| 8.6.1 |                                                  |

| 8.6.2 |                                                  |

| 8.6.3 |                                                  |

|       | Keywords                                         |

| 8.7.1 | Symbol Attribute Component Keywords              |

| 8.7.2 | Parameter Attribute Component Keywords           |

|       | Verb Statements                                  |

| 8.8.1 | \$ASG (Value Assignment Verb)                    |

| 8.8.2 | \$ELSE (Alternate Else Verb)                     |

| 8.8.3 | \$END (Macro Definition Termination Verb)        |

| 8.8.4 | \$ENDIF (IF Termination Verb)                    |

|       |                                                  |

| 8.8.5 | \$IF (Conditional If Verb)                       |

|       |                                                  |

| 8.9<br>8 10           | Model Statements<br>Macro Examples                                                                                                          |                |     |    |   |     |    |       |   |       |   |       |   |       |   |       |   |   |     |    |   | 8-17<br>8-18                           |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----|----|---|-----|----|-------|---|-------|---|-------|---|-------|---|-------|---|---|-----|----|---|----------------------------------------|

| 8.10                  |                                                                                                                                             |                |     |    |   |     |    |       |   |       |   |       |   |       |   |       |   |   |     |    |   | 8-18                                   |

| 8.10                  |                                                                                                                                             |                |     |    |   |     |    |       |   |       |   |       |   |       |   |       |   |   |     |    |   | 8-19                                   |

| 8.10                  | .3 FACT (Factorial Macro                                                                                                                    | )              |     |    |   | ,   |    |       | ÷ |       |   |       |   |       |   |       |   |   |     |    |   |                                        |

|                       | Macro Error Messages                                                                                                                        |                |     |    |   |     |    |       |   |       |   |       |   |       |   |       |   |   |     |    |   |                                        |

| ••••                  |                                                                                                                                             |                | •   |    | • |     | •  | <br>  | • | <br>- | • | <br>• |   |       | • | <br>- | • | · |     | Ċ, | • |                                        |

| 9                     | Link Editor                                                                                                                                 |                |     |    |   |     |    |       |   |       |   |       |   |       |   |       |   |   |     |    |   | 9-1                                    |

| 9.1                   | Description                                                                                                                                 |                |     |    |   |     |    | <br>  |   |       |   |       |   |       |   |       |   |   |     |    |   | 9-2                                    |

| 9.2                   | Program Definition                                                                                                                          |                |     |    |   |     |    |       |   |       |   |       |   |       |   |       |   |   |     |    |   | 9-2                                    |

| 9.3                   | Link Editor Files                                                                                                                           |                |     |    |   |     |    |       |   |       |   |       |   |       |   |       |   |   |     |    |   | 9-3                                    |

| 9.3.1                 |                                                                                                                                             |                |     |    |   |     |    | <br>• | • | <br>  |   |       |   |       |   |       |   |   | • • |    | • | 9-3                                    |

| 9.3.2                 |                                                                                                                                             |                |     |    |   |     |    |       |   |       |   |       |   |       |   |       |   |   |     |    |   |                                        |

| 9.3.3                 | Libraries                                                                                                                                   |                |     |    |   |     |    |       |   |       |   |       |   |       |   | <br>• |   |   |     |    |   | 9-4                                    |

| 9.3.4                 |                                                                                                                                             |                |     |    |   |     |    |       |   |       |   |       |   |       |   |       |   |   |     |    |   | 9-4                                    |

| 9.3.5                 | Listing File                                                                                                                                |                |     |    |   |     |    |       |   |       |   |       |   |       |   |       |   |   |     |    |   | 9-4                                    |

| 9.4                   | Linker Commands                                                                                                                             |                |     |    |   |     |    |       |   |       |   |       |   |       |   |       |   |   |     |    |   | 9-5                                    |

| 9.4.1                 | Entering a Command                                                                                                                          |                |     |    |   |     |    |       |   |       |   |       | • |       |   |       |   |   |     |    |   | 9-5                                    |

| 9.4.2                 |                                                                                                                                             |                |     |    |   |     |    |       |   |       |   |       |   |       |   |       |   |   |     |    |   | 9-5                                    |

| 9.4.3                 |                                                                                                                                             |                |     |    |   |     |    |       |   |       |   |       |   |       |   |       |   |   |     |    |   | 9-7                                    |

| 9.5                   | Linking Examples                                                                                                                            |                |     |    |   |     |    |       |   |       |   |       |   |       |   |       |   |   |     |    |   | 9-36                                   |

| 9.5.1                 |                                                                                                                                             |                |     |    |   |     |    |       |   |       |   |       |   |       |   |       |   |   |     |    |   | 9-39                                   |

| 9.5.2                 |                                                                                                                                             |                |     |    |   |     |    |       |   |       |   |       |   |       |   |       |   |   |     |    |   | 9-41                                   |

| 9.5.3                 |                                                                                                                                             |                |     |    |   |     |    |       |   |       |   |       |   |       |   |       |   |   |     |    |   | 9-43                                   |

| 9.5.4                 |                                                                                                                                             |                |     |    |   |     |    |       |   |       |   |       |   |       |   |       |   |   |     |    |   | 9-47                                   |

| 9.6                   | Link Editor Error Messages                                                                                                                  | ;              | •   |    | • |     |    | <br>• | • | <br>• | • | <br>• | • | <br>• | • |       | • | • |     | ÷  | • | 9-50                                   |

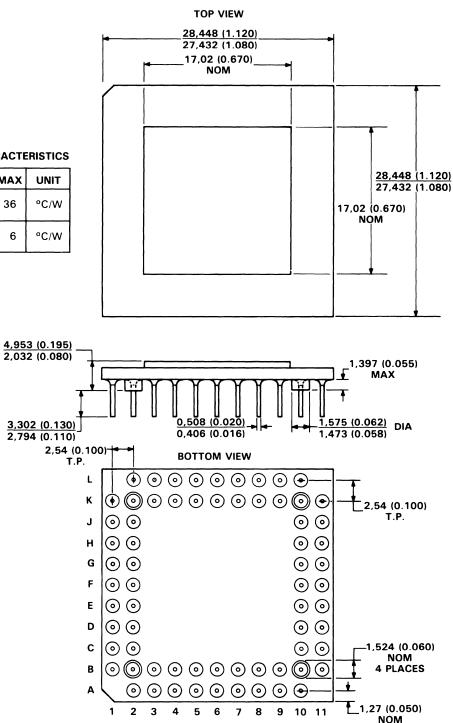

| A<br>B<br>C<br>D<br>E | TMS320C25 Data Sheet<br>TMS32020 Data Sheet<br>TMS320C10 Data Sheet<br>TMS32020/TMS320C25<br>TMS320C25 Instruction<br>TMS320C25 Development | t<br>Sys<br>Cy | cle | Ti | m | ing | js |       |   |       |   |       |   |       |   |       |   |   |     |    |   | A-1<br>B-1<br>C-1<br>D-1<br>E-1<br>F-1 |

## Illustrations

### Figure

-

| 1-1.         | TMS320C25 Digital Signal Processor                                                                                                                              | 1-3  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

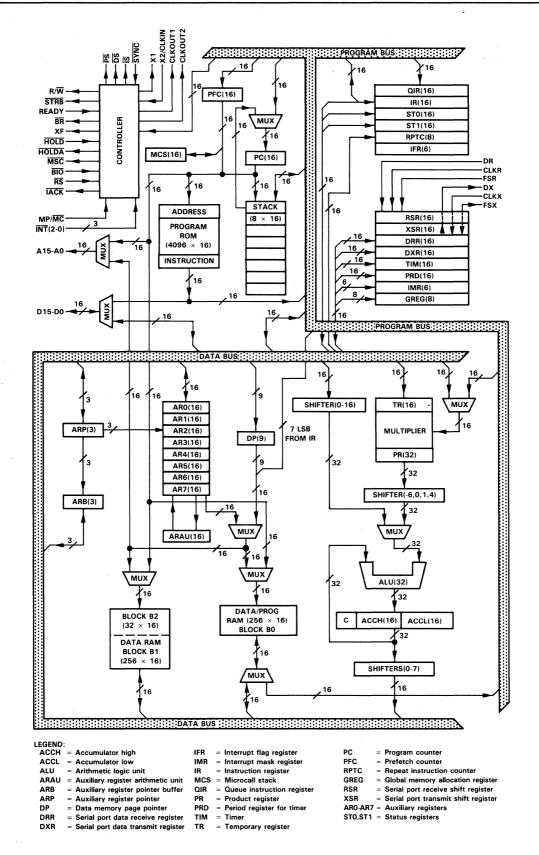

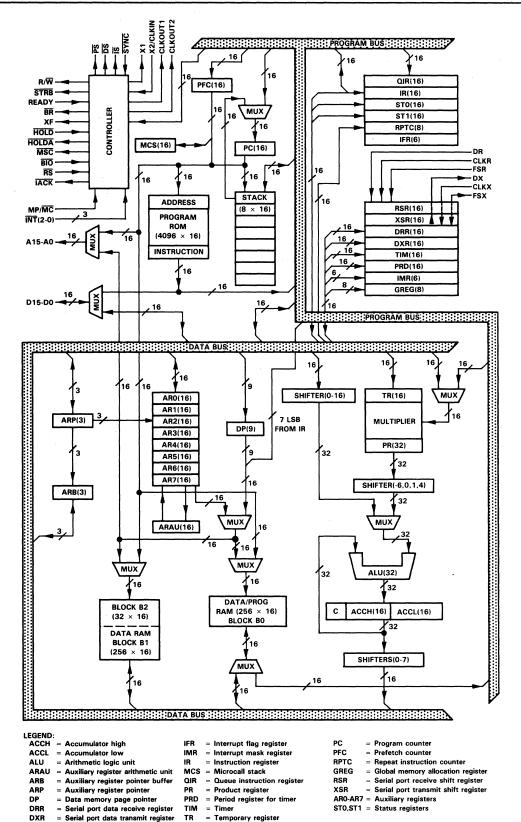

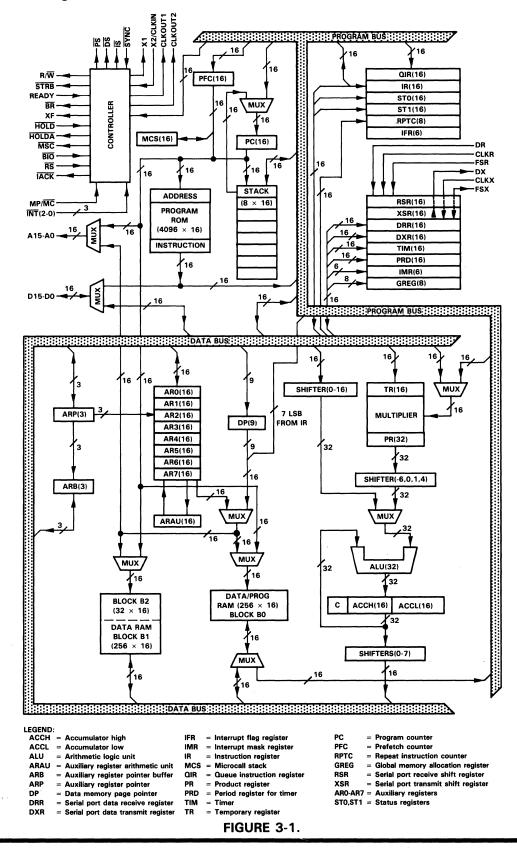

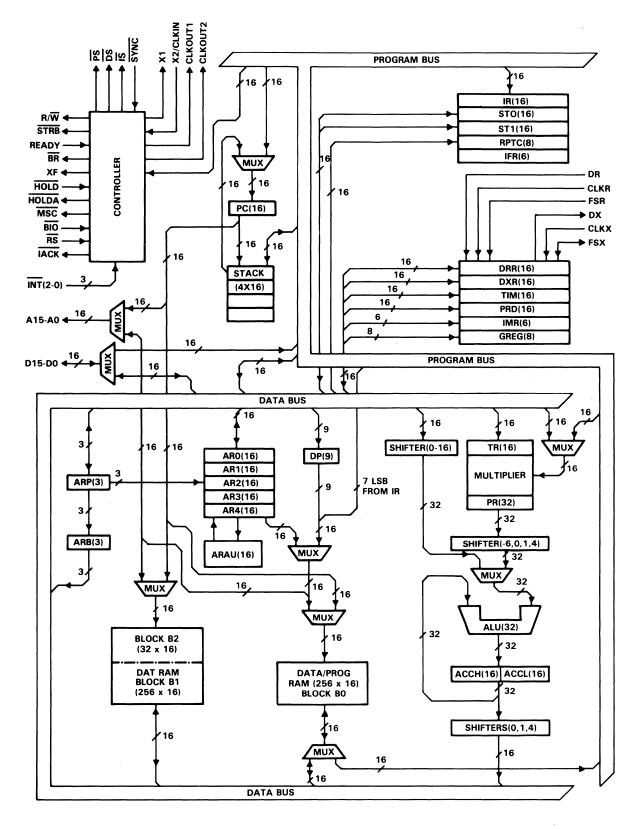

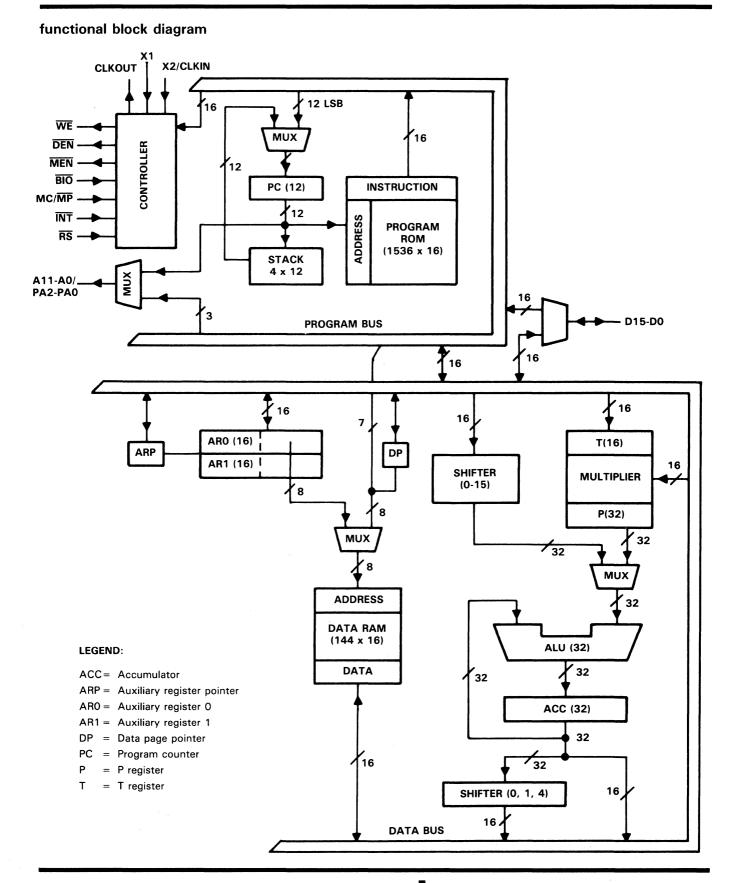

| 2-1.         | TMS320C25 Block Diagram                                                                                                                                         |      |

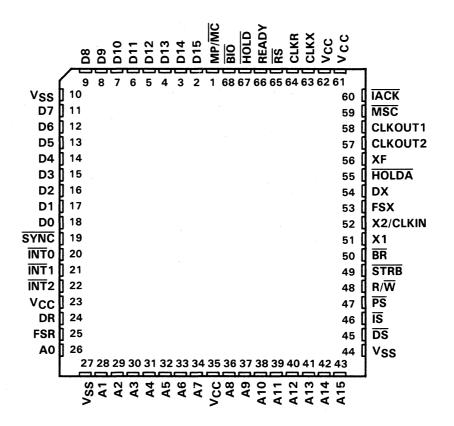

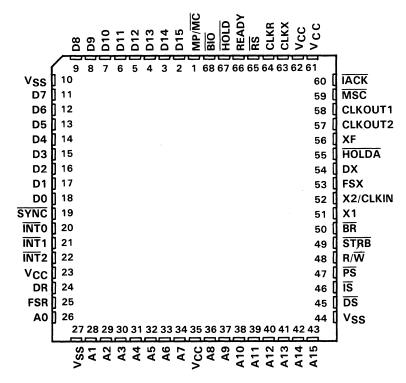

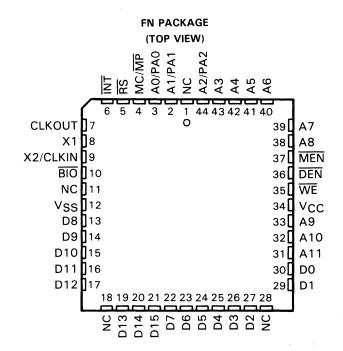

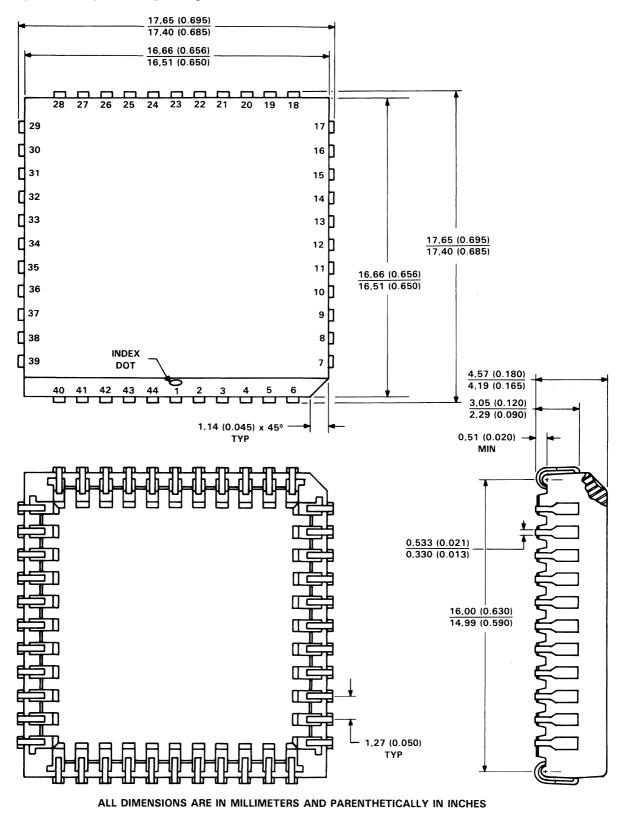

| 2-2.         | TMS320C25 Pin Assignments                                                                                                                                       |      |

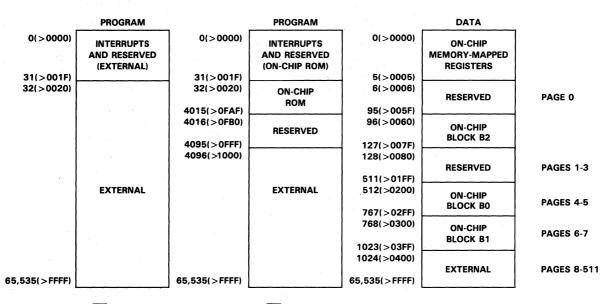

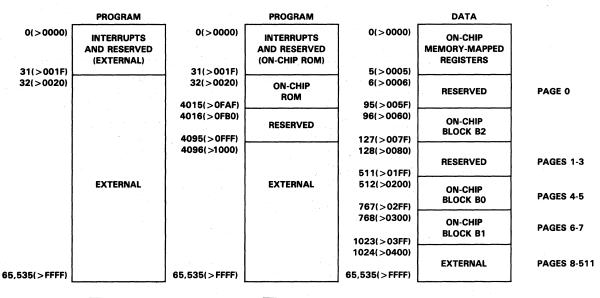

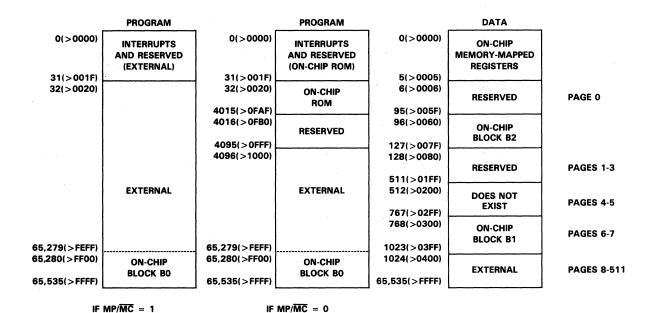

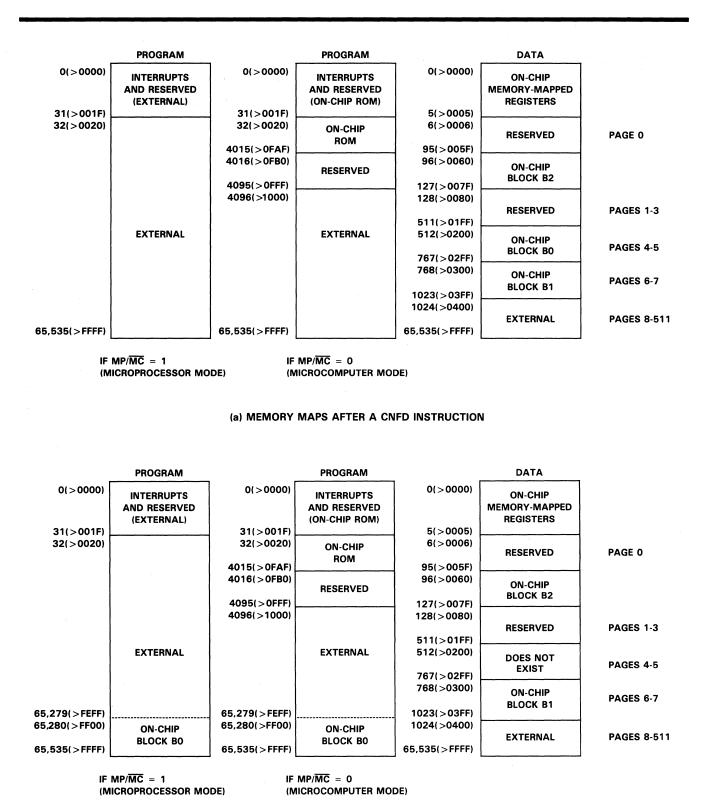

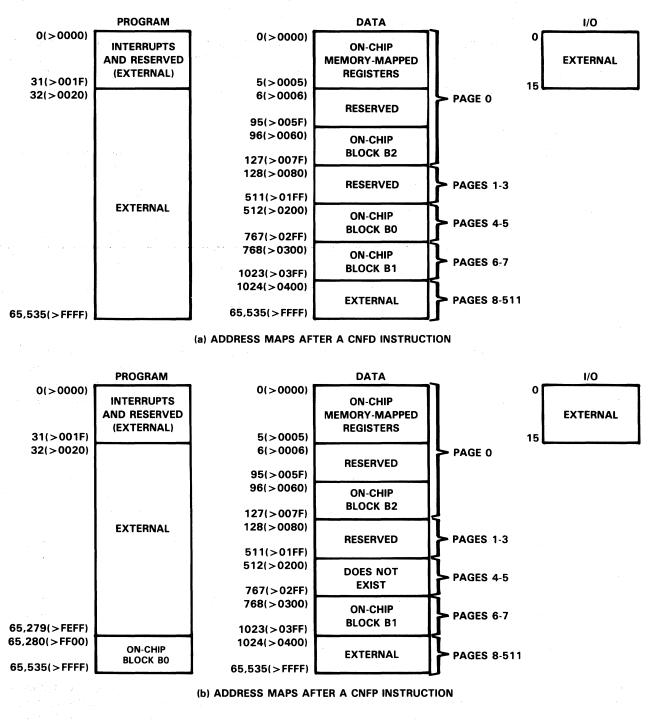

| 2-3.         | TMS320C25 Memory Maps                                                                                                                                           | 2.2  |

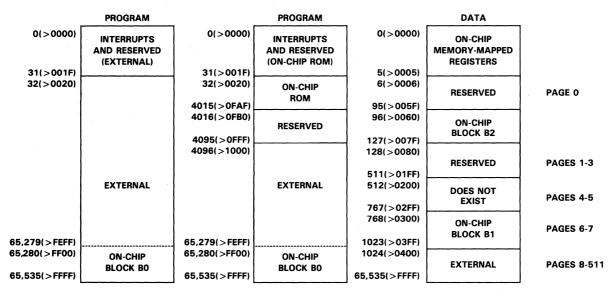

| 2-3.<br>2-4. | A Minimum Processing System                                                                                                                                     |      |

|              | A Minimum Processing System                                                                                                                                     | 2-13 |

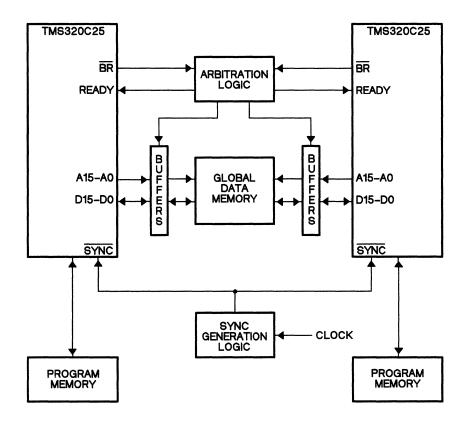

| 2-5.         | Global Memory Parallel Processing                                                                                                                               | 2-14 |

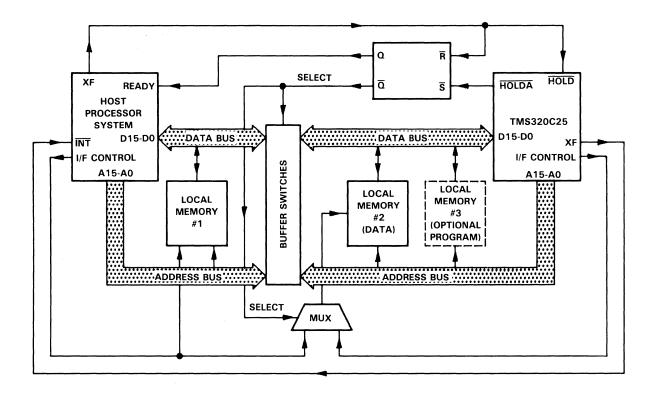

| 2-6.         | Host/Peripheral Coprocessing Using Interface Control Signals                                                                                                    | 2-15 |

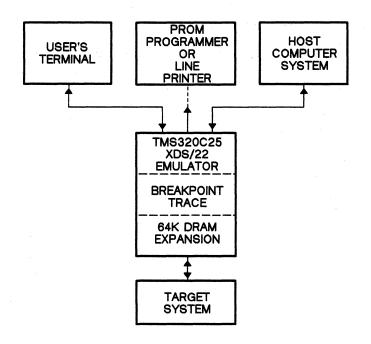

| 2-7.         | TMS320C25 Development Support                                                                                                                                   | 2-22 |

| 3-1.         | TMS320C25 Block Diagram                                                                                                                                         | 3-2  |

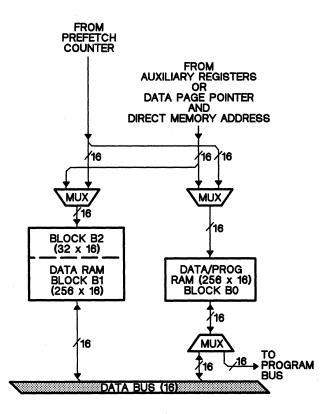

| 3-2.         | On-Chip Data Memory                                                                                                                                             |      |

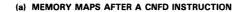

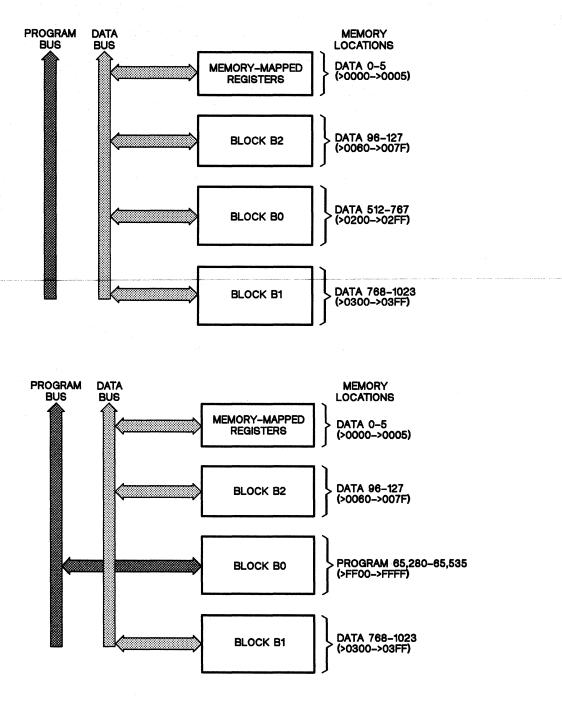

| 3-3.         | Memory Maps                                                                                                                                                     | 3-8  |

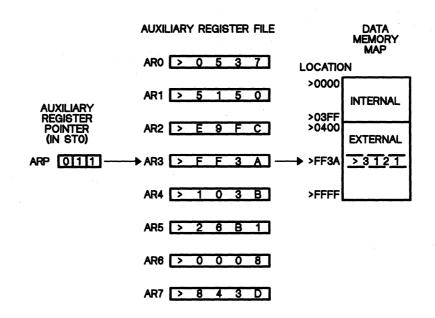

| 3-4.         | Indirect Auxiliary Register Addressing Example                                                                                                                  | 3-10 |

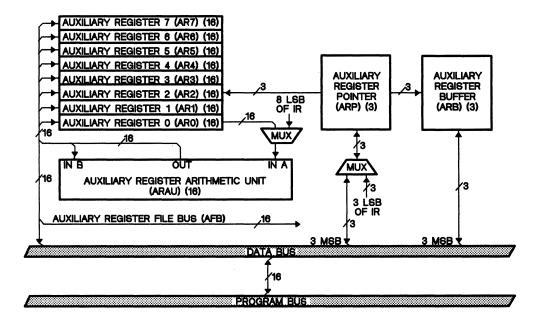

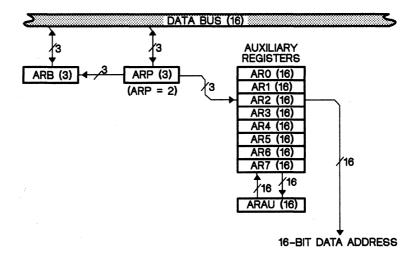

| 3-5.         | Auxiliary Register File                                                                                                                                         |      |

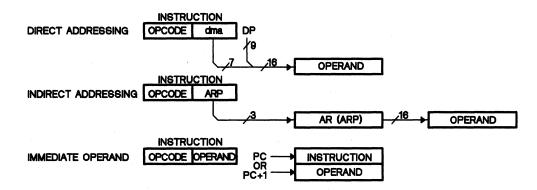

| 3-6.         | Methods of Instruction Operand Addressing                                                                                                                       | 3-12 |

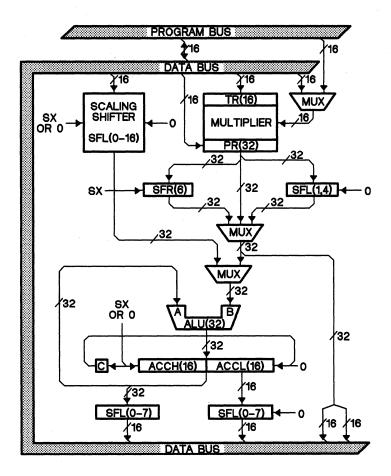

| 3-7.         | Central Arithmetic Logic Unit (CALU)                                                                                                                            | 3-14 |

| 3-8.         | Examples of Carry Bit Operation                                                                                                                                 | 3-15 |

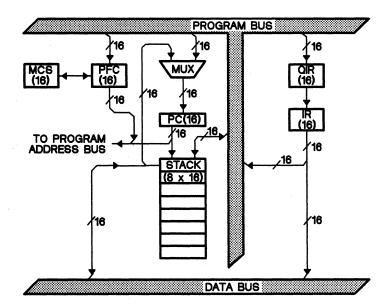

| 3-9.         | Program Counter and Related Hardware                                                                                                                            | 3,18 |

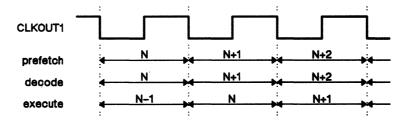

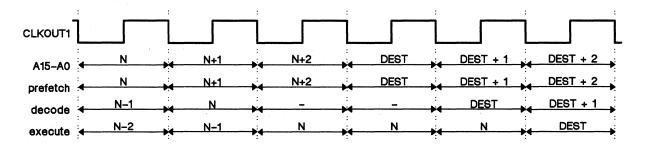

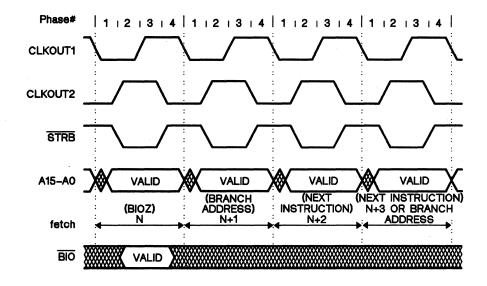

|              | Three-Level Pipeline Operation                                                                                                                                  |      |

| 3-10.        | Three-Level Fipeline Operation                                                                                                                                  | 2 10 |

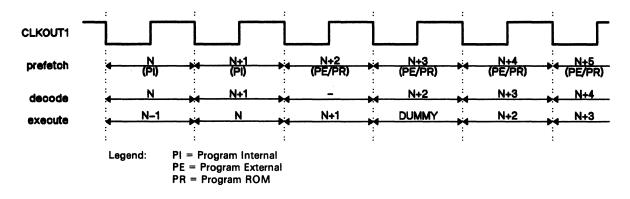

|              | Two-Level Pipeline Operation                                                                                                                                    |      |

| 3-12.        | Pipeline Operation During BANZ Instruction                                                                                                                      | 3-20 |

| 3-13.        | Pipeline Operation When Crossing Program Boundaries                                                                                                             | 3-21 |

| 3-14.        | Status Register Organization                                                                                                                                    | 3-23 |

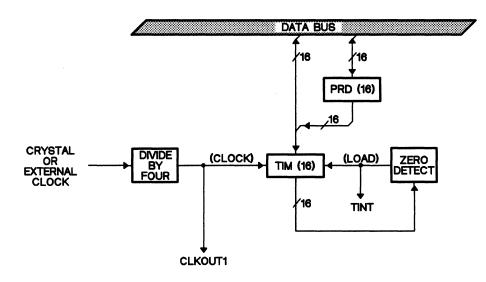

| 3-15.        | Timer Block Diagram                                                                                                                                             | 3-25 |

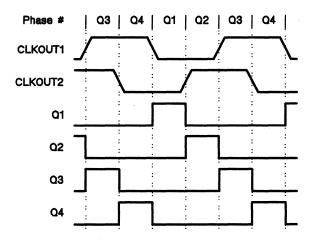

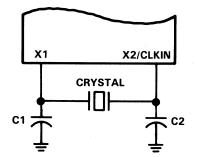

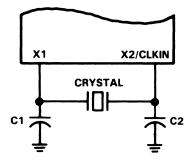

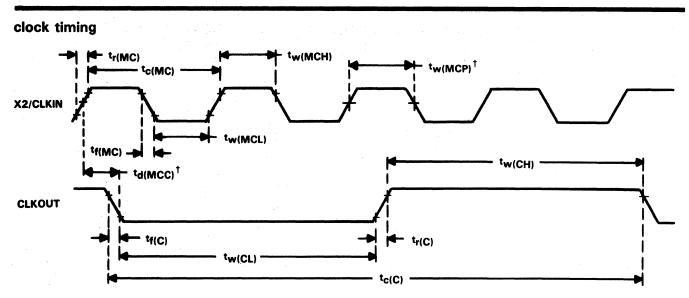

|              | Four-Phase Clock                                                                                                                                                |      |

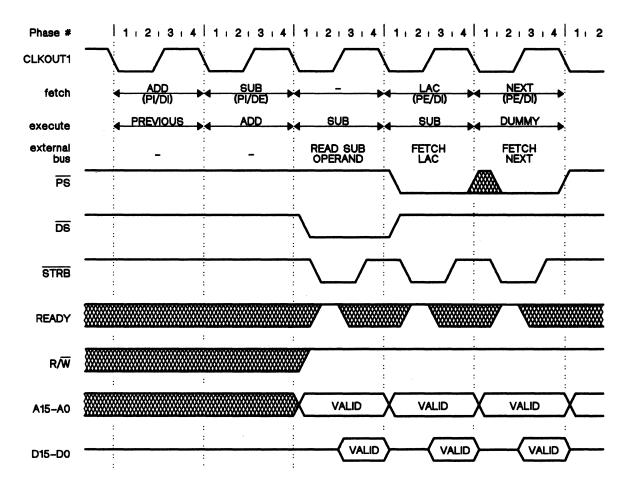

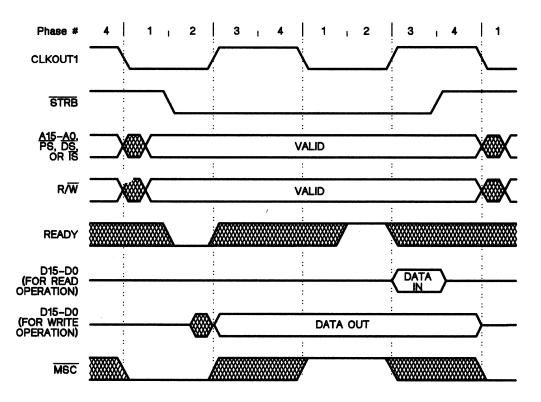

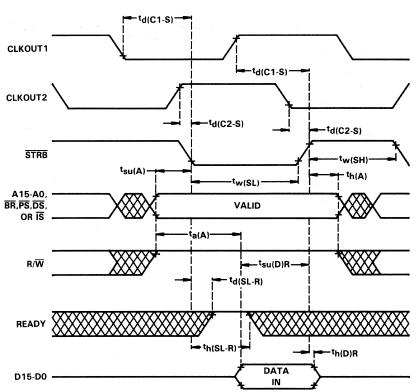

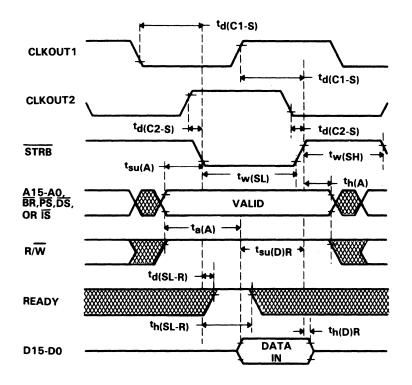

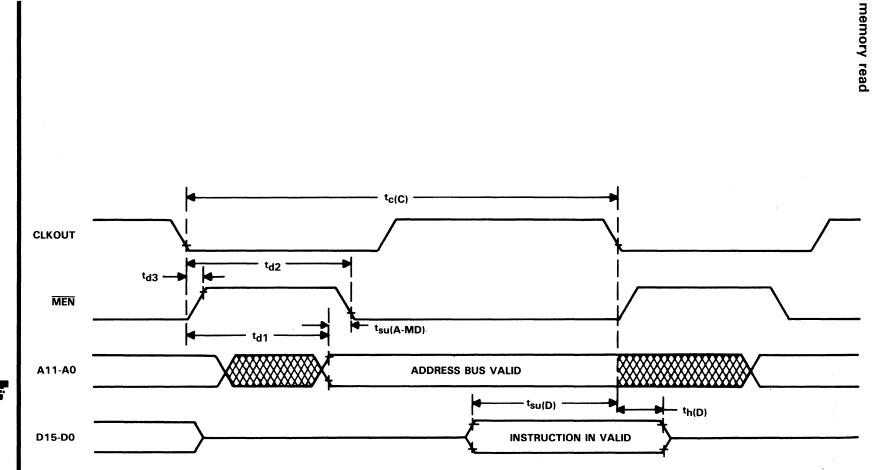

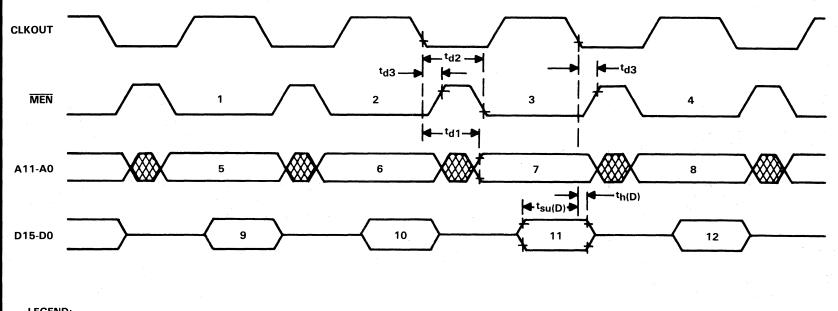

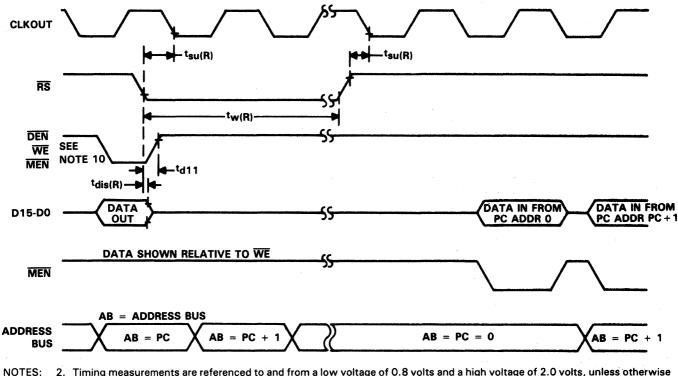

| 3-17.        | Read Cycle Functional Timing                                                                                                                                    | 3-29 |

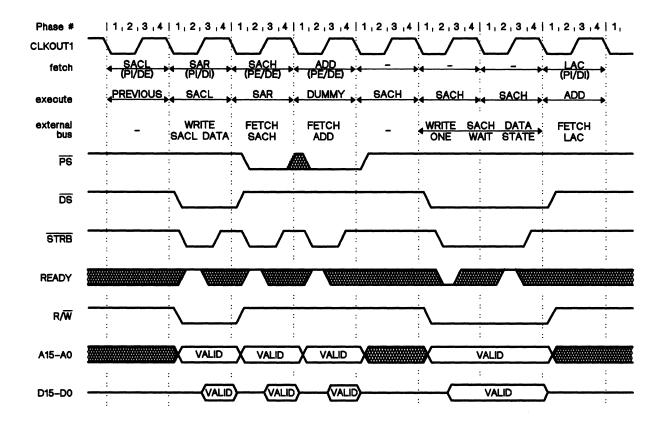

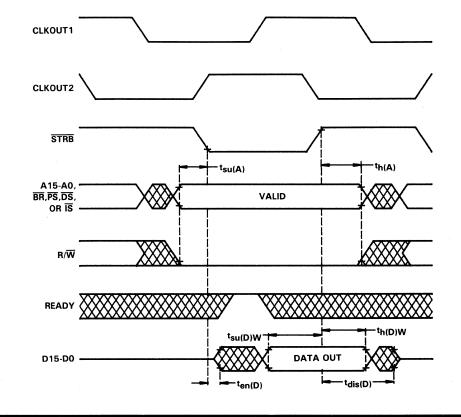

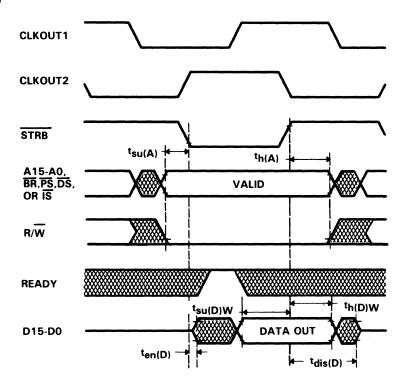

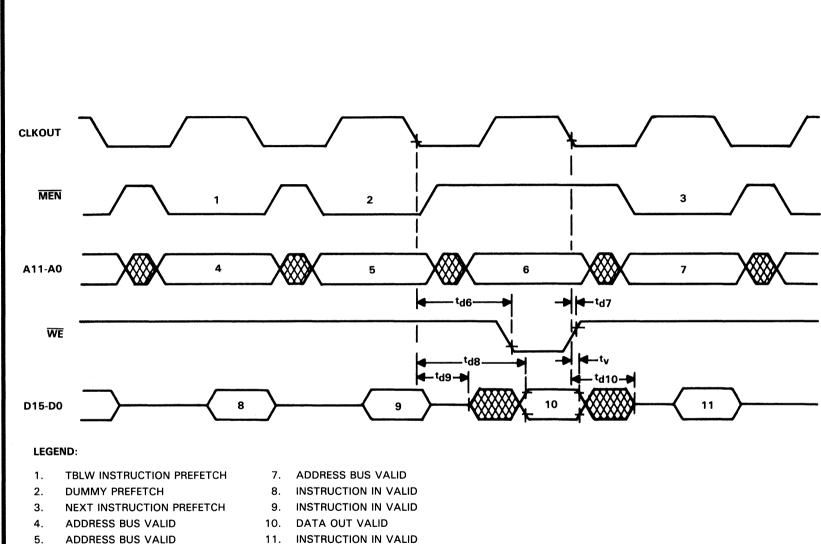

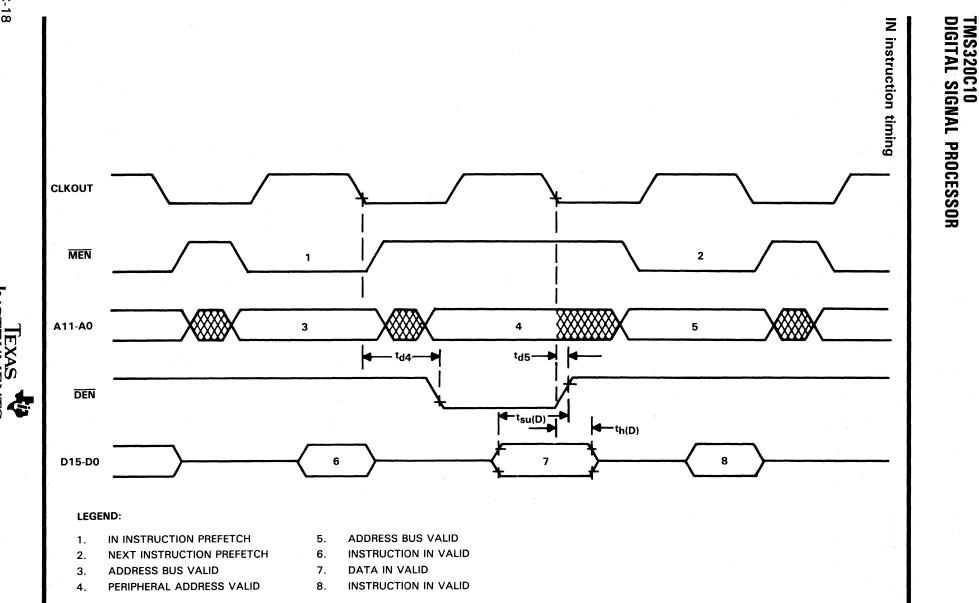

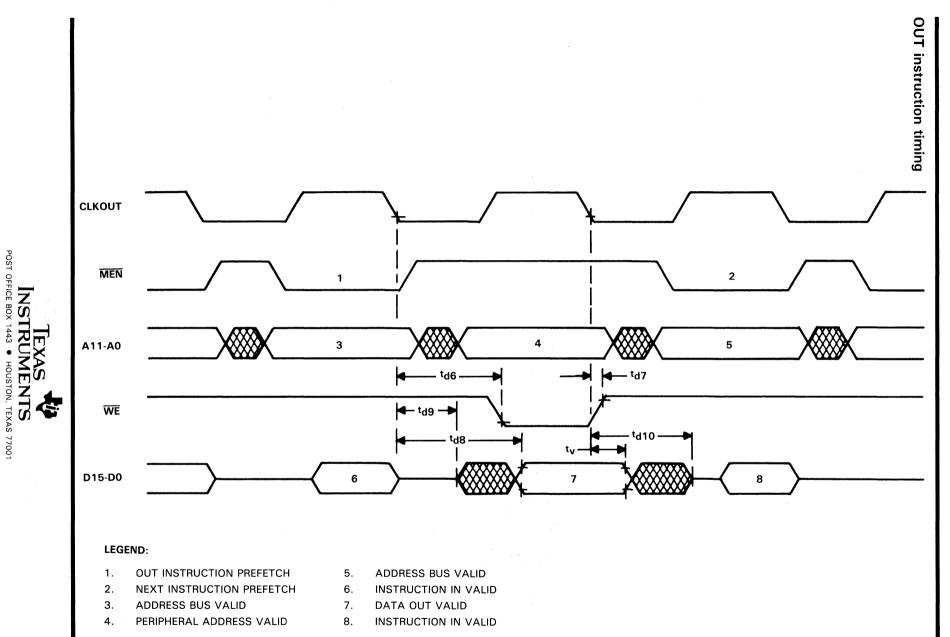

| 3-18.        | Functional Timing of Write Cycles and Wait States                                                                                                               | 3-31 |

|              | Interrupt Mask Register (IMR)                                                                                                                                   |      |

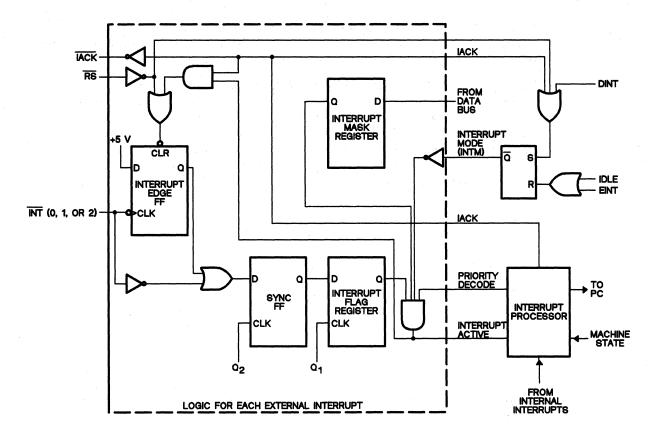

|              | Internal Interrupt Logic Diagram                                                                                                                                |      |

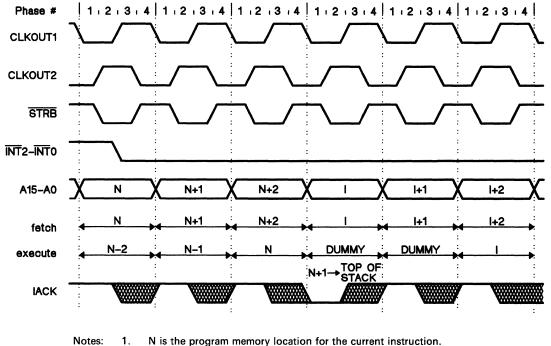

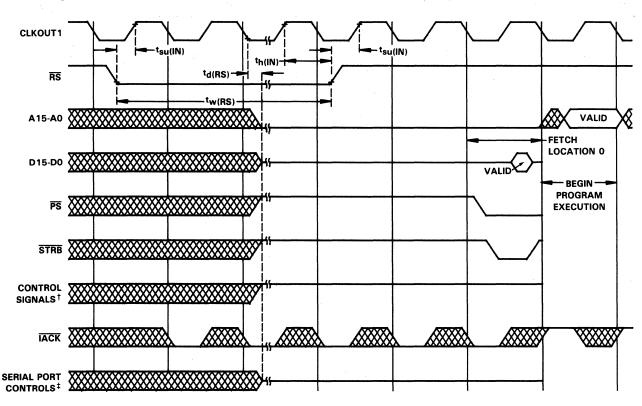

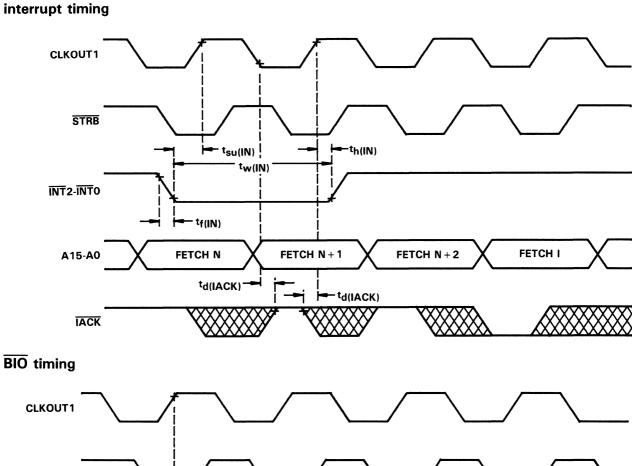

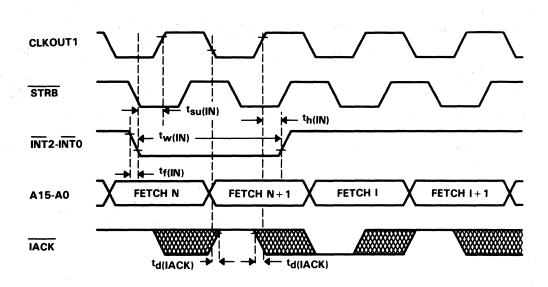

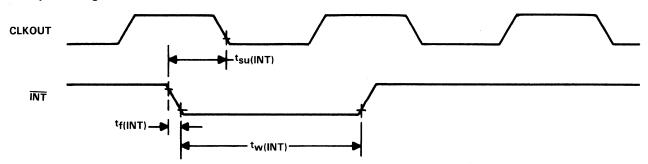

|              | Interrupt Timing Diagram                                                                                                                                        |      |

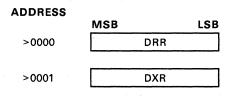

| 3,22         | The DRR and DXR Registers                                                                                                                                       | 3-36 |

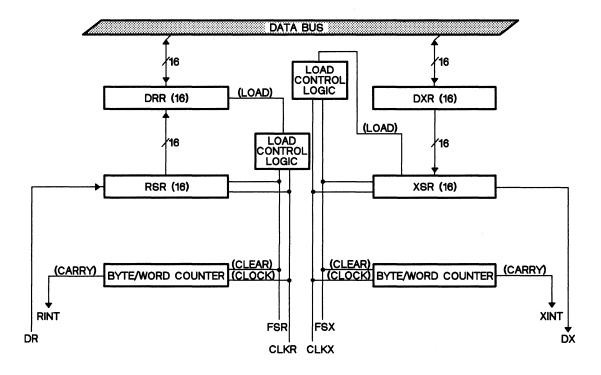

| 3-22.        | Serial Port Block Diagram                                                                                                                                       | 3-37 |

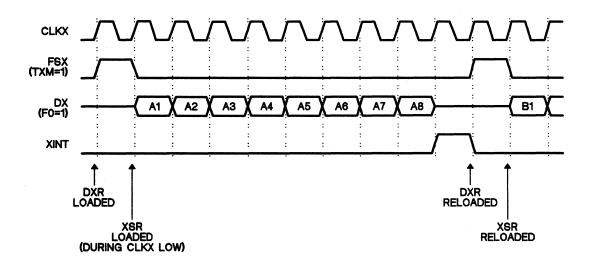

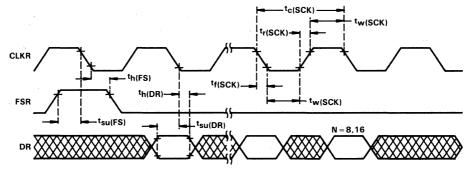

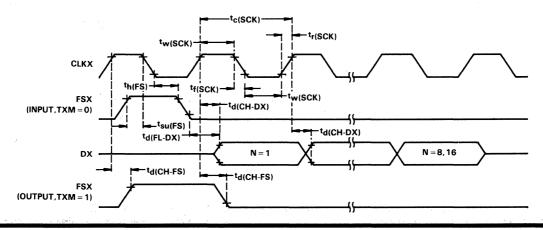

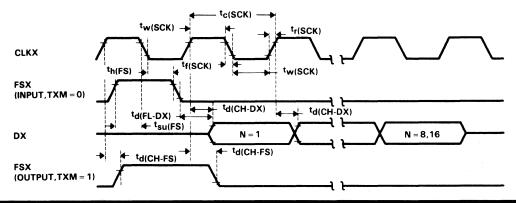

| 2 22.        | Burst-Mode Serial Port Transmit Operation                                                                                                                       | 2 20 |

|              |                                                                                                                                                                 |      |

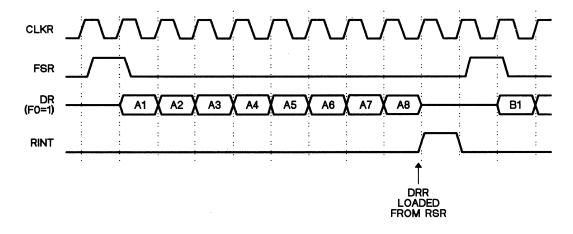

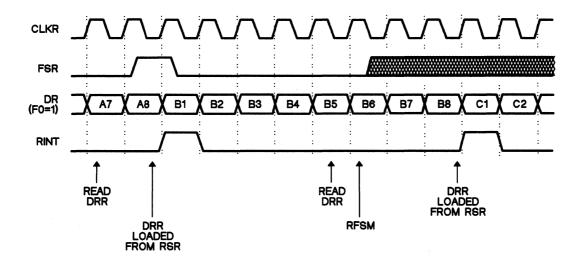

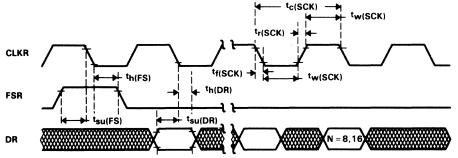

| 3-25.        | Burst-Mode Serial Port Receive Operation                                                                                                                        | 3-39 |

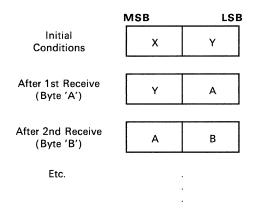

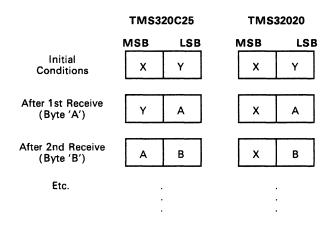

|              | Byte-Mode DRR Operation                                                                                                                                         |      |

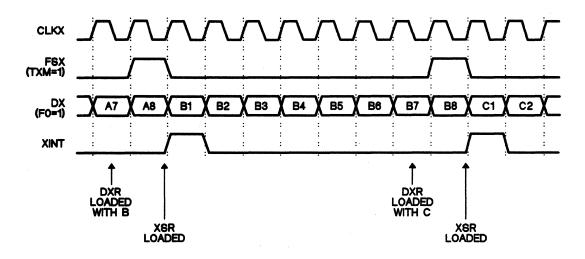

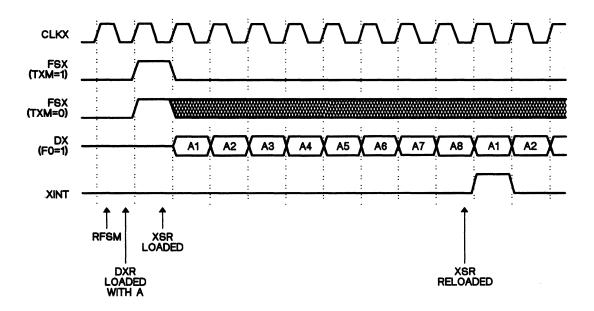

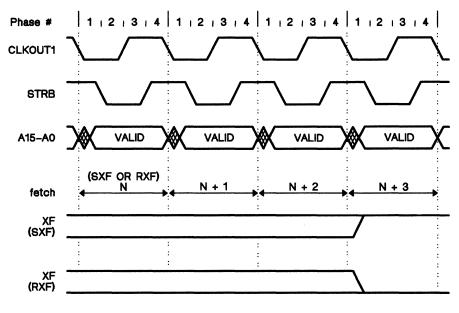

|              | Serial Port Transmit Continuous Operation (FSM=1)                                                                                                               |      |

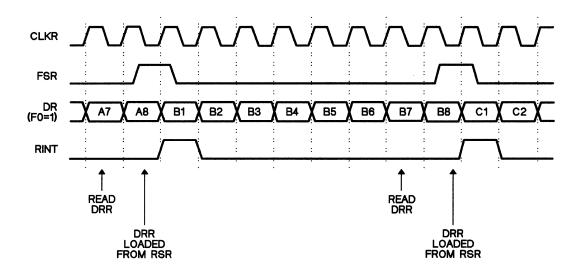

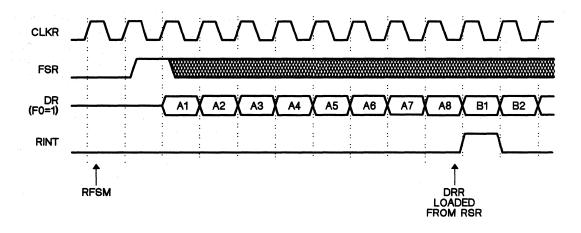

| 3-28.        | Serial Port Receive Continuous Operation (FSM=1)                                                                                                                | 3-41 |

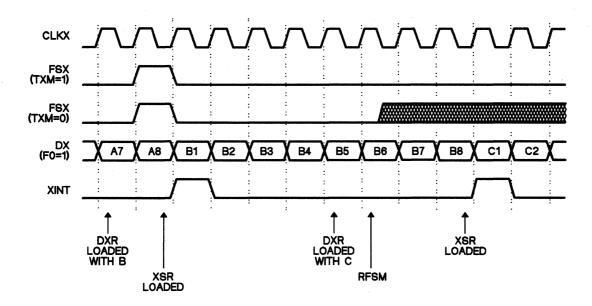

| 3-29.        | Serial Port Transmit Continuous Operation (FSM=0)         Serial Port Receive Continuous Operation (FSM=0)         Continuous Transmit Operation Initialization | 3-42 |

| 3-30.        | Serial Port Receive Continuous Operation (FSM=0)                                                                                                                | 3-42 |

| 3-31.        | Continuous Transmit Operation Initialization                                                                                                                    | 3-43 |

| 3-32.        | Continuous Receive Operation Initialization                                                                                                                     | 3-44 |

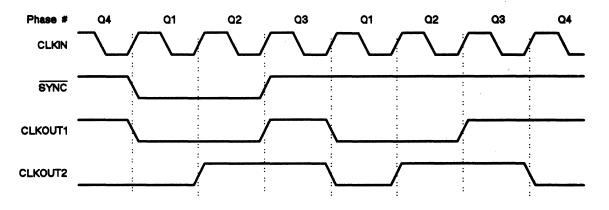

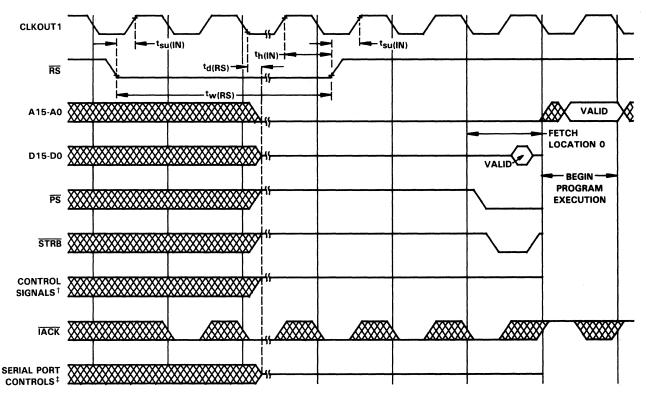

|              | Synchronization Timing Diagram                                                                                                                                  |      |

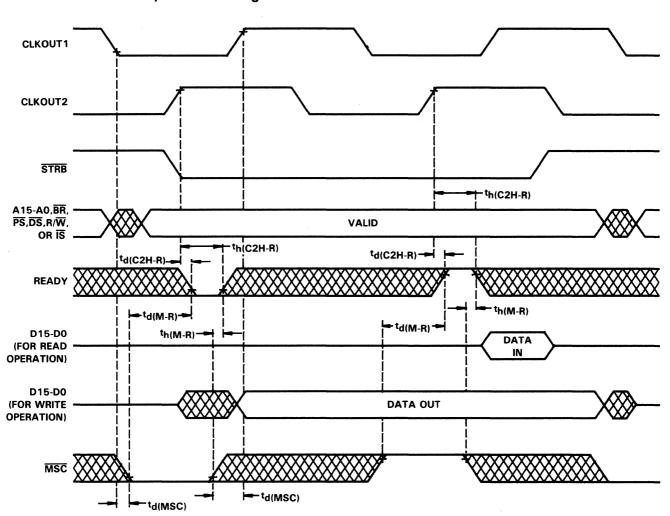

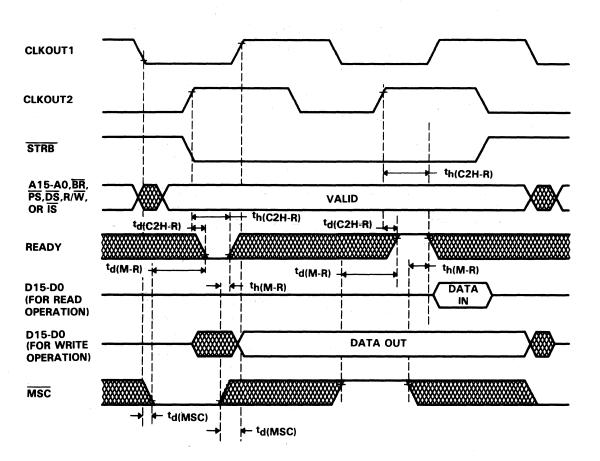

|              | Global Memory Access Timing                                                                                                                                     |      |

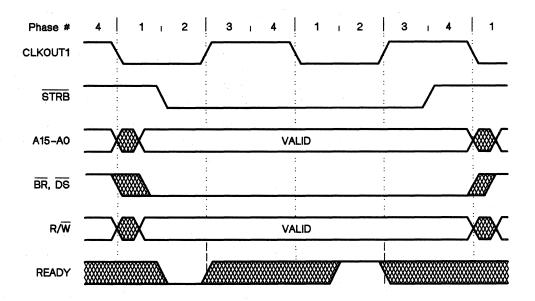

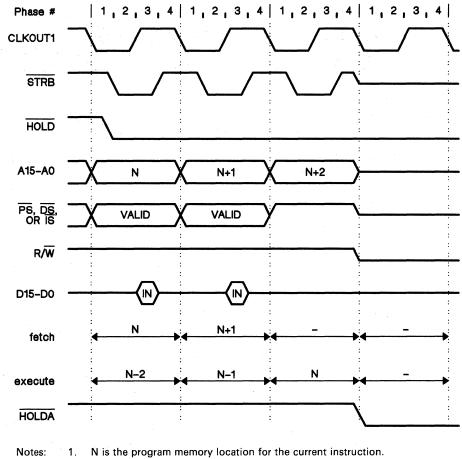

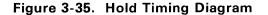

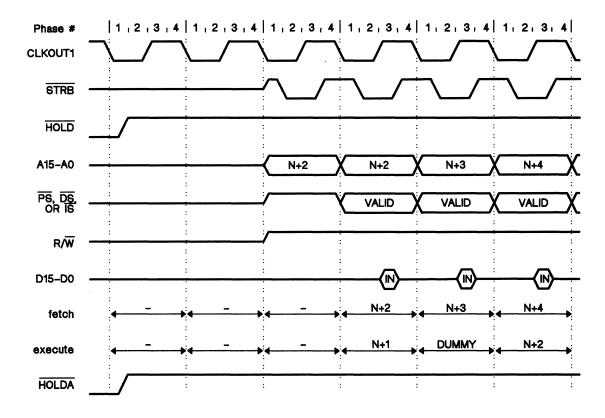

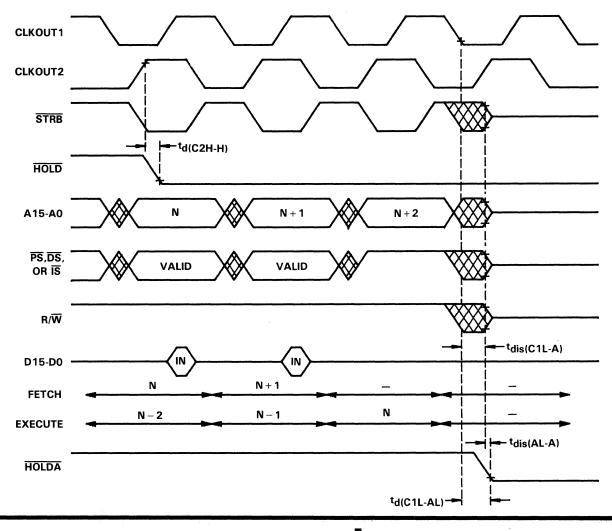

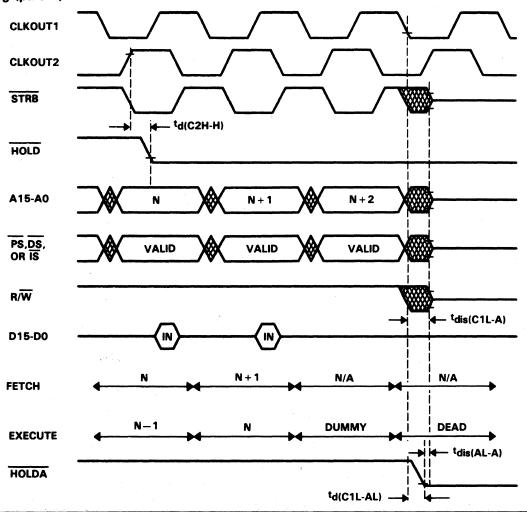

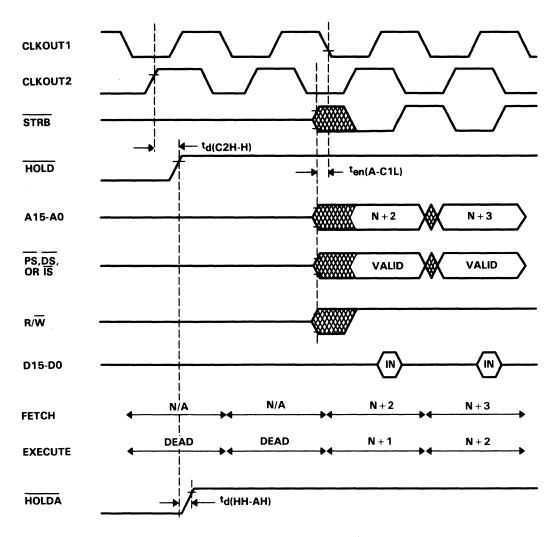

|              | Hold Timing Diagram                                                                                                                                             |      |

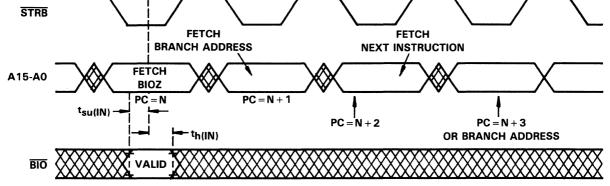

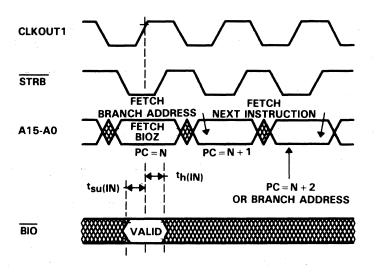

|              | BIO Timing Diagram                                                                                                                                              |      |

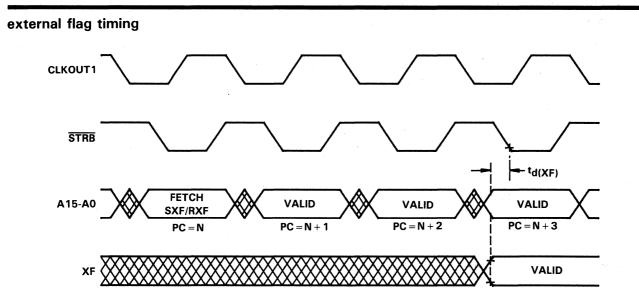

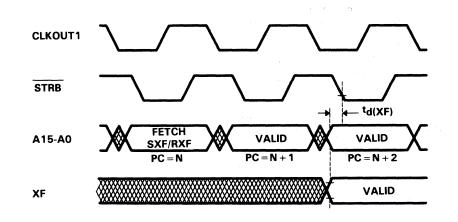

|              | External Flag Timing Diagram                                                                                                                                    |      |

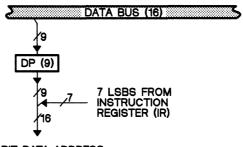

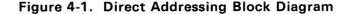

| 4-1.         |                                                                                                                                                                 |      |

|              | Direct Addressing Block Diagram                                                                                                                                 |      |

| 4-2.         | Indirect Addressing Block Diagram                                                                                                                               | 4-3  |

| 5-1.         | On-Chip RAM Configurations                                                                                                                                      | 5-18 |

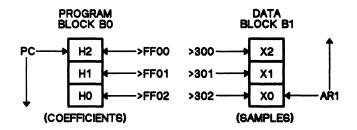

| 5-2.         | MACD Operation                                                                                                                                                  |      |

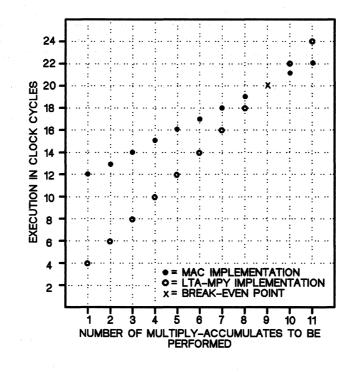

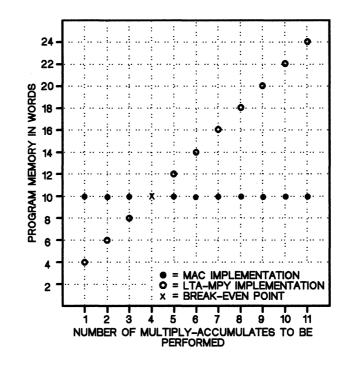

| 5-3.         | Execution Time vs. Number of Multiply-Accumulates                                                                                                               |      |

| 5-4.         | Program Memory vs. Number of Multiply-Accumulates                                                                                                               |      |

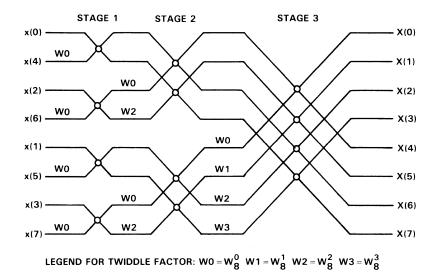

| 5-5.         | An In-Place DIT FFT with In-Order Outputs and Bit-Reversed Inputs                                                                                               | 5-47 |

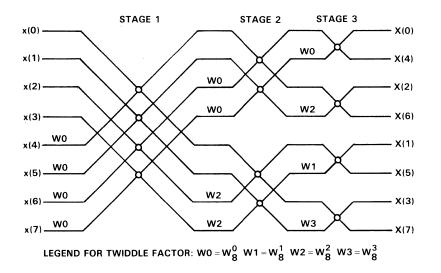

| 5-6.         | An In-Place DIT FFT with In-Order Inputs but Bit-Reversed Outputs                                                                                               |      |

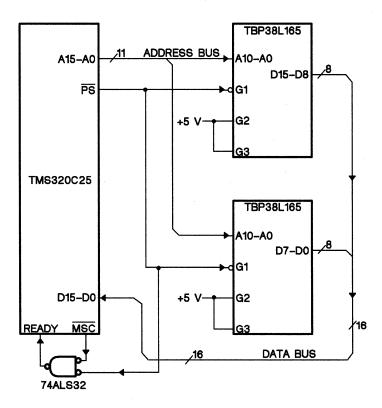

| 6-1.         | Minimal External Program Memory Configuration                                                                                                                   | 6-2  |

|              |                                                                                                                                                                 |      |

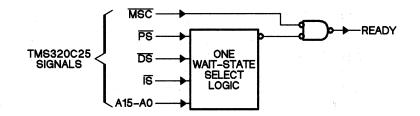

| One Wait-State Generator Using MSC                      | 6-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

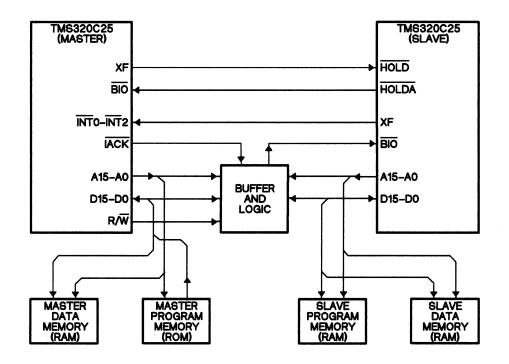

| Direct Memory Access Using a Master-Slave Configuration | 0-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

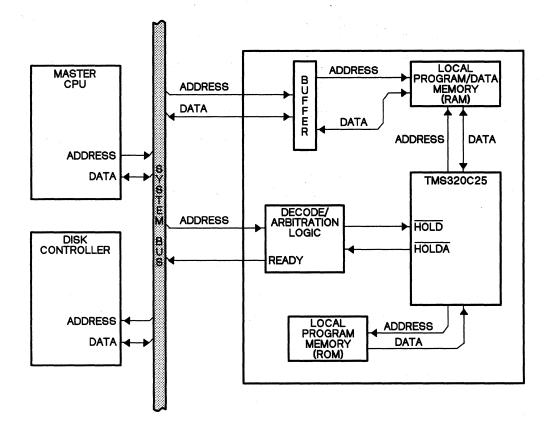

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

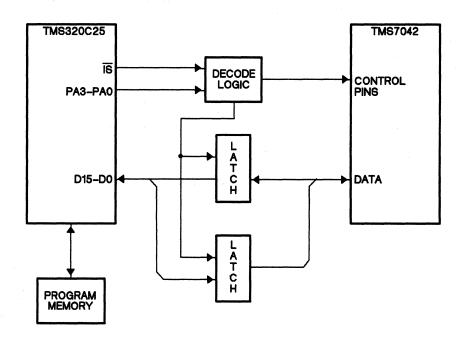

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Sample Object Code                                      | 7-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

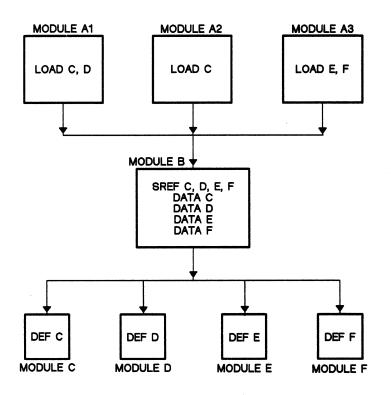

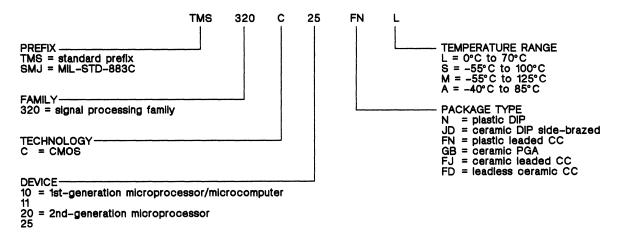

|                                                         | One Wait-State Memory Access Timing<br>One Wait-State Generator Using MSC<br>Direct Memory Access Using a Master-Slave Configuration<br>Direct Memory Access in a PC Environment<br>Global Memory Communication<br>Codec Interface<br>I/O Port Addressing<br>I/O Port Processor-to-Processor Communication<br>Source Statement Line Example<br>Sample Object Code<br>Cross-Reference Listing Format<br>Source for Module MAIN<br>Source for Module MAIN<br>Source for Module INTRPT<br>Listing File for a Simple Link<br>Listing File for a Simple Link<br>Listing File for a Simple Link<br>Listing and Object Files for a Partial Link<br>Listing and Object Files for Relinking the Partial Link Output<br>Source File for Sequential Library Creation<br>Serial Port System Migration<br>TMS320 Family Development Support<br>TMS320 Nomenclature |

Page

## **Tables**

#### Table

| 1-4  |

|------|

| 2-5  |

|      |

| 2-17 |

| 2-18 |

| 3-3  |

| 3-9  |

| 3-17 |

| 3-23 |

| 3-32 |

|      |

| 4-5  |

| 4-5  |

|      |

| 4-10 |

| 5-48 |

| 5-54 |

| 7-8  |

|      |

|      |

| 7-10 |

| 7-11 |

|      |

|      |

|      |

|      |

|      |

|      |

viii

| 7-11. | Fatal Error Listing                                     | 7-53 |

|-------|---------------------------------------------------------|------|

|       | Assembly Information Message Listing                    |      |

| 8-1.  | Variable Qualifiers                                     | 8-7  |

| 8-2.  | Variable Qualifiers for Symbol Components               | 8-8  |

| 8-3.  | Symbol Attribute Component Keywords                     | 8-10 |

| 8-4.  | Parameter Attribute Component Keywords                  | 8-11 |

| 8-5.  | Macro Error Messages                                    | 8-20 |

| 9-1.  | Linker Syntax Symbols                                   | 9-5  |

| 9-2.  | Linker Command Set Summary                              | 9-6  |

| E-1.  | TMS320C25 Instructions by Cycle Class                   | E-1  |

| E-2.  | Cycle Timings for Cycle Classes When Not in Repeat Mode | E-2  |

| E-3.  | Cycle Timings for Cycle Classes When in Repeat Mode     | E-4  |

ł

x

,

## 1. Introduction

The TMS320C25 Digital Signal Processor is a member of the TMS320 family of VLSI digital signal processors and peripherals. The TMS320 family supports realtime digital signal processing (DSP) and computation-intensive applications in the areas of telecommunications, modems, speech processing, graphics/image processing, spectrum analysis, audio processing, digital filtering, high-speed control, instrumentation, and numeric processing.

The architectural investment made in the TMS320 family provides the user with a choice of five distinct processors (TMS32010, TMS320C10, TMS32011, TMS32020, TMS320C25) to best support a wide spectrum of DSP applications. Software compatibility is maintained throughout the family to protect the user's investment in the architecture. Each processor has software and hardware tools to facilitate rapid design.

The first processor in the TMS320 family is the TMS32010, a microcomputer with a 32-bit internal Harvard architecture and a 16-bit external interface capable of executing five million instructions per second. The TMS32020 is the next processor in the family with an architecture based on that of the TMS32010. Major architectural changes made on the TMS32020 enable the device to lower system cost and improve throughput by two to three times over the TMS32010 for DSP applications. The TMS32020 instruction set is a superset of that of the TMS32010, thus maintaining software compatibility.

The TMS320C25 is a pin-compatible CMOS version of the TMS32020 with a faster instruction cycle time and the inclusion of additional hardware and software features. The TMS320C25 is completely object code-compatible with the TMS32020 so that TMS32020 programs run unmodified on the TMS320C25. Some of the major enhancements of the TMS320C25 over the TMS32020 are as follows:

- Faster instruction cycle time: 100 ns

- Low-power CMOS technology with powerdown mode

- 4K words of on-chip masked ROM

- Eight auxiliary registers with a dedicated arithmetic unit

- Eight-level hardware stack

- Fully static double-buffered serial port

- Concurrent DMA using an extended hold operation

- Bit-reversed addressing modes for radix-2 FFTs

- Extended-precision arithmetic and adaptive filtering support

- Full-speed operation of MAC/MACD from external memory

- Accumulator carry bit and related instructions

Development tools and applications support are key advantages to using the TMS320C25. Full-speed emulators, software simulators and assemblers, and extensive documentation including over 735 pages of application reports provide for rapid design and development cycles. Texas Instruments regional technology centers, system application engineers, and third-party support are available for DSP education, training, and design.

#### **1.1 General Description**

The TMS320C25 architecture is based upon that of the TMS32020 digital signal processor. The TMS320C25 increases performance of DSP algorithms through a faster instruction cycle time and innovative additions to the TMS320 family architecture. The TMS320C25 is object code-compatible with the TMS32020, thus enabling current TMS32020 programs to run unmodified on the TMS320C25.

Two versions of the TMS320C25 are available to support price and performance requirements for different applications: 100-ns and 125-ns instruction cycle time versions.

The 100-ns instruction cycle time provides double the throughput for existing applications. Since most instructions are capable of executing in a single cycle, the processor is capable of executing ten million instructions per second (10 MIPS). Increased throughput on the TMS320C25 for many DSP applications is attained by means of single-cycle multiply/accumulate instructions with a data move option, eight auxiliary registers with a dedicated arithmetic unit, instruction set support for adaptive filtering and extended-precision arithmetic, bit-reversal addressing, and faster I/O necessary for data-intensive signal processing.