and a

## TI486SXLC and TI486SXL Microprocessors

# Reference Guide

PC Systems Logic Products

1994

## TI486SXLC and TI486SXL Microprocessors

**Reference Guide**

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1994, Texas Instruments Incorporated

#### Preface

### **Read This First**

#### About This Manual

This manual describes the TI486SXL(C) microprocessor product family. Each chapter except for chapters 3 and 4 cover all versions of the microprocessors. both the TI486SXLC and the TI486SXL. Chapter 3 explicitly covers the TI486SXLC series and chapter 4 explicitly covers the TI486SXL series. This document contains the following chapters:

#### Chapter 1 Product Overview

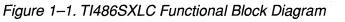

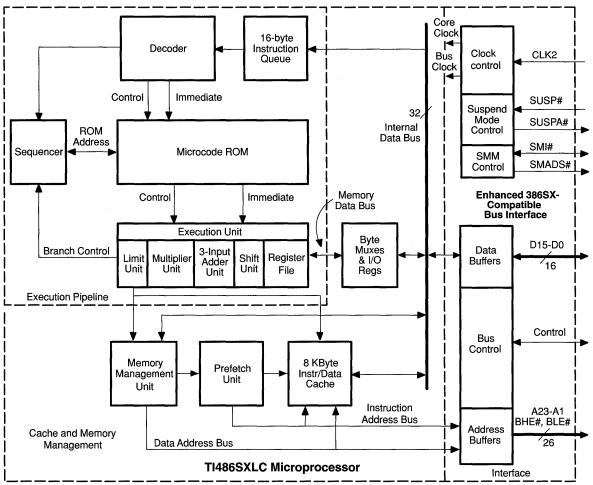

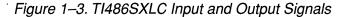

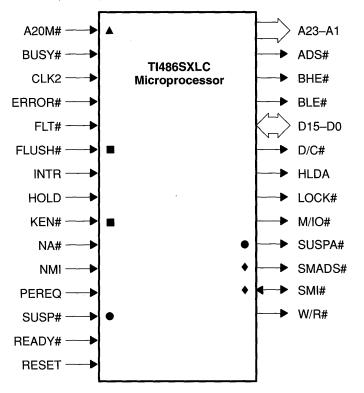

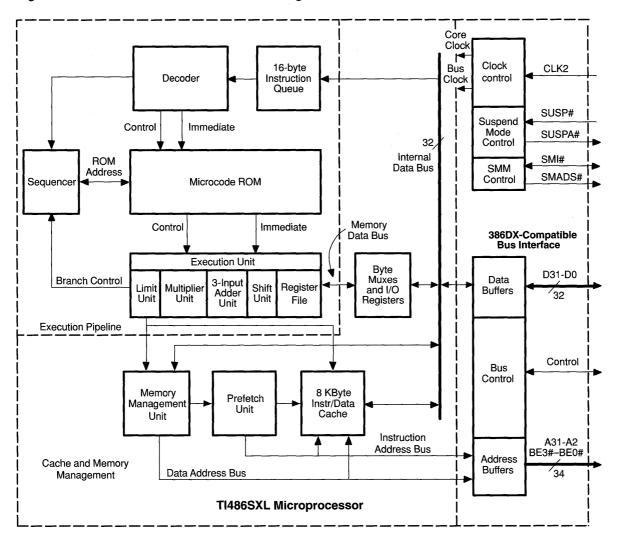

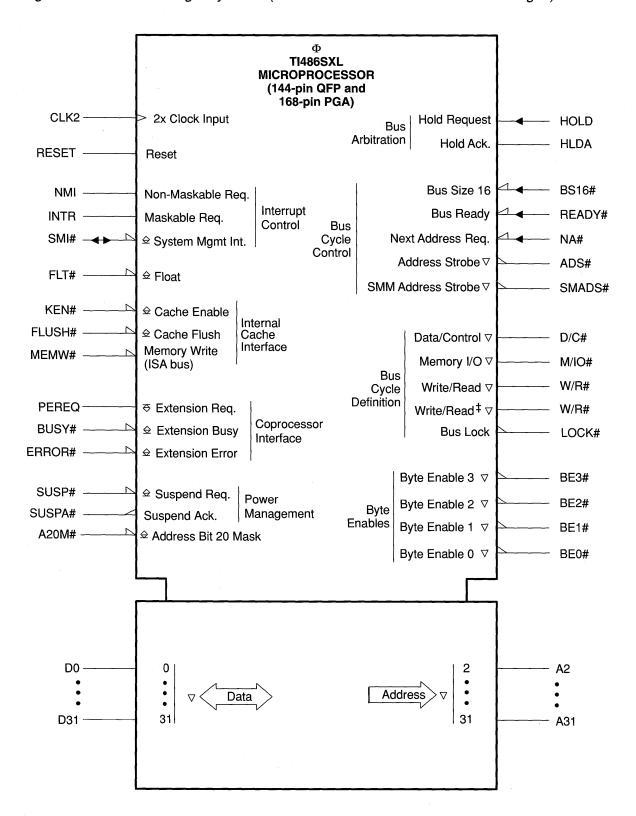

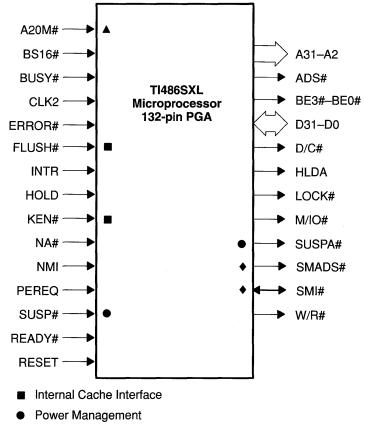

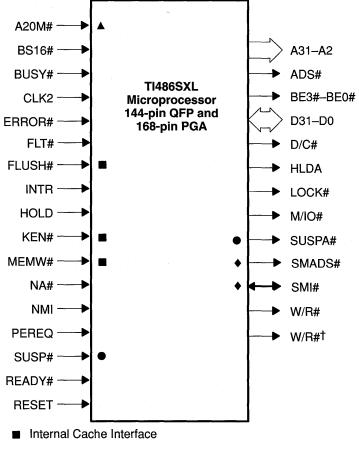

Chapter 1 introduces the features of the TI486SXLC and TI486SXL microprocessor series and defines the differences between them. Each series offers a 3.3-volt version (TI486SXLC–V and TI486SXL–V) for battery-powered applications. A functional block diagram, logic symbol, and I/O signal identifications are provided for each of the two series of microprocessors. Additional material describes selected system architectures such as the execution pipeline, the on-chip cache memory, and the power-management techniques. The system-management mode (SMM) permits the TI486SXL(C) family of microprocessors to respond to and service interrupts with a higher priority than standard 486 processors.

#### Chapter 2 Programming Interface

Chapter 2 describes the internal operations of the TI486SXL(C) family of microprocessors mainly from an application programmer's point of view. Included in this chapter are descriptions of processor initialization, the register sets, memory addressing, various types of interrupts, system-management mode, and the shutdown and halt process. Overviews of real, virtual-8086, and protected operating modes are also included.

#### Chapter 3 TI486SXLC Microprocessor Bus Interface

Chapter 3 provides a summary of the TI486SXLC series processor signals and descriptions of all inputs/outputs, functional timing and bus operations (including pipelined and nonpipelined addressing), various interfaces, and power management.

#### Chapter 4 TI486SXL Microprocessor Bus Interface

Chapter 4 provides a summary of the TI486SXL series processor signals and descriptions of all inputs/outputs, functional timing and bus operations (including pipelined and nonpipelined addressing), various interfaces, and power management.

#### Chapter 5 Electrical Specifications

Chapter 5 provides electrical specifications for the TI486SXL(C) family, including specifications for the 3.3-volt versions. The specifications include electrical connection requirements for all package pins, maximum ratings, recommended operating conditions, dc electrical characteristics, and ac characteristics.

#### Chapter 6 Mechanical Specifications

Chapter 6 provides mechanical specifications for the TI486SXL(C) family that include pin assignments, package physical dimensions, and package thermal characteristics.

#### Chapter 7 Instruction Set

Chapter 7 summarizes the instruction set for the TI486SXL(C) family and provides detailed information of the instruction encoding. The instruction set is the same for all TI486SXL(C) microprocessors. Instructions are listed in an instruction set summary table that provides information on the flags affected and the instruction clock counts for each instruction.

#### Appendix A SMM Programmer's Guide

Appendix A provides detailed information including examples pertinent to programming the TI486SXL(C) system management mode (SMM). Included are system-management interrupt (SMI) examples, testing/debugging SMM code, power management features, loading SMM programs, detection of CPU type, presence of SMM-capable devices, creating macros, and altering SMM code limits.

#### Appendix B BIOS Modifications Guide

Appendix B discusses some BIOS changes that may need to be considered by the PC designer. The areas considered are power-on and hard reset, protected-mode to real-mode switching, and soft reset. Examples of assembler code for turning the cache on and off are provided.

#### Appendix C Design Considerations and Cache Flush

Appendix C provides design considerations, address bit A20 masking, and general cache invalidation procedures.

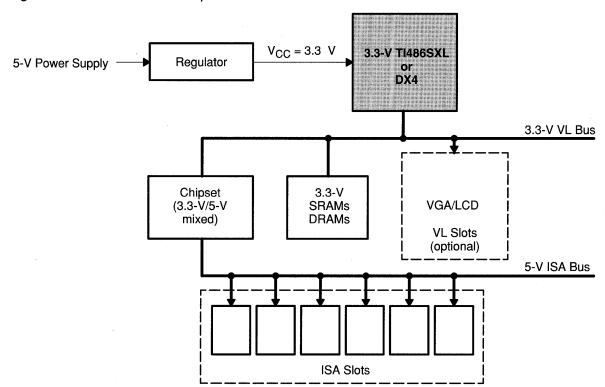

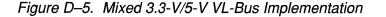

#### Appendix D OEM Modifications for 168-Pin CPGA

Appendix D describes the potential modifications an OEM needs to implement on an existing 486SX/DX/DX4 motherboard to take advantage of the TI486SXL 168 pin CPGA. A system implementation is described for a 3.3-V system that supports a 5-V ISA and a 3.3-V VL bus and another implementation for a mixed 3.3-V/5-V system that supports a 5-V ISA and a 5-V VL bus.

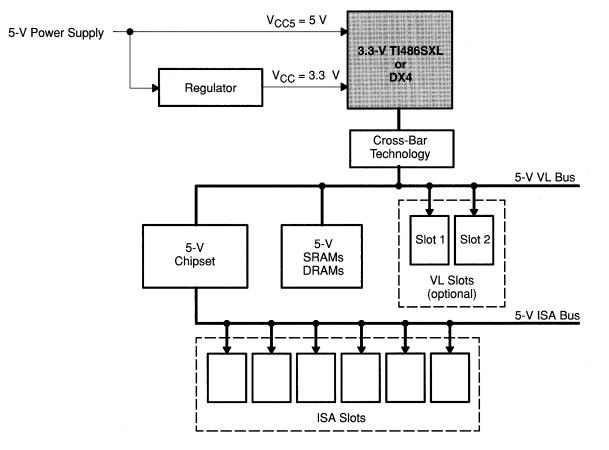

#### Appendix E Thermal Management in Microprocessor-Based Systems

Appendix E provides the reader with basic thermal concepts and the relationship between thermal measurements and the system. In addition, problems associated with comparing thermal specifications from different manufacturers are discussed. Finally, corrective activity within JEDEC is detailed.

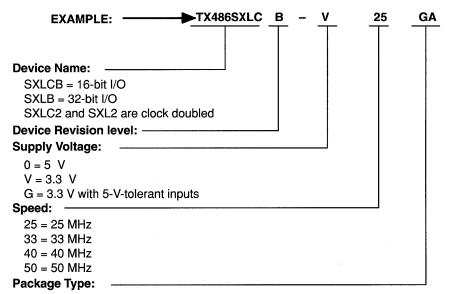

#### Appendix F Ordering Information

Appendix F provides detailed ordering information showing what the components of the part number mean and a description of each microprocessor offered. Versions offered include 5-volt and 3.3-volt versions, each of which are rated to operate at different speeds. The TI486SXLC series devices are packaged in the quad flat pack, and the TI486SXL series devices are packaged in quad flat pack and ceramic PGA packages.

#### Appendix G Glossary

Appendix G contains explanations for the terms, abbreviations, and acronyms used in this manual.

#### Style and Symbol Conventions

This document uses the following conventions.

Program code listings and program code examples are shown in a special typeface similar to a typewriter's.

Here is a sample assembler code program listing:

CLI

MOV EAX, CR0 ; set bit 30, turn off cache OR EAX, 40000000h ; for external cache coherency

In the instruction syntax descriptions, the instruction is in a **bold typeface** and a description of the instruction is in *italic typeface*. Here is an example of an instruction syntax and description:

RSM Resume from SMM Mode

□ Square brackets ([and]) identify the location and sequence for specifying register and/or memory options in the instruction opcode. Here's an example of an opcode that requires register and memory parameters:

Reference: Instruction ADD Integer Add (Register to Memory)

Opcode = 0 [000w] [mod reg r/m]

#### Information About Cautions and Warnings

This book may contain cautions and warnings.

The information in a caution or a warning is provided for your protection. Please read each caution and warning carefully.

#### Trademarks

AMD is a trademark of Advanced Micro Devices.

EPIC is a trademark of Texas Instruments Incorporated.

Intel is a trademark of Intel Corp.

## Contents

| 1 | Prod |         | rview                                                           |      |

|---|------|---------|-----------------------------------------------------------------|------|

|   | 1.1  |         | es                                                              |      |

|   | 1.2  |         | ction                                                           |      |

|   | 1.3  |         | SXLC Series Overview                                            |      |

|   | 1.4  |         | SXL Series Overview                                             |      |

|   | 1.5  |         | nces Between the TI486SXLC Series and TI486SXL Series           |      |

|   | 1.6  | Differe | nces Between the TI486SXL(C) Family and the TI486SLC/DLC Family | 1-16 |

|   | 1.7  | Execut  | ion Pipeline                                                    | 1-17 |

|   | 1.8  | On-Ch   | ip Cache                                                        | 1-17 |

|   | 1.9  | Clock-I | Doubled Mode                                                    | 1-18 |

|   | 1.10 | Power   | Management                                                      | 1-18 |

|   |      | 1.10.1  | System-Management Mode (SMM)                                    | 1-18 |

|   |      | 1.10.2  | Suspend Mode and Static Operation                               | 1-18 |

|   |      | 1.10.3  | 3.3-V Operation                                                 | 1-19 |

|   |      | 1.10.4  | Mixed 3.3-V and 5-V Operation                                   | 1-19 |

| • | _    |         |                                                                 |      |

| 2 |      |         | g Interface                                                     |      |

|   | 2.1  |         | sor Initialization                                              |      |

|   | 2.2  |         | lode Versus Protected Mode                                      |      |

|   | 2.3  |         | tion-Set Overview                                               |      |

|   |      | 2.3.1   |                                                                 |      |

|   |      | 2.3.2   | Register Sets                                                   |      |

|   |      | 2.3.3   | Address Spaces                                                  |      |

|   | 2.4  |         | ation Register Set                                              |      |

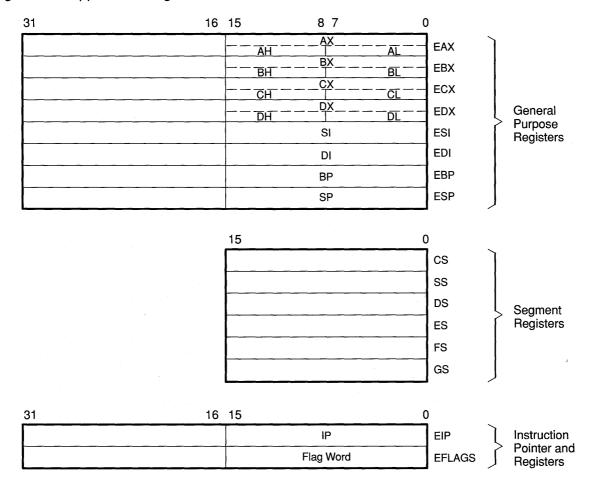

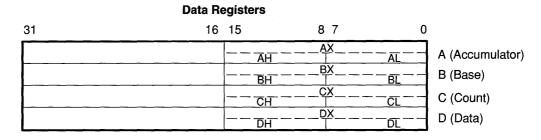

|   |      | 2.4.1   | General Purpose Registers                                       |      |

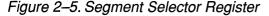

|   |      | 2.4.2   | Segment Registers and Selectors                                 |      |

|   |      | 2.4.3   | Instruction Pointer Register                                    |      |

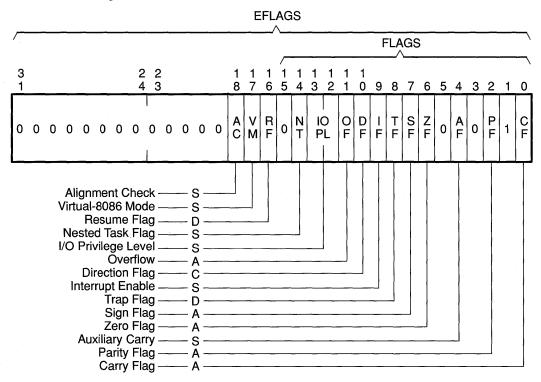

|   |      | 2.4.4   | Flag Word Register                                              |      |

|   | 2.5  | •       | n Register Set                                                  |      |

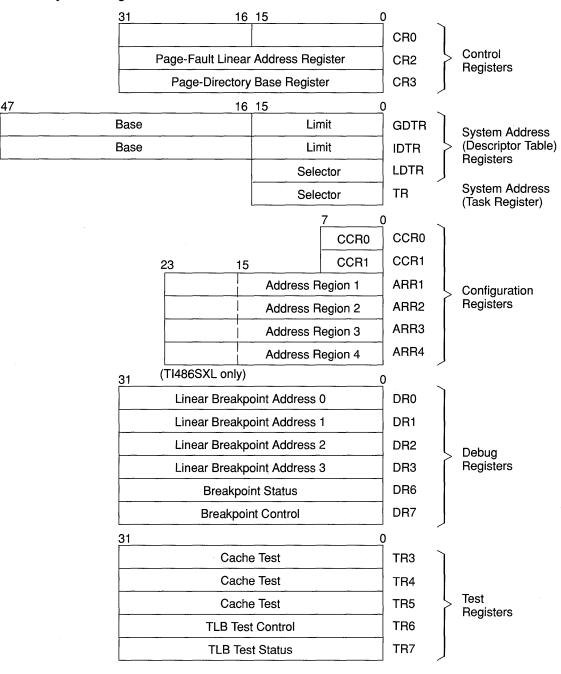

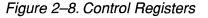

|   |      | 2.5.1   | Control Registers                                               |      |

|   |      | 2.5.2   | Descriptor-Registers and Descriptors                            |      |

|   |      | 2.5.3   | Task Register                                                   |      |

|   |      | 2.5.4   | Configuration Registers                                         |      |

|   |      | 2.5.5   | Debug Registers                                                 |      |

|   |      | 2.5.6   | Test Registers                                                  |      |

|   | 2.6  |         | y Address Space                                                 |      |

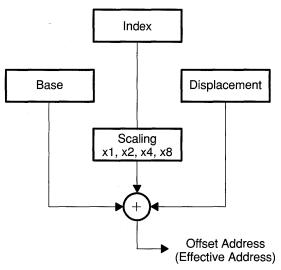

|   |      | 2.6.1   | Offset Mechanism                                                | 2-37 |

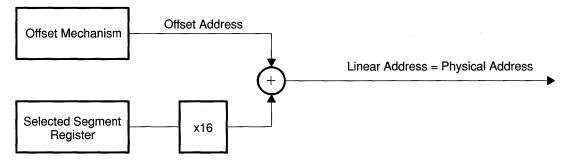

|   |      | 2.6.2   | Real-Mode Memory Addressing                                     |      |

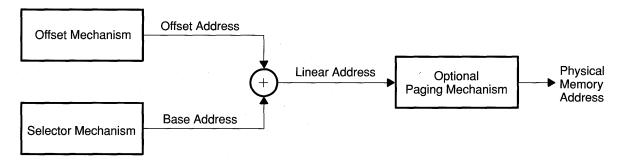

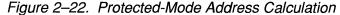

|   |      | 2.6.3   | Protected-Mode Memory Addressing                                | 2-39 |

|   | 2.7        | Interru                                                                                                             | pts and Exceptions                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-43                                                                                                         |

|---|------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

|   |            | 2.7.1                                                                                                               | Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-43                                                                                                         |

|   |            | 2.7.2                                                                                                               | Exceptions                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-44                                                                                                         |

|   |            | 2.7.3                                                                                                               | Interrupt Vectors                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-45                                                                                                         |

|   |            | 2.7.4                                                                                                               | Interrupt and Exception Priorities                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-46                                                                                                         |

|   |            | 2.7.5                                                                                                               | Exceptions in Real Mode                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-47                                                                                                         |

|   |            | 2.7.6                                                                                                               | Error Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-48                                                                                                         |

|   | 2.8        | System                                                                                                              | n-Management Mode                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-49                                                                                                         |

|   |            | 2.8.1                                                                                                               | SMM Operations                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                              |

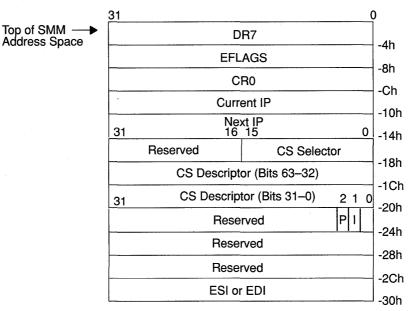

|   |            | 2.8.2                                                                                                               | SMM Memory Space Header                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                              |

|   |            | 2.8.3                                                                                                               | SMM Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                              |

|   |            | 2.8.4                                                                                                               | SMM Memory Space                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                              |

|   |            | 2.8.5                                                                                                               | SMI Service Routine Execution                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                              |

|   |            | 2.8.6                                                                                                               | CPU States Related to SMM and Suspend Mode                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                              |

|   | 2.9        |                                                                                                                     | own and Halt                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                              |

|   | 2.10       |                                                                                                                     | tion                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                              |

|   | 2.10       | 2.10.1                                                                                                              | Privilege Levels                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                              |

|   |            | 2.10.1                                                                                                              | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                              |

|   |            | 2.10.2                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                              |

|   |            | 2.10.3                                                                                                              | •                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                              |

|   | 2.11       | -                                                                                                                   | -8086 Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                              |

|   | 2.11       |                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                              |

|   |            | 2.11.1                                                                                                              | Memory Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                              |

|   |            | 2.11.2                                                                                                              | Protection                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                              |

|   |            | 2.11.3                                                                                                              | Interrupt Handling                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                              |

|   |            | 2.11.4                                                                                                              | Entering and Leaving V86 Mode                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-61                                                                                                         |

| 3 | TI486      | SXLC N                                                                                                              | Aicroprocessor Bus Interface                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 3-1                                                                                                        |

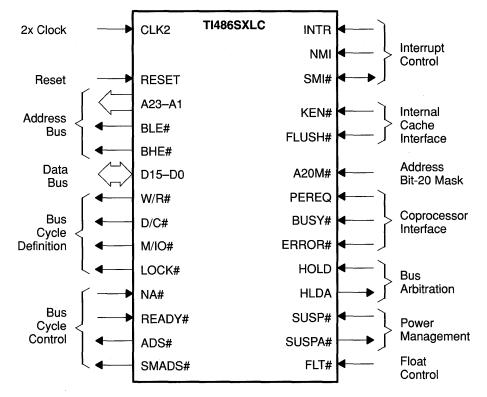

|   | 3.1        | Input/C                                                                                                             | Dutput Signals                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 3-2                                                                                                        |

|   |            | 3.1.1                                                                                                               | TI486SXLC Terminal Function Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                     | . 3-4                                                                                                        |

|   |            | 3.1.2                                                                                                               | Signal States During Reset and Hold Acknowledge                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                              |

|   | 3.2        | Bus-Cy                                                                                                              | ycle Definition                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                              |

|   |            |                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                              |

|   |            | 3.2.1                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                              |

|   |            | 3.2.1<br>3.2.2                                                                                                      | Clock Doubling Using Software Control                                                                                                                                                                                                                                                                                                                                                                                                                        | 3-13                                                                                                         |

|   | 3.3        | 3.2.2                                                                                                               | Clock Doubling Using Software Control                                                                                                                                                                                                                                                                                                                                                                                                                        | 3-13<br>3-15                                                                                                 |

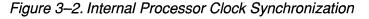

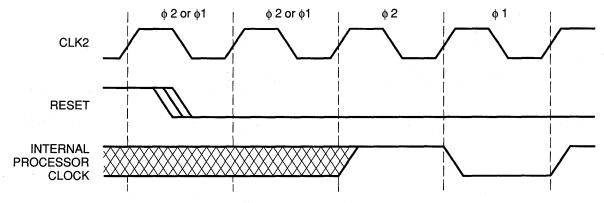

|   | 3.3<br>3.4 | 3.2.2<br>Reset                                                                                                      | Clock Doubling Using Software Control         Power Management         Timing and Internal Clock Synchronization                                                                                                                                                                                                                                                                                                                                             | 3-13<br>3-15<br>3-17                                                                                         |

|   | 3.3<br>3.4 | 3.2.2<br>Reset<br>Bus Op                                                                                            | Clock Doubling Using Software Control<br>Power Management<br>Timing and Internal Clock Synchronization<br>peration and Functional Timing                                                                                                                                                                                                                                                                                                                     | 3-13<br>3-15<br>3-17<br>3-19                                                                                 |

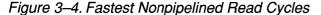

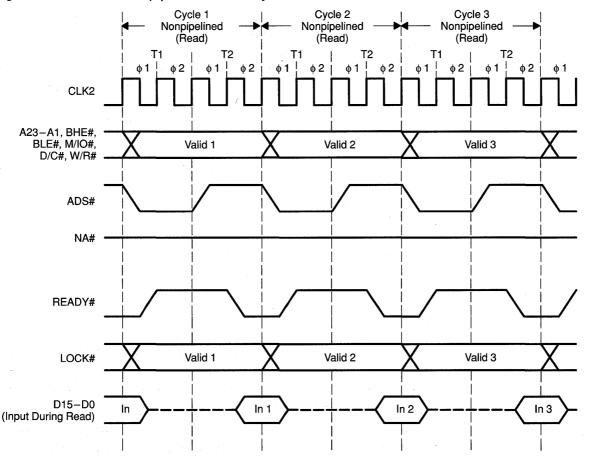

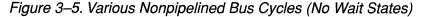

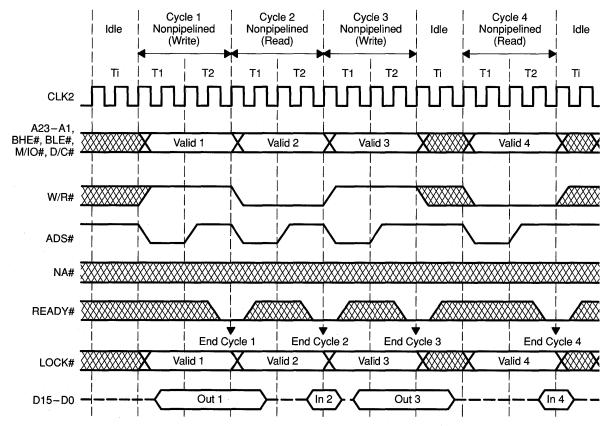

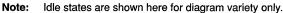

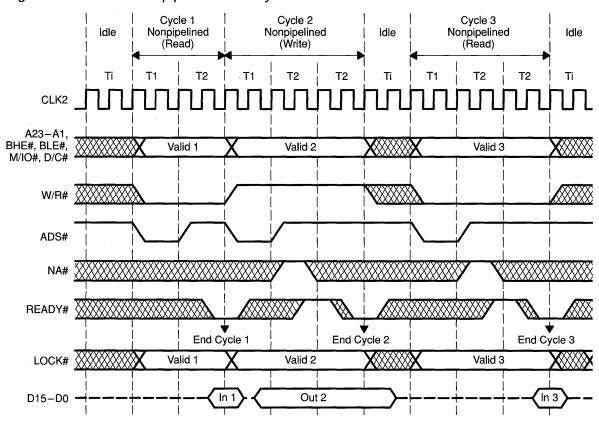

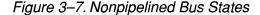

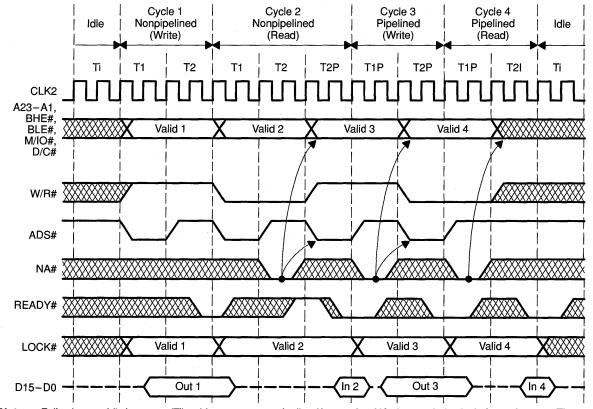

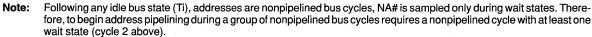

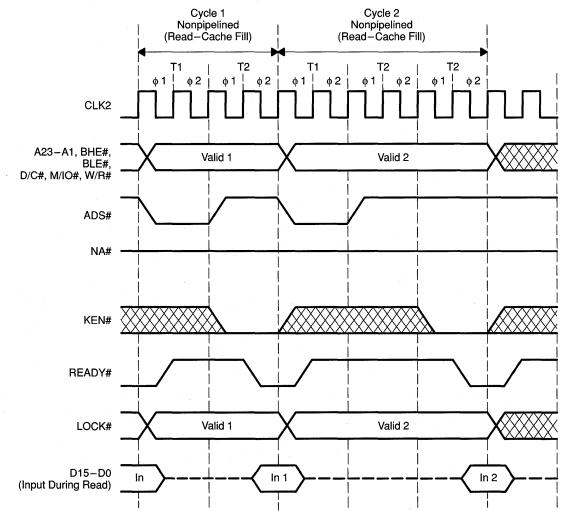

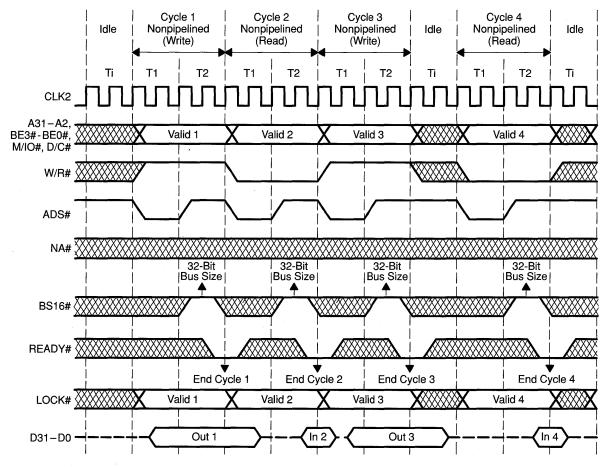

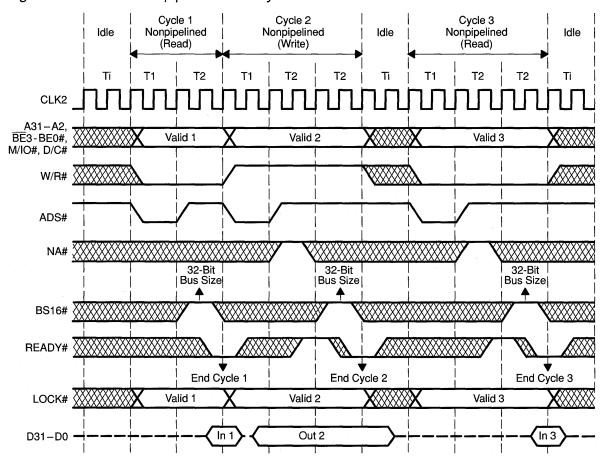

|   |            | 3.2.2<br>Reset<br>Bus Op<br>3.4.1                                                                                   | Clock Doubling Using Software Control<br>Power Management<br>Timing and Internal Clock Synchronization<br>peration and Functional Timing<br>Bus Cycles Using Nonpipelined Addressing                                                                                                                                                                                                                                                                         | 3-13<br>3-15<br>3-17<br>3-19<br>3-20                                                                         |

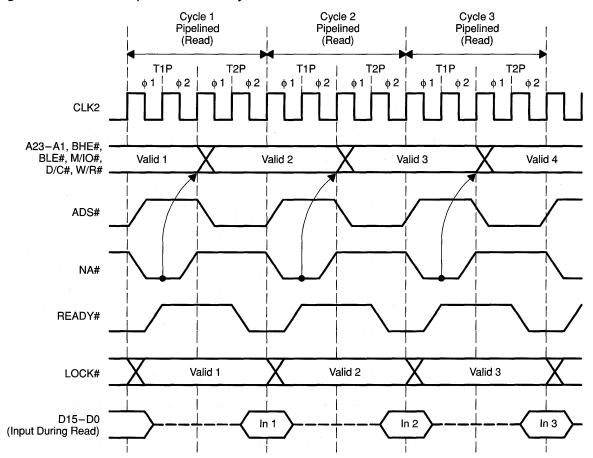

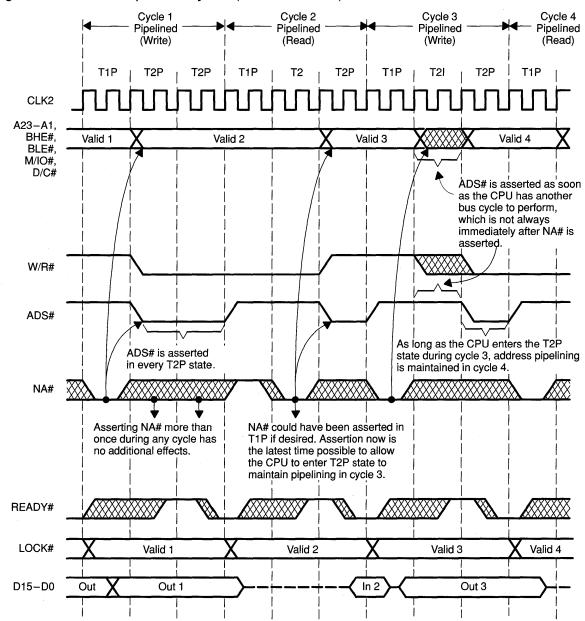

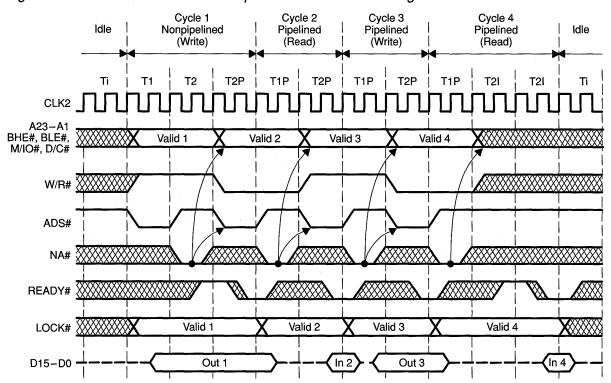

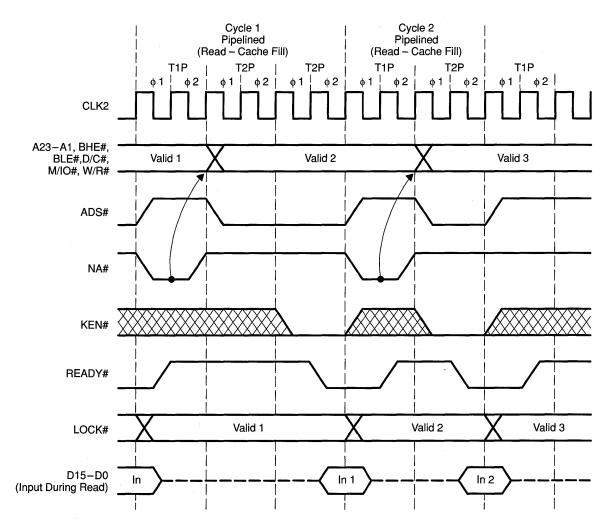

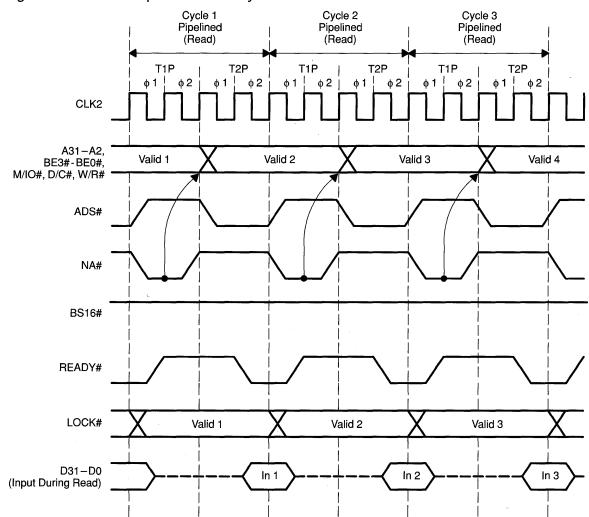

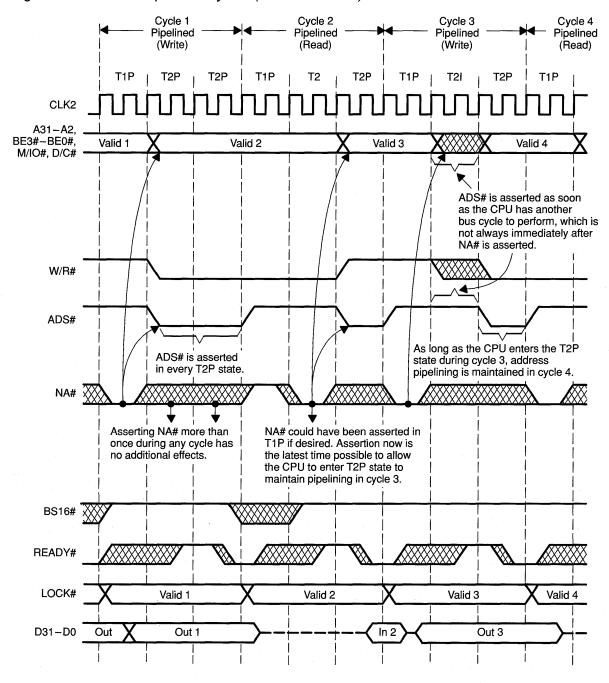

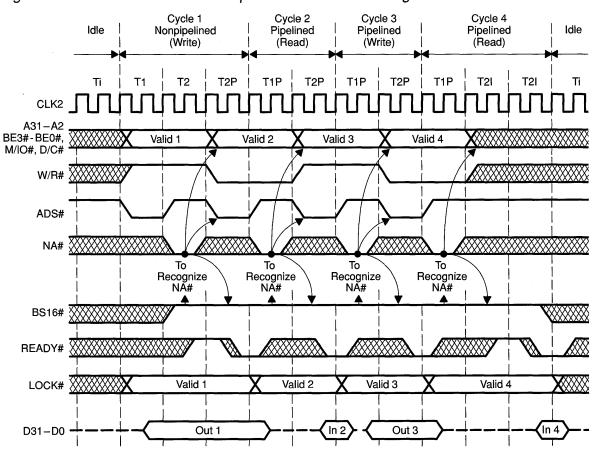

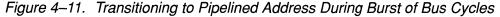

|   |            | 3.2.2<br>Reset<br>Bus Op<br>3.4.1<br>3.4.2                                                                          | Clock Doubling Using Software Control<br>Power Management<br>Timing and Internal Clock Synchronization<br>peration and Functional Timing<br>Bus Cycles Using Nonpipelined Addressing<br>Bus Cycles Using Pipelined Addressing                                                                                                                                                                                                                                | 3-13<br>3-15<br>3-17<br>3-19<br>3-20<br>3-24                                                                 |

|   |            | 3.2.2<br>Reset<br>Bus Op<br>3.4.1<br>3.4.2<br>3.4.3                                                                 | Clock Doubling Using Software Control<br>Power Management<br>Timing and Internal Clock Synchronization<br>peration and Functional Timing<br>Bus Cycles Using Nonpipelined Addressing<br>Bus Cycles Using Pipelined Addressing<br>Locked Bus Cycles                                                                                                                                                                                                           | 3-13<br>3-15<br>3-17<br>3-19<br>3-20<br>3-24<br>3-31                                                         |

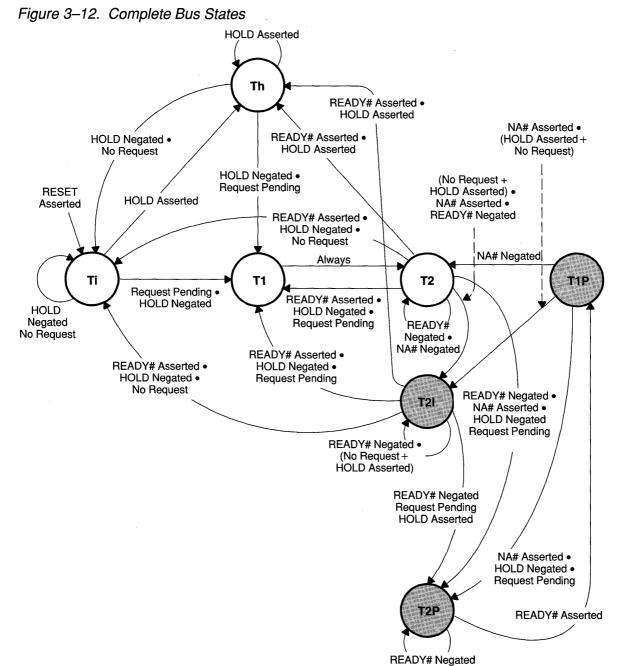

|   |            | 3.2.2<br>Reset<br>Bus Op<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.3                                                        | Clock Doubling Using Software Control<br>Power Management<br>Timing and Internal Clock Synchronization<br>Deration and Functional Timing<br>Bus Cycles Using Nonpipelined Addressing<br>Bus Cycles Using Pipelined Addressing<br>Locked Bus Cycles<br>Interrupt-Acknowledge Cycles                                                                                                                                                                           | 3-13<br>3-15<br>3-17<br>3-19<br>3-20<br>3-24<br>3-31<br>3-31                                                 |

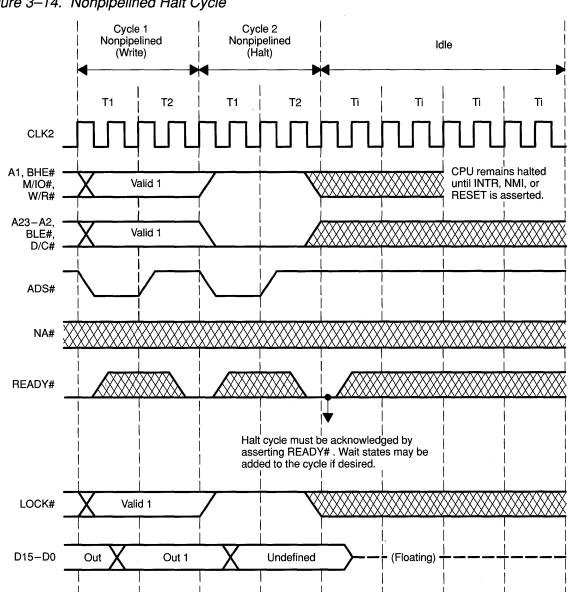

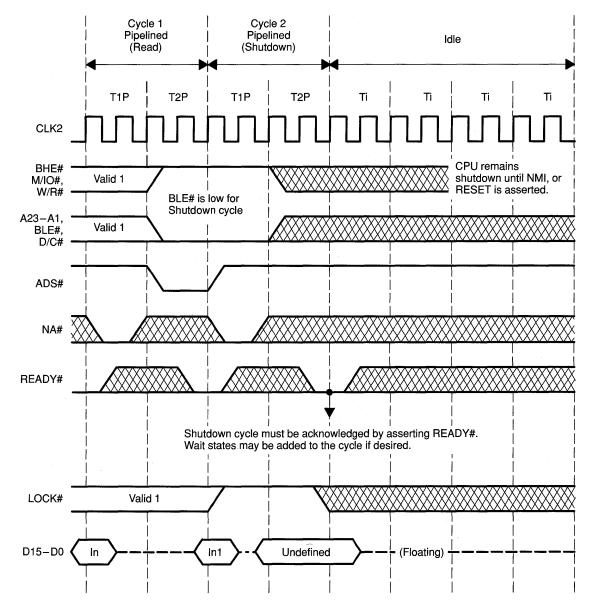

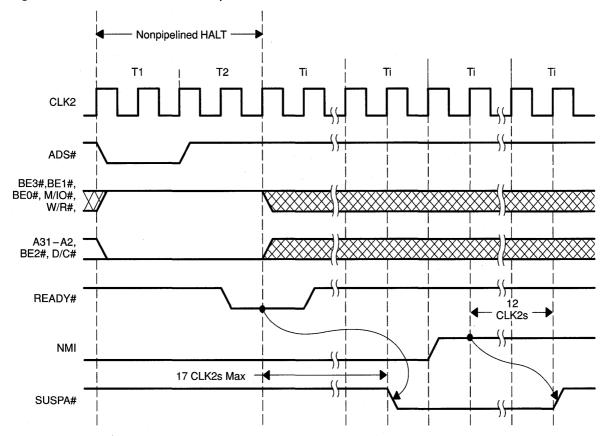

|   |            | 3.2.2<br>Reset<br>Bus Op<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5                                               | Clock Doubling Using Software Control<br>Power Management<br>Timing and Internal Clock Synchronization<br>Deration and Functional Timing<br>Bus Cycles Using Nonpipelined Addressing<br>Bus Cycles Using Pipelined Addressing<br>Locked Bus Cycles<br>Interrupt-Acknowledge Cycles<br>Halt and Shutdown Cycles                                                                                                                                               | 3-13<br>3-15<br>3-17<br>3-20<br>3-24<br>3-31<br>3-31<br>3-33                                                 |

|   |            | 3.2.2<br>Reset<br>Bus Op<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6                                      | Clock Doubling Using Software Control<br>Power Management<br>Timing and Internal Clock Synchronization<br>Deration and Functional Timing<br>Bus Cycles Using Nonpipelined Addressing<br>Bus Cycles Using Pipelined Addressing<br>Locked Bus Cycles<br>Interrupt-Acknowledge Cycles<br>Halt and Shutdown Cycles<br>Internal Cache Interface                                                                                                                   | 3-13<br>3-15<br>3-17<br>3-19<br>3-20<br>3-24<br>3-31<br>3-31<br>3-33<br>3-36                                 |

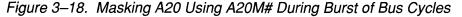

|   |            | 3.2.2<br>Reset<br>Bus Op<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7                             | Clock Doubling Using Software Control<br>Power Management<br>Timing and Internal Clock Synchronization<br>Deration and Functional Timing<br>Bus Cycles Using Nonpipelined Addressing<br>Bus Cycles Using Pipelined Addressing<br>Locked Bus Cycles<br>Interrupt-Acknowledge Cycles<br>Halt and Shutdown Cycles<br>Internal Cache Interface<br>Address Bit-20 Masking                                                                                         | 3-13<br>3-15<br>3-17<br>3-20<br>3-24<br>3-31<br>3-31<br>3-33<br>3-36<br>3-38                                 |

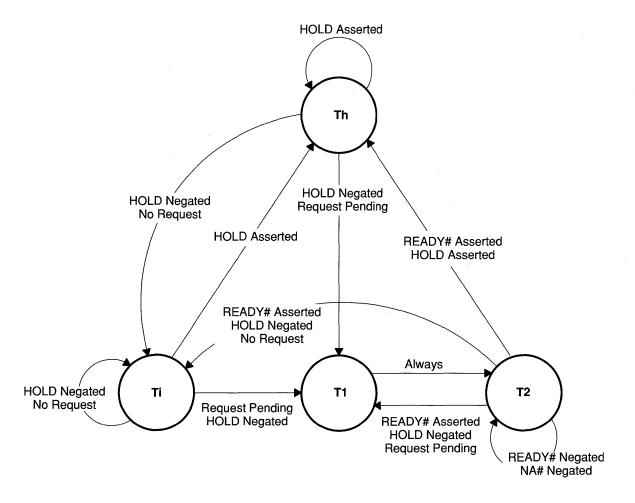

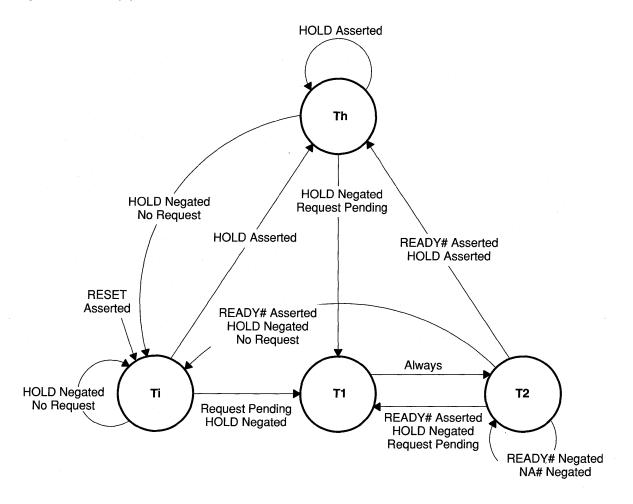

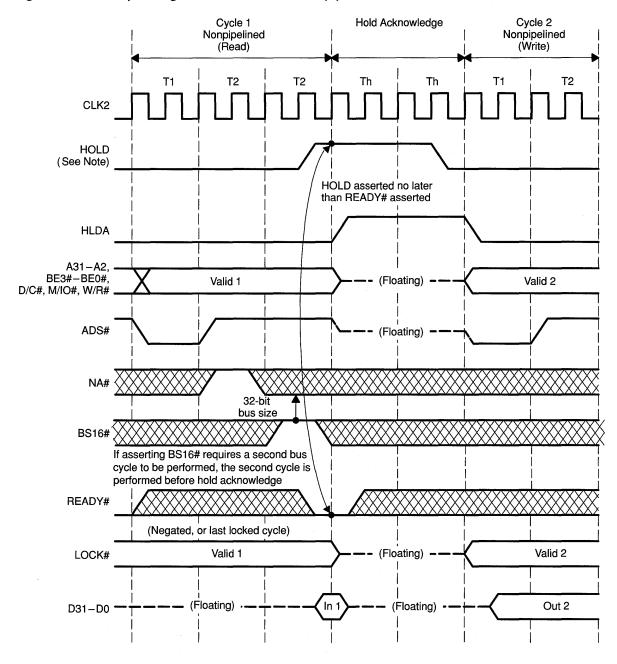

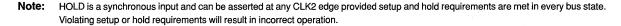

|   |            | 3.2.2<br>Reset<br>Bus Op<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8                    | Clock Doubling Using Software Control<br>Power Management<br>Timing and Internal Clock Synchronization<br>Deration and Functional Timing<br>Bus Cycles Using Nonpipelined Addressing<br>Bus Cycles Using Pipelined Addressing<br>Locked Bus Cycles<br>Interrupt-Acknowledge Cycles<br>Halt and Shutdown Cycles<br>Internal Cache Interface<br>Address Bit-20 Masking<br>Hold-Acknowledge State                                                               | 3-13<br>3-15<br>3-17<br>3-20<br>3-24<br>3-31<br>3-31<br>3-33<br>3-36<br>3-38<br>3-39                         |

|   |            | 3.2.2<br>Reset<br>Bus Op<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9           | Clock Doubling Using Software Control<br>Power Management<br>Timing and Internal Clock Synchronization<br>Deration and Functional Timing<br>Bus Cycles Using Nonpipelined Addressing<br>Bus Cycles Using Pipelined Addressing<br>Locked Bus Cycles<br>Interrupt-Acknowledge Cycles<br>Halt and Shutdown Cycles<br>Internal Cache Interface<br>Address Bit-20 Masking<br>Hold-Acknowledge State<br>Coprocessor Interface                                      | 3-13<br>3-15<br>3-17<br>3-20<br>3-24<br>3-31<br>3-31<br>3-33<br>3-36<br>3-38<br>3-39<br>3-42                 |

|   |            | 3.2.2<br>Reset<br>Bus Op<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9<br>3.4.10 | Clock Doubling Using Software Control<br>Power Management<br>Timing and Internal Clock Synchronization<br>Deration and Functional Timing<br>Bus Cycles Using Nonpipelined Addressing<br>Bus Cycles Using Pipelined Addressing<br>Locked Bus Cycles<br>Interrupt-Acknowledge Cycles<br>Halt and Shutdown Cycles<br>Internal Cache Interface<br>Address Bit-20 Masking<br>Hold-Acknowledge State<br>Coprocessor Interface<br>SMM Interface                     | 3-13<br>3-15<br>3-17<br>3-20<br>3-24<br>3-31<br>3-31<br>3-33<br>3-36<br>3-38<br>3-39<br>3-42<br>3-43         |

|   |            | 3.2.2<br>Reset<br>Bus Op<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9           | Clock Doubling Using Software Control<br>Power Management<br>Timing and Internal Clock Synchronization<br>Deration and Functional Timing<br>Bus Cycles Using Nonpipelined Addressing<br>Bus Cycles Using Pipelined Addressing<br>Locked Bus Cycles<br>Interrupt-Acknowledge Cycles<br>Halt and Shutdown Cycles<br>Internal Cache Interface<br>Address Bit-20 Masking<br>Hold-Acknowledge State<br>Coprocessor Interface<br>SMM Interface<br>Power Management | 3-13<br>3-15<br>3-17<br>3-20<br>3-24<br>3-31<br>3-31<br>3-33<br>3-36<br>3-38<br>3-39<br>3-42<br>3-43<br>3-45 |

| 4 | TI486     | SXL Mi  | croprocessor Bus Interface                                              | 4-1  |

|---|-----------|---------|-------------------------------------------------------------------------|------|

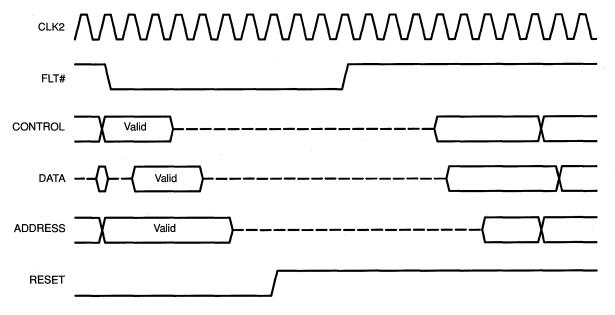

|   | 4.1       | Input/C | Dutput Signals                                                          | 4-2  |

|   |           | 4.1.1   | TI486SXL Terminal Function Descriptions                                 | 4-4  |

|   |           | 4.1.2   | Byte Enable Line Definitions                                            | 4-13 |

|   |           | 4.1.3   | Write Duplication as a Function of BE3# – BE0#                          |      |

|   |           | 4.1.4   | Generating A1 – A0 Using BE3# – BE0#                                    | 4-14 |

|   |           | 4.1.5   | Signal States During Reset and Hold Acknowledge                         | 4-14 |

|   | 4.2       | Bus-Cy  | ycle Definition                                                         | 4-16 |

|   |           | 4.2.1   | Clock Doubling Using Software Control                                   | 4-16 |

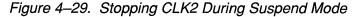

|   |           | 4.2.2   | Power Management                                                        | 4-18 |

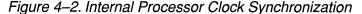

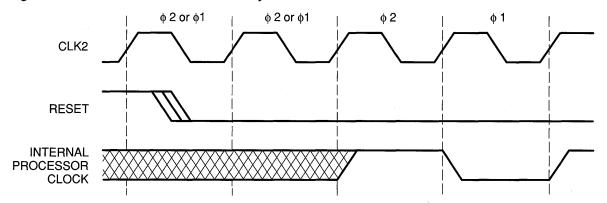

|   | 4.3       | Reset   | Timing and Internal Clock Synchronization                               | 4-20 |

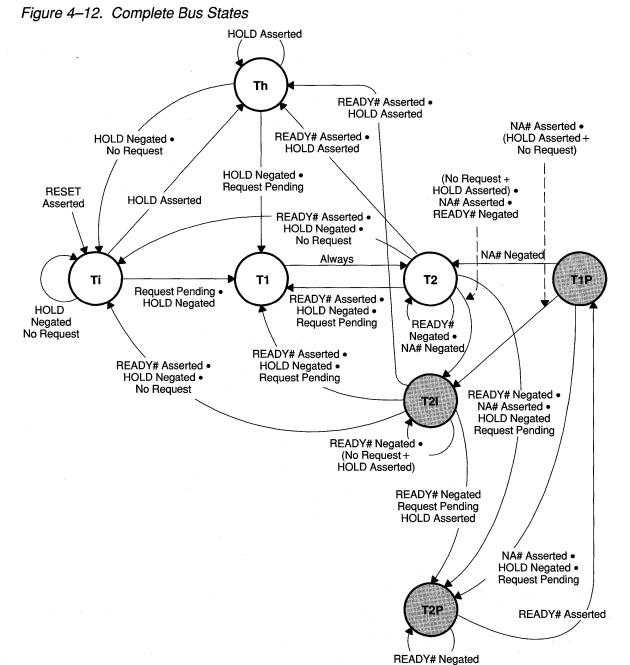

|   | 4.4       | Bus Op  | peration and Functional Timing                                          | 4-22 |

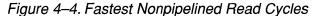

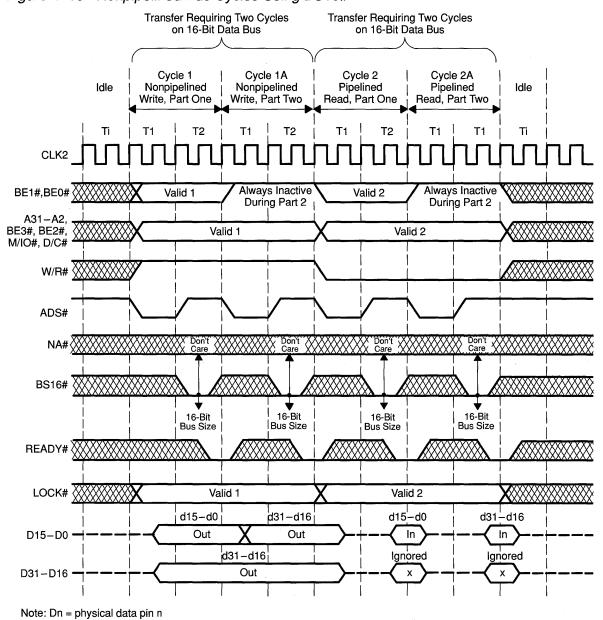

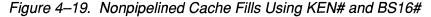

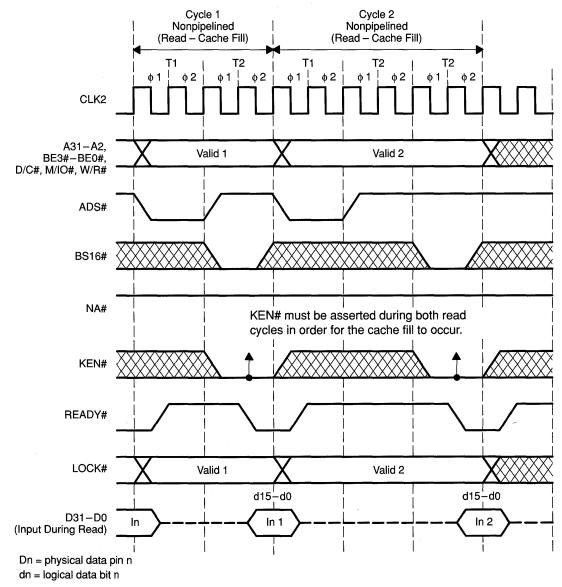

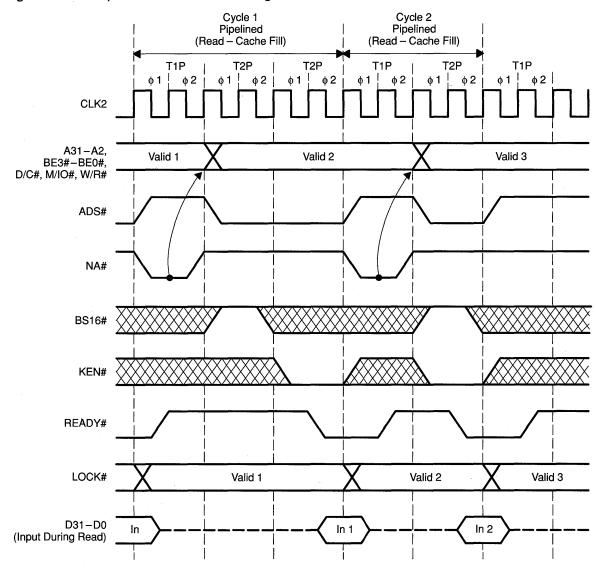

|   |           | 4.4.1   | Bus Cycles Using Nonpipelined Addressing                                | 4-23 |

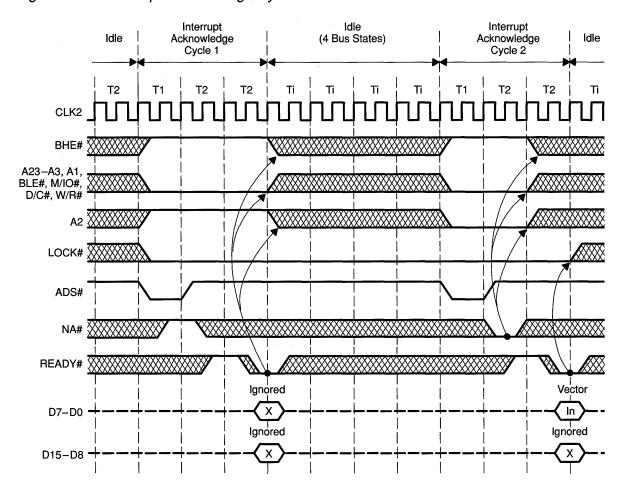

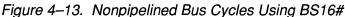

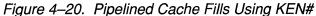

|   |           | 4.4.2   | Bus Cycles Using Pipelined Addressing                                   | 4-27 |

|   |           | 4.4.3   | Bus Cycles Using BS16#                                                  | 4-34 |

|   |           | 4.4.4   | Locked Bus Cycles                                                       | 4-37 |

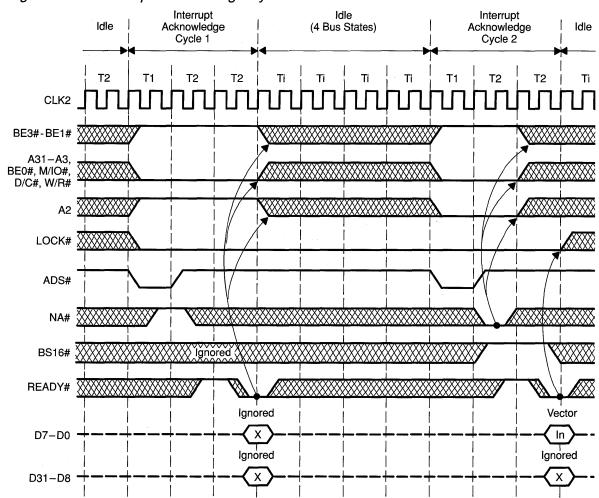

|   |           | 4.4.5   | Interrupt-Acknowledge Cycles                                            | 4-37 |

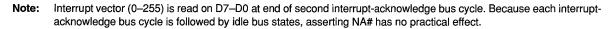

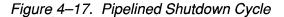

|   |           | 4.4.6   | Halt and Shutdown Cycles                                                | 4-39 |

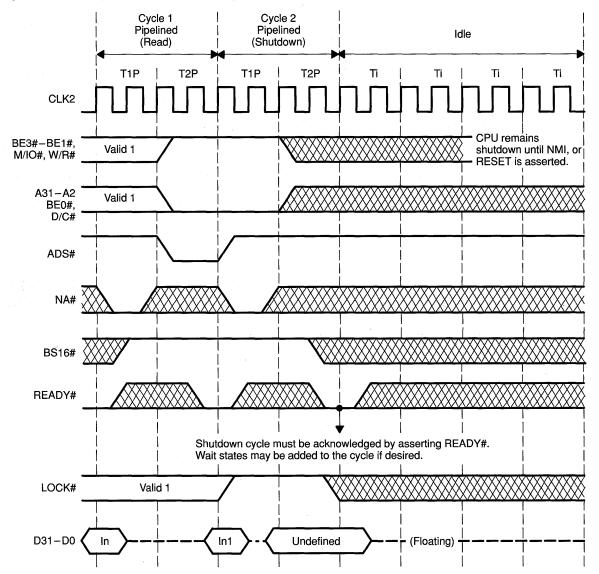

|   |           | 4.4.7   | Internal Cache Interface                                                | 4-42 |

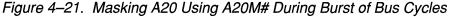

|   |           | 4.4.8   | Address Bit-20 Masking                                                  | 4-45 |

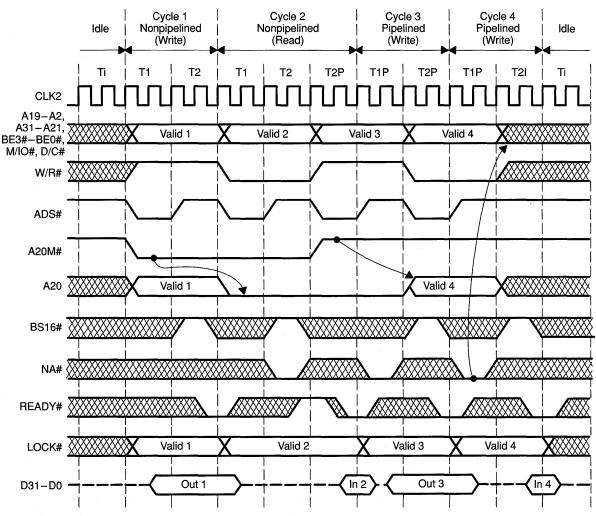

|   |           | 4.4.9   | Hold Acknowledge State                                                  | 4-46 |

|   |           | 4.4.10  | Coprocessor Interface                                                   | 4-49 |

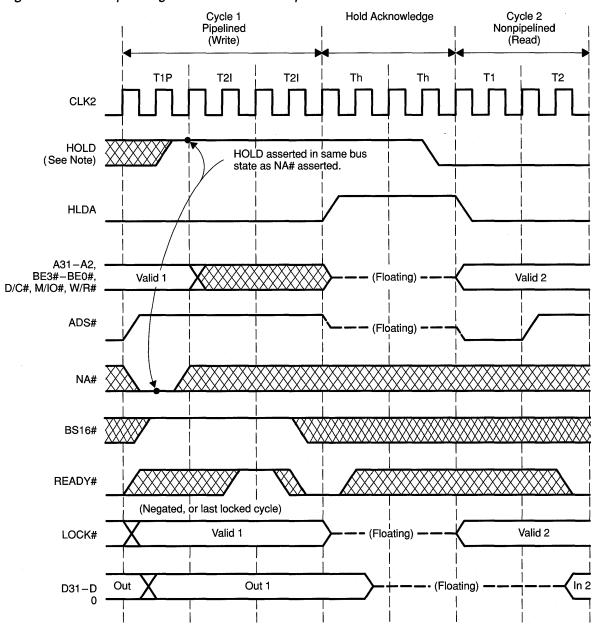

|   |           | 4.4.11  | SMM Interface                                                           | 4-50 |

|   |           | 4.4.12  | Power Management                                                        | 4-52 |

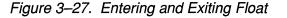

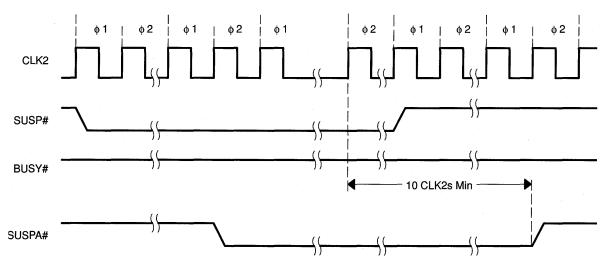

|   |           | 4.4.13  | Float (144-Pin QFP and 168-Pin PGA Pinouts Only)                        | 4-55 |

| _ | <b></b> . |         |                                                                         |      |

| 5 |           | -       | pecifications                                                           |      |

|   | 5.1       |         | cal Connections                                                         |      |

|   |           | 5.1.1   | Power and Ground Connections and Decoupling                             |      |

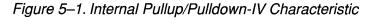

|   |           | 5.1.2   | Pullup/Pulldown Resistors                                               |      |

|   |           | 5.1.3   | NC Designated Terminals                                                 |      |

|   |           | 5.1.4   | Unused Signal Input Terminals                                           |      |

|   | 5.2       |         | te Maximum Ratings                                                      |      |

|   | 5.3       |         | mended Operating Conditions                                             |      |

|   |           | 5.3.1   | 3.3-Volt Microprocessors With 5-Volt Tolerant Inputs, Outputs, and I/Os |      |

|   |           | 5.3.2   | 3.3-Volt Microprocessors                                                |      |

|   |           | 5.3.3   | 5-Volt Microprocessors                                                  |      |

|   | 5.4       |         | ectrical Characteristics                                                |      |

|   |           | 5.4.1   | 3.3-Volt Microprocessors With 5-Volt Tolerant Inputs, Outputs, and I/Os |      |

|   |           | 5.4.2   | 3.3-Volt Microprocessors                                                |      |

|   |           | 5.4.3   | 5-Volt Microprocessors                                                  |      |

|   | 5.5       |         | aracteristics                                                           |      |

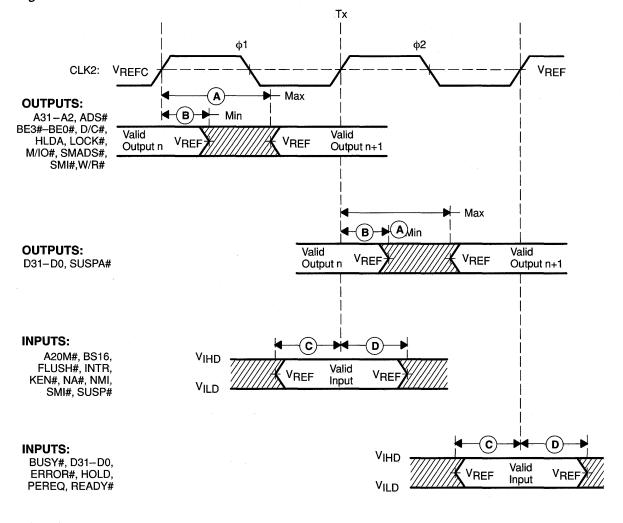

|   |           | 5.5.1   | Measurement Points for AC Characteristics                               |      |

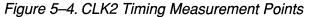

|   |           | 5.5.2   | CLK2 Timing Measurement Points                                          |      |

|   |           | 5.5.3   | AC Data Characteristics Tables                                          |      |

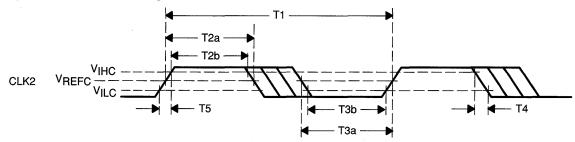

|   |           | 5.5.4   | RESET Setup and Hold Timing                                             |      |

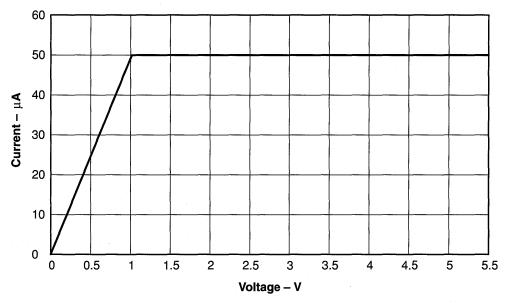

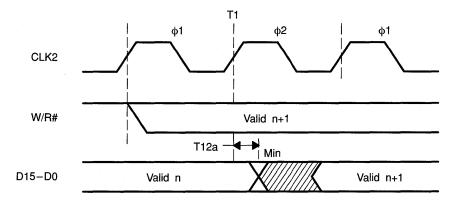

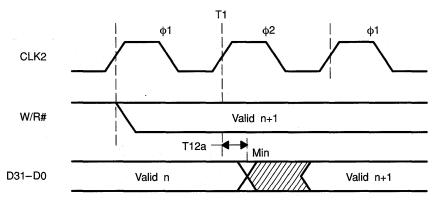

|   |           | 5.5.5   | TI486SXLC Switching Waveforms                                           |      |

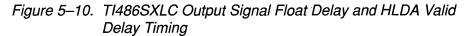

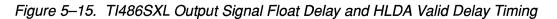

|   |           | 5.5.6   | TI486SXL Switching Waveforms                                            | 5-32 |

ix

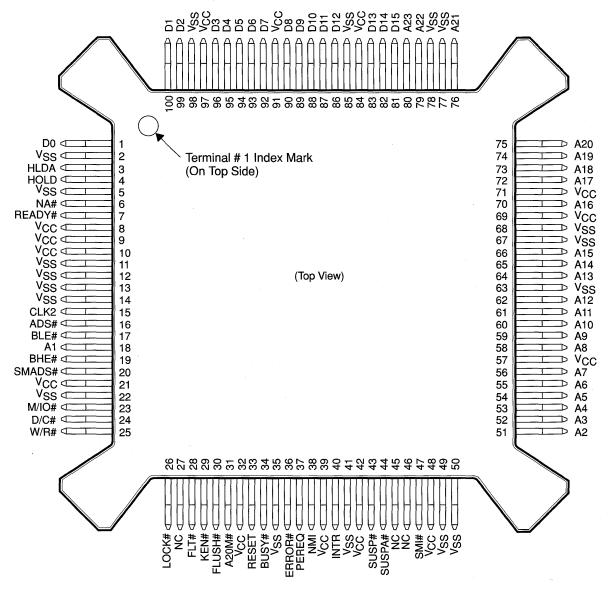

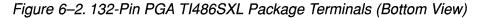

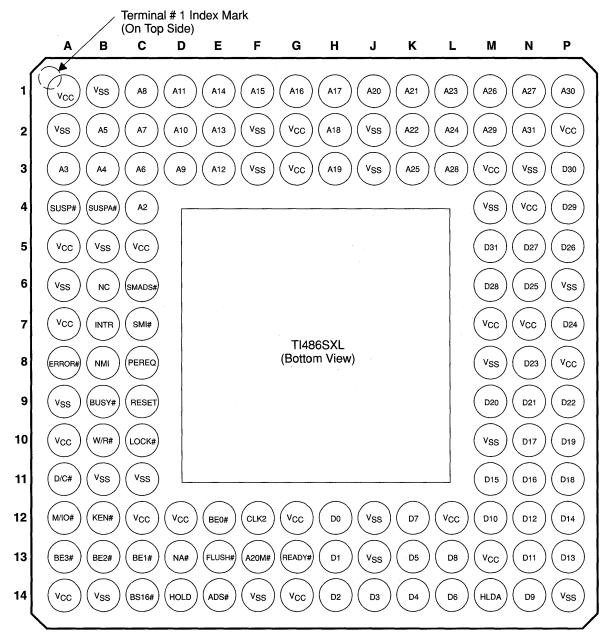

| 6 | Mech                     | anical Specifications                                                                                                                                                                                                                                                                                                                                         | 6-1                                                                        |

|---|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

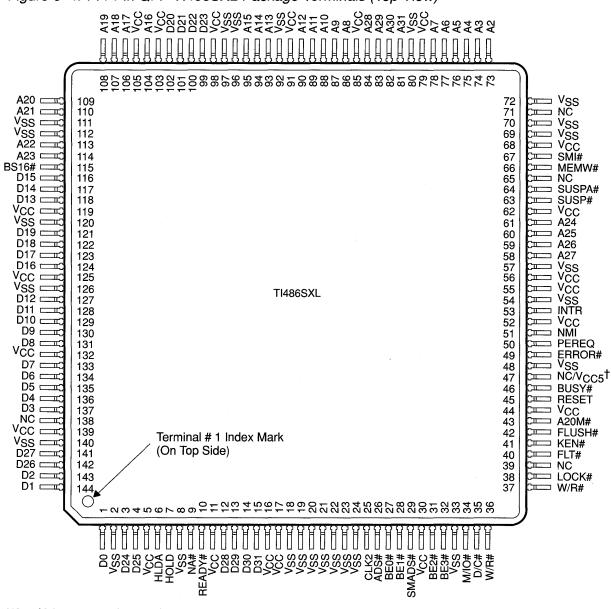

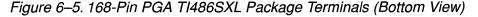

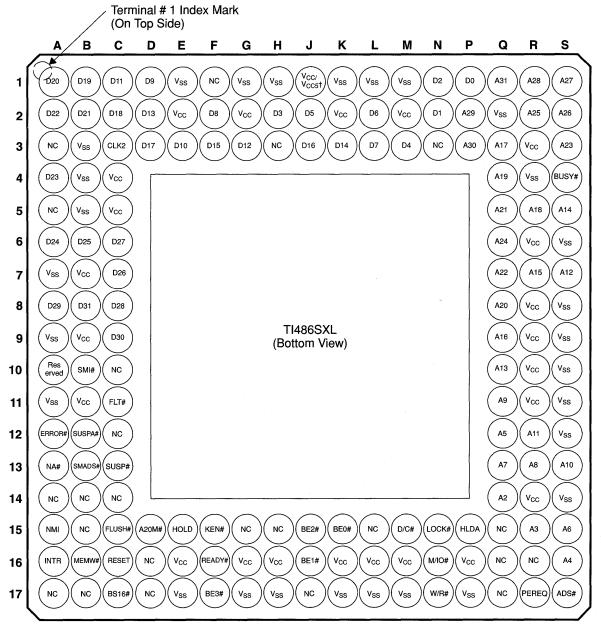

|   | 6.1                      | Terminal Assignments                                                                                                                                                                                                                                                                                                                                          | 6-2                                                                        |

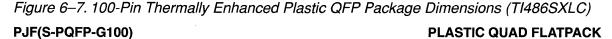

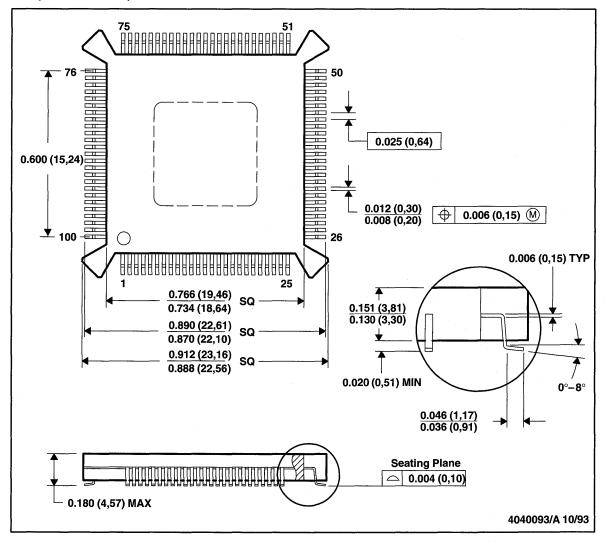

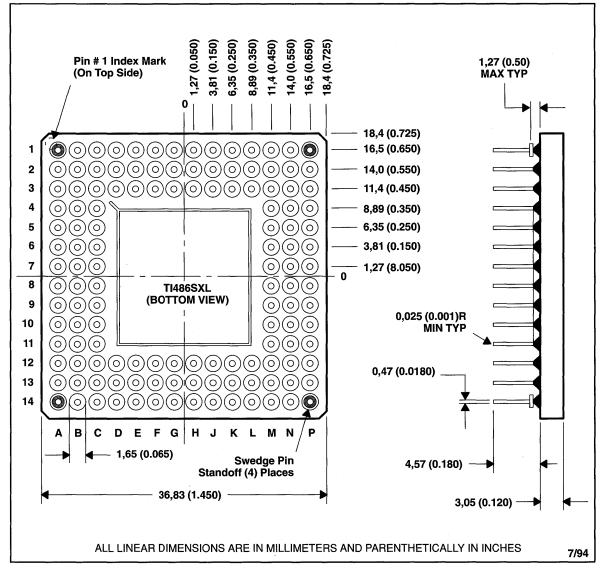

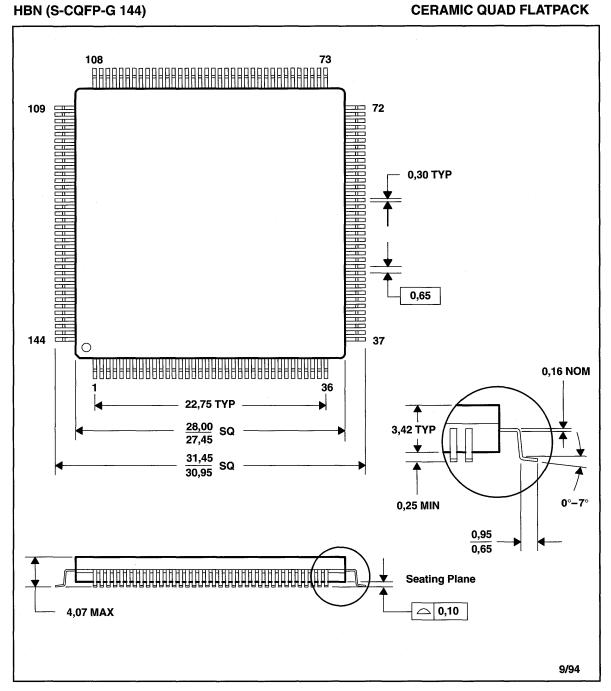

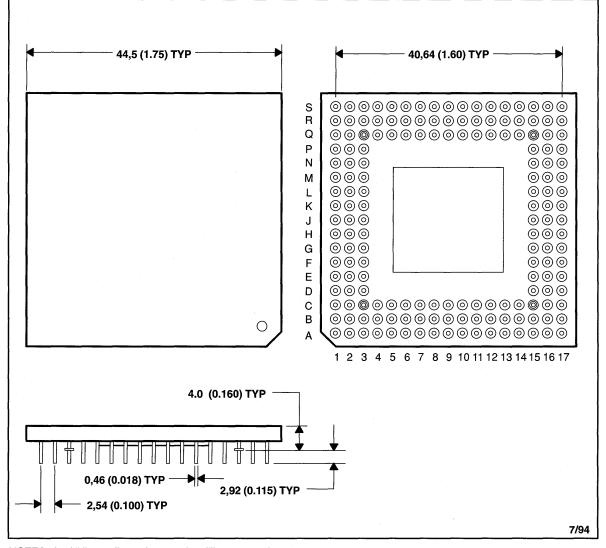

|   | 6.2                      | Package Dimensions                                                                                                                                                                                                                                                                                                                                            | 6-13                                                                       |

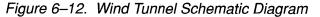

|   | 6.3                      | Thermal Characteristics                                                                                                                                                                                                                                                                                                                                       | 6-18                                                                       |

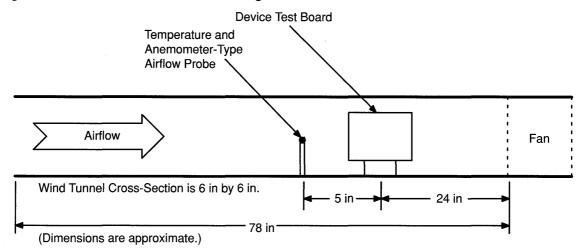

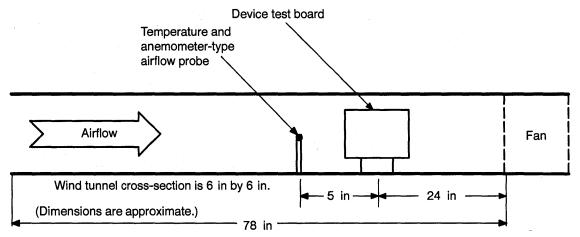

|   |                          | 6.3.1 Airflow Measurement Setup                                                                                                                                                                                                                                                                                                                               | 6-20                                                                       |

|   |                          | 6.3.2 Thermal Parameter Definitions                                                                                                                                                                                                                                                                                                                           | 6-21                                                                       |

| 7 | Instru                   | uction Set                                                                                                                                                                                                                                                                                                                                                    | 7-1                                                                        |

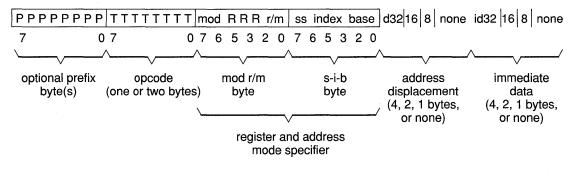

| - | 7.1                      | General Instruction Format                                                                                                                                                                                                                                                                                                                                    |                                                                            |

|   | 7.2                      | Instruction Fields                                                                                                                                                                                                                                                                                                                                            |                                                                            |

|   |                          | 7.2.1 Prefixes                                                                                                                                                                                                                                                                                                                                                |                                                                            |

|   |                          | 7.2.2 Opcode Field                                                                                                                                                                                                                                                                                                                                            |                                                                            |

|   |                          | 7.2.3 w Field                                                                                                                                                                                                                                                                                                                                                 |                                                                            |

|   |                          | 7.2.4 d Field                                                                                                                                                                                                                                                                                                                                                 |                                                                            |

|   |                          | 7.2.5 reg Field                                                                                                                                                                                                                                                                                                                                               |                                                                            |

|   |                          | 7.2.6 mod and r/m Field                                                                                                                                                                                                                                                                                                                                       |                                                                            |

|   |                          | 7.2.7 mod and base Fields                                                                                                                                                                                                                                                                                                                                     |                                                                            |

|   |                          | 7.2.8 ss Field                                                                                                                                                                                                                                                                                                                                                |                                                                            |

|   |                          | 7.2.9 index Field                                                                                                                                                                                                                                                                                                                                             |                                                                            |

|   |                          | 7.2.10 sreg2 Field                                                                                                                                                                                                                                                                                                                                            |                                                                            |

|   |                          | 7.2.11 sreg3 Field                                                                                                                                                                                                                                                                                                                                            |                                                                            |

|   |                          | 7.2.12 eee Field                                                                                                                                                                                                                                                                                                                                              |                                                                            |

|   | 7.3                      | Flags                                                                                                                                                                                                                                                                                                                                                         |                                                                            |

|   | 7.4                      | Clock-Count Summary                                                                                                                                                                                                                                                                                                                                           |                                                                            |

|   | 1.4                      | 7.4.1 Assumptions                                                                                                                                                                                                                                                                                                                                             |                                                                            |

|   |                          | 7.4.2 Abbreviations                                                                                                                                                                                                                                                                                                                                           |                                                                            |

|   | 7.5                      | Instruction Set                                                                                                                                                                                                                                                                                                                                               |                                                                            |

|   |                          |                                                                                                                                                                                                                                                                                                                                                               |                                                                            |

| Α |                          | Programmer's Guide                                                                                                                                                                                                                                                                                                                                            |                                                                            |

|   | A.1                      | SMM Overview                                                                                                                                                                                                                                                                                                                                                  |                                                                            |

|   |                          | A.1.1 Introduction                                                                                                                                                                                                                                                                                                                                            |                                                                            |

|   |                          | A.1.2 SMM Implementation                                                                                                                                                                                                                                                                                                                                      |                                                                            |

|   | A.2                      | TI486SXL(C) Microprocessor Power Management Features                                                                                                                                                                                                                                                                                                          |                                                                            |

|   |                          | A.2.1 Reducing the Clock Frequency                                                                                                                                                                                                                                                                                                                            |                                                                            |

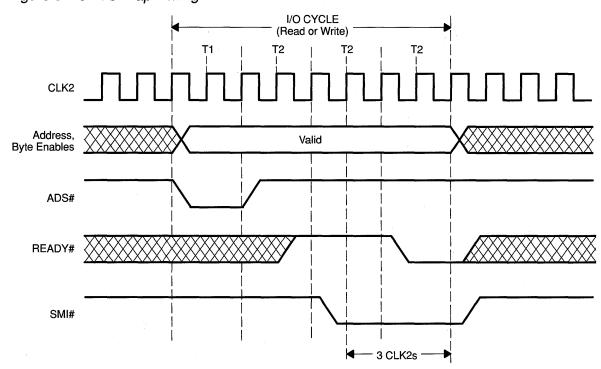

|   | • •                      | A.2.2 Suspend Mode                                                                                                                                                                                                                                                                                                                                            |                                                                            |

|   | A.3                      | SMM Feature Comparison                                                                                                                                                                                                                                                                                                                                        |                                                                            |

|   | A.4                      | SMM Hardware Considerations                                                                                                                                                                                                                                                                                                                                   |                                                                            |

|   |                          | A.4.1 SMM Pins                                                                                                                                                                                                                                                                                                                                                |                                                                            |

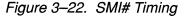

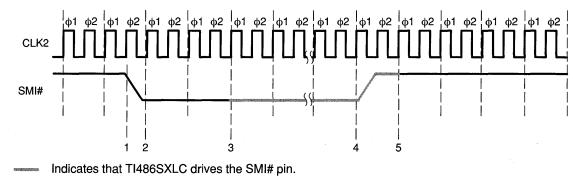

|   |                          | A.4.2 SMI# Pin Timing                                                                                                                                                                                                                                                                                                                                         |                                                                            |

|   |                          | A.4.3 Address Strobes                                                                                                                                                                                                                                                                                                                                         |                                                                            |

|   |                          | A.4.4 Chipset READY#                                                                                                                                                                                                                                                                                                                                          |                                                                            |

|   |                          |                                                                                                                                                                                                                                                                                                                                                               |                                                                            |

|   | A.5                      | SMM Software Considerations                                                                                                                                                                                                                                                                                                                                   |                                                                            |

|   | A.5                      | SMM Software Considerations         A.5.1       Exiting the SMI Handler                                                                                                                                                                                                                                                                                       | A-9                                                                        |

|   | A.5                      | SMM Software ConsiderationsA.5.1Exiting the SMI HandlerA.5.2Accessing Main Memory At the Same Address as SMM Code                                                                                                                                                                                                                                             | A-9<br>A-9                                                                 |

|   |                          | SMM Software ConsiderationsA.5.1Exiting the SMI HandlerA.5.2Accessing Main Memory At the Same Address as SMM CodeA.5.3Miscellaneous Execution Details                                                                                                                                                                                                         | A-9<br>A-9<br>A-9                                                          |

|   | A.6                      | SMM Software Considerations         A.5.1       Exiting the SMI Handler         A.5.2       Accessing Main Memory At the Same Address as SMM Code         A.5.3       Miscellaneous Execution Details         Enabling SMM                                                                                                                                    | A-9<br>A-9<br>A-9<br>A-11                                                  |

|   | A.6<br>A.7               | SMM Software Considerations         A.5.1       Exiting the SMI Handler         A.5.2       Accessing Main Memory At the Same Address as SMM Code         A.5.3       Miscellaneous Execution Details         Enabling SMM       SMM Instruction Summary and Macros                                                                                           | A-9<br>A-9<br>A-9<br>A-11<br>A-12                                          |

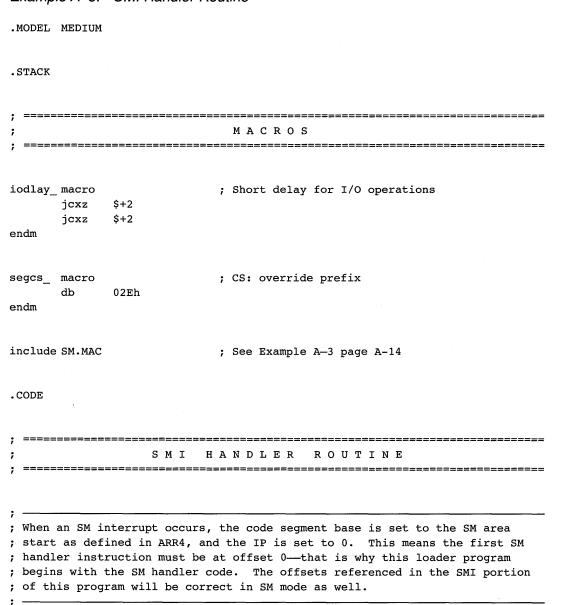

|   | A.6<br>A.7<br>A.8        | SMM Software Considerations         A.5.1       Exiting the SMI Handler         A.5.2       Accessing Main Memory At the Same Address as SMM Code         A.5.3       Miscellaneous Execution Details         Enabling SMM       SMM Instruction Summary and Macros         SMI Handler Example       SMI Handler Example                                     | A-9<br>A-9<br>A-9<br>A-11<br>A-11<br>A-12<br>A-17                          |

|   | A.6<br>A.7<br>A.8<br>A.9 | SMM Software Considerations         A.5.1       Exiting the SMI Handler         A.5.2       Accessing Main Memory At the Same Address as SMM Code         A.5.3       Miscellaneous Execution Details         Enabling SMM       SMM Instruction Summary and Macros         SMI Handler Example       Loading SMM Memory With an SMM Program From Main Memory | A-9<br>A-9<br>A-9<br>A-11<br>A-12<br>A-12<br>A-17<br>A-22                  |

|   | A.6<br>A.7<br>A.8        | SMM Software Considerations         A.5.1       Exiting the SMI Handler         A.5.2       Accessing Main Memory At the Same Address as SMM Code         A.5.3       Miscellaneous Execution Details         Enabling SMM       SMM Instruction Summary and Macros         SMI Handler Example       SMI Handler Example                                     | A-9<br>A-9<br>A-11<br>A-11<br>A-12<br>A-12<br>A-17<br>A-22<br>A-22<br>A-26 |

|   | A.12<br>A.13 | Format of Data Used by SVDC/RSDC Instructions                              |        |

|---|--------------|----------------------------------------------------------------------------|--------|

|   | A.14         | Testing/Debugging SMM Code                                                 |        |

|   | 7.14         | A.14.1 Software Only Debugging                                             |        |

|   |              | A.14.2 Software Debugging Example                                          |        |

|   |              | A.14.3 Clearing the VM Flag Bit                                            |        |

| в | BIOS         | Modifications Guide                                                        | B-1    |

|   | B.1          | Differences Between the TI486SLC/DLC BIOS and the TI486SXL(C) BIOS         | B-2    |

|   | B.2          | Power-Up and Hard Reset                                                    | B-3    |

|   | B.3          | Protected-Mode to Real-Mode Switching                                      | B-3    |

|   | B.4          | Soft Reset-(CONTROL) (ALT) (DELETE)                                        | B-4    |

|   | B.5          | Turning the Internal Cache On and Off                                      | B-4    |

| С | Desig        | n Considerations and Cache Flush                                           | C-1    |

|   | C.1          | Design Considerations                                                      | C-2    |

|   | C.2          | Address Bit A20 Masking                                                    | C-3    |

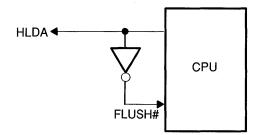

|   | C.3          | General Cache Invalidation                                                 |        |

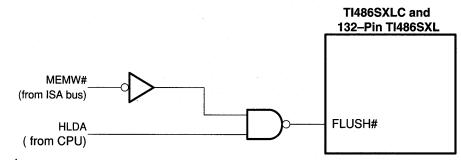

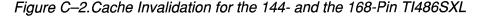

|   |              | C.3.1 Systems With No Secondary Cache or With a Parallel Secondary Cache . | C-4    |

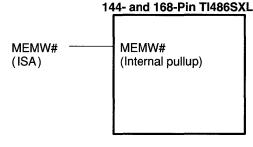

|   |              | C.3.2 Systems With a Serial Secondary Cache                                | C-5    |

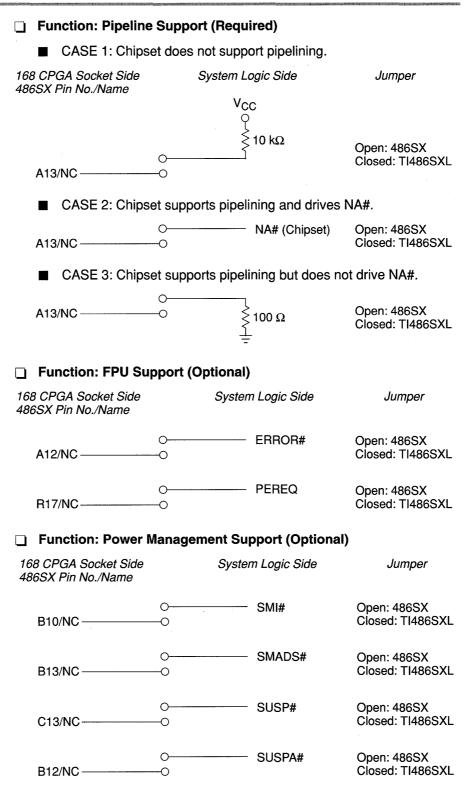

| D | TI486        | SXL OEM Modifications for 168-Pin CPGA                                     | D-1    |

|   | D.1          | Boards Supporting TI486SXL and Intel                                       | D-2    |

|   | D.2          | Boards Supporting TI486SXL and a 486DX                                     | D-5    |

|   | D.3          | Boards Supporting TI486SXL and a 486DX4                                    | D-6    |

|   | D.4          | Boards Supporting the VL Bus                                               | D-7    |

|   |              | D.4.1 Cache Snooping                                                       |        |

|   |              | D.4.2 VL-Bus Clock                                                         |        |