# SLC90E46 ADVANCE INFORMATION

# SLC90E46 SouthBridge (Member of High Performance TeXas Chipset)

#### **FEATURES**

- 324 Pin BGA South Bridge Chip

- Supports Pentium Compatible Processor With SLC90E42 North Bridge Chip

- 3V Operation with 5V Tolerant Buffers

- PCI 2.1 Compliant

- Integrated PCI To ISA Bridge

- Supports PCI Bus up to 33 MHz

- Supports Full ISA or Extended I/O (EIO) Bus

- Supports Full Positive Decode or Subtractive Decode of PCI

- Supports ISA/EIO At 1/4 of PCI Frequency

- Integrated IDE Controller

- Independent Timing Options for up to Four Drives

- Supports PIO Mode 0 to 4, DMA Mode 1 and 2

- Supports "Ultra DMA/33" Synchronous DMA Mode with Transfer Rate up to 33Mbvtes/Second

- Integrated 16 DW Buffer For Each IDE Channel

- Supports Glue-Less "Swap-Bay" Option with Full Electrical Isolation

- Supports Both Legacy and PCI-Native Modes

- Integrated USB Host Controller

- Supports OHCI Host Interface

- Supports Two USB 1.0 Ports for Serial Transfers at 12 or 1.5Mbit/Sec

- Supports Legacy Keyboard and Mouse Software with USB-Based Keyboard and Mouse

- Comprehensive Power Management Capability

- Supports Power-On Suspend and Soft-Off for Desktop Applications

- All Registers Readable/Restorable For Proper Resume From 0V Suspend

- Global and Local Device Management

- Comprehensive Suspend/Resume Logic for Notebook Applications

- Supports Thermal Alarm

- Support For External Microprocessor

- Full Support of ACPI Specification and OS Directed Power Management

- Supports PCI nCLKRUN Protocol

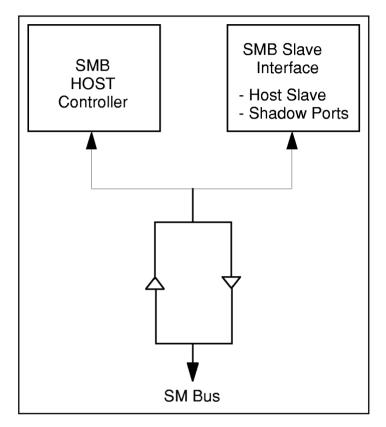

- Integrated SMBus Host Controller

- Host Interface Logic Allows CPU to Communicate Via SMBus

- Slave Interface Logic Allows External SMBus Master to Control Resume Events

- Enhanced DMA Controller

- Two 8237 DMA Controllers

- Supports PCI DMA with 3 PC/PCI Channels and Distributed DMA Protocols

- Supports Type-F DMA with a Deep 4-DW Buffer

- Interrupt Controller

- Two 8259 Interrupt Controllers

- Independently Programmable Edge/Level Sensitivity

- Supports Serial Interrupt

- Supports Optional External I/O APIC

- Integrated 8254 Timer

- Real Time Clock

- 56-Byte Battery Backup CMOS SRAM

- Date Alarm

- Two 8-Byte Lockout Ranges

The SLC90E46 is a multi-function PCI device implementing a PCI-to-ISA bridge function, a PCI IDE function, a Universal Serial Bus host/hub function, and an Enhanced Power Management function. As a PCI-to-ISA bridge, the SLC90E46 integrates most I/O functions found in a common ISA bridge chip, that include two DMA controllers, two interrupt controllers, an 8254 timer, and a Real Time Clock. The DMA controllers support Type-F data transfers on each of the eight channels. The SLC90E46 also supports PC/PCI and Distributed DMA protocols for PCI based DMA applications. The Interrupt Controllers support Edge or Level sensitive programmable inputs and the use of an external I/O APIC and serial interrupts. The SLC90E46 can be configured to provide chip select decoding for BIOS, RTC, keyboard controller, external microcontroller, and two programmable chip selects. The SLC90E46 can be configured as a subtractive decode bridge or as an positive decode bridge. This allows the use of a subtractive decode PCI-to-PCI bridge.

The SLC90E46 supports two IDE channels for up to four IDE devices in either PIO or Bus Master mode. The SLC90E46 also supports "Ultra DMA/33" synchronous DMA compatible devices for up to 33Mbytes per second data transfer rate. The embedded 16DW deep buffers allow zero wait state PCI burst transfer in either direction.

The SLC90E46 integrates a USB host controller that is Open Host Controller Interface (OHCI) compatible. Two USB ports are implemented in the root hub.

The SLC90E46 supports comprehensive power management, including full clock control, device power management for up to 14 devices, global power management and suspend and resume logic with Power On Suspend, Suspend to RAM or Suspend to Disk. It fully supports operating system directed power management via the ACPI specification. A System Management Bus (SMBus) host and slave interface logic is integrated for communication with other on-board devices.

## **TABLE OF CONTENTS**

| 1.   | SLC  | 90E46 PINOUT AND PACKAGE SPECIFICATION                     | .13 |

|------|------|------------------------------------------------------------|-----|

| 1.1. |      | SLC90E46 BGA Package Information                           | .13 |

| 1.2. |      | SLC90E46 PIN ASSIGNMENTS                                   | .16 |

| 1.3. |      | SLC90E46 PIN ASSIGNMENT TABLES IN ALPHABETICAL ORDER       | .17 |

| 2.   | SLC  | 90E46 FUNCTIONAL BLOCK OVERVIEW                            | .22 |

| 2.1. |      | PCI-TO-ISA/EIO BRIDGE                                      |     |

| 2.   | 1.1. | DMA CONTROLLERS, TIMER/COUNTERS, AND INTERRUPT CONTROLLERS | .22 |

| 2.   | 1.2. | RTC                                                        |     |

| 2.   | 1.3. | GPIO and Chip Selects                                      | .23 |

| 2.2. |      | PCI IDE CONTROLLER                                         | .23 |

| 2.3. |      | ENHANCED UNIVERSAL SERIAL BUS (USB) CONTROLLER             | .23 |

| 2.4. |      | Power Management                                           |     |

| 3.   | THE  | SLC90E46 SIGNAL DESCRIPTION                                | .24 |

| 3.1. |      | PCI Interface                                              | .25 |

| 3.2. |      | ISA/EIO Interface Signals                                  | .28 |

| 3.3. |      | XBUS INTERFACE SIGNALS                                     | .31 |

| 3.4. |      | DMA SIGNALS                                                | .33 |

| 3.5. |      | INTERRUPT AND APIC SIGNALS                                 | .34 |

| 3.6. |      | CPU Interface Signals                                      | .36 |

| 3.7. |      | CLOCKS                                                     |     |

| 3.8. |      | IDE Signals - Function 1                                   | .38 |

| 3.9. |      | USB Signals - Function 2                                   |     |

| 3.10 |      | Power Management Signals - Function 3                      | .43 |

| 3.11 |      | OTHER SYSTEM AND TEST SIGNALS                              |     |

| 3.12 |      | GENERAL PURPOSE INPUT AND OUTPUT SIGNALS                   | .46 |

| 3.13 | •    | Power and Ground Signals                                   |     |

| 4.   | SLC  | 90E46 - PCI/ISA BRIDGE REGISTER DESCRIPTION                |     |

| 4.1. |      | PCI/ISA BRIDGE REGISTER MAPPING                            |     |

| 4.   | 1.1. | PCI Configuration Register Mapping Table (Function 0)      |     |

| 4.   | 1.2. | IO Space Register Mapping Table (Function 0)               |     |

| 4.2. |      | PCI/ISA Bridge PCI Register Description (Function 0)       | .54 |

| 4.   | 2.1. | VID Vendor Identification Register                         |     |

| 4.   | 2.2. | DID Device Identification Register                         |     |

| 4.   | 2.3. | PCICMD PCI Command Register                                |     |

|      | 2.4. | PCISTS PCI Status Register                                 |     |

|      | 2.5. | RID Revision Identification Register                       |     |

|      | 2.6. | CLASSC Class Code Register                                 |     |

| 4.   | 2.7. | HEDT Header Type Register                                  |     |

| 4    | 28   | IORT ISA I/O Recovery Timer Register                       | 56  |

| 4.2.9.    | XBCS X-Bus Chip Select Register                               | 57 |

|-----------|---------------------------------------------------------------|----|

| 4.2.10.   | PIRQRC[A:D] PIRQx Route Control Registers                     |    |

| 4.2.11.   | SERIRQC Serial IRQ Control Register                           |    |

| 4.2.12.   | FDMA Type-F DMA Control Register                              |    |

| 4.2.13.   | TOM Top of Memory Register                                    |    |

| 4.2.14.   | MBDMA Motherboard device DMA Control Registers                |    |

| 4.2.15.   | APICBASE APIC Base Address Relocation Register                |    |

| 4.2.16.   | DLC Deterministic Latency Control Register                    |    |

| 4.2.17.   | PDMACFG PCI DMA Configuration Register                        |    |

| 4.2.18.   | DDMABP Distributed DMA Slave Base Pointer Registers           |    |

| 4.2.19.   | GENCFG General Configuration Register                         |    |

| 4.2.20.   | RTCCFG Real Time Clock Configuration Register                 |    |

| 4.2.21.   | SBMISCL South Bridge Miscellaneous Low Register               |    |

| 4.2.22.   | SBMISCH South Bridge Miscellaneous High Register              | 69 |

| 1.3. PCI  | TO ISA/EIO BRIDGE IO SPACE REGISTERS                          | 70 |

| 4.3.1.    | DMA Registers                                                 | 70 |

| 4.3.1.1.  | DMA Command Register                                          | 70 |

| 4.3.1.2.  | DMA Channel Mode Register                                     | 70 |

| 4.3.1.3.  | DMA Request Register                                          | 71 |

| 4.3.1.4.  | Write Single Mask Bit Register                                | 71 |

| 4.3.1.5.  | Read/Write All Mask Bits Register                             | 72 |

| 4.3.1.6.  | DMA Status Register                                           | 72 |

| 4.3.1.7.  | DMA Base and Current Address Registers                        | 73 |

| 4.3.1.8.  | DMA Base and Current Count Registers                          | 73 |

| 4.3.1.9.  | DMA Low Page Registers                                        | 74 |

| 4.3.1.10. | DMA Clear Byte Pointer Register                               | 74 |

| 4.3.1.11. | 5                                                             |    |

| 4.3.1.12. | 5                                                             |    |

| 4.3.2.    | Interrupt Controller Registers                                |    |

| 4.3.2.1.  | ICW1 - Initialization Command Word 1 Register                 |    |

| 4.3.2.2.  | ICW2 - Initialization Command Word 2 Register                 |    |

| 4.3.2.3.  | ICW3 - Initialization Command Word 3 Register (Controller I)  |    |

| 4.3.2.4.  | ICW3 - Initialization Command Word 3 Register (Controller II) |    |

| 4.3.2.5.  | ICW4 - Initialization Command Word 4 Register                 |    |

| 4.3.2.6.  | OCW1 - Operation Control Word 1 Register                      |    |

| 4.3.2.7.  | OCW2 - Operation Control Word 2 Register                      |    |

| 4.3.2.8.  | OCW3 - Operation Control Word 3 Register                      |    |

| 4.3.2.9.  | ELCR1 - Edge/Level Control Register                           |    |

| 4.3.2.10. |                                                               |    |

| 433       | Counter/Timer Registers                                       | 80 |

| 4.3.3.1.  | Timer Control Word Register                      | 80   |

|-----------|--------------------------------------------------|------|

| 4.3.3.2.  | Timer Status Register                            | 82   |

| 4.3.3.3.  | Timer Count Register                             | 83   |

| 4.3.4.    | NMI Register                                     | 83   |

| 4.3.4.1.  | NMISC NMI Status and Control Register            | 84   |

| 4.3.4.2.  | NMIEN NMI Enable Register                        | 85   |

| 4.3.5.    | Real Time Clock Register                         | 85   |

| 4.3.5.1.  | RTCI Real-Time Clock Index Register              | 85   |

| 4.3.5.2.  | RTCD Real-Time Clock Data Register               | 85   |

| 4.3.5.3.  | RTCEI Real-Time Clock Extended Index Register    | 86   |

| 4.3.5.4.  | RTCED Real-Time Clock Extended Data Register     | 86   |

| 4.3.6.    | Advanced Power Management (APM) Registers        | 87   |

| 4.3.6.1.  | APMC Advanced Power Management Control Port      | 87   |

| 4.3.6.2.  | APMS Advanced Power Management Status Port       | 87   |

| 4.3.7.    | X-Bus, Coprocessor, and Reset Registers          | 8888 |

| 4.3.7.1.  | RIRQ Reset X-Bus IRQ12/M and IRQ1 Register       | 8888 |

| 4.3.7.2.  | P92 Port 92 Register                             | 8888 |

| 4.3.7.3.  | CERR Coprocessor Error Register                  | 89   |

| 4.3.7.4.  | RC Reset Control Register                        | 89   |

| 5. SLC90E | 46 - IDE CONTROLLER REGISTER DESCRIPTION         | 90   |

| 5.1. IDE  | Controller Register Mapping Table (Function 1)   | 90   |

| 5.1.1.    | PCI Configuration Registers (Function 1)         | 90   |

| 5.1.2.    | IO Space Registers (Function 1)                  | 91   |

| 5.2. IDE  | Controller PCI Register Description (Function 1) | 91   |

| 5.2.1.    | VID Vendor Identification Register               | 91   |

| 5.2.2.    | DID Device Identification Register               | 91   |

| 5.2.3.    | PCICMD PCI Command Register                      | 91   |

| 5.2.4.    | PCISTS PCI Device Status Register                |      |

| 5.2.5.    | RID Revision Identification Register             |      |

| 5.2.6.    | CLASSC Class Code Register                       |      |

| 5.2.7.    | MLT Master Latency Timer Register                |      |

| 5.2.8.    | HEDT Header Type Register                        |      |

| 5.2.9.    | IDEBASE1 PCI Base Address Register I             |      |

| 5.2.10.   | IDEBASE2 PCI Base Address Register II            |      |

| 5.2.11.   | IDEBASE3 PCI Base Address Register III           |      |

| 5.2.12.   | IDEBASE4 PCI Base Address Register IV            |      |

| 5.2.13.   | BMIBA Bus Master Interface Base Address Register |      |

| 5.2.14.   | INTLINE PCI IDE Interrupt Line                   |      |

| 5.2.15.   | INTPIN PCI IDE Interrupt Pin                     |      |

| 5 2 16    | IDETIM IDE Timing Register                       | QF   |

| 5.2.17.  | SIDETIM Slave IDE Timing Register                        | 96  |

|----------|----------------------------------------------------------|-----|

| 5.2.18.  | UDMACTL Ultra DMA/33 Control Register                    | 97  |

| 5.2.19.  | UDMATIM Ultra DMA/33 Timing Register                     | 98  |

| 5.3. ID  | DE CONTROLLER IO SPACE REGISTERS                         | 99  |

| 5.3.1.   | BMICx Bus Master IDE Command Register (IO)               | 99  |

| 5.3.2.   | BMISx Bus Master IDE Status Register                     | 100 |

| 5.3.3.   | BMIDTPx Bus Master IDE Descriptor Table Pointer Register | 101 |

| 6. SLC90 | DE46 USB REGISTER DESCRIPTION (FUNCTION 2)               | 102 |

| 6.1. P   | CI Configuration Registers                               | 102 |

| 6.1.1.   | Vendor ID Register                                       | 102 |

| 6.1.2.   | Device ID Register                                       | 102 |

| 6.1.3.   | Command Register                                         | 103 |

| 6.1.4.   | Status Register                                          | 103 |

| 6.1.5.   | Revision ID Register                                     | 104 |

| 6.1.6.   | Class Code Register                                      | 105 |

| 6.1.7.   | Cache Line Size                                          | 105 |

| 6.1.8.   | Latency Timer                                            | 105 |

| 6.1.9.   | Header Type Register                                     | 105 |

| 6.1.10.  | BIST                                                     | 106 |

| 6.1.11.  | Base Address Register                                    | 106 |

| 6.1.12.  | Interrupt Line Register                                  | 106 |

| 6.1.13.  | Interrupt Pin Register                                   | 106 |

| 6.1.14.  | Min_Gnt Register                                         | 107 |

| 6.1.15.  | Max_Lat Register                                         | 107 |

| 6.1.16.  | Test Mode Enable Register                                |     |

| 6.1.17.  | ASIC Operational Mode Enable Register                    | 108 |

| 6.2. U   | SB OPENHCI MEMORY MAPPED REGISTERS                       | 109 |

| 6.2.1.   | HCREVISIONfc                                             | 109 |

| 6.2.2.   | HCCONTROL                                                | 110 |

| 6.2.3.   | HCCOMMANDSTATUS                                          |     |

| 6.2.4.   | HCINTERRUPTSTATUS                                        | 112 |

| 6.2.5.   | HCINTERRUPTENABLE                                        |     |

| 6.2.6.   | HCINTERRUPTDISABLE                                       | 114 |

| 6.2.7.   | HCHCCA                                                   |     |

| 6.2.8.   | HCPERIODCURRENTED                                        |     |

| 6.2.9.   | HCCONTROLHEADED                                          |     |

| 6.2.10.  | HCCONTROLCURRENTED                                       |     |

| 6.2.11.  | HCBULKHEADED                                             |     |

| 6.2.12.  | HCBULKCURRENTED                                          | 116 |

| 6.2.13.  | HCDONEHEAD                                               | 116 |

| 6.2.14. | HCFMINTERVAL                                               | 116 |

|---------|------------------------------------------------------------|-----|

| 6.2.15. | HCFRAMEREMAINING                                           | 117 |

| 6.2.16. | HCFMNUMBER                                                 | 117 |

| 6.2.17. | HCPERIODICSTART                                            | 117 |

| 6.2.18. | HCLSTHRESHOLD                                              | 118 |

| 6.2.19. | HCRHDESCRIPTORA                                            |     |

| 6.2.20. | HCRHDESCRIPTORB                                            | 119 |

| 6.2.21. | HCRHSTATUS                                                 | 120 |

| 6.2.22. | HcRhPortStatus[1:2]                                        | 121 |

| 6.2.23. | HceInput                                                   |     |

| 6.2.24. | HCECONTROL                                                 | 124 |

| 6.2.25. | HCEINPUT                                                   | 125 |

| 6.2.26. | HCEOUTPUT                                                  | 125 |

| 6.2.27. | HCESTATUS                                                  |     |

| 7. POV  | /ER MANAGEMENT REGISTER DESCRIPTION (FUNCTION 3)           | 127 |

| 7.1.    | Power Management Register Summary (Function 3)             |     |

| 7.1.1.  | PCI Configuration Registers (Function 3)                   |     |

| 7.1.2.  | Power Management IO Space Registers (Function 3)           |     |

| 7.1.3.  | SMBus Controller IO Space Registers (Function 3)           |     |

| 7.2.    | PCI Configuration Registers (Function 3)                   | 129 |

| 7.2.1.  | VID Vendor Identification Register                         | 129 |

| 7.2.2.  | DID Device Identification Register                         |     |

| 7.2.3.  | PCICMD PCI Command Register                                | 129 |

| 7.2.4.  | PCISTS PCI Device Status Register                          | 130 |

| 7.2.5.  | RID Revision Identification Register                       | 130 |

| 7.2.6.  | CLASSC Class Code Register                                 |     |

| 7.2.7.  | HEDT Header Type Register                                  |     |

| 7.2.8.  | INTLINE Power Management Interrupt Line                    |     |

| 7.2.9.  | INTPIN Power Management Interrupt Pin                      |     |

| 7.2.10. | PMBA Power Management Base Address                         |     |

| 7.2.11. | CNTA Count A Register for Idle Timers (Function 3)         |     |

| 7.2.12. | CNTB Count B Register for Burst & Idle Timers (Function 3) |     |

| 7.2.13. | GPICTL General Purpose Input Control                       |     |

| 7.2.14. | DEVRESD Device Resource D Register                         |     |

| 7.2.15. | DEVACTA Device Activity A                                  |     |

| 7.2.16. | DEVACTB Device Activity B                                  |     |

| 7.2.17. | DEVRESA Device Resource A                                  |     |

| 7.2.18. | DEVRESB Device Resource B                                  |     |

| 7.2.19. | DEVRESC Device Resource C                                  |     |

| 7.2.20. | DEVRESE Device Resource E                                  | 144 |

|    | 7.2.21. | DEVRESF Device Resource F                         | 144 |

|----|---------|---------------------------------------------------|-----|

|    | 7.2.22. | DEVRESG Device Resource G                         | 145 |

|    | 7.2.23. | DEVRESH Device Resource H                         | 146 |

|    | 7.2.24. | DEVRESI Device Resource I                         | 146 |

|    | 7.2.25. | DEVRESJ Device Resource J                         | 147 |

|    | 7.2.26. | PMREGMISC Miscellaneous Power Management          | 147 |

| 7. | 3.      | SMBus Host Controller PCI Configuration Registers | 148 |

|    | 7.3.1.  | SMBBA SMBus Base Address                          | 148 |

|    | 7.3.2.  | SMBHSTCFG SMBus Host Configuration (Function 3)   | 148 |

|    | 7.3.3.  | SMBSLVC SMBus Slave Command (Function 3)          | 148 |

|    | 7.3.4.  | SMBSHDW1 SMBus Slave Shadow Port 1 (Function 3)   | 149 |

|    | 7.3.5.  | SMBSHDW2 SMBus Slave Shadow Port 2 (Function 3)   | 149 |

|    | 7.3.6.  | SMBREV SMBus Revision Identification (Function 3) | 149 |

| 7. | 4.      | Power Management I/O Space Registers              | 150 |

|    | 7.4.1.  | PMSTS Power Management Status Register (IO)       | 150 |

|    | 7.4.2.  | PMEN Power Management Resume Enable Register (IO) | 151 |

|    | 7.4.3.  | PMCNTRL Power Management Control Register (IO)    | 152 |

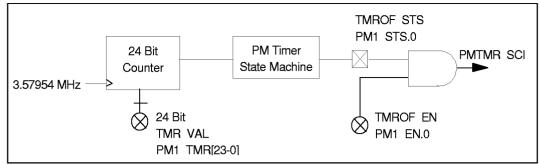

|    | 7.4.4.  | PMTMR Power Management Timer Register (IO)        | 153 |

|    | 7.4.5.  | GPSTS General Purpose Status Register (IO)        | 153 |

|    | 7.4.6.  | GPEN General Purpose Enable Register (IO)         | 154 |

|    | 7.4.7.  | PCNTRL Processor Control Register (IO)            | 155 |

|    | 7.4.8.  | PLVL2 Processor Level 2 Register (IO)             | 156 |

|    | 7.4.9.  | PLVL3 Processor Level 3 Register (IO)             | 156 |

|    | 7.4.10. | GLBSTS Global Status Register (IO)                | 156 |

|    | 7.4.11. | DEVSTS Device Status Register (IO)                | 158 |

|    | 7.4.12. | GLBEN Global Enable Register (IO)                 | 158 |

|    | 7.4.13. | GLBCTL Global Control Register (IO)               | 159 |

|    | 7.4.14. | DEVCTL Device Control Register (IO)               | 160 |

|    | 7.4.15. | GPIREG General Purpose Input Register (IO)        | 163 |

|    | 7.4.16. | GPOREG General Purpose Output Register (IO)       | 163 |

| 7. | 5.      | SMBus IO Space Registers                          |     |

|    | 7.5.1.  | SMBHSTSTS SMBus Host Status Register (IO)         | 164 |

|    | 7.5.2.  | SMBSLVSTS SMBus Slave Status Register (IO)        | 165 |

|    | 7.5.3.  | SMBHSTCNT SMBus Host Control Register (IO)        |     |

|    | 7.5.4.  | SMBHSTCMD SMBus Host Command Register (IO)        |     |

|    | 7.5.5.  | SMBHSTADD SMBus Host Address Register (IO)        |     |

|    | 7.5.6.  | SMBHSTDAT0 SMBus Host Data 0 Register (IO)        |     |

|    | 7.5.7.  | SMBHSTDAT1 SMBus Host Data 1 Register (IO)        |     |

|    | 7.5.8.  | SMBHSTDAT SMBus Block Data Register (IO)          | 168 |

|    | 750     | SMRSI VCNT SMRus Slave Central Projector (IO)     | 169 |

| 7.5.10 | SMBSHDWCMD SMBus Shadow Command Register (IO) | 169 |

|--------|-----------------------------------------------|-----|

| 7.5.11 | . SMBSLVEVT SMBus Slave Event Register (IO)   | 169 |

| 7.5.12 | SMBSLVEVT SMBus Slave Data Register (IO)      | 169 |

| B. PC  | /ISA BRIDGE FUNCTIONAL DESCRIPTION            | 170 |

| 8.1.   | MEMORY AND IO ADDRESS MAP                     | 170 |

| 8.1.1. | I/O Accesses                                  | 170 |

| 8.1.2. | Memory Access                                 | 170 |

| 8.1.3. | BIOS Memory Space                             | 171 |

| 8.2.   | PCI Interface                                 | 173 |

| 8.3.   | ISA/EIO INTERFACE                             | 174 |

| 8.4.   | DMA CONTROLLER                                | 174 |

| 8.4.1. | DMA Transfer Modes                            | 175 |

| 8.4.2. | DMA Transfer Types                            | 176 |

| 8.4.3. | DMA Timing                                    | 177 |

| 8.4.4. | DMA Buffer                                    | 177 |

| 8.4.5. | DMA Channel Priority                          | 177 |

| 8.4.6. | DMA Transfer Sizes                            | 178 |

| 8.4.7. | Address Shifting in 16-Bit DMA I/O Transfer   | 178 |

| 8.4.8. | Autoinitialization                            | 178 |

| 8.4.9. | Special DMA Commands                          | 178 |

| 8.4.10 | ). ISA Refresh                                | 179 |

| 8.5.   | PCI DMA                                       | 179 |

| 8.5.1. | Distributed DMA (DDMA)                        | 180 |

| 8.6.   | Interrupt Controller                          | 183 |

| 8.6.1. | Programming the Interrupt Controller          | 183 |

| 8.6.2. | End of Interrupt Operation                    | 184 |

| 8.6.3. | Modes of Operation                            | 185 |

| 8.6.4. | Cascade Mode                                  | 187 |

| 8.6.5. | Edge and Level Triggered Mode                 | 187 |

| 8.6.6. | Interrupt Masks                               | 188 |

| 8.6.7. | Interrupt Controller Status                   | 188 |

| 8.6.8. | Interrupt Steering                            | 189 |

| 8.7.   | SERIAL INTERRUPTS (SIRQ)                      | 190 |

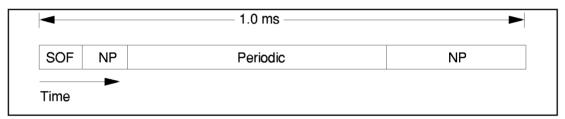

| 8.7.1. | SIRQ Protocol                                 | 190 |

| 8.8.   | TIMER / COUNTERS                              | 192 |

| 8.8.1. | Counter 0                                     | 192 |

| 8.8.2. | Counter 1                                     | 192 |

| 8.8.3. | Counter 2                                     | 192 |

| 8.8.4. | The Interval Timer Programming Interface      | 192 |

| ٥.0    | PEAL TIME CLOOK MODULE                        | 105 |

| 8.9.1.  | RTC Registers and RAM               | 196          |

|---------|-------------------------------------|--------------|

| 8.9.2.  | Register A                          | 198          |

| 8.9.3.  | Register B                          | 200          |

| 8.9.4.  | Register C                          | 201          |

| 8.9.5.  | Register D                          | 201          |

| 8.9.6.  | RTC Update Cycle                    | 202          |

| 8.9.7.  | RTC Interrupt                       | 202          |

| 8.9.8.  | Lockable RAM Ranges                 | 202          |

| 8.9.9.  | RTC External Connections            | 202          |

| 8.10.   |                                     | 203          |

| 8.11.   | STAND ALONE I/O APIC SUPPORT        | 203          |

| 8.12.   | System Reset Logic                  | 203          |

| 8.13.   | Host Interface Logic                | 203          |

| 9. USB  |                                     | 204          |

| 9.1.    |                                     | 205          |

| 9.1.1.  |                                     | 205          |

| 9.1.2.  | List Management                     | 206          |

| 9.2.    | Host Controller                     | 207          |

| 9.2.1.  |                                     | 207          |

| 9.2.2.  | <u> </u>                            | 207          |

| 9.2.3.  | List Processing                     | 207          |

| 10. ID  |                                     | <i>/</i> 208 |

| 10.1.   | IDE Configurations                  | 208          |

| 10.2.   |                                     | 208          |

| 10.2.1. | 3 ,                                 | 209          |

| 10.2.2. | PCI Native Mode                     | 210          |

| 10.3.   | PIO IDE OPERATIONS                  | 210          |

| 10.3.1. | PIO IDE Data Transfer Cycle         | 210          |

| 10.3.2. | 32-Bit PIO IDE Data Transfer Cycle  | 211          |

| 10.3.3. | PIO IDE Data Prefetching and Postin | g211         |

| 10.4.   |                                     | 211          |

| 10.4.1. | Physical Region Descriptor (PRD)    | 212          |

| 10.4.2. | Bus Master Transfer Operation       | 212          |

| 10.5.   |                                     | FION214      |

| 10.5.1. | Ultra DMA/33 Signals                | 214          |

| 10.5.2. | Ultra DMA/33 Operation              | 215          |

| 10.6.   | IDE Data Buffer                     | 216          |

| 11. P   | OWER MANAGEMENT OVERVIEW            | 217          |

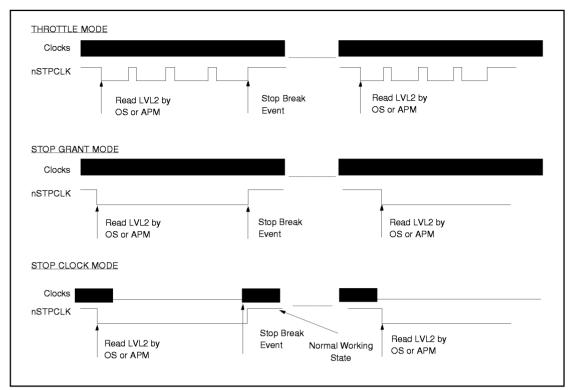

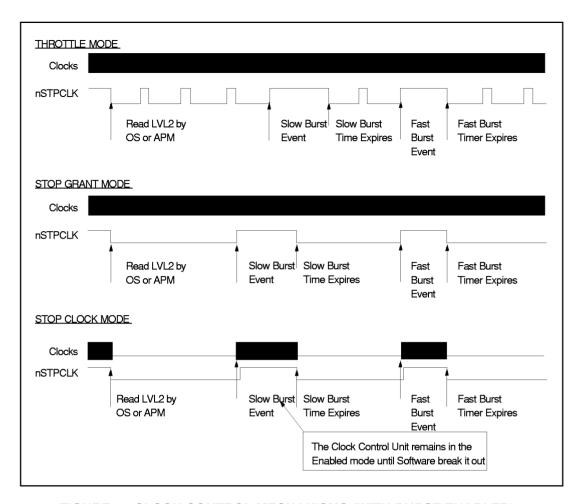

| 11.1.   | System Clock Control                | 219          |

| 11 1 1  | Host Clock Control                  | 221          |

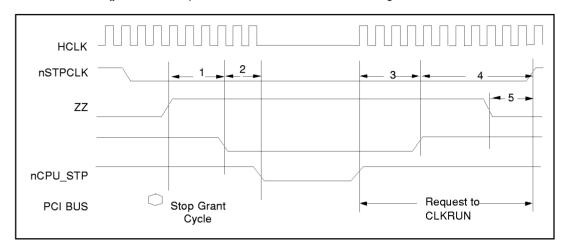

| 11.1.2.    | Stop Clock State Example Sequence                          | 228 |

|------------|------------------------------------------------------------|-----|

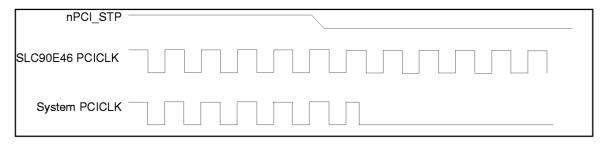

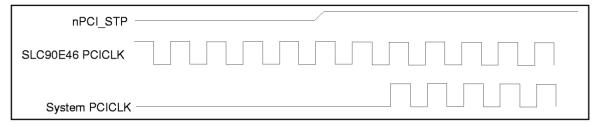

| 11.1.3.    | PCI Clock Control                                          | 230 |

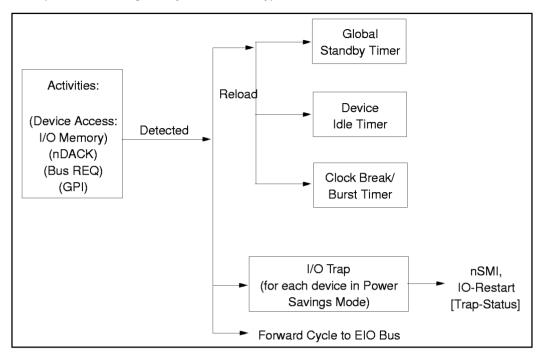

| 11.2. PER  | IPHERAL DEVICE MANAGEMENT                                  | 232 |

| 11.2.1.    | Device Monitor and Idle Timer                              | 233 |

| 11.2.2.    | Device Trap                                                | 233 |

| 11.2.3.    | Peripheral Device Management                               | 234 |

| 11.2.4.    | PCI/ISA Peripheral Devices                                 | 234 |

| 11.2.5.    | Device Specific Details                                    | 236 |

| 11.2.5.1.  | Device 0: IDE Primary Drive 0                              | 236 |

| 11.2.5.2.  | Device 1: IDE Primary Drive 1                              | 237 |

| 11.2.5.3.  | Device 2: IDE Secondary Drive 0                            | 238 |

| 11.2.5.4.  | DEVICE 3: IDE Secondary Drive 1                            | 239 |

| 11.2.5.5.  | DEVICE 4: Audio                                            | 240 |

| 11.2.5.6.  | DEVICE 5: Floppy Disk Drive                                | 241 |

| 11.2.5.7.  | DEVICE 6: Serial Port A                                    | 242 |

| 11.2.5.8.  | DEVICE 7: Serial Port B                                    | 243 |

| 11.2.5.9.  | DEVICE 8: LPT (Parallel Port)                              | 244 |

| 11.2.5.10. | DEVICE 9: Generic I/O Device 0                             | 245 |

| 11.2.5.11. | DEVICE 10: Generic I/O Device 1                            | 246 |

| 11.2.5.12. | DEVICE 11: User Interface (Keyboard, Mouse, Video)         | 247 |

| 11.2.5.13. | DEVICE 12: Cardbus Slot (or Generic I/O and MEM Device)    | 248 |

| 11.2.5.14. | DEVICE 13: Cardbus Slot (or Generic I/O and MEM Device)    | 249 |

| 11.3. Sus  | PEND / RESUME CONTROL MECHANISM                            | 250 |

| 11.3.1.    | Suspend Modes                                              | 250 |

| 11.3.1.1.  | Power On Suspend (POS) Mode                                | 251 |

| 11.3.1.2.  | Suspend to RAM (STR) Mode                                  | 251 |

| 11.3.1.3.  | Suspend to Disk (STD) Mode                                 | 251 |

| 11.3.1.4.  | Mechanical Off (Moff) Mode                                 | 251 |

| 11.3.2.    | System Resume Mechanism                                    | 252 |

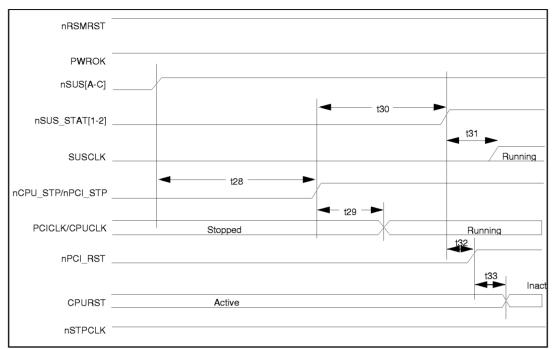

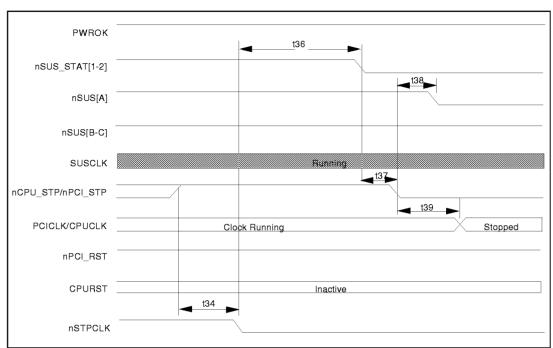

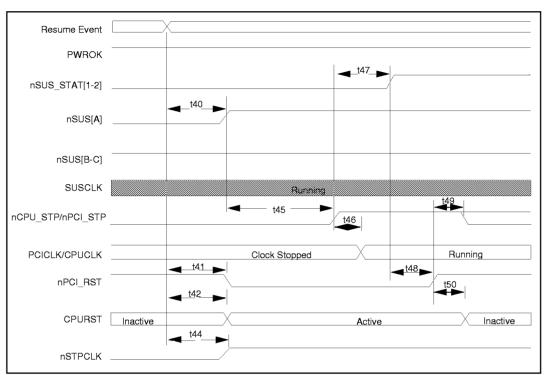

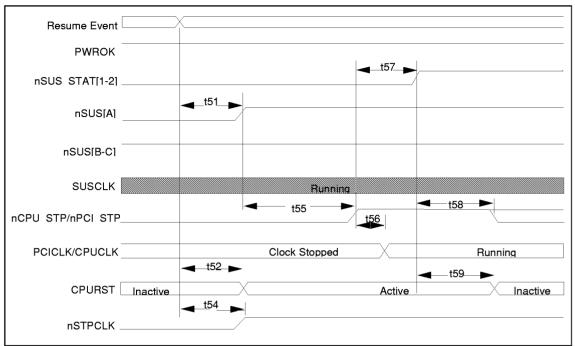

| 11.3.3.    | Suspend and Resume Control Signaling                       | 254 |

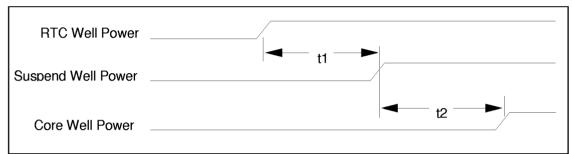

| 11.3.3.1.  | Power Well Timing                                          | 254 |

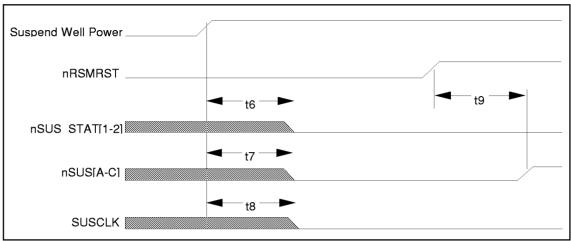

| 11.3.3.2.  | nRSMRST and PWROK Timing                                   | 255 |

| 11.3.3.3.  | Suspend Well Power and RSMRST# Activated Signals           | 256 |

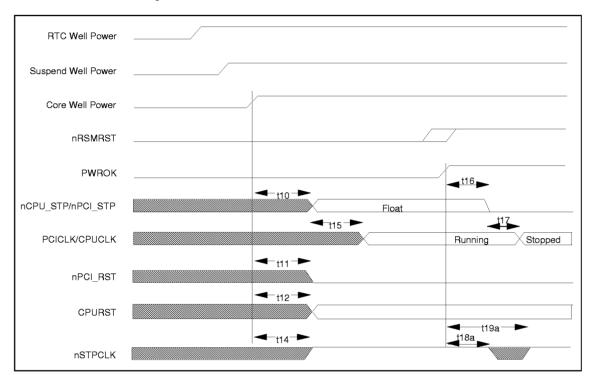

| 11.3.3.4.  | Core Well Power and PWROK Activated Signals (I)            |     |

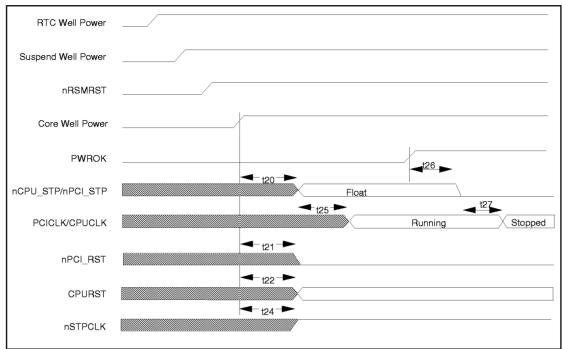

| 11.3.3.5.  | Core Well Power and PWROK Activated Signals (II)           | 259 |

| 11.3.3.6.  | Mechanical Off to On Signal Timing                         | 261 |

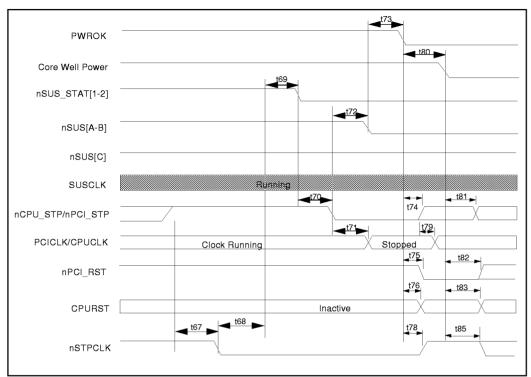

| 11.3.3.7.  | On State to Power on Suspend State Timing                  |     |

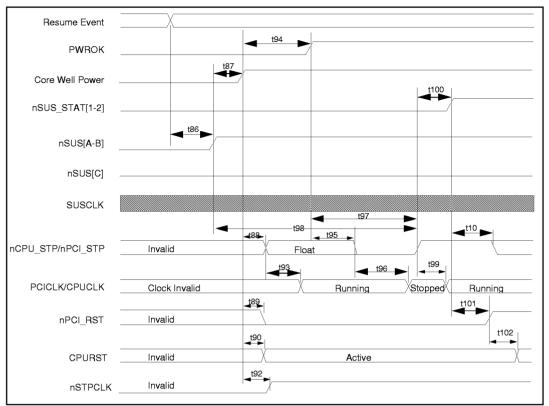

| 11.3.3.8.  | POS to On Signal Timing (I) (with Processor and PCI Reset) |     |

| 11.3.3.9.  | POS to On Signal Timing (II) (with Processor Reset)        |     |

| 11.3.3.10. | POS to On Signal Timing (III) (No Reset)                   | 267 |

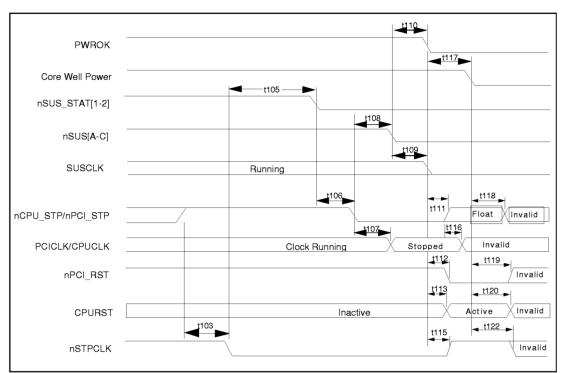

| 11.3.3  | .11. On to STR Signal Timing        | 268 |

|---------|-------------------------------------|-----|

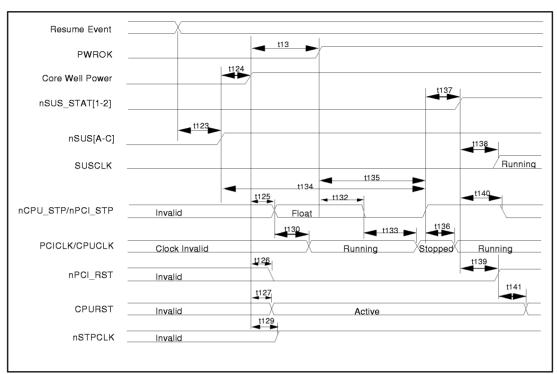

| 11.3.3  | .12. STR to On Signal Timing        | 270 |

| 11.3.3  | .13. On to STD / SOFF Signal Timing | 272 |

| 11.3.3  | .14. STD / SOFF to On Signal Timing | 274 |

| 11.3.4. | Alternate AT Register Access Mode   | 276 |

| 11.4.   | SYSTEM MANAGEMENT                   | 281 |

| 11.4.1. | SMI Assertion Mechanism             | 281 |

| 11.4.2. | nSMI Generation Events              | 281 |

| 11.4.3. | Global Standby Timer                | 285 |

| 11.5.   | ACPI SUPPORT                        | 286 |

| 11.5.1. | SCI Generation                      | 286 |

| 11.5.2. | Power Management Timer              | 286 |

| 11.5.3. | Global Lock Mechanism               | 287 |

| 11.6.   | SYSTEM MANAGEMENT BUS CONTROLLER    | 287 |

| 11.6.1  | .1. Block Read/Write                | 289 |

| 11.6.2. | SMBus Slave Interface               | 290 |

80 Arkay Drive Hauppauge, NY 11788 (516) 435-6000 FAX (516) 273-3123

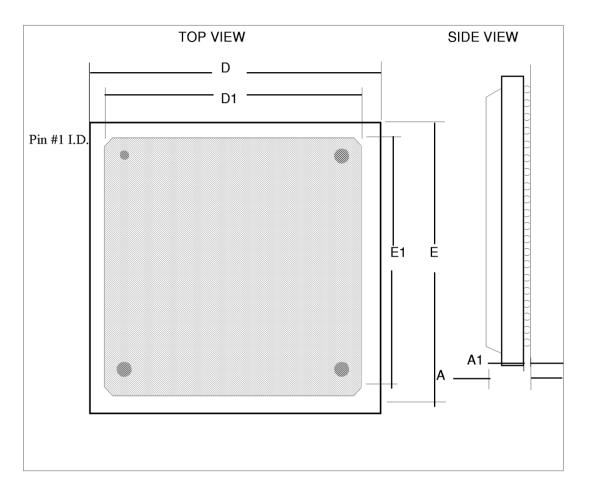

#### 1. SLC90E46 Pinout And Package Specification

The SLC90E46 uses a 324-ball Plastic Ball Grid Array (PBGA) package. These mechanical dimensions and the pinout of the chip are outlined as follows.

#### 1.1. SLC90E46 BGA Package Information

SLC90E46 324-Ball BGA Ball Pattern

# SLC90E46 324-pin Ball Grid Array Package

| SYMBOL | MIN (mm) | NOMINAL (mm) | MAX (mm) |

|--------|----------|--------------|----------|

| Α      | 2.16     | 2.36         | 2.56     |

| A1     | 0.50     | 0.60         | 0.70     |

| D      | 26.80    | 27.00        | 27.20    |

| D1     | 23.90    | 24.00        | 24.10    |

| E      | 26.80    | 27.00        | 27.20    |

| E1     | 23.90    | 24.00        | 24.10    |

| b      | 0.60     | 0.75         | 0.90     |

| е      | 1.07     | 1.27         | 1.47     |

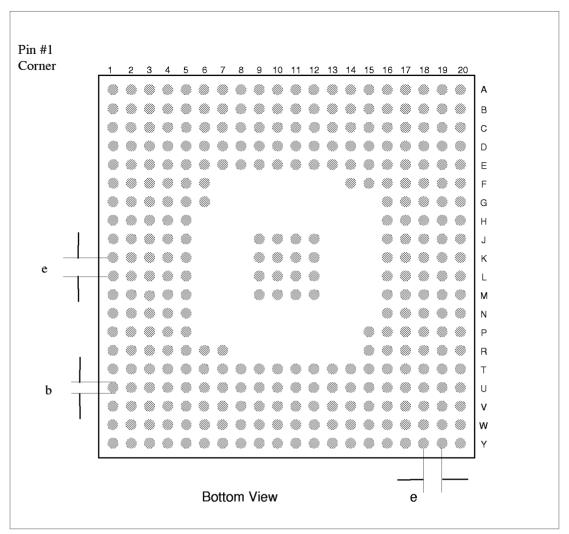

**1.2. SLC90E46 Pin Assignments** The following diagram shows the pin assignment for the SLC90E46.

|              | 2            | 3              | 4              | 5                | 6           | 7        | 8         | 9         | 10       | 11            | 12             | 13               | 14               | 15            | 16         | 17             | 18             | 19                       | 20            |   |

|--------------|--------------|----------------|----------------|------------------|-------------|----------|-----------|-----------|----------|---------------|----------------|------------------|------------------|---------------|------------|----------------|----------------|--------------------------|---------------|---|

| nPCIRST      | ●<br>AD27    | IDSEL          | AD19           | nFRAME           | nSERR       | AD13     | AD9       | AD5       | AD1      | nPCIREQ<br>B  | nPHLD <b>A</b> | SDD6             | SDD4             | SDD13         | SDREQ      | nSDACK         | SDA2           | PDD8                     | PDD7          | А |

| AD31         | AD26         | AD23           | AD18           | nIRDY            | PAR         | AD12     | AD8       | AD4       | AD0      | nPCIREQ<br>C  | nPHOLD         | SDD9             | SDD11            | SDD1          | nSDIOW     | SDA1           | nSDCS1         | PDD9                     | PDD6          | В |

| ●<br>AD30    | AD25         | AD22           | AD17           | nTRDY            | €<br>C/nBE1 | AD11     | G/nBE0    | AD3       | nCLK RUN | NnPCIREQ<br>D | ●<br>SDD7      | SDD5             | SDD3             | SDD14         | nSDIOR     | ●<br>SDA0      | nSDCS3         | PDD10                    | PDD5          | С |

| AD28         | C/nBE3       | AD20           | C/nBE2         | nSTOP            | AD14        | AD10     | AD6       | AD2       | •<br>VSS | POICLK        | SDD8           | SDD10            | SDD2             | SDD15         | SIORDY     | PDD12          | PDD3           | PDD11                    | PDD4          | D |

| AD29         | ●<br>AD24    | AD21           | ●<br>AD16      | nDE <b>V</b> SEL | AD15        | •<br>VSS | ●<br>AD7  | vcc       | nPCIREQ  | voc           | voc            | vss              | SDD12            | SDD0          | vcc        | PDD14          | PDD1           | PDD13                    | PDD2          | Е |

| USBP1+       | GPO28        | ⊕<br>GPO29     | GPO30          | voc              | voc         |          |           |           |          |               |                |                  | voc              | voc           | nPDIOW     | nPDIOR         | PDREQ          | PDD15                    | PDD0          | F |

| nPIRQD       | USBP0+       | GPI21          | GP00           | GPO27            | vcc         |          |           |           |          |               |                |                  |                  |               | PDA0       | PDA2           | PDA1           | nPDACK                   | PIORDY        | G |

| GPI18        | USBP1-       | USBP0-         | GPI19          | GPI20            |             |          |           |           |          |               |                |                  |                  |               | nPDGS3     | nPDCS1         | nAPICOS        | nTHER <b>M</b>           | IRQ0          | Н |

| nOC0         | nOC1         | €<br>GPl14     | NC             | VSS-USB          |             |          |           | vss       | vss      | vss           | •<br>VSS       |                  |                  |               | ●<br>5Vref | NAPIC<br>ACK   | nSTPCLK        | SERIRQ                   | IRQ1          | J |

| nKBCS        | nRTCCS       | ⊕<br>GPl16     | ⊕<br>GPI17     | VCC-USB          |             |          |           | vss       | vss      | vss           | vss            |                  |                  |               | •<br>ZZ    | SPKR           | NAPIC<br>REQ   | nFERR                    | N.G.          | K |

| RTCALE       | GPI13        | CLK48M         | nPCS0          | GPI15            |             |          |           | •<br>VSS  | •<br>VSS | VSS           | •<br>VSS       |                  |                  |               | VOC-RTC    | nIGNNE         | INIT           | INTR                     | •<br>NMI      | L |

| nREQ_A       | nBIOSCS      | n <b>X</b> DIR | n <b>X</b> OE  | •<br>NC          |             |          |           | •<br>VSS  | VSS      | VSS           | •<br>VSS       |                  |                  |               | ●<br>NC    | nRSMRST        | P <b>W</b> RGD | ©<br>CPURST              | n <b>A20M</b> | М |

| nGNT_A       | nREQ_B       | •<br>NC        | nMCCS          | nPOS1            |             |          |           |           |          |               |                |                  |                  |               | vcc-sus    | nSMB           | NC NC          | •                        | nRCIN         | N |

| GATEA20      | nGNT_B       | nREQ_C         | nGNT_C         | nPIRQC           |             |          |           |           |          |               |                |                  |                  | vcc           | LID        | SUSCLK         | ●<br>nRl       | ⊕<br>GPI1                | nSMi          | Р |

| nGPU_<br>STP | nPCI_<br>STP | nPIRQA         | nPIRQB         | •<br>NC          | voc         | voc      |           |           |          |               |                |                  |                  | voc           | vcc-sus    | ©<br>CONFIG1   | GONFIG2        | SMBCLK                   | ⊕<br>RTCX2    | R |

| sD6          | SD3          | OCHRDY         | nIO <b>W</b> R | ●<br>SA16        | vcc         | SYSCLK   | ●<br>SA9  | ■<br>IRQ3 | sA4      | ●<br>SA1      | <br>LA23       | IRQ12/M          | <b>●</b><br>LA18 | nDACK5        | SD9        | nSUS_<br>STAT1 | nSUS_<br>STAT2 | ⊕<br>GPO8                | SMB<br>DATA   | Т |

| IRQ9         | SD2          | nS <b>MW</b> R | SA18           | DREQ3            | DREQ1       | SA11     | ●<br>IRQ5 | sa6       | BALE     | sao           | IRQ10          | LA20             | nDACK0           | n <b>MW</b> R | DREQ6      | DREQ7          |                | nB <b>A</b> TLO <b>W</b> |               | U |

| ●<br>SD7     | DREQ2        | ●<br>SD0       | ●<br>SA19      | nDACK3           | ●<br>SA14   | SA12     | ●<br>IRQ6 | sa7       | TC       | osc           | nIOOS16        | <b>●</b><br>LA21 | IRQ14            | ●<br>nMRD     | nDACK6     | SD11           | nTEST          | nSUSB                    | nEXTSMI       | v |

| RSTDRV       | SD4          | SD1            | nSMRD          | ●<br>SA17        | nDACK1      | nREFRSH  | ●<br>SA10 | IRQ4      | sas      | sA2           | nSBHE          | BQ11             | <b>●</b><br>LA19 | DREQ0         | SD8        | nDACK7         | SD13           | SD15                     | nSUSA         | w |

# 1.3. SLC90E46 Pin Assignment Tables in Alphabetical Order

| SIGNAL                   | BALL NO.    | SIGNAL  | BALL NO.   | SIGNAL        | BALL NO.    |

|--------------------------|-------------|---------|------------|---------------|-------------|

| AD0                      | B10         | nDEVSEL | E5         | LA20          | U13         |

| AD1                      | <b>A</b> 10 | DREQ0   | W15        | LA21          | V13         |

| AD10                     | D7          | DREQ1   | U6         | LA22          | Y13         |

| AD11                     | C7          | DREQ2   | V2         | LA23          | T12         |

| AD12                     | B7          | DREQ3   | U5         | LID           | P16         |

| AD13                     | <b>A</b> 7  | DREQ5   | Y16        | nMCCS         | N4          |

| AD14                     | D6          | DREQ6   | U16        | nMEMCS16      | Y12         |

| AD15                     | E6          | DREQ7   | U17        | nMEMR         | V15         |

| AD16                     | E4          | nEXTSMI | V20        | nMEMW         | U15         |

| AD17                     | C4          | nFERR   | K19        | NMI           | L20         |

| AD18                     | B4          | nFRAME  | A5         | nOC0          | J1          |

| AD19                     | A4          | nGNTA   | N1         | nOC1          | J2          |

| AD2                      | D9          | nGNTB   | P2         | OSC           | V11         |

| AD20                     | D3          | nGNTC   | P4         | PAR           | B6          |

| AD21                     | E3          | nGPI1   | P19        | PCICLK        | D11         |

| AD22                     | C3          | GPI13   | L2         | nPCIREQA      | E10         |

| AD23                     | B3          | GPI14   | J3         | nPCIREQB      | A11         |

| AD24                     | E2          | GPI15   | L5         | nPCIREQC      | B11         |

| AD25                     | C2          | GPI16   | K3         | nPCIREQD      | C11         |

| AD26                     | B2          | GPI17   | K4         | nPCIRST       | A1          |

| AD27                     | <b>A</b> 2  | GPI18   | H1         | nPCI_STP      | R2          |

| AD28                     | D1          | GPI19   | H4         | nPCS0         | L4          |

| AD29                     | E1          | GPI20   | H5         | nPCS1         | N5          |

| AD3                      | C9          | GPI21   | G3         | PD <b>A</b> 0 | G16         |

| AD30                     | C1          | GPO0    | G4         | PDA1          | G18         |

| AD31                     | B1          | GPO8    | T19        | PD <b>A</b> 2 | G17         |

| AD4                      | B9          | GPO27   | G5         | nPDCS1        | H17         |

| AD5                      | <b>A</b> 9  | GPO28   | F2         | nPDCS3        | H16         |

| AD6                      | D8          | GPO29   | F3         | PDD0          | F20         |

| <b>A</b> D7              | E8          | GPO30   | F4         | PDD1          | E18         |

| AD8                      | B8          | IDSEL   | <b>A</b> 3 | PDD10         | C19         |

| AD9                      | <b>A</b> 8  | nIGNNE  | L17        | PDD11         | D19         |

| nAPICACK                 | J17         | INIT    | L18        | PDD12         | D17         |

| nAPICCS                  | H18         | INTR    | L19        | PDD13         | E19         |

| nAPICREQ                 | K18         | nIOCHK  | Y1         | PDD14         | E17         |

| AEN                      | Y4          | IOCHRDY | T3         | PDD15         | F19         |

| A20GATE                  | P1          | nIOCS16 | V12        | PDD2          | E20         |

| n <b>A</b> 20M           | M20         | nIOR    | Y5         | PDD3          | D18         |

| BALE                     | U10         | nIOW    | T4         | PDD4          | D20         |

| nB <b>A</b> TLO <b>W</b> | U19         | nIRDY   | B5         | PDD5          | C20         |

| nBIOSCS                  | M2          | IRQ0    | H20        | PDD6          | B20         |

| nC/BE0                   | C8          | IRQ1    | J20        | PDD7          | <b>A</b> 20 |

| nC/BE1                   | C6          | IRQ3    | T9         | PDD8          | <b>A</b> 19 |

| SIGNAL   | BALL NO.   | SIGNAL  | BALL NO.   | SIGNAL         | BALL NO.    |

|----------|------------|---------|------------|----------------|-------------|

| nC/BE2   | D4         | IRQ4    | <b>W</b> 9 | PDD9           | B19         |

| nC/BE3   | D2         | IRQ5    | U8         | nPDDACK        | G19         |

| CLK48    | L3         | IRQ6    | V8         | PDDREQ         | F18         |

| nCLKRUN  | C10        | IRQ7    | Y8         | nPDIOR         | F17         |

| CONFIG1  | R17        | nIRQ8   | Y20        | nPDIOW         | F16         |

| CONFIG2  | R18        | IRQ9    | U1         | nPHOLD         | B12         |

| CPURST   | M19        | IRQ10   | U12        | nPHLD <b>A</b> | <b>A</b> 12 |

| nCPU_STP | R1         | IRQ11   | W13        | PIORDY         | G20         |

| nDACK0   | U14        | IRQ12/M | T13        | nPIRQA         | R3          |

| nDACK1   | <b>W</b> 6 | IRQ14   | V14        | nPIRQB         | R4          |

| nDACK2   | Y10        | IRQ15   | Y14        | nPIRQC         | P5          |

| nDACK3   | V5         | nKBCCS  | K1         | nPIRQD         | G1          |

| nDACK5   | T15        | LA17    | Y15        | POWEROK        | M18         |

| nDACK6   | V16        | LA18    | T14        | nPWRBTN        | U20         |

| nDACK7   | W17        | LA19    | W14        | nRCIN          | N20         |

| nRI      | P18        | SDD1    | B15        | VCC            | F15         |

|          |            |         |            |                | G6          |

|          |            |         |            |                | P15         |

|          |            |         |            |                | R6          |

|          |            |         |            |                | R7          |

|          |            |         |            |                | R15         |

|          |            |         |            |                | T6          |

| nRSMRST  | M17        | SDD10   | D13        |                |             |

| RTCALE   | L1         | SDD11   | B14        |                |             |

| nRTCCS   | K2         | SDD12   | E14        |                |             |

| RTCX1    | N19        | SDD13   | A15        |                |             |

| RTCX2    | R20        | SDD14   | C15        |                |             |

| nREFRESH | <b>W</b> 7 | SDD15   | D15        |                |             |

| nREQA    | M1         | SDD2    | D14        | VCC-RTC        | L16         |

| nREQB    | N2         | SDD3    | C14        | VCC-SUS        | N16         |

|          |            |         |            |                | R16         |

| nREQC    | P3         | SDD4    | A14        |                |             |

| RSTDRV   | W1         | SDD5    | C13        | VCC-USB        | K5          |

| SA0      | U11        | SDD6    | A13        | VREF           | J16         |

| SA1      | T11        | SDD7    | C12        | VSS            | D10         |

|          |            |         |            |                | E7          |

| SA10     | Q8         | SDD8    | D12        |                |             |

| SIGNAL       | BALL NO.    | SIGNAL     | BALL NO.    | SIGNAL  | BALL NO.   |

|--------------|-------------|------------|-------------|---------|------------|

| SA11         | U7          | SDD9       | B13         | VSS     | E13        |

|              |             |            |             |         | J9         |

|              |             |            |             |         | J10        |

|              |             |            |             |         | J11        |

|              |             |            |             |         | J12        |

|              |             |            |             |         | K9         |

|              |             |            |             |         | K10        |

|              |             |            |             |         | K11        |

|              |             |            |             |         | K12        |

|              |             |            |             |         | L9         |

|              |             |            |             |         | L10        |

|              |             |            |             |         | L11        |

|              |             |            |             |         | M9         |

|              |             |            |             |         | M10        |

| SA12         | V7          | nSDDACK    | A17         |         |            |

| SA13         | Y7          | SDDREQ     | A16         |         |            |

| SA14         | V6          | nSDIOR     | C16         |         |            |

| SA15         | Y6          | nSDIOW     | B16         |         |            |

| SA16         | T5          | nSERR      | A6          |         |            |

| SA17         | W5          | SIORDY     | D16         |         |            |

| SA18         | U4          | SERIRQ     | J19         |         |            |

| SA19         | V4          | nSLP       | K20         |         |            |

| SA2          | W11         | nSMBALERT  | N17         |         |            |

| SA3          | Y11         | SMBCLK     | R19         |         |            |

| SA4          | T10         | SMBDATA    | T20         |         |            |

| SA5          | <b>W</b> 10 | nSMEMR     | W4          |         |            |

| SA6          | U9          | nSMEMW     | U3          |         |            |

| SA7          | V9          | nSMI       | P20         | VSS     | M11<br>M12 |

| SA8          | Y9          | SPKR       | K17         |         |            |

| SA9          | T8          | nSTOP      | D5          | VSS-USB | J5         |

| nSBHE        | <b>W</b> 12 | nSTPCLK    | J18         | nXDIR   | M3         |

| SD0          | V3          | nSUSA      | <b>W</b> 20 | nXOE    | M4         |

| SD1          | <b>W</b> 3  | nSUSB      | V19         | nZEROWS | Y3         |

| SD10         | Y17         | nSUSC      | U18         | ZZ      | K16        |

| SD11         | V17         | SUSCLK     | P17         | N.C.    | J4         |

|              |             |            |             |         | M5         |

|              |             |            |             |         | M16        |

|              |             |            |             |         | N3         |

|              |             |            |             |         | N18        |

| SD12         | Y18         | nSUS STAT1 | T17         |         | R5         |

| SD12<br>SD13 | W18         | nSUS_STATE | T18         |         |            |

|              | Y19         | SYSCLK     | T7          |         |            |

| SD14<br>SD15 | W19         | TC         | V10         |         |            |

|              |             |            |             |         |            |

| SD2          | U2          | nTEST      | V18         |         |            |

| SIGNAL | BALL NO.    | SIGNAL | BALL NO. | SIGNAL | BALL NO. |

|--------|-------------|--------|----------|--------|----------|

| SD3    | T2          | nTHRM  | H19      |        |          |

| SD4    | W2          | nTRDY  | C5       |        |          |

| SD5    | Y2          | USBP0+ | G2       |        |          |

| SD6    | T1          | USBP0- | H3       |        |          |

| SD7    | V1          | USBP1+ | F1       |        |          |

| SD8    | <b>W</b> 16 | USBP1- | H2       |        |          |

| SD9    | T16         | VCC    | E9       |        |          |

|        |             |        | E11      |        |          |

|        |             |        | E12      |        |          |

|        |             |        | E16      |        |          |

|        |             |        | F5       |        |          |

|        |             |        | F6       |        |          |

|        |             |        | F14      |        |          |

| SDA0   | C17         |        |          |        |          |

| SDA1   | B17         |        |          |        |          |

| SDA2   | <b>A</b> 18 |        |          |        |          |

| nSDCS1 | B18         |        |          |        |          |

| nSDCS3 | C18         |        |          |        |          |

| SDD0   | E15         |        |          |        |          |

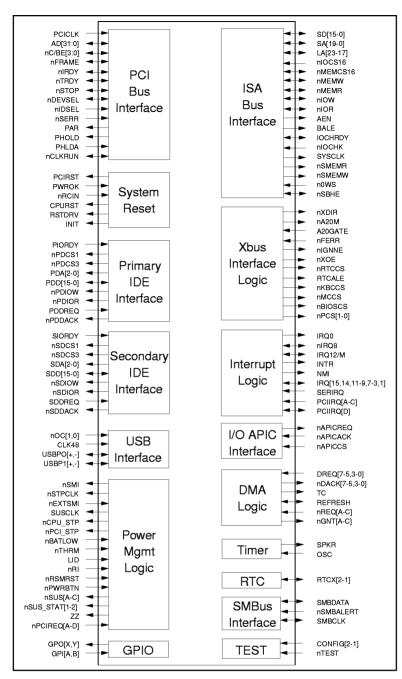

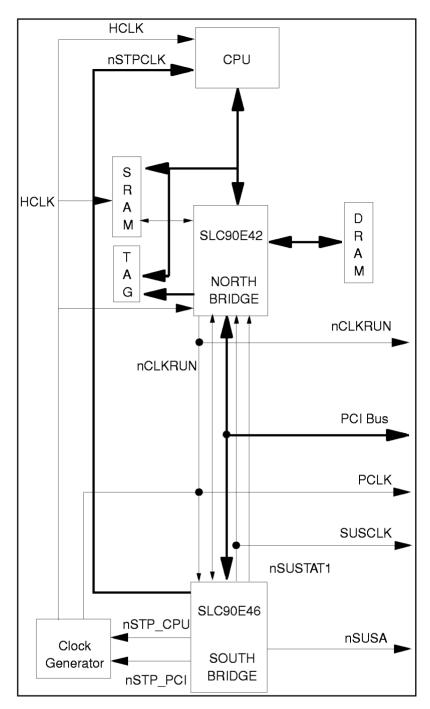

FIGURE 1 - SLC90E46 BLOCK DIAGRAM

#### 2. SLC90E46 Functional Block Overview

The SLC90E46 is a high integration, multiple functions chip. Below is a brief overview of the major functional blocks in the SLC90E46.

#### 2.1. PCI-to-ISA/EIO Bridge

The SLC90E46 is compatible with the PCI 2.1 specification, as well as the ISA bus specification. The SLC90E46 operates as a PCI master for internal modules, such as the IDE controller, USB controller, DMA controller, distributed DMA masters, and ISA masters. The SLC90E46 operates as a slave for its internal registers and for cycles that are passed to the ISA or EIO buses. The SLC90E46 positively decodes all internal registers.

The SLC90E46 can be configured for a full ISA bus or a subset of the ISA bus called the Extended IO (EIO) bus. When EIO bus is configured, unused signals can be configured for General Purpose Inputs and Outputs. Like standard ISA bridge chips, the SLC90E46 also provides byte-swap logic, I/O recovery support, wait-state generation, and SYSCLK generation. Chip select signals are also generated for keyboard controller, BIOS, external RTC, external microcontroller, and two programmable chip selects. The SLC90E46 is designed to directly drive up to 5 ISA slots without external data or address buffering.

The SLC90E46 can be configured as either a subtractive decode PCI to ISA bridge or as positive decode bridge. This allows a system designer to place another subtractive decode bridge in the system, such as a PCI docking chip.

#### 2.1.1. DMA CONTROLLERS, TIMER/COUNTERS, AND INTERRUPT CONTROLLERS

The DMA controllers contain seven independently programmable channels. Channels [0-3] are hardwired to 8-bit, count-by-byte transfers, and channels [5-7] are hardwired to 16-bit, count-by-word transfers. Each of the seven DMA channels can be programmed to support fast Type-F transfers.

The DMA controller supports two different methods for handling legacy DMA via the PCI bus. The Distributed DMA method allows reads and writes to 8237 registers to be distributed to other PCI slave devices. The PC/PCI protocol allows PCI-based peripherals to initiate DMA cycle by encoding requests and grants through three PC/PCI nREQ/nGNT pairs. The two methods can be used concurrently.

The integrated 82C54 controller provides three counters that are used to provide the system timer function, refresh request, and speaker tone. A 14.31818 MHz oscillator input provides the clock source for these three counters.

The SLC90E46 integrates two 8259 interrupt controllers. The two interrupt controllers are cascaded so that 14 external and two internal interrupts are possible. The SLC90E46 also supports a serial interrupt scheme.

#### 2.1.2. RTC

The SLC90E46 contains a Motorola MC146818A-compatible real-time clock with 256 bytes of battery backed RAM. The RTC operates on a 32.768 Khz crystal. The RTC is integrated to keep track of the time of day and storing system data.

The RTC also supports two lockable memory ranges. By setting bits in the configuration space, two 8-byte ranges can be locked to read and write accesses, that prevents unauthorized reading of passwords or other system security information..

#### 2.1.3. GPIO and Chip Selects

The SLC90E46 provides various general purpose inputs and outputs for custom system design. The number of inputs and outputs varies depending on the configuration. The SLC90E46 also provides two programmable chip selects which allow designer to place devices on the X-Bus without the needs for external decoding logic.

#### 2.2. PCI IDE Controller

The SLC90E46 IDE controller supports two IDE channels, up to four IDE devices such as IDE hard disks and CD-ROM drives. Each IDE device can have independent timings. The IDE transfer rate can be up to 14 Mbytes/second in PIO mode, or 33 Mbytes/second in bus master mode. A 16-by- 32-bit buffer is implemented for each channel so that both channels can operate concurrently and achieve optimal transfers.

The two IDE signal channels are electrically isolated. They can be configured to the standard primary and secondary channel (4 devices) or primary drive 0 and primary drive 1 (2 devices). It allows flexibility in system design and device power management.

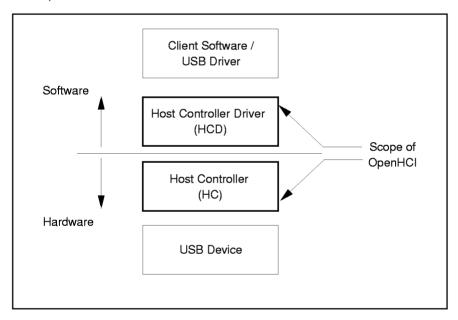

#### 2.3. Enhanced Universal Serial Bus (USB) Controller

The SLC90E46 provides Open Host Controller Interface (OHCI) USB support. This includes support that allow legacy software to use a USB-based keyboard and mouse.

#### 2.4. Power Management

The SLC90E46 power management functions include enhanced clock control, local and global device monitoring, and various low-power (suspend) states, such as Power-On Suspend, Suspend-to-RAM, and Suspend-to-Disk. A hardware-based thermal management circuit allows software-transparent entrance to low-power states. Various external events, such as notebook lid open/close, modem/phone ring, suspend/resume button, battery low warning signals can be connected to the dedicated pins of the SLC90E46. It also contains full support for the ACPI specification.

The SLC90E46 also integrates a SMBus Host controller, which includes a Host interface for the CPU to communicate with SMBus slaves and a Slave interface that allows external masters to activate power management events.

#### 3. The SLC90E46 Signal Description

This section provides a detailed description of each SLC90E46 signal. The signals are arranged in functional groups according to their associated function.

The 'n' symbol at the beginning of a signal name indicates that it is an active low signal. When 'n' is not present before the signal name, it indicates an active high signal.

The term **assert** or **assertion** indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term **negate** or **negation** indicates that a signal is inactive.

Certain signals have different functions, depending on the configuration programmed in the PCI configuration space. This signal whose function is being described is in bold font.

The term **High-Z** means tri-stated.

The term **Undefined** means the signal could be high, low, tri-stated, or in some in-between level.

The following notations are used to describe the signal type.

- I Input is an input-only signal.

- O Totem pole output is a standard active driver.

- I/O Input/Output is a bi-directional, tri-state input/output pin.

- **OD** Open drain.

- **I/OD** Input/Open Drain Output is a standard input buffer with an Open Drain Output.

- s/t/s Sustained tri-state is an active low tri-state signal owned and driven by one and only one agent at a time. The agent that drives a s/t/s pin low must drive it high for at least one clock before letting it float. A new agent can not start driving a s/t/s signal any sooner than one clock after the previous owner tri-states it. An external pull-up resistor is required to sustain the inactive state until another agent drives it and must be provided by the central resource.

- V This is a power supply pin.

All 3V output signals can drive 5V TTL inputs. Most of the 3V input signals are 5V tolerant. The 3V input signals which are powered via the RTC or Suspend power planes should not exceed their power supply voltage. The open drain (OD) CPU interface signals should be pulled up to the CPU interface signal voltages.

## 3.1. PCI Interface

| NAME       | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD[31-0]   | I/O  | Address/Data. PCI address and data lines. Address is driven with nFRAME asserted, data is driven or received in following clocks.                                                                                                                                                                                                                                                                                                                                       |

|            |      | During Reset: High-Z After Reset: High-Z During POS: High-Z                                                                                                                                                                                                                                                                                                                                                                                                             |

| C/nBE[3-0] | 1/0  | <b>Command/Byte Enable.</b> The command is driven with nFRAME asserted, byte enables corresponding to supplied or requested data is driven in following clocks. C/nBE0 applies to byte 0, C/nBE1 applies to byte 1, etc.                                                                                                                                                                                                                                                |

|            |      | During Reset: High-Z After Reset: High-Z During POS: High-Z                                                                                                                                                                                                                                                                                                                                                                                                             |

| nFRAME     | I/O  | <b>FRAME.</b> Its assertion indicates the address phase of a PCI transfer. Negation indicates that one more data transfer will be followed. nFRAME remains tri-stated until driven by the SLC90E46 as an initiator.                                                                                                                                                                                                                                                     |

|            |      | During Reset: High-Z After Reset: High-Z During POS: High-Z                                                                                                                                                                                                                                                                                                                                                                                                             |

| nDEVSEL    | 1/O  | <b>Device Select.</b> The SLC90E46 asserts nDEVSEL to claim a PCI transaction through positive decoding or subtractive decoding (if enabled). As an output, the SLC90E46 asserts nDEVSEL when it samples IDSEL active in configuration cycles to SLC90E46 configuration registers. The SLC90E46 also asserts nDEVSEL when an internal SLC90E46 register is accessed or when the SLC90E46 subtractively or positively decodes a cycle for the ISA/EIO bus or IDE device. |

|            |      | As an input, nDEVSEL indicates the response to a SLC90E46 initiated transaction and is also sampled when deciding whether to subtractively decode the cycle.                                                                                                                                                                                                                                                                                                            |

|            |      | nDEVSEL is asserted or sampled at medium decode time. It remains tri-stated until driven by the SLC90E46 as a target.                                                                                                                                                                                                                                                                                                                                                   |

|            |      | During Reset: High-Z After Reset: High-Z During POS: High-Z                                                                                                                                                                                                                                                                                                                                                                                                             |

| nIRDY      | 1/0  | Initiator Ready. The signal is asserted when the SLC90E46 is ready for a data transfer. A data phase is completed on any clock both nIRDY and nTRDY are sampled asserted.  nIRDY is an input to the SLC90E46 when the SLC90E46 is the target and an output when the SLC90E46 is an initiator. It remains tri-stated until driven by the SLC90E46 as a master.                                                                                                           |

|            |      | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|            |      | During Reset: High-Z After Reset: High-Z During POS: High-Z                                                                                                                                                                                                                                                                                                                                                                                                             |

| NAME   | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                          |

|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nTRDY  | I/O  | <b>Target Ready.</b> The signal is asserted when the SLC90E46 is ready for a data transfer. A data phase is completed on any clock both nIRDY and nTRDY are sampled asserted.                                                                                                                        |

|        |      | nTRDY is an input to the SLC90E46 when the SLC90E46 is the initiator and an output when the SLC90E46 is a target. It remains tristated until driven by the SLC90E46 as a target.                                                                                                                     |

|        |      | During Reset: High-Z After Reset: High-Z During POS: High-Z                                                                                                                                                                                                                                          |

| nSTOP  | 1/0  | <b>Stop.</b> nSTOP indicates that the SLC90E46, as a Target, is requesting the initiator to stop the current transaction. As an initiator, nSTOP causes the SLC90E46 to stop the current transaction.                                                                                                |

|        |      | nSTOP is an output when the SLC90E46 is a Target and an input when the SLC90E46 is an initiator. nSTOP is tri-stated from the leading edge of nPCIRST., and it remains tri-stated until driven by the SLC90E46 as a slave.                                                                           |

|        |      | During Reset: High-Z After Reset: High-Z During POS: High-Z                                                                                                                                                                                                                                          |

| IDSEL  | I    | Initialization Device Select. IDSEL is used as a chip select during PCI configuration read and write cycles. The SLC90E46 samples IDSEL during the address phase of a transaction. The SLC90E46 responds by asserting nDEVSEL if nIDSEL is sampled active during configuration cycle.                |

| nPHLD  | 0    | PCI Hold. The SLC90E46 asserts nPHLD to indicate its desire to use the PCI bus. nPHLD has the highest priority among the five bus request signals. Once the request is granted, nPHLDA will remain asserted until the nPHLD is de-asserted.  During Reset: High-Z After Reset: High During POS: High |

| nPHLDA | 1    | PCI Hold Acknowledge. When it is asserted, it indicates that the                                                                                                                                                                                                                                     |

|        |      | SLC90E46 has been granted use of the PCI bus. Once it is asserted, nPHLDA cannot be de-asserted until nPHLD is de-asserted first.                                                                                                                                                                    |

| nSERR  | 1/0  | System Error. nSERR can be driven active by any PCI device that detects a system error condition. Upon sampling nSERR active, the SLC90E46 can be programmed to generate a non-maskable interrupt (NMI) to the CPU.                                                                                  |

|        |      | During Reset: High-Z After Reset: High-Z During POS: High-Z                                                                                                                                                                                                                                          |

| NAME    | TYPE               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PAR     | 0                  | Parity. PAR is "even" parity and is calculated on 36 bits (AD[31-0] and C/BE[3-0]#). PAR is calculated on 36 bits regardless of the valid byte enables. PAR is driven and tri-stated identically to the AD[31-0] lines except that PAR is delayed by exactly one PCI clock.  PAR is an output during the address phase for all SLC90E46 initiated transactions. It is also an output during the data phase when the SLC90E46 is the initiator of a PCI write transaction, and when it is the target of a read transaction.  During Reset: High-Z After Reset: High-Z During POS: High-Z |

| nCLKRUN | I/O<br>3.3V/5<br>V | Clock Run Enable. SLC90E46 uses this signal to communicate to PCI peripherals that the PCI clock will be stopped. Peripherals can assert nCLKRUN to request that the PCI clock be restarted or to keep it from stopping. The nCLKRUN protocol is specified in the PCI Mobile Design Guide Revision 1.0.                                                                                                                                                                                                                                                                                 |

| DOIDOT  |                    | During Reset: Low After Reset: Low During POS: High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |