# Ethernet/IEEE 802.3 LAN Controller Advance Data Sheet

# **FEATURES**

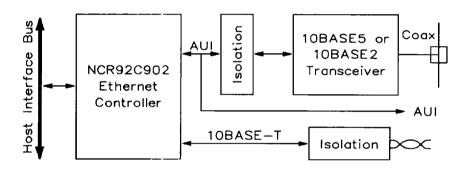

- Integrated Controller, MENDEC and 10BASE-T solution for IEEE 802.3 Local Area Networks (LANs)

- CMOS technology, 5-volt supply

- No external precision components required

- Available in 84-pin PLCC and 100-pin PQFP

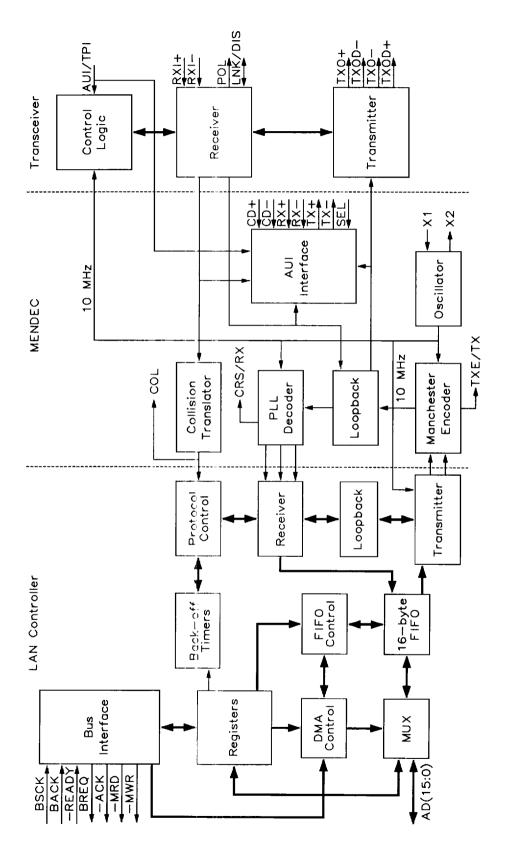

## LAN Controller

- Supports industry standard 8-, 16-, and 32-bit microprocessor interfaces

- Offers three loopback modes:

- □ Controller only

- □ Controller and MENDEC

- □ Controller, MENDEC, and transceiver

- 16-byte internal FIFO with programmable threshold control

- Contains two 16-bit DMA channels

- Provides network statistics storage

- Supports physical, multicast, and broadcast address filtering

#### **MENDEC**

- Provides Manchester encoding/decoding

- Provides 802.3 AUI media interface for 10BASE5 or the NCR92C392 10BASE2 transceiver

- Generates a receive clock from receive data

- External half- or full-step mode of operation at transmit output

- Internal 20 MHz system clock

- Tolerates up to ±20 ns jitter on incoming data

#### 10BASE-T Transceiver

- Meets IEEE 10BASE-T standard for link integrity, AUI and twisted pair squelch, collision detection, SQE test, jabber, and AUI loopback

- High-speed receiver architecture minimizes jitter (patent pending)

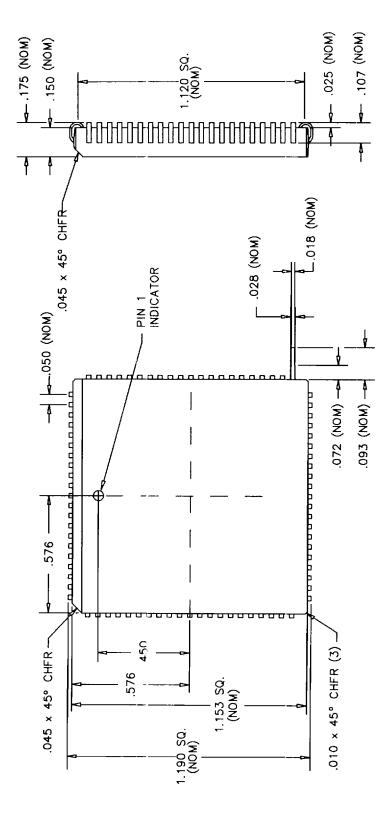

Figure 1 84-pin Plastic Leaded Chip Carrier (PLCC)

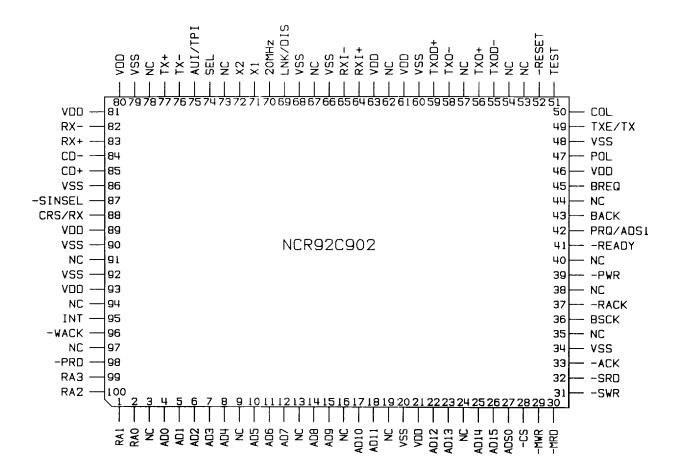

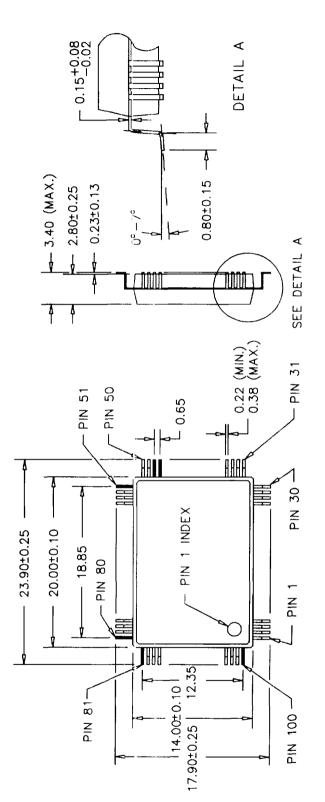

Figure 2 100-pin Plastic Quad Flat Pack (PQFP)

# **Pinout Summary**

|             |        | Pin            | No.             |                              |

|-------------|--------|----------------|-----------------|------------------------------|

| Signal Name | Туре   | 84-pin<br>PLCC | 100-pin<br>PQFP | Pin Descriptions             |

| RA1         | Input  | 10             | 1               | Register Address             |

| RA0         | Input  | 11             | 2               | Register Address             |

| NC          | ł      | -              | 3               | No Connect                   |

| AD0         | In/Out | 12             | 4               | Multiplexed Address/Data Bus |

| AD1         | In/Out | 13             | 5               | Multiplexed Address/Data Bus |

| AD2         | In/Out | 14             | 6               | Multiplexed Address/Data Bus |

| AD3         | In/Out | 15             | 7               | Multiplexed Address/Data Bus |

| AD4         | In/Out | 16             | 8               | Multiplexed Address/Data Bus |

| NC          | -      |                | 9               | No Connect                   |

| AD5         | In/Out | 17             | 10              | Multiplexed Address/Data Bus |

| AD6         | In/Out | 18             | 11              | Multiplexed Address/Data Bus |

| AD7         | In/Out | 19             | 12              | Multiplexed Address/Data Bus |

| NC          | _      |                | 13              | No Connect                   |

| AD8         | In/Out | 20             | 14              | Multiplexed Address/Data Bus |

2

# Pinout Summary [continued]

|             |             | Pin            | No.             |                                               |  |

|-------------|-------------|----------------|-----------------|-----------------------------------------------|--|

| Signal Name | Туре        | 84-pin<br>PLCC | 100-pin<br>PQFP | Pin Descriptions                              |  |

| AD9         | In/Out      | 21             | 15              | Multiplexed Address/Data Bus                  |  |

| NC          |             | _              | 16              | No Connect                                    |  |

| AD10        | In/Out      | 22             | 17              | Multiplexed Address/Data Bus                  |  |

| AD11        | In/Out      | 23             | 18              | Multiplexed Address/Data Bus                  |  |

| NC          | _           | 24             | 19              | No Connect                                    |  |

| NC          |             | 25             |                 | No Connect                                    |  |

| VSS         | Ground      | 26             | 20              | Ground                                        |  |

| VDD         | Power       | 27             | 21              | Power                                         |  |

| AD12        | In/Out      | 28             | 22              | Multiplexed Address/Data Bus                  |  |

| AD13        | In/Out      | 29             | 23              | Multiplexed Address/Data Bus                  |  |

| NC          | _           |                | 24              | No Connect                                    |  |

| AD14        | In/Out      | 30             | 25              | Multiplexed Address/Data Bus                  |  |

| AD15        | In/Out      | 31             | 26              | Multiplexed Address/Data Bus                  |  |

| ADS0        | In/Out      | 32             | $\frac{1}{27}$  | Address Strobe 0                              |  |

| -CS         | Input       | 33             | 28              | Chip Select (active low)                      |  |

| -MWR        | Output      | 34             | 29              | Master Write Strobe (active low)              |  |

| -MRD        | Output      | 35             | 30              | Master Read Strobe (active low)               |  |

| -SWR        | Input       | 36             | 31              | Slave Write Strobe (active low)               |  |

| -SRD        | Input       | 37             | 32              | Slave Read Strobe (active low)                |  |

| -ACK        | Output      | 38             | 33              | Acknowledge (active low)                      |  |

| VSS         | Ground      | 39             | 34              | Ground                                        |  |

| NC          | Ground      |                | 35              | No Connect                                    |  |

| BSCK        | Input       | 40             | 36              | Bus Clock                                     |  |

| -RACK       | <del></del> | 41             | 37              | Read Acknowledge (active low)                 |  |

| NC NC       | Input       | 41             | 38              | No Connect                                    |  |

| -PWR        | Output      | 42             | 39              | Port Write (active low)                       |  |

| NC<br>NC    | Output      | 42             | $\frac{1}{40}$  | No Connect                                    |  |

| -READY      | Immut       | 43             | <del> </del>    |                                               |  |

|             | Input       | 43             | 41              | Ready (active low)                            |  |

| PRQ/ADS1    | Output      |                | 42              | Port Request/Address Strobe 1                 |  |

| BACK        | Input       | 45             | 43              | Bus Acknowledge                               |  |

| NC          | -           | -              | 44              | No Connect                                    |  |

| BREQ        | Output      | 46             | 45              | Bus Request                                   |  |

| VDD         | Power       | 47             | 46              | Power                                         |  |

| POL         | Output      | 48             | 47              | Polarity                                      |  |

| VSS         | Ground      | 49             | 48              | Ground                                        |  |

| TXE/TX      | Output      | 50             | 49              | Transmit Enable/Transmit                      |  |

| COL         | Output      | 51             | 50              | Collision                                     |  |

| TEST        | Input       | 52             | 51              | TEST should be tied low for normal operation. |  |

| -RESET      | Input       | 53             | 52              | Reset (active low)                            |  |

| NC NC       | _           |                | 53              | No Connect                                    |  |

| NC          | -           |                | 54              | No Connect                                    |  |

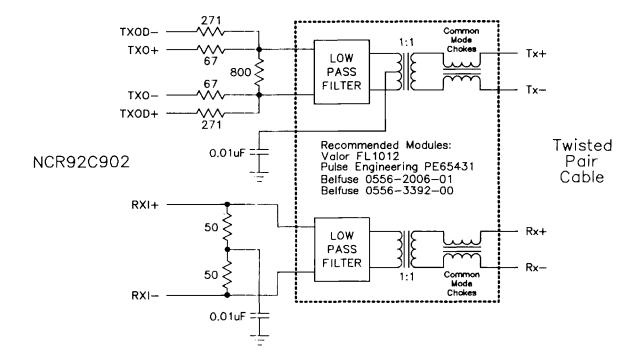

| TXOD-       | Output      | 54             | 55              | Twisted Pair Transmit Output Delay Minus      |  |

| TXO+        | Output      | 55             | 56              | Twisted Pair Transmit Output Plus             |  |

| NC          |             |                | 57              | No Connect                                    |  |

| TXO-        | Output      | 56             | 58              | Twisted Pair Transmit Output Minus            |  |

| TXOD+       | Output      | 57             | .59             | Twisted Pair Transmit Output Delay Plus       |  |

# NCR92C902

# Pinout Summary [continued]

|        | Pin No.                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|--------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Type   | 84-pin<br>PLCC                               | 100-pin<br>PQFP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Ground | 58                                           | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Power  | 59                                           | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| _      |                                              | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | No Connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Power  | 60                                           | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Input  | 61                                           | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Twisted Pair Receive Input Plus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|        | 62                                           | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Twisted Pair Receive Input Minus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Ground | 63                                           | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| -      | ,                                            | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | No Connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Ground | 64                                           | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|        | 65                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | No Connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| _      | 66                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | No Connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| In/Out | 67                                           | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Link/Link Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|        | 68                                           | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20 MHz signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|        |                                              | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Crystal or External Oscillator input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|        |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Crystal feedback output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| -      |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | No Connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Input  | 71                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Mode Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|        |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | AUI/TPI Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|        | L                                            | <u></u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | AUI Transmit Minus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|        |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | AUI Transmit Plus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| _      |                                              | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | No Connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Ground | 75                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|        |                                              | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|        | 77                                           | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|        | 78                                           | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | AUI Receive Minus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|        |                                              | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | AUI Receive Plus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|        |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | AUI Collision Input Minus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|        |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | AUI Collision Input Plus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|        |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|        |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -SNISEL should be tied high for normal operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|        |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Carrier Sense/Receive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|        |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|        |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

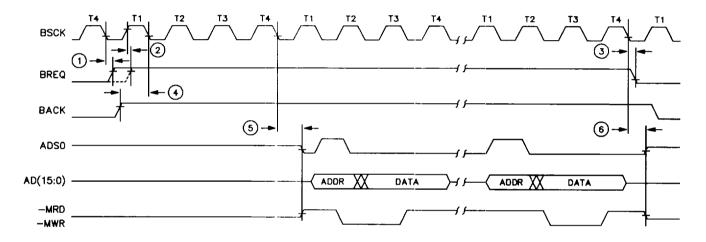

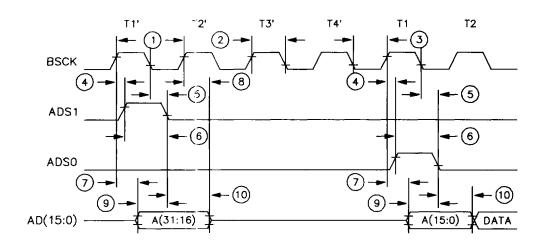

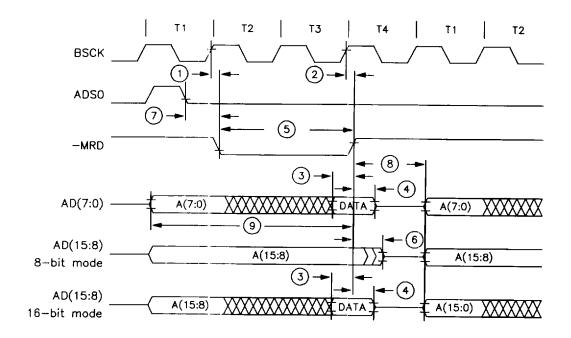

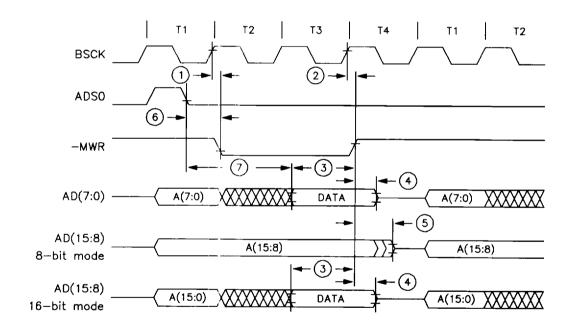

| _      |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | No Connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |