# Programming the NS32FX200 to Drive a Thermal Print Head Printer

1.0 INTRODUCTION

The NS32FX200 is a highly integrated system chip that is designed especially for fax systems based on National Semiconductor's NS32FX161, NS32FX164 or NS32FV16 embedded processors.

The NS32FX200 printer controller:

- Supports a direct interface to a variety of Thermal Print Head (TPH) printers.

- Enables adjustment of the duration of print strobes according to the TPH temperature.

- Provides a programmable strobe mode, strobe cycle, duty cycle and polarity.

- Provides on-chip TPH temperature sensing circuitry.

- Enables variable speeds of thermal paper movement.

- Provides an on-chip bitmap shifter.

- · Supports a variety of document sizes.

This document describes how to program the NS32FX200 printer controller for generating Printing Strobes and Serial Bitmap Input for a TPH printer.

For a complete description and listing of the TPH printer handlers for the NS32FX200 based FAX system please refer to the National Semiconductor Series 32000 Embedded Processors NSFAX Software Reference Manual revision P4.0.

## 2.0 GENERAL DESCRIPTION OF A TPH PRINTER

A Thermal Print Head (TPH) printer has three main elements: a serial-in parallel-out shift register, a TPH and a stepper motor.

The shift register receives the bitmap lines serially from the external printer controller, and latches them inside the TPH printer. The TPH printer prints the image lines on the thermal paper, one at a time, using the print strobes generated by the external printer controller. The stepper motor moves the thermal paper over the printing element.

National Semiconductor Application Note 819 Ziv Azmanov August 1992

A TPH is comprised of heat-generating resistors formed on a ceramic substrate. It uses heat to record images by electrically energizing individual resistors on heat sensitive paper, thermal transfer ribbon or other heat sensitive media.

#### 2.1 Print Strobe Control

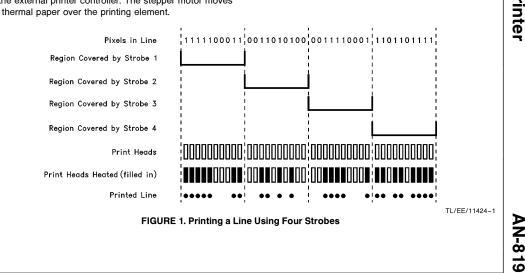

The TPH printer has a printing head for each pixel. A print strobe heats those heads whose pixel is set to 1. Each heated head generates a black dot on the thermal paper. Several strobes are used to print one line. Each strobe heats pixels in a different part of the line (Note 1).

## 2.2 The Printer Data Path

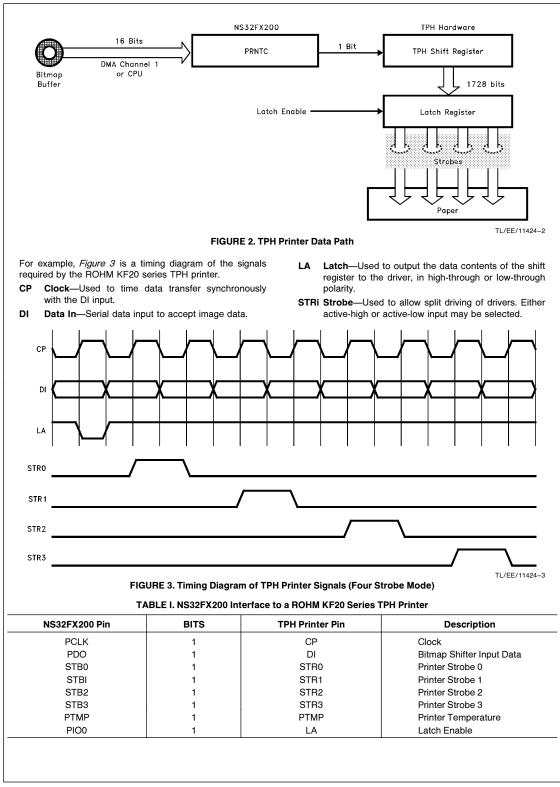

The data path in a TPH printer is a pipeline consisting of the following stages:

1. Send a line to the TPH by transfering a bitmap line from the memory buffer, via the NS32FX200 Bitmap Shifter, to the TPH shift register.

If DMA channel 1 of the NS32FX200 is dedicated to the printer (Note 2), the DMA performs the transfer. Otherwise, the CPU should be used to move the data from external memory to the internal bitmap shifter of the NS32FX200.

- Latch the line that is in the TPH by loading the data that is stored in the TPH shift register, into the latch register.

- Print by using strobes to heat every TPH element whose corresponding bit in the TPH latch is set, so that it will print a black dot.

- Note 1: This is done to reduce the current consumption. Driving all the pixels simultaneously would require a more expensive power supply.

- Note 2: The NS32FX200 DMA channel 1 is originally designed to work as an internal channel dedicated to the printer bitman shifter, but the user can choose to use it for other tasks.

© 1995 National Semiconductor Corporation

RRD-B30M75/Printed in U. S. A

### 2.3 The TPH Printing Session—Theory of Operation

A printing session may be performed during FAX reception, local copy, printing from memory or report printing operations. It consists of the following stages:

- 1. Idle stage.

- 2. Initialize the NS32FX200 and printer hardware.

- Adjust the thermal paper backward to the printing element.

- 4. Advance the thermal paper and print the image lines, one after the other.

- 5. Eject the thermal paper from the printer.

6. Return to stage 3, if there are more pages to be printed. Printing operations are performed by the printer handlers using the Printer Controller (PRNTC) module of the NS32FX200. The printer state is set by the printer interface routines, and is modified according to the status of the printer sensors.

The PRNTC module of the NS32FX200 contains the printer bitmap shifter and the control block of the TPH. Each block is individually enabled or disabled by the Module Configuration (MCFG) register.

The bitmap shifter can operate with either internal or external clocks. DMA channel 1 loads the data to the bitmap shifter.

The bitmap is serially shifted out using either an internal or an external asynchronous clock of 0.5 to 4 MHz. The 16-bit shifter has a buffer latch which is fed by DMA channel 1. This block issues two DMA requests to fill the buffer and the shifter when the block is enabled by the MCFG register.

Shift direction is controlled by the SLNR bit of the Printer Bitmap Configuration (PBCFG) register. The actual bitmap shift starts according to the ECLK bit of the PBCFG register, as follows:

If the clock is internal, i.e., ECLK = 0, data is shifted out when the shifter is not empty, on a falling edge of the clock. The clock frequency is selected by the printer bitmap shifter internal clock generator.

If the clock is external, i.e., ECLK = 1, data is shifted out on a falling edge of the clock. The external asynchronous clock must be frozen while this block is disabled (MCFG,PBMS = 0), and for at least four instructions after the block and the DMA channel are enabled. This prevents shifting of data while the bitmap shifter is disabled, and ensures that the first clock pulse shifts the first bit.

2. After 16 bits have been shifted out, the buffer loads the shifter, and a new DMA is requested (Note 3).

The control block of the TPH includes a stepper motor controller, a strobes generator, a printer interrupt generator and a temperature sensing circuit. The block is synchronized with the time slots (Note 4) of the TCU module. A TPH latch pulse can be generated by software using the Ports module. The TPH control block is enabled by setting the TPHB and COUNT bits in the MCFG register. This generates the control signals (STB0, STB1, STB2 and STB3) for the TPH printer.

The train of strobe pulses starts at a predefined time slot which is selected by the Printer Strobes Start Time Slot (PSTSL) register. It starts with a strobe-on interval, and is followed by a sequence of strobe-off and strobe-on intervals. After the last strobe-on interval is completed, the strobes-done interrupt pulse is generated. The interrupt is periodic, occurring when the predefined time slot is reached, and the train of strobe pulses is completed. The duration of the strobe-on interval is controlled by the STBON register, and the duration of the strobe-off interval is controlled by the STBOFF register.

The temperature of the TPH may vary during a printing session, and cause irregularities in the printout. To ensure a uniform printout, the system must control the temperature of the elements in the print head, and keep it constant. The temperature of these elements is a direct function of the electric charge that gathers in them. The electric charge in the elements in the print head is a direct function of the length of the strobe-on interval. The longer the strobe-on interval, the greater will be the electric charge that gathers in the print elements, and raises their temperature.

To minimize temperature variations in the print elements, the duration of the strobe-on interval is defined based on the temperature of the TPH. The strobe-on and strobe-off intervals may be programmed as strobes are generated, to adjust the duration of each strobe based on the temperature of the print head. This control loop uses the on-chip temperature sensing circuit to detect the changes in the temperature of the print head, and modifies the duration of each strobe accordingly.

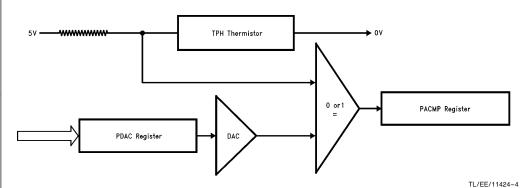

The temperature sensing circuit of the TPH operates in the following manner:

- Digital values between 0 and 63 are written to the PDAC register of the on-chip temperature sensing circuit, and converted to analog voltages between 0V and 5V.

- 2. This voltage is compared to the voltage drop over the thermistor of the TPH.

- 3. Bit 0 in the PACMP register is set or reset, depending on the temperature of the TPH.

- Note 3: The number of shifted bits must be a multiple of 16 to guarantee that all the bitmap data will be shifted out.

- Note 4: The time slots are generated by the NS32FX200 Timing Control Unit (TCU) by using programmable dividers on the chip's CTTL input clock, to divide each 20 ms period into 256 time slots. The time slots are used to synchronize the various components of the fax system, e.g., the printer and scanner with their respective motors. For further details see the data sheet of the NS32FX200, Section 4.2.2.2.

As the temperature rises, the resistance decreases, and causes the voltage to drop over the thermistor. If the temperature of the TPH is higher than is expected, the supplied voltage is higher than the voltage of the thermistor of the TPH, and bit 0 in the PACMP register is set. If the temperature of the TPH is lower than expected, the supplied voltage is lower than the voltage of the thermistor of the TPH, and bit 0 in the PACMP register is reset.

FIGURE 4. TPH Temperature Sensing Circuit

12/22/11424-

There are several ways to use the temperature sensing circuit of the TPH to measure its temperature. In the current implementation, seven digital values distinguish different TPH temperature zones (Note 5). Higher zones correspond to higher TPH temperatures, and to lower digital values. If the TPH temperature is higher than the range of the zone, i.e., if bit 0 in the PACMP register is set, a higher zone is used. Otherwise, i.e., if bit 0 of the PACMP register is 0, a lower zone is used.

In the current implementation, each temperature zone has a corresponding strobe duration value. Before a line is printed, a new zone is selected based on the temperature of the TPH.

Strobe pulses that are enabled by the STBEN bit of the Thermal Print Head Control (TPHC) register, are generated on the STB0-3 output pins of the NS32FX200. After the last strobe-on interval is completed, the STBEN bit is automati-

cally cleared by hardware. To prevent the loss of strobe pulses, the software should verify that the bit is cleared before setting it to 1.

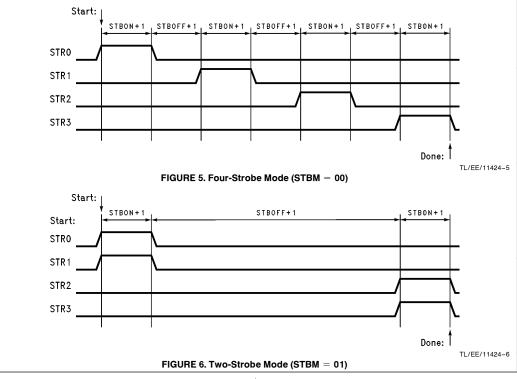

The strobe mode defines both the number of strobes in a train and the distribution of those strobes among the STB0-3 pins. Two strobe modes are supported: two-strobe mode and four-strobe mode. The Strobe Mode (STBM) field of the TPHC register selects the active strobe mode. The timing in these two strobe modes are illustrated in *Figure 5* and *Figure 6*, for an active-high polarity. Note that "Start" marks the beginning of the time slot and "Done" is the strobes-done event.

Note 5: The temperature zones are taken from the TPH Product Specification, which specifies the characteristics of the thermistor. For example, in the R0HM KF2008 - HA TPH, the thermistor operating temperatures are between - 10°C and + 100°C. In the current implementation this range is divided into seven zones.

To use the NS32FX200 Thermal Print Head (TPH) controller to generate printing strobes and serial input data for a TPH printer at 20 MHz, program the NS32FX200 registers as described in this section.

### 3.1 The Configuration Register (MCFG)

MCFG : x716

| When   | the     | MCFG      | register | is  | program    | ned | as   |

|--------|---------|-----------|----------|-----|------------|-----|------|

| shown  | , it ei | nables tl | he TPH c | ont | rol block, | the | bit- |

| map sl | hifter  | and the   | TCU mo   | dul | e.         |     |      |

#### 3.2 The Printer Controller Registers

A TPH printer has a number of basic parameters that define and control the generation of the TPH control signals. The following names for these parameters are used in this section:

| • Line time-                     | The time in milliseconds that is required to print one line.          |

|----------------------------------|-----------------------------------------------------------------------|

| Temperature zone-                | The current TPH temperature zone, ranging from very cold to very hot. |

| <ul> <li>Strobe mode-</li> </ul> | See previous section.                                                 |

• Strobe duration- (line time/4) \* 0.5 ... (line time/4) \* 0.8

Start time- Usually (line time/4) \* 0.2

## **3.2.1 The TPH Control Register** TPHC : 1x<sub>16</sub>

C : 1x<sub>16</sub> TPH Control register. When TPHC is programmed as shown, the STBEN field of this register enables the strobe pulse output signals. The remaining fields may be programmed as desired. The format of TPHC is illustrated below:

| 7        | 5 | 4     | 3   | 2    | 1  | 0  |  |

|----------|---|-------|-----|------|----|----|--|

| reserved |   | STBEN | PIS | SPOL | ST | вм |  |

- STBEN **Strobes Enable.** Set by software to enable generation of pulses on strobe pins. Cleared by hardware after the last strobe-on interval is completed. Results are unpredictable if it is cleared by software.

- PIS **Printer Interrupt Source.** Possible values are: 0 : Strobes-done interrupt pulse

- 1 : DMA channel 1 interrupt pulse

- SPOL Strobe Polarity. Possible values are:

- 0 : Strobe-on active low

- 1 : Strobe-on active high

- STBM **Strobe Mode.** See *Figure 5* and *Figure 6*. Possible values are:

- 00 : Four Strobes (fine resolution)

- 01 : Two Strobes (normal resolution)

- 10 : Reserved

- 11 : Reserved

$\mathsf{PSTSL} \quad : \quad \mathsf{fa_{16}}, \ \mathsf{7a_{16}} \ = \ \mathsf{250}, \ \mathsf{122}$

Printer Strobes Start Time Slot register. Bits 0-6 hold the time slot in which the train of strobe pulses starts, if it is enabled. Bit 7 is reserved. The train of strobes starts at the beginning of the specified time slot. For a line time of 10 ms, program PSTSL as shown.

- STBON :  $758_{16} = 1880$ -temperature zone 0, 2.45 ms, very cold

- :  $70d_{16} = 1805$ -temperature zone 1, 2.35 ms, cold

- :  $6b8_{16} = 1720$ -temperature zone 2, 2.24 ms, cool

- :  $668_{16} = 1640$ -temperature zone 3, 2.14 ms, normal

- :  $61f_{16} = 1567$ -temperature zone 4, 2.04 ms, warm

- :  $5d2_{16} = 1490$ -temperature zone 5, 1.94 ms, hot

- :  $585_{16} = 1413$ -temperature zone 6, 1.84 ms, very hot

- : 523<sub>16</sub> = 1315-temperature zone 7, 1.74 ms, dummy

**Strobe-On Register.** The values shown are for a line time of 10 ms, in four-strobe mode. This 16-bit register is used to define the strobe-on interval, which is (STBON + 1) Master Clock (MCLK) cycles long. Strobe-on time is transformed from milliseconds to MCLK (1.2288 MHz) cycles. The highest value should be less than the strobes duration, which is:

strobe duration = (line time/number of strobes)

- STBOFF :  $27_{16} = 39$ -temperature zone 0, 0.05 ms, very cold

- :  $72_{16} = 114$ -temperature zone 1, 0.15 ms, cold

- :  $c7_{16} = 199$ -temperature zone 2, 0.26 ms, cool

- :  $117_{16} = 279$ -temperature zone 3, 0.36 ms, normal

- :  $160_{16} = 352$ -temperature zone 4, 0.46 ms, warm

- :  $1ad_{16} = 429$ -temperature zone 5, 0.56 ms, hot

- : 1fa<sub>16</sub> = 506-temperature zone 6, 0.66 ms, very hot

- :  $25c_{16} = 604$ -temperature zone 7, 0.76 ms, dummy

Strobe-Off Register. The values shown are for a line time of 10 ms, in four-strobe mode. This 16-bit register is used to define the strobe-off interval, which is (STBOFF + 1) MCLK cycles long.

PDAC : 1f<sub>16</sub>

| Thermal Print Head Printer |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Printer pulse width modulation DAC register. The value shown initializes the printer temperature sensing DAC, for use with a bitmap shifter with an internal clock, and a data shift to the right.                                                                                                                                                                                                                                                                                                                                                                                  |               |             |                                                                                 | Mode Control Register. Set the fields as shown.         The format of MODE1 is illustrated below.         15       10       9       8       4       3       2       1       0                                                                                                                           |                                                                                                                                                                                                                                                        |                   |              |               |                                                                                          |                                                 |        |  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------|---------------|------------------------------------------------------------------------------------------|-------------------------------------------------|--------|--|

| σ                          | PBCFG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | : 0 <sub>16</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |             |                                                                                 | Reserved ADA Reserved DIR NFBY DE                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                        |                   |              |               |                                                                                          | DEC                                             | от     |  |

| lea                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Printer Bitmap shifter Configuration register. The format of the PBCFG is illustrated below:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |               |             | OT                                                                              | Оре                                                                                                                                                                                                                                                                                                     | ration                                                                                                                                                                                                                                                 | Туре.             |              |               | 1020                                                                                     |                                                 |        |  |

| ÷∣                         | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |             | 0 : Do not automatically initialize.<br>DEC <b>Decrement or increment ADCA.</b> |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                        |                   |              |               |                                                                                          |                                                 |        |  |

| Ē                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Reserved SL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |               |             | ECLK                                                                            |                                                                                                                                                                                                                                                                                                         | 0 : Increment.                                                                                                                                                                                                                                         |                   |              |               |                                                                                          |                                                 |        |  |

| ם                          | ECLK External Clock. Possible values are:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |             |                                                                                 | DIR                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                        | nsfer I<br>mplied | destinat     | ion           |                                                                                          |                                                 |        |  |

| nal                        | 0 : Shifter clock is external<br>1 : Shifter clock is external                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |             |                                                                                 |                                                                                                                                                                                                                                                                                                         | 0 : Implied I/O is the destination.<br><b>Device Address control.</b><br>1 : Enable incrementation of ADCA.                                                                                                                                            |                   |              |               |                                                                                          |                                                 |        |  |

|                            | SLNR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Shift direction. Possible values are:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |             |                                                                                 | STAT1                                                                                                                                                                                                                                                                                                   | : 7                                                                                                                                                                                                                                                    |                   |              |               |                                                                                          |                                                 |        |  |

| Ĕ                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0 : Shift to the r<br>1 : Shift to the l                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |             |                                                                                 |                                                                                                                                                                                                                                                                                                         | Status Register. Program this register as shown,                                                                                                                                                                                                       |                   |              |               |                                                                                          |                                                 |        |  |

|                            | PCLON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Printer bitmap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               | nal Clock   | , high time                                                                     |                                                                                                                                                                                                                                                                                                         | to clear it.                                                                                                                                                                                                                                           |                   |              |               |                                                                                          |                                                 |        |  |

| a                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | register. PCL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | k is high for | (PCLON -    | + 1) CTTL                                                                       | CNTL1                                                                                                                                                                                                                                                                                                   | : 1                                                                                                                                                                                                                                                    | 16                |              |               |                                                                                          |                                                 | 1      |  |

| Drive                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | cycles. PCLON<br>MCFG.PBMS is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               | modified of | only when                                                                       | 7                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                        |                   |              | 2             | 1                                                                                        | 0                                               | 0      |  |

| 5                          | PCLOFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Printer bitmap shifter internal Clock low time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |             |                                                                                 |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                        | Rese              | rved         |               | VLD                                                                                      | СН                                              | IEN    |  |

| 0                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | register. PCLA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |             |                                                                                 | Register. F                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                        | the fie           | lds o        | f the         |                                                                                          |                                                 |        |  |

|                            | cycles. PCLOFF may be modified only when<br>MCFG.PBMS is 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |             |                                                                                 |                                                                                                                                                                                                                                                                                                         | CNTL1 register as follows:<br>HEN Channel Enable.                                                                                                                                                                                                      |                   |              |               |                                                                                          |                                                 |        |  |

| 5                          | 3.3 TCU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U.L.I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |             | channel.                                                                        |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                        |                   |              |               |                                                                                          |                                                 |        |  |

| NSZFAZUU                   | The MCLON register, together with the MCLOFF register, are used to generate a 1.2288 MHz MCLK Program them as                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |             |                                                                                 |                                                                                                                                                                                                                                                                                                         | Transfer Validity indicator.<br>0 : Sets single transfer operation mode.                                                                                                                                                                               |                   |              |               |                                                                                          |                                                 |        |  |

| N                          | shown to define a frequency of 19.6608 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |             |                                                                                 | 3.5 I/O Ports Registers                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                        |                   |              |               |                                                                                          |                                                 |        |  |

| 2                          | MCLON : 7 <sub>16</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |             |                                                                                 | PBMS                                                                                                                                                                                                                                                                                                    | Logical OR between PBMS and f <sub>16</sub> .<br>Bits 0, 1, 2 and 3 should be set to 1 to define<br>STB0-3 strobes as output signals from the Pri<br>Controller module. Bit 5 should be set to 0 to<br>fine DMA channel 1 for used by the Printer Bitr |                   |              |               |                                                                                          |                                                 |        |  |

|                            | MCLK On Register. Defines the on time.<br>MCLOFF : 7 <sub>16</sub><br>MCLK Off Register. Defines the off time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |             |                                                                                 |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                        |                   |              |               |                                                                                          | Printer<br>to de-                               |        |  |

|                            | 3.4 DMA Controller Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |             | shifter.                                                                        |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                        |                   |              |               |                                                                                          |                                                 |        |  |

| Ĕ                          | Program the DMA controller registers as shown to dedicate channel 1 to the printer bitmap shifter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |             |                                                                                 | PBEN                                                                                                                                                                                                                                                                                                    | 1 <sub>16</sub>                                                                                                                                                                                                                                        |                   |              |               |                                                                                          |                                                 |        |  |

|                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | : Load the star                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -             |             | al memory                                                                       | DOMO                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                        |                   | Strobes ar   |               | -                                                                                        | as ou                                           | tputs. |  |

|                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | of the bitmap block.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |             |                                                                                 | PCMS                                                                                                                                                                                                                                                                                                    | Logical OR between PCMS and 8 <sub>16</sub> .<br>Port C bit 3 is printer bit map shifter clock. In this                                                                                                                                                |                   |              |               |                                                                                          |                                                 |        |  |

| σ                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | BLTC1 : Load the number of bytes to transfer.<br>MODE1 : 200 <sub>16</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |             |                                                                                 |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                        | e it is ir        | nternal cloc | k.            |                                                                                          |                                                 |        |  |

| <u>ק</u>                   | MODE1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |             |                                                                                 |                                                                                                                                                                                                                                                                                                         | ]1                                                                                                                                                                                                                                                     |                   |              |               |                                                                                          |                                                 |        |  |

| Programming                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               | Enai        | bie the                                                                         | PCLK outp                                                                                                                                                                                                                                                                                               | out signa                                                                                                                                                                                                                                              |                   |              |               |                                                                                          |                                                 |        |  |

|                            | LIFE SU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | JPPORT POLIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Y             |             |                                                                                 |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                        |                   |              |               |                                                                                          |                                                 |        |  |

|                            | NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT<br>DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL<br>SEMICONDUCTOR CORPORATION. As used herein:                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |             |                                                                                 |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                        |                   |              |               |                                                                                          |                                                 |        |  |

|                            | <ol> <li>Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.</li> <li>A critical component is any component of a life support device or system whose failure to perform car be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.</li> </ol> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |             |                                                                                 |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                        |                   |              | can<br>e life |                                                                                          |                                                 |        |  |