# Interfacing the DP8420A/21A/22A to the 80286

### INTRODUCTION

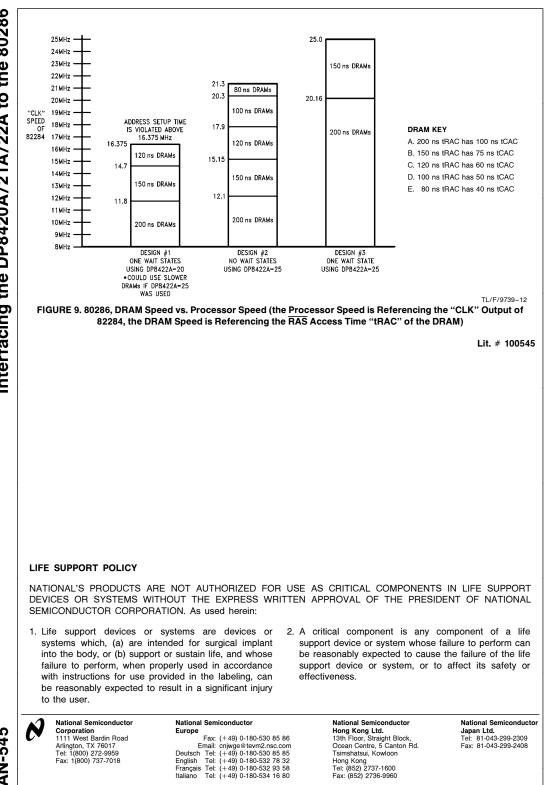

This application note describes how to interface the 80286 microprocessor to the DP8422A DRAM controller (also applicable to DP8420A/21A). There are three designs contained within this application note. The designs differ in terms of the maximum allowable frequency of operation. Design #1 can be used up to 16 MHz (80286-8) with one wait state. Design #2 can be used up to 20 MHz (80286-10) with one wait state. Design #3 can be used up to 25 MHz (80286-12) with one wait state. It is assumed that the reader is already familiar with 80286 access cycles and the DP8422A modes of operation.

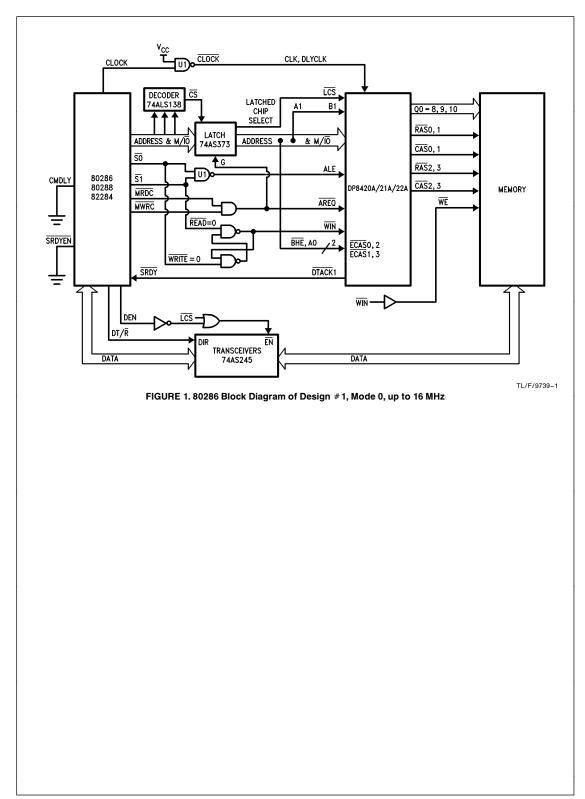

#### DESCRIPTION OF DESIGN # 1, ALLOWS UP TO 16 MHz OPERATION (CLOCK OUTPUT OF THE 82284) WITH NO WAIT STATES USING THE 80286-8

Design #1 (see *Figures 1 and 2*) consists of the DP8422A DRAM controller and several logic gates. These parts interface to the 80286 as shown in the block diagram. It accommodates two banks of DRAM, each bank being 16 bits in width, giving a maximum memory capacity of 16 Mbytes (using 4M-bit X 1 DRAMs). By choosing a different  $\overline{RAS}$  and  $\overline{CAS}$  configuration mode (see programming mode bits section of 8422A data sheet) this application could support 4 banks of DRAM, giving a memory capacity of 32 Mbytes (using 4M-bit X 1 DRAMs).

The memory banks are interleaved. This means that the least significant address bit (A1) is tied to the bank select input of the DP8422A (B1). Because the majority of accesses made by the 80286 will be sequential in nature, one memory bank can be precharging (RAS precharge) while the other bank is being accessed. The interleaved memory system has higher system performance than a non-interleaved memory system, each sequential access will generally be to the same memory bank thereby requiring extra wait states to be inserted into the CPU access cycles to allow for the RAS precharge time.

The user can choose non-address pipelined mode for this design as long as the parameter "AREQ negated to CLK high minimum to guarantee tASR = 0 ns" is guaranteed (45 ns minimum for the 8422A-20, 39 ns for the 8422A-25). At 16 MHz, the user must choose address pipelined mode since it is not possible to meet the above parameter (62.5 ns one clock - 25 ns  $\overline{\text{MRDC}},\overline{\text{MWRC}}$  max valid - 5.5 ns 74AS08 max delay + 1 ns min 74AS00  $\overline{\text{CLOCK}}$  delay = 33.5 ns which is less than the 39 ns the DP8422A-25 needs). When using the DP8422A in address pipelined mode, the DR4Ms chosen should need a minimum column address hold time of 32 ns or less.

The logic shown in this application note forms a complete 80286 memory sub-system, no other logic is needed. This sub-system automatically takes care of:

A. Arbitration between Port A, Port B, and refreshing the DRAM;

TRI-STATE® is a registered trademark of National Semiconductor Corporation

National Semiconductor Application Note 545 Webster (Rusty) Meier Jr. and Joe Tate November 1987

nterfacing the DP8420A/21A/22A to the 80286

- B. The insertion of wait states to the processor (Port A and Port B) when needed (i.e., if RAS precharge is needed, refresh is occurring during a memory access, the other Port is currently doing an access . . . etc.);

- C. Performing byte writes and reads to the 16-bit words in memory.

Since the  $\overline{\text{WE}}$  output of the DP8422A becomes refresh request ( $\overline{\text{RFRQ}}$ ) if the chip is programmed in address pipelining mode, the  $\overline{\text{WIN}}$  signal was buffered to provide  $\overline{\text{WE}}$  to the DRAMs.

The gates labeled "U1" should both be in the same package (74AS00) so that their delays cancel, see the TIMING section for how these delays cancel.

The ready logic can be made faster by programming  $\overline{\text{DTACK0}}$  into the DP8422A and running this through a fast bipolar flip-flop clocked by  $\overline{\text{CLOCK}}$ .

By making use of the enable input on the 74AS373 latch, this application can easily be used in a dual access application. The addresses and chip select are TRI-STATE® through this latch, the write input (WIN), lock input (LOCK), and ECAS0-3 inputs must also be able to be TRI-STATE (a 74AS244 could be used for this purpose). By multiplexing the above inputs, (through the use of the above parts and similar parts for Port B) the DP8422A can be used in a dual access application. All the timing (see TIMING section of this application note) will remain the same whether single or dual accessing is implemented.

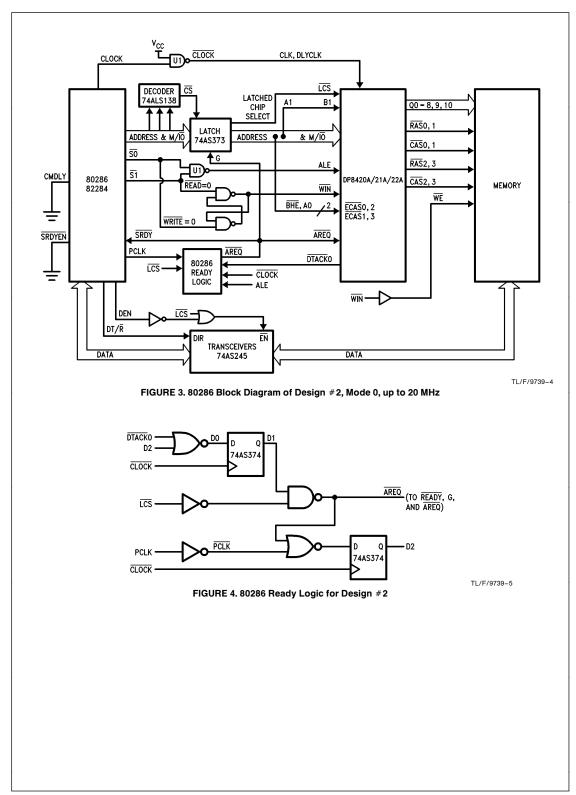

### DESCRIPTION OF DESIGN #2, ALLOWS UP TO 20 MHz OPERATION (CLOCK OUTPUT OF THE 82284) WITH NO WAIT STATES USING THE 80286-10

Design #2 (see *Figures 3, 4, 5*) is basically the same as Design #1 except for the following changes:

- A. The circuit that produces SRDY, the gate signal for the 74AS373 transparent latches, and AREQ has been changed to using DTACK0, several 74AS374 flip-flops, and some logic gates. This was needed for speed in producing the gating signal of the 74AS373 (so as to get adequate address and chip select setup time),

- The output "D1" which is used to produce the AREQ input was gated with CS. This was done to guarantee that the DTACK2 output becomes defined after power up,

- C. This design will work at 20 MHz,

- D. This design has zero wait states inserted in normal sequential accesses, multiple wait states may be inserted on multiple accesses to the same memory bank, during DRAM refreshing, or during accesses from Port B if dual accessing is used (DP8422A only).

In the 80286 READY LOGIC, the 74AS374 flip-flop that produces the D2 output has some gating at its inputs. This gating is used to synchronize the D2 output to the 80286 PCLK so as to end the access at the correct time.

The user can choose non-address pipelined mode for this design as long as the parameter " $\overline{AREQ}$  negated to CLK high minimum to guarantee tASR = 0 ns" is guaranteed

AN-545

© 1995 National Semiconductor Corporation TL/F/9739

RRD-B30M115/Printed in U. S. A

(45 ns minimum for the 8422A-20, 39 ns for the 8422A-25). At 20 MHz, the user should choose address pipelined mode since it is not possible to meet the above parameter (50 ns one clock -8 ns 74AS374 max delay -4.5 ns 74AS00 max delay +1 ns min 74AS00 CLOCK delay =38.5 ns which is less than the 39 ns the DP8422A-25 needs). The user should also keep in mind that when using the DP8422A in address pipelined mode the DRAMs chosen need a minimum column address hold time of 32 ns.

#### DESCRIPTION OF DESIGN #3, ALLOWS UP TO 25 MHz OPERATION (CLOCK OUTPUT OF THE 82284) WITH ONE WAIT STATE USING THE 80286-12

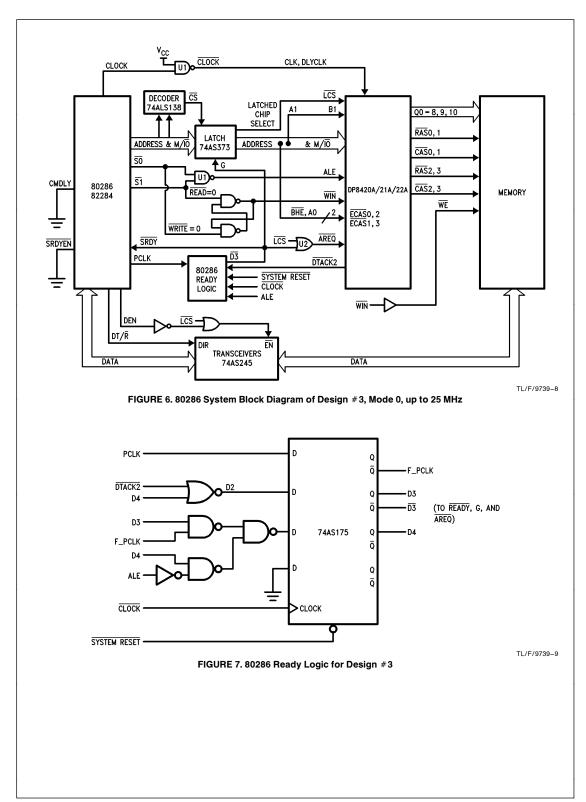

Design #3 (see *Figures 6, 7, 8*) is very similar to Design #2 except for the following changes:

- A. The circuit that produces SRDY, the gate signal for the 74AS373 transparent latches, and AREQ has been changed to use DTACK2, a 74AS175 flip-flop, and some logic gates. This was needed because the 84288-12 was not known to be available, and also for speed in producing the gating signal of the 74AS373,

- B. The AREQ input was gated with CS using gate "U2". This was done to guarantee that the DTACK2 output becomes defined after power up,

- C. This design will work at 25 MHz and possibly beyond, if the 80286 is ever produced at faster speeds (see the TIMING section for Design #3),

- D. This design has one wait state inserted in normal sequential accesses, multiple wait states may be inserted on multiple accesses to the same memory bank, during DRAM refreshing, or during accesses from Port B if dual accessing is used (DP8422A only).

The user can choose non-address pipelined mode for this design as long as the parameter " $\overline{AREQ}$  negated to CLK high minimum to guarantee tASR = 0 ns" is guaranteed (45 ns minimum for the 8422A-20, 39 ns for the 8422A-25). At 25 MHz, the user must choose address pipelined mode since it is not possible to meet the above parameter (40 ns one clock - 7.5 ns 74AS175 max delay - 1 ns min 74AS00 CLOCK delay = 33.5 ns which is less than the 39 ns the DP8422A-25 needs). The user should also keep in mind that when using the DP8422A in address pipelined mode the DRAMs chosen need a minimum column address hold time of 32 ns.

In the 80286 READY LOGIC, the 74AS175 flip-flop that produces the D4 output has some gating at its inputs. This gating is used to synchronize the D4 output to the 80286 PCLK so as to end the access at the correct time.

## 80286 DESIGN #1, UP TO 16 MHz WITH NO WAIT STATES, PROGRAMMING MODE BITS

| Programming<br>Bits | Description                                                                     |  |  |

|---------------------|---------------------------------------------------------------------------------|--|--|

| R0=0                | RAS low two clocks, RAS precharge of                                            |  |  |

| R1 = 1              | two clocks. It should be noted that the                                         |  |  |

|                     | user should choose R0,1 = 11 when                                               |  |  |

|                     | operating above 16 MHz to allow                                                 |  |  |

|                     | enough RAS precharge time                                                       |  |  |

| R2=1                | DTACK low one clock from RAS low                                                |  |  |

| R3=0                |                                                                                 |  |  |

| R4=0                | No WAIT states during burst accesses                                            |  |  |

| R5=0                | -                                                                               |  |  |

| R6 = 1              | If $\overline{\text{WAITIN}} = 0$ , add two clocks to $\overline{\text{DTACH}}$ |  |  |

| R7 = 1              | Select DTACK                                                                    |  |  |

| R8=X                | The user may choose address pipelined                                           |  |  |

|                     | mode (R8=0) remember to choose                                                  |  |  |

|                     | DRAMs with column address hold times                                            |  |  |

|                     | of 32 ns or less, or non-address                                                |  |  |

|                     | pipelined mode (R8=1), at clock                                                 |  |  |

|                     | frequencies below 16 MHz.                                                       |  |  |

| R9=X                |                                                                                 |  |  |

| C0 = X              | Select based upon the input clock                                               |  |  |

| C1 = X              | frequency. Example: if the input clock                                          |  |  |

| C2=X                | frequency is 12 MHz then choose                                                 |  |  |

|                     | C0,1,2=0,0,1 (divide by six, this will                                          |  |  |

|                     | give a frequency of 2 MHz).                                                     |  |  |

| C3 = X              |                                                                                 |  |  |

| C4=1                | RAS and CAS groups selected by "B1"                                             |  |  |

| C5=1                | This mode allows two RAS and two                                                |  |  |

| C6=1                | CAS outputs to go low during an                                                 |  |  |

|                     | access, and allows byte writing in 16-bit                                       |  |  |

|                     | words.                                                                          |  |  |

| C7 = 1              | Column address setup time of 0 ns.                                              |  |  |

| C8 = 1              | Row address hold time of 15 ns.                                                 |  |  |

| C9=1                | Delay CAS during write accesses to one                                          |  |  |

|                     | clock after RAS transitions low                                                 |  |  |

| B0 = 1              | Fall-thru latches                                                               |  |  |

| B1=0                | Access mode 0                                                                   |  |  |

|                     | Non-extend CAS mode                                                             |  |  |

0 = Program with low voltage level

1 = Program with high voltage level

X = Program with either high or low voltage level (don't care condition)

| STATES, PROGRAMMING MODE BITS                                                    |                                                                                                                                                                                                                                | STATE, PROGRAMMING MODE BITS |                                                                                                                                                                                                                         |  |

|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Programming<br>Bits                                                              | Description                                                                                                                                                                                                                    | Programming<br>Bits          | Description                                                                                                                                                                                                             |  |

| R0=1                                                                             | RAS low four clocks, RAS precharge of three clocks                                                                                                                                                                             | R0=1                         | RAS low four clocks, RAS precharge c three clocks                                                                                                                                                                       |  |

| R1=1                                                                             |                                                                                                                                                                                                                                | R1 = 1                       |                                                                                                                                                                                                                         |  |

| R2=0                                                                             | DTACK low from RAS low                                                                                                                                                                                                         | R2=1                         | DTACK low one clock from RAS low                                                                                                                                                                                        |  |

| R3=0                                                                             |                                                                                                                                                                                                                                | R3=0                         |                                                                                                                                                                                                                         |  |

| R4=0                                                                             | No WAIT states during burst accesses                                                                                                                                                                                           | R4=0                         | No WAIT states during burst accesses                                                                                                                                                                                    |  |

| R5=0                                                                             | C C                                                                                                                                                                                                                            | R5=0                         | C C                                                                                                                                                                                                                     |  |

| R6=0                                                                             | If $\overline{\text{WAITIN}} = 0$ , add one clock to                                                                                                                                                                           | R6=0                         | If $\overline{\text{WAITIN}} = 0$ , add one clock to                                                                                                                                                                    |  |

|                                                                                  | DTACK. Since we are not using the WAITIN input it should be tied high on the DP8422A.                                                                                                                                          |                              | DTACK. Since we are using DTACK2<br>the WAITIN input should be tied low or<br>the DP8422A.                                                                                                                              |  |

| R7=1                                                                             | Select DTACK                                                                                                                                                                                                                   | R7=1                         | Select DTACK                                                                                                                                                                                                            |  |

| R8=X                                                                             | The user may choose address pipelined<br>mode ( $R8 = 0$ ), remember to choose<br>DRAMs with column address hold times<br>of 32 ns or less or non-address<br>pipelined mode ( $R8 = 1$ ), at clock<br>frequencies below 20 MHz | R8=X                         | The user must choose address<br>pipelined mode ( $R8 = 0$ ), at clock<br>frequencies above 20 MHz. Also<br>remember to choose DRAMs with<br>column address hold times of 32 ns or<br>less or non-address pipelined mode |  |

| R9=X                                                                             |                                                                                                                                                                                                                                |                              | (R8 = 1), at clock frequencies below                                                                                                                                                                                    |  |

| CO = X                                                                           | Select based upon the input clock                                                                                                                                                                                              |                              | 20 MHz                                                                                                                                                                                                                  |  |

| C1 = X                                                                           | frequency. Example: if the input clock                                                                                                                                                                                         | R9=X                         |                                                                                                                                                                                                                         |  |

| C2=X                                                                             | frequency is 16 MHz then choose                                                                                                                                                                                                | C0 = X                       | Select based upon the input clock                                                                                                                                                                                       |  |

|                                                                                  | C0,1,2 = 0,1,0 (divide by eight, this will                                                                                                                                                                                     | C1 = X                       | frequency. Example: if the input clock                                                                                                                                                                                  |  |

|                                                                                  | give a frequency of 2 MHz).                                                                                                                                                                                                    | C2=X                         | frequency is 12 MHz then choose                                                                                                                                                                                         |  |

| C3=X                                                                             |                                                                                                                                                                                                                                |                              | C0,1,2 = 0,0,1 (divide by six, this will                                                                                                                                                                                |  |

| C4 = 1                                                                           | $\overline{RAS}$ and $\overline{CAS}$ groups selected by "B1".                                                                                                                                                                 |                              | give a frequency of 2 MHz). For a CPU                                                                                                                                                                                   |  |

| C5=1                                                                             | This mode allows two RAS and CAS                                                                                                                                                                                               |                              | frequency of 24 MHz the clock could b                                                                                                                                                                                   |  |

| C6=1                                                                             | outputs to go low during an access, and allows byte writing in 16-bit words.                                                                                                                                                   |                              | divided by two initially to give a 12 MH<br>input to the DELCLK input of the                                                                                                                                            |  |

| C7 = 1                                                                           | Column address setup time of 0 ns.                                                                                                                                                                                             |                              | DP8422A.                                                                                                                                                                                                                |  |

| C8 = 1                                                                           | Row address hold time of 15 ns.                                                                                                                                                                                                | C3=X                         |                                                                                                                                                                                                                         |  |

| C9=1                                                                             | Delay CAS during write accesses to one                                                                                                                                                                                         | C4 = 1                       | RAS and CAS groups selected by "B1                                                                                                                                                                                      |  |

|                                                                                  | clock after RAS transitions low                                                                                                                                                                                                | C5=0                         | This mode allows two $\overline{RAS}$ and two                                                                                                                                                                           |  |

| B0=1                                                                             | Fall-thru latches                                                                                                                                                                                                              | C6=1                         | CAS outputs to go low during an                                                                                                                                                                                         |  |

| B1=0                                                                             | Access mode 0                                                                                                                                                                                                                  |                              | access, and allows byte writing in 16-b                                                                                                                                                                                 |  |

| ECAS0=0                                                                          | Non-extend CAS mode                                                                                                                                                                                                            | 0 <b>-</b> 1                 | words.                                                                                                                                                                                                                  |  |

| 0 = Program with low voltage level                                               |                                                                                                                                                                                                                                | C7=1                         | Column address setup time of 0 ns.                                                                                                                                                                                      |  |

| 1 = Program with high voltage level                                              |                                                                                                                                                                                                                                | C8=1                         | Row address hold time of 15 ns.                                                                                                                                                                                         |  |

| ${\sf X}$ = Program with either high or low voltage level (don't care condition) |                                                                                                                                                                                                                                | C9=1                         | Delay CAS during write accesses to or<br>clock after RAS transitions low                                                                                                                                                |  |

|                                                                                  |                                                                                                                                                                                                                                | B0=1                         | Fall-thru latches                                                                                                                                                                                                       |  |

|                                                                                  |                                                                                                                                                                                                                                | B1=0                         | Access mode 0                                                                                                                                                                                                           |  |

|                                                                                  |                                                                                                                                                                                                                                | $\overline{\text{ECAS}}0=0$  | Non-extend CAS mode                                                                                                                                                                                                     |  |

80286 DESIGN #2, UP TO 20 MHz WITH NO WAIT

### 80286 DESIGN #3, UP TO 25 MHz WITH ONE WAIT

1 = Program with high voltage level

$X\,=\,$  Program with either high or low voltage level (don't care condition)

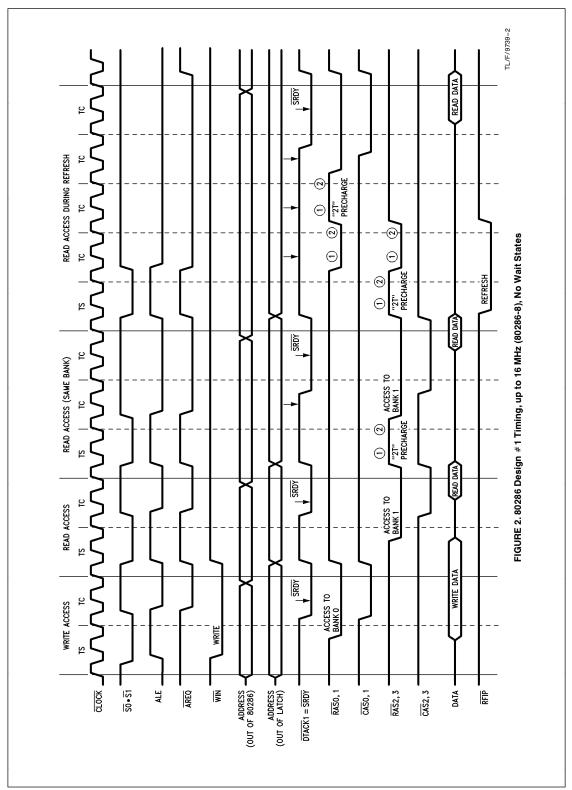

### 80286, DESIGN # 1, ACCESS MODE 0, 16 MHz TIMING (80286-8) WITH NO WAIT STATES DURING SEQUENTIAL ACCESSES

- Maximum time to address valid: <u>MRDC</u>, <u>MWTC</u> make 74AS373 fall-thru at 25 ns (max) from CLOCK low + 5.5 ns (74AS08) + 11.5 ns (74AS373 enable time) = 42 ns

- 2a. Maximum time to ALE high from CLOCK: 40 ns (max status valid) + 4.5 ns (74AS00) = 44.5 ns

- 2b. Maximum time to ALE high from CLOCK (DP8422A CLK):

$\frac{40}{CLOCK}$  and ALE cancel out) = 40 ns

- Minimum ALE high setup time to CLOCK high (DP8422A-20 needs 16 ns):

62.5 ns (one clock period) - 40 ns (#2b, the 74AS00

- U1 delays in the  $\overline{\text{CLOCK}}$  and the ALE path will cancel out) = 22.5 ns

- Minimum address setup time to CLOCK high (DP8422A-20 needs 20 ns):

62.5 ns (one clock period) + 1 ns (min 74AS00 delay,

- $\frac{62.5 \text{ ns}}{\text{CLOCK}}$  one clock period) + 1 ns (min 74AS00 delay, CLOCK) - 42 ns (#1) = 21.5 ns

- 5a. Maximum CS valid time from CLOCK high:

60 ns (maximum address valid from phase two of previous clock) + 22 ns (maximum prop delay of 74ALS138) 1 ns (minimum 74AS00 CLOCK delay) = 81 ns,

THIS IS EQUAL TO 18.5 NS FROM PHASE ONE OF THE CURRENT "TS" INVERTED CLOCK (CLOCK, 81 ns 62.5 ns = 18.5 ns).

- 5b. Maximum time to active high gating signal to 74AS373 transparent latch from  $\overline{\text{CLOCK}}$ :

25 ns ( $\rm \overline{MRDC}, \rm \overline{MWRC}$  maximum delay to inactive) + 5.5 ns (maximum 74AS08 delay) - 1 ns (minimum 74AS00  $\rm \overline{CLOCK}$  delay) = 29.5 ns,

AS CAN BE SEEN  $\overline{\rm CS}$  PRECEDES THIS ACTIVE HIGH GATING SIGNAL, THEREFORE THE MAXIMUM TIME TO THE GATING SIGNAL DETERMINES THE MAXIMUM TIME TO A VALID CHIP SELECT.

5c. Minimum CS setup time to CLOCK high (DP8422A-20 needs 14 ns):

62.5 ns (one clock period) - 29.5 ns (#5b) - 11.5 ns (maximum enable time to valid output for 74AS373) = 21.5 ns

6. Determining tRAC (RAS access time needed by the DRAM):

250 ns (TS + TC) - 62.5 ns (one clock) - 4.5 ns (74AS04 delay) - 10 ns (data setup time) - 7.5 ns (74AS245) - 32 ns (CLK to  $\overline{\text{RAS}}$  low on DP8422A-25) = 133.5 ns

Therefore the tRAC of the DRAM must be 133.5 ns or less.

Determining tCAC (CAS access time) and column address access time needed by the DRAM:

250 ns - 62.5 - 4.5 - 10 ns - 7.5 ns - 89 ns (CLK to CAS low on DP8422A-25) = 76.5 ns

Therefore the tCAC of the DRAM must be 76.5 ns or less.

8. Maximum time to DTACK1 low:

62.5 ns (One clock) + 4.5 ns (max 74AS04  $\overline{\text{CLOCK}}$ delay) +41 ns ( $\overline{\text{DTACK0}}$  low from CLK high) = 108 ns

Minimum DTACK1 setup time to SRDY being sampled (15 ns is needed by the 80286): 125 ns (two clock periods) - 108 ns (#8) = 17 ns

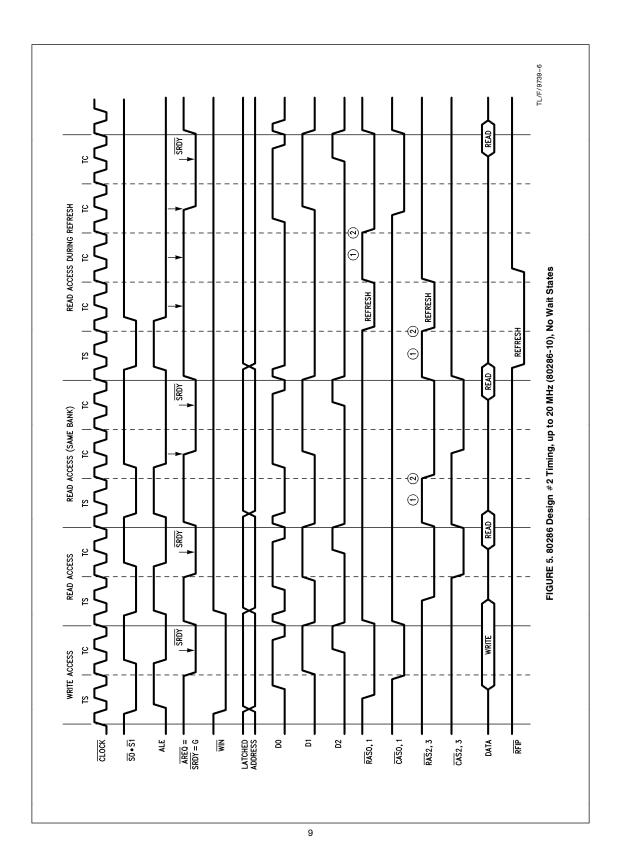

### 80286, DESIGN #2, ACCESS MODE 0, 20 MHz TIMING (80286-10) WITH ZERO WAIT STATES DURING SEQUENTIAL ACCESSES

1. Maximum time to address valid: The "G" input makes the 74AS?

The "G" input makes the 74AS373 fall-thru at 8 ns (max) from CLOCK high (8 ns max delay of 74AS374 low to high) + 11.5 ns (74AS373 enable time) = 19.5 ns

- 2a. Maximum time to ALE high from CLOCK:

- 28 ns (max status valid) + 4.5 ns (74AS00) = 32.5 ns 2b. Maximum time to ALE high from CLOCK (DP8422A CLK):

$\frac{28}{\text{CLOCK}}$  ns (max status valid) + 0 ns (74AS00 delays of  $\frac{28}{\text{CLOCK}}$  and ALE cancel out) = 28 ns

Minimum ALE high setup time to CLOCK high (DP8422A-25 needs 15 ns):

50 ns (one clock period) - 28 ns (#2b, the 74AS00 U1 delays in the CLOCK and the ALE path will cancel out) = 22 ns

- Minimum address setup time to CLOCK high (DP8422A-25 needs 18 ns):

- 50 ns (one clock period) -19.5 ns (#1) = 30.5 ns 5a. Maximum  $\overline{CS}$  valid time from  $\overline{CLOCK}$  high:

47 ns (maximum address valid from phase two of previous clock) + 22 ns (maximum prop delay of 74ALS138) - 1 ns (minimum 74AS00 CLOCK delay) = 68 ns,

THIS IS EQUAL TO 18 NS FROM PHASE ONE OF THE CURRENT "TS" INVERTED CLOCK (CLOCK).

5b. Maximum time to AREQ (active high gating signal to 74AS373 transparent latch from CLOCK:

8 ns (max delay of gate (D1) output of 74AS374 low to high from  $\overline{\text{CLOCK})}~+~4.5$  ns (74AS00,  $\overline{\text{AREQ}}$  is output) =~12.5 ns

AS CAN BE SEEN  $\overline{\rm CS}$  SUCCEEDS THIS ACTIVE HIGH GATING SIGNAL, THEREFORE THE MAXIMUM TIME TO CHIP SELECT DETERMINES THE MAXIMUM TIME TO A VALID LATCHED CHIP SELECT.

5c. Minimum  $\overline{\text{CS}}$  setup time to  $\overline{\text{CLOCK}}$  high (DP8422A-25 needs 13 ns):

50 ns (one clock period) - 18 ns (#5a) - 11.5 ns (maximum enable time to valid output for 74AS373) = 20.5 ns

6. Determining tRAC (RAS access time needed by the DRAM):

200 ns (TS + TC) - 50 ns (one clock) - 4.5 ns (74AS04 delay,  $\overline{CLOCK})$  - 8 ns (data setup time) - 7.5 ns (74AS245) - 26 ns (CLK to  $\overline{RAS}$  low on DP8422A-25) = 104 ns

Therefore the tRAC of the DRAM must be 104 ns or less.

- Determining tCAC (CAS access time) and column address access time needed by the DRAM:

200 ns 50 4.5 8 ns 7.5 ns 79 ns (CLK to CAS low on DP8422A-25) = 51 ns

- Therefore the tCAC of the DRAM must be 51 ns or less. 8. Minimum setup time of D0 low (from DTACK0) to

- CLOCK (74AS374 needs 3 ns): 50 ns (one clock) – 33 ns (DTACK0 low from CLK high) – 4.5 ns (max delay of 74AS02) = 12.5 ns

- 9. Minimum PCLK setup to CLOCK (rising edge of 74AS374, needs 3 ns):

50 ns (one clock) - 35 ns (max PCLK delay) - 5 ns (max 74AS04 delay) - 4.5 ns (max delay of 74AS02) = 5.5 ns

Minimum SRDY setup time to clock where it is sampled (15 ns is needed by the 80286):

50 ns (one clock period) - 8 ns (max delay low to high of "Q" output of 74AS374) - 4.5 ns (max delay of 74AS00) - 4.5 ns (max delay of 74AS00,  $\overline{\text{CLOCK}}$ ) = 33 ns

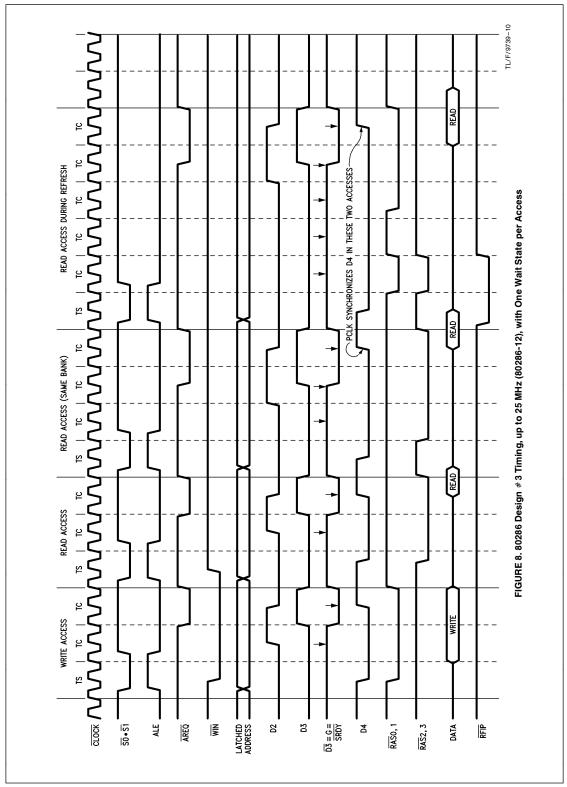

### 80286, DESIGN #3, ACCESS MODE 0, 25 MHz TIMING (80286-12) WITH ONE WAIT STATE DURING SEQUENTIAL ACCESSES

- Maximum time to address valid: The "G" input makes the 74AS373 fall-thru at 7.5 ns (max) from CLOCK high (7.5 ns max delay of 74AS175 low to high) + 11.5 ns (74AS373 enable time) = 19 ns

- 2a. Maximum time to ALE high from CLOCK:22 ns (max status valid) + 4.5 ns (74AS00) = 26.5 ns

- 2b. Maximum time to ALE high from CLOCK (DP8422A CLK):

- $\frac{22 \text{ ns (max status valid)} + 0 \text{ ns (74AS00 delays of } CLOCK \text{ and ALE cancel out)} = 22 \text{ ns}$

- Minimum ALE high setup time to CLOCK high (DP8422A-25 needs 15 ns):

40 ns (one clock period) - 22 ns (#2b, the 74AS00 U1

- delays in the CLOCK and the ALE path will cancel out) = 18 ns

- Minimum address setup time to CLOCK high (DP8422A-25 needs 18 ns):

An address setup time to the setup tis the setup tis the setup tis the setup tis the setup time to

40 ns (one clock period) - 19 ns (#1) = 21 ns

- 5a. Maximum  $\overline{CS}$  valid time from  $\overline{CLOCK}$  high:

- $\begin{array}{l} 37 \text{ ns (maximum address valid from phase two of previous clock)} + 14 \text{ ns (maximum prop delay of 74ALS139)} \\ 1 \text{ ns (minimum 74AS00 } \overline{\text{CLOCK delay})} = 50 \text{ ns,} \\ \\ \text{THIS IS EQUAL TO 10 NS FROM PHASE ONE OF} \\ \text{THE CURRENT "TS" INVERTED CLOCK (} \overline{\text{CLOCK})}. \end{array}$

- 5b. Maximum time to active high gating signal to 74AS373 transparent latch from CLOCK:

7.5 ns (max delay of gate (D3) output of 74AS175 low to high from CLOCK)

AS CAN BE SEEN  $\overline{CS}$  SUCCEEDS THE ACTIVE HIGH GATING SIGNAL, THEREFORE THE MAXIMUM TIME TO  $\overline{CS}$  VALID DETERMINES THE MAXIMUM TIME TO A VALID CHIP SELECT.

5c. Minimum CS setup time to CLOCK high (DP8422A-25 needs 13 ns):

40 ns (one clock period) - 10 ns (#5a) - 11.5 ns (maximum enable time to valid output for 74AS373) = 18.5 ns

Determining tRAC (RAS access time needed by the DRAM):

240 ns (TS + TC + TC) - 40 ns (one clock) - 4.5 ns (74AS04 delay,  $\overline{CLOCK})$  - 8 ns (data setup time) - 7.5 ns (74AS245) - 26 ns (CLK to  $\overline{RAS}$  low on DP8422A-25) = 154 ns

Therefore the tRAC of the DRAM must be 154 ns or less.

Determining tCAC (CAS access time) and column address access time needed by the DRAM:

240 ns - 40 - 4.5 - 8 ns - 7.5 ns - 79 ns (CLK to CAS low on DP8422A-25) = 101 ns Therefore the tCAC of the DRAM must be 101 ns or

less.

- Minimum setup time of D2 low (from DTACK2) to CLOCK (74AS175 needs 3 ns):

40 ns (one clock) - 28 ns (DTACK2 low from CLK high) - 4.5 ns (max delay of 74AS02) = 7.5 ns

- 9. Minimum SRDY setup time to clock where it is sampled (15 ns is needed by the 80286):

40 ns (one clock period) - 10 ns (max delay high to low of  $\overline{Q}$  output of 74AS175) - 4.5 ns (max delay of 74AS00,  $\overline{\text{CLOCK}})$  = 25.5 ns

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications

Interfacing the DP8420A/21A/22A to the 80286

**AN-545**