# Using the TP3401/2/3 ISDN PBX Transceivers

### INTRODUCTION

The TP3401 Digital Adapter for Subscriber Loops (DASL) is a low-cost burst-mode transceiver for 144 kb/s full-duplex on single twisted-pair PBX and private network loops up to 1.8 km in length. Scrambled alternate mark inversion coding is used, together with adaptive equalization and timing-recovery, to ensure low bit error rates on a wide variety of cable types. A multiplexed interface for two 64 kb/s "B" channels and one 16 kb/s "D" channel is provided. This application note, together with the TP3401 datasheet, provides the system designer with a thorough understanding of the device's operation as well as some sections that are useful to the terminal equipment designer. It covers the following topics:

- 1. Typical Application at the Terminal End

- 2. Activation/Deactivation Procedures

- 3. Repeater Mode Application

- 4. Transformer Design Guide

- 5. Surge Protection Methods at the Line Interface

- 6. Bit Error Rate Performance

### **1. TYPICAL APPLICATION AT THE TERMINAL END**

### a. System Description

For the purpose of this application note, a terminal which is designed to offer one PCM voice channel and one data channel will be discussed, although many other combinations can easily be configured.

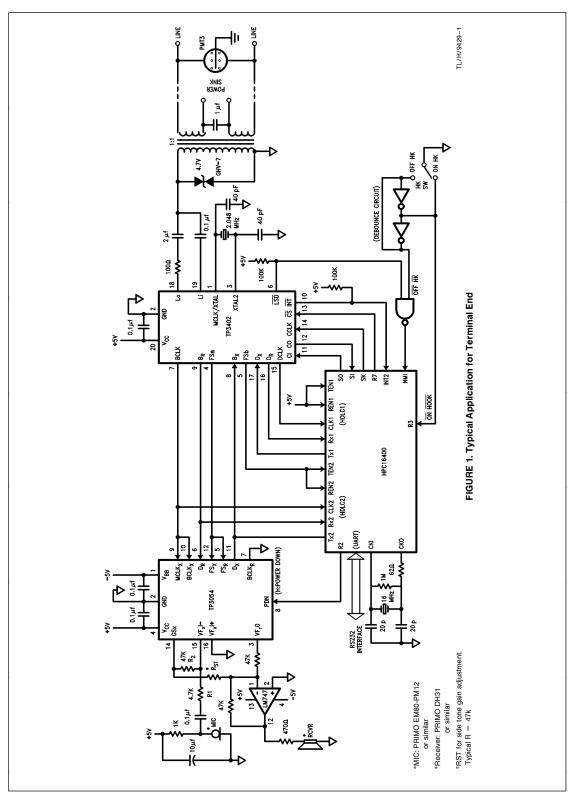

As shown in *Figure 1*, the HPC16400 Microcontroller and TP3054/7 COMBOTM directly interface to DASL at the terminal end of the loop.

### b. Main Controller HPC16400

The HPC16400 is a 16-bit highly integrated microcomputer which supports a wide range of communication application, this chip includes two HDLC channels, a DMA controller, programmable serial interface, UART and MICROWIRE/ PLUS™ serial interface. This set of features makes the HPC16400 an ideal processor for running all the functions of an ISDN Terminal Adapter, TE or Telephone.

In a typical application as shown in *Figure 1*, one of the HDLC channels is dedicated to handle the LAPD protocol in the "D" channel, while the other provides packet-mode access to one of the "B" channels. The MICROWIRE/PLUS serial interface is used to transmit/receive the TP3401 control/status register byte for handling its activation/deactivation. The UART would serve as an RS232 interface running at any of the standard synchronous or asynchronous rates up to 128 kbaud. The DMA controller provides several register sets for packet RAM management with minimal CPU intervention, including "chaining" of successive packets.

National Semiconductor Application Note 509 Casey Tsai and Bart Vos October 1989

### c. COMBO TP3054 Interface Description

The TP3054 is a  $\mu$ -law serial interface PCM Codec/Filter COMBO. When power is first applied, power-on reset circuitry initializes the chip and places it into a power-down state. All non-essential circuits are deactivated and the Dx, VFr0 output pins are put in high impedance states. To power-up the device a logical low level, which is controlled by an HPC16400 I/O pin, must be applied to the MCLKr/PDN pin. For synchronous operation, this application uses the same master clock and bit clock which come from the TP3401 for both the transmit and receive directions. In this mode, a clock must be applied to MCLKx/BCLKx pins and the MCLKr/PDN pin is used as a power-down control; also the BCLKr/CLKSEL pin is tied to ground for selecting master clock frequency 2.048 MHz. Both the FSr and FSx frame sync pulses come from the TP3401 for long frame sync operation.

The analog transmit input is an operational amplifier with provision for gain adjustment using two external resistors, R1 and R2. The analog receive output is added with side tone into the LM747 input, and the LM747 output drives the earphone.

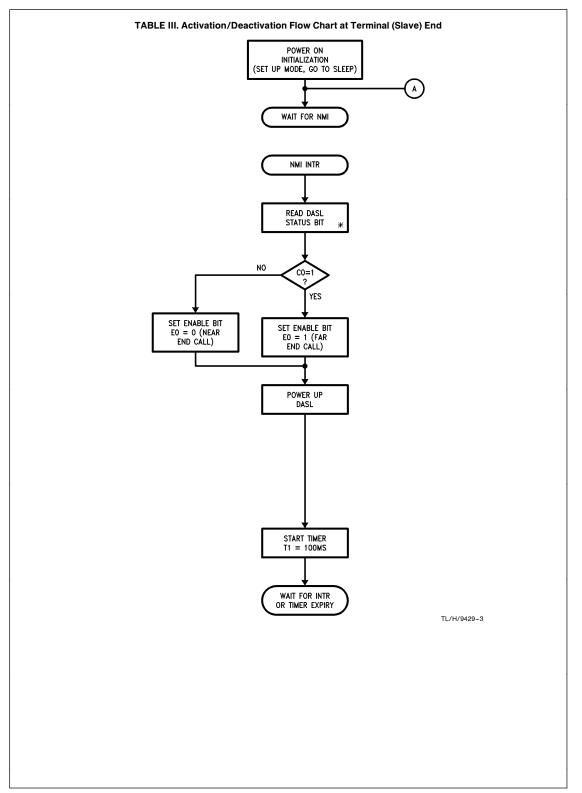

# d. Activation

The line signal detect output or hook switch, applied to the NMI pin, wakes up the HPC16400. After the HPC16400 wakes up, it starts to read DASL status register bits through MICROWIRETM to decide which end is initiating the call. The state of the C0 bit indicates whether the far end or the near end is activating the call; C0 is one ( $\overline{LSD} = 0$ ) for farend activation and C0 is zero (off-hook) for near-end activation.

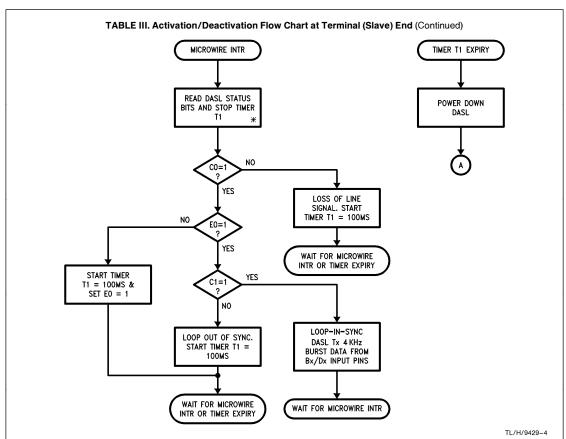

The HPC16400 powers up DASL by writing control register bit C6 = 1 through MICROWIRE. DASL starts sending a 2 kHz burst rate of scrambled 1s in the B and D channels to the line. Now HPC16400 is waiting for a MICROWIRE interrupt to check when DASL is in sync. If DASL status bit C1 changes to one (loop-in-sync), first the HPC16400 enables the HDLC 1 port which starts to handle the D channel at the Tx1 output pin, continuously sending FLAGs (01111110) to the far end and at Rx1 input pin looking for FLAGs. Then the HPC16400 powers up the COMBO for B1 channel communication and enables HDLC 2 port for B2 channel communication.

I/O port R3 is connected to on-hook signal as an input port. The HPC16400 polls this input port every 50 ms after the B1 channel is activated to monitor the hook-switch status. If the logic level of R3 pin changes from high to low, this means the terminal end disconnected the call by hook-switch during the B1 channel activation state, so the HPC16400 passes the B1 channel disconnection message to the network through the D channel. (See Section 2).

© 1995 National Semiconductor Corporation TL/H/9429

RRD-B30M115/Printed in U. S. A

AN-509

### 2. ACTIVATION/DEACTIVATION PROCEDURES

### a. General Outline of the User-Network Interface

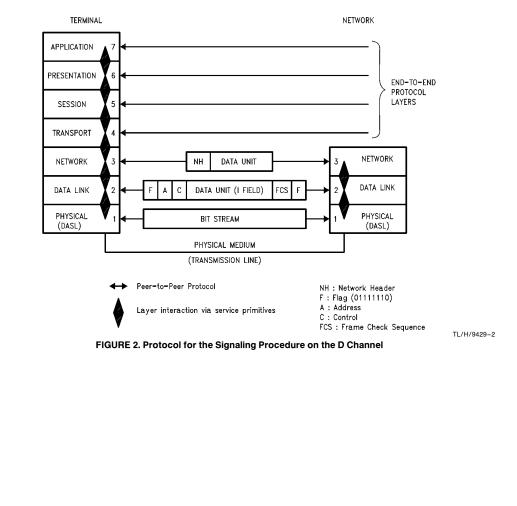

As shown in *Figure 2*, the user-network interface is based on peer-to-peer protocols from layer 1 to layer 3. All signaling messages on the D channel are used to exchange control information between the user and the network for call establishment and termination, and access to network facilities. The main functions in the three protocol layers involving network and terminal are listed below.

Layer 1, physical layer, includes functions for transmission, power feeding, activation/deactivation and maintenance.

Layer 2, data link layer. All data link layer messages in the peer-to-peer protocol are transmitted in frames which are delimited by flags. The denomination of the protocol procedure is LAPD, Link Access Procedures on the D Channel. LAPD includes functions for the provision of one or more logical link connections on the D channel, sequence control of messages, detection of errors and flow control.

Layer 3, network layer, includes functions for establishing, maintaining, and terminating circuit-switched connections, user-to-user signaling connections and packet-switched connections.

**b. The Recommended Activation Procedure (Layer 1)** from the NETWORK, i.e. TP3401 on a line card, is illustrated in Table I.

c. The Recommended Activation Procedure (Layer 1) from the TERMINAL is illustrated in Table II.

d. A Software Control Flow Chart for USER End Activation/Deactivation (Layer 1) is illustrated in Table III.

e. Call Clearing Procedure (Layer 3) is usually initiated by the user or the network sending signaling messages on the D channel across the user-network interface.

Clearing by the user: The terminal sends a DISConnect message. Following the receipt of a DISConnect message, the network considers the call to be in the disconnect-request state and disconnects the B channel that is used in the call, then the network returns a RELease message to the terminal. On receipt of the RELease message the terminal releases the B channel and the call reference, then sends a RELease COMplete message to the network.

Clearing by the network: The network sends a DISConnect message across the user-network interface and disconnects the B channel that was used in the call. Following the receipt of a DISConnect message, the user sends a RE-Lease message to the network. On receipt of the RELease message, the network returns a RELease COMplete message to the terminal and releases the B channel and call reference for future use.

Note 1: Before loop-in-sync (C1 = 1) at the SLAVE (terminal) end, Fsa/Fsb and Fsc (TP3401 only) output pins are zero, the Br data output pin is tri-stated, Dr data output pin is high, BCLK and DCLK are free run-ning outputs at 2.048 MHz and 16 kHz respectively, Bx and Dx data input pins are ignored, Lo output pin is sending 2 kHz burst rate of scrambled 1s in the B and D channels to the line.

- Note 2: Before loop-in-sync (C1 = 1) at the MASTER (network) end, the Br data output pin is high during Fsb enable, otherwise that pin is tristated; Dr data output pin is high,  $\overline{\mathrm{TS}}_{\mathrm{r}}$  output pin is low during B1/B2 received time slot, Bx and Dx data input pins are ignored, Lo output pin is sending 4 kHz burst rate of scrambled 1s in the B and D channels to the line.

- Note 3: After the bit C1 = 1 (loop-in-sync) at the SLAVE (terminal) end, the HPC can start a timer and wait 2 ms to allow the network end to acquire loop-in-sync before attempting to enable B and D channels.

#### **Terminal End** Network End Line HPC or $\mu$ P DASL (SLAVE) DASL (MASTER) HPC or $\mu$ P 1. Powers up DASL by writing control 2. Starts sending 4 kHz burst register bit rate of scrambled 1s in B C6 = 1 through 3. LSD pin goes low to wake up MICROWIRE. and D channels to the HPC. DASL status bit C0 Tx 4 kHz burst Also starts the line Default Timer. 4. Reads DASL status register changes to one and and writes control register generates a MICROWIRE bit C6 = 1 through interrupt to the HPC. **MICROWIRE to** power up DASL. Also starts the Default Timer. 5. Starts sending 2 kHz burst rate of scrambled 1s in the 6. The line signal detect B and D channels to the line. Tx 2 kHz burst circuit changes status 7. Reads DASL status bits C0 to one and register through the 8. Flywheel circuit searches generates a MICROWIRE MICROWIRE for 4 consecutive correctly interrupt to the HPC. interface. 9. Reads DASL status formatted bursts, then sets register. If C1 = 1, the status bit C1 = 1 10. Same as step 8. C1 = 1, loop-in-sync. HPC stops the Timer, Tx 4 kHz burst (loop-in-sync) and enables the HDLC generates a MICROWIRE 11. Same as step 9. (loop-in-sync) (Note 2) port to handle D channel interrupt. DASL starts signaling data first, to send 4 kHz burst data. then enables the B (Note 1) channels for voice data. (Note 3) Tx 4 kHz burst (loop-in-sync)

# **TABLE I. Activation from the Network End**

| HPC or μP           . Powers up DASL by writing control register           bit C6 = 1 through           MICROWIRE. Also           starts Default Timer.                                 | DASL (SLAVE)                                                                                                                                                                                           | Line                                                                           |                                                                                                                                  | vork End                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| ing control register<br>bit C6 = 1 through<br>MICROWIRE. Also                                                                                                                           |                                                                                                                                                                                                        |                                                                                | DASL (MASTER)                                                                                                                    | HPC or μP                                                                                                                                |

|                                                                                                                                                                                         | 2. Starts sending 2 kHz bur-<br>st rate of scrambled 1s<br>in the B and D channels<br>to the line.                                                                                                     | →<br>Tx 2 kHz burst                                                            | 3. The line signal detect<br>circuit changes<br>status bit C0 to<br>one and generates<br>a MICROWIRE<br>interrupt to<br>the HPC. | <ol> <li>Reads DASL status reg<br/>ter and writes control<br/>register bit C6 = 1<br/>through MICROWIRE<br/>to power up DASL.</li> </ol> |

| Reads DASL status register through the MICROWIRE interface.                                                                                                                             | <ol> <li>LSD pin goes low, DASL<br/>status bit C0 changes to<br/>one and generates a<br/>MICROWIRE interrupt to<br/>the HPC.</li> <li>Flywheel circuit search-<br/>es for 4 consecutive co-</li> </ol> | ←<br>Tx 4 kHz burst                                                            | 5. Starts sending 4 kHz<br>burst rate of<br>scrambled 1s in the<br>B and D channels<br>to the line.                              | Also starts the<br>Default Timer.                                                                                                        |

| Reads DASL status register. If $C1 = 1$ , the HPC stops the Timer, enables the HDLC port to handle D channel signaling data first, then enables the B channels for voice data. (Note 3) | rrectly formatted bursts,<br>then sets status bit<br>C1 = 1 (loop-in-sync)<br>and generates a<br>MICROWIRE interrupt.<br>DASL starts to send<br>4 kHz burst data.<br>(Note 1)                          | →<br>Tx 4 kHz burst<br>(loop-in-sync)<br>←<br>Tx 4 kHz burst<br>(loop-in-sync) | 10. Same as step 8.<br>C1 = 1<br>loop-in-sync.<br>(Note 2)                                                                       | 11. Same as step 9.                                                                                                                      |

\*When reading the CO pin, data is always clocked into the CI pin, therefore the CI data word should be set to repeat the previous data word if no change in device mode is intended.

### 3. REPEATER MODE APPLICATION

### a. System Description

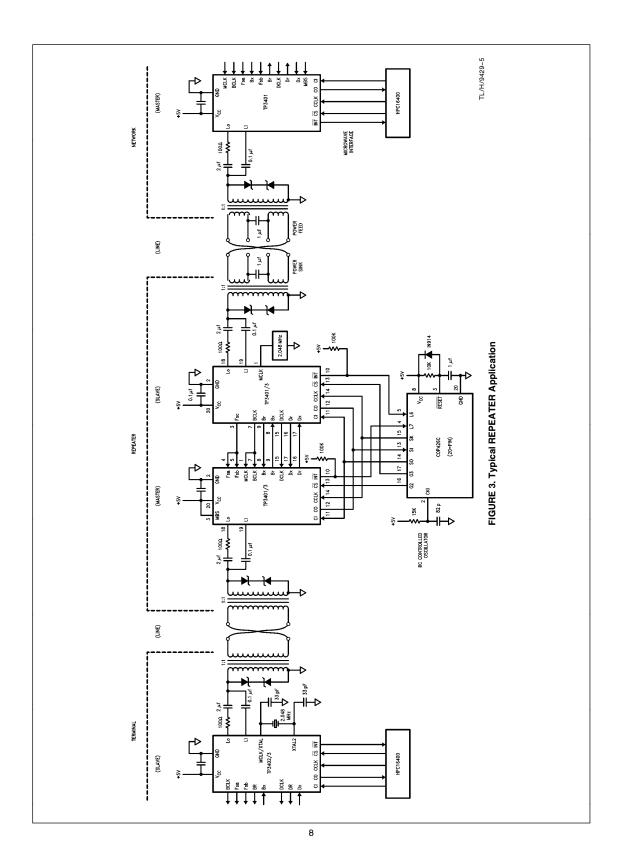

In applications where a range beyond 1.8 km is required, a simple back-to-back connection of two DASLs provides a range extension capability out to 3.6 km. A low-cost microcontroller manages the activation and deactivation of the two loops, and B and D channel data passes transparently through between the two loops. Power for the REPEATER can be sourced from either end of the system.

As shown in *Figure 3*, two DASLs, which are connected back to back as master and slave to form a REPEATER, are directly controlled by a COP426C. The COP426C (Controller Oriented Processor) is a 4-bit complete microcomputer containing all system timing, MICROWIRE serial interface, 1k  $\times$  8 ROM and 64  $\times$  4 RAM, 15 I/O lines, programmable read/ write 8-bit timer/event counter, a true vectored interrupt and three-level subroutine stack.

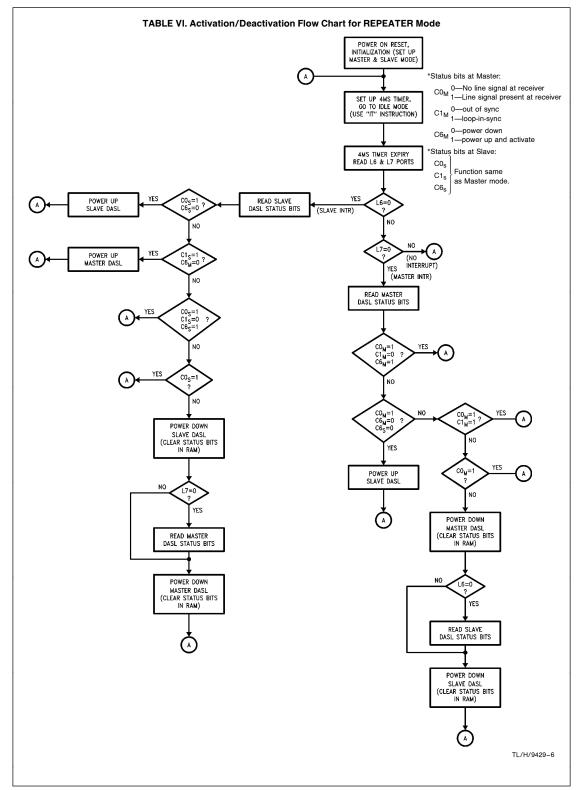

In a typical application, the INT output pins of the two DASLs connect to L6 and L7 input pins of the COP426C. Also the G2 and G3 output pins of COP426C provide a chip select ( $\overline{CS}$ ) signal to each DASL to enable the MICROWIRE serial interface. The COP426C, running on a slow R-C controlled clock, polls the input ports L6 and L7 every 4 ms. If either of these inputs changes to zero, the COP426C starts to run its activation/deactivation program as shown in the flow chart in Table VI; otherwise the COP426C goes to the idle mode, which takes only about 1 mA current for power saving. During activation, the loop at the Network end will always fully synchronize before the loop at the terminal end can synchronize. Network timing is thus passed on to the terminal. Only the Slave-mode DASL on the network side requires a 2.048 MHz clock oscillator; the Master-mode DASL on the terminal side uses the Slave's BCLK output as its MCLK timing source.

**b.** The Recommended Activation Procedure (Layer 1) from the NETWORK is illustrated in Table IV.

c. The Recommended Activation Procedure (Layer 1) from the TERMINAL is illustrated in Table V.

| DASL (SLAVE)                                                                                                                                                                                                                                                                                                                                                                                                | Line                                                                                                               | Repe                                                                                                                                                                                                                                                                                                                                                                                                       | ater                                                                                                                                                                                                                                                                                                                         | Line                                                                                             | Network End                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                                                                                                                                                                                                                             | Line                                                                                                               | DASL (MASTER)                                                                                                                                                                                                                                                                                                                                                                                              | DASL (SLAVE)                                                                                                                                                                                                                                                                                                                 | Line                                                                                             | DASL (MASTER)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                            | 2. DASL status bit C0<br>changes to 1 and<br>generates a<br>MICROWIRE<br>interrupt to COP.<br>COP reads DASL<br>status register and<br>writes control bit<br>C6 = 1 through<br>MICROWIRE to<br>power up the<br>DASL. DASL starts<br>sending 2 kHz burst<br>rate of scrambled<br>1s in the B/D<br>channels to the line.       | ←<br>Transmit<br>4 kHz burst<br>→<br>Transmit<br>2 kHz burst                                     | <ol> <li>HPC powers up DASL t<br/>writing control bit<br/>C6 = 1 through<br/>MICROWIRE and also<br/>starts the Default<br/>Timer. DASL starts<br/>sending 4 kHz burst<br/>rate of scrambled<br/>1s in the B/D<br/>channels to the line.</li> <li>DASL status bit C0 ch-<br/>anges to 1 and genera-<br/>tes a MICROWIRE inter<br/>rupt to the HPC.<br/>HPC reads DASL status<br/>register through the<br/>MICROWIRE interface.</li> </ol>                                                       |  |

| <ol> <li>ESD pin goes low<br/>to wake up HPC,<br/>DASL status bit<br/>C0 changes to 1<br/>and generates<br/>MICROWIRE<br/>interrupt to HPC.<br/>HPC reads DASL<br/>status register<br/>and writes<br/>control bit<br/>C6 = 1 through<br/>MICROWIRE to<br/>power up the<br/>DASL. DASL<br/>starts sending<br/>2 kHz burst<br/>rate of scram-<br/>bled 1s in the<br/>B/D channels to<br/>the line.</li> </ol> | ←<br>Transmit<br>4 kHz burst<br>→<br>Transmit<br>2 kHz burst<br>→<br>Transmit<br>4 kHz burst<br>(loop-in-<br>sync) | <ul> <li>5. COP powers up DASL<br/>by writing control bit<br/>C6 = 1 through<br/>MICROWIRE. DASL<br/>starts sending 4 kHz<br/>burst rate of<br/>scrambled 1s in the<br/>B/D channels to<br/>the line.</li> <li>8. DASL status bit CO<br/>changes to 1 and<br/>generates a<br/>MICROWIRE<br/>interrupt to the<br/>COP. COP reads<br/>DASL status register<br/>through MICRO-<br/>WIRE interface.</li> </ul> | 4. DASL flywheel circuit<br>searches for 4<br>consecutive<br>correctly formatted<br>bursts and sets<br>status bit C1 = 1,<br>also DASL gener-<br>ates MICROWIRE<br>interrupt and<br>sends 4 kHz burst<br>data from digital<br>interface Bx and Dx<br>to the line. COP<br>reads DASL status<br>register through<br>MICROWIRE. | →<br>Transmit<br>4 kHz burst<br>(loop-in-sync)<br>←<br>Transmit<br>4 kHz burst<br>(loop-in-sync) | <ol> <li>DASL flywheel circuit<br/>searches for 4 conse-<br/>cutive correctly for-<br/>matted bursts and sets<br/>status bit C1 = 1, also<br/>DASL generates an<br/>interrupt and sends<br/>4 kHz burst data<br/>that comes from digital<br/>interface BX/Dx to<br/>the line. HPC reads<br/>DASL status register. If<br/>C1 = 1, HPC stops the<br/>Timer, enables the<br/>HDLC port to<br/>handle D channel<br/>signaling data first,<br/>then enables B channel<br/>for voice data</li> </ol> |  |

| 9. Same as step 7.<br>C1 = 1, loop-in-<br>sync.                                                                                                                                                                                                                                                                                                                                                             | ←<br>Transmit<br>4 kHz burst<br>loop-in-                                                                           | 10. Same as step 4.<br>C1 = 1, loop-in-sync.                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                              |                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                                                                                                                                                                                                                                                                                                                                                                                                             | sync)                                                                                                              | ΔΩΤΙΛΑΤΙΟΝ Ο                                                                                                                                                                                                                                                                                                                                                                                               | OMPLETION                                                                                                                                                                                                                                                                                                                    |                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Terminal End                                                                                                                                                                                                           |                                                                                                     | Re                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                          | Network End                                                                                         |                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DASL (SLAVE)                                                                                                                                                                                                           | Line                                                                                                | DASL (MASTER)                                                                                                                                                                        | DASL (SLAVE)                                                                                                                                                                                                                                                                                                                                                             | Line                                                                                                | DASL (MASTER)                                                                                                                                                   |

| 1. HPC powers up DASL by<br>writing control bit<br>C6 = 1 through<br>MICROWIRE and<br>starts the Default<br>Timer. DASL starts<br>sending 2 kHz burst<br>rate of scrambled<br>1s in the B/D chan-<br>nels to the line. | →<br>transmit<br>2 kHz burst                                                                        | 2. DASL status bit C0<br>changes to 1 and<br>generates a<br>MICROWIRE<br>interrupt to<br>the COP. COP<br>reads DASL<br>status register<br>through<br>MICROWIRE<br>interface.         | 3. COP powers up DASL by<br>writing control bit<br>C6 = 1 through<br>MICROWIRE. DASL<br>starts sending 2 kHz<br>burst rate of scrambled<br>1s in the B/D channels<br>to the line.                                                                                                                                                                                        | →<br>Transmit<br>2 kHz burst                                                                        | MICROWIRE<br>interrupt to the HPC<br>HPC reads DASL<br>status register starts                                                                                   |

| 8. DASL status bit C0<br>changes to 1 and<br>generates a MICRO-<br>WIRE interrupt<br>to the HPC.<br>HPC reads DASL<br>MICROWIRE interface.                                                                             | ←<br>transmit<br>4 kHz burst                                                                        | 7. COP powers up DASL<br>by writing control bit<br>C6 = 1 through<br>MICROWIRE. DASL<br>starts sending 4 kHz<br>burst rate of<br>scrambled 1s in<br>the B/D channels<br>to the line. | <ol> <li>Same as step 2.</li> <li>DASL flywheel circuit<br/>searches for 4<br/>consecutive correctly<br/>formatted bursts and<br/>sets status bit<br/>C1 = 1, also DASL<br/>generates an inter-<br/>rupt and sends 4 kHz<br/>burst data from digi-<br/>tal interface Bx and<br/>Dx to the line.<br/>COP reads DASL status<br/>register through<br/>MICROWIRE.</li> </ol> | ←<br>Transmit<br>4 kHz burst<br>→<br>Transmit<br>4 kHz burst<br>(loop-in-<br>sync)<br>←<br>Transmit | power up DASL.<br>DASL starts sending<br>4 kHz burst rate of<br>scrambled 1s in the<br>B/D channels to<br>the line.<br>9. DASL flywheel circu<br>searches for 4 |

| 10. Same as step 9.<br>C1 = 1, loop-in-sync.                                                                                                                                                                           | transmit<br>4 kHz burst<br>(loop-in-<br>sync)<br>←<br>transmit<br>4 kHz burst<br>(loop-in-<br>sync) | 11. Same as step 6.<br>C1 = 1,<br>loop-in-sync.                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                          | 4 kHz burst<br>(loop-in-<br>sync)                                                                   |                                                                                                                                                                 |

|                                                                                                                                                                                                                        | 1                                                                                                   |                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                     | 1                                                                                                                                                               |

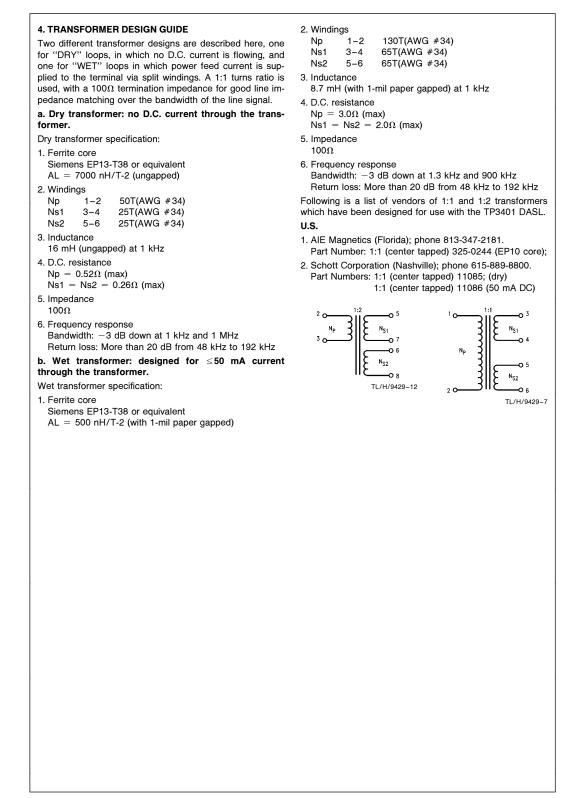

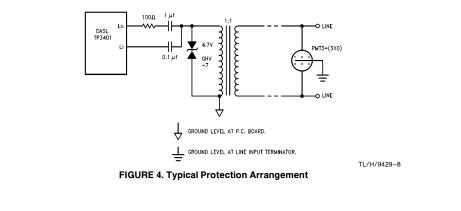

| 5. SURGE PROTECTION METHODS AT THE LINE<br>INTERFACE<br>There are two main sources of transient high voltages, light-<br>ning and short circuit wiring faults to commercial power sys-<br>tems. The induced overvoltage can seriously damage volt-<br>age sensitive components, so at least two levels of protec-<br>tion are required on the line interface as shown in <i>Figure 4</i> .<br>a. Protection at Secondary of Transformer | en in burst mode at 144 kb<br>sion, using 1:1 transformer<br>Loop lengths of up to 2 kb<br>AWG cable have been use | m of 22 AWG, 24 AWG and<br>d.<br>the 22 AWG and 26 AWG ca      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| The protector at the secondary of the transformer is usually<br>placed on the line at a distance greater than 25 meters from<br>the linecard; the impedance of the line will ensure that this<br>protector always operates first. A suitable protector is a gas<br>discharge tube, which has high insulation resistance, low                                                                                                            | A white noise signal, band-<br>at the receiver's input.                                                            | limited to 500 kHz, was inse<br>ured by transmitting 100 mi    |

| capacitance and high current capability, such as a three electrode gas discharge surge arrester PTM3(310).                                                                                                                                                                                                                                                                                                                              | 1 km/24 AWG, input signal noise level ( $\mu V/\sqrt{Hz}$ )                                                        | BER                                                            |

| PMT3(310) Specifications:<br>Manufacturer: General Instrument Corp.<br>D.C. breakdown voltage: 250V                                                                                                                                                                                                                                                                                                                                     | 14.1<br>17.7<br>21.2                                                                                               | 0.0 E-7<br>1.0 E-7<br>1.3 E-5                                  |

| Pulse breakdown voltage: Less than 1600V at a ramp speed<br>of 10,000 V/μs<br>Peak surge current: 10,000 A<br>Holdover voltage: 100V and 150V minimum<br>Surge life: 400 surges average (500A, 10/1000 μs)                                                                                                                                                                                                                              | 2 km/24 AWG, input level<br>noise level (µV/√Hz)<br>3.5<br>5.3<br>7                                                | 95 mV <sub>PP</sub> :<br>BER<br>0.0 E-7<br>9.7 E-7<br>8.8 E-5  |

| Capacitance: Less than 5 pF<br><b>b. Protection at Primary of Transformer</b><br>The protection at the primary of the transformer can be pro-<br>vided by either a Zener diode or Varister; in the application<br>shown in <i>Figure 4</i> is one GHV-7 Varister.                                                                                                                                                                       | 1 km/22 AWG, input level<br>noise level (μV/√Hz)<br>22.1<br>28.3<br>35.4                                           | 440 mV <sub>PP</sub> :<br>BER<br>0.0 E-7<br>2.0 E-6<br>9.1 E-5 |

| GHV-7 Specifications:<br>Manufacturer: General Semiconductor Industries, Inc.<br>Breakdown voltage Bv: 4.7V                                                                                                                                                                                                                                                                                                                             | 33.4<br>1.8 km/26 AWG, input leve<br>noise level (μV/√Hz)<br>3.5                                                   |                                                                |

Max surge current: 30 A (8.4 ms), 100 A (1.0 ms) Capacitance: Less than 150 pF

### 6. BIT ERROR RATE PERFORMANCE

### a. General Description

On the receiver side of DASL, data detection is accomplished by threshold comparison synchronized to the received signal timing. A first-order adaptive equalizer has been computer optimized and field tested on a variety of PBX and short range subscriber networks. Performance objectives are based on standard twisted pair cable characteristics. The equalized signal is processed by a wave-difference time-extractor and loop filter circuit followed by level data-detection. A novel design of an early-late DPLL with effective 30 ns step increments guarantees timing precision and stability.

# b. Test Set-Up

n takismis-

nd 26

able,

erted

nillion

| BER                      |

|--------------------------|

| 0.0 E-7                  |

| 1.0 E-7                  |

| 1.3 E-5                  |

| 95 mV <sub>PP</sub> :    |

| BER                      |

| 0.0 E-7                  |

| 9.7 E-7                  |

| 8.8 E-5                  |

| 440 mV <sub>PP</sub> :   |

| BER                      |

| 0.0 E-7                  |

| 2.0 E-6                  |

| 9.1 E-5                  |

| el 75 mV <sub>PP</sub> : |

| BER                      |

| 0.0 E-7                  |

| 4.3 E-7                  |

| 8.4 E-6                  |

|                          |

In addition to the above mentioned test method, BE rates have also been measured in the presence of a single tone interference signal at approximately twice the frequency of the main spectral lobe (in this case 400 kHz).

Range 1 km/24 AWG cable, 295 mV<sub>PP</sub> input level:

BER = 0.0 E7 for a 53 mV\_{PP} sine wave at 400 kHz.

Range 2 km/24 AWG cable, 95 mVPP input level:

BER = 0.0 E-7 for a 14.4 mV<sub>PP</sub> sine wave at 400 kHz.

## LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Japan Ltd. Tel: 81-043-299-2309 Fax: 81-043-299-2408

| 1 | National Semiconductor | National Semiconductor              | National Semiconductor<br>Hong Kong Ltd. |  |

|---|------------------------|-------------------------------------|------------------------------------------|--|

| V | Corporation            | Europe                              |                                          |  |

| • | 1111 West Bardin Road  | Fax: (+49) 0-180-530 85 86          | 13th Floor, Straight Block,              |  |

|   | Arlington, TX 76017    | Email: cnjwge@tevm2.nsc.com         | Ocean Centre, 5 Canton Rd                |  |

|   | Tel: 1(800) 272-9959   | Deutsch Tel: (+49) 0-180-530 85 85  | Tsimshatsui, Kowloon                     |  |

|   | Fax: 1(800) 737-7018   | English Tel: (+49) 0-180-532 78 32  | Hong Kong                                |  |

|   |                        | Français Tel: (+49) 0-180-532 93 58 | Tel: (852) 2737-1600                     |  |

|   |                        | Italiano Tel: (+49) 0-180-534 16 80 | Fax: (852) 2736-9960                     |  |

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.