# High Performance ECL Data ECLinPS and ECLinPS Lite

### **DATA SHEET CLASSIFICATIONS**

### **Product Preview**

This heading on a data sheet indicates that the device is in the formative stages or in design (under development). The disclaimer at the bottom of the first page reads: "This document contains information on a product under development. Motorola reserves the right to change or discontinue this product without notice."

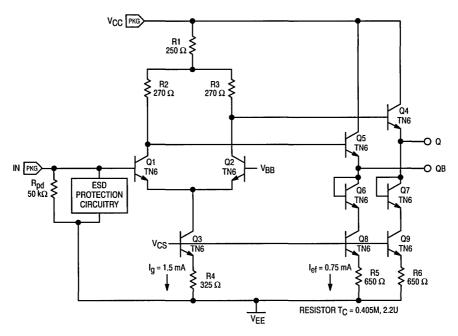

### Advance Information

This heading on a data sheet indicates that the device is in sampling, pre-production, or first production stages. The disclaimer at the bottom of the first page reads: "This document contains information on a new product. Specifications and information herein are subject to change without notice."

# Fully Released

A fully released data sheet contains neither a classification heading nor a disclaimer at the bottom of the first page. This document contains information on a product in full production. Guaranteed limits will not be changed without written notice to your Motorola Semiconductor Sales Office.

The data sheets contained in this book were the most current available as of the date of publication, December 1993.

A more current version of data sheets designated *Product Preview* or *Advance Information* may be available.

# **High Performance ECL Data**

**ECLinPS and ECLinPS Lite**

**General Information**

**ECLinPS Family Specifications** & Device Data Sheets

**ECLinPS Lite Family Specifica**tions & Device Data Sheets

**Design Guide & Application Notes**

ECLinPS, ECLinPS Lite, MOSAIC, MECL 10K and MECL 10H are trademarks of Motorola Inc The brands or product names mentioned are trademarks or registered trademarks of their respective holders.

#### Suggested References:

The user is referred to the following for general information on the MECL and 100K ECL families:

Motorola MECL Device Data Book, Motorola Inc., 1987. Stock code DL122/D.

F100K ECL Data Book, Fairchild Camera and Instrument Corp.

Motorola MECL System Design Handbook, second edition. Motorola Inc., 1983. Stock code HB205R1/D. Signetics ECL 10K/100K Data Manual.

# High Performance ECL Data ECLinPS and ECLinPS Lite

This databook contains device specifications for Motorola's ECLinPS advanced ECL logic family.

ECLinPS (ECL in picoseconds) was developed in response to the need for an even higher performance ECL family of standard logic functions, particularly in the Computer, Automated Test, Instrumentation and Communications industries. Family general features as well as specific functions were developed in close consultation with ECL systems design engineers.

ECLinPS offers the user a single gate delay of 500ps max., including package delay, and a flip-flop toggle frequency of 1100MHz.

ECLinPS is compatible with two different ECL standards. Each function is available with either MECL 10H compatibility (MC10Exxx series) or 100K compatibility (MC100Exxx series).

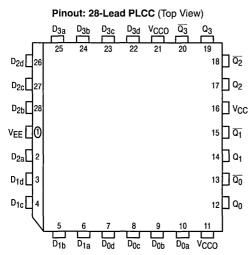

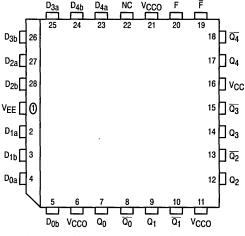

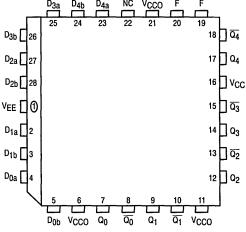

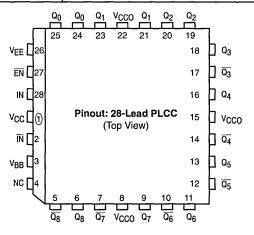

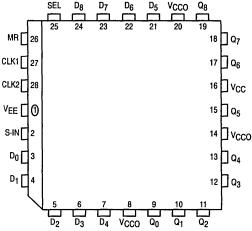

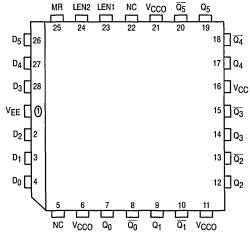

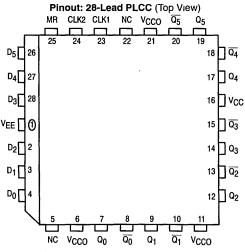

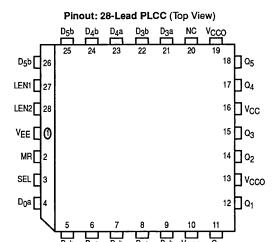

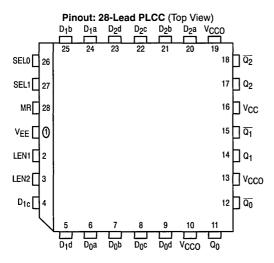

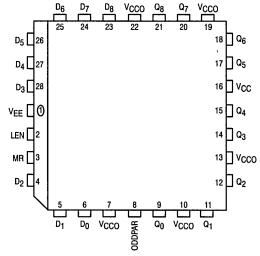

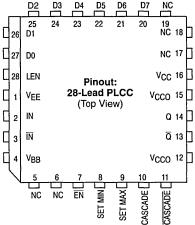

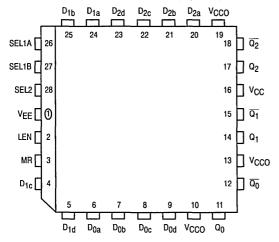

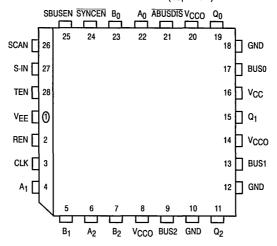

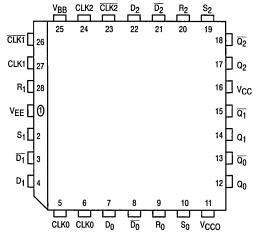

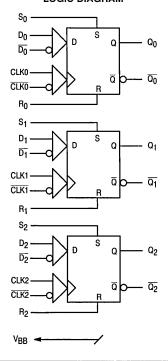

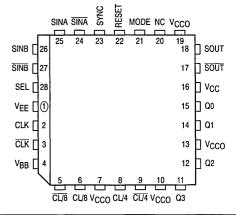

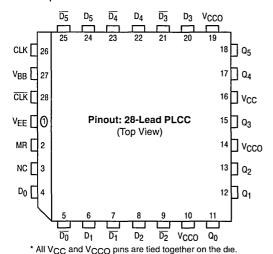

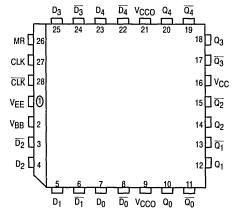

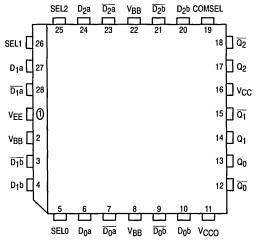

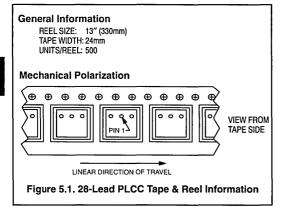

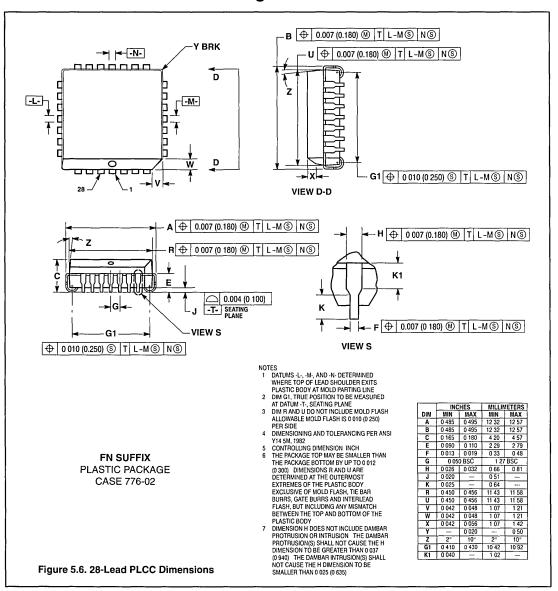

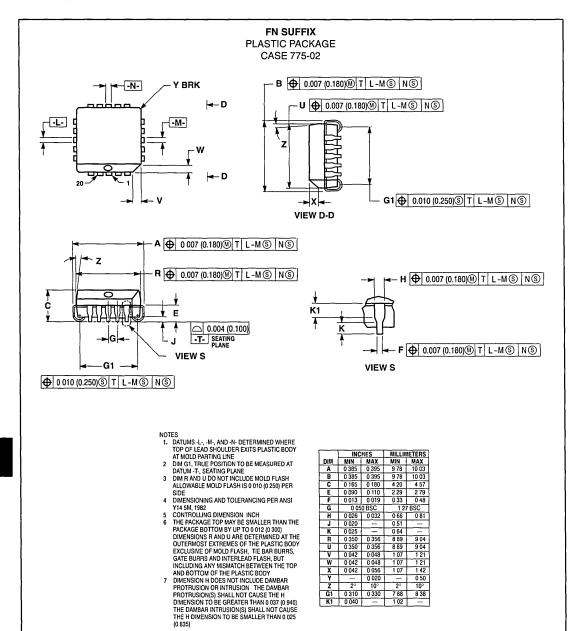

ECLinPS is offered in the 28-lead plastic leaded chip carrier (PLCC), a J-lead surface mount IC package. This package was selected for high performance, reduced parasitics and good thermal handling in a low cost, standard package, and reflects an industry trend towards surface mount assembly.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers. employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and (A) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

© Motorola, Inc. 1993 Previous Edition © 1989 "All Rights Reserved"

## **CONTENTS**

| General Information              | MC10E452/MC100E4522-130                                        |

|----------------------------------|----------------------------------------------------------------|

| Numeric Index                    | MC10E457/MC100E4572-132                                        |

| Device Nomenclature              | MC10E16512-135                                                 |

| Selection Guide1-3               | MC10E1652                                                      |

| Family Overview 1-5              | FCI inDC I ita Data-basta                                      |

| Electrical Characteristics 1-10  | ECLinPS Lite Datasheets                                        |

| Engineering Evaluation Board1-15 | Family Specifications 3-2                                      |

|                                  | Applications Information                                       |

| ECLinPS Data Sheets              | MC10EL01/MC100EL01                                             |

| Family Specifications            | MC10EL04/MC100EL04                                             |

| MC10E016/MC100E0162-3            | MC10EL05/MC100EL05                                             |

| MC10E101/MC100E1012-9            | MC10EL07/MC100EL07                                             |

| MC10E104/MC100E104 2-11          | MC10EL11/MC100EL11                                             |

| MC10E107/MC100E1072-13           | MC10EL12/MC100EL12                                             |

| MC10E111/MC100E111 2-15          | MC10EL15/MC100EL15                                             |

| MC10E112/MC100E112 2-18          | MC10EL16/MC100EL16                                             |

| MC10E116/MC100E116 2-20          | MC10EL31/MC100EL31                                             |

| MC10E122/MC100E1222-22           | MC10EL32/MC100EL32                                             |

| MC10E131/MC100E1312-24           | MC10EL33/MC100EL333-22                                         |

| MC10E136/MC100E1362-26           | MC10EL34/MC100EL34                                             |

| MC10E137/MC100E1372-33           | MC10EL35/MC100EL353-26                                         |

| MC10E141/MC100E1412-36           | MC10EL51/MC100EL51                                             |

| MC10E142/MC100E1422-38           | MC10EL52/MC100EL523-30                                         |

| MC10E143/MC100E1432-40           | MC10EL57/MC100EL57                                             |

| MC10E150/MC100E1502-42           | MC10EL58/MC100EL58                                             |

| MC10E151/MC100E1512-44           | MC10EL89                                                       |

| MC10E154/MC100E1542-46           | MC10ELT20/MC100ELT203-38                                       |

| MC10E155/MC100E1552-48           | MC10ELT21/MC100ELT21                                           |

| MC10E156/MC100E1562-51           | MC10ELT22/MC100ELT22                                           |

| MC10E157/MC100E1572-53           | MC100ELT23 3-41                                                |

| MC10E158/MC100E1582-55           | MC10ELT24/MC100ELT243-42                                       |

| MC10E160/MC100E1602-57           | MC10ELT25/MC100ELT253-43                                       |

| MC10E163/MC100E1632-59           | MC10ELT26/MC100ELT263-44                                       |

| MC10E164/MC100E1642-61           | MC10ELT28/MC100ELT283-45                                       |

| MC10E166/MC100E1662-63           | Design Guide & Application Notes                               |

| MC10E167/MC100E1672-65           | •••                                                            |

| MC10E171/MC100E1712-67           | Design Guide:                                                  |

| MC10E175/MC100E1752-69           | System 4-2                                                     |

| MC10E193/MC100E1932-71           | Transmission Line Theory                                       |

| MC10E195/MC100E1952-73           | System Interconnect                                            |

| MC10E196/MC100E1962-76           | Interfacing With ECLinPS                                       |

| MC10E197 2-81                    | Packaging and Thernal Information 4-32                         |

| MC10E211/MC100E211 2-95          | Quality and Reliability 4-39                                   |

| MC10E212/MC100E2122-100          | A 11 11 A 1                                                    |

| MC10E241/MC100E2412-102          | Application Notes:                                             |

| MC10E256/MC100E2562-104          | ECLinPS Circuit Performance at<br>Standard VIH Levels (AN1404) |

| MC10E336/MC100E3362-107          | ECL Clock Distribution                                         |

| MC10E337/MC100E3372-109          | Techniques (AN1405) 4-49                                       |

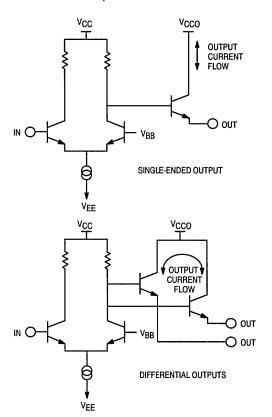

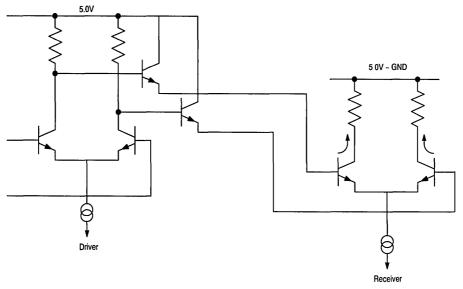

| MC10E404/MC100E4042-112          | Designing With PECL (AN1406) 4-56                              |

| MC10E416/MC100E4162-114          | ECLinPS I/O SPICE Kit (AN1503) 4-65                            |

| MC10E431/MC100E431 2-116         | Metastability and the ECLinPS                                  |

| MC10E445/MC100E445               | Family (AN1504) 4-75                                           |

| MC10E446/MC100E4462-124          | Logic Literature Listing4-83                                   |

| MC10E451/MC100E4512-128          | Distributor and Worldwide Sales Offices 4-84                   |

# igh Performance ECL Data LinPS and ECLinPS Lite

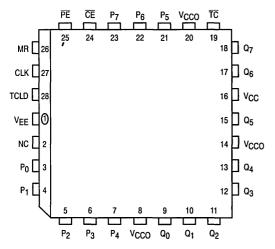

This section contains a numerical listing of LinPS and ECLinPS Lite family functions, a hnical overview of the ECLinPS Lite families as I as an outline of their electrical characteristics. addition, this section outlines the procedures 1 philosophies used to AC test the families. 210E/EL series devices are compatible with MECL 10H family. MC100E/EL series are npatible with 100K ECL.)

#### **INTENTS**

| meric Index 1-                 |

|--------------------------------|

| vice Nomenclature 1-           |

| ection Guide 1-                |

| nily Overview 1-               |

| ctrical Characteristics 1-1    |

| gineering Evaluation Board 1-1 |

# **General Information**

## SECTION 1 Numeric Index

#### Numeric Index — ECLinPS Devices

| MC10/<br>MC100 | Function                       | Page |

|----------------|--------------------------------|------|

| E016           | 8-Bit Synch Binary Counter     | 2-3  |

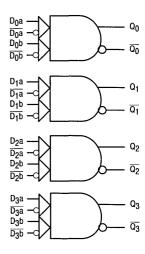

| E101           | Quad 4-Input OR/NOR Gate       | 2-9  |

| E104           | Quint 2-Input AND/NAND Gate    | 2-11 |

| E107           | Quint 2-Input XOR/XNOR Gate    | 2-13 |

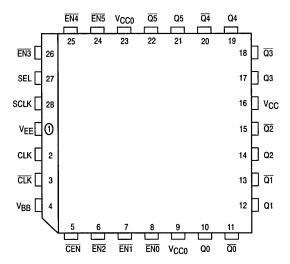

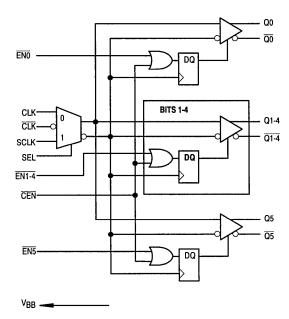

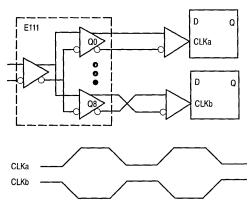

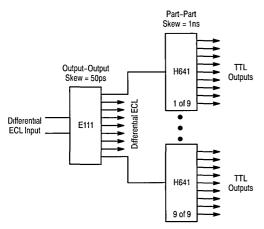

| E111           | 1:9 Differential Clock Driver  | 2-15 |

| E112           | Quad Drive, Common Enable      | 2-18 |

| E116           | Quint Diff Line Receiver       | 2-20 |

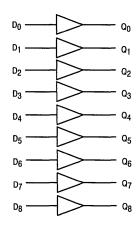

| E122           | 9-Bit Buffer                   | 2-22 |

| E131           | 4-Bit D Flip-Flop              | 2-24 |

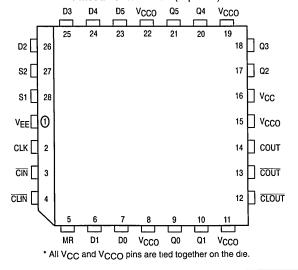

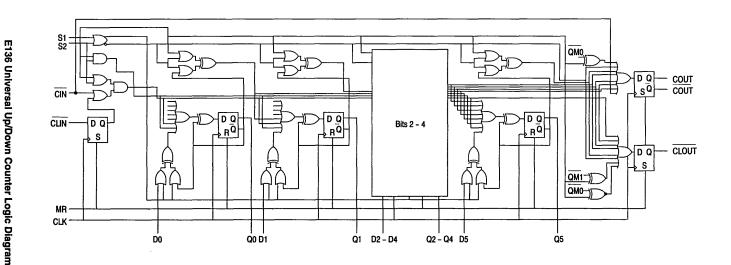

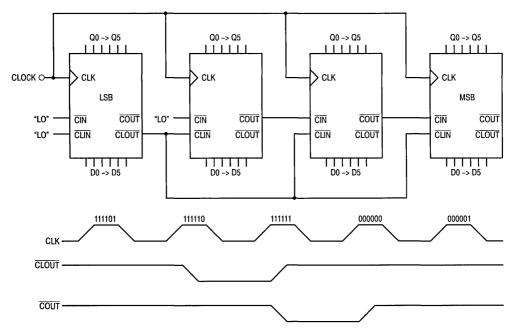

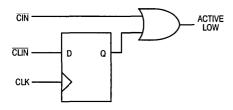

| E136           | 6-Bit Universal Counter        | 2-26 |

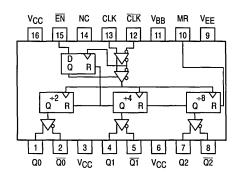

| E137           | 8-Bit Ripple Counter           | 2-33 |

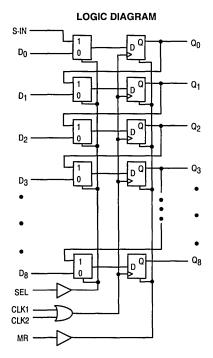

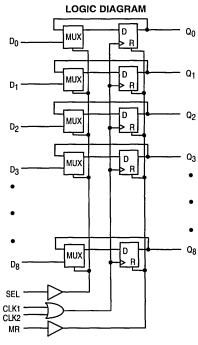

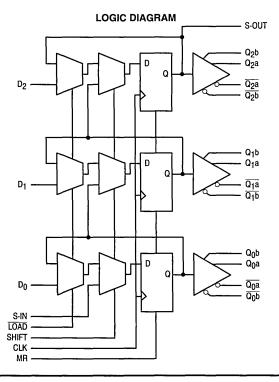

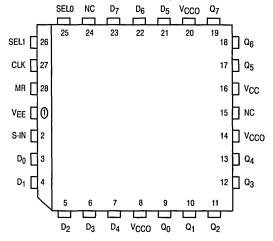

| E141           | 8-Bit Universal Shift Register | 2-36 |

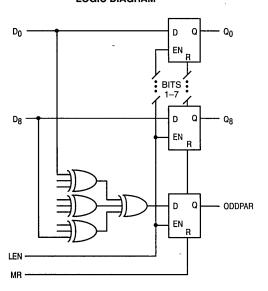

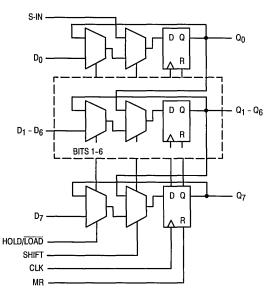

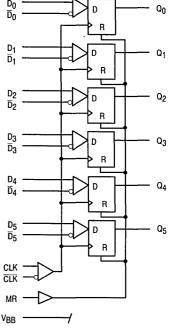

| E142           | 9-Bit Shift Register           | 2-38 |

| E143           | 9-Bit Hold Register            | 2-40 |

| E150           | 6-Bit D Latch                  | 2-42 |

| E151           | 6-Bit D Register               | 2-44 |

| E154           | 5-Bit 2:1 Mux Latch            | 2-46 |

| E155           | 6-Bit 2:1 Mux Latch            | 2-48 |

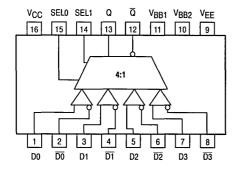

| E156           | 3-Bit 4:1 Mux Latch            | 2-51 |

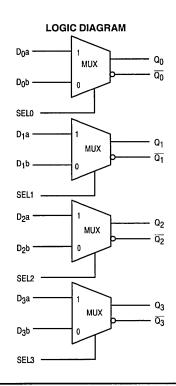

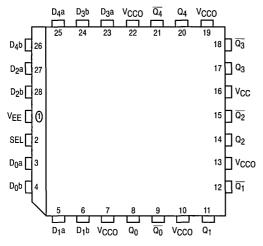

| E157           | Quad 2:1 Mux, Separate Selects | 2-53 |

| E158           | 5-Bit 2:1 Multiplexer          | 2-55 |

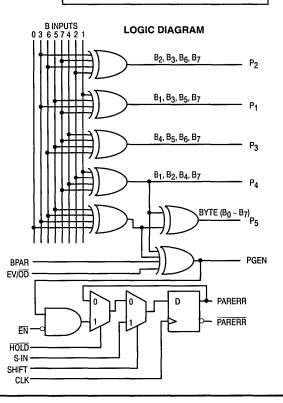

| E160           | 12-Bit Parity Gen/Checker      | 2-57 |

| E163           | 2-Bit 8:1 Multiplexer          | 2-59 |

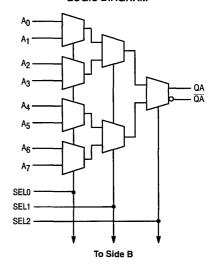

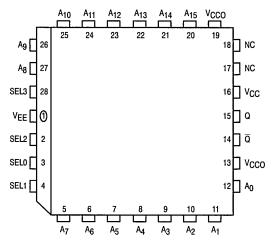

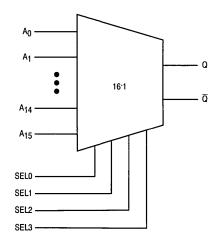

| E164           | 16:1 Multiplexer               | 2-61 |

| MC10/<br>MC100 | Function                            | Page  |

|----------------|-------------------------------------|-------|

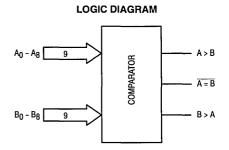

| E166           | 9-Bit Magnitude Comparator          | 2-63  |

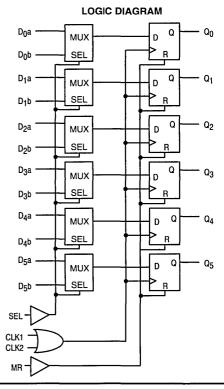

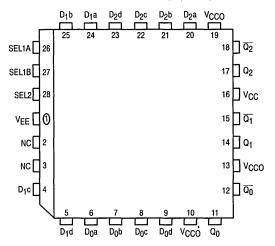

| E167           | 6-Bit 2:1 Mux Register              | 2-65  |

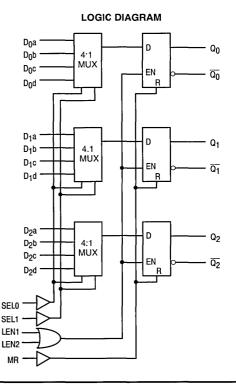

| E171           | 3-Bit 4:1 Multiplexer               | 2-67  |

| E175           | 9-Bit Latch w/ Parity Gen/Checker   | 2-69  |

| E193           | 8-Bit EDAC/Parity                   | 2-71  |

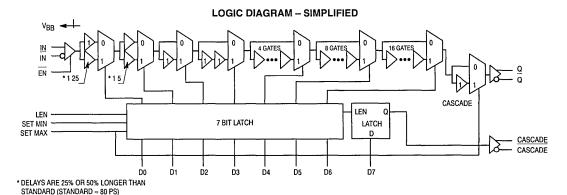

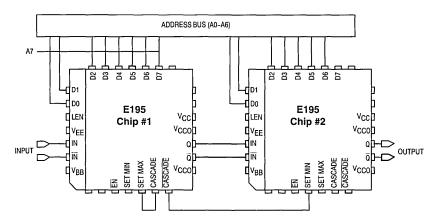

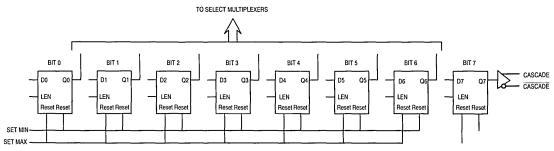

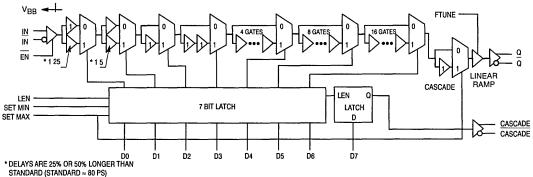

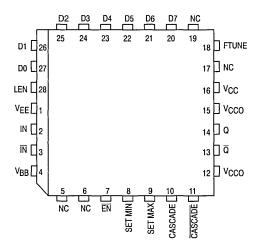

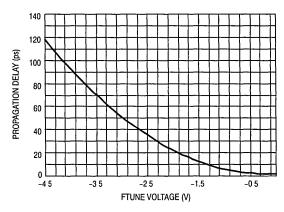

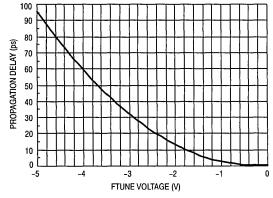

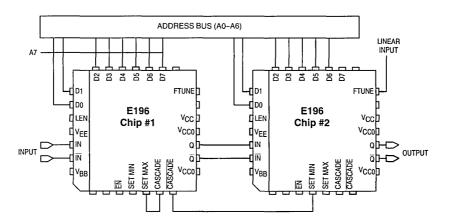

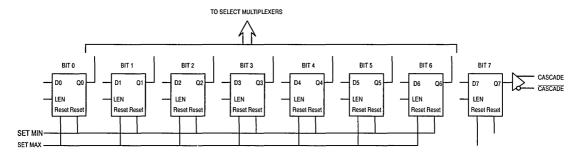

| E195           | Programmable Delay Chip             | 2-73  |

| E196           | Programmable Delay Chip             | 2-76  |

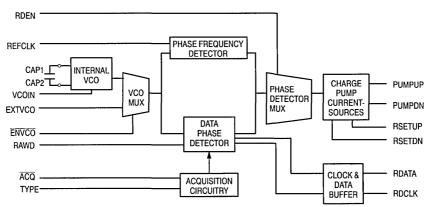

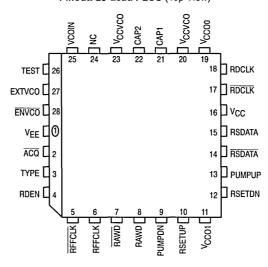

| E197*          | High Speed Data Separator           | 2-81  |

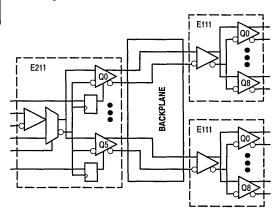

| E211           | 1:6 Differential Clock Distribution | 2-95  |

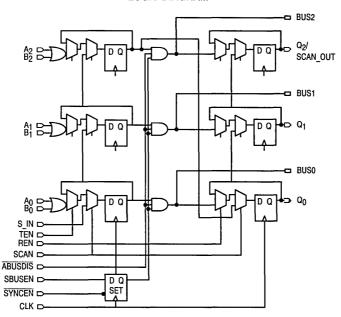

| E212           | 3-Bit Scannable ECL Driver          | 2-100 |

| E241           | 8-Bit Scannable Register            | 2-102 |

| E256           | 3-Bit 4:1 Mux Latch                 | 2-104 |

| E336           | 3-Bit Registered Bus Transceiver    | 2-107 |

| E337           | 3-Bit Scannable Bus Tracnsceiver    | 2-109 |

| E404           | Quad High Freq Diff AND             | 2-112 |

| E416           | Quint High Freq Line Receiver       | 2-114 |

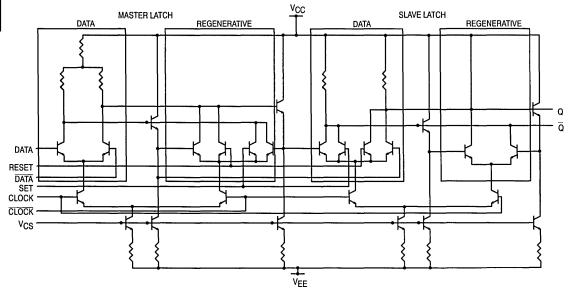

| E431           | 3-Bit Diff Set/Reset Flip-Flop      | 2-116 |

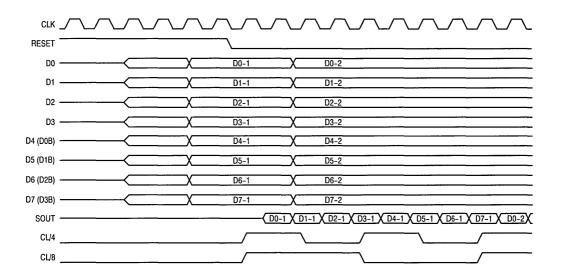

| E445           | 1:4 Serial/Parallel Converter       | 2-118 |

| E446           | 4:1 Parallel/Serial Converter       | 2-124 |

| E451           | 6-Bit D Reg Diff D and Clk          | 2-128 |

| E452           | 5-Bit D Reg Diff D Clk and Q        | 2-130 |

| E457           | Triple High Freq Diff 2:1 Mux       | 2-132 |

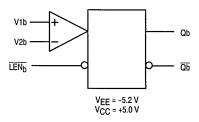

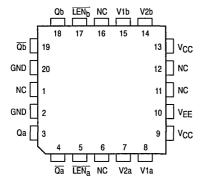

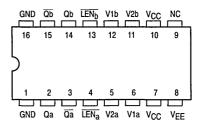

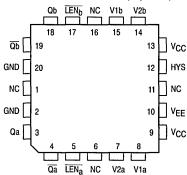

| E1651*         | Dual Analog Comparator              | 2-135 |

| E1652*         | Dual Analog Comparator              | 2-139 |

#### Numeric Index — ECLinPS Lite Devices

| MC10/<br>MC100 | Function                          | Page |

|----------------|-----------------------------------|------|

| EL01           | 4-Input OR/NOR                    | 3-5  |

| EL04           | 2-Input AND/NAND                  | 3-6  |

| EL05           | 2-Input Differential AND/NAND     | 3-7  |

| EL07           | 2-Input XOR/XNOR                  | 3-9  |

| EL11           | 1:2 Differential Fanout Buffer    | 3-10 |

| EL12           | Low Impedance Driver              | 3-12 |

| EL15           | 1:4 Clock Distribution Chip       | 3-13 |

| EL16           | Differential Line Receiver        | 3-16 |

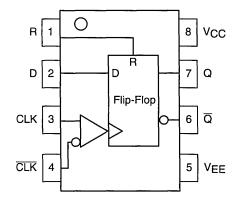

| EL31           | D Flip-Flop With Set and Reset    | 3-18 |

| EL32           | Integrated ÷2 Divider, Diff Input | 3-20 |

| EL33           | Integrated +4 Divider, Diff Input | 3-22 |

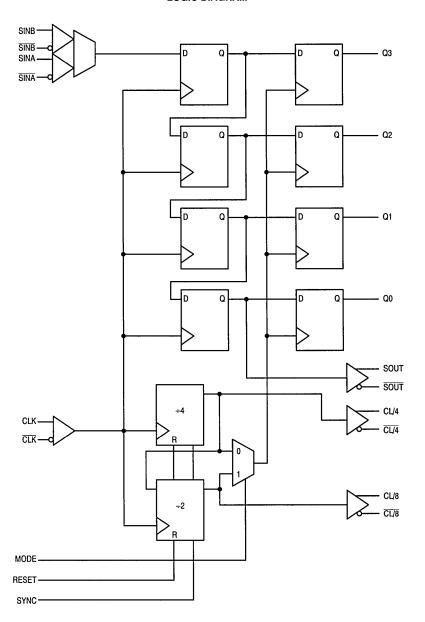

| EL34           | ÷2, ÷4, ÷8 Clock Generation Chip  | 3-24 |

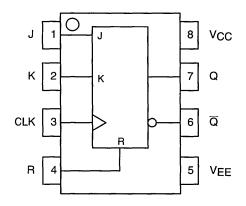

| EL35           | JK Flip-Flop                      | 3-26 |

| MC100  | Function                            | Page |

|--------|-------------------------------------|------|

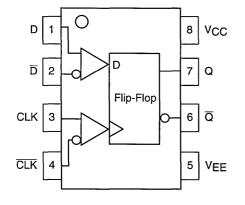

| EL51   | D Flip-Flop w/ Reset and Diff Clock | 3-28 |

| EL52   | D Flip-Flop w/ Diff Data and Clock  | 3-30 |

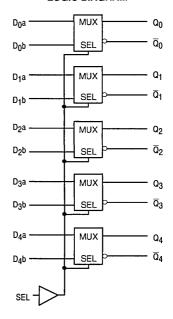

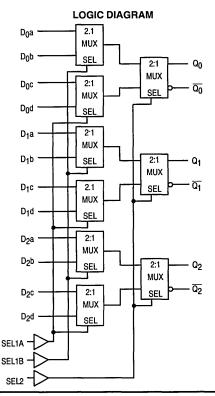

| EL57   | 4:1 Differential Multiplexer        | 3-32 |

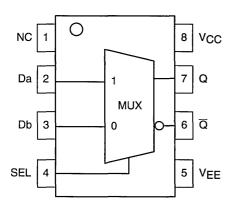

| EL58   | 2:1 Multiplexer                     | 3-34 |

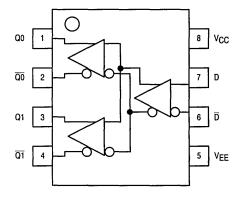

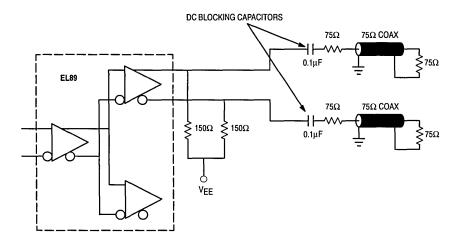

| EL89*  | Coaxial Cable Driver                | 3-35 |

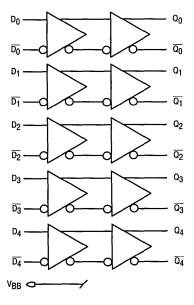

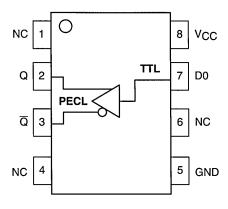

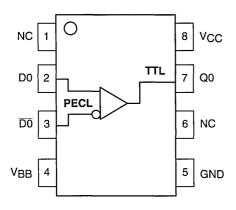

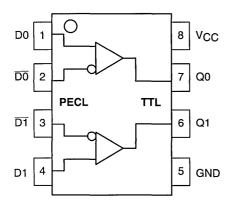

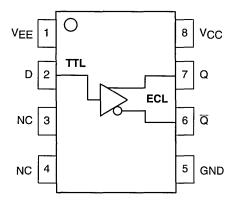

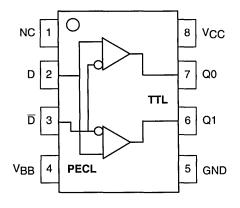

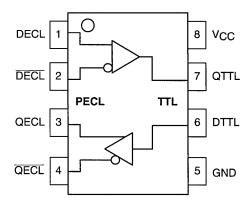

| ELT20  | TTL to Differential PECL Translator | 3-38 |

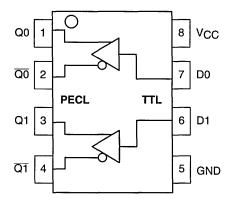

| ELT21  | Differential PECL to TLL Translator | 3-39 |

| ELT22  | Dual TTL to Diff PECL Translator    | 3-40 |

| ELT23† | Dual Diff PECL to TTL Translator    | 3-41 |

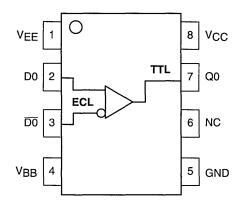

| ELT24  | Dual TTL to Diff ECL Translator     | 3-42 |

| ELT25  | Dual Diff ECL to TTL Translator     | 3-43 |

| ELT26  | 1:2 Fanout Diff PECL to TTL Trans   | 3-44 |

| ELT28  | TTL to Diff PECL/Diff PECL to TTL   | 3-45 |

|        |                                     |      |

MC10/

<sup>\*10</sup>E version only

<sup>\*</sup> Available in 10EL version only.

<sup>†</sup> Available in 100ELT version only.

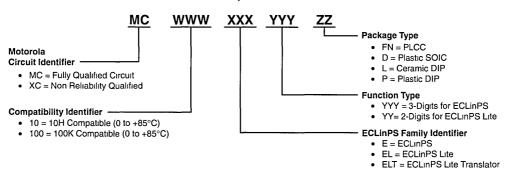

# SECTION 2 Device Nomenclature

#### **ECLinPS**, **ECLinPS** Lite

# **SECTION 3 Selection Guide**

EL01

| Gates                   |  |  |  |

|-------------------------|--|--|--|

| Single 4-Input OR/NOR   |  |  |  |

| Quad 4-Input OR/NOR     |  |  |  |

| Single 2-Input AND/NAND |  |  |  |

|   | Quad 4-Input OH/NOH                  | E101 |

|---|--------------------------------------|------|

|   | Single 2-Input AND/NAND              | EL04 |

|   | Quint 2-Input AND/NAND               | E104 |

|   | Single 2-Input Differential AND/NAND | EL05 |

|   | Single 2-Input XOR/XNOR              | EL07 |

|   | Quint 2-input XOR/XNOR               | E107 |

| i | Quad 2-Input AND/NAND, Differential  | E404 |

#### Buffers

| 9-Bit Buffer    |                  | E122 |

|-----------------|------------------|------|

| 1.2 Differentia | al Fanout Buffer | EL11 |

| 1:4 Clock Dis   | stribution Chip  | EL15 |

| 1.9 Differentia | al Clock Driver  | E111 |

| Single Driver   | With Enable      | EL12 |

| Quad Driver     | with Enable      | E112 |

| 3-Bit Scanna    | ble Driver       | E212 |

#### Flip-Flops/Registers

| Single D (Set & Reset)                     | EL31 |

|--------------------------------------------|------|

| 4-Bit D (Async Set & Reset)                | E131 |

| Single D (Reset & Differential Clock)      | EL51 |

| 6-Bit D (Async Reset)                      | E151 |

| 6-Bit D (Differential Data & Clock Inputs) | E451 |

#### Flip-Flops/Registers (continued)

| 9-Bit Hold Register                  | E143 |

|--------------------------------------|------|

| 3-Bit D (Edge Triggered Set & Reset) | E431 |

| Single JK                            | EL35 |

| Single D (Differential Data & Clock) | EL52 |

| 5-Bit Differential D Register        | E452 |

#### Latches

| Γ | 6-Bit D (Async Reset)            | E150 |

|---|----------------------------------|------|

|   | 9-Bit Latch w/Parity Gen/Checker | E175 |

#### Multiplexers

| Single 4.1 Differential Multiple | xer EL57 |

|----------------------------------|----------|

| Single 2:1 Multiplexer           | EL58     |

| 5-Bit 2:1 Multiplexer            | E158     |

| 3-Bit 4:1 Multiplexer            | E171     |

| 2-Bit 8:1 Multiplexer            | E163     |

| Single 16:1 Multiplexer          | E164     |

| Quad 2.1 Mux, Individual Sele    | ect E157 |

| Triple 2:1 Mux, Differential     | E457     |

#### **Mux-Latches**

| 5-Bit 2:1 Mux-Latch | E154 |

|---------------------|------|

| 6-Bit 2:1 Mux-Latch | E155 |

| 3-Bit 4:1 Mux-Latch | E156 |

| 3-Bit 4:1 Mux-Latch | E256 |

# 1

# Selection Guide (continued)

#### **Mux-Registers**

| 6-Bit 2:1 Mux-Register                    | E167 |

|-------------------------------------------|------|

| Counters                                  |      |

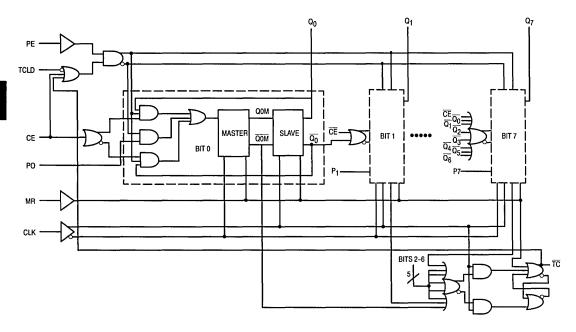

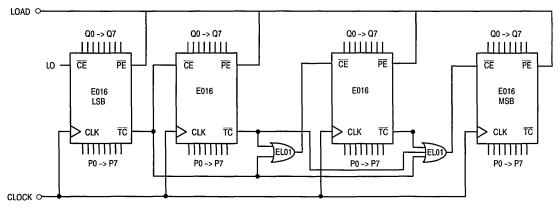

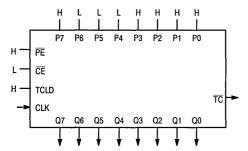

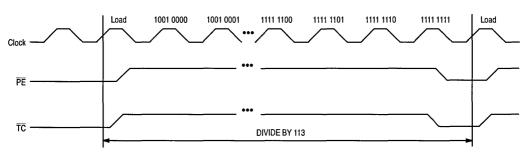

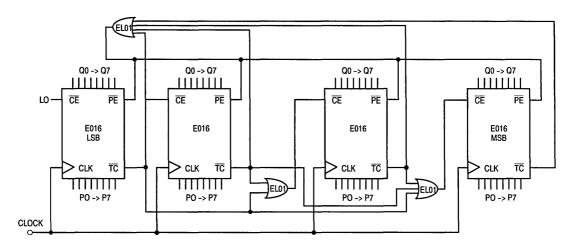

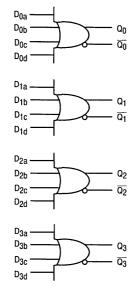

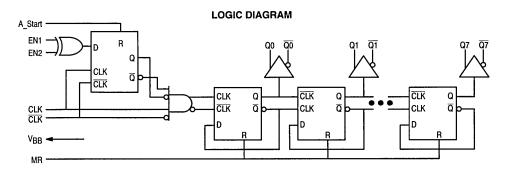

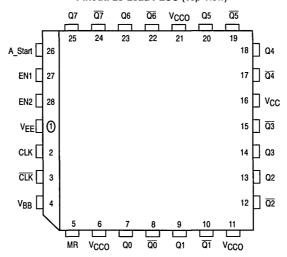

| 8-Bit Synchronous Binary Counter          | E016 |

| 6-Bit Synchronous Universal Counter       | E136 |

| 8-Bit Triple Counter                      | E137 |

| Shift Registers                           | •    |

| 8-Bit Shift Register (bidirectional)      | E141 |

| 8-Bit Scannable Register (unidirectional) | E241 |

| 9-Bit Shift Register (unidirectional)     | E142 |

| 9-Bit Hold Register                       | E143 |

| 3-Bit Scannable Driver                    | E212 |

| Parity Generator/Comparator               |      |

|                                           |      |

| 12-Bit Parity Generator/Checker         | E160 |

|-----------------------------------------|------|

| 9-Bit Magnitude Comparator              | E166 |

| 8-Bit Error Detection/Correction (EDAC) | E193 |

| 9-Bit Latch w/Parity Gen/Checker        | E175 |

#### **Line Receivers**

| Quint Differential Line Receiver            | E116 |

|---------------------------------------------|------|

| 1:9 Differential Clock Driver               | E111 |

| 6-Bit D Reg., Diff Data & CLK Inputs        | E451 |

| Quint High Freq. Differential Line Receiver | E416 |

| 5-Bit Differential D Register               | E452 |

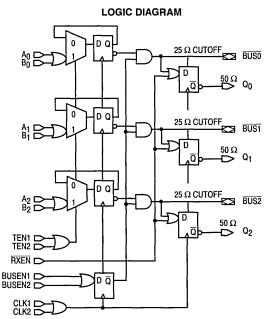

#### **Bus Transceivers**

| 3-Bit Registered Bus Transceiver         | E336 |

|------------------------------------------|------|

| 3-Bit Scannable Register Bus Transceiver | E337 |

#### Translators

| TLL to Differential PECL Translator            | ELT20  |

|------------------------------------------------|--------|

| Differential PECL to TTL Translator            | ELT21  |

| Dual TTL to Differential PECL Translator       | ELT22  |

| Dual Differential PECL to TTL Translator       | ELT23† |

| Dual TTL to Differential ECL Translator        | ELT24  |

| Dual Differential ECL to TTL Translator        | ELT25  |

| 1:2 Fanout Differential PECL to TTL Translator | ELT26  |

| TTL to Diff PECL/Diff PECL to TTL Translator   | ELT28  |

#### Miscellaneous

| Miscellancous                                |        |

|----------------------------------------------|--------|

| Integrated +2 Divider, Differential Input    | EL32   |

| Integrated +4 Divider, Differential Input    | EL33   |

| +2, +4, +8 Clock Generation Chip             | EL34   |

| Coaxial Cable Driver                         | EL89*  |

| Programmable Delay Chip, Digital             | E195   |

| Programmable Delay Chip, Digital & Analog    | E196   |

| Hard Disk Data Separator                     | E197*  |

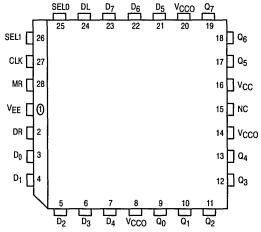

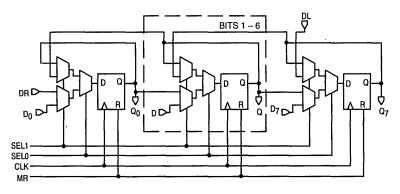

| 1:4 Serial/Parallel Converter                | E445   |

| 4:1 Parallel/Serial Converter                | E446   |

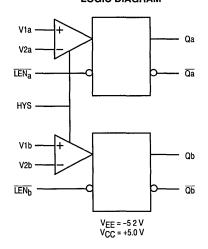

| Dual Analog Comparator with Latch            | E1651* |

| Dual Analog Comparator w/ Latch & Hysteresis | E1652* |

<sup>\*</sup> Available in 10E or 10EL Version Only.

<sup>†</sup> Available in 100ELT Version Only

# MOTOROLA SEMICONDUCTOR GENERAL INFORMATION

# SECTION 4 Family Overview

#### Introduction

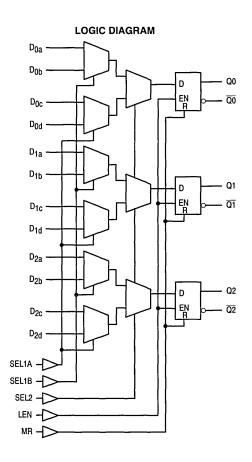

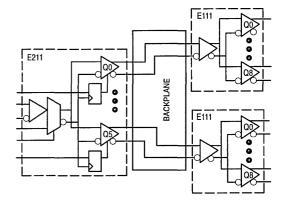

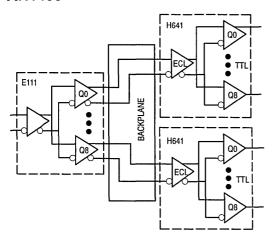

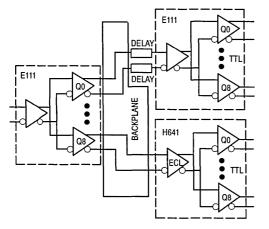

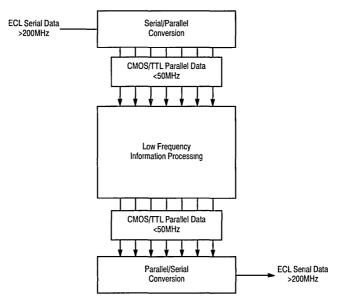

Recent advances in bipolar processes have led to a proliferation of very high speed LSI and VLSI gate arrays in high end computer applications. The advent of these high speed arrays has created a need for a high speed logic family to tie or "glue" them together. Because arrays have a finite amount of circuitry and I/O pins, glue functions which are sensitive to either of these parameters may be better performed off of the array. In addition glue functions which require very tight skew control may be difficult to perform on an array due to the inherent skew of the large packages associated with large gate arrays. Therefore although the trend is to push more and more of the logic onto the array, there are design constraints which make performing some of the logic, such as clock distribution, multiplexing, decoding, latching, memory addressing and translating, in glue an attractive alternative.

The high end computer segment is not the only market segment pushing for higher performance logic parts. ATE, instrumentation and communication designs can have data rate requirements ranging from 300MHz to as high as 2.5GHz. Because large high speed arrays do not always lend themselves to passing high frequency signals on and off chip, portions of the designs must be realized with discrete logic. The current bipolar logic families are not capable of operating at these high frequencies.

To answer the call for a very high speed bipolar logic family Motorola has designed and produced the ECLinPS (ECL in Pico Seconds) logic family. The family was designed to meet the most stringent of system requirements in speed, skew and board density as well as maintaining compatibility to existing ECL families.

#### **ECL Design Benefits**

The speed benefits of an ECL design over those of alternative logic technologies are well documented, however there are a number of other important features that make ECL an attractive technology for system designs. The ECLinPS logic family, as with other ECL families, affords the following advantages:

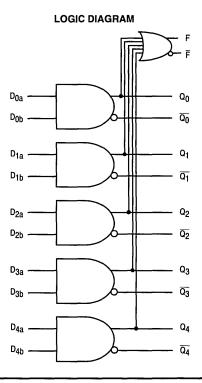

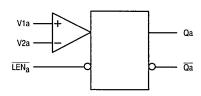

#### **Complimentary Outputs**

Complimentary outputs are available on many functions with equal propagation delays between the two paths. This alleviates the need for external inverters and saves system power and board space while maintaining exceptional system timing.

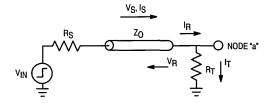

#### **Transmission Line Drive Capability**

The low output impedance, high input impedance and high current drive capability of ECL makes it an ideal technology for driving transmission lines. Regardless of the technology, as system speeds increase, interconnect becomes more of a transmission line phenomenon. With ECL no special line driving devices are necessary, as all ECL devices are line drivers.

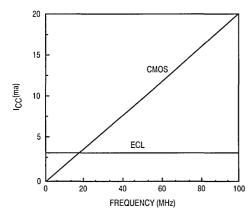

#### **Constant Power Supply Current Drain**

Because of the differential amplifier design used for ECL circuits, the current is not switched on and off but rather simply steered between two paths. Thus the current drain of an ECL device is independent of the logic state and the frequency of operation. This current stability greatly simplifies system power supply design.

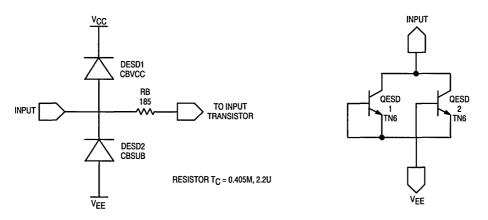

#### Input Pulldown Resistors

ECL inputs have  $50K\Omega-75K\Omega$  internal pulldown resistors which pull the input to VEE (logic LOW) when left open. This allows unused inputs to be left open and greatly simplifies logic design.

#### **Differential Drive Capability**

Because of the presence of high current drive complimentary outputs, ECL circuits are ideally suited for driving twisted pair lines or cables over long distances. With common mode noise rejection of 1V or more, ECL line receivers are less susceptible to common mode noise. In addition, their differential inputs need only a few hundred millivolt voltage differences to correctly interpret the logic.

#### **High Speed Design Philosophy**

Today a truly high speed logic family needs more than simply short propagation delays. The minimization of all types of skew, as well as a level of logic density which affords a smaller amount of board space for an equivalent function, are also necessities of a high speed family. The following summary will outline the steps taken by Motorola to achieve these goals in the development of the ECLinPS logic family.

#### **Fast Propagation Delays**

The ECLinPS family boasts 500ps maximum packaged gate delays and typical flip-flop toggle frequencies of 1.4GHz. Simple gate functions show typical propagation delays of 360ps at 25mW of power for a speed power

product of only 9pJ. For higher density devices internal gates run at 100ps with 5mW of power for a speed power product of only 0.5pJ.

#### **Internal Differential Interconnect**

The propagation delay window size, skew between rising and falling inputs and susceptibility to noise are all phenomenon which are exacerbated by VBB switching reference variation. By extensively using differential interconnects internal to the chip, the ECLinPS family has been able to achieve superior performance in these areas.

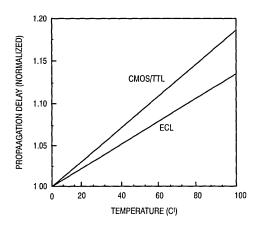

#### **Propagation Delay Temperature Insensitivity**

The variation of propagation delay through an ECLinPS device across temperature is typically less than 50ps. This stability allows for faster designs due to tighter delay windows across temperature.

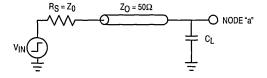

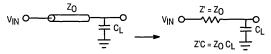

#### Input Impedance and Loading Capacitance

The input structures of the ECLinPS family show a positive real impedance across the applicable input frequency range. This ensures that the system will remain stable and operate as designed over a wide range of input frequencies. The input loading capacitance typically measures only 1.5pF and is virtually independent of input fanout as the device capacitance is less than 5% of the total. Because the propagation delay of a signal down a transmission line is adversely affected by loading capacitance, the overall system speed is enhanced.

#### **Input Buffers**

To minimize propagation delays in a system environment, inputs with a large internal fanout are buffered to minimize the loading capacitance on the transmission line.

#### **High Level of Integration**

28-pin designs allow for the design of 9-bit functions for implementation in byte plus parity applications. Full byte plus parity implementation reduces total package count and saves expensive board space.

#### **Space Efficient Package**

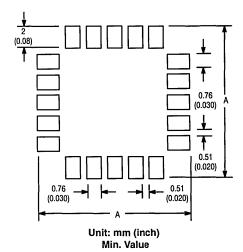

Surface mount PLCC package affords a high level of integration with a minimum amount of required board space. Quad layout of the package equalizes pin lengths thus minimizing the skew between similar internal paths.

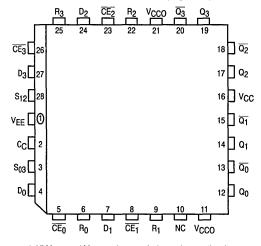

#### Flow Through Pin Assignment

Input and output pins have been laid out in a flow through pattern with the inputs on one side of the package and the outputs on the other. This flow through pattern helps to simplify the PC board layout operation.

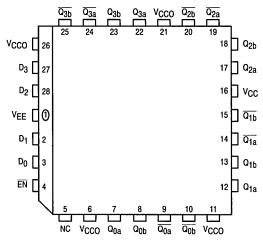

#### Multiple V<sub>CCO</sub> pins

To minimize the noise generated in simultaneous switching situations, a minimum of three single-ended outputs per VCCO has been employed in the family.

Optimum placement of these VCCOs also results in superior output-to-output skew.

#### Advanced Bipolar Processing

The ECLinPS logic family is fabricated using Motorola's MOSAIC III process, a process which is two generations ahead of the process used in the development of the 10H family. The small geometries and feature sizes of the MOSAIC III process enable the ECLinPS logic family to boast of a nearly three-fold improvement in speed at less than half the power of existing ECL logic families.

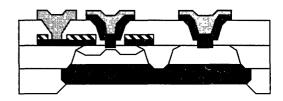

The MOSAIC III process is a double polysilicon process which uses a unique self-alignment scheme for device electrode and isolation definition. The process features self aligned submicron emitters as well as polysilicon base, collector and emitter electrodes. In addition, polysilicon resistors, diodes and capacitors are available to minimize the parasitic capacitance of an ECL gate. Figure 1.1 shows a cross section for an NPN device using the MOSAIC III process.

Figure 1.1. MOSAIC III Cross Section

By incorporating the use of polysilicon contacts and resistors through the MOSAIC III process, the parasitic capacitances of an ECLinPS gate are minimized, thus minimizing the time constants which comprise the switching delays of the gate. The resultant gates show delays of 100ps for internal gates and 200ps for output gates capable of driving  $50\Omega$  loads. The small geometries of the process, nearly 350% reduction in device area compared to a 10H device, allow these internal gate delays to be achieved at only  $800\mu\text{A}$  of current.

#### **Universal Compatibility**

Each member of the ECLinPS family is available in both of the existing ECL standards: 10E series devices are compatible with the MECL 10H family; 100E series devices are compatible with ECL 100K. In addition, to maintain compatibility with temperature-compensated, three-level series-gated gate arrays, the 100E devices are guaranteed to operate without degradation to a  $V_{\mbox{\footnotesize FE}}$  of -5.46V.

The section below presents a comparison between the two standards in the new context of the ECLinPS family.

The user is also referred to the Electrical Characteristics section of this book as well as appropriate family data books and other literature for descriptive information on the earlier ECL families.

Because no supplier previous to Motorola has offered both ECL standards on an identical process, comparison of existing 10H and 100K style devices has some limitations. Comparison of the two standards fabricated with two different processes has sometimes led to the erroneous conclusion that there are inherent AC performance differences between them. In reality this is not the case. The only inherent difference between the two standards is the difference in the behavior of the DC characteristics with temperature.

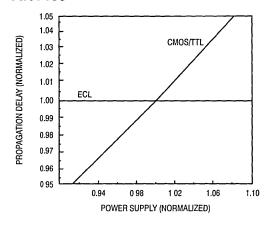

#### **AC Performance**

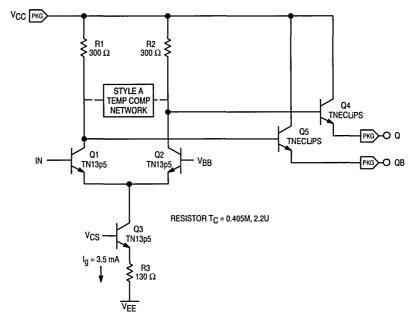

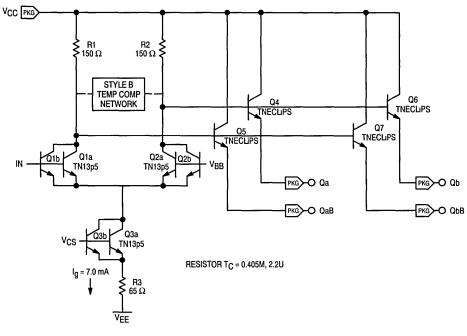

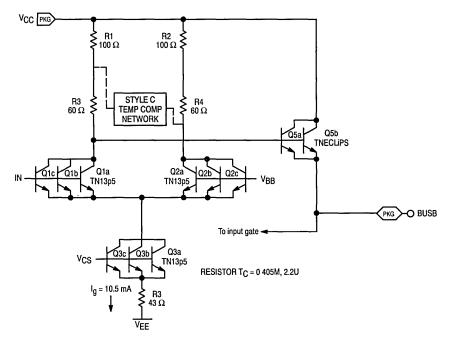

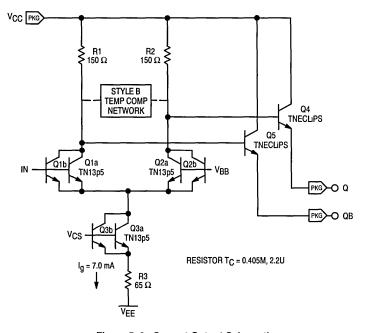

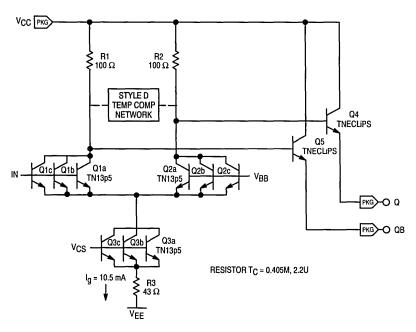

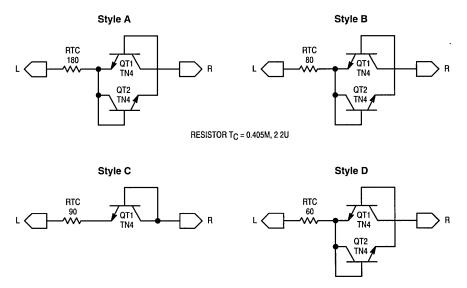

From an IC design standpoint the only differences between a 10E device and a 100E device in the ECLinPS family is a small temperature compensation network in the 100E output gate, and very minimal differences in the two bias generator networks. Therefore one would expect that from an AC stand-point the performance of the two standards in the ECLinPS family should be nearly identical; measurements prove this to be the case. There is no significant measurable difference in the rise/fall times, propagation delays or toggle frequencies when comparing a 10E and 100E device. The minor difference between previous 10H and 100K designs is due to the fact that the two are fabricated on different processes, and in some cases are designed for operation at different power levels.

#### Summary

Summarizing the above information, in general, the two ECL design standards, although differing somewhat in DC parameters, are nearly identical when one compares the AC performance for a given device. There may be very small differences in the AC measurements due to the slightly smaller output swing of the 100E device. However, these differences are negligible when compared to the absolute value of the measurements. Therefore, from an AC stand-point, there is no real advantage in using one standard over the other, thus removing AC performance as a decision variable in high-speed system design.

#### **Packaging**

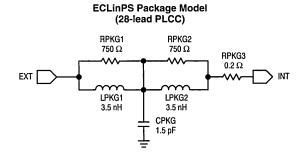

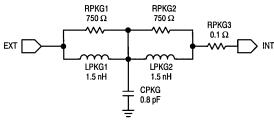

During the definition phase of the ECLinPS family, much attention was placed on the identification of a suitable package for the family. The package had to meet the criteria of minimum parasitics and propagation delays along with an attractive I/O vs board space relationship. Although the DIP package offered a level of familiarity and convenience, the performance of the package with a very high speed logic family was inadequate. In addition to the obvious parasitics and board space problems, the propagation delays through the DIP package were nearly twice as long as the delay through the silicon.

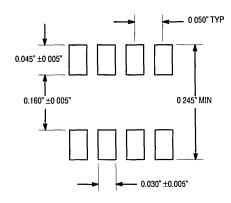

The 28-pin PLCC package emerged as the clear favorite both internally and with the high speed market in general. The package offers a quad layout to minimize both lead lengths and lead length differences. As a result, the parasitics and delays of the package are very well suited for a high speed logic family. In addition, the nearly matched lead lengths allow for tighter skew among similar paths through the chip.

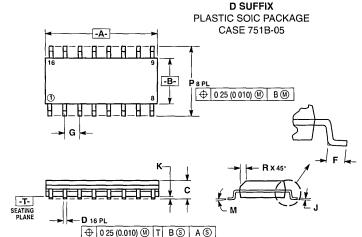

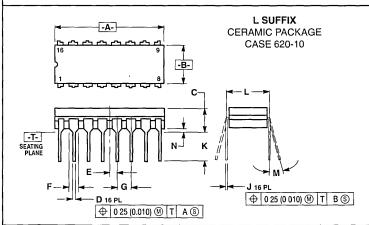

The board density potential of the PLCC is also attractive in that it allows for a nearly 100% reduction in board space when compared to the DIP alternative. The package is approximately a half inch square with 50 mil spaced J-bend leads. More detailed measurements can be found in the package section of this data book. The J-bend leads provide a smaller footprint than a gull wing package and propose fewer temperature expansion coefficient mismatch problems than the leadless alternative.

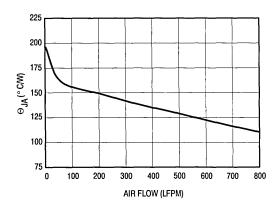

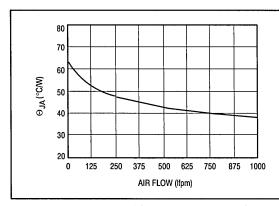

Thermally, the standard PLCC exhibits a  $\Theta$ JA of 43.5°C per watt at 500lfpm air flow. With this thermal resistance most 28-pin functions can be implemented with the MOSAIC III process without encountering any severe thermal problems. For more details on thermal issues of the ECLinPS family refer to the thermal section of this data book.

#### **Abbreviation Definitions**

The following is a list of abbreviations found in this data book and a brief definition of each.

#### Current

| lcc             | Total power supply current drawn from the positive supply by an ECLinPS unit under test.                         |

|-----------------|------------------------------------------------------------------------------------------------------------------|

| IEE             | Total power supply current drawn from an ECLinPS device under test by the negative supply.                       |

| lıL             | Current drawn by the input of an ECLinPS device with a specified low level (V $_{IL}$ min) forced on the input.  |

| INH             | Current drawn by the input of an ECLinPS device with a specified high level (V $_{IH}$ max) forced on the input. |

| lout            | The current sourced by an output under specified load conditions.                                                |

| Voltage         |                                                                                                                  |

| $V_{BB}$        | The switching reference voltage.                                                                                 |

| $V_{BE}$        | Base-to-emitter voltage drop of a transistor at specified collector and base currents.                           |

| V <sub>CB</sub> | Collector-to-base voltage drop of a transistor at specified collector and base currents.                         |

| vcc                 | The most positive supply voltage to an ECLinPS device.                                                                                                         | VCUT               | The logic LOW voltage level for ECL BUS outputs which attain cutoff of the output emitter follower.                                    |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| vcco                | Power supply connection to the output emitter follower of an ECLinPS gate. For the ECLinPS logic family V <sub>CC</sub> and V <sub>CCO</sub> are common nodes. | V <sub>SUP</sub>   | The maximum voltage difference between VEE and VCC for the E1651 comparator.                                                           |

|                     | , 100 mm 1000 ms 11                                                                                                                                            | Timing Pa          | arameters                                                                                                                              |

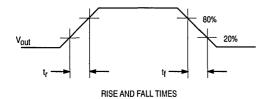

| VEE                 | The most negative supply voltage to an ECLinPS device.                                                                                                         | tR                 | Waveform rise time of an output signal measured from the 20% to 80% levels of the signal.                                              |

| VIH                 | Nominal input logic HIGH voltage level.                                                                                                                        |                    | non the 20% to 00% levels of the signal.                                                                                               |

| V <sub>IH</sub> max | Maximum (most positive) logic HIGH voltage level for which all parametric specifications hold.                                                                 | tF                 | Waveform fall time of an output signal measured from the 20% to 80% levels of the signal.                                              |

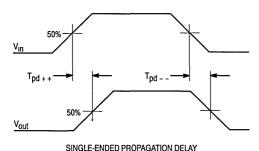

| V <sub>IH</sub> min | Minimum (least positive) logic HIGH voltage level for which all parametric specifications hold.                                                                | T <sub>PD±±</sub>  | Propagation delay of a signal measured for a rising/falling input to a rising/falling output.                                          |

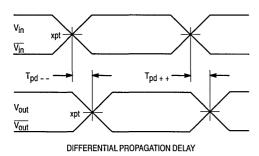

| $v_{IL}$            | Nominal input logic LOW voltage.                                                                                                                               | xpt                | The crossing point of a differential input or output signal. The reference point for which differential delays are measured.           |

| V <sub>IL</sub> max | Maximum (most positive) logic LOW voltage level for which all parametric specifications hold.                                                                  | T <sub>PLH</sub>   | The propagation delay for an output transitioning from a logic LOW level to a logic HIGH level.                                        |

| V <sub>IL</sub> min | Minimum (least positive) logic HIGH voltage level for which all parametric specifications hold.                                                                | T <sub>PHL</sub>   | The propagation delay for an output transitioning from a logic HIGH level to a logic LOW level.                                        |

| VOH                 | Output logic HIGH voltage level for the specified load condition.                                                                                              | fMAX               | Maximum input frequency for which an ECLinPS flip flop will function correctly.                                                        |

| VOHA                | Output logic HIGH voltage level with the inputs biased at $V_{IH}$ min or $V_{OL}$ max.                                                                        | fCOUNT             | Maximum input frequency for which an ECLinPS counter will function properly.                                                           |

| V <sub>OH</sub> max | Maximum (most positive) logic HIGH output voltage level.                                                                                                       | <sup>f</sup> SHIFT | Maximum input frequency for which an ECLinPS shift register will function properly.                                                    |

| V <sub>OH</sub> min | Minimum (least positive) logic HIGH output voltage level.                                                                                                      | <sup>t</sup> SKEW  | The maximum delay difference between similar paths on a single ECLinPS device.                                                         |

| V <sub>OL</sub>     | Output logic LOW voltage level for the specified load condition.                                                                                               | t <sub>S</sub>     | Setup time: the minimum amount of time an input must transition before a clock transition to ensure                                    |

| VOLA                | Output logic LOW voltage level with the inputs biased at $V_{IH}$ min or $V_{OL}$ max.                                                                         |                    | proper function of the device.                                                                                                         |

| V <sub>OL</sub> max | Maximum (most positive) logic LOW output voltage level.                                                                                                        | tΗ                 | Hold time: the minimum amount of time an input must remain asserted after a clock transition to ensure proper operation of the device. |

| V <sub>OL</sub> min | Minimum (least positive) logic LOW output voltage level.                                                                                                       | tRR                | Release time or Reset Recovery Time: the minimum amount of time after a signal is de-asserted that a different input must wait before  |

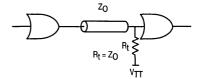

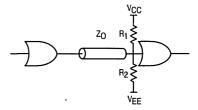

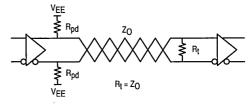

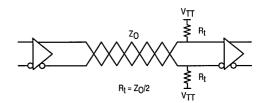

| VTT                 | Output termination voltage for ECLinPS open emitter follower outputs.                                                                                          |                    | assertion to ensure proper functionality of the device.                                                                                |

| Vpp                 | Mınimum peak-to-peak ınput voltage for differential input devices.                                                                                             | t <sub>W</sub> min | Minimum pulse width of a signal necessary to ensure proper functionality of a device.                                                  |

| VCMR                | The voltage range in which the logic HIGH voltage level of a differential input signal must fall for a differential input device.                              |                    |                                                                                                                                        |

#### Temperature

| TSTG | The maximum temperature at which a device may be stored without damage or performance degradation.     |

|------|--------------------------------------------------------------------------------------------------------|

| TJ   | Junction (or die) temperature of an integrated circuit device.                                         |

| TA   | Ambient (environment) temperature existing in the immediate vicinity of an integrated circuit package. |

| ΘЈΑ  | Thermal resistance of an integrated circuit package between the junction and the ambient.              |

| ΘJC  | Thermal resistance of an integrated circuit package between the junction and the case.                 |

| ΘCA  | Thermal resistance of an integrated circuit package between the case and the ambient.                  |

| lfpm | Linear feet per minute.                                                                                |

#### Miscellaneous

| DUT              | Device under test.                                                                                     |

|------------------|--------------------------------------------------------------------------------------------------------|

| C <sub>IN</sub>  | Input capacitance of a device.                                                                         |

| $z_{IN}$         | Input impedance of a device.                                                                           |

| COUT             | Output capacitance of a device.                                                                        |

| Z <sub>OUT</sub> | Output impedance of a device.                                                                          |

| PD               | The total dc power applied to a device, not including any power delivered from the device to the load. |

| $R_{L}$          | Load resistance.                                                                                       |

| RT               | Transmission line termination resistor.                                                                |

| Rp               | An input pull-down resistor.                                                                           |

| PUT              | Pin under test.                                                                                        |

| SMA              | Industry standard PCB connector.                                                                       |

# SECTION 5 Electrical Characteristics

#### **DC Characteristics**

#### **ECLinPS Transfer Curves**

As mentioned in the previous section, except for the E1651, E1652 and E197 all ECLinPS devices are offered in either 10E or 100E versions to be compatible with 10H or 100K ECL logic respectively. The following information will overview the DC characteristics of the two versions of ECLinPS devices, for more detailed discussions the reader is referred to the MECL and F100K data books.

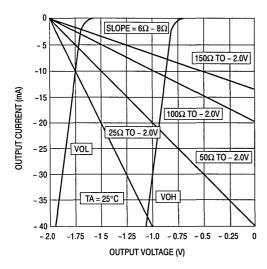

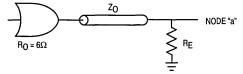

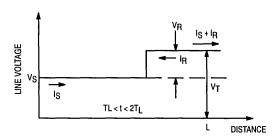

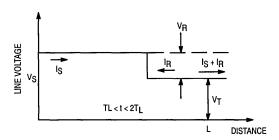

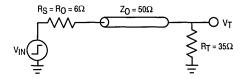

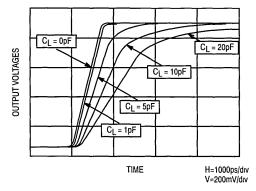

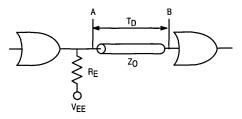

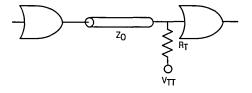

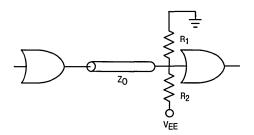

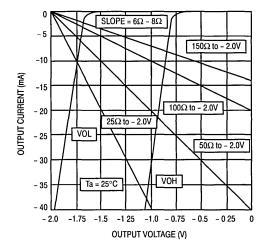

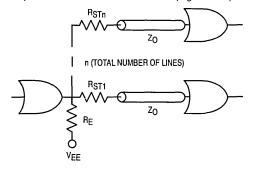

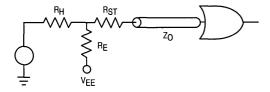

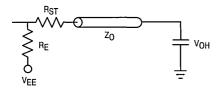

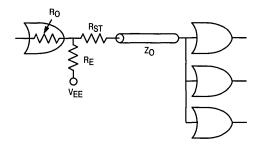

Both 10E and 100E devices produce  $\approx 800\text{mV}$  output swings into a specified  $50\Omega$  to -2.0V load. However, because of the low output impedance (Figure 2.1) of both standards, neither is limited to  $50\Omega$  loads. Larger load resistances can be used to reduce the system power without sacrificing the speed of the device. Of course the overall system speed will be reduced due to the increased delays of the interconnect traces. In addition, to better drive high capacitive lines, smaller resistances, down to  $25\Omega$ , can be used without violating the 50mA max output current specification. It is however recommended that for lines of less than  $35\Omega$ , specialized  $25\Omega$  driver circuits or "ganged" output schemes should be used to ensure optimum long term reliability of the device.

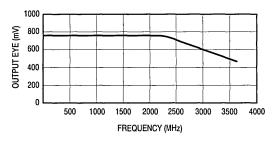

Figure 2.1. Output Characteristics vs Load

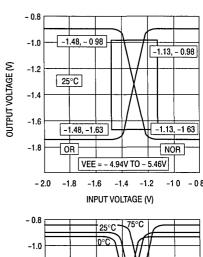

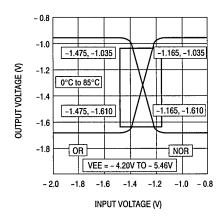

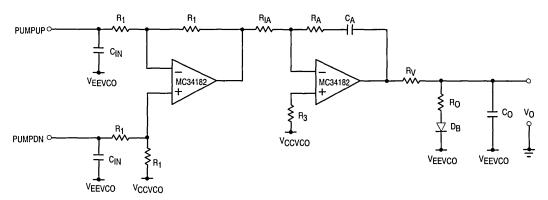

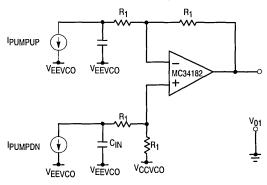

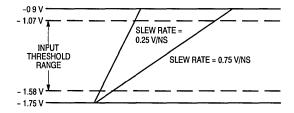

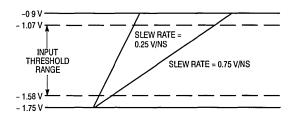

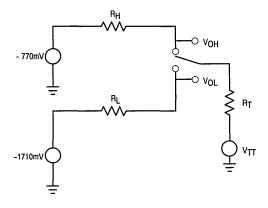

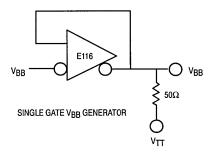

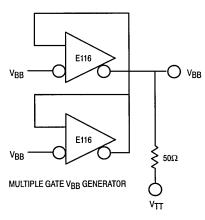

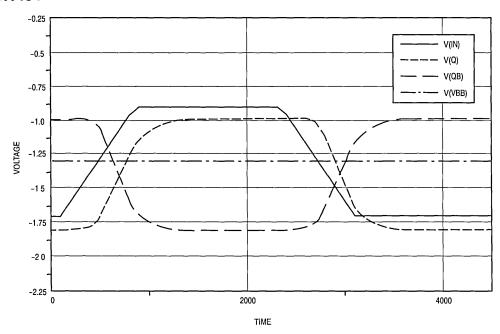

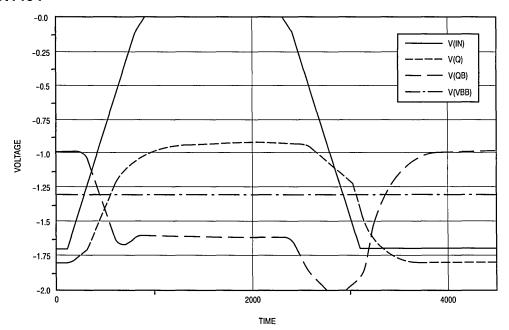

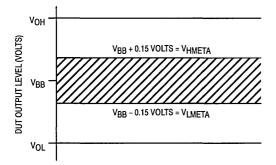

The 10E devices are voltage compensated but not temperature compensated, therefore, although the output voltage levels are insensitive to variations in VEE, they do vary with temperature. The transfer curves in Figure 2.2 pictorially illustrate the behavior of the 10E outputs. In order to maintain noise margins over temperature, it is important that the VBB switching reference tracks with temperature in such a way as to remain centered between the VOH and VOL levels. As shown in Table 2.1, the temperature tracking rates of the VOH and VOL for a 10E device are not equal. Therefore, it is necessary to design the VBB reference such that it tracks at a rate equal to the average rate of the difference between the

Figure 2.2. ECLinPS 10E Transfer Curves

high and low output level tracking rates. Table 2.1 also outlines the temperature tracking behavior of a 10E  $V_{BB}$  switching reference.

| 10E                                       | min    | typ | max  |  |  |

|-------------------------------------------|--------|-----|------|--|--|

| ΔV <sub>OH</sub> /ΔT (mV/°C)              | 1.1    | 1.2 | 1.4  |  |  |

| ΔV <sub>OL</sub> /ΔT (mV/°C)              | 0      | 0.4 | 0.6  |  |  |

| ΔV <sub>BB</sub> /ΔT (mV/°C)              | 0.6    | 0.8 | 1.0  |  |  |

| ΔV <sub>OH</sub> /ΔV <sub>EE</sub> (mV/V) | 0      | 5   | 20   |  |  |

| ΔV <sub>OL</sub> /ΔV <sub>EE</sub> (mV/V) | 0      | 10  | 30   |  |  |

| ΔVBB/ΔVEE (mV/V)                          | 0      | 5   | 20   |  |  |

| 100E                                      | min    | typ | max  |  |  |

| ΔV <sub>OH</sub> /ΔT (mV/°C)              | - 0.15 | 0   | 0.15 |  |  |

| ΔV <sub>OL</sub> /ΔT (mV/°C)              | - 0.30 | 0   | 0.30 |  |  |

| ΔV <sub>BB</sub> /ΔT (mV/°C)              | - 0.20 | 0   | 0.20 |  |  |

| ΔVOH/ΔVEE (mV/V)                          | 0      | 5   | 20   |  |  |

| ΔV <sub>OL</sub> /ΔV <sub>EE</sub> (mV/V) | 0      | 10  | 30   |  |  |

| ΔV <sub>BB</sub> /ΔV <sub>EE</sub> (mV/V) | 0      | 5   | 20   |  |  |

Table 2.1. ECLinPS Voltage Level Tracking Rates

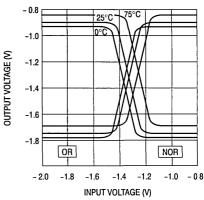

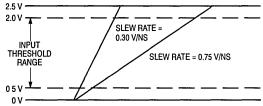

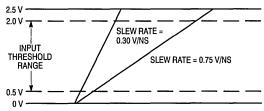

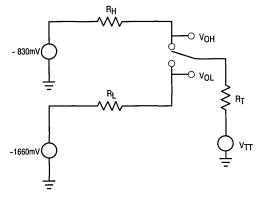

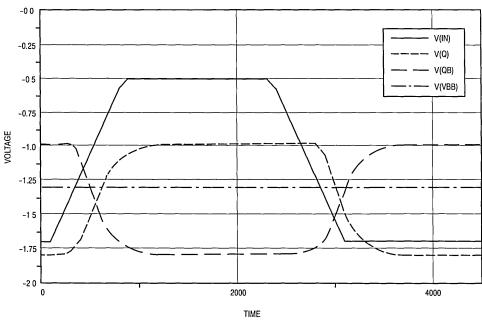

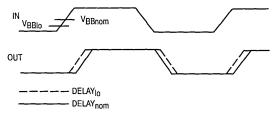

The 100E devices, on the other hand, are temperature and voltage compensated, therefore, the output levels remain fairly constant over variations in both VEE and temperature. Figure 2.3 shows the transfer characteristics for a 100E device. The associated tracking rates are illustrated in Table 2.1. Notice that in this case the VBB switching reference is designed to remain constant over temperature to maintain an optimum position within the output swing of the device. This flat temperature tracking of the internal reference levels leads to a phenomena particular to the 100E devices.

Figure 2.3. ECLinPS 100E Transfer Characteristics

Since the V<sub>BE</sub>s of the current source transistor reduce with temperature, if the current source reference remains constant, as is the case for 100E devices, the I<sub>EE</sub> of the device will vary with temperature. Careful scrutiny of the data sheets will reveal that the worst case I<sub>EE</sub> for a function is higher for the 100E version than the 10E version of that device. As a result, from a power standpoint a 100E device operating at 85°C with a – 4.5V V<sub>EE</sub> will be nearly identical to a 10E device operating with a – 5.2V V<sub>EE</sub> under identical temperature conditions.

Although differing somewhat in many DC parameters, 10E and 100E devices do share a couple of the same DC characteristics. Both designs show superior IEE vs VEE tracking rates due to the design of the voltage regulator. With a tracking rate of <3%/V, this variation can effectively be ignored during system design. The output level and reference level variation with VEE are also outstanding as can be seen in Table 2.1.

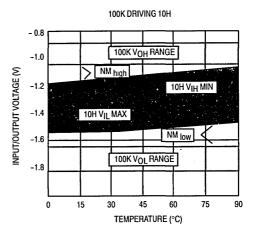

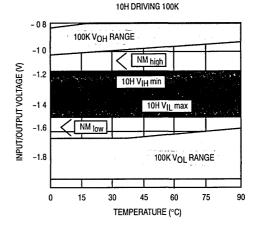

#### **Noise Margin**

The noise margin of a device is a measure of a device's resistance to undesirable switching. For ECLinPS, as well as all ECL devices, noise margin is a DC specification. The noise margin is defined as the difference between the voltage level of an output of the sending device and the required voltage level of the input of the receiving device. Therefore a worst case noise margin can be calculated from the ECLinPS data sheets by simply subtracting the V<sub>IL</sub> max or V<sub>IH</sub> min from the V<sub>OL</sub> min or V<sub>OH</sub> max respectively. Table 2.2 below illustrates the worst case and typical noise margins for both 10E and 100E ECLinPS devices. Notice that the typical noise margins are approximately 100mV larger than the worst case.

|                         | 10  | Œ   | 100E |     |  |  |

|-------------------------|-----|-----|------|-----|--|--|

|                         | min | typ | min  | typ |  |  |

| NM <sub>HIGH</sub> (mV) | 150 | 240 | 140  | 210 |  |  |

| NM <sub>LOW</sub> (mV)  | 150 | 280 | 145  | 230 |  |  |

Table 2.2. DC Noise Margins

As mentioned above, the noise margins of a device are a DC measurement and thus can lead to some false impressions of the noise immunity of a system. For instance, from the chart the worst case noise margin is 140mV for a high level of a 100E device. This would suggest that an undershoot on this line of greater than 140mV could cause an error in the system. This however is not necessarily the case as the determination as to whether or not an AC noise signal is propagated is dependent on line impedances, output impedances and propagation delays as well as noise margins.

#### **AC Characteristics**

#### **Parameter Definitions**

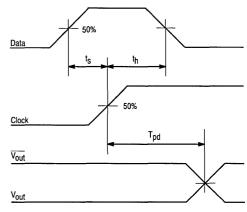

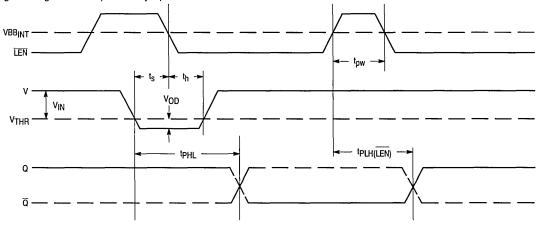

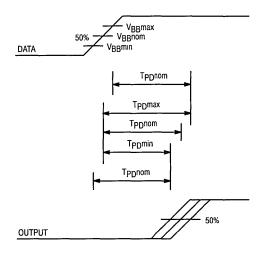

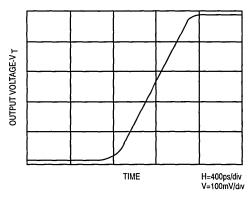

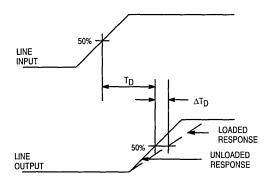

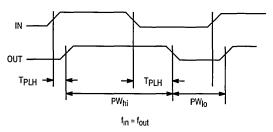

The device data sheets in Section 3 contain specifications for the propagation delays and rise/fall times for each of the devices in the ECLinPS family. In addition, where applicable, skew, setup/hold, maximum toggle frequencies (fMAX), reset recovery and minimum pulse width specifications are included. The waveforms and terminologies used in describing the propagation delays and rise/fall times of the ECLinPS family are depicted in Figure 2.4 below.

Figure 2.4. ECLinPS TpD Measurement Waveforms

Propagation delays and rise/fall times are generally well understood parameters, however, there is sometimes confusion surrounding the definitions of more specialized AC parameters such as skew, setup/hold times, release times, and maximum frequency. The following few paragraphs will outline the ways in which Motorola defines these parameters.

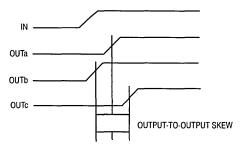

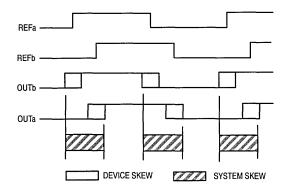

#### Skew Times

In the design of high speed systems skew plays nearly as important a role as propagation delay. The majority of the devices in the ECLinPS family have the skew between outputs specified. This skew specification represents the typical difference between the delays of similar paths on a single chip. No maximum value for skew is specified due to the difficulty in the production testing of this parameter. The user is encouraged to contact an ECLinPS application engineer to obtain actual evaluation data if this parameter is critical in their designs.

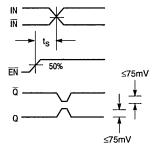

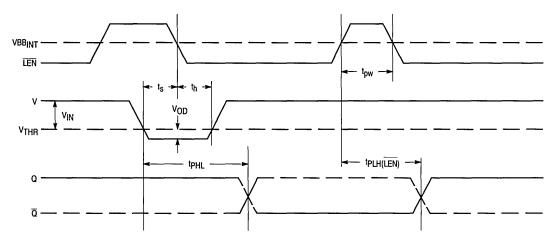

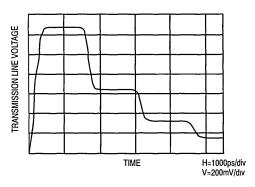

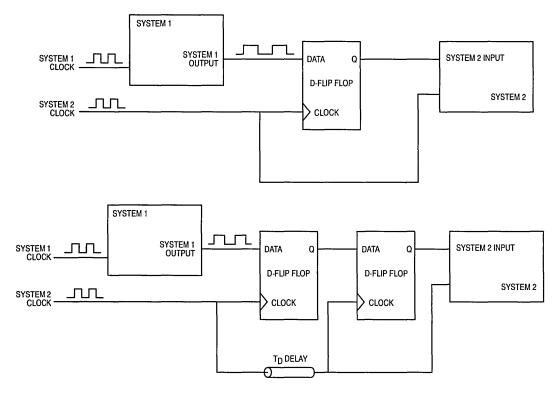

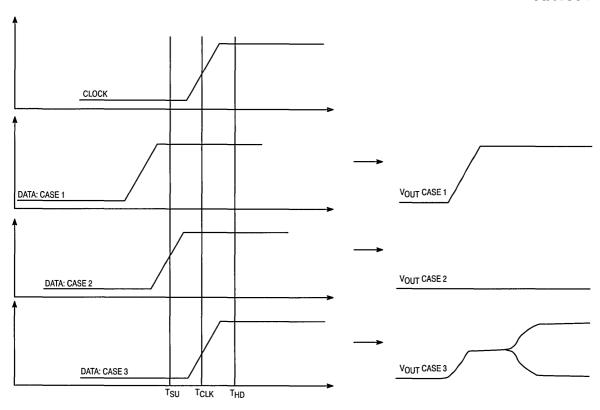

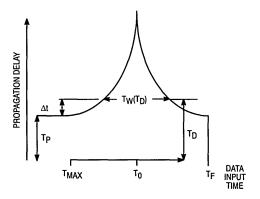

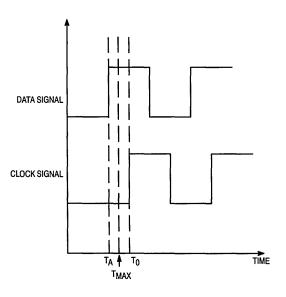

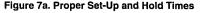

#### Set-Up and Hold Times

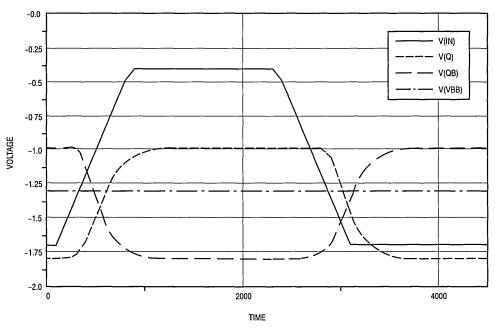

Motorola defines the setup time of a device as the minimum time, prior to the transition of the clock, that an input must be stable to ensure that the device operates properly. The hold time, on the other hand, is defined as the minimum time that an input must remain stable after the transition of the clock to ensure that the device operates properly. Figure 2.5 illustrates the way in which Motorola defines setup and hold times.

Figure 2.5. Set-Up and Hold Waveforms

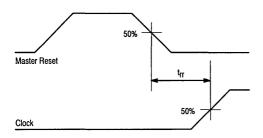

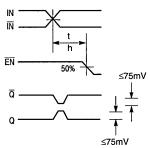

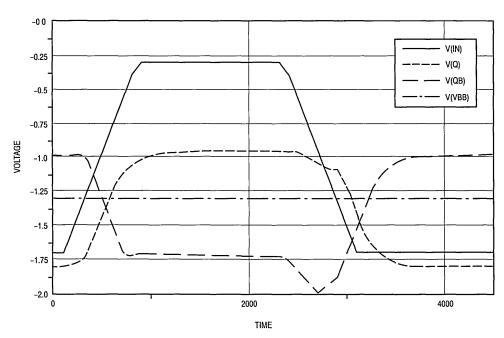

#### Release Times

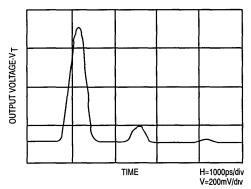

Release times are defined as the minimum amount of time an input must wait to be clocked after an enable, master reset or set signal is deactivated to ensure proper operation. Because more times than not this specification is in reference to a master reset operation, this parameter is often called reset recovery time. Figure 2.6 illustrates the definition of release time in the Motorola data sheets.

Figure 2.6. ECLinPS Release Time Waveforms

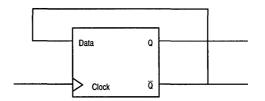

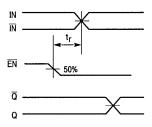

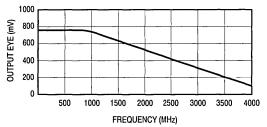

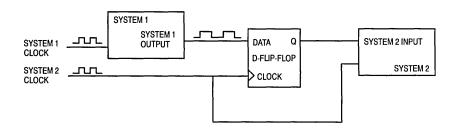

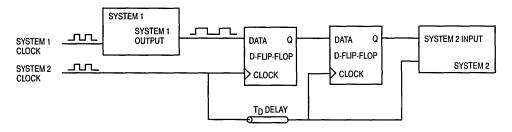

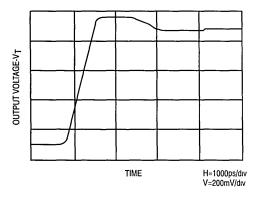

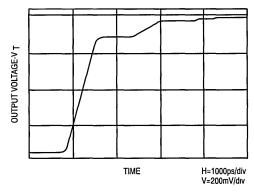

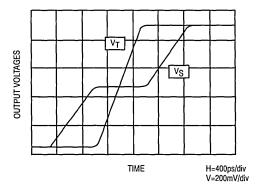

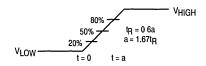

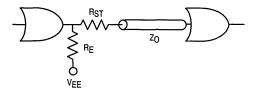

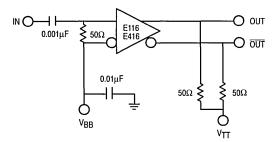

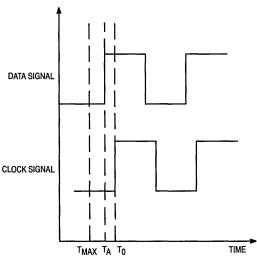

In general fMAX is measured in the manner shown in Figure 2.7 with the fail criterion being either a swing of 600mV or less, or a miscount. However, in some cases, the feedback method of testing can lead to a pessimistic value of fMAX because the feedback path delay is such that the setup times of the device are violated. If this is the case, it is necessary to have two free running signal generators to ensure that the setup times are observed. This parameter, along with fSHIFT and fCOUNT. represents the maximum frequency at which a particular flip flop, shift register or counter can be clocked with the divide, shift or count operation guaranteed. This number is generated from worst case operating conditions, thus, under nominal operating conditions, the maximum toggle frequency is higher.

#### **AC Testing ECLinPS Devices**

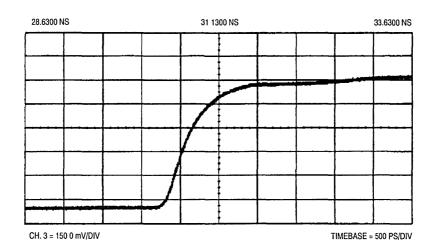

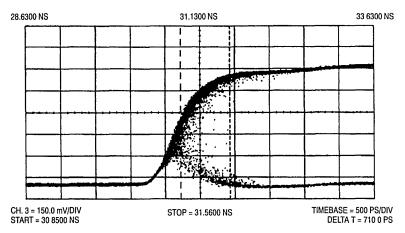

fMAX Measurement

The introduction of the ECLinPS family raised the performance of silicon to a new domain. As the propagation delays of logic devices become ever faster the task of

Figure 2.7. fMAX Measurement

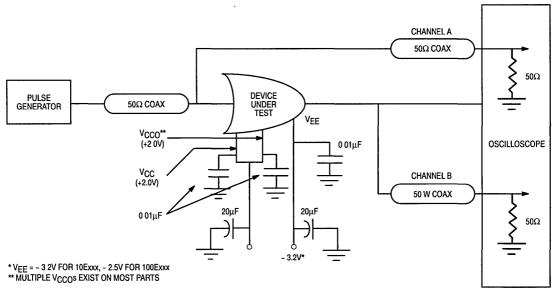

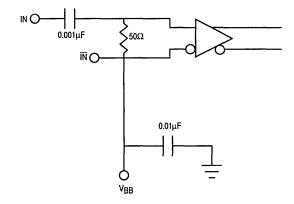

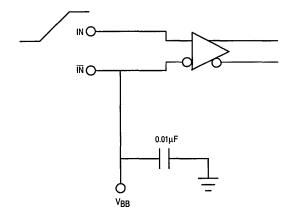

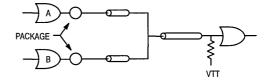

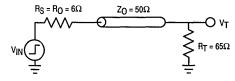

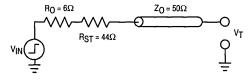

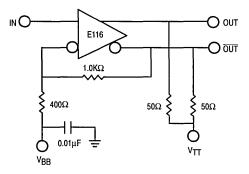

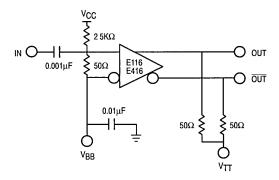

correlating between test setups becomes increasingly challenging. To obtain test results which correlate with Motorola, various testing techniques must be adhered to. A typical schematic for an ECLinPS test setup is illustrated in

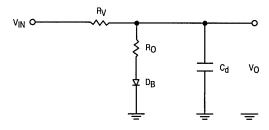

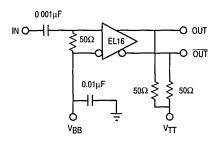

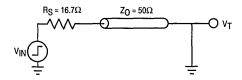

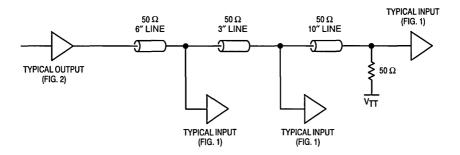

A solid ground plane is a must in the test setup, as the two power supplies are bypassed to this ground plane. A 20µF capacitor from the two power supplies to ground is used to dampen any supply variations. An RF quality 0.01 µF capacitor from each power pin to ground is used to decouple the fixture. These 0.01µF capacitors should be located as close to the power pins of the package as possible. In addition, in order to minimize the inductance of the power pins, all of the power leads should be kept as short as possible. The power supplies are shifted by +2.0V so that the load comprises only the precision  $50\Omega$  input impedance of the oscilloscope. Use of this technique will assure that the customer and Motorola are terminating devices into equivalent loads and will improve test correlation.

Figure 2.8. Typical ECLinPS Test Setup

To further standardize testing, any unused outputs should be loaded with  $50\Omega$  to ground.

Because the power supplies are shifted, the input levels must also be shifted by an equal amount. Table 2.3 gives the typical input levels for the ECLinPS family and their corresponding +2.0V shifted levels.

| 10Exxx          | Typical | Shifted |  |  |  |  |

|-----------------|---------|---------|--|--|--|--|

| V <sub>IL</sub> | -1.75V  | + 0.25V |  |  |  |  |

| V <sub>IH</sub> | - 0.90V | +1.10V  |  |  |  |  |

| 100Exxx         | Typical | Shifted |  |  |  |  |

| V <sub>IL</sub> | -1.70V  | + 0.30V |  |  |  |  |

| $v_{IH}$        | - 0.95V | +1.05V  |  |  |  |  |

Table 2.3. ECL Levels after Translating by +2.0V

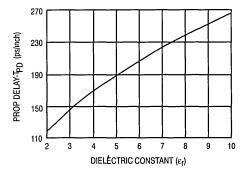

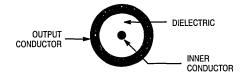

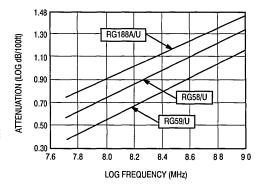

The test fixture should be in a controlled impedance  $50\Omega$  environment, with any non- $50\Omega$  interconnects, or stubs, kept as short as possible (<1/4″). This controlled impedance environment will help to minimize overshoot and ringing, two phenomena which can lead to inaccuracies in AC measurements. To minimize degradation of the input and output edge rates, a  $50\Omega$  coaxial cable with a teflon dielectric is recommended, however any other cable with a bandwidth of >5.0GHz is adequate. In addition, the cables from the device under test (DUT) to the inputs of the scope

should be matched in length to prevent any errors due to different path lengths from the DUT to the scope. The interconnect fittings should be  $50\Omega$  SMA straight or SMA launchers to minimize impedance mismatches at the interface of the coax and test PC board. Although a teflon laminate board is preferable, an FR4 laminate board is acceptable as long as the signal traces are kept to five inches or less. Longer traces will result in significant edge rate degradation of the input and output signals.

To make the board useful for incoming inspection or other volume testing, the board needs to be fitted with a socket. Although not suitable for AC testing due to different pin lengths and large parasitics, there are through hole sockets which are adequate for DC testing of ECLinPS devices. For AC testing purposes a 28-pin PLCC surface mount socket is recommended.

To ease the correlation issue, Motorola has developed a universal AC test board which is now available to customers. The board is fitted with a PLCC socket and comes with instructions on how it can be configured for the different device types in the family. For ordering information see the description on the following page.

Finally, to ensure correlation between Motorola and the customer, high-performance, state-of-the-art measuring equipment should be used. The pulse generator must be capable of producing the required input levels with rise and fall times of 500ps. In addition, if f<sub>MAX</sub> is going to be tested, a frequency of up to 1.5GHz may be needed. The oscilloscope should also be of the utmost in performance with a minimum bandwidth of 5.0 GHz.

Figure 2.9. ECLinPS AC Test Board

# MOTOROLA SEMICONDUCTOR GENERAL INFORMATION

# SECTION 6 Engineering Evaluation Board for 28-Pin ECL Devices in the PLCC Package

#### DESCRIPTION

This board is designed to provide a low cost characterization tool for evaluating ECL devices in the ECLinPS Product Family. The board provides a high bandwidth  $50\Omega$  controlled impedance environment. The board is universal and can be configured by the user for any of the 28-pin PLCC devices in the family depending on the input, output, and power pinout layout of the device. The table below indicates common input/output/power devices.

| Group  | Base Device | Pin Compatible Devices |

|--------|-------------|------------------------|

| CONF1  | E196        | E195                   |

| CONF2  | E142        | E016,E141,E143,E241    |

| CONF3  | E337        | E336                   |

| CONF4  | E212        | E104,E107,E150,E151    |

| CONF5  | E156        | E155,E167,E171,E256    |

| CONF6  | E158        | E116,E122,E175,E416    |

| CONF7  | E154        | E452                   |

| CONF8  | E101        | E131,E157,E404         |

| CONF9  | E112        |                        |

| CONF10 | E431        | E457                   |

| CONF11 | E111        |                        |

| CONF12 | E164        | E160                   |

| CONF13 | E451        |                        |

| CONF14 | E163        | E166                   |

| CONF15 | E193        |                        |

|        |             |                        |

Table 1. Cross Reference of Board Configurations

The board is designed to test devices using the fly-by (Kelvin contact) test method, therefore one input force trace and one input sense trace exist for each input pin. This allows termination of the input and output signals into the highly accurate 50 ohm impedance of an oscilloscope. The layout is engineered to have equal length traces from the device under test (DUT) socket to the sense outputs which simplifies the calibration requirements for accurate AC measurements.

The kit provides a printed circuit board with an attached surface mount socket as well as assembly instructions. For superior impedance control from the cable to the board, Motorola recommends the use of SMA coaxial connectors.

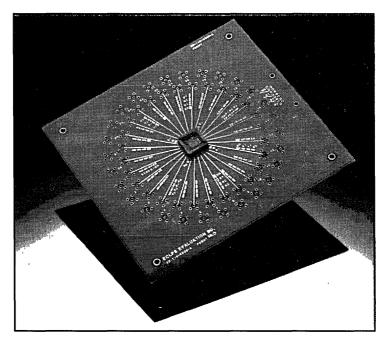

Figure 1. Front View of ECLinPS Evaluation Board

## **Engineering Evaluation Board**

Table 2. Pin Cross Reference

| Group  | Part(s) | P1              | P2   | Р3  | P4 | P5  | P6  | P7  | P8   | P9  | P10 | P11 | P12 | P13 | P14             |

|--------|---------|-----------------|------|-----|----|-----|-----|-----|------|-----|-----|-----|-----|-----|-----------------|

| CONF1  | E196    | VEE             | 1    | I   | VB | NC  | NC  | ı   | ı    |     | 0   | 0   | Vcc | 0   | 0               |

| CONF2  | E142    | VEE             | 1    | I   | t  | 1   | 1   | 1   | Vcc  | 0   | 0   | 0   | 0   | 0   | Vcc             |

| CONF3  | E337    | VEE             | 1    | 1   | 1  | 1   |     | ı   | Vcc  | 1   | NC  | 0   | NC  | ı   | Vcc             |

| CONF4  | E212    | ν <sub>EE</sub> | 1    | ı   | ı  | l i | Vcc | 0   | 0    | 0   | 0   | vcc | 0   | 0   | 0               |

| CONF5  | E156    | ν <sub>EE</sub> | 1    | 1   | ı  | 1   | l i | 1   | 1    | ı   | vcc | 0   | 0   | vcc | 0               |

| CONF6  | E158    | ν <sub>EE</sub> | I/VB | ı   | ı  | 1   | 1   | Vcc | 0    | 0   | Vcc | 0   | 0   | vcc | 0               |

| CONF7  | E154    | VEE             | I/VB | ı   | 1  | 1   | ŀ   | 1   | 1    | Vcc | 0   | 0   | 0   | 0   | 0               |

| CONF8  | E101    | ν <sub>EE</sub> | ı    | - 1 | ı  | 1   | 1   | 1   | 1    | ı   | 1   | Vcc | 0   | 0   | 0               |

| CONF9  | E112    | VEE             | 1    | ı   | 1  | NC  | vcc | 0   | 0    | 0   | 0   | vcc | 0   | 0   | 0               |

| CONF10 | E431    | VEE             | I/VB | 1   | 1  | 1   | ı   | 1   | I/VВ |     |     | vcc | 0   | 0   | 0               |

| CONF11 | E111    | vcc             | 1    | VВ  | NC | 0   | 0   | 0   | vcc  | 0   | 0   | 0   | 0   | 0   | 0               |

| CONF12 | E164    | VEE             | 1    | ı   | ı  | i   | [ ı | 1   | 1    | 1   |     | 1   | l t | Vcc | 0               |

| CONF13 | E451    | VEE             | l '  | NC  | 1  | 1   | ı   | ı   | 1    | l   | Vcc | 0   | 0   | 0   | vcc             |

| CONF14 | E163    | VEE             | 1    | ı   | ı  | ı   |     | 1   | } ı  |     |     | 1   | 0   | 0   | v <sub>cc</sub> |

| CONF15 | E193    | VEE             | ı    | ı   | I  | 1   | 1   | - 1 |      | Vcc | 0   | 0   | 0   | 0   | Vcc             |

Table 2. Pin Cross Reference (continued)

| Part(s)<br>(cont'd) | P15 | P16             | P17 | P18 | P19 | P20 | P21 | P22  | P23 | P24 | P25  | P26 | P27 | P28 | # of<br>Connec-<br>tors |

|---------------------|-----|-----------------|-----|-----|-----|-----|-----|------|-----|-----|------|-----|-----|-----|-------------------------|

| E196                | Vcc | Vcc             | NC  | 1   | NC  | 1   | 1   | ı    | 1   | 1   | 1    | 1   | 1   | 1   | 35                      |

| E142                | 0   | Vcc             | 0   | 0   | 0   | Vcc | 1   | 1    | ı   | ı   | 1    | 1   | 1   | 1   | 37                      |

| E337                | 0   | vcc             | 1   | NC  | 0   | vcc | ı   |      | 1   | 1   | ı    | 1   | 1   |     | 37                      |

| E212                | 0   | Vcc             | 0   | 0   | 0   | 0   | vcc | 0    | 1   | 1   | 1    | ļ i | ı   | l i | 33                      |

| E156                | 0   | vcc             | 0   | 0   | vcc | 1   | 1   |      | ı   | 1   | 1    | ı   | ı   | 1   | 40                      |

| E158                | 0   | vcc             | 0   | 0   | vcc | 0   | 0   | vcc  | ı   | 1   | 1    | 1   | 1   | 1   | 32                      |

| E154                | 0   | v <sub>cc</sub> | 0   | 0   | 0   | 0   | vcc | 1 1  | ı   | l I | 1    | ı   | ı   | 1   | 38                      |

| E101                | 0   | vcc             | 0   | 0   | 0   | 0   | Vcc | ı    | ı   | 1   | 1    | 1   | 1   | ] ı | 40                      |

| E112                | 0   | vcc             | 0   | 0   | 0   | 0   | vcc | 0    | 0   | 0   | 0    | vcc | ı   | 1   | 26                      |

| E431                | 0   | Vcc             | 0   | 0   | 1   | 1   | 1   | I/VB | ı   | 1   | I/VB |     | -1  | 1   | 44                      |

| E111                | Vcc | 0               | 0   | 0   | 0   | 0   | 0   | Vcc  | 0   | 0   | 0    | VEE | 1   | 1   | 25                      |

| E164                | 0   | vcc             | 0   | 0   | vcc | ı   | ı   | lι   | ı   | 1   | ı    |     | 1   | 1   | 44                      |

| E451                | 0   | vcc             | 0   | 0   | vcc | ı   | ı   | ı    | 1   | ı   | ı    | ۱ ا | VВ  | 1   | 37                      |

| E163                | NC  | vcc             | 0   | 0   | Vcc | 1   | 1   | l 1  | 1   | 1   | 1    |     | 1   |     | 42                      |

| E193                | 0   | Vcc             | 0   | 0   | 0   | Vcc | i   |      | ı   | ı   | 1    | i   | 1   | 1   | 38                      |

KEY:

- I designates an input

- O designates an output

- V<sub>EE</sub> designates the lower voltage rail

- V<sub>CC</sub> designates the upper voltage rail NC designates a no connect

- VB designates VBB output which should not be terminated into 50 ohms

### **Egineering Evaluation Board**

#### ASSEMBLING THE ECLINPS EVALUATION BOARD

The evaluation board is designed for characterizing devices in a laboratory environment using high bandwidth sampling oscilloscopes such as the Hewlett Packard 54120T, the Tektronix 11800 Series, or the Tektronix 7854. The board is designed using Kelvin contact (fly-by) techniques to present the input signals to the DUT. Each pin on the board has two traces, one force and one sense. Input pins use one force and one sense line, while outputs need only a sense line. This means that input signals are terminated through the sense line into the 50 ohm input of a sampling oscilloscope instead of at the input to the DUT. Please refer to the AC Testing section of the ECLinPS Data Book for further information and a simplified figure of the test setup.

The first step in building a board is determining which input/output/power configuration is necessary for the device of interest. Table 1 on the first page of the Applications Information shows all the board configurations. For example, if the devices of interest were the E104 and the E151, then CONF2 would be selected. Table 2 is a pin cross reference for each configuration.

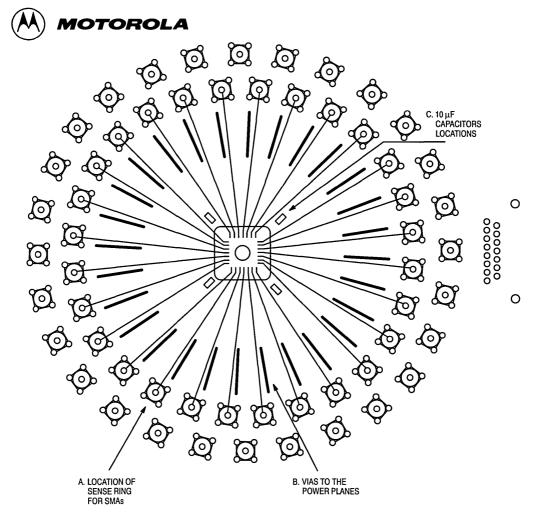

#### I. Installing the SMA Connectors

Table 2 indicates the number of SMA connectors needed to populate an evaluation board for a given configuration. Depending on the device and the parameters of interest, it may not be necessary to install the full complement of SMA connectors. For example, some devices have two clock inputs or common clocks and individual clocks. Figure 1 is the frontview of the ECLinPS evaluation board. Item A points to the inner ring which connects to the sense traces of the DUT. The outer ring connects to the force traces. An input requires one SMA connector for the force and one SMA connector for the sense, while an output only requires a connection to the sense trace. Insert all the SMA connectors into the board and solder to the board. A simple assembly technique is to place a stiff piece of cardboard (8"×7" or larger) on top of all the connectors and hold the board and cardboard together. Invert the board, place on a level surface, and all the connectors will be seated properly and can be soldered in place.

#### II. Connecting Power Planes to DUT Socket

There are four voltage planes on the ECLPSBD28. One is dedicated to ground and the other three, B1, B2, B3, are uncommitted. These planes are accessible through a power connection and sets of four vias that are adjacent to each sense trace. This is identified as Item B in Figure 1. For standard parts, B1 can be assigned  $V_{CC}$ , B2 can be assigned to  $V_{EE}$ , and B3 can be assigned to ground. Table 2 indicates which pins need to be connected to the various supply voltages. On the front side of the board, solder a jumper wire from the closest  $V_{EE}$  or  $V_{CC}$  via to the sense trace for each  $V_{CC}$ ,  $V_{CCO}$ , and  $V_{EE}$  pin. Near the DUT there are sets of ground/bias plane vias that accommodate power supply decoupling capacitors. These are identified as Item C. On the front side of the board install 10  $\mu$ F capacitors and on the back side install a 0.01  $\mu$ F high frequency capacitor in parallel to decouple the  $V_{EE}$  and  $V_{CC}$  planes.

#### **III. Cutting Force Traces for Outputs**

Because of the design of the board, all force traces for output pins will appear as transmission line stubs connected to the output pin. On the back side of the board, cut the force traces associated with the outputs using a razor blade knife. It is important to cut the trace very close to the DUT area to minimize the stub length. Also cut the force traces that are connected to V<sub>CC</sub>, V<sub>CCO</sub>, and V<sub>EE</sub> pins.

#### IV. Installing the Chip Capacitors for the VCC/VCCO Pins

In the kit are  $0.01\,\mu\text{F}$  chip capacitors for use in decoupling the V<sub>CC</sub> and V<sub>CCO</sub> pins to the ground plane. This is critical because the power pins are not directly connected to the V<sub>CC</sub> plane as in an actual board layout. On the back side of the board beneath the DUT socket are pads for each pin which allow connection of chip capacitors to the center island (GND) for each V<sub>CC</sub> and V<sub>CCO</sub> pin. Stand the chip capacitors on edge when soldering them in place so that adjacent pins are not shorted together.

# 1

### **Engineering Evaluation Board**

#### V. Final Assembly

The board power plane interface is designed to accommodate a 15-pin right angle D connector. This can be used directly, or wires can be inserted into the vias to connect to the power planes that were connected to the DUT in part II. Attach standoffs into the four 0.25 inch holes at the corners of the board. This completes the assembly of the evaluation board and it should be ready to test.

#### VI. SMA Connector Suppliers

Below are two suppliers who manufacture PC Mount SMA connectors which interface to the evaluation board. Motorola has used these two connectors before, but there are other vendors who manufacture similar products.

EF Johnson 299 Johnson Ave. P.O. Box 1249 Waseca, Minnesota 56093 (800) 247-8343 or (507) 835-6222 0.200" PC Mount SMA Jack Receptacle 142-0701-201

MACOM Omni Spectra 140 Fourth Avenue Waltham, Massachusetts 02254 (617) 890-4750 0.200" PC Mount SMA Straight Jack 2062-0000-00 1

# ligh Performance ECL Data CLinPS and ECLinPS Lite

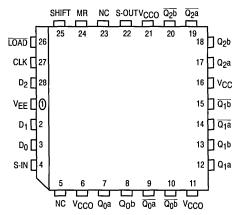

This section contains AC & DC specifications r each ECLinPS device type. Specifications mmon to all device types can be found in the st part of this section. While specifications inque to a particular device can be found in the dividual data sheets following the family pecifications.

# **ECLinPS Family Specifications**& Device Data Sheets

#### ata Sheet Classification

dvance Information — product in the sampling or pre-production stage at the time of publication.

roduct Preview — product in the design stage at the time of publication.

# **ECLinPS Family Specifications**

### **Absolute Maximum Ratings**

Beyond which device life maybe impaired.1

| Characteristic                                           | Symbol          | Rating                 | Unit |

|----------------------------------------------------------|-----------------|------------------------|------|

| Power Supply (V <sub>CC</sub> = 0V)                      | VEE             | - 8 to 0               | Vdc  |

| Input Voltage (VCC = 0V)                                 | VI              | 0 to 6V                | Vdc  |

| Output Current — Continuous<br>— Surge                   | lout            | 50<br>100              | mA   |

| Operating Temperature Range<br>10E Series<br>100E Series | TA              | 0 to + 85<br>0 to + 85 | °C   |

| Operating Range <sup>2</sup>                             | V <sub>EE</sub> | - 5.7 to - 4.2         | V    |

<sup>1.</sup> Unless specified otherwise on individual data sheet.

10E series: - 4.94V to - 5.46V

#### 10E Series DC Characteristics

$V_{EE} = -5.2V \pm 5\%$ ;  $V_{CC} = V_{CCO} = GND^{1}$

|                |                     | 0°    | 0°C   |       | °C    | 75    | °C   8 |       | °C    |      |

|----------------|---------------------|-------|-------|-------|-------|-------|--------|-------|-------|------|

| Symbol         | Characteristic      | Min   | Max   | Min   | Max   | Min   | Max    | Min   | Max   | Unit |

| VOH            | Output HIGH Voltage | -1020 | - 840 | - 980 | - 810 | - 920 | -735   | - 910 | -720  | mV   |

| VOL            | Output LOW Voltage  | -1950 | -1630 | -1950 | -1630 | -1950 | -1600  | -1950 | -1595 | mV   |

| VIH            | Input HIGH Voltage  | -1170 | - 840 | -1130 | - 810 | -1070 | -735   | -1060 | -720  | mV   |

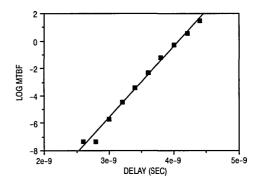

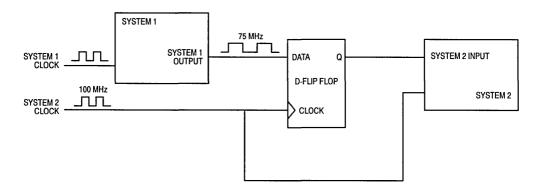

| VIL            | Input LOW Voltage   | -1950 | -1480 | -1950 | -1480 | -1950 | -1450  | -1950 | -1445 | mV   |