# TELECOMMUNICATIONS DEVICE DATA

DL136 REV 1

Selection Guides

3

# Application Notes and Technical Articles

Handling and Design Guidelines

Quality and Reliability 6

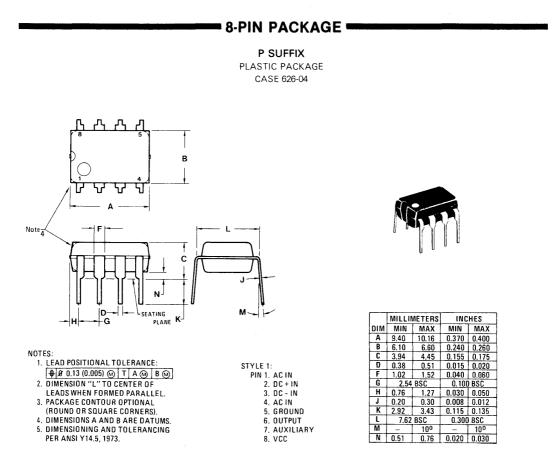

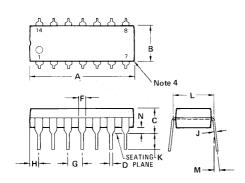

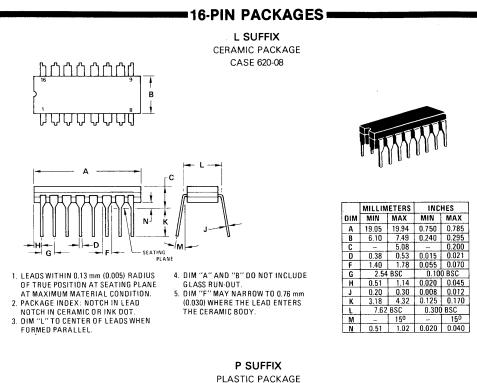

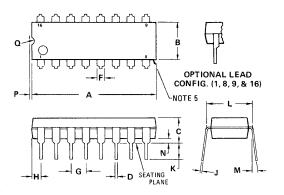

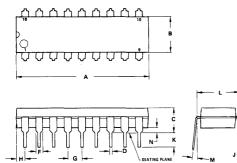

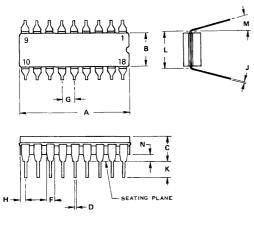

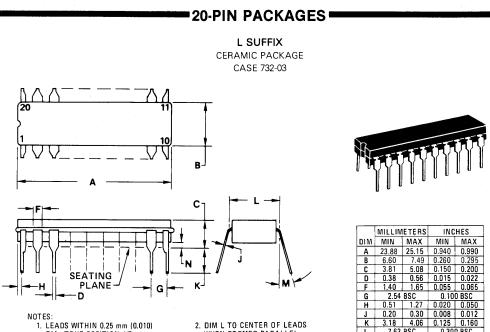

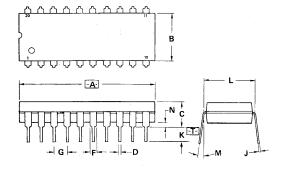

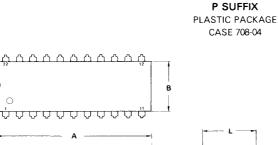

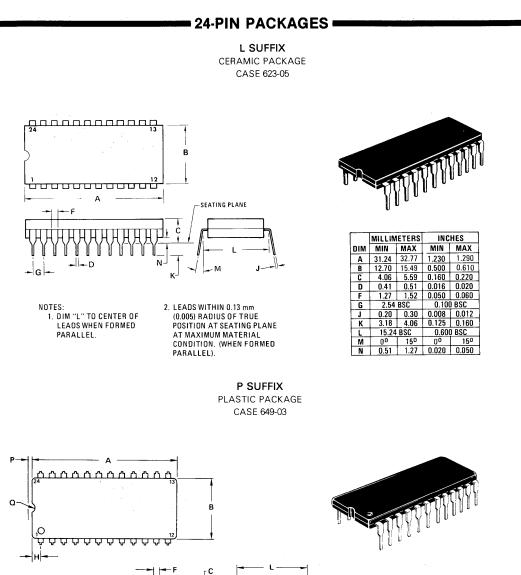

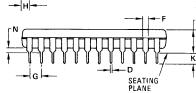

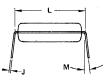

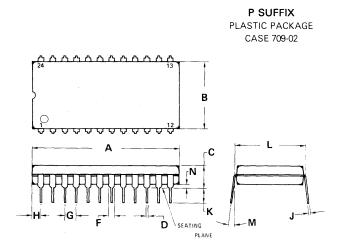

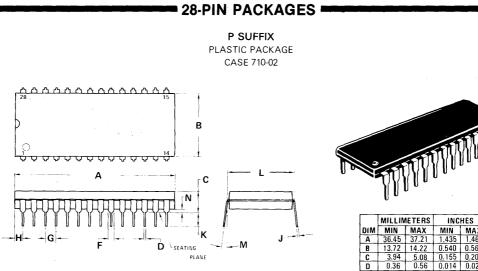

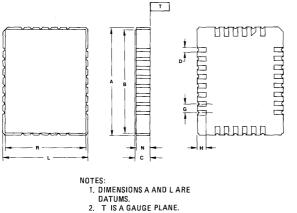

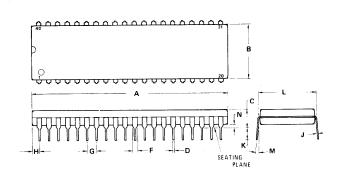

Mechanical Data 7

Prepared by Technical Information Center

Motorola is a major supplier of Semiconductors to Telecommunications equipment manufacturers worldwide, and our data manuals for such standard products as dedicated MOS and Bipolar Telecom ICs, CMOS Special Circuits, High-Speed CMOS, ECL, TTL, Linear, Power Transistors, Microprocessors, and Memories, are on the reference shelves of designers throughout the industry.

This data book pulls together Motorola's Semiconductor Products which are dedicated to applications in Telecommunications. It reflects both the growing portfolio of Motorola devices for Telecommunications and the need for designers to have product information at hand in a convenient form.

Many of the products presented here are new, for new applications in an industry which is presently one of the most dynamic and fastest growing—Telecommunications. It was possible only to include a limited amount of application material. Hence these products are supported by applications and product specialists within the Motorola Semiconductor organizations. Should you require further details or assistance in designing with any of these devices, your Motorola Semiconductor Sales Office can put you in touch with the relevant expertise within our organization.

Motorola reserves the right to make changes to any product herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product described herein; neither does it convey any license under its patent rights nor the rights of others.

Motorola, Inc. general policy does not recommend the use of its components in life support applications, where in a failure or malfunction of the component may directly threaten life or injury. Per Motorola Terms and Conditions of Sale, the user of Motorola components in life support applications assumes all risk of such use and indemnifies Motorola against all damages.

> Series B © MOTOROLA INC., 1985 Previous Edition © 1984 "All Rights Reserved"

Printed in U.S.A.

# ALPHANUMERIC INDEX

This index includes all Motorola devices used specifically in telecommunication applications. Information for the devices identified with page numbers appears in this book. All other devices are fully characterized in the book referenced at the right of the device number.

Linear-See DL128, Linear and Interfaces Integrated Circuits

MECL-See DL122R1, MECL Device Data

MCU - See DL132R1, Single-Chip Microcomputer Data

MPU - See DL133, 8-Bit Microprocessor & Peripheral Data

Opto – See DL118R1, Optoelectronics Device Data

- RZD See DL125, Rectifier and Zener Diodes Data

- SF See DL130, CMOS/NMOS Special Functions Data

- SS See DL126, Small-Signal Transistor Data

| Device<br>Number | Function                                      | Page   |

|------------------|-----------------------------------------------|--------|

|                  | Function                                      | Number |

| MC1374           | TV Modulator Circuit                          | Linear |

| MC1376           | FM Modulator Circuit                          | Linear |

| MC1496           | Balanced Modulator-Demodulator                | Linear |

| MC1648           | Voltage-Controlled Oscillator                 | MECL   |

| MC3356           | Wideband FSK Receiver                         | Linear |

| MC3357           | Low Power FM IF                               | Linear |

| MC3359           | High Gain Low-Power FM IF                     | Linear |

| MC3361           | Low-Voltage Narrow-Band FM IF                 | Linear |

| MC3362           | Low Voltage FM/FSK Receiver                   | Linear |

| MC3393           | Two-Modulus Prescaler                         | Linear |

| MC3396           | Divide-by-20 Prescaler                        | Linear |

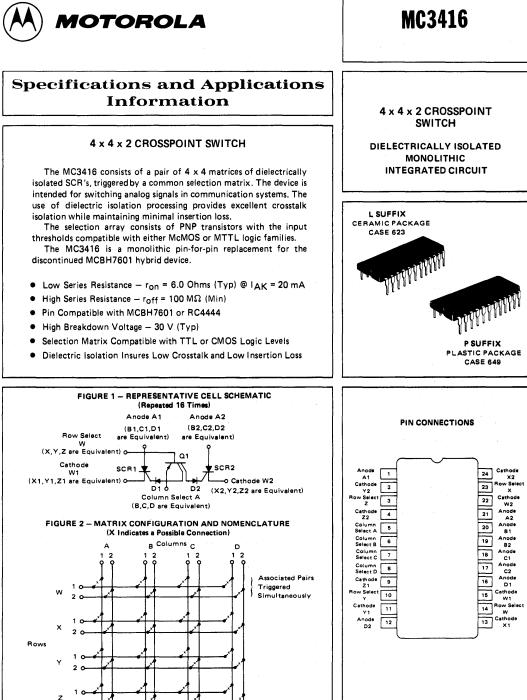

| MC3416           | Crosspoint Switch $(4 \times 4 \times 2)$     | 2-3    |

| MC3417           | CVSD Modulator-Demodulator (3-Bit Algorithm)  | 2-12   |

| MC3418           | CVSD Modulator-Demodulator (4-Bit Algorithm)  | 2-12   |

| MC3419           | See MC34F19                                   |        |

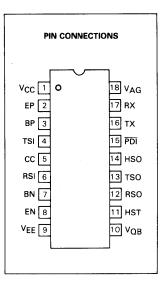

| MC3419-1L        | Subscriber Loop Interface Circuit             | 2-30   |

| MC34F19          | Subscriber Loop Interface Circuit             | 2-46   |

| MC3517           | CVSD Modulator-Demodulator (3-Bit Algorithm)  | 2-12   |

| MC3518           | CVSD Modulator-Demodulator (4-Bit Algorithm)  | 2-12   |

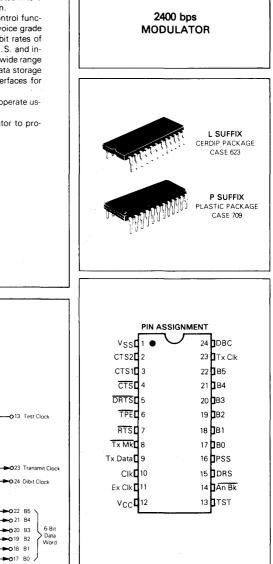

| MC6172           | 2400 bps Digital Modulator (DPSK)             | 2-62   |

| MC6173           | 2400 bps Digital Demodulator (DPSK)           | 2-70   |

| MC6800           | 8-Bit Microprocessor Unit                     | MPU    |

| MC6801           | 8-Bit Microcomputer Unit                      | MCU    |

| MC6804           | 8-Bit Microcomputer Unit                      | MCU    |

| MC68HC04         | 8-Bit HCMOS Microcomputer Unit                | MCU    |

| MC6805           | 8-Bit HMOS Microcomputer Series               | MCU    |

| MC68HC05         | 8-Bit HCMOS Microcomputer Series              | MCU    |

| MC6809           | 8-Bit Microprocessing Unit                    | MPU    |

| MC6850           | Asynchronous Communications Interface Adapter | MPU    |

| MC68HC51         | Asynchronous Communications Interface Adapter | MPU    |

| MC6852           | Synchronous Serial Data Adapter               | MPU    |

| MC68HC53         | Asynchronous Communications Interface Adapter | MPU    |

| MC6854           | Advanced Data-Link Controller                 | MPU    |

Device Number Page Number

| Number    | Function                                                      | Number |

|-----------|---------------------------------------------------------------|--------|

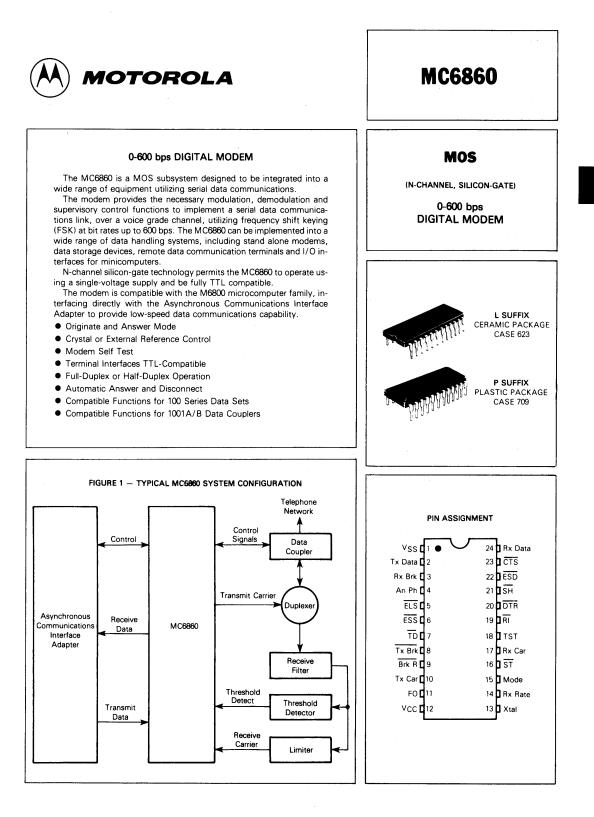

| MC6860    | 0-600 bps Mod/Demodulator (Bell 103)                          | 2-85   |

| MC12002   | Analog Mixer                                                  | MECL   |

| MC12009   | Two-Modulus Prescaler ( + 5/ + 6)                             | MECL   |

| MC12011   | Two-Modulus Prescaler ( ÷ 8/ ÷ 9)                             | MECL   |

| MC12013   | Two-Moduls Prescaler ( $\div$ 10/ $\div$ 11)                  | MECL   |

| MC12015   | Low-Power Two-Modulus Prescaler (+ 32/ + 33)                  | MECL   |

| MC12016   | Low-Power Two-Modulus Prescaler ( + 48 + 41)                  | MECL   |

| MC12017   | Low-power Two-Modulus Prescaler ( + 64/ + 65)                 | MECL   |

| MC12018   | 520 MHz Low-Power Prescaler ( + 128/ + 129)                   | MECL   |

| MC12019   | Low-Power Two-Modulus Prescaler ( + 20/ + 21)                 | MECL   |

| MC12022   | 1.0 GHz Low-Power Two-Modulus Prescaler ( + 128/ + 129)       | MECL   |

| MC12023   | Low-Power Prescaler (+64)                                     | MECL   |

| MC12071   | High-Speed Prescaler ( + 64/ + 256)                           | MECL   |

| MC12073   | Low-Power Prescaler ( + 64)                                   | MECL   |

| MC12074   | Low-Power Prescaler ( ÷ 256)                                  | MECL   |

| MC12090   | High-Speed Prescaler (+2)                                     | MECL   |

| MC13010   | TV Parallel Sound IF and AFT                                  | Linear |

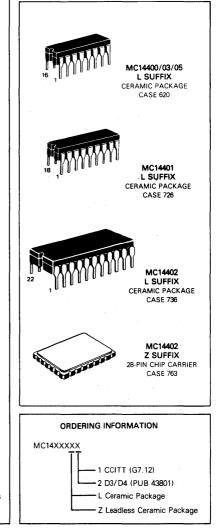

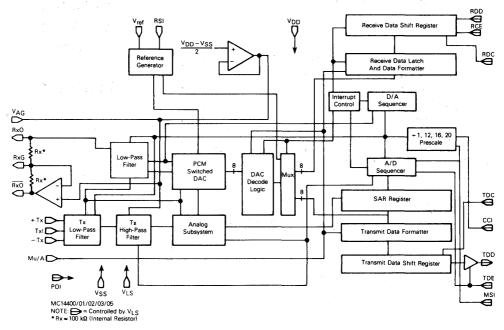

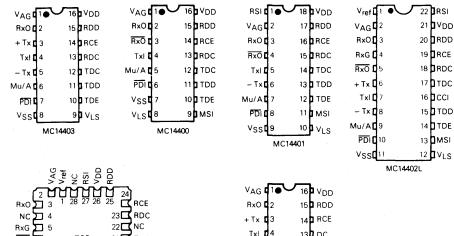

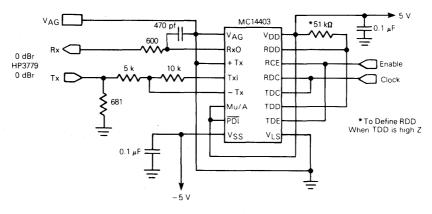

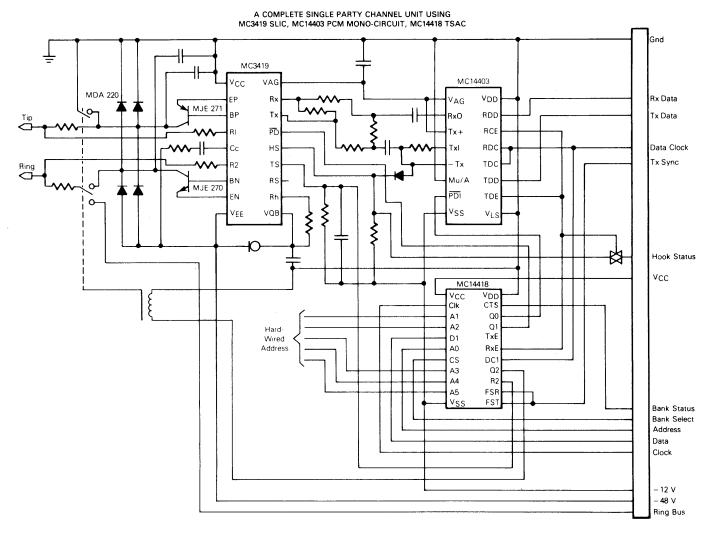

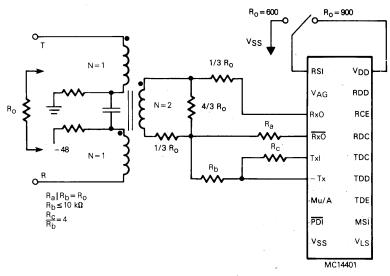

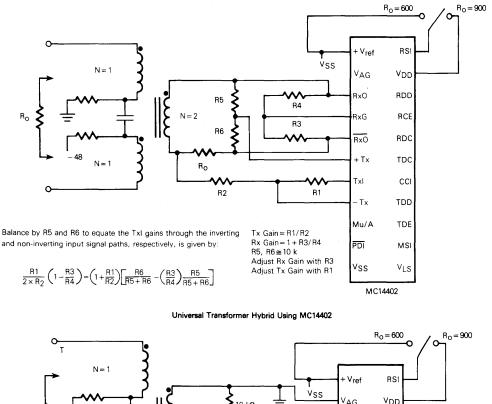

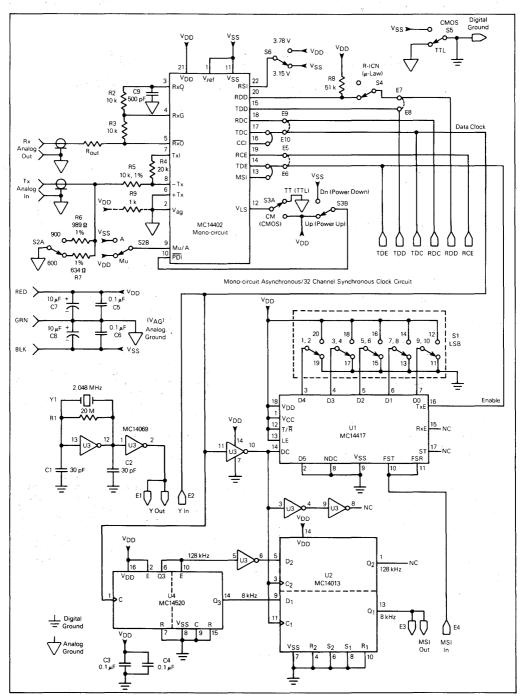

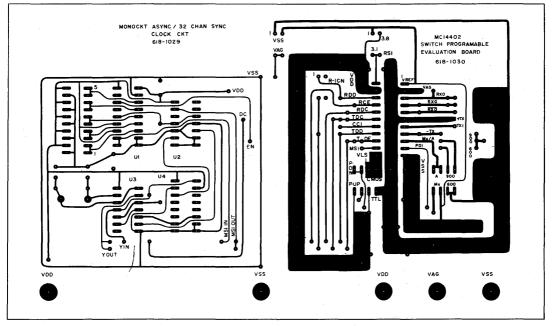

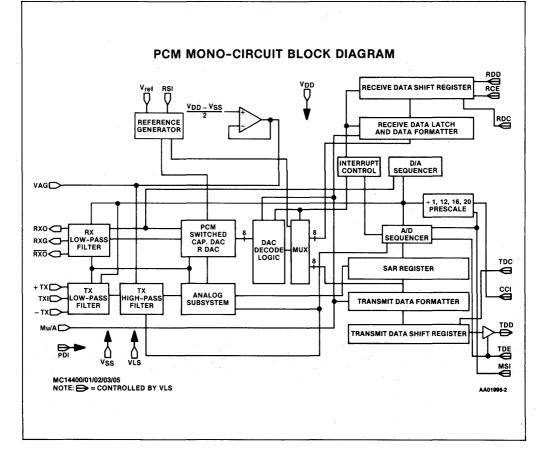

| MC14400   | Single-Chip PCM Codec/Filter Mono-circuit                     | 2-99   |

| MC14401   | Single-Chip PCM Codec/Filter Mono-circuit                     | 2-99   |

| MC14402   | Single-Chip PCM Codec/Filter Mono-circuit                     | 2-99   |

| MC14403   | Single-Chip PCM Codem/Filter Mono-circuit                     | 2-99   |

| MC14405   | Single-Chip PCM Codec/Filter Mono-circuit                     | 2-99   |

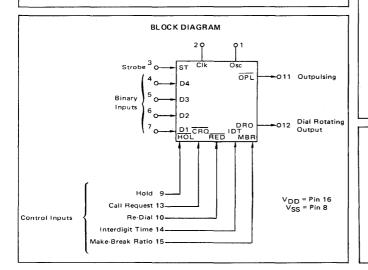

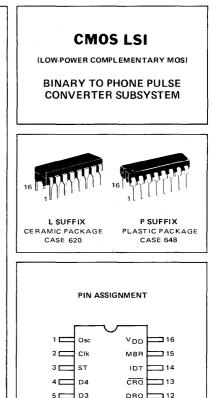

| MC14408   | Binary to Phone Pulse Converter                               | 2-113  |

| MC14409   | Binary to Phone Pulse Converter                               | 2-113  |

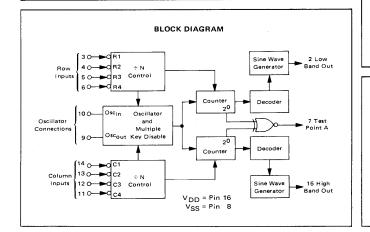

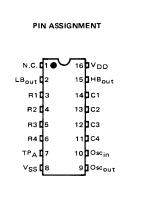

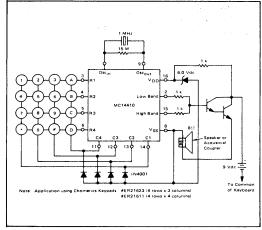

| MC14410   | 2-of-8 Tone Encoder                                           | 2-121  |

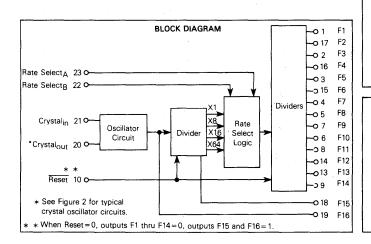

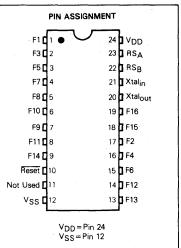

| MC14411   | Bit Rate Generator                                            | 2-125  |

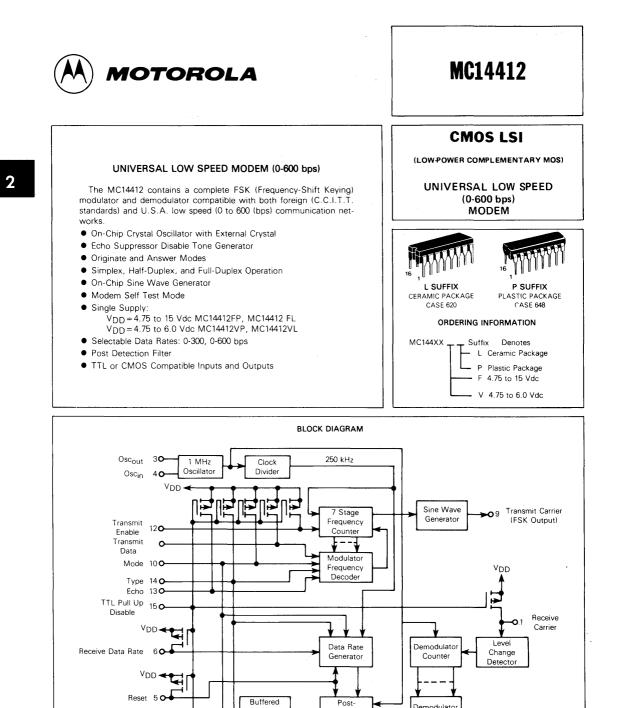

| MC14412   | 0-600 bps Modulator (Bell 103/CCITT V.21)                     | 2-128  |

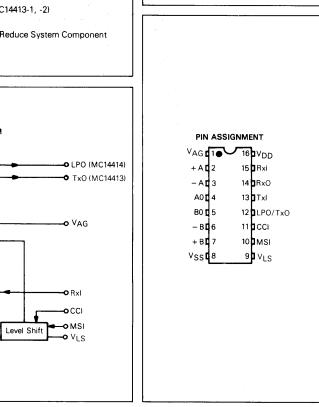

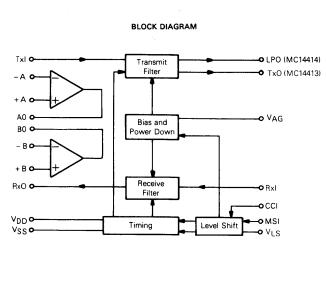

| MC14413-1 | PCM Band-Pass/Low-Pass Filter (CCITT)                         | 2-134  |

| MC14413-2 | PCM Band-Pass/Low-Pass Filter (D3/D4)                         | 2-134  |

| MC14414-1 | PCM Dual Low-Pass Filter (CCITT)                              | 2-134  |

| MC14414-2 | PCM Dual Low-Pass Filter (D3/D4)                              | 2-134  |

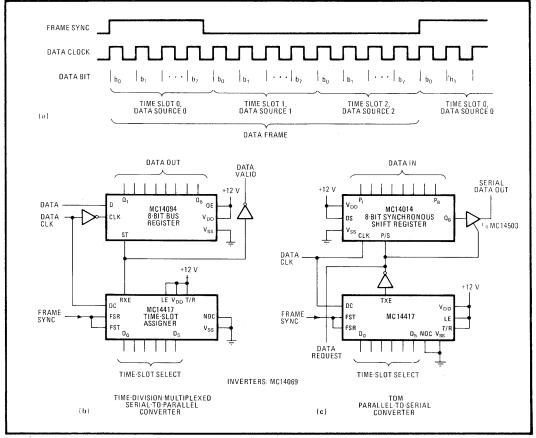

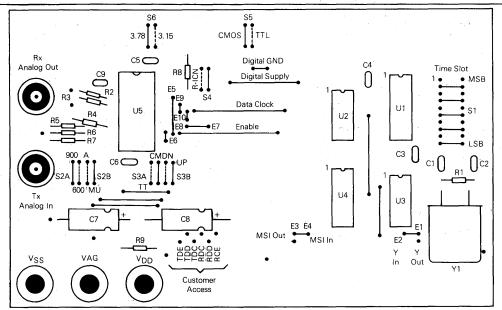

| MC14416   | Time Slot Assigner Circuit (Serial)                           | 2-149  |

| MC14417   | Time Slot Assigner Circuit (Parallel)                         | 2-169  |

| MC14418   | Time Slot Assigner Circuit (Programmable)                     | 2-149  |

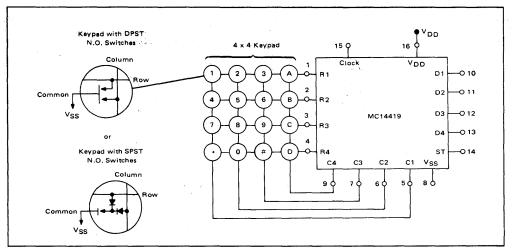

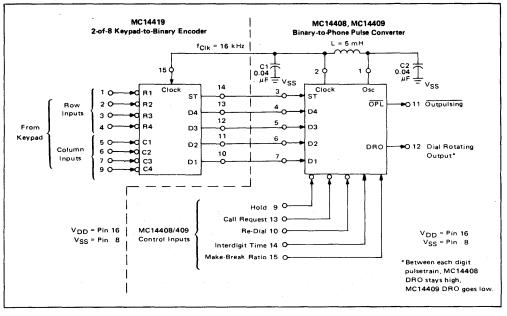

| MC14419   | 2-of-8 Keypad-to-Binary Encoder                               | 2-173  |

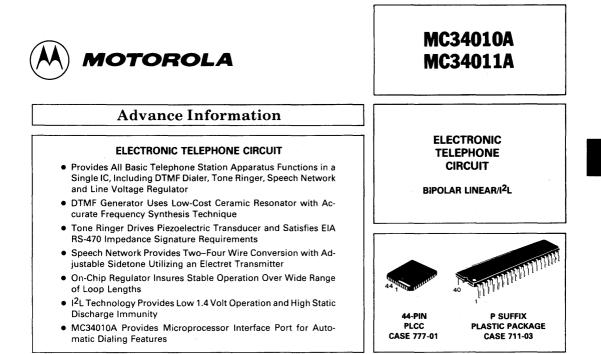

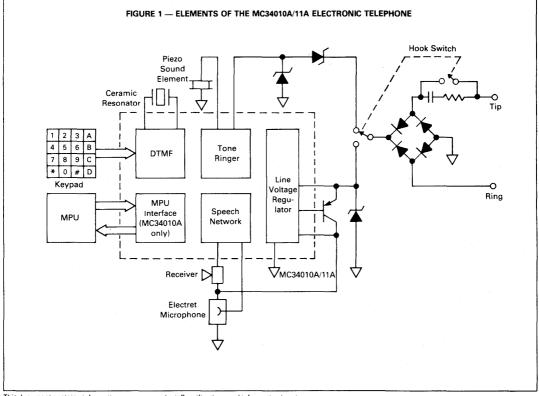

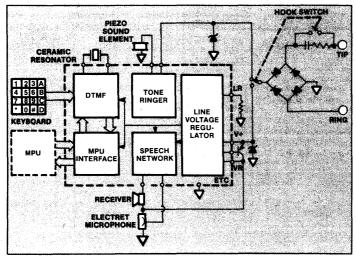

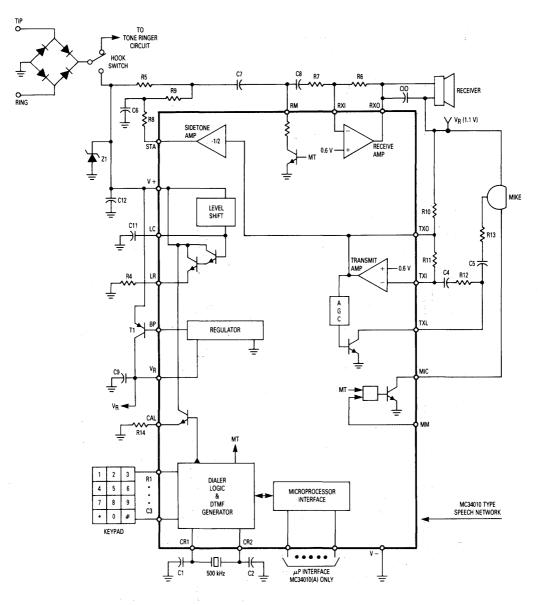

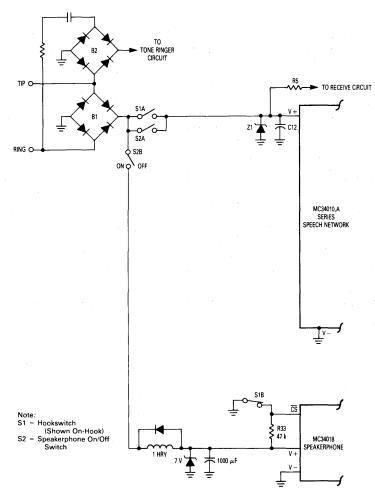

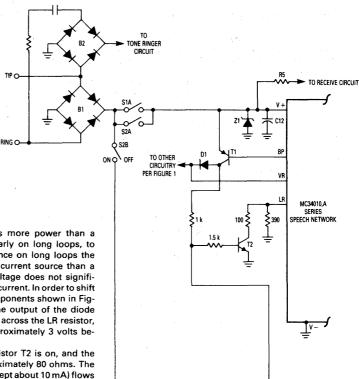

| MC34010   | Electronic Telephone Circuit (MCU Interface)                  | 2-177  |

| MC34011   | Electronic Telephone Circuit                                  | 2-177  |

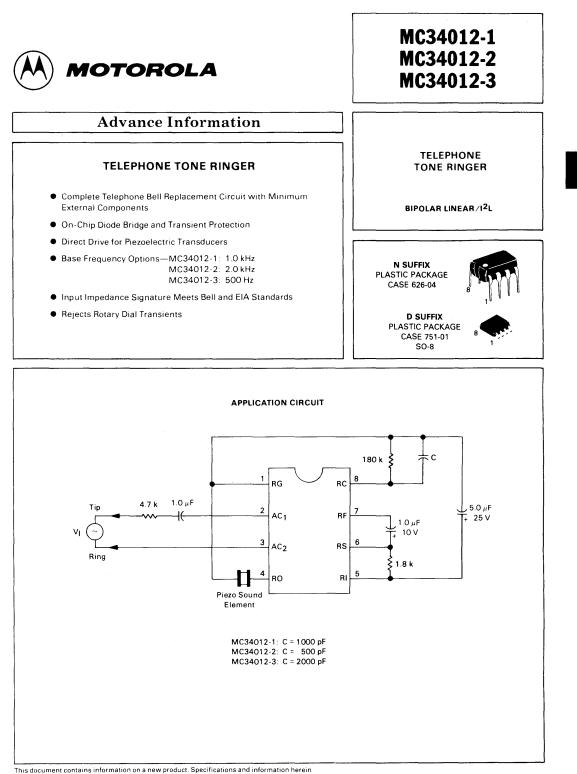

| MC34012   | Telephone Tone Ringer                                         | 2-201  |

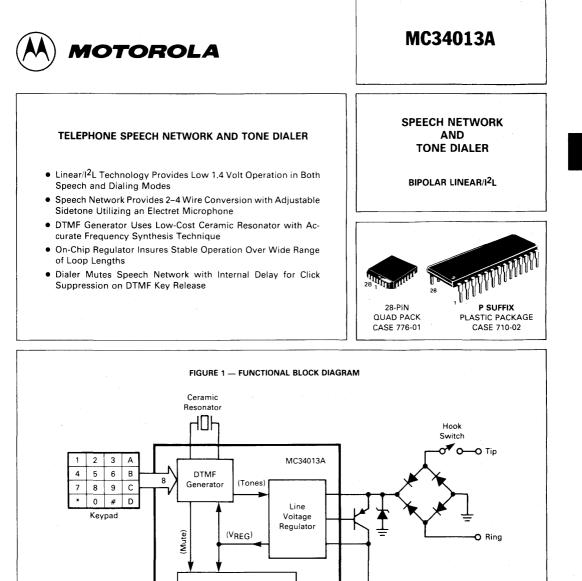

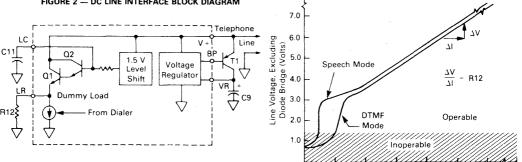

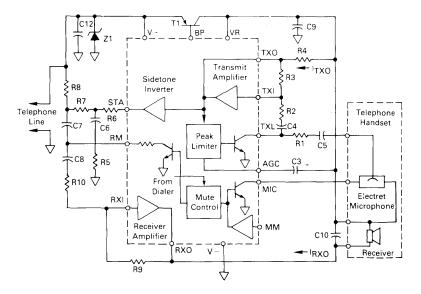

| MC34013   | Speech Network and Tone Dialer                                | 2-209  |

| MC34014   | Telephone Speech Network With Dialer Interface                | 2-224  |

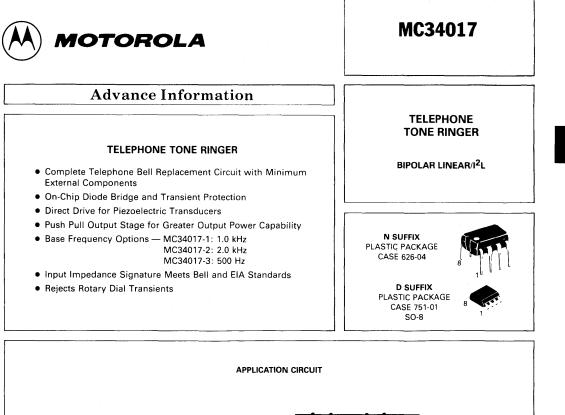

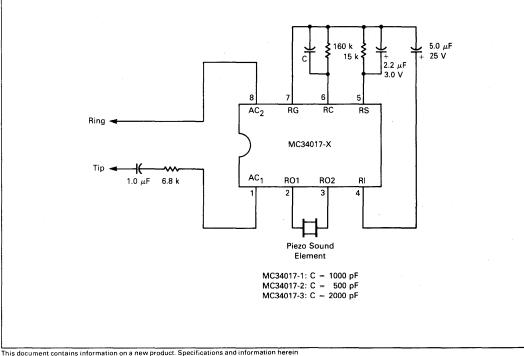

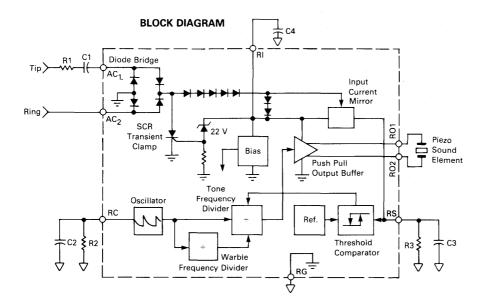

| MC34017   | Telephone Tone Ringer                                         | 2-241  |

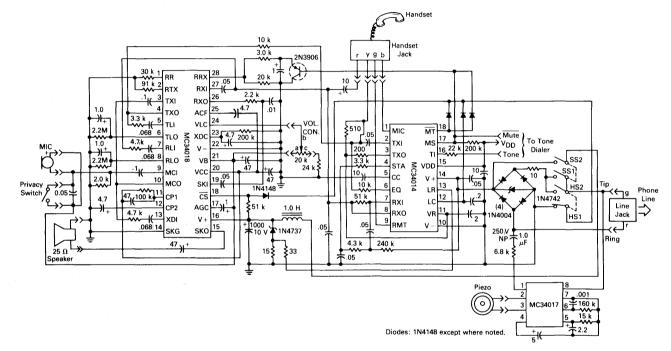

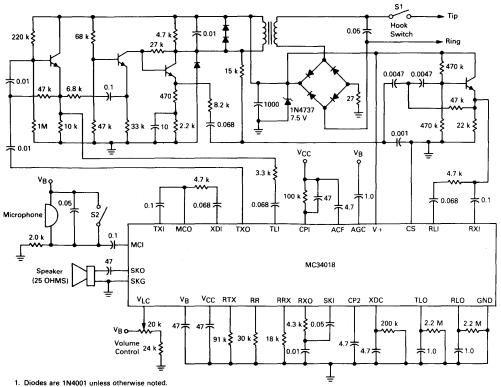

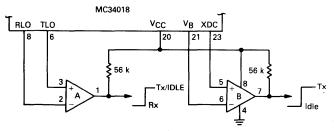

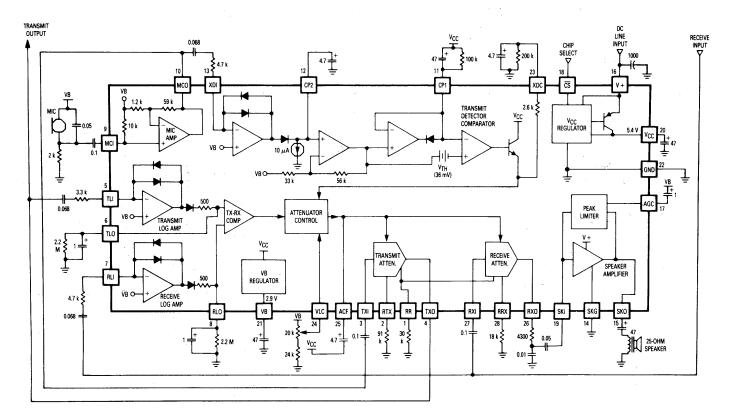

| MC34018   | Speakerphone Network                                          | 2-249  |

| MC34129   | Low Power Switching Power Supply                              | *      |

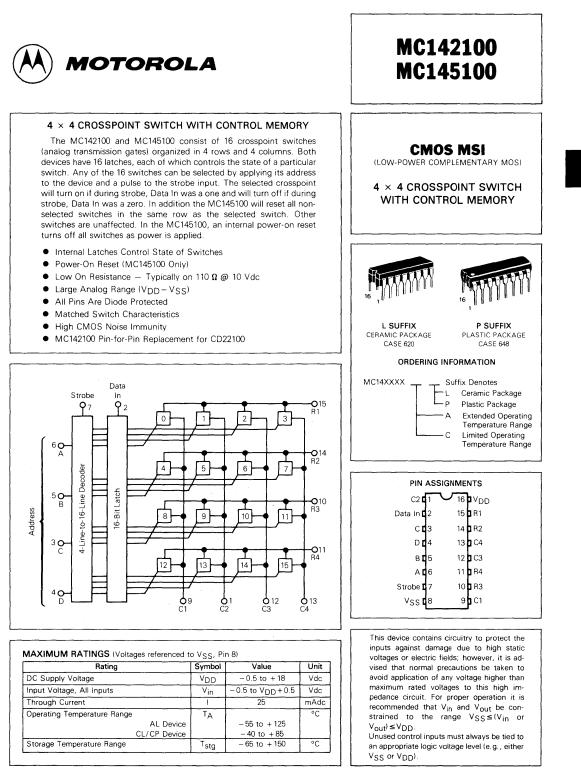

| MC142100  | Crosspoint Switch With Control Memory $(4 \times 4 \times 1)$ | 2-263  |

| MC142101  | Crosspoint Switch With Control Memory $(4 \times 4 \times 2)$ | 2-269  |

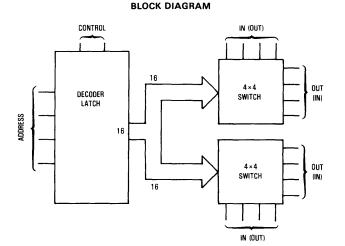

| MC142103  | Transcoder                                                    | 2-270  |

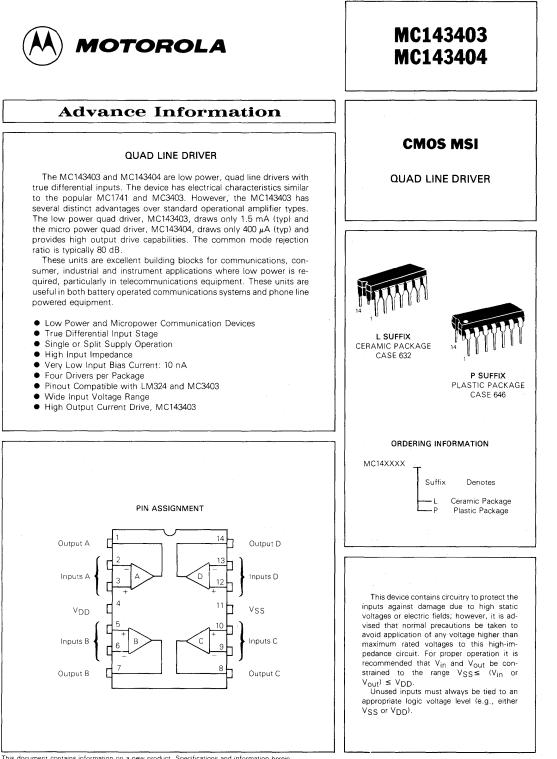

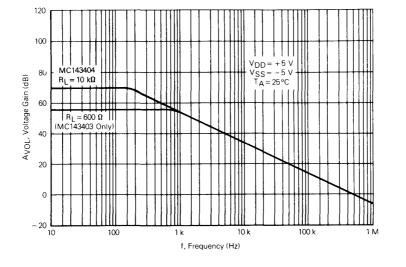

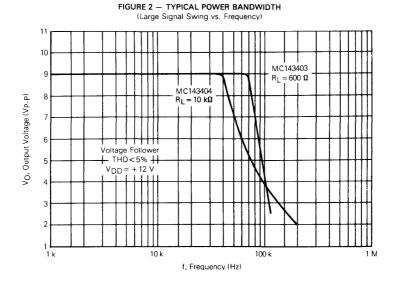

| MC143403  | Quad Line Driver                                              | 2-271  |

| MC143404  | Quad Line Driver                                              | 2-271  |

|           |                                                               |        |

# Device Number

| MC145026             | Programmable Encoder                                          | SF             |

|----------------------|---------------------------------------------------------------|----------------|

| MC145027             | Programmable Decoder                                          | SF             |

| MC145028             | Programmable Decoder                                          | SF             |

| MC145029             | Programmable Decoder                                          | SF             |

| MC145100             | Crosspoint Switch With Control Memory $(4 \times 5 \times 1)$ | 2-263          |

| MC145106             | PLL Parallel Programmable Frequency Synthesizer               | 2 200<br>SF    |

| MC145145             | PLL 4-Bit Data Bus Programmable                               | SF             |

| MC145146             | PLL 4-Bit Data Bus Programmable                               | SF             |

| MC145151             | PLL Parallel Programmable                                     | SE             |

| MC145152             | PLL Parallel Programmable                                     | SF             |

| MC145155             | PLL Serial Programmable                                       | SF             |

| MC145156             | PLL Serial Programmable                                       | SF             |

| MC145150             | PLL Serial Programmable                                       | SF             |

| MC145157             |                                                               | SF             |

|                      | PLL Serial Programmable                                       | SF             |

| MC145159             | PLL Serial Programmable                                       | SF             |

| MC145168             | Dual PLL 4-Bit BCD Programmable                               | 3F<br>2-275    |

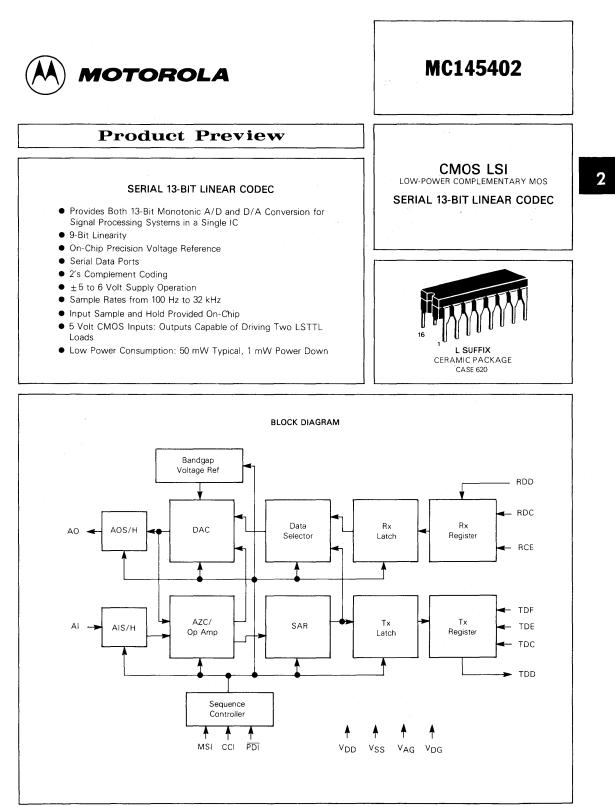

| MC145402             | 13-Bit Linear Codec                                           | 2-275          |

| MC145406<br>MC145409 |                                                               | 2-270          |

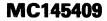

|                      | Integrated Pulse Dialer With Redial                           | 2-282          |

| MC145411             | Bit Rate Generator                                            | 2-200<br>2-291 |

| MC145412             | Pulse/Tone Repertory Dialer                                   | 2-291          |

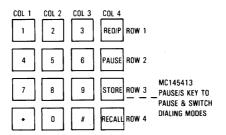

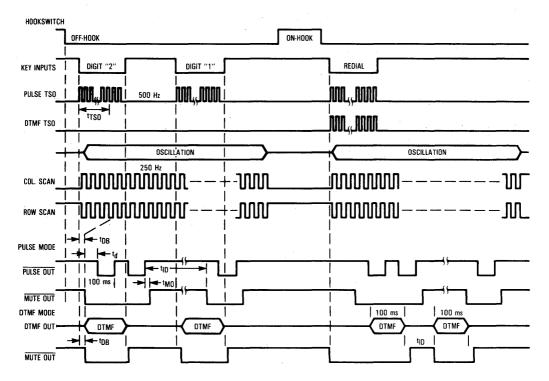

| MC145413             | Pulse/Tone Repertory Dialer                                   | 2-291<br>2-297 |

| MC145414             | Dual Tunable Low-Pass Sampled Data Filter                     |                |

| MC145415             | Dual Tunable Linear Phase Low-Pass Sampled Data Filter        | 2-304          |

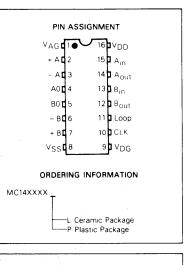

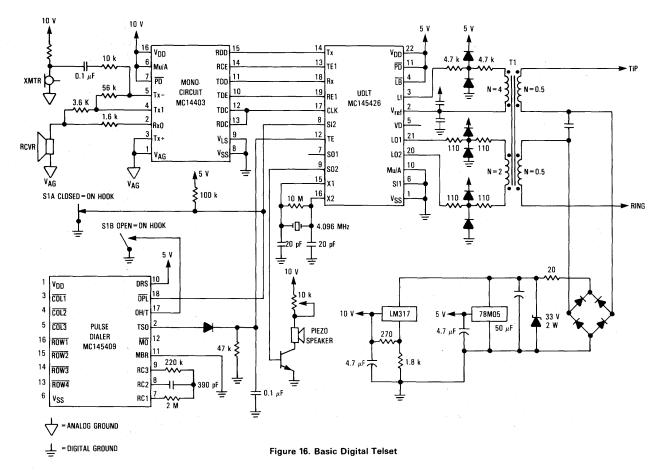

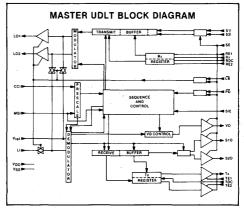

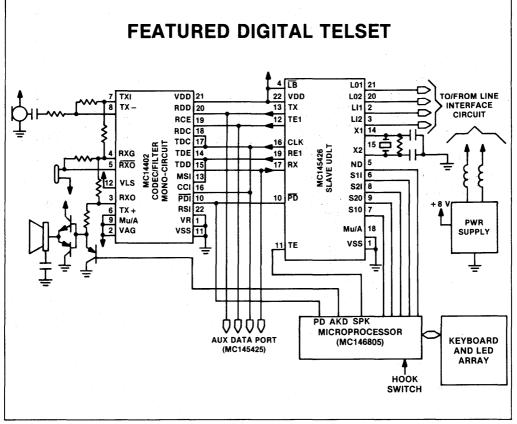

| MC145418             | Digital-Loop Transceiver (Master)                             | 2-309          |

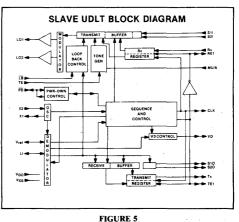

| MC145419             | Digital-Loop Transceiver (Slave)                              | 2-309          |

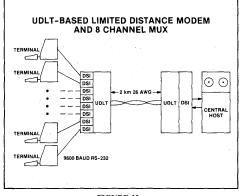

| MC145421             | 160 kbps ISDN UDLT (Master)                                   | 2-323          |

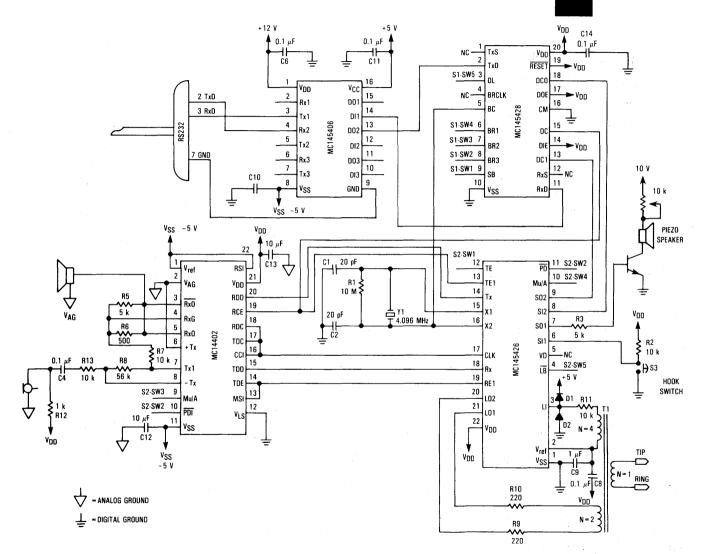

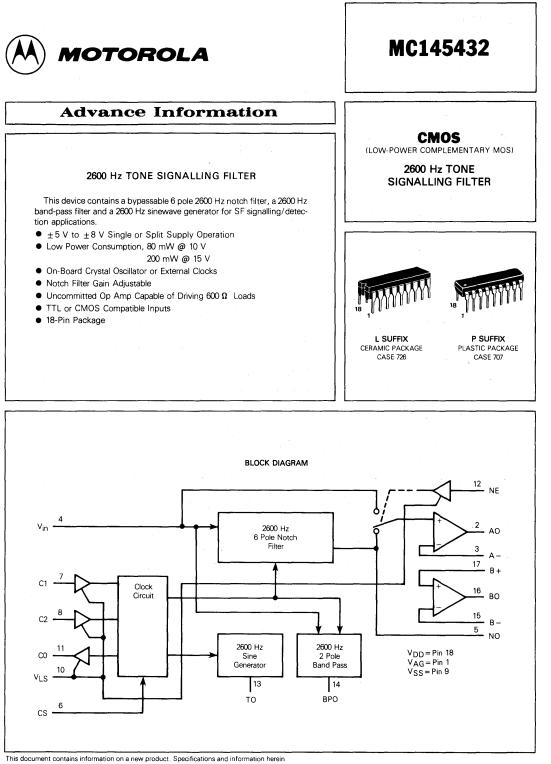

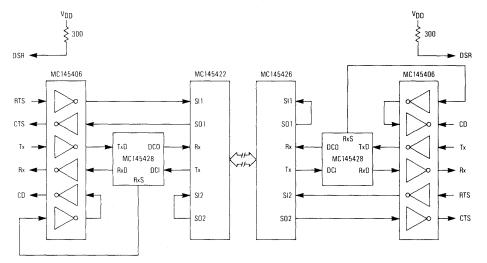

| MC145422             | Universal Digital Loop Transceiver (2-Wire Master)            | 2-324          |

| MC145425             | 160 kbps ISDN UDLT (Slave)                                    | 2-323          |

| MC145426             | Universal Digital Loop Transceiver (2-Wire Slave)             | 2-324          |

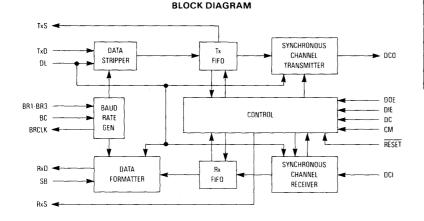

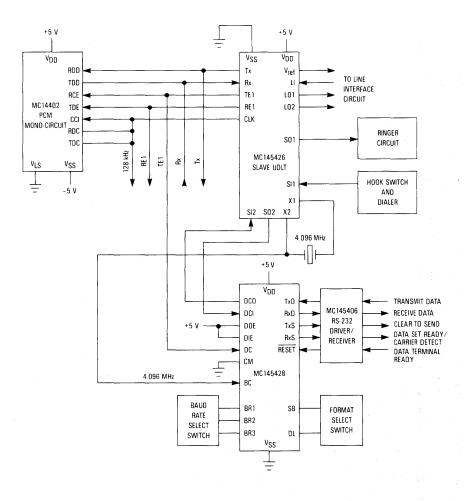

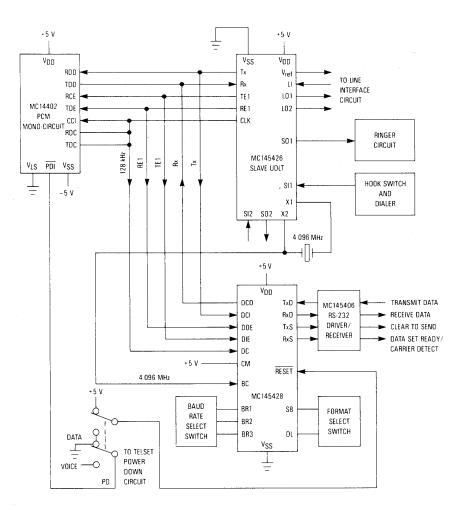

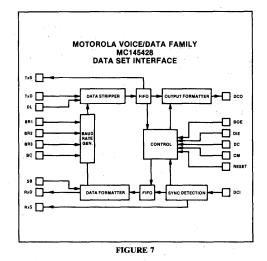

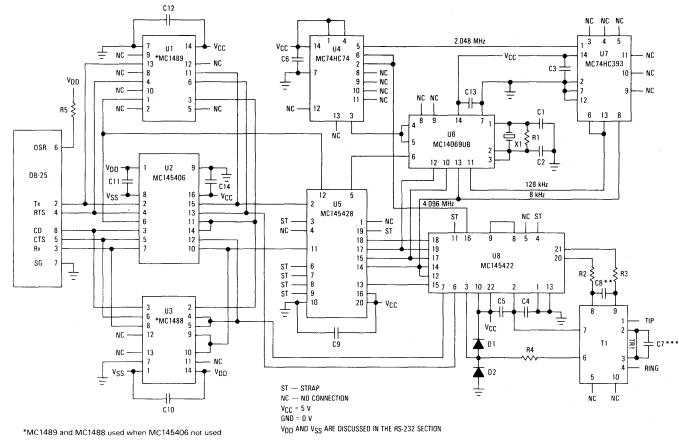

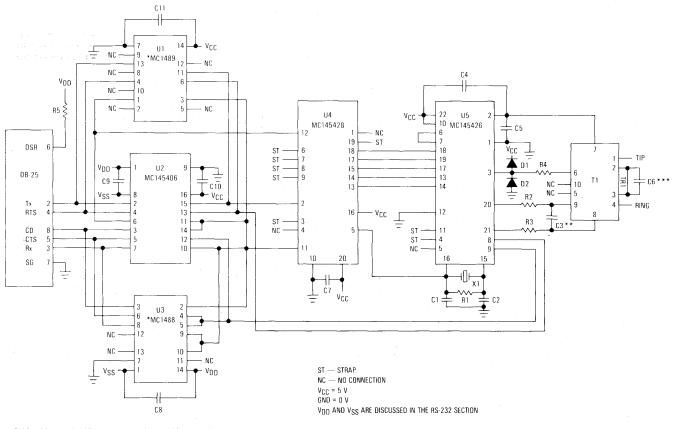

| MC145428             | Data Set Interface (DSI)                                      | 2-343          |

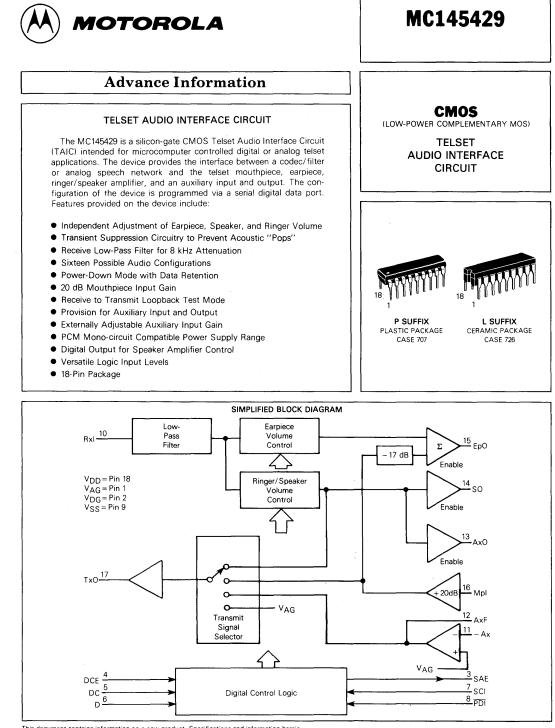

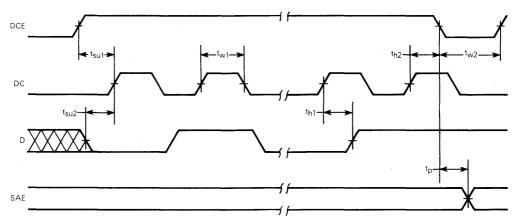

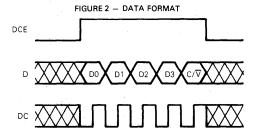

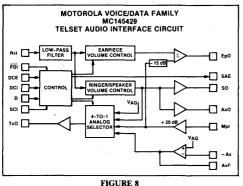

| MC145429             | Telset Audio Interface Circuit (TAIC)                         | 2-356          |

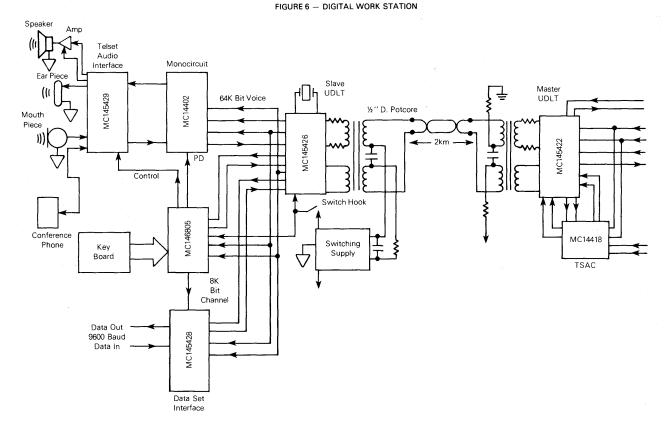

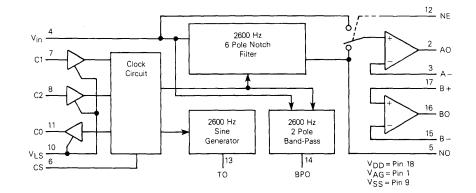

| MC145432             | Notch/Band-Pass 2600 Hz Tone Signalling Filter                | 2-365          |

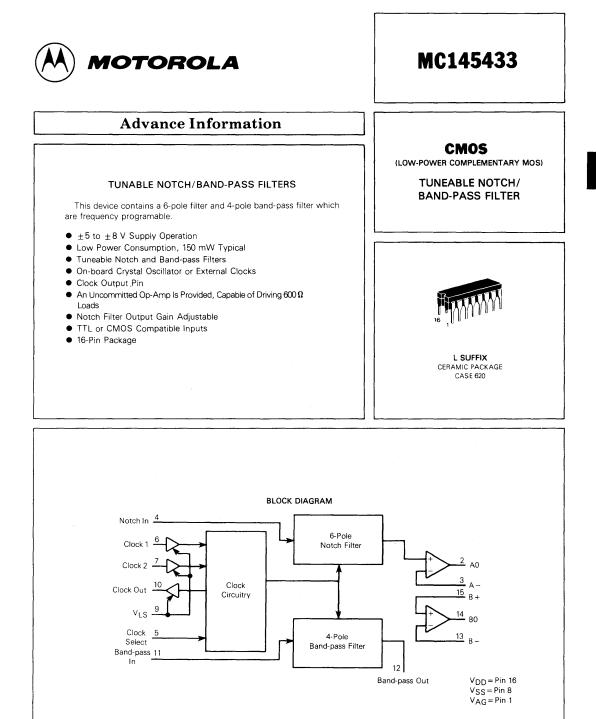

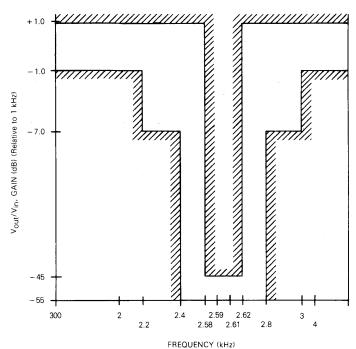

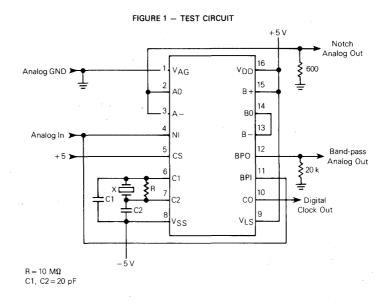

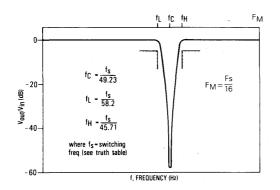

| MC145433             | Tunable Notch/Band-Pass Filter                                | 2-371          |

| MC145439             | Transcoder                                                    | 2-377          |

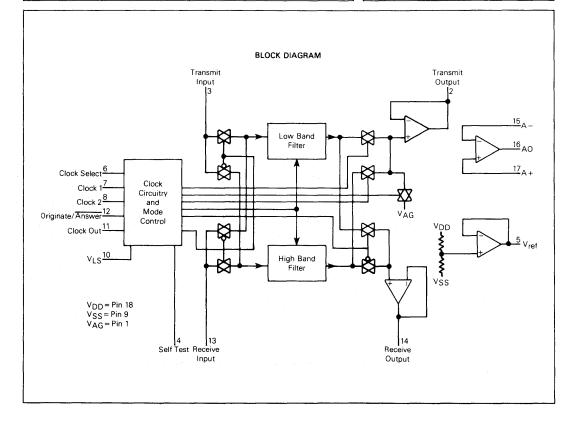

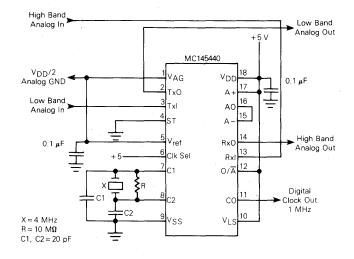

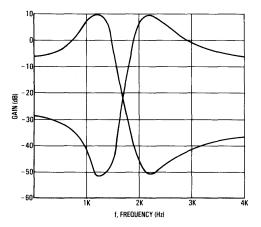

| MC145440             | 300 bps Modem Band-Pass Switch Capacitor Filter (Bell 103)    | 2-378          |

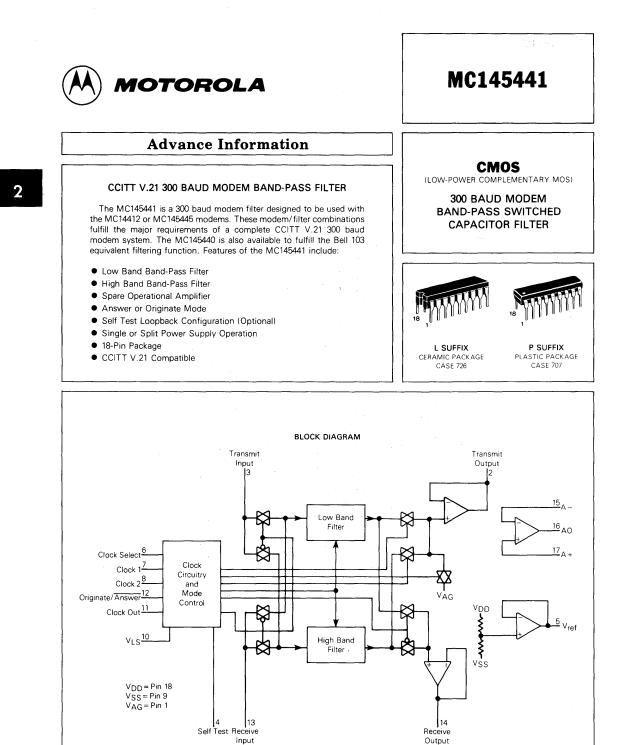

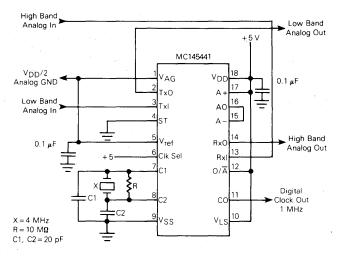

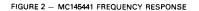

| MC145441             | 300 bps Modem Band-Pass Switch Capacitor Filter (CCITT V.21)  | 2-384          |

| MC145445             | 0-600 bps Mod/Demodulator (Bell 103/CCITT V.21)               | 2-390          |

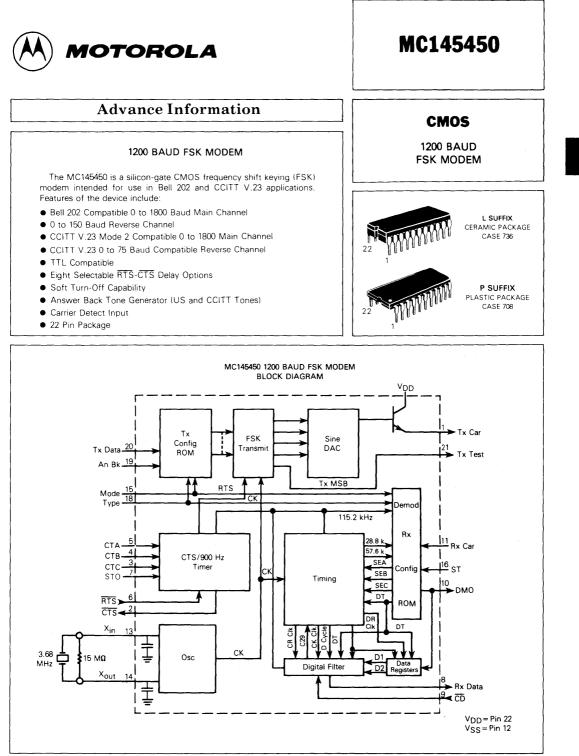

| MC145450             | 0-1800 bps Mod/Demodulator (Bell 202/CCITT V.23)              | 2-395          |

| MC146805             | 8-Bit CMOS Microprocessor Series                              | MCU            |

| MC68000              | 16-Bit Microprocessor                                         | *              |

| MC68153              | Bus Interrupter Module                                        | *              |

| MC68590              | LAN Controller for Ethernet                                   |                |

| MC68452              | Bus Arbitration Module                                        | *              |

| MC68652              | Multi-Protocol Communications Controller                      | *              |

| MC68661              | Enhanced Programmable Communications Interface                | *              |

| MC68681              | Dual Asynchronous Receiver/Transmitter (DUART)                | *              |

| MC68901              | Multi-Function Peripheral                                     | *              |

# **DISCRETE DEVICES**

| 1N6274<br>4N25 | MO-sorb Zener Overvoltage Suppressors                 | RZD<br>Opto |

|----------------|-------------------------------------------------------|-------------|

| MDA220         | Bridge Rectifier                                      | RZD         |

| MFOD1100       | Pin Photo Diode for Fiber Optic Systems               | Opto        |

| MFOE1200       | High-Power AlGaAs LED Fiber Optic Emitter             | Opto        |

| MJE270         | MPN Power Transistors                                 | Power       |

| MJE270         | PNP Power Transistors                                 | Power       |

| MOC3030        | Zero Voltage Crossing Optically Isolated Triac Driver | Opto        |

| MPSA42/43      | NPN 300 V/200 V TO-92 Transistors                     | SS          |

# **Selection Guides**

# SELECTOR GUIDE

This index includes all Motorola devices used specifically in telecommunication applications. Information for the devices identified with page numbers appears in this book. All other devices are fully characterized in the book referenced at the right of the device number.

Linear – See DL128, Linear and Interfaces Integrated Circuits MECL – See DL122R1, MECL Device Data MCU – See DL132R1, Single-Chip Microcomputer Data MPU – See DL133, 8-Bit Microprocessor & Peripheral Data Opto – See DL118R1, Optoelectronics Device Data RZD – See DL125, Rectifier and Zener Diodes Data SF – See DL130, CMOS/NMOS Special Functions Data SS – See DL126, Small-Signal Transistor Data

# Device

Number

Function

# Page Number

# FILTERS

| MC14413-1<br>MC14413-2<br>MC14414-1<br>MC14414-2<br>MC145414<br>MC145415<br>MC145432<br>MC145433<br>MC145440 | PCM Band-Pass/Low-Pass Filter (CCITT)<br>PCM Band-Pass/Low-Pass Filter (D3/D4)<br>PCM Dual Low-Pass Filter (CCITT)<br>PCM Dual Low-Pass Filter (D3/D4)<br>Dual Tunable Low-Pass Sampled Data Filter<br>Dual Tunable Linear Phase Low-Pass Sampled Data Filter<br>Notch/Band-Pass 2600 Hz Tone Signalling Filter<br>Tunable Notch/Band-Pass Filter<br>300 bps Modem Band-Pass Switch Capacitor Filter (Bell 103) | 2-134<br>2-134<br>2-134<br>2-134<br>2-297<br>2-304<br>2-365<br>2-371<br>2-378 |

|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| MC145440                                                                                                     | 300 bps Modem Band-Pass Switch Capacitor Filter (Bell 103)                                                                                                                                                                                                                                                                                                                                                      | 2-378                                                                         |

| MC145441                                                                                                     | 300 bps Modem Band-Pass Switch Capacitor Filter (CCITT V.21)                                                                                                                                                                                                                                                                                                                                                    | 2-384                                                                         |

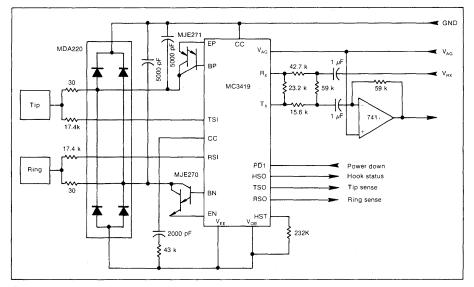

# CENTRAL SWITCHING EQUIPMENT

| MC3417    | CVSD Modulator-Demodulator (3-Bit Algorithm) | 2-12  |

|-----------|----------------------------------------------|-------|

| MC3418    | CVSD Modulator-Demodulator (4-Bit Algorithm) | 2-12  |

| MC3419    | See MC34F19                                  |       |

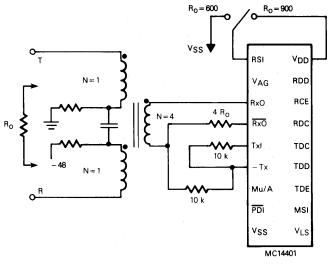

| MC3419-11 | Subscriber Loop Interface Circuit            | 2-30  |

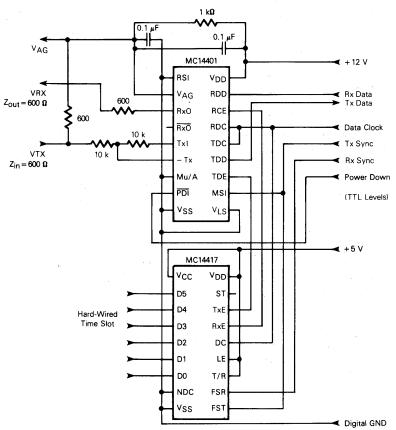

| MC34F19   | Subscriber Loop Interface Circuit            | 2-46  |

| MC3517    | CVSD Modulator-Demodulator (3-Bit Algorithm) | 2-12  |

| MC3518    | CVSD Modulator-Demodulator (4-Bit Algorithm) | 2-12  |

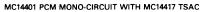

| MC14400   | Single-Chip PCM Codec/Filter Mono-Circuit    | 2-99  |

| MC14401   | Single-Chip PCM Codec/Filter Mono-Circuit    | 2-99  |

| MC14402   | Single-Chip PCM Codec/Filter Mono-Circuit    | 2-99  |

| MC14403   | Single-Chip PCM Code/Filter Mono-Circuit     | 2-99  |

| MC14405   | Single-Chip PCM Codec/Filter Mono-Circuit    | 2-99  |

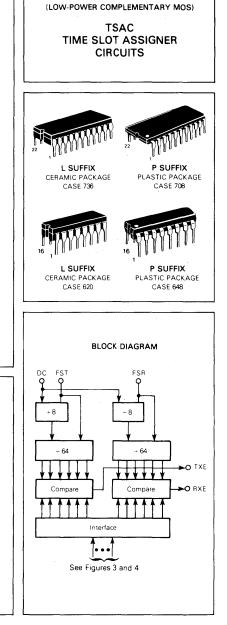

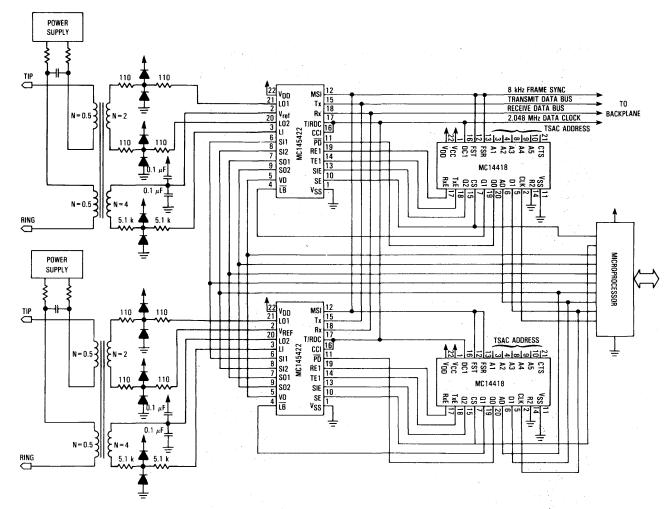

| MC14416   | Time Slot Assigner Circuit (Serial)          | 2-149 |

| MC14417   | Time Slot Assigner Circuit (Parallel)        | 2-169 |

| MC14418   | Time Slot Assigner Circuit (Programmable)    | 2-149 |

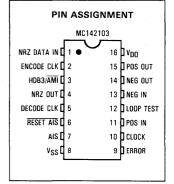

| MC142103  | Transcoder                                   | 2-270 |

| MC145439  | Transcoder                                   | 2-377 |

Device Number

# CROSSPOINT SWITCHES

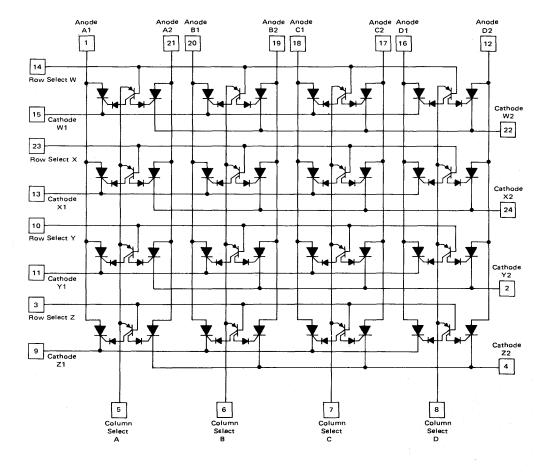

| MC3416   | Crosspoint Switch $(4 \times 4 \times 1)$                     | 2-3   |

|----------|---------------------------------------------------------------|-------|

| MC142100 | Crosspoint Switch With Control Memory (4 × 4 × 1)             | 2-263 |

| MC145100 | Crosspoint Switch With Control Memory $(4 \times 4 \times 1)$ | 2-263 |

| MC142101 | Crosspoint Switch With Central Memory $(4 \times 4 \times 2)$ | 2-269 |

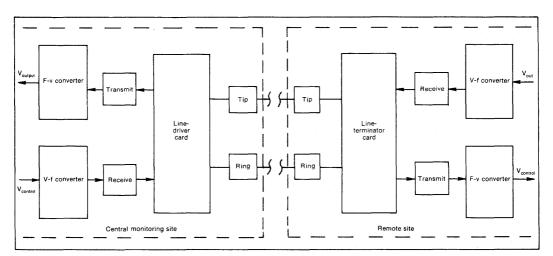

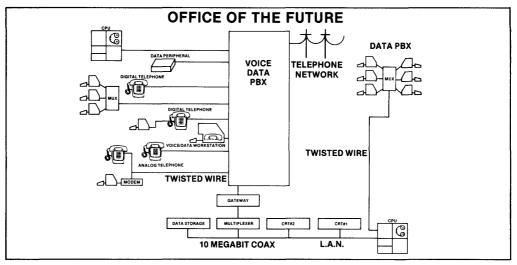

# INTEGRATED VOICE/DATA

| MC34129  | Low Power Switching Power Supply                   | *     |

|----------|----------------------------------------------------|-------|

| MC145418 | Digital-Loop Transceiver (Master)                  | 2-309 |

| MC145419 | Digital-Loop Transceiver (Slave)                   | 2-309 |

| MC145422 | Universal Digital Loop Transceiver (2-Wire Master) | 2-324 |

| MC145426 | Universal Digital Loop Transceiver (2-Wire Slave)  | 2-324 |

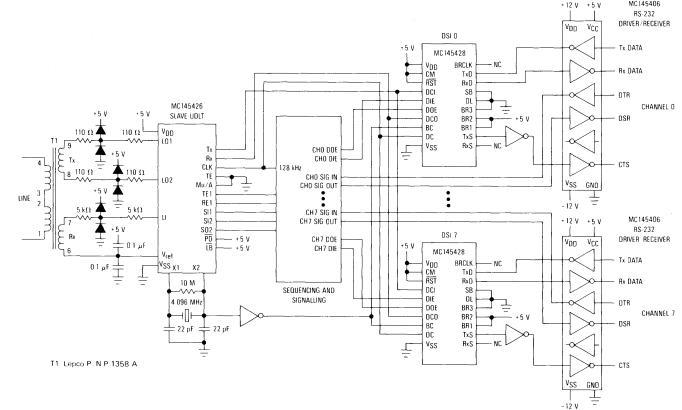

| MC145428 | Data Set Interface (DSI)                           | 2-343 |

| MC145429 | Telset Audio Interface Circuit (TAIC)              | 2-356 |

| MC145421 | 160 kbps ISDN UDLT (Master)                        | 2-323 |

| MC145425 | 160 kbps ISDN UDLT (Slave)                         | 2-323 |

|          |                                                    |       |

# CORDED TELEPHONE

| MC34010  | Electronic Telephone Circuit (MCU Interface)      | 2-177 |

|----------|---------------------------------------------------|-------|

| MC34011  | Electronic Telephone Circuit                      | 2-177 |

| MC34012  | Telephone Tone Ringer                             | 2-201 |

| MC34013  | Speech Network and Tone Dialer                    | 2-209 |

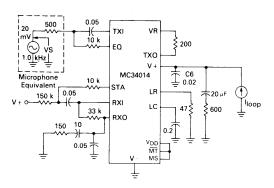

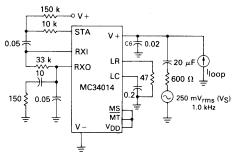

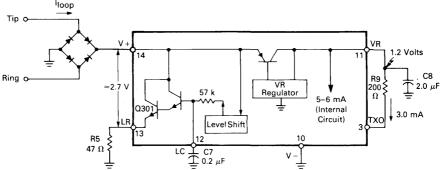

| MC34014  | Telephone Speech Network With Dialer Interface    | 2-224 |

| MC34017  | Telephone Tone Ringer                             | 2-241 |

| MC34018  | Speakerphone Network                              | 2-249 |

| MC34129  | Low Power Switching Power Supply                  | *     |

| MC14408  | Binary to Phone Pulse Converter                   | 2-113 |

| MC14409  | Binary to Phone Pulse Converter                   | 2-113 |

| MC14410  | 2-of-8 Tone Encoder                               | 2-121 |

| MC14419  | 2-to-8 Keypad-to-Binary Encoder                   | 2-173 |

| MC145409 | Integrated Pulse Dialer With Redial               | 2-282 |

| MC145412 | Pulse/Tone Repertory Dialer                       | 2-291 |

| MC145413 | Pulse/Tone Repertory Dialer                       | 2-291 |

| MC145426 | Universal Digital Loop Transceiver (2-Wire Slave) | 2-324 |

| MC145428 | Data Set Interface (DSI)                          | 2-343 |

| MC145429 | Telset Audio Interface Circuit (TAIC)             | 2-356 |

# CORDLESS TELEPHONE

| MC1376 | FM Modulator Circuit           | Linear |

|--------|--------------------------------|--------|

| MC1496 | Balanced Modulator-Demodulator | Linear |

# Device Number

# Page Number

| MC3356   | Wideband FSK Receiver                                   | Linear |

|----------|---------------------------------------------------------|--------|

| MC3357   | Low Power FM IF                                         | Linear |

| MC3359   | High Gain Low-Power FM IF                               | Linear |

| MC3361   | Low-Voltage Narrow-Band FM IF                           | Linear |

| NC3362   | Low Voltage FM/FSK Receiver                             | Linear |

| MC12002  | Analog Mixer                                            | MECL   |

| MC12015  | Low-Power Two-Modulus Prescaler ( ÷ 32/ ÷ 33)           | MECL   |

| MC12016  | Low-Power Two-Modulus Prescaler ( $\div$ 40/ $\div$ 41) | MECL   |

| MC12017  | Low-Power Two-Modulus Prescaler ( $\div$ 64/ $\div$ 65) | MECL   |

| MC12019  | Low-Power Two-Modulus Prescaler ( ÷ 28/ ÷ 21)           | MECL   |

| MC34012  | Telephone Tone Ringer                                   | 2-201  |

| MC34013  | Speech Network and Tone Dialer                          | 2-209  |

| MC34014  | Telephone Speech Network With Redialer Interface        | 2-224  |

| MC145026 | Programmable Encoder                                    | SF     |

| MC145027 | Programmable Decoder                                    | SF     |

| MC145028 | Programmable Decoder                                    | SF     |

| MC145029 | Programmable Decoder                                    | SF     |

| MC145106 | PLL Parallel Programmable Frequency Synthesizer         | SF     |

| MC145145 | PLL 4-Bit Data Bus Programmable                         | SF     |

| MC145146 | PLL 4-Bit Data Bus Programmable                         | SF     |

| MC145151 | PLL Parallel Programmable                               | SF     |

| MC145152 | PLL Parallel Programmable                               | SF     |

| MC145155 | PLL Serial Programmable                                 | SF     |

| MC145156 | PLL Serial Programmable                                 | SF     |

| MC145157 | PLL Serial Programmable                                 | SF     |

| MC145158 | PLL Serial Programmable                                 | SF     |

| MC145168 | Dual PLL 4-Bit BCD Programmable                         | SF     |

| MC145409 | Integrated Pulse Dialer With Redial                     | SF     |

| MC145412 | Pulse/Tone Repertory Dialer                             | 2-291  |

| MC145413 | Pulse/Toner Repertory Dialer                            | 2-291  |

|          |                                                         |        |

# MODEMS

| MC6172   | 2400 bps Digital Modulator (DPSK)                            | 2-62  |

|----------|--------------------------------------------------------------|-------|

| MC6173   | 2400 bps Digital Demodulator (DPSK)                          | 2-70  |

| MC6860   | 8-600 bps Modulator/Demodulator (Bell 103)                   | 2-85  |

| MC14411  | Bit Rate Generator                                           | 2-125 |

| MC14412  | 0-600 bps Modulator/Demodulator (Bell 103/CCITT V.21)        | 2-128 |

| MC143403 | Quad Line Driver                                             | 2-271 |

| MC143404 | Quad Line Driver                                             | 2-271 |

| MC145406 | RS-232/V.28 Driver/Receiver                                  | 2-276 |

| MC145411 | Bit Rate Generator                                           | 2-288 |

| MC145440 | 300 bps Modem Band-Pass Switch Capacitor Filter (Bell 103)   | 2-378 |

| MC145441 | 300 bps Modem Band-Pass Switch Capacitor Filter (CCITT V.21) | 2-384 |

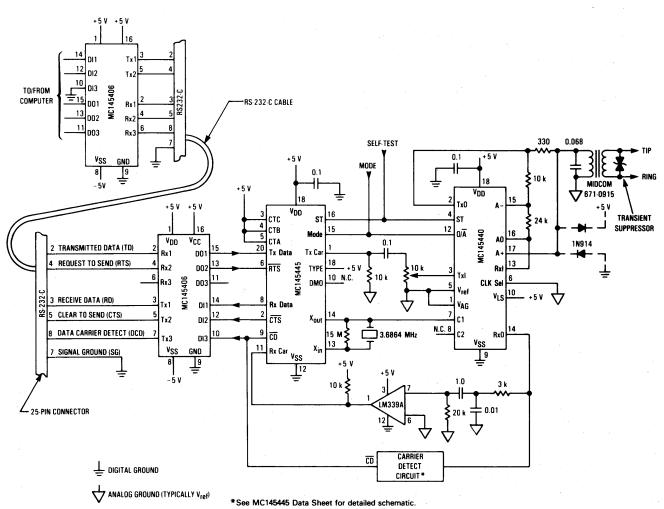

| MC145445 | 0-600 bps Modulator/Demodulator (Bell 103/CCITT V.21)        | 2-390 |

| MC145450 | 0-1800 bps Modulator/Demodulator (Bell 202/CCITT V.23)       | 2-395 |

# DATA COMMUNICATIONS

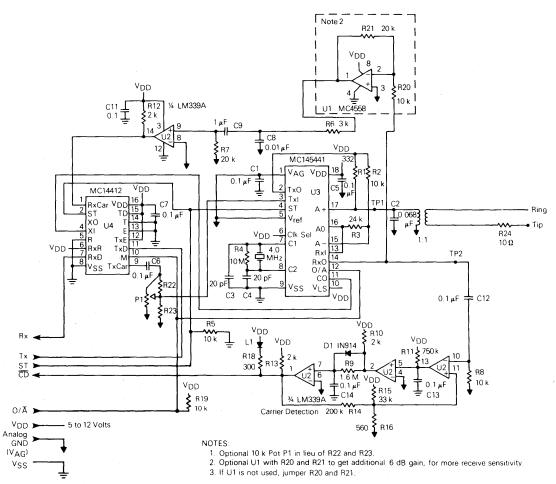

| MC6850<br>MC68HC51<br>MC6852<br>MC68HC53<br>MC6854<br>MC68153<br>MC68452 | Asynchronous Communications Interface Adapter  | MPU<br>MPU<br>MPU<br>MPU<br>* |

|--------------------------------------------------------------------------|------------------------------------------------|-------------------------------|

|                                                                          |                                                |                               |

|                                                                          |                                                | MPU                           |

| MC68153                                                                  |                                                | *                             |

| MC68452                                                                  |                                                |                               |

| MC68652                                                                  | Multi-Protocol Communications Controller       | *                             |

| MC68661                                                                  | Enhanced Programmable Communications Interface | *                             |

| MC68681                                                                  | Dual Asynchronous Receiver/Transmitter (DUART) | * .                           |

| MC68901                                                                  | Multi-Function Peripheral                      | *                             |

|                                                                          |                                                |                               |

# LOCAL AREA NETWORK

| MC68590    | LAN Controller for Ethernet | * |

|------------|-----------------------------|---|

| 1010000000 |                             |   |

# **RF MODEMS**

| MC1374   | TV Modulator Circuit                                    | Linear |

|----------|---------------------------------------------------------|--------|

| MC1376   | FM Modulator Circuit                                    | Linear |

| MC1496   | Balanced Modulator-Demodulator                          | Linear |

| MC3356   | Wideband FSK Receiver                                   | Linear |

| MC3393   | Two-Modulus Prescaler                                   | Linear |

| MC3396   | Divide By 28 Prescaler                                  | Linear |

| MC12002  | Analog Mixer                                            | MECL   |

| MC12009  | Two-Modulus Prescaler ( ÷ 5/ ÷ 6)                       | MECL   |

| MC12011  | Two-Modulus Prescaler ( ÷ 8/ ÷ 9)                       | MECL   |

| MC12013  | Two-Modulus Prescaler ( ÷ 10/ ÷ 11)                     | MECL   |

| MC12015  | Low-Power Two-Modulus Prescaler ( ÷ 32/ ÷ 33)           | MECL   |

| MC12016  | Low-Power Two-Modulus Prescaler ( ÷ 48/ ÷ 41)           | MECL   |

| MC12017  | Low-Power Two-Modulus Prescaler ( $\div$ 64/ $\div$ 65) | MECL   |

| MC12018  | 520 MHz Low-Power Prescaler ( ÷ 128/ ÷ 129)             | MECL   |

| MC12019  | Low-Power Two-Modulus Prescaler ( $\div 28/ \div 21$ )  | MECL   |

| MC12022  | 1.0 GHz Low-Power Two-Modulus Prescaler ( ÷ 128/ ÷ 129) | MECL   |

| MC12023  | Low-Power Prescaler ( ÷ 64)                             | MECL   |

| MC12071  | High-Speed Prescaler ( ÷ 64/ ÷ 256)                     | MECL   |

| MC12073  | Low-Power Prescaler ( ÷ 64)                             | MECL   |

| MC12074  | Low-Power Prescaler ( ÷ 256)                            | MECL   |

| MC12090  | High-Speed Prescaler ( ÷ 2)                             | MECL   |

| MC145106 | PLL Parallel Programmable Frequency Synthesizer         | SF     |

| MC145145 | PLL 4-Bit Data Bus Programmable                         | SF     |

1

| Device<br>Number                                                                 | Function                                                                                                                                                                                                            | Page<br>Number                   |

|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| MC145146<br>MC145151<br>MC145152<br>MC145155<br>MC145156<br>MC145157<br>MC145158 | PLL 4-Bit Data Bus Programmable .<br>PLL Parallel Programmable .<br>PLL Parallel Programmable .<br>PLL Serial Programmable .<br>PLL Serial Programmable .<br>PLL Serial Programmable .<br>PLL Serial Programmable . | SF<br>SF<br>SF<br>SF<br>SF<br>SF |

# MICROPROCESSOR PRODUCTS

| MC6800   | 8-Bit Microprocessor Unit        | MPU |

|----------|----------------------------------|-----|

|          | 8-Bit Microprocessing Unit       | MPU |

|          | 8-Bit Microcomputer Unit         | MCU |

|          | 8-Bit Microcomputer Unit         | MCU |

|          | 8-Bit HCMOS Microcomputer Unit   | MCU |

|          | 8-Bit HMOS Microcomputer Series  | MCU |

| MC146805 | 8-Bit CMOS Microprocessor Series | MCU |

| MC68HC05 | 8-Bit HCMOS Microcomputer Series | MCU |

| MC68000  | 16-Bit Microprocessor            | *   |

# VOLTAGE SUPRESSORS

| 1N6274 | MO-sorb Zener Overvoltage Supressors | RZD |

|--------|--------------------------------------|-----|

| MDA220 | Bridge Rectifier                     | RZD |

# POWER DRIVERS

| MFOD1100  | Pin Photo Diode for Fiber Optic Systems   | Opto |

|-----------|-------------------------------------------|------|

| MFOE1200  | High-power AIGaAs LED Fiber Optic Emitter | Opto |

| MPSA42/43 | NPN 300V TO-92 Transistors                | SS   |

# **OPTICAL CIRCUITS**

| MOC3030 | Triac Driver Coupler | Opto |

|---------|----------------------|------|

|         | OPTO Coupler         |      |

\*Contact your Motorola representative for the most up-to-date information.

1-8

Data Sheets

2

÷ ..

2

2-3

# MAXIMUM RATINGS (Unless otherwise noted, T<sub>A</sub> = 25<sup>o</sup>C)

| Rating                                                         | Symbol          | Value              | Unit |

|----------------------------------------------------------------|-----------------|--------------------|------|

| Anode-Cathode Current – Continuous<br>(only one SCR at a time) | IAK             | 150                | mA   |

| Enable Current                                                 | 1 <sub>En</sub> | 10                 | mA   |

| Operating Ambient Temperature Range                            | TA              | 0 to +70           | °C   |

| Storage Temperature Range                                      | Tstg            | -65 to +150        | °C   |

| Junction Temperature Range                                     | T J             | 150 <sup>0</sup> C | °C   |

# ELECTRICAL CHARACTERISTICS (Unless otherwise noted, TA = 0 to 70°C)

| Characteristic                                                                                     | Symbol            | Min            | Max        | Unit  |

|----------------------------------------------------------------------------------------------------|-------------------|----------------|------------|-------|

| Anode Cathode Breakdown Voltage<br>(I <sub>AK</sub> = 25µA)                                        | BVAK              | 25             | _          | Vdc   |

| Cathode-Anode Breakdown Voltage<br>(I <sub>K A</sub> = 25µA)                                       | BVKA              | 25             |            | Vdc   |

| Base-Cathode Breakdown Voltage<br>(Ι <sub>ΒΚ</sub> = 25μΑ)                                         | BV <sub>BK</sub>  | 25             | -          | Vdc   |

| Cathode-Base Breakdown Voltage<br>(I <sub>KB</sub> = 25µA)                                         | BVKB              | 25             |            | Vdc   |

| Base-Emitter Breakdown Voltage<br>(I <sub>BE</sub> = 25μΑ)                                         | BVBE              | 25             | ·          | Vdc   |

| Emitter-Cathode Breakdown Voltage<br>(I <sub>EK</sub> = 25µA)                                      | BVEK              | 25             | _          | Vdc   |

| OFF State Resistance<br>(V <sub>AK</sub> = 10 V)                                                   | roff              | 100            | -          | MΩ    |

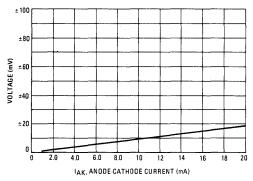

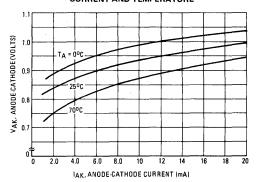

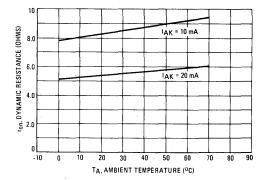

| Dynamic ON Resistance<br>(Center Current = 10 mA) (See Figure 8)<br>(Center Current = 20 mA)       | ron               | 4.0<br>2.0     | 12<br>10   | Ω     |

| Holding Current<br>(See Figure 10)                                                                 | ļ. <sup>I</sup> Η | 0.7            | 3.0        | mA    |

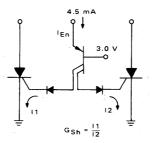

| Enable Current<br>(VBE = 1.5 V) (See Figure 7)                                                     | IEn               | 4.0            |            | mA    |

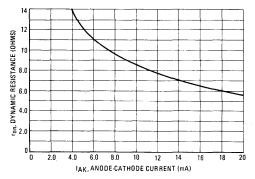

| Anode-Cathode ON Voltage<br>(I <sub>AK</sub> = 10 mA)<br>(I <sub>AK</sub> = 20 mA)                 | VAK               | -              | 1.0<br>1.1 | · V   |

| Gate Sharing Current Ratio @ Cathodes<br>(Under Select Conditions with Anodes Open) (See Figure 3) | G <sub>Sh</sub>   | 0.8            | 1.25       | mA/mA |

| Inhibit Voltage<br>(Vg = 3.0 V) (See Figure 9)                                                     | Vinh              |                | 0.3        | V     |

| Inhibit Current<br>(V <sub>B</sub> = 3.0 V) (See Figure 9)                                         | linh              | -              | 0.1        | mA    |

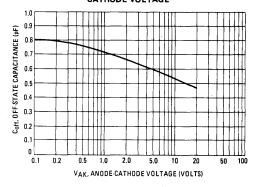

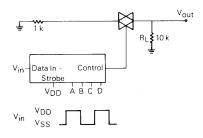

| OFF State Capacitance<br>(V <sub>AK</sub> = 0 V)(See Figure 6)                                     | C <sub>off</sub>  | -              | 2.0        | pF    |

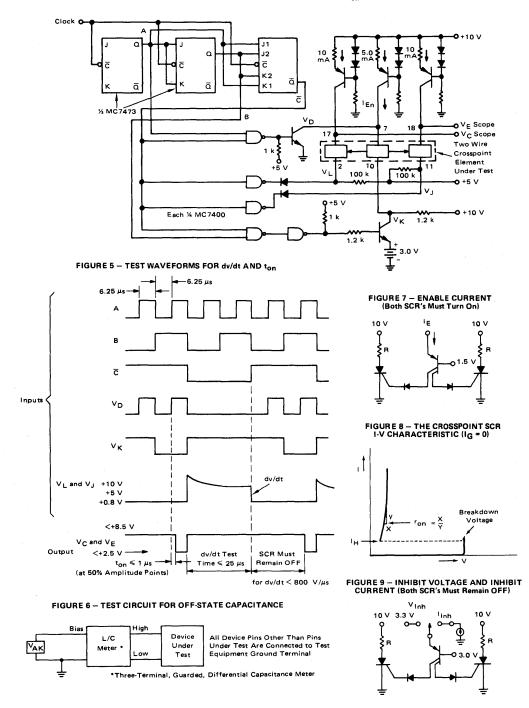

| Turn-ON Time<br>(See Figure 4)                                                                     | ton               | <del>-</del> . | 1.0        | μs    |

| Minimum Voltage Ramp (Which Could Fire the SCR Under<br>Transient Conditions)                      | dv/dt             | 800            | -          | V/µs  |

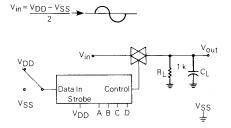

#### FIGURE 3 - TEST CIRCUIT

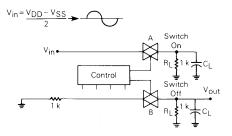

FIGURE 4 - TEST CIRCUIT FOR dv/dt AND ton

#### FIGURE 10 - HOLDING CURRENT versus AMBIENT TEMPERATURE 2.0 IH, HOLDING CURRENT (mA) 1.6 1.2 0.8 0.4 0 -10 n 10 20 30 40 50 60 70 80 90 TA, AMBIENT TEMPERATURE (°C)

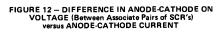

FIGURE 14 – DYNAMIC ON RESISTANCE versus ANODE-CATHODE CURRENT

FIGURE 11 – ANODE-CATHODE ON VOLTAGE versus CURRENT AND TEMPERATURE

TYPICAL CHARACTERISTICS

FIGURE 13 - OFF-STATE CAPACITANCE versus ANODE-CATHODE VOLTAGE

FIGURE 15 – DYNAMIC ON RESISTANCE versus AMBIENT TEMPERATURE

# MC3416

2

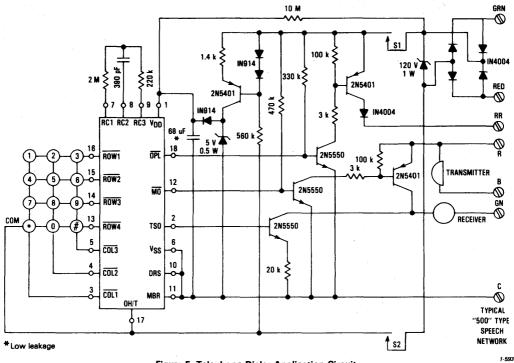

# TELEPHONE APPLICATION OF THE CROSSPOINT SWITCH

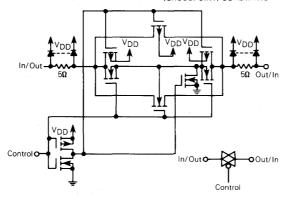

The MC3416 crosspoint switch is designed to provide a low-loss analog switching element for telephony signals. It can be addressed and controlled from standard binary decoders and is CMOS compatible. With proper system organization the MC3416 can significantly reduce the size and cost of existing crosspoint matrices.

# SIGNAL PATH CONSIDERATIONS

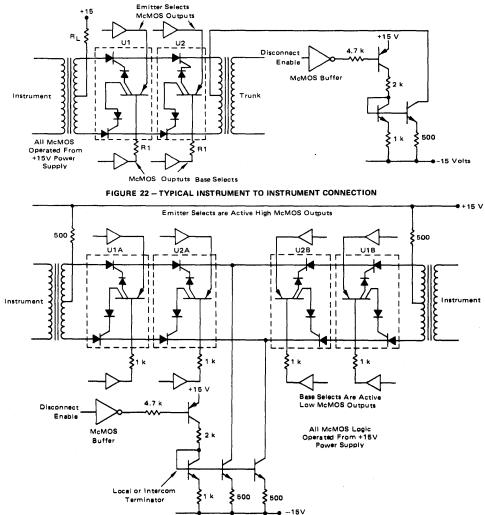

The MC3416 is a balanced 4 x 4 2-wire crosspoint array. It is ideal for balanced transmission systems, but may be applied effectively in a number of single ended applications. Multiple chips may be interconnected to form larger crosspoint arrays. The major design constraint in using SCR crosspoints is that a forward dc current must be maintained through the SCR to retain an ac signal path. This requires that each subscriber-input to the array be capable of sourcing dc current as well as its ac signal. With each subscriber acting as a dc source, each trunk output then acts as a current sink. The instrument-to-trunk connection in Figure 21 shows this configuration. However, with each subscriber acting as a dc source, some method of interconnecting them without a trunk must be provided. Such a local or intercom termination is shown in Figure 22. Here both subscribers source dc current and exchange ac signals. The central current sink accepts current from both subscribers while the high output impedance of the current sink does not disturb the system.

These configurations are system compatible. The dc

FIGURE 21 - INSTRUMENT-TO-TRUNK CONNECTION

# MC3416

current restriction is not a restriction in the design of an efficient crosspoint array. Because of the current sink terminations, a signal path may use differing numbers of crosspoints in any connection or in two sides of the same connection further relaxing restrictions in array design.

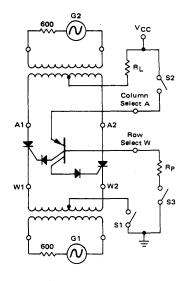

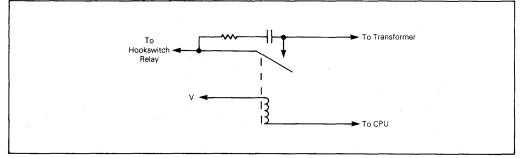

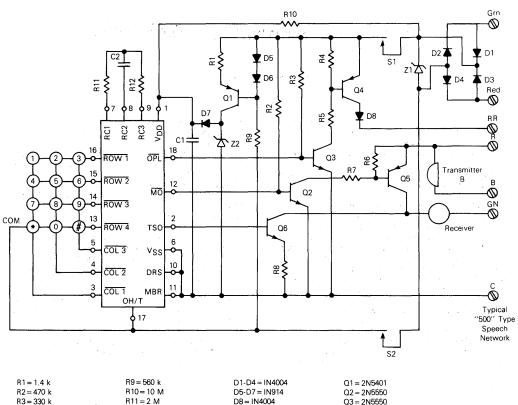

Figure 23 demonstrates circuit operation. S1, S2, and S3 are open. The Crosspoint SCR's are off as they have no gate drive or dc current path through S1. By closing S2 and S3, gate drive is provided, but the SCR's still remain off as there is no dc current path to hold them on. Close S1 and the circuit is enabled, but with S2 and S3 off there is still no signal path. Closing S2 and S3 with S1 closed - current is injected into both gates and they switch on. DC current through RL splits around the center-tapped winding and flows through each SCR, back through the lower winding and through S1 to ground. If S2 and S3 are opened, that current path still remains and the SCRs remain on. If an ac signal is injected at either G1 or G2, it will be transmitted to the other signal port with negligible loss in the SCR's. To disconnect the ac signal path the SCR's must be commutated off. By opening S1 the dc current path is interrupted and the SCR's switch off. The ac signal path is disconnected. With S1 closed the circuit is enabled and may be addressed again from S2 and S3. This circuit demonstrates a balanced transmission configuration. The transmission characteristics of the SCR's simulate a relay contact in that the ac signal does not incur a contact voltage drop across the crosspoint. The memory characteristics of the crosspoint are demonstrated by the selective application of S1, S2, and S3.

The selection of R<sub>L</sub> is governed by the power supply voltage and the desired dc current. If 10 mA is to flow through each SCR then R<sub>L</sub> must pass 20 mA. Thus,  $(V_{CC} - V_{AK})/R_L = 20$  mA. The selection of Rp is governed by the characteristics for crosspoint turn on. Adequate enable current must be injected into the column select and Rp should drop at least 1.5 Volts. The PNP transistor has a typical gain of one. Thus, Rp should pass at least 2 mA to provide 4 mA column select current.

#### FIGURE 23- CROSSPOINT OPERATION DEMONSTRATION CIRCUIT

| S1                               | S2                              | S3 | LINE CONDITION |  |  |

|----------------------------------|---------------------------------|----|----------------|--|--|

| ON                               | ON X OFF Enabled, Not Connected |    |                |  |  |

| ON OFF X Enabled, Not Connected  |                                 |    |                |  |  |

| ON ON ON Addressed and Connected |                                 |    |                |  |  |

| ON X X G1 Connected to G2        |                                 |    |                |  |  |

| OFF                              | х                               | X  | Disconnected.  |  |  |

|                                  |                                 | X  | ≈ irrelevant   |  |  |

#### ADDRESSING CONSIDERATIONS

The MC3416 crosspoint switch is addressed by selecting and turning on the PNP transistor that controls the SCR pair desired. The drive requirements of the MC3416 can be met with standard McMOS outputs. A particular crosspoint is addressed by putting a logical "1" on the emitter and a logical "0" on the base of the appropriate transistor. A resistor in the base circuit of the transistor is required to limit the current and must also drop 1.5 Volts to assure forward bias of the two diodes in the collector circuits. The gate current required for SCR turn on is 1 mA typically. The McMOS one-of-n decoders listed in Table I provide both active high and active low outputs and are well suited for standard addressing organizations. The major design constraint in organizing the addressing structure is that any signal path which is to be addressed must create a dc path from a source to a sink. If that path requires two crosspoints they must be addressed simultaneously. Of course, once the path is selected, the addressing hardware is free to initiate other signal paths. To meet the dc path

# MC3416

# APPLICATIONS INFORMATION (continued)

requirement, crosspoint arrays should be designed in blocks such that any given dc path requires only one crosspoint per block. A signal path, however, may still use two crosspoints in the same block by sequentially addressing two dc paths to the same terminator. For example, the left or right pairs of crosspoints in Figure 22 must be addressed simultaneously but the left pair may be addressed in sequence after addressing the right pair. This is not a difficult constraint to meet and it does not require unnecessary addressing hardware.

|                       | TABLEI              |                    |

|-----------------------|---------------------|--------------------|

|                       | Active High Outputs | Active Low Outputs |

| Dual Binary to 1 of 4 | MC14555             | MC14556            |

| 4-bit latch/4 to 16   | MC14514             | MC14515            |

| BCD to Decimal Decode | MC14028             |                    |

# DISCONNECT TECHNIQUES

Since the crosspoint switch maintains signal paths by keeping dc currents through active SCR's, disconnects are easily accomplished by interrupting the dc current path. This can be done anywhere in the circuit, but if the disconnect is done at the terminator then all signal paths established to that terminator are broken simultaneously. In both Figures 21 and 22 this is done by turning off the current sink circuit with a McMOS buffer gate. MC14049 or MC14050 buffers will drive the transistor switch. Once a disconnect is completed, the terminator may be re-enabled and used for another call. Usage of the terminators may be easily monitored with optoelectronic couplers in the collectors of the current sinks without disturbing transmission characteristics.

| See Application Note AN-760 for additional applications | suggestions. |

|---------------------------------------------------------|--------------|

|---------------------------------------------------------|--------------|

# THERMAL INFORMATION

The maximum power consumption an integrated circuit can tolerate at a given operating ambient temperature can be found from the equation:

$$P_{D}(T_{A}) = \frac{T_{J}(max) - T_{A}}{R_{\theta \mid \Delta}(T_{VP})}$$

Where:  $P_D(T_A)$  = Power Dissipation allowable at a given operating ambient temperature. This must be greater than

the sum of the products of the supply voltages and supply currents at the worst case operating condition.

- $\begin{array}{l} T_{J(max)} = Maximum \mbox{ Operating Junction Temperature} \\ as listed in the Maximum Ratings Section \\ T_{A} = Maximum \mbox{ Desired Operating Ambient} \end{array}$

- Temperature  $R_{\partial JA}(Typ)$  = Typical Thermal Resistance Junction to

Ambient

# Specifications and Applications Information

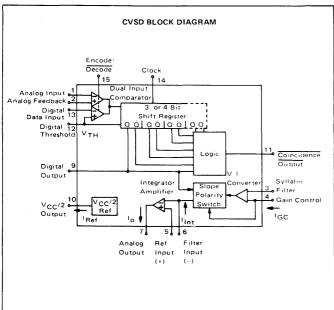

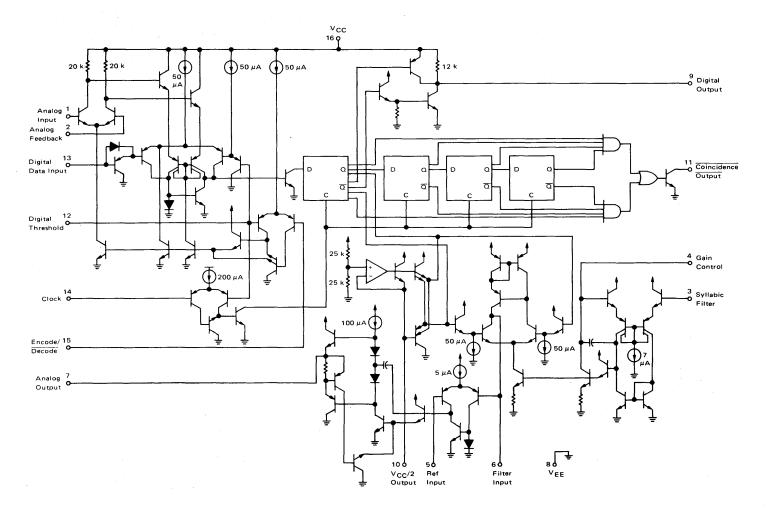

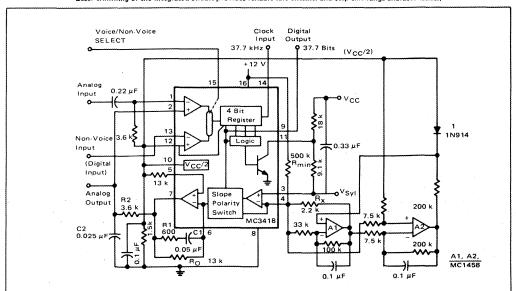

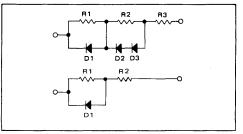

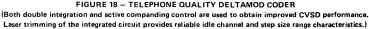

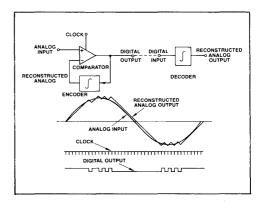

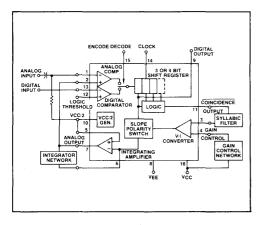

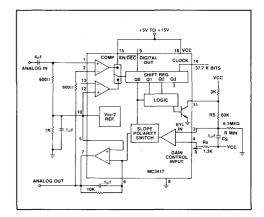

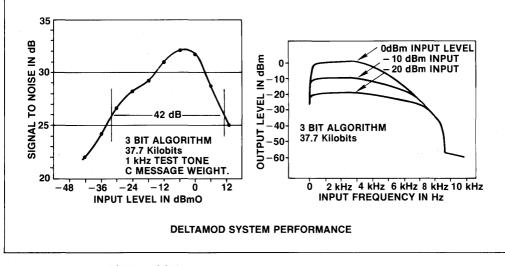

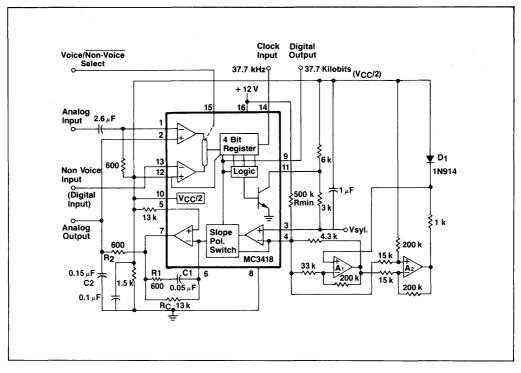

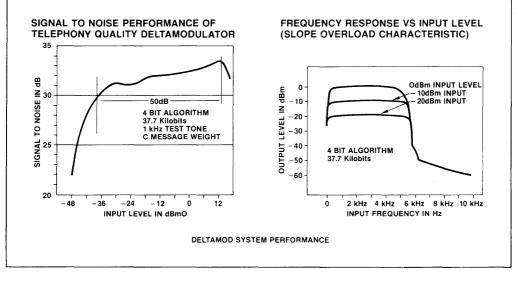

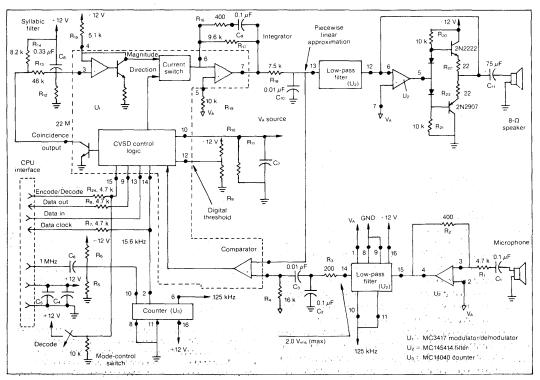

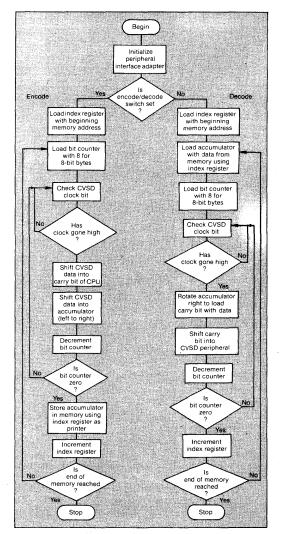

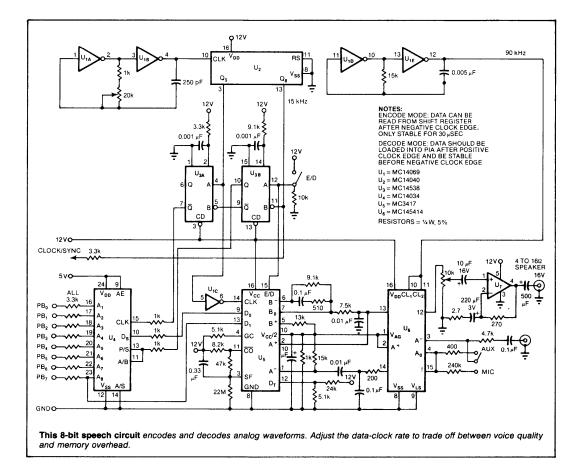

# CONTINUOUSLY VARIABLE SLOPE DELTA MODULATOR/DEMODULATOR

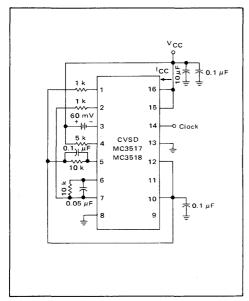

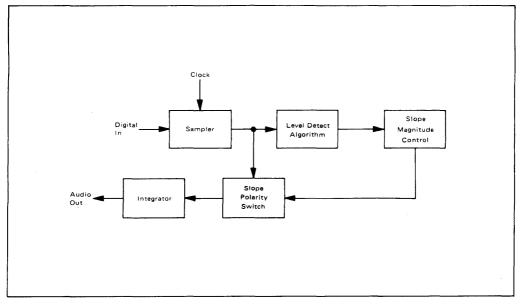

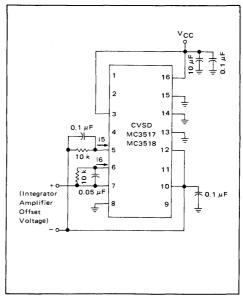

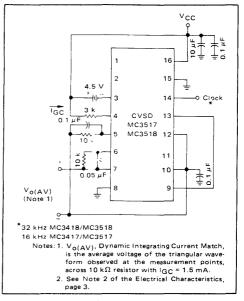

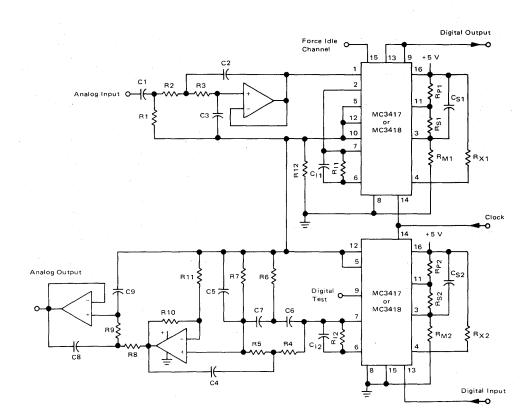

Providing a simplified approach to digital speech encoding/ decoding, the MC3517/18 series of CVSDs is designed for military secure communication and commercial telephone applications. A single IC provides both encoding and decoding functions.

- Encode and Decode Functions on the Same Chip with a Digital Input for Selection

- Utilization of Compatible I<sup>2</sup>L Linear Bipolar Technology

- CMOS Compatible Digital Output

- Digital Input Threshold Selectable (V<sub>CC</sub>/2 reference provided on chip)

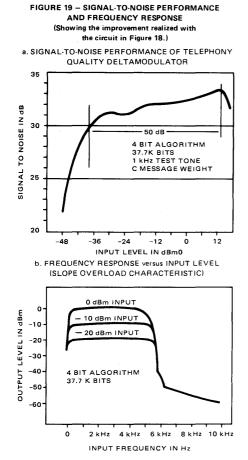

- MC3417/MC3517 has a 3-Bit Algorithm (General Communications)

- MC3418/MC3518 has a 4-Bit Algorithm (Commercial Telephone)

# MC3417, MC3517 MC3418, MC3518

# CONTINUOUSLY VARIABLE SLOPE DELTA MODULATOR/DEMODULATOR

LASER-TRIMMED

## ORDERING INFORMATION

| Device  | Package     | Temperature<br>Range                   |

|---------|-------------|----------------------------------------|

| MC3417L | Ceramic DIP | 0 <sup>0</sup> C to +70 <sup>0</sup> C |

| MC3418L | Ceramic DIP | 0 <sup>0</sup> C to +70 <sup>0</sup> C |

| MC3517L | Ceramic D1P | -55°C to +125°C                        |

| MC3518L | Ceramic DIP | -55°C to +125°C                        |

# MAXIMUM RATINGS

(All voltages referenced to  $V_{EE}$ ,  $T_A = 25^{\circ}C$  unless otherwise noted.)

| Rating                                                      | Symbol           | Value                                       | Unit |  |

|-------------------------------------------------------------|------------------|---------------------------------------------|------|--|

| Power Supply Voltage                                        | Vcc              | -0.4 to +18                                 | Vdc  |  |

| Differential Analog Input Voltage                           | VID              | ± 5.0                                       | Vdc  |  |

| Digital Threshold Voltage                                   | ∨тн              | -0.4 to V <sub>CC</sub>                     | Vdc  |  |

| Logic Input Voltage<br>(Clock, Digital Data, Encode/Decode) | VLogic           | -0.4 to +18                                 | Vdc  |  |

| Coincidence Output Voltage                                  | VO(Con)          | -0.4 to +18                                 | Vdc  |  |

| Syllabic Filter Input Voltage                               | VI(Syl)          | -0.4 to V <sub>CC</sub>                     | Vdc  |  |

| Gain Control Input Voltage                                  | VI(GC)           | -0.4 to V <sub>CC</sub>                     | Vdc  |  |

| Reference Input Voltage                                     | VI(Ref)          | V <sub>CC</sub> /2 - 1.0 to V <sub>CC</sub> | Vdc  |  |

| V <sub>CC</sub> /2 Output Current                           | <sup>I</sup> Ref | -25                                         | mA   |  |

# ELECTRICAL CHARACTERISTICS

$(V_{CC} = 12 V, V_{EE} = Gnd, T_A = 0^{\circ}C$  to +70°C for MC3417/18,  $T_A = -55^{\circ}C$  to +125°C for MC3517/18 unless otherwise noted.)

| Characteristic                                                                                                                                    |                                      | MC3417/MC3517 |                             |                           | MC3418/MC3518 |                               |                          |           |

|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------|-----------------------------|---------------------------|---------------|-------------------------------|--------------------------|-----------|

|                                                                                                                                                   | Symbol                               | Min           | Тур                         | Max                       | Min           | Тур                           | Max                      | Unit      |

| Power Supply Voltage Range (Figure 1)                                                                                                             | VCCR                                 | 4.75          | 12                          | 16.5                      | 4.75          | 12                            | 16.5                     | Vdc       |

| Power Supply Current (Figure 1)<br>(Idle Channel)                                                                                                 | 'cc                                  |               |                             |                           |               |                               |                          | mA        |

| (V <sub>CC</sub> = 5.0 V)<br>(V <sub>CC</sub> = 15 V)                                                                                             |                                      | -             | 3.7<br>6.0                  | 5.0<br>10                 | -             | 3.7<br>6.0                    | 5.0<br>10                |           |

| Clock Rate                                                                                                                                        | SR                                   |               | 16 k                        | -                         | -             | 32 k                          | _                        | Samples/s |

| Gain Control Current Range (Figure 2)                                                                                                             | IGCR                                 | 0.001         | -                           | 3.0                       | 0.001         | -                             | 3.0                      | mA        |

| Analog Comparator Input Range<br>(Pins 1 and 2)<br>$(4.75 V \le V_{CC} \le 16.5 V)$                                                               | VI                                   | 1.3           | -                           | V <sub>CC</sub> – 1.3     | 1.3           | -                             | V <sub>CC</sub> – 1.3    | Vdc       |

| Analog Output Range (Pin 7)<br>$(4.75 \text{ V} \leq \text{V}_{CC} \leq 16.5 \text{ V}, \text{I}_{O} = \pm 5.0 \text{ mA})$                       | Vo                                   | 1.3           | -                           | V <sub>CC</sub> - 1.3     | 1.3           | -                             | V <sub>CC</sub> – 1.3    | Vdc       |

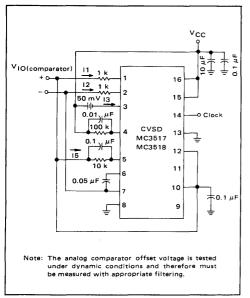

| Input Bias Currents (Figure 3)<br>(Comparator in Active Region)                                                                                   | 1 IB                                 |               |                             |                           |               |                               |                          | μA        |

| Analog Input (I1)<br>Analog Feedback (I2)<br>Syllabic Filter Input (I3)<br>Reference Input (I5)                                                   |                                      | -             | 0.5<br>0.5<br>0.06<br>-0.06 | 1.5<br>1.5<br>0.5<br>-0.5 |               | 0.25<br>0.25<br>0.06<br>-0.06 | 1.0<br>1.0<br>0.3<br>0.3 |           |

| Input Offset Current                                                                                                                              |                                      |               | -0.00                       | -0.5                      |               | 0.00                          | -0.5                     | μΑ        |

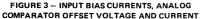

| (Comparator in Active Region)<br>Analog Input/Analog Feedback<br>  1- 2  Figure 3<br>Integrator Amplifier                                         | 110                                  | -             | 0.15<br>0.02                | 0.6<br>0.2                | -             | 0.05<br>0.01                  | 0.4<br>0.1               | #A        |

| II5-I6  - Figure 4<br>Input Offset Voltage<br>V/I Converter (Pins 3 and 4) - Figure 5                                                             | VIO                                  | -             | 2.0                         | 6.0                       | -             | 2.0                           | 6.0                      | mV        |

| Transconductance<br>V/I Converter, 0 to 3.0 mA<br>Integrator Amplifier, 0 to ± 5.0 mA Load                                                        | gm                                   | 0.1<br>1.0    | 0.3<br>10                   |                           | 0.1<br>1.0    | 0.3<br>10                     | -                        | ∙mA/mV    |

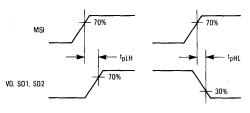

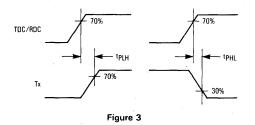

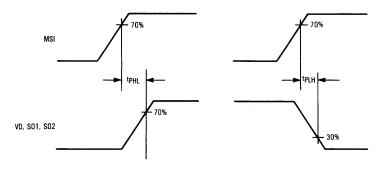

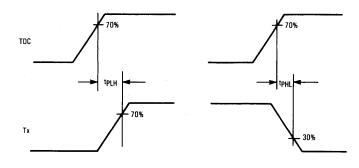

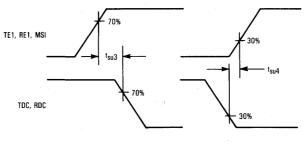

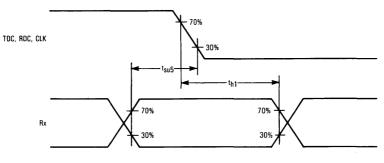

| Propagation Delay Times (Note 1)<br>Clock Trigger to Digital Output<br>(CL = 25 pF to Gnd)                                                        | <sup>t</sup> РLН<br><sup>t</sup> РНL | -             | 1.0<br>0.8                  | 2.5<br>2.5                |               | 1.0<br>0.8                    | 2.5<br>2.5               | μs        |

| Clock Trigger to Coincidence Output<br>( $C_L = 25 \text{ pF}$ to Gnd)<br>( $R_L = 4 \text{ k}\Omega$ to $V_{CC}$ )                               | <sup>t</sup> PLH<br><sup>t</sup> PHL | . –           | 1.0<br>0.8                  | 3.0<br>2.0                | -             | 1.0<br>0.8                    | 3.0<br>2.0               |           |

| Coincidence Output Voltage —<br>Low Logic State<br>(1 <sub>OL</sub> ( <sub>Con</sub> ) = 3.0 mA)                                                  | V <sub>OL</sub> (Con)                | -             | 0.12                        | 0.25                      |               | 0.12                          | 0.25                     | Vdc       |

| Coincidence Output Leakage Current –<br>High Logic State<br>( $V_{OH}$ = 15.0 V, 0 <sup>o</sup> C $\leq$ T <sub>A</sub> $\leq$ 70 <sup>o</sup> C) | IOH(Con)                             | -             | 0.01                        | 0.5                       | -             | 0.01                          | 0.5                      | μA        |

NOTE 1. All propagation delay times measured 50% to 50% from the negative going (from V<sub>CC</sub> to +0.4 V) edge of the clock.

# ELECTRICAL CHARACTERISTICS (continued)

|                                                                                                    |                   | MC3417/MC3517         |                       |                       | MC3418/MC3518         |                       |                       |      |

|----------------------------------------------------------------------------------------------------|-------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|------|

| Characteristic                                                                                     | Symbol            | Min                   | Тур                   | Max                   | Min                   | Тур                   | Max                   | Unit |

| Applied Digital Threshold Voltage Range<br>(Pin 12)                                                | · V <sub>TH</sub> | +1.2                  | -                     | V <sub>CC</sub> - 2.0 | +1.2                  | -                     | V <sub>CC</sub> ~ 2.0 | Vdc  |

| Digital Threshold Input Current                                                                    | ll(th)            |                       |                       |                       |                       |                       |                       | μA   |

| $(1.2 \vee \leq \vee_{th} \leq \vee_{CC} - 2.0 \vee)$                                              |                   |                       |                       | 5.0                   |                       |                       | 5.0                   |      |

| (V <sub>IL</sub> applied to Pins 13, 14 and 15)<br>(V <sub>IH</sub> applied to Pins 13, 14 and 15) |                   | _                     | - 10                  | 5.0<br>50             |                       | -10                   | 5.0<br>-50            |      |

| Maximum Integrator Amplifier Output Current                                                        | <sup>1</sup> 0    | ± 5.0                 |                       | -                     | ±5.0                  |                       |                       | mA   |

| / <sub>CC</sub> /2 Generator Maximum Output Current                                                |                   | +10                   |                       |                       | +10                   | _                     |                       | mA   |

| (Source only)                                                                                      | Ref               | +10                   |                       | _                     | +10                   |                       |                       |      |

| <pre>/CC/2 Generator Output Impedance   (0 to +10 mA)</pre>                                        | ZRef              | -                     | 3.0                   | 6.0                   | -                     | 3.0                   | 6.0                   | Ω    |

| /CC/2 Generator Tolerance                                                                          | εr                | -                     | _                     | ± 3.5                 |                       | _                     | ± 3.5                 | %    |

| (4.75 V ≤ V <sub>CC</sub> ≤ 16.5 V)                                                                |                   |                       |                       |                       |                       |                       |                       |      |

| ogic Input Voltage (Pins 13, 14 and 15)                                                            |                   |                       |                       |                       |                       |                       |                       | Vdd  |

| Low Logic State                                                                                    | VIL               | Gnd                   | -                     | V <sub>th</sub> ~ 0.4 | Gnd                   | -                     | V <sub>th</sub> - 0.4 |      |

| High Logic State                                                                                   | VIH               | V <sub>th</sub> + 0.4 | _                     | 18.0                  | V <sub>th</sub> + 0.4 | _                     | 18.0                  |      |

| Dynamic Total Loop Offset Voltage                                                                  | ΣVoffset          |                       |                       |                       |                       |                       |                       | mV   |

| (Note 2) - Figures 3, 4 and 5                                                                      |                   |                       |                       |                       |                       |                       |                       |      |

| $I_{GC} = 12.0 \ \mu A, \ V_{CC} = 12 \ V$                                                         |                   |                       |                       |                       |                       |                       |                       |      |

| $T_A = 25^{\circ}C$                                                                                |                   | -                     | -                     | -                     | -                     | ± 0.5                 | ± 1.5                 |      |

| $0^{\circ}C \le T_{A} \le +70^{\circ}C$ MC3417/18                                                  |                   | -                     | -                     | -                     | -                     | ± 0.75                | ± 2.3                 |      |

| $-55^{\circ}C \le T_{A} \le +125^{\circ}C \text{ MC3517/18}$                                       | l                 | -                     | -                     | -                     | -                     | ± 1.5                 | ± 4.0                 |      |

| $I_{GC} = 33.0 \ \mu A, \ V_{CC} = 12 \ V$                                                         |                   | ľ                     |                       |                       |                       |                       |                       |      |

| $T_{A} = 25^{\circ}C$                                                                              |                   | -                     | ± 2.5                 | ± 5.0                 | -                     | , <del>-</del>        | ~                     |      |

| $0^{\circ}C \le T_{A} \le +70^{\circ}C$ MC3417/18<br>-55°C $\le T_{A} \le +125^{\circ}C$ MC3517/18 |                   | -                     | ± 3.0                 | ± 7.5                 | -                     | -                     | -                     |      |

|                                                                                                    |                   | -                     | ± 4.5                 | ± 10                  | -                     | -                     | -                     |      |

| $I_{GC} = 12.0 \ \mu A, \ V_{CC} = 5.0 \ V$<br>$T_A = 25^{\circ}C$                                 |                   |                       |                       | 1                     |                       |                       |                       |      |

| $0^{\circ}C \le T_{A} \le +70^{\circ}C$ MC3417/18                                                  |                   |                       | -                     | _                     | . —                   | ± 1.0<br>± 1.3        | ± 2.0<br>± 2.8        |      |

| $-55^{\circ}C \le T_{A} \le +125^{\circ}C \text{ mc3517/18}$                                       |                   | _                     | _                     |                       | _                     | ± 2.5                 | ± 2.6<br>± 5.0        |      |

| $I_{GC} = 33.0 \ \mu A, \ V_{CC} = 5.0 \ V$                                                        |                   | _                     | _                     | _                     |                       | - 2.5                 |                       |      |

| $T_A = 25^{\circ}C$                                                                                |                   | _                     | ± 4.0                 | ± 6.0                 | _                     | _                     | ·                     |      |

| $0^{\circ}C \le T_{A} \le +70^{\circ}C$ MC3417/18                                                  |                   | -                     | ± 4.5                 | ± 8.0                 | _                     | -                     | ·                     |      |

| -55°C ≤ T <sub>A</sub> ≤ +125°C MC3517/18                                                          |                   |                       | ± 5.5                 | ± 10                  | _                     | _                     | -                     |      |

| Digital Output Voltage                                                                             | h                 |                       |                       | 1                     |                       |                       | 1 1                   | Vde  |

| $(I_{OL} = 3.6 \text{ mA})$                                                                        | VOL               | - 1                   | 0.1                   | 0.4                   | - 1                   | 0.1                   | 0.4                   |      |

| $(I_{OH} = -0.35 \text{ mA})$                                                                      | VOH               | V <sub>CC</sub> - 1.0 | V <sub>CC</sub> - 0.2 | - 1                   | V <sub>CC</sub> - 1.0 | V <sub>CC</sub> - 0.2 |                       |      |

| Syllabic Filter Applied Voltage (Pin 3)                                                            | VI(Syl)           | +3.2                  |                       | Vcc                   | +3.2                  | -                     | Vcc                   | Vde  |

| (Figure 2)                                                                                         |                   |                       |                       |                       |                       |                       |                       |      |

| Integrating Current (Figure 2)                                                                     | . Hinti           |                       |                       | [                     |                       |                       |                       |      |

| $(I_{GC} = 12.0 \ \mu A)$                                                                          |                   | 8.0                   | 10                    | 12                    | 8.0                   | 10                    | 12                    | μA   |

| (I <sub>GC</sub> = 1.5 mA)                                                                         |                   | 1.45                  | 1.50                  | 1.55                  | 1.45                  | 1.50                  | 1.55                  | mΑ   |

| (I <sub>GC</sub> = 3.0 mA)                                                                         |                   | 2.75                  | 3.0                   | 3.25                  | 2.75                  | 3.0                   | 3.25                  | mA   |

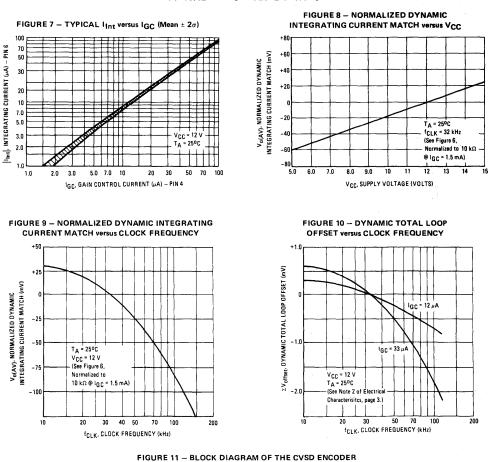

| Dynamic Integrating Current Match                                                                  | VO(Ave)           | -                     | ± 100                 | ± 250                 | -                     | ± 100                 | ± 250                 | m۷   |

| (I <sub>GC</sub> = 1.5 mA) Figure 6                                                                |                   |                       |                       |                       |                       |                       |                       |      |

| nput Current - High Logic State                                                                    | Чн                |                       |                       |                       |                       | 1                     |                       | μA   |

| (V <sub>1H</sub> = 18 V)                                                                           |                   |                       |                       |                       |                       |                       |                       |      |

| Digital Data Input                                                                                 |                   | -                     | -                     | +5.0                  | -                     | -                     | +5.0                  |      |

| Clock Input                                                                                        |                   | -                     | - '                   | +5.0                  | -                     |                       | +5.0                  |      |

| Encode/Decode Input                                                                                |                   | ~~                    |                       | +5.0                  | -                     |                       | +5.0                  | -    |

| nput Current – Low Logic State                                                                     | μL                |                       |                       |                       |                       |                       |                       | μA   |

| $(V_{IL} = 0 V)$                                                                                   |                   |                       |                       | 10                    |                       |                       | 10                    |      |

| Digital Data Input                                                                                 |                   | -                     | -                     | -10                   | -                     | - 1                   | -10                   |      |

| Clock Input<br>Encode/Decode Input                                                                 |                   | -                     | -                     | -360<br>-36           | -                     |                       | -360                  |      |

| Clock Input, VIL = 0.4 V                                                                           |                   |                       | -                     | -36                   | -                     |                       | -36<br>-72            |      |

| Glock input, VIL - 0.4 V                                                                           |                   | I –                   | L                     | -/2                   |                       | L                     | -12                   |      |

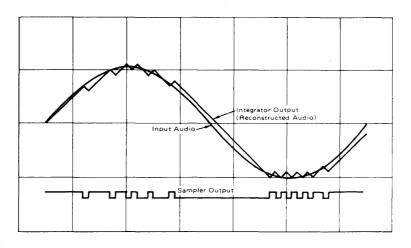

NOTE 2. Dynamic total loop offset (ΣV<sub>offset</sub>) equals V<sub>IO</sub> (comparator) (Figure 3) minus V<sub>IOX</sub> (Figure 5). The input offset voltages of the analog comparator and of the integrator amplifier include the effects of input offset current through the input resistors. The slope polarity switch current mismatch appears as an average voltage across the 10 k integrator resistor. For the MC3417/MC3517, the clock frequency is 16.0 kHz. For the MC3418/MC3518, the clock frequency is 32.0 kHz. Idle channel performance is guaranteed if this dynamic total loop offset is less than one-half of the change in integrator output voltage during one clock cycle (ramp step size). Laser trimming is used to insure good idle channel performance.

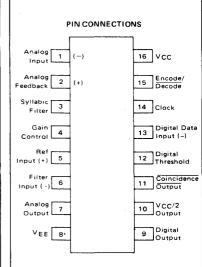

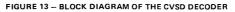

# **DEFINITIONS AND FUNCTION OF PINS**

## Pin 1 - Analog Input

This is the analog comparator inverting input where the voice signal is applied. It may be ac or dc coupled depending on the application. If the voice signal is to be level shifted to the internal reference voltage, then a bias resistor between pins 1 and 10 is used. The resistor is used to establish the reference as the new dc average of the ac coupled signal. The analog comparator was designed for low hysteresis (typically less than 0.1 mV) and high gain (typically 70 dB).

#### Pin 2 — Analog Feedback

This is the non-inverting input to the analog signal comparator within the IC. In an encoder application it should be connected to the analog output of the encoder circuit. This may be pin 7 or a low pass filter output connected to pin 7. In a decode circuit pin 2 is not used and may be tied to  $V_{CC}/2$  on pin 10, ground or left open.

The analog input comparator has bias currents of 1.5  $\mu$ A max, thus the driving impedances of pins 1 and 2 should be equal to avoid disturbing the idle channel characteristics of the encoder.

#### Pin 3 - Syllabic Filter

This is the point at which the syllabic filter voltage is returned to the IC in order to control the integrator step size. It is an NPN input to an op amp. The syllabic filter consists of an RC network between pins 11 and 3. Typical time constant values of 6 ms to 50 ms are used in voice codecs.

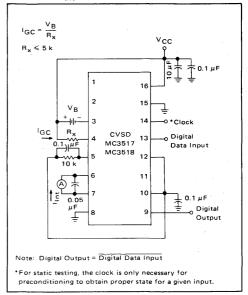

#### Pin 4 – Gain Control Input

The syllabic filter voltage appears across CS of the syllabic filter and is the voltage between V<sub>CC</sub> and pin 3. The active voltage to current (V-1) converter drives pin 4 to the same voltage at a slew rate of typically 0.5 V/ $\mu$ s. Thus the current injected into pin 4 (I<sub>GC</sub>) is the syllabic filter voltage divided by the R<sub>x</sub> resistance. Figure 6 shows the relationship between I<sub>GC</sub> (x-axis) and the integrating current, I<sub>Int</sub> (y-axis). The discrepancy, which is most significant at very low currents, is due to circuitry within the slope polarity switch which enables trimming to a low total loop offset. The R<sub>x</sub> resistor is then varied to adjust the loop gain of the codec, but should be no larger than 5.0 k $\Omega$  to maintain stability.

#### Pin 5 – Reference Input

This pin is the non-inverting input of the integrator amplifier. It is used to reference the dc level of the output signal. In an encoder circuit it must reference the same voltage as pin 1 and is tied to pin 10.

#### Pin 6 - Filter Input

This inverting op amp input is used to connect the integrator external components. The integrating current

$(I_{1nt})$  flows into pin 6 when the analog input (pin 1) is high with respect to the analog feedback (pin 2) in the encode mode or when the digital data input (pin 13) is high in the decode mode. For the opposite states,  $I_{1nt}$  flows out of Pin 6. Single integration systems require a capacitor and resistor between pins 6 and 7. Multipole configurations will have different circuitry. The resistance between pins 6 and 7 should always be between 8 k $\Omega$  and 13 k $\Omega$  to maintain good idle channel characteristics.

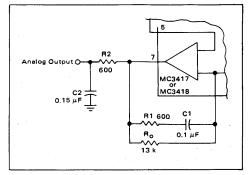

#### Pin 7 – Analog Output

This is the integrator op amp output. It is capable of driving a 600-ohm load referenced to  $V_{CC}/2$  to +6 dBm and can otherwise be treated as an op amp output. Pins 5, 6, and 7 provide full access to the integrator op amp for designing integration filter networks. The slew rate of the internally compensated integrator op amp is typically 0.5 V/ $\mu$ s. Pin 7 output is current limited for both polarities of current flow at typically 30 mA.

#### Pin 8 – VEE

The circuit is designed to work in either single or dual power supply applications. Pin 8 is always connected to the most negative supply.

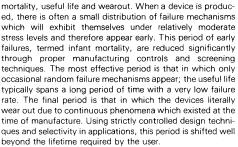

#### Pin 9 – Digital Output