## MOTOROLA INC.

# MECL SYSTEM DESIGN HANDBOOK

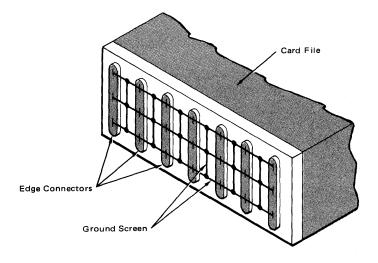

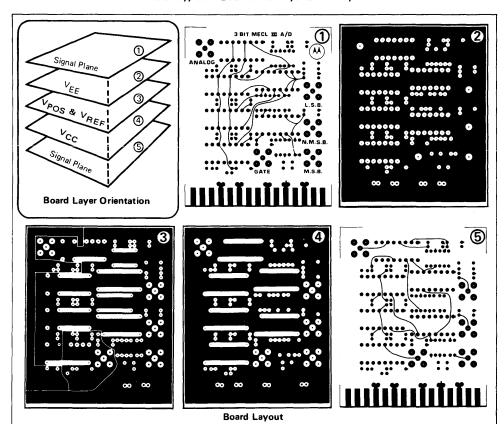

# MECL SYSTEM DESIGN HANDBOOK

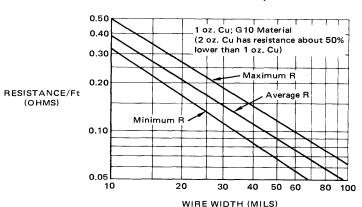

#### Fourth Edition

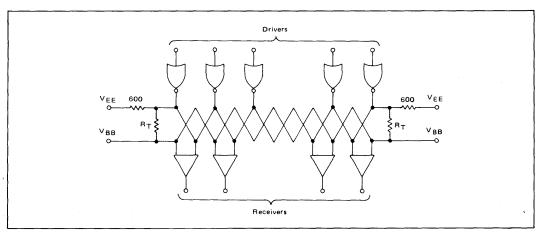

Compiled by the Computer Applications Engineering Department

Author William R. Blood, Jr.

Circuit diagrams external to Motorola products are included as a means of illustrating typical semiconductor applications; consequently, complete information sufficient for construction purposes is not necessarily given. The information in this book has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described any license under the patent rights of Motorola Inc. or others.

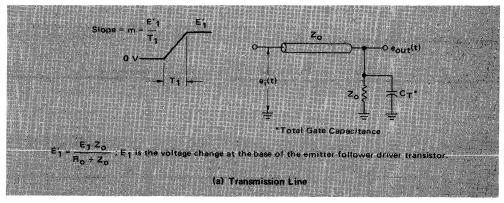

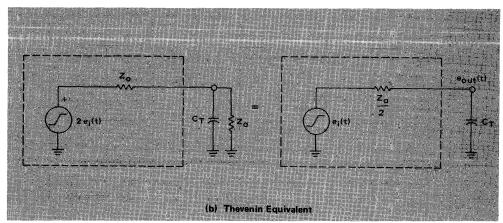

MECL, MECL I, MECL II, MECL III, MECL 10K/10KH, MTTL, MTTL III, Micro T, and MDTL are trademarks of Motorola Inc.

Fourth Edition Second Printing © MOTOROLA INC., 1983 Previous Edition © 1980

#### **PREFACE**

In response to the demand for higher performance systems, engineers are looking at digital integrated circuit families which are faster than the popular TTL types. Motorola's Emitter Coupled Logic (MECL) circuits have the characteristics to meet the performance requirements for present and future systems. MECL 10K/10KH are ideal for computer and communications systems, while state-of-the-art instrumentation equipment uses MECL III and MECL 10KH.

As circuit speeds increase, wiring rules and system design techniques must be adjusted accordingly. Designing with MECL is no more difficult than designing high performance equipment with slower forms of logic. High performance system design for any form of logic, however, does require an understanding of the factors which affect system performance. In fact, many of the MECL features such as transmission line drive capability, complementary outputs, Wired-OR, and versatile logic functions can add as much to system performance as the short propagation delays and high toggle rates.

In the past, several articles and application notes have been written about MECL circuits and systems. However, there was a need for a book which would completely define MECL operation. This book has been written to give the designer the information to establish design rules for his own high performance systems.

The information in this book is based on equations derived from electronic theory, laboratory tests, and inputs from MECL users. All of the rules and tables are for conservative system design with MECL circuits. It is important to realize that the circuits can operate properly under conditions much more adverse than suggested in this book.

In addition to the technical contributors, Jon De Laune, Jerry Prioste and Cary R. Champlin, the author would like to thank Lloyd Maul, Mike Lee, Reg Hamer, Don Murray, Mike Stowe and Tom Balph whose knowledge of MECL has added to the completeness and accuracy of this book. Finally, great appreciation is due to the many technicians, engineers, and managers who took their valuable time to read all or part of this book as it was developed.

### **Table of Contents**

| Introduction vi                                      |          |

|------------------------------------------------------|----------|

| What Is MECL? vi                                     |          |

| History of MECL vi                                   |          |

| Why Use MECL? viii                                   |          |

| The Advantages of MECL ix                            |          |

| MECL Areas of Application ix                         |          |

| Purpose of This Book x                               |          |

| CHAPTER 1 – MECL Families                            | 1        |

| The Basic MECL Gate                                  | 1        |

| Noise Margin                                         | 8        |

| MECL Circuit Types                                   | 10       |

| MECL Flip-Flops                                      | 12       |

| Operation of Flip-Flop                               | 12       |

| MECL Family Comparison                               | 14       |

| •                                                    |          |

| CHAPTER 2 – Using MECL                               | 19       |

| MECL Design Rules                                    |          |

| A. Logic Design Considerations                       | 19       |

| B. System Layout Considerations                      | 25       |

| C. Circuit Board Layout Techniques                   | 26       |

| D. Backplane Wiring                                  | 27       |

| E. System Considerations                             | 28       |

| MECL 10K/10KH Design Rules                           | 29       |

| A. General Considerations                            | 29       |

| B. Printed Circuit Card Layout Techniques            | 29       |

| C. Power Supply Bypassing on Circuit Cards           | 30       |

| D. Backplane and Loading Considerations              | 30       |

| E. System Distribution and Grounding                 | 31       |

| F. Loading Rules for MECL 10K/10KH                   | 32       |

| MECL III Design Rules                                | 35       |

| A. Circuit Card Layout                               |          |

| B. Transmission Line (Microstrip Line)               | 36<br>36 |

| C. On-Card Clock Distribution via Transmission Lines | 37       |

| D. Off-Card Clock Distribution                       | 38       |

| E. Testing MECL III                                  | 38       |

|                                                      | 30       |

| CHAPTER 3 - Printed Circuit Board Connections        | 41       |

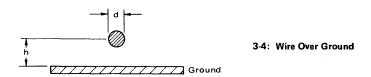

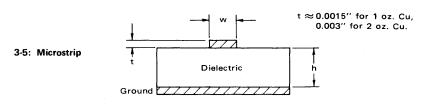

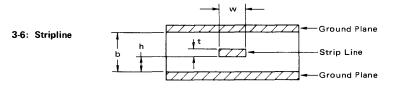

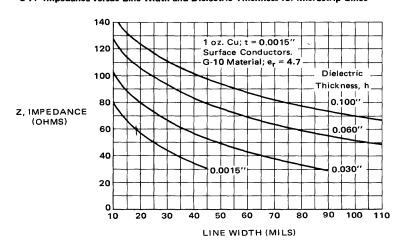

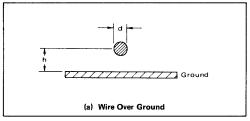

| Transmission Line Geometries                         | 43       |

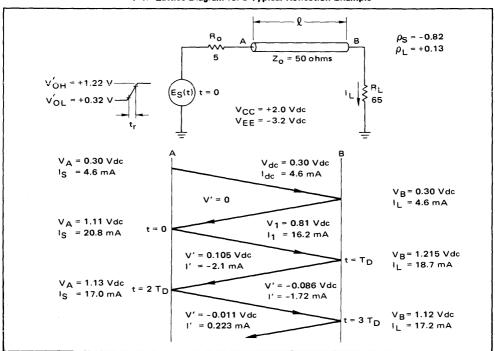

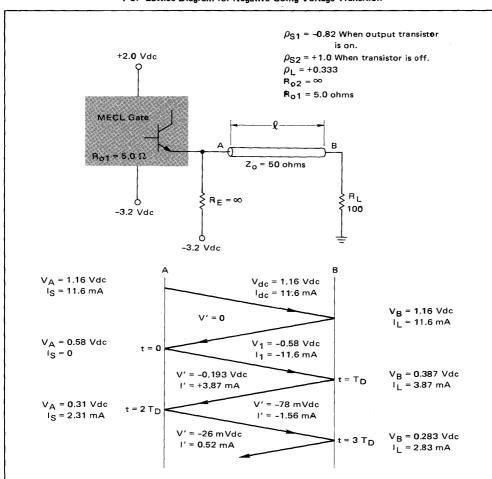

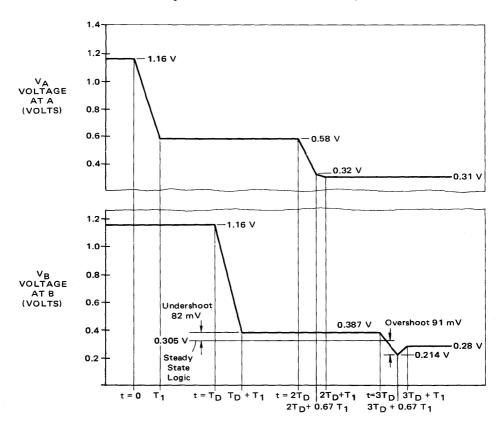

| Basic Transmission Line Operation                    | 48       |

| Unterminated Lines                                   | 49       |

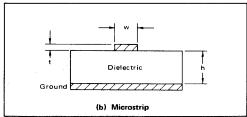

| Series Damped and Series Terminated Lines            | 52       |

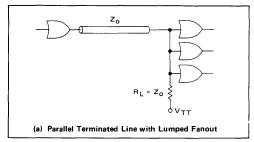

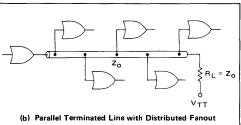

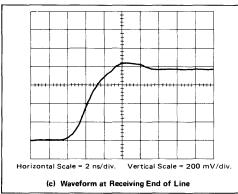

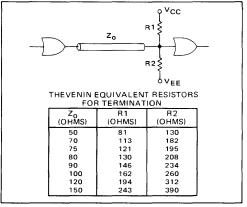

| Parallel Terminated Lines                            | 58       |

| Transmission Line Comparison                         | 59       |

| Wirewrapped Cards                                    | 61       |

| CHAPTER 4 – System Interconnections                  | 63       |

| Connectors                                           | 65       |

| Coaxial Cable                                        | 65       |

| Differential Twisted Pair Lines and Receivers        | 70       |

| Ribbon Cable                                         | 76       |

| Schottky Diode Termination                           | 77       |

| Parallel Wire Cables                                 | 82       |

| Twisted Pair Cable, Driven Single-Ended              | 89       |

| CHAPTER 5 – Power Distribution                                                  | 93         |

|---------------------------------------------------------------------------------|------------|

| System Power Calculations                                                       | 94         |

| Power Supply Considerations                                                     | 97         |

| System Power Distribution                                                       | 98         |

| Backplane Power Distribution                                                    | 101        |

| On-Card Power Distribution                                                      | 102        |

| V <sub>TT</sub> Termination Voltage Distribution                                | 105        |

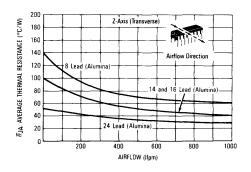

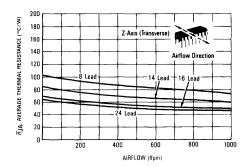

| CHAPTER 6 – Thermal Considerations                                              | 107        |

| MECL Integrated Circuit Heat Transfer                                           | 108        |

| MECL DC Thermal Characteristics                                                 | 112        |

| Heat Dissipation Techniques                                                     | 116        |

| Mounting Techniques                                                             | 120        |

| CHAPTER 7 — Transmission Line Theory                                            |            |

| Transmission Line Design Information, With Examples                             | 121        |

| Signal Propagation Delay for Microstrip and Strip Lines With                    | 121        |

| Distributed or Lumped Loads                                                     | 129        |

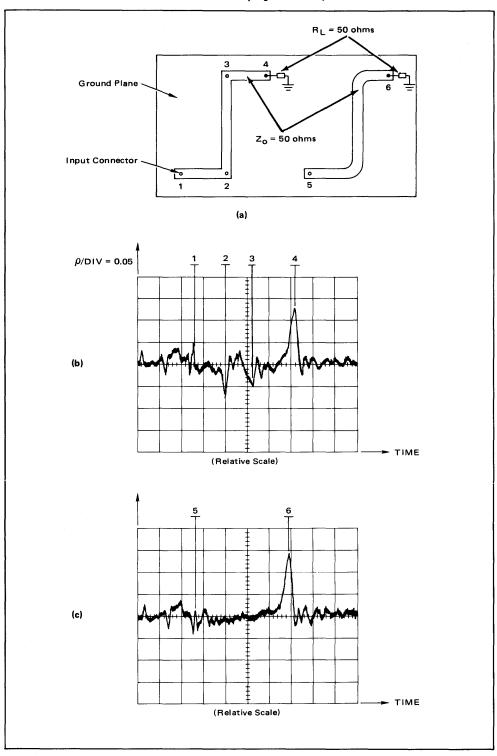

| Microstrip Transmission Line Techniques, Evaluated Using TDR                    | .27        |

| Measurements, With Examples                                                     | 132        |

| The Effect of Loading on a Parallel Terminated Transmission Line,               |            |

| With Examples                                                                   | 145        |

| Analysis: Series Terminated Lines Compared to Parallel Terminated               | 150        |

| Lines, With Example                                                             | 152<br>159 |

| Bibliography                                                                    | 172        |

|                                                                                 | 1/2        |

| CHAPTER 8 – MECL Applications                                                   | 173        |

| Interconnection Techniques                                                      | 173        |

| AC Noise Immunity of MECL 10K                                                   | 195        |

| Testing MECL 10K/10KH Logic Circuits                                            | 201        |

| Interfacing with MECL 10K/10KH                                                  | 207        |

| Bussing with MECL 10K/10KH                                                      | 216        |

| IC Crystal Controlled Oscillators                                               | 224        |

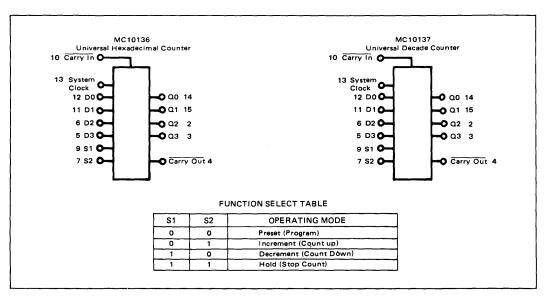

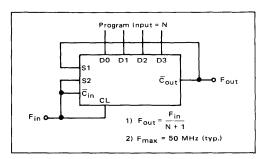

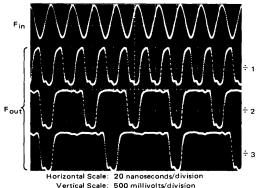

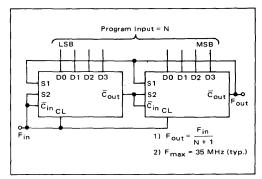

| Programmable Counters Using the MC10136 and MC10137 MECL 10K Universal Counters | 229        |

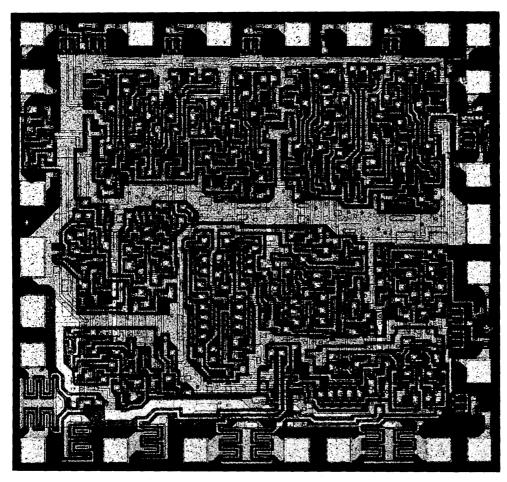

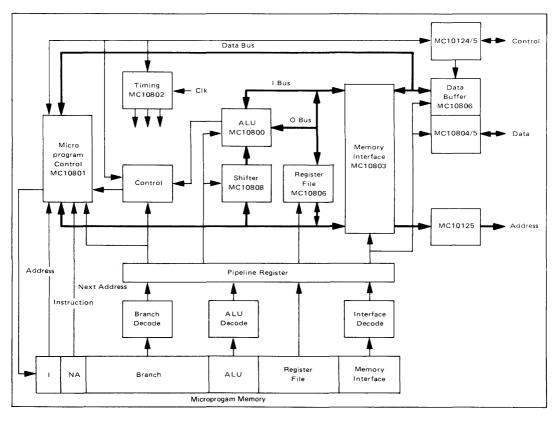

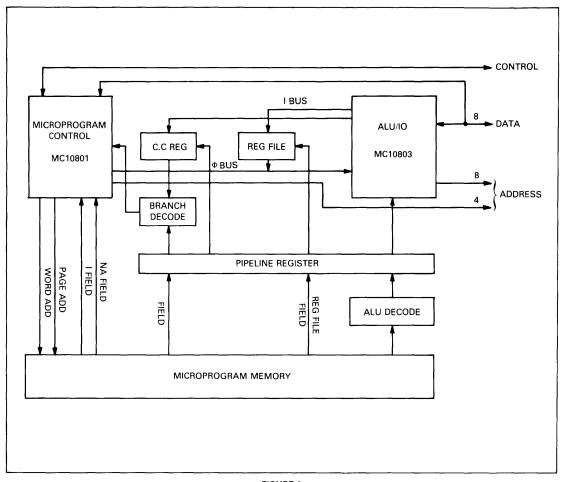

| MC10800 MECL LSI Circuits are Designed for                                      | 22)        |

| High-Performance Microprogrammed Processors                                     | 233        |

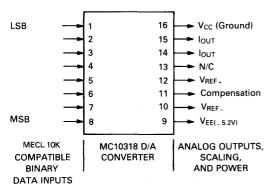

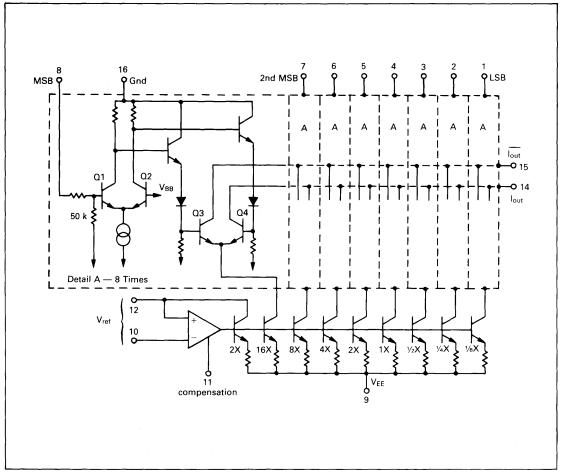

| High-Resolution Waveforms Result when a                                         |            |

| Very High-Speed D/A Converter gets Driven by a                                  | 244        |

| Microprogrammed ECL Processor                                                   |            |

| Array-Based Logic Boosts System Performance                                     |            |

| APPENDIX I – MECL Hardware                                                      | 255        |

| Index of Tabulated Data                                                         | 258        |

#### Introduction

#### What is MECL?

The term MECL identifies Motorola's emitter coupled logic. Emitter coupled logic is a non-saturating form of digital logic which eliminates transistor storage time as a speed limiting characteristic, permitting very high speed operation. "Emitter Coupled" refers to the manner in which the emitters of a differential amplifier within the integrated circuit are connected. The differential amplifier provides high impedance inputs and voltage gain within the circuit. Emitter follower outputs restore the logic levels and provide low output impedance for good line driving and high fanout capability.

#### **History of MECL**

Motorola has offered MECL circuits in five logic families: MECL I, MECL II, MECL III, MECL 10,000 (MECL 10K), and MECL 10H000 (MECL 10KH).

The MECL I family was the first digital monolithic integrated circuit line produced by Motorola. Introduced in 1962, MECL I was considerably beyond the state-of-the-art at that time. Several years passed before any other form of logic could equal the 8 ns gate propagation delays and 30 MHz toggle rates of MECL I. As a result of its reliability and performance, MECL I was designed into many advanced systems.

In 1977 MECL I was phased out of production. Features of the more advanced MECL III and 10K favor their being used in new designs. For example, MECL I required a separate bias driver package to be connected to each logic function. This means increased package count and extra circuit board wiring. Also the 10-pin packages used for MECL I limit the number of gates per package and the number of gate inputs. No provision was made for operation of MECL I with transmission lines, as they were unnecessary with the 8 ns rise and fall times.

In 1966 Motorola introduced the more advanced MECL II. The basic gate featured 4 ns propagation delays and flip-flop circuits that would toggle at over 70 MHz. MECL II immediately set a new standard for performance that has been equaled by non-ECL logic only with the introduction of Schottky TTL in 1970.

Motorola continued with the development of MECL II and flip-flop speeds were increased first to 120 MHz for the JK circuit, and then to 180 MHz for the type D flip-flop. To drive these high speed flip-flops, high speed line drivers were introduced with 2 ns propagation delays and 2 ns rise and fall times. With 2 ns edges, transmission lines could be used to preserve the waveforms and limit overshoot and

ringing on longer lines. Consequently, a part was designed to drive 50-ohm lines. Because of the significant speed increase of the line drivers and high speed flip-flops over the basic MECL II parts, these circuits are commonly called MECL II-1/2, although they are part of the MECL II family.

MECL II circuits have a temperature compensated bias driver internal to the circuits (except for the line receiver which requires no internal bias). The internal bias source simplifies circuit interconnections and tracks with both temperature and supply voltage to retain noise margin under varied operating conditions.

Complex functions became available in MECL II when trends shifted toward more complicated circuits. The family had adders, data selectors, multiplexers, decoders and a Nixie\* tube decoder/driver. MECL II was discontinued in 1979 superseded by MECL III, MECL 10K and MECL 10KH.

Motorola's continuing development of ECL made possible an even faster logic family. As a result, MECL III was introduced in 1968. Its 1 ns gate propagation delays and greater than 500 MHz flip-flop toggle rates remain the industry leaders. The 1 ns rise and fall times require a transmission line environment for all but the smallest systems. For this reason, all circuit outputs are designed to drive transmission lines and all output logic levels are specified when driving 50-ohm loads. Because of MECL III's fast edge speeds, multi-layer boards are recommended above 200 MHz. For the first time with MECL, internal input pulldown resistors are included with the circuits to eliminate the need to tie unused inputs to VEE. The Hi-Z 50 k $\Omega$  input resistors are used with transmission lines for most applications. MECL III's popularity is with high speed test and communications equipment.

Trends in large high speed systems showed the need for an easy to use logic family with 2 ns propagation delays. To fill this requirement, Motorola introduced the MECL 10K series in 1971. In order to make the circuits comparatively easy to use, edge speed was slowed to 3.5 ns (10%-90%) while the important propagation delay was held to 2.0 ns. The slow edge speed permits use of wire wrap and standard printed circuit lines. However, the circuits are specified to drive transmission lines for optimum performance.

Because of technological advances in processing as well as market demands for even higher performance devices, Motorola introduced its newest high-speed ECL family, MECL 10KH in 1981. This family provides propagation delays of 1 ns with edge speeds slowed to 1.8 ns (10-90%). These speeds, which are attained with no increase in power over MECL 10K, are due to both advanced circuit design techniques and Motorola's new oxide isolated process called MOSAIC (Motorola Oxide Self Alligned Implanted Circuits). This process allows smaller device geometries, improved fTs (greater bandwidth) and reduced paracitic capacitances.

To enhance existing systems, many of the MECL 10KH devices are pinout/ functional duplications of the MECL 10K family. Also, MECL 10K/10KH are provided with logic levels that are completely compatible with MECL III and the MECL Macrocell Arrays to facilitate using all families in the same system. Another important feature of MECL10K/10KH is the significant power reduction over both MECL III and the older MECL II. Also, because of this low gate power and advanced circuit design techniques, the MECL 10KH family has many new functions not available by the other families. Although MECL 10K continues to be the most widely used ECL family in the industry, MECL 10KH is setting new standards in speed and power.

<sup>\*</sup>T.M. – Burroughs Corp.

#### Why Use MECL?

Circuit speed is, of course an obvious reason for designing with MECL. MECL 10K/10KH offer shorter propagation delays and higher toggle rates than any non-ECL type of logic. Equally important to the circuit speed are the characteristics of MECL circuits which permit entire systems to operate at high speeds.

The ability of the faster MECL families to drive transmission lines becomes increasingly important in larger and faster systems. While a transmission line environment imposes some additional design rules and restrictions, the advantages of longer signal paths, better fanout, improved noise immunity, and faster operation, often more than compensate for the restrictions.

When using MECL 10K/10KH without transmission lines, the high input impedances permit the use of series-damping resistors to increase wiring lengths and to improve waveforms. Unlike non-ECL forms of logic, MECL circuits have constant power supply requirements, independent of operating frequency. This simplifies power supply design, since circuit speed need not be considered a variable. At fast circuit speeds MECL can offer a considerable power saving over the other types of logic.

In addition to faster operation, the line driving features of MECL circuits can be exploited to improve system performance. For one, the parts specified to drive transmission lines will drive coaxial cables over distances limited only by the bandwidth of the cable. In addition, the shielding in coaxial cable gives good isolation from external noise.

More economical than using coaxial cable, is the ability of the MECL circuits to differentially drive and receive signals on twisted pair lines. Using this technique, signals have been sent over twisted pair lines up to 1000 feet in length.

The complementary outputs and Wired-OR capabilities of MECL circuits result in faster system operation with reduced package count and a power saving. The complementary outputs are inherent in the circuit design and both outputs have equal propagation delay. This eliminates the timing problems associated with using an inverter to get a complement signal. The logic OR function is obtained by wiring circuit-outputs together. The propagation delay of the Wired-OR connection is much less than a gate function and can save power, as only one pulldown resistor or termination is required per Wired-OR.

Another advantage when designing with MECL is the low noise generated by the circuits. Unlike totem pole outputs, the emitter follower does not generate a large current spike when switching logic states, so the power lines stay comparatively noise free. The low current-switching in signal paths, relatively small voltage swing (typically 800 mV), and low output impedances, cut down crosstalk and noise.

Generated noise is also reduced by MECL's relatively slow rise and fall times. For each MECL family the edge speed is equal to or greater than the propagation delay. The low noise associated with MECL is especially important when the logic circuits are to be used in a system which contains low level analog or communications signals.

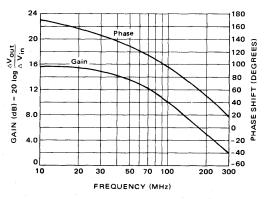

The flexibility of the MECL line receivers and Schmitt triggers to act as linear amplifiers leads to many functions that may be performed with standard MECL circuits. For example, in addition to amplifying low level signals to MECL levels, these MECL circuits can be used as crystal oscillators, zero crossing detectors, power buffers, Schmitt triggers, RF and video amplifiers, one-shot multivibrators, etc.

#### The Advantages of MECL

- 1. Highest speed IC logic available

- 2. Low cost

- 3. Low output impedance

- 4. High fanout capability

- 5. Constant supply current as a function of frequency or logic state

- 6. Very low noise generation

- 7. Complementary logic outputs save on package count

- 8. Low crosstalk between signal leads

- 9. All outputs are buffered

- 10. Outputs can be tied together giving the Implied-OR function

- 11. Common mode rejection of noise and supply variations is 1 V or greater for differential line receiving

- 12. Bias supplies are internal, allowing MECL use with a single power supply

- 13. Minimal degradation of parameters occurs with temperature variations

- 14. Large family of devices yields economical designs

- 15. Power dissipation can be reduced through use of Implied-OR and the "Series Gating" technique

- 16. Easy data transmission over long distances by using the balanced twisted pair technique with standard parts

- 17. Constant noise immunity versus temperature

- 18. Best speed-power product available

- 19. All positive logic functions are available

- 20. Adapts easily to MSI and LSI techniques

#### **MECL Areas of Application**

- 1. Instrumentation

- 2. High speed counters

- 3. Computers

- 4. Medical electronics

- 5. Military systems

- 6. Large real-time computers

- 7. Aerospace and communication satellite systems

- 8. Ground support system

- 9. High speed A/D conversion

- 10. Digital communication systems

- 11. Data transmission (twisted pair)

- 12. Frequency synthesizers

- 13. Phase array radar

- 14. High speed memories

- 15. Data delay lines

#### Purpose of This Book

Rules and guidelines for using the various MECL families comprise the subject matter of this book. Because of edge speed and bit rate capabilities, each family has differing system requirements. The family name will therefore be referenced for the examples and figures in the text, whenever applicable. The information in this book is meant to apply to MECL III and MECL 10K/10KH. The information about MECL 10K/10KH will also apply to the M10800 LSI processor family. This book aims at giving the reader an understanding of the MECL families, as well as the knowledge needed to confidently design with and use MECL.

Chapter 1 discusses the operation of MECL circuits and the characteristics of the various families. It also shows methods for internally connecting the basic gates to provide efficient complex functions. Of more importance to the user is Chapter 2 — a list of rules providing a condensed reference for using the various MECL families.

Chapters 3, 4, 5, and 6 elaborate on those rules giving a technical background for good system design and presenting test results showing MECL circuits in various modes of operation. Chapter 3 describes circuit-to-circuit interconnections on a card. Both open wire and transmission line techniques are covered. Chapter 4 expands the wiring techniques to show methods for card-to-card and panel-to-panel interconnections. Chapter 5 elaborates on power distribution, showing how voltage drops and power line noise affect noise immunity. Chapter 6 discusses thermal considerations. Attention is given to the problems of calculating chip temperature, removing heat from the system, and to the effect of thermal differences on noise immunity.

Chapter 7 provides background necessary for understanding transmission lines as they apply to MECL. Derivations of equations are shown, along with test results correlating with the theoretical analysis. This chapter should be especially useful when selecting a transmission line impedance and when determining the effect of fanout or stray capacitance on the line.

Chapter 8 contains application ideas for MECL circuits. Included are methods for interfacing various logic families with MECL, and numerous useful circuits designed with MECL for high performance.

Finally, a brief appendix illustrates some of the peripheral hardware and components of use in MECL Systems.

#### The Basic MECL Gate

An understanding of the basic circuits used in the construction of a logic family is important in order to successfully design and trouble-shoot a system which uses the family. This chapter describes MECL circuits, compares MECL families, and gives some suggested rules for using MECL circuits in system design.

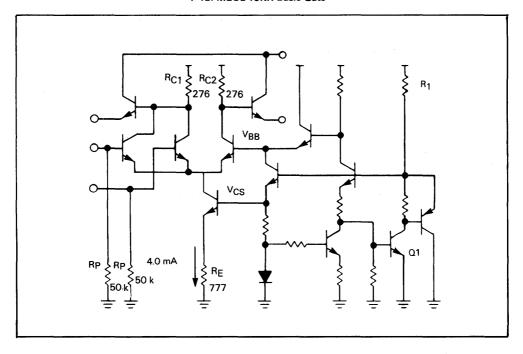

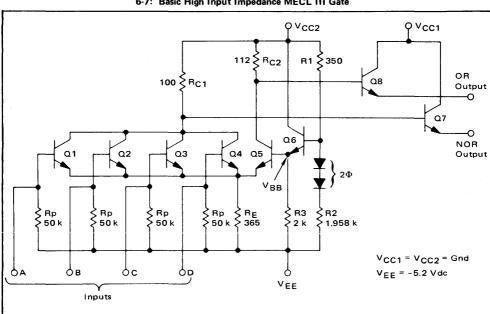

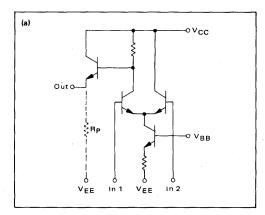

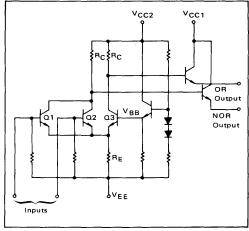

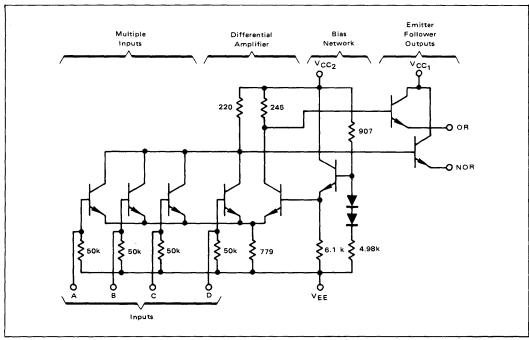

Figure 1-1a shows a typical MECL 10K gate, — the basic gate circuit for the MECL 10K family. The figure shows the separate functional circuits within the gate.

The differential amplifier section contains the current steering element that provides the actual logic gating of the circuit. It also provides the voltage gain necessary for a narrow linear threshold region.

Internal Temperature and Voltage Emitter Compensated Follower Differential Input Amplifier Bias Network Outputs V<sub>CC2</sub> V<sub>CC1</sub> R<sub>C2</sub> \$ 245 907 RC1 \$ 217 Q8 OR IВ Output NOR Q6 Output  $V_{BB}$ **Q4** QЗ 1E I RE RP Rρ Rp Rρ 6.1 k 4.98 k 50 k 50 k 50 k 50 k В С D Inputs

1-1a: MECL 10K Basic Gate

#### 1-1b: MECL 10KH Basic Gate

An internal temperature and voltage compensated bias driver supplies a reference voltage for the differential amplifier. The bias voltage, VBB, is set at the midpoint of the signal logic swing. With the recommended – 5.2 volts supply voltage and 25°C ambient temperature, VBB is - 1.29 volts dc for either MECL 10K/10KH or MECL III. The diodes in the voltage divider line, together with Q6, provide temperature compensation by maintaining a level consistent with the midpoint of the logic levels despite changing temperatures.

One additional feature of the bias supply is its ability to track supply voltage changes. Consequently MECL 10K gates, for example, are specified to operate from a - 5.2 volt  $\pm$  10% supply. In fact, they are capable of working over a much wider range (- 3.0 to - 8.0 volts) although ac performance would be degraded.

A typical MECL 10KH gate can be seen in Fig. 1-1b. This figure shows that both the bias regulator and the emitter resistor source of the MECL 10K gate has been replaced by a voltage regulator and a constant current source, respectively, in the MECL 10KH gate.

The new voltage regulator controls both variations in the output voltage as well as the AC characteristics of the devices. The constant current source allows the use of matched collector resistors which produces better matched delays, matched output tracking rates with temperature and less variation in the output voltage level with changes in the power supply. There is also a considerable improvement in noise margins over MECL 10K. MECL 10KH is specified to operate from a - 5.2 volt ± 5% power supply.

The emitter followers are output drivers. They provide level shifting from the differential amplifier to MECL output levels, and provide a low output impedance for driving transmission lines. MECL 10K/10KH and MECL III circuits use open emitter outputs. The reason is that since these circuits are designed for use with transmission lines, and since the line termination provides an output load, internal pulldown resistors would be a waste of power.

MECL 10K/10KH and MECL III circuit families, designed to drive transmission lines, have two  $V_{CC}$  power voltage inputs.  $V_{CC1}$  is used to supply current to the output drivers, while  $V_{CC2}$  supplies the remainder of the circuit. Separate  $V_{CC}$  lines are used to eliminate crosstalk between circuits in a package. More important, the use of two lines speeds up circuit performance by eliminating a voltage spike which otherwise would occur on the bias voltage,  $V_{BB}$ , caused by the relatively heavy currents associated with transmission lines. Each  $V_{CC}$  pin should be connected to the system ground by as short a path as possible (all  $V_{CC}$  pins are connected to the same system ground).

The input pulldown resistors shown in Figure 1-1a and b are characteristic of MECL 10K/10KH and MECL III. MECL 10K/10KH and MECL III use  $50~k~\Omega$  resistors to drain off the input transistor leakage current. These resistors hold unused inputs at a fixed zero level, so unused inputs are left open.

#### **MECL Logic Levels**

The following calculations illustrate the current switching operation of a MECL 10K gate. Similar calculations may be performed for the other MECL families by substituting appropriate resistor values and voltage levels.

When all gate inputs are at a voltage,  $V_{in}$ , equal to a logic  $\emptyset$  level,  $|V_{IL} \min| \ge V_{in}| \ge V_{IL}$  max|, the input transistors Q1 through Q4 in Figure 1-1a will not be conducting current, because the commn emitter point of these four transistors is at about -2.09 V: i.e.,  $V_{BB} + V_{BEQ5} \approx -1.29 \text{ V} + (-0.80 \text{ V})$ . This is not enough forward bias (base to emitter) on Q1 through Q4 for conduction. Thus, current flows through  $R_{C2}$ , Q5, and  $R_{E}$ . This current,  $I_{E0}$ , is:

$$I_{E}\emptyset = \frac{V_{EE} - (V_{BB} + V_{BE})}{R_E} \approx -4.0 \text{ mA}.$$

The voltage drop at the collector resistor. RC2, may be calculated as:

$$V_{RC2} = I_{E0}R_{C2} + I_{B}R_{C2} \approx (-4.0 \text{ mA}) \cdot (245 \Omega) = -0.98V.$$

The output transistor base current, IB, is small compared to the switch current, so the second term above can be ignored.

The OR output is then obtained through an emitter-follower, Q8, which cuts the output level by one base-emitter drop, giving a voltage level:

$$V_{OL\ OR} = V_{RC2} + V_{BE}$$

where: VBE = base to emitter drop on Q8, with logic zero current level (i.e., 6 mA thru Q8).

So:

$$V_{OL OR} \approx -0.98 \text{ V} + (-0.77 \text{ V}) \approx -1.75 \text{ V},$$

typical at  $T_A = 25^{\circ}C$ .

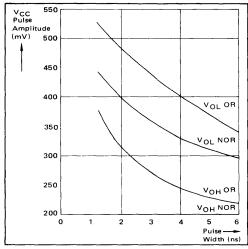

The base of the NOR output emitter-follower, Q7, is at about -0.05 V, yielding an output of -0.89 V typical, at an output device current level of 22.5 mA and T<sub>A</sub> = 25°C. (These output voltage and current levels assume 50-ohm loads to a terminating voltage, V<sub>TT</sub>, of -2.0 V).

If one or more of the gate inputs is switched to a voltage level,  $V_{in}$ , equal to a nominal logic 1 level,  $|V_{IH \ min}| \ge |V_{in}| \ge |V_{IH \ max}|$ , a current  $I_{E1}$  flows through  $R_{C1}$ , Q1-Q4, and  $R_E$ . This current is:

$$I_{E1} = \frac{V_{EE} - (V_{in} + V_{BE})}{R_{E}} \approx -4.51 \text{ mA},$$

where:  $V_{in} = -0.89 \text{ V}$

$V_{BE} = -0.80 \text{ V}$

The current flow through  $R_{C1}$  produces a voltage at the collector nodes of Q1 through Q4:

$$V_{RC1} \approx I_{E1}R_{C1} = (-4.51 \text{ mA}) \cdot (217 \Omega) \approx -0.98 \text{ V}.$$

Finally, the output is obtained through an emitter follower, Q7, which drops the collector voltage level one base-emitter drop, so that:

$$V_{OL\ NOR} = V_{RC1} + V_{BE}$$

(output device at 6 mA)

$\approx -0.98 \text{ V} + (-0.77 \text{ V}) = -1.75 \text{ V},$

typical at  $T_A = 25^{\circ}C$ .

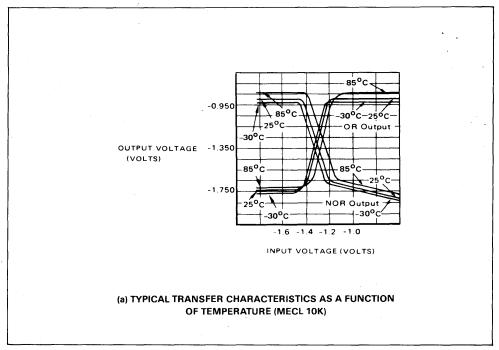

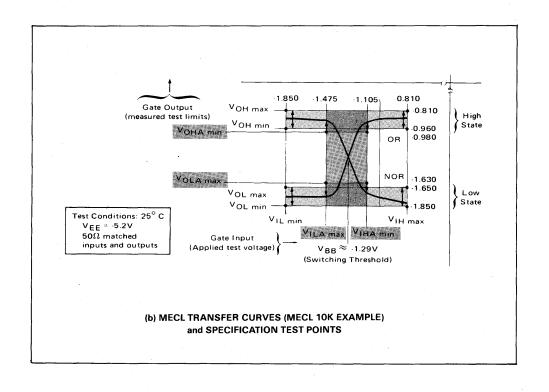

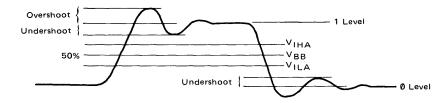

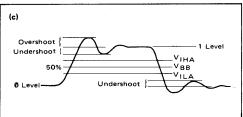

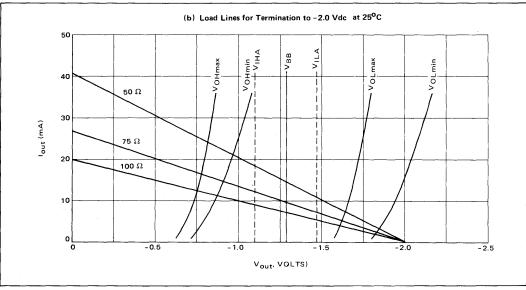

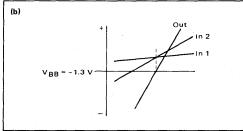

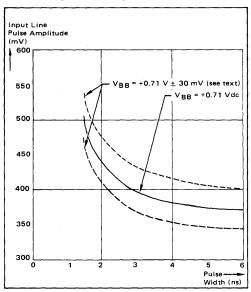

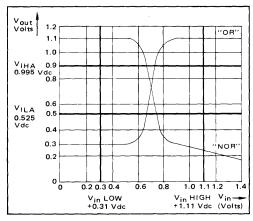

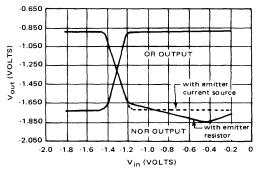

The transfer curves in Figures 1-2(a) and (b) indicate the behavior of the MECL 10K gate while switching. Note from the data in Figure 1-3 and from the NOR transfer characteristic: for  $V_{in}$  increasing from  $V_{IL}$  min to  $V_{ILA}$  max, the output remains at a high level. When  $V_{in}$  increases from  $V_{ILA}$  max to  $V_{IHA}$  min, the NOR output will switch to a low level. Then, as the input continues more positive than  $V_{IHA}$  min, the output continues more negative with a slope of about -0.24. This is caused by the collector input node going more negative because of increasing collector current as  $V_{in}$  goes more positive.

If the input continues in the positive direction, saturation will be reached at an input of about -0.4 volts. Beyond that point, the base-collector junction is forward biased to saturation and the collector voltage and output will go more positive with the increasing input level. Since the saturation point is well above  $V_{OH\ max}$ , operation in this mode will not occur in normal system operation. The OR output level depends on Q5's collector voltage (cf Fig. 1-1a). This output is unaffected by input levels except in the active transfer region.

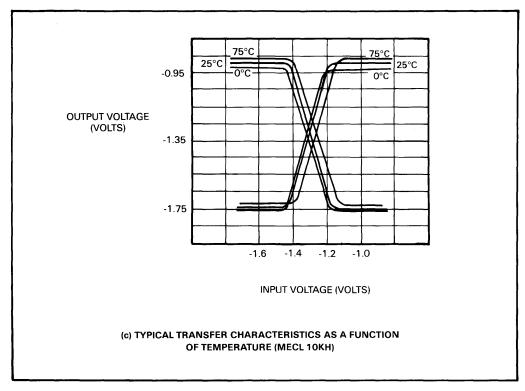

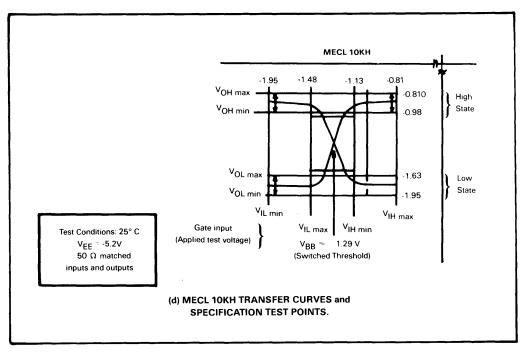

Fig. 1-2 (c) and (d) demonstrates the switching behavior of MECL 10KH and Fig. 1-3 (c) lists the DC test parameters for 10KH. As can be seen in Fig 1-2 (d) the NOR output stays level after V<sub>in</sub> reaches V<sub>IH</sub> min as opposed to MECL 10K which slopes downward.

#### 1-2; MECL 10K Transfer Characteristic and Specification Points

1-2: MECL 10KH Transfer Characteristics Specification Points

| Forcing<br>Function | Parameter         | -55°C①                         | -30°c②                        | 0°C@              | <sub>25°C</sub> ②                         | 25°C①                          | <sub>75</sub> °c③ | 85°c②                         | 125°C①                         | Unit |

|---------------------|-------------------|--------------------------------|-------------------------------|-------------------|-------------------------------------------|--------------------------------|-------------------|-------------------------------|--------------------------------|------|

|                     |                   | MC10500<br>MC10600<br>MCM10500 | MC10100<br>MC10200<br>MC10800 | MCM10100          | MC10100<br>MC10200<br>MC10800<br>MCM10100 | MC10500<br>MC10600<br>MCM10500 | MCM10100          | MC10100<br>MC10200<br>MC10800 | MC10500<br>MC10600<br>MCM10500 |      |

| V <sub>IHmax</sub>  | VOHmax<br>VOHmin  | -0.880<br>-1.080               | -0.890<br>-1.060              | -0.840<br>-1.000  | -0.810<br>-0.960                          | -0.780<br>-0.930               | -0.720<br>-0.900  | ~0.700<br>~0.890              | -0.630<br>-0.825               | Vdc  |

| VIHAmin             | VOHAmin           | -1.100<br>-1.255#              | -1.080<br>-1.205              | -1.020<br>-1.145# | -0.980<br>-1.105                          | -0.950<br>-1.105               | -0.920<br>-1.045  | -0.910<br>-1.035              | -0.845<br>-1.000               | Vdc  |

| VILAmax             | VOLAmax           | -1.510<br>-1.635               | -1.500<br>-1.655              | -1.490<br>-1.645  | -1.475<br>-1.630                          | -1.475<br>-1.600               | -1.450<br>-1.605  | -1.440<br>-1.595              | -1.400<br>-1.525               | Vdc  |

| V <sub>ILmin</sub>  | VOLmax<br>VOLmin@ | -1.655<br>-1.920               | 1.675<br>1.890                | -1.665<br>-1.870  | -1.650<br>-1.850                          | -1.620<br>-1.850               | -1.625<br>-1.830  | -1.615<br>-1.825              | -1.545<br>-1.820               | Vdc  |

| VILmin              | INLmin            | 0.5                            | 0.5                           | 0.5               | 0.5                                       | 0.5                            | 0.3               | 0.3                           | 0.3                            | μА   |

NOTES: 1)MC10500, MC10600, and MCM10500 series specified driving 100  $\Omega$  to –2.0 V.

(3) MC10100, MC10200, MC10800 and MCM10100 series specified driving 50  $\Omega$  to -2.0 V. (3) Memories (MCM10100) specified 0-75°C for commercial temperature range, 50  $\Omega$  to -2.0 V. Military temperature range memories (MCM10500) specified per Note 1.

(4) Special circuits such as MC10123, and MC10800 family bus outputs have lower than normal

V<sub>OLmin</sub>. See individual data sheets for specific values.

#The MCM10149 specified V  $_{IHA}$  min @ -55°C to be -1.175 V and @ 0°C to be -1.130 V

Each MECL 10K series device as been designed to meet the dc specifications shown in the test table, after thermal equilibrium has been established. The circuits is in a test socket or mounted on a printed circuit board and transverse airflow greater than 500 linear fpm is maintained.  $V_{EE} = -5.2V \pm 0.010 V$ .

#### (a) MECL 10K DC TEST PARAMETERS

| Forcing<br>Function | Parameter | -30°C  | 25°C   | 85°C   | Unit |

|---------------------|-----------|--------|--------|--------|------|

| V <sub>IHmax</sub>  | VOHmax    | -0.875 | -0.810 | -0.700 | Vdc  |

|                     | VOHmin    | -1.045 | -0.960 | -0.890 |      |

|                     | VOHAmin   | -1.065 | -0.980 | -0.910 | Vdc  |

| VIHAmin             |           | -1.180 | -1.095 | -1.025 |      |

| VILAmax             |           | -1.515 | -1.485 | -1.440 | Vdc  |

|                     | VOLAmax   | -1.630 | -1.600 | -1.555 |      |

|                     | VOLmax    | -1.650 | -1.620 | -1.575 | Vdc  |

| V <sub>ILmin</sub>  | VOLmin    | -1.890 | -1.850 | -1.830 |      |

| V <sub>ILmin</sub>  | INLmin    | 0.5    | 0.5    | 0.3    | μА   |

NOTE: All outputs loaded 50 Ω to -2.0 Vdc except MC1648 which has an internal output pulldown resistor.

#### **ELECTRICAL CHARACTERISTICS**

Each MECL III series device has been designed to meet the dc specification shown in the test table, after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and transverse airflow greater than 500 linear fpm is maintained.  $V_{EE} = -5.2 \text{ V} \pm 0.10 \text{ V}$ .

(b) MECL III DC TEST PARAMETERS

1-3 (continued) (C) MECL 10KH DC TEST PARAMETERS

| Forcing<br>Function | Parameter                                  | 0°C            | 25°C           | 75°C           | Unit |

|---------------------|--------------------------------------------|----------------|----------------|----------------|------|

| V <sub>IH max</sub> | V <sub>OH max</sub>                        | -0.84<br>-1.02 | 81<br>98       | 735<br>92      | Vdc  |

| V <sub>IL min</sub> | V <sub>OL max</sub><br>V <sub>OL min</sub> | -1.63<br>-1.95 | -1.63<br>-1.95 | -1.60<br>-1.95 | Vdc  |

| V <sub>IL min</sub> | I <sub>INL min</sub>                       | 0.5            | 0.5            | 0.3            | μА   |

Suffice it to say that while the manufacture of MECL circuits is not a primary concern of the user, nevertheless ease of manufacture does translate directly into end product cost. Although not as easy to build as some slower logic families because of smaller transistor geometries, MECL does have some features which facilitate processing. First, the voltage gain of the basic gate circuit (approximately 4.0 for MECL 10K) is essentially independent of transistor beta. So transistor beta can be allowed to vary from a low of about 70 in high speed MECL to a high in excess of 300, which permits easy processing limits. Second, the output voltage levels depend on diode drops for a high output, and diode drops and resistor ratios for a low output. Resistance ratios can be held to within  $\pm 5\%$  even though absolute values vary by  $\pm 20\%$ . Again, this eases processing.

Third, since the transistors used do not saturate, the gold doping which is commonly required to decrease storage time is not required in MECL processing; therefore yields are better. Fourth, collector-emitter voltages are low, due to circuit design, again relaxing processing restrictions. Such advantages, together with Motorola's ability to control processing, permit high volume production of all MECL circuits. In effect, this means low-cost high performance circuits for the designer.

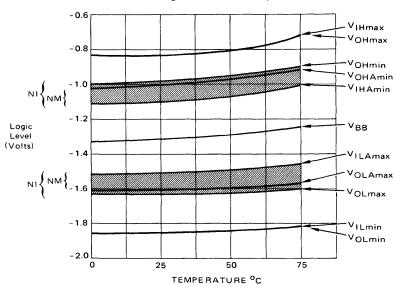

#### Noise Margin

#### MECL 10K and MECL III

Noise margin is a dc voltage specification which measures the immunity of a circuit to adverse operating conditions. Noise margin is defined as the difference between the worse case input logic level (VIHA min or VILA max) and the guaranteed worst case output (VOHA min or VOLA max) for those inputs. Figure 1-3 lists the worst case limits for MECL 10K/10KH and MECL III.

High level noise margin is obtained by subtracting (VIHA min) from (VOHA min); similarly, low level noise margin is (VILA max) minus (VOLA max). Worst-case noise margin is guaranteed to be at least 0.125 volts for MECL 10K and 0.115 volts for MECL III in dual in-line packages. Using typical output voltage levels for MECL circuits, noise margins are usually better than guaranteed — by about 75 millivolts.

#### MECL 10KH

The MECL 10KH family has only one set of output voltages (V<sub>OH</sub> and V<sub>OL</sub>) with minimum and maximum values specified. The minimum value of V<sub>OH</sub> and the maximum value of V<sub>OL</sub> of the MECL 10KH family is synonomous with the V<sub>OHA</sub> and V<sub>OLA</sub> specifications of the MECL 10K family.

The VOH values for the MECL 10KH circuits are equal to or better than the MECL 10K levels at all temperatures. Input voltages (VIH min and VIL max for MECL 10KH,

which are synonomous with V<sub>IHA</sub> and V<sub>ILA</sub> of MECL 10K) are also improved. These improvements have resulted in a "1" level noise margin equal to the "0" level noise margin of 150 mV. The reduction in operating temperature range for MECL 10KH and the improvement in tracking rate allow for a lower V<sub>OL</sub> level for MECL 10KH (-1950 m V instead of -1850 m V for MECL 10K). The change in this level does not affect system noise margins. Although some of the interface levels change with temperature, the changes in voltage levels are well within the tolerance ranges that would keep the families compatible. Fig. 1-4 lists some noise margins for V<sub>EF</sub> supply variations.

| Parameter            |      | -1  | EE<br>0%<br>Min | -5  | EE<br>i%<br>Min | V <sub>EE</sub> + |     | +5  | <sup>/</sup> EE<br>-5%<br>p Min |  |

|----------------------|------|-----|-----------------|-----|-----------------|-------------------|-----|-----|---------------------------------|--|

| Noise Margin<br>High | 10KH | 224 | 150             | 227 | 150             | 230               | 150 | 233 | 150                             |  |

| V <sub>NH</sub> (mV) | 10K  | 127 | 47              | 166 | 86              | 205               | 125 | 241 | 164                             |  |

| Noise Margin<br>Low  | 10KH | 264 | 150             | 267 | 150             | 270               | 150 | 273 | 150                             |  |

| V <sub>NL</sub> (mV) | 10K  | 223 | 103             | 249 | 129             | 275               | 155 | 301 | 181                             |  |

Fig. 1-4 — NOISE MARGIN versus POWER-SUPPLY CONDITIONS

A second noise parameter of interest to the designer is obtained by cascading worst case gates and measuring the minimum "noise" input that will propagate through the gates. This measurement is more indicative of actual system operation than dc noise margin, and is often referred to as "noise immunity" or "ac noise immunity". Testing has shown that this "noise immunity" is typically at least 40 millivolts greater than the dc noise margin specified by voltage levels. However, ac noise immunity is rather difficult to measure. Consequently it is not specified on the data sheets.

In system design, the user is concerned with noise margin when devices at different temperatures and different power supply voltages interface with each other. Figure 1-3 tabulates the worst case change in logic levels as a function of temperature. Equally important is the change in output levels as a function of supply voltage (cf Figure 5-2). The logic 1 levels are relatively independent of power supply voltage, and the change in the output level is typically less than 0.05 of the VEE change. The change in the  $\emptyset$  level is a function of the resistor ratios in the current switch and is typically 0.25 of the VEE change. These values illustrate the rejection of power supply variations that is characteristic of MECL. Detailed information on noise margin changes due to power supply and temperature variations is given in Chapters 5 and 6.

MECL 10KH and MECL 10K compatibility is demonstrated below. The method for determining compatiblity is to show acceptable noise margins for MECL 10KH, MECL 10K and mixed MECL 10K/MECL 10KH systems. The assumption is that the families are compatible if the noise margin for a mixed system is equal to or better than the same system using only MECL 10K series.

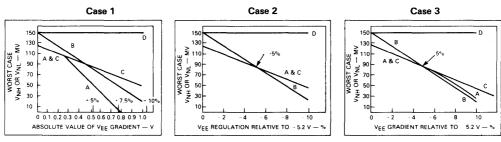

Using an all MECL 10K system as a reference, three possible logic mixes must be considered: MECL 10K driving MECL 10KH; MECL 10 KH driving MECL 10K; and MECL 10KH driving MECL 10KH. The system noise margin for the three configurations can now be calculated for the following cases (see fig. 1-5).

In Case 1, the system uses multiple power supplies, each independently voltage regulated to some percentage tolerance. Worst case is where one device is at the plus

<sup>\*</sup>Temp 0 to 75° C

extreme and the other device is at the minus extreme of the supply tolerance.

In Case 2, a system operates on a single supply or several supplies slaved to a master supply. The entire system can drift, but all devices are at the same supply voltage.

In Case 3, a system has excessive supply drops throughout. Supply gradients are due to resistanc drops in  $V_{EE}$  bus.

The analysis indicates that the noise margins for a MECL 10K/10KH system equal or exceed the margins for an all 10K system for supply tolerance up to  $\pm 5\%$ . The results of the analysis are shown in Fig. 1-5.

FIGURE 1.5 — NOISE MARGIN versus POWER-SUPPLY VARIATION

A. MECL 10K DRIVING MECL 10K B. MECL 10K DRIVING MECL 10KH C. MECL 10KH DRIVING MECL

#### **MECL Circuit Types**

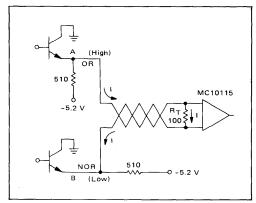

It is possible to connect the basic MECL differential amplifiers together within a circuit to increase logic flexibility, speed, and power efficiency. Two techniques, series gating and collector dotting, add the NAND and AND logic functions to the basic OR and NOR operation of the MECL gate with very little increase in propagation delay. A third technique, Wired-OR, gives the logic OR function by tying together two or more emitter-follower transistors. This is used internally in complex functions to save speed and power and, unlike collector dotting, may also be used externally by connecting logic outputs together.

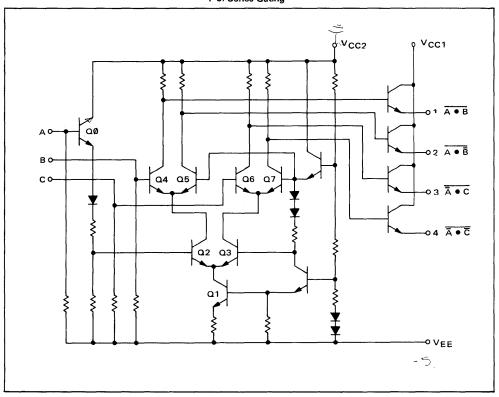

Series gating is accomplished by connecting MECL differential amplifiers in a current-switch "tree", building up from a current source, Q1, as shown in Figure 1-6. The A input controls the switch, Q2/Q3 through the level shifter  $Q\emptyset$  and the associated resistor diode network. The bias network is modified to provide the proper voltage level at Q3, a level which is lower than that on Q7 and Q5. The two upper switch pairs are controlled by inputs B and C. The overall circuit generates the four logic functions:  $\overline{A \cdot B}$ ,  $\overline{A \cdot B}$ ,  $\overline{A \cdot C}$ , and  $\overline{\overline{A \cdot C}}$ . MECL circuits use up to three levels of series gating, permitting up to eight logic functions with one current source.

The propagation delay from an input, to a top current switch is approximately one gate delay. The propagation delay from an input to a lower level current switch is slightly longer because of the input level shifter  $Q\emptyset$ . Typically, the latter takes about 1.5 gate delays. More specific information is found on the data sheet for a particular part.

Series gating is an advantage in MECL logic since it provides the AND or NAND logic functions. Together with the OR/NOR function of the basic gate, MECL has the four basic logic functions needed for efficient logic design. Series gating is used internally in most MECL complex functions and flip flops.

1-6: Series Gating

1-7: Collector Dotting

Sequential Logic: The MECL Flip-Flop

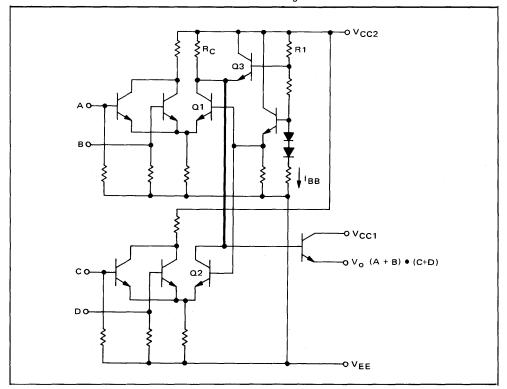

Collector dotting is a second logic technique which is used in the MECL 10K/10KH series. With it, the logic AND function can be generated by interconnecting one collector node of separate differential current switches as shown in Figure 1-7. When connected this way the two 2-input OR gates give the logic function:

$$V_0 = (A + B) \cdot (C + D)$$

Only one collector resistor ( $R_C$ ) is used for the two transistors Q1 and Q2. The interconnection requires that at least one input to each gate be at a logic 1 level for the output to be at the logic 1 level. Since it is possible to have both Q1 and Q2 conducting at the same time (all inputs low), a clamp is used to limit the current in  $R_C$  and maintain the output  $\emptyset$  logic level voltage. This clamp consists of R1 and Q3. They insure that the Q1/Q2 collector node never goes more negative than (IBBR1 + VBEQ3). Propagation delays for all inputs to collector dotted circuits are equal and are typically about 20% greater than the basic gate delay.

To allow for temperature variations, the collector-dotted logic functions are designed to have the same VOL as normal logic gates at TA = T max when only one gate has all of its inputs at a logic 0 level. Therefore, when all gates have all their inputs at a logic 0 level, VOL will be slightly more negative than a normal gate. This does not limit device operation, but does give an increase in noise immunity for the logic 0 level.

The collector dot (OR-AND) logic function, series gating, and the Wired-OR characteristics of MECL combine to provide the means for designing very efficient and fast complex logic functions.

#### **MECL Flip-Flops**

In addition to the basic gate, the flip-flops in a logic line provide a necessary building block. All MECL 10K/10KH and MECL III flip-flops, use the direct coupled master-slave circuit as shown in Figure 1-8 for the MC1670. In each direct coupled circuit the master is updated while the clock is low, and data is transferred to the slave on the positive excursion of the clock. This type of circuit offers better noise protection than ac coupled circuits and is not susceptible to overshoot on the inputs. Also, the master-slave flip-flops do not have the rise time limitations of ac coupled circuits.

#### **Operation Of Flip-Flop**

In the circuit of Figure 1-8 assume that initially Q,  $C_1$ ,  $C_2$ , R, S, and D are at  $\emptyset$  levels and that  $\overline{\mathbb{Q}}$  is at the 1 level. Since the clocks and the R and S inputs are low, transistors 1Q3 and 2Q3 are conducting. In the slave section only transistors 2Q6 and 2Q7 are in series with 2Q3. The output of the slave section is fed back to these two transistors in order to form a latch. Thus, when the clock is low, the output state of the slave is maintained. In the master section, the current path is through 1Q3 and 1Q9.

Now assume that the D input goes high. The high-input signal on the base of 1Q4 causes it to conduct, and 1Q9 to turn off. The voltage drop across resistor RC1 causes a low-state voltage on the base of 1Q11 and therefore on the emitter of 1Q11. Since there is essentially no current flow through RC2, the base of transistor

13

1-8: MECL III Master-Slave Type D Flip-Flop (MC1670)

1Q10 is in a high state. This is reflected in the emitter of 1Q10, and in turn is transferred to the base of 1Q6. 1Q6 is biased for conduction but, since there is no current path, it does not conduct.

Now assume one of the clocks goes high. As the clock signal rises, transistor 1Q2 turns on and transistor 1Q3 turns off. This provides a current path for the common-emitter transistors 1Q5, 1Q6, 1Q7, and 1Q8. Since the bases of all these devices except 1Q6 are in the low state, current flow is through 1Q6. This maintains the base and emitter of 1Q11 low, and the base and emitter of 1Q10 high. The high state on 1Q10 is transferred to 2Q4 of the slave section.

As the clock continues to rise 2Q2 begins to turn on and 2Q3 to turn off. (Reference voltages in the master and slave units are slightly offset to insure prior clocking of the master section). With transistor 2Q2 conducting and the base of 2Q4 in a high state, the current path now includes 2Q2, 2Q4, and resistor RC3. The voltage drop across the resistor places a low-state voltage on the base of 2Q11, and therefore on the emitter, of 2Q11. The lack of current flow through RC4 causes a high-state input to the base of 2Q10. Finally these states are fed back to the latch transistors, 2Q6 and 2Q7 and appear on the Q and  $\overline{Q}$  outputs.

As the clock voltage falls, transistor 2Q2 turns off and 2Q3 turns on. This provides a current path through the latch transistors, "locking in" the slave output.

In the master section, the falling clock voltage turns on transistor 1Q3 and turns off 1Q2. This enables the input transistor 1Q4 so that the master section will again track the D input.

A separation of thresholds between the master and slave flip-flops is caused by R8. The current through this resistor produces an offset between the thresholds of the transistor pairs 1Q2/1Q3 and 2Q2/2Q3. This offset disables the D input of the master flip-flop prior to the enabling of the information transfer from master to slave via transistors 2Q4 and 2Q9. This disabling operation prevents false information from being transferred directly from master to slave during the clock transition, particularly likely if the D input changes at this time. The offsetting resistor, R8, also allows a relatively slow-rising clock waveform to be used without the danger of losing information during the transition of the clock.

Both set and reset inputs are symmetrically connected. Therefore, their action is similar although results are opposite. As a logic 1 level is applied to the S input transistor, 1Q2 begins to conduct because its base is now being driven through 1Q19 which is in turn connected to S. Transistor 1Q5 is now on, and the feedback devices 1Q6 and 1Q7 latch this information into the master flip-flop. A similar action takes place in the slave with transistors 2Q2, 2Q5, 2Q6, and 2Q7.

#### **MECL Family Comparison**

A list of MECL circuit characteristics is tabulated in Figure 1-9. The various families are compared with respect to both features and performance. Because of the speed difference between the 10,100 series and 10,200 series, these products are given separate columns. The following paragraphs describe the MECL characteristics in the order of Figure 1-9. Differences between standard and military products are pointed out when significant.

- 1... Introduction year relates to the first year product was introduced. Several years are normally required to fill a product line and work continues to update MECL with new LSI, memories, and logic.

- 2. . . All MECL circuits incorporate internal VBB bias drivers. The bias circuits are designed to operate over a wide range of temperatures, supply voltages, and circuit power

dissipation. All MECL parts have the same logic level and threshold voltages regardless of power dissipation. The M10800 and MECL 10KH families feature a voltage compensation network that holds logic levels constant with supply voltage.

3... MECL 10K/10KH and MECL III circuits feature open emitter outputs for easy interface to terminated transmission lines. The MC1648 VCO is an exception and can be used without an external resistor.

1-9: MECL Family Comparison

| 2. 据其2. 经国际企业的 医克里氏                                | THE REPORT OF | ME               |                  |          |          |  |

|----------------------------------------------------|---------------|------------------|------------------|----------|----------|--|

| FEATURE                                            | MECL 10KH     | 10,100<br>10,500 | 10,200<br>10,600 | 10,800   | MECL III |  |

| 1. Year Introduced                                 | 1981          | 1971             | 1973             | 1976     | 1968     |  |

| 2. Bias Driver                                     | V.C.*         | 10,000           | 10,000           | V.C.*    | 10,000   |  |

| 3. Output Pulldown Resistors                       | No            | No               | No               | No       | No       |  |

| 4. Input Pulldown Resistors                        | Yes           | Yes              | Yes              | Yes      | Yes      |  |

| Maximum Input D.C.     Loading Current             | 265µA         | 265µA            | 410µA            | 350µA    | 350µA    |  |

| 6 Specified Ouput Current                          | ≈22mA         | ≈22mA            | ≈22mA            | ≈22mA    | ≈22ma    |  |

| 7. Maximum Output Current                          | 50mA          | 50mA             | 50mA             | 50mA     | 40mA     |  |

| 8. Transmission Line<br>Drive                      | Yes           | Yes              | Yes              | Yes      | Yes      |  |

| 9. DC Loading Fanout                               | 83            | 83               | 54               | 63       | 68       |  |

| 10. Input Capacitance                              | 2.9 pf        | 2.9 pf           | 3.3 pf           | H 45     | 3.3 pf   |  |

| 11. Output Impedance                               | 7 ohm         | 7 ohm            | 7 ohm            | 7 ohm    | 5 ohm    |  |

| 12. Gate Progration Delay (typical)                | 1.0 ns        | 2 ns             | 1.5 ns           | 1-2.5 ns | 1 ns     |  |

| 13. Gate Edge Speed (10 to 90%)                    | 1.8 ns        | 3.5 ns           | 2.5 ns           | 3.5 ns   | 1 ns     |  |

| 14. Flip-Flop Toggle Speed (min                    | 250 MHz       | 125 MHz          | 200 MHz          | N.A.     | 500 MHz  |  |

| 15. Gate Power                                     | 25 mW         | 25 mW            | 25 mW            | 2.3 mW   | 60 mW    |  |

| 16. Open Wire Length (Less than 100 mV undershoot) | 3″            | 6"               | 3"               | 6"       | 1"       |  |

| 17. Wire-wrap Capability                           | Yes           | Yes              | Yes              | Yes      | No       |  |

| 18. Use of series damping<br>Resistors             | Yes           | Yes              | Yes              | Yes      | Yes      |  |

| 19. Separate V <sub>CC</sub> Inputs                | Yes           | Yes              | Yes              | Yes      | Yes      |  |

| 20. Speed-Power Product                            | 25 pJ         | 50 pJ            | 37 pJ            | 4.6 pJ   | 60 pJ    |  |

| 21. Wire-or Capability                             | Yes           | Yes              | Yes              | Yes      | Yes      |  |

| 22. Full Military Temp. Range                      | TBD**         | Yes              | Yes              | No       | No       |  |

| 23. Flat Package.                                  | Special       | Yes              | Yes              | No       | Yes      |  |

| 24. Dual-In-Line Package                           | Yes           | Yes              | Yes              | Quil     | Yes      |  |

| * Voltage compensated                              |               |                  |                  |          |          |  |

| ** To be determined                                | 图3.400 3.65图  |                  | THE THE          |          |          |  |

4. . . All MECL single-ended inputs have internal (typical 50 k $\Omega$ ) input pull down resistors. This simplifies wiring since unused inputs can be left floating and assume a solid logic Ø VOL state. Differential devices such as line receivers and the MECL to TTL translator do not have input pull down resistors and should be connected as described on the individual data sheets.

5. . . Maximum input DC loading current is specified on individual circuit data sheets. The numbers here apply to a single input of a basic gate. If a package input goes to more than one point in a circuit, such as a gate strobe line would, additional current may be required.

Calculating the input current,  $I_{in}$ , for MECL 10K/10KH with a worst-case input resistor value of 30 k $\Omega$  ( $R_{in}$ ) gives an input resistor current of:

$$I_{in} = \frac{V_R}{R_{in}} = 143 \,\mu A$$

$$V_R = |V_{EE} - V_1| = 4.3 \text{ V},$$

where:  $V_R$  = voltage drop across the input resistor,  $R_{in}$ , with a logic 1 input,

$V_{EE} = -5.2 \text{ V supply voltage,}$

$V_1 = -0.9 \text{ V (a typical logic 1 level)}.$

The typical 50 k $\Omega$  value will use slightly less current, but either resistance value is very high compared to the output circuit impedance or the line impedance.

6-8. . . Output voltage levels are specified at currents representative of circuit operation. MECL 10K/10KH and MECL III are designed to drive  $50\,\Omega$  transmission lines terminated to -2 Vdc (measured from V<sub>CC</sub>). The current, I<sub>TT</sub>, required by the line termination is:

$$I_{TT} = \frac{V_{TT} - V_1}{Z_0} = \frac{(-2.0 + 0.9) \text{ V}}{50 \Omega} = -22 \text{ mA}.$$

Consequently, the outputs are specified with 50 ohm loads. The 50 ohm load is a worst-case specification and does not require that system design be restricted to  $50\,\Omega$  transmission lines. MECL 10K/10KH works well over a range of 50 to 120 ohm environments. Full military MECL 10,500 and and 10,600 series are limited to 100 ohm (11mA) loads.

The maximum permissible output currents of 50 mA for MECL 10K/10KH and 40 mA for MECL III insure a good safety margin over the specified currents.

- 9... The dc loading fanouts for MECL 10K/10KH and MECL III are computed by dividing the output current by the input current. However, both ac limitations and current needed in the transmission line termination can be expected to restrict the system fanout to a smaller number than the one computed.

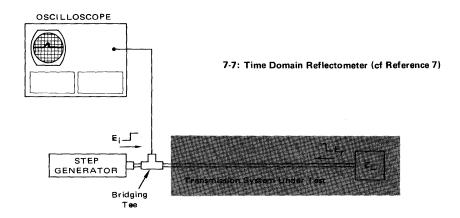

- 10. . . Two techniques are used to measure circuit input capacitance. One method uses an impedance meter, such as the H.P. 4815A RF Vector Impedance Meter, to measure impedance and phase angle. The other technique uses a time domain reflectometer (TDR) to measure the effect of capacitance on the impedance

- of a transmission line. (The mathematical relationships used to calculate input capacitance from TDR data are presented later in Chapter 7). Although small, the input capacitance will affect system rise time and transmission line propagation delay as a function of fanout at high MECL speeds.

- 11. . . DC output impedance can be calculated from measurements of the output voltage as a function of output current:  $Z = \Delta V/\Delta I$ . The gate output impedance must be much lower than the line characteristic impedance in order to provide full MECL signal levels when driving transmission lines. The output impedance (resistive load) is the parallel value of the output transistor and pull down resistor. It should be noted that capacitance charging rate during a negative transition is limited by current flow through the pull down circuit.

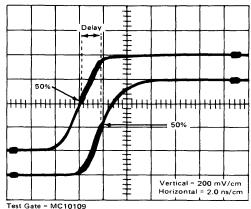

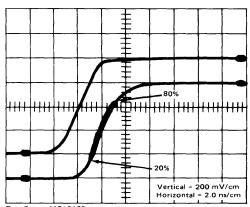

- 12-13. . . Gate propagation delay, edge speed, toggle rate, and power dissipation are standard data sheet information. Propagation delay  $(t_{pd})$  is measured from the 50% amplitude point on the input signal to the 50% amplitude point on the output signal. Normally the edge speed given is measured between the 10 and the 90% amplitude points on the output signal. However, because of the amount of rounding on the upper 10% of the MECL 10K/10KH edges, these families are specified with 20 to 80% edge speeds for easier correlation. Nevertheless, 3.5 ns is a typical 10 to 90% figure for MECL 10K and 1.8 ns is a typical 10 to 90% figure for MECL 10KH.

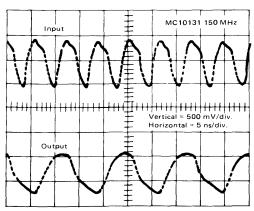

- 14. . . Toggle speeds are minimum rates for the flip-flops in a family. For MECL III the 500 MHz shown is for the MC1690 D flip-flop. The family has divide by 4 prescalers which operate at 1 GHz.

- 15. . . Gate power for the MECL 10K/10KH and MECL III gates is specified with open emitter outputs, as is usual with most ECL product lines. The wide variety of output loads both resistors used with transmission lines and pull down resistors makes a power specification under load difficult to define. In a system, the output power is added to the gate power to find total power.

- 16-17. . . Open wire length and wire wrap usage are a function of edge speed and the propagation velocity of the wire. The distances shown are maxima, selected to give less than 100 mV undershoot at the receiving end of the line with a fanout of one. Additional information on line driving is found in Chapter 3. Wire wrap may be used with all families but MECL III. The 1 ns edges associated with MECL III cause too much reflection from the wire wrap connection to permit practical use. The open wire maximum line lengths still apply when using wire wraps, unless some form of resistor damping or line termination is used.

- 18. . . Damping resistors consist of small resistors (5 to 75 ohms) that are placed in series with a line at the output of the driving circuit to extend the permissible line length. The resistor provides a closer match between the line and the output impedance of the circuit than a direct connection. This match limits overshoot and ringing, and allows the use of line lengths somewhat greater than twice the non-damped lengths.

- 19... Separate V<sub>CC</sub> inputs (V<sub>CC1</sub>, V<sub>CC2</sub>) are characteric of MECL 10K/10KH and MECL III. The separate V<sub>CC</sub> pins are used to minimize any crosstalk between circuits in a package which might occur with the high switching currents when driving transmission lines. Separate V<sub>CC</sub> lines do not affect using the parts and only require that two package

pins be connected to a single ground plane or ground bus. A few MECL 10K/10KH parts such as the MC10186 and the MC10H186A have only 1 V<sub>CC</sub> pin because the function requires 14 I/O pins. These circuits keep V<sub>CC1</sub> and V<sub>CC2</sub> separate on the chip and use two bonding wires to the common V<sub>CC</sub> package pin.

- 20. . . Speed-power product is a measure of a logic family's efficiency. Propagation delay (nanoseconds) is multipled by the gate power dissipation (milliwatts) to get a measure of efficiency in terms of energy (picojoules). It is interesting to note that gate efficiency has improved with each succeeding logic line introduced. The speed-power product is slightly inaccurate because power figures are used which do not include output loading (discussed previously). However, TTL speed-power products can be inaccurate also as they are generally computed for the circuits operating at a low rate. Such figures would be much worse for circuits operating near top switching rates. Gate power and speed-power for the M10800 family are calculated by dividing the number of equivalent gates in a logic function by the circuit power dissipation. The numbers are averages for the LSI circuits rather than any specific gate. Internal gates use less power than output gates with 50 line drive.

- $21\ldots$  Wired-OR is a technique used with all MECL circuits to obtain the logic OR function by connecting circuit outputs together. When several (more than 5) circuits are connected with Wired-OR outputs, it is possible to get a noise spike on the output if all gates are at a 1 output, and all gates but one are simultaneously changed to a logic  $\emptyset$ . The noise spike is due to the one gate suddenly having to source the output current previously supplied by the other circuits. The pulse width is normally less than the gate propagation delay and of insufficient amplitude to propagate in the system.

- 22-25... The remaining family features are self-explanatory. Packaging and temperature range for MECL 10K/10KH are based on initially introduced circuits. Other configurations are being investigated to meet future requirements.

The design guidelines presented here are intended to assist the MECL user to apply MECL families in a system. The rules listed have been tried out in complete systems with good results. As rise times become less than 3 ns, special design rules must be followed. For rise times of 1.5 ns or shorter, designing with transmission lines is necessary.

MECL 10K/10KH and MECL III logic families are treated separately because of the differences in their capabilities and design techniques to be used. Reasons for the rules, methods for applying them, and test data are found in the following chapters under associated subjects. MECL 10K/10KH may be used with or without transmission lines and termination techniques. Rules for both design approaches are covered separately. Terminated transmission lines are recommended for large printed circuit boards and larger systems having several circuit boards.

#### 1. MECL 10K/10KH without terminated lines

MECL 10K/10KH family of integrated circuits is designed to provide high circuit speed without putting a premium on special system layout techniques. This feature simplifies design with the emitter coupled logic family because most of the techniques used with high-speed TTL apply to MECL 10K/10KH. The ability of MECL 10K/10KH to interface with MECL III enables very high-speed systems to gain power economy, eased design rules, a large choice of logic functions, and lower system cost.

MECL 10K rise, fall and propagation delay times are typically each 2 ns. However, since rise and fall times are measured at 20-80% and are typically 3.5 ns 10-90%, transmission line techniques are not mandatory. The 10-90% rise and fall times of MECL 10KH are typically 1.8 ns, and are 1 ns 20-80%. Standard double-sized circuit boards and backplane wiring with ground planes are commonly used with MECL 10K/10KH.

Because of the wide variety of MECL 10K/10KH system sizes and interfaces, not all techniques will apply to every system. The designer should use these rules as guides, modifying them sensibly as required for a particular system.

#### A. Logic Design Considerations

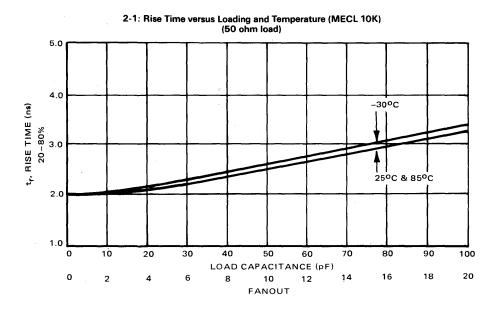

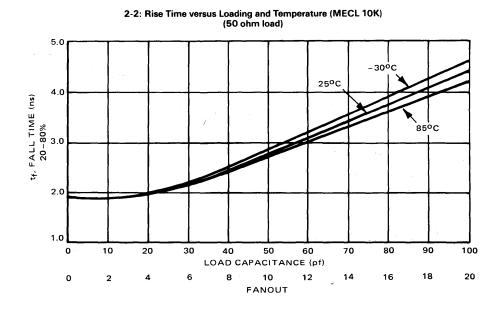

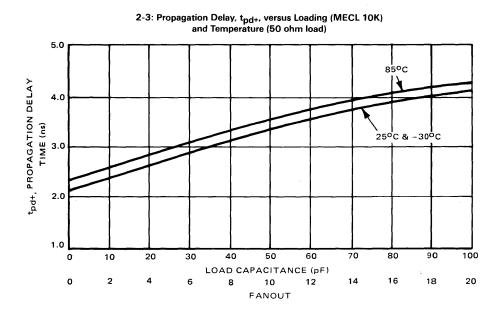

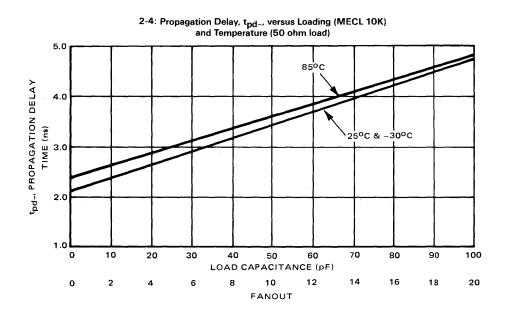

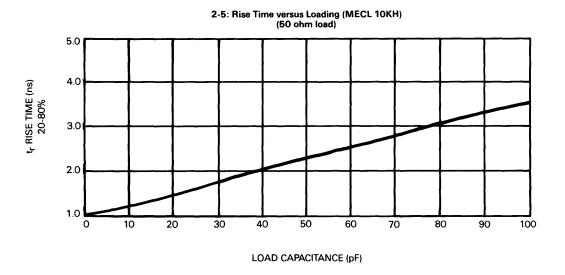

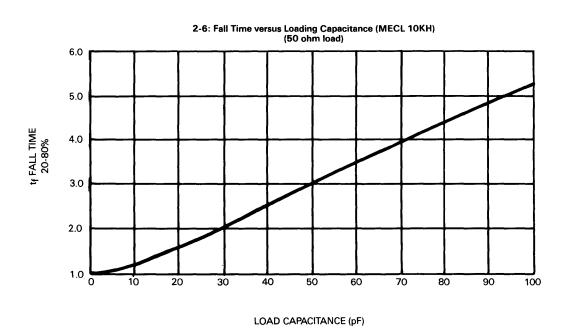

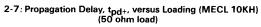

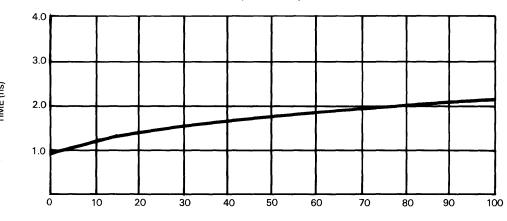

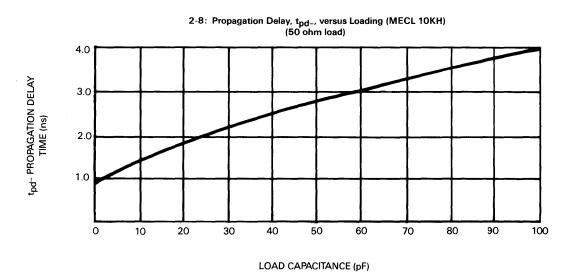

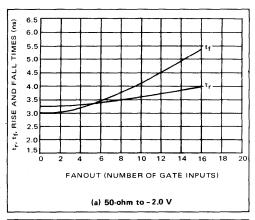

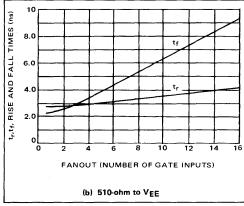

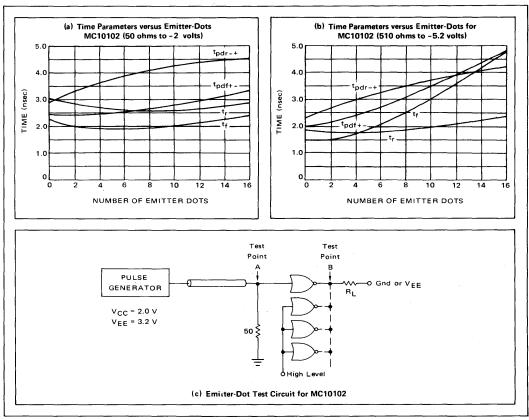

1. MECL rise, fall and propagation delay times are a function of fanout and capacitive loading. Figures 2-1 through 2-8 show the reduction in speeds with load placed near the output pin. Consequently when MECL 10K/10KH is operating near its upper speed limit, fanout should be restricted as indicated by the curves. Because of the emitter follower outputs, fall time and propagation delay to a \$\phi\$ level is more affected by capacitive loading than rise time and propagation delay to a 1 level (note that the curves in Figure 2-4 are steeper than those in Figure 2-3).

#### MECL 10K/10KH Parameters versus Loading and Temperature

tpd+ PROPAGATION DELAY

LOAD CAPACITANCE (pF)

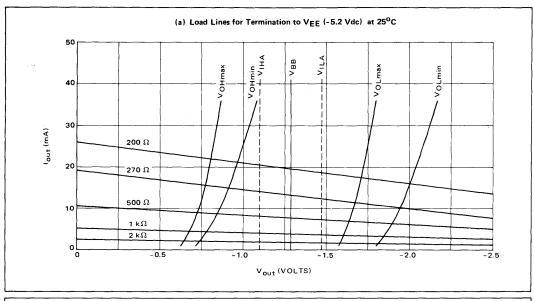

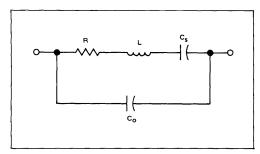

- 2. Fall-time and  $t_{pd}$  may be improved by using a smaller load resistor between the output and -5.2 Vdc. A 240  $\Omega$  resistor will cut the delay caused by capacitive loading nearly in half. Load resistors less than 180  $\Omega$  should not be used because the heavy load may cause a reduction in noise immunity when the output is in the 1 state, due to increased output emitter-follower VBE drop. Normally 510  $\Omega$  load resistors provide a good speed-power system design.

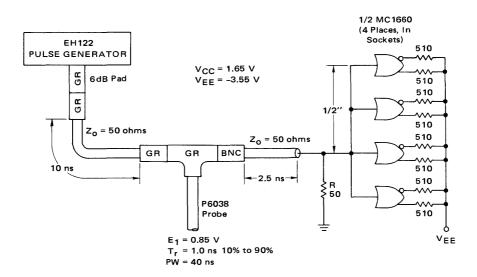

- 3. When driving flip-flops at high speed, clock driver circuits such as the MC10210, MC10211, MC10H210, MC10H211 or MECL III gates should be used. MECL III gates such as the MC1660 or MC1662 can provide the bandwidth necessary for clocking several flip-flops at once as in a shift register or synchronous counter operating at high speed.

- 4. When driving a long string of flip-flops at speeds lower than 80 MHz (clock), two gates may be operated in parallel for additional drive. The MC10110 or MC10111 is useful in this application since its multiple OR or NOR outputs may be wired together.

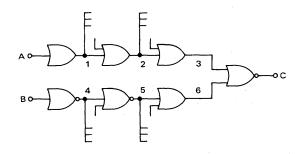

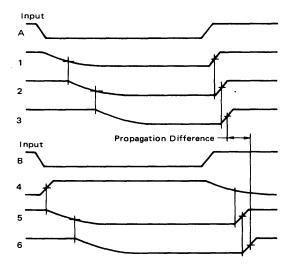

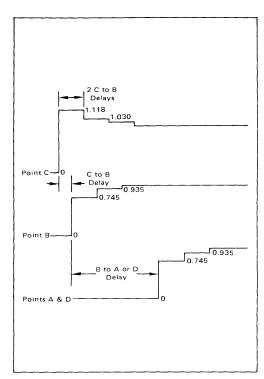

- 5. The high operating speed of MECL and the effect of loading on propagation delay must be considered when parallel circuits converge at one point, as shown in Figure 2-9. Unequal delays along paths A and B can result in momentary outputs at point C, each lasting a time equal to the propagation delay difference between A and B. This can be compensated for by additional timing in the form of a strobe, or by adjusting the fanouts along A and B. If possible, unused gate inputs can be paralleled to simulate a larger fanout where required; otherwise a small capacitor can be substituted for the needed fanout (about 5 pF per gate input is recommended).

2-9: Parallel Signal Paths

Under heavy loading, propagation delay along path A will be less than along path B because of the use of OR outputs in A as opposed to the NOR outputs in B. This difference (Figure 2-10) is due to the effect of loading on the fall time, rather than being due to a timing difference between OR and NOR outputs. As a matter of fact, under light loading, propagation delays for both NOR and OR outputs are identical.

When designing clocks for high-speed flip-flops, these timing differences become increasingly important. For example, the MC10231 flip-flops can toggle on a 2.5 ns pulsewidth clock, consequently timing chain skewing in the order of 2.5 ns can cause false operation.

2-10: Propagation Differences

#### B. System Layout Considerations

- 1. System grounding and propagation delays in interconnecting leads are factors to be considered before laying out a system. Depending on the type of wire used, the wiring propagation time of a signal can greatly affect overall system speed. In normal backplane wiring it is realistic to expect a 2 ns per foot delay. Propagation delay is less in coaxial cable, but more for signal conductors in a multilayer circuit board.

- 2. System sections such as shift registers and synchronous counters should be on one card. Propagation delay between shift register clocks on separate boards can cause erroneous operation. Where timing is critical, equal length clock lines (to shift registers or other circuits on separate cards) should be run from a common clock to the card connectors. Such lines will also help limit overshoot and ringing (discussed further in section D. "Backplane Wiring").

- 3. The Wire-OR capability of MECL can be a powerful tool for reducing power, propagation delay, and package count. However, since the Wire-OR connection switches current when in operation (8 mA for a 510 ohm pulldown resistor), long interconnect lines can cause voltage transients due to signal line propagation delay. It is recommended that Wire-OR outputs be kept within a package or between nearby packages. Wire OR between circuit boards should be avoided except for bus lines where only one output goes high at a time. Large number Wire-OR ties can cause a loss of low-level noise margin because all outputs supply current to the pull-down resistor. A good rule is to limit the Wire-OR number to an average of 1 mA per output (6 outputs for 510 ohm pulldown, 8 for 390 ohms, 10 for 330 ohms, etc.).

- 4. Sections of a system where high fanout may be necessary (such as adders with lookahead carry) should be kept on one card. Signal path length should be reduced as fanout is increased to minimize both line delay and reflections.

## C. Circuit Board Layout Techniques

- 1. The size of a MECL system circuit board is not restricted by the logic family. System requirements should determine card size. Terminated transmission line techniques should be considered for circuit boards larger than 6 by 8 inches.

- 2. Standard double-sided circuit boards with a good ground distribution may be used with MECL 10K/10KH. A low impedance ground is necessary since any noise on the ground line may be coupled into signal lines. Also, any voltage drop across ground will subtract from the noise immunity of the MECL circuits. Grounding techniques are discussed at length in Chapter 5 "Power Distribution".

- 3. As with TTL, bypass capacitors between ground and -5.2V should be used with MECL. A 1.0  $\mu$ F capacitor should be located on the board at the power supply inputs. Bypass capacitors, 0.01 to 0.1  $\mu$ F, should be connected once every four or five packages. When breadboarding or using MECL 10K/10KH without a good ground plane, a 0.1  $\mu$ F bypass capacitor should be used for every two packages. RF quality capacitors (low inductance) are recommended because of high-circuit speeds. Unlike TTL, MECL does not have large current spikes during switching. A 510 ohm pulldown resistor requires 8 mA for a logic 1 and 6 mA for a logic  $\emptyset$  or a delta of 2 mA switched current. The function of the bypass capacitors is to supply the small switching current of the pulldown resistor, circuit input capacitance, and circuit board stray capacitance, thus preventing spikes on the power leads.

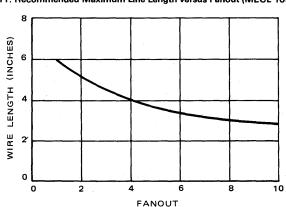

- 4. As with any high-speed system, signal lines should be kept as short as possible to minimize ringing and overshoot, as well as to simplify timing considerations arising from the propagation delay of a signal along a conductor. Ringing and overshoot are due to the intrinsic inductance and capacitance of the line itself, as well as lumped capacitance at the end of the line. Intrinsic inductance and capacitance are reduced by shortening the lines. A graph of recommended maximum line length as a function of fanout for MECL 10K is shown in Figure 2-11. Since increased fanout adds capacitance at the end of the line, the line should be shortened as shown by the following curve. Detailed unterminated signal line length information is found in Chapter 3, "Printed Circuit Board Connections".

2-11: Recommended Maximum Line Length versus Fanout (MECL 10K)

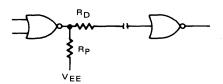

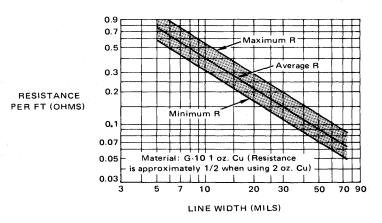

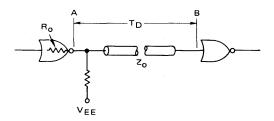

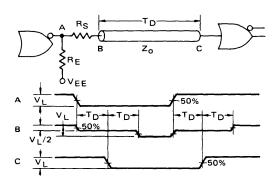

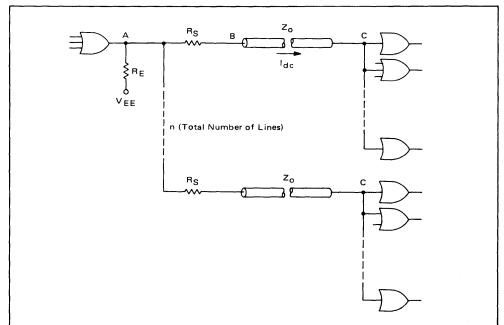

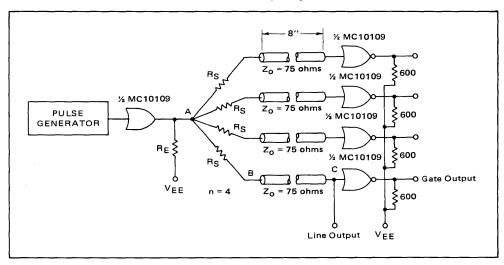

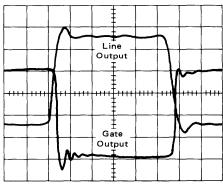

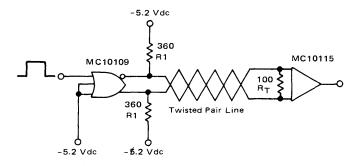

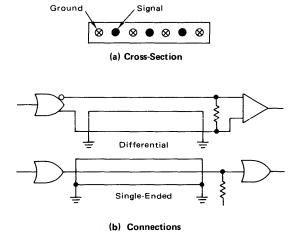

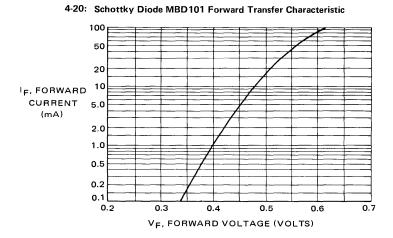

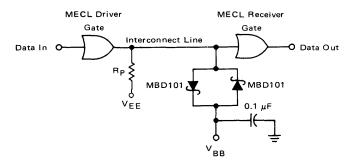

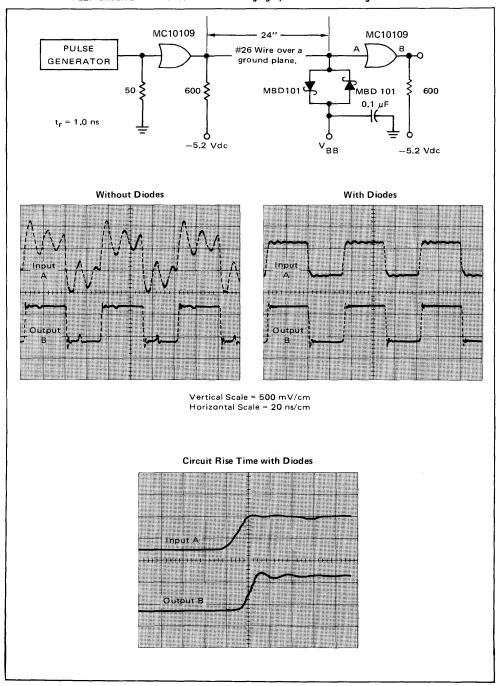

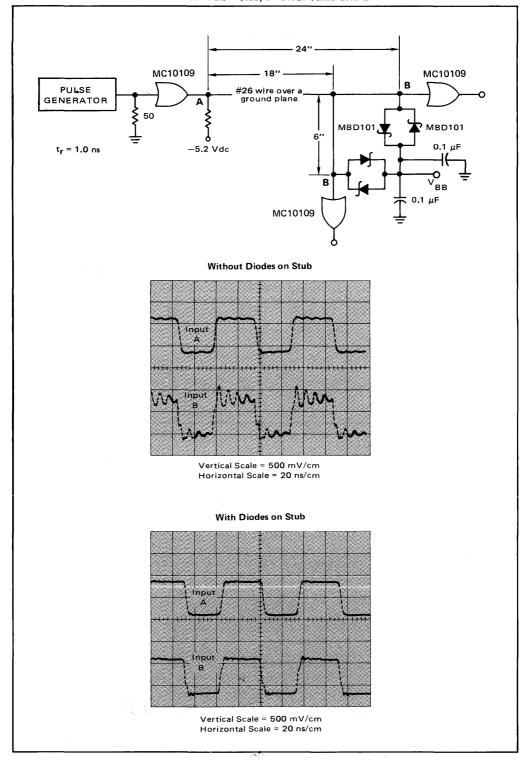

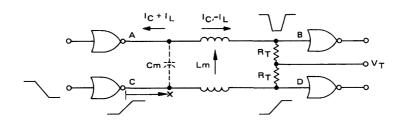

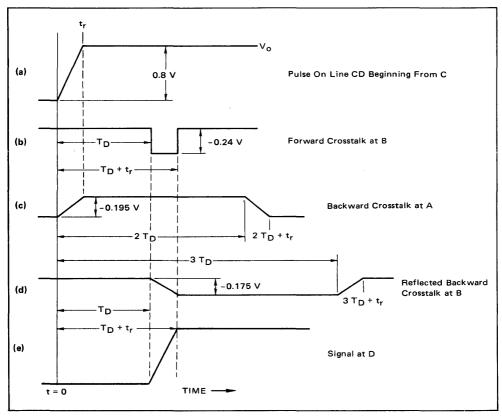

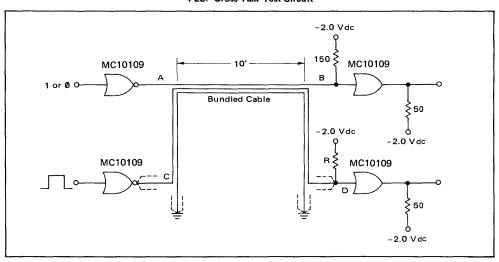

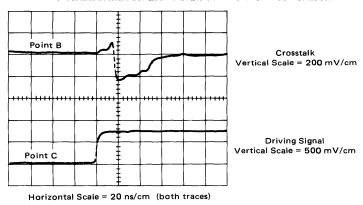

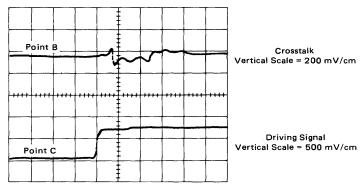

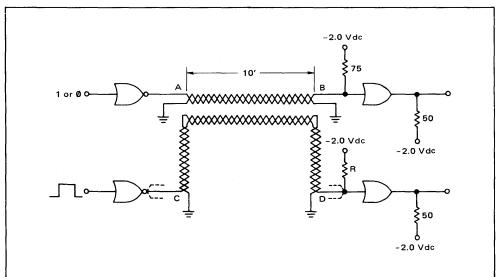

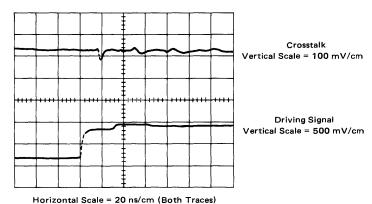

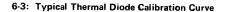

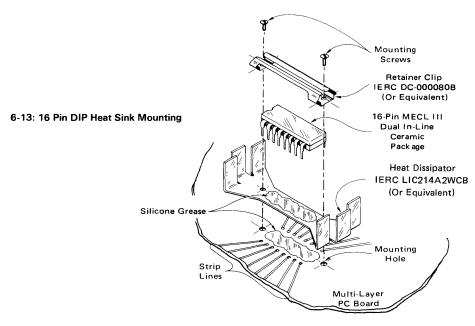

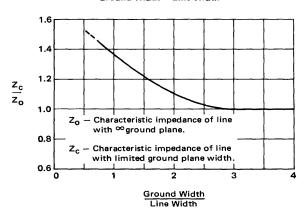

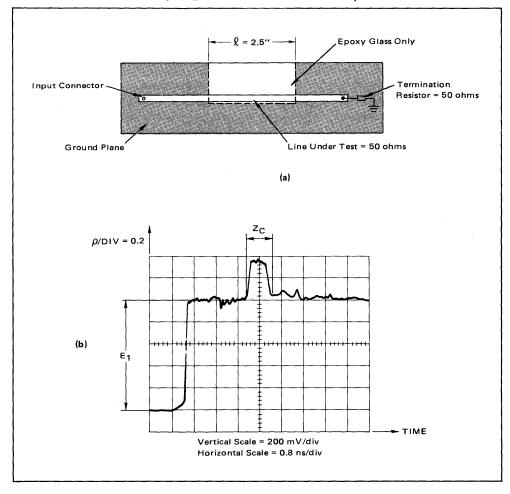

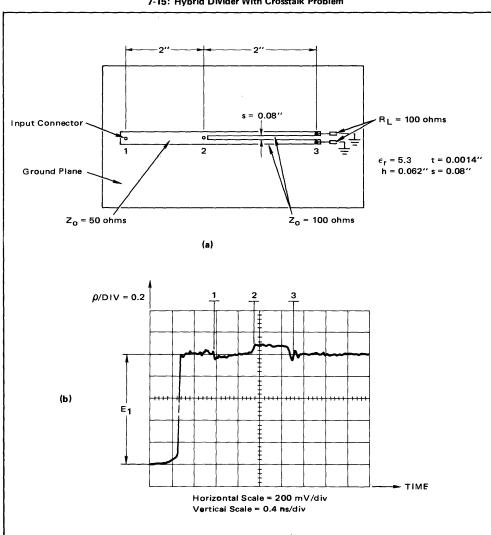

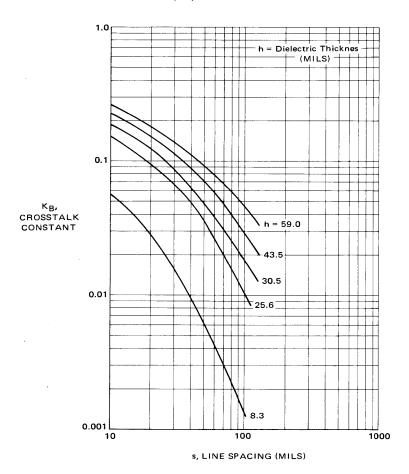

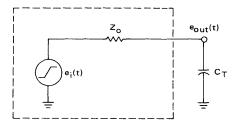

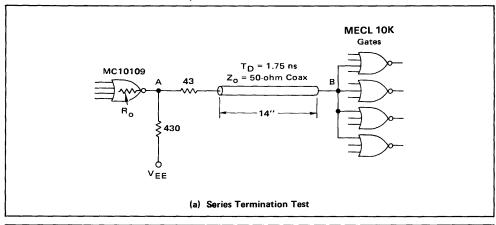

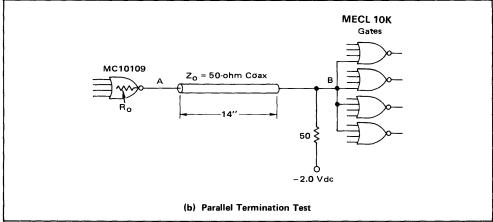

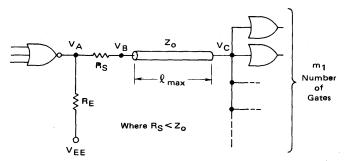

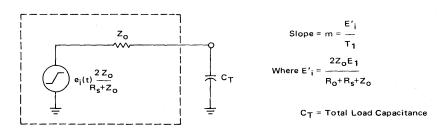

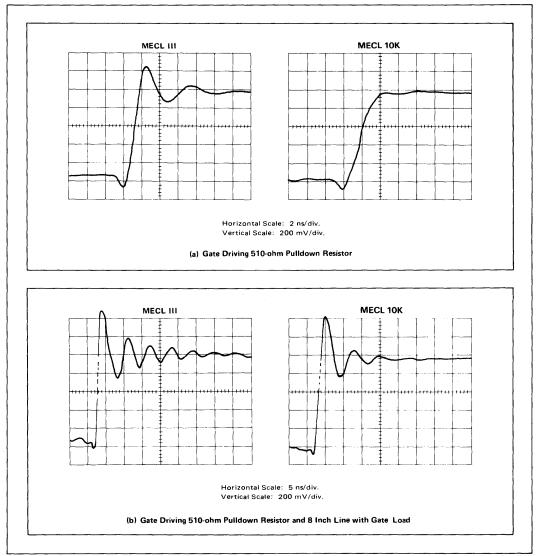

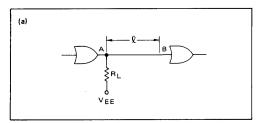

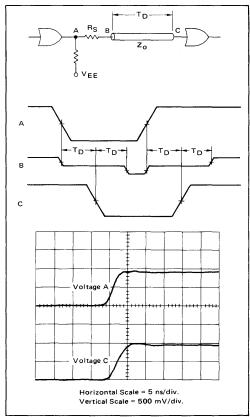

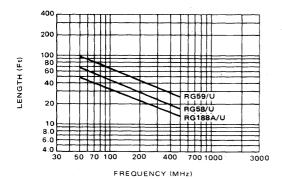

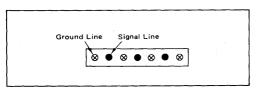

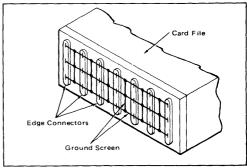

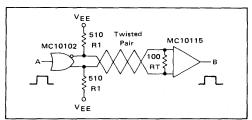

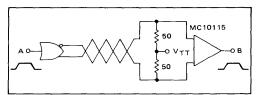

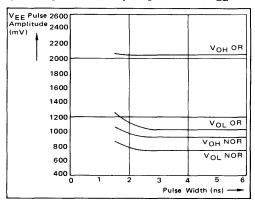

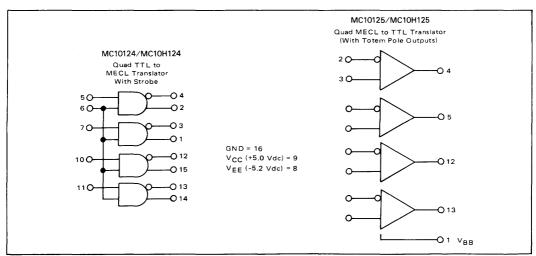

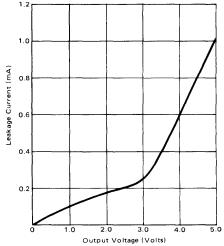

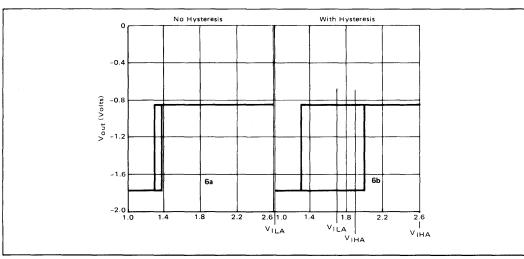

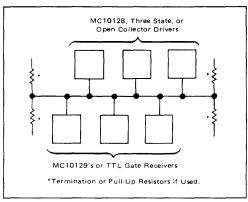

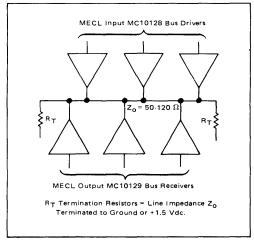

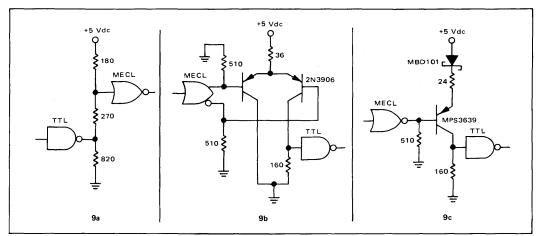

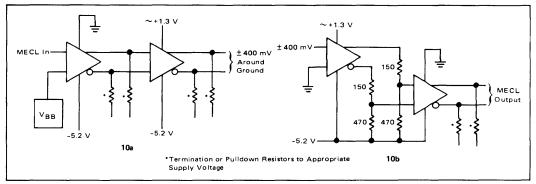

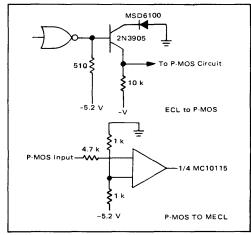

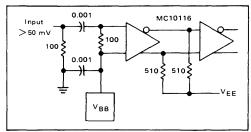

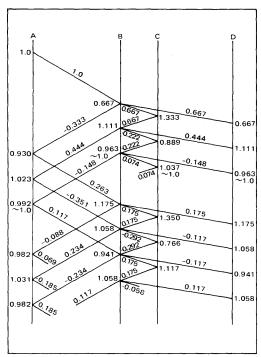

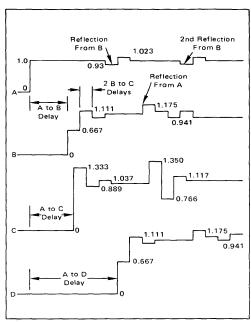

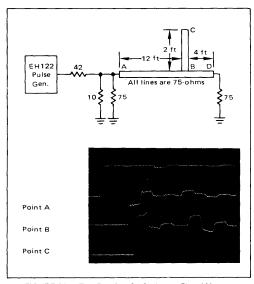

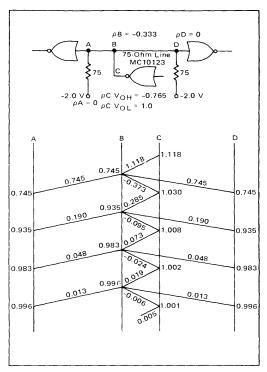

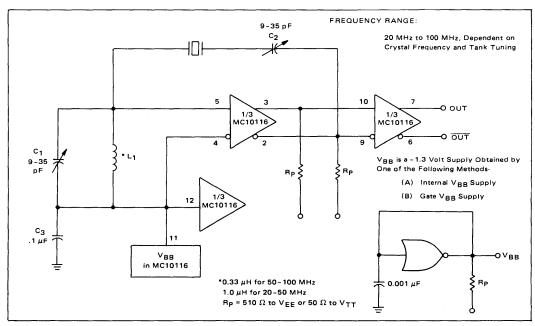

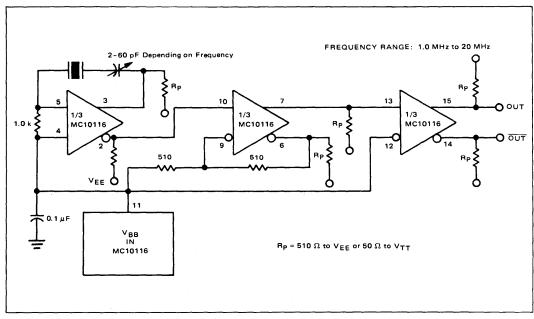

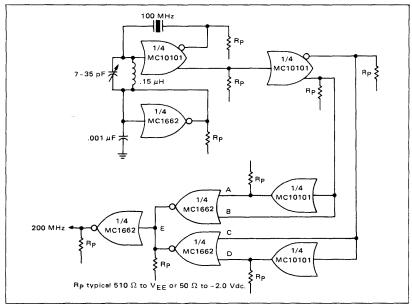

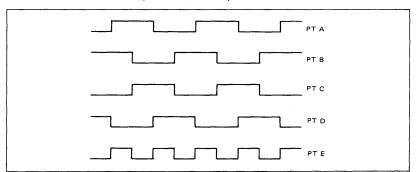

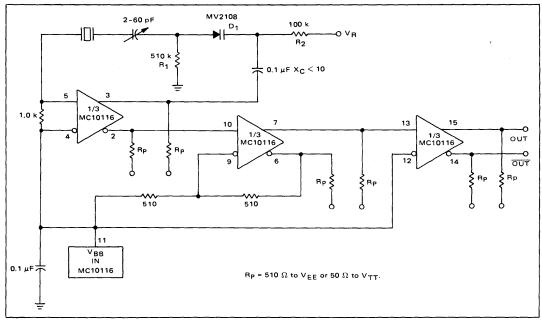

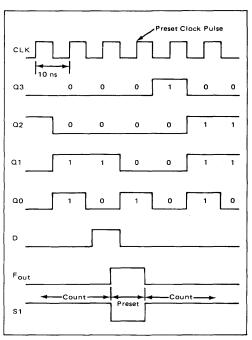

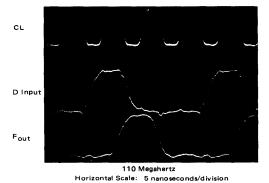

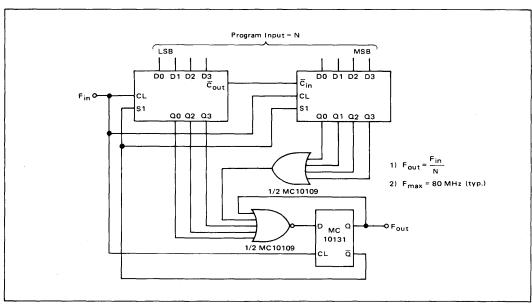

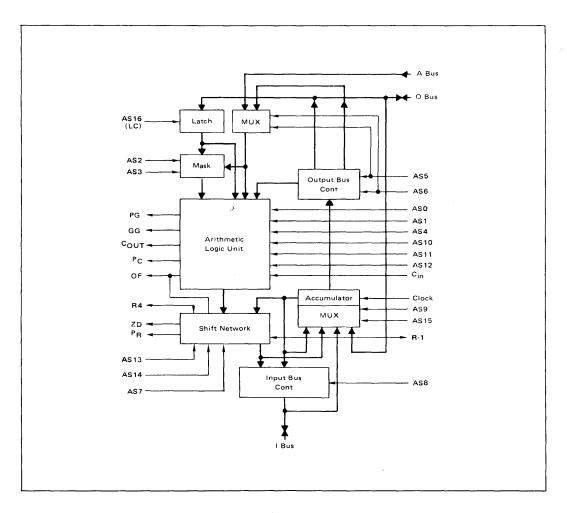

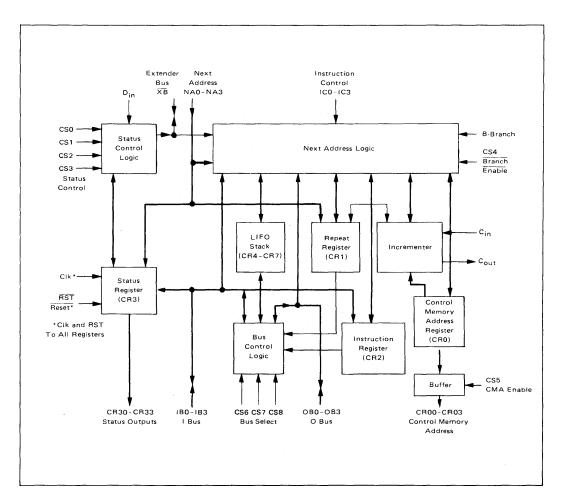

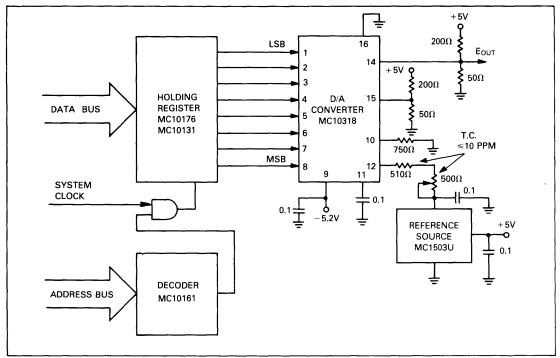

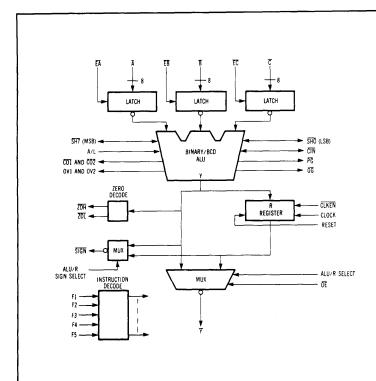

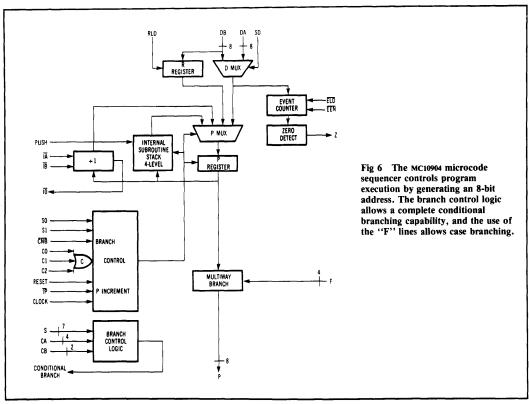

5. Longer line lengths are possible if a series damping resistor is used. The resistor is placed at the output of a gate, in series with the signal line as shown in Figure 2-12. The resistor value depends on the fanout and the required line length. Resistors under 150 ohms for a fanout of one, or under 30 ohms for fanouts greater than five, are normally used for damping. Values larger than these produce rise and fall time degradation and loss of noise immunity due to IR voltage drop in the resistor.