This presentation is a self paced tutorial of the 68HC05 family of 8-bit microcontrollers.

The Tutorial starts with an architectural overview of the 68HC05 central processor unit (CPU). It covers memory organization, the CPU programmer's model, stack pointer operation, and the 68HC05 instruction set and its addressing modes. Once learned, this knowledge is applicable to all 68HC05 devices, because they all use the same CPU.

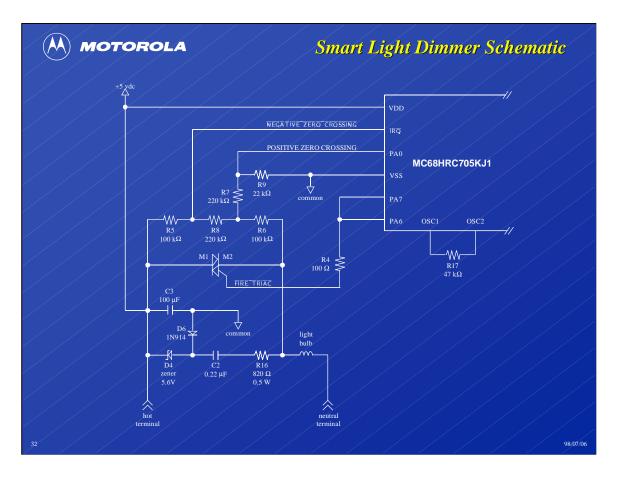

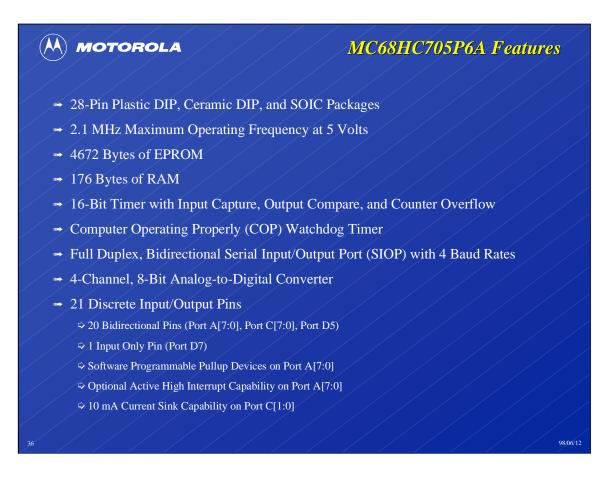

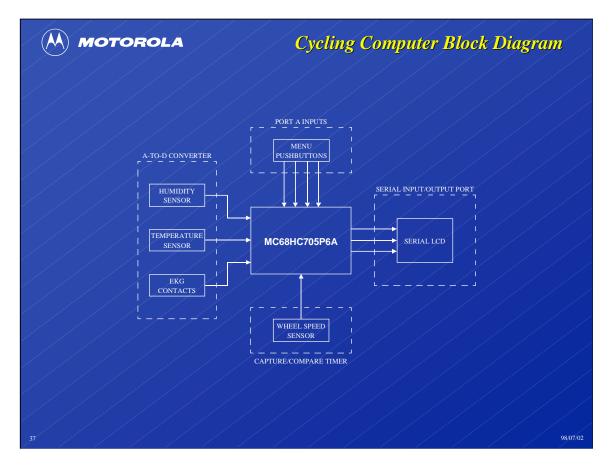

In the second part of this tutorial, two sample applications illustrate the use of some common 68HC05 peripherals. One of these is a smart light dimmer in which the very low cost MC68HC705KJ1 provides features not available on conventional electro-mechanical dimmers. The other is a cycling computer that uses the MC68HC705P6A to monitor rider heart rate, temperature, humidity, speed, and distance traveled.

Other common 68HC05 peripherals are covered in the third and final section of this tutorial. These provide some of the communication, timing, and display features of embedded control applications not illustrated in the previous examples.

|                               | DLA                              | 68HC05 Memory Organization                             |

|-------------------------------|----------------------------------|--------------------------------------------------------|

| \$0000<br>\$0020<br>\$0100    | LO & CONTROL<br>REGISTERS<br>RAM | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ |

|                               | ROM/EPROM                        |                                                        |

| Sxx00 –<br>SxxF0 –<br>SxxFT – | BOOT ROM<br>VECTORS              | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |

|                               |                                  | 98.07/0                                                |

The 68HC05 is a Von Neumann computer. All storage and input/output resources are memory mapped into a single linear address space.

The memory map is organized as bytes, begins at \$0000, and ends at \$xxFF, where, depending on factors like ROM or EPROM array size, 'xx' is \$03, \$07, \$0F, \$1F, \$3F, or \$7F.

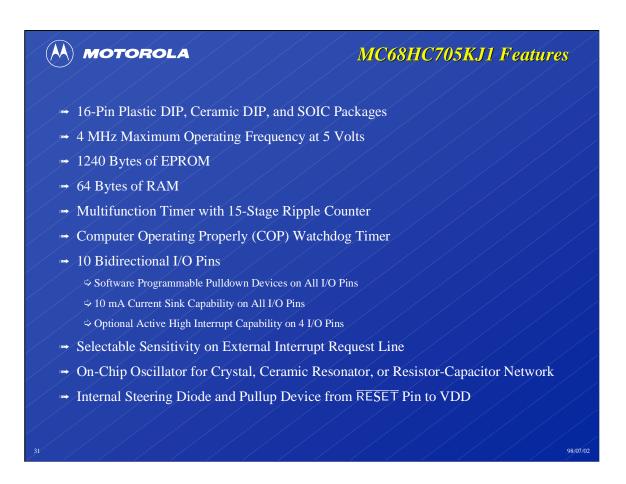

The address space on a 68HC05 device is usually sized just large enough to contain the integrated ROM or EPROM, RAM, and control registers. The MC68HC705KJ1, for example, has a 2-Kbyte ('xx' equals \$07) memory map containing 1240 bytes of EPROM, 64 bytes of RAM, and 14 bytes of other processor accessible resources.

The 68HC05 is also a Big Endian machine. A 16-bit piece of data, or word, is stored in memory with its high byte at address N and its low byte at address N + 1. This ordering applies whether the word is part of an assembled instruction (such as an index register offset), a return address residing on the stack, or the address of a service routine contained in an interrupt vector. See the examples above.

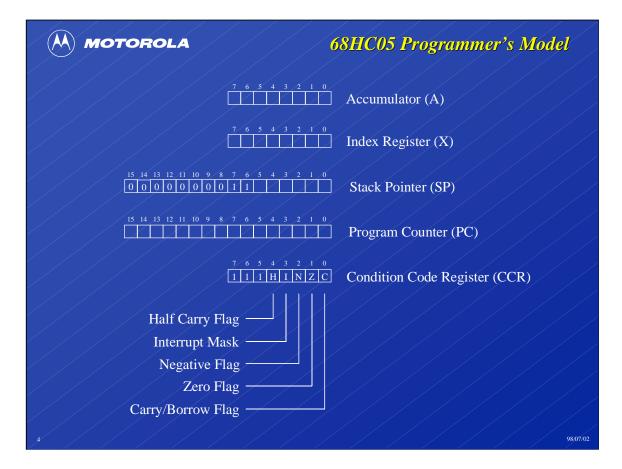

The 68HC05 central processor unit (CPU) consists of an accumulator (A), an index register (X), a stack pointer (SP), a program counter (PC), and a condition code register (CCR).

Data can be read from memory into the accumulator and the index register. Likewise, data can be written into memory from the accumulator and the index register. The accumulator, however, is the only register upon which arithmetic and combinatorial logic operations can be performed. Only the index register can provide user-generated effective addresses for operands read into or written from the accumulator. Both the accumulator and the index register support bitwise shift and rotate operations.

Most accumulator, index register, and memory operations affect status flags in the condition code register. The carry bit is set when an arithmetic carry or borrow has taken place. Shift and rotate operations also move bits through the carry bit. The zero flag is set when all bits of an operand or result are zero. Likewise, the negative flag is set when the MSB of an operand or result is one. The I bit masks interrupts and is set during interrupt processing. Software can also set and clear the I bit. To facilitate BCD arithmetic, the half carry flag is set when a carry from bit three to bit four of an operand occurs as the result of an ADC or ADD instruction.

| ٢, | ١. |   |    |  |     |

|----|----|---|----|--|-----|

|    |    |   |    |  | OLÁ |

| Τ  |    | 1 | ١, |  |     |

#### **Program Counter Operation**

| Program Counter | <b>Opcode/Operand Read</b> | Instruction |

|-----------------|----------------------------|-------------|

| \$1000          | \$B6                       | LDA \$80    |

| \$1001          | \$80                       |             |

| \$1002          | \$47                       | ASRA        |

| \$1003          | \$47                       | ASRA        |

| \$1004          | \$4C                       | I NCA       |

| \$1005          | \$B7                       | STA \$80    |

| \$1006          | \$80                       |             |

| \$1007          | \$CD                       | JSR \$13FE  |

| \$1008          | \$13                       |             |

| \$1009          | \$FÉ                       |             |

| \$13FE          | \$4F                       | CLRA /      |

The program counter (PC) increments by one after each byte of an instruction or operand is read. Jumps, branches, returns, and interrupts load the PC with a new value.

The program counter (PC) points to the address of the current instruction. It advances one byte at a time as instructions and operands are fetched during the course of normal program execution.

Jumps, branches, returns, and interrupts can change program flow and, thus, the normal procession of the PC. The address of a jump or branch is specified by the instruction's addressing mode (i.e. a relative offset for a branch). Return from interrupt (RTI) and from subroutine (RTS) instructions load the PC with a return address stored on the stack. Interrupts load the PC with a value specified by the vector associated with the interrupt source.

|         | before<br>SR SUBROUTIN | E     |        | after<br>JSR SUBROUTINE        |             |        | after<br>RTS                                     |             |

|---------|------------------------|-------|--------|--------------------------------|-------------|--------|--------------------------------------------------|-------------|

| \$00FF  |                        | SP    | \$00FF | Low Byte of<br>Return Address  | [ / ]       | \$00FF | Low Byte of<br>Return Address                    | SP          |

| \$00FE  | xx                     |       | \$00FE | High Byte of<br>Return Address |             | \$00FE | High Byte of<br>Return Address                   |             |

| \$00FD  | xx                     |       | \$00FD | xx                             | <b>←</b> SP | \$00FD | xx                                               |             |

| \$00FC  | xx                     | 1 / , | \$00FC | xx                             |             | \$00FC | xx                                               |             |

| /<br>/f | before<br>INTERRUPT    |       |        | after<br>INTERRUPT             |             |        | after<br>RTI                                     | 1           |

| \$00FF  | <br>                   | → SP  | \$00FF | Low Byte of<br>Return Address  | 1//         | \$00FF | Low Byte of                                      | <b>↓</b> SP |

| \$00FE  |                        |       | \$00FE | High Byte of<br>Return Address |             | \$00FE | Return Address<br>High Byte of<br>Return Address |             |

| \$00FD  | xx                     |       | \$00FD | Index<br>Register              |             | \$00FD | Index<br>Register                                |             |

| \$00FC  | xx                     |       | \$00FC | Accumulator                    |             | \$00FC | Accumulator                                      |             |

| \$00FB  | / xx /                 |       | \$00FB | Condition Code<br>Register     |             | \$00FB | Condition Code<br>Register                       |             |

| \$00FA  | / xx /                 | 1 / / | \$00FA | xx                             | SP SP       | \$00FA | xx                                               |             |

Processor state is saved on the stack when changes in program flow occur. The 68HC05 has a 64-byte hardware-controlled stack. Reset initializes the stack pointer to \$00FF; the RSP instruction does the same. No other instructions allow direct user manipulation of the stack.

When a byte is 'pushed' onto the stack, it is written to the location pointed to by the stack pointer, and then the stack pointer is decremented by one. When a byte is 'pulled' from the stack, the stack pointer is incremented by one, and the location pointed to by the stack pointer is then read.

When the stack pointer is at \$00C0, the next push will store a byte at \$00C0 and roll the stack pointer to \$00FF. This is stack pointer overflow. Subsequent pushes will overwrite information stored on the stack from \$00FF on down. Similarly, underflow occurs when the stack pointer is at \$00FF and the next pull rolls the stack pointer to \$00C0 and reads the byte there.

Subroutines called with the BSR and JSR instructions save a two byte return address on the stack. Interrupts save a two byte return address, the index register, the accumulator, and the condition code register.

The examples above show how subroutine calls and interrupts and their respective return instructions affect the stack.

|                          | -A 68HC05 Instruction Set — Part                                                                     |

|--------------------------|------------------------------------------------------------------------------------------------------|

| Memory Read              | ls & Writes                                                                                          |

| LDA<br>LDX<br>STA<br>STX | load the accumulator<br>load the index register<br>store the accumulator<br>store the index register |

| Register Tran            | sfers                                                                                                |

| TAX<br>TXA               | transfer the accumulator to the index register<br>transfer the index register to the accumulator     |

| Clear Memory             | y & Registers                                                                                        |

| CLR<br>CLRA<br>CLRX      | clear a memory location<br>clear the accumulator<br>clear the index register                         |

The LDA and LDX instructions read or "load" data from memory. The memory location read can be specified using one of several addressing modes discussed later.

The STA and STX instructions write or "store" data to memory. As with LDA and LDX, several addressing modes are available to specify the desired memory location.

The "clear" instructions are memory efficient ways to zero a memory location or register.

For example, CLR \$01 (read as "clear direct address \$01") requires 2 bytes of storage and executes in 5 clock cycles.

On the other hand, LDA #\$00 (read as "load accumulator with immediate value \$00") and STA \$01 (read as "store accumulator to direct address \$01") require 4 bytes of storage and execute in 6 cycles.

Likewise, CLRA and CLRX each require only 1 byte of storage, versus 2 each for LDA #\$00 (read as "load accumulator with immediate value \$00") and LDX #\$00 (read as "load index register with immediate value \$00").

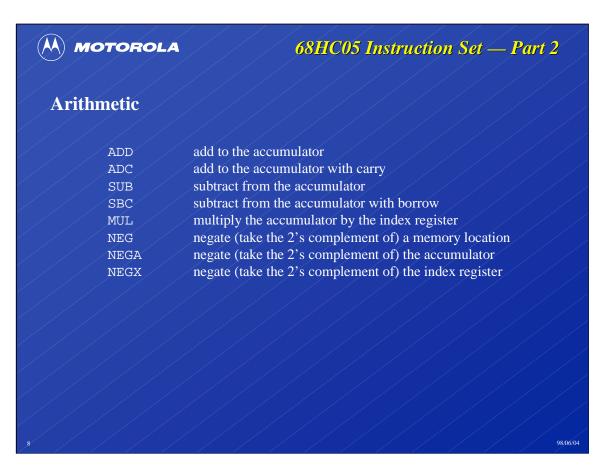

The ADD and SUB instructions, respectively, add or subtract a byte to or from the accumulator. ADC and SBC do the same but with a carry or borrow if the condition code register carry bit (C) is set.

The MUL instruction performs an unsigned multiply of the index register (X) and the accumulator (A). The result is stored with the upper byte in X and the lower byte in A.

NEG, NEGA, and NEGX take the two's complement of a memory location, the accumulator, or the index register. The two's complement of a number is zero minus that number.

| ecrement &   | Increment Memory & Registers                             |

|--------------|----------------------------------------------------------|

| INC          | increment a memory location by one                       |

| INCA         | increment the accumulator by one                         |

| INCX         | increment the index register by one                      |

| DEC          | decrement a memory location by one                       |

| DECA         | decrement the accumulator by one                         |

| DECX         | decrement the index register by one                      |

| oolean Logic |                                                          |

| AND          | logical AND of the accumulator and an operand            |

| ORA          | inclusive OR of the accumulator and an operand           |

| EOR          | exclusive OR of the accumulator and an operand           |

| COM          | take the one's complement of (invert) a memory location  |

| COMA         | take the one's complement of (invert) the accumulator    |

| COMX         | take the one's complement of (invert) the index register |

In addition to the ADD/ADC and SUB/SBC instructions, the 68HC05 has dedicated increment and decrement instructions to add one to or subtract one from a memory location, the accumulator, or the index register.

The AND, ORA, and EOR instructions, respectively, take the logical AND, inclusive OR, and exclusive OR of the accumulator and an operand and store the result in the accumulator.

COM, COMA, and COMX take the one's complement of a memory location, the accumulator, or the index register. The one's complement of a number is simply the binary inversion of its bits.

# NP

| MOTOROLA       | 68HC05 Instruction Set — Part 4                          |

|----------------|----------------------------------------------------------|

| Shift Memory & | Registers                                                |

| ASL            | arithmetically shift a memory location left by one bit   |

| ASLA           | arithmetically shift the accumulator left by one bit     |

| ASLX           | arithmetically shift the index register left by one bit  |

| ASR            | arithmetically shift a memory location right by one bit  |

| ASRA           | arithmetically shift the accumulator right by one bit    |

| ASRX           | arithmetically shift the index register right by one bit |

| LSL            | logically shift a memory location left by one bit        |

| LSLA           | logically shift the accumulator left by one bit          |

| LSLA           | logically shift the index register left by one bit       |

| LSLX           | logically shift the index register left by one bit       |

| LSR            | logically shift a memory location right by one bit       |

| LSRA           | logically shift the accumulator right by one bit         |

| LSRX           | logically shift the index register right by one bit      |

These instructions allow left and right shifts of memory locations, the accumulator, and the index register.

Arithmetic shift left and logical shift left are the same operation, and the ASL, ASLA, and ASLX opcodes are the same as those for LSL, LSLA, and LSLX. In either case, the operand is shifted one bit to the left, with the MSB moving into the condition code register carry (C) bit and a zero moving into the LSB.

Assemblers for the 68HC05 will recognize both the arithmetic shift left and logical shift left instructions and assemble them to the same opcodes.

Arithmetic shift right and logical shift right are two different operations. In both cases, though, the operand is shifted one bit to the right, with the LSB moving into the carry bit.

When an operand is arithmetically shifted right, the MSB remains unchanged. This preserves the sign of the operand. The arithmetic right shift of \$0 (-128 in decimal), for example, is \$C0 (-64 in decimal).

The MSB of an operand logically shifted right is always set to zero.

| cotate Memoi          | ry & Registers                                    |

|-----------------------|---------------------------------------------------|

| ROL                   | rotate a memory location left by one bit          |

| ROLA                  | rotate the accumulator left by one bit            |

| ROLX                  | rotate the index register left by one bit         |

| ROR                   | rotate a memory location right by one bit         |

| RORA                  | rotate the accumulator right by one bit           |

| RORX                  | rotate the index register right by one bit        |

| <b>Test Registers</b> | & Memory                                          |

| BIT                   | bit test the accumulator and set the N or Z flags |

| CMP                   | compare an operand to the accumulator             |

| CPX                   | compare an operand to the index register          |

| TST                   | test a memory location and set the N or Z flags   |

| TSTA                  | test the accumulator and set the N or Z flags     |

| TSTX                  | test the index register and set the N or Z flags  |

Rotate instructions operate in a fashion similar to shift instructions. A rotated operand is first shifted in the direction indicated by the instruction. The empty bit created by the shift (LSB for left and MSB for right) takes the state of the condition code register carry (C) bit, and the carry bit takes the state of the bit shifted out of the operand (MSB for left and LSB for right).

The BIT instruction sets the condition code register negative (N) or (Z) flags based on the logical AND of the accumulator and an operand. The result of this logical AND is discarded.

The compare instructions allow subsequent branch operations to determine if an argument is equal to, not equal to, greater than, greater than or equal to, less than, or less than or equal to the value in the designated register.

A register and an operand are "compared" by non-destructively subtracting the operand from the register and setting the condition code register C, N, or Z bits.

The test instructions set the negative and zero flags by non-destructively subtracting zero from a memory location (TST), the accumulator (TSTA), or the index register (TSTX).

| A) MOTOROL    | -A 68HC05 Instruction Set — Part              |

|---------------|-----------------------------------------------|

| Branches on ( | Condition Code Register Bits                  |

| BCC           | branch if carry clear ( $C = 0$ )             |

| BCS           | branch if carry set $(C = 1)$                 |

| BEQ           | branch if equal $(Z = 0)$                     |

| BNE           | branch if not equal $(Z = 1)$                 |

| внсс          | branch if half carry clear $(H = 0)$          |

| BHCS          | branch if half carry set $(H = 1)$            |

| BHI           | branch if higher (C or $Z = 0$ )              |

| BHS           | branch if higher or same $(C = 0)$            |

| BLS           | branch if lower or same (C or $Z = 1$ )       |

| BLO           | branch if lower $(C = 1)$                     |

| BMI           | branch if minus $(N = 1)$                     |

| BPL           | branch if plus $(N = 0)$                      |

| BMC           | branch if interrupts are not masked $(I = 0)$ |

| BMS           | branch if interrupts are masked $(I = 1)$     |

|               |                                               |

|               |                                               |

|               |                                               |

This group of branch instructions allow changes in program flow based on the states of various condition code register bits. Branch instructions use the relative addressing mode and can move backward 128 bytes or forward 127 bytes in memory from the address of the next instruction.

Notice that the BCS (branch if carry set) and BLO (branch if lower) instructions test the same condition code register bit. These instructions are the same and have the same opcode. The same is also true of BCC (branch if carry clear) and BHS (branch if higher or same).

Assemblers for the 68HC05 will recognize BCS, BLO, BCC, and BHS and assemble them to the appropriate opcodes.

| Oth | her Branche | es                                                    |

|-----|-------------|-------------------------------------------------------|

|     | BIH         | branch if $\overline{IRQ}$ pin is high                |

|     | BIL         | branch if $\overline{IRQ}$ pin is low                 |

|     | BRA         | branch always                                         |

|     | BRN         | branch never                                          |

|     | BSR         | branch to subroutine and save return address on stack |

| Sin | gle Bit Ope | rations                                               |

|     | BCLR        | clear the designated memory bit                       |

|     | BSET        | set the designated memory bit                         |

|     | BRCLR       | branch if the designated memory bit is clear          |

|     | BRSET       | branch if the designated memory bit is set            |

These "other" branch instructions do not examine bits in the condition code register to change program flow. BIH and BIL, in particular, test the state of the actual  $\overline{IRQ}$  pin, not the condition code register interrupt mask (I) bit.

BRN is useful as a three clock cycle no operation instruction. The actual NOP instruction executes in two clock cycles and has a different opcode.

The single bit operations allow setting and clearing of and branching on the set or clear states of single bits in a byte operand. These instructions use the direct addressing mode only and can operand on any bit in the first 256 locations of memory (i.e. internal RAM and peripheral control registers).

The BCLR and BSET instructions each have eight opcodes, one for each bit in a byte. BCLR and BSET require two bytes of storage and execute in five clock cycles which makes them the most memory and time efficient way to clear or set a bit. The same operations using the LDA, AND/ORA, and STA instructions require six bytes and nine clock cycles.

BRCLR and BRSET are similarly efficient, needing only three bytes and five cycles for an operation that would otherwise require six bytes and eight cycles if using a sequence of LDA, AND/ORA, and BEQ/BNE instructions.

|                   | LA 68HC05 Instruction Set — Part 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Jumps & Ret       | urns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| JMP               | jump to specified address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| JSR               | jump to subroutine and save return address on stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RTS               | pull address from stack and return from subroutine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RTI               | pull registers from stack and return from interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Miscellaneous     | s Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CLC               | clear the condition code register carry bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SEC               | set the condition code register carry bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CLI               | clear the condition code register interrupt mask bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SEI               | set the condition code register interrupt mask bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                   | all Channels in it is the second |

| SWI               | software initiated interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                   | reset the stack pointer to \$00FF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SWI<br>RSP<br>NOP | reset the stack pointer to \$00FF<br>no operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SWI<br>RSP        | reset the stack pointer to \$00FF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

JMP and JSR are analogous to BRA and BSR and allow changes in program flow to be made with 16-bit addresses or index register offsets.

RTS is used to return from a BSR or JSR subroutine call. It pulls only a return address from the stack. RTI is used to return from an interrupt service routine and pulls the condition code register, accumulator, and index register, as well as a return address, from the stack.

The SWI instruction allows an interrupt to be taken under software control, regardless of the state of the condition code register interrupt mask (I) bit. SWI stacks a return address and all of the CPU registers, and jumps to an address specified by its own interrupt vector.

WAIT and STOP allow a 68HC05 device two enter one of two low power modes. WAIT clears the interrupt mask bit (I = 0) and halts the CPU. This allows interrupts from on-chip peripherals or external interrupt pins (e.g.  $\overline{IRQ}$ ) to re-start execution.

STOP also clears the I bit, but it halts the entire MCU by stopping the clock oscillator. This is the lowest power mode available on a 68HC05 and only interrupts from dedicated external interrupt pins, like  $\overline{IRQ}$ , can re-start execution.

#### M) MOTOROLA

Addressing Modes — Summary

# Several different addressing modes are available to support the data requirements of different 68HC05 instructions.

| Inherent               | (INH)    |

|------------------------|----------|

| Immediate              | (IMM)    |

| Extended               | (EXT)    |

| Direct                 | (DIR)    |

| Indexed, 16-Bit Offset | (IX2)    |

| Indexed, 8-Bit Offset  | (IX1)    |

| Indexed, No Offset     | (IX)     |

| Relative               | (REL)    |

| Bit Set and Clear      | (BSC)    |

| Bit Test and Branch    | (BTB)    |

|                        |          |

|                        | 98/06/04 |

The simple availability of powerful instructions does not alone comprise a good microcontroller architecture. Flexible addressing modes are also needed so that these instructions can efficiently access the different types of data that may be distributed in memory.

In addition to its 65 basic instructions, the 68HC05 has eight addressing modes that determine the source and/or destination of the data upon which these instructions operate.

For practical reasons, no single 68HC05 instruction can use all eight addressing modes. Branches, for example, are relative operations, so it would make no sense for them to use any addressing mode other than relative.

On the other hand, those instructions that must be capable of operating on any memory location and the accumulator or the index register should have the widest selection of addressing modes. Thus, these instructions, like ADD, CMP, and LDA, can use all modes except inherent and relative.

| Motorola Addres                                                                          | ssing Modes — INH                |

|------------------------------------------------------------------------------------------|----------------------------------|

| The operand of an instruction that uses inherent addressing is the instruction's opcode. | implied by or <i>inherent</i> in |

| Some instructions explicitly name registers                                              |                                  |

| ASLA, CLRX, DECA, INCX, ROLA, RORX                                                       | , RSP, TAX, TXA                  |

| Others explicitly name condition code register bits                                      |                                  |

| CLC, CLI, SEC, SEI                                                                       |                                  |

| Still others affect one or more unnamed registers                                        |                                  |

| MUL, RTI, RTS, STOP, SWI, WAIT                                                           |                                  |

| And some have no operands whatsoever                                                     |                                  |

| NOP                                                                                      |                                  |

|                                                                                          |                                  |

| 16                                                                                       | 98,06/04                         |

Instructions that use inherent addressing need only one byte of program storage. These are the simplest 68HC05 instructions because they have fixed operands.

Any instruction that operates directly on a named register without an attendant read or write cycle uses inherent addressing. ASLX, CLRA, DECX, INCA, RSP, and TXA are obvious examples. The same also applies to the CLC, CLI, SEC, and SEI instructions that directly manipulate condition code register bits.

Inherent mode instructions that do not explicitly name registers typically affect multiple registers or a single condition code register bit. MUL, for example, uses the accumulator and the index register. SWI and RTI operate on all of the CPU registers, while STOP and WAIT only clear the condition code register interrupt mask (I) bit.

Instructions that use inherent addressing can have no other addressing modes, only analogous instructions that use other addressing modes. For example, LSLA, LSLX, and LSL all perform a logical shift left. LSLA operates only on the accumulator, LSLX only on the index register, and LSL only on a memory location.

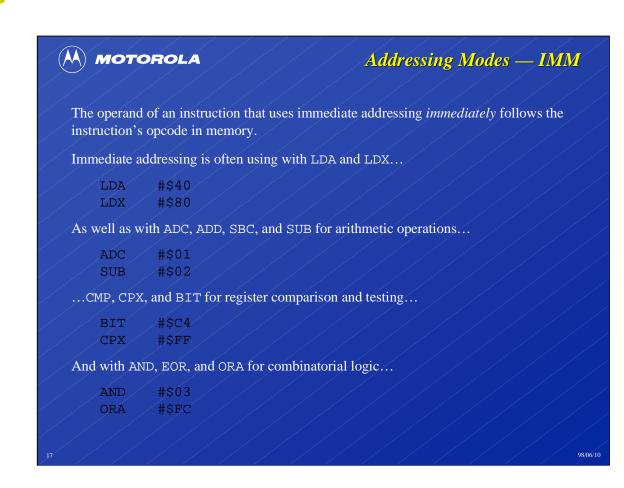

Immediate addressing is used to specify values that remain constant during program execution. On the 68HC05, the address from which an immediate value is read is always one more than the address of the instruction reading that value.

Assembling LDA #\$40 at address \$1000, for example, will place \$A6 (the opcode for LDA when immediate addressing is used) in memory location \$1000 and \$40 (the operand) in memory location \$1001.

The pound sign (#) is used to designate an operand as an immediate value in Motorola assembly language syntax. It can also be used with assembler-defined symbols. For example, if ASCTONUM is equated to \$30, the instruction SUB #ASCTONUM will subtract \$30 (decimal 48) from the accumulator.

Pound sign omission is a common assembly language programming error. LDA \$40 will not load the accumulator with immediate value \$40 (decimal 64). The absent pound sign designates \$40 as a direct address, so LDA \$40 will load the accumulator with the contents of memory location \$0040. For similar reasons, adding a pound sign where it is not required is also a common error.

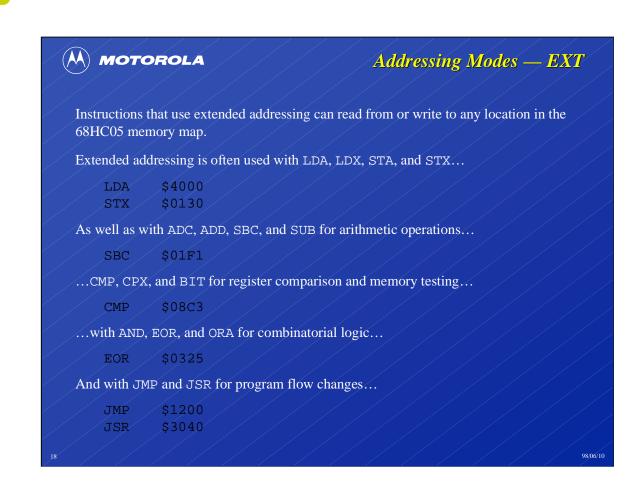

Extended addressing allows any location in the 68HC05 memory map to be read from or written to using a single instruction. The address is always specified using a 16-bit value.

All instructions that use extended mode addressing require three bytes of program storage, one for the opcode and two for the operand.

| Instructions<br>\$00 to \$FF. | that use direct addressing  | can only read from or write to memory locations |

|-------------------------------|-----------------------------|-------------------------------------------------|

| All read-mo                   | dify-write instructions sup | port direct addressing                          |

| ASL                           | \$00                        |                                                 |

| ASR                           | \$FF                        |                                                 |

| CLR                           | \$02                        |                                                 |

| COM                           | \$FD                        |                                                 |

| DEC                           | \$04                        |                                                 |

| INC                           | \$FB                        |                                                 |

| LSL                           | \$06                        |                                                 |

| LSR                           | \$F9                        |                                                 |

| NEG                           | \$08                        |                                                 |

| ROL                           | \$F7                        |                                                 |

| ROR                           | \$0A                        |                                                 |

| TST                           | \$F5                        |                                                 |

|                               |                             | addressing also support direct addressing.      |

Direct addressing is like a simplified form of extended addressing. It allows any location between \$0000 and \$00FF to be read from or written to by specifying only the lower eight address bits. Direct mode instructions execute in one less cycle and require one less byte of storage than their extended mode counterparts.

Some instructions, like test, shift, rotate, complement, negate, decrement, and increment have direct, but not extended, mode forms. This may seem to be an omission from the 68HC05, but careful consideration reveals that this is not the case.

Every instruction that has a direct, but not extended, mode form performs a read-modify-write operation. The targets for these instructions must be on-chip RAM or peripheral control registers. Most RAM on 68HC05 devices is located below address \$00FF. Similarly, on-chip peripheral registers are mapped starting at address \$0000.

Because the vast majority of read-modify-write operations will target addresses between \$0000 and \$00FF, the lack of extended addressing (as well as indexed addressing with 16-bit offsets) does not impair device functionality.

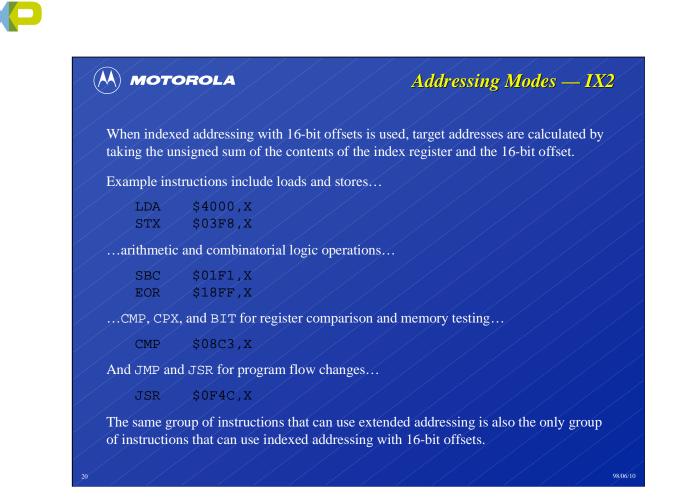

Instructions that use indexed addressing with 16-bit offsets can read from or write to any location in the 68HC05 memory map. These instructions always require three bytes of storage.

Target addresses are formed by taking the unsigned sum of the 16-bit offset and the contents of the index register and always range from \$0000 to \$FFFF. Thus, if X = \$41, the instruction STA \$FFE0,X will write to address \$0021.

Indexed addressing with 16-bit offsets is especially useful for accessing tabular or string data stored in on-chip ROM which, on most 68HC05 devices, resides primarily above \$0100.

|             | that use indexed addressi<br>ation between \$0000 and | ng with 8-bit offsets can read from or write to any \$01FE inclusive. |

|-------------|-------------------------------------------------------|-----------------------------------------------------------------------|

| All read-mo | dify-write instructions su                            | pport this addressing mode                                            |

| ASL         | \$00,X                                                |                                                                       |

| ASR         | \$FF,X                                                |                                                                       |

| CLR         | \$02,X                                                |                                                                       |

| COM         | \$FD,X                                                |                                                                       |

| DÉC         | \$04,X                                                |                                                                       |

| INC         | \$FB,X                                                |                                                                       |

| LSL         | \$06,X                                                |                                                                       |

| LSR         | \$F9,X                                                |                                                                       |

| NEG         | \$08,X                                                |                                                                       |

| ROL         | \$F7,X                                                |                                                                       |

| ROR         | \$0A,X                                                |                                                                       |

| TST         | \$F5,X                                                |                                                                       |

Instructions that use indexed addressing with an 8-bit offset have access to the first 511 locations in memory. These instructions execute in one less cycle and require one less byte of storage than their counterparts that use 16-bit offsets.

Target addresses are formed by taking the unsigned sum of the 8-bit offset and the contents of the index register and can range from \$0000 (offset = 00000 and X = 000) to \$01FE (offset = FF and X = FF).

Most 68HC05 devices have 512 bytes of RAM or less, which makes indexed addressing with 8-bit offsets especially useful for operations on tabular or string data maintained in on-chip RAM.

| simply the co |                                        | at uses indexed addressing without an offset is<br>r zero extended to 16 bits. |

|---------------|----------------------------------------|--------------------------------------------------------------------------------|

| All read-mod  | lify-write instructions sup            | port this addressing mode                                                      |

| ASL           | ,x                                     |                                                                                |

| ASR           | , X                                    |                                                                                |

| CLR           |                                        |                                                                                |

| СОМ           | X                                      |                                                                                |

| DEC           | , X                                    |                                                                                |

| INC           |                                        |                                                                                |

| LSL           | X                                      |                                                                                |

| LSR           | , x / / /                              |                                                                                |

| NEG           | X                                      |                                                                                |

| ROL           | ,x                                     |                                                                                |

| ROR           | ,x//////////////////////////////////// |                                                                                |

|               | X                                      |                                                                                |

Instructions that use indexed addressing without offsets can only access memory locations \$00 to \$FF. Target addresses for these instructions are formed by zero extending the contents of the 8-bit index register to 16 bits.

This is the fastest indexed addressing mode, with instructions needing one less cycle to execute than if an 8-bit offset if used. Looked at differently, these instructions execute as quickly as their direct mode counterparts but require only one byte of storage.

| M MOTOROLA Addressing Modes — RE                                                                                                                                                   |          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Relative addressing is used only by branch instructions to calculate the target address of a change in program flow <i>relative</i> to the value of the program counter (PC).      | £        |

| Each branch instruction requires two bytes of storage — one for the branch opcode and one for the signed two's complement 8-bit relative offset.                                   |          |

| This offset is relative to the address of the next instruction, which is the address of the branch instruction plus two.                                                           |          |

| Consider the following line of code                                                                                                                                                |          |

| HERE BEQ THERE                                                                                                                                                                     |          |

| If the label HERE equates to address \$1000 and this is a <b>FORWARD</b> branch, the target address can be between \$1002 (offset of \$00) and \$1081 (offset of \$7F).            |          |

| Similarly, if the label HERE equates to address \$1000 and this is a <b>REVERSE</b> branch, the target address can be between \$0F82 (offset of \$80) and \$1000 (offset of \$FE). |          |

|                                                                                                                                                                                    | 98/06/09 |

Only branch instructions use relative addressing. A branch instruction executes in three clock cycles and consists of two bytes. The first byte is the opcode for the particular branch condition, and the second byte is a signed two's complement offset from the address of the next instruction.

The target address of a branch instruction is calculated as...

# New Program Counter = Address of Branch Opcode + 2 + Signed Offset

Because the offset for a branch is from the address of the next instruction, the smallest practical negative offset is -2 (\$FE). An offset of zero causes no change in program flow, essentially making the branch instruction a three cycle NOP.

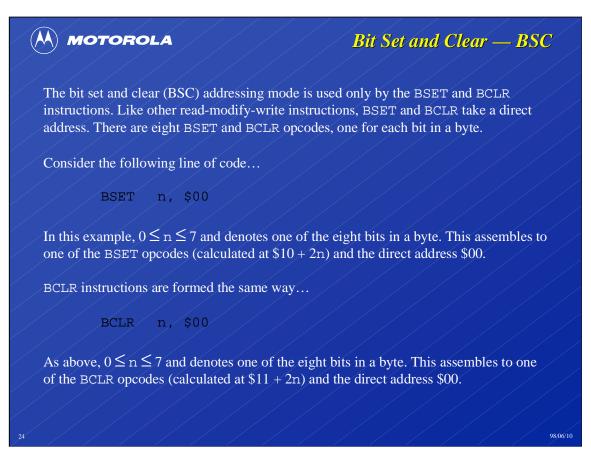

Bit set and bit clear instructions have a unique addressing mode that is similar to direct mode. The source code format for these instructions is:

# BSET/BCLR bit\_number, direct\_address

Although each instruction has two operands, an assembled BSET or BCLR instruction consists only of an opcode and a direct address. Each bit that can be modified has its own BSET and BCLR opcodes.

The BSET opcodes for bits 0, 1, 2, 3, 4, 5, 6, and 7 are \$10, \$12, \$14, \$16, \$18, \$1A, \$1C, and \$1E, respectively. Similarly, the BCLR opcodes for bits 0, 1, 2, 3, 4, 5, 6, and 7 are \$11, \$13, \$15, \$17, \$19, \$1B, \$1D, and \$1F, respectively.

Like other read-modify-write instructions that take a direct address, BSET and BCLR execute in 5 clock cycles.

| (/ | M MOTOROLA Bit Test and Branch – BTB                                                                                                                                                                                                                                      |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | The bit test and branch (BTB) addressing mode is used only by the BRSET and BRCLR instructions. BRSET and BRCLR take a direct address and have eight opcodes to denote each bit in a byte, just like BSET and BCLR.                                                       |

|    | Consider the following line of code                                                                                                                                                                                                                                       |

|    | BRSET n, \$00, TARGET                                                                                                                                                                                                                                                     |

|    | In this example, $0 \le n \le 7$ and denotes one of the eight bits in a byte. This assembles to one of the BRSET opcodes (calculated at $\$00 + 2n$ ), the direct address $\$00$ , and an offset to TARGET relative to the address of the instruction that follows BRSET. |

|    | BRCLR instructions are formed the same way                                                                                                                                                                                                                                |

|    | BRCLR n, \$00, TARGET                                                                                                                                                                                                                                                     |

|    | As above, $0 \le n \le 7$ and denotes one of the eight bits in a byte. This assembles to one of the BRCLR opcodes (calculated at $\$01 + 2n$ ), the direct address $\$00$ , and an offset to TARGET relative to the address of the instruction that follows BRCLR.        |

| 5  | 9806/10                                                                                                                                                                                                                                                                   |

Like the bit set and bit clear instructions, the branch on bit set and branch on bit clear instructions also have a unique addressing mode. This bit test and branch (BTB) addressing mode is best described as a cross between the bit set and clear (BSC) and relative (REL) addressing modes. The source code format for these instructions is:

# BRSET/BRCLR bit\_number, direct\_address, offset

Although each instruction has three operands, an assembled BRSET or BRCLR instruction consists of an opcode, a direct address, and a signed two's complement offset to the target address. Each bit that can be tested has its own BRSET and BRCLR opcodes.

Target addresses for bit test and branch instructions are calculated as...

# New Program Counter = Address of BRCLR/BRSET Opcode + 3 + Signed Offset

Like a regular branch, the target address for BRSET and BRCLR is offset from the address of the next instruction. This makes the smallest practical negative offset for branch on bit set/clear -3 (\$FD). These instructions execute in five clock cycles.

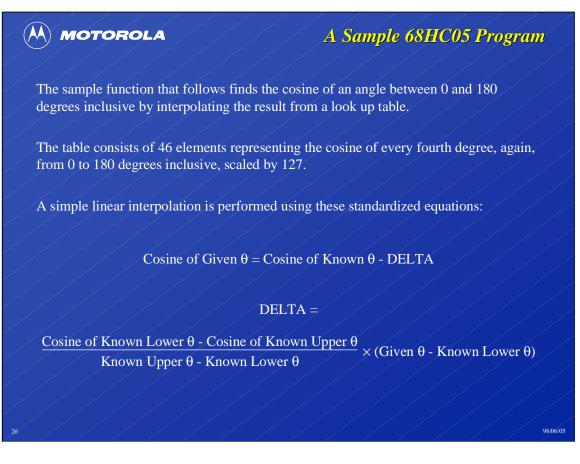

To simplify the interpolation math, the look up table includes the cosine of every fourth degree  $(0^{\circ}, 4^{\circ}, 8^{\circ}, \text{ and so on})$  rather than, say, every fifth degree  $(0^{\circ}, 5^{\circ}, 10^{\circ}, \text{ and so on})$ .

This makes the difference between the known upper and lower angles four, and allows the division of the difference between the cosines of the known lower and upper angles to be accomplished with two right shift instructions.

Similarly, because all the known angles are multiples of four, the difference between the given angle and the known lower angle is found by logically ANDing the given angle with three.

These simplifications allow the interpolation to be taken with only three mathematical operations:

- 1. the difference between the cosine of the known angle and delta

- 2. the difference in the numerator of the delta fraction

- 3. the product of the two delta terms

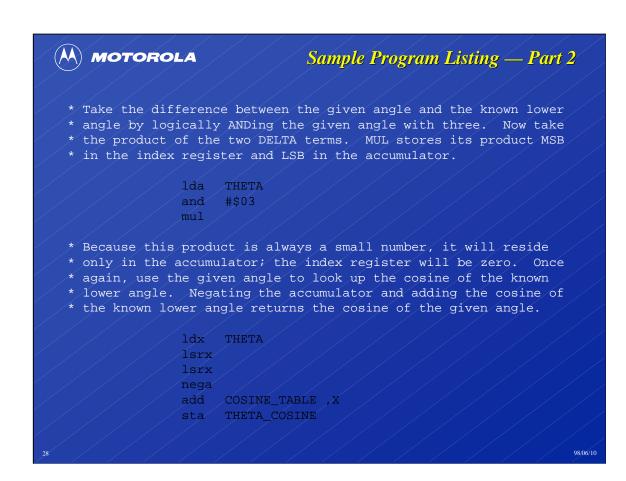

M MOTOROLA Sample Program Listing — Part 1 \* The function begins by reading the given angle, THETA, from \* on-chip RAM (using direct mode addressing) and dividing it by \* four. This is used as an offset into the look up table. FIND\_COSINE ldx THETA lsrx lsrx \* Using indexed addressing with a 16-bit offset, the cosine of \* the known lower angle is loaded into the accumulator, and the \* cosine of the known upper angle is subtracted from it. This \* difference is then divided by four, which is the difference \* between the known upper angle and the known lower angle. Save \* this result in the index register to take the delta product. sub COSINE TABLE + 1,X lsra 98/06/10

The FIND\_COSINE subroutine starts by reading the given angle, THETA, from on-chip RAM. This would likely be done using direct addressing, because RAM on most 68HC05 devices is located below \$00FF. There is usually no explicit need to denote whether an instruction should use direct or extended addressing — most assemblers will make this determination automatically, based on the value to which the symbol THETA is equated.

THETA is loaded into the index register and shifted right two places (effectively dividing it by four) and used with the offset COSINE\_TABLE, to read the cosine of the first known angle less than THETA. The value at COSINE\_TABLE + 1 subtracted from the accumulator would be the cosine of the first known angle greater than THETA. The offset COSINE\_TABLE can be eight or sixteen bits, and as with THETA, most assemblers will determine which addressing mode should be used.

The difference between the cosines of the first known angles less than and greater than THETA is then divided by four (again, using two right shift instructions). Next, it is transferred to the index register where it will be multiplied by the difference between THETA and the first known angle less than THETA.

As noted previously, the following relation is always true because the difference between any two adjacent known angles is always four.