# **User's Manual**

# PREFACE

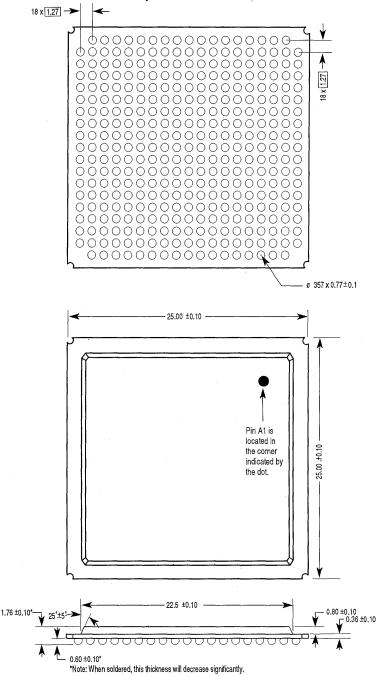

The complete documentation package for the MC68356 consists of MC68356UM/AD, the *MC68356 Signal Processing Communications Engine User's Manual;* MC68356/D, the *MC68356 Signal Processing Communications Engine Product Brief;* DSP56KFAMUM/AD the *DSP56000 Digital Signal Processor Family Manual;* and M68000PM/AD, the *M68000 Programmer's Reference Manual.* Information on Plastic Ball Grid Array (PBGA) layout considerations is available in AN1231/D, "Plastic Ball Grid Array Application Note", available from your local Motorola sales office.

The *MC68356 Signal Processing Communications Engine User's Manual* describes the programming, capabilities, registers, and operation of the MC68356; the *MC68356 Signal Processing Communications Engine Product Brief* provides a brief description of the MC68356 capabilities; the *DSP56000 Digital Signal Processor Family Manual* describes programming and the instruction set for the DSP engine; and the *M68000 Programmer's Reference Manual* describes programming and the instruction set for the IMP processor.

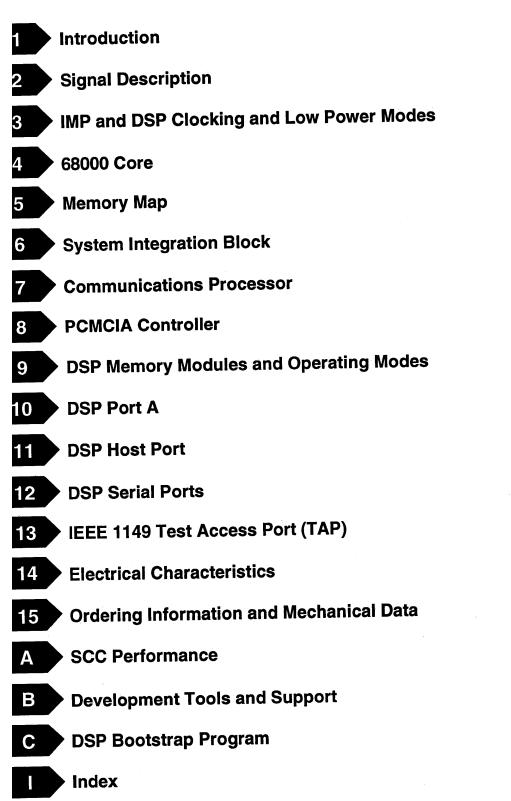

This user's manual is organized as follows:

- Section 1 Introduction

- Section 2 Signal Description

- Section 3 IMP and DSP Clocking and Low Power Modes

- Section 4 68000 Core

- Section 5 Memory Map

- Section 6 System Integration Block

- Section 7 Communications Processor

- Section 8 PCMCIA Controller

- Section 9 DSP Memory Modules and Operating Modes

- Section 10 DSP Port A

- Section 11 DSP Host Port

- Section 12 DSP Serial Ports

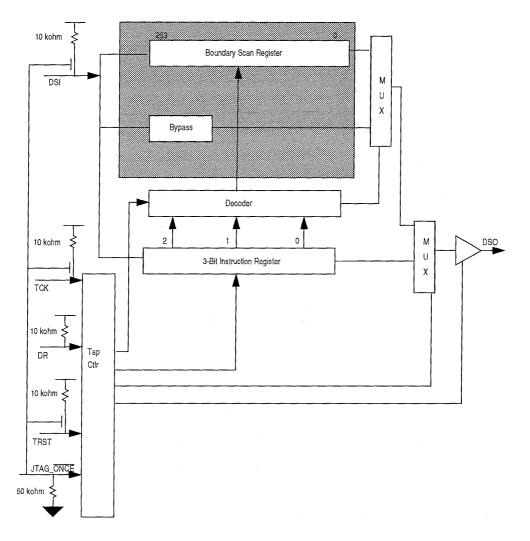

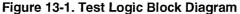

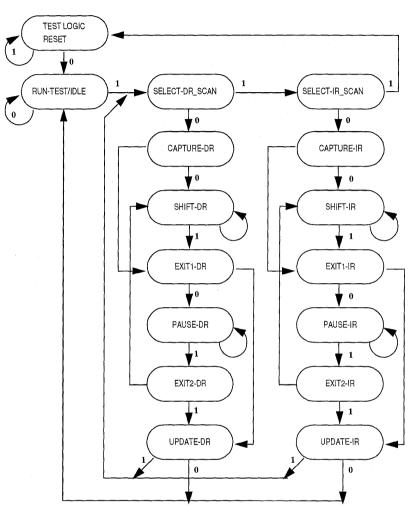

- Section 13 IEEE 1149 Test Access Port (TAP)

- Section 14 Electrical Specifications

- Section 15 Ordering Information and Mechanical Data

- Appendix A SCC Performance

- Appendix B Development Tools and Support

- Appendix C DSP Bootstrap Program

# **Applications and Technical Information**

For questions or comments pertaining to technical information, questions, and applications, please contact one of the following sales offices nearest you.

i

# --- Sales Offices ---

#### **UNITED STATES**

| ALABAMA, Huntsville<br>ARIZONA, Tempe<br>CALIFORNIA, Agoura Hills<br>CALIFORNIA, Los Angeles<br>CALIFORNIA, Irvine<br>CALIFORNIA, San Diego<br>CALIFORNIA, San Diego<br>CALIFORNIA, Sunnyvale<br>COLORADO, Colorado Springs<br>COLORADO, Colearwater<br>GEORIDA, Pompano Beach/<br>FLORIDA, Clearwater<br>GEORGIA, Atlanta<br>IDAHO, Boise<br>ILLINOIS, Chicago/Hoffman Estates<br>INDIANA, Fort Wayne<br>INDIANA, Fort Wayne<br>INDIANA, Kokomo<br>IOWA, Cedar Rapids<br>KANSAS, Kansas City/Mission<br>MARYLAND, Columbia | $\begin{array}{c} (205) \ 464-6800\\ (602) \ 897-5056\\ (818) \ 706-1929\\ (310) \ 417-8848\\ (714) \ 753-7360\\ (916) \ 922-7152\\ (619) \ 541-2163\\ (408) \ 749-0510\\ (719) \ 599-7497\\ (303) \ 337-3434\\ (203) \ 949-4100\\ (407) \ 628-2636\\ (305) \ 486-9776\\ (813) \ 538-7750\\ (404) \ 729-7100\\ (208) \ 323-9413\\ (708) \ 490-9500\\ (219) \ 436-5818\\ (317) \ 571-0400\\ (317) \ 457-6634\\ (319) \ 373-1328\\ (913) \ 451-8555\\ (410) \ 381-1570\\ \end{array}$ | MASSACHUSETTS, Marborough<br>MASSACHUSETTS, Woburn<br>MICHIGAN, Detroit<br>MINNESOTA, Minnetonka<br>MISSOURI, St. Louis<br>NEW JERSEY, Fairfield<br>NEW YORK, Hauppauge<br>NEW YORK, Hauppauge<br>NEW YORK, Poughkeepsie/Fishkill<br>NORTH CAROLINA, Raleigh<br>OHIO, Cleveland<br>OHIO, Columbus Worthington<br>OHIO, Columbus Worthington<br>OHIO, Columbus Worthington<br>OHIO, Dayton<br>OKLAHOMA, Tulsa<br>OREGON, Portland<br>PENNSYL VANIA, Colmar<br>Philadelphia/Horsham<br>TEXNESSEE, Knoxville<br>TEXAS, Austin<br>TEXAS, Houston<br>TEXAS, Plano<br>VIRGINIA, Richmond<br>WASHINGTON, Bellevue<br>Seattle Access<br>WISCONSIN, Milwaukee/Brookfield |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

Field Applications Engineering Available Through All Sales Offices

| CANADA<br>BRITISH COLUMBIA, Vancouver<br>ONTARIO, Toronto<br>ONTARIO, Ottawa | (604) 293-7605<br>(416) 497-8181<br>(613) 226-3491 | MALAYSIA, Penang<br>MEXICO, Mexico City<br>MEXICO, Guadalajara<br>Marketing | 60(4)374514<br>52(5)282-2864<br>52(36)21-8977<br>52(36)21-9023 |

|------------------------------------------------------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------|

| QUEBEC, Montreal                                                             | (514) 731-6881                                     | Customer Service<br>NETHERLANDS, Best                                       | 52(36)669-9160<br>(31)49988 612 11                             |

| INTERNATIONAL                                                                |                                                    | PUERTO RICO, San Juan                                                       | <b>` (809)793-217</b> (                                        |

| AUSTRALIA, Melbourne<br>AUSTRALIA, Sydney                                    | (61-3)887-0711<br>(61(2)906-3855                   | SINGAPORE<br>SPAIN, Madrid                                                  | (65)2945438<br>34(1)457-8204                                   |

| BRAZIL, Sao Paulo                                                            | 55(11)815-4200                                     | or                                                                          | 34(1)457-8254                                                  |

| CHINA, Beijing<br>FINLAND, Helsinki                                          | 86 505-2180<br>358-0-35161191                      | SWEDEN, Solna<br>SWITZERLAND, Geneva                                        | 46(8)734-8800<br>41(22)7991111                                 |

| Car Phone                                                                    | 358(49)211501                                      | SWITZERLAND, Zurich                                                         | 41`(1)´730 4074                                                |

| FRANCE, Paris/Vanves<br>GERMANY, Langenhagen/ Hanover                        | 33(1)40 955 900<br>49(511)789911                   | TAIWAN, Taipei<br>THAILAND, Bangkok                                         | 886(2)717-7089<br>(66-2)254-4910                               |

| GERMANY, Munich                                                              | 49 89 92103-0                                      | UNITED KINGDOM, Aylesbury                                                   | 44(296)395-252                                                 |

| GERMANY, Nuremberg<br>GERMANY, Sindelfingen                                  | 49 911 64-3044<br>49 7031 69 910                   | FULL LINE REPRESE                                                           | NTATIVES                                                       |

| GERMANY, Wiesbaden                                                           | 49 611 761921                                      | COLORADO, Grand Junction                                                    |                                                                |

| HONG KONG, Kwai Fong<br>Tai Po                                               | 852-4808333<br>852-6668333                         | Cheryl Lee Whitely<br>KANSAS, Wichita                                       | (303) 243-9658                                                 |

| INDIA, Bangalore                                                             | (91-812)627094                                     | Melinda Shores/Kelly Greiving                                               | (316) 838 0190                                                 |

|                                                                              | 972(3)753-8222                                     | NEVADA, Reno<br>Galena Technology Group                                     | (702) 746 0642                                                 |

| ITALY, Milan<br>JAPAN, Aizu                                                  | 39(2)82201<br>81(241)272231                        | NEW MEXICO, Albuguerque                                                     | (702) 746 0642                                                 |

| JAPAN, Atsugi                                                                | 81(0462)23-0761                                    | S&S Technologies, Inc.                                                      | (505) 298-7177                                                 |

| JAPAN, Kumagaya<br>JAPAN, Kyushu                                             | 81(0485)26-2600<br>81(092)771-4212                 | <b>UTAH</b> , Salt Lake City<br>Utah Component Sales, Inc.                  | (801) 561-5099                                                 |

| JAPAN, Mito                                                                  | 81(0292)26-2340                                    | WASHINGTON, Spokane<br>Doug Kenley                                          | (509) 924-2322                                                 |

| JAPAN, Nagoya<br>JAPAN, Osaka                                                | 81(052)232-1621<br>81(06)305-1801                  | ARGENTINÁ, Buenos Aires                                                     | . ,                                                            |

| JAPAN, Sendai                                                                | 81(22)268-4333                                     | Argonics, S.A.                                                              | (541) 343-1787                                                 |

| JAPAN, Tachikawa<br>JAPAN, Tokyo                                             | 81(0425)23-6700<br>81(03)3440-3311                 | HYBRID COMPONENTS                                                           |                                                                |

| JAPAN, Yokohama<br>KOREA, Pusan                                              | 81 (045) 472-2751<br>82 (51) 4635-035              | Elmo Semiconductor<br>Minco Technology Labs Inc.                            | (818) 768-7400<br>(512) 834-2022                               |

| KOREA, Pusan<br>KOREA, Seoul                                                 | 82(2)554-5188                                      | Semi Dice Inc.                                                              | (310) 594-4631                                                 |

# TABLE OF CONTENTS

Paragraph Number

#### Title

Page Number

#### PREFACE

#### Section 1 Introduction

| 1.1   | MC68356 Key Features                                            | 1-1 |

|-------|-----------------------------------------------------------------|-----|

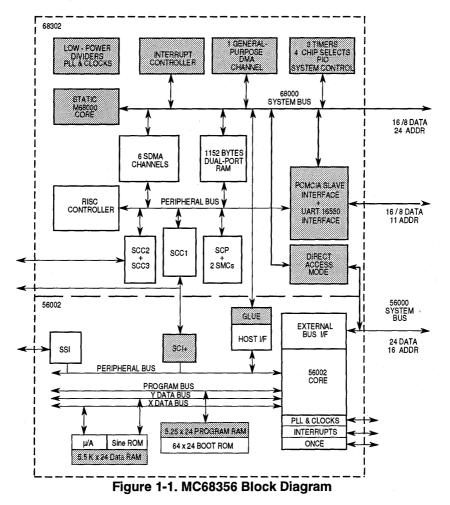

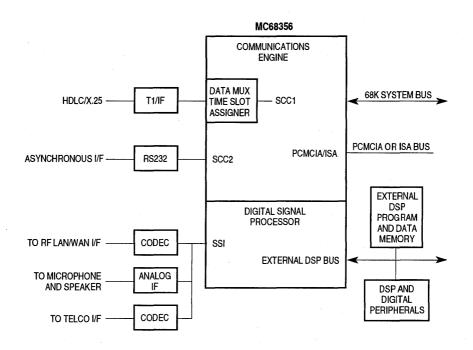

| 1.2   | MC68356 Architecture Overview                                   |     |

| 1.2.1 | Integrated Multiprotocol Processor (IMP) Portion of the MC68356 |     |

| 1.2.2 | DSP Portion of the MC68356                                      |     |

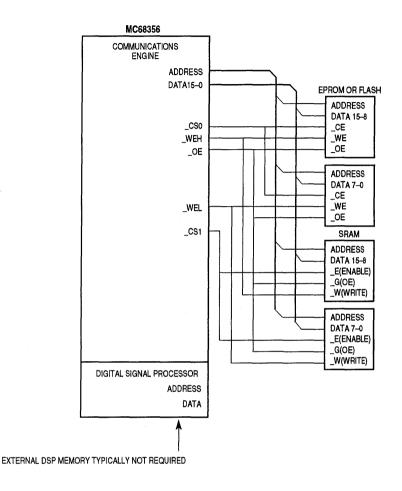

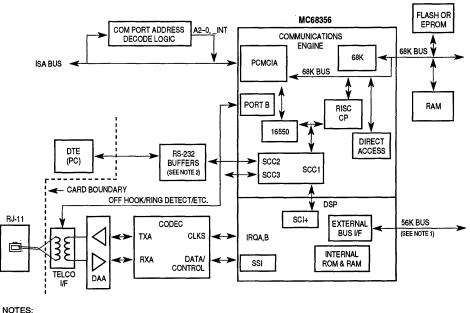

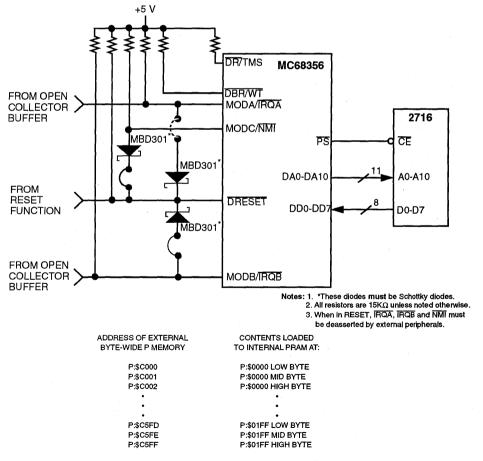

| 1.3   | Designing with MC68356                                          | 1-6 |

| 1.3.1 | Hardware Compatibility Issues                                   |     |

| 1.3.2 | Glueless Interfaces                                             |     |

| 1.3.3 | Software Compatibility Issues                                   | 1-7 |

| 1.4   | Applications for MC68356                                        |     |

| 1.4.1 | General Purpose Application                                     |     |

| 1.4.2 | MC68356 Minimum Memory System Configuration                     |     |

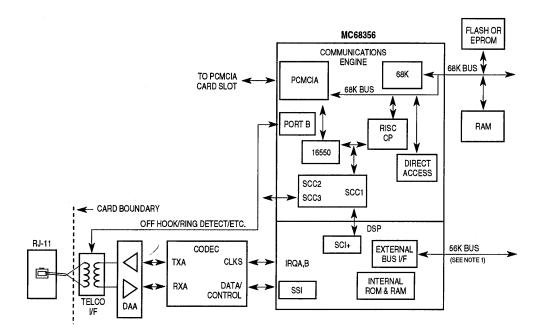

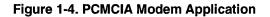

| 1.4.3 | Modem Applications                                              |     |

| 1.4.4 | Fax/Modem Software Availability                                 |     |

|       |                                                                 |     |

#### Section 2 Signal Description

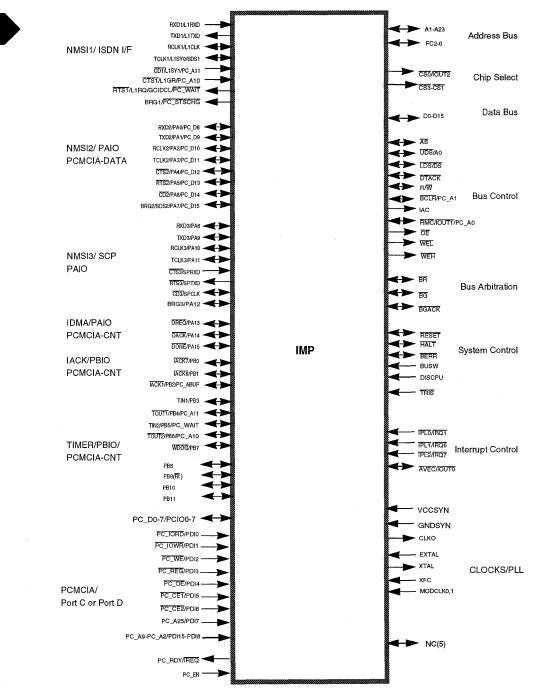

| 2.1    | IMP Pins                                    |      |

|--------|---------------------------------------------|------|

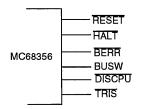

| 2.1.1  | System Control                              |      |

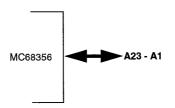

| 2.1.2  | IMP Address Bus Pins (A23–A1)               |      |

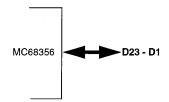

| 2.1.3  | IMP Data Bus Pins (D15—D0)                  |      |

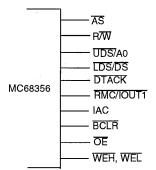

| 2.1.4  | Bus Control Pins                            |      |

| 2.1.5  | Bus Arbitration Pins                        |      |

| 2.1.6  | Interrupt Control Pins                      |      |

| 2.1.7  | IMP Bus Interface Signal Summary            | 2-14 |

| 2.1.8  | Physical Layer Serial Interface Pins        |      |

| 2.1.9  | Typical Serial Interface Pin Configurations |      |

| 2.1.10 | NMSI1 or ISDN Interface Pins                |      |

| 2.1.11 | NMSI2 Port or Port A Pins                   |      |

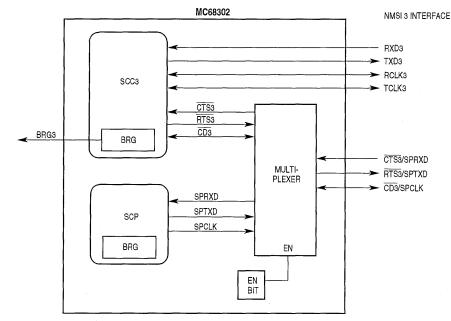

| 2.1.12 | NMSI3 Port or Port A Pins or SCP Pins       | 2-20 |

| 2.1.13 | IDMA or Port A Pins                         |      |

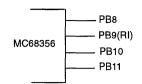

| 2.1.14 | IACK or PIO Port B Pins                     |      |

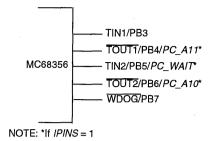

| 2.1.15 | Timer Pins                                  | 2-22 |

| 2.1.16 | Parallel I/O Pins with Interrupt Capability | 2-23 |

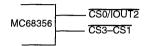

| 2.1.17 | Chip-Select Pins                            |      |

| 2.1.18 | No-Connect Pins                             | 2-25 |

|        |                                             |      |

# Title

# Page Number

| Paragraph<br>Number | Title                                  | Page<br>Numbe |

|---------------------|----------------------------------------|---------------|

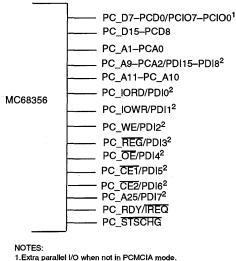

| 2.2                 | PCMCIA Pins                            | 2-25          |

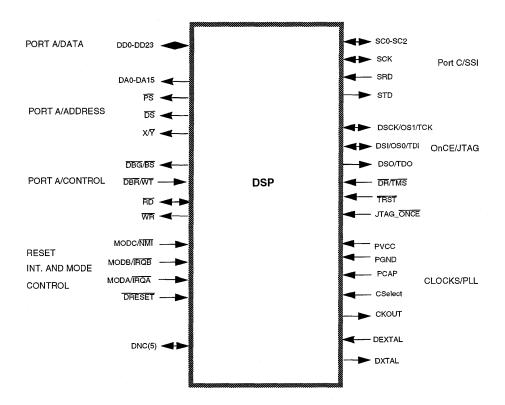

| 2.3                 | DSP Pins                               | 2-28          |

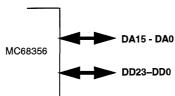

| 2.3.1               | Port A Address and Data Bus            | 2-29          |

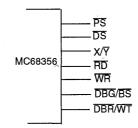

| 2.3.2               | Port A Bus Control                     | 2-30          |

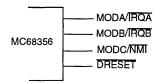

| 2.3.3               | Interrupt and Mode Control             | 2-32          |

| 2.3.4               | Synchronous Serial Interface (SSI)     | 2-35          |

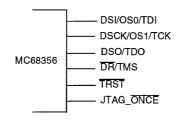

| 2.3.5               | On-Chip Emulation (OnCE) and JTAG Pins |               |

| 2.3.5.1             | On-Chip Emulation Pins                 |               |

| 2.3.5.2             | JTAG Pins                              | 2-38          |

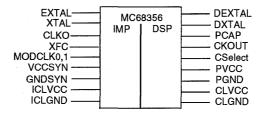

| 2.3.6               | IMP and DSP Clock and PLL Pins         |               |

| 2.3.6.1             | IMP PLL and Clock Pins                 | 2-38          |

| 2.3.6.2             | DSP PLL and Clock Pins                 | 2-40          |

| 2.4                 | Power and Ground Pins                  | 2-41          |

| 2.5                 | When to Use Pullup Resistors           |               |

## Section 3

## **Clock Generation and Low Power Control**

| 3.1     | Clock Generation and Low Power Control     | 3-1  |

|---------|--------------------------------------------|------|

| 3.2     | PLL and Oscillator Changes to IMP and DSP  | 3-1  |

| 3.2.1   | Clock Control Register                     |      |

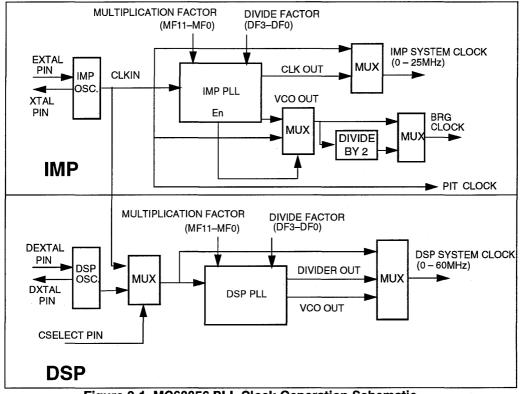

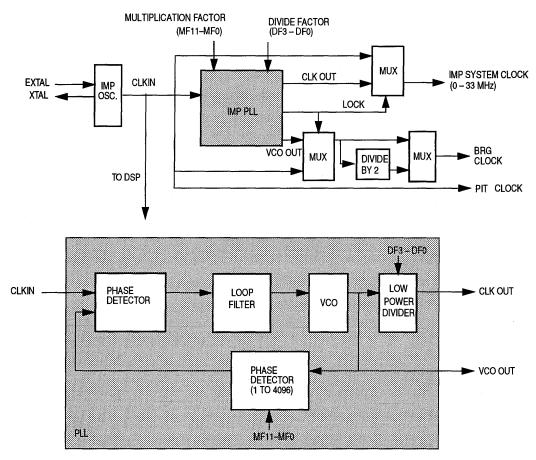

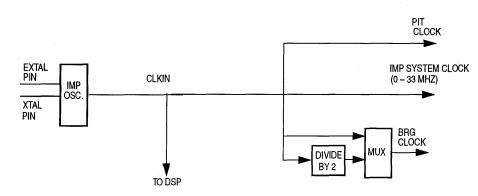

| 3.3     | MC68356 System Clock Generation            |      |

| 3.3.1   | Default System Clock Generation            |      |

| 3.4     | IMP System Clock Generation                |      |

| 3.4.1   | System Clock Configuration                 |      |

| 3.4.2   | On-Chip Oscillator                         |      |

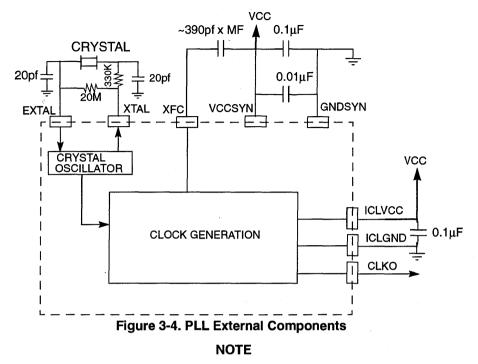

| 3.4.3   | Phase-Locked Loop (PLL)                    | 3-6  |

| 3.4.3.1 | Frequency Multiplication                   |      |

| 3.4.3.2 | Skew Elimination                           |      |

| 3.4.3.3 | Low Power PLL Clock Divider                | 3-7  |

| 3.4.3.4 | IMP PLL and Clock Control Register (IPLCR) | 3-8  |

| 3.4.4   | IMP Internal Clock Signals                 |      |

| 3.4.4.1 | IMP System Clock                           |      |

| 3.4.4.2 | BRG Clock                                  |      |

| 3.4.4.3 | PIT Clock                                  | 3-10 |

| 3.4.5   | IMP PLL Pins                               | 3-10 |

| 3.4.5.1 | VCCSYN                                     | 3-10 |

| 3.4.5.2 | GNDSYN                                     |      |

| 3.4.5.3 | XFC                                        | 3-10 |

| 3.4.5.4 | MODCLK1-MODCLK0                            |      |

| 3.5     | IMP Power Management                       |      |

| 3.5.1   | IMP Low Power Modes                        |      |

| 3.5.1.1 | STOP Mode                                  |      |

| 3.5.1.2 | DOZE Mode                                  | 3-11 |

| 3.5.1.3 | STAND_BY Mode                              | 3-12 |

| 3.5.1.4 | SLOW_GO Mode                               |      |

|         |                                            |      |

| _ |   |   |    |

|---|---|---|----|

|   | t | Ľ | Δ  |

|   | L |   | C. |

#### Page Number

|         |                                                             | unibe  |

|---------|-------------------------------------------------------------|--------|

| 3.5.1.5 | NORMAL Mode                                                 | . 3-12 |

| 3.5.1.6 | IMP Operation Mode Control Register (IOMCR)                 | . 3-12 |

| 3.5.1.7 | Low Power Drive Control Register (LPDCR)                    |        |

| 3.5.1.8 | Default Operation Modes                                     |        |

| 3.5.2   | Low Power Support                                           |        |

| 3.5.2.1 | Enter the SLOW_GO mode                                      |        |

| 3.5.2.2 | Entering the STOP/ DOZE/ STAND_BY Mode                      | . 3-14 |

| 3.5.2.3 | IMP Wake-Up from Low Power STOP Modes                       | . 3-15 |

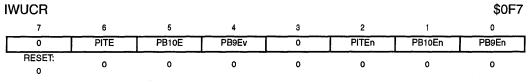

| 3.5.2.4 | IMP Wake-Up Control Register – IWUCR                        | . 3-15 |

| 3.5.2.5 | IMP Control of DSP Low Power Modes                          | . 3-16 |

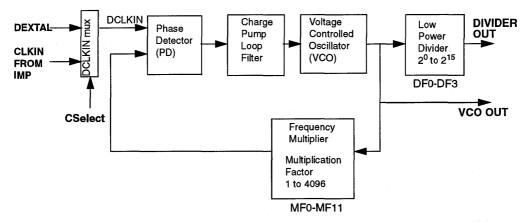

| 3.6     | DSP PLL Clock Oscillator Introduction                       |        |

| 3.7     | PLL Components                                              | . 3-17 |

| 3.7.1   | DCLKIN Mux                                                  | . 3-18 |

| 3.7.2   | Phase Detector and Charge Pump Loop Filter                  | . 3-18 |

| 3.7.3   | Voltage Controlled Oscillator (VCO)                         |        |

| 3.7.4   | Frequency Multiplier                                        | . 3-18 |

| 3.7.5   | Low Power Divider (LPD)                                     |        |

| 3.7.6   | DSP PLL Control Register (PCTL)                             |        |

| 3.7.6.1 | PCTL Multiplication Factor Bits (MF0-MF11) - Bits 0-11      |        |

| 3.7.6.2 | PCTL Division Factor Bits (DF0-DF3) - Bits 12-15            |        |

| 3.7.6.3 | PCTL DXTAL Disable Bit (XTLD) - Bit 16                      |        |

| 3.7.6.4 | PCTL STOP Processing State Bit (PSTP) - Bit 17              | . 3-20 |

| 3.7.6.5 | PCTL PLL Enable Bit (PEN) - Bit 18                          |        |

| 3.7.6.6 | PCTL Clock Output Disable Bits (COD0-COD1) - Bits 19-20     | . 3-21 |

| 3.7.6.7 | PCTL Chip Clock Source Bit (CSRC) - Bit 21                  | . 3-21 |

| 3.7.6.8 | PCTL CKOUT Clock Source Bit (CKOS) - Bit 22                 |        |

| 3.7.6.9 | PCTL Reserved Bit - Bit 23                                  |        |

| 3.8     | DSP PLL Pins                                                |        |

| 3.9     | DSP PLL Operation Considerations                            |        |

| 3.9.1   | Operating Frequency                                         |        |

| 3.9.2   | Hardware Reset                                              |        |

| 3.9.3   | Operation with DSP PLL Disabled                             | . 3-24 |

| 3.9.4   | Changing the MF0-MF11 Bits                                  |        |

| 3.9.5   | Change of DF0-DF3 Bits                                      |        |

| 3.9.6   | Loss of Lock                                                |        |

| 3.9.7   | STOP Processing State                                       |        |

| 3.9.8   | CKOUT Considerations                                        |        |

| 3.9.9   | Synchronization Among DCLKIN, CKOUT, and the Internal Clock |        |

| 3.9.10  | DSP Low Power Modes                                         | 3-25   |

|         |                                                             |        |

# Section 4

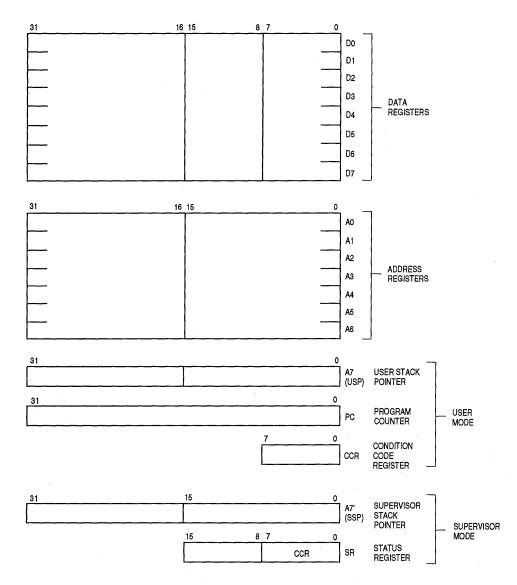

# MC68000/MC68008 Core

| Programming Model       |                                           |

|-------------------------|-------------------------------------------|

| Instruction Set Summary |                                           |

| Address Spaces          |                                           |

| Exception Processing    |                                           |

|                         | Instruction Set Summary<br>Address Spaces |

Paragraph Number

| Paragraph<br>Number | Title                    | Page<br>Number |

|---------------------|--------------------------|----------------|

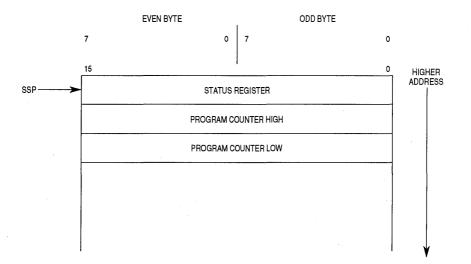

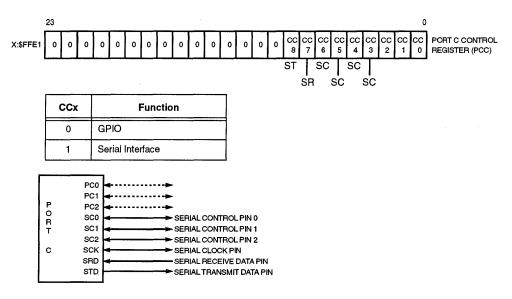

| 4.4.1               | Exception Vectors        | 4-8            |

| 4.4.2               | Exception Stacking Order |                |

| 4.5                 | Interrupt Processing     |                |

| 4.6 | M68000 Signal Differences4-1 | 1 |

|-----|------------------------------|---|

|     |                              |   |

# Section 5

## Memory Map

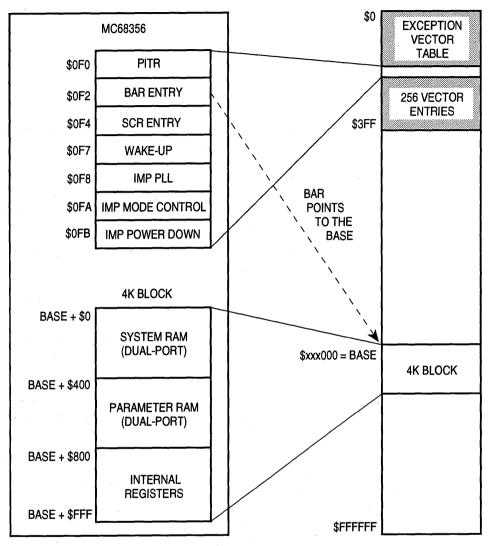

| 5.1 | IMP Configuration Control      | 5-1 |

|-----|--------------------------------|-----|

| 5.2 | System Configuration Registers | 5-3 |

| 5.3 | Internal Registers map         | 5-7 |

| 5.4 | Event Registers                |     |

# Section 6

# System Integration Block (SIB)

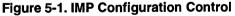

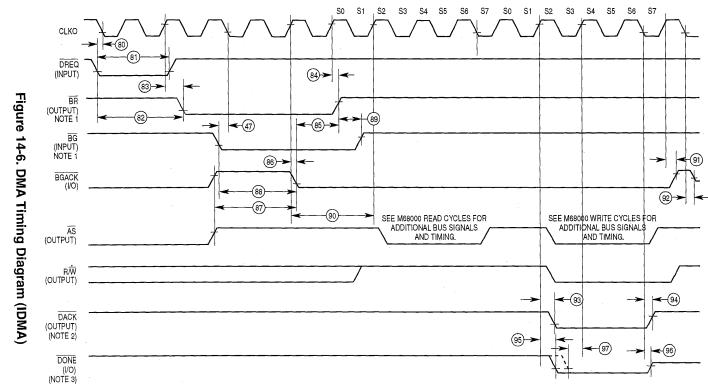

| 6.1     | DMA Control                                 | 6-2  |

|---------|---------------------------------------------|------|

| 6.1.1   | Key Features                                | 6-2  |

| 6.1.2   | IDMA Registers (Independent DMA Controller) | 6-3  |

| 6.1.2.1 | Channel Mode Register (CMR)                 | 6-4  |

| 6.1.2.2 | Source Address Pointer Register (SAPR)      | 6-6  |

| 6.1.2.3 | Destination Address Pointer Register (DAPR) |      |

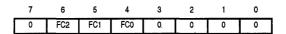

| 6.1.2.4 | Function Code Register (FCR)                | 6-7  |

| 6.1.2.5 | Byte Count Register (BCR)                   |      |

| 6.1.2.6 | Channel Status Register (CSR)               | 6-7  |

| 6.1.3   | Interface Signals                           |      |

| 6.1.3.1 | DREQ and DACK                               | 6-8  |

| 6.1.3.2 | DONE                                        | 6-8  |

| 6.1.4   | IDMA Operational Description                | 6-9  |

| 6.1.4.1 | Channel Initialization                      | 6-9  |

| 6.1.4.2 | Data Transfer                               | 6-9  |

| 6.1.4.3 | Address Sequencing                          | 6-10 |

| 6.1.4.4 | Transfer Request Generation                 | 6-11 |

| 6.1.4.5 | Block Transfer Termination                  | 6-12 |

| 6.1.5   | IDMA Programming                            | 6-13 |

| 6.1.6   | DMA Bus Arbitration                         | 6-14 |

| 6.1.7   | Bus Exceptions                              | 6-14 |

| 6.1.7.1 | RESET                                       | 6-15 |

| 6.1.7.2 | BUS ERROR                                   | 6-15 |

| 6.1.7.3 | HALT                                        | 6-15 |

| 6.1.7.4 | Relinguish and Retry                        | 6-15 |

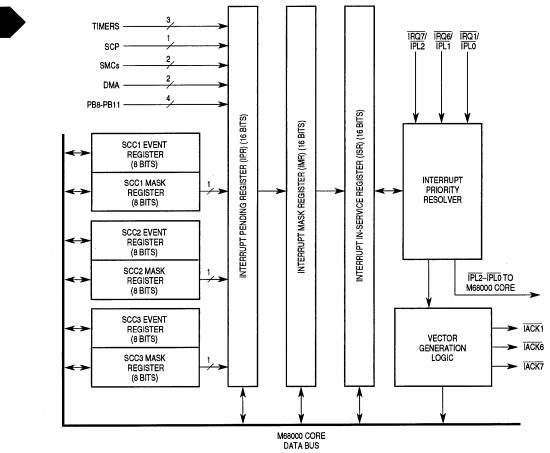

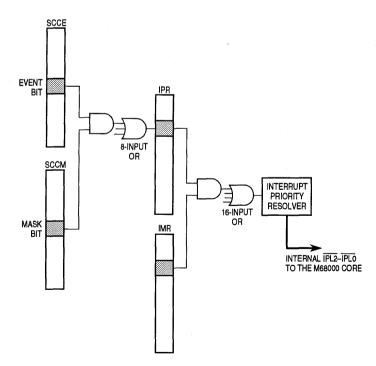

| 6.2     | Interrupt Controller                        | 6-15 |

| 6.2.1   | Overview                                    | 6-16 |

| 6.2.1.1 | IMP Interrupt Processing Overview           | 6-17 |

| 6.2.1.2 | Interrupt Controller Overview               |      |

| 6.2.2   | Interrupt Priorities                        |      |

| 6.2.2.1 | INRQ and EXRQ Priority Levels               | 6-19 |

| 6.2.2.2 | INRQ Interrupt Source Priorities            |      |

| Paragraph<br>Number | Title                                             | Page<br>Number |

|---------------------|---------------------------------------------------|----------------|

| 6.2.2.3             | Nested Interrupts                                 | 6-20           |

| 6.2.3               | Masking Interrupt Sources and Events              | 6-21           |

| 6.2.4               | Interrupt Vector                                  | 6-22           |

| 6.2.5               | Interrupt Controller Programming Model            | 6-23           |

| 6.2.5.1             | Global Interrupt Mode Register (GIMR)             | 6-23           |

| 6.2.5.2             | Interrupt Pending Register (IPR)                  | 6-26           |

| 6.2.5.3             | Interrupt Mask Register (IMR)                     |                |

| 6.2.5.4             | Interrupt In-Service Register (ISR)               |                |

| 6.2.6               | Interrupt Handler Examples                        | 6-28           |

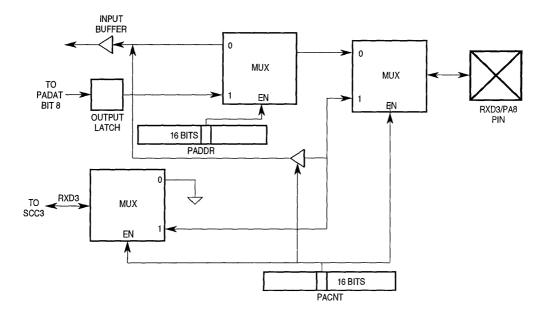

| 6.3                 | Parallel I/O Ports                                | 6-29           |

| 6.3.1               | Port A                                            | 6-29           |

| 6.3.2               | Port B                                            | 6-31           |

| 6.3.2.1             | PB7–PB0                                           |                |

| 6.3.2.2             | PB11–PB8                                          | 6-32           |

| 6.3.3               | Port C                                            | 6-33           |

| 6.3.4               | Port D                                            | 6-33           |

| 6.3.5               | Port Registers                                    |                |

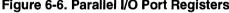

| 6.4                 | Dual-Port Ram                                     | 6-34           |

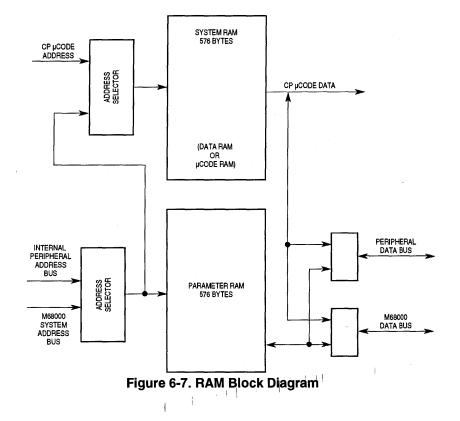

| 6.5                 | Timers                                            |                |

| 6.5.1               | Timer Key Features                                |                |

| 6.5.2               | General Purpose Timer Units                       |                |

| 6.5.2.1             | Timer Mode Register (TMR1, TMR2)                  |                |

| 6.5.2.2             | Timer Reference Registers (TRR1, TRR2)            |                |

| 6.5.2.3             | Timer Capture Registers (TCR1, TCR2)              |                |

| 6.5.2.4             | Timer Counter (TCN1, TCN2)                        |                |

| 6.5.2.5             | Timer Event Registers (TER1, TER2)                |                |

| 6.5.2.6             | General Purpose Timer Example                     |                |

| 6.5.2.6.1           | Timer Example 1                                   |                |

| 6.5.2.6.2           | Timer Example 2                                   |                |

| 6.5.3               | Timer 3 - Software Watchdog Timer                 |                |

| 6.5.3.1             | Software Watchdog Timer Operation                 |                |

| 6.5.3.2             | Software Watchdog Reference Register (WRR)        |                |

| 6.5.3.3             | Software Watchdog Counter (WCN)                   |                |

| 6.5.4               | Periodic Interrupt Timer                          | 6-42           |

| 6.5.4.1             | Overview                                          | 6-42           |

| 6.5.4.2             | Periodic Timer Period Calculation                 |                |

| 6.5.4.3             | Using the Periodic Timer As a Real-Time Clock     |                |

| 6.5.4.4             | Periodic Interrupt Timer Register (PITR)          |                |

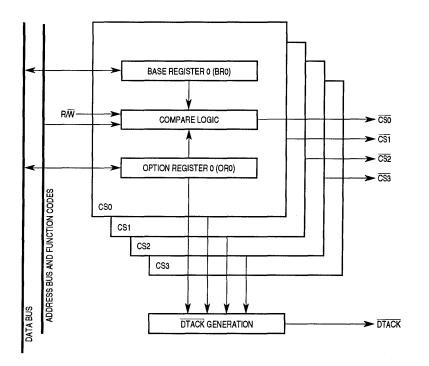

| 6.6                 | External Chip-Select Signals and Wait-State Logic |                |

| 6.6.1               | Chip-Select Logic Key Features                    | 6-48           |

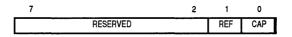

| 6.6.2               | Chip-Select Registers                             |                |

| 6.6.2.1             | Base Register (BR3–BR0)                           |                |

| 6.6.2.2             | Option Registers (OR3–OR0)                        |                |

| 6.6.2.3             | PCMCIA Protection Register (PPR)                  |                |

| 6.6.3               | Chip Select Example                               | 6-52           |

| Paragraph<br>Number | Title                                              | Page<br>Number |

|---------------------|----------------------------------------------------|----------------|

| 6.7                 | System Control                                     | 6-53           |

| 6.7.1               | System Control Register (SCR)                      | 6-53           |

| 6.7.2               | System Status Bits                                 | 6-54           |

| 6.7.3               | System Control Bits                                |                |

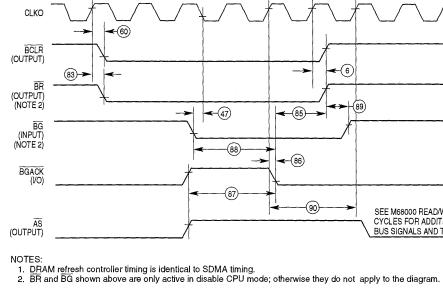

| 6.7.4               | Disable CPU Logic (M68000)                         | 6-57           |

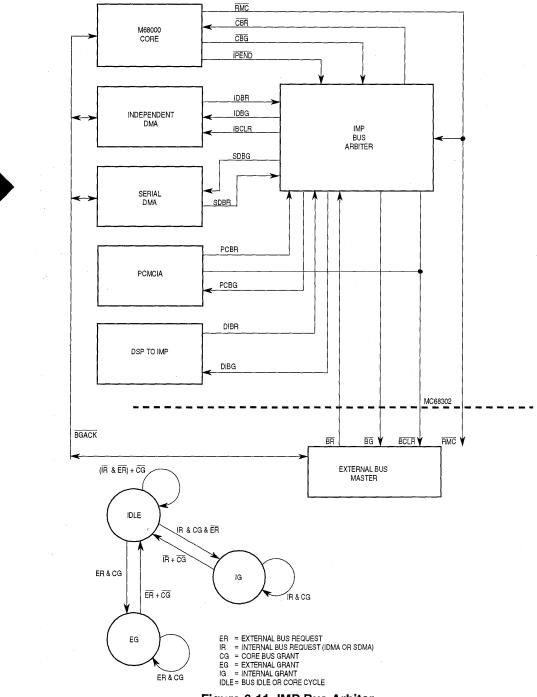

| 6.7.5               | Bus Arbitration Logic                              |                |

| 6.7.5.1             | Internal Bus Arbitration                           |                |

| 6.7.5.2             | External Bus Arbitration                           |                |

| 6.7.6               | Hardware Watchdog                                  |                |

| 6.8                 | Dynamic RAM Refresh Controller                     |                |

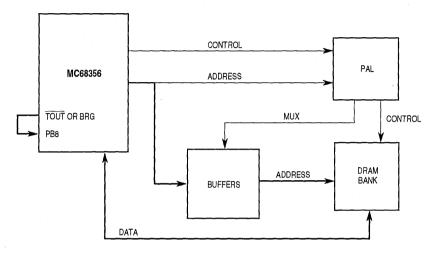

| 6.8.1               | Hardware Setup                                     | 6-63           |

| 6.8.2               | DRAM Refresh Controller Bus Timing                 |                |

| 6.8.3               | Refresh Request Calculations                       |                |

| 6.8.4               | Initialization                                     |                |

| 6.8.5               | DRAM Refresh Memory Map                            |                |

| 6.8.6               | Programming Example                                |                |

| 6.9                 | IMP Control of the DSP Reset, Modes and Interrupts |                |

| 6.9.1               | IMP Control of DSP Reset at Power-On Reset         |                |

| 6.9.2               | IMP-DSP Reset and Mode Interconnections Register   |                |

## Section 7

# **Communications Processor (CP)**

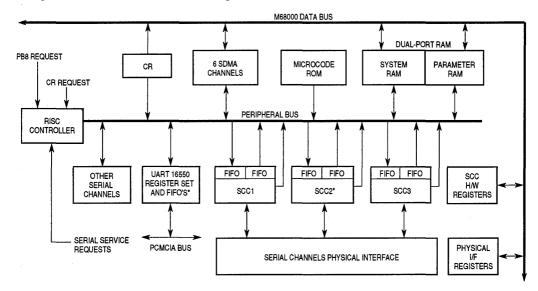

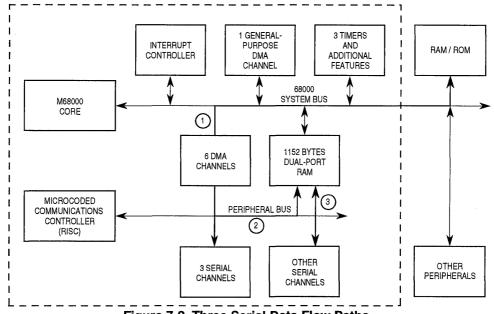

| 7.1       | Main Controller                                          | 7-1  |

|-----------|----------------------------------------------------------|------|

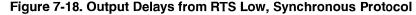

| 7.2       | SDMA Channels                                            | 7-3  |

| 7.3       | Command Set                                              | 7-5  |

| 7.3.1     | Command Execution Latency                                | 7-6  |

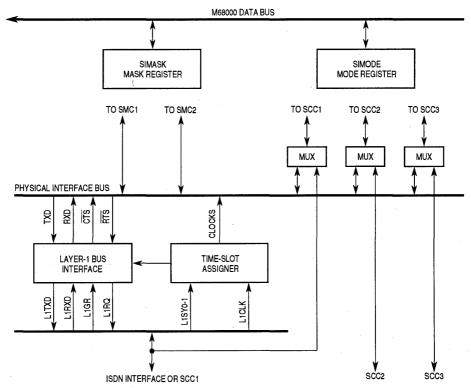

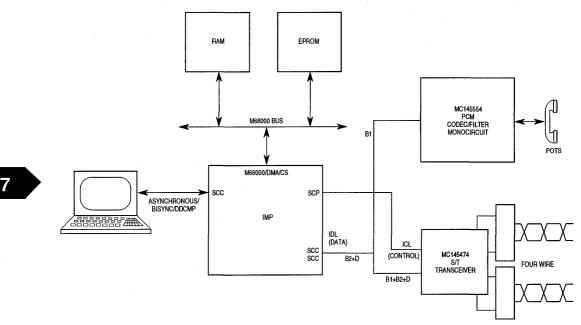

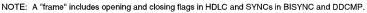

| 7.4       | Serial Channels Physical Interface                       | 7-7  |

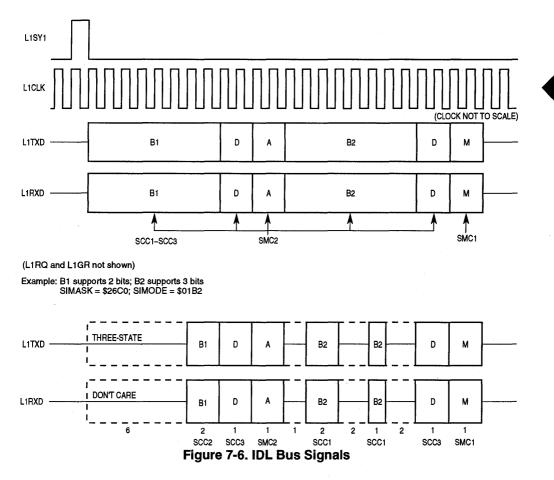

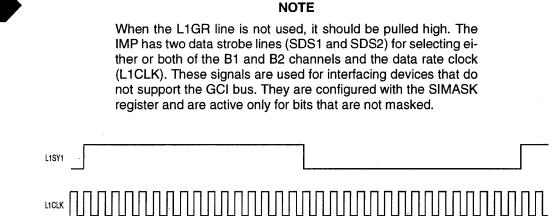

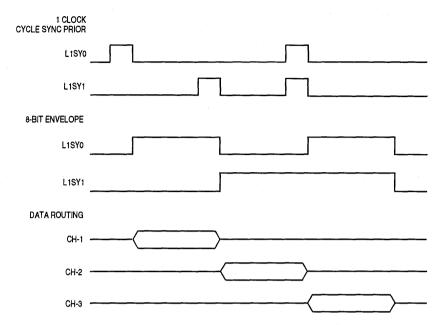

| 7.4.1     | IDL Interface                                            |      |

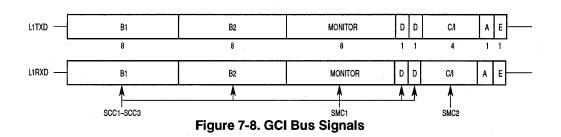

| 7.4.2     | GCI Interface                                            | 7-13 |

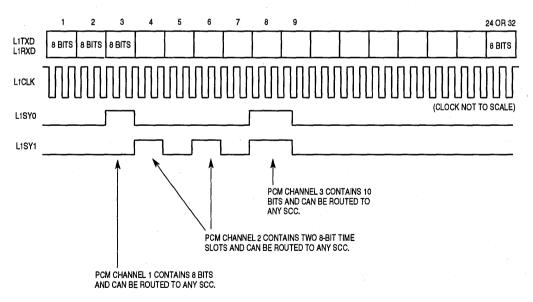

| 7.4.3     | PCM Highway Mode                                         | 7-16 |

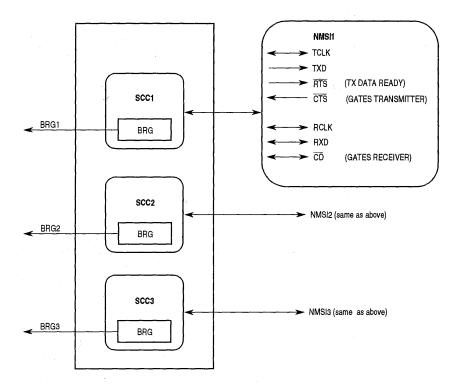

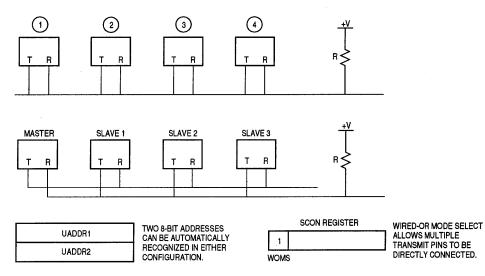

| 7.4.4     | Nonmultiplexed Serial Interface (NMSI)                   | 7-19 |

| 7.4.5     | Serial Interface Registers                               |      |

| 7.4.5.1   | Serial Interface Mode Register (SIMODE)                  | 7-19 |

| 7.4.5.2   | Serial Interface Mask Register (SIMASK)                  | 7-22 |

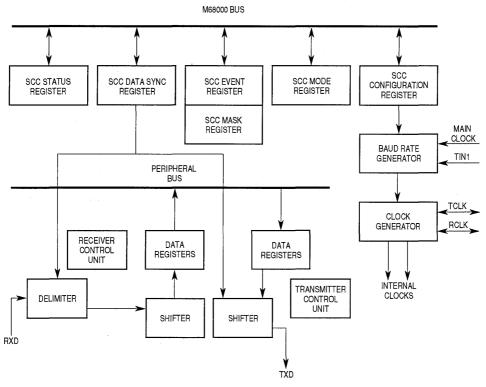

| 7.5       | Serial Communication Controllers (SCCs)                  | 7-22 |

| 7.5.1     | SCC Features                                             | 7-24 |

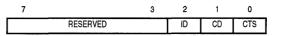

| 7.5.2     | SCC Configuration Register (SCON)                        | 7-24 |

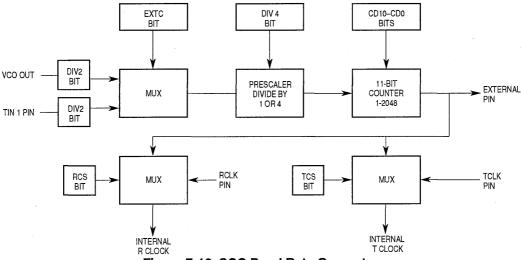

| 7.5.2.1   | Divide by 2 Input Blocks                                 | 7-26 |

| 7.5.2.2   | Asynchronous Baud Rate Generator Examples                | 7-26 |

| 7.5.2.3   | Synchronous Baud Rate Generator Examples                 | 7-27 |

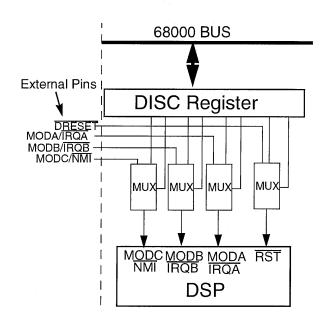

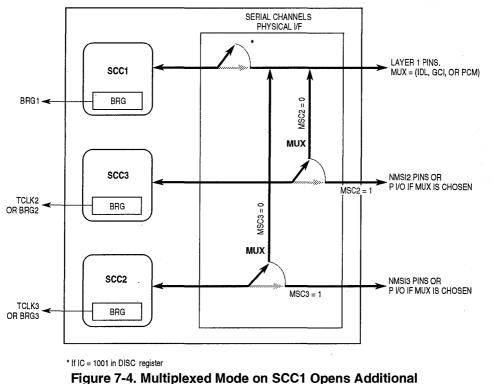

| 7.5.3     | DSP Interconnection and Serial Connections Register-DISC | 7-27 |

| 7.5.3.1   | BRG1 and RCLK1/TCLK1 Pin Options                         | 7-27 |

| 7.5.3.2   | SCI+ Serial Connections                                  | 7-28 |

| 7.5.3.2.1 | Normal Mode (IC3 – IC0 = 0000)                           | 7-29 |

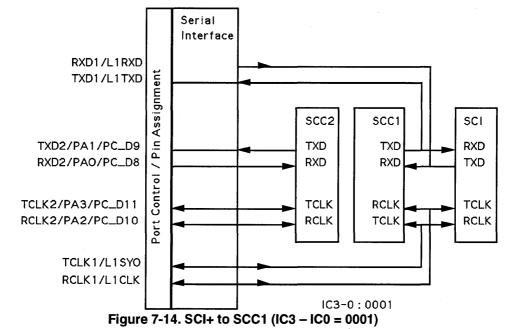

| 7.5.3.2.2 | SCI+ to SCC1 (IC3 – IC0 = 0001)                          | 7-29 |

|           |                                                          |      |

| Paragraph<br>Number  | Title                                                        | Page<br>Number |

|----------------------|--------------------------------------------------------------|----------------|

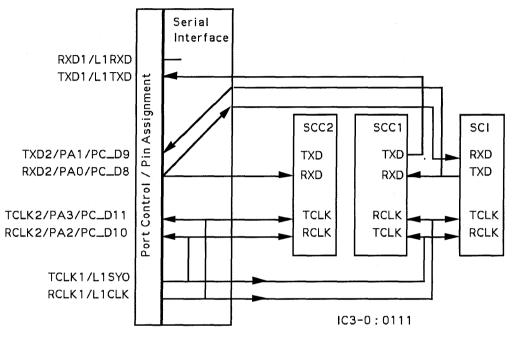

| 7.5.3.2.3            | SCI+ to DTE: (IC3 – IC0 = 0111)                              | 7-30           |

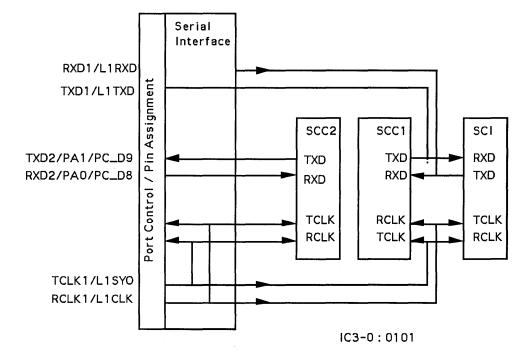

| 7.5.3.2.4            | Clocks:NMSI1 Driving the SCI+ and NMSI2 (DTE), Data: SCC1 to |                |

|                      | SCI+ and SCC2 to NMSI2 (IC3 - IC0 = 0101)                    |                |

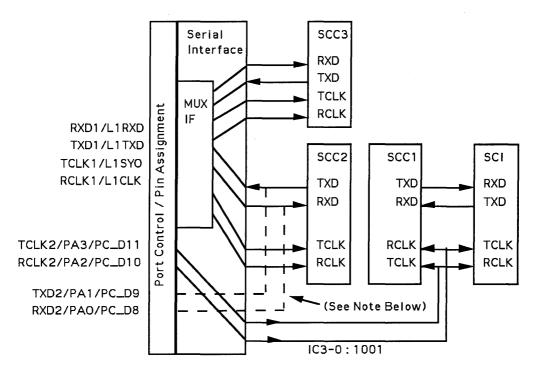

| 7.5.3.2.5            | SCI+ Clocks with ISDN (IC3 - IC0 = 1001)                     |                |

| 7.5.4                | SCC Mode Register (SCM)                                      | 7-33           |

| 7.5.5                | SCC Data Synchronization Register (DSR)                      | 7-37           |

| 7.5.6                | Buffer Descriptors Table                                     |                |

| 7.5.7                | SCC Parameter RAM Memory Map                                 |                |

| 7.5.7.1              | Data Buffer Function Code Register (TFCR, RFCR)              |                |

| 7.5.7.2              | Maximum Receive Buffer Length Register (MRBLR)               |                |

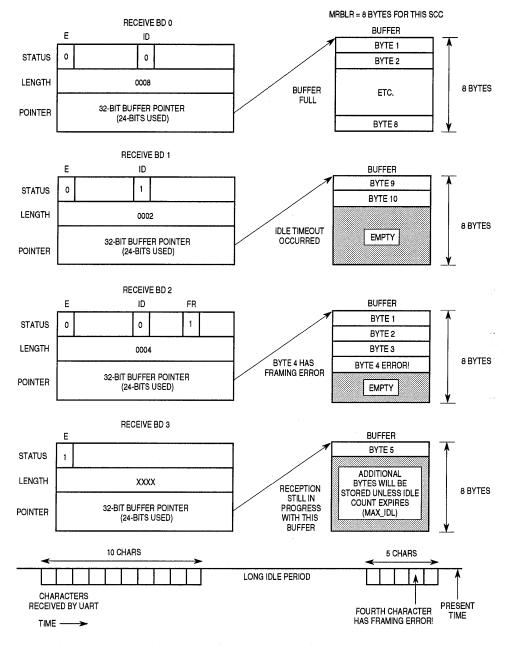

| 7.5.7.3              | Receiver Buffer Descriptor Number (RBD#)                     |                |

| 7.5.7.4              | Transmit Buffer Descriptor Number (TBD#)                     |                |

| 7.5.7.5              | Other General Parameters                                     |                |

| 7.5.8                | SCC Initialization                                           |                |

| 7.5.9                | Interrupt Mechanism                                          |                |

| 7.5.9.1              | SCC Event Register (SCCE)                                    |                |

| 7.5.9.2              | SCC Mask Register (SCCM)                                     |                |

| 7.5.9.3              | SCC Status Register (SCCs)                                   |                |

| 7.5.9.4              | Bus Error on SDMA Access                                     |                |

| 7.5.10               | SCC Transparent Mode                                         |                |

| 7.5.11               | Disabling the SCCs                                           |                |

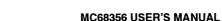

| 7.5.12               | UART Controller                                              |                |

| 7.5.12.1             | Normal Asynchronous Mode                                     |                |

| 7.5.12.2             | UART Memory Map<br>UART Programming Model                    |                |

| 7.5.12.3             | UART Command Set                                             |                |

| 7.5.12.4<br>7.5.12.5 | UART Address Recognition                                     |                |

| 7.5.12.5             | UART Control Characters and Flow Control                     |                |

| 7.5.12.6             | Send Break                                                   |                |

| 7.5.12.7             | Send Preamble (IDLE)                                         |                |

| 7.5.12.9             | Wakeup Timer                                                 |                |

| 7.5.12.10            | UART Error-Handling Procedure.                               |                |

| 7.5.12.11            | Fractional Stop Bits                                         |                |

| 7.5.12.12            | UART Mode Register                                           |                |

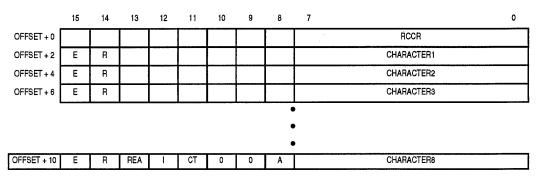

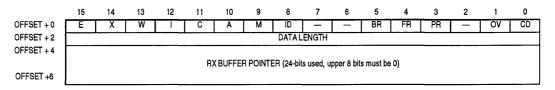

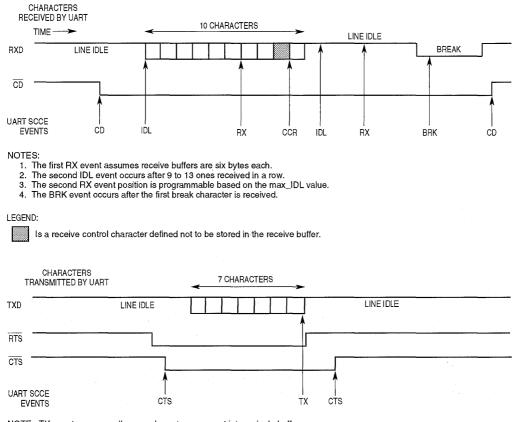

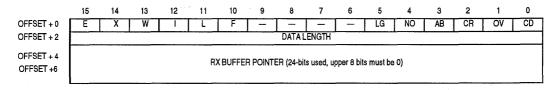

| 7.5.12.12            | UART Receive Buffer Descriptor (Rx BD)                       |                |

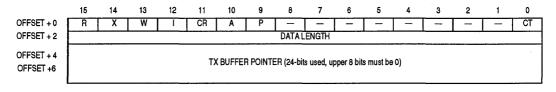

| 7.5.12.14            | UART Transmit Buffer Descriptor (Tx BD)                      |                |

| 7.5.12.15            | UART Event Register                                          |                |

| 7.5.12.16            | UART MASK Register                                           |                |

| 7.5.12.17            | S-Records Programming Example                                | 7-71           |

| 7.5.13               | Autobaud Controller                                          |                |

| 7.5.13.1             | Autobaud Channel Reception Process                           |                |

| 7.5.13.2             | Autobaud Channel Transmit Process                            |                |

| 7.5.13.3             | Autobaud Parameter RAM                                       |                |

| 7.5.13.4             | Autobaud Programming Model                                   |                |

| 7.5.13.4.6           | Preparing for the Autobaud Process                           |                |

|                      |                                                              |                |

| Paragraph<br>Number | Title                                              | Page<br>Number |

|---------------------|----------------------------------------------------|----------------|

| 7.5.13.4.7          | Enter_Baud_Hunt Command                            |                |

| 7.5.13.4.8          | Autobaud Command Descriptor                        |                |

| 7.5.13.4.9          | Autobaud LookUp Table                              |                |

|                     | LookUp Table Example                               | 7-81           |

| 7.5.13.5            | Determining Character Length and Parity            |                |

| 7.5.13.6            | Autobaud Reception Error Handling Procedure        |                |

| 7.5.13.7            | Autobaud Transmission                              |                |

| 7.5.13.7.1          | Automatic Echo                                     |                |

| 7.5.13.7.2          | Smart Echo                                         |                |

| 7.5.13.8            | Reprogramming to UART Mode or Another Protocol     |                |

| 7.5.14              | HDLC Controller                                    | 7-84           |

| 7.5.14.1            | HDLC Channel Frame Transmission Processing         | 7-86           |

| 7.5.14.2            | HDLC Channel Frame Reception Processing            |                |

| 7.5.14.3            | HDLC Memory Map                                    |                |

| 7.5.14.4            | HDLC Programming Model                             | 7-88           |

| 7.5.14.5            | HDLC Command Set                                   | 7-88           |

| 7.5.14.6            | HDLC Address Recognition                           |                |

| 7.5.14.7            | HDLC Maximum Frame Length Register (MFLR)          | 7-90           |

| 7.5.14.8            | HDLC Error-Handling Procedure                      | 7-90           |

| 7.5.14.9            | HDLC Mode Register                                 |                |

| 7.5.14.10           | HDLC Receive Buffer Descriptor (Rx BD)             | 7-93           |

| 7.5.14.11           | HDLC Transmit Buffer Descriptor (Tx BD)            | 7-97           |

| 7.5.14.12           | HDLC Event Register                                | 7-98           |

| 7.5.14.13           | HDLC Mask Register                                 |                |

| 7.5.15              | BISYNC Controller                                  |                |

| 7.5.15.1            | BISYNC Channel Frame Transmission Processing       |                |

| 7.5.15.2            | BISYNC Channel Frame Reception Processing          | 7-103          |

| 7.5.15.3            | BISYNC Memory Map                                  |                |

| 7.5.15.4            | BISYNC Command Set                                 |                |

| 7.5.15.5            | BISYNC Control Character Recognition               |                |

| 7.5.15.6            | BSYNC-BISYNC SYNC Register                         |                |

| 7.5.15.7            | BDLE-BISYNC DLE Register                           |                |

| 7.5.15.8            | BISYNC Error-Handling Procedure                    | 7-108          |

| 7.5.15.9            | BISYNC Mode Register                               |                |

| 7.5.15.10           | BISYNC Receive Buffer Descriptor (Rx BD)           |                |

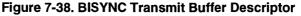

| 7.5.15.11           | BISYNC Transmit Buffer Descriptor (Tx BD)          | 7-113          |

| 7.5.15.12           | BISYNC Event Register                              | 7-116          |

| 7.5.15.13           | BISYNC Mask Register                               | 7-116          |

| 7.5.15.14           | Programming the BISYNC Controllers                 | 7-117          |

| 7.5.16              | Transparent Controller                             |                |

| 7.5.16.1            | Transparent Channel Buffer Transmission Processing |                |

| 7.5.16.2            | Transparent Channel Buffer Reception Processing    |                |

| 7.5.16.3            | Transparent Memory Map                             | 7-120          |

| 7.5.16.4            | Transparent Commands                               |                |

| 7.5.16.5            | Transparent Synchronization                        | 7-122          |

Title

Page Number

| Number     |                                                          | Numbe |

|------------|----------------------------------------------------------|-------|

| 7.5.16.6   | Transparent Error-Handling Procedure                     |       |

| 7.5.16.7   | Transparent Mode Register                                |       |

| 7.5.16.8   | Transparent Receive Buffer Descriptor (RxBD)             |       |

| 7.5.16.9   | Transparent Transmit Buffer Descriptor (Tx BD)           |       |

| 7.5.16.10  | Transparent Event Register                               |       |

| 7.5.16.11  | Transparent Mask Register                                |       |

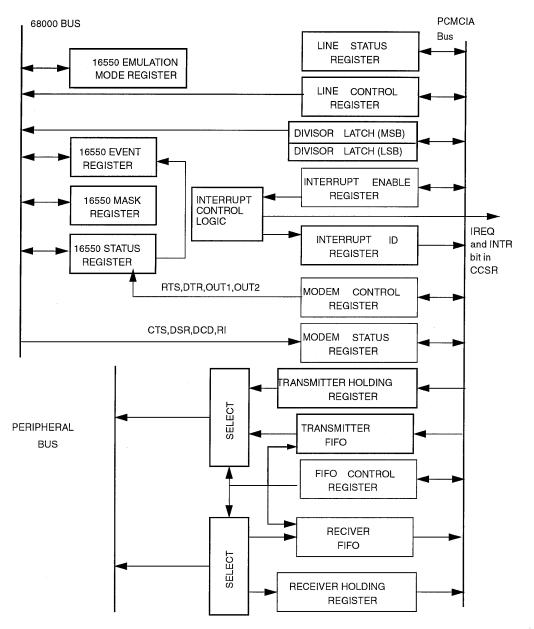

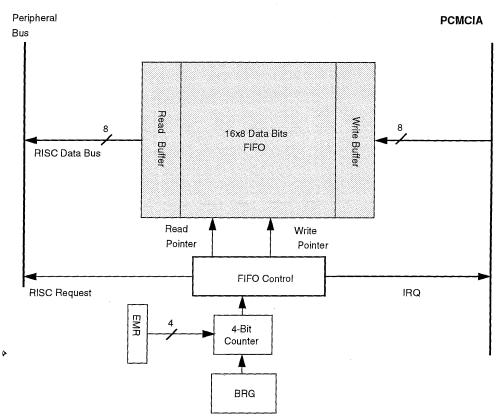

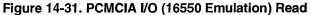

| 7.6        | 16550 Emulation Controller                               |       |

| 7.6.1      | 16550 Emulation Controller Features                      |       |

| 7.6.2      | 16550 Emulation Controller Overview                      |       |

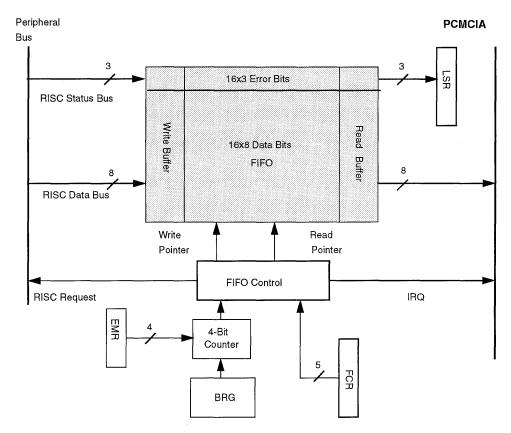

| 7.6.2.1    | 16550 Emulation Controller FIFOs Overview                |       |

| 7.6.3      | PC Accesses                                              |       |

| 7.6.4      | PC Programmer Model                                      |       |

| 7.6.4.1    | 16550 Emulation Registers Description                    |       |

| 7.6.4.1.1  | Line Control Register (LCR)                              |       |

| 7.6.4.1.2  | Line Control Register (LSR)                              |       |

| 7.6.4.1.3  | Line Status Register (LSR) (Read Only)                   |       |

| 7.6.4.1.4  | FIFO Control Register FCR (Write Only)                   |       |

| 7.6.4.1.5  | Interrupt Identification Register -IIR (Read Only)       |       |

| 7.6.4.1.6  | Interrupt Enable Register - IER                          |       |

| 7.6.4.1.7  | MODEM Control Register - MCR                             |       |

| 7.6.4.1.8  | MODEM Status Register                                    |       |

| 7.6.4.1.9  | Divisor Latch (LS) - DLL                                 |       |

| 7.6.4.1.10 | Divisor Latch (LM) - DLM                                 |       |

| 7.6.4.1.11 | Receive Buffer Register - RBR                            |       |

| 7.6.4.1.12 | Transmit Holding Register - THR                          |       |

| 7.6.4.1.13 | Scratchpad Register - SCR                                |       |

| 7.6,5      | 68000 Programming Model                                  |       |

| 7.6.5.1    | 16550 Memory Map                                         |       |

| 7.6.5.2    | 16550 Emulation Mode Register - EMR                      |       |

| 7.6.5.3    | 16550 Command Set                                        |       |

| 7.6.5.4    | Transmit Commands                                        |       |

| 7.6.5.4.14 | STOP TRANSMIT Command                                    |       |

| 7.6.5.4.15 | RESTART TRANSMIT Command                                 |       |

| 7.6.5.5    | Receive Commands                                         |       |

| 7.6.5.5.16 | ENTER HUNT MODE Command                                  |       |

| 7.6.5.6    | 16550 Control Characters (Receiver)                      |       |

| 7.6.5.6.17 | Transmission of Out-of-Sequence Characters (Transmitter) |       |

| 7.6.5.7    | BREAK Support (Receiver)                                 |       |

| 7.6.5.8    | Send Break (Transmitter)                                 |       |

| 7.6.5.9    | 16550 Error Handling                                     |       |

| 7.6.5.9.18 | IDLE Sequence Receive                                    |       |

| 7.6.5.9.19 | BREAK Sequence                                           |       |

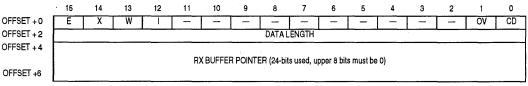

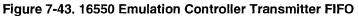

| 7.6.5.10   | 16550 Rx Buffer Descriptor (Rx BD)                       |       |

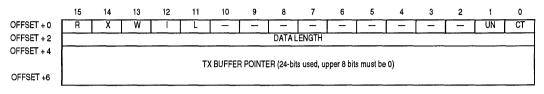

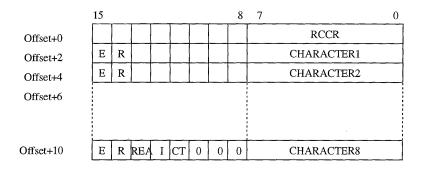

| 7.6.5.11   | 16550 Tx Buffer Descriptor (Tx BD)                       |       |

| 7.6.5.12   | 16550 Event Register                                     |       |

|            |                                                          |       |

Paragraph Number

| Paragraph<br>Number | Title                                        | Page<br>Number |

|---------------------|----------------------------------------------|----------------|

| 7.6.5.13            | 16550 Mask Register                          | 7-154          |

| 7.6.5.14            | 16550 Status Register                        | 7-154          |

| 7.7                 | Serial Communication Port (SCP)              |                |

| 7.7.1               | SCP Programming Model                        | 7-157          |

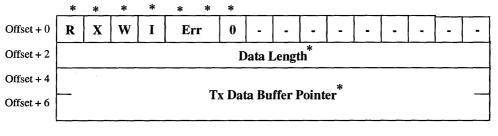

| 7.7.2               | SCP Transmit/Receive Buffer Descriptor       | 7-158          |

| 7.7.3               | SCP Transmit/Receive Processing              | 7-158          |

| 7.8                 | Serial Management Controllers (SMCs)         | 7-159          |

| 7.8.1               | SMC Overview                                 | 7-159          |

| 7.8.1.1             | Using IDL with the SMCs                      | 7-159          |

| 7.8.1.2             | Using GCI with the SMCs                      | 7-159          |

| 7.8.2               | SMC Programming Model                        | 7-161          |

| 7.8.3               | SMC Commands                                 |                |

| 7.8.4               | SMC Memory Structure and Buffers Descriptors | 7-162          |

| 7.8.4.1             | SMC1 Receive Buffer Descriptor               | 7-162          |

| 7.8.4.2             | SMC1 Transmit Buffer Descriptor              | 7-163          |

| 7.8.4.3             | SMC2 Receive Buffer Descriptor               | 7-164          |

| 7.8.4.4             | SMC2 Transmit Buffer Descriptor              | 7-164          |

| 7.8.5               | SMC Interrupt Requests                       | 7-164          |

|                     |                                              |                |

#### Section 8 PCMCIA Controller

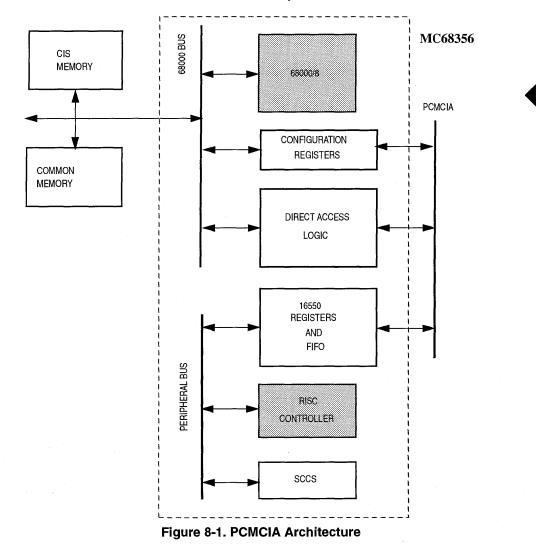

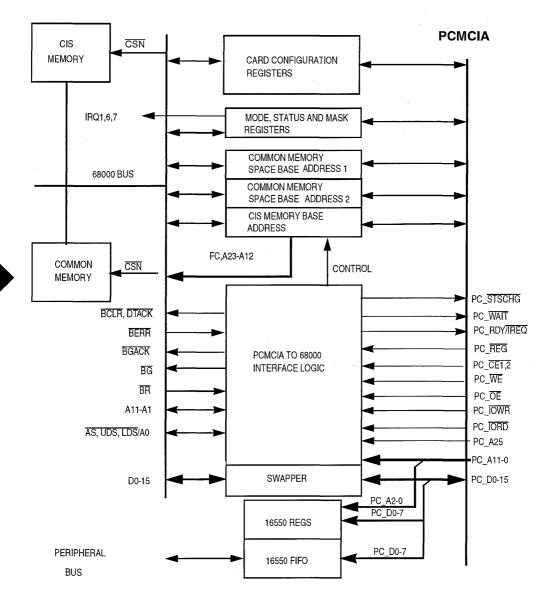

| 8.1     | PCMCIA Controller Functional Overview                     | 0.0  |

|---------|-----------------------------------------------------------|------|

|         |                                                           |      |

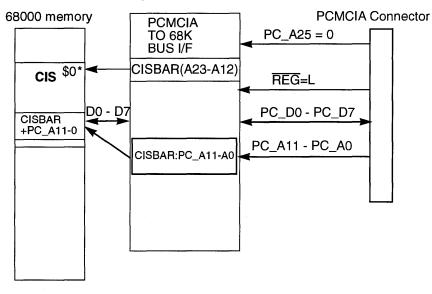

| 8.1.1   | Attribute Memory Accesses                                 |      |

| 8.1.2   | Configuration Registers                                   |      |

| 8.1.3   | Card Information Structure                                | 8-6  |

| 8.1.4   | I/O Space Accesses                                        |      |

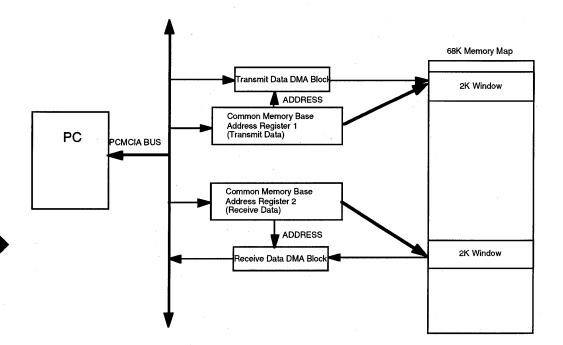

| 8.1.5   | Common Memory and Direct Access Mode Accesses             |      |

| 8.1.6   | Protecting Memory and Internal Space from PCMCIA Accesses | 8-12 |

| 8.1.7   | PCMCIA Controller Initialization                          | 8-13 |

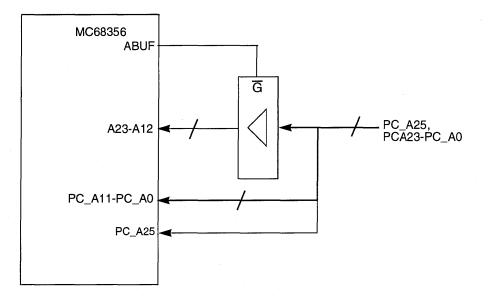

| 8.1.8   | PCMCIA to 68000 Bus Access and Monitoring Options         | 8-13 |

| 8.2     | Power Down Options                                        | 8-14 |

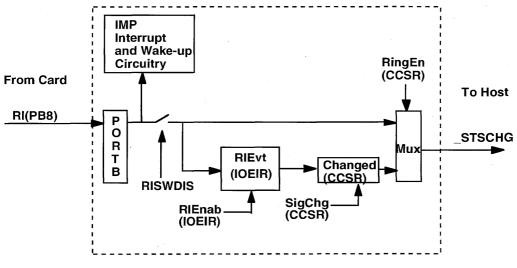

| 8.2.1   | PCMCIA Ring Indication                                    | 8-15 |

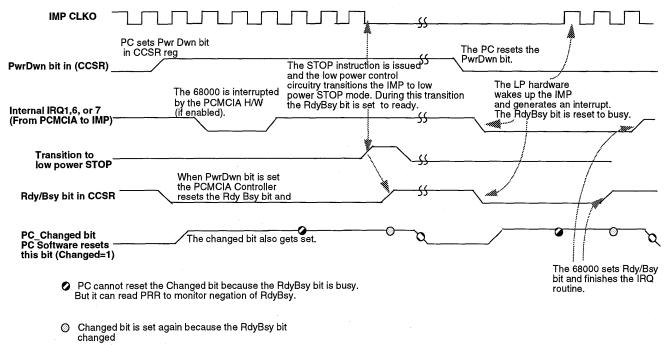

| 8.2.1.1 | Wake Up Using the PwrDwn Bit                              |      |

| 8.2.2   | Wake Up Options                                           | 8-16 |

| 8.2.2.1 | Wake Up on PCMCIA Access in STAND-BY mode                 | 8-17 |

| 8.2.2.2 | Power Down and Wake Up Using the PwrDwn Bit               | 8-17 |

| 8.2.2.3 | PCMCIA Host Interrupts                                    | 8-17 |

| 8.2.2.4 | The Ready Busy Signal (Rdy/Bsy)                           | 8-19 |

| 8.3     | PCMCIA Pins                                               | 8-19 |

| 8.3.1   | PCMCIA Pins Supported by the MC68356                      | 8-19 |

| 8.3.2   | PCMCIA Pins Not Supported                                 |      |

| 8.3.3   | Pullup Control Register – PUCR                            | 8-20 |

| 8.4     | Programmer's Model                                        | 8-22 |

| 8.4.1   | PCMCIA Controller Accesses                                | 8-22 |

| 8.4.2   | PCMCIA Mode Register - PCMR                               | 8-22 |

|         |                                                           |      |

#### MC68356 USER'S MANUAL

# Title

#### Page Number

| 8.4.3    | PCMCIA Configuration Registers Write Event Register - PCRWE | R 8-26  |

|----------|-------------------------------------------------------------|---------|

| 8.4.4    | PCMCIA Configuration Registers Write Mask Register - PCRWM  | IR 8-27 |

| 8.4.5    | PCMCIA Access Wake-Up Event Register - PCAWER               | 8-27    |

| 8.4.6    | PCMCIA Access Wake-up Mask Register - PCAWMR                | 8-28    |

| 8.4.7    | PCMCIA Host (PC) Event Register - PCHER                     | 8-29    |

| 8.4.8    | CIS Base Address Register - CISBAR                          | 8-29    |

| 8.4.9    | Common Memory Space Base Address Register - CMBAR1,2        | 8-30    |

| 8.4.10   | Card Configuration Registers                                | 8-31    |

| 8.4.10.1 | Configuration Option Register - COR                         | 8-31    |

| 8.4.10.2 | Card Configuration and Status Register - CCSR               | 8-32    |

| 8.4.10.3 | Pin Replacement Register Organization - PRR                 | 8-33    |

| 8.4.10.4 | Socket and Copy Register - SCR                              | 8-34    |

| 8.4.10.5 | I/O Event Indication Register - IOEIR                       | 8-35    |

| 8.4.10.6 | Reserved Registers                                          | 8-36    |

|          |                                                             |         |

#### Section 9 DSP Memory Modules and Operating Modes

| 9.1   | Memory Modules and Operating Modes                     | 0_1 |

|-------|--------------------------------------------------------|-----|

| •••   |                                                        |     |

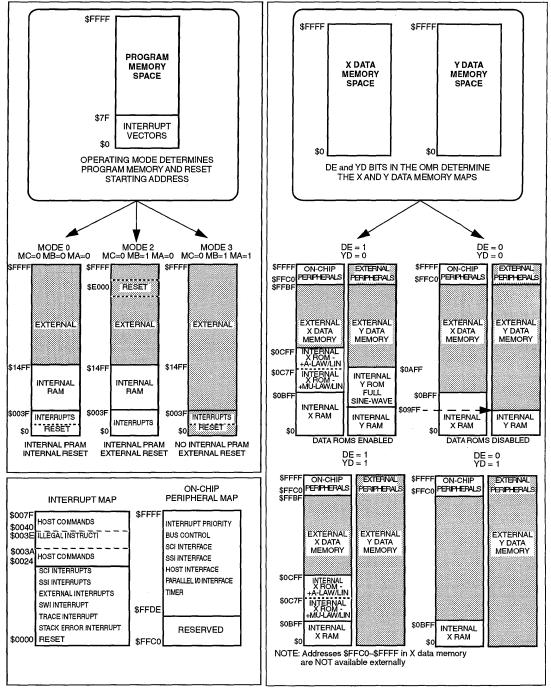

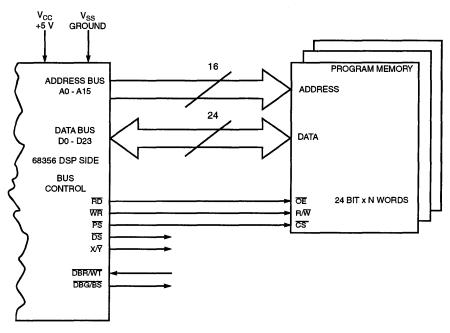

| 9.2   | DSP56002 Data and Program Memory                       |     |

| 9.2.1 | Program Memory                                         |     |

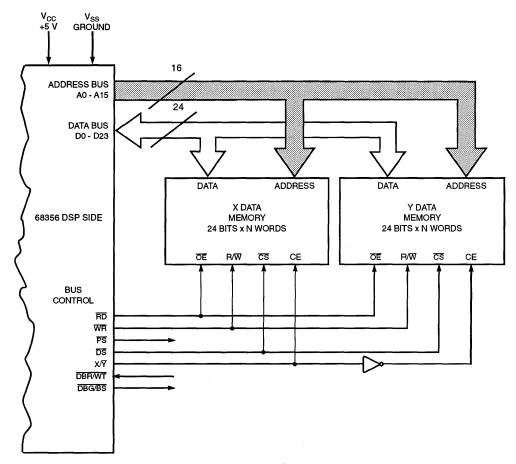

| 9.2.2 | X Data Memory                                          | 9-2 |

| 9.2.3 | Y Data Memory                                          | 9-2 |

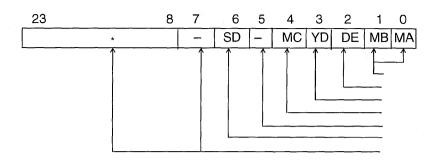

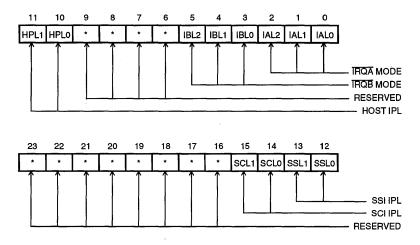

| 9.3   | DSP56002 Operating Mode Register (OMR)                 | 9-2 |

| 9.3.1 | Chip Operating Mode (Bits 0 and 1)                     | 9-4 |

| 9.3.2 | Data ROM Enable (Bit 2)                                | 9-4 |

| 9.3.3 | Internal Y Memory Disable Bit (Bit 3)                  | 9-4 |

| 9.3.4 | Chip Operating Mode (Bit 4)                            | 9-5 |

| 9.3.5 | Reserved (Bit 5)                                       | 9-5 |

| 9.3.6 | Stop Delay (Bit 6)                                     | 9-5 |

| 9.3.7 | Reserved OMR Bits (Bits 7–23)                          | 9-5 |

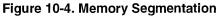

| 9.4   | DSP56002 Operating Modes                               | 9-5 |

| 9.4.1 | Single Chip Mode (Mode 0)                              | 9-6 |

| 9.4.2 | Bootstrap From EPROM (Mode 1)                          | 9-6 |

| 9.4.3 | Normal Expanded Mode (Mode 2)                          | 9-9 |

| 9.4.4 | Development Mode (Mode 3)                              | 9-9 |

| 9.4.5 | Reserved (Mode 4)                                      | 9-9 |

| 9.4.6 | Bootstrap From Host (Mode 5)                           | 9-9 |

| 9.4.7 | Bootstrap From SCI (Mode 6)                            | 9-9 |

| 9.4.8 | Reserved (Mode 7)9                                     | ·10 |

| 9.5   | DSP56002 Interrupt Priority Register                   | -10 |

| 9.6   | DSP56002 Phase-Locked Loop (PLL) Multiplication Factor | 10  |

Paragraph

Number

# Paragraph Number

Title

#### Page Number

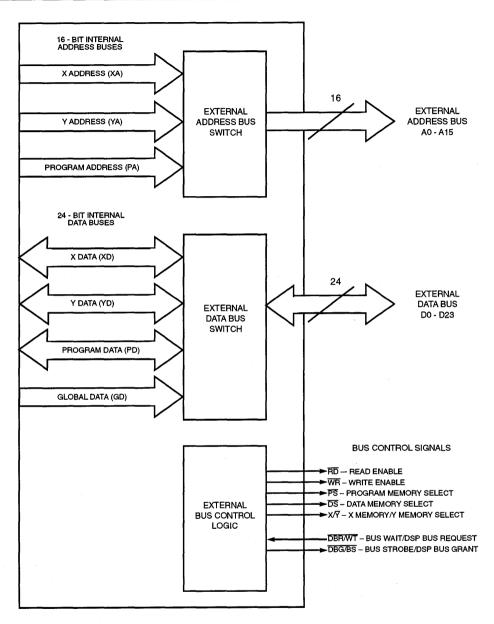

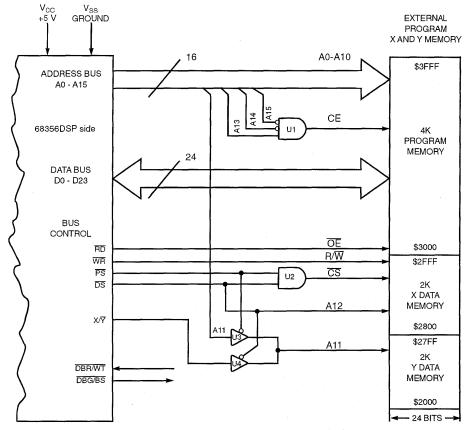

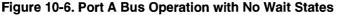

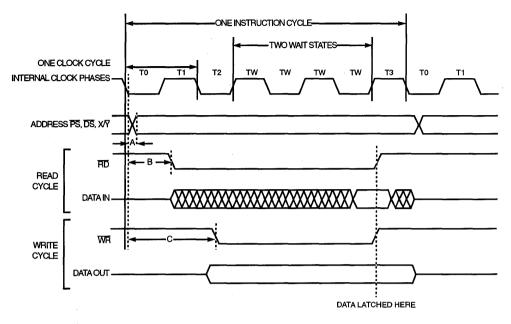

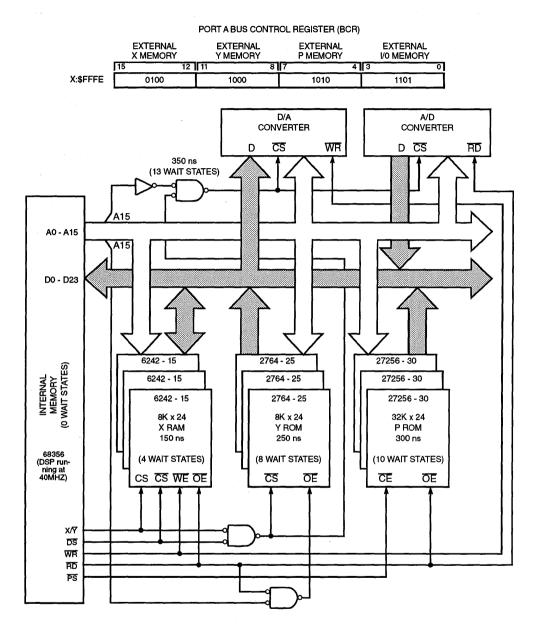

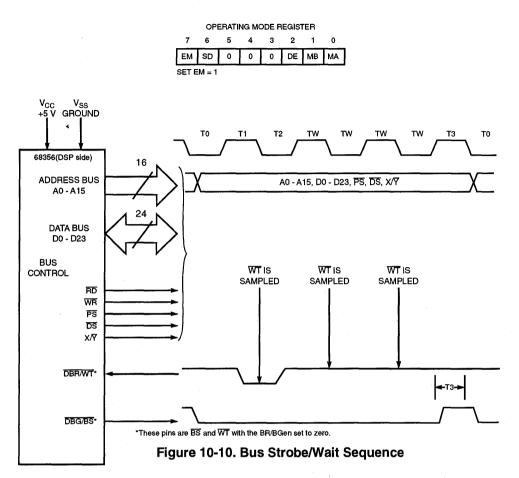

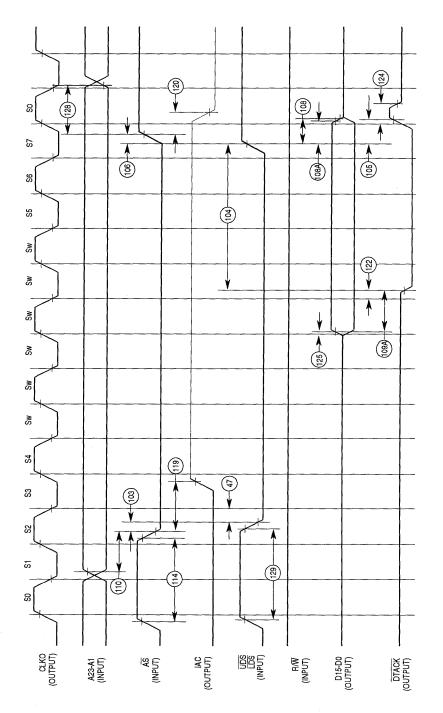

#### Section 10 DSP Port A

| Introduction                                                      |

|-------------------------------------------------------------------|

| DSP Port A Interface10-1                                          |

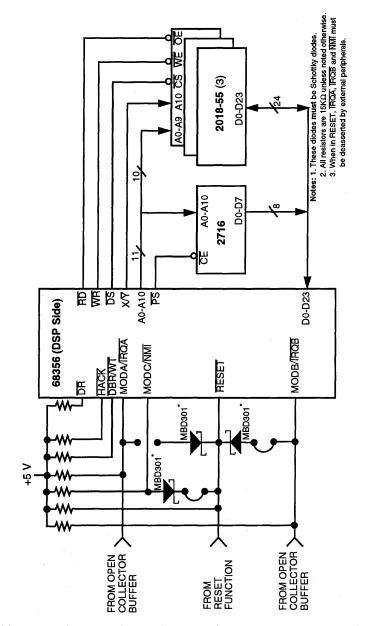

| Port A Timing10-7                                                 |

| Port A Wait States10-9                                            |

| Bus Control Register (BCR)10-9                                    |

| Bus Strobe and Wait Pins                                          |

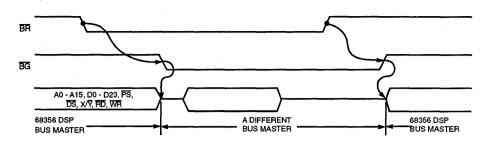

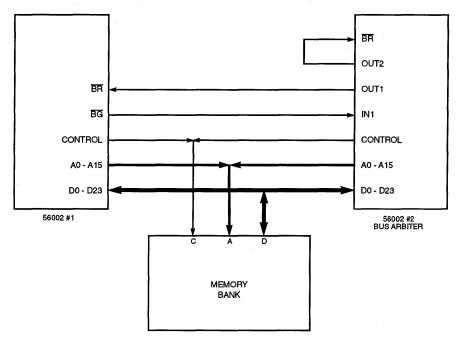

| Bus Arbitration and Shared Memory10-13                            |

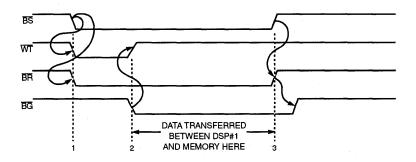

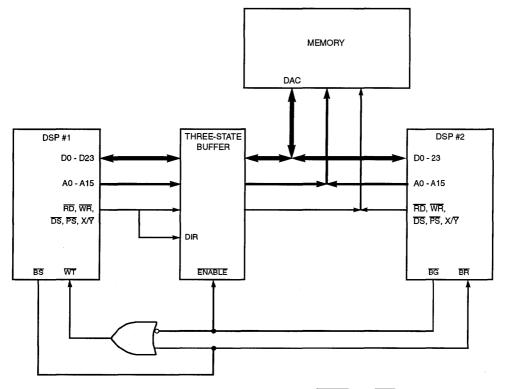

| Bus Arbitration Using Only DBR and DBG With Internal Control10-14 |

| Bus Arbitration Using DBR and BG, and WT and BS With No           |

| Overhead 10-15                                                    |

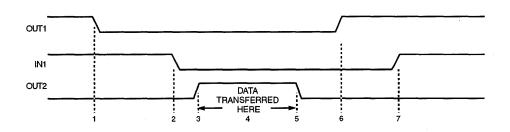

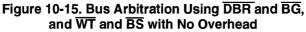

| Signaling Using Semaphores10-17                                   |

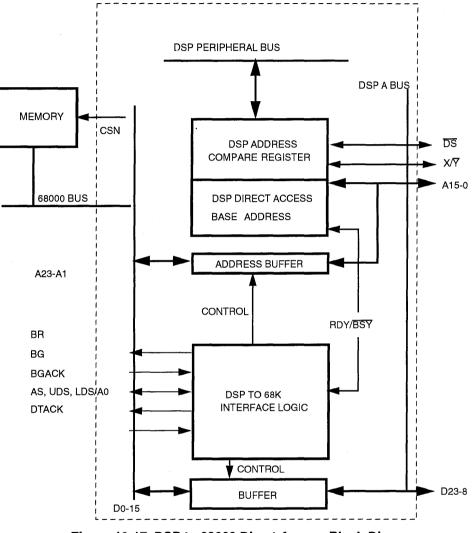

| DSP to Imp Direct Access Mechanism10-19                           |

| DSP to IMP Write Accesses10-21                                    |

| DSP to IMP Read Accesses10-22                                     |

| Programmer's Model10-23                                           |

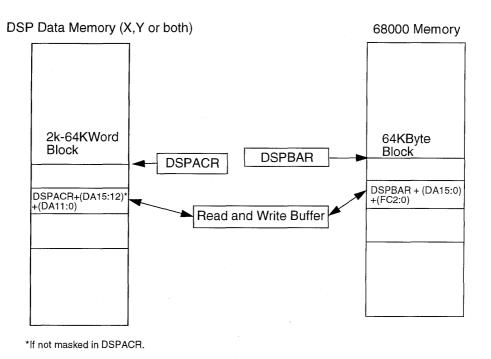

| DSP Address Compare Register - DSPACR 10-23                       |

| DSP Base Address Register - DSPBAR10-25                           |

|                                                                   |

#### Section 11 DSP Host Port

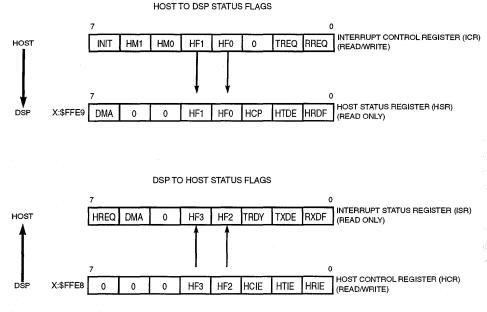

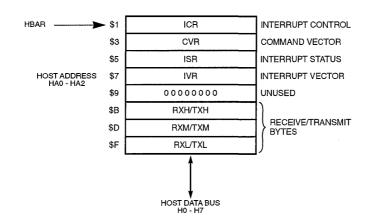

| 11.1       | Introduction                                    | 11-1 |

|------------|-------------------------------------------------|------|

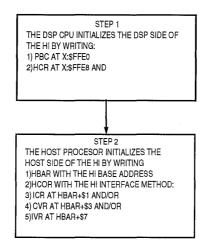

| 11.1.1     | Enabling the Host Interface                     | 11-2 |

| 11.1.2     | Host Interface - DSP CPU Viewpoint              |      |

| 11.1.3     | Programming Model – DSP CPU Viewpoint           |      |

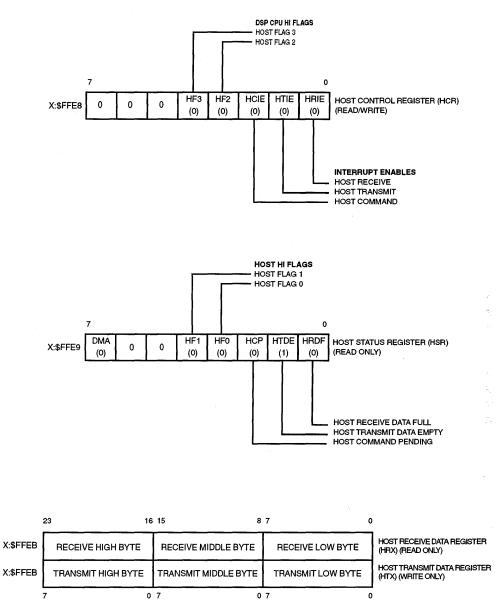

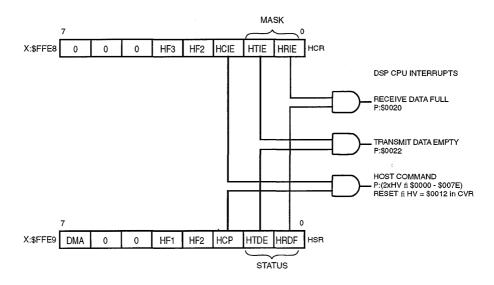

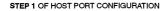

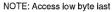

| 11.1.3.1   | Host Control Register (HCR)                     |      |

| 11.1.3.1.1 | HCR Host Receive Interrupt Enable (HRIE) Bit 0  |      |

| 11.1.3.1.2 | HCR Host Transmit Interrupt Enable (HTIE) Bit 1 |      |

| 11.1.3.1.3 | HCR Host Command Interrupt Enable (HCIE) Bit 2  |      |

| 11.1.3.1.4 | HCR Host Flag 2 (HF2) Bit 3                     |      |

| 11.1.3.1.5 | HCR Host Flag 3 (HF3) Bit 4                     | 11-5 |

| 11.1.3.1.6 | HCR Reserved Control (Bits 5, 6, and 7)         | 11-6 |

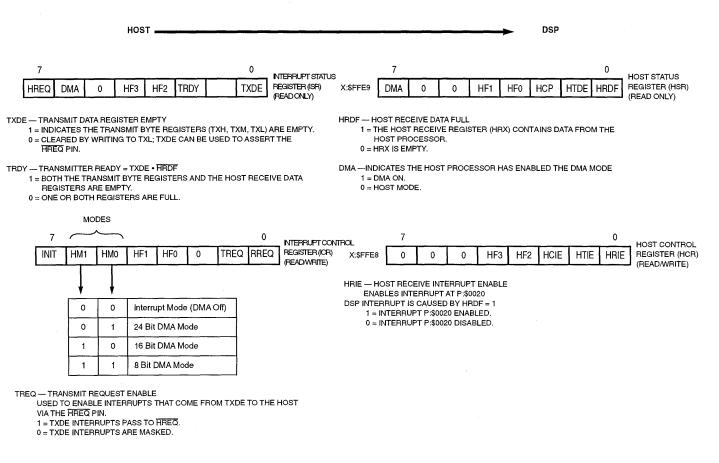

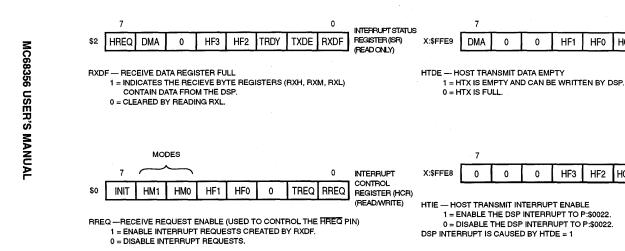

| 11.1.3.2   | Host Status Register (HSR)                      | 11-6 |

| 11.1.3.2.1 | HSR Host Receive Data Full (HRDF) Bit 0         |      |

| 11.1.3.2.2 | HSR Host Transmit Data Empty (HTDE) Bit 1       | 11-6 |

| 11.1.3.2.3 | HSR Host Command Pending (HCP) Bit 2            | 11-6 |

| 11.1.3.2.4 | HSR Host Flag 0 (HF0) Bit 3                     | 11-7 |

| 11.1.3.2.5 | HSR Host Flag 1 (HF1) Bit 4                     | 11-7 |

| 11.1.3.2.6 | HSR Reserved Status (Bits 5 and 6)              | 11-7 |

| 11.1.3.2.7 | HSR DMA Status (DMA) Bit 7                      | 11-7 |

| 11.1.3.3   | Host Receive Data Register (HRX)                | 11-8 |

| 11.1.3.4   | Host Transmit Data Register (HTX)               | 11-8 |

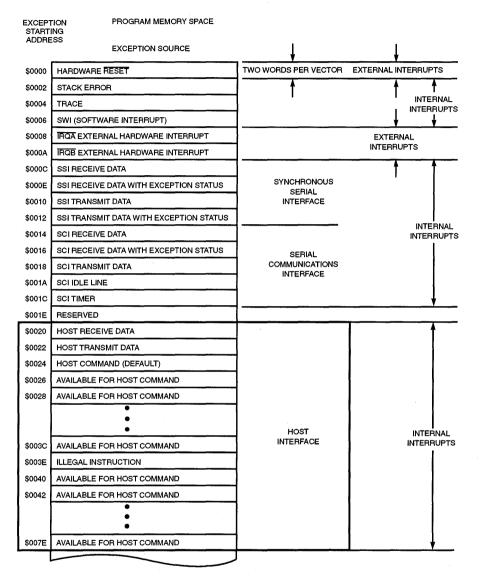

| 11.1.3.5   | Register Contents After Reset                   | 11-8 |

| 11.1.3.6   | Host Interface DSP CPU Interrupts               | 11-8 |

| _ |     |    |

|---|-----|----|

| т | - ÷ | 2  |

|   | 11  | ıe |

| Paragraph<br>Number      | Title                                                                | Page<br>Numbe |

|--------------------------|----------------------------------------------------------------------|---------------|

| 11.1.3.7                 | Host Port Usage Considerations - DSP Side                            | 11-8          |

| 11.1.4                   | Host Interface – Host Processor Viewpoint                            |               |

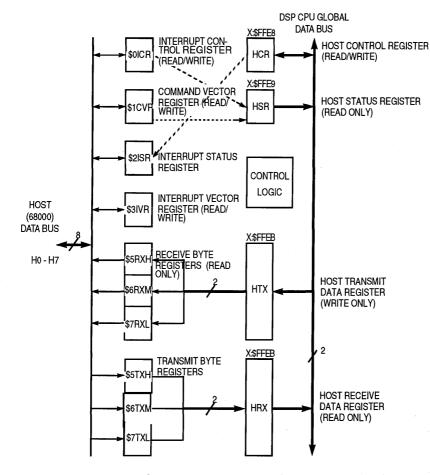

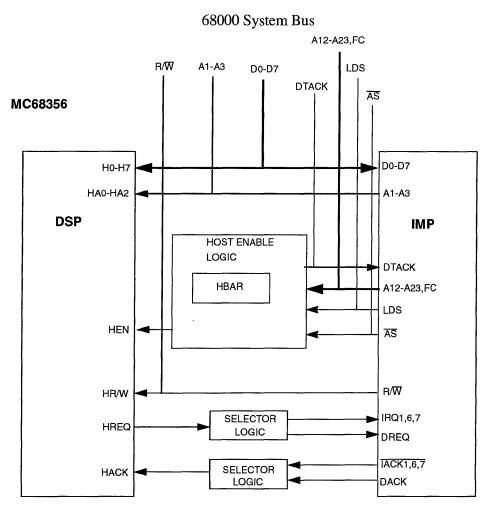

| 11.2                     | Host Port to 68000 Bus Connection                                    | 11-9          |

| 11.2.1                   | DSP Host Port Configuration Option Register - HCOR                   | 11-11         |

| 11.2.2                   | DSP Host Port Base Address Register - HBAR                           |               |

| 11.2.3                   | Programming Model – Host Processor Viewpoint                         |               |

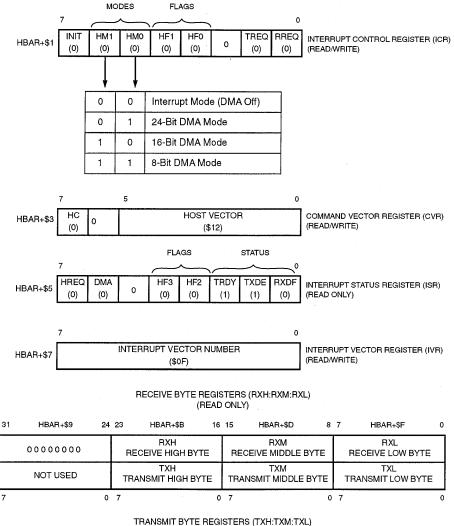

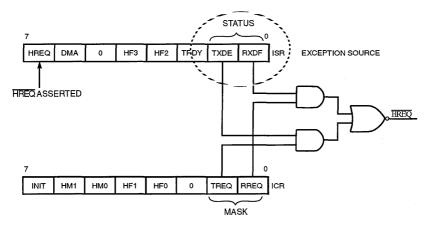

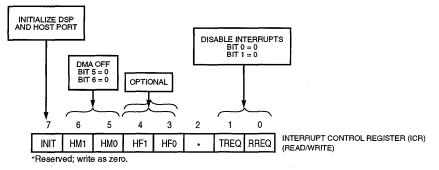

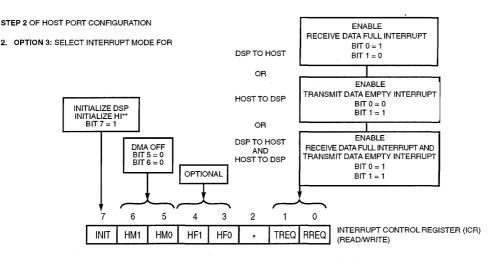

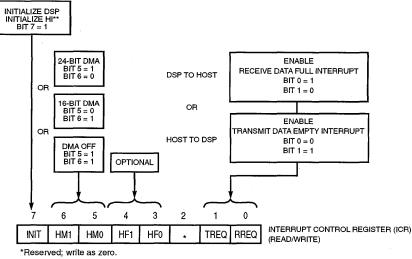

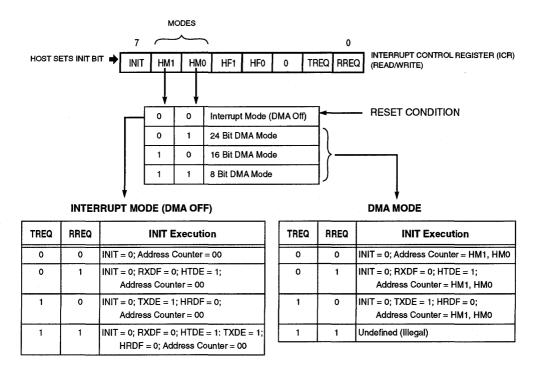

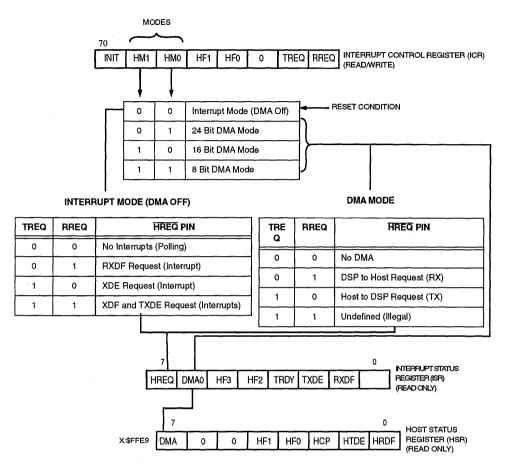

| 11.2.3.1                 | Interrupt Control Register (ICR)                                     |               |

| 11.2.3.1.1               | ICR Receive Request Enable (RREQ) Bit 0                              | 11-14         |

| 11.2.3.1.2               | ICR Transmit Request Enable (TREQ) Bit 1                             | 11-16         |

| 11.2.3.1.3               | ICR Reserved Bit (Bit 2)                                             |               |

| 11.2.3.1.4<br>11.2.3.1.5 | ICR Host Flag 0 (HF0) Bit 3<br>ICR Host Flag 1 (HF1) Bit 4           |               |

| 11.2.3.1.5               | ICR Host Mode Control (HM1 and HM0 bits) Bits 5 and 6                |               |

| 11.2.3.1.7               | ICR Initialize Bit (INIT) Bit 7                                      |               |

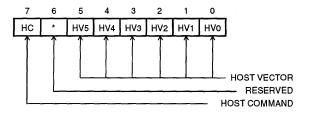

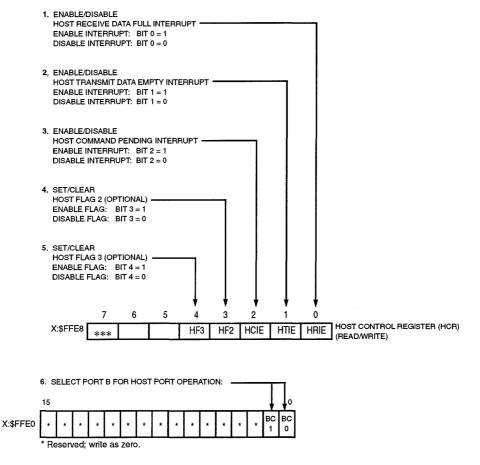

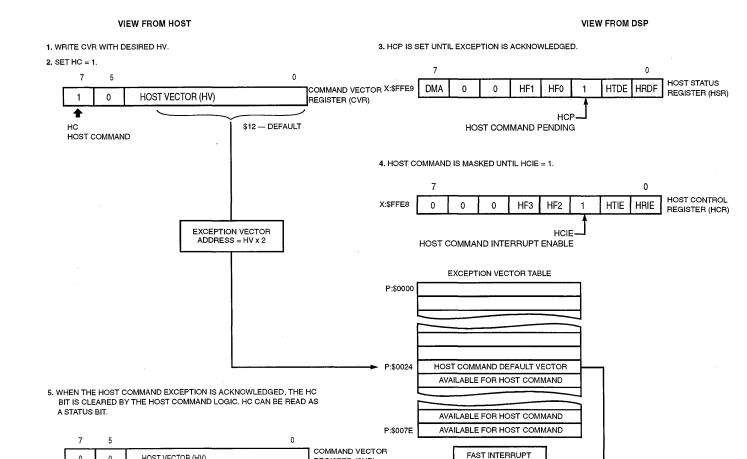

| 11.2.3.2                 | Command Vector Register (CVR)                                        |               |

| 11.2.3.2.1               | CVR Host Vector (HV) Bits 0–5                                        |               |

| 11.2.3.2.2               | CVR Reserved Bit (Bit 6)                                             |               |

| 11.2.3.2.3               | CVR Host Command Bit (HC) Bit 7                                      |               |

| 11.2.3.3                 | Interrupt Status Register (ISR)                                      |               |

| 11.2.3.3.1               | ISR Receive Data Register Full (RXDF) Bit 0                          |               |

| 11.2.3.3.2               | ISR Transmit Data Register Empty (TXDE) Bit 1                        |               |

| 11.2.3.3.3               | ISR Transmitter Ready (TRDY) Bit 2                                   |               |

| 11.2.3.3.4               | ISR Host Flag 2 (HF2) Bit 3                                          | 11-21         |

| 11.2.3.3.5               | ISR Host Flag 3 (HF3) Bit 4                                          | 11-21         |

| 11.2.3.3.6               | ISR Reserved Bit (Bit 5)                                             |               |

| 11.2.3.3.7               | ISR DMA Status (DMA) Bit 6                                           |               |

| 11.2.3.3.8               | ISR Host Request (HREQ) Bit 7                                        | 11-21         |

| 11.2.3.4                 | Interrupt Vector Register (IVR)                                      | 11-22         |

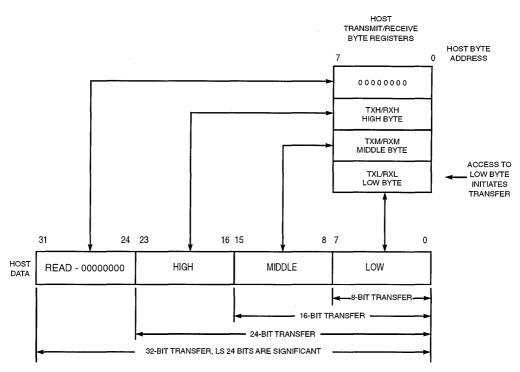

| 11.2.3.5                 | Receive Byte Registers (RXH, RXM, RXL)                               |               |

| 11.2.3.6                 | Transmit Byte Registers (TXH, TXM, TXL)                              |               |

| 11.2.3.7                 | Registers After Reset                                                |               |

| 11.2.4<br>11.2.4.1       | Servicing the Host Interface                                         |               |

| 11.2.4.1                 | HI Host Processor Data Transfer<br>HI Interrupts Host Request (HREQ) |               |

| 11.2.4.3                 | Polling                                                              |               |

| 11.2.4.4                 | Servicing Non-DMA Interrupts                                         |               |

| 11.2.4.5                 | Servicing DMA Interrupts                                             |               |

| 11.2.5                   | HI Application Examples                                              |               |

| 11.2.5.1                 | HI Initialization                                                    |               |

| 11.2.5.2                 | Polling/Interrupt Controlled Data Transfer                           |               |

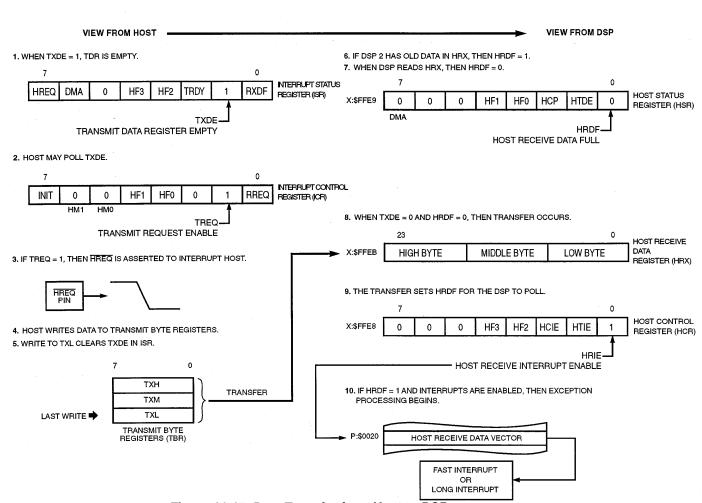

| 11.2.5.2.1               | Host to DSP - Data Transfer                                          |               |

| 11.2.5.2.2               | Host to DSP – Command Vector                                         |               |

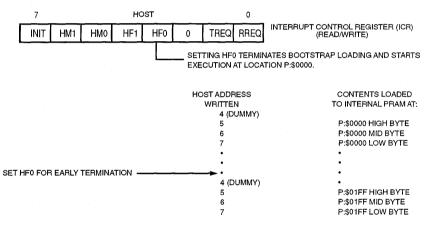

| 11.2.5.2.3               | Host to DSP - Bootstrap Loading Using the HI                         |               |

| 11.2.5.2.4               | DSP to Host Data Transfer                                            |               |

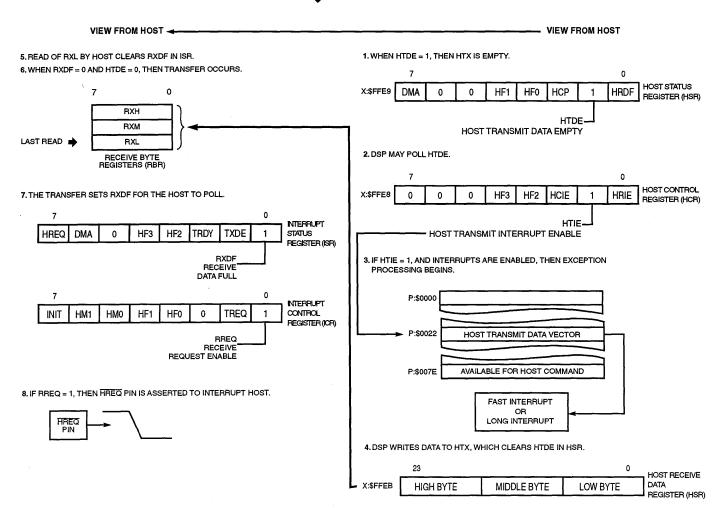

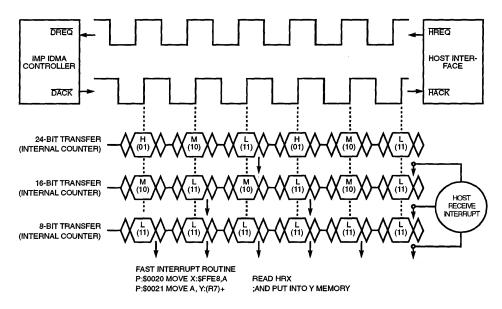

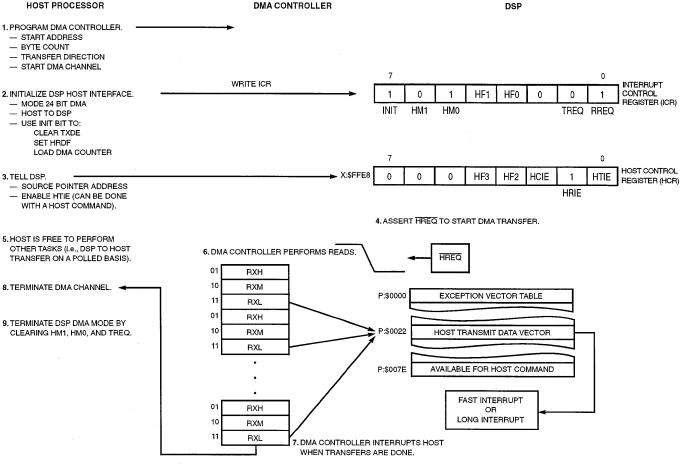

| 11.2.5.3                 | DMA Data Transfer                                                    | 11-38         |

|                          |                                                                      |               |

| Paragraph<br>Number  | Title                                                       | Page<br>Number |

|----------------------|-------------------------------------------------------------|----------------|

| 11.2.5.3.1           | Host To DSP Internal Processing                             | 11-41          |

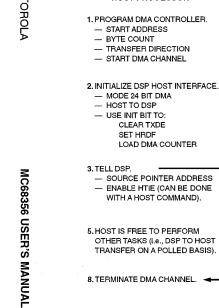

| 11.2.5.3.2           | Host to DSP DMA Procedure                                   |                |

| 11.2.5.3.3           | DSP to Host Internal Processing                             |                |

| 11.2.5.3.4           | DSP to Host DMA Procedure                                   |                |

| 11.2.5.4             | Host Port Usage Considerations-Host Side                    | 11-46          |

|                      | Section 12                                                  |                |

|                      | DSP Serial Ports                                            |                |

| 12.1                 | Introduction                                                |                |

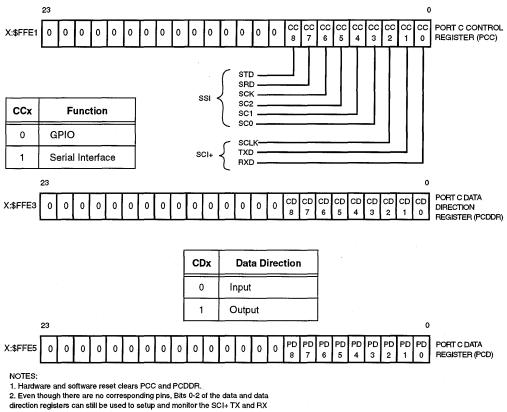

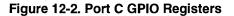

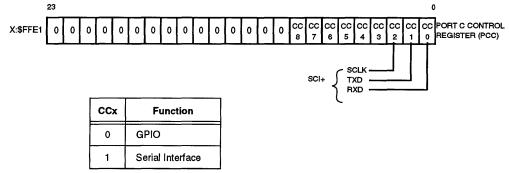

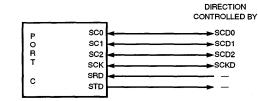

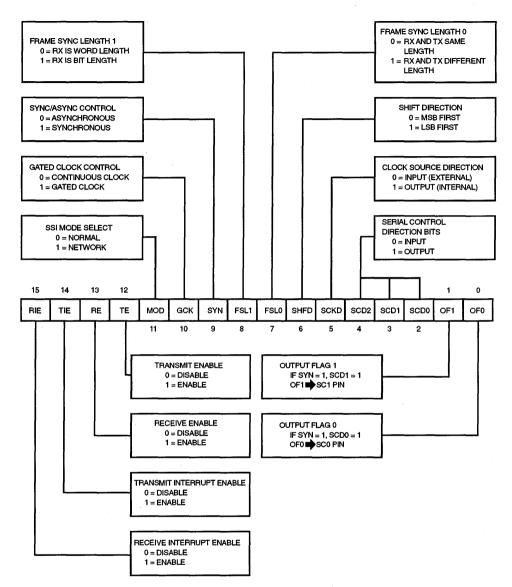

| 12.2                 | General-Purpose I/O (Port C)                                |                |

| 12.2.1               | Programming General Purpose I/O                             |                |

| 12.2.2               | Port C General Purpose I/O Timing                           |                |

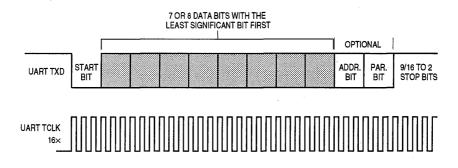

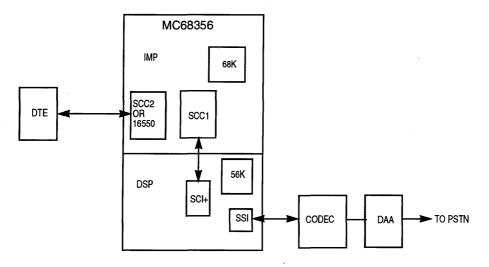

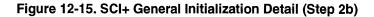

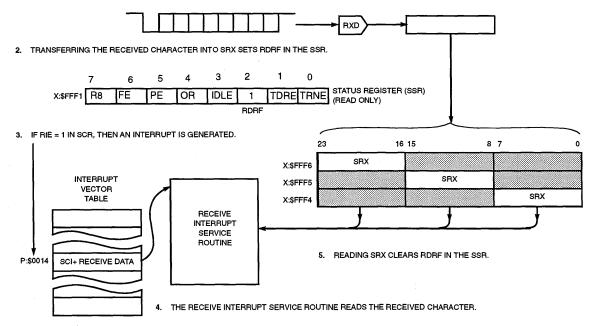

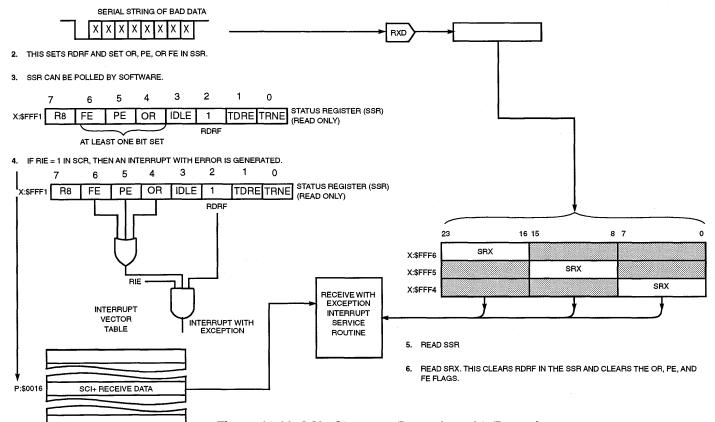

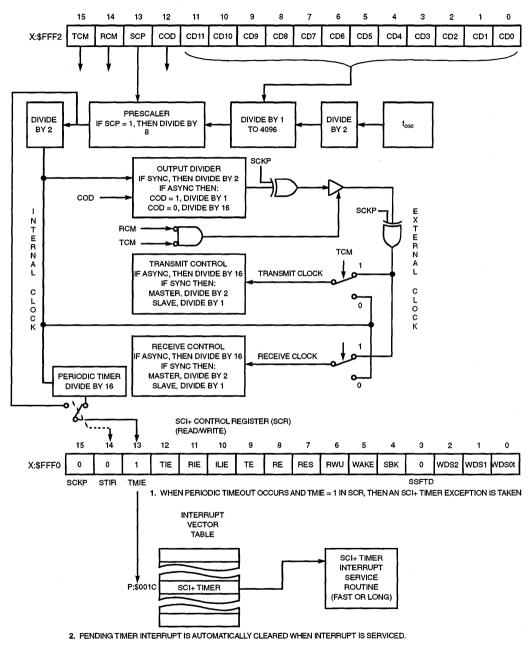

| 12.3                 | Serial Communication Interface (SCI+)                       |                |

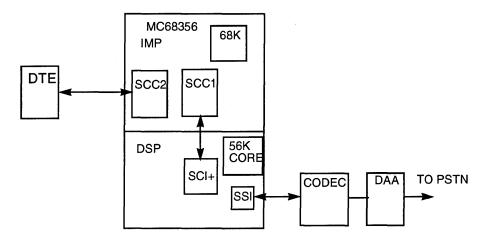

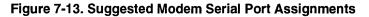

| 12.3.1               | SCI+ to IMP Connection Options                              |                |

| 12.3.2               | The SCI+ in a Modern Application                            |                |

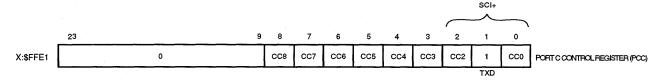

| 12.3.3               | Programming Port C to Enable the SCI+                       |                |

| 12.3.3.1             | Receive Data (RXD)                                          |                |

| 12.3.3.2<br>12.3.3.3 | Transmit Data (TXD)<br>SCI+ Serial Clocks (TXCLK and RXCLK) |                |

| 12.3.3.3             |                                                             |                |

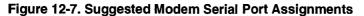

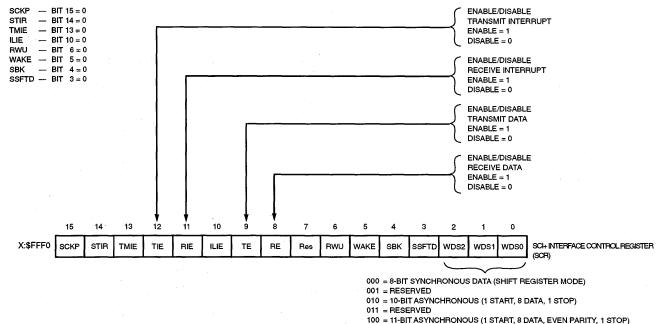

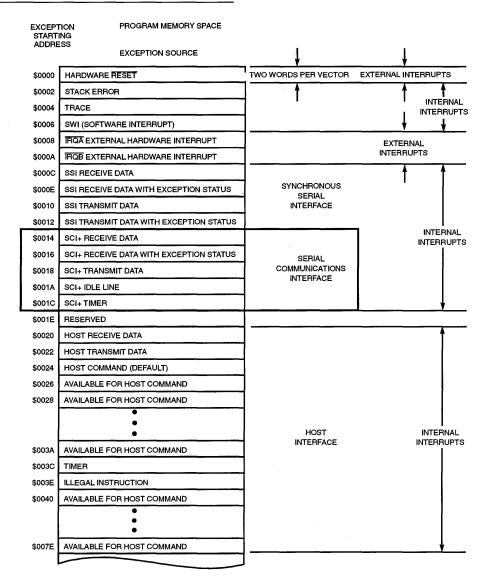

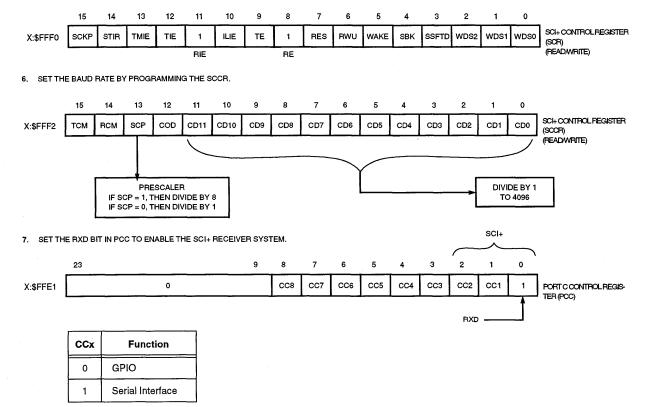

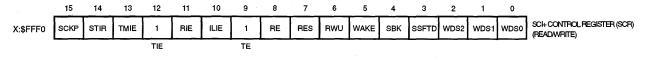

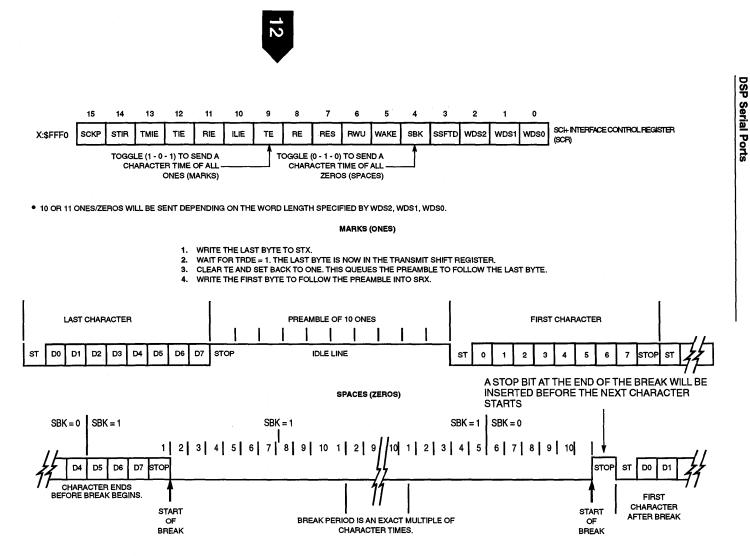

| 12.3.4               | SCI+ Programming Model<br>SCI+ Control Register (SCR)       |                |

| 12.3.4.1             | SCR Word Select (WDS0, WDS1, WDS2) Bits 0, 1, and 2         |                |

| 12.3.4.1.2           | SCR SCI+ Shift Direction (SSFTD) Bit 3                      |                |

| 12.3.4.1.3           | SCR Send Break (SBK) Bit 4                                  |                |

| 12.3.4.1.4           | SCR Wakeup Mode Select (WAKE) Bit 5                         |                |

| 12.3.4.1.5           | SCR Receiver Wakeup Enable (RWU) Bit 6                      |                |

| 12.3.4.1.6           | Bit 7                                                       |                |

| 12.3.4.1.7           | SCR Receiver Enable (RE) Bit 8                              |                |

| 12.3.4.1.8           | SCR Transmitter Enable (TE) Bit 9                           |                |

| 12.3.4.1.9           | SCR Idle Line Interrupt Enable (ILIE) Bit 10                |                |

| 12.3.4.1.10          | SCR SCI+ Receive Interrupt Enable (RIE) Bit 11              | 12-15          |

| 12.3.4.1.11          | SCR SCI+ Transmit Interrupt Enable (TIE) Bit 12             |                |

| 12.3.4.1.12          | SCR Timer Interrupt Enable (TMIE) Bit 13                    |                |

| 12.3.4.1.13          | SCR SCI+ Timer Interrupt Rate (STIR) Bit 14                 | 12-16          |

| 12.3.4.1.14          | SCR SCI+ Clock Polarity (SCKP) Bit 15                       |                |

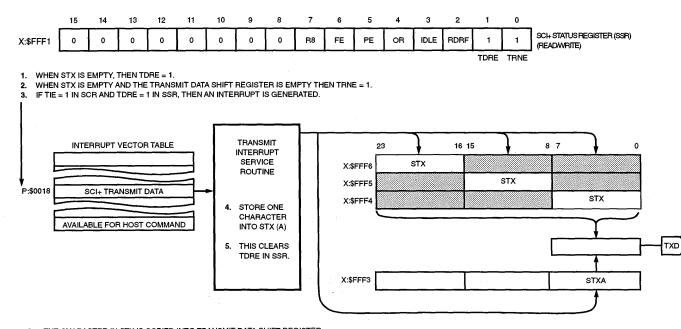

| 12.3.4.2             | SCI+ Status Register (SSR)                                  |                |

| 12.3.4.2.1           | SSR Transmitter Empty (TRNE) Bit 0                          | 12-16          |

| 12.3.4.2.2           | SSR Transmit Data Register Empty (TDRE) Bit 1               |                |

| 12.3.4.2.3           | SSR Receive Data Register Full (RDRF) Bit 2                 |                |

| 12.3.4.2.4           | SSR Idle Line Flag (IDLE) Bit 3                             |                |

| 12.3.4.2.5           | SSR Overrun Error Flag (OR) Bit 4                           |                |

| 12.3.4.2.6           | SSR Parity Error (PE) Bit 5                                 |                |

| 12.3.4.2.7           | SSR Framing Error Flag (FE) Bit 6                           |                |

| 12.3.4.2.8           | SSR Received Bit 8 Address (R8) Bit 7                       |                |

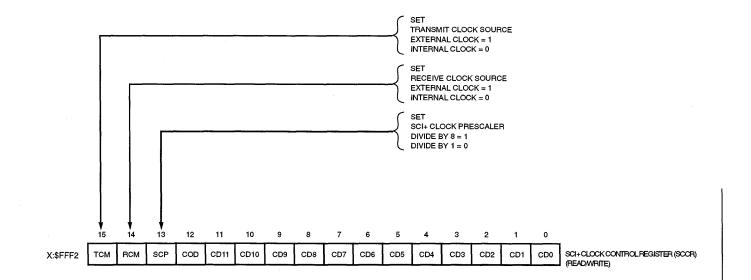

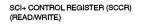

| 12.3.4.3             | SCI+ Clock Control Register (SCCR)                          | 12-10          |

| Paragraph<br>Number | Title                                                 | Page<br>Number |

|---------------------|-------------------------------------------------------|----------------|

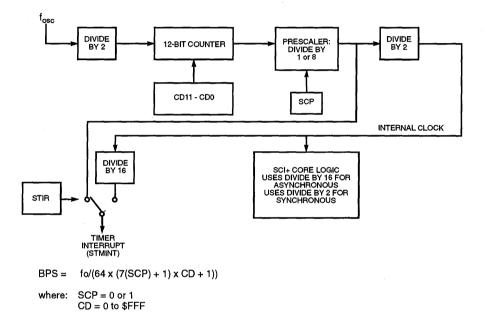

| 12.3.4.3.1          | SCCR Clock Divider (CD11–CD0) Bits 11–0               |                |

| 12.3.4.3.2          | SCCR Clock Out Divider (COD) Bit 12                   | 12-19          |

| 12.3.4.3.3          | SCCR SCI+ Clock Prescaler (SCP) Bit 13                |                |

| 12.3.4.3.4          | SCCR Receive Clock Mode Source Bit (RCM) Bit 14       | 12-20          |

| 12.3.4.3.5          | SCCR Transmit Clock Source Bit (TCM) Bit 15           | 12-20 🌷        |

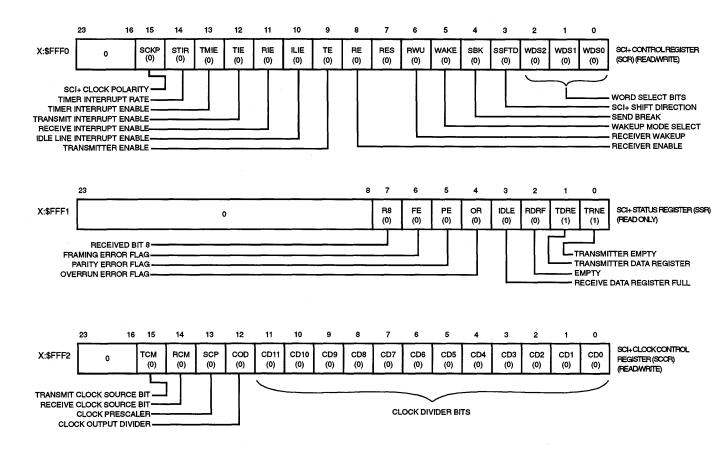

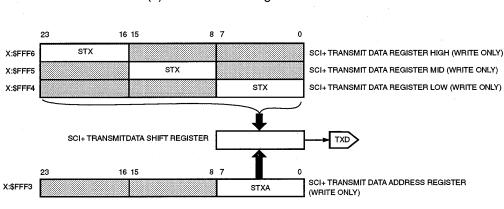

| 12.3.4.4            | SCI+ Data Registers                                   |                |

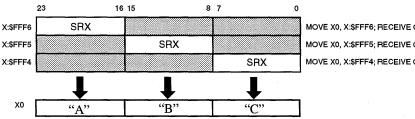

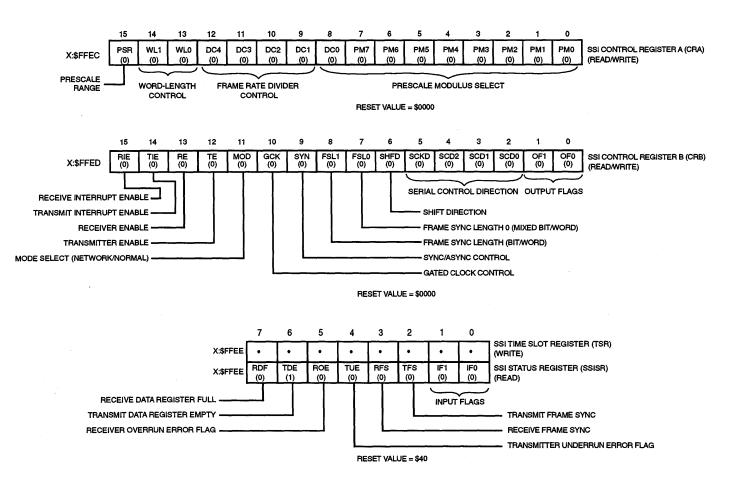

| 12.3.4.4.1          | SCI+ Receive Registers                                | 12-21          |

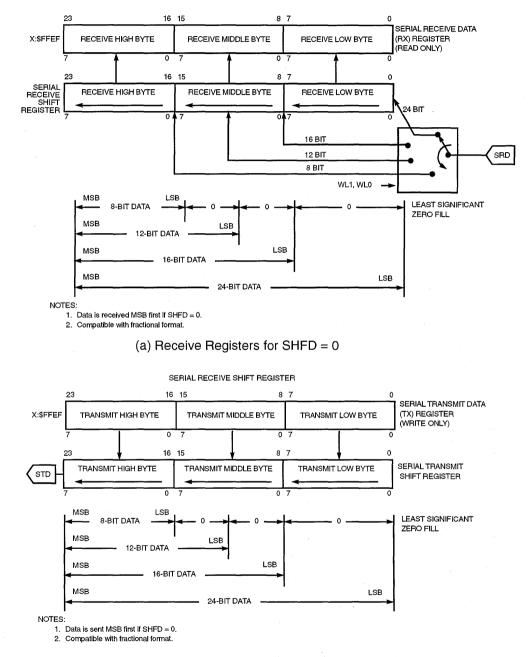

| 12.3.4.4.2          | SCI+ Transmit Registers                               | 12-21          |

| 12.3.4.5            | Preamble, Break, and Data Transmission Priority       | 12-23          |

| 12.3.5              | Register Contents After Reset                         | 12-23          |

| 12.3.6              | SCI+ Initialization                                   |                |

| 12.3.7              | SCI+ Exceptions                                       | 12-29          |

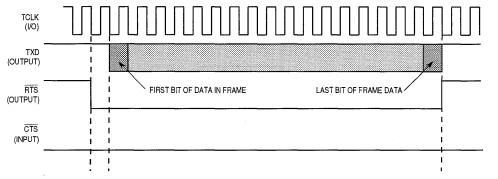

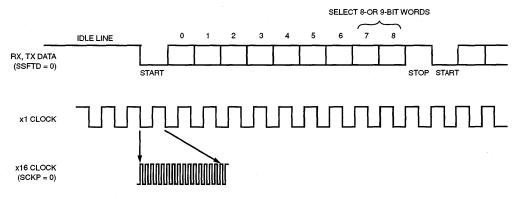

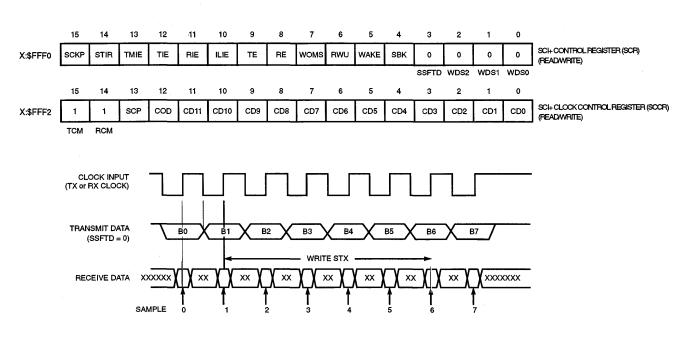

| 12.3.8              | Synchronous Data                                      |                |

| 12.3.9              | Asynchronous Data                                     | 12-35          |

| 12.3.9.1            | Asynchronous Data Reception                           |                |

| 12.3.9.2            | Asynchronous Data Transmission                        |                |

| 12.3.10             | SCI+ Timer                                            |                |

| 12.3.11             | Bootstrap Loading Through the SCI+ (Operating Mode 6) | 12-45          |

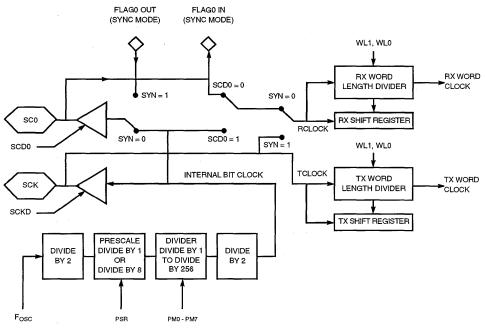

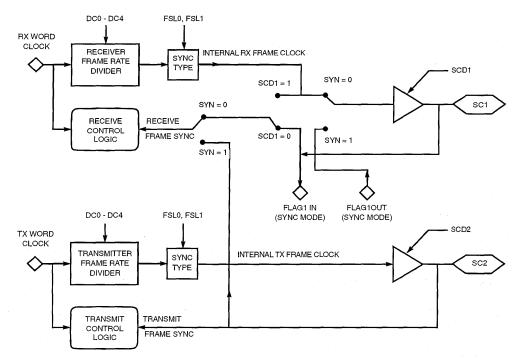

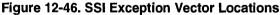

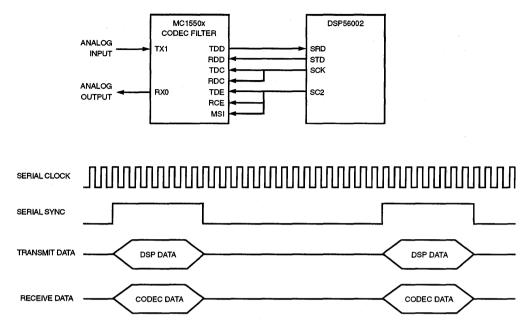

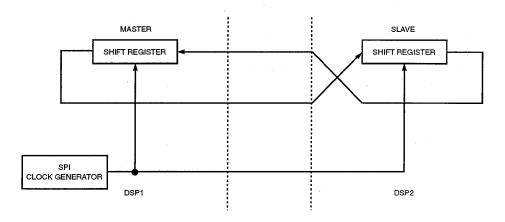

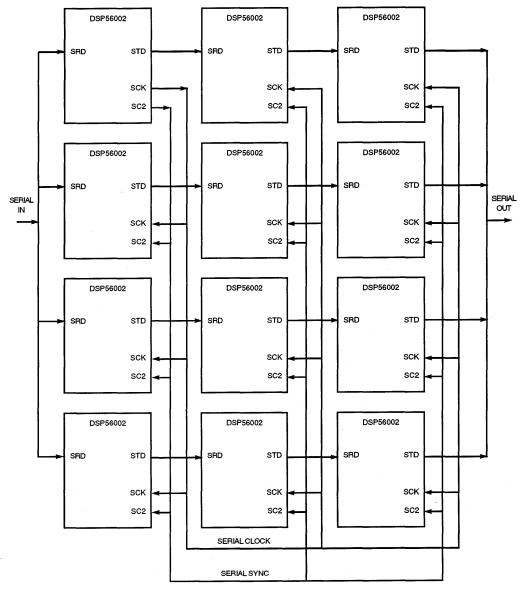

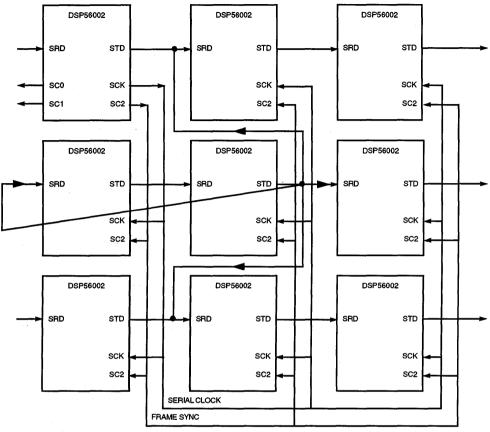

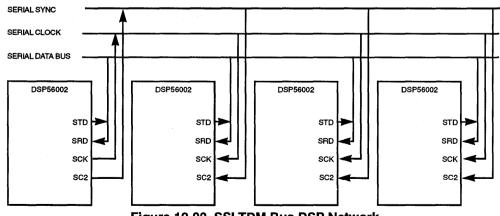

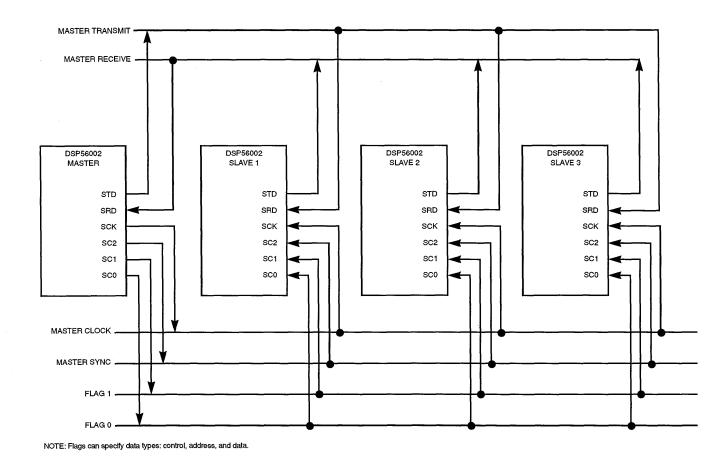

| 12.4                | Synchronous Serial Interface (SSI)                    |                |

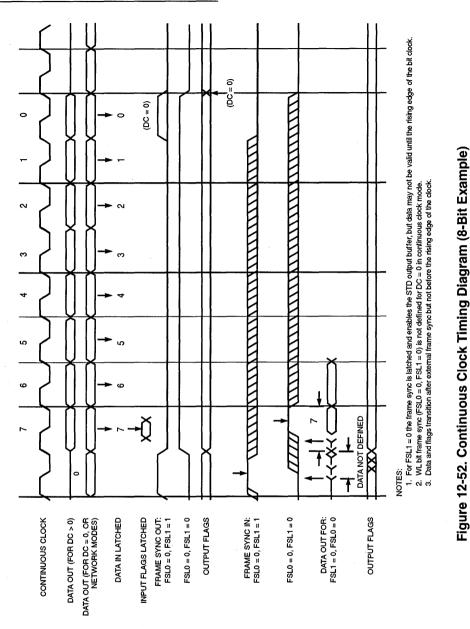

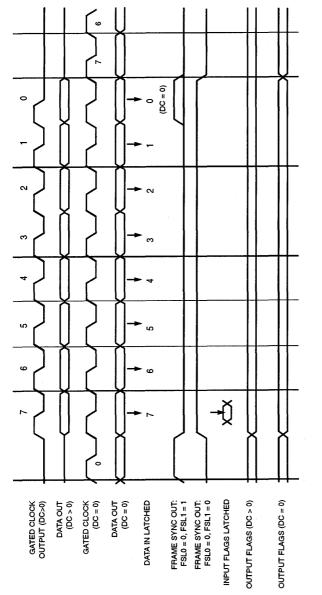

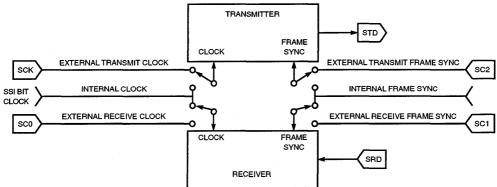

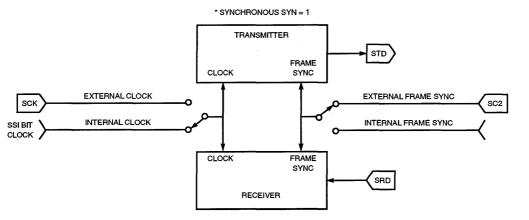

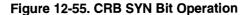

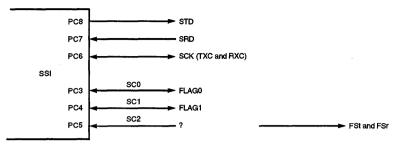

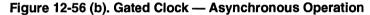

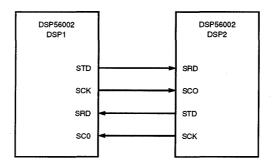

| 12.4.1              | SSI Data and Control Pins                             | 12-51          |

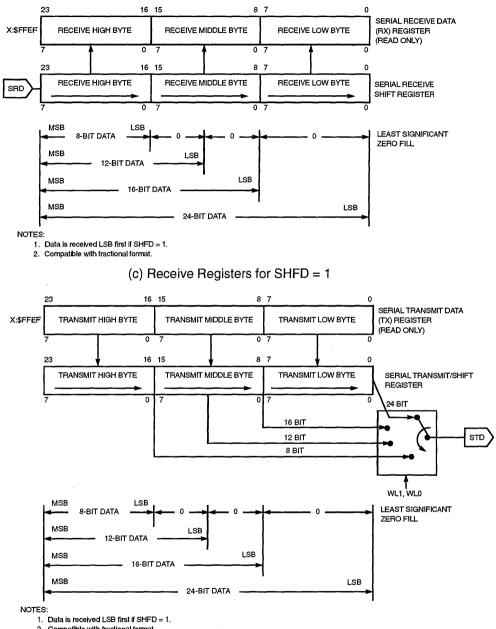

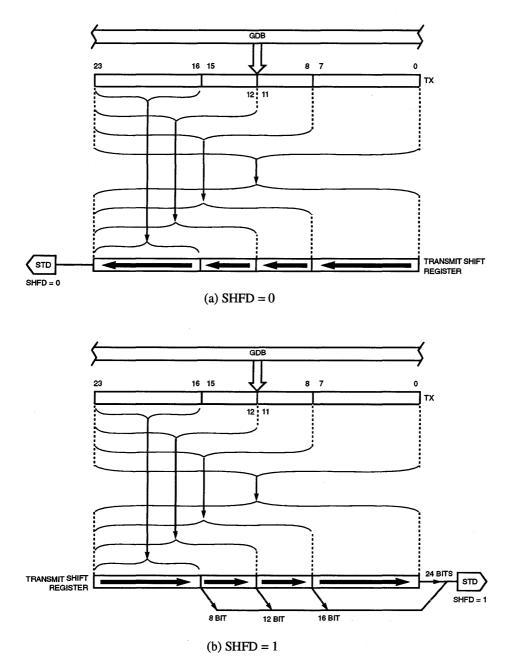

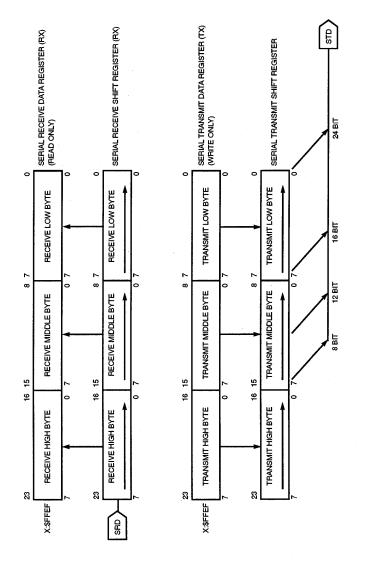

| 12.4.1.1            | Serial Transmit Data Pin (STD)                        | 12-53          |

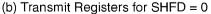

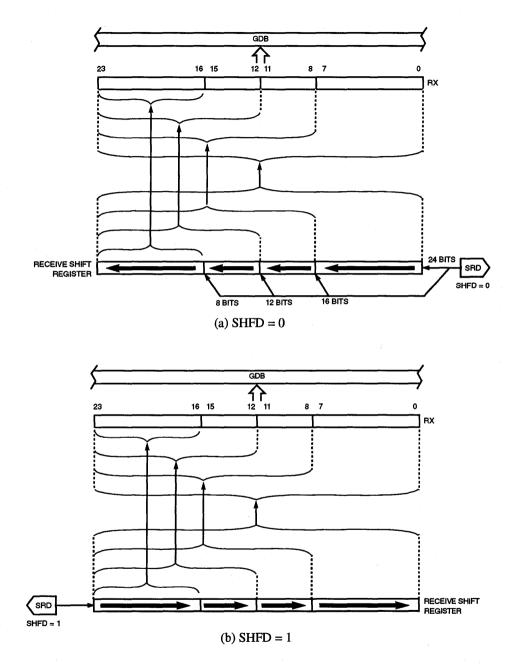

| 12.4.1.2            | Serial Receive Data Pin (SRD)                         | 12-53          |

| 12.4.1.3            | Serial Clock (SCK)                                    |                |

| 12.4.1.4            | Serial Control Pin (SC0)                              | 12-54          |

| 12.4.1.5            | Serial Control Pin (SC1)                              | 12-54          |

| 12.4.2              | SSI Programming Model                                 |                |

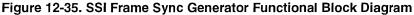

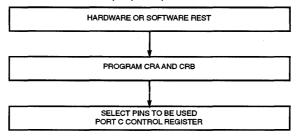

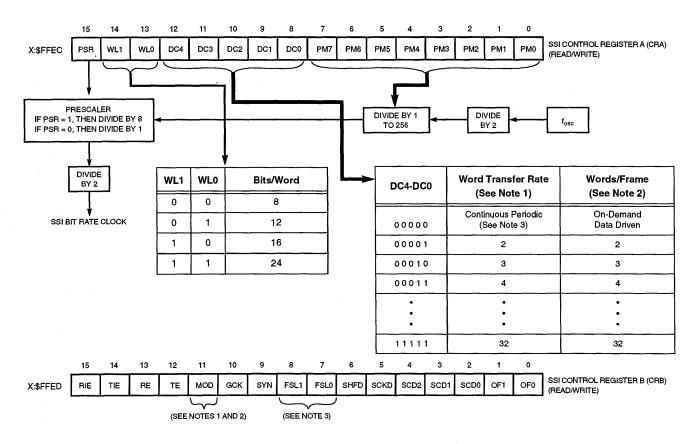

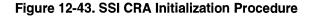

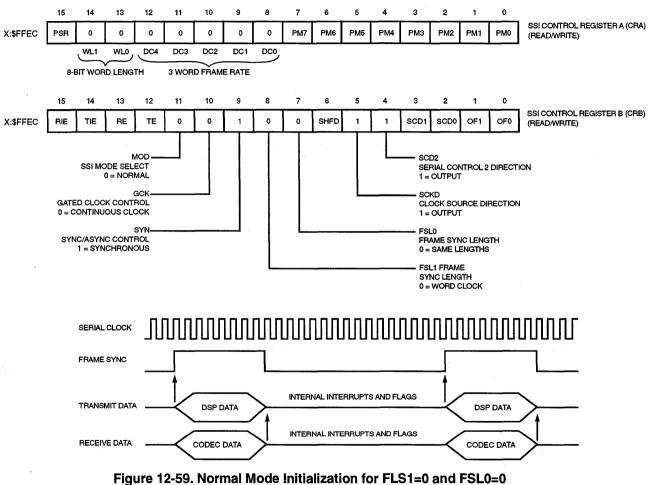

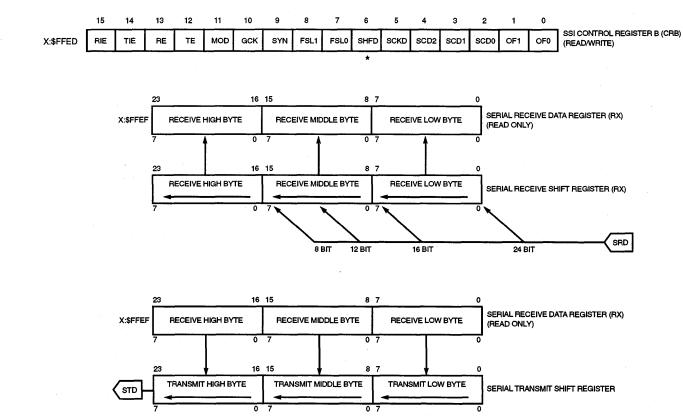

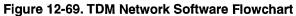

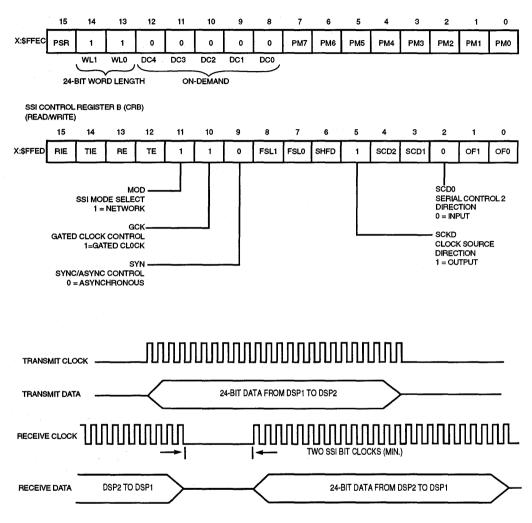

| 12.4.2.1            | SSI Control Register A (CRA)                          | 12-56          |

| 12.4.2.1.1          | CRA Prescale Modulus Select (PM7-PM0) Bits 0-7        | 12-56          |

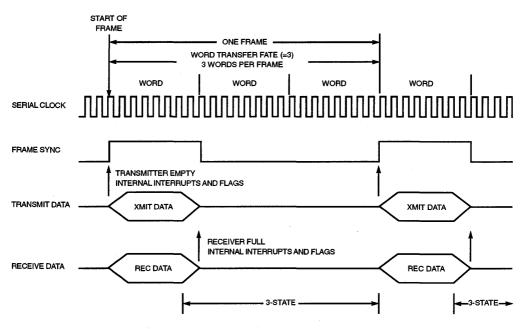

| 12.4.2.1.2          | CRA Frame Rate Divider Control (DC4–DC0) Bits 8–12    | 12-56          |

| 12.4.2.1.3          | CRA Word Length Control (WL0, WL1) Bits 13 and 14     | 12-56          |

| 12.4.2.1.4          | CRA Prescaler Range (PSR) Bit 15                      |                |

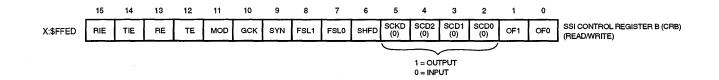

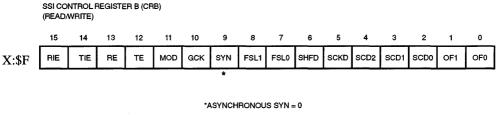

| 12.4.2.2            | SSI Control Register B (CRB)                          |                |

| 12.4.2.2.1          | CRB Serial Output Flag 0 (OF0) Bit 0                  | 12-60          |

| 12.4.2.2.2          | CRB Serial Output Flag 1 (OF1) Bit 1                  | 12-60          |

| 12.4.2.2.3          | CRB Serial Control 0 Direction (SCD0) Bit 2           |                |

| 12.4.2.2.4          | CRB Serial Control 1 Direction (SCD1) Bit 3           |                |

| 12.4.2.2.5          | CRB Serial Control 2 Direction (SCD2) Bit 4           | 12-61          |

| 12.4.2.2.6          | CRB Clock Source Direction (SCKD) Bit 5               | 12-61          |

| 12.4.2.2.7          | CRB Shift Direction (SHFD) Bit 6                      | 12-61          |

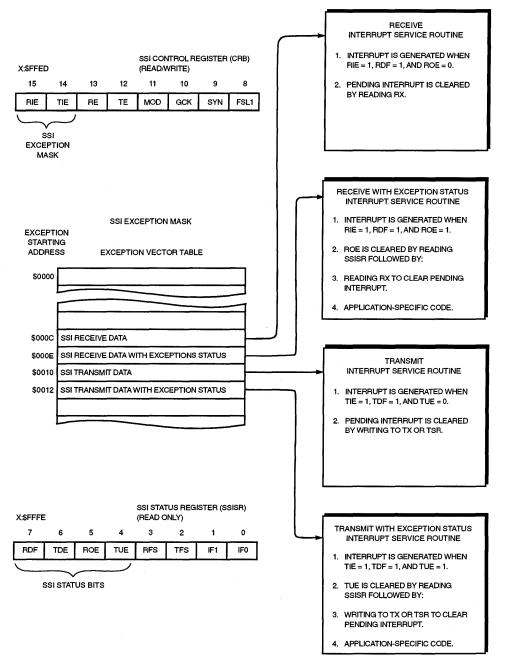

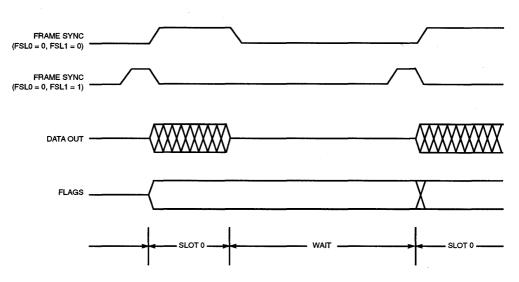

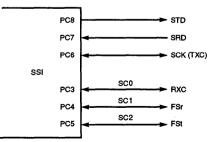

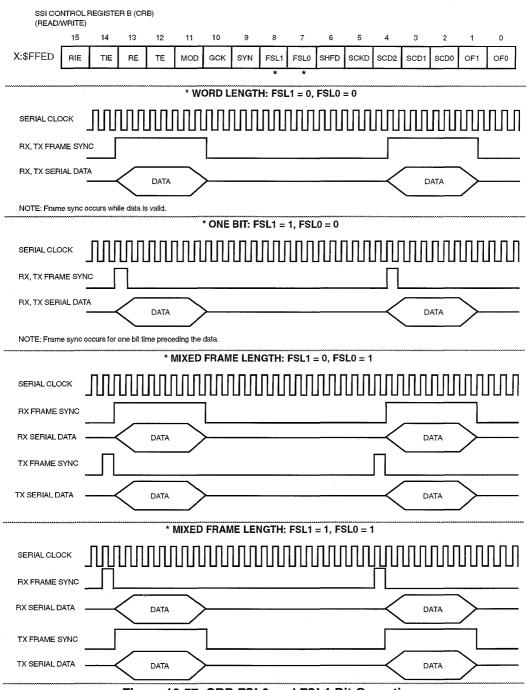

| 12.4.2.2.8          | CRB Frame Sync Length (FSL0 and FSL1) Bits 7 and 8    | 12-61          |

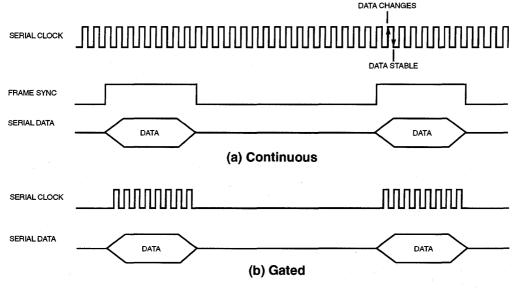

| 12.4.2.2.9          | CRB Sync/Async (SYN) Bit 9                            |                |

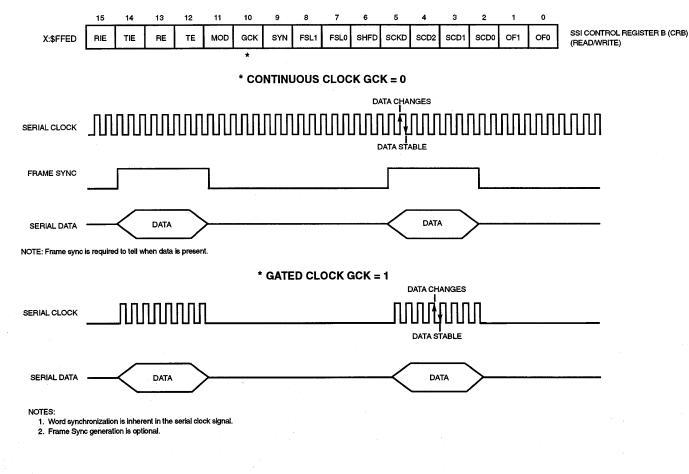

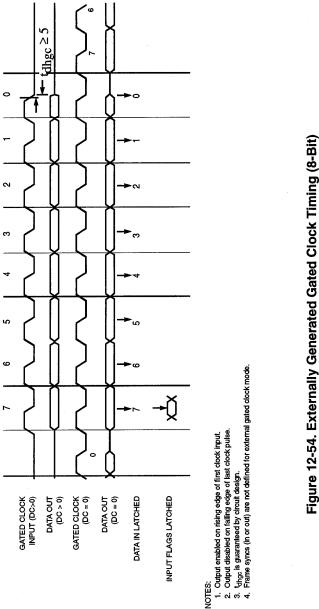

| 12.4.2.2.10         | CRB Gated Clock Control (GCK) Bit 10                  |                |

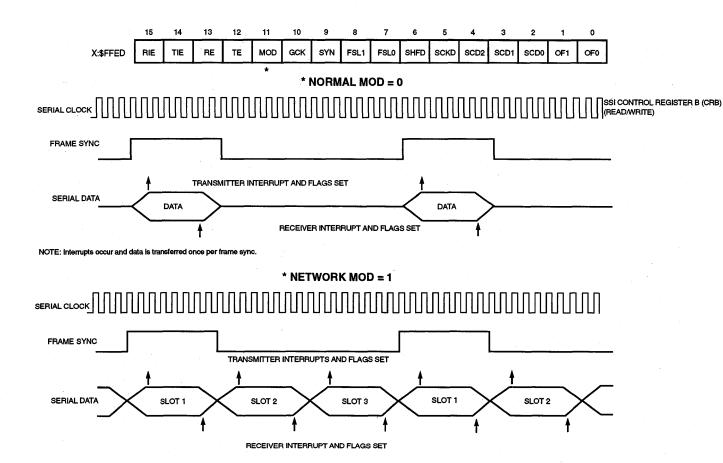

| 12.4.2.2.11         | CRB SSI Mode Select (MOD) Bit 11                      | 12-63          |

| 12.4.2.2.12         | CRB SSI Transmit Enable (TE) Bit 12                   |                |

| 12.4.2.2.13         | CRB SSI Receive Enable (RE) Bit 13                    |                |

| Paragraph<br>Number | Title Page<br>Number                                     |

|---------------------|----------------------------------------------------------|

| 12.4.2.2.14         | CRB SSI Transmit Interrupt Enable (TIE) Bit 1412-64      |

| 12.4.2.2.15         | CRB SSI Receive Interrupt Enable (RIE) Bit 1512-65       |

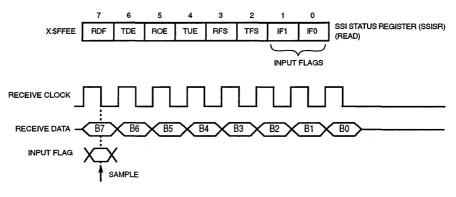

| 12.4.2.3            | SSI Status Register (SSISR)12-65                         |

| 12.4.2.3.1          | SSISR Serial Input Flag 0 (IF0) Bit 012-65               |

| 12.4.2.3.2          | SSISR Serial Input Flag 1 (IF1) Bit 112-65               |

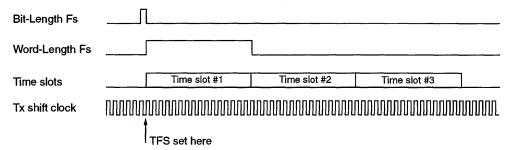

| 12.4.2.3.3          | SSISR Transmit Frame Sync Flag (TFS) Bit 2 12-65         |

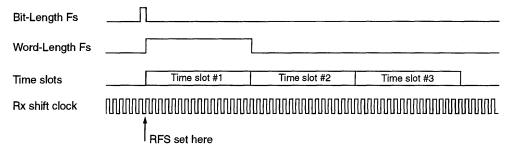

| 12.4.2.3.4          | SSISR Receive Frame Sync Flag (RFS) Bit 3 12-66          |

| 12.4.2.3.5          | SSISR Transmitter Underrun Error Flag (TUE) Bit 4 12-67  |

| 12.4.2.3.6          | SSISR Receiver Overrun Error Flag (ROE) Bit 512-68       |

| 12.4.2.3.7          | SSISR SSI Transmit Data Register Empty (TDE) Bit 6 12-68 |

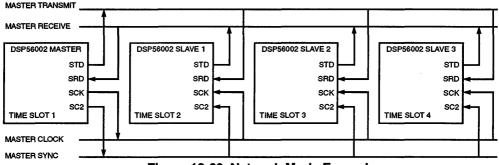

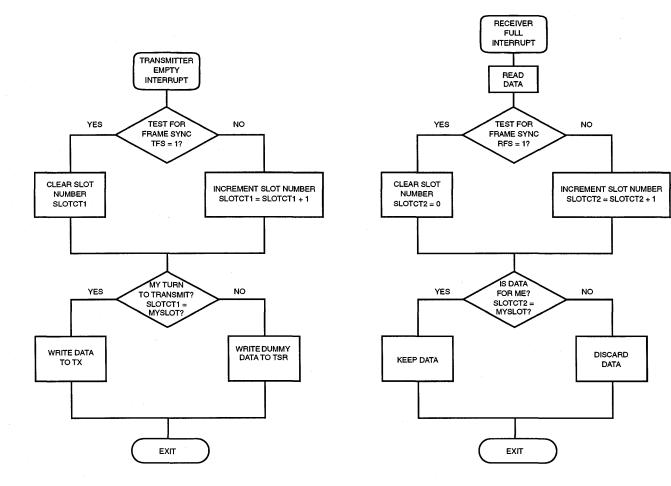

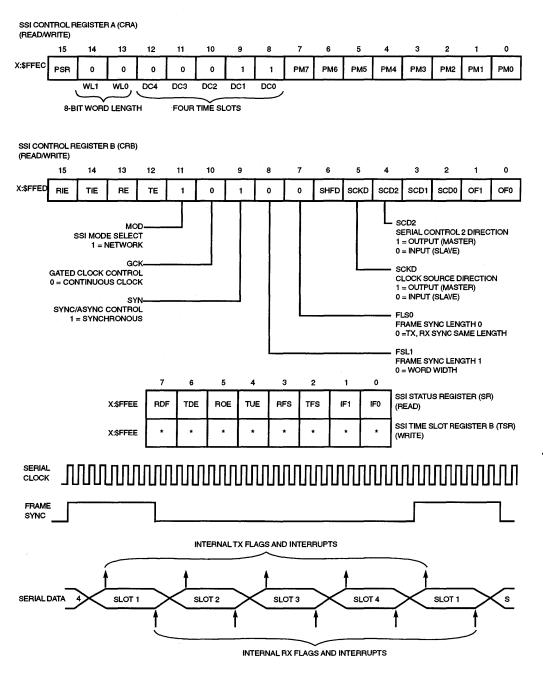

| 12.4.2.3.8          | SSISR SSI Receive Data Register Full (RDF) Bit 712-68    |