## Pentium<sup>™</sup> Processor User's Manual Volume 3: Architecture and Programming Manual

ini

intel pentium

T. R. 16.1

Founded in 1968 to pursue the integration of large numbers of transistors onto tiny silicon chips, Intel's history has been marked by a remarkable number of scientific breakthroughs and innovations. In 1971, Intel introduced the 4004, the first microprocessor. Containing 2300 transistors, this first commercially available computer-on-a-chip is primitive compared with today's million-plus transistor products.

Innovations such as the microprocessor, the erasable programmable read-only memory (EPROM) and the dynamic random access memory (DRAM) revolutionized electronics by making integrated circuits the mainstay of both consumer and business computing products.

Over the last two-and-a-half decades, Intel's business has evolved and today the company's focus is on delivering an extensive line of component, module and system-level building block products to the computer industry. The company's product line covers a broad spectrum, and includes microprocessors, flash memory, microcontrollers, a broad line of PC enhancement and local area network products, multimedia technology products, and massively parallel supercomputers. Intel's 32-bit X86 architecture, represented by the Intel386<sup>TM</sup> and Intel486<sup>TM</sup> microprocessor families, is the de facto standard of modern business computing in millions of PCs worldwide.

Intel has over 26,000 employees located in offices and manufacturing facilities around the world. Today, Intel is the largest semiconductor company in the world.

### LITERATURE

To order Intel literature or obtain literature pricing information in the U.S. and Canada call or write Intel Literature Sales. In Europe and other international locations, please contact your **local** sales office or distributor.

INTEL LITERATURE SALES P.O. Box 7641 Mt. Prospect, IL 60056-7641 In the U.S. and Canada call toll free (800) 548-4725 This 800 number is for external customers only.

#### **CURRENT HANDBOOKS**

Product line handbooks contain data sheets, application notes, article reprints, and other design information. All handbooks can be ordered individually, and most are available in a pre-packaged set in the U.S. and Canada.

| Title                                                                       | Intel<br>Order Number | ISBN          |

|-----------------------------------------------------------------------------|-----------------------|---------------|

| SET OF TWELVE HANDBOOKS<br>(Available in U.S. and Canada)                   | 231003                | N/A           |

| CONTENTS LISTED BELOW FOR INDIVIDUAL ORDERING:                              |                       |               |

| CONNECTIVITY                                                                | 231658                | 1-55512-174-8 |

| EMBEDDED APPLICATIONS (1993/94)                                             | 270648                | 1-55512-179-9 |

| EMBEDDED MICROCONTROLLERS & PROCESSORS<br>(2 volume set)                    | 270645                | 1-55512-176-4 |

| MEMORY PRODUCTS                                                             | 210830                | 1-55512-172-1 |

| MICROCOMPUTER PRODUCTS                                                      | 280407                | 1-55512-173-X |

| MICROPROCESSORS (2 volume set)                                              | 230843                | 1-55512-169-1 |

| MOBILE COMPUTER PRODUCTS                                                    | 241420                | 1-55512-186-1 |

| i750®, i860™, i960® PROCESSORS AND RELATED PRODUCTS                         | 272084                | 1-55512-185-3 |

| PACKAGING                                                                   | 240800                | 1-55512-182-9 |

| PERIPHERAL COMPONENTS                                                       | 296467                | 1-55512-181-0 |

| PRODUCT OVERVIEW<br>(A guide to Intel Architectures and Applications)       | 210846                | N/A           |

| PROGRAMMABLE LOGIC                                                          | 296083                | 1-55512-180-2 |

| ADDITIONAL LITERATURE:<br>(Not included in handbook set)                    |                       |               |

| AUTOMOTIVE                                                                  | 231792                | 1-55512-125-X |

| COMPONENTS QUALITY/RELIABILITY                                              | 210997                | 1-55512-132-2 |

| CUSTOMER LITERATURE GUIDE                                                   | 210620                | N/A           |

| INTERNATIONAL LITERATURE GUIDE<br>(Available in Europe only)                | E00029                | N/A           |

| MILITARY AND SPECIAL PRODUCTS (2 volume set)                                | 210461                | 1-55512-189-6 |

| SYSTEMS QUALITY/RELIABILITY                                                 | 231762                | 1-55512-091-9 |

| HANDBOOK DIRECTORY<br>(Index of all data sheets contained in the handbooks) | 241197                | N/A           |

intel

## Pentium<sup>™</sup> Processor User's Manual Volume 3: Architecture and Programming Manual

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and may only be used to identify Intel products:

| 376™             | i860™                 |

|------------------|-----------------------|

| Above™           | i960®                 |

| ActionMedia®     | Intel287™             |

| BITBUS™          | Intel386™             |

| Code Builder™    | Intel387™             |

| DeskWare™        | Intel486™             |

| Digital Studio™  | Intel487™             |

| DVI®             | Intel®                |

| EtherExpress™    | intel inside®         |

| ETOX™            | Intellec®             |

| ExCA™            | iPSC®                 |

| Exchange and Go™ | iRMX®                 |

| FaxBACK®         | iSBC®                 |

| Grand Challenge™ | iSBX™                 |

| i®               | iWARP™                |

| ICE™             | LANDesk™              |

| iCOMP™           | LANPrint <sup>®</sup> |

| iLBX™            | LANProtect™           |

| Inboard™         | LANSelect®            |

| Indeo™           | LANShell®             |

| i287™            | LANSight™             |

| i386™            | LANSpace®             |

| i387™            | LANSpool®             |

| i486™            | MAPNET™               |

| i487™            | Matched™              |

| i750®            |                       |

Media Mail™ NetPort® NetSentry™ NetSight<sup>™</sup> OpenNET™ ÖverDrive™ Paragon™ Pentium™ ProSolver™ RapidCAD™ READY-LAN™ Reference Point® BMX/80™ RxServer™ SatisFAXtion® SmartWire™ SnapIn 386™ Storage Broker™ StoradeExpress™ SugarCube™ The Computer Inside™ TokenExpress™ Visual Edge™ **WYPIWYF®**

MCS®

MDS is an ordering code only and is not used as a product name or trademark MDS is a registered trademark of Mohawk Data Sciences Corporation.

CHMOS and HMOS are patented processes of Intel Corp.

Intel Corporation and Intel's FASTPATH are not affiliated with Kinetics, a division of Excelan, Inc. or its FASTPATH trademark or products.

OS/2 is a registered trademark of IBM Corp. UNIX is a registered trademark of UNIX System Laboratories, Inc. Windows is a trademark of Microsoft Corp.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Corporation Literature Sales P.O. Box 7641 Mt. Prospect, IL 60056-7641

© INTEL CORPORATION 1993

# int

### **TABLE OF CONTENTS**

#### **CHAPTER 1 GETTING STARTED** Page 1.1. 111 Part I—Application and Numeric Programming ......1-2 Part II-System Programming ......1-2 1.1.2. Part III—Compatibility ......1-4 1.1.3. 1.1.4. 1.1.5. Part V—Instruction Set ......1-4 1.1.6. 1.2. RELATED LITERATURE 1-4 1.3. 1.3.1. Bit and Byte Order ......1-5 1.3.2. 1.3.3. Instruction Operands......1-6 1.3.4. Hexadecimal Numbers......1-7 1.3.5. Segmented Addressing......1-7 1.3.6.

#### **CHAPTER 2** INTRODUCTION TO THE INTEL PENTIUM PROCESSOR FAMILY

#### PART I—APPLICATION AND NUMERIC PROGRAMMING

#### CHAPTER 3

| CHAPTER 3                              |      |

|----------------------------------------|------|

| BASIC PROGRAMMING MODEL                |      |

| 3.1. MEMORY ORGANIZATION               |      |

| 3.1.1. Unsegmented or "Flat" Model     |      |

| 3.1.2. Segmented Model                 |      |

| 3.2. DATA TYPES                        |      |

| 3.3. REGISTERS                         |      |

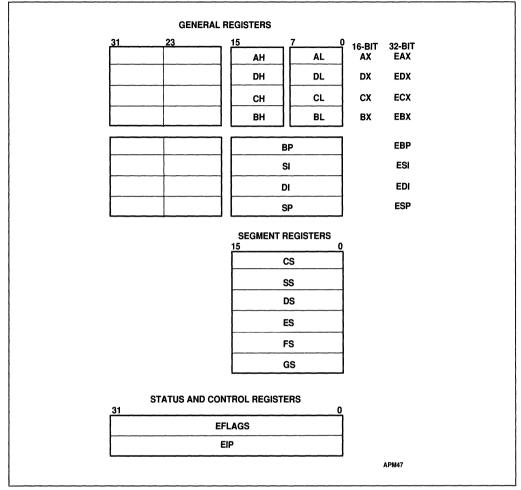

| 3.3.1. General Registers               |      |

| 3.3.2. Segment Registers               |      |

| 3.3.3. Stack Implementation            | 3-12 |

| 3.3.4. Flags Register                  | 3-13 |

| 3.3.4.1. STATUS FLAGS                  |      |

| 3.3.4.2. CONTROL FLAG                  |      |

| 3.3.5. Instruction Pointer             |      |

| 3.4. INSTRUCTION FORMAT                |      |

| 3.5. OPERAND SELECTION                 | 3-17 |

| 3.5.1. Immediate Operands              | 3-18 |

| 3.5.2. Register Operands               | 3-18 |

| 3.5.3. Memory Operands                 |      |

| 3.5.3.1. SEGMENT SELECTION             | 3-19 |

| 3.5.3.2. EFFECTIVE-ADDRESS COMPUTATION |      |

| 3.6. INTERRUPTS AND EXCEPTIONS         |      |

**CHAPTER 4**

# Int

Page

#### APPLICATION PROGRAMMING 4.1. 411 4.1.2. 4.1.3. 4.2. 4.2.1. Comparison and Sign Change Instruction ......4-7 4.2.2. 4.2.3. 4.2.4. 4.3. 4.3.1. 4.3.2. 44 441 442 4.4.3. 444 4441 4442 4.4.4.3. 4444 FAST BIT STRING INSERT AND EXTRACT ......4-18 4.4.4.5. 4.4.5. 4.4.6. 45 4.5.1. 4.5.1.1. 4.5.1.2. 4.5.1.3. 4.5.2. 4.5.2.1. 4.5.2.2. EXECUTING A LOOP OR REPEAT ZERO TIMES ...... 4-25 4.5.2.3. . . .

| 4.5.3.  | Software Interrupts                           |  |

|---------|-----------------------------------------------|--|

| 4.6.    | STRING OPERATIONS                             |  |

| 4.6.1.  | Repeat Prefixes                               |  |

| 4.6.2.  | Indexing and Direction Flag Control           |  |

| 4.6.3.  | String Instructions                           |  |

| 4.7.    | INSTRUCTIONS FOR BLOCK-STRUCTURED LANGUAGES   |  |

| 4.8.    | FLAG CONTROL INSTRUCTIONS                     |  |

| 4.8.1.  | Carry and Direction Flag Control Instructions |  |

| 4.8.2.  | Flag Transfer Instructions                    |  |

| 4.9.    | NUMERIC INSTRUCTIONS                          |  |

| 4.10.   | SEGMENT REGISTER INSTRUCTIONS                 |  |

| 4.10.1. | Segment-Register Transfer Instructions        |  |

| 4.10.2. |                                               |  |

| 4.10.3. | Data Pointer Instructions                     |  |

| 4.11.   | MISCELLANEOUS INSTRUCTIONS                    |  |

| 4.11.1. |                                               |  |

| 4.11.2. | No-Operation Instruction                      |  |

| 4.11.3. | Translate Instruction                         |  |

| 4.11.4. |                                               |  |

| 4.11.5. |                                               |  |

|         | -                                             |  |

|                     |                                                        | Page |

|---------------------|--------------------------------------------------------|------|

| 4.11.6.             | . Compare-and-Exchange Instructions                    |      |

| 4.11.7.             |                                                        |      |

|                     |                                                        |      |

| CHAP                | PTER 5                                                 |      |

| FEATL               | URE DETERMINATION                                      |      |

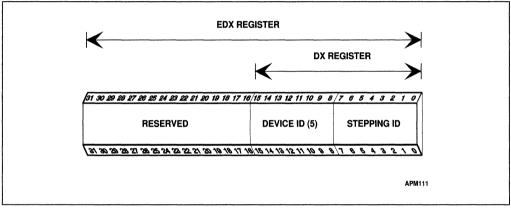

| 5.1.                | CPU IDENTIFICATION                                     |      |

|                     | FPU DETECTION                                          |      |

| 5.3.                | SAMPLE CPUID IDENTIFICATION/FPU DETECTION CODE         | 5-2  |

|                     |                                                        |      |

| CHAP                | PTER 6                                                 |      |

|                     | ERIC APPLICATIONS                                      |      |

|                     | INTRODUCTION TO NUMERIC APPLICATIONS                   | 6-1  |

| 6.1.1.              | History                                                |      |

| 6.1.2.              | Performance                                            |      |

| 6.1.3.              | Ease of Use                                            |      |

| 6.1.4.              | Applications                                           | 6-4  |

| 6.1.5.              | Programming Interface                                  | 6-5  |

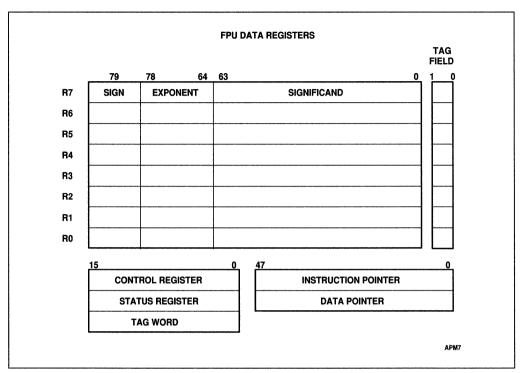

| 6.2.                | ARCHITECTURE OF THE FLOATING-POINT UNIT                |      |

| 6.2.1.              | Numerical Registers                                    | 6-7  |

| 6.2.1.1.            |                                                        |      |

| 6.2.1.2.            |                                                        |      |

| 6.2.1.3             |                                                        |      |

| 6.2.1.4             |                                                        | 6-12 |

| 6.2.1.5             |                                                        | 6-14 |

| 6.2.1.6             |                                                        | 6-15 |

| 6.2.2.              | Computation Fundamentals                               |      |

| 6.2.2.1.            |                                                        |      |

| 6.2.2.2             |                                                        |      |

| 6.2.2.2             |                                                        |      |

| 6.2.2.2             |                                                        |      |

| 6.2.2.2             |                                                        |      |

| 6.2.2.3.<br>6.2.2.4 |                                                        |      |

|                     | I. PRECISION CONTROL<br>FLOATING-POINT INSTRUCTION SET | 0-24 |

| 6.3.1.              | Source and Destination Operands                        |      |

| 6.3.2.              | Data Transfer Instructions                             | 6-25 |

| 6.3.3.              | Nontranscendental Instructions                         |      |

| 6.3.4.              | Comparison Instructions                                |      |

| 6.3.5.              | Transcendental Instructions                            |      |

| 6.3.6.              | Constant Instructions                                  |      |

| 6.3.7.              | Control Instructions                                   |      |

|                     | NUMERIC APPLICATIONS                                   |      |

| 6.4.1.              | High-Level Languages                                   |      |

| 6.4.1.1.            |                                                        |      |

| 6.4.1.2             |                                                        |      |

| 6.4.1.3             | B. ASM386/486                                          | 6-35 |

| 6.4.1.3             | B.1. Defining Data                                     | 6-35 |

| 6.4.1.3             | 3.2. Records and Structures                            | 6-37 |

| 6.4.1.3             | 3.3. Addressing Methods                                | 6-38 |

| 6.4.1.4             |                                                        |      |

| 6.4.1.5             |                                                        |      |

| 6.4.1.6.            | 6. MANAGING CONCURRENCY                                | 6-43 |

| 6.4.1.7.          | EXCEPTION SYNCHRONIZATION                                                | Page        |

|-------------------|--------------------------------------------------------------------------|-------------|

| 6.4.1.8.          | PROPER EXCEPTION SYNCHRONIZATION                                         |             |

| 0.4.1.0.          |                                                                          |             |

| СНАРТІ            | B 7                                                                      |             |

|                   | L COMPUTATIONAL SITUATIONS                                               |             |

| 7.1. S            | PECIAL NUMERIC VALUES                                                    |             |

| 7.1.1.            | Denormal Real Numbers                                                    |             |

| 7.1.2.            | Zeros                                                                    |             |

| 7.1.3.            | Infinity                                                                 |             |

| 7.1.4.            | NAN (Not-A-Number)                                                       | 7-15        |

| 7.1.4.1.          | SIGNALING NANŚ                                                           |             |

| 7.1.4.2.          | QUIET NANS                                                               | 7-16        |

| 7.1.5.            | Indefinite                                                               | 7-17        |

| 7.1.6.            | Encoding of Data Types                                                   | 7-18        |

| 7.1.6.1.          | UNSUPPORTED FORMATS                                                      | 7-18        |

| 7.1.7.            | Numeric Exceptions                                                       | 7-18        |

| 7.1.8.            | Handling Numeric Exceptions                                              | 7-19        |

| 7.1.8.1.          | AUTOMATIC EXCEPTION HANDLING                                             | 7-19        |

| 7.1.8.2.          | SOFTWARE EXCEPTION HANDLING                                              | 7-20        |

| 7.1.9.            | Invalid Operation                                                        | 7-21        |

| 7.1.9.1.          | STACK EXCEPTION                                                          | 7-21        |

| 7.1.9.2.          | INVALID ARITHMETIC OPERATION                                             |             |

| 7.1.10.           | Division by Zero                                                         | 7-22        |

| 7.1.11.           | Denormal Operand                                                         |             |

| 7.1.12.           | Numeric Overflow and Underflow                                           |             |

| 7.1.12.1.         | OVERFLOW                                                                 |             |

| 7.1.12.2.         | UNDERFLOW                                                                |             |

| 7.1.13.           | Inexact (Precision)                                                      |             |

| 7.1.14.           | Exception Priority                                                       |             |

| 7.1.15.           | Standard Underflow/Overflow Exception Handler                            |             |

|                   |                                                                          |             |

| CHAPTI            | ER 8<br>IC PROGRAMMING EXAMPLES                                          |             |

|                   | ONDITIONAL BRANCHING EXAMPLES                                            | 0.4         |

|                   |                                                                          |             |

| 8.2. E<br>8.3. Fl | XCEPTION HANDLING EXAMPLES<br>LOATING-POINT TO ASCII CONVERSION EXAMPLES | 8-4         |

| 8.3. FI<br>8.3.1. |                                                                          |             |

|                   | Function Partitioning                                                    | 8-20        |

| 8.3.2.<br>8.3.3.  | Exception Considerations                                                 |             |

| 8.3.3.            | Special Instructions<br>Description of Operation                         | 8-20        |

| 8.3.4.<br>8.3.5.  | Scaling the Value                                                        | 8-21        |

| 8.3.5.            | INACCURACY IN SCALING                                                    | ۵۰۵۵ مر م   |

| 8.3.5.1.          | AVOIDING UNDERFLOW AND OVERFLOW                                          | 22-8<br>م م |

| 8.3.5.3.          | FINAL ADJUSTMENTS                                                        | 0-22 0      |

| 8.3.6.            | Output Format                                                            |             |

| 0.0.0.            | Output i onnat                                                           | 0-22        |

#### PART II—SYSTEM PROGRAMMING

#### **CHAPTER 9**

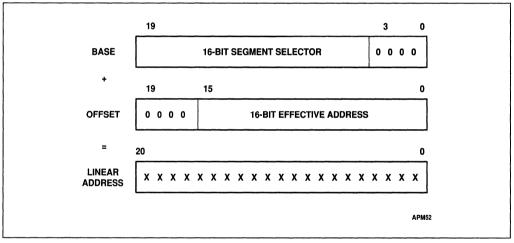

#### **REAL-ADDRESS MODE SYSTEM ARCHITECTURE**

| Page |

|------|

|------|

| 9.1. | ADDRESS TRANSLATION              | 9-  | 1 |

|------|----------------------------------|-----|---|

| 9.2. | REGISTERS AND INSTRUCTIONS       | 9-2 | 2 |

| 9.3. | INTERRUPT AND EXCEPTION HANDLING | 9-; | 2 |

| 9.4. | REAL-ADDRESS MODE EXCEPTIONS     | 9-: | 3 |

#### **CHAPTER 10**

#### PROTECTED MODE SYSTEM ARCHITECTURE OVERVIEW

| 10.1. S | YSTEM REGISTERS             |  |

|---------|-----------------------------|--|

|         | System Flags                |  |

| 10.1.2. | Memory-Management Registers |  |

| 10.1.3. | Control Registers           |  |

|         | Debug Registers             |  |

| 10.2. S | YSTEM INSTRUCTIONS          |  |

#### **CHAPTER 11**

#### PROTECTED MODE MEMORY MANAGEMENT

| 11.1. S   | ELECTING A SEGMENTATION MODEL           |       |

|-----------|-----------------------------------------|-------|

| 11.1.1.   | Flat Model                              |       |

| 11.1.2.   | Protected Flat Model                    |       |

| 11.1.3.   | Multisegment Model                      |       |

| 11.2. S   | EGMENT TRANSLATION                      |       |

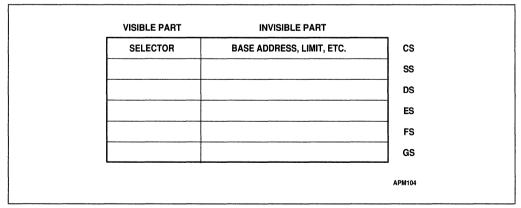

| 11.2.1.   | Segment Registers                       | 11-9  |

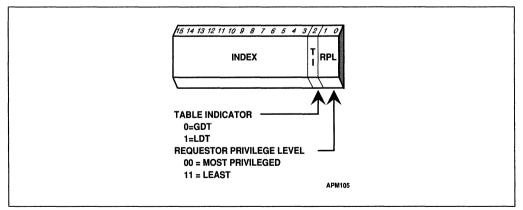

| 11.2.2.   | Segment Selectors                       |       |

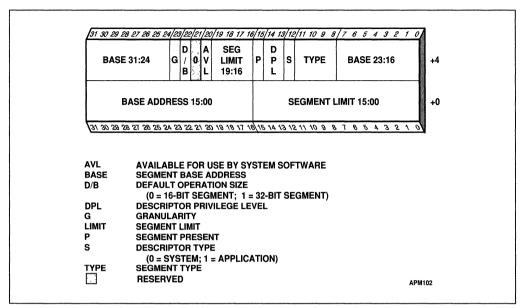

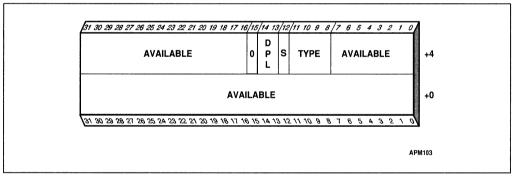

| 11.2.3.   | Segment Descriptors                     |       |

| 11.2.4.   | Segment Descriptor Tables               | 11-15 |

| 11.2.5.   | Descriptor Table Base Registers         |       |

| 11.3. P   | AGE TRANSLATION                         |       |

| 11.3.1.   | Paging Options                          | 11-18 |

| 11.3.2.   | Linear Address                          | 11-18 |

| 11.3.3.   | Page Tables                             | 11-18 |

| 11.3.4.   | Page-Table Entries                      | 11-19 |

| 11.3.4.1. | PAGE FRAME ADDRESS                      | 11-20 |

| 11.3.4.2. | PRESENT BIT                             |       |

| 11.3.4.3. | ACCESSED AND DIRTY BITS                 | 11-21 |

| 11.3.4.4. | READ/WRITE AND USER/SUPERVISOR BITS     |       |

| 11.3.4.5. | PAGE-LEVEL CACHE CONTROL BITS           | 11-22 |

| 11.3.5.   | Translation Lookaside Buffers           |       |

| 11.4. C   | OMBINING SEGMENT AND PAGE TRANSLATION   |       |

| 11.4.1.   | Flat Model                              | 11-23 |

| 11.4.2.   | Segments Spanning Several Pages         | 11-23 |

| 11.4.3.   | Pages Spanning Several Segments         |       |

| 11.4.4.   | Non-Aligned Page and Segment Boundaries |       |

| 11.4.5.   | Aligned Page and Segment Boundaries     |       |

| 11.4.6.   | Page-Table Per Segment                  | 11-25 |

#### CHAPTER 12 PROTECTION

I

| 12.1. | SEGMENT-LEVEL PROTECTION           | 12-1 |

|-------|------------------------------------|------|

| 12.2. | SEGMENT DESCRIPTORS AND PROTECTION | 12-2 |

# intel

|                                                            | Page |

|------------------------------------------------------------|------|

| 12.2.1. Type Checking                                      |      |

| 12.2.2. Limit Checking                                     |      |

| 12.2.3. Privilege Levels                                   |      |

| 12.3. RESTRICTING ACCESS TO DATA                           |      |

| 12.3.1. Accessing Data in Code Segments                    |      |

| 12.4. RESTRICTING CONTROL TRANSFERS                        |      |

| 12.5. GATE DESCRIPTORS                                     |      |

| 12.5.1. Stack Switching                                    |      |

| 12.5.2. Returning from a Procedure                         |      |

| 12.6. INSTRUCTIONS RESERVED FOR THE OPERATING SYSTEM       |      |

| 12.6.1. Privileged Instructions                            |      |

| 12.6.2. Sensitive Instructions                             |      |

| 12.7. INSTRUCTIONS FOR POINTER VALIDATION                  |      |

| 12.7.1. Descriptor Validation                              |      |

| 12.7.2. Pointer Integrity and RPL                          |      |

| 12.8. PAGE-LEVEL PROTECTION                                |      |

| 12.8.1. Page-Table Entries Hold Protection Parameters      |      |

| 12.8.1.1. RESTRICTING ADDRESSABLE DOMAIN                   |      |

| 12.8.1.2. TYPE CHECKING                                    |      |

| 12.8.2. Combining Protection of Both Levels of Page Tables |      |

| 12.8.3. Overrides to Page Protection                       |      |

| 12.9. COMBINING PAGE AND SEGMENT PROTECTION                |      |

|                                                            |      |

### **CHAPTER 13**

#### PROTECTED-MODE MULTITASKING

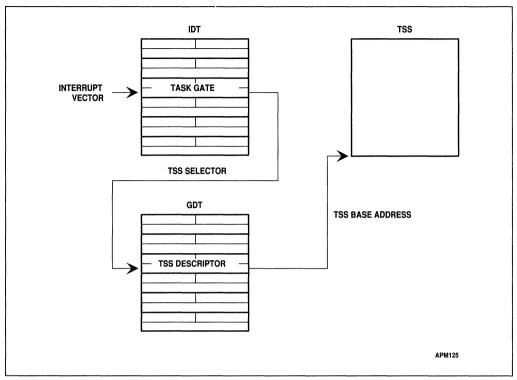

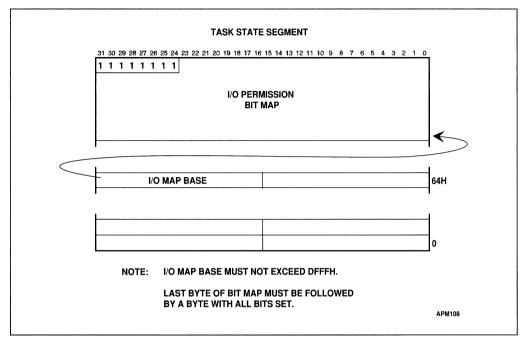

| 13.1.   | TASK STATE SEGMENT                    |  |

|---------|---------------------------------------|--|

| 13.2.   | TSS DESCRIPTOR                        |  |

|         | TASK REGISTER                         |  |

|         | TASK GATE DESCRIPTOR                  |  |

| 13.5.   | TASK SWITCHING                        |  |

|         | TASK LINKING                          |  |

| 13.6.1. | Busy Bit Prevents Loops               |  |

| 13.6.2. | Modifying Task Linkages               |  |

| 13.7.   | TASK ADDRESS SPACE                    |  |

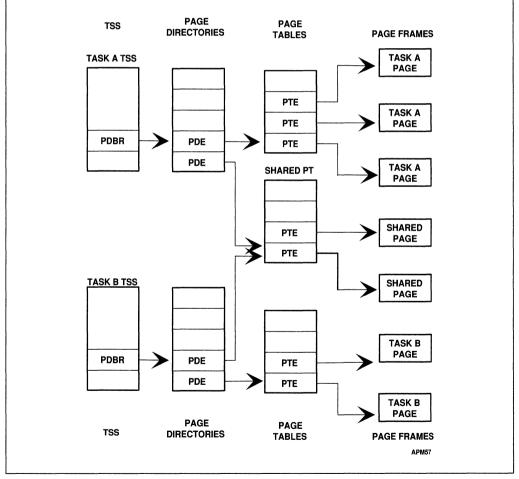

| 13.7.1. | Task Linear-to-Physical Space Mapping |  |

| 13.7.2. | Task Logical Address Space            |  |

#### **CHAPTER 14**

#### PROTECTED-MODE EXCEPTIONS AND INTERRUPTS

| 14.1. EXCEPTION AND INTERRUPT VECTORS                         | 14-1 |

|---------------------------------------------------------------|------|

| 14.2. INSTRUCTION RESTART                                     | 14-3 |

| 14.3. ENABLING AND DISABLING INTERRUPTS                       | 14-3 |

| 14.3.1. NMI Masks Further NMIs                                | 14-3 |

| 14.3.2. IF Masks INTR                                         | 14-3 |

| 14.3.3. RF Masks Debug Faults                                 | 14-4 |

| 14.3.4. MOV or POP to SS Masks Some Exceptions and Interrupts | 14-4 |

| 14.4. PRIORITY AMONG SIMULTANEOUS EXCEPTIONS AND INTERRUPTS   |      |

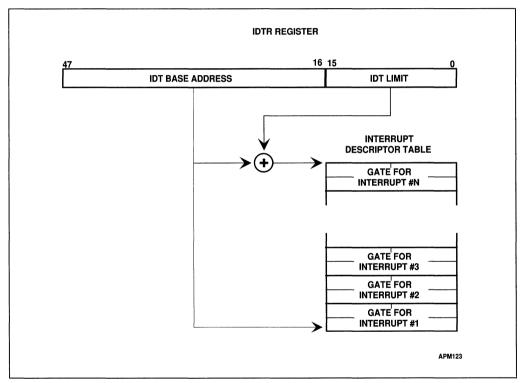

| 14.5. INTERRUPT DESCRIPTOR TABLE                              | 14-5 |

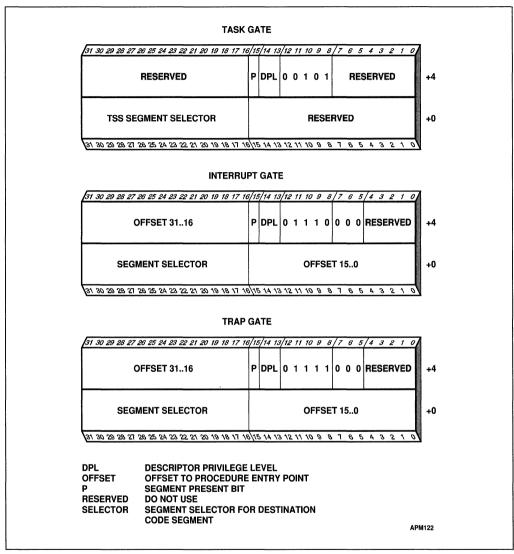

| 14.6. IDT DESCRIPTORS                                         | 14-7 |

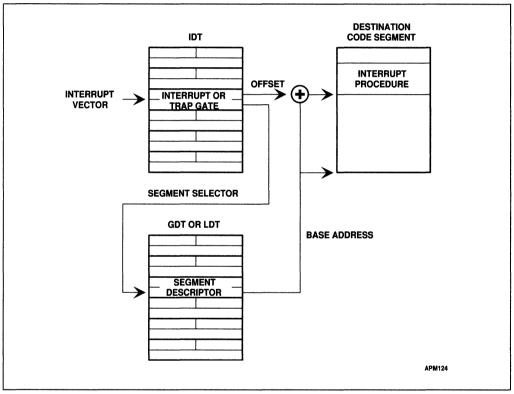

| 14.7. INTERRUPT TASKS AND INTERRUPT PROCEDURES                |      |

| 14.7.1. Interrupt Procedures                                  | 14-9 |

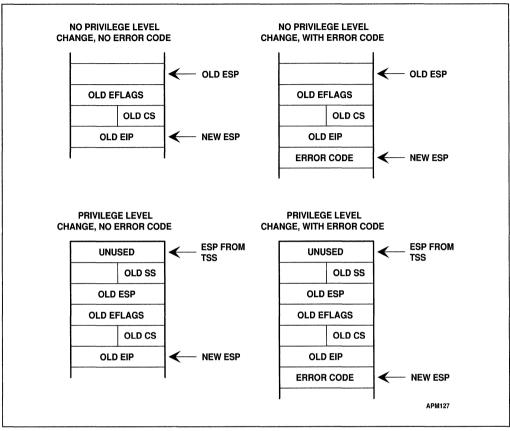

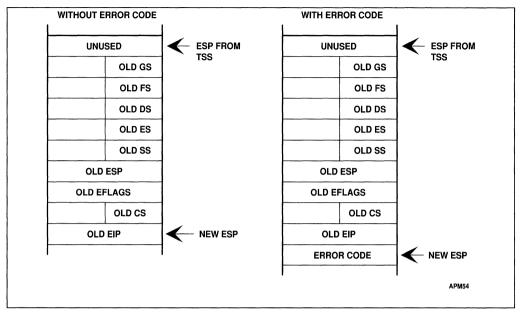

| 14.7.1.1. STACK OF INTERRUPT PROCEDURE                        | 14-9 |

|                                                       | Page  |

|-------------------------------------------------------|-------|

| 14.7.1.2. RETURNING FROM AN INTERRUPT PROCEDURE       | 14-10 |

| 14.7.1.3. FLAG USAGE BY INTERRUPT PROCEDURE           | 14-10 |

| 14.7.1.4. PROTECTION IN INTERRUPT PROCEDURES          | 14-11 |

| 14.7.2. Interrupt Tasks                               |       |

| 14.8. ERROR CODE                                      | 14-13 |

| 14.9. EXCEPTION CONDITIONS                            |       |

| 14.9.1. Interrupt 0-Divide Error                      |       |

| 14.9.2. Interrupt 1—Debug Exceptions                  |       |

| 14.9.3. Interrupt 3—Breakpoint                        |       |

| 14.9.4. Interrupt 4-Overflow                          | 14-14 |

| 14.9.5. Interrupt 5—Bounds Check                      |       |

| 14.9.6. Interrupt 6—Invalid Opcode                    |       |

| 14.9.7. Interrupt 7—Device Not Available              |       |

| 14.9.8. Interrupt 8—Double Fault                      |       |

| 14.9.9. Interrupt 9(Intel reserved Do not use.)       |       |

| 14.9.10. Interrupt 10Invalid TSS                      |       |

| 14.9.11. Interrupt 11-Segment Not Present             |       |

| 14.9.12. Interrupt 12-Stack Exception                 |       |

| 14.9.13. Interrupt 13—General Protection              | 14-19 |

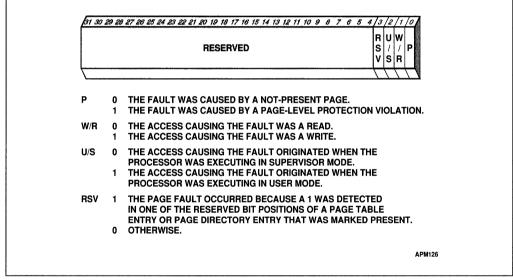

| 14.9.14. Interrupt 14—Page Fault                      | 14-20 |

| 14.9.14.1. PAGE FAULT DURING TASK SWITCH              | 14-21 |

| 14.9.14.2. PAGE FAULT WITH INCONSISTENT STACK POINTER |       |

| 14.9.15. Interrupt 16—Floating-Point Error            | 14-22 |

| 14.9.15.1. NUMERICS EXCEPTION HANDLING                | 14-23 |

| 14.9.15.2. SIMULTANEOUS EXCEPTION RESPONSE            |       |

| 14.9.16. Interrupt 17—Alignment Check                 | 14-24 |

| 14.9.17. Interrupt 18—Machine Check                   | 14-25 |

| 14.10. EXCEPTION SUMMARY                              |       |

| 14.11. ERROR CODE SUMMARY                             | 14-28 |

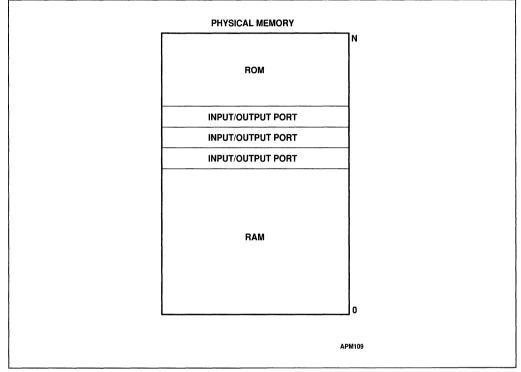

#### CHAPTER 15 INPUT/OUTPUT

| 15.1. I/O ADDRESSING              |  |

|-----------------------------------|--|

| 15.1.1. I/O Address Space         |  |

| 15.1.2. Memory-Mapped I/O         |  |

| 15.2. I/O INSTRUCTIONS            |  |

| 15.2.1. Register I/O Instructions |  |

| 15.2.2. Block I/O Instructions    |  |

| 15.3. PROTECTED-MODE I/O          |  |

| 15.3.1. I/O Privilege Level       |  |

| 15.3.2. I/O Permission Bit Map    |  |

| 15.3.3. Paging and Caching        |  |

| 15.4. ORDĚRING OF I/O             |  |

|                                   |  |

#### **CHAPTER 16**

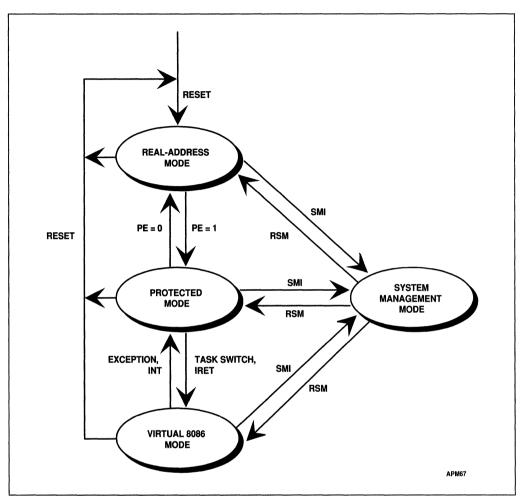

### INITIALIZATION AND MODE SWITCHING

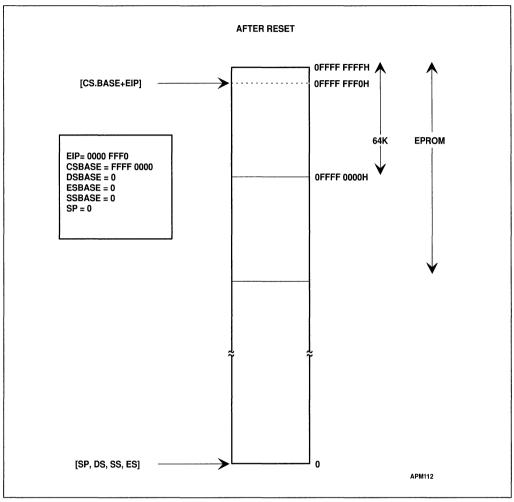

| 16.1.1.       Processor State After Reset       16-1         16.1.2.       First Instruction Executed       16-5         16.2.       FPU INITIALIZATION       16-5         16.2.1.       Configuring the Numerics Environment       16-6         16.2.2.       FDU INITIALIZATION       16-6 | 16.1. P | PROCESSOR INITIALIZATION    |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------|--|

| 16.2. FPU INITIALIZATION                                                                                                                                                                                                                                                                     | 16.1.1. | Processor State After Reset |  |

| 16.2.1. Configuring the Numerics Environment                                                                                                                                                                                                                                                 |         |                             |  |

|                                                                                                                                                                                                                                                                                              | 16.2. F | PU INITIALIZATION           |  |

| 10.0 C EDIL Östhusus Emulation 10.0                                                                                                                                                                                                                                                          |         |                             |  |

| 16.2.2. FPU Software Emulation                                                                                                                                                                                                                                                               | 16.2.2. | FPU Software Emulation      |  |

# int<sub>el</sub>.

|         |                                              | Page |

|---------|----------------------------------------------|------|

| 16.3.   | CACHE ENABLING                               |      |

| 16.4.   | SOFTWARE INITIALIZATION IN REAL-ADDRESS MODE |      |

| 16.4.1. | System Tables                                |      |

| 16.4.2  |                                              |      |

| 16.5.   | SOFTWARE INITIALIZATION IN PROTECTED MODE    |      |

| 16.5.1. | System Tables                                |      |

| 16.5.2  | Interrupts                                   |      |

| 16.5.3  |                                              |      |

| 16.5.4  | Tasks                                        |      |

| 16.5.5  | TLB, BTB and Cache Testing                   |      |

| 16.6.   | MODE SWITCHING                               |      |

| 16.6.1  |                                              |      |

| 16.6.2  |                                              |      |

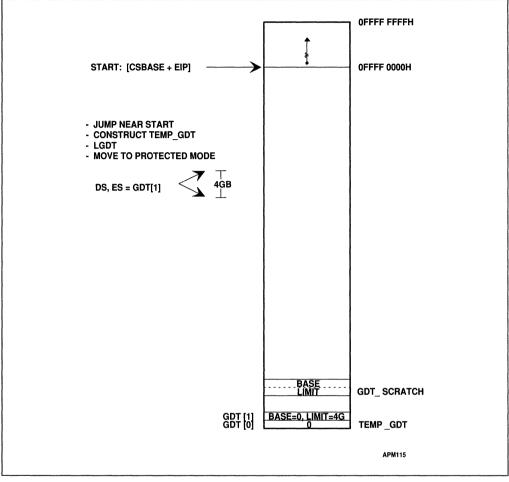

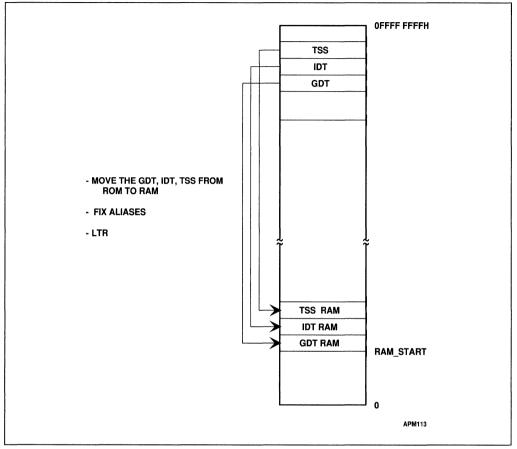

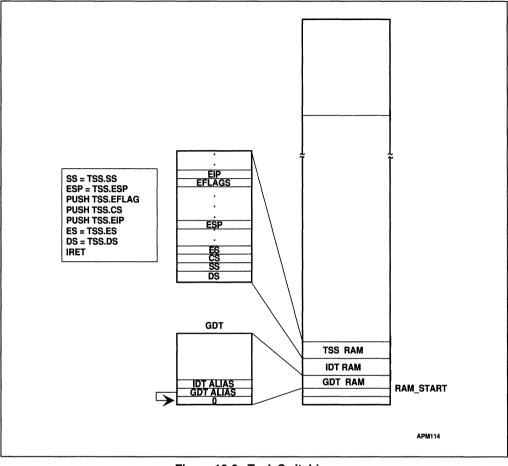

| 16.7.   | INITIALIZATION AND MODE SWITCHING EXAMPLE    |      |

| 16.7.1. | Goal of this Example                         |      |

| 16.7.2  | Memory Layout Following Reset                |      |

| 16.7.3  |                                              |      |

| 16.7.4  | Tool Usage                                   |      |

| 16.7.5  | STARTUP.ASM Listing                          |      |

| 16.7.6  |                                              |      |

| 16.7.7  | Supporting Files                             |      |

### **CHAPTER 17**

#### DEBUGGING

| 17.1. DEBUGGING SUPPORT                    |      |

|--------------------------------------------|------|

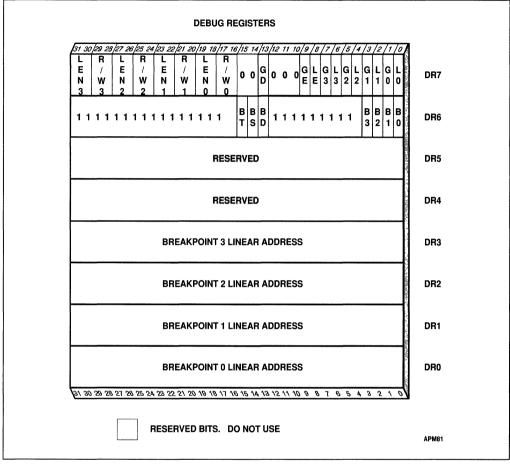

| 17.2. DEBUG REGISTERS                      |      |

| 17.2.1. Debug Address Registers (DR0-DR3)  |      |

| 17.2.2. Debug Control Register (DR7)       |      |

| 17.2.3. Debug Status Register (DR6)        |      |

| 17.2.4. Debug Registers DR4 and DR5        |      |

| 17.2.5. Breakpoint Field Recognition       | 17-5 |

| 17.3. DEBUG EXCEPTIONS                     |      |

| 17.3.1. Interrupt 1—Debug Exceptions       |      |

| 17.3.1.1. INSTRUCTION-BREAKPOINT FAULT     |      |

| 17.3.1.2. DATA MEMORY AND I/O BREAKPOINTS  |      |

| 17.3.1.3. GENERAL-DETECT FAULT             |      |

| 17.3.1.4. SINGLE-STEP TRAP                 |      |

| 17.3.1.5. TASK-SWITCH TRAP                 |      |

| 17.3.2. Interrupt 3—Breakpoint Instruction |      |

|                                            |      |

#### **CHAPTER 18**

### CACHING, PIPELINING AND BUFFERING

| 18.1. INTERNAL INSTRUCTION AND DATA CACHES |  |

|--------------------------------------------|--|

| 18.1.1. Data Cache                         |  |

| 18.1.2. Data Cache Update Policies         |  |

| 18.1.3. Instruction Cache                  |  |

| 18.2. OPERATION OF THE INTERNAL CACHES     |  |

| 18.2.1. Cache Control Bits                 |  |

| 18.2.2. Cache Management Instructions      |  |

| 18.2.3. Self-Modifying Code                |  |

| 18.3. PAGE-LEVEL CACHE MANAGEMENT          |  |

| 18.3.1. PCD Bit                            |  |

#### Page

| 18.3.2. | . PWT Bit                        | 18-6 |

|---------|----------------------------------|------|

| 18.4.   | ADDRESS TRANSLATION CACHES       | 18-6 |

| 18.5.   | CACHE REPLACEMENT ALGORITHM      | 18-6 |

| 18.6.   | EXECUTION PIPELINING AND PAIRING | 18-6 |

| 18.7.   | WRITE BUFFERS                    | 18-7 |

| 18.8.   | SERIALIZING INSTRUCTIONS         | 18-7 |

#### CHAPTER 19 MULTIPROCESSING

| MOLI    |                                  |      |

|---------|----------------------------------|------|

| 19.1.   | LOCKED BUS CYCLES                | 19-1 |

| 19.1.1. | LOCK Prefix and the LOCK# Signal | 19-2 |

|         | Automatic Locking                |      |

|         | MEMORY ACCESS ORDERING           |      |

### **CHAPTER 20**

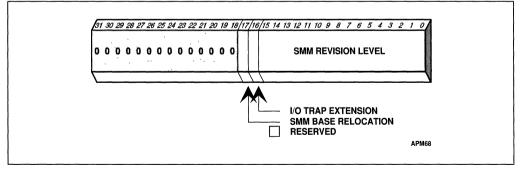

### SYSTEM MANAGEMENT MODE

| 20.1. THE SMI INTERRUPT                                           |  |

|-------------------------------------------------------------------|--|

| 20.2. SMM INITIAL STATE                                           |  |

| 20.2.1. System Management Mode Execution                          |  |

| 20.3. SMRAM PROCESSOR STATE DUMP FORMAT                           |  |

| 20.3.1. System Management Mode Revision Identifier (Offset FEFCH) |  |

| 20.3.2. I/O Trap Restart (Offset FF00H)                           |  |

| 20.3.3. Halt Auto Restart (Offset FF02H)                          |  |

| 20.3.4. State Dump Base (Offset FEF8H)                            |  |

| 20.4. RELOCATING SMRAM                                            |  |

| 20.5. RETURNING FROM SMM                                          |  |

|                                                                   |  |

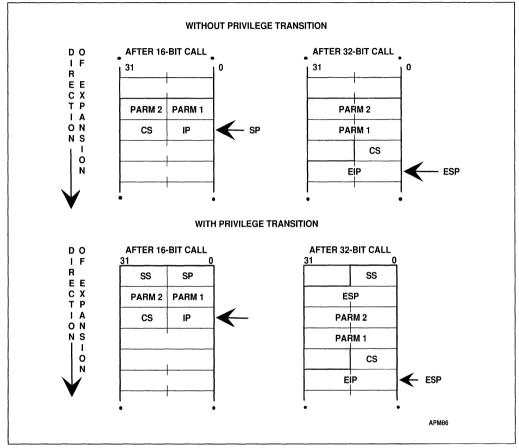

#### PART III—COMPATIBILITY

#### CHAPTER 21

#### **MIXING 16-BIT AND 32-BIT CODE**

| 21.1.    | USING 16-BIT AND 32-BIT ENVIRONMENTS                | 21-1 |

|----------|-----------------------------------------------------|------|

| 21.2.    | MIXING 16-BIT AND 32-BIT OPERATIONS                 | 21-2 |

| 21.3.    | SHARING DATA AMONG MIXED-SIZE CODE SEGMENTS         | 21-3 |

| 21.4.    | TRANSFERRING CONTROL AMONG MIXED-SIZE CODE SEGMENTS | 21-3 |

| 21.4.1.  | Size of Code-Segment Pointer                        | 21-4 |

|          | Stack Management for Control Transfer               |      |

| 21.4.2.1 | . CONTROLLING THE OPERAND SIZE FOR A CALL           | 21-6 |

| 21.4.2.2 | 2. CHANGING SIZE OF A CALL                          | 21-6 |

| 21.4.3.  | Interrupt Control Transfers                         | 21-6 |

| 21.4.4.  | Parameter Translation                               | 21-7 |

| 21.4.5.  | The Interface Procedure                             | 21-7 |

|          |                                                     |      |

#### CHAPTER 22

#### VIRTUAL-8086 MODE

| 22.1.   | EXECUTING 8086 CPU CODE               |  |

|---------|---------------------------------------|--|

| 22.1.1. | Registers and Instructions            |  |

|         | Address Translation                   |  |

|         | STRUCTURE OF A VIRTUAL-8086 TASK      |  |

| 22.2.1. | Paging for Virtual-8086 Tasks         |  |

|         | Protection within a Virtual-8086 Task |  |

|         |                                       |  |

•

# intel®

|                                                            | Page |

|------------------------------------------------------------|------|

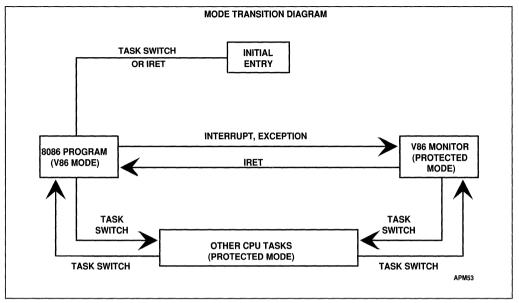

| 22.3. ENTERING AND LEAVING VIRTUAL-8086 MODE               |      |

| 22.3.1. Transitions Through Task Switches                  |      |

| 22.3.2. Transitions Through Trap Gates and Interrupt Gates |      |

| 22.4. SENSITIVE INSTRUCTIONS                               |      |

| 22.5. VIRTUAL INTERRUPT SUPPORT                            |      |

| 22.6. EMULATING 8086 OPERATING SYSTEM CALLS                |      |

| 22.7. VIRTUAL I/O                                          |      |

| 22.7.1. I/O-Mapped I/O                                     |      |

| 22.7.2. Memory-Mapped I/O                                  |      |

| 22.7.3. Special I/O Buffers                                |      |

| 22.8. DIFFERENCES FROM 8086 CPU                            |      |

| 22.9. DIFFERENCES FROM Intel 286 CPU                       |      |

| 22.9.1. Privilege Level                                    |      |

| 22.9.2. Bus Lock                                           |      |

| 22.10. DIFFERENCES FROM Intel386 AND Intel486 CPU'S        |      |

#### CHAPTER 23 COMPATIBILITY

| 23.1. R            | ESERVED BITS                                                | .23-1  |

|--------------------|-------------------------------------------------------------|--------|

| 23.2. IN           | ITEGER UNIT                                                 | .23-1  |

| 23.2.1.            | New Functions and Modes                                     | .23-2  |

| 23.2.2.            | Serializing Instructions                                    | .23-2  |

| 23.2.3.            | Detecting the Presence of New Features                      | .23-2  |

| 23.2.4.            | Undefined Opcodes                                           | . 23-3 |

| 23.2.5.            | Clock Counts                                                |        |

| 23.2.6.            | Initialization and Reset                                    |        |

| 23.2.6.1.          | INTEGER UNIT INITIALIZATION AND RESET                       |        |

| 23.2.6.2.          | FPU/NPX INITIALIZATION AND RESET                            | .23-3  |

| 23.2.6.3.          | Intel486 SX MICROPROCESSOR AND Intel487 SX MATH COPROCESSOR |        |

|                    | INITIALIZATION                                              |        |

| 23.2.7.            |                                                             |        |

| 23.2.7.1.          | NEW PENTIUM PROCESSOR INSTRUCTIONS                          |        |

| 23.2.7.2.          | NEW Intel486 PROCESSOR INSTRUCTIONS                         |        |

| 23.2.7.3.          | NEW Intel386 PROCESSOR INSTRUCTIONS                         |        |

| 23.2.8.<br>23.2.9. | Obsolete Instructions                                       |        |

| 23.2.9.            | Flags<br>NEW PENTIUM PROCESSOR FLAGS                        | .23-8  |

| 23.2.9.1.          | NEW FERTION FROCESSOR FLAGS                                 |        |

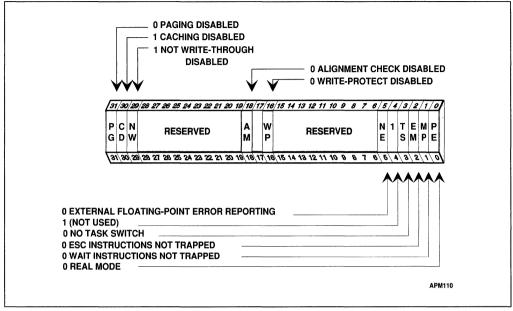

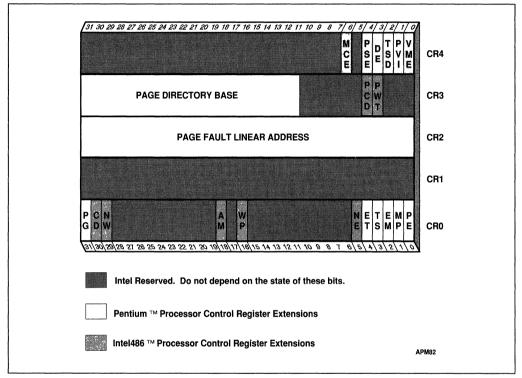

|                    | Control Registers                                           |        |

| 23.2.10.1          |                                                             | 23-10  |

| 23.2.10.1          |                                                             |        |

|                    | Debug Registers                                             |        |

| 23.2.11.1          |                                                             | 23-13  |

| 23.2.11.2          |                                                             |        |

| 23.2.11.3          |                                                             |        |

| 23.2.12.           | Test Registers                                              |        |

| 23.2.13.           | Model Specific Registers                                    |        |

| 23.2.14.           | Exceptions                                                  | 23-14  |

| 23.2.14.1          |                                                             | 23-14  |

| 23.2.14.2          |                                                             |        |

| 23.2.14.3          | 3. NEW Intel386 PROCESSOR EXCEPTIONS                        | 23-15  |

| 23.2.14.4          | I. INTERRUPT PROPAGATION DELAY                              | 23-15  |

|                                                                     | Page  |

|---------------------------------------------------------------------|-------|

| 23.2.14.5. PRIORITY OF EXCEPTIONS                                   | 23-15 |

| 23.2.14.6. DIVIDE-ERROR EXCEPTIONS                                  |       |

| 23.2.14.7. WRITES USING THE CS REGISTER PREFIX                      | 23-16 |

| 23.2.14.8. NMI INTERRUPTS                                           |       |

| 23.2.14.9. INTERRUPT VECTOR TABLE LIMIT                             | 23-16 |

| 23.2.15. Descriptor Types and Contents                              | 23-16 |

| 23.2.16. Changes in Segment Descriptor Loads                        |       |

| 23.2.17. Task Switching and Task State Segments                     | 23-17 |

| 23.2.17.1. PENTIUM PROCESSOR TASK STATE SEGMENTS                    | 23-17 |

| 23.2.17.2. TSS SELECTOR WRITES                                      |       |

| 23.2.17.3. ORDER OF READS/WRITES TO THE TSS                         | 23-17 |

| 23.2.17.4. USING A 16-BIT TSS WITH 32-BIT CONSTRUCTS                | 23-17 |

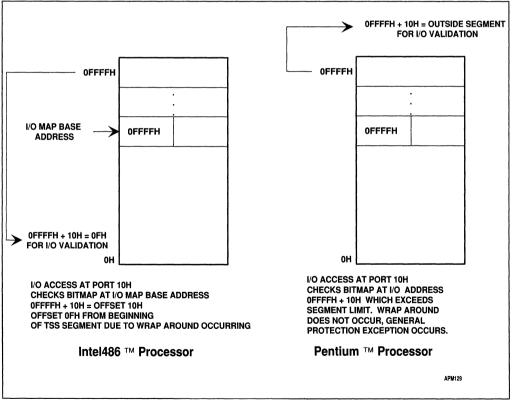

| 23.2.17.4.1. Differences In I/O Map Base Addresses                  |       |

| 23.2.17.4.2. Caching, Pipelining, Prefetching                       | 23-18 |

| 23.2.17.5. SELF MODIFYING CODE WITH CACHE ENABLED                   | 23-19 |

| 23.2.18. Paging                                                     |       |

| 23.2.18.1. PENTIUM PROCESSOR PAGING                                 | 23-20 |

| 23.2.18.2. Intel486 PROCESSOR PAGING.                               |       |

| 23.2.18.3. ENABLING AND DISABLING PAGING                            | 23-20 |

| 23.2.19. Stack Operations                                           | 23-20 |

| 23.2.19.1. PUSH SP                                                  | 23-20 |

| 23.2.19.2. FLAGS PUSHED ON THE STACK                                |       |

| 23.2.19.3. SELECTOR PUSHES/POPS                                     | 23-21 |

| 23.2.19.4. ERROR CODE PUSHES                                        |       |

| 23.2.19.5. FAULT HANDLING EFFECTS ON THE STACK                      | 23-22 |

| 23.2.19.6. INTERLEVEL RET/IRET FROM A 16-BIT INTERRUPT OR CALL GATE | 23-22 |

| 23.2.20. Mixing 16- and 32-Bit Segments                             |       |

| 23.2.21. Segment and Address Wraparound                             | 23-23 |

| 23.2.21.1. ŠEGMENT WRAPAROUND                                       |       |

| 23.2.22. Write Buffers and Memory Ordering                          | 23-23 |

| 23.2.23. Bus Locking                                                | 23-24 |

| 23.2.24. Bus Hold                                                   |       |

| 23.2.25. Two Ways to Run Intel 286 CPU Tasks                        |       |

| 23.3. FLOATING-POINT UNIT                                           |       |

| 23.3.1. Control Register Bits                                       | 23-26 |

| 23.3.1.1. EXTENSION TYPE (ET) BIT                                   | 23-26 |

| 23.3.1.2. NUMERIC EXCEPTION (NE) BIT                                | 23-26 |

| 23.3.1.3. MONITOR COPROCESSOR (MP) BIT<br>23.3.1.4. FPU STATUS WORD | 23-26 |

| 23.3.1.4. FPU STATUS WORD                                           | 23-26 |

| 23.3.1.5. CONTROL WORD                                              | 23-27 |

| 23.3.1.6. TAG WORD                                                  |       |

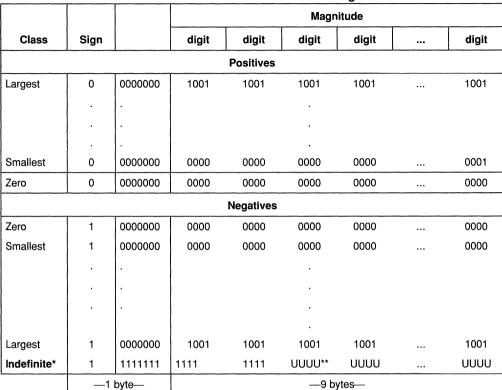

| 23.3.2. Data Types                                                  | 23-28 |

| 23.3.2.1. NaN'S                                                     | 23-28 |

| 23.3.2.2. PSEUDOZERO, PSEUDO-NaN, PSEUDEOINFINITY, AND UNNORMAL     |       |

|                                                                     | 23-28 |

| 23.3.3. Exceptions                                                  | 23-29 |

| 23.3.3.1. DENORMAL EXCEPTIONS                                       |       |

| 23.3.3.2. OVERFLOW EXCEPTIONS                                       |       |

| 23.3.3.3. UNDERFLOW EXCEPTIONS                                      |       |

| 23.3.3.4. EXCEPTION PRECEDENCE                                      | 23-30 |

| 23.3.3.5. CS AND IP FOR FPU EXCEPTIONS                              |       |

| 23.3.3.6. FPU ERROR SIGNALS                                         | 23-31 |

| 23.3.3.7. INVALID OPERATION ON DENORMALS                            | 23-31 |

|                                                    | Page |

|----------------------------------------------------|------|

| 23.3.3.8. ALIGNMENT EXCEPTIONS                     |      |

| 23.3.3.9. SEGMENT FAULT DURING FLDENV              |      |

| 23.3.3.10. INTERRUPT 7 — DEVICE NOT AVAILABLE      |      |

| 23.3.3.11. INTERRUPT 9 COPROCESSOR SEGMENT OVERRUN |      |

| 23.3.3.12. INTERRUPT 13 — GENERAL PROTECTION       |      |

| 23.3.3.13. INTERRUPT 16 FLOATING-POINT ERROR       |      |

| 23.3.4. Instructions                               |      |

| 23.3.5. Transcendental Instructions                |      |

| 23.3.6. Obsolete Instructions                      |      |

| 23.3.6.1. WAIT PREFIX DIFFERENCES                  |      |

| 23.3.6.2. OPERANDS SPLIT ACROSS SEGMENTS/PAGES     |      |

| 23.3.6.3. FPU INSTRUCTION SYNCHRONIZATION          |      |

|                                                    |      |

#### PART IV—OPTIMIZATION

#### CHAPTER 24 OPTIMIZATION

|         | ADDRESSING MODES AND REGISTER USAGE |      |

|---------|-------------------------------------|------|

| 24.2.   | ALIGNMENT                           | 24-2 |

| 24.2.1. | . Code Alignment                    | 24-2 |

| 24.2.2. | . Data Alignment                    | 24-2 |

| 24.3.   | PREFIXED OPCODES                    | 24-3 |

| 24.4.   | OPERAND AND REGISTER USAGE          | 24-3 |

| 24.5.   | INTEGER INSTRUCTION SELECTION       | 24-3 |

|         |                                     |      |

### PART V—INSTRUCTION SET

## CHAPTER 25

| INSTRUCTION SET                                            |       |

|------------------------------------------------------------|-------|

| 25.1. OPERAND-SIZE AND ADDRESS-SIZE ATTRIBUTES             |       |

| 25.1.1. Default Segment Attribute                          |       |

| 25.1.2. Operand-Size and Address-Size Instruction Prefixes |       |

| 25.1.3. Address-Size Attribute for Stack                   |       |

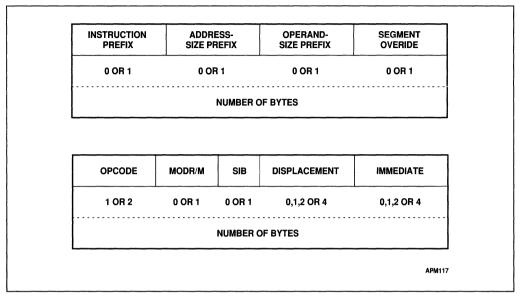

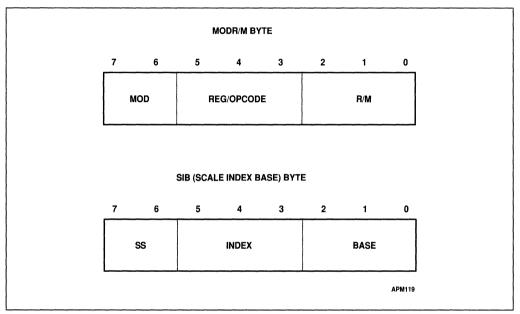

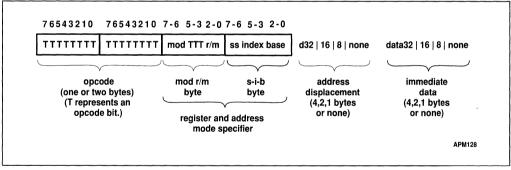

| 25.2. INSTRUCTION FORMAT                                   |       |

| 25.2.1. ModR/M and SIB Bytes                               |       |

| 25.2.2. How to Read the Instruction Set Pages              |       |

| 25.2.2.1. OPCODE COLUMN                                    |       |

| 25.2.2.2. INSTRUCTION COLUMN                               |       |

| 25.2.2.3. CLOCKS COLUMN                                    |       |

| 25.2.2.4. DESCRIPTION COLUMN                               | 25-13 |

| 25.2.2.5. OPERATION                                        |       |

| 25.2.2.6. DESCRIPTION                                      |       |

| 25.2.2.7. FLAGS AFFECTED                                   | 25-17 |

| 25.2.2.8. PROTECTED MODE EXCEPTIONS                        | 25-17 |

| 25.2.2.9. REAL ADDRESS MODE EXCEPTIONS                     |       |

| 25.2.2.10. VIRTUAL-8086 MODE EXCEPTIONS                    |       |

| AAA—ASCII Adjust after Addition                            |       |

| AAD—ASCII Adjust AX before Division                        |       |

| AAM—ASCII Adjust AX after Multiply                         |       |

| AAS-ASCII Adjust AL after Subtraction                      | 25-22 |

| ADC—Add with Carry                                         |       |

|                                                            |       |

# intel

|                                                           | Page   |

|-----------------------------------------------------------|--------|

| ADD-Add                                                   |        |

| AND-Logical AND                                           | 25-25  |

| ARPL—Adjust RPL Field of Selector                         | 25-26  |

| BOUND—Check Array Index Against Bounds                    | 25-27  |

| BSF-Bit Scan Forward                                      | 25-29  |

| BSR-Bit Scan Reverse                                      |        |

| BSWAP—Byte Swap                                           |        |

| BTBit Test                                                |        |

| BTC—Bit Test and Complement                               | 25-35  |

| BTR-Bit Test and Reset                                    |        |

| BTS—Bit Test and Set                                      | 25-39  |

| CALL—Call Procedure                                       | 25-41  |

| CBW/CWDE—Convert Byte to Word/Convert Word to Doubleword  | 25-47  |

| CDQ-Convert Double to Quad                                | 25-48  |

| CLC—Clear Carry Flag                                      |        |

| CLDClear Direction Flag                                   |        |

| CLI-Clear Interrupt Flag                                  |        |

| CLTS—Clear Task-Switched Flag in CR0                      |        |

| CMC—Complement Carry Flag                                 |        |

| CMP—Compare Two Operands                                  | 25-55  |

| CMPS/CMPSB/CMPSW/CMPSD—Compare String Operands            |        |

| CMPXCHG—Compare and Exchange                              | 25-58  |

| CMPXCHG8B—Compare and Exchange 8 Bytes                    | 25-60  |

| CPUID—CPU Identification                                  | 25-62  |

| CWD/CDQ—Convert Word to Double/Convert Double to Quad     | 25-64  |

| CWDE—Convert Word to Doubleword                           |        |

| DAA—Decimal Adjust AL after Addition                      | 25-66  |

| DAS—Decimal Adjust AL after Subtraction                   |        |

| DEC—Decrement by 1                                        |        |

| DIV—Unsigned Divide                                       |        |

| ENTER—Make Stack Frame for Procedure Parameters           |        |

| F2XM1—Compute 2x–1                                        |        |

| FABS—Absolute Value                                       | 25-74  |

| FADD/FADDP/FIADD—Add                                      |        |

| FBLD—Load Binary Coded Decimal                            |        |

| FBSTP—Store Binary Coded Decimal and Pop                  | 25-79  |

| FCHS—Change Sign                                          |        |

| FCLEX/FNCLEX—Clear Exceptions                             | 25-81  |

| FCOM/FCOMP/FCOMPP—Compare Real                            | 25-82  |

| FCOS—Cosine                                               | 25-84  |

| FDECSTP—Decrement Stack-Top Pointer                       | 25-85  |

| FDIV/FDIVP/FIDIV—Divide                                   |        |

| FDIVR/FDIVRP/FIDIVR—Reverse Divide                        |        |

| FFREE—Free Floating-Point Register                        |        |

| FICOM/FICOMP—Compare Integer                              |        |

| FILD-Load Integer                                         |        |

| FINCSTP—Increment Stack-Top Pointer                       | 25-94  |

| FINIT/FNINIT—Initialize Floating-Point Unit               | 25-95  |

| FIST/FISTP—Store Integer                                  |        |

| FLD—Load Real                                             |        |

| FLD1/FLDL2T/FLDL2E/FLDPI/FLDLG2/FLDLN2/FLDZ—Load Constant |        |

| FLDCW—Load Control Word                                   |        |

| FLDENV—Load FPU Environment                               | 25-102 |

|                                                           | .5 .00 |

# int<sub>el</sub>.

|                                                                             | De    |     |

|-----------------------------------------------------------------------------|-------|-----|

| FMUL/FMULP/FIMUL—Multiply                                                   |       | 105 |

| FNOP—No Operation                                                           | 25-   | 106 |

| FPATAN—Partial Arctangent                                                   | 25-   | 107 |

| FPREM—Partial Remainder                                                     |       |     |

| FPREM1—Partial Remainder                                                    |       |     |

| FPTAN—Partial Tangent                                                       |       |     |

| FRNDINT—Round to Integer                                                    |       |     |

| FRSTOR—Restore FPU State                                                    | 25-   | 115 |

| FSAVE/FNSAVE—Store FPU State                                                | 25    | 117 |

| FSCALE—Scale                                                                |       |     |

| FSIN—Sine                                                                   |       |     |

| FSINCOS—Sine and Cosine                                                     |       |     |

| FSQRT—Square Root                                                           |       |     |

| FST/FSTP—Store Real                                                         | 25    | 120 |

| FSTCW/FNSTCW—Store Control Word                                             | 25-   | 124 |

| FSTENV/FNSTENV—Store FPU Environment                                        | 20-   | 107 |

| FSTSW/FNSTSW—Store Status Word                                              |       |     |

| FSUB/FSUBP/FISUB—Subtract                                                   |       |     |

| FSUBR/FSUBRP/FISUBR—Reverse Subtract                                        | 20-   | 101 |

|                                                                             |       |     |

| FTST—TEST<br>FUCOM/FUCOMP/FUCOMPP—Unordered Compare Real                    | .20-  | 100 |

| FUCOM/FUCOMP/FUCOMPP-Unordered Compare Real                                 | .20-  | 100 |

|                                                                             |       |     |

| FXAM—Examine<br>FXCH—Exchange Register Contents                             | .20-  | 130 |

| FXCH—Exchange Register Contents<br>FXTRACT—Extract Exponent and Significand | .20-  | 140 |

|                                                                             |       |     |

| FYL2X—Compute y × log2x<br>FYL2XP1—Compute y × log2(x +1)                   | .20-  | 144 |

| HLT—Halt                                                                    | . 20- | 140 |

|                                                                             |       |     |

| IDIV—Signed Divide                                                          |       |     |

| IMUL—Signed Multiply                                                        |       |     |

| IN—Input from Port<br>INC—Increment by 1                                    | .23-  | 101 |

| INC—Increment by T<br>INS/INSB/INSW/INSD—Input from Port to String          | . 20- | 100 |

| INS/INSB/INSB/INSD/INSD/Input from Port to Stilling                         | .20-  | 154 |

| INT/INTO—Call to Interrupt Procedure<br>INVD—Invalidate Cache               | .20-  | 100 |

| INVD—Invalidate Cache<br>INVLPG—Invalidate TLB Entry                        |       |     |

| IRET/IRETD—Interrupt Return                                                 |       |     |

| Jcc—Jump if Condition is Met                                                | .20-  | 171 |

| JMP—Jump                                                                    |       |     |

| LAHF—Load Flags into AH Register                                            | 25-   | 170 |

| LAR—Load Access Rights Byte                                                 | 25    | 100 |

| LDS/LES/LFS/LGS/LSS—Load Full Pointer                                       | 25    | 192 |

| LEA-Load Effective Address                                                  | 25-   | 18/ |

| LEA/Load Elective Address                                                   |       |     |

| LEAVE-Ingrit Leven rocedure Exit                                            |       |     |

| LES-Load Full Pointer                                                       |       |     |

| LGDT/LIDT—Load Global/Interrupt Descriptor Table Register                   | 25-   | 180 |

| LGS—Load Full Pointer                                                       |       |     |

| LLDT-Load Local Descriptor Table Register                                   | 25-   | 192 |

| LIDT—Load Interrupt Descriptor Table Register                               | 25-   | 102 |

| LMSW—Load Machine Status Word                                               |       |     |

| LOCK—Assert LOCK# Signal Prefix                                             |       |     |

| LODS/LODSB/LODSW/LODSD—Load String Operand                                  | 25-   | 196 |

|                                                                             | . 20- | 100 |

# intel

|                                                             | Pa  | age |

|-------------------------------------------------------------|-----|-----|

| LOOP/LOOPcond—Loop Control with CX Counter                  | 25- | 198 |

| LSL—Load Segment Limit                                      | 25- | 200 |

| LSS-Load Full Pointer                                       | 25- | 202 |

| LTR-Load Task Register                                      | 25- | 203 |

| MOV-Move Data                                               | 25- | 204 |

| MOVMove to/from Control Registers                           | 25- | 206 |

| MOV-Move to/from Debug Registers                            |     |     |

| MOVS/MOVSB/MOVSW/MOVSD—Move Data from String to String      | 25- | 209 |

| MOVSX—Move with Sign-Extend                                 | 25- | 211 |

| MOVZX—Move with Zero-Extend                                 | 25- | 212 |

| MUL-Unsigned Multiplication of AL, AX, or EAX               | 25- | 213 |

| NEG—Two's Complement Negation                               | 25- | 215 |

| NOP—No Operation                                            | 25- | 216 |

| NOT-One's Complement Negation                               | 25- | 217 |

| OR-Logical Inclusive OR                                     | 25- | 218 |

| OUT-Output to Port                                          | 25- | 219 |

| OUTS/OUTSB/OUTSW/OUTSD—Output String to Port                |     |     |

| POP-Pop a Word from the Stack                               | 25- | 224 |

| POPA/POPAD—Pop all General Registers                        | 25- | 227 |

| POPF/POPFD-Pop Stack into FLAGS or EFLAGS Register          | 25- | 229 |

| PUSH—Push Operand onto the Stack                            |     |     |

| PUSHA/PUSHAD—Push all General Registers                     | 25- | 233 |

| PUSHF/PUSHFD—Push Flags Register onto the Stack             |     |     |

| RCL/RCR/ROL/RORRotate                                       |     |     |

| RDMSR—Read from Model Specific Register                     | 25- | 240 |

| REP/REPE/REPZ/REPNE/REPNZ—Repeat Following String Operation |     |     |

| RET—Return from Procedure                                   | 25- | 245 |

| ROL/ROR—Rotate                                              |     |     |

| RSM—Resume from System Management Mode                      | 25- | 250 |

| SAHF—Store AH into Flags                                    | 25- | 251 |

| SAL/SAR/SHL/SHR—Shift Instructions                          | 25- | 252 |

| SBB—Integer Subtraction with Borrow                         |     |     |

| SCAS/SCASB/SCASW/SCASD—Compare String Data                  | 25- | 257 |

| SETco-Byte Set on Condition                                 | 25- | 259 |

| SGDT/SIDT—Store Global/Interrupt Descriptor Table Register  | 25- | 261 |

| SHL/SHR—Shift Instructions                                  | 25- | 263 |

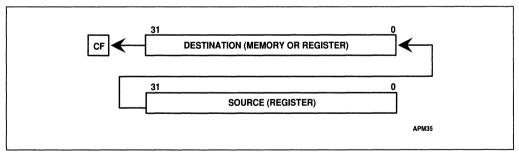

| SHLD—Double Precision Shift Left                            | 25- | 264 |

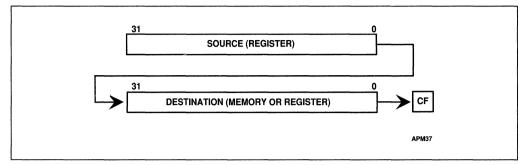

| SHRD—Double Precision Shift Right                           | 25- | 266 |

| SIDT—Store Interrupt Descriptor Table Register              |     |     |

| SLDT—Store Local Descriptor Table Register                  | 25- | 269 |

| SMSW—Store Machine Status Word                              | 25- | 270 |

| STC—Set Carry Flag                                          | 25- | 271 |

| STD—Set Direction Flag                                      | 25- | 272 |

| STI-Set Interrupt Flag                                      |     |     |

| STOS/STOSB/STOSW/STOSD—Store String Data                    | 25- | 275 |

| STR—Store Task Register                                     | 25- | 277 |

| SUB—Integer Subtraction                                     | 25- | 278 |

| TEST-Logical Compare                                        |     |     |

| VERR, VERW—Verify a Segment for Reading or Writing          | 25- | 281 |

| WAIT—Wait                                                   |     |     |

| WBINVD—Write-Back and Invalidate Cache                      |     |     |

| WRMSR—Write to Model Specific Register                      |     |     |

| XADD—Exchange and Add                                       | 25- | 288 |

| <b>U</b>                                                    | -   |     |

|                                             | Page   |

|---------------------------------------------|--------|

| XCHG—Exchange Register/Memory with Register |        |

| XLAT/XLATB—Table Look-up Translation        |        |

| XOR—Logical Exclusive OR                    | 25-291 |

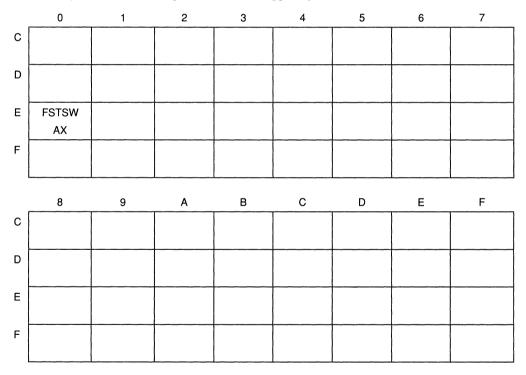

#### APPENDIX A OPCODE MAP

#### APPENDIX B FLAG CROSS-REFERENCE

APPENDIX C STATUS FLAG SUMMARY

#### APPENDIX D CONDITION CODES

#### APPENDIX E NUMERIC EXCEPTION SUMMARY

APPENDIX F INSTRUCTION FORMAT AND TIMING

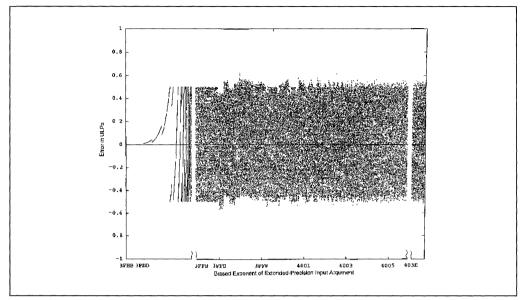

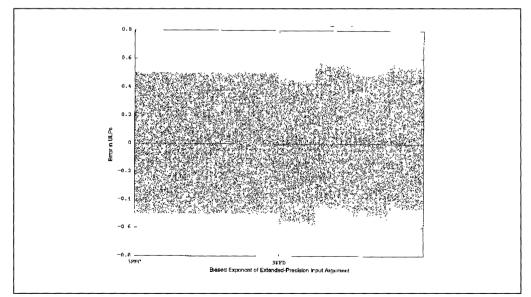

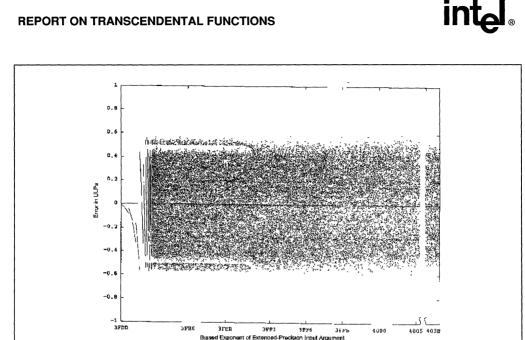

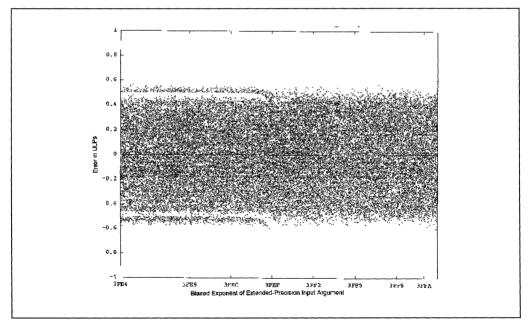

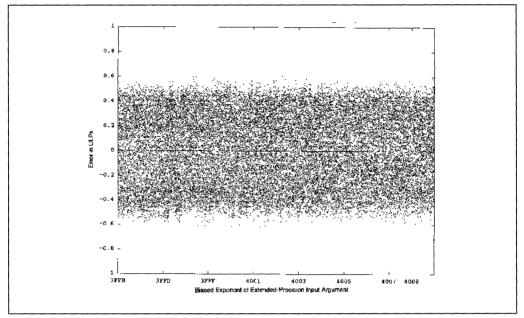

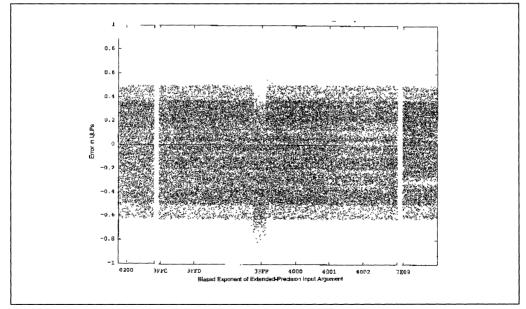

#### APPENDIX G REPORT ON TRANSCENDENTAL FUNCTIONS

#### APPENDIX H ADVANCED FEATURES

#### GLOSSARY

### **Figures**

| Figure | Title                                             | Page |

|--------|---------------------------------------------------|------|

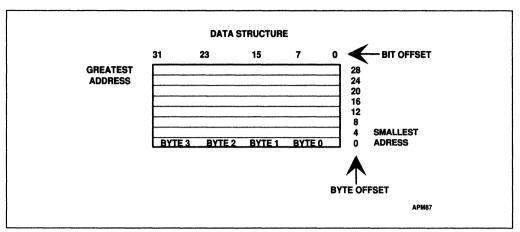

| 1-1.   | Bit and Byte Order                                |      |

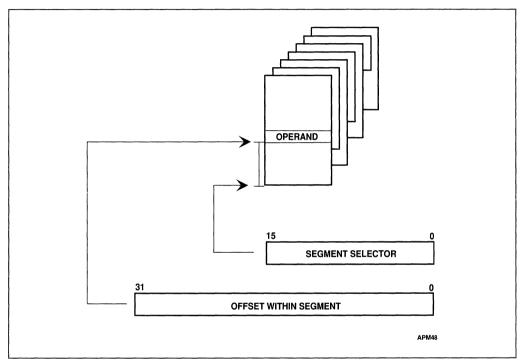

| 3-1.   | Segmented Addressing                              | 3-3  |

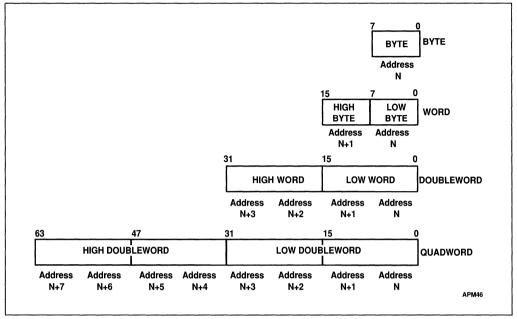

| 3-2.   | Fundamental Data Types                            |      |

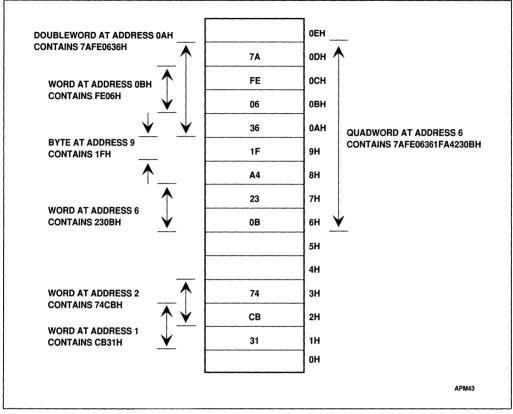

| 3-3.   | Bytes, Words, Doublewords and Quadwords in Memory |      |

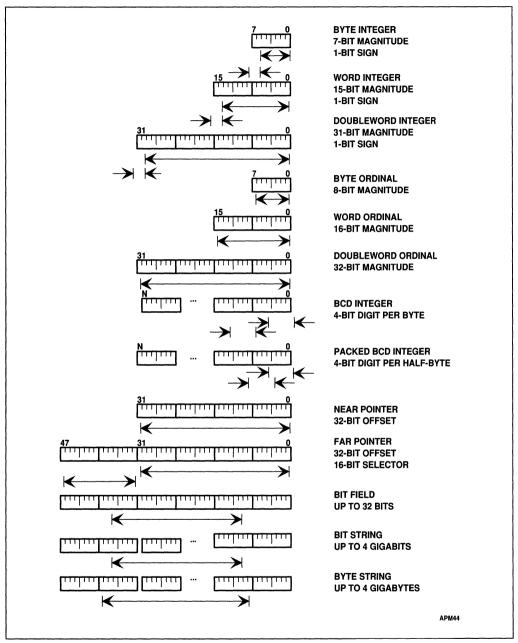

| 3-4.   | Data Types                                        |      |

| 3-5.   | Application Register Set                          | 3-9  |

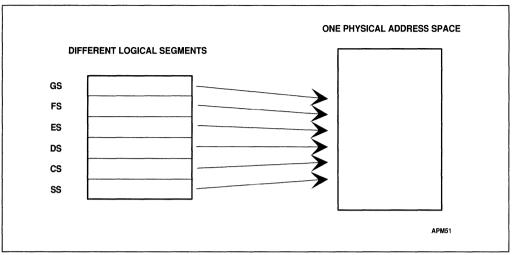

| 3-6.   | An Unsegmented Memory                             | 3-11 |

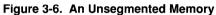

| 3-7.   | A Segmented Memory                                | 3-11 |

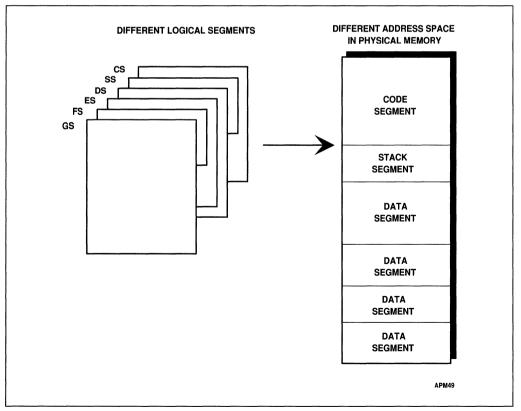

| 3-8.   | Stacks                                            |      |

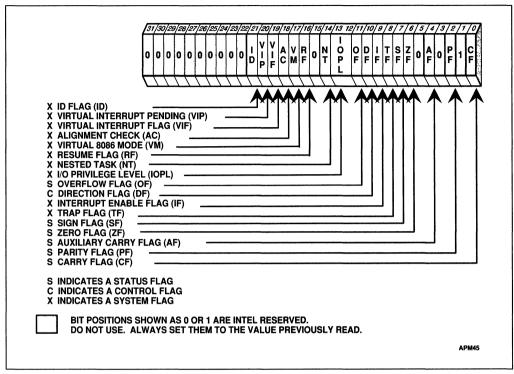

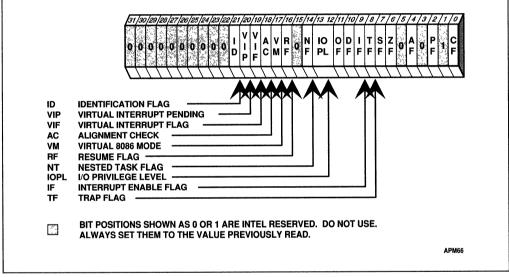

| 3-9.   | EFLAGS Register                                   |      |

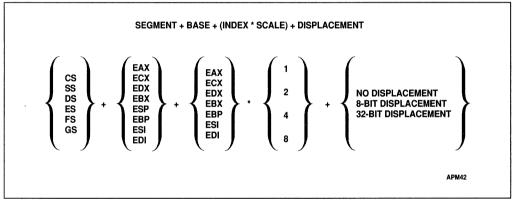

| 3-10.  | Effective Address Computation                     | 3-21 |

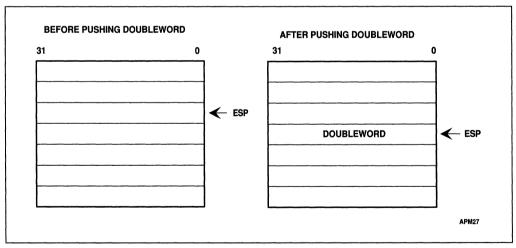

| 4-1.   | PUSH Instruction                                  | 4-2  |

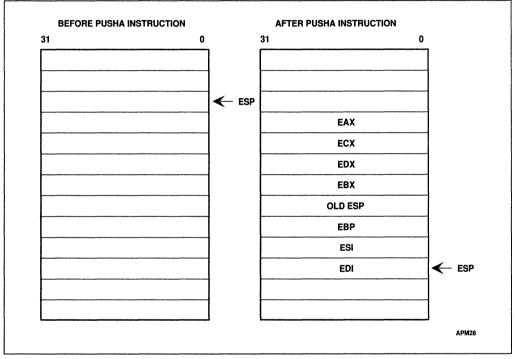

| 4-2.   | PUSHA Instruction                                 |      |

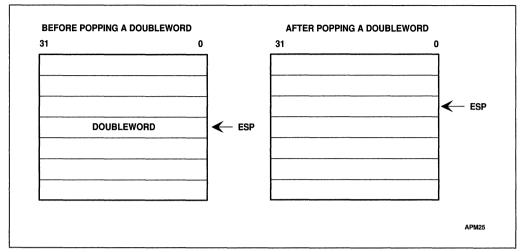

| 4-3.   | POP Instruction                                   |      |

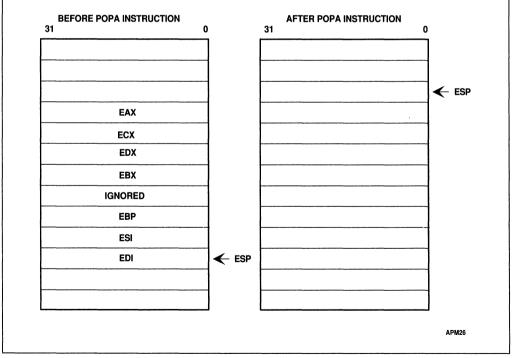

| 4-4    | POPA Instruction                                  |      |

# intel

| Figure         | Title                                                                | Page   |

|----------------|----------------------------------------------------------------------|--------|

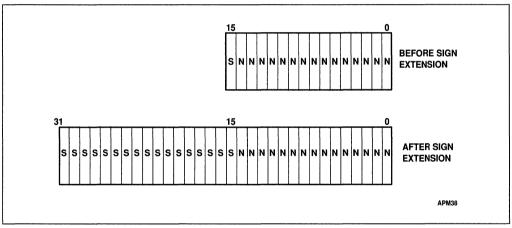

| 4-5.           | Sign Extension                                                       |        |

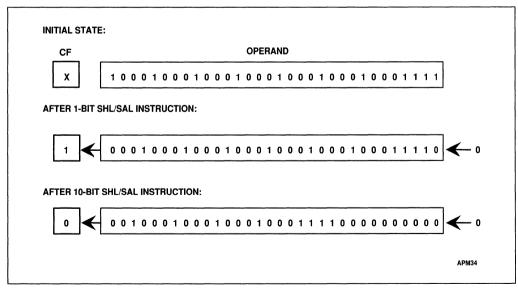

| 4-6.           | SHL/SAL Instruction                                                  |        |

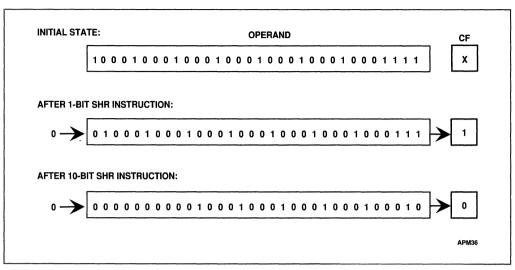

| 4-7.           | SHR Instruction                                                      |        |

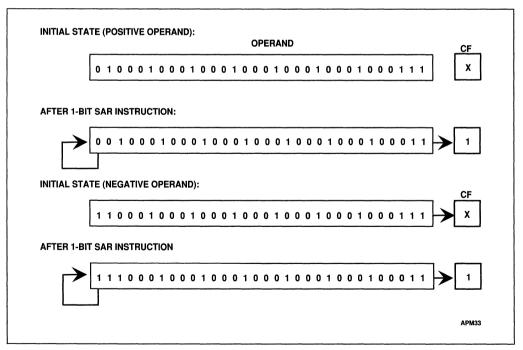

| 4-8.           | SAR Instruction                                                      |        |

| 4-9.           | SHLD Instruction                                                     |        |

| 4-10.          | SHRD Instruction                                                     |        |

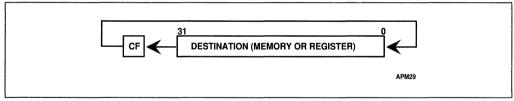

| 4-11.          | ROL Instruction                                                      |        |

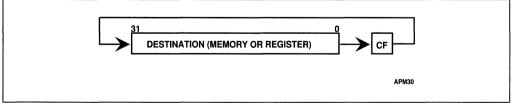

| 4-12.          | ROR Instruction                                                      |        |

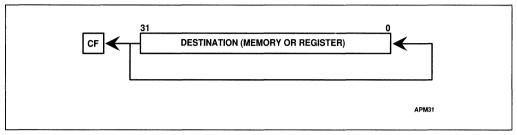

| 4-13.          | RCL Instruction                                                      | .4-17  |

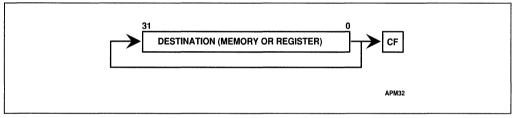

| 4-14.          | RCR Instruction                                                      |        |

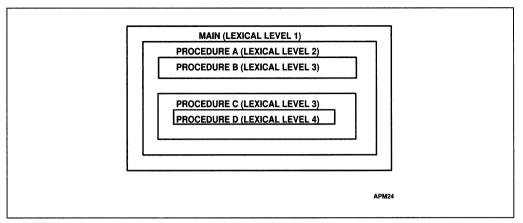

| 4-15.          | Nested Procedures                                                    |        |

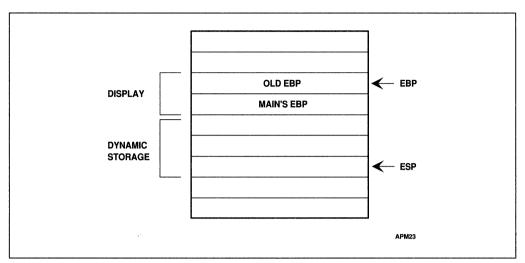

| 4-16.          | Stack Frame After Entering MAIN                                      |        |

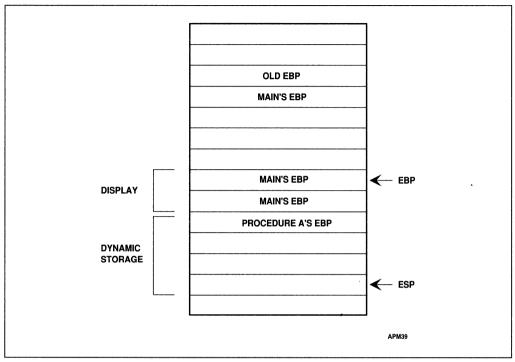

| 4-17.          | Stack Frame After Entering PROCEDURE A                               | .4-33  |

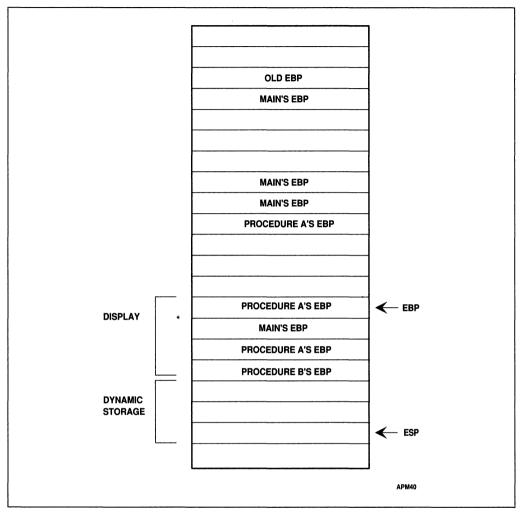

| 4-18.          | Stack Frame After Entering PROCEDURE B                               | .4-34  |

| 4-19.          | Stack Frame After Entering PROCEDURE C                               |        |

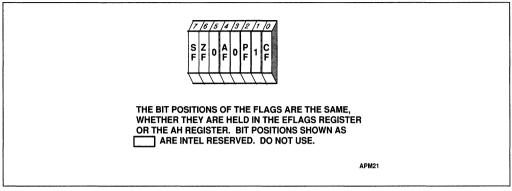

| 4-20.          | Low Byte of EFLAGS Register                                          | .4-37  |

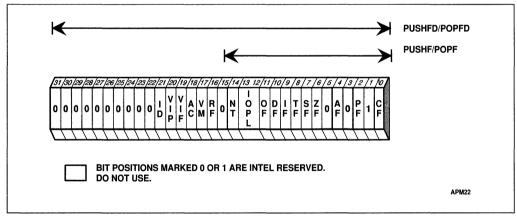

| 4-21.<br>4-22. | Flags Used with PUSHF and POPF                                       |        |

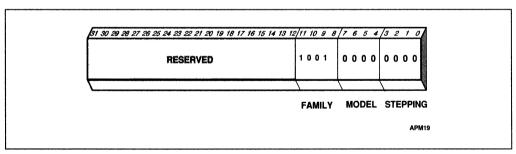

| 4-22.<br>6-1.  | EAX Following the CPUID Instruction                                  | . 4-44 |

| 6-1.<br>6-2.   | Floating-point Unit Register Set                                     | 6-8    |

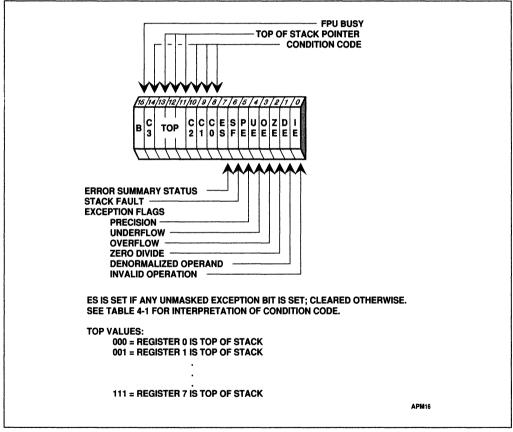

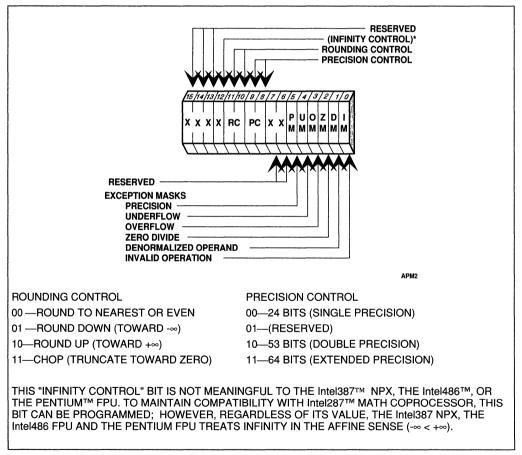

| 6-2.<br>6-3.   | FPU Status Word<br>FPU Control Word Format                           | 6-9    |

| 6-3.<br>6-4.   |                                                                      |        |

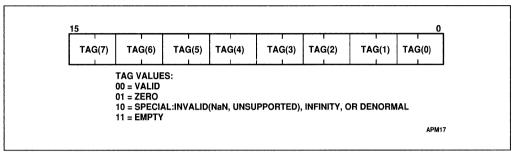

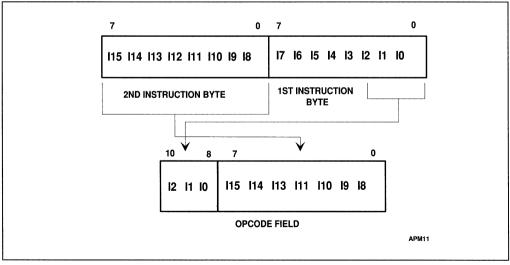

| 6-5.           | Tag Word Format<br>Opcode Field                                      |        |

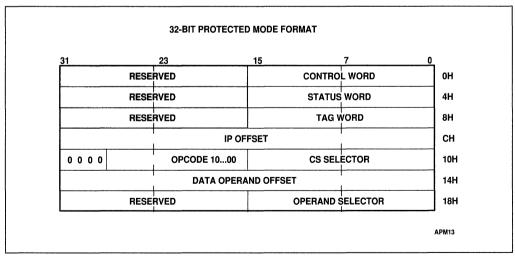

| 6-6.           | Protected Mode Numeric Instruction and Data Pointer Image in Memory, | .0-14  |

| 0-0.           | 32-Bit Format                                                        | 6.15   |

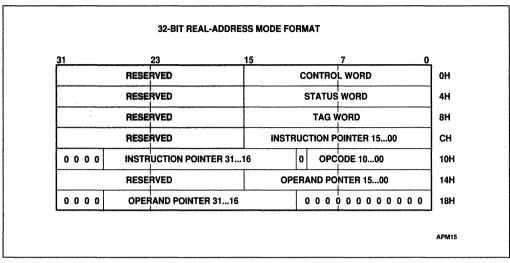

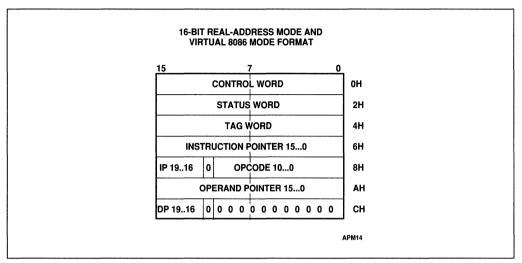

| 6-7.           | Real Mode Numeric Instruction and Data Pointer Image in Memory,      | .0-15  |

| 07.            | 32-Bit Format                                                        | 6-16   |

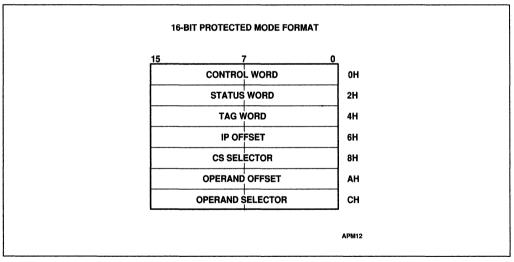

| 6-8.           | Protected Mode Numeric Instruction and Data Pointer Image in Memory, | .0 10  |

| 0 0.           | 16-Bit Format                                                        | 6-16   |

| 6-9.           | Real Mode Numeric Instruction and Data Pointer Image in Memory,      |        |

|                | 16-Bit Format                                                        | 6-17   |

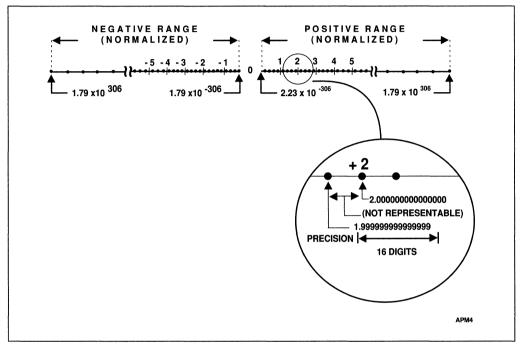

| 6-10.          | Double-Precision Number System                                       |        |

| 6-11.          | Numerical Data Formats                                               |        |

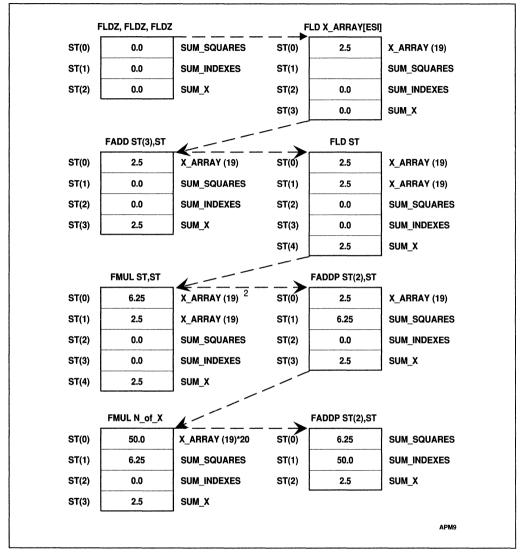

| 6-12.          | Instructions and Register Stack                                      |        |

| 7-1.           | Arithmetic Example Using Infinity                                    |        |

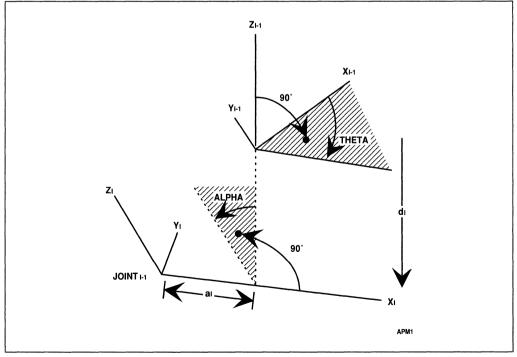

| 8-1.           | Relationships Between Adjacent Joints                                | 8-23   |

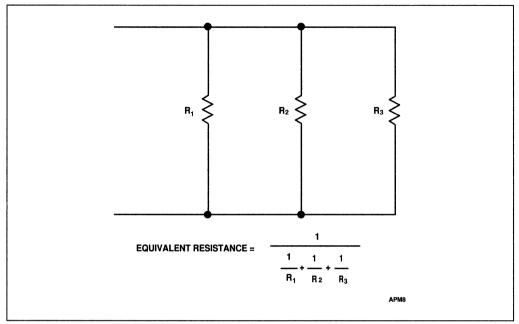

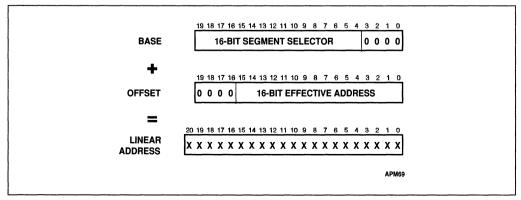

| 9-1.           | 8086 Address Translation                                             |        |

| 10-1.          | System Flags                                                         |        |

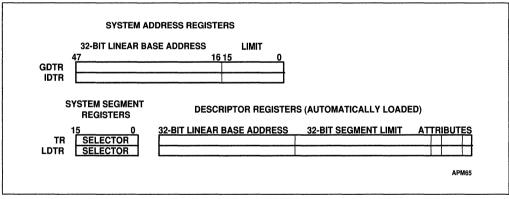

| 10-2.          | Memory Management Registers                                          |        |

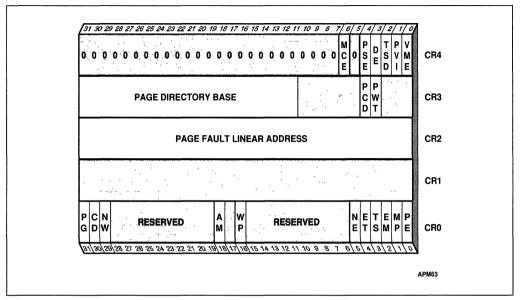

| 10-3.          | Control Registers                                                    | 10-6   |

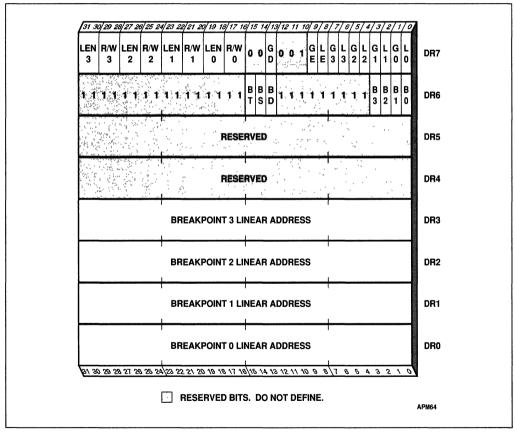

| 10-4.          | Debug Registers                                                      | 10-9   |

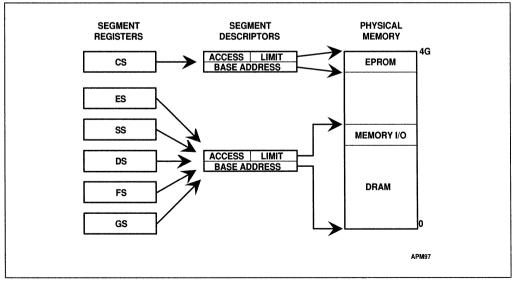

| 11-1.          | Flat Model                                                           |        |

| 11-2.          | Protected Flat Model                                                 |        |

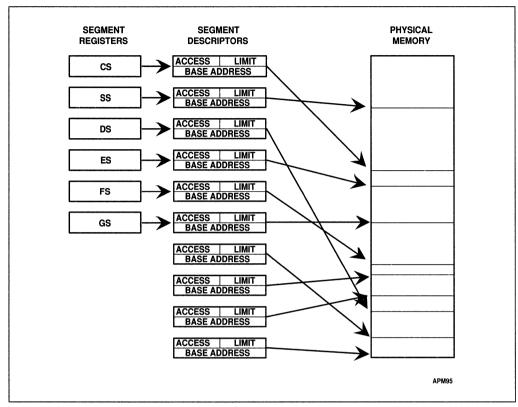

| 11-3.          | Multisegment Model                                                   |        |

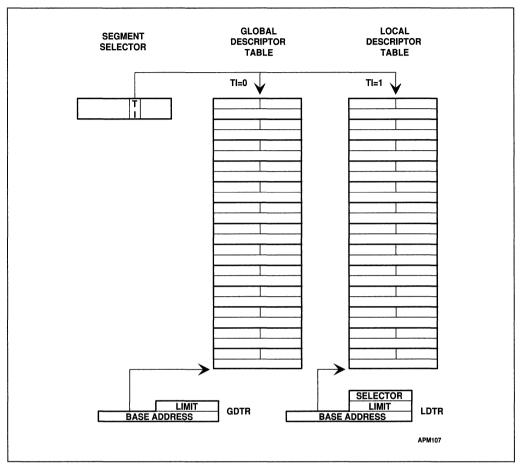

| 11-4.          | TI Bit Selects Descriptor Table                                      |        |

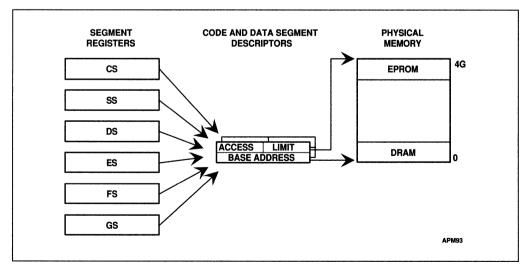

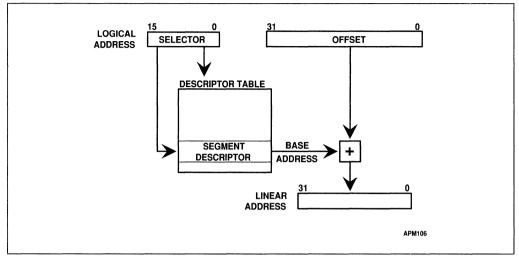

| 11-5.          | Segment Translation                                                  | . 11-9 |

| 11-6.          | Segment Registers                                                    |        |

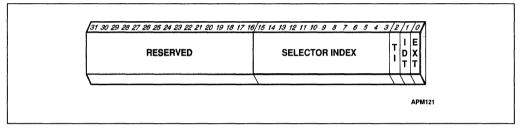

| 11-7.          | Segment Selector                                                     |        |

| 11-8.          | Segment Descriptors                                                  | 1-12   |

| 11-9.          | Segment Descriptor (Segment Not Present)                             |        |

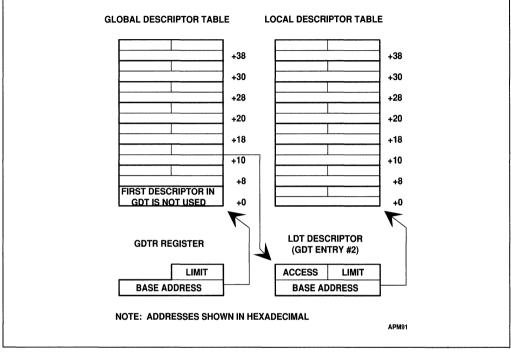

| 11-10.         | Descriptor Tables                                                    | 11-16  |

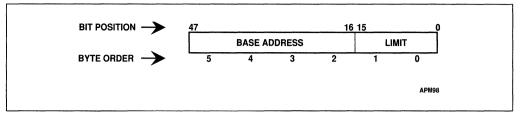

| 11-11.         | Pseudo-Descriptor Format                                             |        |

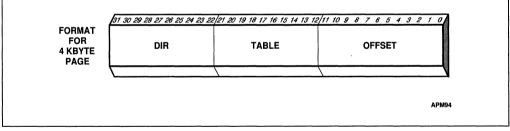

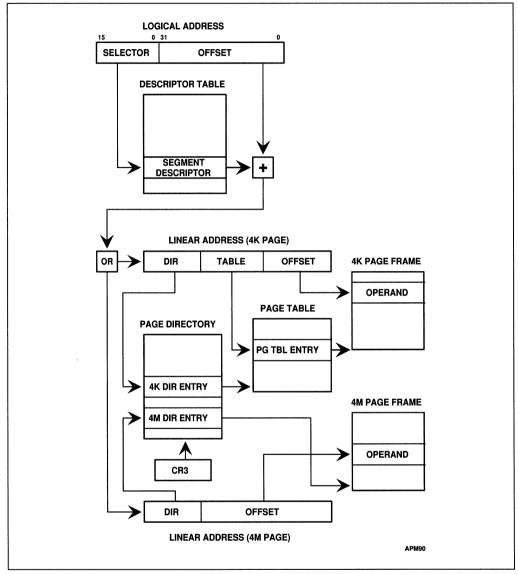

| 11-12.         | Format of a Linear Address 1                                         | 11-18  |

# intel

| Figure         | Title                                                                   | Page   |

|----------------|-------------------------------------------------------------------------|--------|

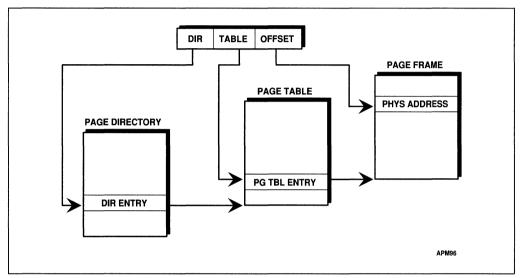

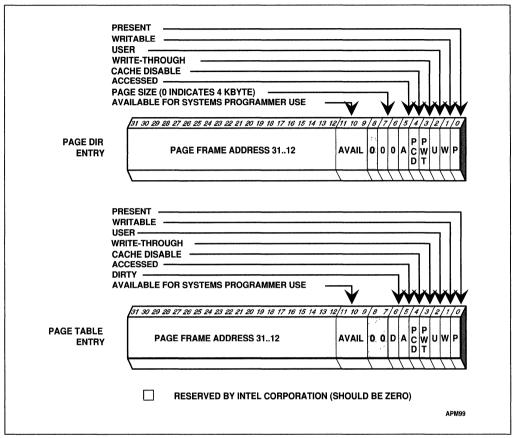

| 11-13.         | Page Translation                                                        | 11-19  |

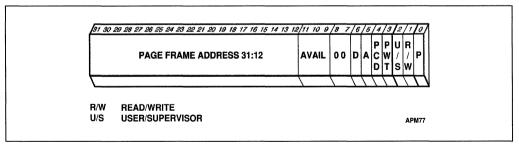

| 11-14.         | Format of Page Directory and Page Table Entries for 4K Pages            | 11-20  |

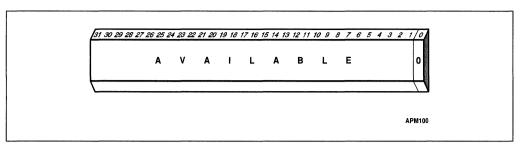

| 11-15.         | Format of a Page Table Entry for a Not-Present Page                     |        |

| 11-16.         | Combined Segment and Page Address Translation                           | 11-24  |

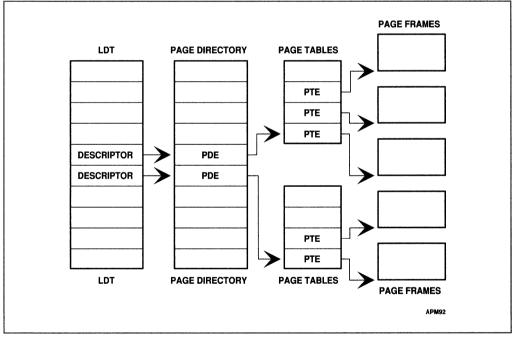

| 11-17.         | Each Segment Can Have Its Own Page Table                                |        |

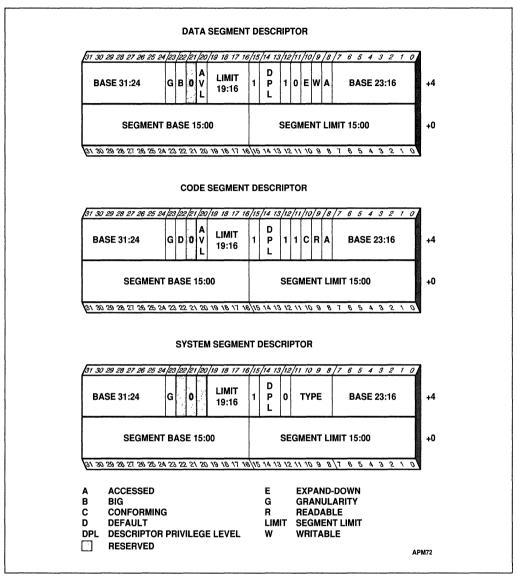

| 12-1.          | Descriptor Fields Used for Protection                                   | . 12-3 |

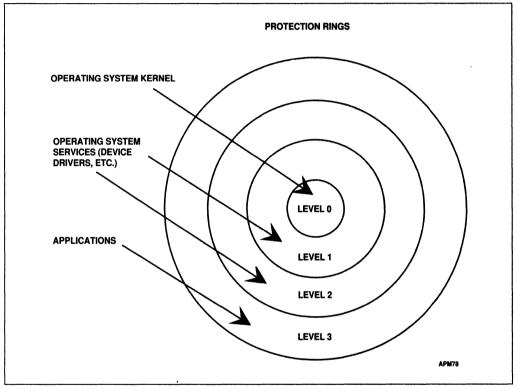

| 12-2.          | Protection Rings                                                        |        |

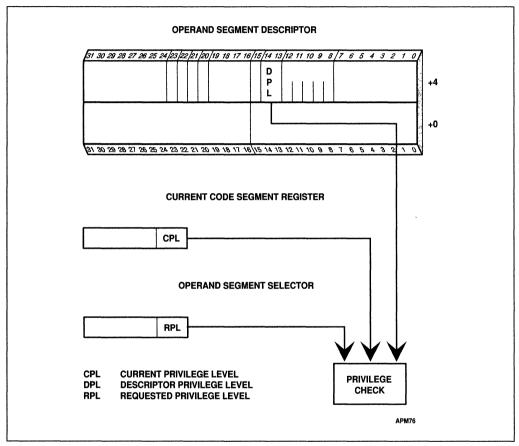

| 12-3.          | Privilege Check for Data Access                                         |        |

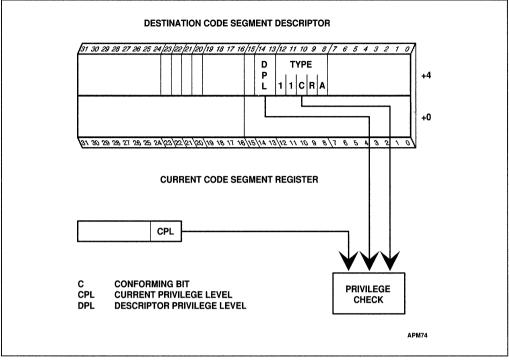

| 12-4.          | Privilege Check for Control Transfer Without Gate                       | 12-10  |

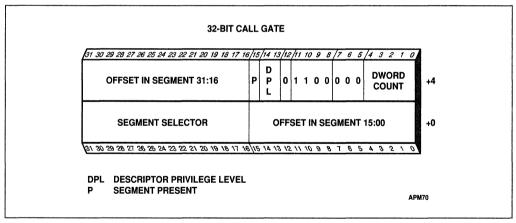

| 12-5           | Call Gate                                                               | 12-11  |

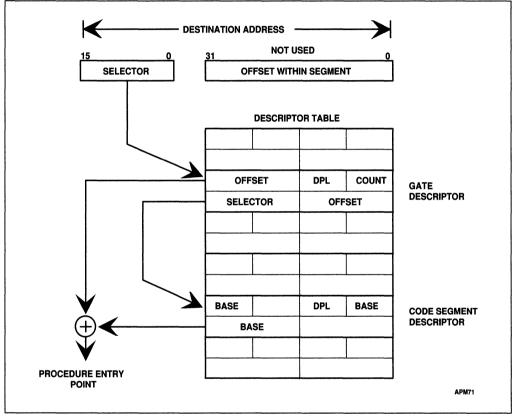

| 12-6.          | Call Gate Mechanism                                                     |        |

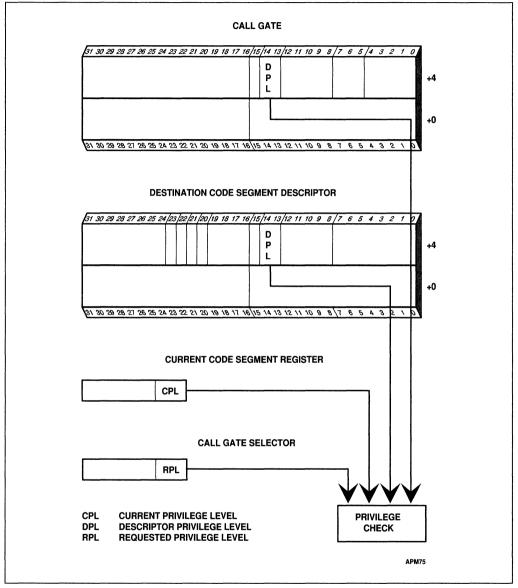

| 12-7.          | Privilege Check for Control Transfer with Call Gate                     | 12-12  |

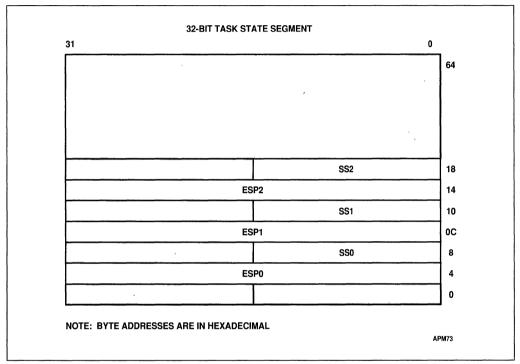

| 12-8.          | Initial Stack Pointers in a TSS                                         | 12-13  |

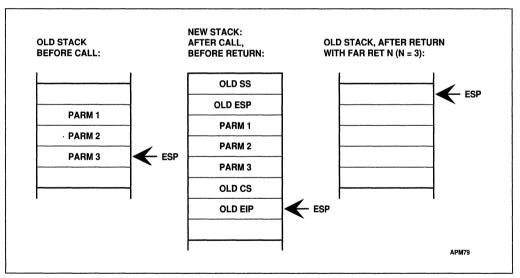

| 12-0.          | Stack Frame During Interlevel Call                                      | 12-15  |

| 12-9.          | Protection Fields of a Page Table Entry                                 |        |

| 12-10.         |                                                                         |        |

|                | 32-Bit Task State Segment                                               |        |

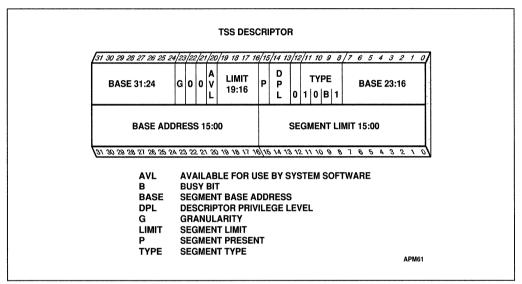

| 13-2.          | TSS Descriptor                                                          |        |

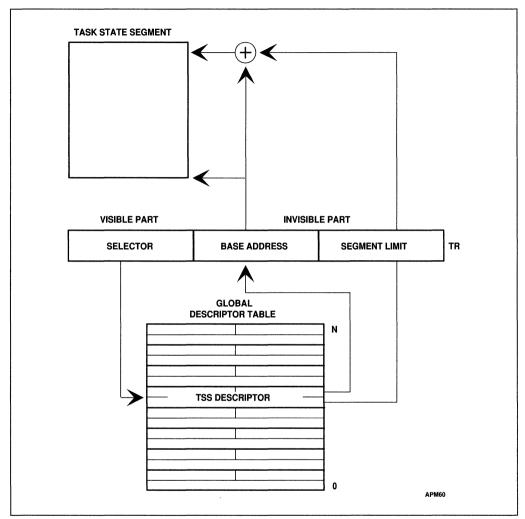

| 13-3.          | Task Register                                                           |        |

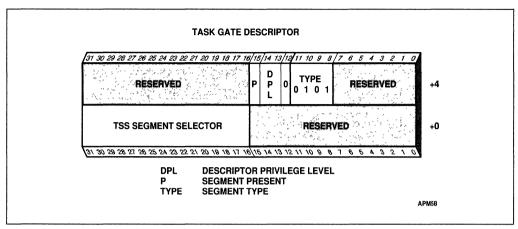

| 13-4.          | Task Gate Descriptor                                                    | 13-7   |

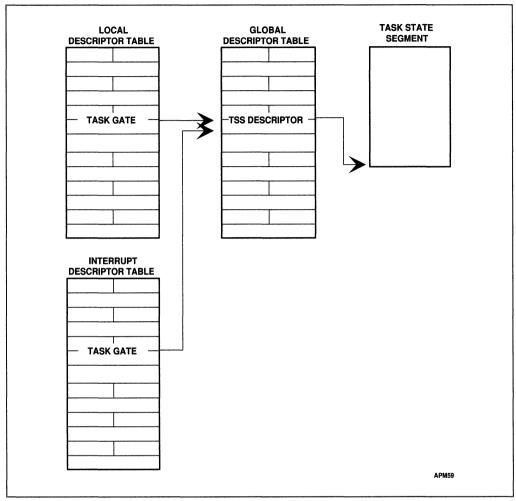

| 13-5.          | Task Gates Reference Tasks                                              | 13-8   |

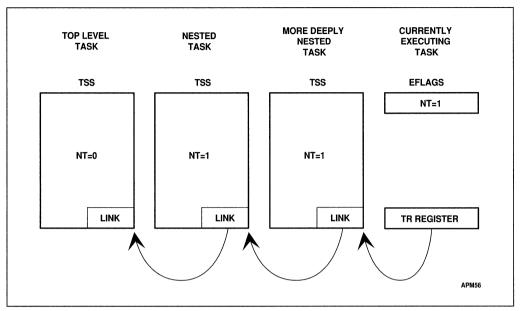

| 13-6.          | Nested Tasks                                                            |        |