# inte

# Intel Architecture MMX<sup>TM</sup> Technology

**Programmer's Reference Manual**

March 1996 Order No. 243007-002 Subject to the terms and conditions set forth below, Intel hereby grants you a nonexclusive, nontransferable license, under its patents and copyrights on the example code sequences contained in Chapters 3, 4 and 5 of the **Programmer's Reference Manual**, to use, reproduce and distribute such example code sequences solely as part of your computer program(s) and solely in order to allow your computer program(s) to implement the multimedia instruction extensions contained in such sequences solely with respect to the Intel instruction set architecture. No other license, express, implied, statutory, by estoppel or otherwise, to any other intellectual property rights is granted herein.

THIS DOCUMENT AND ALL INFORMATION, PROPOSALS, SAMPLES AND OTHER MATERIALS PROVIDED IN CONNECTION WITH OR IN RELATION TO THIS DOCUMENT (INCLUDING, WITHOUT LIMITATION, THE EXAMPLE CODE SEQUENCES) ARE PROVIDED 'AS IS' WITH NO WARRANTIES, EXPRESS, IMPLIED, STATUTORY OR OTHERWISE, AND INTEL SPECIFICALLY DISCLAIMS ANY IMPLIED WARRANTY OF MERCHANTABILITY, NONINFRINGEMENT OR FITNESS FOR ANY PARTICULAR PURPOSE.

Any use or distribution of this document or the materials contained herein must fully comply with all then current laws of the United States including, without limitation, rules and regulations of the United States Office of Export Administration and other applicable U.S. governmental agencies.

THIS DOCUMENT AND THE MATERIALS PROVIDED HEREIN ARE PROVIDED WITHOUT CHARGE. THEREFORE, IN NO EVENT WILL INTEL BE LIABLE FOR ANY DAMAGES OF ANY KIND, INCLUDING DIRECT OR INDIRECT DAMAGES, LOSS OF DATA, LOST PROFITS, COST OF COVER OR SPECIAL, INCIDENTAL, CONSEQUENTIAL, DAMAGES ARISING FROM THE USE OF THE MATERIALS PROVIDED HEREIN, INCLUDING WITHOUT LIMITATION THE EXAMPLE CODE SEQUENCES, HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY. THIS LIMITATION WILL APPLY EVEN IF INTEL OR ANY AUTHORIZED AGENT OF INTEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

Information in this document is provided in connection with Intel products. No license under any patent or copyright is granted expressly or impliedly by this publication. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products.

Intel retains the right to make changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to their specifications known as errata.

\*Other brands and names are the property of their respective owners.

Copyright © Intel Corporation 1996

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing product orders.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation

P.O. Box 7641

Mt. Prospect IL 60056-764

or call 1-800-879-4683

#### **IMPORTANT INFORMATION ABOUT THIS DOCUMENT**

Following are changes to the text in this manual that were not available until press time. Please note these changes when using the information contained in this manual.

|                                                                                                                         | Documentation changes                                                                                                                                                                       |                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Location in Document                                                                                                    | <b>Document Currently Reads</b>                                                                                                                                                             | Change to Document                                                                                                                                                                                  |

| Page 5-34:<br>PCMPGTB/PCMPGTW/PCMPGT<br>D—Packed Compare for Greater<br>Than<br>Heading: Description<br>Paragraph: Four | The PCMPGTD instruction<br>compares the signed words in the<br>destination operand to the<br>corresponding signed words in the<br>source operand.                                           | The PCMPGTD instruction<br>compares the signed<br><b>doublewords</b> in the destination<br>operand to the corresponding<br>signed <b>doublewords</b> in the source<br>operand.                      |

| Page 5-51:<br>PSRLW/PSRLD/PSRLQ-Packed<br>Shift Right Logical,<br>Heading: Description<br>Paragraph: Four               | The PSLLD instruction shifts each<br>of the two doublewords in the<br>destination register to the right by<br>the number of bits specified in the<br>count operand.                         | The <b>PSRLD</b> instruction shifts each<br>of the two doublewords in the<br>destination register to the right by<br>the number of bits specified in the<br>count operand.                          |

| Page 5-56: PSUBSB/PSUBSW/<br>Packed Subtract with Saturation<br>Heading: Description<br>Paragraph: Three                | The PSUBB instruction subtracts<br>the signed bytes of the source<br>operand from the signed bytes of<br>the destination operand, and writes<br>the results to the destination<br>register. | The <b>PSUBSB</b> instruction subtracts<br>the signed bytes of the source<br>operand from the signed bytes of<br>the destination operand, and writes<br>the results to the destination<br>register. |

| Page 5-56: PSUBSB/PSUBSW/<br>Packed Subtract with Saturation<br>Heading: Description<br>Paragraph: Four                 | The PSUBW instruction subtracts<br>the signed words of the source<br>operand from the signed words of<br>the destination operand and writes<br>the results to the destination<br>register.  | The <b>PSUBSW</b> instruction<br>subtracts the signed words of the<br>source operand from the signed<br>words of the destination operand<br>and writes the results to the<br>destination register.  |

#### **Documentation Changes**

#### **TABLE OF CONTENTS**

#### **CHAPTER 1**

#### INTRODUCTION TO THE INTEL ARCHITECTURE MMX<sup>TM</sup> TECHNOLOGY

| 1.1.   | ABOUT THE INTEL ARCHITECTURE MMX™ TECHNOLOGY       | .1-1 |

|--------|----------------------------------------------------|------|

| 1.1.1. | Single Instruction, Multiple Data (SIMD) Technique | .1-1 |

|        | Performance Improvement                            |      |

|        | ABOUT THIS MANUAL                                  |      |

|        | RELATED DOCUMENTATION                              |      |

#### **CHAPTER 2**

| INTEL ARCHITECTURE MMX™ TECHNOLOGY FEATURES  |     |

|----------------------------------------------|-----|

| 2.1. NEW FEATURES                            | 2-1 |

| 2.2. NEW DATA TYPES                          | 2-1 |

| 2.3. MMX™ REGISTERS                          | 2-2 |

| 2.4. EXTENDED INSTRUCTION SET                |     |

| 2.4.1. Packed Data                           | 2-3 |

| 2.4.2. Saturation Arithmetic Vs. Wrap Around | 2-4 |

| 2.4.3. Instruction Group Overview            |     |

| 2.4.3.1. ARITHMETIC INSTRUCTIONS             | 2-5 |

| 2.4.3.2. COMPARISON INSTRUCTIONS             | 2-6 |

| 2.4.3.3. CONVERSION INSTRUCTIONS             | 2-6 |

| 2.4.3.4. LOGICAL INSTRUCTIONS                | 2-6 |

| 2.4.3.5. SHIFT INSTRUCTIONS                  | 2-7 |

| 2.4.3.6. DATA TRANSFER INSTRUCTIONS          |     |

| 2.4.3.7. EMMS (EMPTY MMX™ STATE) INSTRUCTION |     |

| 2.4.4. Instruction Operand                   |     |

| 2.5. COMPATIBILITY                           |     |

|                                              |     |

#### **CHAPTER 3**

#### **APPLICATION PROGRAMMING MODEL**

| 3.1.    | DATA FORMATS                                                                   | 3-1 |

|---------|--------------------------------------------------------------------------------|-----|

| 3.1.1.  | Memory Data Formats                                                            | 3-1 |

| 3.1.2.  | IA MMX <sup>™</sup> Register Data Formats                                      |     |

| 3.1.3.  | IA MMX <sup>™</sup> Instructions and the Floating-Point Tag Word               |     |

| 3.2.    | PREFIXES                                                                       | 3-3 |

| 3.3.    | WRITING APPLICATIONS WITH IA MMX™ CODE                                         |     |

| 3.3.1.  | Detecting IA MMX <sup>™</sup> Technology Existence Using the CPUID Instruction | 3-3 |

| 3.3.2.  | The EMMS Instruction                                                           | 3-4 |

| 3.3.3.  | Interfacing with IA MMX <sup>™</sup> Technology Procedures and Functions       | 3-5 |

| 3.3.4.  | Writing Code with IA MMX <sup>™</sup> and Floating-Point Instructions          | 3-5 |

| 3.3.4.1 |                                                                                |     |

| 3.3.5.  | Multitasking Operating System Environment                                      |     |

| 3.3.5.1 | . COOPERATIVE MULTITASKING OPERATING SYSTEM                                    | 3-7 |

| 3.3.5.2 | PREEMPTIVE MULTITASKING OPERATING SYSTEM                                       |     |

| 3.3.6.  | Exception Handling in IA MMX <sup>™</sup> Application Code                     | 3-8 |

| 3.3.7.  | Register Mapping                                                               |     |

#### CHAPTER 4

#### SYSTEM PROGRAMMING MODEL

| 4.1.    | CONTEXT SWITCHING                                                        | 4-1 |

|---------|--------------------------------------------------------------------------|-----|

| 4.1.1.  | Cooperative Multitasking Operating System                                | 4-1 |

| 4.1.2.  | Preemptive Multitasking Operating System                                 |     |

| 4.2.    | EXCEPTIONS                                                               |     |

| 4.3.    | COMPATIBILITY WITH EXISTING SOFTWARE ENVIRONMENTS                        | 4-4 |

| 4.3.1.  | Register Aliasing                                                        | 4-4 |

| 4.3.2.  | The Effect of Floating-Point and MMX™ Instructions on the Floating-Point |     |

|         | Tag Word                                                                 | 4-7 |

| 4.3.2.1 |                                                                          |     |

| 4.3.3.  | Context Switch Support                                                   | 4-8 |

| 4.3.4.  | Floating-Point Exceptions                                                | 4-8 |

| 4.3.5.  | Debugging                                                                |     |

| 4.3.6.  | Emulation of the Instruction Set                                         | 4-9 |

| 4.3.7.  | Exception handling in Operating Systems                                  |     |

|         |                                                                          |     |

#### **CHAPTER 5**

| INTEL ARCHITECTURE MMX™ INSTRUCTION SET                 |      |

|---------------------------------------------------------|------|

| 5.1. INSTRUCTION SYNTAX                                 |      |

| 5.2. INSTRUCTION FORMAT                                 |      |

| 5.3. NOTATIONAL CONVENTIONS                             | 5-3  |

| 5.4. HOW TO READ THE INSTRUCTION SET PAGES              |      |

| EMMS—Empty MMX State                                    | 5-8  |

| MOVD-Move 32 Bits                                       | 5-10 |

| MOVQ-Move 64 Bits                                       |      |

| PACKSSWB /PACKSSDW—Pack with Signed Saturation          | 5-14 |

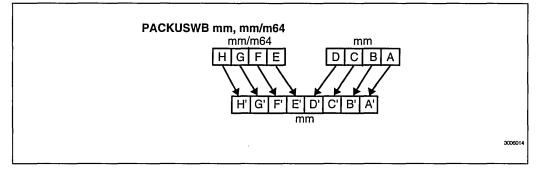

| PACKUSWB—Pack with Unsigned Saturation                  | 5-16 |

| PADDB/PADDW/PADDD—Packed Add                            | 5-18 |

| PADDSB/PADDSW—Packed Add with Saturation                |      |

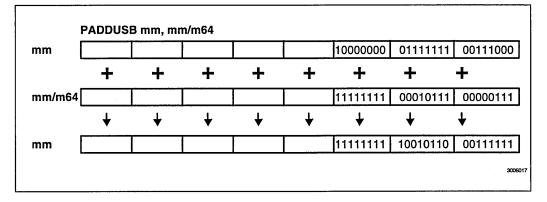

| PADDUSB/PADDUSW—Packed Add Unsigned with Saturation     | 5-23 |

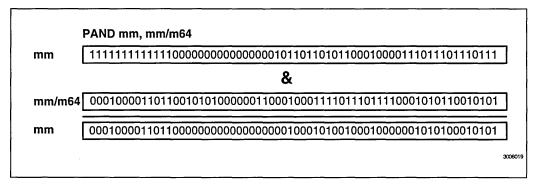

| PAND—Bitwise Logical And                                | 5-26 |

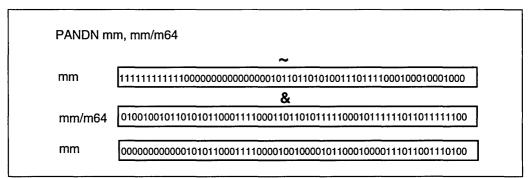

| PANDN—Bitwise Logical And Not                           | 5-28 |

| PCMPEQB/PCMPEQW/PCMPEQD—Packed Compare for Equal        | 5-30 |

| PCMPGTB/PCMPGTW/PCMPGTD—Packed Compare for Greater Than | 5-33 |

| PMADDWD—Packed Multiply and Add                         | 5-36 |

| PMULHW—Packed Multiply High                             | 5-38 |

| PMULLW—Packed Multiply Low                              | 5-40 |

| POR-Bitwise Logical Or                                  | 5-42 |

| PSLLW/PSLLD/PSLLQ—Packed Shift Left Logical             |      |

| PSRAW/PSRAD—Packed Shift Right Arithmetic               |      |

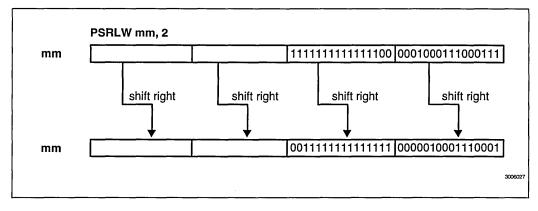

| PSRLW/PSRLD/PSRLQ—Packed Shift Right Logical            | 5-50 |

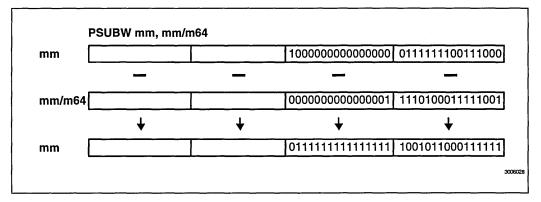

| PSUBB/PSUBW/PSUBD—Packed Subtract                       |      |

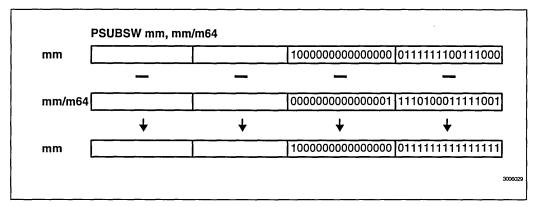

| PSUBSB/PSUBSW—Packed Subtract with Saturation           |      |

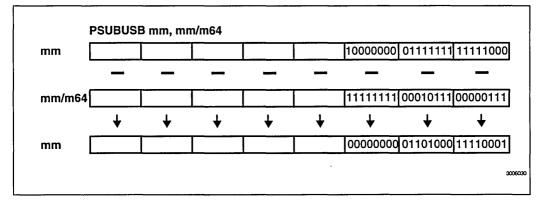

| PSUBUSB/PSUBSW—Packed Subtract Unsigned with Saturation |      |

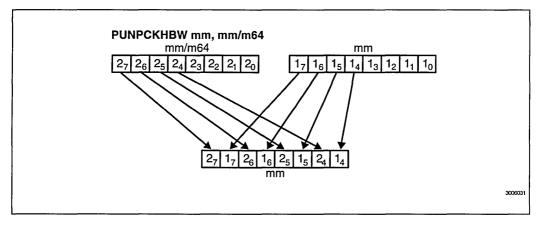

| PUNPCKHBW/PUNPCKHWD/PUNPCKHDQ—Unpack High Packed Data   |      |

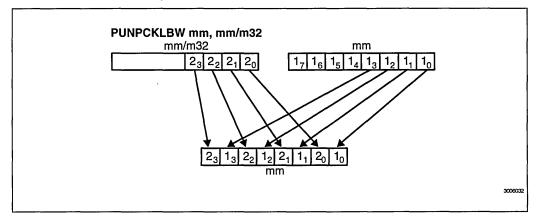

| PUNPCKLBW/PUNPCKLWD/PUNPCKLDQ—Unpack Low Packed Data    |      |

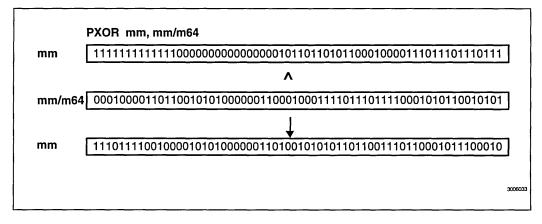

| PXOR—Bitwise Logical Exclusive OR                       | 5-66 |

#### APPENDIX A IA MMX™ INSTRUCTION SET SUMMARY

#### APPENDIX B

IA MMX<sup>™</sup> INSTRUCTION FORMATS AND ENCODINGS

#### **APPENDIX C**

ALPHABETICAL LIST OF IA MMX™ INSTRUCTION SET MNEMONICS

#### **APPENDIX D**

IA MMX<sup>™</sup> INSTRUCTION SET OPCODE MAP

### Figures

| Figure | Title                                                             | Page |

|--------|-------------------------------------------------------------------|------|

| 2-1.   | Packed Data Types                                                 | 2-2  |

| 2-2.   | MMX™ Register Set                                                 |      |

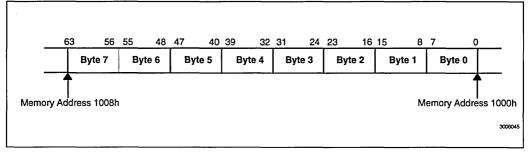

| 3-1.   | Eight Packed Bytes in Memory (at address 1000H)                   |      |

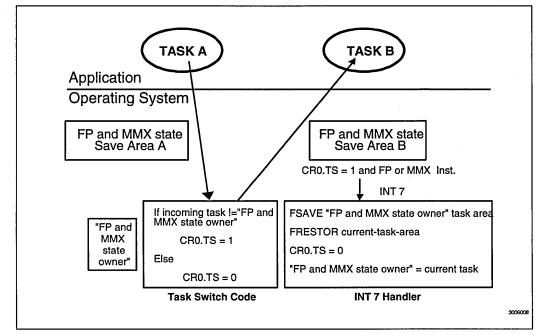

| 4-1.   | Example of FP and MMX State Saving in Operating System            |      |

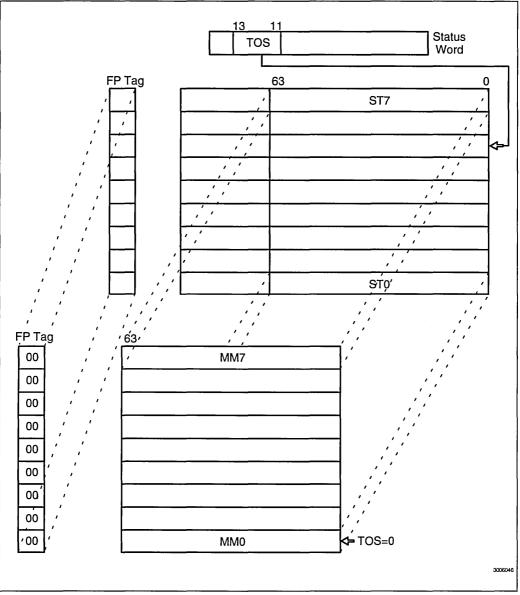

| 4-2.   | Aliasing of MMX™ to Floating-Point Registers                      |      |

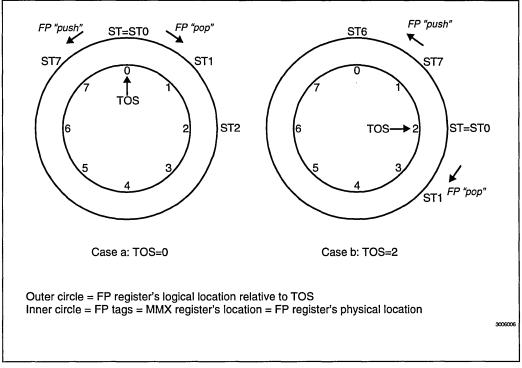

| 4-3.   | Mapping of MMX <sup>™</sup> Registers to Floating Point Registers |      |

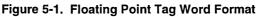

| 5-1.   | Floating Point Tag Word Format                                    |      |

| B-1.   | Key to Codes for Datatype Cross-Reference                         |      |

#### Tables

| Table | Title                                                                               | Page |

|-------|-------------------------------------------------------------------------------------|------|

| 2-1.  | Data Range Limits for Saturation                                                    |      |

| 3-1.  | IA MMX <sup>™</sup> Instruction Behavior with Prefixes Used by Application Programs | 3-3  |

| 4-1.  | Effect of the FP and MMX Instructions on the FP Tag Word                            |      |

| 4-2.  | Effects of MMX™ Instruction on FP State                                             |      |

| A-1.  | IA MMX Instruction Set Summary, Grouped into Functional Categories                  | A-2  |

| B-1.  | Encoding of Granularity of Data (gg) Field                                          |      |

| B-2.  | Encoding of 32-bit General Purpose (reg) Field for Register-to-Register             |      |

|       | Operations                                                                          | B-2  |

| B-3.  | Encoding of 64-bit MMX <sup>™</sup> Register (mmxreg) Field                         |      |

| B-4.  | IA MMX Instruction Formats and Encodings                                            |      |

| C-1.  | IA MMX <sup>™</sup> Instruction Set Mnemonics                                       | C-1  |

| D-1.  | Opcode Map (First Byte is (0FH)                                                     | D-3  |

| D-2.  | Opcodes Determined by Bits 5, 4, 3 of Mod R/M Byte                                  |      |

#### Examples

| Example | Title                                                       | Page |

|---------|-------------------------------------------------------------|------|

| 3-1.    | Partial sequence of IA MMX™ technology detection by CPUID . |      |

| 3-2.    | Floating-point and MMX <sup>™</sup> Code                    |      |

intel

# 1

### Introduction to the Intel Architecture MMX<sup>TM</sup> Technology

#### CHAPTER 1 INTRODUCTION TO THE INTEL ARCHITECTURE MMX™ TECHNOLOGY

#### 1.1. ABOUT THE INTEL ARCHITECTURE MMX™ TECHNOLOGY

The media extensions for the Intel Architecture (IA) were designed to enhance performance of advanced media and communication applications. The MMX<sup>TM</sup> technology provides a new level of performance to computer platforms by adding new instructions and defining new 64-bit data types, while preserving compatibility with software and operating systems developed for the Intel Architecture.

The MMX technology introduces new general-purpose instructions. These instructions operate in parallel on multiple data elements packed into 64-bit quantities. They perform arithmetic and logical operations on the different data types. These instructions accelerate the performance of applications with compute-intensive algorithms that perform localized, recurring operations on small native data. This includes applications such as motion video, combined graphics with video, image processing, audio synthesis, speech synthesis and compression, telephony, video conferencing, 2D graphics, and 3D graphics

The IA MMX instruction set has a simple and flexible software model with no new mode or operating-system visible state. The MMX instruction set is fully compatible with all Intel Architecture microprocessors. All existing software continues to run correctly, without modification, on microprocessors that incorporate the MMX technology, as well as in the presence of existing and new applications that incorporate this technology.

#### 1.1.1. Single Instruction, Multiple Data (SIMD) Technique

The MMX technology uses the Single Instruction, Multiple Data (SIMD) technique. This technique speeds up software performance by processing multiple data elements in parallel, using a single instruction. The MMX technology supports parallel operations on byte, word, and doubleword data elements, and the new quadword (64-bit) integer data type.

#### INTRODUCTION TO THE INTEL ARCHITECTURE MMX™ TECHNOLOGY

intel

#### **1.1.2.** Performance Improvement

Modern media, communications, and graphics applications now include sophisticated algorithms that perform recurring operations on small data types. The MMX technology directly addresses the need of these applications. For example, most audio data is represented in 16-bit (word) quantities. The MMX instructions can operate on four of these words simultaneously with one instruction. Video and graphics information is commonly represented as palletized 8-bit (byte) quantities; one MMX instruction can operate on eight of these bytes simultaneously.

#### 1.2. ABOUT THIS MANUAL

It is assumed that the reader is familiar with the Intel Architecture software model and Assembly language programming.

This manual describes the IA MMX instruction set and introduces the architectural features, instruction set, data types, data formats, application programming model, and system programming model of the MMX technology. It also explains how to use the new instructions to significantly increase the performance of applications.

In this context, architecture refers to the conceptual structure and functional behavior of MMX technology as seen by a programmer, but not the logical organization or performance aspects of the actual implementation.

This manual is organized into five chapters, including this chapter (Chapter 1), and four appendices:

#### Chapter 1—Introduction to the Intel Architecture MMX<sup>™</sup> Technology

**Chapter 2—Intel Architecture MMX<sup>TM</sup> Technology Features:** This chapter provides an overview of the IA MMX technology and its new features.

Chapter 3—Application Programming Model: This chapter describes the software conventions and architecture of the IA MMX technology. It defines the steps for writing MMX code.

Chapter 4—System Programming Model: This chapter discusses interfacing with the operating system and compatibility with Intel Architecture.

**Chapter 5—Intel Architecture MMX<sup>TM</sup> Instruction Set:** This chapter details the instructions, mnemonics, and instruction notations. A full description including graphical representations of the new instructions is presented.

Appendix A—IA MMX<sup>TM</sup> Instruction Set Summary: This appendix summarizes the instructions by functional groups.

## intel architecture MMX™ TECHNOLOGY

Appendix B—IA MMX<sup>TM</sup> Instruction Formats and Encodings: This appendix lists the instruction formats and encodings. It also lists a detailed break-down of the instruction operations and the supported data types.

Appendix C—Alphabetical list of IA MMX<sup>™</sup> Instruction Set Mnemonics: This appendix summarizes operand types, encodings in hexadecimal, and the formats used.

**Appendix D—IA MMX<sup>TM</sup> Instruction Set Opcode Map:** This appendix provides a detailed encoding table of opcode mappings.

#### **1.3. RELATED DOCUMENTATION**

Refer to the following documentation for more information related to Intel Architecture:

Pentium<sup>®</sup> Processor Family Developer's Manual, Volume 3: Architecture and Programming Manual. Intel Corporation, Order Number 240897.

Pentium<sup>®</sup> Pro Processor Developer's Manual, Volumes 2 and 3. Intel Corporation, Order Numbers 242691 and 242692.

Intel Architecture MMX<sup>™</sup> Technology Developers' Manual - Intel Corporation, Order Number 243010.

Refer to Intel's corporate website for the latest information on related documentation:

http://www.intel.com

.

### Intel Architecture MMX<sup>TM</sup> Technology Features

#### CHAPTER 2 INTEL ARCHITECTURE MMX™ TECHNOLOGY FEATURES

This chapter provides a general overview of the architectural features of the Intel Architecture  $MMX^{TM}$  technology.

#### 2.1. NEW FEATURES

MMX technology provides the following new features, while maintaining backward compatibility with all existing Intel Architecture microprocessors, IA applications, and operating systems.

- New data types

- Eight MMX registers

- Enhanced instruction set

The performance of applications which use these new features of MMX technology can be enchanced.

#### 2.2. NEW DATA TYPES

The principal data type of the IA MMX technology is the packed fixed-point integer. The decimal point of the fixed-point values is implicit and is left for the user to control for maximum flexibility.

The IA MMX technology defines the following four new 64-bit data types (See Figure 2-1):

| Packed byte       | Eight bytes packed into one 64-bit quantity     |

|-------------------|-------------------------------------------------|

| Packed word       | Four words packed into one 64-bit quantity      |

| Packed doubleword | Two doublewords packed into one 64-bit quantity |

| Quadword          | One 64-bit quantity                             |

#### INTEL ARCHITECTURE MMX<sup>™</sup> TECHNOLOGY FEATURES

| 63    | 56      | 55                 | 48      | 47       | 40     | 39       | 32 | 31 | 24       | 23   | 16 | 15 | 8 | 7        | 0    |

|-------|---------|--------------------|---------|----------|--------|----------|----|----|----------|------|----|----|---|----------|------|

|       |         |                    |         |          |        |          |    |    |          |      |    |    |   |          |      |

|       |         | _                  |         |          |        |          |    |    |          |      |    |    |   |          |      |

| Packe | d word  | d (4x16            | 6 bits) |          |        |          |    |    |          |      |    |    |   |          |      |

| 63    |         |                    | 48      | 47       |        |          | 32 | 31 |          |      | 16 | 15 |   |          | 0    |

|       |         |                    |         |          |        |          |    |    |          |      |    |    |   |          |      |

|       |         |                    |         |          |        |          |    |    |          |      |    |    |   |          |      |

|       | <u></u> |                    |         |          |        | <u>.</u> |    | -  |          |      |    |    |   |          |      |

|       | <u></u> |                    |         |          |        |          |    |    | <u> </u> | 14   |    |    |   |          |      |

|       | ed dout | blewor             | ds (2x  | 32 bits  | .)     |          |    |    | <u> </u> |      |    |    |   | <u>.</u> |      |

| Packe | ed dout | blewor             | ds (2x  | :32 bits | ;)     |          | 32 | 31 |          | 7.   |    |    |   | -        | 0    |

|       | ed dout | blewor             | ds (2x  | :32 bits | ;)     |          | 32 | 31 |          |      |    |    |   |          |      |

|       | ed dout | blewor             | ds (2x  | :32 bits | )      |          | 32 | 31 |          | ···· |    |    |   |          | 0    |

| 63    |         |                    |         | 32 bits  | »)<br> |          | 32 | 31 |          |      |    |    |   |          |      |

| 63    |         | blewor<br>54 bits) |         | 32 bits  | ;)     |          | 32 | 31 |          |      |    |    |   |          | 0    |

| 63    |         |                    |         | 32 bits  | ;)<br> |          | 32 | 31 |          |      |    |    |   |          | <br> |

int\_\_\_\_

Figure 2-1. Packed Data Types

#### 2.3. MMX<sup>™</sup> REGISTERS

The IA MMX technology provides eight 64-bit, general-purpose registers. These registers are aliased on the floating-point registers. The operating system handles the MMX technology as it would handle floating-point. (See Section 4.3 for more details on register aliasing.)

The MMX registers can hold packed 64-bit data types. The MMX instructions access the MMX registers directly using the register names MM0 to MM7 (See Figure 2-2).

MMX registers can be used to perform calculations on data. They cannot be used to address memory; addressing is accomplished by using the integer registers and standard IA addressing modes.

#### INTEL ARCHITECTURE MMX™ TECHNOLOGY FEATURES

| 63  | <u> </u> |

|-----|----------|

| MM7 |          |

| MM6 |          |

| MM5 |          |

| MM4 |          |

| ММЗ |          |

| MM2 |          |

| MM1 |          |

| ММО |          |

|     |          |

|     | 300604   |

Figure 2-2. MMX<sup>™</sup> Register Set

#### 2.4. EXTENDED INSTRUCTION SET

The IA MMX instruction set supplies a rich set of instructions that operate on all data elements of a packed data type, in parallel. The MMX instructions can operate on either signed or unsigned data elements.

The MMX instructions implement two new principles (discussed in section 2.4.2.):

- Operations on packed data

- Saturation arithmetic

#### 2.4.1. Packed Data

The MMX instructions can operate on groups of eight bytes, four words, and two doublewords. These groups of 64 bits are referred to as packed data. The same 64 bits of data can be treated as any one of the packed data types. Data is cast by the type specified by the instruction.

For example, the PADDB (Add Packed Bytes) instruction adds two groups of eight packed bytes. The PADDW (Add Packed Words) instruction, which adds packed words, could

#### INTEL ARCHITECTURE MMX™ TECHNOLOGY FEATURES

operate on the same 64 bits as the PADDB instruction treating the 64 bits as four 16-bit words.

#### 2.4.2. Saturation Arithmetic and Wrap Around

The MMX technology supports a new arithmetic capability known as saturating arithmetic. Saturation is best defined by contrasting it with wraparound mode.

In wraparound mode, results that overflow or underflow are truncated and only the lower (least significant) bits of the result are returned. That is, the carry is ignored.

In saturation mode, results of an operation that overflow or underflow are clipped (saturated) to a data-range limit for the data type (see Table 2-1). The result of an operation that exceeds the range of a data-type saturates to the maximum value of the range. A result that is less than the range of a data type saturates to the minimum value of the range. This is useful in many cases, such as color calculations.

For example, when the result exceeds the data range limit for signed bytes, it is saturated to 0x7F (0xFF for unsigned bytes). If a value is less than the data range limit, it is saturated to 0x80 for signed bytes (0x00 for unsigned bytes).

Saturation provides a useful feature of avoiding wraparound artifacts. In the example of color calculations, saturation causes a color to remain pure black or pure white without allowing for an inversion.

|          | Lower       | Limit   | Upper Limit |         |

|----------|-------------|---------|-------------|---------|

| Signed   | Hexadecimal | Decimal | Hexadecimal | Decimal |

| Byte     | 80H         | -128    | 7FH         | 127     |

| Word     | 8000H       | -32,768 | 7FFFH       | 32,767  |

| Unsigned |             |         |             |         |

| Byte     | 00H         | 0       | FFH         | 255     |

| Word     | 0000H       | 0       | FFFFH       | 65,535  |

| Table 2-1. Data R | Range Limits | for Saturation |

|-------------------|--------------|----------------|

|-------------------|--------------|----------------|

MMX instructions do not indicate overflow or underflow occurrence by generating exceptions or setting flags.

#### INTEL ARCHITECTURE MMX™ TECHNOLOGY FEATURES

#### 2.4.3. Instruction Group Overview

This section provides an overview of the MMX instruction groups. See Chapter 5 for detailed information on the instructions, including information on encoding, operation, and exceptions.

The fifty-seven new MMX instructions are grouped into these categories:

- Arithmetic Instructions

- Comparison Instructions

- Conversion Instructions

- Logical Instructions

- Shift Instructions

- Data Transfer Instructions

- Empty MMX State (EMMS) Instruction

#### 2.4.3.1. ARITHMETIC INSTRUCTIONS

#### **Packed Addition and Subtraction**

The PADD (Packed Add) and PSUB (Packed Subtract) instructions add or subtract the signed or unsigned data elements of the source operand to or from the destination operand in wraparound mode. These instructions support packed byte, packed word, and packed doubleword data types.

The PADDS (Packed Add with Saturation) and PSUBS (Packed Subtract with Saturation) instructions add or subtract the signed data elements of the source operand to or from the signed data elements of the destination operand and saturate the result to the limits of the signed data-type range. These instructions support packed byte and packed word data types.

The PADDUS (Packed Add Unsigned with Saturation) and PSUBUS (Packed Subtract Unsigned with Saturation) instructions add or subtract the unsigned data elements of the source operand to or from the unsigned data elements of the destination operand and saturate the result to the limits of the unsigned data-type range. These instructions support packed byte and packed word data types.

#### **Packed Multiplication**

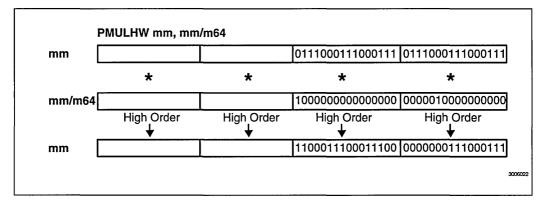

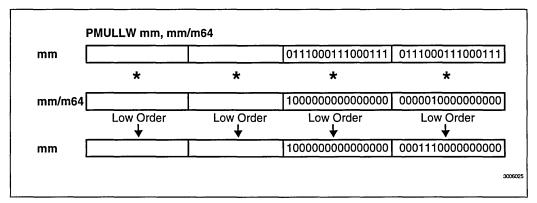

Packed multiplication instructions perform four multiplications on pairs of signed 16-bit operands, producing 32-bit intermediate results. Users may choose the low-order or high-order parts of each 32-bit result.

#### INTEL ARCHITECTURE MMX<sup>TM</sup> TECHNOLOGY FEATURES

The PMULHW (Packed Multiply High) and PMULLW (Packed Multiply Low) instructions multiply the signed words of the source and destination operands and write the high-order or low-order 16 bits of each of the results to the destination operand.

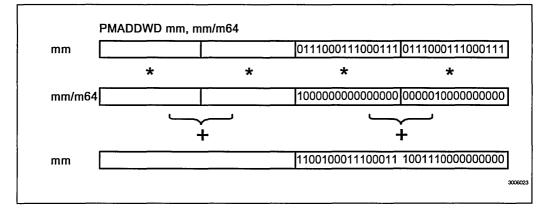

#### Packed Multiply Add

The PMADDWD (Packed Multiply and Add) instruction calculates the products of the signed words of the source and destination operands. The four intermediate 32-bit doubleword products are summed in pairs to produce two 32-bit doubleword results.

#### 2.4.3.2. COMPARISON INSTRUCTIONS

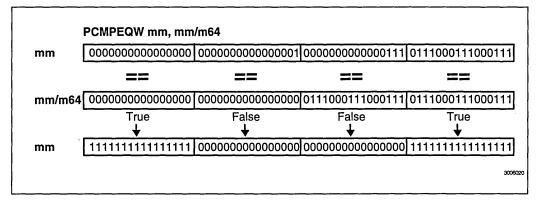

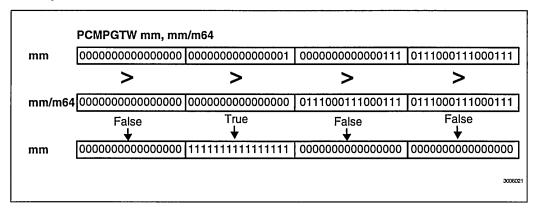

The PCMPEQ (Packed Compare for Equal) and PCMPGT (Packed Compare for Greater Than) instructions compare the corresponding data elements in the source and destination operands for equality or value greater than, respectively. These instructions generate a mask of ones or zeros which are written to the destination operand. Logical operations can use the mask to select elements. This can be used to implement a packed conditional move operation without a branch or a set of branch instructions. No flags are set.

These instructions support packed byte, packed word and packed doubleword data types.

#### 2.4.3.3. CONVERSION INSTRUCTIONS

#### **Pack and Unpack**

The Pack and Unpack instructions perform conversions between the packed data types.

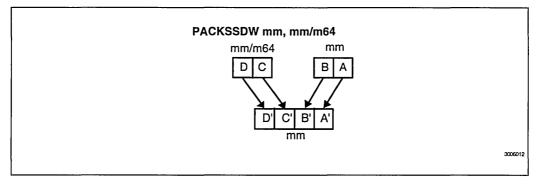

The PACKSS (Packed with Signed Saturation) instruction converts signed words into signed bytes or signed doublewords into signed words, in signed saturation mode.

The PACKUS (Packed with Unsigned Saturation) instruction converts signed words into unsigned bytes, in unsigned saturation mode.

The PUNPCKH (Unpack High Packed Data) and PUNPCKL (Unpack Low Packed Data) instructions convert bytes to words, words to doublewords, or doublewords to quadwords.

#### 2.4.3.4. LOGICAL INSTRUCTIONS

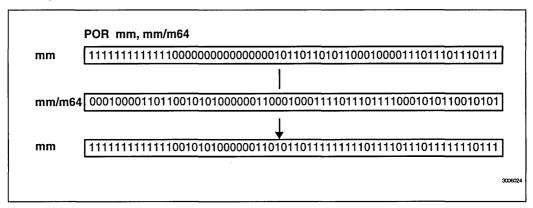

The PAND (Bitwise Logical And), PANDN (Bitwise Logical And Not), POR (Bitwise Logical OR), and PXOR (Bitwise Logical Exclusive OR) instructions perform bitwise logical operations on 64-bit quantities.

#### INTEL ARCHITECTURE MMX™ TECHNOLOGY FEATURES

#### 2.4.3.5. SHIFT INSTRUCTIONS

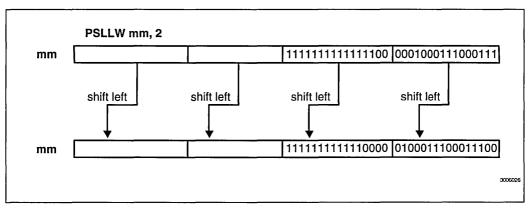

The logical shift left, logical shift right and arithmetic shift right instructions shift each element by a specified number of bits. The logical left and right shifts also enable a 64-bit quantity (quadword) to be shifted as one block, assisting in data type conversions and alignment operations.

The PSLL (Packed Shift Left Logical) and PSRL (Packed Shift Right Logical) instructions perform a logical left or right shift, and fill the empty high or low order bit positions with zeros. These instructions support packed word, packed doubleword, and quadword data types.

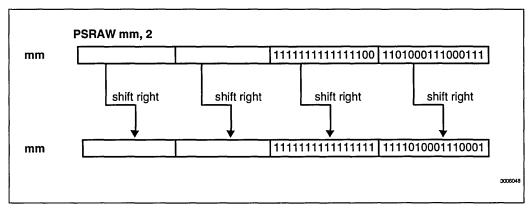

The PSRA (Packed Shift Right Arithmetic) instruction performs an arithmetic right shift, copying the sign bit into empty bit positions on the upper end of the operand. This instruction supports packed word and packed doubleword data types.

#### 2.4.3.6. DATA TRANSFER INSTRUCTIONS

The MOVD (Move 32 Bits) instruction transfers 32 bits of packed data from memory to MMX registers and visa versa, or from integer registers to MMX registers and visa versa.

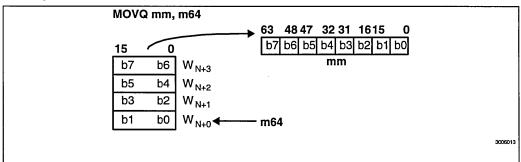

The MOVQ (Move 64 Bits) instruction transfers 64-bits of packed data from memory to MMX registers and vise versa, or transfers data between MMX registers.

#### 2.4.3.7. EMMS (EMPTY MMX<sup>™</sup> STATE) INSTRUCTION

The EMMS instruction empties the MMX state. This instruction must be used to clear the IA MMX state (empty the floating-point tag word) at the end of an MMX routine before calling other routines that can execute floating-point instructions.

#### 2.4.4. Instruction Operand

All MMX instructions, except the EMMS instruction, reference and operate on two operands: the source and destination operands. The right operand is the source and the left operand is the destination. The destination operand may also be a second source operand for the operation. The instruction overwrites the destination operand with the result.

For example, a two-operand instruction would be decoded as:

DEST(left operand) ← DEST (left operand) OP SRC (right operand)

The source operand for all the MMX instructions (except the data transfer instructions), can reside either in memory or in an MMX register. The destination operand resides in an MMX register.

#### INTEL ARCHITECTURE MMX™ TECHNOLOGY FEATURES

For data transfer instructions, the source and destination operands can also be an integer register (for the MOVD instruction) or memory location (for both the MOVD and MOVQ instructions).

#### 2.5. COMPATIBILITY

The IA MMX state is aliased upon the IA floating-point state. No new state or mode is added to support the MMX technology. The same floating-point instructions that save and restore the floating-point state also handle the IA MMX state (for example, during context switching).

MMX technology uses the same interface techniques between the floating-point architecture and the operating system (primarily for task switching purposes). For more detail, see Section 4.1.

3

### **Application Programming Model**

#### CHAPTER 3 APPLICATION PROGRAMMING MODEL

This chapter describes the application programming environment as seen by compiler writers and assembly-language programmers. It also describes the architectural features which directly affect applications.

#### 3.1. DATA FORMATS

#### 3.1.1. Memory Data Formats

The Intel Architecture MMX<sup>™</sup> technology introduces new packed data types, each 64 bits long. The data elements can be:

- eight packed, consecutive 8-bit bytes

- four packed, consecutive 16-bit words

- two packed, consecutive 32-bit doublewords

The 64 bits are numbered 0 through 63. Bit 0 is the least significant bit (LSB), and bit 63 is the most significant bit (MSB).

The low-order bits are the lower part of the data element and the high-order bits are the upper part of the data element. For example, a word contains 16 bits numbered 0 through 15, the byte containing bits 0-7 of the word is called the low byte, and the byte containing bits 8-15 is called the high byte.

Bytes in a multi-byte format have consecutive memory addresses. The ordering is always little endian. That is, the bytes with the lower addresses are less significant than the bytes with the higher addresses.

Figure 3-1. Eight Packed Bytes in Memory (at address 1000H)

#### 3.1.2. IA MMX<sup>™</sup> Register Data Formats

Values in IA MMX registers have the same format as a 64-bit quantity in memory. MMX registers have two data access modes: 64-bit access mode and 32-bit access mode.

The 64-bit access mode is used for 64-bit memory access, 64-bit transfer between MMX registers, all pack, logical and arithmetic instructions, and some unpack instructions.

The 32-bit access mode is used for 32-bit memory access, 32-bit transfer between integer registers and MMX registers, and some unpack instructions.

#### 3.1.3. IA MMX<sup>™</sup> Instructions and the Floating-Point Tag Word

After each MMX instruction, the entire floating-point tag word is set to Valid (00s). The Empty MMX State (EMMS) instruction sets the entire floating-point tag word to Empty (11s).

Section 4.3.2. describes the effects of floating-point and MMX instructions on the floating-point tag word. For details on floating-point tag word, refer to the *Pentium® Processor Family Developer's Manual*, Volume 3, Section 6.2.1.4.

**APPLICATION PROGRAMMING MODEL**

#### 3.2. PREFIXES

Table 3-1 details the effect of a prefix on IA MMX instructions.

| Prefix Type        | The Effect of Prefix on IA MMX <sup>™</sup> Instructions |

|--------------------|----------------------------------------------------------|

| Address size (67H) | Affects IA MMX instructions with a memory operand.       |

|                    | Ignored by IA MMX instructions without a memory operand. |

| Operand size (66H) | Ignored.                                                 |

| Segment override   | Affects IA MMX instructions with a memory operand.       |

|                    | Ignored by IA MMX instructions without a memory operand. |

| Repeat             | Ignored.                                                 |

| Lock (F0H)         | Generates an invalid opcode exception.                   |

#### Table 3-1. IA MMX<sup>™</sup> Instruction Behavior with Prefixes Used by Application Programs

See the *Pentium<sup>®</sup> Processor Family Developer's Manual*, Volume 3, Section 3.4. for information related to prefixes.

#### 3.3. WRITING APPLICATIONS WITH IA MMX™ CODE

### 3.3.1. Detecting IA MMX<sup>™</sup> Technology Existence Using the CPUID Instruction

Use the CPUID instruction to determine whether the processor supports the IA MMX instruction set (refer to the *Pentium® Processor Family Developer's Manual*, Volume 3, Chapter 25, for more detail on the CPUID instruction). When the IA MMX technology support is detected by the CPUID instruction, it is signaled by setting bit 23 (IA MMX technology bit) in the feature flags to 1. In general, two versions of the routine can be created: one with scalar instructions and one with MMX instructions. The application will call the appropriate routine depending on the results of the CPUID instruction. If MMX technology support is detected, then the MMX routine is called; if no support for the MMX technology exists, the application calls the scalar routine.

#### NOTE

The CPUID instruction will continue to report the existence of the IA MMX technology if the CR0.EM bit is set (which signifies that the CPU is configured to generate exception Int 7 that can be used to emulate floating

point instructions). In this case, executing an MMX instruction results in an invalid opcode exception.

Example 3-1 illustrates how to use the CPUID instruction. This example does not represent the entire CPUID sequence, but shows the portion used for IA MMX technology detection.

#### Example 3-1. Partial sequence of IA MMX™ technology detection by CPUID

|                  |                                   | ; identify existence of CPUID instruction                                 |

|------------------|-----------------------------------|---------------------------------------------------------------------------|

| ····<br>···      |                                   | ; identify Intel processor                                                |

| <br>mov<br>CPUID | EAX, 1                            | ; request for feature flags<br>: 0Fh. 0A2h CPUID instruction              |

| test<br>jnz      | EDX, 00800000h<br>MMX_Technology_ | ; Is IA MMX technology bit (Bit 23 of EDX) in feature flags set?<br>Found |

#### 3.3.2. The EMMS Instruction

When integrating the MMX routine into an application running under an existing operating system (OS), programmers need to take special precautions, similar to those when writing floating-point (FP) code.

When an MMX instruction executes, the floating-point tag word is marked valid (00s). Subsequent floating-point instructions that will be executed may produce unexpected results because the floating-point stack seems to contain valid data. The EMMS instruction marks the floating-point tag word as empty. Therefore, it is imperative to use the EMMS instruction at the end of every MMX routine.

The EMMS instruction must be used in each of the following cases:

- Application utilizing FP instructions calls an MMX technology library/DLL

- Application utilizing MMX instructions calls a FP library/DLL

- Switch between MMX code in a task/thread and other tasks/threads in cooperative operating systems.

If the EMMS instruction is not used when trying to execute a floating-point instruction, the following may occur:

• Depending on the exception mask bits of the floating-point control word, a floatingpoint exception event may be generated.

#### **APPLICATION PROGRAMMING MODEL**

- A "soft exception" may occur. In this case floating-point code continues to execute, but generates incorrect results. This happens when the floating-point exceptions are masked and no visible exceptions occur. The internal exception handler (microcode, not user visible) loads a NaN (Not a Number) with an exponent of 11..11B onto the floating-point stack. The NaN is used for further calculations, yielding incorrect results.

- A potential error may occur only if the operating system does NOT manage floatingpoint context across task switches. These operating systems are usually cooperative operating systems. It is imperative that the EMMS instruction execute at the end of all the MMX routines that may enable a task switch immediately after they end execution (explicit yield API or implicit yield API).

#### 3.3.3. Interfacing with IA MMX<sup>™</sup> Technology Procedures and Functions

The MMX technology enables direct access to all the MMX registers. This means that all existing interface conventions that apply to the use of other general registers such as EAX, EBX will also apply to the MMX register usage.

An efficient interface might pass parameters and return values via the pre-defined MMX registers, or a combination of memory locations (via the stack) and MMX registers. This interface would have to be written in assembly language since passing parameters through MMX registers is not currently supported by any existing C compilers. Do not use the EMMS instruction when the interface to the MMX code has been defined to retain values in the MMX register.

If a high-level language, such as C, is used, the data types could be defined as a 64-bit structure with packed data types.

When implementing usage of IA MMX instructions in high level languages other approaches can be taken, such as:

- Passing MMX type parameters to a procedure by passing a pointer to a structure via the integer stack.

- Returning a value from a function by returning the pointer to a structure.

### 3.3.4. Writing Code with IA MMX<sup>™</sup> and Floating-Point Instructions

The MMX technology aliases the MMX registers on the floating-point registers. The main reason for this is to enable MMX technology to be fully compatible and transparent to

existing software environments (operating systems and applications). This way operating systems will be able to include new applications and drivers that use the IA MMX technology.

An application can contain both floating-point and MMX code. However, the user is discouraged from causing frequent transitions between MMX and floating-point instructions by mixing MMX code and floating-point code.

#### 3.3.4.1. RECOMMENDATIONS AND GUIDELINES

Do not mix MMX code and floating-point code at the instruction level for the following reasons:

- The TOS (top of stack) value of the floating-point status word is set to 0 after each MMX instruction. This means that the floating-point code loses its pointer to its floating-point registers if the code mixes MMX instructions within a floating-point routine.

- An MMX instruction write to an MMX 64-bit register writes ones (11s) to the exponent part of the corresponding floating-point register.

- Floating-point code that uses register contents that were generated by the MMX instructions may cause floating-point exceptions or incorrect results. These floating-point exceptions are related to undefined floating-point values and floating-point stack usage.

- All MMX instructions (except EMMS) set the entire tag word to the valid state (00s in all tag fields) without preserving the previous floating-point state.

- Frequent transitions between the MMX and floating-point instructions may result in significant performance degradation in some implementations.

If the application contains floating-point and MMX instructions, follow these guidelines:

- Partition the MMX technology module and the floating-point module into separate instruction streams (separate loops or subroutines) so that they contain only instructions of one type.

- Do not rely on register contents across transitions.

- When the MMX state is not required, empty the MMX state using the EMMS instruction.

- Exit the floating-point code section with an empty stack.

intel

Example 3-2. Floating-point and MMX<sup>™</sup> Code

| FP_code:   |          |                                   |

|------------|----------|-----------------------------------|

| MMX_code:  | ••       | (*leave the FP stack empty*)      |

| FP_code 1: | <br>EMMS | (*mark the FP tag word as empty*) |

|            | <br>     | (*leave the FP stack empty*)      |

#### 3.3.5. Multitasking Operating System Environment

An application needs to identify the nature of the multitasking operating system on which it runs. Each task retains its own state which must be saved when a task switch occurs. The processor state (context) consists of the integer registers and floating-point and MMX registers.

Operating systems can be classified into two types:

- Cooperative multitasking operating system

- Preemptive multitasking operating system

The behavior of the two operating system types in context switching is described in Section 4.1.1.

#### 3.3.5.1. COOPERATIVE MULTITASKING OPERATING SYSTEM

Cooperative multitasking operating systems do not save the FP or MMX state when performing a context switch. Therefore, the application needs to save the relevant state before relinquishing direct or indirect control to the operating system.

#### 3.3.5.2. PREEMPTIVE MULTITASKING OPERATING SYSTEM

Preemptive multitasking operating systems are responsible for saving and restoring the FP and MMX state when performing a context switch. Therefore, the application does not have to save or restore the FP and MMX state.

#### 3.3.6. Exception Handling in IA MMX<sup>™</sup> Application Code

MMX instructions generate the same type of memory-access exceptions as other Intel Architecture instructions. Some examples are: page fault, segment not present, and limit violations. Existing exception handlers can handle these types of exceptions. They do not have to be modified.

Unless there is a pending floating-point exception, MMX instructions do not generate numeric exceptions. Therefore, there is no need to modify existing exception handlers or add new ones.

If a floating-point exception is pending, the subsequent MMX instruction generates a numeric error exception (Int 16 and/or FERR#). The MMX instruction resumes execution upon return from the exception handler.

#### 3.3.7. Register Mapping

The IA MMX registers and their tags are mapped to physical locations of the floating-point registers and their tags. Register aliasing and mapping is described in more detail in Section 4.3.1.

intel

### System Programming Model

.

## CHAPTER 4 SYSTEM PROGRAMMING MODEL

This chapter presents the interface of the Intel Architecture  $MMX^{TM}$  technology to the operating system.

## 4.1. CONTEXT SWITCHING

This section describes the behavior of operating systems during context switching.

Different operating systems take different approaches for state-saving:

- Some operating systems save the entire floating-point state.

- Some save the floating-point state only when it is required.

- Some may save a partial floating-point state.

The existing task switch code for IA implementations (including floating-point code) does not change for systems that include MMX code.

## 4.1.1. Cooperative Multitasking Operating System

In a cooperative operating system, application tasks can predetermine when it is about to be switched out. Tasks can prepare in advance for the switch.

Application programmers must know whether the operating system performs a state save or whether it is their responsibility to perform a state save.

## 4.1.2. Preemptive Multitasking Operating System

In a preemptive multitasking operating system, the application cannot know when it is preempted. Applications cannot prepare in advance for task switching. The operating system is responsible for saving and restoring the state when necessary.

The IA MMX technology was defined to support the same state-saving and restoring techniques as the floating-point state-saving and restoring techniques. Existing operating systems can continue to run without modifications.

### SYSTEM PROGRAMMING MODEL

Figure 4-1 illustrates an example of an operating system implementing floating-point or MMX state saving.

Detecting when to save the FP or MMX state needs to be saved is the same process used for detecting when the floating-point state needs to be saved. If CR0.TS=1 (task switch bit in control register 0), then the next FP or MMX instruction generates exception Int 7.

- 1. The operating system maintains a *save area* for each task (Save Areas A and B in Figure 4-1).

- 2. It defines a variable that indicates which task "owns" the FP or MMX state.

- 3. On a task switch, the OS sets the CR0.TS to 1 if the incoming task does not own the FP or MMX state. Otherwise, it sets it to 0.

- 4. If a new task attempts to use an MMX instruction, (while CR0.TS=1), exception Int 7 is generated. The Int 7 handler ("owned" by the operating system) saves the FP or MMX state to the save area of the FP or MMX state owner and restores the FP or MMX state from the save area of the current task.

5. The ownership of the FP or MMX state then changes to the current task and CR0.TS=0.

Figure 4-1. Example of FP and MMX State Saving in Operating System

### SYSTEM PROGRAMMING MODEL

## 4.2. EXCEPTIONS

MMX instructions do not generate numeric exceptions or affect the processor architecture status flags. Previously pending floating-point numeric errors are reported.

The MMX instructions can generate the following exceptions:

• Memory access exceptions:

#SS Interrupt 12 - Stack exception

#GP Interrupt 13 - General Protection

#PF Interrupt 14 - Page Fault

#AC Interrupt 17 - Alignment Check, if enabled by CPU configuration.

• System exceptions:

#UD Interrupt 6 - Invalid Opcode

Executing an MMX instruction when CR0.EM=1 generates an Invalid Opcode exception.

#NM Interrupt 7 - Device not available. The TS bit in CR0 is set.

• Pending floating-point error:

#MF Interrupt 16 - Pending floating-point error

• Other exceptions that occur indirectly due to faulty execution of the above exceptions. For example: Interrupt 12 occurs due to MMX instructions, and the interrupt gate directs the processor to invalid TSS (task state segment).

The MMX instructions are accessible from all operation modes of IA: Protected mode, Real address mode, and Virtual 8086 mode.

## 4.3. COMPATIBILITY WITH EXISTING SOFTWARE ENVIRONMENTS

## 4.3.1. Register Aliasing

The MMX state is aliased on the floating-point state:

- MMX registers MM0-MM7 are aliased on the 64-bit mantissas of the floating-point register (See Figure 4-2).

- A value written to an MMX register using MMX instructions also appears in one of the eight floating-point registers (bits 63-0). The exponent field of the corresponding floating-point register (bits 78-64) and its sign bit (bit 79) are set to ones (11s).

- The mantissa of a floating-point value written to a floating-point register by floating-point instructions also appears in an MMX register.

## SYSTEM PROGRAMMING MODEL

Figure 4-2. Aliasing of MMX<sup>™</sup> to Floating-Point Registers

### SYSTEM PROGRAMMING MODEL

MMX registers map to the physical locations of floating-point registers. MMX register mapping is fixed and does not change when the TOS (Top Of Stack field in the floating-point status word, bits 11-13) changes.

The value of the TOS is set to 0 after each MMX instruction.

In the floating-point context, STn refers to the relative location of a FP register, n, to the TOS. However, the FP tag bits refer to the physical locations of the FP register. The MMX registers always refer to the physical location.

In Figure 4-3, the inner circle refers to the physical location of the FP and MMX registers. The outer circle refers to FP register's relative location to the current TOS.

When the TOS=0 (case a in Figure 4-3), ST0 points to the physical location 0 on the floating-point stack. MM0 maps to ST0, MM1 maps to ST1, and so on.

When the TOS=2 (case b in Figure 4-3), ST0 points to the physical location 2. MM0 maps to ST6, MM1 maps to ST7, MM2 maps to ST0, and so on.

Figure 4-3. Mapping of MMX<sup>™</sup> Registers to Floating Point Registers

## 4.3.2. The Effect of Floating-Point and MMX<sup>™</sup> Instructions on the Floating-Point Tag Word

Using an MMX instruction (except EMMS) validates (sets to 00s) the entire floating-point tag word.

The EMMS instruction sets the entire FP tag bits register to empty (11s in each tag field).

FSAVE and FSTENV instructions read the FP tag word and store the contents of the FP tag word in memory. Executing these instructions calculates the precise values of the FP tag word fields based on the current contents of the registers. After executing these instructions, all tag bit values are valid for MMX instructions: Valid, Zero, Special, Empty. The value of the FP tag word does not affect the MMX registers or execution of MMX instructions.

Table 4-1 summarizes the effect of FP or MMX instructions and FSAVE/ FSTENV instructions on the tag bit fields in an FP or MMX register and defines their value in memory.

| Instruction Type | Instruction                    | Tag Bits                                                   | Calculated FP Tag<br>Word in Memory After<br>FSAVE/FSTENV |

|------------------|--------------------------------|------------------------------------------------------------|-----------------------------------------------------------|

| MMX™             | All (except EMMS)              | All registers' tags are set to zeros (00).                 | 00, 01, 10                                                |

| MMX              | EMMS                           | All registers' tags are set to ones (11).                  | 11                                                        |

| FP               | All (except FRSTOR,<br>FLDENV) | Individual register tag is set to 00 or 11.                | Each register's tags are set to 00, 11, 01 or 10.         |

| FP               | FRSTOR, FLDENV                 | All registers' tags are<br>set to 00 or 11 or 01 or<br>10. | Each register's tags are set to 00, 11, 01 or 10.         |

| Table 4-1. Effect o | of the FP and M | MMX Instructions | on the FP | <b>Tag Word</b> |

|---------------------|-----------------|------------------|-----------|-----------------|

|---------------------|-----------------|------------------|-----------|-----------------|

#### SYSTEM PROGRAMMING MODEL

#### 4.3.2.1. ALIASING SUMMARY

Table 4-2 summarizes the effects of the MMX instructions on the floating-point state.

| Instruction<br>Type                             | FP Tag Word                     | TOS<br>(SW <sub>1311</sub> ) | Other FP<br>Environment<br>(CW, Data Ptr,<br>Code Ptr, Other<br>Fields) | Exponent Bits +<br>Signed Bit of<br>MMn (7964) | Mantissa Part<br>of MMn ( <sub>6300</sub> ) |

|-------------------------------------------------|---------------------------------|------------------------------|-------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------|

| MMX register<br>read from MMX<br>register (MMn) | All fields set to<br>00 (Valid) | 000                          | Unchanged                                                               | Unchanged                                      | Unchanged                                   |

| MMX register<br>write to MMX<br>register (MMn)  | All fields set to<br>00 (Valid) | 000                          | Unchanged                                                               | Set to ones (11)                               | Overwritten                                 |

| EMMS                                            | All fields set to<br>11 (Empty) | 000                          | Unchanged                                                               | Unchanged                                      | Unchanged                                   |

Note: MMn refers to one MMX register.

## 4.3.3. Context Switch Support

If the task switch bit (TS) in control register 0 (CR0) is set (CR0.TS=1), the first FP or MMX instruction that executes will trigger Int 7, Device not available (DNA). Causing a DNA fault enables an operating system to save the context of the FP or MMX registers with the same code currently used to save the FP state. Both the FSAVE (Store FP state) and FRSTOR (Restore FP state) instructions are used to save and restore either the FP or MMX state.

See Section 4.1. for more details on context switching.

## 4.3.4. Floating-Point Exceptions

When floating-point exceptions are enabled and a FP exception is pending, subsequent MMX instruction execution reports an FP error (Int 16 and/or FERR# signal). The pending exception is handled by the FP exception handler. Execution resumes at the interrupted MMX instruction.

Before the MMX instruction is executed, the FP state is maintained and is visible to the FP exception handler.

See Section 3.3.6 for more detail.

### SYSTEM PROGRAMMING MODEL

## 4.3.5. Debugging

The debug features for Intel Architecture implementations operate in the same manner on the MMX instruction set. This enables debuggers to debug code that uses the MMX technology.

## 4.3.6. Emulation of the Instruction Set

There is no emulation support for microprocessors that support the MMX technology.

The CR0.EM bit used to emulate floating-point instructions cannot be used in the same way for MMX instruction emulation. If an MMX instruction executes when the CR0.EM bit is set, an invalid opcode exception (Int 6) is generated.

## 4.3.7. Exception handling in Operating Systems

This section specifies system exceptions. Exception handling in MMX code is discussed in Section 3.3.6.

An invalid opcode exception (Int 6) can occur due to MMX instruction execution two cases:

- On implementations that do not support IA MMX technology.

- When CR0.EM=1 and an MMX instruction is executed.

The CR0.EM bit is used to emulate the FP instructions in software. In this case, the operating system does not save the FP hardware state on task switches and does not save the MMX state. An invalid opcode exception is generated to flag this event to the operating system, and prevent application errors from occurring.

. . . . .

5

## Intel Architecture MMX<sup>TM</sup> Instruction Set

## CHAPTER 5 INTEL ARCHITECTURE MMX™ INSTRUCTION SET

This chapter presents the Intel Architecture MMX<sup>™</sup> instructions in alphabetical order, with a full description of each instruction.

The IA MMX technology defines fifty-seven new instructions. The instructions are grouped into the following functional categories:

- Arithmetic Instructions

- Comparison Instructions

- Conversion Instructions

- Logical Instructions

- Shift Instructions

- Data Transfer Instructions

- Empty MMX State (EMMS) Instruction

Appendix A summarizes the MMX instructions grouped by categories of related functions. Appendix B provides instruction formats and encodings, and Appendix C provides an alphabetical list of instruction mnemonics, their source data types, encodings in hexadecimal, and format. Appendix D provides an Opcode Map of the MMX instructions.

Many of the instructions have multiple variations depending on the data types they support. Each variation has a different suffix. For example the PADD instruction has three variations: PADDB, PADDW, and PADDD, where the letters B, W, and D represent byte, word, and doubleword.

## 5.1. INSTRUCTION SYNTAX

Instructions vary by:

- Data type: packed bytes, packed words, packed doublewords or quadwords

- Signed Unsigned numbers

- Wraparound Saturate arithmetic

intel

A typical MMX instruction has this syntax:

- Prefix: **P** for Packed

- Instruction operation: for example ADD, CMP, or XOR

- Suffix:

- US for Unsigned Saturation

- S for Signed saturation

- B, W, D, Q for the data type: packed byte, packed word, packed doubleword, or quadword.

Instructions that have different input and output data elements have two data-type suffixes. For example, the conversion instruction converts from one data type to another. It has two suffixes: one for the original data type and the second for the converted data type.

This is an example of an instruction mnemonic syntax :

#### PADDUSW (Packed Add Unsigned with Saturation for Word)

| Р   | = | Packed                    |

|-----|---|---------------------------|

| ADD | = | the instruction operation |

| US  | = | Unsigned Saturation       |

| W   | = | Word                      |

## 5.2. INSTRUCTION FORMAT

The IA MMX instructions use the existing IA instruction format. All instructions, except the EMMS instruction, use the ModR/M format. All are preceded by the 0F prefix byte. For more details about the ModR/M format refer to *Pentium® Processor Family Developer's Manual Volume 3*, Section 25.2.1.

For data-transfer instructions, the destination and source operands can reside in memory, integer registers, or MMX registers. For all other IA MMX instructions, the destination operands reside in MMX registers, and the source operands reside in memory, MMX registers, or immediate operands.

All existing address modes are supported using the SIB (Scale Index Base) format.

## 5.3. NOTATIONAL CONVENTIONS

The following conventions apply to all MMX instructions (except the EMMS instruction):

- The instructions reference and operate on two operands: the source and destination operands. The right operand is the source and the left operand is the destination. The destination operand may also supply one of the inputs for the operation. The instruction overwrites the destination operand with the result.

- When one of the operands is a memory location, the linear address corresponds to the address of the least significant byte of the referenced memory data.

- The MMX instructions do not affect the condition flags.

## 5.4. HOW TO READ THE INSTRUCTION SET PAGES

The following is an example of the format used for each MMX instruction description in this chapter:

## PSLL—Packed Shift Left Logical

| Opcode   | Instruction      | Description                                                                                                           |

|----------|------------------|-----------------------------------------------------------------------------------------------------------------------|

| 0F F1 /r | PSLLW mm, mm/m64 | Shift all words in MMX register to left by an amount<br>specified in MMX register/memory, while shifting in<br>zeros. |

The above table gives the instruction mnemonic and a brief description of the mnemonic. The columns content are explained below.

## **Opcode Column**

The "Opcode" column provides the complete opcode produced for each form of the instruction.

The codes are defined as hexadecimal bytes, in the same order in which they appear in memory. Definitions of entries other than hexadecimal bytes are as follows:

- /digit: (digit is between 0 and 7) indicates that the ModR/M byte of the instruction uses only the r/m (register or memory) operand. The reg field contains the digit that provides a technology to the instruction's opcode.

- /r: indicates that the ModR/M byte of the instruction contains both a register operand and an r/m operand.

- **ib**: a 1-byte, immediate operand to the instruction that follows the opcode, ModR/M bytes, and scale-indexing bytes. The opcode determines if the operand is a signed value.

## Instruction Column

The "Instruction" column contains the instruction syntax. The following is a list of the symbols used to represent operands in the instruction statements:

- imm8: an immediate byte value, imm8 is a signed number between -128 and +127 inclusive.

- r/m32: a doubleword register or memory operand used for instructions whose operand-size attribute is 32 bits.

- mm/m32: indicates the lowest 32 bits of an MMX register or a 32-bit memory location.

- mm/m64: indicates a 64-bit MMX register or a 64-bit memory location.

## **Description Column**

The "Description" column briefly explains the instruction activity.

## Operation

The "Operation" section contains an algorithmic description of the operation performed by the instruction.

The register name or memory location implies the contents of the register or memory.

The bit values are written from high-order to low-order and indicate the address within the register or memory. The bit addresses are specified along with the register name or memory location in brackets. For example mm(7..0) represents the low-order 8 bits in an MMX register.

The algorithms are composed of the following elements:

- Comments are enclosed with the symbol pairs "(\*" and "\*)".

- Compound statements are enclosed between the keywords of the "if" statement (IF, THEN, ELSE).

- $A \leftarrow B$ ; indicates that the value of B is assigned to A.

- The symbols =, <>, >, <, ≥, and ≤ are relational operators used to compare two values, meaning equal, not equal, greater or equal, less or equal, respectively. A relational expression such as A=B is TRUE if the value for A is equal to B; otherwise it is FALSE.

The following functions are used in the algorithmic descriptions:

- ZeroExtend (value) returns a value zero-extended to the operand-size attribute of the instruction. For example, if OperandSize = 32, ZeroExtend of a byte value of -10 converts the byte from F6H to doubleword with hexadecimal value 000000F6H. If the value passed to ZeroExtend and the operand-size attribute are the same size, ZeroExtend returns the value unaltered.

- SignExtend (value) returns a value sign-extended to the operand-size attribute of the instruction. For example, if OperandSize = 32, SignExtend of a byte containing the value -10 converts the byte from F6H to doubleword with hexadecimal value FFFFFF6H. If the value passed to SignExtend and the operand-size attribute are the same size, SignExtend returns the value unaltered.

- SaturateSignedWordToSignedByte converts a signed 16-bit value to a signed 8-bit value. If the signed 16-bit value is less than -128, it is represented by the saturated value -128 (0x80). If it is greater than 127, it is represented by the saturated value 127 (0x7F).

- SaturateSignedDwordToSignedWord converts a signed 32-bit value to a signed 16-bit value. If the signed 32-bit value is less than -32768, it is represented by the saturated value -32768 (0x8000). If it is greater than 32767, it is represented by the saturated value 32767 (0x7FFF).

- SaturateSignedWordToUnsignedByte converts a signed 16-bit value to an unsigned 8-bit value. If the signed 16-bit value is less than zero it is represented by the saturated value zero (0x00). If it is greater than 255 it is represented by the saturated value 255 (0xFF).

- SaturateToSignedByte represents the result of an operation as a signed 8-bit value. If the result is less than -128, it is represented by the saturated value -128 (0x80). If it is greater than 127, it is represented by the saturated value 127 (0x7F).

- SaturateToSignedWord represents the result of an operation as a signed 16-bit value. If the result is less than -32768, it is represented by the saturated value -32768 (0x8000). If it is greater than 32767, it is represented by the saturated value 32767 (0x7FFF).

- SaturateToUnsignedByte represents the result of an operation as a signed 8-bit value. If the result is less than zero it is represented by the saturated value zero (0x00). If it is greater than 255, it is represented by the saturated value 255 (0xFF).

- **SaturateToUnsignedWord** represents the result of an operation as a signed 16-bit value. If the result is less than zero it is represented by the saturated value zero (0x00). If it is greater than 65535, it is represented by the saturated value 65535 (0xFFFF).

## Description

The "Description" section describes the operation for all variations of the instruction.

## Example

The "Example" section contains a graphical representation of the instruction's functional behavior.

## Exceptions

The "Exceptions" section lists the exceptions in the three different modes: Protected mode, Real Address mode, and Virtual-8086 mode.

## INTEL ARCHITECTURE MMX<sup>TM</sup> INSTRUCTION SET

Refer to Section 4.2 of this document for more detail on these exceptions. See also the *Pentium*® *Processor Family Manual, Volume 3*, Section 9.4 and Chapter 14.

## intel

## EMMS—Empty MMX<sup>™</sup> State

| Opcode | Instruction | Description                   |

|--------|-------------|-------------------------------|

| 0F 77  | EMMS        | Set the FP tag word to empty. |

## Operation

TW  $\leftarrow$  0xFFFF;

## Description

The EMMS instruction sets the values of the floating-point (FP) tag word to empty (all ones). EMMS marks the registers as available, so they can subsequently be used by floating-point instructions.

If a floating-point instruction loads into one of the registers before it has been reset by the EMMS instruction, a floating-point stack overflow can occur, which results in an FP exception or incorrect result.

All other MMX instructions validate the entire FP tag word (all zeros).

NOTE

This instruction must be used to clear the MMX state at the end of all MMX routines, and before calling other routines that may execute floating-point instructions.

15 0 I I. 1 L FP tag(7) FP tag(6) FP tag(5) FP tag(4) FP tag(3) FPtaq(2) FPtag(1) FPtaq(0) Tag values: 00 = Valid10 = Valid01 = Valid11 = Empty3006047

Figure 5-1 shows the format of the FP Tag Word.

## Flags Affected

None.

## INTEL ARCHITECTURE MMX<sup>TM</sup> INSTRUCTION SET

## **Protected Mode Exceptions**

#UD if CR0.EM = 1; #NM if TS bit in CR0 is set; #MF if there is a pending FPU exception.

## **Real Address Mode Exceptions**

#UD if CR0.EM = 1; #NM if TS bit in CR0 is set; #MF if there is a pending FPU exception.

## Virtual 8086 Mode Exceptions

#UD if CR0.EM = 1; #NM if TS bit in CR0 is set; #MF if there is a pending FPU exception.

## intel

## MOVD—Move 32 Bits

| Opcode   | Instruction            | Description                                                |

|----------|------------------------|------------------------------------------------------------|

| 0F 6E /r | MOVD <i>mm, r/m32</i>  | Move 32 bits from integer register/memory to MMX register. |

| 0F 7E /r | MOVD <i>r/m32, mm_</i> | Move 32 bits from MMX register to integer register/memory. |

## Operation

```

IF destination = mm

THEN

mm(63..0) ← ZeroExtend(r/m32);

ELSE

r/m32 ← mm(31..0);

```

## Description

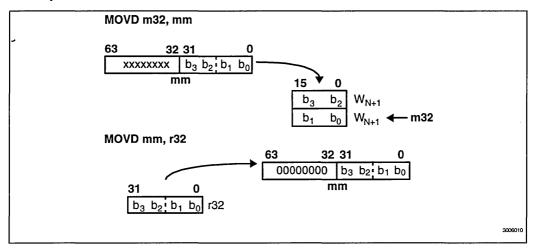

The MOVD instruction copies 32 bits from the source operand to the destination operand.

The destination and source operands can be either MMX registers, 32-bit memory operands, or 32-bit integer registers. The MOVD cannot transfer data from an MMX register to an MMX register, from memory to memory, or from an integer register to an integer register.

When the destination operand is an MMX register, the 32-bit source operand is written to the low-order 32 bits of the 64-bit destination register. The destination register is zero-extended to 64 bits.

When the source operand is an MMX register, the low-order 32 bits of the MMX register are written to the 32-bit integer register or 32-bit memory location.

### INTEL ARCHITECTURE MMX™ INSTRUCTION SET

## Example

## Flags Affected

None.

## **Protected Mode Exceptions**

#GP(0) if the destination is in a nonwritable segment; #GP(0) for an illegal memory operand effective address in the CS, DS, ES, FS, or GS segments; #SS(0) for an illegal address in the SS segment; #PF(fault-code) for a page fault; #AC for unaligned memory reference if the current privilege level is 3; #UD if CR0.EM = 1; #NM if TS bit in CR0 is set; #MF if there is a pending FPU exception.

## **Real Address Mode Exceptions**