# 82786 CHMOS GRAPHICS COPROCESSOR

- High Performance Graphics

- Fast Polygon and Line Drawing

- High Speed Character Drawing

- Advanced DRAM/VRAM Controller for Graphics Memory up to 4 Mbytes

- Supports up to 200 MHz CRTs or 1400 by 1400 by 1 Bit (2K\*2K\*2)

- Up to 1024 Simultaneous Colors

- Integral DRAM/VRAM Controller, Shift Registers and DMA Channel

- IBM Personal Computer Color Graphics Adapter-Compatible

- International Character Support

- Interface Designed for Device-Independent Standards — Virtual Device Interface - Graphics Kernal System

- NAPLPS

- Hardware Windows

- Fast Bit-Block Copies Between System and Bit-Map Memories

- Integral Video DRAM Support - Up to 1900 by 1900 by 8

- Third-Party Software Support

- Multi-tasking Support

- Provides Support for Rapid Filling with Patterns

- Programmable Video Timing

- Advanced CHMOS Technology

- Supports Dual Port Video DRAMs & Sequential Access DRAMs

- 88 Pin Grid Array and Leadless Chip Carrier

(See Intel Packaging; Order Number: 231369-001)

The 82786 is a powerful, yet simple component designed for microcomputer graphics applications including personal computers, engineering workstations, terminals, and laser printers. Its advanced software interface makes applications and systems level programming efficient and straight-forward. Its performance and high-integration make it a cost-effective component while improving the performance of nearly any design. Hardware windows provide instantaneous changes of display contents and support multiple graphics applications from multiple graphics bit maps. Applications programs written for the IBM Personal Computer can be run within one or more windows of the display when used with Intel CPUs.

The 82786 works with all Intel microprocessors, and is a high-performance replacement for sub-systems and boards which have traditionally used discrete components and/or software for graphics functions. The 82786 requires minimal support circuitry for most system configurations, and thus reduces the cost and board space requirements of many applications. The 82786 is based on Intel's advanced CHMOS III process.

> 0 vs 0 vs 0 0 0 0 OBLANK 0 0 0 0 0 0 0 ORAO ORAT 0 O DRA2 O 0 O 413 O 412 ORAS 0 O DRA 0 0 0 0 vœ 0 O RAS1 0 0 0 0 O ak 09 0 0 O SEN 0 12 O HLIDA 12 O O O O O O O O HREQ N/KOJ CSJ READYJ DO1 0 0 0 0 0 13 0 O BHE# 0 ORD 0 0 O ∞3 0 O ₿7 0 0 0 0 231676-27 Figure 1. 82786 Pinout—Bottom View

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied. Information contained herein supersedes previously published specifications on these devices from Intel. November 1986 © Intel Corporation, 1986 Order Number: 231676-002

# INTRODUCTION

The 82786 is an intelligent peripheral capable of both drawing and refreshing raster displays. It has an integrated drawing engine with a high level VDI like graphics commands. Multiple character sets (fonts) can be used simultaneously for text display applications. The 82786 provides hardware support for fast manipulation and display of multiple windows on the screen. It supports high resolution displays with a 25 MHz pixel clock and can display up to 256 colors simultaneously. Using multiple 82786s and/or in conjunction with dual port video DRAMs (VRAMs), the 82786 is virtually unlimited in terms of color support and resolution.

#### Table 1. 82786 Pin Description

82786

| Symbol | Pin<br>Number                                                                                               | Туре | Description                                                                                                                                                                                                                                                                             |

|--------|-------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A21:0  | A09,B08,A08,B07,<br>A06,B06,A05,B05,<br>A04,B04,A03,B03,<br>A02,B02,B01,C02,<br>C01,D02,D01,E02,<br>E01,F02 | 1/0  | Address lines for the External Bus. Inputs for Slave Mode<br>accesses of the 82786 supported Graphics memory array or<br>82786 internal memory or I/O mapped registers. Driven by the<br>82786 when it is the External Bus Master.                                                      |

| D15:0  | N12,M12,M13,L12,<br>L13,K12,K13,J12,<br>J13,H12,H13,G12,<br>G13,F13,F12,E13                                 |      | Data Bus for the 82786 Graphics memory array and the External<br>Bus.                                                                                                                                                                                                                   |

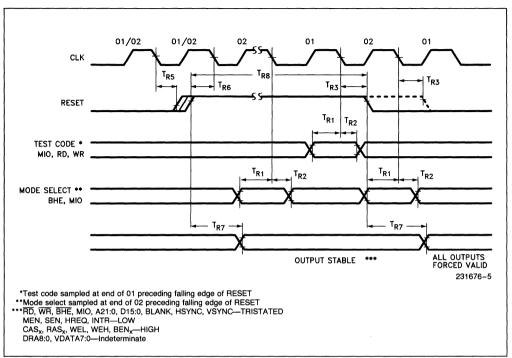

| BHE    | B13                                                                                                         | 1/0  | Byte High Enable. An input of the 82786 Slave Interface; driven<br>LOW by the 82786 when it is a Bus Master. Determines<br>asynchronous vs. synchronous operation for RD, WR and HLDA<br>inputs at the falling (trailing) edge of RESET. A HIGH state selects<br>synchronous operation. |

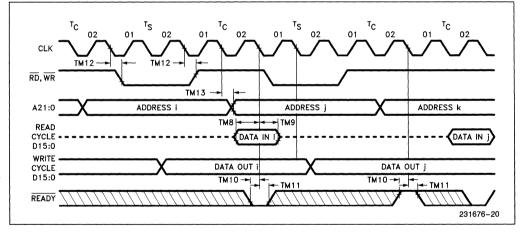

| RD     | D13                                                                                                         |      | Read Strobe. An input of the 82786 Slave Interface; driven by the 82786 when it is a Bus Master. Selects normal/test mode at falling RESET.                                                                                                                                             |

| WR     | C13                                                                                                         |      | Write Strobe. An input of the 82786 Slave Interface; driven by the 82786 when it is a Bus Master. Selects normal/test mode at falling RESET.                                                                                                                                            |

| M/ĪŌ   | C12                                                                                                         | 1/0  | Memory or I/O indication. An input of the 82786 Slave Interface;<br>driven HIGH by the 82786 when it is the Bus Master. Determines<br>synchronous 80286 or 80186 interface at the falling edge of<br>RESET. A LOW state selects a synchronous 80286 interface.                          |

| CS     | D12                                                                                                         | I    | Chip Select. Slave Interface input qualifying the access.                                                                                                                                                                                                                               |

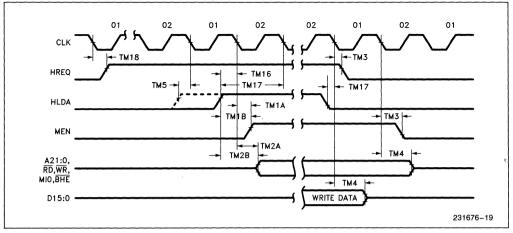

| MEN    | B11                                                                                                         | 0    | Master Enable. Driven HIGH when the 82786 is in control of the External Bus. (i.e., HLDA received in response to a 82786 HREQ.) Used to steer the data path and select source of bus cycle status commands.                                                                             |

| SEN    | A11                                                                                                         | 0    | Slave Enable. Driven HIGH when the 82786 is executing a Slave<br>bus cycle for an External Master into the 82786 controlled memory<br>or registers. Used to enable the data path and as a READY<br>indication to the External Bus Master.                                               |

| READY  | E12                                                                                                         | I    | Synchronous input to the 82786 when executing External Bus cycles. Identical to 80286 READY.                                                                                                                                                                                            |

| Symbol          | Pin<br>Number                               | Туре | Description                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------|---------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HREQ            | B12                                         | 0    | Hold Request. Driven HIGH by the 82786 when an access is being made to the External Bus by the Display or Graphics Processors. Remains HIGH until the 82786 no longer needs the External Bus.                                                                                                                                                                                  |

| HLDA            | A12                                         | I    | Hold Acknowledge. Input in response to a HREQ output.<br>Asynchronous vs. synchronous input determined by state of $\overline{\text{BHE}}$ pin at falling RESET.                                                                                                                                                                                                               |

| INTR            | B10                                         | 0    | Interrupt. The logical OR of a Graphics Processor and Display<br>Processor interrupt. Cleared with an access to the BIU Interrupt<br>Register.                                                                                                                                                                                                                                 |

| RESET           | A10                                         | 1    | Reset input, internally synchronized, halts all activity on the 82786<br>and brings it to a defined state. The leading edge of RESET<br>synchronizes the 82786 clock to phase 2. The trailing edge<br>latches the state of $\overline{BHE}$ to establish the type of Slave Interface. It<br>also latches $\overline{RD}$ , $\overline{WR}$ and MIO) to set certain test modes. |

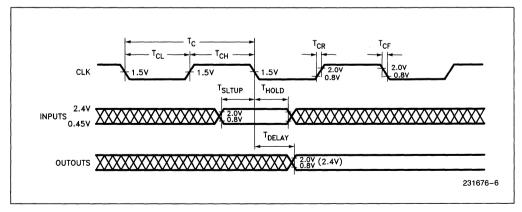

| CLK             | BO9                                         | I    | Double frequency clock input. Clock input to which pin timings are referenced. 50% duty cycle.                                                                                                                                                                                                                                                                                 |

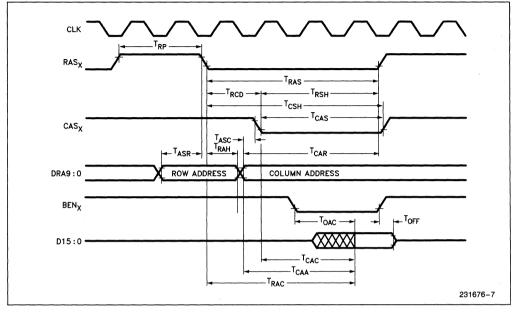

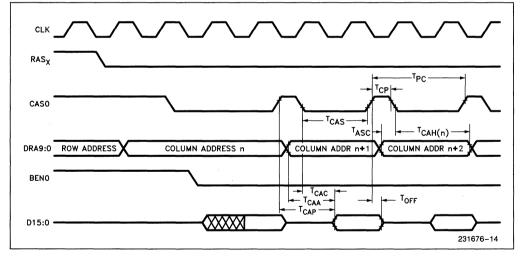

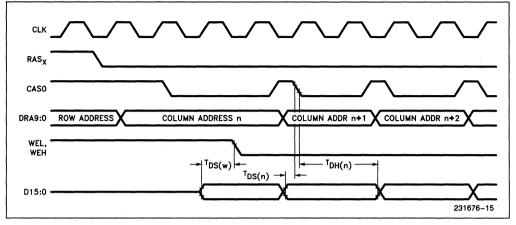

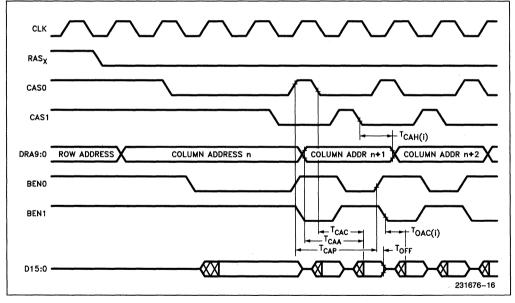

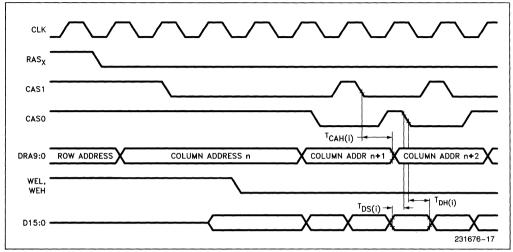

| CAS0            | M09                                         | 0    | Column Address Strobe 0. Drives the CAS inputs of the even word<br>Graphics memory bank if interleaved; identical to CAS1 if non<br>interleaved Graphics memory. Capable of driving 16 DRAM/<br>VRAM CAS inputs.                                                                                                                                                               |

| CAS1            | N09                                         | 0    | Column Address Strobe 1. Drives the CAS inputs of the odd word<br>Graphics memory bank if interleaved; identical to CAS0 if non-<br>interleaved Graphics memory. Capable of driving 16 DRAM/<br>VRAM CAS inputs.                                                                                                                                                               |

| RAS2:0          | M07,N08,M08                                 | 0    | Row Address Strobe. Drives the RAS input pins of up to 16<br>DRAMs/VRAMs. Drives the first three rows of both banks of<br>Graphics memory.                                                                                                                                                                                                                                     |

| DRA9/RAS3       | N06                                         | 0    | Multiplexed most significant Graphics memory address line and RAS3. DRA9 when using 1 Mb DRAMS; RAS3 otherwise.                                                                                                                                                                                                                                                                |

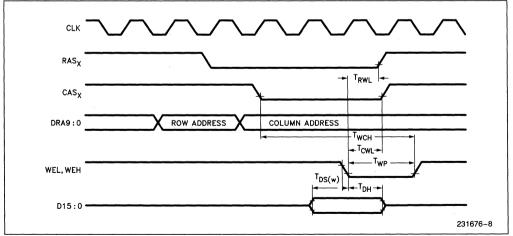

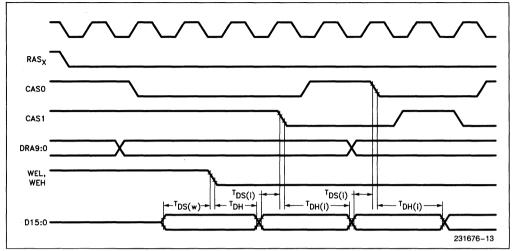

| WEL             | N10                                         | 0    | Write Enable Low Byte. Active LOW strobe to the lower order byte of Graphics memory.                                                                                                                                                                                                                                                                                           |

| WEH             | M10                                         | 0    | Write Enable High Byte. Active LOW strobe to the higher order byte of Graphics memory.                                                                                                                                                                                                                                                                                         |

| DRA8:0          | M06,N05,M05,<br>N04,M04,N03,<br>M03,N02,M02 | 0    | Multiplexed Graphics memory Address. Graphics memory row and<br>column address are multiplexed on these lines. Capable of driving<br>32 DRAMs/VRAMs.                                                                                                                                                                                                                           |

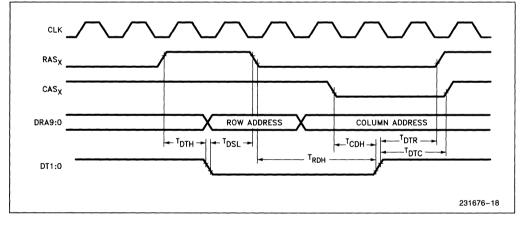

| BEN1:0<br>DT1:0 | N11,M11                                     | 0    | Multiplexed Bank Enable and Data Transfer Line. In normal memory cycle enables the output of the Graphics memory array on to the 82786 data bus, D15:0. In data transfer cycle, loads the serial register in dual port video DRAMs (VRAMs). BEN1/DT1 and BEN0/DT0 control Bank1 and Bank0 respectively.                                                                        |

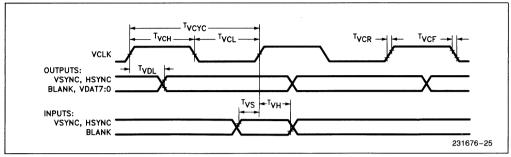

| BLANK           | F01                                         | 1/0  | Output used to blank the display at particular positions on the screen. May also be configured as input to allow the 82786 to be synchronized with external sources.                                                                                                                                                                                                           |

| Table 1.82786 Pin Description (Continued) | Table 1. | 82786 I | Pin D | escription | (Continued) |

|-------------------------------------------|----------|---------|-------|------------|-------------|

|-------------------------------------------|----------|---------|-------|------------|-------------|

82786

| Symbol                 | Pin<br>Number                           | Туре | Description                                                                                                                                                                                                      |

|------------------------|-----------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DATA</sub> 7:0  | H02,J01,J02,<br>K01,K02,L01,<br>L02,M01 | 0    | Video data output.                                                                                                                                                                                               |

| V <sub>CLK</sub>       | H01                                     | 1    | Video Clock input used to drive the display section of the 82786.<br>Maximum frequency of 25 MHz.                                                                                                                |

| H <sub>SYNC</sub> /WS0 | G02                                     |      | Horizontal Sync. Window status is multiplexed on this pin. May<br>also be configured as input to allow the 82786 to be synchronized<br>with external sources. May also be configured to output Window<br>status. |

| V <sub>SYNC</sub> /WS1 | G01                                     | 1/0  | Vertical Sync. Window status is multiplexed on this pin. May also<br>be configured as input to allow the 82786 to be synchronized with<br>external sources. May also be configured to output Window status.      |

| V <sub>SS</sub>        | A01,M01,A13,<br>N13                     |      | 4 V <sub>SS</sub> pins.                                                                                                                                                                                          |

| V <sub>CC</sub>        | N07,A07                                 |      | 2 V <sub>CC</sub> pins.                                                                                                                                                                                          |

# ARCHITECTURE

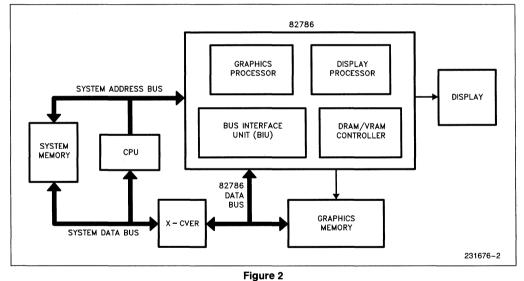

The 82786 is a high integration device which contains three basic modules (figure 2):

- 1. Display Processor (DP)

- 2. Graphics Processor (GP)

- 3. Bus Interface Unit (BIÚ) with DRAM/VRAM Controller.

#### **Display Processor**

The 82786 Display Processor controls the CRT timings and generates the serial video data stream for the display. It can assemble several windows on the screen from different bit-maps scattered across the memory accessible to the 82786.

#### **Graphics Processor**

The 82786 Graphics Processor executes commands from a Graphics Command Block (GCMB) (placed in memory by the host CPU) and updates the bit-map memory for the Display Processor. The Graphics Processor has high level VDI like commands and can draw graphical objects and text at high speeds.

# **Bus Interface Unit (BIU)**

The BIU controls all communication between the 82786, external CPU and memory. The BIU includes an integrated DRAM/VRAM controller that can take advantage of the high speed burst access modes of page mode and fast page mode DRAMs to perform block transfers. The Display Processor and Graphics Processor use the BIU to access the bit-maps in memory.

# Memory Structure and Internal Registers

The 82786 address range is 4 Mbytes. This is divided between the Graphics memory directly supported by the 82786 and External system memory. The 82786 distinguishes between Graphics memory and External system memory by assuming Graphics memory space starts at address OH and goes up to whatever amount of Graphics memory is configured. External system memory occupies the rest of the address space. The amount of Graphics memory/ Configured, and therefore the Graphics memory/External system memory boundary, is controlled by the "DRAM Control Register" in the BIU. The upper limit of configured Graphics memory is 4 Mbytes.

A 128 byte block (contiguous) of internal control registers is distributed throughout the three modules on the 82786. This block can be either memory or I/O mapped in the CPU address space. The base address and memory or I/O mapped for this register block is programmable through the "Internal Relocation Register" in the BIU.

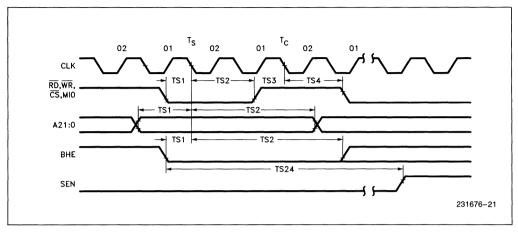

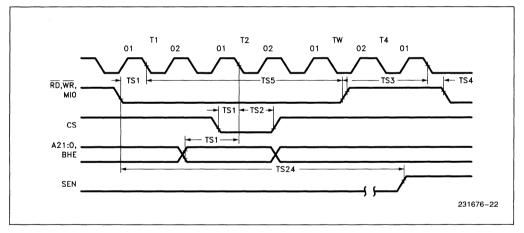

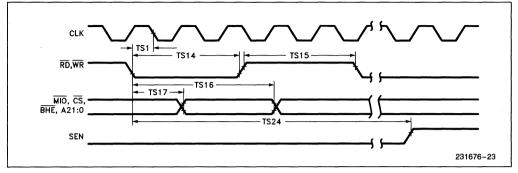

# External Memory Access (Master Mode)

The 82786 goes into "Master Mode" whenever it needs to access a memory address that is beyond the upper limit of configured graphics memory. This memory is typically external memory shared between the 82786 and the external CPU. The bus timings in this mode are similar to the 80286 style bus timings. An 82786 request for the bus is indicated by a high level on the HREQ line. The 82786 drives the external bus (A21:0, D15:0,  $\overline{\text{RD}}$ ,  $\overline{\text{WR}}$ , MIO and  $\overline{\text{BHE}}$ ) only after receiving a HLDA (acknowledge) from the external master. The HLDA line could be externally synchronized (82786 synchronous mode) or internally synchronized (82786 asynchronous mode). The 82786 will deactivate the HREQ line when it no longer needs to access external memory or when it senses an inactive HLDA. The 82786 indicates that it is in control of the external bus by a high level on the MEN output.

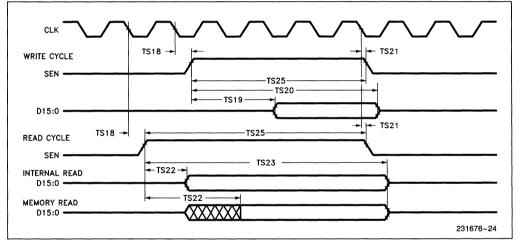

# Slave Mode

The 82786 Slave Interface allows an external CPU access into the Graphics memory array or the 82786 Internal Registers. The external CPU directs a (read/write) slave access to the 82786 by asserting the 82786 CS input. When the 82786 is not driving the external bus, the A21.0, RD, WR, MIO and BHE lines are inputs. The RD, WR, MIO and CS lines are constantly monitored by the 82786 to detect a CPU cycle directed at the 82786. After beginning a slave access to the 82786, the external CPU must go into a wait state. The 82786 will not process new slave commands from the CPU before the previous command has been serviced. The 82786 indicates the termination of the slave access by a high level on the SEN output. The data bus transceivers can be enabled by SEN.

# **SEN as Slave Ready Indication**

SEN is optimized for connection to the 82284 ARDY or SRDY input when the Slave Interface is set in synchronous 80286 mode. When operating in sync with the 80286, slave write cycles can always execute with a minimum of 2 wait states. The number of wait states for a read cycle is a function of the DRAM/VRAM speed. For 2 wait state reads, SEN is connected to SRDY. For 3 wait state reads, it is connected to ARDY. Write cycles in both cases execute with 2 wait states because the 82786 issues SEN with different timing during write cycles.

The 82786 supports byte accesses to Graphics memory. The combination of  $\overline{BHE}$  and A0 generate the proper WEL and WEH signals.  $\overline{BHE}$  and A0 are ignored for read cycles. Since the Display and Graphics Processors always generate word addresses, the slave cycles directed to graphics memory are the only time WEL may not exactly follow WEH.

The 82786 will acknowledge a slave access from an external CPU while waiting for an acknowledge (HLDA) to its own request for the external bus. This prevents a potential deadlock situation.

#### Synchronous/Asynchronous Operation

The synchronous/asynchronous mode is selected by the state of the  $\overline{BHE}$  input at the falling edge of reset. A high state selects synchronous operation. The synchronous interface requires that the 82786 and the 80286/80186 clock inputs are shared. For the 80286 case, a common RESET ensures that the 82786 and the 80286 initialize to the same state. With the 80186, external hardware must ensure that the 82786 phase1 is coincident with the 80186 CLKOUT LOW. In the Master Mode, the HLDA line is sampled synchronously or asynchronously. The 82786 slave interface provides for synchronous or asynchronous sampling of the command lines ( $\overline{RD}$ and  $\overline{WR}$ ).

# EIGHT AND SIXTEEN BIT HOST

On reset, the 82786 always assumes an 8 bit host interface. The first few accesses to the 82786 must be 8 bit accesses. The 82786 can be switched to a 16 bit interface by setting the "BCP" bit in the "BIU Control Register".

In 16 bit mode, the Internal Register Block is only word addressable. Odd word or odd byte accesses to the internal locations will not produce the desired result. Even byte access, however will work as desired. The least significant address bit, A0, is ignored in 16 bit mode.

In 8 bit mode, the internal registers must be accessed by two successive bus cycles. This is not necessary for reads, but is necessary for writes to the internal registers. The low byte (A0 = 0) must be written first, followed by the high byte (A0 = 1) of the register. A21:1 must be the same for both bus cycles. The register is not changed until the second byte (the high byte) is written to the 82786. There is no restriction on the time between the two bus cycles, but if successive low bytes are written before a high byte is written, the last low byte is the one written to the register. The BIU latches even bytes (A0 = 0) of write data in a temporary register. When an odd byte is subsequently written to location address + 1, this byte and the even byte in the temporary register are written to the desired location. A lock out mechanism prevents a high byte write to modify an internal register if there is no valid word in the temporary register.

There is no crossing done by the 82786 in 8 bit mode: low bytes are transferred on the low data lines D7:0 and the high bytes on D15:8. An external cross creates the 8 bit bus for the host. This is not additional hardware since a crossover is needed for an 8 bit host accessing of the memory array anyway.

#### MEMORY ACCESS ARBITRATION

The BIU receives requests to access the Graphics Memory from the Display Processor, the Graphics Processor and the External CPU. Additionally the internal DRAM/VRAM Controller also generates refresh requests. The DRAM/VRAM refresh requests are always highest priority. The other requests are arbitrated with programmable priorities. A higher priority request can interrupt lower priority memory cycles. Block transfers however can only be interrupted on doubleword boundaries.

There are two priority levels for requests from the Display and Graphics Processors: a First Priority (FPL) and a Subsequent Priority (SPL). The First Priority is the priority at which the first request of a bus cycle is arbitrated with. The Subsequent Priority is the priority associated with subsequent requests of a block transfer bus cycle. This allows for block transfers to execute with a different priority level. If a higher priority request occurs while a block transfer is executing, the BIU suspends the current block transfer and acknowledges the higher priority request. After completion of that higher priority memory access, the requests are arbitrated again. The suspended block transfer is arbitrated with its SPL priority since it is still executing a block transfer. The External Request has no Subsequent Priority level since it cannot execute block transfers. The default priorities from highest to lowest following RESET are:

| External | FPL | 7 |

|----------|-----|---|

| Display  | FPL | 6 |

| Graphics | FPL | 5 |

| Displays | SPL | З |

| Graphics | SPL | 2 |

Three bit codes describe the priorities so 7 is the highest and 0 is the lowest. If two priority registers are programmed with the same value, a default priority chain is used. The default order is, from highest to lowest priority:

- 1. Display Processor

- 2. Graphics Processor

- 3. External

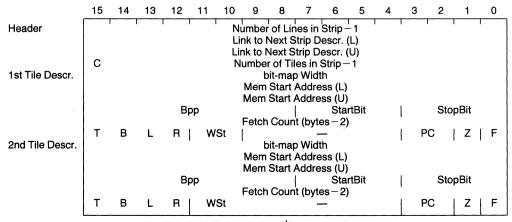

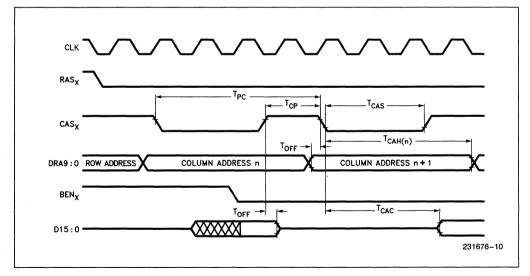

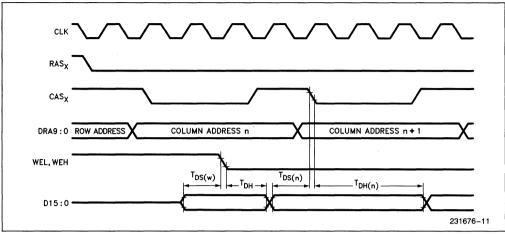

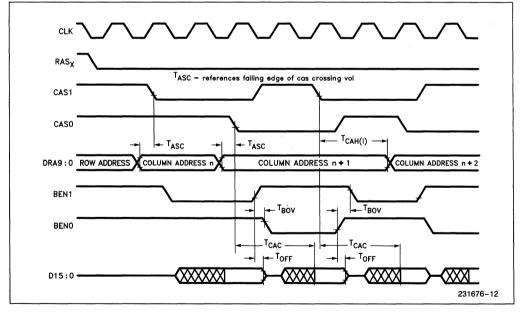

#### **Graphics Memory Interface**

The 82786 directly supports up to 32 DRAMs without additional external logic. This capability has the advantage of Simple utilization of cost effective memory devices and significant performance improvement through the use of either standard Page Mode or the newer Fast Page Mode/Static Column Decode sequential access RAMs. The Fast Page Mode/Static Column Decode parts enable the 82786 to cycle the DRAMs in 100 ns instead of the 200 ns used for Page Mode parts. The 82786 also allows the memory to consist of either standard single port memory devices or dual port Video RAM devices (VRAMs).

The 82786 supports a wide range of DRAM/VRAM configurations. The choices include interleaving or non-interleaving (1 or 2 banks - one CAS line/bank), number of rows per bank (1, 2, 3 or 4 - one RAS line/row), width (x1, x4 or x8), height (16k, 64k, 256k or 1M) and performance (Page Mode or Fast Page Mode/Static Column Mode). The only limitation is the address space limit of 4Mbytes. The 82786 DRAM/VRAM address lines (DRAx) can directly drive 32 memory devices while the RAS, CAS, WE and BEN lines can directly drive 16 devices. When the memory array consists of more than 32(16) devices then external drivers have to be used to drive the memory array.

There are some special DRAM configurations:

- i) When 1 Mb \* 1 DRAMs are used, RAS3 is used as DRA9.

- ii) When only one interleaved row is configured (32 devices), RAS1 is identical to RAS0. Additional buffering on RAS0 is therefore not required.

- iii) When two non interleaved rows are configured (32 devices), CAS1 is identical to CAS0. Additional buffering on CAS0 is therefore not required.

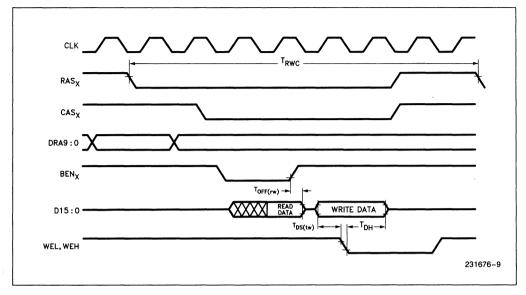

# **DRAM Cycle Types**

The 82786 supports two fundamental memory cycle types: single and block. A single cycle involves a single 16 bit word, while a block transfer is a minimum of 2 16 bit words with no maximum length. The single cycle types supported and their cycle times are given below. The cycle times are counted in system clocks, 1/<sub>2</sub> the CLK input frequency.

- 1. Single Reads 3 cycles 300 ns @ 10 MHz

- 2. Single Writes 3 cycles 300 ns @ 10 MHz

- 3. Read-Modify- 4 cycles 400 ns @ 10 MHz Writes

The block cycles use the high speed sequential access modes of page mode, fast page mode (ripple mode) and static column DRAMs. Typical performance numbers for this case are:

| 1. Page Mode,<br>Non-Interleaved      | 2 cycles 10 Mb/s @ 10 MHz  |

|---------------------------------------|----------------------------|

| 2. Page Mode,<br>Interleaved          | 1 cycle 20 Mb/s @ 10 MHz   |

| 3. Fast Page Mode,<br>Non-Interleaved | 1 cycle 20 Mb/s @ 10 MHz   |

| 4. Fast Page Mode,<br>Interleaved     | .5 cycles 40 Mb/s @ 10 MHz |

All accesses into the graphics memory by the Display Processor use the high speed sequential access mode whenever possible. The Graphics Processor uses a single Read-Modify-Write cycles for all pixel drawing operations. Block copy operations by the Graphics Processor use the high speed sequential access modes. External CPU access into graphics memory is always a single read or write cycle. When configured to interface with dual port VRAMs, the 82786 generates Page Mode and Fast Page Mode style control signals for memory access through the normal random access port. It also executes a data transfer cycle when the video shift register in the VRAMs have to be loaded.

#### **Graphics Memory Refresh**

The BIU has an internal DRAM/VRAM refresh controller. The refresh period is programmable through the "DRAM/VRAM Refresh Control" Register in the BIU. All configured rows are refreshed simultaneously by activating the corresponding RAS lines periodically (RAS only refresh). The refresh row address (10 bits) is generated internally. On power up, the refresh row address is undefined. On normal reset, the refresh row address is not affected. It is initialized only if the 82786 is reset into the "BIU Test Mode". Not modifying the refresh address during RESET allows for a "warm RESET" implementation: contents of DRAM/VRAM can be insured to remain valid if RESET is short enough (less than three DRAM/VRAM refresh cycles). DRAM/VRAM refresh will continue at the proper row after RESET goes inactive again.

The graphics memory refresh cycles are always the highest priority cycles. There is some latency possible between the internal refresh request and the actual refresh cycle. This latency is critical only in one case: The 82786 is in a wait state while executing a bus cycle on the External Bus.

The worst case is a refresh request occurring just after the 82786 receives a HLDA from the host CPU to execute a block transfer on the External bus. Refresh requests can interrupt block transfers, but only on doubleword boundaries — the 82786 must execute 2 full bus cycles on the External Bus before the refresh cycle is run. The possibility of many wait states when executing these two bus cycles creates a need for a large refresh latency tolerance. The 82786 can queue up to 3 refresh requests internally. In the default mode (refresh request @ 15.2 micro seconds) and at 10 MHz operation, this implies that each bus cycle to external memory should not have more than 225 wait states.

There is no warm up logic on the 82786. The system must either wait for sufficient number of refresh cycles to execute or the boot software on the host can

quickly access the memory array for the required number of cycles.

The default value of the DRAM/VRAM Control Register configures the array as 4 rows of Non-Interleaved Page Mode 256k  $\times$  1 with refresh requests generated every 15.2 micro seconds.

#### Internal Register and Graphics Memory Slave Access

The external master can access either 82786 internal memory I/O mapped registers or the Graphics memory. The 82786 internal address space consists of a contiguous 128 byte block. It is mapped to memory or I/O space depending on the state of the  $M/\overline{IO}$  bit in the "Internal Relocation Register". The 82786 determines the access type (memory vs I/O) by the  $M/\overline{IO}$  pin. An address comparison is done between the Internal Relocation Register and the incoming address to determine if the CPU access is directed to internal memory/IO mapped registers.

Intel reserves the right to add functions to future versions of the 82786. Users should not use reserved locations in order to ensure future compatibility.

#### PERFORMANCE

Slave performance is measured here by assuming a request is made to an idle 82786. A synchronous interface is assumed.

Minimum 80286 Wait States = 3 (10 MHz 80286 and 82786)

Minimum 80386 Wait States = 8 (16 MHz 80386, 8 MHz 82786)

Minimum 80186 Wait States = 3 (10 MHz 80186 and 82786, WT = 1)

Minimum 80186 Wait States = 2 (10 MHz 80186 and 82786, WT = 0)

The values mentioned above are for read cycles. In some cases, write cycles can operate with fewer wait states. For instance, the 80286 can execute 2 wait state synchronous write cycles. The 80186 can execute write cycles with one less wait state than mentioned above.

For asynchronous interfaces, if the CPU is operating at the same frequency as the 82786, the number of wait states are typically 1 more than those indicated above. For CPUs operating at a slower frequency than the 82786, the number of wait states are, on the average, less than 1 greater than those given above. In some cases, (eg. a 6 MHz 80286) an asynchronous interface acutally has less wait states than those quoted above for the synchronous interface.

#### **INTERNAL REGISTERS**

The 82786 Internal Register block is relocatable by programming the address in the "Internal Relocation Register" in the BIU. The register block can be memory or I/O mapped. The Register Block is physically distributed between the three 82786 modules, BIU, Graphics Processor and Display Processor.

Accesses to reserved locations have no effect; they execute normally but may produce indeterminate read data. No register is altered when a write is executed to a reserved location.

Location of Internal Registers within 128 byte block:

#### Byte

| ords |

|------|

|      |

| ords |

|      |

| ords |

|      |

|      |

The BIU register map is as follows:

**Byte**

| Internal Relocation |

|---------------------|

| Reserved            |

| BIU Control         |

| Refresh Control     |

| DRAM Control        |

| Display Priority    |

| Graphics Priority   |

| External Priority   |

|                     |

The field definitions for the BIU Registers are as follows:

#### **Internal Relocation**

|                     | 15 | 14 | 13   | 12 | ••• | 4 :   | 32 | 1 | 0  |  |

|---------------------|----|----|------|----|-----|-------|----|---|----|--|

| Addr =<br>BASE + 0H |    |    | Base | )  | A   | ddres | S  |   | мю |  |

| Reset values: xxx0  |    |    |      |    |     |       |    |   |    |  |

The Base Address determines the location of the 128 byte Internal Register Block. The MIO bit selects between memory or I/O mapping. If it is set (1), the Register Block is memory mapped. At RESET, the Base Address is set so that the Internal Relocation Register is located at every 128-byte address in the entire I/O space whenever  $\overline{CS}$  is asserted. The Base Address must be written into this register before any other registers can be accessed.

# **BIU Control**

|                  | -  | -  | 4   | -  | _  | -   | •   |  |

|------------------|----|----|-----|----|----|-----|-----|--|

| Addr = BASE + 4H | VR | WΤ | BCP | GI | DI | WPI | WP2 |  |

| RESET value:     |    |    |     |    |    |     |     |  |

- VR: If set (1) then the 82786 generates dual port video DRAM (VRAM) type memory cycles for display data fetch. If reset (0) then conventional page mode type memory cycles are performed to fetch display data.

- WT: Determines the minimum number of wait states possible in a synchronous 80186 interface. If set (1), there is a minimum of 2 (3) wait states during memory write (read) cycles.

- BCP: Determines whether the Internal Register block is accessed as bytes or words by the external CPU. If set (1), a /16 bit interface is selected.

- GI: Graphics Processor Interrupt. Set when the Graphics Processor issues an Interrupt. Cleared with RESET or a read of this register.

- DI: Display Processor Interrupt. Set when the Display Processor issues an Interrupt. Cleared with RESET or a read of this register.

- WP1: Write Protection One. When set (1), all BIU Register contents except for the WP1 and WP2 bits of this register are write protected.

- WP2: Write Protection Two. When set (1), all BIU Register contents are write protected, including WP1 and this bit, WP2. The only way to regain write access to the BIU registers after this bit is set, is to RESET the 82786.

# **Refresh Control**

|                  | 6              | 5 | 4 | 3 | 2 | 1 | 0 |

|------------------|----------------|---|---|---|---|---|---|

| Addr = BASE + 6H | Refresh Scalar |   |   |   |   |   |   |

| RESET value:     |                | 0 | 1 | 0 | 0 | 1 | 0 |

The Refresh Scalar is a 6 bit quantity that determines the frequency of refresh cycles to the Graphics memory.

Refresh interval = (Scalar + 1) \* 16 \* Input clock period

#### **DRAM/VRAM** Control

|                  | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|------------------|-----|-----|-----|-----|-----|-----|-----|--|

| Addr = BASE + 8H | RW1 | RW0 | DC1 | DC0 | HT2 | HT1 | нто |  |

| RESET value:     | 1   | 1   | 0   | 0   | 1   | 0   | 1   |  |

RW1:0: Number of Graphics memory Rows. One of the variables in defining the Graphics memory/External system boundary. Also disables RAS signals not driving any DRAMs/VRAMs.

#### RW1 RW0

| 0 | 0 | : | 1 Rows |

|---|---|---|--------|

| 0 | 1 | : | 2 Rows |

| 1 | 0 | : | 3 Rows |

| 1 | 1 | : | 4 Rows |

DC1:0: DRAM/VRAM Configuration. Controls the rate of block transfers and orientation of CAS1 and CAS0.

#### DC1 DC0

| 0<br>0  | 0<br>1 | : | Page Mode, Non-Interleaved<br>Page Mode, Interleaved |

|---------|--------|---|------------------------------------------------------|

| 1       | 0      | : | Fast Page Mode, Non-Interleaved                      |

| 1       | 1      | : | Fast Page Mode, Interleaved                          |

| 1170.0. | 00     |   |                                                      |

HT2:0: DRAM/VRAM Height. Defines the HEIGHT (not size) of each DRAM/VRAM chip in the system. All DRAMs/VRAMs must be the same size.

| HT2 | HT1 | HT0 |   |              |

|-----|-----|-----|---|--------------|

| 0   | 0   | 0   |   | 8K Devices   |

| 0   | 0   | 1   | : | 16K Devices  |

| 0   | 1   | 0   | : | 32K Devices  |

| 0   | 1   | 1   | : | 64K Devices  |

| 1   | 0   | 0   | : | 128K Devices |

| 1   | 0   | 1   | : | 256K Devices |

| 1   | 1   | 0   | : | 512K Devices |

| 1   | 1   | 1   | : | 1M Devices   |

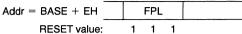

#### **Display Processor Priority**

| _                | 6               | 5 | 4   | 3 | 2 | 1 | 0 |

|------------------|-----------------|---|-----|---|---|---|---|

| Addr = BASE + AH | = BASE + AH FPL |   | SPL |   |   |   |   |

| RESET value:     |                 | 1 | 1   | 0 | 0 | 1 | 1 |

# **Graphics Processor Priority**

| Addr = BASE + CH |   | FPL |   |   | SPL |   |  |

|------------------|---|-----|---|---|-----|---|--|

| RESET value:     | 1 | 0   | 1 | 0 | 1   | 0 |  |

# **External CPU Priority**

Specifies the priorities of the Display Processor, Graphics Processor and External CPU requests for the first request (FPL) and subsequent requests for block transfers (SPL). Code 111 is highest priority. Code 000 is lowest priority.

# RESET AND INITIALIZATION

The state of  $\overrightarrow{BHE}$  at trailing RESET determines synchronous vs. asynchronous operation. In Master mode, synchronous/asynchronous operation affects the sampling of the HLDA signal only. In Slave mode, synchronous/asynchronous operation affects the sampling of  $\overrightarrow{RD}/\overrightarrow{WR}$  signals. Synchronous operation is set if  $\overrightarrow{BHE}$  is sensed HIGH at trailing RESET. This enables direct connection of the 80286  $\overrightarrow{BHE}$  pin in synchronous systems since it is driven HIGH during RESET. The 80186 "tristates" its  $\overrightarrow{BHE}$  during RESET so a small static load on this line can select asynchronous operation.

All internal registers are set to their default values on reset. The first slave I/O write access to the 82786 will always be directed at the Internal Registers (ignoring the upper fifteen address bits). The Internal Relocation Register must be programmed before any other Internal registers can be accessed. The DRAM/VRAM configuration registers must also be programmed to conform to any specific environment.

The 82786 assumes an 8 bit external CPU interface on reset. The graphics memory interface is always 16 bits wide. The BCP bit in the "BIU Control Register" must be set to 1 to enable a 16 bit external interface. Interrupts are cleared on reset.

# **GRAPHICS PROCESSOR**

# Introduction

The Graphics Processor (Graphics Processor) is an independent processor within the 82786. Its primary task is to draw bit-map graphics. It executes commands residing in the memory, accessing the memory through the Bus Interface Unit (BIU). The Graphics Processor addresses 4 MB of linear memory (22 bit addresses).

The Graphics Processor draws into a predefined area in the memory which is referred to as a "bitmap". A bit-map can be thought of as a rectangular drawing area composed of pixels. A coordinate system is defined for this bit-map with the origin at the upper left corner, the x-coordinate increasing from left to right and the y-coordinate increasing from top to bottom. A bit-map can be up to 32K pixels wide and 32K pixels high.

The 82786 can draw several graphics primitives such as points, lines, arcs, circles, rectangles, polygons and characters. During the figure drawing process, the 82786 follows several programmable attributes.

The graphics attributes supported by the 82786 are:

color depth (bits/pixel) texture logical operation color bit mask clipping rectangle

Each graphics primitive can be drawn in any one of 2, 4, 16 or 256 "Colors". The color details (bits/pixel and exact color) are programmable. The "Texture" controls the appearance of any line (or figure). The texture pattern can be up to 16 bits long thus enabling drawing of solid, dashed, dotted, dot-dash etc. types of lines. Each bit in the Texture corresponds to one pixel. The 82786 supports all sixteen binary "Logical Operation" between a figure being drawn in bit-map memory and the existing contents of memory. It is thus possible to overlay a figure on a background. The "Color Bit Mask" restricts the drawing operation to only some "color planes". The aspectific area in the bit-map.

The pixel information is stored in the bit-map memory in a packed pixel format. Different color bits for the same pixel are stored in adjacent bit positions within the same byte. Each byte represents 1, 2, 4 or 8 pixels (in one of 256, 16, 4 or 2 colors).

The Graphics Processor fetches its commands directly from a linked list Memory-resident Graphics Processor Command Block (GCMB). The GCMB is created and maintained by the CPU. The initial address for the GCMB is contained in a Graphics Processor Opcode Register in the 82786. Addresses for subsequent (next) GCMBs are contained in the previous GCMBs. The Graphics Processor can be forced to stop by appropriate commands.

When the Graphics Processor is idle, it is said to be in the "Poll State". This is the default mode after reset. While in the Poll State, the Graphics Processor continuously monitors its internal "Opcode Register". A valid command in this register starts the Graphics Processor. The first command placed in the internal Opcode Register must always be a "LINK" command directing the Graphics Processor to the main GCMB in memory.

| Internal Opc | Address<br>Internal Opcode<br>Register |             | Function             |        |

|--------------|----------------------------------------|-------------|----------------------|--------|

| BASE + 20h   | GR0                                    | OPCODE      |                      | GECL   |

| BASE + 22h   | GR1                                    | Parameter 1 | (Link Address        | Lower) |

| BASE + 24h   | GR2                                    | Parameter 2 | (Link Address Upper) |        |

**Graphics Processor Internal Registers used in Poll State**

#### **Graphic Processor Command Format**

The commands are placed (along with their parameters) sequentially in memory. Several GCMBs may be linked together through a LINK command. All commands have a standard format as described below:

| 15          | 8           | 7 |   |   |   |   |   | 1 | 0    |

|-------------|-------------|---|---|---|---|---|---|---|------|

|             | OPCODE      | 0 | 0 | 0 | 0 | 0 | 0 | 0 | GECL |

|             | Parameter 1 |   |   |   |   |   |   |   |      |

|             |             |   |   |   |   |   |   |   |      |

| Parameter i |             |   |   |   |   |   |   |   |      |

|             | etc.        |   |   |   |   |   |   |   |      |

Each command to the Graphics Processor consists of an opcode, a Graphics End of Command List

# **Graphics Processor Status Register**

(GECL) bit and a list of parameters as required by the command. The opcode is 8-bits wide. The remaining 7-bits in the first word of the command must be all 0's to ensure future compatibility. Also, whenever a parameter for the command is an address, 32-bits have been set aside but the 82786 uses only 22-bit addresses. The user must ensure that the higher 10-bits in the address parameter are always all 0's. All commands must lie at even byte addresses.

After fetching each command, the Graphics Processor checks the GECL bit. If the GECL bit is not set, the command is executed and the next command is then fetched from the GCMB. If the GECL bit is found to be set, the Graphics Processor does not execute the command and enters a POLL state.

One of the 82786 internal registers contains the Graphics Processor Status Byte. The bits in the Status Byte are represented as:

| Address<br>BASE + 26H | GPOLL | GRCD | GINT | GPSC | GBCOV | GBMOV | GCTP | GIBMD |  |

|-----------------------|-------|------|------|------|-------|-------|------|-------|--|

|-----------------------|-------|------|------|------|-------|-------|------|-------|--|

1. GPOLL - Poll State

Indicates if the Graphics Processor is in a POLL state.

2. GRCD - Reserved Command

This bit is set if the Graphics Processor encounters an illegal opcode.

- GINT This bit is set as a result of the INTR\_GEN command.

- 4. GPSC Pick Successful

This bit is set or cleared while the Graphics Processor is in the PICK mode. The bit is set if the pick operation resulted in success on any command.

5. GBCOV - bit-map Overflow for BitBlt or CharBlt

An attempt to execute a CHAR or a BitBlt command with any portion of the destination rectangle lying outside the clip rectangle causes this bit to be set. 6. GBMOV - bit-map Overflow for Geometric Commands

An attempt to draw a pixel lying outside clip rectangle as a result of any geometric drawing commands (LINE, CIRCLE etc.) would cause this bit to be set. The reason for separating these two bits is the difference between the clipping operations for the two types of commands.

7. GCTP - Character Trap

This bit indicates that a character specified in the character string as a parameter for the CHAR command had its TRAP bit set.

8. GIBMD - Illegal Bit Map Definition

This bit is set if the DEF\_BIT\_MAP command is executed with illegal parameters. The illegal parameters are bits per pixel defined to be other than 1, 2, 4 or 8 or Xmax defined to be greater than 32k-1. All the status bits except GPOLL are cleared upon reset. The GPOLL bit is set on reset.

# **Graphics Instruction Pointer**

The Graphics Processor Instruction Pointer is a 22 bit quantity stored in two registers in the Graphics processor. It points to the current command in the GCMB.

|       |                           | Address    |

|-------|---------------------------|------------|

| GCIPL | Instruction Pointer Lower | BASE + 28h |

| GCIPH | IP Upper                  | BASE + 2Ah |

# **Clipping Rectangle**

The 82786 can be instructed to restrict drawing to certain portion of the bit-map only. This portion is called the "Clipping Rectangle". The default clipping rectangle is the entire bit-map. The clipping rectangle must be redefined after a DEF\_BIT\_MAP command. For figures that are partially inside and partially outside the clipping rectangle, only the part inside the clipping rectangle is updated in the bit-map. For Block Transfer and Character drawing operations, if any part of the destination area lies outside the clipping rectangle, the command is not executed and the bit-map is left unchanged.

In order for the clipping to have predictable results, there are some restrictions on the x,y coordinates of each pixel. The rules to be observed are:

- For lines, circles, polygons, polylines, BitBlts and CharBlts, each pixel lying on the figure (both the visible and the invisible parts) must not have its x or y coordinate outside ± 32K range.

- 2. For circular arcs, the above restriction applies to the circle of which the arc is a part.

#### **Pick Mode**

The Graphics Processor can be put in the "PICK Mode" by executing the ENTER\_PICK command. In the PICK Mode, the Graphics Processor performs all pixel computations for all drawing, BitBlt and Character commands. However, the bit-map memory is not updated. Instead every computed pixel is compared against the clipping rectangle. If any computed pixel is found to lie within the clipping rectangle, the GPSC bit in the Graphics Processor Status Register is set.

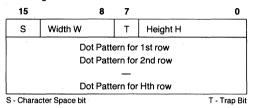

#### **Character Font Storage**

The character fonts are stored in memory. Starting from an even address, the character information is

stored in consecutive words of memory forming a character block. Each block can be of different lengths for different characters. A character font is selected by programming its base address into the 82786 through the DEF\_CHAR\_SET command. The font could be established for 8 or 16 bit character codes. Each character block within a font has the following format:

Each character block must start at a word address and the dot patterns for each line of the font must reside in separate words. The height and width of each character cannot be more than 16 pixels. In case the width of a character is less than 16 pixels, the dot pattern for each line must be stored as right justified.

Note that width and height of the character refer to the difference between their limiting x and y coordinates respectively. Thus width = 0 specifies a character one pixel wide and a height = 0 specifies a character one pixel high.

# **Graphics Registers**

All the registers in the Graphics Processor can be read from or written into, through the Graphics Processor commands - DUMP\_REG and LOAD\_REG. Each register is identified by a 9-bit Register Id.

These registers are different from the registers that are mapped into the 82786's On-Chip-Memory (I/O) space, i.e., they are accessible only through the DUMP\_REG and the LOAD\_REG command. There are four user accessible graphics registers. They are listed below.

| REGISTER                     | REGISTER—ID                                    | REGISTER                                                                                                  |

|------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| NAME                         | (# of bits)                                    | FUNCTION                                                                                                  |

| GPOEM<br>GIMR<br>GSP<br>GCNT | 0003 (6)<br>0004 (8)<br>010C (21)<br>0015 (16) | Poll Mask<br>Interrupt Mask<br>Stack Pointer<br>Character Count while<br>drawing characters in<br>bit-map |

There are some other registers in the Graphics Processor. These registers are normally of no use to a user except in the event of saving and restoring them during a CPU context switch. Any other direct access to these registers must be avoided.

| REGISTER<br>NAME | REGISTER—ID<br>(# of bits) |

|------------------|----------------------------|

| GP REG 5         | 0007 (2,2)                 |

| GP REG 6         | 010B (21)                  |

| GP REG 7         | 010D (21)                  |

| GP REG 8         | 010F (21)                  |

| GP REG 9         | 0010 (16)                  |

| GP REG 10        | 0011 (16)                  |

| GP REG 11        | 0012 (16)                  |

| GP REG 12        | 0013 (16)                  |

| GP REG 13        | 0016 (16)                  |

| GP REG 14        | 001C (4)                   |

| GP REG 16        | 0090 (16)                  |

| GP REG 17        | 0091 (16)                  |

| GP REG 18        | 0096 (16)                  |

| GP REG 19        | 0097 (16)                  |

| GP REG 20        | 0099 (16)                  |

| GP REG 21        | 009B (16)                  |

| GP REG 22        | 009C (16)                  |

# Graphics Processor Exception Handling

The status bits GPOLL, GRCD, GINT, GPSC, GBCOV, GBMOV, GCTP, and GIBMD are capable of generating an interrupt to the CPU depending upon the Interrupt Mask Register (GIMR). If the corresponding bit in the GIMR is a "0" an interrupt is generated. If another bit in the Graphics Processor Status Register is set before an acknowledgement for a previously generated interrupt, then another interrupt is not generated. Reading the Status Register serves the purpose of an Interrupt Acknowledge to the Graphics Processor. Reading the Graphics Processor Status Register clears the offending status bit(s) - bits not masked out in the Interrupt Mask. If the interrupt is generated due to the GPOLL bit, then this bit is not cleared on an interrupt acknowledge. However this does not generate repeated interrupts.

The status bits GINT, GPSC, GBCOV, GBMOV, GTRP and GIBMD can also cause the Graphics Processor to stop its normal instruction fetch/execution and enter the POLL state. This is determined by the contents of the POLL on Exception Mask register (GPOEM). The GPOEM is 6 bits wide. If the corresponding bit in the GPOEM is a "0", the POLL state is entered. On entering the POLL state, the internal GECL bit in the GR0 register is automatically set. When the processor is in the POLL state, it can be restarted by writing the appropriate opcode into the register GR0 (which writes a zero into the GECL bit). The act of clearing the GECL bit also causes the status bits that caused the POLL state to be cleared. Interrupt generation due to the GPOLL bit is enabled on exit from the POLL state.

The status bit GRCD when set, always causes the Graphics Processor to enter the Poll State. The Interrupt and the POLL mechanisms are two independent mechanisms. It is possible for the Graphics Processor to issue an interrupt and not POLL, or to issue an interrupt and POLL, or not to issue an interrupt and POLL or do none of them - all depending upon the GIMR and the GPOEM Register.

#### **Initialization And Software Abort**

There are two ways to force the Graphics Processor to enter the POLL state:

- i) An attempt to write into the Graphics Processor Status Register is considered a software ABORT signal.

- ii) An attempt to write into the Graphics Current Instruction Pointer also initiates a software ABORT.

The ABORT signal causes the Graphics Processor to enter POLL state after the execution of the currently executing command.

Upon RESET, the Graphics Processor immediately enters a well defined state. The following events take place:

- 1. Command execution is halted and the Graphics Processor enters the POLL state.

- 2. The GECL bit of register GR0 is set to indicate an End of Command List.

- 3. All status bits except GPOLL are cleared. GPOLL is set.

- 4. Interrupt Mask Register (GIMR) is set to all ones (disabled).

- 5. Poll on Exception Mask register (GPOEM) is set to all ones (disabled).

- 6. Graphics Processor exits the pick mode.

The Graphics Processor command set is divided into the following classes:

- 1. Non-Drawing Commands

- 2. Drawing Control Commands

- 3. Geometric Commands

- 4. Bit Block Transfer (BitBlt) Commands

- 5. Character Block Transfer (CharBlt) Commands

| Command               | Opcode | Command          | Opcode |

|-----------------------|--------|------------------|--------|

| LINK                  | 02     | DEF_CHAR_ORIENT  | 4E     |

| NOP                   | 03     | ABSMOVE          | 4F     |

| DEFTEXTUREOPAQUE      | 06     | RELMOVE          | 52     |

| DEFTEXTURETRANSPARENT | 07     | POINT            | 53     |

| DEFCHARSETWORD        | 0A     | LINE             | 54     |

| DEF_CHAR_SET_BYTE     | 0B     | RECT             | 58     |

| INTR_GEN              | 0E     | BITBLT           | 64     |

| ENTER_MACRO           | 0F     | ARC_EXCLUSION    | 68     |

| EXITMACRO             | 17     | ARC_INCLUSION    | 69     |

| DEFBITMAP             | 1A     | POLYGON          | 73     |

| DUMPREG               | 29     | POLYLINE         | 74     |

| LOAD_REG              | 34     | CIRCLE           | 8E     |

| DEF_COLOR             | 3D     | CHAROPAQUE       | A6     |

| DEFLOGICALOP          | 41     | CHAR_TRANSPARENT | A7     |

| ENTER_PICK            | 44     | BITBLTM          | AE     |

| EXITPICK              | 45     | INCRPOINT        | B4     |

| DEF_CLIP_RECT         | 46     | HORIZ_LINES      | BA     |

| DEFCHARSPACE          | 4D     |                  |        |

#### List of Graphics Processor Commands (Higher Byte - Hex)

82786

#### NON-DRAWING COMMANDS

| NOP = No Operation            | 0300h | ]                |                   |             |

|-------------------------------|-------|------------------|-------------------|-------------|

| LINK = Link to Next Command   | 0200h | Link Address Low | Link Address High |             |

| INTR_GEN = Generate Interrupt | 0E00h |                  |                   |             |

| DUMP_REG = Dump Register      | 2900h | Dump Address Low | Dump Address High | Register ID |

| LOAD_REG = Load Register      | 3400h | Load Address Low | Load Address High | Register ID |

| ENTER_MACRO = Enter Macro     | 0F00h | Macro Addr Low   | Macro Addr High   |             |

| EXITMARCO = Exit Macro        | 1700h |                  |                   |             |

| HALT = Enter Poll State       | xxx1h |                  |                   |             |

#### DRAWING CONTROL COMMANDS

| DEFBITMAP = Define bit-map                         | 1A00h      | Origin Addr Low  | Origin Addr High                   | Xmax | Ymax | Bits/pixel |

|----------------------------------------------------|------------|------------------|------------------------------------|------|------|------------|

| DEFCLIPRECT = Define Clip<br>Rectangle             | 4600h      | xmin             | ymin                               | xmax | ymax | ]          |

| DEFCOLORS = Define Colors                          | 3D00h      | Foreground Color | Background Color                   |      |      |            |

| DEF_TEXTURE = Define Texture<br>Opaque/Transparent | 0600/0700h | Pattern          | ]                                  |      |      |            |

| DEF_LOGICAL_OP = Define<br>Logic Operation         | 4100h      | Color Bit Mask   | Function Code<br>(see table below) |      |      |            |

The functions performed and their codes are:

| FCODE | FUNCTION              | FCODE | FUNCTION                    |

|-------|-----------------------|-------|-----------------------------|

| 0000  | 0                     | 1000  | CMP (source) AND CMP (dest) |

| 0001  | source AND dest       | 1001  | CMP (source) XOR dest       |

| 0010  | CMP (source) AND dest | 1010  | CMP (source)                |

| 0011  | dest                  | 1011  | CMP (source) OR dest        |

| 0100  | source AND CMP(dest)  | 1100  | CMP (dest)                  |

| 0101  | source                | 1101  | source OR CMP (dest)        |

| 0110  | source XOR dest       | 1110  | CMP (source) OR CMP (dest)  |

| 0111  | source OR dest        | 1111  | 1                           |

| DEFCHARSET = Define Character Set<br>(Word/Byte mode) | 0A00/0B00h | Font Addr Low  | Font Addr High |

|-------------------------------------------------------|------------|----------------|----------------|

| DEF_CHAR_ORIENT = Define Char Orientation             | 4000h      | Path /Rotation |                |

There are four defined values for both the path and rotation. They are:

| CODE | INCREMENT   |

|------|-------------|

| 00   | 0 degrees   |

| 01   | 90 degrees  |

| 10   | 180 degrees |

| 11   | 270 degrees |

| DEF_CHAR_SPACE = Define Inter Char Space | 4D00h | Inter Char Space |              |

|------------------------------------------|-------|------------------|--------------|

| ABS_MOV = Move                           | 4F00h | x coordinate     | y coordinate |

| REL_MOV = Relative Move                  | 5200h | dx               | dy           |

| ENTER_PICK = Enter Pick Mode             | 4400h |                  |              |

| EXIT_PICK = Exit Pick Mode               | 4500h |                  |              |

#### **GEOMETRIC COMMANDS**

| POINT = Draw Point                   | 5300h | dx             | dy              |              |

|--------------------------------------|-------|----------------|-----------------|--------------|

| INCR_POINT = Draw Incremental Points | B400h | Array Addr Low | Array Addr High | N (# of pts) |

#### **INCREMENTAL POINTS ARRAY**

| INC4 | INC3 | INC2   | INC1   |

|------|------|--------|--------|

|      | _    | —      | —      |

|      | incN | incN-1 | incN-2 |

The upper two bits of the "inc" field specify the increment for the x coordinate while the lower two bits specify the increment for the y coordinate, The encoding for the two bits is as follows:

| CODE | INCREMENT |

|------|-----------|

| 00   | 0         |

| 01   | +1        |

| 10   | -1        |

| 11   | Unused    |

| LINE = Draw Line                                 | 5          | 5400h        | dx               | dy                                                  |                |

|--------------------------------------------------|------------|--------------|------------------|-----------------------------------------------------|----------------|

| CIRCLE = Draw Circle                             | 8          | E00h         | radius           |                                                     |                |

| RECT = Draw Rectangle                            | 5          | 5800h        | dx               | dy                                                  |                |

| POLYLINE = Draw Polyline                         | 7          | 7400h        | Array Addr Low   | Array Addr High                                     | N (# of lines) |

| POLYGON = Draw Polygon                           | 7          | 7300h        | Array Addr Low   | Array Addr High                                     | N (# of lines) |

| POLYLINE/POLYGON ARRAY                           |            | ł            | HORIZONTAL L     | INE ARRAY                                           |                |

| dx1<br>dy1<br><br>dxN<br>dyN                     |            |              |                  | dxy<br>dyl<br>deltaX1<br>—<br>dxN<br>dyn<br>deltaXN |                |

| ARC = Draw Arc<br>(Exclusion/Inclusion)          | 6800/6900h | dxmin        | dymin            | dxmax                                               | dymax radius   |

| HORIZ_LINES = Draw Series of<br>Horizontal Lines | BA00/BA01h | Array Addr L | _ow Array Addr H | ligh N (# of lines)                                 | ]              |

82786

#### **BITBLT COMMANDS**

| BITBLT = Bit Block Transfer                     | 6400h       | Source x coord  | Source y coord   | dx     | dy     |

|-------------------------------------------------|-------------|-----------------|------------------|--------|--------|

| within bit-map                                  | AE00h       | Source Addr Low | Source Addr High | Source | e Xmax |

| BITBITM = Bit Block Transfer<br>across bit-maps | Source Ymax | Source x coord  |                  | dx     | dy     |

#### CHARBLT COMMANDS

|                              |            |                |                 |              | Ł |

|------------------------------|------------|----------------|-----------------|--------------|---|

| CHAR = Draw Character String | A600/A700h | String Ptr Low | String Ptr High | N(# of char) |   |

| (opaque/transparent)         |            |                |                 |              |   |

#### CHARACTER STRING FORMAT

| Word Mode |  |

|-----------|--|

| char1     |  |

| char2     |  |

|           |  |

| charN     |  |

|           |  |

#### **DISPLAY PROCESSOR**

#### Introduction

The Display Processor (Display Processor) is an independent processor responsible for controlling the display of video data on a CRT, laser printer and other display devices. Its functions include the generation of horizontal and vertical timing signals, blanking signal and the control of 8 Video Data output pins.

| Byte  | Mode    |

|-------|---------|

| char2 | char1   |

| char4 | char3   |

|       |         |

| charN | charN-1 |

The 82786 can function in two distinct types of graphics memory environments – i) using single port DRAMs (normal display mode) and ii) using dual port video DRAMs (VRAM mode). When the 82786 is configured to interface with single port DRAMs, the Display Processor uses the BIU to fetch the screen parameters and display data from memory. The Display Processor then internally shifts the video data into the video stream for screen refresh. When configured to run with VRAMs, the Display Processor uses the BIU to load the shift registers in the VRAMs at the beginning of every scan line. The screen

refresh is then done by the second port of the VRAMs. The BIU and Graphics Processor have the rest of the scan line time to access the graphics memory.

# **Bit Map Organization**

The Display Processor is optimized to display data in packed bit-map form. The Graphics Processor writes pixel data in the memory in this form. The Display Processor supports display of 1, 2, 4 or 8 bits/pixel data, stored in sequential bit-map form, with the first (left-hand) pixel to be displayed occupying the Most Significant Bit(s) of a word in memory, and subsequent pixels occupying sequentially lower bits in the word. Ascending word addresses represent subsequent pixels, moving left to right and top to bottom on the screen.

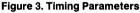

#### Windows and Normal Display Mode

In the normal display mode, Windows may be displayed on the screen in a flexible format. There can be up to 16 window segments or tiles appearing on any single display line. There is no limit on the number of windows vertically (limited by the number of scan lines in the active display area). At the basic video rate (25 MHz, 8 bpp), these windows may be placed at pixel resolution on the screen, and mapped at pixel resolution into the bit-map. Windows can be made to overlap, by breaking the windows into tiles and assembling the tiles on the screen.

# Cursor (Normal Display Mode)

The Display Processor supports a single hardware cursor which may be  $8 \times 8$  pixels or  $16 \times 16$  pixels. This cursor may be positioned anywhere on the screen with a pixel resolution. The cursor may be defined to be transparent or opaque, and may be either a block cursor with its hot-spot at the top-left of the cursor pattern, or a cross-hair cursor one pixel across, stretching the width and height of the screen with its hot-spot at the center of the corsor. The cursor color and pattern (shape) are programmable. The cursor may be programmed off if not required, or to implement a blinking cursor.

# Video Rates (Normal Display Mode)

The Display Processor is clocked from an external Video Clock. In this mode, the 82786 fetches video data from memory into an internal FIFO. An internal shift register then generates the serial video data

stream to the display. The 82786 will support CRT screens of up to about 640 x 480 pixels at 8 bits/pixel and 60 Hz non-interlaced, or about 1024 x 640 x 8 at 60 Hz interlaced. The Display Processor supports Interlaced, non-interlaced and interlace-sync displays.

The Display Processor also has higher speed modes which enable the user to trade off bits/pixel for dotrate. Thus it is possible to run at a maximum of 8 bpp with a 25 MHz dot-rate, 4 bpp at a 50 MHz dot-rate, 2 bpp at a 100 MHz dot-rate or 1 bpp at 200 MHz dot-rate; with corresponding increase in size and resolution. Note that in the high speed modes, horizontal window and cursor placement resolution is reduced to 2, 4 or 8 pixel resolution at 50 MHz, 100 MHz, or 200 MHz rates respectively.

# **VRAM Mode**

In the VRAM mode, the first tile for every scan line is used to load the shift register in the VRAMs by executing a data transfer cycle. Subsequent tiles (if any) for all strips will still be available through the VDATA pins of the 82786. The window status bits can be used to internally multiplex the VRAM video stream and the 82786 generated video stream. The address for this data transfer cycle is determined from the Tile Descriptor. The 82786 BEN# pin is used as a DT pin for this case. If the graphics memory banks are interleaved, then both banks are loaded in the transfer cycle. During the Blank period, Default VData appears on the VDATA pins.

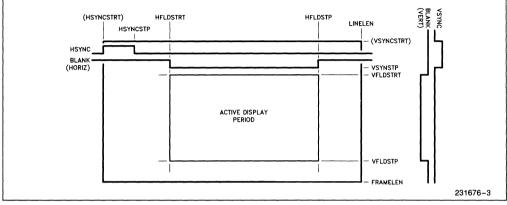

# **CRT Controller**

CRT timing signals HSYNC, VSYNC, and BLANK are each programmable at a pixel resolution, giving a maximum display size of  $4096 \times 4096$  pixels. If high-speed or very-high-speed display modes are selected, the horizontal resolution of the CRT timing signals becomes 2 pixels, 4 pixels or 8 pixels at 50 MHz, 100 MHz and 200 MHz respectively.

# **Window Status**

The HSync and VSync CRT timing pins may be configured to serve as Window Status output pins, which can be programmed to present a predefined code while the Tile Processor is displaying a tile. This code is programmable as part of the Tile Descriptor, and may be used externally to multiplex in video data from another source, or select a pallette range for a particular window, etc. External logic must be used to enable VSync and HSync as CRT timing signals when Blank is high, and as encoded Window Status signals when Blank is low. This is valid in both DRAM and VRAM modes.

# **Zoom Support**

The Display Processor allows windows to be zoomed in the normal display mode. The zoom factor is an integer between 1 and 64. There are independent zoom factors for the x and y direction. The zoom function results in pixel replication.

All zoomed windows on a display are zoomed by the same amount. A window is therefore either zoomed or not zoomed. Zoom offset is not supported—a pixel must either be fully displayed or not displayed at all. This places a restriction on window placement a window may not be placed such that a zoomed pixel is partially obscured. VRAM displays can be zoomed vertically by using this feature. Horizontal zooming of VRAM windows requires external hardware support.

# **Extended 82786 Systems**

The CRT timing signal pins may be configured as output pins (for the normal stand-alone 82786 system), or as input pins for a system in which multiple 82786's are ganged in parallel to provide a greater number of bits/pixel, higher dot rates, larger display area, or more windows. In multiple 82786 systems, each of the Display Processors run in lock step, allowing the individual outputs to be combined on a single display. The HSync, VSync and Blank pins for the "Slave" 82786 are configured as inputs and are driven by the "Master" 82786.

When programmed as inputs, VSync and HSync still serve as outputs for Window Status while Blank is inactive.

# **External Video Source**

The HSync and VSync pins on the 82786 can be configured as inputs to synchronize the 82786 to external video sources (VCR, broadcast TV etc.). In this case, the Blank pin is configured as output and the active 82786 display period is determined by the programmed 82786 parameters.

# **Memory Bandwidth Requirements**

The memory bandwidth required by the Display Processor depends on the display size and mode of operation. The 82786 has a 40 Mbyte/sec maximum bandwidth during fast block accesses to Graphics Memory. In the normal display mode the Display Processor makes use of these fast block reads for screen refresh, thereby minimizing its use of the memory bus, which the other 82786 modules share. For worst-case displays, when the Display Processor is running at its maximum speed of 25 MHz and 8 bits/pixel, about 50% of the memory bandwidth is used for display refresh. Correspondingly, at only 1 bit/pixel the Display Processor's bus requirements are reduced to about one-eighth of its requirement at 8 bpp. In the VRAM mode, the Display Processor does not fetch any of the display data. The display data is passed directly from the graphics memory to the pixel logic. In this case about 1% of the graphics memory bandwidth is required by the Display Processor to fetch the Strip Descriptors. The Display Processor Access to memory can be "tuned" through a programmable trip point for the Display Processor Data FIFO. This controls the length and frequency of block transfers to fill the FIFO of display data fetches.

#### **Display Processor Registers**

There are two different register sets for the Display Processor. Six of the 82786 Internal Registers are dedicated to the Display Processor. These registers are memory (or I/O) mapped in the external CPU address space. They can therefore be directly accessed by the external CPU. Another set of registers is totally local to the Display Processor. These are the display control registers and are used for display parameters.

# 82786 Registers For Display Processor

There are six of these Registers. They are listed below:

| Address   | Function                 |

|-----------|--------------------------|

| Base + 40 | Display Processor Opcode |

| Base + 42 | Param1                   |

| Base + 44 | Param2                   |

| Base + 46 | Param3                   |

| Base + 48 | Display Processor Status |

| Base + 4A | Default Video            |

The Display Processor Opcode and the three parameter registers are used to send a command to the Display Processor. The Display Processor Status Register contains the status for the Display Processor. This is described in more detail later. The Default Video Register contains the data that appears on the Video Out pins during the blanking intervals. The CPU can use this register to address an external pallette RAM while loading the pallette, thereby eliminating a separate address path and external logic.

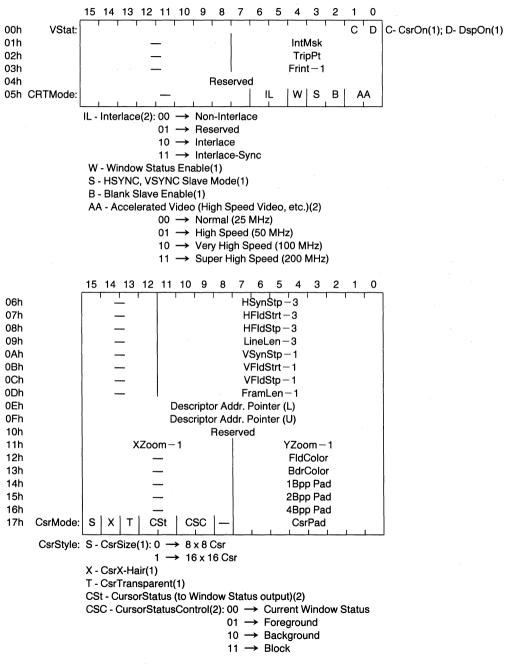

# **Display Control Registers**

The display control registers can be loaded under control of the Display Processor during the Vertical Blanking interval. This synchronizes parameter updates with display refresh and ensures that the display remains clean, with no updates occurring during data display.