© INTEL CORPORATION, 1983

ORDER NUMBER: 210973-001

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein

Intel retains the right to make changes to these specifications at any time, without notice

Contact your local sales office to obtain the latest specifications before placing your order

The following are trademarks of Intel Corporation and may only be used to identify Intel Products

BXP, CREDIT, I, ICE, I<sup>2</sup>ICE, ICS, IDBP, IDIS, ILBX, I<sub>m</sub>, IMMX, Insite, INTEL, int<sub>e</sub>l, Intelevision, Intellec, int<sub>e</sub>ligent Identifier<sup>™</sup>, int<sub>e</sub>IBOS, int<sub>e</sub>ligent Programming<sup>™</sup>, Intellink, iOSP, IPDS, IRMS, ISBC, ISBX, ISDM, ISXM, Library Manager, MCS, Megachassis, Micromainframe, MULTIBUS, Multichannel<sup>™</sup> Plug-A-Bubble, MULTIMODULE, PROMPT, Ripplemode, RMX/80, RUPI, System 2000, and UPI, and the combination of ICE, ICS, IRMX, ISBC, MCS, or UPI and a numerical suffix

MDS is an ordering code only and is not used as a product name or trademark MDS<sup>®</sup> is a registered trademark of Mohawk Data Sciences Corporation.

\* MULTIBUS is a patented Intel bus.

Additional copies of this manual or other Intel literature may be obtained from

Intel Corporation Literature Department 3065 Bowers Avenue Santa Clara, CA 95051

# INTRODUCTION TO THE 80186 MICROPROCESSOR

### CONTENTS

| 1. INTRODUCTION                                             | 1<br>2      |

|-------------------------------------------------------------|-------------|

| 2.1 The CPU                                                 | 2           |

| 2.2 80186 CPU Enhancements                                  | 2<br>2<br>3 |

| 2.3 DMA Unit                                                | 3           |

| 2.4 Timers                                                  | - 3         |

| 2.5 Interrupt Controller                                    | 3           |

| 2.6 Clock Generator<br>2.7 Chip Select and Ready Generation | 3           |

| 2.7 Chip Select and Ready Generation                        |             |

| Unit<br>2.8 Integrated Peripheral Accessing                 | 3           |

| 2.8 Integrated Peripheral Accessing                         | 3           |

| 3. USING THE 80186                                          | 4           |

| 3.1 Bus Interfacing to the 80186                            | 4           |

| 3.1.1 Overview                                              | 4           |

| 3.1.2 Physical Address Generation                           | 5           |

| 3.1.3 80186 Data Bus Operation                              | 7           |

| 3.1.4 80188 Data Bus Operation                              | 7           |

| 3.1.5 General Data Bus Operation                            | 8           |

| 3.1.6 Control Signals                                       | 9           |

| 3.1.6.1 RD and WR                                           | 9           |

| 3.1.6.2 Queue Status Signals                                | 11          |

| 3.1.6.3 Status Lines                                        | 11<br>11    |

| 3.1.7 HALT Timing                                           | 12          |

| 3.1.8 8288 and 8289 Interfacing                             | 12          |

| 3.1.9 Ready Interfacing                                     | 13          |

| 3.1.10 Bus Performance Issues                               | 16          |

| 3.2 Example Memory Systems                                  | 16          |

| 3.2.1 2764 Interface                                        | 16          |

| 3.2.2 2186 Interface                                        | 17          |

| 3.2.3 8203 DRAM Interface                                   | 19          |

| 3.2.4 8207 DRAM Interface                                   | 19          |

| 3.3 HOLD/HLDA Interface                                     | 21          |

| 3.3. LEULU Response                                         | 21          |

| 3.3.2 HOLD/HLDA Timing and Bus                              |             |

| Latency      3.3.3 Coming out of hold                       | 21          |

| 3.3.3 Coming out of hold                                    | 23          |

| 3.4 Differences Between the 8086 bus                        |             |

| and the 80186 Bus                                           | 23          |

| 4. DMA UNIT INTERFACING                                     | 26          |

| 4.1 DMA Features                                            | 26          |

| 4.2 DMA Unit Programming<br>4.3 DMA Transfers               | 26          |

| 4.4 DMA Requests                                            | 28<br>28    |

| 4.4.1 DMA Requests timing and                               | 20          |

| latency                                                     | 28          |

| 4.5 DMA Acknowledge                                         | 20<br>30    |

| 4.6 Internally Generated DMA                                | 30          |

| Requests                                                    | 30          |

| 4.7 Externally Synchronized DMA                             | 50          |

| Transfers                                                   | 30          |

|                                                             |             |

|    | 4.7.1 Source Synchronized DMA                                                                   |             |

|----|-------------------------------------------------------------------------------------------------|-------------|

|    | Transfers<br>4.7.2 Destination Synchronized DMA                                                 | 30          |

|    | 4.7.2 Destination Synchronized DMA                                                              |             |

|    | Transfers                                                                                       | 30          |

|    | 4.8 DMA Halt and NMI                                                                            | 32          |

|    | 4.9 Example DMA Interfaces                                                                      | 32<br>32    |

|    | 4.9.1 8272 Floppy Disk Interface<br>4.9.2 8274 Serial Communication                             | 52          |

|    | Interface                                                                                       | 34          |

| 5. | Interface                                                                                       | 34          |

|    | 5.1 Timer Operation                                                                             | 34          |

|    | 5.2 Timer Registers<br>5.3 Timer Events                                                         | 34          |

|    | 5.3 Timer Events                                                                                | 37          |

|    | 5.4 Timer Input Pin Operation                                                                   | 37          |

|    | 5.5 Timer Output Pin Operation                                                                  | 38          |

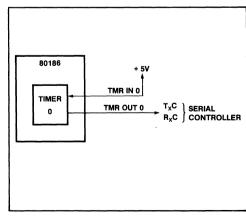

|    | 5.6 Sample 80186 Timer Applications .<br>5.6.1 80186 Timer Real Time Clock                      | 38<br>39    |

|    | 5.6.2 80186 Timer Baud Rate                                                                     | 39          |

|    | Generator                                                                                       | 39          |

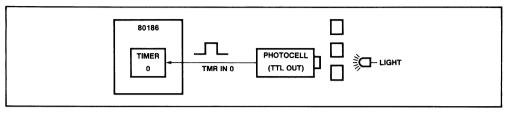

|    | 5.6.3 80186 Timer Event Counter                                                                 | 39          |

| 6. | . 80186 INTERRUPT CONTROLLER                                                                    |             |

|    |                                                                                                 | 40          |

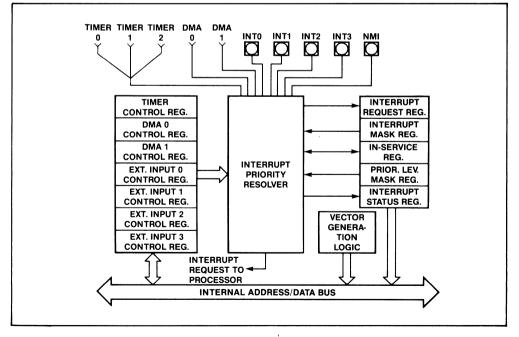

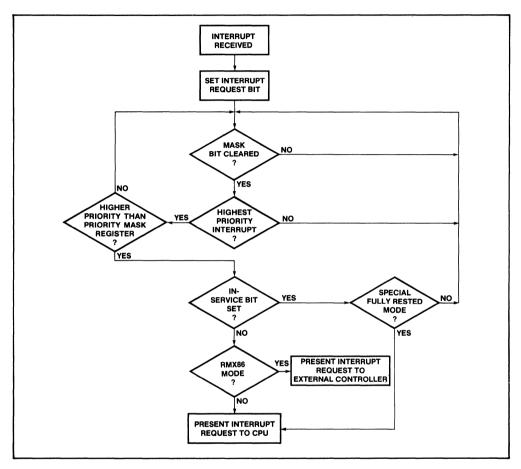

|    | 6.1 Interrupt Controller Model                                                                  | 40          |

|    | <ul><li>6.2 Interrupt Controller Operation</li><li>6.3 Interrupt Controller Registers</li></ul> | 40          |

|    | 6.3 Interrupt Controller Registers                                                              | 40          |

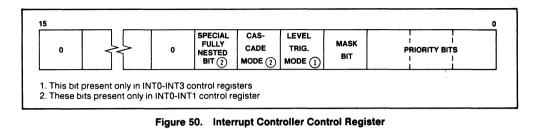

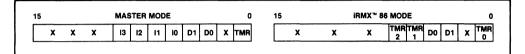

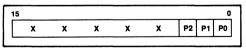

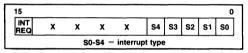

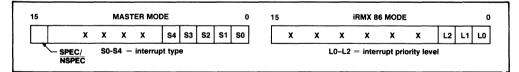

|    | 6.3.1 Control Registers<br>6.3.2 Request Register                                               | 40<br>41    |

|    | 6.3.3 Mask Register and Priority Masl                                                           |             |

|    | Register                                                                                        | <b>`</b> 41 |

|    | Register       6.3.4 In-Service Register                                                        | 41          |

|    | 6.3.5 Poll and Poll Status Registers .                                                          | 42          |

|    | 6.3.6 End of Interrupt Register                                                                 | 42          |

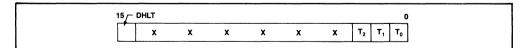

|    | 6.3.7 Interrupt Status Register<br>6.3.8 Interrupt Vector Register                              | 43          |

|    | 6.3.8 Interrupt Vector Register                                                                 | 43          |

|    | 6.4 Interrupt Sources                                                                           | 43          |

|    | 6.4.1 Internal Interrupt Sources<br>6.4.2 External Interrupt Sources                            | 43          |

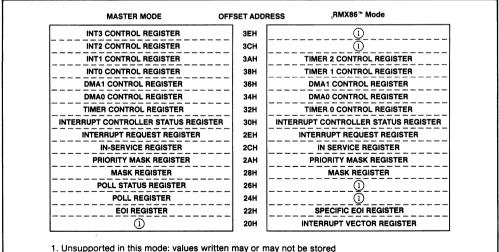

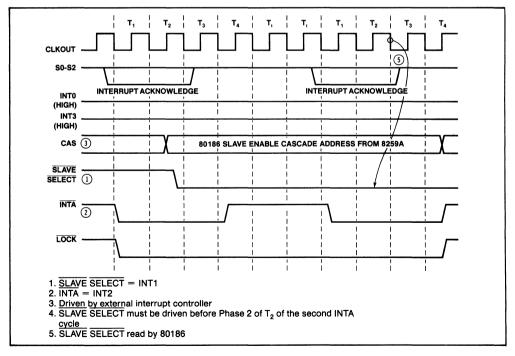

|    | 6.4.3 iRMX 86 Mode Interrupt                                                                    | . 43        |

|    | Sources                                                                                         | 44          |

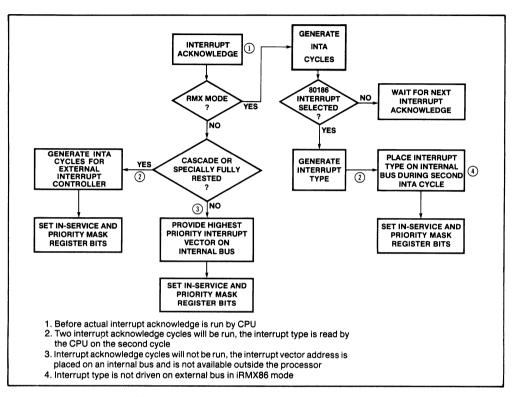

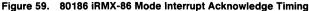

|    | 6.5 Interrupt Response                                                                          |             |

|    | 6.5.1 Internal Vectoring, Master                                                                |             |

|    | Mode                                                                                            | 45          |

|    | 6.5.2 Internal Vectoring, iRMX 86                                                               |             |

|    | Mode                                                                                            | 46          |

|    | 6.5.3 External Vectoring                                                                        | 47          |

|    | 6.6 Interrupt Controller External                                                               | 47          |

|    | Connections                                                                                     | . 47<br>48  |

|    | 6 6 2 Cascade Mode                                                                              | 40          |

|    | 6.6.2 Cascade Mode<br>6.6.3 Special Fully Nested Mode                                           | 48          |

|    |                                                                                                 |             |

| 6.6.4 iRMX 86 Mode                    | 49   |

|---------------------------------------|------|

| 6.7 Example 8259A/Cascade Mode        |      |

| Interface                             | 50   |

| 6.8 Example 80130 iRMX 86 Mode        |      |

| Interface                             | 50   |

| 6.9 Interrupt Latency                 | 50   |

| 7. CLOCK GENERATOR                    | 51   |

| 7.1 Crystal Oscillator                | 51   |

| 7.2 Using an External Oscillator      | 51   |

| 7.3 Clock Generator                   | 52   |

| 7.4 Ready Generation                  | 52   |

| 7.5 Reset                             | 52   |

| 8. CHIP SELECTS                       | 52   |

| 8.1 Memory Chip Selects               | 53   |

| 8.2 Peripheral Chip Selects           | 53   |

| 8.3 Ready Generation                  | 53   |

| 8.4 Examples of Chip Select Usage     | 54   |

| 8.5 Overlapping Chip Select Areas     | 54   |

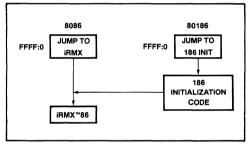

| 9. SOFTWARE IN AN 80186 SYSTEM        | 55   |

| 9.1 System Initialization in an 80186 |      |

| Śystem                                | 55   |

| 9.2 Initialization for iRMX 86        | . 55 |

| 9.3 Instruction Execution Differences |      |

| Between the 8086 and 80186            | 55   |

| 10. CONCLUSIONS                       | 56   |

|                                       |      |

| APPENDIX A — Peripheral Control             |    |

|---------------------------------------------|----|

| Block                                       | 58 |

| A.1 Setting the Base Location of the        |    |

| Peripheral Control Block                    | 58 |

| A.2 Peripheral Control Block Registers      | 59 |

| APPENDIX B — Synchronizers                  | 60 |

| B.1 Why Synchronizers Are Required .        | 60 |

| B.2 80186 Synchronizers                     | 60 |

| APPENDIX C — 80186 Example DMA              |    |

| Interface Code                              | 61 |

| APPENDIX D — 80186 Example Timer            |    |

| Interface Code                              | 64 |

| <b>APPENDIX E — 80186 Example Interrupt</b> |    |

| Controller Interface Code                   | 68 |

| APPENDIX F — 80186/8086 Example             |    |

| System Initialization Code                  | 70 |

| APPENDIX G — 80186 Wait State               |    |

| Performance                                 | 72 |

| APPENDIX H — 80186 New                      |    |

| Instructions                                | 76 |

| APPENDIX I — 80186/80188                    |    |

| Differences                                 | 78 |

#### 1. INTRODUCTION

As state of the art technology has increased the number of transistors possible on a single integrated circuit, these devices have attained new, higher levels of both performance and functionality. Riding this crest are the Intel 80186 and 80286 microprocessors. While the 80286 has added memory protection and management to the basic 8086 architecture, the 80186 has integrated six separate functional blocks into a single device.

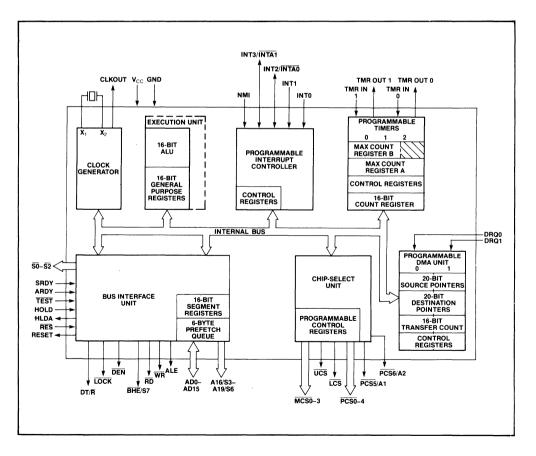

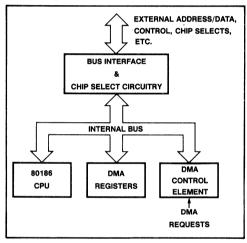

The purpose of this note is to explain, through example, the use of the 80186 with various peripheral and memory devices. Because the 80186 integrates a DMA unit, timer unit, interrupt controller unit, bus controller unit and chip select and ready generation unit with the CPU on a single chip (see Figure 1), system construction is simplified since many of the peripheral interfaces are integrated onto the device.

The 80186 family actually consists of two processors: the 80186 and 80188. The only difference between the two processors is that the 80186 maintains a 16-bit external data bus while the 80188 has an 8-bit external data bus. Internally, they both implement the same processor with the same integrated peripheral components. Thus, except where noted, all 80186 information in this note also applies to the 80188. The implications of having an 8-bit external data bus on the 80188 are explicitly noted in appendix I. Any parametric values included in this note are taken from the iAPX 186 Advance Information data sheet, and pertain to 8Mhz devices.

Figure 1. 80186 Block Diagram

#### 2. OVERVIEW OF THE 80186

#### 2.1 The CPU

The 80186 CPU shares a common base architecture with the 8086, 8088 and 80286. It is completely object code compatible with the 8086/88. This architecture features four 16-bit general purpose registers (AX,BX, CX,DX) which may be used as operands in most arithmetic operations in either 8 or 16 bit units. It also features four 16-bit "pointer" registers (SI,DI,BP,SP) which may be used both in arithmetic operations and in accessing memory based variables. Four 16-bit segment registers (CS,DS,SS,ES) are provided allowing simple memory partitioning to aid construction of modular programs. Finally, it has a 16-bit instruction pointer and a 16-bit status register.

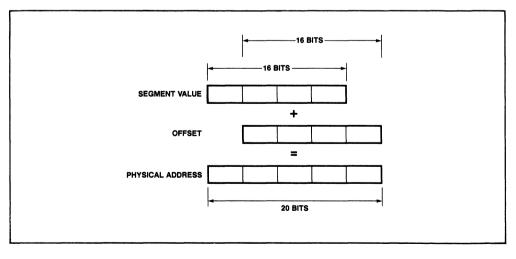

Physical memory addresses are generated by the 80186 identically to the 8086. The 16-bit segment value is left shifted 4 bits and then is added to an offset value which is derived from combinations of the pointer registers, the instruction pointer, and immediate values (see Figure 2). Any carry out of this addition is ignored. The result of this addition is a 20-bit physical address which is presented to the system memory.

The 80186 has a 16-bit ALU which performs 8 or 16-bit arithmetic and logical operations. It provides for data movement among registers, memory and I/O space. In addition, the CPU allows for high speed data transfer from one area of memory to another using string move instructions, and to or from an I/O port and memory using block I/O instructions. Finally, the CPU provides a wealth of conditional branch and other control instructions.

In the 80186, as in the 8086, instruction fetching and instruction execution are performed by separate units: the bus interface unit and the execution unit, respectively. The 80186 also has a 6-byte prefetch queue as does the 8086. The 80188 has a 4-byte prefetch queue as does the 8088. As a program is executing, opcodes are fetched from memory by the bus interface unit and placed in this queue. Whenever the execution unit requires another instruction, it takes it out of the queue. Effective processor throughput is increased by adding this queue, since the bus interface unit may continue to fetch instructions while the execution unit executes a long instruction. Then, when the CPU completes this instruction, it does not have to wait for another instruction to be fetched from memory.

#### 2.2 80186 CPU Enhancements

Although the 80186 is completely object code compatible with the 8086, most of the 8086 instructions require fewer clock cycles to execute on the 80186 than on the 8086 because of hardware enhancements in the bus interface unit and the execution unit. In addition, the 80186 provides many new instructions which simplify assembly language programming, enhance the performance of high level language implementations, and reduce object code sizes for the 80186. These new instructions are also included in the 80286. A complete description of the architecture and instruction execution of the 80186 can be found in volume I of the iAPX86/186 users manual. The algorithms for the new instructions are also given in appendix H of this note.

Figure 2. Physical Address Generation in the 80186

#### 2.3 DMA Unit

The 80186 includes a DMA unit which provides two high speed DMA channels. This DMA unit will perform transfers to or from any combination of I/O space and memory space in either byte or word units. Every DMA cycle requires two to four bus cycles, one or two to fetch the data to an internal register, and one or two to deposit the data. This allows word data to be located on odd boundaries, or byte data to be moved from odd locations to even locations. This is normally difficult, since odd data bytes are transferred on the upper 8 data bits of the 16-bit data bus, while even data bytes are transferred on the lower 8 data bits of the data bus.

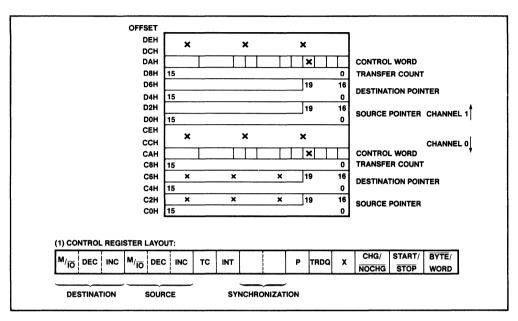

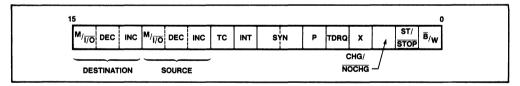

Each DMA channel maintains independent 20-bit source and destination pointers which are used to access the source and destination of the data transferred. Each of these pointers may independently address either I/O or memory space. After each DMA cycle, the pointers may be independently incremented, decremented, or maintained constant. Each DMA channel also maintains a transfer count which may be used to terminate a series of DMA transfers after a pre-programmed number of transfers.

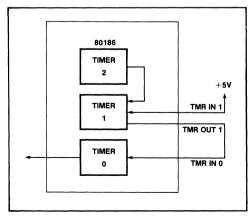

#### 2.4 Timers

The 80186 includes a timer unit which contains 3 independent 16-bit timer/counters. Two of these timers can be used to count external events, to provide waveforms derived from either the CPU clock or an external clock of any duty cycle, or to interrupt the CPU after a specified number of timer "events." The third timer counts only CPU clocks and can be used to interrupt the CPU after a programmable number of CPU clocks, to give a count pulse to either or both of the other two timers after a programmable number of CPU clocks, or to give a DMA request pulse to the integrated DMA unit after a programmable number of CPU clocks.

#### 2.5 Interrupt Controller

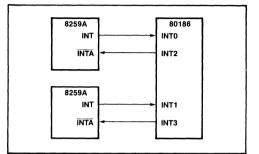

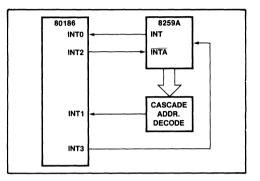

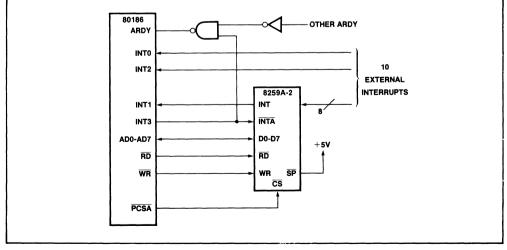

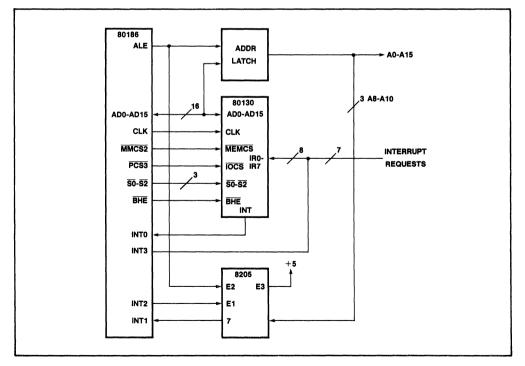

The 80186 includes an interrupt controller. This controller arbitrates interrupt requests between all internal and external sources. It can be directly cascaded as the master to two external 8259A interrupt controllers. In addition, it can be configured as a slave controller to an external interrupt controller to allow complete compatibility with an 80130, 80150, and the iRMX® 86 operating system.

#### 2.6 Clock Generator

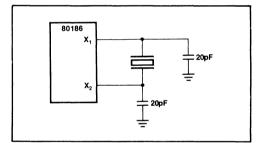

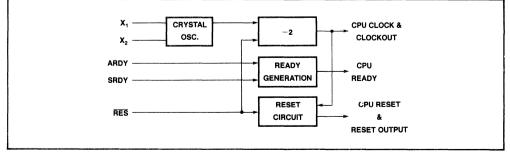

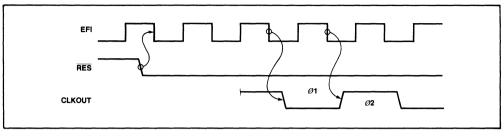

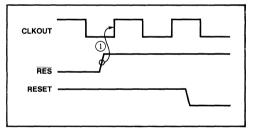

The 80186 includes a clock generator and crystal oscillator. The crystal oscillator can be used with a parallel resonant, fundamental mode crystal at 2X the desired CPU clock speed (i.e., 16 MHz for an 8 MHz 80186), or with an external oscillator also at 2X the CPU clock. The output of the oscillator is internally divided by two to provide the 50% duty cycle CPU clock from which all 80186 system timing derives. The CPU clock is externally available, and all timing parameters are referenced to this externally available signal. The clock generator also provides ready synchronization for the processor.

#### 2.7 Chip Select and Ready Generation Unit

The 80186 includes integrated chip select logic which can be used to enable memory or peripheral devices. Six output lines are used for memory addressing and seven output lines are used for peripheral addressing.

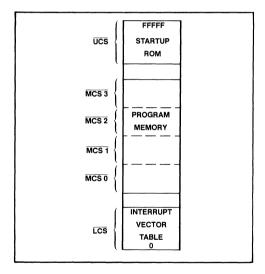

The memory chip select lines are split into 3 groups for separately addressing the major memory areas in a typical 8086 system: upper memory for reset ROM, lower memory for interrupt vectors, and mid-range memory for program memory. The size of each of these regions is user programmable. The starting location and ending location of lower memory and upper memory are fixed at 00000H and FFFFH respectively; the starting location of the mid-range memory is user programmable.

Each of the seven peripheral select lines address one of seven contiguous 128 byte blocks above a programmable base address. This base address can be located in either memory or I/O space in order that peripheral devices may be I/O or memory mapped.

Each of the programmed chip select areas has associated with it a set of programmable ready bits. These ready bits control an integrated wait state generator. This allows a programmable number of wait states (0 to 3) to be automatically inserted whenever an access is made to the area of memory associated with the chip select area. In addition, each set of ready bits includes a bit which determines whether the external ready signals (ARDY and SRDY) will be used, or whether they will be ignored (i.e., the bus cycle will terminate even though a ready has not been returned on the external pins). There are 5 total sets of ready bits which allow independent ready generation for each of upper memory, lower memory, mid-range memory, peripheral devices 0-3 and peripheral devices 4-6.

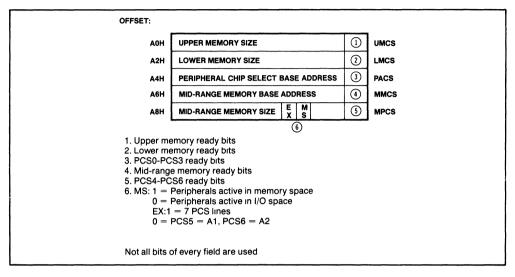

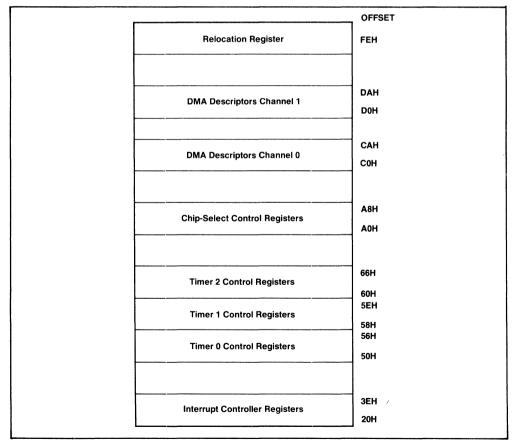

#### 2.8 Integrated Peripheral Accessing

The integrated peripheral and chip select circuitry is controlled by sets of 16-bit registers accessed using standard input, output, or memory access instructions. These peripheral control registers are all located within a 256 byte block which can be placed in either memory or I/O space. Because they are accessed exactly as if they were external devices, no new instruction types are required to access and control the integrated peripherals. For more information concerning the interfacing and accessing of the integrated 80186 peripherals not included in this note, please consult the 80186 data sheet, or volume II of the iAPX86/186'users manual.

#### 3. USING THE 80186

#### 3.1 Bus Interfacing to the 80186

#### 3.1.1 OVERVIEW

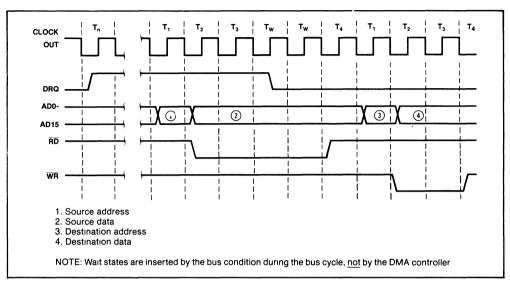

The 80186 bus structure is very similar to the 8086 bus structure. It includes a multiplexed address/data bus, along with various control and status lines (see Table 1). Each bus cycle requires a minimum of 4 CPU clock cycles along with any number of wait states required to accommodate the speed access limitations of external memory or peripheral devices. The bus cycles initiated by the 80186 CPU are identical to the bus cycles initiated by the 80186 integrated DMA unit.

In the following discussion, all timing values given are for an 8 MHz 80186. Future speed selections of the part may have different values for the various parameters.

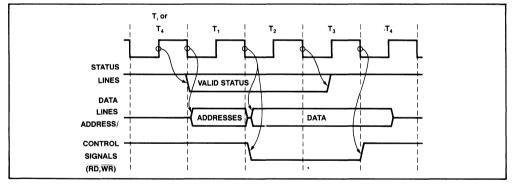

Each clock cycle of the 80186 bus cycle is called a "T" state, and are numbered sequentially  $T_1$ ,  $T_2$ ,  $T_3$ ,  $T_w$  and  $T_4$ . Additional idle T states ( $T_1$ ) can occur between  $T_4$  and  $T_1$  when the processor requires no bus activity (instruction fetches, memory writes, I/O reads, etc.). The ready signals control the number or wait states ( $T_w$ ) inserted in each bus cycle. This number can vary from 0 to positive infinity.

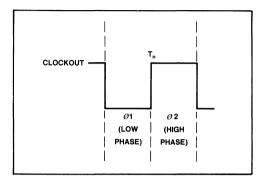

Figure 3. T-state in the 80186

The beginning of a T state is signaled by a high to low transition of the CPU clock. Each T state is divided into two phases, phase 1 (or the low phase) and phase 2 (or the high phase) which occur during the low and high levels of the CPU clock respectively (see Figure 3).

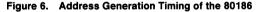

Different types of bus activity occur for all of the Tstates (see Figure 4). Address generation information occurs during  $T_1$ , data generation during  $T_2$ ,  $T_3$ ,  $T_w$  and

Figure 4. Example Bus Cycle of the 80186

| Table 1. | 80186 | Bus | Signals |

|----------|-------|-----|---------|

|----------|-------|-----|---------|

| Function               | Signal Name                                                          |

|------------------------|----------------------------------------------------------------------|

| address/data           | AD0-AD15                                                             |

| address/status         | A16/S3-A19-S6,BHE/S7                                                 |

| co-processor control   | TEST                                                                 |

| local bus arbitration  | HOLD,HLDA                                                            |

| local bus control      | $ALE, \overline{RD}, \overline{WR}, DT/\overline{R}, \overline{DEN}$ |

| multi-master bus       | LOCK                                                                 |

| ready (wait) interface | SRDY,ARDY                                                            |

| status information     | $\overline{S0}-\overline{S2}$                                        |

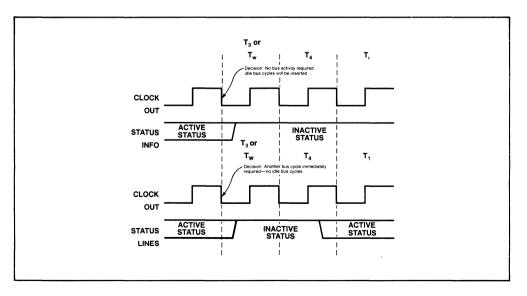

$T_4$ . The beginning of a bus cycle is signaled by the status lines of the processor going from a passive state (all high) to an active state in the middle of the T-state immediately before  $T_1$  (either a  $T_4$  or a  $T_1$ ). Because information concerning an impending bus cycle occurs during the T-state immediately before the first T-state of the cycle itself, two different types of  $T_4$  and  $T_1$  can be generated: one where the T state is immediately followed by a bus cycle, and one where the T state is immediatly followed by an idle T state.

During the first type of  $T_4$  or  $T_1$ , status information concerning the impending bus cycle is generated for the bus cycle immediately to follow. This information will be available no later than  $t_{CHSV}$  (55ns) after the low-tohigh transition of the 80186 clock in the middle of the T state. During the second type of  $T_4$  or  $T_1$  the status outputs remain inactive (high), since no bus cycle is to be started. This means that the decision per the nature of a  $T_4$  or  $T_1$  state (i.e., whether it is immediately followed by a  $T_1$  or a  $T_1$ ) is decided at the beginning of the T-state immediately preceding the  $T_4$  or  $T_1$  (see Figure 5). This has consequences for the bus latency time (see section 3.3.2 on bus latency).

#### 3.1.2 PHYSICAL ADDRESS GENERATION

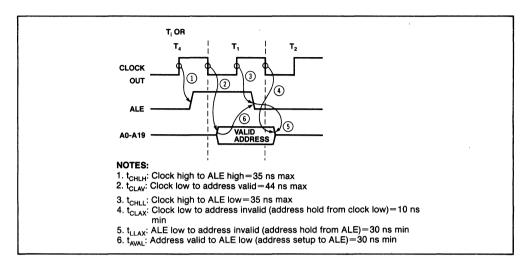

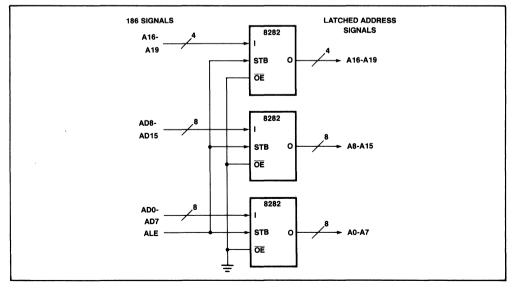

Physical addresses are generated by the 80186 during T<sub>1</sub> of a bus cycle. Since the address and data lines are multiplexed on the same set of pins, addresses must be

latched during  $T_1$  if they are required to remain stable for the duration of the bus cycle. To facilitate latching of the physical address, the 80186 generates an active high ALE (Address Latch Enable) signal which can be directly connected to a transparent latch's strobe input.

Figure 6 illustrates the physical address generation parameters of the 80186. Addresses are guaranteed valid no greater then  $t_{CLAV}$  (44ns) after the beginning of  $T_1$ , and remain valid at least  $t_{CLAX}$  (10ns) after the end of  $T_1$ . The ALE signal is driven high in the middle of the T to state (either  $T_4$  or  $T_1$ ) immediately preceding  $T_1$  and is driven low in the middle of  $T_1$ , no sooner than  $t_{AVAL}$  (30 ns) after addresses become valid. This parameter ( $t_{AVAL}$ ) is required to satisfy the address latch set-up times of address valid until strobe inactive. Addresses remain stable on the address/data bus at least  $t_{LLAX}$  (30 ns) after ALE goes inactive to satisfy address latch hold times of strobe inactive to address invalid.

Because ALE goes high long before addresses become valid, the delay through the address latches will be chiefly the propagation delay through the latch rather than the delay from the latch strobe, which is typically longer than the propagation delay. For the Intel 8282 latch, this parameter is  $t_{IVOV}$  the input valid to output valid delay when strobe is held active (high). Note that the 80186 drives ALE high one full clock phase earlier than the 8086 or the 8288 bus controller, and keeps it high throughout the 8086 or 8288 ALE high time (i.e., the 80186 ALE pulse is wider).

Figure 5. Active-Inactive Status Transitions in the 80186

A typical circuit for latching physical addresses is shown in Figure 7. This circuit uses 3 8282 transparent octal non-inverting latches to demultiplex all 20 address bits provided by the 80186. Typically, the upper 4 address bits are used only to select among various memory components or subsystems, so when the integrated chip selects (see section 8) are used, these upper bits need not be latched. The worst case address generation time from the beginning of  $T_1$  (including address latch propagation time ( $t_{IVOV}$ ) of the Intel 8282) for the circuit is:

$t_{CLAV} (44ns) + t_{IVOV} (30ns) = 74ns$

Figure 7. Demultiplexing the Address Bus of the 80186

Many memory or peripheral devices may not require addresses to remain stable throughout a data transfer. Examples of these are the 80130 and 80150 operating system firmware chips, and the 2186 8K x 8 iRAM. If a system is constructed wholly with these types of devices, addresses need not be latched. In addition, two of the peripheral chip select outputs of the 80186 may be configured to provide latched A1 and A2 outputs for peripheral register selects in a system which does not demultiplex the address/data bus.

One more signal is generated by the 80186 to address memory:  $\overline{BHE}$  (Bus High Enable). This signal, along with A0, is used to enable byte devices connected to either or both halves (bytes) of the 16-bit data bus (see section 3.1.3 on data bus operation section). Because A0 is used only to enable devices onto the lower half of the data bus, memory chip address inputs are usually driven by address bits A1-A19, NOT A0-A19. This provides 512K unique word addresses, or 1M unique BYTE addresses.

Of course,  $\overline{BHE}$  is not present on the 8 bit 80188. All data transfers occur on the 8 bits of the data bus.

#### 3.1.3 80186 DATA BUS OPERATION

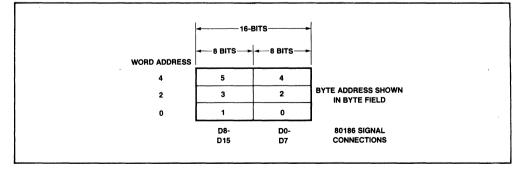

Throughout  $T_2$ ,  $T_3$ ,  $T_w$ , and  $T_4$  of a bus cycle the multiplexed address/data bus becomes a 16-bit data bus. Data transfers on this bus may be either in bytes or in words. All memory is byte addressable, that is, the upper and lower byte of a 16-bit word each have a unique byte address by which they may be individually accessed, even though they share a common word address (see Figure 3-6).

All bytes with even addresses (A0 = 0) reside on the lower 8 bits of the data bus, while all bytes with odd addresses (A0 = 1) reside on the upper 8 bits of the data bus. Whenever an access is made to only the even byte, A0 is driven low, BHE is driven high, and the data transfer occurs on D0-D7 of the data bus. Whenever an access is made to only the odd byte,  $\overline{BHE}$  is driven low, A0 is driven high, and the data transfer occurs on D8-D15 of the data bus. Finally, if a word access is performed to an even address, both A0 and  $\overline{BHE}$  are driven low and the data transfer occurs on D0-D15.

Word accesses are made to the addressed byte and to the next higher numbered byte. If a word access is performed to an odd address, two byte accesses must be performed, the first to access the odd byte at the first word address on D8-D15, the second to access the even byte at the next sequential word address on D0-D7. For example, in Figure 8, byte 0 and byte 1 can be individually accessed (read or written) in two separate bus cycles (byte accesses) to byte addresses 0 and 1 at word address 0. They may also be accessed together in a single bus cycle (word access) to word address 0. However, if a word access is made to address 1, two bus cycles will be required, the first to access byte 1 at word address 0 (note byte 0 will not be accessed), and the second to access byte 2 at word address 2 (note byte 3 will not be accessed). This is why all word data should be located at even addresses to maximize processor performance.

When byte reads are made, the data returned on the half of the data bus not being accessed is ignored. When byte writes are made, the data driven on the half of the data bus not being written is indeterminate.

#### 3.1.4 80188 DATA BUS OPERATION

Because the 80188 externally has only an 8 bit data bus, the above discussion about upper and lower bytes of the data bus does not apply to the 80188. No performance improvement will occur if word data is placed on even boundaries in memory space. All word accesses require two bus cycles, the first to access the lower byte of the word; the second to access the upper byte of the word.

Any 80188 access to the integrated peripherals must be done 16 bits at a time: thus in this special case, a word access will occur in a single bus cycle in the 80188. The

Figure 8. Physical Memory Byte/Word Addressing in the 80186

external data bus will record only a single byte being transferred, however.

#### 3.1.5 GENERAL DATA BUS OPERATION

Because of the bus drive capabilities of the 80186 (200pF, sinking 2mA, sourcing 400uA, roughly twice that of the 8086), this bus may not require additional buffering in many small systems. If data buffers are not used in the system, care should be taken not to allow bus contention between the 80186 and the devices directly connected to the 80186 data bus. Since the 80186 floats the address/data bus before activating any command lines, the only requirement on a directly connected device is that it floats its output drivers after a read BE-FORE the 80186 begins to drive address information for the next bus cycle. The parameter of interest here is the minimum time from RD inactive until addresses active for the next bus cycle (t<sub>RHAV</sub>) which has a minimum value of 85ns. If the memory or peripheral device cannot disable its output drivers in this time, data buffers will be required to prevent both the 80186 and the peripheral or memory device from driving these lines concurrently. Note, this parameter is unaffected by the addition of wait states. Data buffers solve this problem because their output float times are typically much faster than the 80186 required minimum.

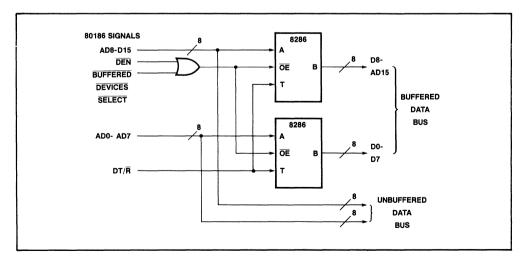

If buffers are required, the 80186 provides a  $\overline{\text{DEN}}$  (Data ENable) and  $\overline{\text{DT/R}}$  (Data Transmit/Receive) signals to simplify buffer interfacing. The  $\overline{\text{DEN}}$  and  $\overline{\text{DT/R}}$  sig-

nals are activated during all bus cycles, whether or not the cycle addresses buffered devices. The DEN signal is driven low whenever the processor is either ready to receive data (during a read) or when the processor is ready to send data (during a write) (that is, any time during an active bus cycle when address information is not being generated on the address/data pins). In most systems, the DEN signal should NOT be directly connected to the OE input of buffers, since unbuffered devices (or other buffers) may be directly connected to the processor's address/data pins. If DEN were directly connected to several buffers, contention would occur during read cycles, as many devices attempt to drive the processor bus. Rather, it should be a factor (along with the chip selects for buffered devices) in generating the output enable input of a bi-directional buffer.

The  $DT/\overline{R}$  signal determines the direction of data propagation through the bi-directional bus buffers. It is high whenever data is being driven out from the processor, and is low whenever data is being read into the processor. Unlike the  $\overline{DEN}$  signal, it may be directly connected to bus buffers, since this signal does not usually directly enable the output drivers of the buffer. An example data bus subsystem supporting both buffered and unbuffered devices is shown in Figure 9. Note that the A side of the 8286 buffer is connected to the 80186, the B side to the external device. The B side of the buffer has greater drive capacity than the A side (since it is meant to drive much greater loads). The  $DT/\overline{R}$  signal can directly drive the T (transmit) signal of the buffer, since it has the correct polarity for this configuration.

Figure 9. Example 80186 Buffered/Unbuffered Data Bus

Figure 10. Read Cycle Timing of the 80186

#### 3.1.6 CONTROL SIGNALS

The 80186 directly provides the control signals RD,  $\overline{WR}$ ,  $\overline{LOCK}$  and  $\overline{TEST}$ . In addition, the 80186 provides the status signals  $\overline{S0}$ - $\overline{S2}$  and S6 from which all other required bus control signals can be generated.

#### RD and WR 3.1.6.1

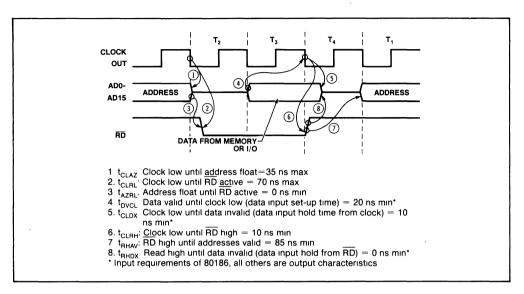

The  $\overline{RD}$  and  $\overline{WR}$  signals strobe data to or from memory or I/O space. The  $\overline{RD}$  signal is driven low off the beginning of  $T_2$ , and is driven high off the beginning of  $T_4$  during all memory and I/O reads (see Figure 10). RD will not become active until the 80186 has ceased driving address information on the address/data bus. Data is sampled into the processor at the beginning of  $T_4$ . RD will not go inactive until the processor's data hold time (10ns) has been satisfied.

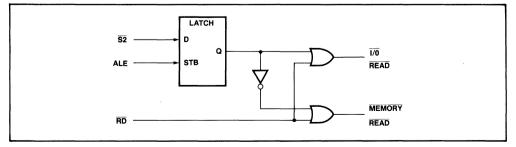

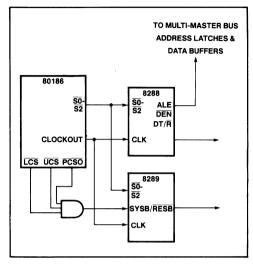

Note that the 80186 does not provide separate I/O and memory  $\overline{RD}$  signals. If separate I/O read and memory read signals are required, they can be synthesized using the  $\overline{S2}$  signal (which is low for all I/O operations and high for all memory operations) and the  $\overline{RD}$  signal (see Figure 11). It should be noted that if this approach is used, the  $\overline{S2}$  signal will require latching, since the  $\overline{S2}$  signal (like S0 and S1) goes to a passive state well before the beginning of  $T_4$  (where RD goes inactive). If S2 was directly used for this purpose, the type of read command (I/O or memory) could change just before T<sub>4</sub> as S2 goes to the passive state (high). The status signals may be latched using ALE in an identical fashion as is used to latch the address signals (often using the spare bits in the address latches).

Often the lack of a seperate I/O and memory  $\overline{RD}$  signal

Figure 11. Generating I/O and Memory Read Signals from the 80186 9

is not important in an 80186 system. Each of the 80186 chip select signals will respond on only one of memory or I/O accesses (the memory chip selects respond only to accesses memory space; the peripheral chip selects can respond to accesses in either I/O or memory space, at programmer option). Thus, the chip select signal enables the external device only during accesses to the proper address in the proper space.

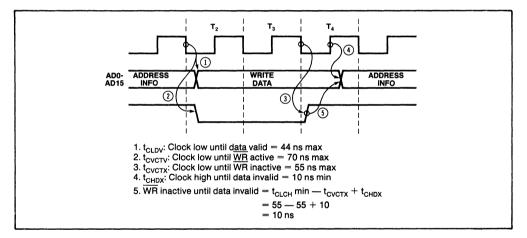

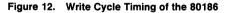

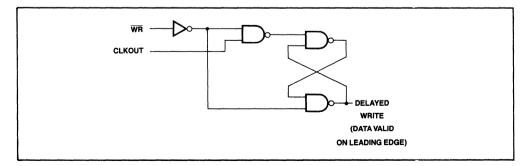

The  $\overline{WR}$  signal is also driven low off the beginning of  $T_2$ and driven high off the beginning of  $T_4$ . Like the RD signal, the  $\overline{WR}$  signal is active for all memory and I/O writes, and also like the RD signal, separate I/O and memory writes may be generated using the latched S2 signal along with the  $\overline{WR}$  signal (see Figure 12). More importantly, however, is the active going edge of write. At the time  $\overline{WR}$  makes its active (high to low) transition, valid write data is NOT present on the data bus. This has consequences when using this signal as a write enable signal for DRAMs and iRAMs since both of these devices require that the write data be stable on the data bus at the time of the inactive to active transition of the WE signal. In DRAM applications, this problem is solved by a DRAM controller (such as the Intel 8207 or 8203), while with iRAMs this problem may be solved by placing cross-coupled NAND gates between the CPU and the iRAMs on the WR line (see Figure 13). This will delay the active going edge of the WR signal to the iRAMs by a clock phase, allowing valid data to be driven onto the data bus.

Figure 13. Synthesizing Delayed Write from the 80186

#### 3.1.6.2 Queue Status Signals

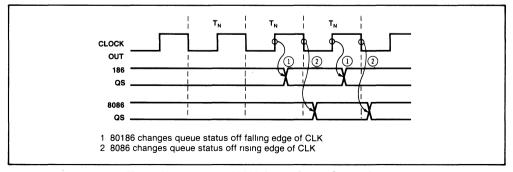

If the  $\overline{RD}$  line is externally grounded during reset and remains grounded during processor operation, the 80186 will enter "queue status" mode. When in this mode, the  $\overline{WR}$  and ALE signals become queue status outputs, reflecting the status of the internal prefetch queue during each clock cycle. These signals are provided to allow a processor extension (such as the Intel 8087 floating point processor) to track execution of instructions within the 80186. The interpretation of QSO (ALE) and QS1 ( $\overline{WR}$ ) are given in Table 2. These signals change on the high-to-low clock transition, one clock phase earlier than on the 8086. Note that since execution unit operation is independent of bus interface unit operation, queue status lines may change in any T state.

Table 2. 80186 Queue Status

| QS1 | QSO | Interpretation                                  |  |

|-----|-----|-------------------------------------------------|--|

| 0   | 0   | no operation                                    |  |

| 0   | 1   | first byte of instruction taken from queue      |  |

| 1   | 0   | queue was reinitialized                         |  |

| 1   | 1   | subsequent byte of instruction taken from queue |  |

Since the ALE,  $\overline{RD}$ , and  $\overline{WR}$  signals are not directly available from the 80186 when it is configured in queue status mode, these signals must be derived from the status lines  $\overline{S0}$ - $\overline{S2}$  using an external 8288 bus controller (see below). To prevent the 80186 from accidentally entering queue status mode during reset, the  $\overline{RD}$  line is internally provided with a weak pullup device.  $\overline{RD}$  is the ONLY three-state or input pin on the 80186 which is supplied with a pullup or pulldown device.

#### 3.1.6.3 Status Lines

The 80186 provides 3 status outputs which are used to indicate the type of bus cycle currently being executed. These signals go from an inactive state (all high) to one of seven possible active states during the T state immediately preceding  $T_1$  of a bus cycle (see Figure 5). The possible status line encodings and their interpretations are given in Table 3. The status lines are driven to their inactive state in the T state ( $T_3$  or  $T_w$ ) immediately preceding  $T_4$  of the current bus cycle.

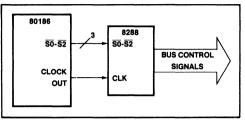

The status lines may be directly connected to an 8288 bus controller, which can be used to provide local bus control signals or multi-bus control signals (see Figure 14). Use of the 8288 bus controller does not preclude the use of the 80186 generated RD, WR and ALE signals, however. The 80186 directly generated signals may be used to provide local bus control signals, while an 8288 is used to provide multi-bus control signals, for example.

| Table 3. | 80186 | Status | Line | Inter | oretation |

|----------|-------|--------|------|-------|-----------|

|----------|-------|--------|------|-------|-----------|

| S2 | <b>S</b> 1 | S2 | Operation             |

|----|------------|----|-----------------------|

| 0  | 0          | 0  | interrupt acknowledge |

| 0  | 0          | 1  | read I/O              |

| 0  | 1          | 0  | write I/O             |

| 0  | 1          | 1  | halt                  |

| 1  | 0          | 0  | instruction fetch     |

| 1  | 0          | 1  | read memory           |

| 1  | 1          | 0  | write memory          |

| 1  | 1          | 1  | passive               |

The 80186 provides two additional status signals: S6 and S7. S7 is equivalent to BHE (see section 3.1.2) and appears on the same pin as BHE. BHE/S7 changes state, reflecting the bus cycle about to be run, in the middle of the T state  $(T_4 \text{ or } T_i)$  immediately preceding  $T_1$  of the bus cycle. This means that BHE/S7 does not need to be latched, i.e., it may be used directly as the BHE signal. S6 provides information concerning the unit generating the bus cycle. It is time multiplexed with A19, and is available during  $T_2$ ,  $T_3$ ,  $T_4$  and  $T_w$ . In the 8086 family, all central processors (e.g., the 8086, 8088 and 8087) drive this line low, while all I/O processors (e.g., 8089) drive this line high during their respective bus cycles. Following this scheme, the 80186 drives this line low whenever the bus cycle is generated by the 80186 CPU, but drives it high when the bus cycle is generated by the integrated 80186 DMA unit. This allows external devices to distinguish between bus cycles fetching data for the CPU from those transfering data for the DMA unit.

Three other status signals are available on the 8086 but not on the 80186. They are S3, S4, and S5. Taken together, S3 and S4 indicate the segment register from which the current physical address derives. S5 indicates the state of the interrupt flip-flop. On the 80186, these signals will *ALWAYS* be low.

#### 3.1.6.4 TEST and LOCK

Finally, the <u>80186</u> provides a TEST input and a LOCK output. The TEST input is used in conjunction with the

processor WAIT instruction. It is typically driven by a processor extension (like the 8087) to indicate whether it is busy. Then, by executing the WAIT (or FWAIT) instruction, the central processor may be forced to temporarily suspend program execution until the processor extension indicates that it is idle by driving the TEST line low.

The  $\overline{LOCK}$  output is driven low whenever the data cycles of a LOCKED instruction are executed. A LOCKED instruction is generated whenever the LOCK prefix occurs immediately before an instruction. The LOCK prefix is active for the single instruction immediately following the LOCK prefix. This signal is used to indicate to a bus arbiter (e.g., the 8289) that a series of locked data transfers is occurring. The bus arbiter should under no circumstances release the bus while locked transfers are occurring. The 80186 will not recognize a bus HOLD, nor will it allow DMA cycles to be run by the integrated DMA controller during locked data transfers. LOCKED transfers are used in multiprocessor systems to access memory based semaphore variables which control access to shared system resources (see AP-106, "Multiprogramming with the iAPX88 and iAPX86 Microsystems," by George Alexy (Sept. 1980)).

On the 80186, the  $\overline{LOCK}$  signal will go active during T<sub>1</sub> of the first DATA cycle of the locked transfer. It is driven inactive 3 T-states after the beginning of the last DATA cycle of the locked transfer. On the 8086, the LOCK signal is activated immediately after the LOCK prefix is executed. The LOCK prefix may be executed well before the processor is prepared to perform the locked data transfer. This has the unfortunate consequence of activating the  $\overline{LOCK}$  signal before the first LOCKED data cycle is performed. Since LOCK is active before the processor requires the bus for the data transfer, opcode pre-fetching can be LOCKED. However, since the 80186 does not activate the  $\overline{LOCK}$  signal until the processor is ready to actually perform the locked transfer, locked pre-fetching will not occur with the 80186.

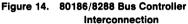

Note that the  $\overline{LOCK}$  signal does not remain active until the end of the last data cycle of the locked transfer. This may cause problems in some systems if, for example, the processor requests memory access from a dual ported RAM array and is denied immediate access (because of a DRAM refresh cycle, for example). When the processor finally is able to gain access to the RAM array, it may have already dropped its  $\overline{LOCK}$  signal, thus allowing the dual port controller to give the other port access to the RAM array instead. An example circuit which can be used to hold  $\overline{LOCK}$  active until a RDY has been received by the 80186 is shown in Figure 15.

#### 3.1.7 HALT TIMING

A HALT bus cycle is used to signal the world that the

80186 CPU has executed a HLT instruction. It differs from a normal bus cycle in two important ways.

Figure 15. Circuit Holding Lock Active Until Ready is Returned

The first way in which a HALT bus cycle differs from a normal bus cycle is that since the processor is entering a halted state, none of the control lines (RD or WR) will be driven active. Address and data information will not be driven by the processor, and no data will be returned. The second way a HALT bus cycle differs from a normal bus cycle is that the  $\overline{SO-S2}$  status lines go to their passive state (all high) during  $T_2$  of the bus cycle, well before they go to their passive state during a normal bus cycle.

Like a normal bus cycle, however, ALE is driven active. Since no valid address information is present, the information strobed into the address latches should be ignored. This ALE pulse can be used, however, to latch the HALT status from the  $\overline{S0}$ - $\overline{S2}$  status lines.

The processor being halted does not interfere with the operation of any of the 80186 integrated peripheral units. This means that if a DMA transfer is pending while the processor is halted, the bus cycles associated with the DMA transfer will run. In fact, DMA latency time will improve while the processor is halted because the DMA unit will not be contending with the processor for access to the 80186 bus (see section 4.4.1).

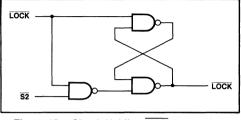

#### 3.1.8 8288 AND 8289 INTERFACING

The 8288 and 8289 are the bus controller and multimaster bus arbitration devices used with the 8086 and 8088. Because the 80186 bus is similar to the 8086 bus, they can be directly used with the 80186. Figure 16 shows an 80186 interconnection to these two devices.

The 8288 bus controller generates control signals ( $\overline{RD}$ , WR, ALE, DT/R, DEN, etc.) for an 8086 maximum mode system. It derives its information by decoding status lines  $\overline{SO}$ - $\overline{S2}$  of the processor. Because the 80186 and the 8086 drive the same status information on these lines, the 80186 can be directly connected to the 8288 just as in an 8086 system. Using the 8288 with the 80186 does not prevent using the 80186 control signals directly. Many systems require both local bus control signals and system bus control signals. In this type of system, the 80186 lines could be used as the local signals, with the

Figure 16. 80186/8288/8289 Interconnection

8288 lines used as the system signals. Note that in an 80186 system, the 8288 generated ALE pulse occurs later than that of the 80186 itself. In many multimaster bus systems, the 8288 ALE pulse should be used to strobe the addresses into the system bus address latches to insure that the address hold times are met.

The 8289 bus arbiter arbitrates the use of a multi-master system bus among various devices each of which can become the <u>bus</u> master. This component also decodes status lines  $\overline{S0}$ - $\overline{S2}$  of the processor directly to determine when the system bus is required. When the system bus is required, the 8289 forces the processor to wait until it has acquired control of the bus, then it allows the processor to drive address, data and control information onto the system bus. The system determines when it requires system bus resources by an address decode. Whenever the address being driven coincides with the address of an on-board resource, the system bus is not required and thus will not be requested. The circuit shown factors the 80186 chip select lines to determine when the system bus should be requested, or when the 80186 request can be satisfied using a local resource.

#### 3.1.9 READY INTERFACING

The 80186 provides two ready lines, a synchronous ready (SRDY) line and an asynchronous ready (ARDY) line. These lines signal the processor to insert wait states ( $T_w$ ) into a CPU bus cycle. This allows slower devices to respond to CPU service requests (reads or writes). Wait states will only be inserted when both ARDY and SRDY are low, i.e., only one of ARDY or SRDY need be active to terminate a bus cycle. Any number of wait states may be inserted into a bus cycle. The 80186 will ignore the RDY inputs during any accesses to the integrated peripheral registers, and to any area where the chip select ready bits indicate that the external ready should be ignored.

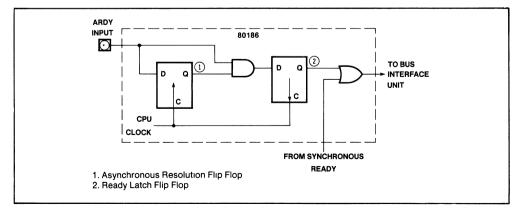

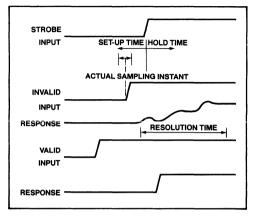

The timing required by the two RDY lines is different. The ARDY line is meant to be used with asynchronous ready inputs. Thus, inputs to this line will be internally synchronized to the CPU clock before being presented to the processor. The synchronization circuitry used with the ARDY line is shown in Figure 17. Figure 18A and 18B show valid and invalid transitions of the ARDY line (and subsequent wait state insertion). The first flip-flop is used to "resolve" the asynchronous transition of the ARDY line. It will achieve a definite level (either high or low) before its output is latched into the second flip-

Figure 17. Asynchronous Ready Circuitry of the 80186

flop for presentation to the CPU. When latched high, it allows the level present on the ARDY line to pass directly to the CPU; when latched low, it forces not ready to be presented to the CPU (see Appendix B for 80186 synchronizer information).

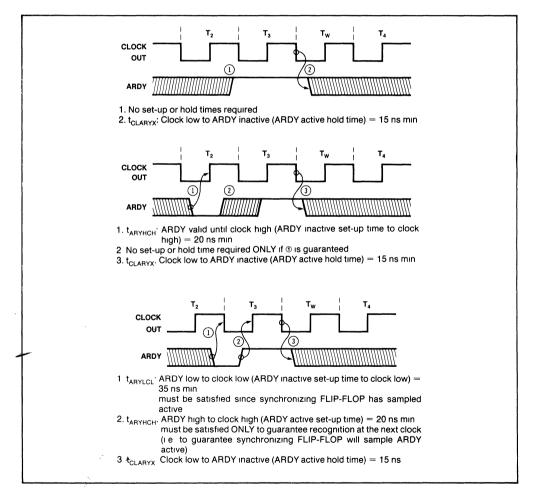

With this scheme, notice that only the active going edge of the ARDY signal is synchronized. Once the synchronization flip-flop has sampled high, the ARDY input directly drives the RDY flip-flop. Since inputs to this RDY flip-flop must satisfy certain setup and hold times, it is important that these setup and hold times ( $t_{ARYLCL}$ = 35ns and  $t_{CHARYX}$  = 15 ns respectively) be satisfied by any inactive going transition of the ARDY line. The reason ARDY is implemented in this manner is to allow a slow device the greatest amount of time to respond with a not ready after it has been selected. In a normally ready system, a slow device must respond with a not ready quickly after it has been selected to prevent the processor from continuing and accessing invalid data from the slow device. By implementing ARDY in the above fashion, the slow device has an additional clock phase to respond with a not ready.

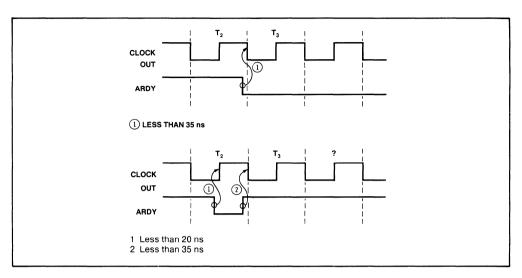

If RDY is sampled active into the RDY flip-flop at the beginning of  $T_3$  or  $T_w$  (meaning that ARDY was sam-

Figure 18A. Valid ARDY Transitions

Figure 18B. Invalid ARDY Transitions

pled high into the synchronization flip-flop in the middle of a T state, and has remained high until the beginning of the next T state), that T state will be immediately followed by T<sub>4</sub>. If RDY is sampled low into the RDY flipflop at the beginning of T<sub>3</sub> or T<sub>w</sub> (meaning that either ARDY was sampled low into the synchronization flipflop OR that ARDY was sampled high into the synchronization flip-flop, but has subsequently changed to low before the ARDY setup time) that T state will be immediately followed by a wait state (T<sub>w</sub>). Any asynchronous transition on the ARDY line not occurring during the above times, that is, when the processor is not "looking at" the ready lines, will not cause CPU malfunction. Again, for ARDY to force wait states to be inserted, SRDY must be driven low, since they are internally ORed together to form the processor RDY signal.

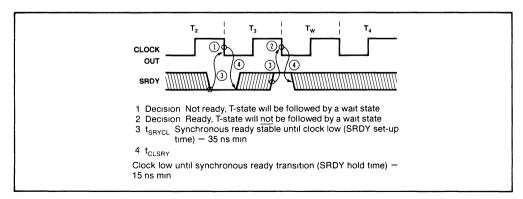

The synchronous ready (SRDY) line requires that ALL transitions on this line during  $T_2$ ,  $T_3$  or  $T_w$  satisfy a certain setup and hold time ( $t_{SRYCL}$  = 35 ns and  $t_{CLSRY}$  = 15 ns respectively). If these requirements are not met, the CPU will not function properly. Valid transitions on this line, and subsequent wait state insertion is shown in Figure 19. The processor looks at this line at the beginning of each  $T_3$  and  $T_w$ . If the line is sampled active at the beginning of either of these two cycles, that cycle will

Figure 19. Valid SRDY transitions on the 80186

be immediately followed by  $T_4$ . On the other hand, if the line is sampled inactive at the beginning of either of these two cycles, that cycle will be followed by a  $T_w$ . Any asynchronous transition on the SRDY line not occurring at the beginning of  $T_3$  or  $T_w$ , that is, when the processor is not "looking at" the ready lines will not cause CPU malfunction.

#### 3.1.10 BUS PERFORMANCE ISSUES

Bus cycles occur sequentially, but do not necessarily come immediately one after another, that is the bus may remain idle for several T states ( $T_i$ ) between each bus access initiated by the 80186. This occurs whenever the 80186 internal queue is full and no read/write cycles are being requested by the execution unit or integrated DMA unit. The reader should recall that a separate unit, the bus interface unit, fetches opcodes (including immediate data) from memory, while the execution unit actually executes the pre-fetched instructions. The number of clock cycles required to execute an 80186 instruction vary from 2 clock cycles for a register to register move to 67 clock cycles for an integer divide.

If a program contains many long instructions, program execution will be CPU limited, that is, the instruction queue will be constantly filled. Thus, the execution unit does not need to wait for an instruction to be fetched. If a program contains mainly short instructions or data move instructions, the execution will be bus limited. Here, the execution unit will be required to wait often for an instruction to be fetched before it continues its operation. Programs illustrating this effect and performance degradation of each with the addition of wait states are given in appendix G.

All instruction fetches are word (16-bit) fetches from even addresses unless the fetch occurs as a result of a jump to an odd location. This maximizes the utilization of each bus cycle used for instruction fetching, since each fetch will access two bytes of information. It is also good programming practice to locate all word data at even locations, so that both bytes of the word may be accessed in a single bus cycle (see discussion on data bus interfacing for further information, section 3.1.3 of this note).

Although the amount of bus utilization, i.e., the percentage of bus time used by the 80186 for instruction fetching and execution required for top performance will vary considerably from one program to another, a typical instruction mix on the 80186 will require greater bus utilization than the 8086. This is caused by the higher performance execution unit requiring instructions from the prefetch queue at a greater rate. This also means that the effect of wait states is more pronounced in an 80186 system than in an 8086 system. In all but a few cases, however, the performance degradation incurred by adding a wait state is less than might be expected because instruction fetching and execution are performed by separate units.

#### 3.2 Example Memory Systems

#### 3.2.1 2764 INTERFACE

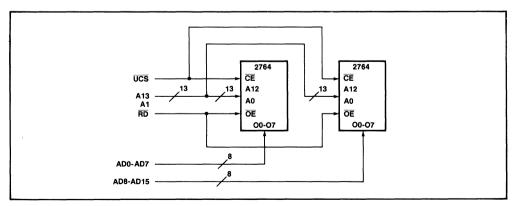

With the above knowledge of the 80186 bus, various memory interfaces may be generated. One of the simplest of these is the example EPROM interface shown in Figure 20.

The addresses are latched using the address generation circuit shown earlier. Note that the A0 line of each EPROM is connected to the A1 address line from the 80186, NOT the A0 line. Remember, A0 only signals a data transfer on the lower 8 bits of the 16-bit data bus! The EPROM outputs are connected directly to the address/data inputs of the 80186, and the 80186 RD signal is used as the  $\overline{OE}$  for the EPROMs.

The chip enable of the EPROM is driven directly by the chip select output of the 80186 (see section 8). In this configuration, the access time calculation for the EPROMs are:

time from

address:

$$(3 + N)$$

\* $t_{CLCL} - t_{CLAV} - t_{IVOV}(8282) - t_{DVCL}$

$$= 375 + (N * 125) - 44 - 30 - 20$$

$$= 281 + (N * 125) ns$$

time from

chip select:

$$(3 + N)$$

\* $t_{CLCL} - t_{CLCSV} - t_{DVCL}$

$$= 375 + (N * 125) - 66 - 20$$

$$= 289 + (N * 125)$$

ns

time from

$\frac{\text{RD}}{\text{(OE)}} (\frac{(2 + N)t_{\text{CLCL}} - t_{\text{CLRL}} - t_{\text{DVCL}}}{(2 + N)t_{\text{CLCL}} - (2 + N)t_{\text{CLRL}} - (2 + N)t_{\text{CLRL}}} = 250 + (N * 125) - 70 - 20$ = 160 + (N \* 125) ns

where:

$t_{CLAV}$  = time from clock low in  $T_1$  until addresses are valid

$t_{CLCL} = clock period of processor$

$t_{IVOV} =$  time from input valid of 8282 until output valid of 8282

- $t_{DVCL} = 186$  data valid input setup time until clock low time of  $T_4$

- $t_{CLCSV} = time from clock low in T_1 until chip selects are valid$

$t_{CLRL} = time from clock low in T_2 until \overline{RD} goes low$

N = number of wait states inserted

Thus, for 0 wait state operation, 250ns EPROMs must be used. The only significant parameter not included above is  $t_{RHAV}$  the time from RD inactive (high) until the 80186 begins driving address information. This parameter is 85ns, which meets the 2764-25 (250ns speed selection) output float time of 85ns. If slower EPROMs are used, a discrete data buffer *MUST* be inserted between the EPROM data lines and the address/data bus, since these devices may continue to drive data information on the multiplexed address/data bus when the 80186 begins to drive address information for the next bus cycle.

#### 3.2.2 2186 INTERFACE

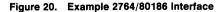

An example interface between the 80186 and 2186 iRAMs is shown in Figure 21. This memory component is almost an ideal match with the 80186, because of its large integration, and its not requiring address latching.

Figure 21. Example 2186/80186 Interface

The 2186 internally is a dynamic RAM integrated with refresh and control circuitry. It operates in two modes, pulse mode and late cycle mode. Pulse mode is entered if the  $\overrightarrow{CE}$  signal is low to the device a maximum of 130ns, and requires the command input ( $\overrightarrow{RD}$  or  $\overrightarrow{WE}$ ) to go active within 90ns after  $\overrightarrow{CE}$ . Because of these requirements, interfacing the 80186 to the 2186 in pulse mode would be difficult. Instead, the late cycle mode is used. This affords a much simpler interface with no loss of performance. The iRAM automatically selects between these modes by the nature of the control signals.

The 2186 is a leading edge triggered device. This means that address and data information are strobed into the device on the active going (high to low) transition of the command signal. This requires both  $\overline{CE}$  and  $\overline{WR}$  be delayed until the address and data driven by the 80186 are guaranteed stable. Figure 21 shows a simple circuit which can be used to perform this function. Note that ALE CANNOT be used to delay  $\overline{CE}$  if addresses are not latched externally, because this would violate the address hold time required by the 2186 (30ns).

Because the 2186s are RAMs, data bus enables ( $\overline{BHE}$  and A0, see previous section) MUST be used to factor either the chip enables or write enables of the lower and upper bytes of the 16-bit RAM memory system. If this is not done, all memory writes, including single byte writes, will write to both the upper and lower bytes of the memory system. The example system shown uses  $\overline{BHE}$  and A0 as factors to the 2186 CE. This may be done, because both of these signals (A0 and  $\overline{BHE}$ ) are valid when the address information is valid from the 80186.

The 2186 requires a certain amount of recovery time between its chip enable going inactive and its chip enable going active insure proper operation. For a "normal" cycle (a read or write), this time is  $t_{EHEL} = 40$ ns. This means that the 80186 chip select lines will go inactive soon enough at the end of a bus cycle to provide the required recovery time even if two consecutive accesses are made to the iRAMs. If the 2186 CE is asserted without a command signal (WE or OE), a "False Memory Cycle" (FMC) will be generated. Whenever a FMC is generated, the recovery time is much longer; another memory cycle must not be initiated for 200ns. As a result, if the memory system will generate FMCs,  $\overline{CE}$  must be taken away in the middle of the T state  $(T_3 \text{ or } T_w)$  immediately preceding T<sub>4</sub> to insure two consecutive cycles to the iRAM will not violate this parameter. Status going passive (all high) can be used for this purpose. These lines will all go high during the first phase of the next to last T state (either  $T_3$  or  $T_w$ ) of a bus cycle (see section 3.1.5).

Finally, since it is a dynamic device, the 2186 requires refresh cycles to maintain data integrity. The circuitry to generate these refresh cycles is integrated within the 2186. Because of this, the 2186 has a ready line which is used to suspend processor operation if a processor RAM access coincides with an internally generated refresh cycle. This is an open collector output, allowing many of them to be wire-OR'ed together, since more than one device may be accessed at at time. These lines are also normally ready, which means that they will be high whenever the 2186 is not being accessed, i.e., they will only be driven low if a processor request coincides with an internal refresh cycle. Thus, the ready lines from the iRAM must be factored into the 80186 RDY circuit only during accesses to the iRAM itself. Since the 2186 refresh logic operates asynchronously to the 80186, this RDY line must be synchronized for proper operation with the 80186, either by the integrated ready synchronizer or by an external circuit. The example circuit uses the integrated synchronizer associated with the ARDY processor input.

The ready lines of the 2186 are active unless a processor access coincides with an internal refresh cycle. These lines must go inactive soon enough after a cycle is requested to insert wait states into the data cycle. The 2186 will drive this line low within 50ns after  $\overline{CE}$  is received, which is early enough to force the 80186 to insert wait states if they are required. The primary concern here is that the ARDY line be driven not active before its setup time in the middle of  $T_2$ . This is required by the nature of the asynchronous ready synchronization circuitry of the 80186. Since the RDY pulse of the 2186 may be as narrow as 50ns, if ready was returned after the first stage of the synchronizer, and subsequently changed state within the ready setup and hold time of the high to low going edge of the CPU clock at the end of  $T_2$ , improper operation may occur (see section 3.1.6).

The example interface shown has a zero wait state RAM read access time from  $\overline{CE}$  of:

$$3 * t_{CLCL} - t_{CLCSV} - (TTL delay) - t_{DVCL}$$

= 375 - 66 - 30 - 20 ns

= 259 ns

where:

$t_{CLCL} = CPU$  clock cycle time

- $t_{CLCSV}$  = time from clock low in  $T_1$  until chip selects are valid

- $t_{DVCL} = 80186$  data in setup time before clock low in  $T_4$

The data valid delay from  $\overline{OE}$  active is less than 100ns, and is therefore not an access time limiter in this interface. Additionally, the 2186 data float time from  $\overline{RD}$  inactive is less than the 85ns 80186 imposed maximum. The  $\overline{CE}$  generation circuit shown in Figure 21 provides an address setup time of at least 11ns, and an address hold time of at least 35ns (assuming a maximum two level TTL delay of less than 30ns). Write cycle address setup and hold times are identical to the read cycle times. The circuit shown provides at least  $\frac{11 \text{ ns}}{\text{WE}}$ , easily meeting the Ons setup and 40ns hold times required by the 2186.

For more information concerning 2186 timing and interfacing, please consult the 2186 data sheet, or the application note AP-132, "Designing Memory Systems with the 8Kx8 iRAM" by John Fallin and William Righter (June 1982).

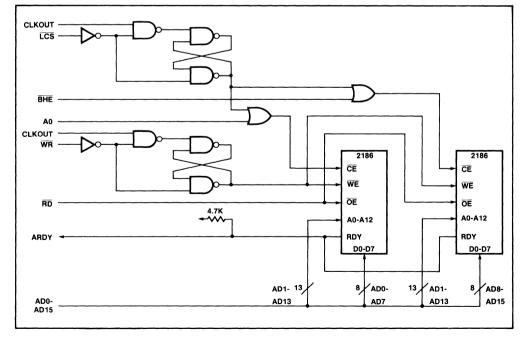

#### 3.2.3 8203 DRAM INTERFACE

An example 8203/DRAM interface is shown in Figure 22. The 8203 provides all required DRAM control signals, address multiplexing, and refresh generation. In this circuit, the 8203 is configured to interface with 64K DRAMs.

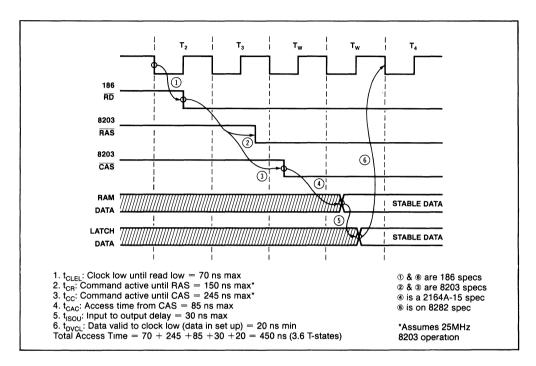

All 8203 cycles are generated off control signals ( $\overline{RD}$  and  $\overline{WR}$ ) provided by the 80186. These signals will not go active until T<sub>2</sub> of the bus cycle. In addition, since the 8203 clock (generated by the internal crystal oscillator of the 8203) is asynchronous to the 80186 clock, all memory requests by the 80186 must be synchronized to the 8203 before the cycle will be run. To minimize this synchronization time, the 8203 should be used with the highest speed crystal that will maintain DRAM compatibility. Even if a 25 MHz crystal is used (the maximum allowed by the 8203) two wait states will be required by the example circuit when using 150ns DRAMs with an 8 MHz 80186, three wait states if 200ns DRAMs are used (see timing analysis, Figure 23).

The entire RAM array controlled by the 8203 can be selected by one or a group of the 80186 provided chip selects. These chip selects can also be used to insert the wait states required by the interface.

Figure 22. Example 8203/DRAM/80186 Interface

Figure 23. 8203/2164A-15 Access Time Calculation

Since the 8203 is operating asynchronously to the 80186, the RDY output of the 8203 (used to suspend processor operation when a processor DRAM request coincides with a DRAM refresh cycle) must be synchronized to the 80186. The 80186 ARDY line is used to provide the necessary ready synchronization. The 8203 ready outputs operate in a normally not ready mode, that is, they are only driven active when an 8203 cycle is being executed, and a refresh cycle is not being run. This is fundamentally different than the normally ready mode used by the 2186 iRAMs (see previous section). The 8203 SACK signal is presented to the 80186 only when the DRAM is being accessed. Notice that the SACK output of the 8203 is used, rather than the XACK output. Since the 80186 will insert at least one full CPU clock cycle between the time RDY is sampled active, and the time data must be present on the data bus, using the  $\overline{XACK}$  signal would insert unnecessary additional wait states, since it does not indicate ready until valid data is available from the memory.

For more information about 8203/DRAM interfacing and timing, please consult the 8203 data sheet, or AP97A, "Interfacing Dynamic RAM to iAPX86/88 Systems Using the Intel 8202A and 8203" by Brad May (April 1982).

#### 3.2.4 8207 DRAM INTERFACE

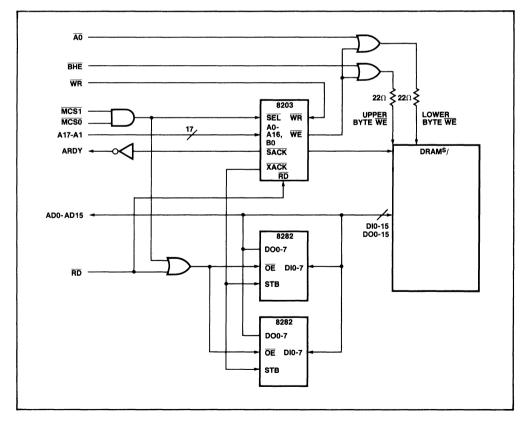

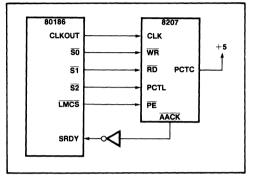

The 8207 advanced dual-port DRAM controller provides a high performance DRAM memory interface specifically for 80186 or 80286 microcomputer systems. This controller provides all address multiplexing and DRAM refresh circuitry. In addition, it synchronizes and arbitrates memory requests from two different ports (e.g., an 80186 and a Multibus), allowing the two ports to share memory. Finally, the 8207 provides a simple interface to the 8206 error detection and correction chip.

The simplest 8207 (and also the highest performance) interface is shown in Figure 24. This shows the 80186 connected to an 8207 using the 8207 slow cycle, synchronous status interface. In this mode, the 8207 decodes the type of cycle to be run directly from the status lines of the 80186. In addition, since the 8207 CLOCKIN is driven by the CLOCKOUT of the 80186, any performance degradation caused by required memory request synchronization between the 80186 and the 8207 is not present. Finally, the entire memory array driven by the

8207 may be selected using one or a group of the 80186 memory chip selects, as in the 8203 interface above.

Figure 24. 80186/8207/DRAM Interface

The 8207 AACK signal may be used to generate a synchronous ready signal to the 80186 in the above interface. Since dynamic memory periodically requires refreshing, 80186 access cycles may occur simultaneously with an 8207 generated refresh cycle. When this occurs, the 8207 will hold the AACK line high until the processor initiated access is run (note, the sense of this line is reversed with respect to the 80186 SRDY input). This signal should be factored with the DRAM (8207) select input and used to drive the SRDY line of the 80186. Remember that only one of SRDY and ARDY needs to be active for a bus cycle to be terminated. If asynchronous devices (e.g., a Multibus interface) are connected to the ARDY line with the 8207 connected to the SRDY line, care must be taken in design of the ready circuit such that only one of the RDY lines is driven active at a time to prevent premature termination of the bus cycle.

#### 3.3 HOLD/HLDA Interface

The 80186 employs a HOLD/HLDA bus exchange protocol. This protocol allows other asynchronous bus master devices (i.e., ones which drive address, data, and control information on the bus) to gain control of the bus to perform bus cycles (memory or I/O reads or writes).

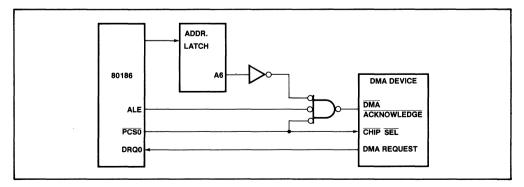

#### 3.3.1 HOLD RESPONSE

In the HOLD/HLDA protocol, a device requiring bus control (e.g., an external DMA device) raises the HOLD line. In response to this HOLD request, the 80186 will raise its HLDA line after it has finished its current bus activity. When the external device is finished with the bus, it drops its bus HOLD request. The 80186 responds by dropping its HLDA line and resuming bus operation.

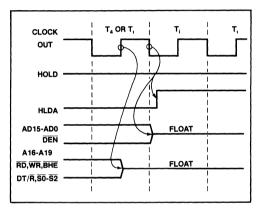

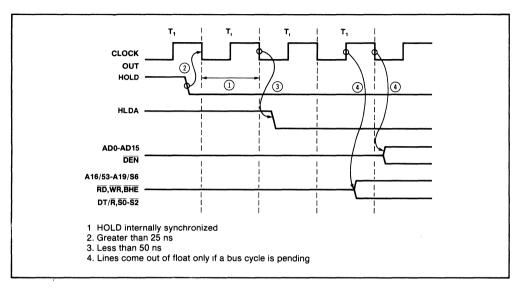

When the 80186 recognizes a bus hold by driving HLDA high, it will float many of its signals (see Figure 25). AD0 - AD15 (address/data 0 - 15) and DEN (data enable) are floated within  $t_{CLAZ}$  (35ns) after the same clock edge that HLDA is driven active. A16-A19 (address\_16 - 19), RD, WR, BHE (Bus High Enable), DT/R (Data Transmit/Receive) and S0 - S2 (status 0 - 2) are floated within  $t_{CHCZ}$  (45ns) after the clock edge immediately before the clock edge on which HLDA comes active.

Figure 25. Signal Float/HLDA Timing of the 80186

Only the above mentioned signals are floated during bus HOLD. Of the signals not floated by the 80186, some have to do with peripheral functionality (e.g., TmrOut). Many others either directly or indirectly control bus devices. These signals are ALE (Address Latch Enable, see section 3.1.2) and all the chip select lines (UCS, LCS, MCS0-3, and PCS0-6). The designer must be aware that the chip select circuitry does not look at externally generated addresses (see section 10 for a discussion of the chip select logic). Thus, for memory or peripheral devices which are addressed by external bus master devices, discrete chip select and ready generation logic must be used.

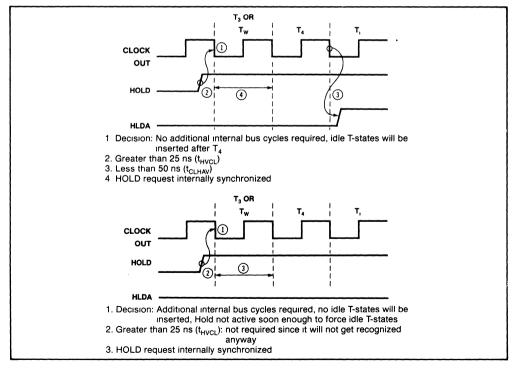

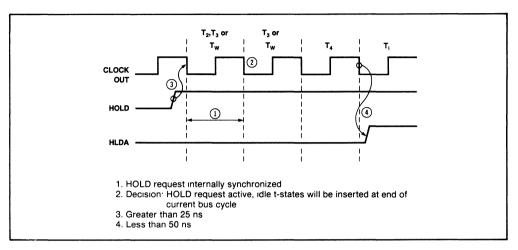

#### 3.3.2 HOLD/HLDA TIMING AND BUS LATENCY

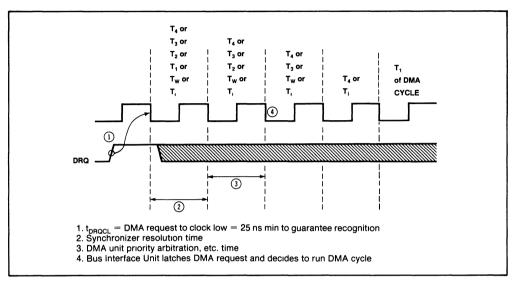

The time required between HOLD going active and the 80186 driving HLDA active is known as bus latency. Many factors affect this latency, including synchronization delays, bus cycle times, locked transfer times and interrupt acknowledge cycles.

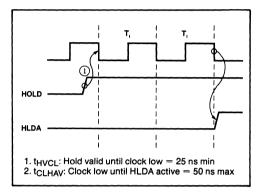

The HOLD request line is internally synchronized by the 80186, and may therefore be an asynchronous signal. To guarantee recognition on a certain clock edge, it must satisfy a certain setup and hold time to the falling edge of the CPU clock. A full CPU clock cycle is required for this synchronization, that is, the internal HOLD signal is not presented to the internal bus arbitration circuitry until one full clock cycle after it is latched from the HOLD input (see Appendix B for a dis-

Figure 26. 80186 Idle Bus Hold/HLDA Timing

cussion of 80186 synchronizers). If the bus is idle, HLDA will follow HOLD by two CPU clock cycles plus a small amount of setup and propagation delay time. The first clock cycle synchronizes the input; the second signals the internal circuitry to initiate a bus hold. (see Figure 26).

Many factors influence the number of clock cycles between a HOLD request and a HLDA. These may make bus latency longer than the best case shown above. Perhaps the most important factor is that the 80186 will not relinquish the local bus until the bus is idle. An idle bus occurs whenever the 80186 is not performing any bus transfers. As stated in section 3.1.1, when the bus is idle, the 80186 generates idle T-states. The bus can become idle only at the end of a bus cycle. Thus, the 80186 can recognize HOLD only after the end of its current bus cycle. The 80186 will normally insert no T<sub>1</sub> states between  $T_4$  and  $T_1$  of the next bus cycle if it requires any bus activity (e.g., instruction fetches or I/O reads). However, the 80186 may not have an immediate need for the bus after a bus cycle, and will insert T, states independent of the HOLD input (see section 3.1.7).

When the HOLD request is active, the 80186 will be

Figure 27. HOLD/HLDA Timing in the 80186

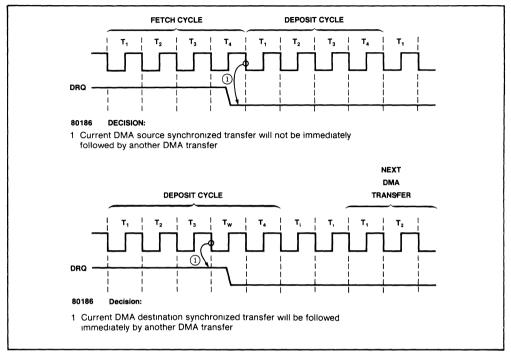

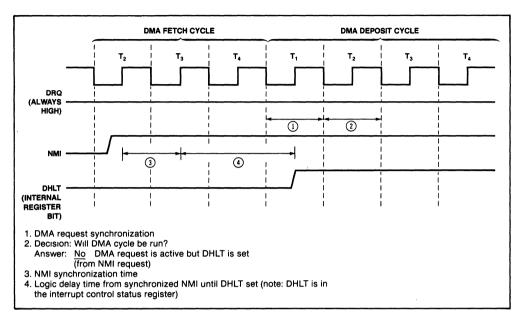

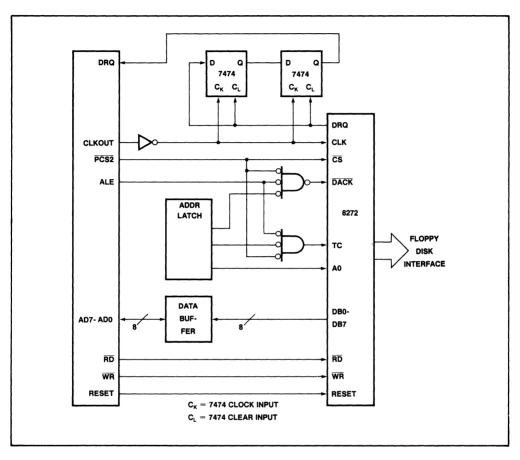

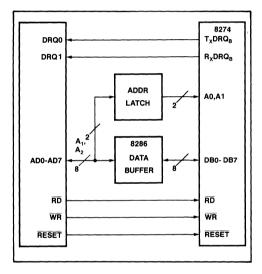

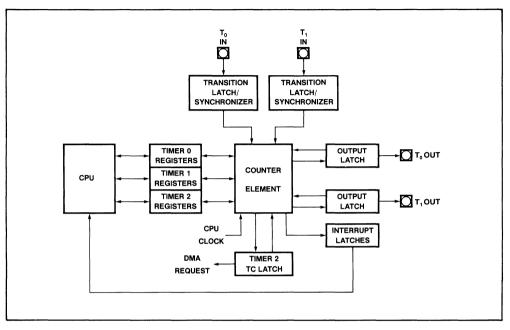

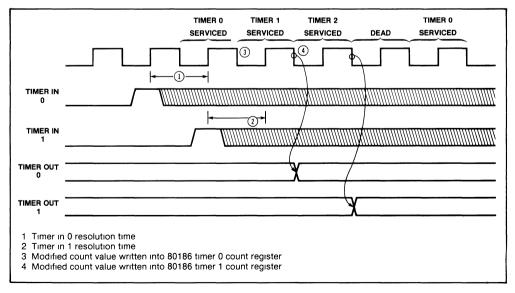

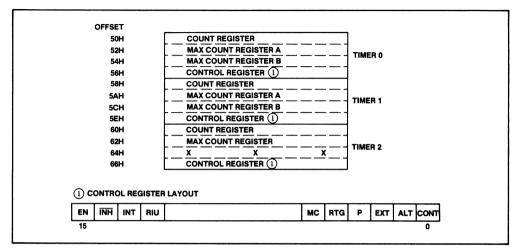

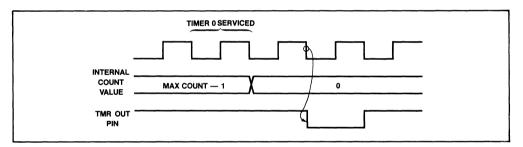

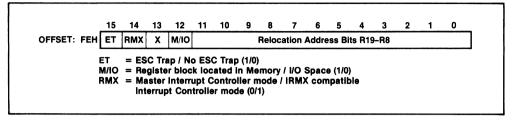

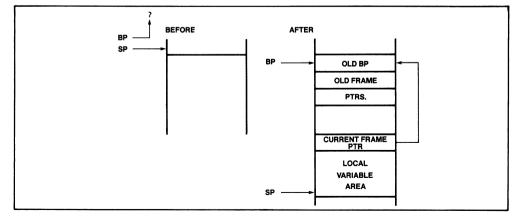

Figure 27A. HOLD/HLDA Timing in the 80186