# 80186/188, 80C186/C188 Hardware Reference Manual

intel

Order Number: 270788-001

# LITERATURE

To order Intel Literature or obtain literature pricing information in the U.S. and Canada call or write Intel Literature Sales. In Europe and other international locations, please contact your local sales office or distributor.

INTEL LITERATURE SALES P.O. BOX 7641 Mt. Prospect, IL 60056-7641 In the U.S. and Canada call toll free (800) 548-4725

# **CURRENT HANDBOOKS**

Product line handbooks contain data sheets, application notes, article reprints and other design information.

| TITLE                                                                                       | LITERATURE<br>ORDER NUMBER |

|---------------------------------------------------------------------------------------------|----------------------------|

| SET OF 11 HANDBOOKS<br>(Available in U.S. and Canada only)                                  | 231003                     |

| EMBEDDED APPLICATIONS                                                                       | 270648                     |

| 8-BIT EMBEDDED CONTROLLERS                                                                  | 270645                     |

| 16-BIT EMBEDDED CONTROLLERS                                                                 | 270646                     |

| 16/32-BIT EMBEDDED PROCESSORS                                                               | 270647                     |

| MEMORY                                                                                      | 210830                     |

| MICROCOMMUNICATIONS<br>(2 volume set)                                                       | 231658                     |

| MICROCOMPUTER SYSTEMS                                                                       | 280407                     |

| MICROPROCESSORS                                                                             | 230843                     |

| PERIPHERALS                                                                                 | 296467                     |

| PRODUCT GUIDE<br>(Overview of Intel's complete product lines)                               | 210846                     |

| PROGRAMMABLE LOGIC                                                                          | 296083                     |

| ADDITIONAL LITERATURE<br>(Not included in handbook set)                                     |                            |

| AUTOMOTIVE                                                                                  | 231792                     |

| COMPONENTS QUALITY/RELIABILITY HANDBOOK                                                     | 210997                     |

| INTEL PACKAGING OUTLINES AND DIMENSIONS<br>(Packaging types, number of leads, etc.)         | 231369                     |

| INTERNATIONAL LITERATURE GUIDE                                                              | E00029                     |

| LITERATURE PRICE LIST (U.S. and Canada)<br>(Comprehensive list of current Intel Literature) | 210620                     |

| MILITARY<br>(2 volume set)                                                                  | 210461                     |

| SYSTEMS QUALITY/RELIABILITY                                                                 | 231762                     |

LITINCOV/10/89

# U.S. and CANADA LITERATURE ORDER FORM

| NAME:                                                 |                                       |                                                                                       |                                  |                         |

|-------------------------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------|----------------------------------|-------------------------|

| COMPANY:                                              |                                       |                                                                                       |                                  |                         |

| ADDRESS:                                              |                                       |                                                                                       |                                  |                         |

| CITY:                                                 |                                       | STATE:                                                                                | ZIP:                             | ·                       |

| COUNTRY:                                              |                                       |                                                                                       |                                  |                         |

| PHONE NO.: (                                          | )                                     |                                                                                       |                                  |                         |

| ORDER NO.                                             | т                                     | ITLE                                                                                  | QTY. PRICE                       | TOTAL                   |

|                                                       |                                       |                                                                                       | ×=                               |                         |

|                                                       |                                       | <u></u>                                                                               | ×=                               |                         |

|                                                       |                                       |                                                                                       | X=<br>X=                         |                         |

|                                                       |                                       |                                                                                       | ^                                |                         |

|                                                       |                                       |                                                                                       | X=                               |                         |

|                                                       |                                       |                                                                                       | ×=                               | =                       |

|                                                       |                                       |                                                                                       | ×=                               | =                       |

|                                                       | ······                                |                                                                                       | ×=                               | =                       |

|                                                       | . <u> </u>                            | · .<br>· · · · · · · · · · · · · · · · · ·                                            | ×=                               | <u> </u>                |

|                                                       |                                       |                                                                                       | Subtotal                         |                         |

|                                                       |                                       |                                                                                       | Must Add Your<br>Local Sales Tax |                         |

| Postage: add                                          | d 10% of subtotal                     | ····                                                                                  | Postage                          |                         |

|                                                       |                                       |                                                                                       | Total                            |                         |

| accept VISA, Master<br>for delivery.                  | rCard or American Expres              | any purchase order with thi<br>s. Make payment to Intel L<br>Expiration Date          | iterature Sales. Allow           | m).we also<br>2-4 weeks |

|                                                       |                                       |                                                                                       |                                  |                         |

| Signature                                             |                                       |                                                                                       |                                  |                         |

| Mail To: Intel Literati<br>P.O. Box 70<br>Mt. Prospec | ure Sales<br>641<br>ct, II 60056-7641 | International Customer<br>should use the Internationa<br>Sales Office or Distributor. | I order form or contact          |                         |

|                                                       | a in the U.C. and Can                 | a dia 1                                                                               |                                  |                         |

For phone orders in the U.S. and Canada Call Toll Free: (800) 548-4725

Prices good until 12/31/90. Source HB

# INTERNATIONAL LITERATURE ORDER FORM

| NAME:               |          |

|---------------------|----------|

| COMPANY:            |          |

| ADDRESS:            |          |

| CITY: STA           | TE: ZIP: |

| COUNTRY:            |          |

| PHONE NO.: ( )      |          |

| ORDER NO.     TITLE | X=       |

|                     | X=       |

|                     | ×=       |

|                     |          |

|                     | ×=       |

\_\_\_\_\_X\_\_\_\_=\_\_\_\_\_ Subtotal \_\_\_\_\_\_ Must Add Your Local Sales Tax \_\_\_\_\_\_ Total \_\_\_\_\_

# PAYMENT

Cheques should be made payable to your local Intel Sales Office (see inside back cover.)

Other forms of payment may be available in your country. Please contact the Literature Coordinator at your local Intel Sales Office for details.

The completed form should be marked to the attention of the LITERATURE COORDINATOR and returned to your local Intel Sales Office.

# intel®

# 80186/188, 80C186/C188 HARDWARE REFERENCE MANUAL

1990

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and may only be used to identify Intel products:

376, 386, 387, 486, 4-SITE, Above, ACE51, ACE96, ACE186, ACE196, ACE960, BITBUS, COMMputer, CREDIT, Data Pipeline, DVI, ETOX, FaxBACK, Genius, i, <sup>1</sup>, i486, i750, i860, ICE, iCEL, ICEVIEW, iCS, iDBP, iDIS, I<sup>2</sup>ICE, iLBX, iMDDX, iMMX, Inboard, Insite, Intel, Intel, Intel386, int<sub>e</sub>IBOS, Intel Certified, Intelevision, int<sub>e</sub>ligent Identifier, int<sub>e</sub>ligent Programming, Intellic, Intellink, iOSP, iPAT, iPDS, iPSC, iRMK, iRMX, iSBC, iSBX, iSDM, iSXM, Library Manager, MAPNET, MCS, Megachassis, MICROMAINFRAME, MULTIBUS, MULTICHANNEL, MULTIMODULE, MultiSERVER, ONCE, OpenNET, OTP, PRO750, PROMPT, Promware, QUEST, QueX, Quick-Frase, Quick-Pulse Programming, Ripplemode, RMX/80, RUPI, Seamless, SLD, SugarCube, TooITALK, UPI, Visual Edge, VLSiCEL, and ZapCode, and the combination of ICE, iCS, iRMX, iSBC, iSBX, ISXM, MCS, or UPI and a numerical suffix.

MDS is an ordering code only and is not used as a product name or trademark. MDS® is a registered trademark of Mohawk Data Sciences Corporation.

MULTIBUS is a patented Intel bus.

CHMOS and HMOS are patented processes of Intel Corp.

Intel Corporation and Intel's FASTPATH are not affiliated with Kinetics, a division of Excelan, Inc. or its FASTPATH trademark or products.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Corporation Literature Sales P.O. Box 7641 Mt. Prospect, IL 60056-7641

©INTEL CORPORATION 1989

# CUSTOMER SUPPORT

#### **INTEL'S COMPLETE SUPPORT SOLUTION WORLDWIDE**

Customer Support is Intel's complete support service that provides Intel customers with hardware support, software support, customer training, consulting services and network management services. For detailed information contact your local sales offices.

After a customer purchases any system hardware or software product, service and support become major factors in determining whether that product will continue to meet a customer's expectations. Such support requires an international support organization and a breadth of programs to meet a variety of customer needs. As you might expect, Intel's customer support is quite extensive. It can start with assistance during your development effort to network management. 100 Intel sales and service offices are located worldwide—in the U.S., Canada, Europe and the Far East. So wherever you're using Intel technology, our professional staff is within close reach.

#### HARDWARE SUPPORT SERVICES

Intel's hardware maintenance service, starting with complete on-site installation will boost your productivity from the start and keep you running at maximum efficiency. Support for system or board level products can be tailored to match your needs, from complete on-site repair and maintenance support to economical carry-in or mail-in factory service.

Intel can provide support service for not only Intel systems and emulators, but also support for equipment in your development lab or provide service on your product to your end-user/customer.

## SOFTWARE SUPPORT SERVICES

Software products are supported by our Technical Information Service (TIPS) that has a special toll free number to provide you with direct, ready information on known, documented problems and deficiencies, as well as work-arounds, patches and other solutions.

Intel's software support consists of two levels of contracts. Standard support includes TIPS (Technical Information Phone Service), updates and subscription service (product-specific troubleshooting guides and; *COMMENTS Magazine*). Basic support consists of updates and the subscription service. Contracts are sold in environments which represent product groupings (e.g., iRMX<sup>®</sup> environment).

#### **CONSULTING SERVICES**

Intel provides field system engineering consulting services for any phase of your development or application effort. You can use our system engineers in a variety of ways ranging from assistance in using a new product, developing an application, personalizing training and customizing an Intel product to providing technical and management consulting. Systems Engineers are well versed in technical areas such as microcommunications, real-time applications, embedded microcontrollers, and network services. You know your application needs; we know our products. Working together we can help you get a successful product to market in the least possible time.

#### **CUSTOMER TRAINING**

Intel offers a wide range of instructional programs covering various aspects of system design and implementation. In just three to ten days a limited number of individuals learn more in a single workshop than in weeks of self-study. For optimum convenience, workshops are scheduled regularly at Training Centers worldwide or we can take our workshops to you for on-site instruction. Covering a wide variety of topics, Intel's major course categories include: architecture and assembly language, programming and operating systems, BITBUS<sup>™</sup> and LAN applications.

#### **NETWORK MANAGEMENT SERVICES**

Today's networking products are powerful and extremely flexible. The return they can provide on your investment via increased productivity and reduced costs can be very substantial.

Intel offers complete network support, from definition of your network's physical and functional design, to implementation, installation and maintenance. Whether installing your first network or adding to an existing one, Intel's Networking Specialists can optimize network performance for you.

# **Table of Contents**

| 1.0      |      | RODUCTION                                                                |      |

|----------|------|--------------------------------------------------------------------------|------|

|          | 1.1  | The 80186 Product Family                                                 | 1-1  |

|          | 1.2  | How to Use the Hardware Reference                                        | 1-2  |

| <u> </u> |      | ERVIEW OF THE 80186 FAMILY                                               |      |

| 2.0      |      |                                                                          |      |

|          | 2.1  | Architectural Overview                                                   |      |

|          |      | 2.1.1 Execution Unit                                                     |      |

|          |      | 2.1.2 Bus Interface Unit                                                 |      |

|          |      | 2.1.3 General Registers                                                  |      |

|          |      | 2.1.4 Segment Registers                                                  |      |

|          |      | 2.1.5 Instruction Pointer                                                |      |

|          |      | 2.1.6 Flags                                                              | 2-4  |

|          |      | 2.1.7 Memory Segmentation                                                | 2-5  |

|          |      | 2.1.8 Logical Addresses                                                  | 2-5  |

|          |      | 2.1.9 Dynamically Relocatable Code                                       | 2-8  |

|          |      | 2.1.10 Stack Inplementation                                              | 2-9  |

|          |      | 2.1.11 Reserved Memory and I/O Space                                     | 2-10 |

|          | 2.2  | Software Overview                                                        | 2-10 |

|          |      | 2.2.1 Instruction Set                                                    |      |

|          |      | 2.2.1.1 Data Transfer Instructions                                       | 2-10 |

|          |      | 2.2.1.2 Arithmetic Instructions                                          |      |

|          |      | 2.2.1.3 Bit Manipulation Instructions                                    | 2-11 |

|          |      | 2.2.1.4 String Instructions                                              | 2-13 |

|          |      | 2.2.1.5 Program Transfer Instructions                                    | 2.13 |

|          |      | 2.2.1.6 Processor Control Instructions                                   | 2-14 |

|          |      | 2.2.2 Addressing Modes                                                   |      |

|          |      | 2.2.2.1 Register and Immediate Operand Addressing Modes                  | 2-15 |

|          |      | 2.2.2.1 Negister and miniediate Operand Addressing Modes                 | 2-10 |

|          |      | 2.2.2.2 Memory Addressing Mode                                           | 2-10 |

|          |      | 2.2.2.3 I/O Port Addressing<br>2.2.3 Data Types Used in the 80186 Family | 2-21 |

|          | 00   | 2.2.3 Data Types Used III the outoo Fathily                              | 2-21 |

|          |      | DMA Control Unit                                                         |      |

|          |      | Timers                                                                   |      |

|          | 2.5  | Interrupt Control Unit                                                   | 2-22 |

|          |      | Clock Generator                                                          |      |

|          | 2.7  | Chip Select and READY Generation Unit                                    | 2-23 |

|          | 2.8  | DRAM Refresh Control Unit (80C186/80C188 Only)                           | 2-23 |

|          |      | Power-Save Unit (80C186/80C188 Only)                                     |      |

|          | 2.10 | Access to Integrated Peripherals                                         | 2-23 |

| 3.0      | 801  | 86 BUS INTERFACE UNIT                                                    |      |

| 0.0      |      | T-States                                                                 | 3-1  |

|          | 22   | Physical Address Generation                                              | 3.3  |

|          | 2.2  | Data Bus                                                                 | 3_1  |

|          | 0.0  | 3.3.1 80186/80C186 Data Bus Operation                                    |      |

|          |      |                                                                          |      |

|          |      | 3.3.2 80188/80C188 Data Bus Operation                                    | 3-4  |

|          | ~ .  | 3.3.3 Peripherals Interface                                              | 3-5  |

|          | 3.4  | Bus Control Signals                                                      | 3-5  |

|          |      | 3.4.1 RD and WR                                                          | 3-5  |

|          |      | 3.4.2 Queue Status Lines                                                 |      |

|          |      | 3.4.3 Status Line                                                        |      |

|          |      | 3.4.4 Software-Initiated Bus Control                                     | 3-8  |

|          |      | 3.4.4.1 TEST Input and LOCK Output                                       |      |

|          |      | 3.4.4.2 Processor HALT                                                   | 3-8  |

# Table of Contents (continued)

|     | 0.5      | Transferration Observation Observation           | ~ ~        | ~      |

|-----|----------|--------------------------------------------------|------------|--------|

|     |          | Transcevier Control Signals                      |            |        |

|     | 3.6      | READY Interfacing                                | 3-9        | Э.     |

|     | 3.7      | Execution Unit/Bus Interface Unit Relationship   | 3-1        | 10     |

|     |          | 3.7.1 Prefetch Queue and Bus Performance         |            |        |

|     |          | 3.7.2 Bus Performance and CPU Performance        | 3-1        | 13     |

|     |          | 3.7.3 Wait States and CPU Performance            |            |        |

|     | 3.8      | HOLD/HLDA Interface                              |            |        |

|     | 0.0      | 3.8.1 Response to HOLD                           |            |        |

|     |          | 3.8.2 HOLD/HLDA Timing and Bus Latency           |            |        |

|     |          |                                                  |            |        |

|     | <b>.</b> | 3.8.3 Leaving HOLD                               | 3-1        | 1/     |

|     | 3.9      | Priority of Bus Cycle Types                      | 3-1        | 17     |

| 4.0 | CLO      | DCK GENERATOR                                    |            |        |

|     | 1 1      | Crystal Oscillator                               | 1.1        | í      |

|     | 4.1      | Using an External Oscillator                     | 4-1        | 4      |

|     |          |                                                  |            |        |

|     | 4.3      | Output from Clock Generator                      | 4-ż        | 2      |

|     | 4.4      | RESET                                            | 4-2        | 2      |

| 50  | PFF      | RIPHERAL CONTROL BLOCK                           |            |        |

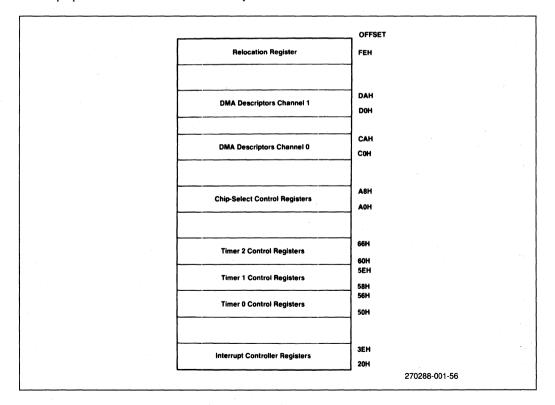

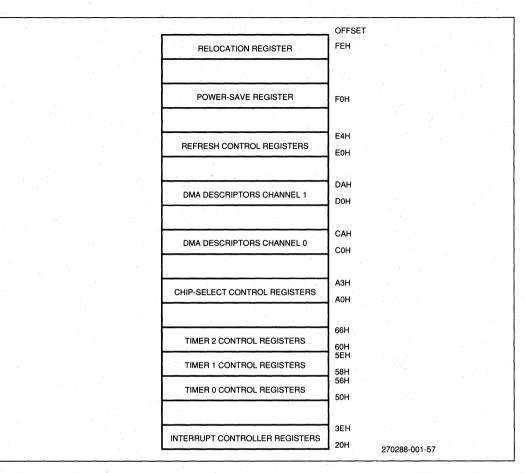

| 0.0 | E 4      | RIPHERAL CONTROL BLOCK Setting the Base Location | E 4        | 4      |

|     | 5.1      | Setting the base Location                        | 5-1<br>5-1 | 1      |

|     | 5.2      | Peripheral Control Block Registers               | 5-0        | 5      |

|     | 5.3      | Peripheral Configuration at RESET                | 5-3        | 3      |

| 6.0 | TIM      | ERUNIT                                           |            |        |

| 0.0 | 6 1      | Timer Unit Programming                           | 6          | i.     |

|     |          |                                                  |            |        |

|     |          | Timer Events                                     |            |        |

|     |          | Timer Input Pin Operation                        |            |        |

|     | 6.4      | Timer Output Pin Operation                       | 6-4        | ŧ      |

|     | 6.5      | Example Timer Initialization Code                | 6-5        | ō      |

|     |          | 6.5.1 Real Time Clock                            | 6-5        | 5      |

|     |          | 6.5.2 Baud Rate Generator                        | 6-8        | 3      |

|     |          | 6.5.3 Event Counter                              | 6-8        | 3      |

| 70  | CUI      | P SELECT/READY LOGIC                             |            |        |

| 1.0 |          |                                                  |            |        |

|     |          | Memory Chip Selects                              |            |        |

|     |          | Peripheral Chip Selects                          |            |        |

|     | 7.3      | READY Generation                                 | 7-2        | 2      |

|     | 7.4      | Overlapping Chip Select Blocks                   | 7-3        | 3      |

|     | 7.5      | Chip Selects and the 80C186 in Enhanced Mode     | 7-3        | 3      |

|     |          | Example System Initialization Code               |            |        |

| -   |          |                                                  |            |        |

| 8.0 | DIM      | A CONTROL UNIT                                   | 14         |        |

|     |          | DMA Features                                     |            |        |

|     | 8.2      | DMA Unit Programming                             | 8-1        | 1      |

|     | 8.3      | DMA Channel Priority                             | 8-2        | 2      |

|     | 8.4      | DMA Transfers                                    | 8-3        | 3      |

|     | 8.5      | DMA Requests                                     | 8-3        | 3      |

|     |          | 8.5.1 DMA Request Timing and Latency             | 8-4        | 4      |

|     |          | 8.5.2 DMA Acknowledge                            | 8-/        | 4      |

|     | 86       | Internally Generated DMA Requests                | 8.4        | 5      |

|     | 0.0      | Externally Supervised DMA Transform              | 0-0        | י<br>ב |

|     | Ø./      | Externally Synchronized DMA Transfers            |            |        |

|     |          | 8.7.1 Source Synchronized DMA Transfers          |            |        |

|     | 1.0      | 8.7.2 Destination Synchronized DMA Transfers     |            |        |

|     | 8.8      | DMA Halt and NMI                                 | 8-7        | 7      |

|     | 8.9      | Example DMA Interface Code                       | 8-7        | 7      |

|     |          |                                                  |            |        |

# Table of Contents (continued)

# 9.0 INTERRUPTS

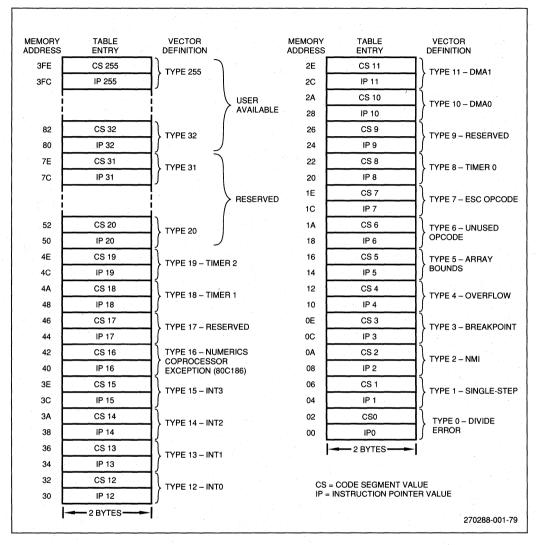

| 9.1 | Interru  | upt Control Model                                         | 9-1   |

|-----|----------|-----------------------------------------------------------|-------|

| 9.2 | Interru  | upt Characteristics Related to Type                       | 9-1   |

|     | 9.2.1    | Interrupts Handled Directly by the CPU                    | 9-1   |

|     |          | 9.2.1.1 Instruction-Generated Traps and Exceptions        | 9-1   |

|     |          | 9.2.1.2 Non-Maskable Interrupt (NMI)                      | 9-4   |

|     |          | 9.2.1.3 User-Defined Software Interrupts                  | 9-4   |

|     | 9.2.2    | Interrupts Handled by the Integrated Interrupt Controller | 9-4   |

| 93  | Other    | Interrupt Characteristics                                 | 9-4   |

| 0.0 | 931      | Interrupt Latency                                         | 9-4   |

|     | 932      | Interrupt Masks and Nesting                               | 9-5   |

|     | 933      | Interrupt Priority                                        | 9-5   |

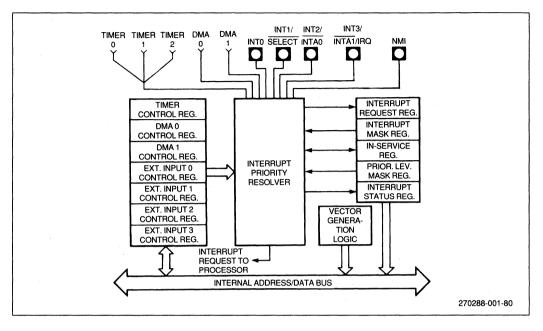

| 94  | Interri  | upt Control Unit Operation Modes                          | 9-8   |

| 9.4 | Maete    | er Mode                                                   | 9-8   |

| 5.5 | 051      | Master Mode External Connections                          | 0.8   |

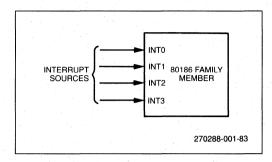

|     | 5.5.1    | 9.5.1.1 Direct Input Mode                                 | 0.8   |

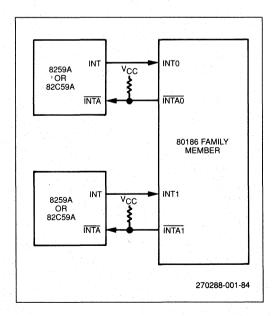

|     |          | 9.5.1.2 Casade Mode                                       | 0.8   |

|     | 052      | Master Mode Programming                                   | 0_0   |

|     | 9.5.2    | 9.5.2.1 Control Registers in Master Mode                  | 0.0   |

|     |          | 9.5.2.2 Cascade Mode                                      | 0.10  |

|     |          | 9.5.2.3 Special Fully Nested Mode                         | 0 10  |

|     |          | 9.5.2.4 Request Register in Master Mode                   | 0 11  |

|     |          | 9.5.2.5 Mask Register in Master Mode                      | 0 11  |

|     |          | 9.5.2.6 Priority Mask Register in Master Mode             | 0 11  |

|     |          | 9.5.2.7 In-Service Register in Master Mode                | 0 11  |

|     |          | 9.5.2.8 Poll and Poll Status Registers                    | 0 1 1 |

|     |          | 9.5.2.9 End of Interrupt Register in Master Mode          | 0 10  |

|     |          | 9.5.2.9 End of Interrupt Register in Master Mode          | 9-12  |

|     | 0 5 0    | 9.5.2.10 Interrupt Status Register in Master Mode         | 9-12  |

|     | 9.5.3    | Master Mode interrupt Sources                             | 9-13  |

|     |          |                                                           |       |

|     | 054      | 9.5.3.2 External Sources                                  |       |

|     | 9.5.4    | Master Mode Interrupt Response                            | 9-13  |

|     |          | 9.5.4.1 Internal Vectoring in Master Mode                 |       |

|     |          | 9.5.4.2 External Vectoring in Master Mode                 | 9-14  |

|     |          | 9.5.4.3 Master Mode Interrupt Response Time               | 9-14  |

| ~ ~ |          | Example Master Mode Initialization                        |       |

| 9.6 | Slave    | Mode                                                      | 9-15  |

|     |          | Slave Mode External Connections                           |       |

|     | 9.6.2    | Slave Mode Programming                                    | 9-17  |

|     |          | 9.6.2.1 Control Registers in Slave Mode                   | 9-17  |

|     |          | 9.6.2.2 Request Register in Slave Mode                    |       |

|     |          | 9.6.2.3 Mask Register in Slave Mode                       | 9-17  |

|     |          | 9.6.2.4 Priority Mask Register in Slave Mode              | 9-17  |

|     |          | 9.6.2.5 In-Service Register in Slave Mode                 |       |

|     |          | 9.6.2.6 End of Interrupt Register in Slave Mode           | 9-19  |

|     |          | 9.6.2.7 Interrupt Status Register in Slave Mode           | 9-19  |

|     | <b>.</b> | 9.6.2.8 Interrupt Vector Register                         |       |

|     | 9.6.3    | Slave Mode Interrupt Sources                              | 9-20  |

|     | 9.6.4    | Slave Mode Interrupt Response                             | 9-20  |

|     |          | 9.6.4.1 Internal Vectoring in Slave Mode                  | 9-20  |

|     |          | 9.6.4.2 External Vectoring in Slave Mode                  | 9-21  |

|     |          |                                                           |       |

# Table of Contents (continued)

| 9.6.4.3 Slave Mode Interrupt Response Time                                      |               |

|---------------------------------------------------------------------------------|---------------|

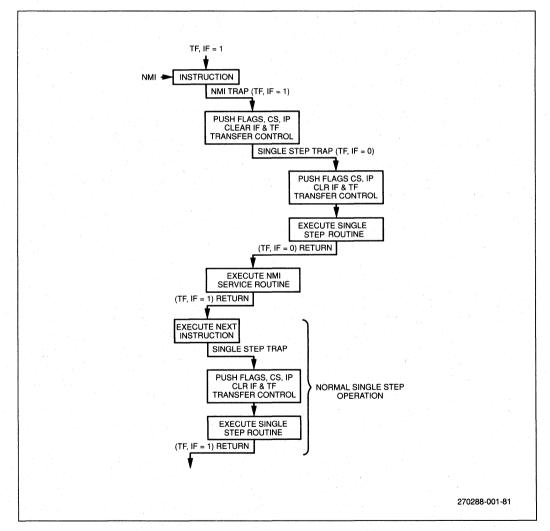

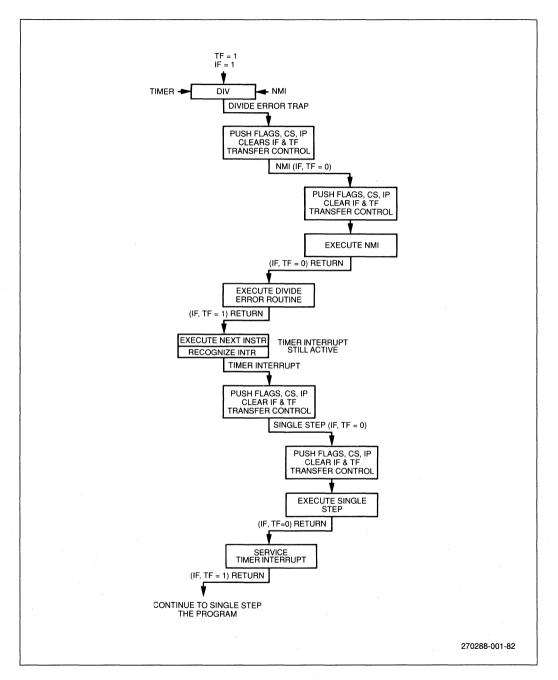

| 9.6.5 Example Slave Mode Initialization<br>9.7 Interrupt Controller Flow Charts | 9-22<br>9-23  |

| 10.0 REFRESH CONTROL UNIT (80C186/80C188 ONLY)                                  |               |

| 10.1 Refresh Control Unit Programming                                           | 10-1          |

| 10.2 Refresh Control Unit Operation                                             |               |

| 10.3 Refresh Addresses                                                          |               |

| 10.4 Refresh Operation and Bus HOLD                                             |               |

| 10.5 Example RCU Initialization Code                                            | 10-4          |

| 11.0 POWER-SAVE UNIT (80C186/80C188 ONLY)                                       |               |

| 11.1 Power-Save Unit Programming                                                |               |

| 11.2 Power-Save Operation                                                       |               |

| 11.3 Example Power-Save Initialization Code                                     | 11-2          |

| 12.0 HARDWARE PROVISIONS FOR FLOATING POINT MATH                                |               |

| 12.1 Using the 80186/80188 with the 8087 Numerics Coprocessor                   |               |

| 12.1.1 Overview of Numerics Coprocessing                                        |               |

| 12.1.28087 Instruction Set<br>12.1.2.1 Data Transfer Instructions               |               |

| 12.1.2.1 Data transfer instructions                                             |               |

| 12.1.2.2 Anumetic instructions                                                  |               |

| 12.1.2.4 Transcendental Instructions                                            |               |

| 12.1.2.5 Constant Instructions                                                  |               |

| 12.1.2.6 Processor Control Instructions                                         |               |

| 12.1.38087 Data Types                                                           |               |

| 12.1.480186(80188)/8087 Interface                                               | 12-4          |

| 12.1.580186(80188) Bus Cycles during Numerics Coprocessing                      | 12-6          |

| 12.2 Using the 80C186 with the 80C187 Numerics Processor Extension              |               |

| 12.2.1 Overview of the 80C187 Numerics Processor Extension                      |               |

| 12.2.280C187 Additions to Instruction Set<br>12.2.380C186/80C187 Interface      |               |

| 12.2.480C186 Bus Cycles with the Numerics Processor Extension                   | /-2.2<br>12_8 |

| APPENDIX A – DIFFERENCE BETWEEN THE 80186 FAMILY                                |               |

| AND THE BOOC BOOD                                                               |               |

| AND THE 8086/8088<br>A.1 CPU Performance                                        | Λ -1          |

| A.1 CPO Performance                                                             | A-1           |

| A.3 Local Bus Controller and Control Signals                                    | Δ_1           |

| A.4 HOLD/HLDA vs. REQUEST/GRANT                                                 | A-1           |

| A.5 Status Information                                                          | A-1           |

| A.6 Bus Utilization                                                             |               |

| A.7 Instruction Execution                                                       | A-2           |

| APPENDIX B – SYNCHRONIZATION OF EXTERNAL INPUTS                                 |               |

| B.1 Why Synchronizers are Required                                              | B-1           |

| B.2 80186 Synchronizers                                                         | B-1           |

| <b>APPENDIX C – SUMMARY OF DIFFERENCES AMONG FAMILY MEMBERS</b>                 |               |

| C.1 Differences Due to Data Bus Width                                           | C-1           |

| C.2 Differences Between NMOS and CMOS Devices                                   | C-1           |

|                                                                                 |               |

# Introduction

# 1

# CHAPTER 1 INTRODUCTION

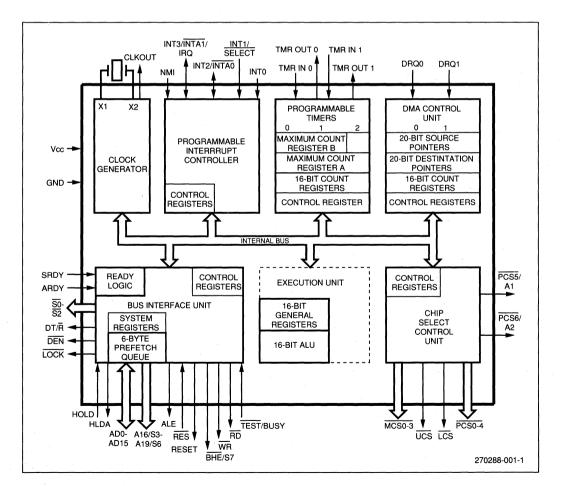

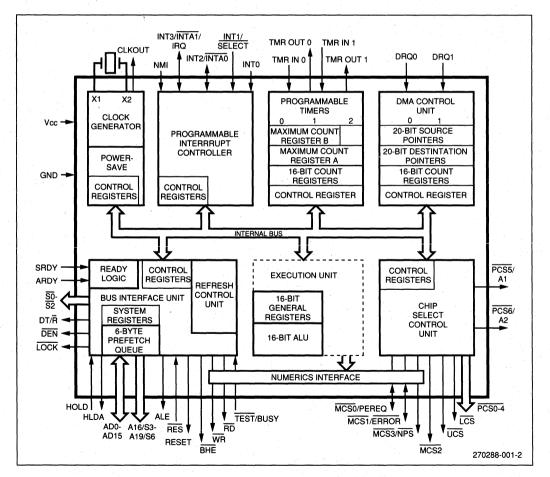

The 80186 microprocessor family holds the position of industry standard among high integration microprocessors. VLSI technology incorporates the most commonly used peripheral functions with a 16-bit CPU on the same silicon die to assure compatibility and high reliability. The 80186 family reputation for flexibility and uncomplicated programming makes it the first choice embedded microprocessor for such applications as local area network equipment, PC add-on cards, terminals, disk storage subsystems, avionics, and medical instrumentation. Figure 1 is a block diagram of the 80186 processor.

#### 1.1 THE 80186 PRODUCT FAMILY

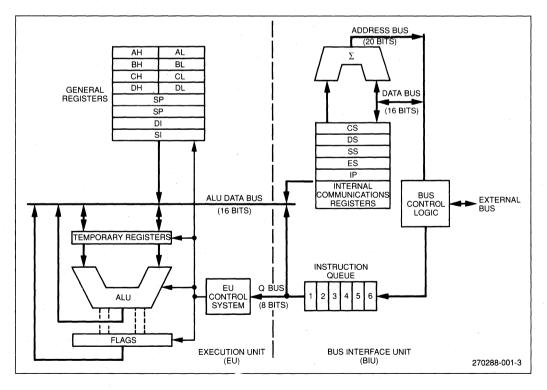

The 80186 family actually consists of four devices: the original 80186 and 80188, and the newer 80C186 and 80C188 microprocessors manufactured on Intel's CHMOS III process. The 80188 and 80C188 are 16-bit microprocessors but have 8-bit external data buses. The 80C186 and 80C188 offer the advantage of increased speed (up to 16 MHz) and important new features including a Refresh Control Unit, Power-Save logic, and ONCE<sup>™</sup>Mode (see Figure 2).

#### Figure 1. 80186 Block Diagram

All family members employ a 20-bit address bus for a one megabyte memory address space and a 64 kilobyte I/O address space. All processors use the same instruction format. Software written for one CPU will execute on the other CPUs without alteration (with the possible exception of floating-point code).

For simplicity, this Hardware Reference uses phrases like "80186 family processor" to refer to features and functions shared commonly by the 80186, 80188, 80C186, and 80C188. This manual refers to specific member or members of the product family directly by product number.

#### 1.2 HOW TO USE THE HARDWARE REFERENCE

The purpose of this Hardware Reference is to explain the operation of 80186 family processors with a degree of detail not possible in the data sheet. The emphasis is on the integrated peripheral set, since that is the essence of the 80186 family. The designer with questions about the function of a particular peripheral is encouraged to turn directly to the specific sections suggested by the table of contents.

Figure 2. 80C186 Block Diagram

# Overview of the 80186 Family 2

# CHAPTER 2 OVERVIEW OF THE 80186 FAMILY

The 80186 processor shares a common base arc/atecture with the 8086, 8088, 80286, 386TM, and 486TM processors. It is completely object code compatible with the well-known 8086/ 8088. However, most instructions require fewer clocks to execute on the 80186 family because of hardware enhancements in the Bus Interface Unit and the Execution Unit. In addition, there are a number of additional instructions which simplify programming and reduce code size (see Appendix A.7).

The 80186 family operates virtually the same as the 8086. The added benefits of the 80186 family are the on-chip DMA, Timer, Interrupt Control, Chip Select, and READY Generation Units. This concept of **high integration** greatly simplifies system design.

The 80186 family operates from a single +5 V supply. It is available in several standard package configurations. For a given product, the pinout is identical among any of the available 68-pin packages: Pin Grid Array (PGA), Leadless Chip Carrier (LCC), and Plastic Leaded Chip Carrier (PLCC). This means that sockets for any of the three package types may be mounted on a printed circuit board drilled with the same 68-pin pattern.

#### 2.1 ARCHITECTURAL OVERVIEW

An 80186 family processor incorporates two separate processing units: an Execution Unit (EU) and a Bus Interface Unit (BIU). The EU is functionally identical among all family members. In the 80186/80C186 the BIU is configured for a 16-bit external data bus and in the 80188/80C188 the BIU is configured for an 8-bit external data bus. The two units are connected by an instruction prefetch queue.

The EU executes instructions and the BIU fetches instructions, reads operands, and writes results. Whenever the EU requires another opcode byte, it takes the byte out of the prefetch

Figure 3. Simplied Functional Bock Diagram of 80186 Family CPU

queue. The two units can operate independently of one another and are able, under most circumstances, to extensively overlap instruction fetches and execution.

An 80186 family processor has a 16-bit Arithmetic Logic Unit (ALU) which performs 8-bit or 16-bit arithmetic and logical operations. It provides for data movement among registers, memory and I/O space. In addition, the CPU allows for high speed data transfer from one area of memory to another using string move instructions, and to or from an I/O port and memory using block I/O instructions. Finally, the CPU provides many conditional branch and control instructions.

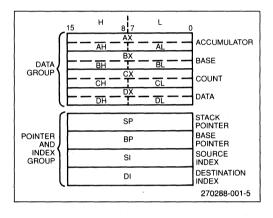

This architecture features 14 basic registers which are grouped as general registers, segment registers, pointer registers, and status and control registers. The four 16-bit general purpose registers (AX, BX, CX, and DX) may be used as operands in most arithmetic operations in either 8- or 16-bit units. The four 16-bit pointer registers (SI, DI, BP, and SP) may be used both in arithmetic operations and in accessing memory-based variables. Four 16-bit segment registers (CS, DS, SS, and ES) allow simple memory partitioning to aid modular programming. The status and control registers consist of an instruction pointer (IP) and a status word register containing flag bits.

Figure 3 is a simplified CPU block diagram.

## 2.1.1 EXECUTION UNIT

The EU is responsible for the execution of all instructions, for providing data and addresses to the BIU, and for manipulating the general registers and the flag register. A 16-bit Arithmetic Logic Unit (ALU) in the EU maintains the CPU status and control flags, and manipulates the general registers and instruction operands. All registers and data paths in the EU are 16 bits wide for fast internal transfers. The EU does not connect directly to the system bus. It obtains instructions from a queue maintained by the BIU. Likewise, when an instruction requires access to memory or to a peripheral device, the EU requests the BIU to obtain and store the data. All addresses manipulated by the EU are 16 bits wide. The BIU, however, performs an address calculation that gives the EU access to the full megabyte of memory space.

When the EU is ready to execute an instruction, it fetches the instruction object code byte from the BIU's instruction queue and then executes the instruction. If the queue is empty when the EU is ready to fetch an instruction byte, the EU waits for the instruction byte to be fetched. If a memory location or I/O port must be addressed during the execution of an instruction, the EU requests the BIU to perform the required bus cycle.

### 2.1.2 BUS INTERFACE UNIT

The 80186/80C186 and 80188/80C188 BIUs are functionally identical, but are implemented differently to match the structure and performance characteristics of their respective system buses. Data is transferred between the CPU and memory or peripheral devices upon demand from the EU. The BIU executes all external bus cycles. This unit consists of the segment registers, the instruction pointer, the instruction code queue, and several miscellaneous registers. The BIU transfers data to and from the EU on the ALU data bus.

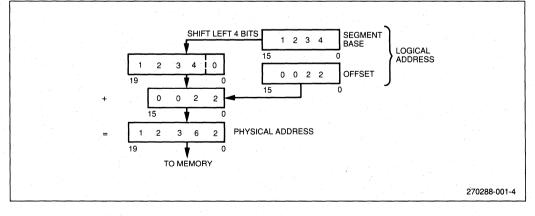

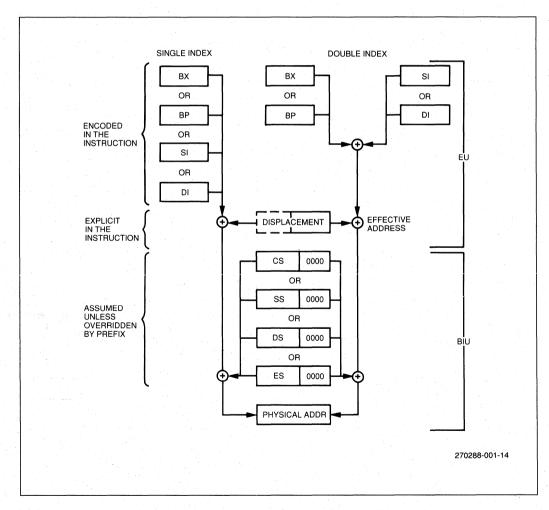

The BIU generates 20-bit physical addresses in a dedicated adder. The adder shifts a 16-bit segment value left 4 bits and then adds an offset value derived from combinations of the pointer registers, the instruction pointer, and immediate values (see Figure 4). Any carry of this addition is ignored.

During periods when the EU is busy executing instructions, the BIU "looks ahead" and prefetches more instructions from

#### **Figure 4. Physical Address Generation**

memory. As long as the prefetch queue is partially full, the EU can quickly retrieve instructions upon demand.

## 2.1.3 GENERAL REGISTERS

80186 family CPUs have eight 16-bit general registers (see Figure 5). The general registers are subdivided into two sets of four registers each. These are the data registers (also called the H & L group for high and low), and the pointer and index registers (also called the P & I group).

#### **Figure 5. General Registers**

The data registers are unique in that their upper and lower halves are separately addressable. This means that each data register can be used interchangeably as a 16-bit register or as two 8-bit registers. The other CPU registers are always accessed as 16-bit only. The CPU can use data registers without

| Table 1. Im | plicit Use | of General | Registers |

|-------------|------------|------------|-----------|

|-------------|------------|------------|-----------|

| REGISTER | OPERATIONS                                                             |

|----------|------------------------------------------------------------------------|

| AX       | Word Multiply, Word Divide,<br>Word I/O                                |

| AL       | Byte Multiply, Byte Divide, Byte<br>I/O, Translate, Decimal Arithmetic |

| AH       | Byte Multiply, Byte Divide                                             |

| BX       | Translate                                                              |

| СХ       | String Operations, Loops                                               |

| CL       | Variable Shift and Rotate                                              |

| DX       | Word Multiply, Word Divide,<br>Indirect I/O                            |

| SP       | Stack Operations                                                       |

| SI       | String Operations                                                      |

| DI       | String Operations                                                      |

constraint in most arithmetic and logic operations. Most arithmetic and logic operations can also use the pointer and index registers. Additionally, some instructions use certain registers implicitly (see Table 1), therefore allowing compact yet powerful encoding.

The state of any of the general registers is undefined at RE-SET.

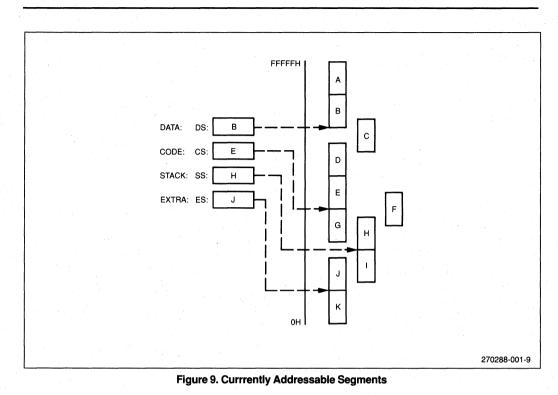

#### 2.1.4 SEGMENT REGISTERS

The 80186 family memory space (up to one megabyte) is divided into logical segments of up to 64 Kbytes each. The CPU has direct access to four segments at a time. The base addresses (starting locations) of these memory segments are contained in the segment registers (see Figure 6). The CS register points to the current code segment. Instructions are fetched from the CS segment. The SS register points to the current stack segment. The DS register points to the current data segment. The DS register points to the current data segment. The data segment generally contains program variables. The ES register points to the current extra segment, which also is typically used for data storage. The segment registers are accessible to programs and can be manipulated with several instructions.

| 15 |    | 0                |

|----|----|------------------|

|    | CS | CODE<br>SEGMENT  |

|    | DS | DATA<br>SEGMENT  |

|    | SS | STACK<br>SEGMENT |

|    | ES | EXTRA<br>SEGMENT |

|    |    | 270288-001-6     |

#### Figure 6. Segment Registers

Upon RESET, the CS register is initialized to 0FFFFH, and the DS, ES, and SS register are all initialized to zero.

#### 2.1.5 INSTRUCTION POINTER

The BIU updates a 16-bit instruction pointer (IP) register so that it contains the offset (distance in bytes) of the next instruction from the beginning of the current code segment. In other words, the IP register points to the next instruction. During normal execution, the instruction pointer contains the offset of the next instruction to be **fetched** by the BIU. Whenever the IP register is saved on the stack, however, it is first automatically adjusted to point to the next instruction to be **executed**. Programs do not have direct access to the instruction pointer, but it may change, be saved, or be restored as a result of program execution.

RESET initializes the instruction pointer to 0000H. The concatenation of CS and IP values comprises a starting execution address of 0FFFF0H (see Section 2.1.8 for a description of address formation).

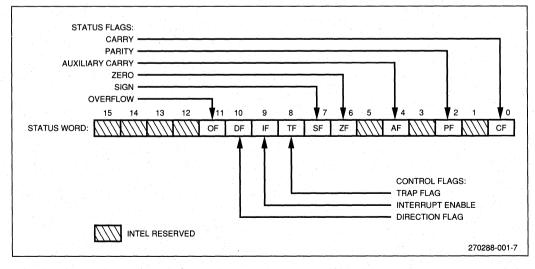

## 2.1.6 FLAGS

An 80186 family processor has six one-bit status flags (see Figure 7) that the EU posts as the result of an arithmetic or logic operation. Program branch instructions allow a program to alter its execution depending on conditions flagged by prior operation. Different instructions affect the status flags differently, generally reflecting the following states:

- If the auxiliary flag (AF) is set, there has been a carry out from the low nibble into the high nibble or a borrow from the high nibble into the low nibble of an 8-bit quantity (low-order byte of a 16-bit quantity). This flag is used by decimal arithmetic instructions.

- If the carry flag (CF) is set, there has been a carry out of, or a borrow into, the high-order bit of the instruction result (8- or 16-bit). The flag is used by instructions that add and subtract multibyte numbers. Rotate instructions can also isolate a bit in memory or a register by placing it in the carry flag.

- If the overflow flag (OF) is set, an arithmetic overflow has occurred; that is, a significant digit has been lost because

the size of the result exceeded the capacity of its destination location. An Interrupt On Overflow instruction is available that will generate an interrupt in this situation.

- If the sign flag (SF) is set, the high-order bit of the result is a 1. Since negative binary numbers are represented in standard two's complement notation, SF indicates the sign of the result (0 = positive, 1 = negative).

- If the parity flag (PF) is set, the result has even parity, an even number of 1-bits. This flag can be used to check for data transmission errors.

- If the zero flag (ZF) is set, the result of the operation is 0.

The additional control flags (see Figure 7) can be set and cleared by programs to alter processor operations:

- Setting the direction flag (DF) causes string instructions to auto-decrement; that is, to process strings from the high address to the low address, or "right to left". Clearing DF causes string instructions to auto-increment, or process strings "left to right."

- Setting the interrupt-enable flag (IF) allows the CPU to recognize maskable external or internal interrupt requests. Clearing IF disables these interrupts. The interrupt-enable flag has no effect upon software interrupts or non-maskable externally generated interrupts.

- Setting the trap flag (TF) puts the processor into singlestep mode for debugging. In this mode, the CPU automati-

Figure 7. Status Word Format

cally generates an internal interrupt after each instruction, allowing a program to be inspected as it executes instruction by instruction.

Both the status and control flags are contained in a 16-bit status word (see Figure 7). The RESET condition of the status word is 0F000H.

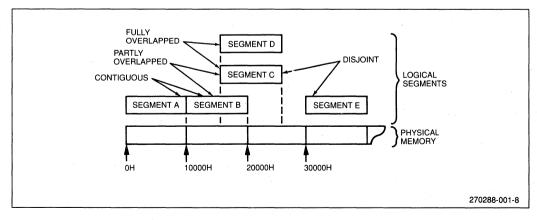

### 2.1.7 MEMORY SEGMENTATION

Programs for the 80186 family view the one megabyte memory space as a group of segments that are user-defined according to application. A segment is a logical unit of memory that may be up to 64 Kbytes long. Each segment if made up of contiguous memory locations and is an independent, separately-addressable unit. Software assigns every segment a base address (starting location) in memory space. All segments begin on 16-bit memory boundaries. There are no other restrictions on segment locations. Segments may be adjacent, disjoint, partially overlapped, or fully overlapped (see Figure 8). A physical memory location may be mapped into (covered by) one or more logical segments.

The four segment registers point to four "currently addressable" segments (see Figure 9). The currently addressable segments provide a work space consisting of 64 Kbytes for code, a 64K stack, and 128K of data storage. Programs obtain access to code and data in other segments by changing the segment registers to point to the desired segments.

The segmented memory structure of the 80186 family is a hardware provision to encourage modular programming. Every program will use segmentation differently. Smaller applications tend to initialize the segment registers and then simply forget them. Larger applications give careful consideration to segment definition and use.

#### 2.1.8 LOGICAL ADDRESSES

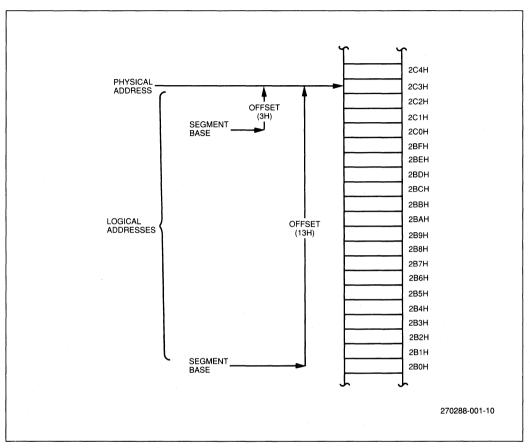

It is useful to think of every memory location as having two kinds of addresses, physical and logical. A physical address is a 20-bit value that identifies each unique byte location in the memory space. Physical addresses range from 0H to FFFFFH. All exchanges between the CPU and memory components use a physical address.

Programs deal with logical, rather than physical addresses. Program code can be developed without prior knowledge of where the code is to be located in memory; in larger applications, dynamic management of memory resources is a necessity. A logical address consists of a segment base value and an offset value. For any given memory location, the segment base value locates the first byte of the segment and the offset value is the distance, in bytes, of the target location from the beginning of the segment. Segment base and offset values are unsigned 16-bit quantities. Many different logical addresses can map to the same physical location. In the example (see Figure 10), physical memory location 2C3H is contained in two different overlapping segments, one beginning at 2B0H and the other at 2C0H.

If left alone, the processor automatically assigns segments based on the specific addressing needs of the program. The segment register to be selected is automatically chosen according to the rules in Table 2. All information in one segment type generally shares the same logical attributes (e.g., code or data), leading to programs which are shorter, faster, and better structured.

Figure 8. Segment Locations in Physical Memory

intel

## **OVERVIEW OF THE 80186 FAMILY**

Figure 10. Logical and Physical Address

To generate a physical address, the BIU must first obtain the logical address. The logical address of a memory location can come from different sources, depending on the type of reference that is being made (see Table 2).

Segment base addresses are always held in the segment registers. The BIU conveniently assumes which segment register contains the base address according to the type of memory reference made. However, it is possible for a programmer to explicitly direct the BIU to access a variable in any of the currently addressable segments (except for the destination operand of a string instruction). In assembly language, this is done by preceding an instruction with a segment override prefix.

| TYPE OF MEMORY REFERENCE    | DEFAULT<br>SEGMENT<br>BASE | ALTERNATE<br>SEGMENT<br>BASE | OFFSET            |

|-----------------------------|----------------------------|------------------------------|-------------------|

| Instruction Fetch           | CS                         | NONE                         | IP                |

| Stack Operation             | SS                         | NONE                         | SP                |

| Variable (except following) | DS                         | CS, ES, SS                   | Effective Address |

| String Source               | DS                         | CS, ES, SS                   | SI                |

| String Destination          | ES                         | NONE                         | DI                |

| BP Used As Base Register    | SS                         | CS, DS, ES                   | Effective Address |

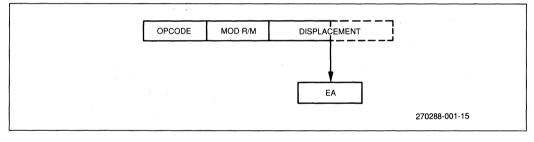

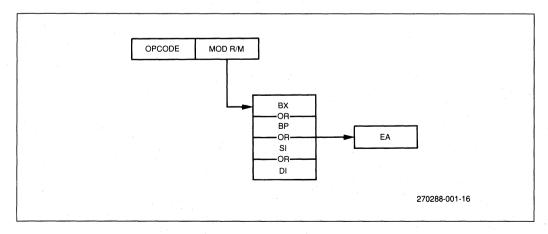

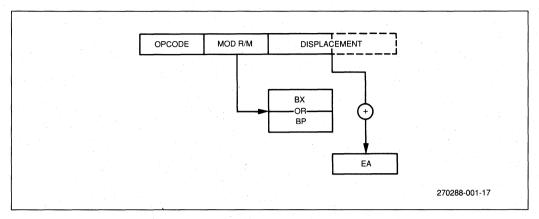

#### Table 2. Logical Address Sources

Instructions are always fetched from the current code segment; the IP register contains the offset of the target instruction from the beginning of the segment. Stack instructions always operate on the current stack segment; the SP (stack pointer) register contains the offset of the top of the stack. Most variables (memory operands) are assumed to reside in the current data segment, but a program can instruct the BIU to override this assumption. Often, the offset of a memory variable is not directly available and must be calculated at execution time. This calculation is based on the addressing mode (see Section 2.2.2) specified in the instruction; the result is called the operand's effective address (EA).

Strings are addressed differently than other variables. The source operand of a string instruction is assumed to lie in the current data segment, but the program may use another currently addressable segment. The operand's offset is taken from the SI (source index) register. The destination operand of a string instruction always resides in the current extra segment;

its offset is taken from the DI (destination index) register. The string instructions automatically adjust the SI and DI registers as they process the strings one byte or word at a time.

When register BP, the base pointer register, is designated as a base register in an instruction, the variable is assumed to reside in the current stack segment. Therefore, register BP provides a convenient way to address data on the stack. However, the BP register can also be used to access data in any of the other currently addressable segments.

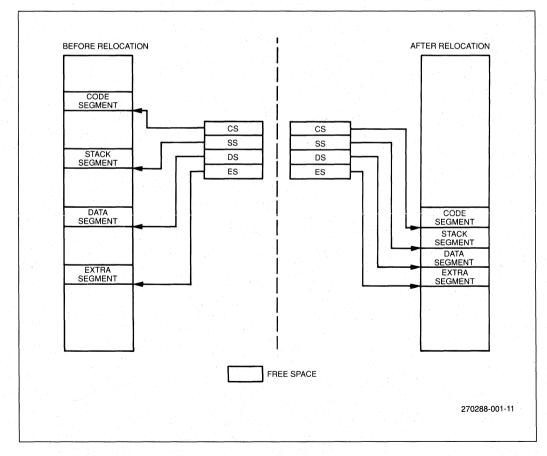

#### 2.1.9 DYNAMICALLY RELOCATABLE CODE

The segmented memory structure of the 80186 family makes it possible to write programs that are position-independent, or dynamically relocatable. Dynamic relocation allows a multiprogramming or multitasking system to make particularly

#### Figure 11. Dynamic Code Relocation

effective use of available memory. The processor can write inactive programs to a disk and reallocate the space they occupied to other programs. If a disk-resident program is needed later, it can be read back into any available memory location and restarted. Similarly, if a program needs a large contiguous block of storage, and the total amount is only available in nonadjacent fragments, other program segments can be compacted to free up a continuous space. This process is illustrated graphically in Figure 11.

To be dynamically relocatable, a program must not load or alter its segment registers and must not transfer directly to a location outside the current code segment. In other words, all offsets in the program must be relative to fixed values contained in the segment registers. This allows the program to be moved anywhere in memory as long as the segment registers are updated to point to the new base addresses.

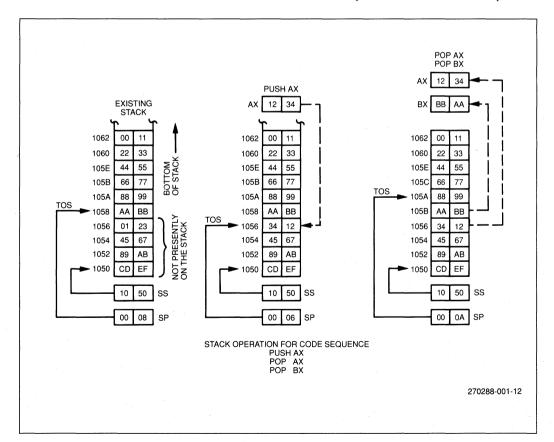

#### 2.1.10 STACK IMPLEMENTATION

Stacks in the 80186 family are implemented in memory and are located by the stack segment register (SS) and the stack pointer (SP). A system may have numerous stacks, and a stack may be up to 64 Kbytes long, the maximum length of a segment. An attempt to grow a stack beyond 64K overwrites the beginning of the segment. Only one stack is directly addressable at a time. The SS register contains the base address of the current stack; however, the base address is not the origination point of the stack. The SP register contains an offset which points to the top of stack (TOS).

Stacks are 16 bits wide; instructions that operate on a stack add and remove stack elements one word at a time. An element is pushed onto the stack (see Figure 12) by first **decrementing** the SP register by 2 and then writing the data word. An element is popped off the stack by copying it from TOS and then **incrementing** the SP register by 2. In other words, the stack goes **down** in memory toward its base address. Stack operations

Figure 12. Stack Operation

never move elements on the stack, nor do they erase them. The top of the stack changes only as a result of updating the stack pointer.

### 2.1.11 RESERVED MEMORY AND I/O SPACE

Two specific areas in memory and one area in I/O space are reserved in the 80186 family.

- Locations 0H through 3FFH in low memory are reserved for interrupt vectors.

- Locations 0FFFF0H through 0FFFFFH in high memory are reserved for system reset code since the processor begins execution at 0FFFF0H.

- Locations 0F8H through 0FFH in I/O space are reserved for communication with other Intel hardware products. On the 80C186, these addresses are used as I/O ports for the 80C187 numerics processor extension.

The peripheral control block (see Section 5.0) may reside in memory or I/O space. All unused locations in the peripheral control block are also reserved.

## 2.2 SOFTWARE OVERVIEW

All 80186 family members execute exactly the same instructions. This instruction set includes all the 8086/8088 instructions plus several useful additions and enhancements. The following sections provide a description of the instructions by category and a detailed discussion of the various operand addressing modes.

Software for 80186 family systems does not need to be written in assembly language. The processor provides direct hardware support for programs written in the many high-level languages available. Most high-level languages store variables in memory; the symmetrical instruction set supports direct operation on memory operands, including operands on the stack. The hardware addressing modes provide efficient, straightforward implementations of based variables, arrays, arrays of structures and other high-level language data constructs. A powerful set of memory-to-memory string operations is available for efficient character data manipulation. Finally, routines with critical performance requirements that cannot be met with high-level languages may be written in assembly language and linked with high-level code.

#### 2.2.1 INSTRUCTION SET

Instructions in the 80186 processor family treat different types of operands uniformly. Nearly every instruction can operate on either byte or word data. Register, memory and immediate operands may be specified interchangeably in most instructions. The exception to this is that immediate values serve as source and not destination operands. In particular, memory variables may be added to, subtracted from, shifted, compared, and so on, in place, without moving them in and out of registers. This saves instructions, registers, and execution time in assembly language programs. In high-level languages, where most variables are memory-based, compilers can produce faster and shorter object programs.

The 80186 family instruction set can be viewed as existing on two levels. One is the assembly level and the other is the machine level. To the assembly language programmer, the 80186 family appears to have a repertoire of about 100 instructions. One MOV (data move) instruction, for example, transfers a byte of a word from a register of a memory location or an immediate value to either a register or a memory location. The 80186 family CPUs, however, recognize 28 different machine versions of the MOV instruction.

The two levels of instruction set address two different requirements: efficiency and simplicity. The approximately 300 forms of machine-level instructions make very efficient use of storage. For example, the machine instruction that increments a memory operand is three or four bytes long because the address of the operand must be encoded in the instruction. To increment a register, however, does not require as much information, so the instruction can be shorter. The 80186 family has eight different machine-level instructions that increment a different 16-bit register. Each of these instructions is only one byte long.

The assembly level instructions simplify the programmer's view of the instruction set. The programmer writes one form of an INC (increment) instruction and the assembler examines the operand to determine which machine level instruction to generate. The following paragraphs provide a functional description of the assembly-level instructions.

# 2.2.1.1 DATA TRANSFER INSTRUCTIONS

The instruction set contains 14 data transfer instructions. These instructions move single bytes and words between memory and registers, and also move single bytes and words between the AL or AX registers and I/O ports. Table 3 lists the four types of data transfer instructions and their functions.

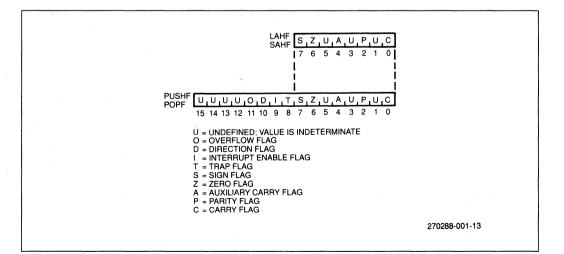

Data transfer instructions are categorized as general purpose, input/output, address object, and flag transfer. The stack manipulation instructions which are used for transferring flag contents, and the instructions for loading segment registers are also included in this group. Figure 13 shows the flag storage formats. The address object instructions manipulate the addresses of variables instead of the contents of values of the variables. This is useful for list processing, based variable, and string operations.

#### Table 3. Data Transfer Instructions

|                                | GENERAL PURPOSE             |  |  |

|--------------------------------|-----------------------------|--|--|

| MOV                            | Move byte or word           |  |  |

| PUSH                           | Push word onto stack        |  |  |

| POP                            | Pop word off stack          |  |  |

| PUSHA                          | Push registers onto stack   |  |  |

| POPA                           | Pop registers off stack     |  |  |

| XCHG                           | Exchange byte or word       |  |  |

| XLAT                           | Translate byte              |  |  |

|                                | INPUT/OUTPUT                |  |  |

| IN                             | Input byte or word          |  |  |

| OUT                            | Output byte or word         |  |  |

| ADDRESS OBJECT AND STACK FRAME |                             |  |  |

| LEA                            | Load effective address      |  |  |

| LDS                            | Load pointer using DS       |  |  |

| LES                            | Load pointer using ES       |  |  |

| ENTER                          | Build stack frame           |  |  |

| LEAVE                          | Tear down stack frame       |  |  |

|                                | FLAG TRANSFER               |  |  |

| LAHF                           | Load AH register from flags |  |  |

| SAHF                           | Store AH register in flags  |  |  |

| PUSHF                          | Push flags onto stack       |  |  |

| POPF                           | Pop flags off stack         |  |  |

#### 2.2.1.2 ARITHMETIC INSTRUCTIONS

The arithmetic instructions (see Table 4) operate on four types of numbers:

- 1. Unsigned binary.

- 2. Signed binary (integers).

- 3. Unsigned packed decimal.

- 4. Unsigned unpacked decimal.

Table 5 shows the interpretations of various bit patterns according to each number type.

Binary numbers may be 8 or 16 bits long. Decimal numbers are stored in bytes, two digits per byte for packed decimal and one digit per byte for unpacked decimal. The processor always assumes that the operands specified in arithmetic instructions contain data that represent valid numbers for the instruction being performed. Invalid data may produce unpredictable results. The processor analyzes arithmetic results and posts certain characteristics of the operation to six flags.

## 2.2.1.3 BIT MANIPULATION INSTRUCTIONS

There are three groups of instructions for manipulating bits within both bytes and word. These three groups are logical, shifts and rotates. Table 6 lists these three groups of bit manipulation instructions with their functions.

#### Figure 13. Flag Storage Format

#### Table 4. Arithmetic Instructions

|      | ADDITION                             |

|------|--------------------------------------|

| ADD  | Add byte or word                     |

| ADC  | Add byte or word with carry          |

| INC  | Increment byte or word by 1          |

| AAA  | ASCII adjust for addition            |

| DAA  | Decimal adjust for addition          |

|      | SUBTRACTION                          |

| SUB  | Subtract byte or word                |

| SBB  | Subtract byte or word with<br>borrow |

| DEC  | Decrement byte or word by 1          |

| NEG  | Negate byte or word                  |

| CMP  | Compare byte or word                 |

| AAS  | ASCII adjust for subtraction         |

| DAS  | Decimal adjust for subtraction       |

|      | MULTIPLICATION                       |

| MUL  | Multiply byte or word unsigned       |

| IMUL | Integer multiply byte or word        |

| AAM  | ASCII adjust for multiply            |

|      | DIVISION                             |

| DIV  | Divide byte or word unsigned         |

| IDIV | Integer divide byte or word          |

| AAD  | ASCII adjust for division            |

| CBW  | Convert byte to word                 |

| CWD  | Convert word to doubleword           |

| Table 6. Bit Manipulation Instructions |                                               |  |

|----------------------------------------|-----------------------------------------------|--|

|                                        | LOGICALS                                      |  |

| NOT                                    | "Not" byte or word                            |  |

| AND                                    | "And" byte or word                            |  |

| OR                                     | "Inclusive or" byte or word                   |  |

| XOR                                    | "Exclusive or" byte or word                   |  |

| TEST                                   | "Test" byte or word                           |  |

|                                        | SHIFTS                                        |  |

| SHL/SAL                                | Shift logical/arithmetic left<br>byte or word |  |

| SHR                                    | Shift logical right byte or word              |  |

| SAR                                    | Shift arithmetic right byte or<br>word        |  |

| ROTATES                                |                                               |  |

| ROL                                    | Rotate left byte or word                      |  |

| ROR                                    | Rotate right byte or word                     |  |

| RCL                                    | Rotate through carry left byte<br>or word     |  |

| RCR                                    | Rotate through carry right byte<br>or word    |  |

#### Table 5. Arithmetic Interpretation of 8-Bit Numbers

| HEX | BIT PATTERN | UNSIGNED<br>BINARY | SIGNED<br>BINARY | UNPACKED<br>DECIMAL | PACKED<br>DECIMAL |

|-----|-------------|--------------------|------------------|---------------------|-------------------|

| 07  | 00000111    | 7                  | +7               | 7                   | 7                 |

| 89  | 10001001    | 137                | -119             | invalid             | 89                |

| C5  | 11000101    | 197                | -59              | invalid             | invalid           |

The logical instructions include the Boolean operators NOT, AND, inclusive OR, and exclusive OR (XOR). A TEST instruction that sets the flags as a result of a Boolean AND operation, but does not alter either of its operands, is also included.

The bits in bytes and words may be shifted arithmetically or logically. Up to 255 shifts may be performed, according to the value of the count operand coded in the instruction. The count may be specified as an immediate value or as a variable in the

CL register, allowing the shift count to be a variable supplied at execution time. Arithmetic shifts may be used to multiply and divide binary numbers by powers of two. Logical shifts can be used to isolate bits in bytes or words.

Bits in bytes and words can also be rotated. The processor does not discard the bits rotated out of an operand; the bits circles back to the other end of the operand. As in the shift instructions, the number of bits to be rotated is taken from the count operand, which may specify either an immediate value, or the CL register. The carry flag may act as an extension of the operand in two of the rotate instructions, allowing a bit to be isolated in CF and then tested by a JC (jump if carry) or JNC (jump if not carry) instruction.

#### 2.2.1.4 STRING INSTRUCTIONS

Five basic string operations allow strings of bytes or words to be operated on, one element (byte or word) at a time. Strings of up to 64 Kbytes may be manipulated with these instructions. Instructions are available to move, compare and scan for a value, as well as moving string elements to and from the accumulator. Table 7 lists the string instructions. These basic operations may be preceded by a special one-byte prefix that causes the instruction to be repeated by the hardware, allowing long strings to be processed much faster than would be possible with a software loop. The repetitions can be terminated by a variety of conditions, and repeated operations may be interrupted and resumed.

#### **Table 7. String Instructions**

| REP         | Repeat                          |

|-------------|---------------------------------|

| REPE/REPZ   | Repeat while equal/zero         |

| REPNE/REPNZ | Repeat while not equal/not zero |

| MOVS        | Move byte or word string        |

| MOVSB/MOVSW | Move byte or word string        |

| INS         | Input byte or word string       |

| OUTS        | Output byte or word string      |

| CMPS        | Compare byte or word<br>string  |

| SCAS        | Scan byte or word string        |

| LODS        | Load byte or word string        |

| STOS        | Store byte or word string       |

|             |                                 |

The string instructions operate similarly in many respects (refer to Table 8). A string instruction may have a source operand, a destination operand, or both. The hardware assumes that a source string resides in the current data segment. A segment prefix may be used to override this assumption. A destination string must be in the current extra segment. The assembler checks the attributes of the operands to determine if the elements of the strings are bytes or words. However, the assembler does not use the operand names to address strings. Instead, the contents of register SI (source index) are used as an offset to address the current element of the source string. Also, the contents of register DI (destination index) are taken as the offset of the current destination string element. These registers must be initialized to point to the source/destination strings before executing the string instructions. The LDS, LES and LEA instructions are useful in performing this function.

#### Table 8. String Instruction Register and Flag Use

| SI    | Index (offset) for source string                       |

|-------|--------------------------------------------------------|

| DI    | Index (offset) for destination<br>string               |

| CX    | Repetition counter                                     |

| AL/AX | Scan value<br>Destination for LODS<br>Source for STOS  |

| DF    | 0 = auto-increment SI, DI<br>1 = auto-decrement SI, DI |

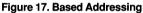

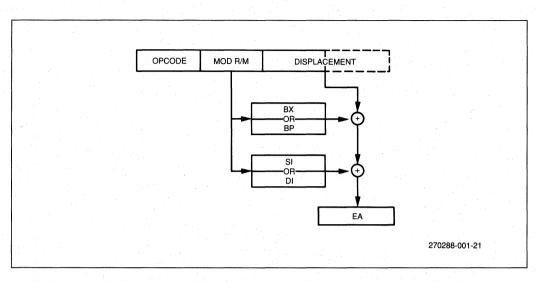

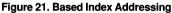

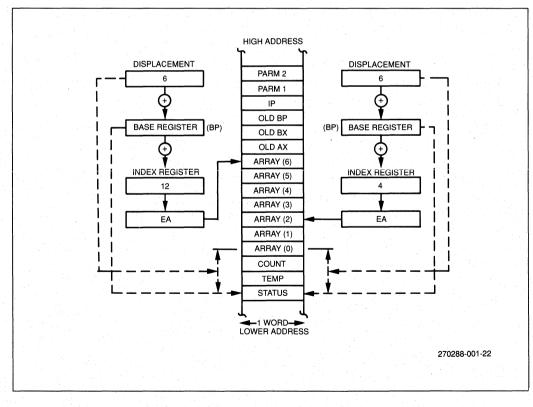

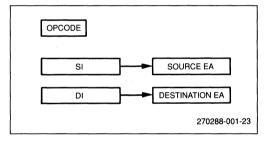

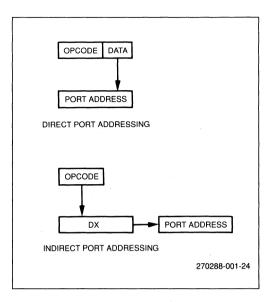

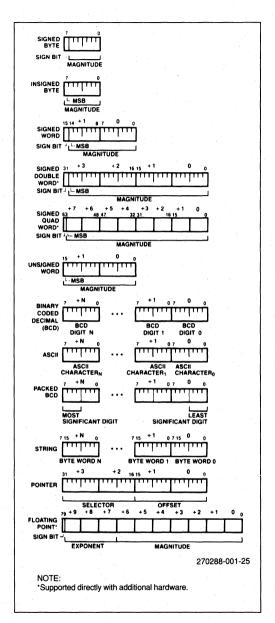

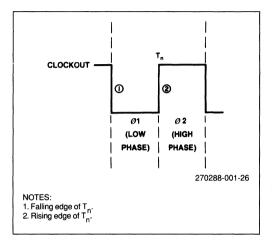

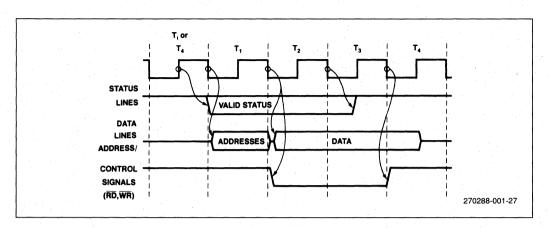

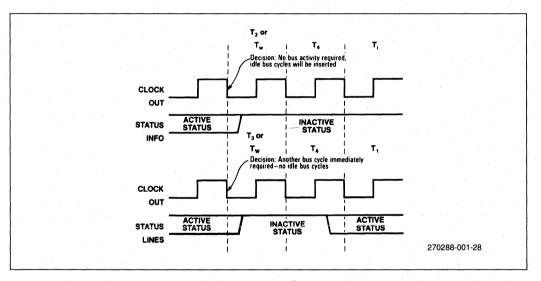

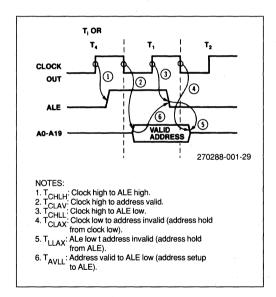

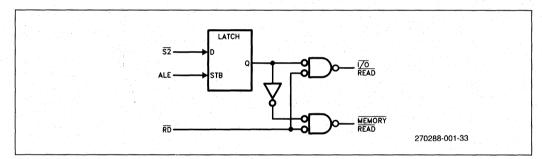

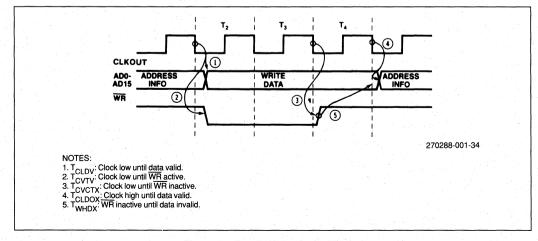

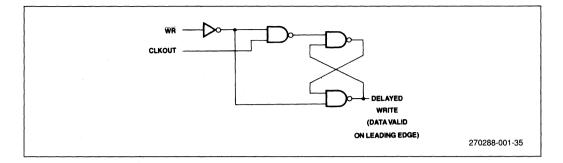

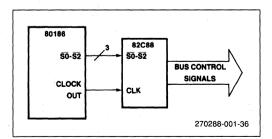

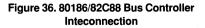

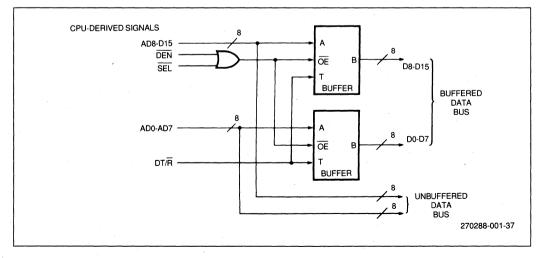

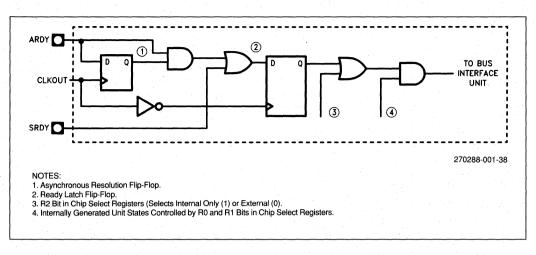

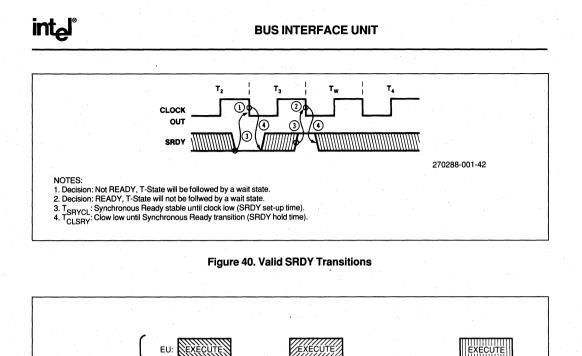

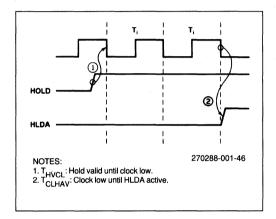

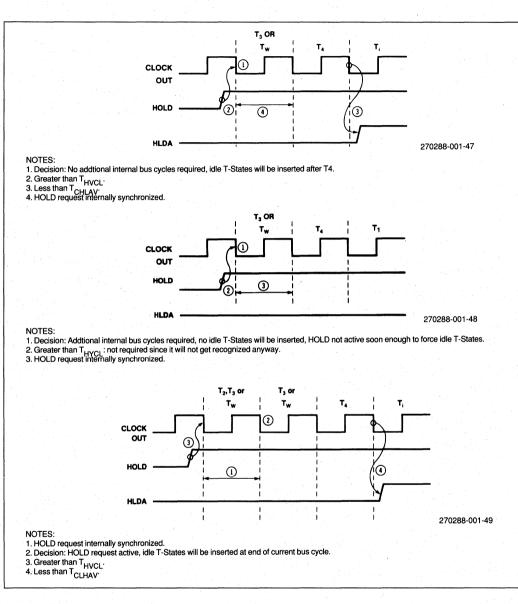

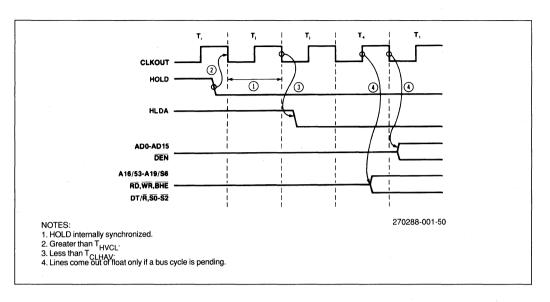

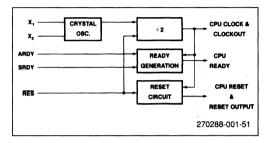

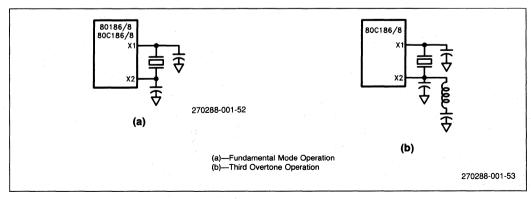

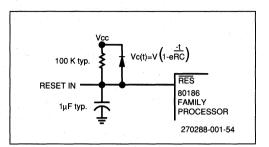

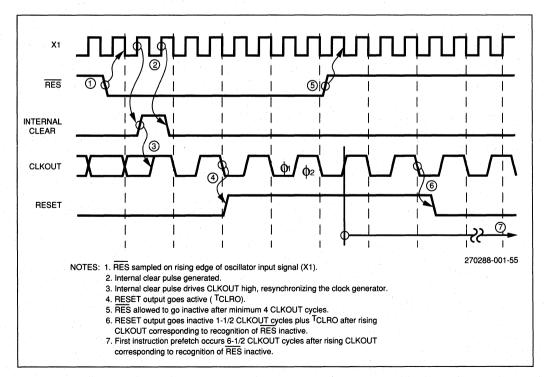

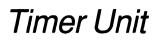

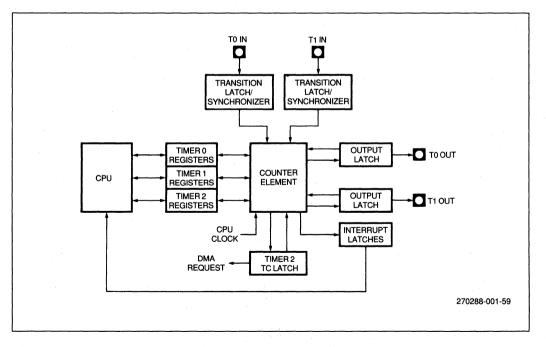

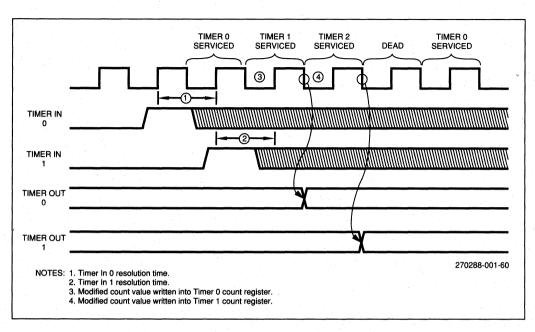

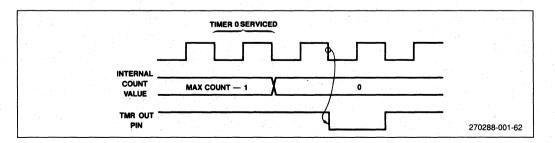

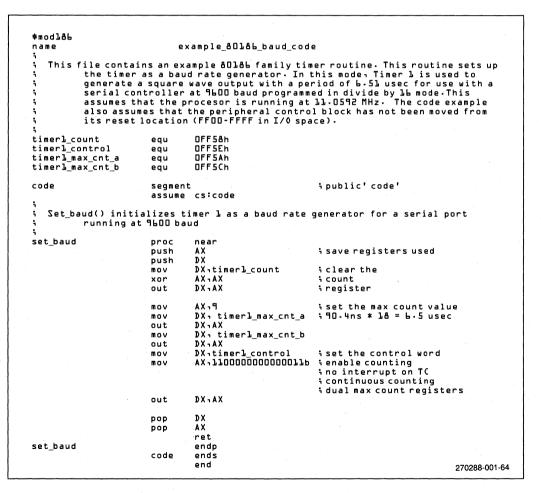

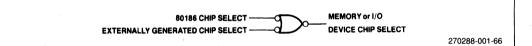

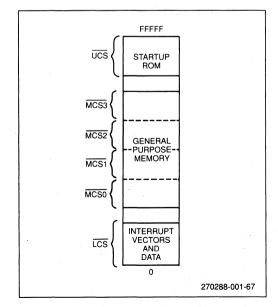

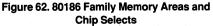

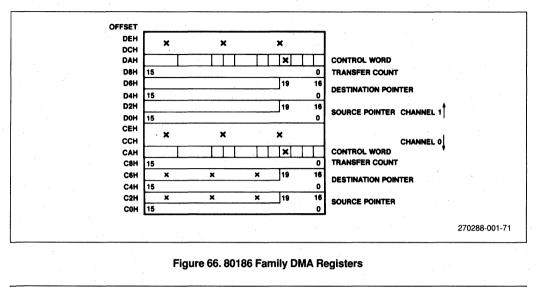

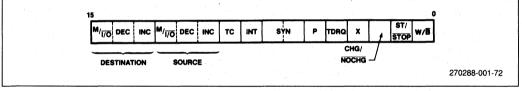

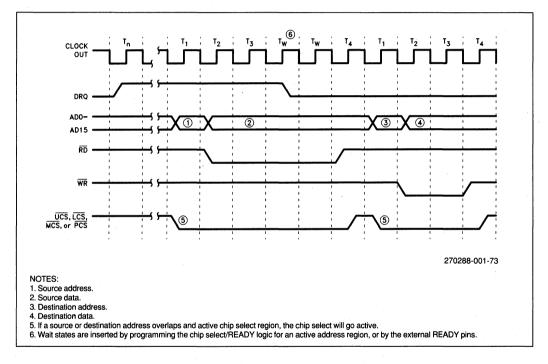

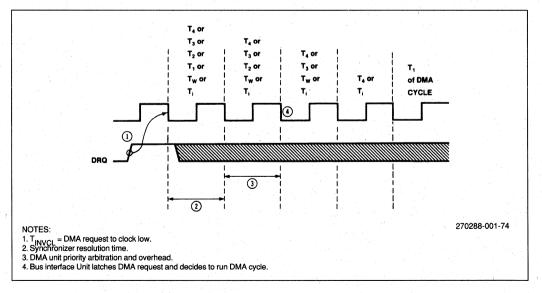

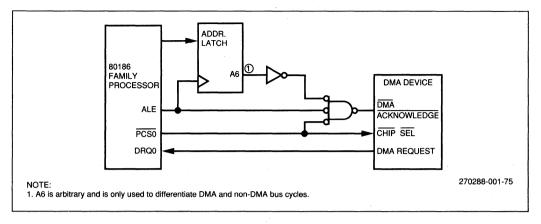

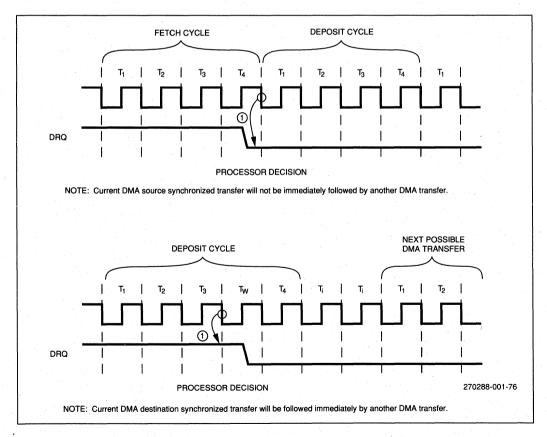

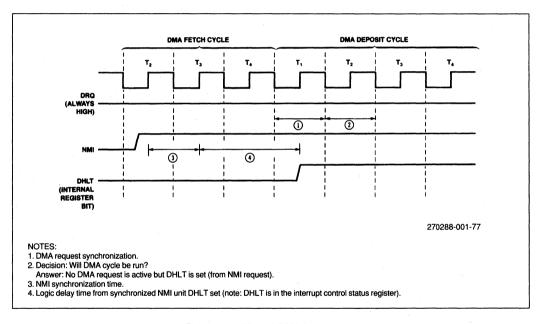

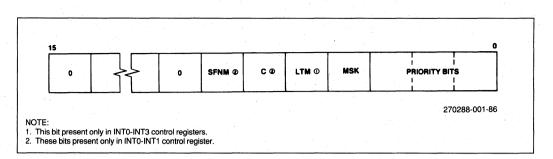

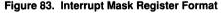

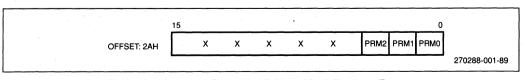

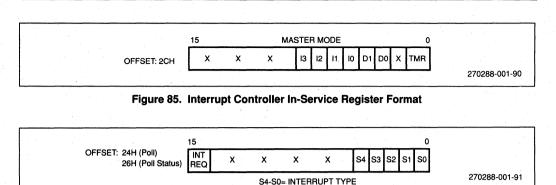

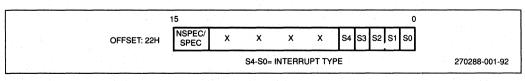

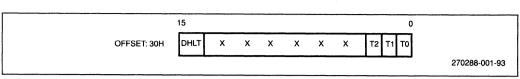

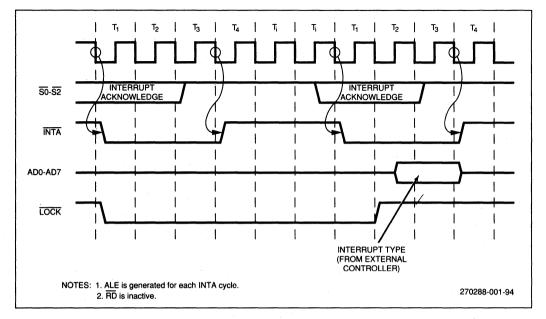

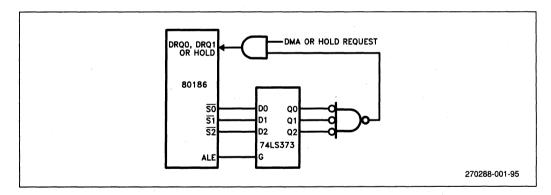

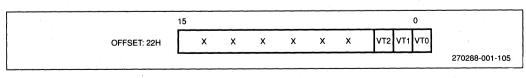

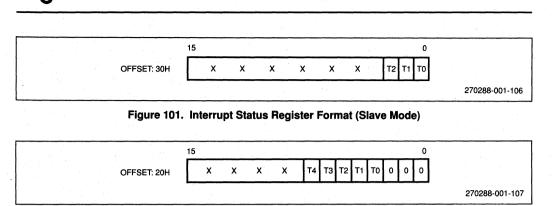

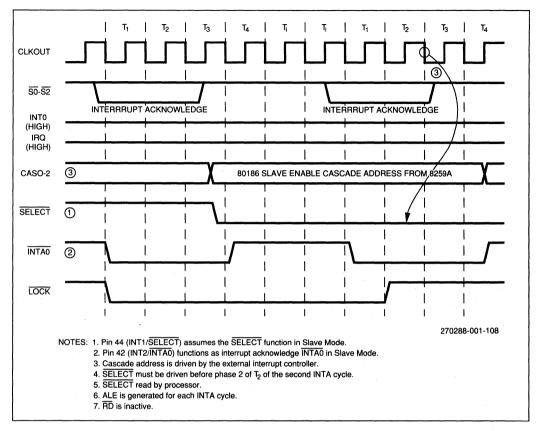

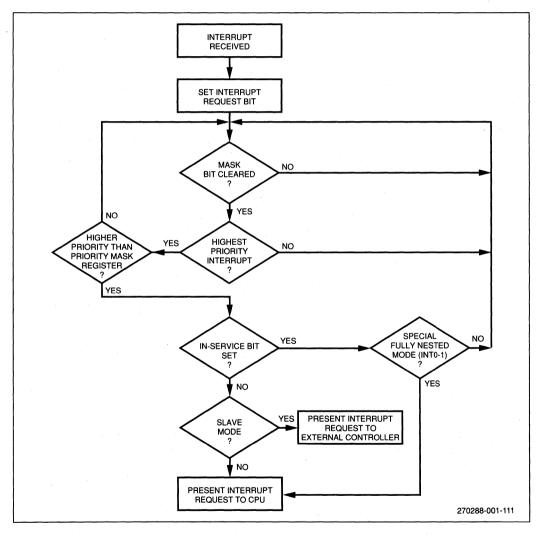

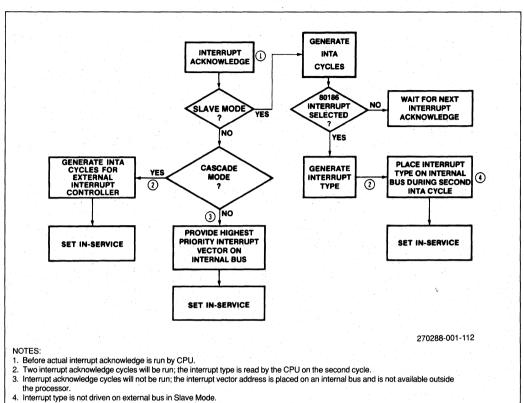

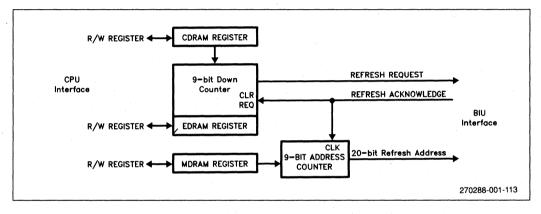

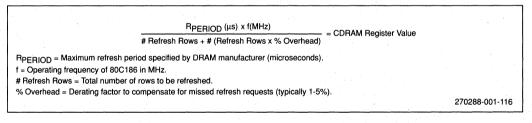

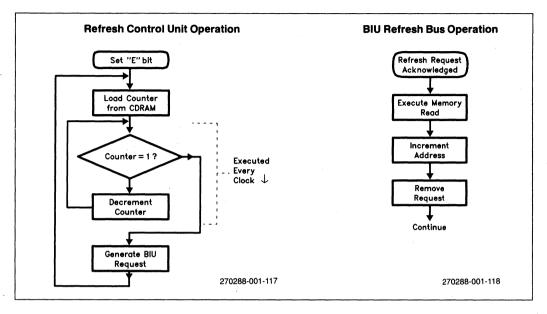

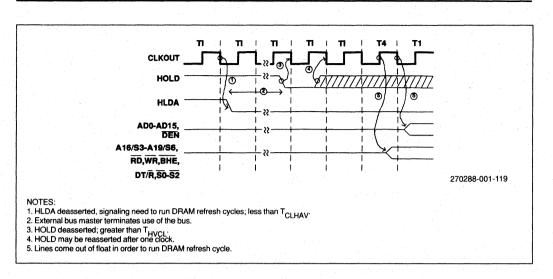

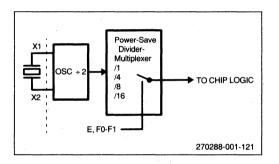

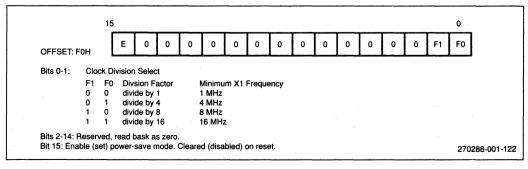

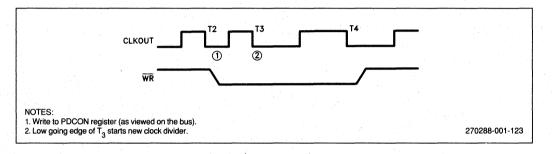

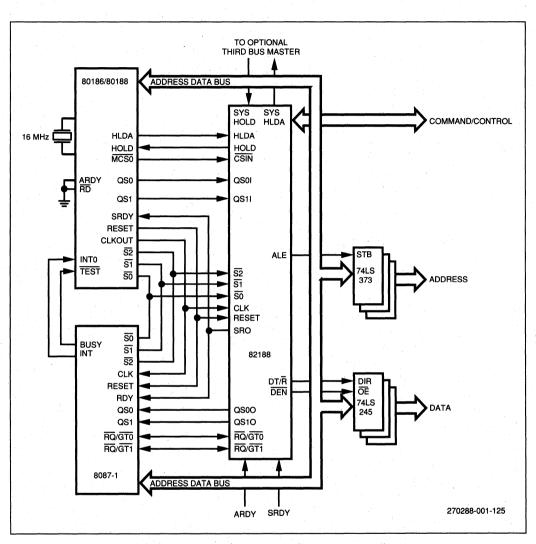

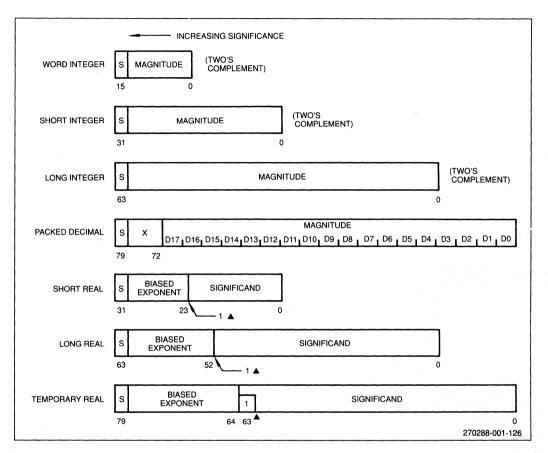

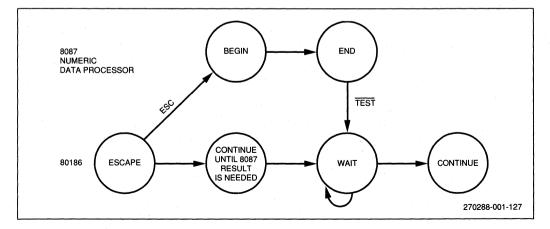

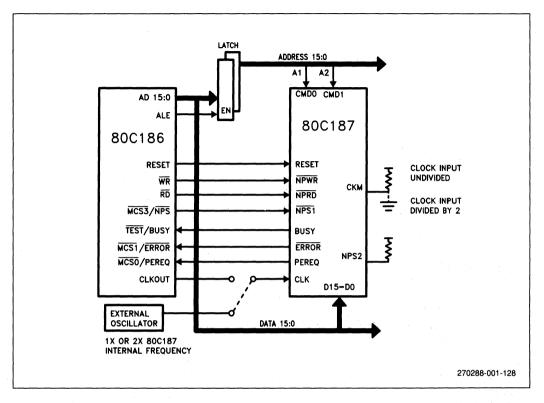

| ZF    | Scan/compare terminator                                |