.

•.

752-0030-01 Rev.1

IBM, AT, XT, PS/2 Enhanced Graphics Adapter, Color Graphics Adapter, are trademarks of International Business Machines. Intel, IAPX 386/486 are trademarks of Intel Corporation. Hercules Graphics is a trademark of Hercules Computer Technology. Copyright 1990, Headland Technology Inc

#### Notice

These data sheets are provided for the general information of the customer. Headland Technology Inc makes no warranty for the use of its products and bears no responsibility for any errors which may appear in this document. Headland Technology Inc retains the right to make changes to these specifications at any time without notice. Headland makes no commitment to update or keep current the information contained in this document.

Headland subjects its products to normal quality control sampling techniques which are intended to provide an assurance of high quality products suitable for the usual commercial applications. Headland does not do testing appropriate to provide 100% product quality assurance and does not assume any liability for consequential or incidental damages arising from any use of its products. If such products are to be used in applications in which personal injury might occur from failure, purchaser must do its own quality assurance testing appropriate to such applications.

> Headland Technology Inc 46221 Landing Parkway Fremont, CA 94538 Tel 415-623-7857 Fax 415-656-0397

## Table of Contents

| Features                          | 1  | Data Rotate                           | 45 |

|-----------------------------------|----|---------------------------------------|----|

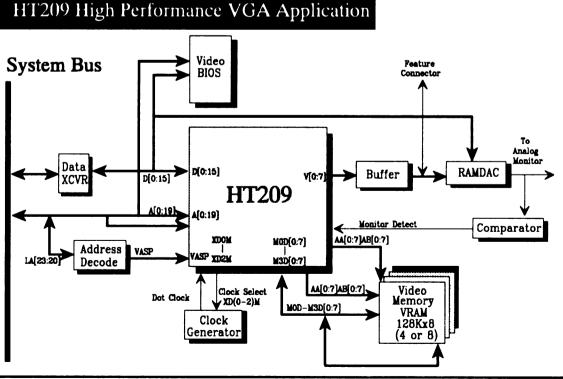

| HT209 Block Diagram               | 1  | Read Map Select                       | 43 |

| General Description               | 2  | Mode                                  | 47 |

| Overview                          | 2  | Miscellaneous                         | 49 |

| Compatibility                     | 3  | Color Don't Care                      | 50 |

| Buses                             | 3  | Bit Mask                              | 50 |

| Performance                       | 3  | Attribute Controller Registers        | 52 |

| Resolution & Color                | 5  | Index                                 | 53 |

| Virtual VGA                       | 5  | Palette                               | 55 |

| 3270 Compatible Text Mode Support | 5  | Mode Control                          | 54 |

| Clock Switches                    | 5  | Summary of Operation                  | 55 |

| Multiple VGA Support              | 5  | Overscan Color                        | 56 |

| • ••                              | 6  | Color Plane Enable                    | 58 |

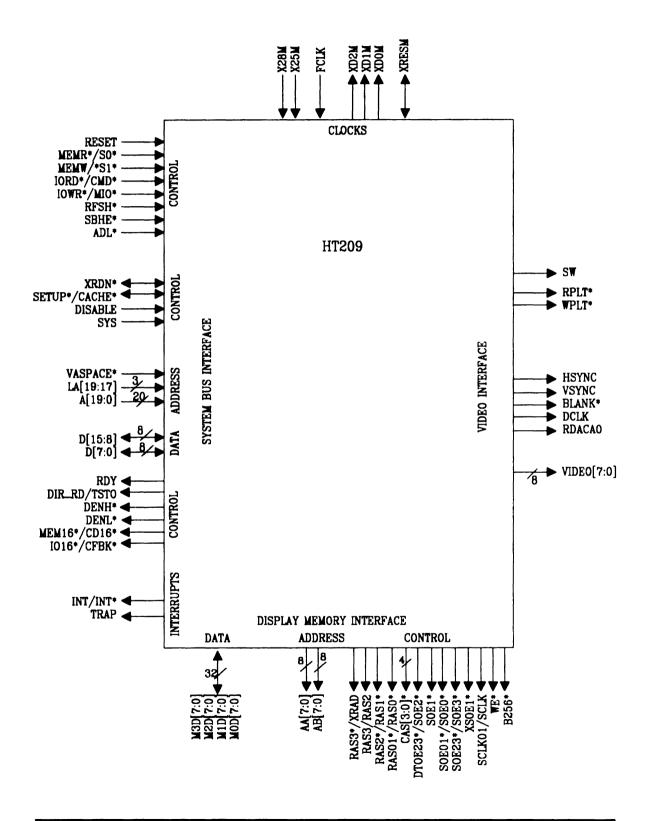

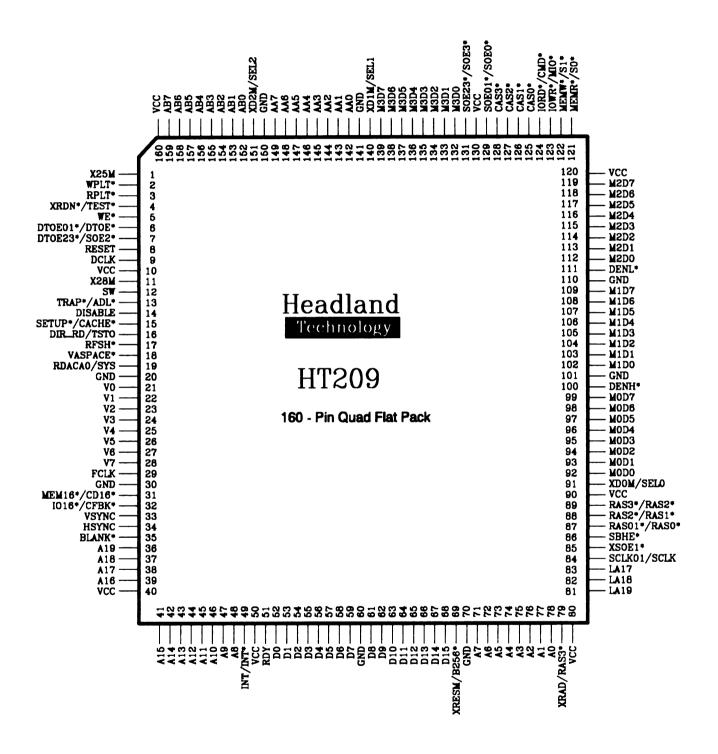

| Internal Block Diagram<br>Pin Out | 7  | Horizontal Panning                    | 57 |

| Pin Names                         | 8  | Color Select                          | 58 |

|                                   |    |                                       |    |

| Pin Descriptions                  | 10 | CRT Controller Register               | 59 |

| I/O Port Summary                  | 18 | CRT Controller Index                  | 60 |

| VGA Register Summary              | 19 | Horizontal Total                      | 60 |

| General Registers                 | 23 | Horizontal Display Enable             | 61 |

| Miscellaneous Output Register     | 24 | Horizontal Blanking Start             | 61 |

| Clock Select Source               | 25 | Horizontal Blanking End               | 61 |

| Feature Control                   | 26 | Horizontal Retrace Start              | 62 |

| Feature Read                      | 26 | Horizontal Retrace End                | 63 |

| Display Status                    | 27 | Vertical Total                        | 64 |

| Input Status Settings             | 27 | Overflow Register                     | 64 |

| Palcue Pixel Mask                 | 28 | Preset Row Scan                       | 64 |

| Palette State                     | 28 | Character Cell Height                 | 65 |

| Color Palette Read Mode           | 29 | Cursor Start Register                 | 66 |

| Color Palette Write Mode          | 29 | Cursor End Register                   | 67 |

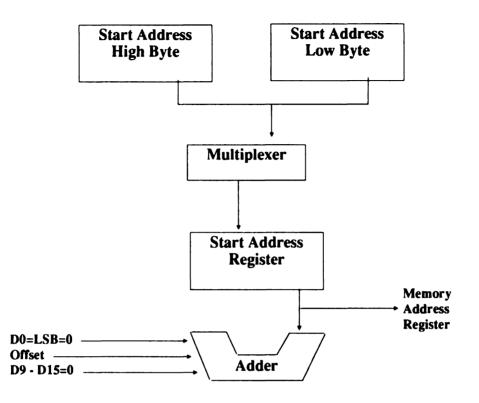

| Color Palette Data                | 30 | Start Address High                    | 67 |

| Alternate Video Subsystem         | 30 | Start Address Low                     | 68 |

| Alternate 16 Bit Set Up           | 31 | Cursor Location High                  | 68 |

| Power on Reset                    | 31 | Cursor Location Low                   | 69 |

| ROM Mapping & Video Subsystem     | 32 | Vertical Retrace Start                | 69 |

| Sequencer Registers               | 34 | Vertical Retrace End                  | 70 |

| Sequencer/Extensions Register     | 35 | Vertical Display Enable               | 71 |

| Reset Register                    | 35 | Offset Register                       | 71 |

| Clocking Mode                     | 36 | Underline Row Scan                    | 72 |

| Plane Mask                        | 37 | Vertical Blanking Start               | 73 |

| Character Map Select              | 39 | Vertical Blanking End                 | 74 |

| Secondary Character Map           | 39 | CRT Mode                              | 74 |

| Primary Character Map             | 39 | Internal Memory Address Counter       | 75 |

| Memory Mode Register              | 40 | Line Compare                          | 76 |

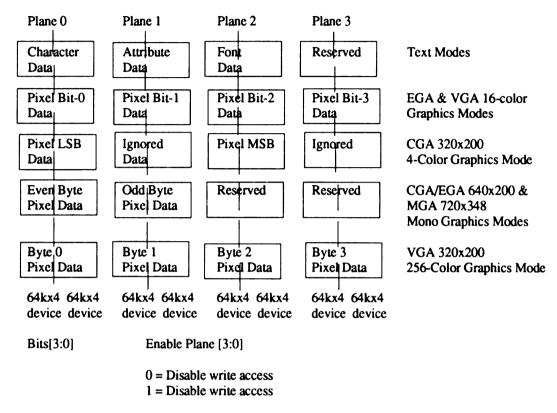

| Chain4 Memory Modes               | 40 | Identification                        | 77 |

| Extensions Control                | 41 | Graphics Controller Data Latch        | 77 |

| Reset Horizontal Character        | 41 | Attribute Controller Index/Data Latch | 78 |

| Graphics Control Registers        | 42 | Clear Vertical Display Enable         | 78 |

| Graphics Controller Index         | 43 | Extension Registers                   | 79 |

| Set/Reset                         | 43 | Chip Revision                         | 81 |

| Enable Set/Reset                  | 44 | Chip Identification                   | 81 |

| Color Compare                     | 44 | Pointer Pattern Address               | 82 |

| Pointer Horizontal Position High     | 84     | Switch Readback Register           | 99  |

|--------------------------------------|--------|------------------------------------|-----|

| Pointer Horizontal Position Low      | 84     | Extended Clock Control             | 99  |

| Pointer Vertical Position High       | 85     | Page Select                        | 101 |

| Pointer Vertical Position Low        | 85     | Extended Foreground Color          | 102 |

| Graphics Controller Memory Latch [0: | :3] 86 | Extended Background Color          | 102 |

| Extended Clock Select Register       | 86     | Compatibility Control              | 103 |

| Misc.Output Register Clock Select    | 86     | Extended Timing Select             | 105 |

| Cursor Attribute Register            | 87     | Foreground/Background Control      | 107 |

| Scratch RAM                          | 87     | 16 Bit Interface Control           | 108 |

| Monochrome Lock                      | 88     | DRAM Performance                   | 111 |

| Miscellaneous Control 2              | 88     | VRAM Performance                   | 111 |

| Horizontal Overflow                  | 89     | RAM Performance - Allowable Timing | 112 |

| Miscellaneous Control 1              | 90     | System Bus Timing                  |     |

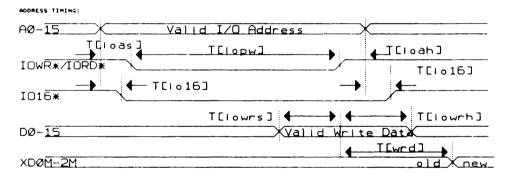

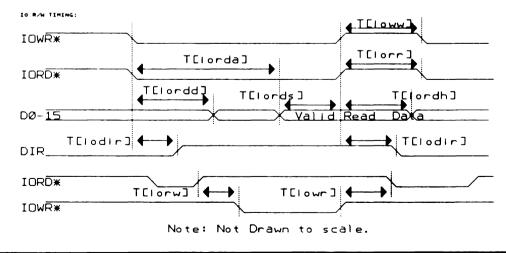

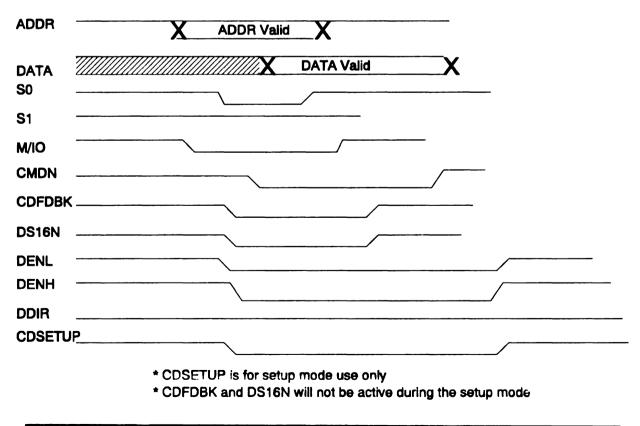

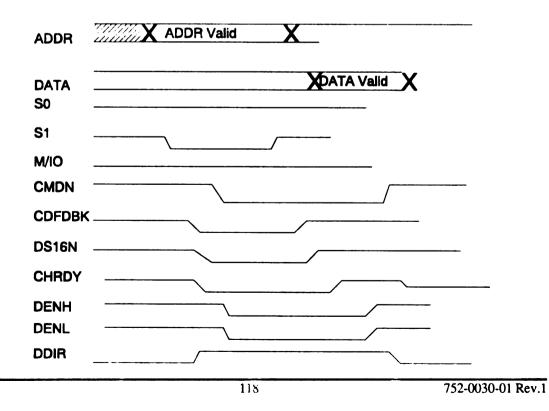

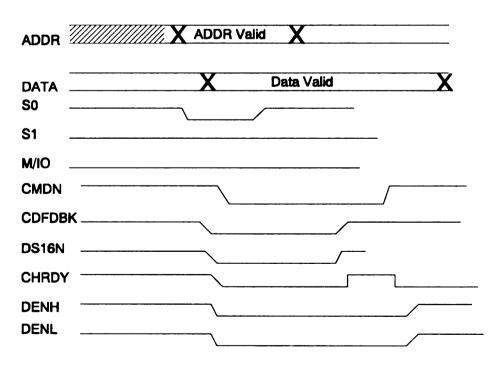

| Interlace Value                      | 91     | I/O Read/Write                     | 113 |

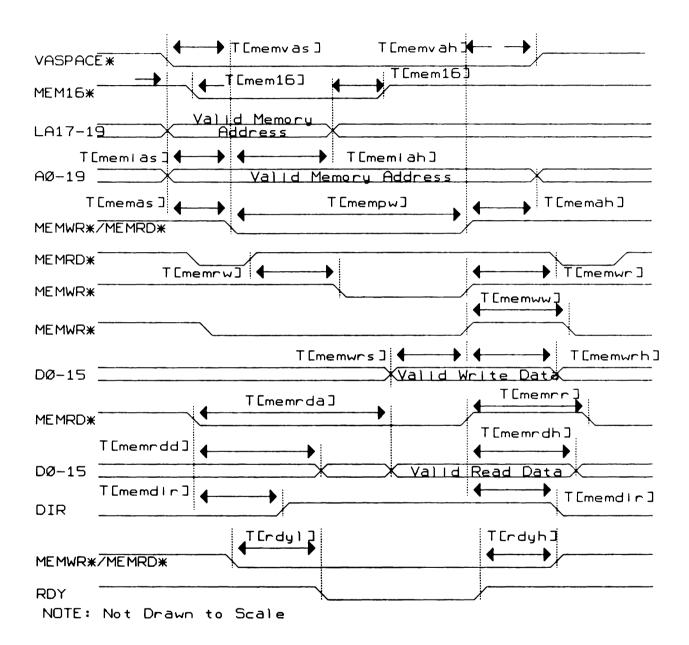

| Trap Control Register                | 92     | Memory Timing                      | 114 |

| Write Protect Control                | 93     | Micro-Channel                      |     |

| Lower Split Bank                     | 94     | I/O Write                          | 116 |

| Upper Split Bank                     | 94     | I/O Read                           | 117 |

| Switch Strobe                        | 95     | MEMRD                              | 118 |

| Overline                             | 95     | MEMWR                              | 119 |

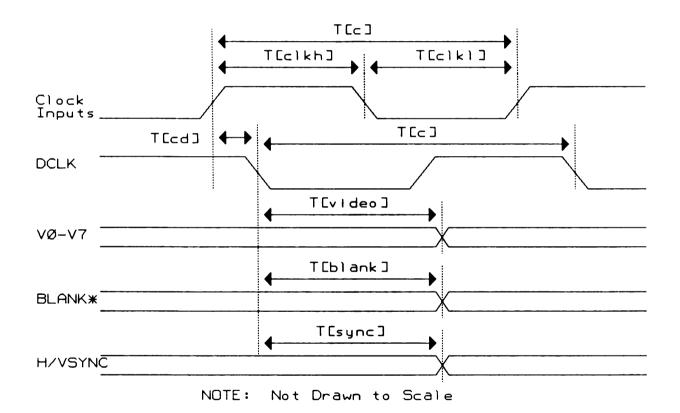

| Foreground Latch Registers [0:3]     | 96     | Clock and Video Timing             | 120 |

| Masked Write Control                 | 96     | DC Characteristics                 | 121 |

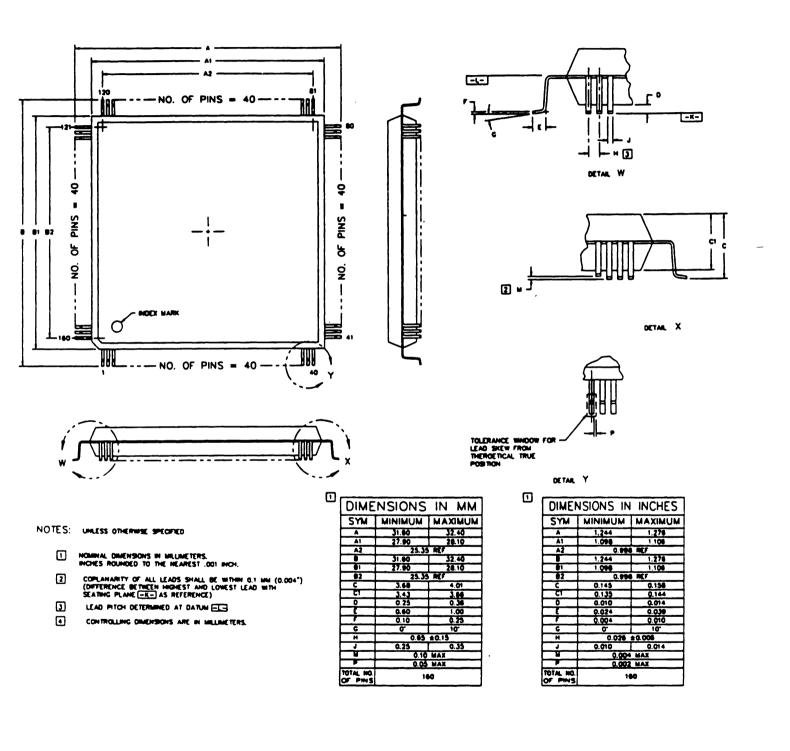

| Masked Write Mask                    | 97     | Package Outline                    | 122 |

| Foreground/Background Pattern        | 97     | Product Order Information          | 123 |

| 1 MByte RAM Bank Select              | 98     | Sales Representatives              | 124 |

|                                      |        |                                    |     |

#### **FEATURES**

- Fully hardware compatible with the IBM VGA

- Hercules and CGA register compatibility; BIOS compatible with the EGA

- Fast host access to 120ns DRAM video memory: every other cycle or better for all standard VGA graphics modes plus any time during horizontal and vertical retrace; paged DRAM mode supports host access every fourth cycle up to 800x600 graphics resolutions

- Built-in support for VRAMs; provides host access every cycle for all standard linear VGA graphics modes, every second cycle up to 800x600, every fourth cycle up to 1024x768; VRAM operation transparent to existing application programs

- Software-selectable 16-bit memory and I/O interface logic eliminates 8-bit bus emulation wait states in 80286 and 80386 computers; true word access in text mode and odd/even graphics modes (including hi-res modes).

- Supports both PC/AT and PS/2 bus interfaces

- Operates with dot clocks of up to 75MHz

- Foreground/background write mode speeds bit-mapped fonts and dithered fills

- Supports 132-column text on all monitors with 120ns DRAMs (Text to 40MHz with 120ns RAMs, 50MHz with 100ns, & 65MHz with 80ns)

- Supports up to 800x600 256-color and 1024x768 256-color non-interlaced resolutions

- Interlace capability for 8514 monitor support

- Hardware graphics pointer

- 3270 compatible text mode (blink, reverse video, under/overline, color, and 8 font selections)

- Supports dual VGA boards in one system (1 color, 1 monochrome)

#### **OVERVIEW**

The HT209 chip is hardware and software compatible with the IBM<sup>TM</sup> VGA while providing improved performance and additional functionality. Designed to operate at dot clock rates up to 75 MHz, the HT209 supports both monochrome and color high resolution graphics and text display modes on displays such as IBM's PS/2<sup>TM</sup> analog monitors and the NEC MultiSync<sup>TM</sup> and Sony MultiScan<sup>TM</sup> monitors. The HT209 is intended to be used with an external palette, such as the IMSG176, which provides blanking and look-up of the 8 bits per pixel generated by the HT209 into a larger color set.

The HT209 implements all registers, data paths, and functionality of the IBM VGA, including features not currently used by IBM.

The HT209 can be programmed to present 16-bit display memory and I/O interfaces to the host, eliminating 8-bit bus emulation wait states in AT<sup>TM</sup>, Micro Channel<sup>TM</sup>, and other high-performance buses. The HT209 is designed to interface to the PC<sup>TM</sup>, AT and Micro Channel buses with minimal external support circuitry.

All memory cycles not used to refresh the display or video memory can be allocated to process host memory requests. During display enable the HT209 can achieve a 1:2 interleave with 120ns DRAMs for all standard VGA graphics modes, including 640x480 modes, and a 1:4 paged mode interleave with 120ns DRAMs in 800x600 60Hz graphics modes.

Once the BIOS has initialized VRAM mode, the HT209 supports VRAMs transparently to all software without any sacrifice of VGA compatibility. No external logic is required to support VRAMs. In VRAM mode, a 1:1 interleave can be achieved for all standard VGA graphics modes, a 1:2 interleave can be achieved for 800x600 graphics modes. A 1:4 interleave can be achieved for 1024x768 graphics modes and 132-column text modes. A 1:4 interleave can also be achieved for all other graphics modes up to 65MHz and text modes up to 40MHz.

Hardware support is provided to display a 32x32 pixel pattern for use as a mouse pointer.

#### COMPATIBILITY

The HT209 is fully compatible with the IBM VGA at the register level. In fact, the HT209 incorporates useful registers not documented by IBM and supports modes which are not used by the current IBM VGA BIOS. These modes and registers are not described by IBM but are none the less powerful and likely to be used in the future.

The HT209 chip provides the same BIOS level compatibility with the EGA, CGA, and MDA as does the IBM VGA. In addition, it provides register level compatibility with CGA and Hercules adapters.

#### **BUSES**

With only minimal support logic, the HT209 operates directly on the Micro Channel, AT, and PC buses. Both 8 bit and 16 bit data transfers are supported for I/O, display memory, and BIOS ROM.

## **RAM CONFIGURATIONS**

The HT209 supports multiple RAM configurations including DRAMs, VRAMs in both 256K bit (64kx4) and 1MB (256kx4) and (128kx8) configurations. If 256K bit chips are used, multiple banks are supported. It also supports 64k x 16 DRAMs.

## PERFORMANCE

The HT209 is designed to be a high performance VGA chip, greatly speeding up all graphics operations in both IBM and enhanced text and graphics modes. This performance improvement is achieved by:

- 1. reducing wait states,

- 2. using masked VRAM writes,

- 3. providing a hardware pointer,

- 4. implementing special data paths to speed up dithered fills and text, and

- 5. supporting a 16 bit ROM interface.

In order to reduce wait states, the HT209 offers timing states that provide 3 1/2 times the display memory bandwidth of the IBM VGA in all standard VGA graphics modes with standard 120ns DRAMs. Even at 800x600 resolutions using 120ns DRAMs, the HT209 provides nearly three times the memory bandwidth of the IBM VGA at 640x480 resolution. At all VGA compatible modes, the CPU gets access every other character clock; at 800x600, a special paged mode allows the CPU access every fourth character clock. By contrast, the IBM VGA allows access every seventh character clock in its 640x480 mode. The HT209 allows CPU access as much as possible during non-display times.

Wait states are reduced even more dramatically when VRAMs are used with the HT209. VRAMs are a dual-ported memory chip, the normal row/column access constitutes one port, and the shift register the other. The ports are linked only in that a row access must be used to load the shift register which is used for refreshing the display. The addressing of the memory is arranged so that a row of the memory chip contains bits that describe adjacent pixels on a scan line. The shift register is loaded at the beginning of the scan line, and then shifted to obtain the values of subsequent pixels. Since the shift register can operate at only about 30MHz, several chips are usually operated in parallel, and a final high-speed video buffer produces values at pixel rates. If necessary, the VRAM shift register can be loaded again during a scan line to accomodate long scan lines. Only infrequently must update accesses be suspended so that a row access can reload the shift register.

HT209 VRAM allows up to seven times the memory bandwidth of the IBM VGA. At 800x600 resolutions the band width is more than five times greater than the IBM 640x480 mode. In fact, at all modes up to 720x540, including all VGA compatible modes, the CPU gets an access every character clock. At 800x600, the CPU gets an access every other character clock and at 1024x768 the CPU gets an access every fourth character clock.

Greater memory bandwidth does not by itself greatly improve display performance. True high

performance video requires that the improved memory bandwidth be available in all modes, not just the enhanced ones so that all software will run faster. In addition the display memory bandwidth must be available to the CPU. The HT209 accomplishes that.

Most video adapters are strictly 8 bit devices and consequently have a minimum of three wait states inserted during every CPU access on AT compatible buses. The HT209 supports independently selectable 16 bit interfaces to the system memory and the I/O buses, eliminating wait states when emulating the 8 bit bus. The benefit of the 16 bit bus is clear since pixels are controlled by manipulating display memory.

What is not so obvious is that the 16 bit I/O interface will also produce comparable improvement in all graphics modes since the Bit Mask, Sct/Reset, Map Mask, and other indexed VGA registers are written to as often as once per pixel when drawing graphics.

The HT209 adds another feature to reduce wait states to virtually zero on CPU writes: the "FastWrite<sup>TM</sup>" feature. When the CPU writes to display memory, the HT209 immediately lets the CPU continue processing rather than forcing a wait state until the write operation is completed. Therefore, the write operation continues in the background while the CPU continues processing independently. The background processing of the write allows the CPU to write as fast as it does to normal system RAM. This is a vast improvement over other display adapters which is often 14 times slower than system RAM.

This FastWrite feature is especially suitable with the 16 bit memory interface and VRAMs. Together, these features allow display memory to approach system RAM in overall performance. This is about an order of magnitude of speed improvement over the IBM display adapter in most cases and no less than 2 to 3 times in all cases. The HT209 supports masked writes to VRAMs (write per bit writes), which allow selected bits within a display memory byte to be modified without first reading the byte. This feature cuts in half the number of display memory accesses required when drawing lines, clipping on fills and bitblts, and drawing transparent text. Additionally, it frees up the Bit Mask register for use in combining foreground and background patterns, thereby speeding up color expansion of binary data, especially opaque text.

The HT209's 32x32 hardware pointer (which works in all modes, including text modes) improves both the appearance and performance of environments which use pointers, such as Microsoft Windows<sup>TM</sup>. The improvement in appearance occurs because the hardware pointer eliminates the need to erase the pointer whenever the bit-map is drawn into, thereby eliminating flicker. The improvement in performance occurs because the hardware pointer eliminates the considerable time required to save and restore the area of bit-map covered by the pointer and to draw the pointer.

In order to boost filling and text drawing performance, especially in Windows<sup>TM</sup>, the HT209 provides all data paths required to draw independently-controllable foreground and background colors or dither patterns with a single CPU write; the masked write feature makes it possible to do all this with a single write to VRAMs even when the operation is not byte-aligned. By contrast, two to twelve display memory accesses are required to draw dithered text on a standard VGA. The HT209 also provides a special data path for expanding two-color font data into 16-color text on a 16-color background with a single CPU write.

The net effect of these performance enhancements is a chip, the HT209, around which an adapter can be built which is two to ten times faster than the IBM VGA, running off-the-shelf software. Specially optimized software, such as Windows<sup>TM</sup> drivers, achieves even higher performance.

### **RESOLUTION & COLOR**

The HT209 supports much higher resolution, with more simultaneous colors, than does the IBM VGA. In addition to all standard IBM VGA modes, the HT209 supports 800x600 256-color modes with 120ns DRAMs. VRAMs support 1024x768 256-color and 720x540 256-color modes as well as all the above-mentioned modes.

As regards text modes, in addition to all IBM VGA text modes the HT209 supports 132column text on PS/2-type fixed-frequency monitors with 120ns DRAMs, and supports 132column text on PS/2 monitors as well with VRAMs.

#### VIRTUAL VGA

The HT209 provides all internal controls and external pins required to support up to four virtual VGA sessions in 1MB of memory. (This requires 256K DRAMs/VRAMs.) This feature dramatically increases video speed when switching tasks for multitasking environments such as 80386 virtual 8086 operating systems.

## **3270-COMPATIBLE TEXT MODE SUPPORT**

In 3270 emulations, the VGA attribute is used as the extended attribute. The extended attribute byte contains bits for controlling character blink, reverse video, underline, overline (overstrike), color, and 8 font selections. The first byte contains the same character code and attribute as normal text mode, and the second byte is used as an extended attribute byte.

#### **CLOCK SWITCHES**

The HT209 provides support for up to 11 external clocks. Support is provided for driving an external 8-frequency clock synthesizer.

## **MULTIPLE VGA SUPPORT**

The VGA normally responds to I/O port addresses 3Bx-3Cx in monochrome mode and 3Cx-3Dx in color mode. The HT209 can be set up to disable response to 3Cx for compatibility with older CGA and MGA graphics standards. This ability is also useful to allow two HT209-based boards to be used in the same system, one configured to monochrome mode with 3Cx I/O port addressing disabled and one configured to normal VGA color mode.

#### **Pinout**

| Pin #              | Pin Name  | Туре | Alt.             | Туре | Function                                                                   |

|--------------------|-----------|------|------------------|------|----------------------------------------------------------------------------|

|                    |           |      |                  |      | Processor                                                                  |

| 71-78              | A[7:0]    | 1    |                  |      | System Bus Address Bits                                                    |

| 41-48              | A[15:8]   |      |                  |      | System Bus Address Bits                                                    |

| 36-39              | A[19:16]  | 1    |                  |      | System Bus Address Bits                                                    |

| 100                | DENH*     | 0    |                  |      | Data Bus Enable High                                                       |

| 111                | DENL*     | 0    |                  |      | Data Bus Enable Low                                                        |

| 16                 | DIR_RD    | 0    | TSTO             | 0    | Direction Control for Data Bus Tranceivers (high=read from chip)           |

| 14                 | DISABLE   | Ι    |                  |      | Chip disable (typically connected to I/O port 46E8 bit-3)                  |

| 49                 | INT       | TS   | INT <sup>•</sup> | TS   | Interrupt Request (8mA) (PC=active high, PS/2=active low)                  |

| 32                 | I/O16*    | 0    | CFBK*            | 0    | Interrupt request 8mA                                                      |

| 123                | IOWR*     | 1    | MI/O*            | I    | PC/AT: I/O Write Strobe PS/2:MI/O*                                         |

| 124                | IORD*     | -    | CMD*             | 1    | PC/AT:I/O Read Strobe PS/2:CMD*                                            |

| 81-83              | LA[19:17] |      |                  |      | System Bus Unlatched Address Bit                                           |

| 31                 | MEM16*    | 0    | CD16*            | 0    | PC/AT: 16-bit memory select PS/2:CDDS16*(16-bit memory I/O select)         |

| 121                | MEMR*     | -    | S0*              | 1    | PC/AT:Memory Read Strobe PS/2:S0                                           |

| 122                | MEMW*     | 1    | S1*              | -    | PC/AT:Memory Write Strobe PS/2:S1                                          |

| 51                 | RDY       | TS   |                  |      | Data Ready (also can be interpreted as active low WAIT*) (8mA)             |

| 8                  | RESET     | 1    |                  |      | System Reset (active high)                                                 |

| 17                 | RFSH*     | -    |                  |      | Memory Refresh                                                             |

| 3                  | RPLT      | 0    |                  |      | Read Strobe for External Color Palette                                     |

| 86                 | SBHE*     | 1    |                  |      | High Byte Enable                                                           |

| 15                 | SETUP*    | 1    | CACHE*           |      | Setup Mode (L=only respond to I/O port 102, H=don't respond to 102)        |

| 13                 | TRAP*     | 0    | ADL*             | TS   | PC/AT:I/O Trap Detected (to external NMI cache) PS/2:ADL* No Connect       |

| 18                 | VASPACE*  | 1    |                  |      | Valid Address Space (drive low for A[23:20]=0)PS/2:MAD also required       |

| 2                  | WPLT*     | 0    |                  |      | Write Strobe for External Color Palette                                    |

| 4                  | XRDN*     | 1/0  | TSTO             | 1    | Enable for External Devices (low at reset puts chip into test mode) or ROM |

|                    |           |      |                  |      | Chip Select (when enabled)                                                 |

|                    |           |      |                  |      | Processor Data                                                             |

|                    | D[15:8]   | I/O  |                  |      | Bi-directional Data to/from System Bus (MSB)                               |

| 5 <del>9</del> -52 | D[7:0]    | 1/0  |                  |      | Bi-directional Data to/from System Bus (LSB)                               |

|                    |           |      |                  |      | Display Memory Data                                                        |

| <del>99</del> -92  | MOD[7:0]  | 1/0  |                  |      | Bi-directional Data Bus to Display Memory Plane 0                          |

| 109-102            | M1D[7:0]  | I/O  |                  |      | Bi-directional Data Bus to Display Memory Plane 1                          |

|                    | M2D[7:0]  | 1/0  |                  |      | Bi-directional Data Bus to Display Memory Plane 2                          |

| 139-132            | M3D[7:0]  | 1/0  |                  |      | Bi-directional Data Bus to Display Memory Plane 3                          |

| Pin #                | Pin Name      | Туре    | Alt.   | Туре | Function                                                              |  |  |  |  |  |

|----------------------|---------------|---------|--------|------|-----------------------------------------------------------------------|--|--|--|--|--|

|                      |               |         |        |      | Display Memory Address                                                |  |  |  |  |  |

| 149-142              | AA[7:0]       | 0       |        |      | Address Bus to Display Memory Planes 0 and 1                          |  |  |  |  |  |

| 15 <del>9</del> -152 | AB[7:0]       | 0       |        |      | Address Bus to Display Memory Planes 2 and 3                          |  |  |  |  |  |

| 128-125              | CAS*[3:0]     | 0       |        |      | Display Memory Column Address Strobe Planes 3-0                       |  |  |  |  |  |

| 6                    | DTOE01*       | 0       | DTOE*  | 0    | Display Memory Data Transfer/Output Enable Planes 0-1 (banked DTOE)   |  |  |  |  |  |

| 7                    | DTOE23*       | 0       | SOE2*  | 0    | Display Memory Data Transfer/Output Enable Planes 2-3 (banked SOE2)   |  |  |  |  |  |

| 87                   | RAS01*        | 0       | RAS0*  | 0    | Display Memory Row Address Strobe Planes 0 and 1 (banked mode Ras0)   |  |  |  |  |  |

| 88                   | RAS2*         | 0       | RAS1*  | 0    | Display Memory Row Address Strobe Plane 2 (banked mode Ras1)          |  |  |  |  |  |

| 89                   | RAS3*         | 0       | RAS2*  | 0    | Display Memory Row Address Strobe Plane 3 (banked mode Ras2)          |  |  |  |  |  |

| 129                  | SOE01*        | 0       | SOE0*  | 0    | Display Memory Serial Output Enable Planes 0 and 1 (banked mode SOE0) |  |  |  |  |  |

| 131                  | SOE23*        | 0       | SOE1*  | 0    | Serial Output Enable to Upper 512K of memory (128k x 8 VRAMs)         |  |  |  |  |  |

| 79                   | XRAD          | 0       | RAS3*  | 0    | 1M RAM mode: A8 all planes; Banked mode: RAS 3                        |  |  |  |  |  |

|                      |               |         |        |      | Display Memory Control                                                |  |  |  |  |  |

| 84                   | SCLK01        | 0       | SCLK   | 0    | Display Memory Serial Clock Planes 0 and 1 (banked SCLK)              |  |  |  |  |  |

| 85                   | SOE23*        | 0       |        | 0    | Serial Output Enable to Upper 512k of Memory (128kx8 VRAMs).          |  |  |  |  |  |

| 5                    | WE*           | 0       |        |      | Display Memory Write Enable (8mA)                                     |  |  |  |  |  |

| 69                   | XRESM         | 1       | B256*/ | TS   | Clock Input 3 if Enabled; If not L=Banked Memory Mode or URAS*        |  |  |  |  |  |

|                      |               |         | URAS*  |      | (RAS to upper 512k if using 128kx8's)                                 |  |  |  |  |  |

|                      |               |         |        |      | Clocks                                                                |  |  |  |  |  |

| 19                   | RDACA0        | 0       | SYS    | -    | High during reset = PC/AT, L=PS/2) (Internal 100k PU)                 |  |  |  |  |  |

| 9                    | DCLK          | 0       |        |      | Video Dot Clock to External Color Palette                             |  |  |  |  |  |

| 29                   | FCLK          |         |        |      | Feature Connector Dot Clock (clock input 2 and 6)                     |  |  |  |  |  |

| 12                   | SW            |         |        |      | Switch Input (Feature Read 4) (typically from RGB Output Comparator)  |  |  |  |  |  |

| 1                    | X25M          |         |        |      | Clock Input 0 - 25.175MHz                                             |  |  |  |  |  |

| 11                   | X28M          |         |        |      | Clock Input 1 - 28.322MHz                                             |  |  |  |  |  |

| 91                   | XDOM          |         | SEL0   | TS   | Clock Input 4 - 50.350MHz (clock/switch select output 0)              |  |  |  |  |  |

| 140                  | XD1M          |         | SEL1   | TS   | Clock Input 5 - 65.000MHz (clock/switch select output 1)              |  |  |  |  |  |

| 151                  | XD2M          |         | SEL2   | TS   | Clock Input 7 - 40.000MHz (clock/switch select output 2)              |  |  |  |  |  |

|                      |               |         |        |      | Video Interface                                                       |  |  |  |  |  |

| 35                   | BLANK*        | 0       |        |      | Video Blanking to External Color Palette                              |  |  |  |  |  |

| 34                   | HSYNC         | 0       |        |      | Horizontal Sync                                                       |  |  |  |  |  |

| 28-21                | V[7:0]        | 0       |        |      | Video Output to External Color Palette                                |  |  |  |  |  |

| 33                   | VSYNC         | 0       |        |      | Vertical Sync                                                         |  |  |  |  |  |

| 10,40,50             | ,80,90,120,1  | 30,160  |        |      | VCC                                                                   |  |  |  |  |  |

| 20,30,60             | ),70,101,110, | 141,150 | )      |      | GND                                                                   |  |  |  |  |  |

| Pin<br>Symbol | Pin<br>Number          | Pin<br>Type | Pull<br>Up/Dn* | Description                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------|------------------------|-------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[0:19]       | 78-71, 48-41,<br>39-36 | Ι           |                | Address Bus: System address bus for memory and I/O opera-<br>tions. Address latches are provided in the HT209 chip for PS/2<br>mode, so unlatched addresses must be provided (LA19 may be<br>connected to A19, LA18 to A18, and LA17 to A17). In PC/AT<br>mode, A[0:19] are connected to the latched address lines<br>provided by the PC/AT bios and LA[17:19] are connected to<br>unlatched address lines provided by the PC/AT bus. |

| AA[0:7]       | 142-149                | 0           |                | Address bus A:Display Memory Address Bus A - Address bus for planes 0 and 1                                                                                                                                                                                                                                                                                                                                                           |

| AB[0:7]       | 152-159                | 0           |                | Address bus B:Display Memory Address Bus B - Address bus for planes 2 and 3                                                                                                                                                                                                                                                                                                                                                           |

| BLANK*        | 35                     | 0           |                | Blanking Video - a low on this pin indicates that video data is<br>blanked (the screen is black). This pin is normally connected<br>to the blanking input of the external color palette.                                                                                                                                                                                                                                              |

| CAS*[0:3]     | 125-128                | Ο           |                | Column Address Strobe[0:3]:In all modes, these pins are<br>Column Address Strobes. The falling edge of CAS latches<br>column addresses from the AA and AB address buses into the<br>RAM chips.                                                                                                                                                                                                                                        |

| D[0:15]       | 52-59,<br>61-68        | I/O         |                | Data bus: From CPU[0:7] LSB, [8:15] MSB, Bidirectional bus for I/O and memory data.                                                                                                                                                                                                                                                                                                                                                   |

| DCLK          | 9                      | 0           |                | Dot CLocK: this signal is used to shift video data. All video data timing is referenced to this signal. This pin is normally connected to the clock input of the external color palette.                                                                                                                                                                                                                                              |

| DENH*         | 100                    | 0           |                | Data ENable High: Data bus transceiver enable for D[15:8]. Also used as output enable high for BIOS ROMs.                                                                                                                                                                                                                                                                                                                             |

| DENL*         | 111                    | 0           |                | Data ENable Low - Data bus transceiver enable for D[7:0]. Also used as output enable low for BIOS ROMs.                                                                                                                                                                                                                                                                                                                               |

## **Pin Descriptions**

| Pin<br>Symbol     | Pin<br>Number | Pin<br>Type | Pull<br>Up/Dn* | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------|---------------|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIR_RD/TST0       | 16            | 0           |                | DIRection: This pin controls the direction of data transfers on<br>the data bus. It is driven high when an I/O or memory read<br>cycle is being performed by the system processor. This signal<br>may also be used for slot-8 control in PC/XT systems if<br>connected to an inverting open collector driver whose output<br>drives PC bus pin AA7. In chip test mode (see XRDN*/TEST<br>pin), this pin is the test output.                                                                                                                                                                                                                |

| DISABLE           | 14            | I           |                | DISABLE: this pin may be driven high to disable all memory<br>and I/O operations to the chip. In a display adapter configura-<br>tion this pin is normally driven from register bit-3 of I/O port<br>46E8 (inverted). This emulates the function of PS/2 Model 50<br>and 60 I/O port 3C3 bit 0 (Video Subsystem Enable).                                                                                                                                                                                                                                                                                                                   |

| DTOE01*/<br>DTOE* | 6             | 0           |                | Data Transfer Output Enable for planes 0 and 1 in non-banked<br>mode. Data Transfer Output Enable for all planes in banked<br>mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DTOE23*/<br>SOE2* | 7             | 0           |                | Data Transfer Output Enable for planes 2 & 3 in non-banked mode. Serial Output Enable for plane 2 in banked mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| FCLK              | 29            | I           |                | Feature CLocK: (Clock input 2 and 6) - Connect to feature connector clock input pin if available, otherwise connect to ground or other clock source as desired.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| HSYNC             | 34            | 0           |                | Horizontal SYNC: The polarity of this signal is controlled by bit-6 of the Miscellaneous output register (I/O address 3C2h).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| INT/INT*          | 49            | TS          |                | INTerrupt: CPU interrupt - in a PC/AT this pin is active high;<br>in a PS/2 it is active low. The interrupt will occur at the start<br>of the vertical retrace interval if enabled by clearing Vertical<br>Retrace End Register (CR11) bit-5 and setting bit-4. This<br>signal will then stay active until reset by clearing CR11 bit-4.<br>(Bit-4 must then be set to enable the next vertical retrace<br>interrupt). This pin is either driven low or not driven at all:<br>PC/AT: interrupt disabled - output floats<br>interrupt enabled & interrupting - output floats<br>interrupt enabled & not interrupting - output<br>driven low |

| Pin<br>Symbol           | Pin<br>Number | Pin<br>Type  | Pull<br>Up/Dn*              | Description                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------|---------------|--------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         |               |              |                             | PS/2 interrupt disabled - output floats<br>interrupt enabled & interrupting - output<br>driven low<br>interrupt enabled & not interrupting - output                                                                                                                                                                                                                                             |

|                         |               |              |                             | floats<br>This pin has 8 mA source and sink capability and can be<br>connected directly to the system bus.                                                                                                                                                                                                                                                                                      |

| IO16*/CFBK*             | 32            | 0            |                             | Input/Output 16-bit select: In a PC/AT this pin is asserted to indicate that the current I/O operation is transferring 16 bits. Card Select FeedBacK: In a PS/2 this pin is connected to CDSFDBK* and is asserted by the chip for any I/O or memory access to the graphics card. The PC/AT bus requires 24mA drive on its IOCS16* signal, so this pin is used to enable an external bus driver. |

| IORD*/CMD*              | 124           | I            |                             | I/O ReaD: In a PC/AT this pin indicates that an I/O read operation is in progress. In a PS/2 this pin is the CoMmanD strobe input.                                                                                                                                                                                                                                                              |

| IOWR*/MIO*              | 123           | I            |                             | I/O WRite: In a PC/AT this pin indicates that an I/O write operation is in progress. In a PS/2 this pin is the Memory I/O select input.                                                                                                                                                                                                                                                         |

| LA[17:19]               | 83-81         | I            |                             | UnLatched Address bus for memory and I/O operations (PC/AT)                                                                                                                                                                                                                                                                                                                                     |

| M0D[0:7]                | 92-99         | I/O          | *                           | Memory Display data bus 0: Bidirectional data for plane 0                                                                                                                                                                                                                                                                                                                                       |

|                         | a list of PU' | s on the d   | lisplay mem                 | ory data lines to ensure that the chip is reset properly to AT                                                                                                                                                                                                                                                                                                                                  |

| mode.<br>RDB7=BKPG      | С             | enal         |                             | ress decode in ROM decode space (if internal ROM decode is<br>nit ROM decode to 0xC0000 - 0xC5FFF and 0xC6800-0xC7FFF<br>(6000)                                                                                                                                                                                                                                                                 |

| RDB6=EIROM              |               |              |                             | ROM decode                                                                                                                                                                                                                                                                                                                                                                                      |

| RDB[5,4]=ME             | MCFG[1,0]     |              | mory config<br>35 RDB4      | uration bits, as follows:<br>Memory Configuration                                                                                                                                                                                                                                                                                                                                               |

|                         |               | 0            | 0                           | 64K x 4                                                                                                                                                                                                                                                                                                                                                                                         |

|                         |               | 0            | 1                           | 128K x 8                                                                                                                                                                                                                                                                                                                                                                                        |

|                         |               | 1            | 0                           | 256K X 4                                                                                                                                                                                                                                                                                                                                                                                        |

| RDB3=I46E8              |               | 46E<br>the H | 8 decoded in<br>HT209. Note | 64K X 16<br>nternally, with the SETUP and DISABLE register bits internal to<br>e that in this mode, the external DISABLE pin still functions, but<br>becomes an output, indicating the status of the internal flag.                                                                                                                                                                             |

| RDB2=LCK16              |               | (Wri         | ite protect 1               | 6 bit mode bits SRFF0, SRFF1, SRFF3, and SRC8:4)                                                                                                                                                                                                                                                                                                                                                |

| RDB1=RDOB<br>RDB0=T16BI |               | (For         |                             | odd data bus)<br>F0, SRFF1, SRFF2, to a true state on reset. Also force SRC8:4 if                                                                                                                                                                                                                                                                                                               |

| 6/01                    |               |              |                             | 12 752 0030 01 Bay 1                                                                                                                                                                                                                                                                                                                                                                            |

| Pin<br>Symbol        | Pin<br>Number | Pin<br>Type | Pull<br>Up/Dn* | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------|---------------|-------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M1D[0:7]             | 102-109       | I/O         |                | Memory Display data bus 1: Bidirectional data for plane 1.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| M2D[0:7]             | 112-119       | I/O         |                | Memory Display data bus 2: Bidirectional data for plane 2.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| M3D[0:7]             | 132-139       | I/O         |                | Memory Display data bus 3: Bidirectional data for plane 3.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MEMCS16*/<br>CDDS16* | 31            | 0           |                | MEMory select 16: in a PC/AT this pin is asserted to indicate<br>that the current memory operation is transferring 16 bits. Card<br>Data 16: in a PS/2 this pin is connected to CDDS16* (card data<br>select 16) and indicates that the current memory I/O operation<br>is transferring 16 bits. The PC/AT bus requires 24mA drive<br>on its MEMCS16* signal, so this pin is used to enable an<br>external bus driver.                                                                      |

| MEMR*/S0*            | 121           | Í           |                | MEMory Read: In a PC/AT this pin indicates that a memory read operation is in progress. In a PS/2 this pin is the S0* input.                                                                                                                                                                                                                                                                                                                                                                |

| MEMW*/S1*            | 122           | I           |                | MEMory Write: In a PC/AT this pin indicates that memory<br>write operation is in progress. In a PS/2, this pin is the S1*<br>input.                                                                                                                                                                                                                                                                                                                                                         |

| RAS01*/RAS0          | * 87          | 0           |                | Row Address Strobe for Banks 0 and 1 in non-banked mode.<br>Row Address Strobe for bank 0 in banked mode.                                                                                                                                                                                                                                                                                                                                                                                   |

| RAS2*/RAS1*          | 88            | 0           |                | Row Address Strobe for bank 2 in non-banked mode. Row Address Strobe for bank 1 in banked mode.                                                                                                                                                                                                                                                                                                                                                                                             |

| RAS3*/RAS2*          | 89            | 0           |                | Row Address Strobe for bank 3 in non-banked mode. Row Address Strobe for bank 2 in banked mode.                                                                                                                                                                                                                                                                                                                                                                                             |

| RDACA0/SYS           | 19            | I/O         |                | RAMDACA0-Output/SYStem Input: This pin is sampled by<br>the chip at the end of reset to determine the system type. High<br>indicates PC/AT and low indicates PS/2. This determines the<br>function of many of the system interface signal pins. At all<br>other times, this pin is theRAMDAC A0 Input. This pin is<br>internally pulled up with 100K ohms so may be left uncon-<br>nected in PC/AT systems; it should be connected to ground<br>through a 10K ohm resistor in PS/2 systems. |

| Pin<br>Symbol          | Pin<br>Number | Pin<br>Type | Pull<br>Up/Dn*                                                                                                                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------|---------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDY                    | 51            | TS          |                                                                                                                                                           | ReaDY: This pin is used to synchronize display memory<br>read/write operations. This signal is in a high impedance state<br>until a display memory read or write operation is initiated, then<br>it is driven low. When the operation is completed, it is driven<br>high until the strobe goes away, then released. If fast-write<br>mode is selected, this pin is not driven for memory write<br>operations. This pin has 8mA source and sink capability and<br>can be connected directly to the system bus. |

| RESET                  | 8             | I           |                                                                                                                                                           | RESET: Chip hardware asynchronous reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RFSH*                  | 17            | I           |                                                                                                                                                           | ReFreSH: indicates that the current memory operation is a system RAM refresh operation and should be ignored.                                                                                                                                                                                                                                                                                                                                                                                                 |

| RPLT*                  | 3             | 0           |                                                                                                                                                           | Read PaLeTte external color strobe: active for I/O read opera-<br>tions to ports 3C6, 3C8 and 3C9.                                                                                                                                                                                                                                                                                                                                                                                                            |

| SBHE*                  | 86            | I           |                                                                                                                                                           | System Byte High Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SCLK01/SCLF            | <b>K</b> 84   | 0           |                                                                                                                                                           | Serial CLocK for banks 0 and 1 in non-banked mode. Serial CLocK for all banks 128K x 8 VRAM mode - SCLK to all memory.                                                                                                                                                                                                                                                                                                                                                                                        |

| SETUP*/CAC             | HE*15         | I           |                                                                                                                                                           | SETUP: pin is driven low to place the chip in "setup" mode.<br>In setup mode, the chip only responds to I/O port 102; if not in<br>setup mode, the chip does not respond to I/O port 102. If<br>Internal 46E8 decode is used, this pin is an output and indicates<br>that the FastWrite cache is empty and therefore the current<br>write cycle can be 0WS. Refer to the PS/2 Model 50/60<br>Technical Reference Manual page 2-24 for further explanation<br>of the setup mechanism.                          |

| SOE01*/ 129 (<br>SOE0* |               | 0           |                                                                                                                                                           | Serial Output Enable planes 0 and 1 in non-banked mode.<br>Serial Output Enable plane 0 in banked mode.                                                                                                                                                                                                                                                                                                                                                                                                       |

| SOE23*/<br>SOE3*       | 131           | 0           |                                                                                                                                                           | Serial Output Enable - non banked mode to planes 2 and 3, banked mode to bank 3.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SW 12 I                |               |             | SWitch: the state of this pin may be read in Feature Read Register bit-4 (I/O Address 3C2). This pin is typically connected to the RGB output comparator. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

## **Pin Descriptions**

| Pin<br>Symbol | Pin<br>Number | Pin<br>Type | Puli<br>Up/Dn* | Description                                                                                                                                                                                                                                                                                                                       |

|---------------|---------------|-------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TRAP*/ADL*    | 13            | I/O         |                | TRAP:pin can be used for software trapping on any I/O accesses and can also be used for NMI based emulation in PC mode. In microchannel mode this is a no connect pin. The TRAP*/ADL* is downward compatible with previous designs and can be left connected to the ADL*.                                                         |

| V[0:7]        | 21-28         | 0           |                | Video output bus: these pins are the 8 bits of video data out<br>and are typically connected to the video data inputs of the<br>external color palette.                                                                                                                                                                           |

| VASPACE*      | 18            | Ι           |                | Valid Address SPACE: must be asserted to indicate that the current address is in the proper range (determined by decode of the upper address bits). In a PC/AT this is typically when A23 through A20 are low. In a PS/2 this must also be qualified with the memory address valid signal (MADE24 in the IBM PS/2 documentation). |

|               |               |             |                | This is a chip select for memory operations. Functionality in<br>AT mode is determined by extended register Bit for 1M linear<br>decode<br>Mode 1: Normal, VASPACE* used only to qualify<br>MEMCS16*<br>Mode2:1M linear decode qualifies all memory reads and<br>writes (i.e. chip select)                                        |

| VSYNC         | 33            | 0           |                | Vertical SYNC: The polarity of this signal is controlled by bit-7 of the Miscellaneous output register (I/O address 3C2).                                                                                                                                                                                                         |

| WE*           | 5             | 0           |                | Write Enable: In all modes, this pin is write enable for display<br>memory planes 0-3. When low, display memory writes are<br>enabled to occur on the falling edge of CAS* to the plane(s)<br>selected by the RAS* signals.                                                                                                       |

| WPLT*         | 2             | 0           |                | Write PaLeTte: write strobe for external color palette. Active for I/O write operations to ports 3C6-3C9.                                                                                                                                                                                                                         |

| Pin<br>Symbol | Pin<br>Number | Pin<br>Type | Pull<br>Up/Dn* |                                          |                                        |                                                                                                                                                       |

|---------------|---------------|-------------|----------------|------------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Х25М          | 1             | Ι           |                | generato<br>for selec<br>pin).<br>Summar | r output if used<br>tion of the clock  | ct to 25.175MHz or external clock<br>(see description of XD0-2M signals<br>frequency generated for input on this<br>nections for use with Video Seven |

|               |               |             |                | Clk                                      | Pin                                    | F/W & VRAM VGA                                                                                                                                        |

|               |               |             |                | 0                                        | X25M                                   | 25.175MHz                                                                                                                                             |

|               |               |             |                | ĩ                                        | X28M                                   | 28.322MHz                                                                                                                                             |

|               |               |             |                | 2                                        | FCLK                                   | Feature Connector Clock                                                                                                                               |

|               |               |             |                | 3                                        | XRESM                                  | External Clock or 0MHz                                                                                                                                |

|               |               |             |                | 4                                        | XD0M                                   | 50.350MHz                                                                                                                                             |

|               |               |             |                | 5                                        | XD1M                                   | 65.000MHz                                                                                                                                             |

|               |               |             |                | 6                                        | FCLK                                   | Feature Connector Clock                                                                                                                               |

|               |               |             |                | 7                                        | XD2M                                   | 40.000MHz                                                                                                                                             |

| X28M          | 11            | I           |                | Clock in                                 | put 1 - Connect t                      | ao 28.322MHz.                                                                                                                                         |

| XD0M/SEL0     | 91            | I/O         |                | 0, otherv                                | vise this pin is ex                    | ed Clock Direction"(Index F8) bit =<br>ternal clock SELect output bit-0 (for<br>clock generator).                                                     |

| XD1M/SEL1     | 140           | I/O         |                | 0, otherv                                | vise this pin is ex                    | ed Clock Direction" (Index F8) bit =<br>ternal clock SELect output bit-1 (for<br>clock generator).                                                    |

| XD2M/SEL2     | 151           | I/O         |                | 0, otherv                                | vise this pin is ex                    | ed Clock Direction" (Index F8) bit =<br>ternal clock SELect output bit-2 (for<br>clock generator).                                                    |

| XRAD/RAS3*    | 79            | 0           |                | mode thi<br>bank 3 if                    | is pin is unused.<br>SRC8.7=0. It is l | dress Strobe 3 - In non-banked 256K<br>In banked 256K mode it is RAS for<br>RAS for bank 1 for SRC8.7=1. In 1M<br>ry address A8 to all planes.        |

## **Pin Descriptions**

| Pin<br>Symbol             | Pin<br>Number | Pin<br>Type | Pull<br>Up/Dn* | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |