Fairchild Corporation

Semiconductor & Integrated Circuit Fabrication Techniques

# Semiconductor &

## Integrated Circuit Fabrication Techniques

## Semiconductor & Integrated Circuit Fabrication Techniques

### Fairchild Corporation

A series of seminars for the semiconductor technician generated the idea for this book. The contents have been expanded to include many aspects of process design of interest to the engineer. The book provides an excellent overview to semiconductor technology because it is written on two levels, each topic covered first for the technician, then in more depth for the engineer.

The preparation of semiconductors is discussed according to the manufacturing sequence; thus, the reader develops a better understanding of the entire process, from silicon crystal formation through the final quality control inspections.

Because silicon can be produced fairly easily in chemically stable layers, it has become the most widely-used material for semiconductor manufacture; the authors concentrate on the technology of high quality silicon devices.

Quality control techniques are covered at each step of wafer preparation so that you can fabricate first quality devices. During silicon crystal manufacture, many variables can cause imperfections in the crystals, among them poor cleaning procedures, contaminants, and inaccurate temperature control.

(continued on the back flap)

The manufacturing process is broken down into readily understood steps-each covered in a separate chapter. Among the major considerations are epitaxial deposition, which produces better current handling capacity and higher switching speed; oxidation, which can be accomplished by dry, wet, or anodic process; diffusion, which introduces controlled amounts of chosen impurities into selected regions of the silicon crystal; photomasking, involving the transfer of an image onto the semiconductor surface; chemical vapor deposition of materials for scratch protection, controlled oxidation, or a conductive layer; metallization, or connection of the devices in the substrata for circuit functions; and finally device processing into packaged, tested units for final sale.

Appendices include a glossary and reference information on scientific notation and use of graphs in addition to solutions to exercises contained in the book.

About the authors: Peter Gise received a B.S. in physics and a B.S. in electrical engineering from Lafayette College. He also holds M.S. and Ph.D. degrees in electrical engineering from the University of Santa Clara. Richard Blanchard received a combined B.S. and M.S. from MIT, and a Ph.D. in electrical engineering from Stanford University.

RESTON PUBLISHING COMPANY, INC. A Prentice-Hall Company Reston, Virginia

## Semiconductor and Integrated Circuit Fabrication Techniques

#### PETER E. GISE RICHARD BLANCHARD

Prepared by

The Fairchild Management and

Career Development Center

## Semiconductor and Integrated Circuit Fabrication Techniques

RESTON PUBLISHING COMPANY, INC.

A Prentice-Hall Company

Reston, Virginia

#### Library of Congress Cataloging in Publication Data

Fairchild Camera and Instrument Corporation. Semiconductor processing.

Includes bibliographical references and index.

1. Semiconductors. I. Title.

TK7871.85.F298 1979 ISBN 0-87909-668-3 621.3815'2

78-18373

© 1979 by Reston Publishing Company, Inc.

A Prentice-Hall Company

Reston, Virginia

All rights reserved. No part of this book may be reproduced in any way or by any means, without permission in writing from the publisher.

1 3 5 7 9 10 8 6 4 2

PRINTED IN THE UNITED STATES OF AMERICA

## **Contents**

#### Preface ix

#### 1 Semiconductor Physics I 1

- 1-1 ATOMIC STRUCTURE 1

- 1-2 CLASSIFICATION OF MATERIALS 4

REVIEW EXERCISES 11

#### 2 Semiconductor Physics II 13

- 2-1 RESISTIVITY 15

- 2-2 CARRIER TRANSPORT 17

REVIEW EXERCISES 19

#### 3 Wafer Preparation I 20

- 3-1 SILICON CRYSTAL GROWTH 21

- 3-2 WAFER ORIENTATION, SAWING, AND POLISHING 23

REVIEW EXERCISES 24

#### 4 Wafer Preparation II 26

- 4-1 CRYSTAL ORIENTATION 26

- 4-2 DOPING OF CRYSTALS DURING GROWTH 28

- 4-3 CRYSTAL DEFECTS 30

REVIEW EXERCISES 31

#### 5 Epitaxial Deposition I 32

- 5-1 INTRODUCTION 32

- 5-2 THEORY 34

- 5-3 GROWTH OF AN EPITAXIAL LAYER 39

REVIEW EXERCISES 41

| 6 | Epi | taxial | Deposi | tion | 11 | 43 |

|---|-----|--------|--------|------|----|----|

|---|-----|--------|--------|------|----|----|

- 6-1 INTRODUCTION 43

6-2 EVALUATION OF EPITAXIAL LAYERS 45

REVIEW EXERCISES 49

- 7 Oxidation | 50

- 7-1 INTRODUCTION 50

- 7-2 EQUIPMENT FOR THERMAL OXIDATION 52

- 7-3 THE OXIDATION PROCESS 52

- 7-4 OXIDE EVALUATION 55

- 7-5 RECENT ADVANCES IN OXIDATION TECHNOLOGY 59

REVIEW EXERCISES 59

- 8 Oxidation II 60

- 8-1 OXIDE THICKNESS DETERMINATION 60

- 8-2 OXIDATION REACTION 62

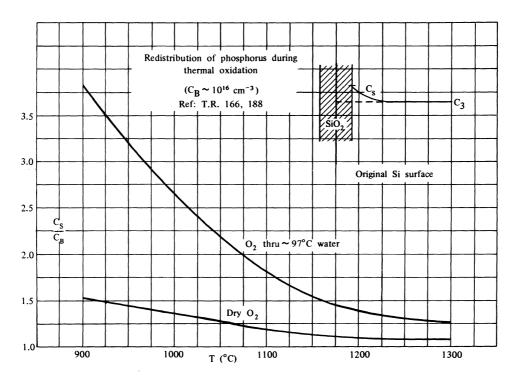

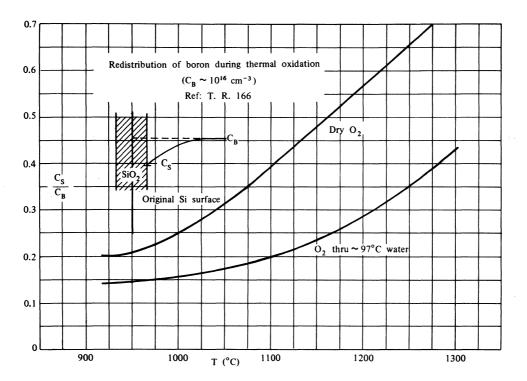

- 8-3 REDISTRIBUTION OF DOPANT ATOMS DURING THERMAL OXIDATION 64

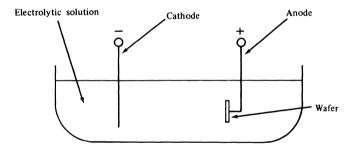

- 8-4 ANODIC OXIDATION 67

- **REVIEW EXERCISES 67**

- 9 Impurity Introduction and Redistribution I 69

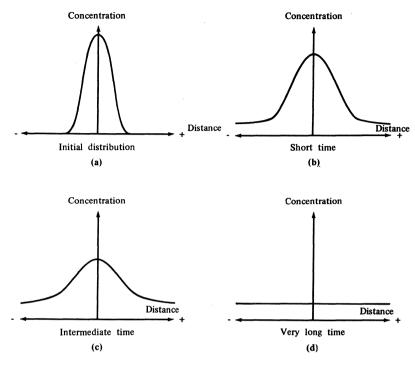

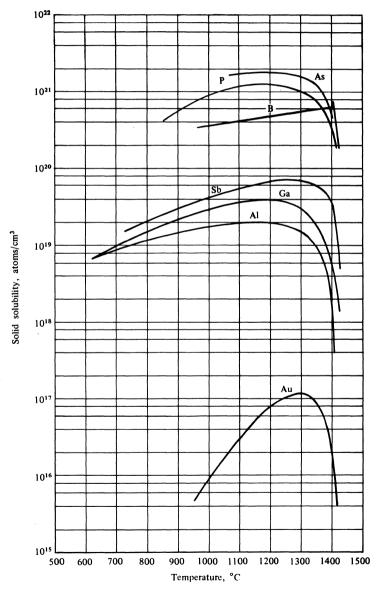

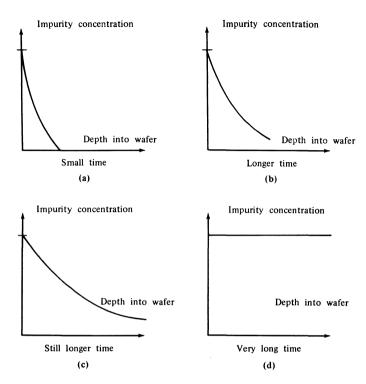

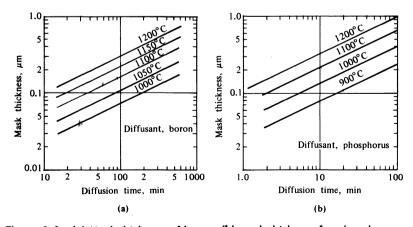

- 9-1 THE IDEA OF DIFFUSION 69

- 9-2 THE DIFFUSION PROCESS 70

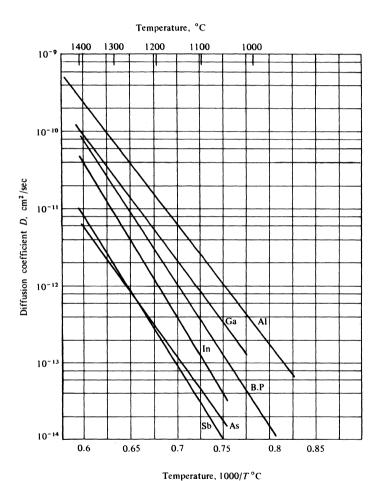

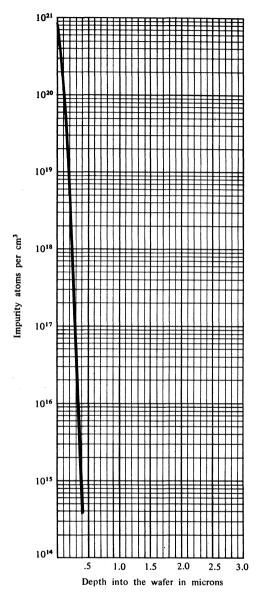

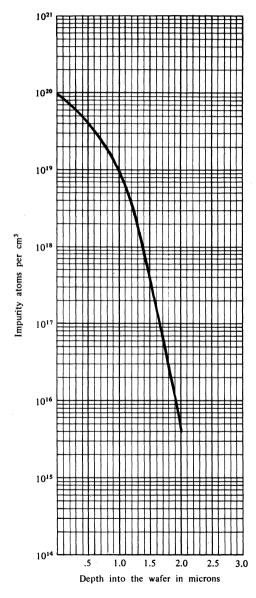

- 9-3 DIFFUSION ANALYSIS 80

- 9-4 ION IMPLANTATION 80

REVIEW EXERCISES 82

#### 10 Impurity Introduction and Redistribution II 84

10-1 MATHEMATICS OF DIFFUSION

REVIEW EXERCISES 99

#### 11 Photomasking 101

- 11-1 INTRODUCTION 101

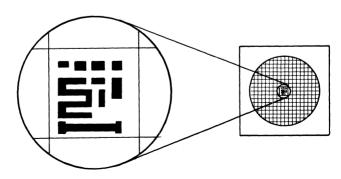

- 11-2 GENERATION OF A PHOTOMASK 101

REVIEW EXERCISES 109

#### 12 Chemical Vapor Deposition 111

- 12-1 INTRODUCTION 111

- 12-2 CVD PROCEDURES AND USES 114

REVIEW EXERCISES 119

#### 13 Metallization 120

- 13-1 METALLIZATION REQUIREMENTS 120

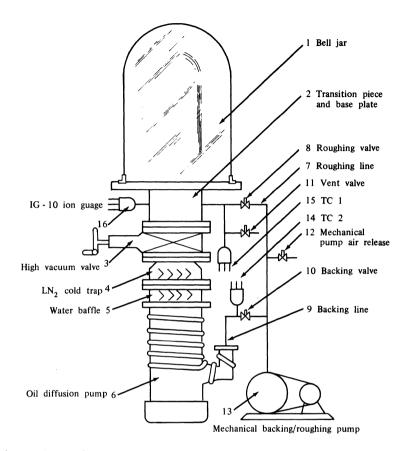

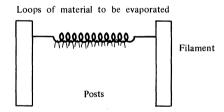

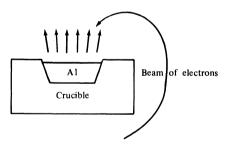

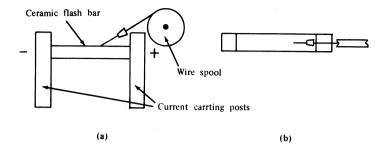

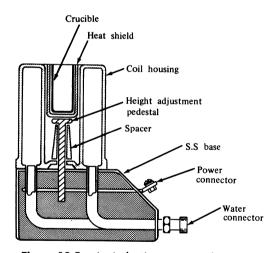

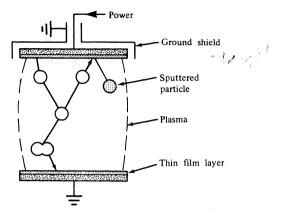

- 13-2 VACUUM DEPOSITION 121

- 13-3 DEPOSITION TECHNIQUES 124

- 13-4 VACUUM DEPOSITION CYCLE 127

REVIEW EXERCISES 128

#### 14 Device Processing: from Alloy to Sale 129

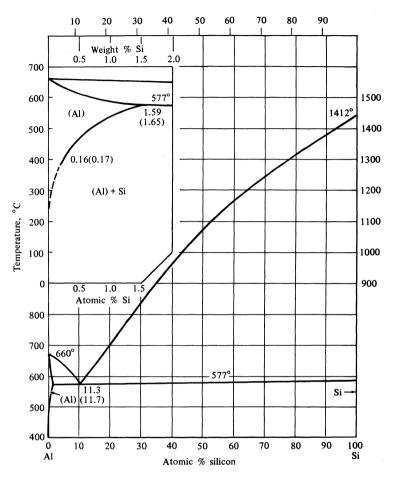

- 14-1 ALLOY/ANNEAL 129

- 14-2 POST-ALLOY SAMPLE PROBE 131

- 14-3 SCRATCH PROTECTION 132

- 14-4 BACKSIDE PREPARATION 132

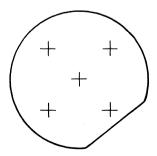

- 14-5 WAFER SORT 132

- 14-6 DEVICE SEPARATION 133

- 14-7 DIE-ATTACH (OR DIE BONDING) 134

- 14-8 WIRE BONDING 135

- 14-9 PACKAGE CONSIDERATIONS 135

- 14-10 FINAL TEST 136

- 14-11 MARK AND PACK 136 REVIEW EXERCISES 136

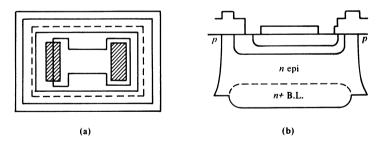

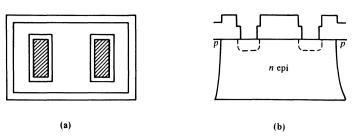

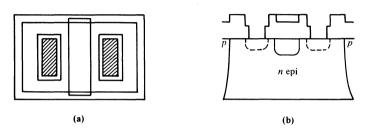

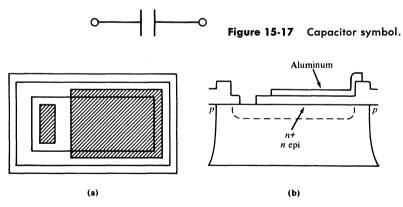

#### 15 Devices 138

- 15-1 BIPOLAR TECHNOLOGY 138

- 15-2 DEVICES FABRICATED USING STANDARD BIPOLAR TECHNOLOGY 139

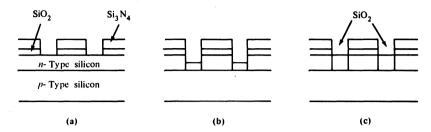

- 15-3 MOS TECHNOLOGY 147

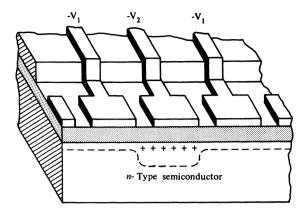

- 15-4 OTHER MOS TECHNOLOGIES 149

REVIEW EXERCISES 150

#### 16 Contamination Control 151

- 16-1 CHEMICALS AND CLEANING PROCEDURES 151

- 16-2 WATER 153

- 16-3 AIR 155

- 16-4 GASES 157

- 16-5 PERSONNEL/CLEAN ROOM 157

REVIEW EXERCISES 157

#### 17 Advanced Silicon Technology 159

- 17-1 DOMINANT TRENDS IN TECHNOLOGY: SUBTRATE SIZE AND DEVICE DENSITY 159

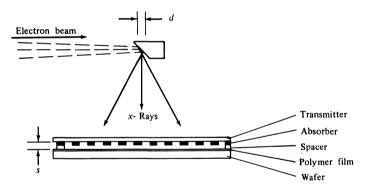

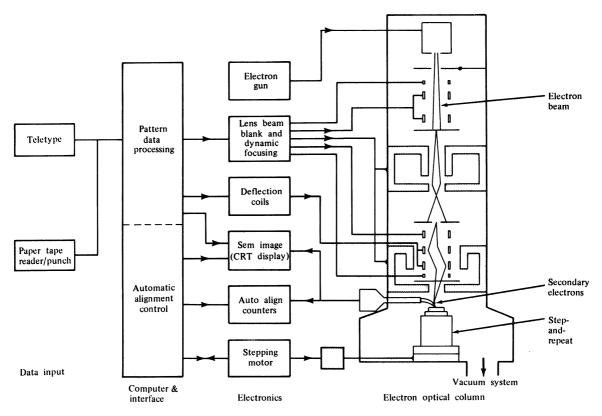

- 17-2 ALIGNMENT/EXPOSURE STEP 160

- 17-3 DEVELOPMENTS IN PROCESSING TECHNOLOGY 163

- 17-4 DEVELOPMENTS IN DEVICE TECHNOLOGY 164

REVIEW EXERCISES 166

#### 18 Nonsilicon Technology 167

18-1 LIGHT-EMITTING DIODES (LED'S) 167

18-2 OPTICAL INTEGRATED CIRCUITS 168

18-3 LIQUID CRYSTAL DISPLAYS 168

18-4 QUARTZ CRYSTAL OSCILLATORS 169

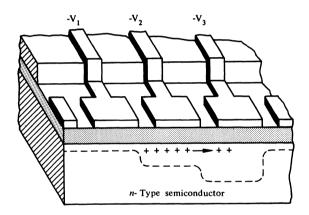

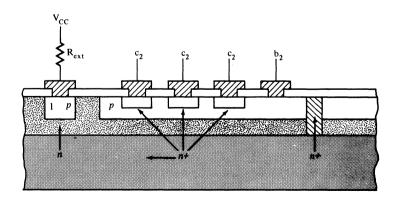

18-5 MAGNETIC BUBBLE OR MAGNETIC DOMAIN DEVICES 169

18-6 HYBRID TECHNOLOGY 169

REVIEW EXERCISES 170

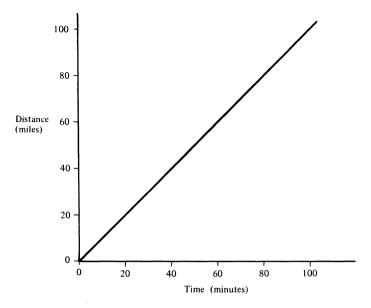

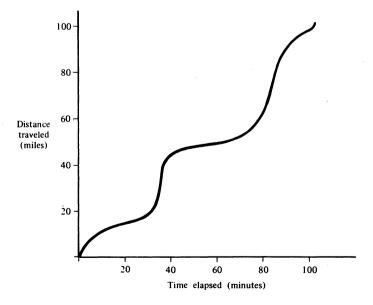

Appendix 1: Scientific Notation 171

Appendix II: Use of Graphs 176

Appendix III: Units 180

Glossary 183

Solutions 191

Index 207

### **Preface**

The purposes of this text are to provide a single source of reference to those individuals involved in the processing of semiconductors, and to introduce students of other technologies to the technology of semiconductor processing. The text arose from a sequence of college courses for the semiconductor technician, and was expanded to include many aspects of process design of interest to the processing engineer.

The more complex lessons in the text are approached at two levels of detail. The first level covers the basics of the particular topic and terminates at the technician level. The second level covers more advanced material and should be used at the engineering level.

Each lesson should take an average of two hours to complete. For such self-paced study audio cassettes are available. The set may be purchased from Fairchild Camera & Instrument Corporation, Corporate Training, Mountain View, California.

## Semiconductor and Integrated Circuit Fabrication Techniques

## Semiconductor Physics I

#### 1-1 ATOMIC STRUCTURE

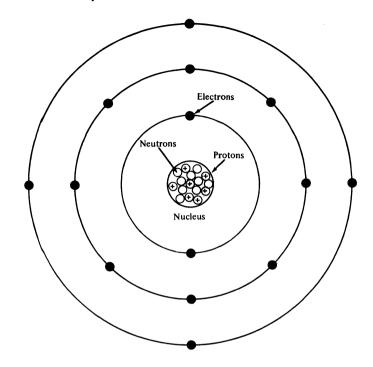

Early structural models of the atom pictured it as having a nucleus composed of positively charged protons and electrically neutral neutrons, surrounded by orbitals or shells containing negatively charged electrons. (Figure 1-1). This model of the atom is being continuously refined by atomic physicists, but the features of the model are sufficient to explain many of the physical phenomena observed in many materials, including most semiconductors.

An atom that has the same number of electrons and protons is electrically neutral. However, the gain or loss of electrons from the orbitals surrounding the nucleus produces an atom that is charged either positively or negatively. An atom charged in such a fashion is called an ionized atom or an ion. The majority of the physical and chemical properties of an atom are determined by the number of electrons in the outermost orbital, since these electrons are the means by which the atom interacts with the outside world.

All atoms with the same number of protons (regardless of the number of neutrons or electrons) are the same element. Unionized atoms with the same number of protons must also have the same number of electrons. Hence, only the number of neutrons contained in the nucleus can differ. Atoms with the same number of protons but a different number of neutrons are isotopes of the element.

Studies by several nineteenth century chemists detected similarities in the physical and chemical properties of elements having

Figure 1-1 A silicon atom.

different densities. Grouping of elements with similar properties based on their densities led to the Periodic Table (Figure 1-2). This table was arrived at largely by experimental means, but it offers large insights into the behavior of materials. The uncomplicated but accurate picture of semiconductors obtained through use of the Periodic Table is sufficient for all but advanced work in semiconductors.

The Periodic Table (modified from Mendeleev's) is based upon the arrangement of electrons around the nucleus of an atom. Every atom has orbitals or shells that can be occupied by electrons. The orbitals closer to the nucleus can hold fewer electrons than the orbitals farther away. Electrons fill orbitals starting from the innermost. The rows of elements in the Periodic Table correspond to the filling of an orbital with electrons. When an orbital is filled, a new row in the Periodic Table is begun. Elements that are in the same column in the Periodic Table have the same number of electrons in the outermost orbital. The columns are given "group numbers" which tell the number of electrons in the outer orbital. (We will now concentrate on the Group I elements.)

| GROUP       |             | i                      | II             | 111                     | IV             | V              | VI             | VII            |               | VIII            |                | 0                |

|-------------|-------------|------------------------|----------------|-------------------------|----------------|----------------|----------------|----------------|---------------|-----------------|----------------|------------------|

| Period<br>1 | Series<br>1 | 1H<br>1.0080           |                |                         |                |                |                |                |               |                 |                | 2He<br>4.003     |

| 2           | 2           | 3Li<br>6.940           | 4Be<br>9.013   | 5B<br>10.82             | 6C<br>12.010   | 7N<br>14.008   | 80<br>16.000   | 9F<br>19.00    |               |                 |                | 10Ne<br>  20.183 |

| 3           | 3           | 11Na<br>22.997         | 12Mg<br>24.32  | 13 Al<br>26.97          | 14Si<br>28.06  | 15P<br>30.98   | 16S<br>32.066  | 17Cl<br>35.457 |               |                 |                | 18A<br>39.944    |

| 4           | 4           | 19K<br>39.096          | 20Ca<br>40.08  | 21Sc<br>45.10           | 22Ti<br>47.90  | 23V<br>50.95   | 24Cr<br>52.01  | 25Mn<br>54.93  | 26Fe<br>55.85 | 27Co<br>58.94   | 28Ni<br>58.69  | <br>             |

|             | 5           | 29Cu<br>63.54          | 30Zn<br>65.38  | 31Ga<br>69.72           | 32Ge<br>72.60  | 33 As<br>74.91 | 34Se<br>78.96  | 35Br<br>79.916 |               |                 |                | 36Kr<br>83.7     |

| _           | 6           | 37Rb<br>85.48          | 38Sr<br>87.63  | 39Y<br>88.92            | 40Zr<br>91.22  | 41 Nb<br>92.91 | 42Mo<br>95.95  | 43Tc           | 44Ru<br>101.7 | 45 Rh<br>102.91 | 46Pd<br>106.7  |                  |

| 5           | 7           | 47 Ag<br>107.880       | 48Cd<br>112.41 | 49In<br>114.76          | 50Sn<br>118.70 | 51Sb<br>121.76 | 52Te<br>127.61 | 531<br>126.92  |               |                 |                | 54Xe<br>131.3    |

| 6           | 8           | 55Cs<br>132.91         | 56Ba<br>137.36 | 6 57-71<br>Rare earths* | 72Hf<br>178.6  | 73Ta<br>180.88 | 74W<br>183.92  | 75Re<br>186.31 | 76Os<br>190.2 | 771r<br>193.1   | 78Pt<br>195.23 |                  |

|             | 9           | 79 <b>A</b> u<br>197.2 | 80Hg<br>200.61 | 81Ti<br>204.39          | 82Pb<br>207.21 | 83Bi<br>209.00 | 84Po<br>210    | 85 At          |               |                 |                | 86Rn<br>1 222    |

| 7           | 10          | 87Fr                   | 88Ra<br>226.05 | 89 Actinide series**    |                |                |                |                |               |                 |                | 1                |

Atomic weighs are the most recent adopted by the International Union of Chemistry; none are given for artificially produced elements.

| *Rare earths:      |  |  |      |       |      |      | 66Dy<br>162.46 |  |  |  |

|--------------------|--|--|------|-------|------|------|----------------|--|--|--|

| **Actinide series: |  |  | 94Pu | 95 Am | 96Cm | 97Bk | 98Cf           |  |  |  |

Figure 1-2 Periodic table of the elements.

#### 4 Semiconductor Physics I

Dimitri Ivanovich Mendeleev, the Russian chemist who devised the Periodic Table, noted that atoms with eight electrons in their outer orbitals are chemically inert. The observation that atoms have a complete set of electrons when they have eight electrons in the outer shell, explains the way elements reacted to form compounds. Group I elements (with one electron in their outer shell) react with Group VII elements (with seven electrons in their outer shell). The Group VII atom "borrows" the electron to complete its outer shell, leaving the Group I atom with zero electrons in its outer shell, but with completed shells beneath. Each element then has a full complement of electrons in its outer shell. The atoms are held together by the electric force between the atoms with one extra electron and the atom with one less electron. This type of bonding is known as ionic bonding.

If a Group II and a Group VI element combine, each atom satisfies its need for electrons. However, the Group VI atom has difficulty capturing the extra electrons, so it shares them instead. The bond formed is less ionic (electron-taking) and more covalent (electron-sharing). In a similar fashion, Group III atoms combine with Group V atoms, and group IV atoms combine with Group IV atoms. A Group IV atom will share one of its four electrons with each of its four nearest neighbors part of the time, and borrow one electron from its neighbors part of the time.

#### 1-2 CLASSIFICATION OF MATERIALS

One method used by scientists to classify materials is to group them by their ability to conduct electricity. Three broad classifications of materials are:

- 1. Insulator—does not conduct electricity to an appreciable degree.

- 2. Metal—conducts electricity easily.

- 3. Semiconductor—conducts electricity poorly when pure.

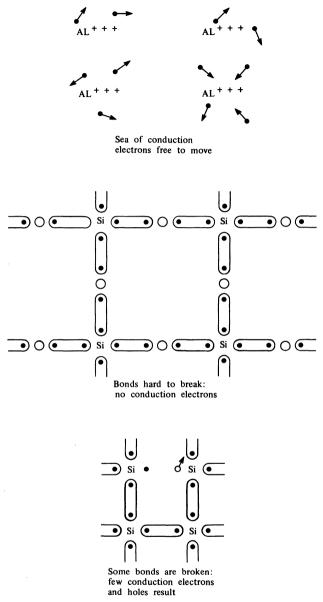

If we look at the electron structure of these three classifications of materials (Figure 1-3), we see that:

- 1. Insulators have all electrons tightly bound, so none are free to carry current.

- 2. Metals have many electrons readily available to carry current

- 3. Semiconductors have some electrons free to carry current.

ý

Figure 1-3 Bonding diagrams of a metal, an insulator, and a semiconductor.

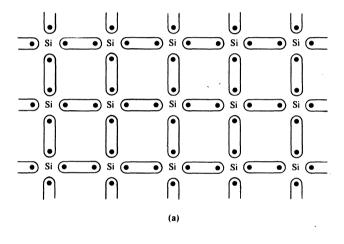

Taking a closer look at semiconductors, of which silicon and germanium are the most widely used, we see that they both belong to Group IV in the Periodic Table. When these elements are crystalline,

#### 6 Semiconductor Physics I

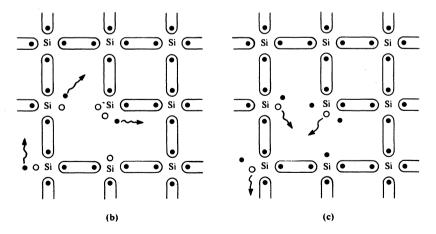

an atom shares one of its four electrons with each of its nearest neighbors (Figure 1-4a). However, at any temperature greater than absolute zero (0°K), some of the bonds linking the atoms are broken (Figure 1-4b). The broken bonds produce electrons free to conduct electricity. In addition, the broken bond corresponding to the absence of an electron is also free to move in the lattice (Figure 1-4c). (The absence of an electron is called a hole; this concept is similar to that calling the absence of water a bubble.) In a pure semiconductor crystal, the number of broken bonds depends only on the temperature. Since every broken bond produces both a hole and an electron, they are present in

Figure 1-4 (a) Silicon at absolute zero; (b) electron conduction in silicon; (c) hole conduction in silicon.

equal numbers. The symbol n is used to signify the number of electrons/cm<sup>3</sup> in a semiconductor, while the symbol p signifies the number of holes/cm3 in a semiconductor. Since they are equal in pure or "intrinsic" silicon, we can say that n equals p. The number of broken bonds in an intrinsic sample is called  $n_i$ , and it follows that

$$n = p = n_i, \quad \text{and} \tag{1-1}$$

$$n \cdot p = n_i^2 \tag{1-2}$$

where  $n^2$  depends only on temperature. In silicon at room temperature (27° C)  $n_i = 1.4 \times 10^{10} / \text{cm}^3$ , and  $n_i^2 \approx 2 \times 10^{20} / \text{cm}^6$ .

The presence of equal numbers of holes and electrons leads to no interesting phenomena, but the ability to increase the number of holes or electrons by adding trace amounts of impurities called dopants, means that regions of semiconductor materials can be altered to perform useful functions. Silicon has four electrons in the outer shell which it shares with its four nearest neighbors. The substitution for silicon of an atom from Group V, for example phosphorus, results in the phosphorus sharing one of its five electrons with each of its four nearest neighbors (Figure 1-5a). The extra electron is not needed for bonding purposes, and is free to conduct electrical current. Semiconductors containing an excess of conduction electrons are called n-type. In an analogous manner, additional holes can be provided by substituting an atom like boron for a silicon atom (Figure 1-5b). Semiconductors containing an excess of holes are called p-type. Atoms supplying additional electrons for the conduction process are called donors; the number of donors/cm<sup>3</sup> in a semiconductor is  $N_D$ . Atoms that supply additional holes for the coduction process are called acceptors; the number of acceptors/cm<sup>3</sup> in a semiconductor is  $N_A$ . For silicon, potential donor atoms are the atoms of Group V with five electrons in their outer shell.

Figure 1-5 (a) Extra electron easy to remove; (b) extra hole easy to remove.

The atoms frequently used to dope silicon n-type are phosphorus, arsenic, and antimony. Potential acceptors for silicon are the Group III atoms with three electrons in their outer shell. The atoms used to dope silicon p-type are boron, aluminum, and gallium (boron is used most frequently).

An increase in the number of conduction electrons present in a semiconductor causes a corresponding decrease in the number of holes, and vice versa. The equation  $n \cdot p = n_i^2$  is valid even when n does not equal p ( $n \neq p$ ). If only donor atoms have been added to silicon and the number of donors is less than  $10^{19}/\text{cm}^3$ , ( $N_D < 10^{19}/\text{cm}^3$ ), all of the donors produce conduction electrons. It follows that, in this case,

the donors produce conduction electrons. It follows that, in this case,  $n = N_D$ , and  $p = \frac{n_i^2}{N_D}$ . In a similar fashion, if only acceptors are added to a bar of silicon, and their number is less than  $10^{19}/\text{cm}^3$ ,  $(N_A < 10^{19}/\text{cm}^3)$ , each acceptor atom produces one hole. In this case,  $p = N_A$ , and  $n = \frac{n_i^2}{N_A}$ .

When both donors and acceptors are added to a semiconductor, they tend to cancel each other out. When more donor than acceptor atoms are added,  $(N_A < N_D)$ , the donor atoms cancel out the effect of all of the acceptor atoms, and the number of electrons is the difference between the number of donors and the number of acceptors  $(n = N_D - N_A)$ . In an analogous manner, if more acceptor atoms are added than donor atoms, the acceptor atoms cancel out the effect of all of the donor atoms, and the number of holes is the difference between the number of acceptors and the number of donors  $(p = N_A - N_D)$ . In both cases, the product of  $n \cdot p$  remains constant, so the carrier type in the minority can be determined using the formula  $n \cdot p = n_i^2$ .

The amount of dopant present in a semiconductor is determined by measuring its conductivity or resistivity. The resistivity of a material is the opposing force a material has to a voltage placed across it. The symbol for resistivity is the Greek letter  $\rho$ . The units of resistivity are ohm-centimeters ( $\Omega$ -cm). The conductivity is related to the resistivity by the equation

$$\sigma = \frac{1}{\rho} \tag{1-3}$$

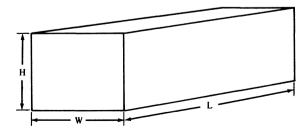

The conductivity of a sample depends upon the number of free carriers (holes and/or electrons) and their mobility or the ease with which they move through the sample. If the resistivity (or the conductivity) of a material is known, the resistance of a box-shaped piece of material is determined by the formula:

$$R = \frac{\rho L}{A} \tag{1-4}$$

where

R =the resistance of the material (units of ohms)

L = the length of the material from contact to contact

A =the cross-sectional area of the material (area = height  $\times$  width)

The resistance of a piece of material is related to the applied voltage (V) and the current that flows (I) by the equation:

$$V = RI \text{ or } R = \frac{V}{I} \tag{1-5}$$

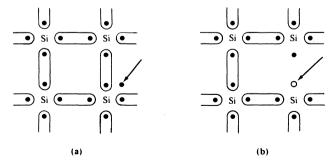

In a semiconductor (and in other industrial materials as well) the "sheet resistance" of a material is an often-measured parameter. The symbol for sheet resistance is  $R_s$ . Sheet resistance is measured in ohms per square  $(\Omega/\Box)$ . The resistance of a resistor made up of n squares laid in a row is  $nR_s$ . (For instance, if 10 squares of material are laid in a row with  $R_s = 100 \ \Omega/\Box$ ,  $nR_s = 10R_s = 1000 \ \Omega$ .) Sheet resistance is measured using a four-point probe. (Figure 1-6.). The formula relating sheet resistance to current and voltage is:

$$R_s = 4.53 \frac{V}{I} \tag{1-6}$$

This equation is valid when:

- 1. The thickness of the layer being measured is much less than the spacing between the probes, and

- 2. The size of the piece of material being measured is much greater in length and width than the probe spacing.

Figure 1-6 Four-point probe.

If a thin layer of material is uniformly doped and the sheet resistance is known, the resistivity  $\rho$  is found with the equation:

$$\rho = R_s \times \text{thickness} \qquad \text{or} \qquad \rho = R_s \cdot t \tag{1-7}$$

If the thickness of the sample is much greater than the probe spacing, the formula

$$\rho = 2\pi S \frac{V}{I} \qquad (\pi = 3.14159) \tag{1-8}$$

relates the current and voltage readings of a four-point probe to the resistivity of the material, where S is the spacing between the probes on the four-point probe.

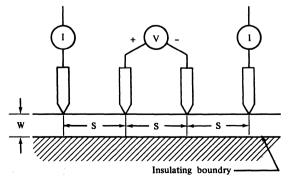

The resistivity of silicon depends upon the number of acceptor and donor atoms added and the temperature. When only acceptor or donor atoms have been added to a bar of silicon, the resistivity of the silicon can be obtained from Figure 1-7. Conversely, the doping concentration of a uniformly doped sample can be determined if the resistivity is known. To determine the resistivity of a sample if the doping concentration and type is known, find the doping concentration along the bottom of the graph, then proceed upward until the line corresponding to the type of dopant (p-type or n-type) is encountered. Then proceed horizontally to the left to obtain the resistivity. The inverse operation is performed to obtain the doping concentration from the resistivity.

Figure 1-7 n-type and p-type resistivity.

#### REVIEW EXERCISES: SEMICONDUCTOR PHYSICS I

- 1. A sample of silicon is doped with 1015 atoms/cm3 of phosphorus

- a. Determine the donor concentration  $N_D$ ,

- **b.** Determine the acceptor concentration  $N_A$ ,

- **c.** Determine the electron concentration n.

- **d.** Determine the hole concentration p

- e. Determine the resistivity  $\rho$

- 2. A sample of silicon is doped with  $2 \times 10^{16}$  atoms/cm<sup>3</sup> of boron.

- **a.** Determine the donor concentration  $N_D$ ,

- **b.** Determine the acceptor concentration  $N_A$ ,

- **c.** Determine the electron concentration n,

- **d.** Determine the hole concentration p,

- **e.** Determine the resistivity  $\rho$

- 3. If a sample of silicon is doped with  $3 \times 10^{17}$  atoms of arsenic and  $5 \times 10^{17}$  atoms of boron.

- **a.** Determine the donor concentration  $N_D$ ,

- **b.** Determine the acceptor concentration  $N_A$ ,

- **c.** Determine the electron concentration n.

- **d.** Determine the hole concentration p.

- 4. A 4-point probe measurement has been made on a sample resulting in:

$$V = 5 \times 10^{-3} \text{ volts}$$

$I = 4.5 \times 10^{-3} \text{ amps}$

What is the sheet resistance  $R_s$  of the sample?

5. A sample of material has the following properties:

its length is 100 microns;

its width is 5 microns;

its height is 2 microns;

its resistivity is 2 ohm-centimeters.

Determine the resistance of the bar of material.

- **6.** A sample of germanium is uniformly doped with boron atoms to produce an impurity concentration of  $5 \times 10^{16}$  atoms/cm<sup>3</sup>. If the intrinsic carrier concentration at  $300^{\circ}$ K is  $2.43 \times 10^{13}$  carriers/cm<sup>3</sup>, determine the hole and electron concentrations for this sample.

- 7. If the temperature of the sample in problem 6 is increased, the imbalance between the majority and minority carrier concentrations decreases. If the intrinsic carrier concentration increases exponentially with temperature at the rate of 6% per °K, at what temperature is the minority carrier concentration equal to 2% of the majority carrier concentration?

- 8. An unknown semiconductor material has a hole concentration of  $10^{15}$  carriers/cm<sup>3</sup> and an electron concentration of  $4 \times 10^{13}$  carriers/cm<sup>3</sup>. Determine the intrinsic carrier concentration and the net impurity concentration.

- 9. A silicon sample is doped with  $2 \times 10^{16}$  acceptors/cm³ and  $5 \times 10^{15}$  donors/cm³. What type of impurity and in what concentration should be added to make the equilibrium electron and hole concentrations the same at room temperature?

- 10. A silicon bar with a length of 1 cm and a height and width of 0.1 cm has a resistance measured from end to end of 10 ohms. If a hot probe measurement indicates the bar to be *n*-type, determine the donor concentration.

## Semiconductor Physics II

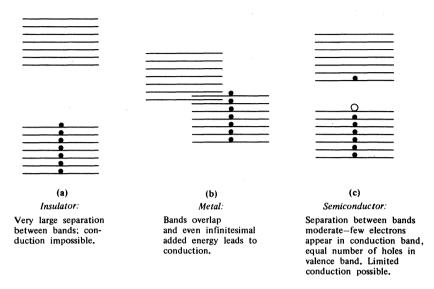

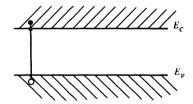

The classification of materials into metals, insulators, and semiconductors can be viewed in a way different from that used in the first part of this presentation. The allowable orbitals or shells that electrons can occupy correspond to allowable energy levels for the electrons. As atoms are brought together, these energy levels enlarge to form allowable energy bands for electrons. An insulator can be viewed as having a completely full energy band separated by a large energy gap from the next allowable band (Figure 2-1a). Similarly, a metal can be viewed as having two overlapping energy bands, allowing electrons to move easily to a higher energy level to carry current (Figure 2-1b). A semiconductor can be seen as having two energy levels separated by only a narrow energy band (Figure 2-1c). The energy present in the crystal is sufficient to cause a few of the electrons in the lower (valence) energy band to jump to the upper (conduction) energy band (Figure 2-2). This jump results in electrons in the conduction band and holes in the valence band.

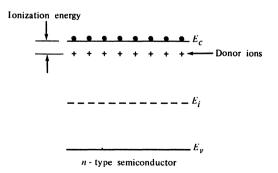

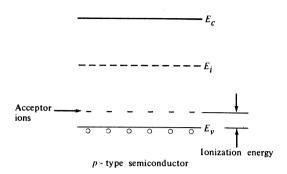

The addition of donor or acceptor dopants to a semiconductor adds impurity energy levels in the energy band gap near the conduction and valence band. Donor atoms produce electrons, so the donor impurity level is just below the conduction band (Figure 2-3). Acceptor atoms introduce levels that can be occupied by electrons just above the valence band. The occupation of these levels by electrons from the valence band results in holes (Figure 2-4). When both donor and acceptor atoms are added to a semiconductor, electrons from the donor level occupy the acceptor level until it is filled, or until all of the donor atoms have left the donor level.

#### 14 Semiconductor Physics II

Figure 2-1 Energy-level diagram of (a) insulator (b) metal and (c) semiconductor.

Figure 2-2 Transition of an electron from valence band to conduction band.

Figure 2-3 Donor levels in semiconductors.

Figure 2-4 Acceptor levels in semiconductors.

The band model of semiconductors complements the bond model discussed previously. Familiarity with both of these models aids in understanding the various phenomena encountered in the semiconductor field.

#### 2-1 RESISTIVITY

The addition of impurities to a semiconductor modifies the resistivity in a manner that produces useful behavior in semiconductors. The conductivity of a material depends on the number of holes and electrons, the charge each particle carries (called q, the charge of an electron =  $1.6 \times 10^{-19}$  coulombs), and the ease with which the holes and electrons move through the material. The formula for the conductivity of a material can be written as:

$$\sigma = qn\mu_n + qp\mu_p \tag{2-1}$$

where  $\mu_p = \text{hole mobility}$   $\mu_n = \text{electron mobility}$

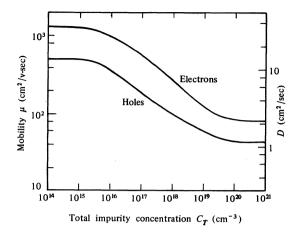

The terms n and p are determined as previously discussed. The ease with which carriers (either holes or electrons) move through a crystal is influenced by the total number of impurity atoms present. Each impurity atom in the lattice is a slight disruption in the otherwise regular crystal structure. A graph of the mobility of both holes and electrons in silicon at 27°C is shown in Figure 2-5. The total dopant concentration  $C_T$  is the sum of the number of donor and acceptor atoms.

$$C_T = N_A + N_D \tag{2-2}$$

Figure 2-5 Electron and hole mobilities in silicon.

The graph of resistivity versus impurity concentration shown in Figure 1-7 is valid when only acceptor or donor atoms are added to silicon. If both types of impurities are added, the resistivity of the material must be calculated.

**Example 1**  $N_D = 2 \times 10^{15}/\text{cm}^3$ ;  $N_A = 4 \times 10^{15}/\text{cm}^3$  at 27°C; determine the resistivity of the sample. First, determine n and p.

$$p=N_A-N_D=2\times 10^{15}/\mathrm{cm}^3$$

$n=\frac{n_s^2}{p}=1\times 10^5$   $\mu_n$  and  $\mu_p$  are found by noting that  $N_D+N_A=6\times 10^{15}/\mathrm{cm}^3$

$$\mu_n = 1100 \text{ cm}^2/\text{v-sec}; \mu_p = 400 \text{ cm}^2/\text{v-sec}$$

$$\sigma = q (\mu_n n + \mu_p p) \cong q \mu_p p$$

now

$$ρ = \frac{1}{σ} = \frac{1}{(1.6 \times 10^{-19}) (400) (2 \times 10^{15})} = 7.8 Ω-cm$$

**Example 2**  $N_D = 6 \times 10^{17} / \text{cm}^3$ ;  $N_A = 3 \times 10^{17} / \text{cm}^3$  at 27°C; determine the resistivity of the sample.

First, determine n and p.

$$n = N_D - N_A = 3 \times 10^{17}/\text{cm}^3$$

$p = \frac{n_i^2}{n} = 6.7 \times 10^2/\text{cm}^3$

$\mu_n$  and  $\mu_p$  are found by first determining  $C_T = N_A + N_D$ ; thus  $\mu_n \cong 700$ ,  $\mu_p = 200$ .

$\sigma = q (\mu_n n + \mu_p p) \cong q \mu_n n = (1.6 \times 10^{-19})$

$(700) (3 \times 10^{17})$

$\sigma = 3.36 \times 10^1 = 33.6 \frac{1}{\Omega \text{-cm}}$

$\rho = .028 \Omega \text{-cm}$

#### 2-2 CARRIER TRANSPORT

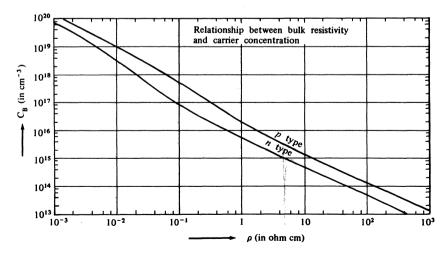

The carriers present in a semiconductor move by one of two processes, drift or diffusion. Drift is the motion caused by the presence of an electric field. With no applied field, carriers move about randomly in a semiconductor (Figure 2-6a). Under the influence of an applied field, the carriers acquire a directed component of motion (Figure 2-6b). The sum of the directed components of drift result in current flow in the sample. Carriers also move by the process of diffusion. Diffusion is the motion of particles from regions of high concentration to regions of low concentration caused by random motion. The result of both types of carrier motion determines the total current flow in a material.

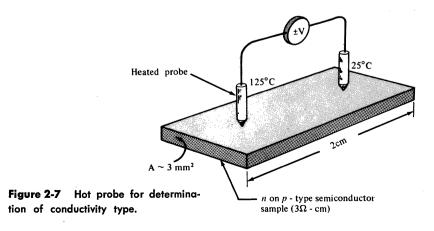

The diffusion of the mobile carrier (either holes in p-type silicon or electrons in n-type silicon) from higher temperature regions to lower temperature regions can be used to determine whether a sample of silicon is n-type or p-type. If an area of a silicon wafer is heated locally, as shown in Figure 2-7, the majority carriers diffuse away from the hot region, a voltage is then produced, and can be measured to determine the conductivity of the sample. If the sample is n-type, the voltage on the hot probe is positive with respect to a second probe. Similarly, if the sample is p-type, the voltage on the hot probe is negative with respect to a second probe. This testing technique is useful on samples unless there is just a thin layer of oppositely doped material on the surface of the wafer.

Figure 2-6 Drift under the influence of an electric field.

#### REVIEW EXERCISES: SEMICONDUCTOR PHYSICS II

- 1. A bar of silicon is doped with  $2 \times 10^{15}$  arsenic atoms. Calculate the resistivity of this bar, and compare your answer with Figure 1-7.

- 2. A bar of silicon contains  $1 \times 10^{18}$  boron atoms/cm<sup>3</sup>, and  $3 \times 10^{18}$ antimony atoms/cm<sup>3</sup>.

- **a.** Determine the donor and acceptor concentrations  $(N_D \text{ and } N_A)$ .

- **b.** Determine the hole and electron concentrations (p and n).

- c. Determine the mobilities of the holes and the electrons ( $\mu_p$  and  $\mu_n$ ).

- d. Determine the resistivity of the bar.

- e. Why does the answer from (d) differ from that obtained from Figure 1-7, with  $N_D = 3 \times 10^{18} / \text{cm}^3$ ?

- 3. An *n*-type silicon cube 1.0 cm on a side is doped with  $1 \times 10^{14}$ donors/cm<sup>3</sup>. A smaller p-type region, measuring 0.5 cm on a side, is diffused into the center of the top surface of the cube. If the resistivity of the p-region is 2.5  $\Omega$  -cm, find the acceptor concentration in the p-region and the total number of impurity atoms in the p-region.

- 4. Draw the energy level diagram for silicon in equilibrium at 27°C and doped with  $3 \times 10^{17}$  phosphorus atoms/cm<sup>3</sup> and  $2.9 \times 10^{17}$ boron atoms/cm<sup>3</sup>. Are all the impurities ionized?

- 5. When two opposite type impurities are added to a semiconductor such that the number of donors equals the number of acceptors the crystal is said to be compensated. Is the resulting crystal electrically intrinsic? Explain.

- **6.** Under what conditions are the following expressions valid?

- a.  $np = n_i^2$

- **b.**  $p + N_D = n + N_A$ .

- 7. A piece of silicon is doped with  $7 \times 10^{15}$  boron atoms/cm<sup>3</sup> and  $3 \times 10^{15}$  phosphorous atoms/cm<sup>3</sup>. Find the electron and hole concentrations at 27°C.

- 8. Given a silicon sample 1 cm on a side at 27°C, find the resistance between any two faces.

## Wafer Preparation I

The silicon used in the fabrication of semiconductor devices is very pure and is in the shape of flat, circular wafers. Each wafer of silicon is a single crystal. The preparation of these wafers prior to the actual fabrication sequence that produces electrical devices is a complex procedure that is a story in itself.

Silicon is a very abundant material on the Earth's surface. However, it is found in the form of compounds, and must be separated from other elements before it can be used. Sand available in many locations is silicon dioxide (SiO<sub>2</sub>) containing less than 1% impurities. This sand is used as the starting point for the manufacture of silicon wafers. The following steps are followed in the production of ultrapure silicon for semiconductor devices.

Step 1. Silicon dioxide (sand) is mixed with carbon and reacted to form silicon (99% pure) and carbon dioxide.

$$SiO_2 + C \rightarrow Si + CO_2 \uparrow$$

(3-1)

This reaction produces both silicon and a gaseous byproduct that is easily exhausted. The silicon following this reaction is 99% pure; far from the quality of silicon required by contemporary technology. Further steps are necessary to remove additional unwanted impurities. **Step 2.** Silicon is reacted with hydrogen chloride to form trichlorosilane.

$$Si + 3HCl \rightarrow SiHCl_3 + H_2 \uparrow$$

(3-2)

The production of trichlorosilane leaves behind the unwanted impurities, in many cases yielding a chemical with sufficient purity for semiconductor devices. If higher purity is desired, the trichlorosilane may be distilled.

**Step 3.** The trichlorosilane is decomposed using electric current in a chamber with a controlled atmosphere, producing rods of ultrapure polycrystalline silicon.

$$SiHCl_3 + H_2 \rightarrow Si + 3HCl$$

(3-3)

The polycrystalline silicon (silicon containing many crystals) is now ready for the crystal-growing process.

#### 3-1 SILICON CRYSTAL GROWTH

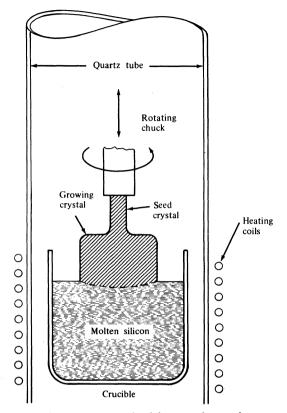

Two methods are presently used to grow single-crystal silicon. These two methods are called Czochralski and float zone crystal growth, respectively. (These two crystal growth methods are often abbreviated as CZ and FZ). Czochralski crystal growth utilizes a crucible in which pieces of polycrystalline silicon have been heated to their melting point of 1415°C (Figure 3-1). The crucible containing the silicon is made of quartz (SiO<sub>2</sub>) and is heated by either induction (RF) or thermal resistance methods. The crucible rotates during the growth process to prevent the formation of local hot or cold regions. The atmosphere around the crystal-growing apparatus or crystal puller is controlled to prevent contamination of the molten silicon. Argon is often used as the ambient gas. When the temperature of the silicon has stabilized, an arm with a piece of silicon mounted on the end is slowly lowered until it comes into contact with the surface of the molten silicon. This piece of silicon is called the seed crystal, and is the starting point for the subsequent growth of a much larger crystal. As the bottom of the seed crystal begins to melt in the molten silicon, the downward motion of the rod holding the silicon is reversed. As the seed crystal is slowly withdrawn from the melt, the molten silicon adhering to the crystal freezes or solidifies, taking on the crystal structure of the seed crystal. The rod continues its upward movement, forming an even larger crystal. The

Figure 3-1 Czochralski crystal growth.

crystal growth terminates when the silicon in the crucible is depleted. By carefully controlling the temperature of the crucible and the rotation speeds of the crucible and the rod, precise control of the diameter of the crystal is maintained. The desired impurity concentration is obtained by adding the impurities to the melt in the form of heavily doped silicon prior to crystal growth.

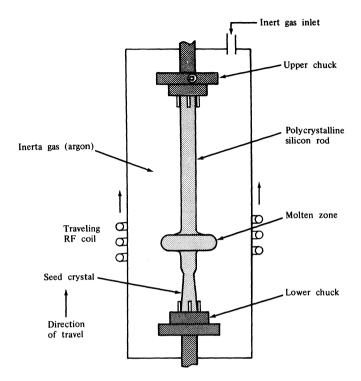

Float zone crystal growth proceeds directly from the rod of polycrystalline silicon previously obtained. A rod of silicon of the appropriate diameter is held at the top and placed in the crystal-growth chamber. A single seed crystal is clamped beneath, in contact with the other end of the polycrystalline rod (Figure 3-2). The rod is enclosed in a chamber with a controlled atmosphere and an induction heating coil is placed around it. The coil melts a small length of the rod starting with part of the single seed crystal. The molten zone is then slowly moved upward along the length of the rod by moving the coil upward.

Figure 3-2 Float zone crystal growth.

The molten region that freezes first is in contact with the single seed crystal. This region assumes the crystal structure of the seed. As the molten zone proceeds along the length of the rod, the polycrystalline rod melts and then freezes, becoming a single crystal rod of silicon. The diameter of the crystal is controlled by the motion of the heating coil. The desired impurity level is obtained by starting with polycrystalline silicon doped to the appropriate level.

The single crystal grown by either the Czochralski or the float zone technique is now ready to be sliced into wafers.

#### 3-2 WAFER ORIENTATION, SAWING, AND POLISHING

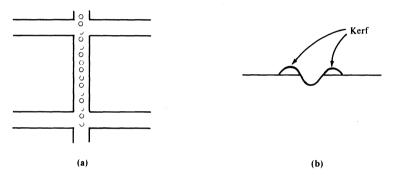

The silicon crystals are first ground perfectly round (if necessary), and the rotational orientation of the crystal is ascertained. The seed crystal has determined which crystal face will be present on the wafer surface, but the rotational position of the rod determines other axes of the crystal. Since the bar of silicon is one crystal, it has preferential break or cleavage planes. It is critical for later device separation to align the circuits precisely with respect to their cleavage planes. This precise alignment is accomplished by grinding a flat along the crystal (prior to sawing) that is used as a reference during all subsequent processing steps. X-ray diffraction provides a fast and accurate method of determining the crystal orientation prior to grinding the flat.

The silicon crystal is then sawed into thin slices called wafers. Extreme care is taken to minimize the amount of the single crystal silicon that is lost in the sawing process by using the inside diameter of a ring-shaped saw blade. The blade is coated with diamond powder to enable it to cut through the hard silicon. The sawing process leaves wafers with saw marks on both sides that must be removed. A silicon etchant is used to remove the saw marks and any accompanying damage from both sides of the wafer.

Care must be taken to remove any crystal damage introduced by the sawing operations, or the damage may prevent the successful fabrication of devices. The wafers are next mounted on large circular polishing plates using either wax or a vacuum to hold them. The polishing plates are mounted on a polisher, and one side of the wafer receives a mirrorlike finish. The polishing operation uses a polishing solution that simultaneously chemically etches and mechanically polishes the wafers. The polishing pad must be tough and durable. When the wafers have reached the proper thickness range and surface quality, the polishing plates are removed and the wafers are dismounted. The wafers are thoroughly cleaned to remove any residual contamination, and inspected to insure that wafers with imperfect surfaces are not shipped. Wafers that pass the final inspection are ready to start on their journey to become devices.

#### REVIEW EXERCISES: WAFER PREPARATION I

- 1. Why is it desirable to end up with a solid and a gas—or a liquid and a gas—following a chemical reaction?

- 2. a. What contaminant may CZ silicon contain that FZ silicon may not contain?

- **b.** Where does this contaminant come from?

- 3. Does silicon or silicon dioxide have a higher melting point? Why?

- 4. a. Why is the crystal orientation of a wafer important?

- **b.** How is the orientation denoted?

- Define the term polysilicon. 5.

- 6. What is the purpose of the argon gas during crystal growth?

- 7. Why is a seed crystal used for crystal growth?

- What two variables are used to control the diameter of the silicon 8. rod?

# Wafer Preparation II

#### 4-1 CRYSTAL ORIENTATION

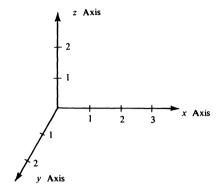

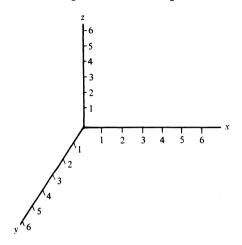

The orientation of a silicon crystal is an important parameter in the device fabrication sequence. One method used to describe the orientation of crystals is through the use of Miller indices. The Miller indices of a plane of silicon are determined by the point at which the plane intersects the x, y, and z axes, as shown in Figure 4-1. To determine the Miller indices of a plane from the points of intersection, the following procedure is used:

$$x \text{ index} = \frac{1}{x \text{ point of intersection}}$$

(4-1)

$$y \text{ index} = \frac{1}{y \text{ point of intersection}}$$

(4-2)

$$z \text{ index} = \frac{1}{z \text{ point of intersection}}$$

(4-3)

If we consider the plane intersecting the set of axes in Figure 4-1, we can determine the Miller indices of the plane. This plane intersects the axes at x = 1, y = 1, and z = 1; the Miller indices are:

$$x \text{ index} = \frac{1}{x \text{ point of intersection}} = \frac{1}{1} = 1$$

Figure 4-1 The crystal axis set.

y index =

$$\frac{1}{y \text{ point of intersection}} = \frac{1}{1} = 1$$

z index =  $\frac{1}{z \text{ point of intersection}} = \frac{1}{1} = 1$

This plane is a  $\langle 111 \rangle$  plane of the crystal. Other planes parallel to this one are also <111> planes. The <111> planes intersect the crystal axes so that a triangle is formed by their intersection. Crystals that are cut in the <111> plane can be recognized by the triangular pits that will etch in their surface, or the triangular pieces of silicon that result when the wafers are dropped.

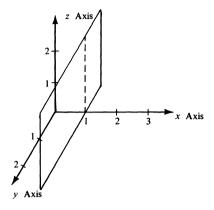

If we consider the same set of indices, and take a plane that intersects the x axis at x = 1, but never intersects the y or z axes, as shown in Figure 4-2, the Miller indices of the plane are found as follows:

$$x \text{ index} = \frac{1}{x \text{ point of intersection}} = \frac{1}{1} = 1$$

$$y \text{ index} = \frac{1}{y \text{ point of intersection}} = \frac{1}{\infty} = 0$$

$$z \text{ index} = \frac{1}{z \text{ point of intersection}} = \frac{1}{\infty} = 0$$

(For mathematical reasons, a plane that does not intersect an axis is considered to intersect the axis at infinity  $(\infty)$ .)

Figure 4-2 A < 100 > crystal plane.

Thus this is the <100> plane. The <100> plane intersects the crystal axes so that rectangles are formed, therefore <100> crystals form etch pits with square corners, and a <100> wafer will break into rectangular pieces of silicon if it is shattered.

Silicon with either a <111> or <100> crystal orientation is used for almost all device fabrication. These two orientations satisfy almost all requirements, so use of other orientations is generally not required.

#### 4-2 DOPING OF CRYSTALS DURING GROWTH

Following the growth of crystals using either the float zone or the Czochralski method, the concentration of dopant along the crystal depends on both the material used as dopant, and on its original concentration. A term called the "distribution coefficient", k, determines the ratio of the concentration of the dopant in the solid to the concentration of dopant in the liquid.

$$k = \frac{C_s}{C_l} = \frac{\text{Concentration of dopant in the solid phase}}{\text{Concentration of dopant in the liquid phase}}$$

(4-4)

The distribution coefficient of various n-type and p-type dopants is given in Table 4-1.

In Czochralski crystal growth, the gradual freezing of the crystal produces an ever-increasing concentration of dopant in the melt, since the ratio of the concentration of dopant in the solid to that of the

p-type

p-type

p-type

| Dopant          | Distribution<br>Coefficient k | Type of<br>Dopant |

|-----------------|-------------------------------|-------------------|

| Phosphorous (P) | .32                           | n-type            |

| Arsenic (As)    | .27                           | n-type            |

| Antimony (Sb)   | .02                           | <i>n</i> -type    |

| Boron           | .72                           | p-type            |

$1.8 \times 10^{-3}$

$9.2 \times 10^{-3}$

$3.6 \times 10^{-4}$

(B) Aluminum

(Al) Gallium

(Ga) Indium

(In)

TABLE 4-1: Distribution Coefficients for Common Dopants in Silicon

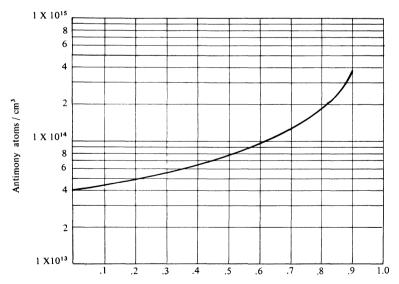

liquid is less than one. A typical graph of the concentration as a function of distance along the crystal for k = .04 is shown in Figure 4-3.

**Figure 4-3** The dopant concentration along a Czochralski crystal for an initial dopant concentration of  $10^{15}$  antimony atoms/cm<sup>3</sup> (k=.04).

#### 30 Wafer Preparation II

The situation is slightly different in float-zone silicon, but the impurities are swept along in the molten zone as it proceeds from one end of the crystal to the other, resulting in a similar distribution of impurities.

#### 4-3 CRYSTAL DEFECTS

A variety of crystal defects can be present in grown ingots of silicon and other semiconductors. These defects may impact the ability to successfully process wafers from these crystals, or the yield on devices made with these wafers. Two types of defect often encountered are:

- 1. Crystal dislocation. These are localized imperfections in the crystal structure caused by plastic deformation from uneven heating or cooling, or other problems.

- **2.** Planar slip. A type of plastic deformation visible because one part of the crystal bar sheared with respect to another.

Both of these common defects, as well as other less common problems can be decorated using a preferential etch. Such an etch attacks silicon along defect boundaries, revealing the nature and extent of the defect.

Crystal defects have been essentially eliminated from silicon grown by using either the float zone or the Czochralski method. However, defects are often inadvertently introduced during subsequent processing, so their study is of continuing importance. Dislocations, slip, and other defects are usually introduced if wafers are improperly heated or cooled during any of the high-temperature processing steps.

#### REVIEW EXERCISES: WAFER PREPARATION II

- 1. a. Determine the Miller indices of a plane intersecting a set of axes at  $x = \frac{1}{2}, y = 1, z = \infty.$

- b. Sketch the plane in the axes provided.

- 2. What value of k will result in a flat profile for the dopant?

- What p-type dopant of Table 4-1 will yield the flattest impurity 3. profile during crystal growth?

- What are the two most common crystal orientations utilized for 4. silicon processing?

- 5. Describe two types of crystal defects found in wafers cut from grown ingots of silicon.

# Epitaxial Deposition I

#### 5-1 INTRODUCTION

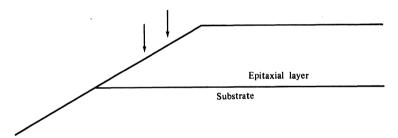

Epitaxial deposition is the deposition of a single crystal layer on a substrate (often, but not always, of the same composition as the deposited layer), such that the crystal structure of the layer is an extension of the crystal structure of the substrate. One use of epitaxial deposition in semiconductor processing is in the fabrication of light-emitting diodes. The carefully tailored materials and doping profile that result in the generation of light are usually obtained by using epitaxial techniques in conjunction with high-temperature diffusions. A more frequent use of epitaxial deposition is in the production of discrete devices and bipolar integrated circuits using silicon.

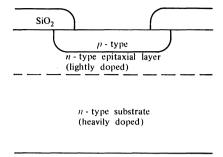

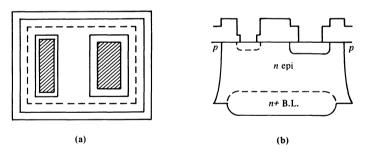

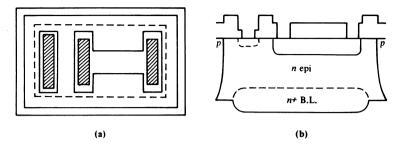

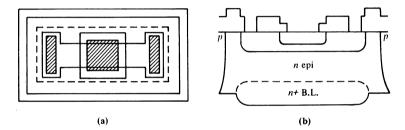

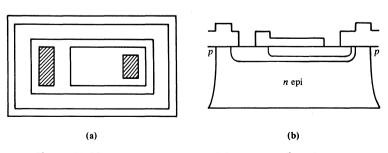

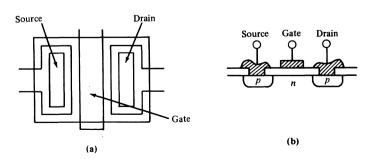

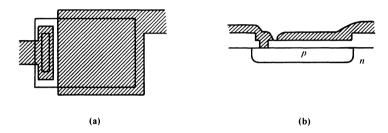

In the fabrication of silicon diodes and transistors, devices with higher switching speed, breakdown voltage, or current-handling capability can be obtained using epitaxial deposition. In diode fabrication, a heavily doped silicon substrate used as the starting material will result in low resistance to the flow of current. The high doping level results in a low reverse junction breakdown, though, so an epitaxial layer of lightly doped silicon of the same conductivity type is deposited on the substrate for the actual fabrication of the junction. The cross section of a typical diode fabricated in this manner is shown in Figure 5-1.

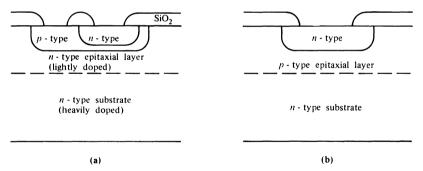

A transistor may be fabricated in an analogous manner, using an epitaxial layer for the lightly doped collector region, and diffusing in a base and an emitter. Figure 5-2a shows a transistor fabricated in this manner. The epitaxial layer may also be of the opposite conduc-

Figure 5-1 Cross section of a diode fabricated using epitaxial silicon.

tivity type, in which case the epitaxial layer serves as the base of the transistor and the emitter is added during a subsequent high-temperature diffusion. A cross section of a device fabricated in this manner is shown in Figure 5-2b.

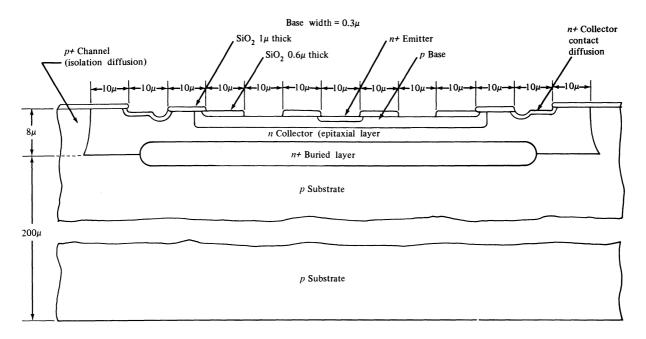

Figure 5-2 Cross sections of transistors fabricated using epitaxial silicon.

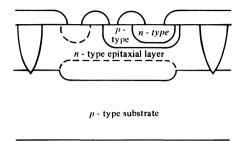

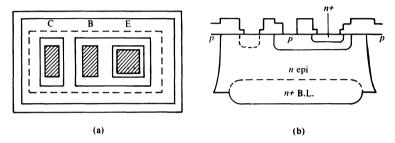

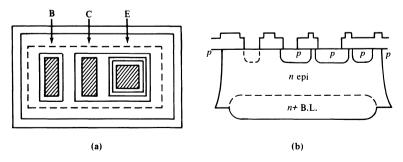

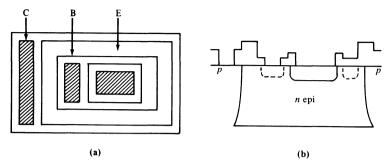

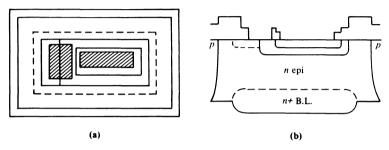

In the fabrication of bipolar integrated circuits, a lightly doped silicon substrate of one conductivity type is used as starting material, and a lightly doped epitaxial layer of the opposite conductivity type is deposited on it. (In most cases, a high concentration of the same type dopant used in the epitaxial layer is diffused into regions of the substrate prior to epitaxial deposition, to provide a low-resistance path to the active region of devices.) The substrate helps provide electrical isolation between devices in adjacent pockets when the circuit is in operation. A cross section of a transistor in a typical bipolar integrated circuit is shown in Figure 5-3.

Figure 5-3 Cross section of a bipolar integrated circuit.

#### 5-2 THEORY

#### Introduction

Two conditions must be met before epitaxial deposition can occur. First, there must be available sites for the depositing atoms to lose their extra energy and become part of the existing crystal structure. Such sites are called nucleation sites. The availability of suitable nucleation sites greatly influences both the speed with which film growth begins, and the steady-state film growth rate. Second, the atoms to be deposited must reach the substrate and find a lattice site to settle into. These two conditions are separated below to facilitate discussion, but in reality the arrival of atoms at a surface and the availability of nucleation sites cannot be separated. (For the remainder of Chapters 5 and 6, the epitaxial deposition of silicon will be discussed.)

#### **Preparation of Nucleation Sites**

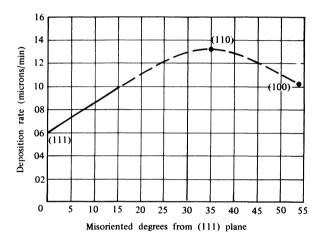

Nucleation sites may be prepared prior to placing the substrates in an epitaxial reactor, or may be induced once substrates are in the reactor. In either case, the success with which nucleation sites are prepared is a strong function of the crystal orientation of the substrate. In almost all silicon epitaxial growth, the substrate is 3°-7° off a major axis to allow the easy preparation of nucleation sites by exposing the edges of successive layers of the crystal. Figure 5-4 shows the successive layers of the crystal which are exposed as a result of the substrate crystal orientation being 3° to 7° off a major axis. Figure 5-5 shows the effect of substrate orientation on the deposition rate of silicon.

The use of an etching technique to increase the number of nucleation sites prior to placing the substrate in the reactor must of

Figure 5-4 The effect of substrate misorientation on the exposure of nucleation sites.

Figure 5-5 Substrate misorientation vs. deposition rate.

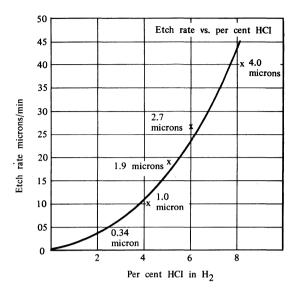

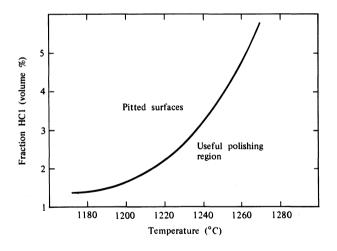

necessity use a silicon etchant. Mixtures of hydrofluoric and nitric acid are common silicon etches, and have been used for this purpose. However, the most widely used method of obtaining suitable nucleation sites is to introduce HCl gas just prior to the beginning of actual epitaxial deposition. The HCl etches the top layer of silicon from the substrate, thus removing any crystal defects that may be present at the surface of the wafer. Removal of this layer leaves a surface ready for a subsequent deposition. The etch rate of silicon as a function of HCl concentration in a horizontal reactor is shown in Figure 5-6. The etch rate of silicon is nearly linear for HCl concentrations of 1–4% in hydrogen, so percentages in this range are often used for etching. However, if the fraction of HCl is too high, a pitted substrate surface results. The maximum allowable fraction of HCl in hydrogen at any temperature is shown in Figure 5-7. A total thickness of .25 to 1.0 microns is usually removed from the substrate prior to actual deposition.

### 36 Epitaxial Deposition I

Figure 5-6 Etch rate vs. HCl concentration in hydrogen in a horizontal reactor.

Figure 5-7 Allowable fraction of HCl in H<sub>2</sub> vs. temperature.

#### **Deposition**

Vacuum Deposition Under carefully controlled conditions, it has been possible to obtain epitaxial silicon using sputtering or evapora-

tion techniques. However, the low deposition rates and the difficulty of obtaining a high quality crystal structure have prevented these techniques from being used commercially.

**Vapor Growth** Epitaxial silicon has been successfully deposited from silicon tetrachloride (SiCl<sub>4</sub>), Silane (SiH<sub>4</sub>), trichlorosilane (SiHCl<sub>3</sub>), dichlorosilane (SiH<sub>2</sub>Cl<sub>2</sub>), and other compounds. However, since the first two reactants are used for most industrial epitaxial deposition, only their behavior will be covered in this text.

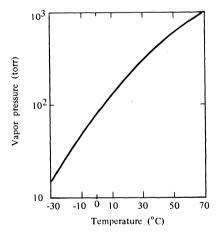

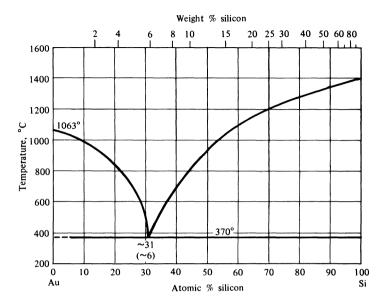

Hydrogen Reduction of Silicon Tetrachloride Silicon tetrachloride is commercially available with sufficient purity to provide the lightly doped epitaxial layers needed for device fabrication. It is kept in a carefully controlled constant-temperature bath at temperatures near 0°C in a liquid state. Hydrogen flows through or over the SiCl<sub>4</sub> to obtain the silicon tetrachloride necessary for deposition. The concentration of SiCl<sub>4</sub> in the hydrogen is determined by its flow rate and the temperature of the constant-temperature bath. The effect of temperature on the vapor pressure of SiCl<sub>4</sub> is shown in Figure 5-8.

Figure 5-8 Vapor pressure of SiCl<sub>4</sub> vs. temperature.

Deposition temperatures of 1150°-1300°C are normally used with SiCl<sub>4</sub> to obtain a good single crystal layer. This relatively high temperature may cause significant additional diffusion of already present doped regions if care is not taken. The reaction commonly recognized as the one resulting in epitaxial growth is

$$SiCl_4(g) + 2H_2(g) \rightarrow Si(s) + 4HCl(g).$$

(5-1)

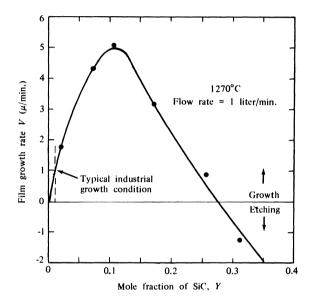

However, if excessive SiCl<sub>4</sub> is introduced, a competing reaction removes silicon from the substrate:

$$Si(s) + SiCl_4(g) \rightarrow 2SiCl_2(g)$$

(5-2)

The net result of these reactions is shown in Figure 5-9.

Figure 5-9 Growth rate of silicon vs. mole fraction of SiCl<sub>4</sub>.

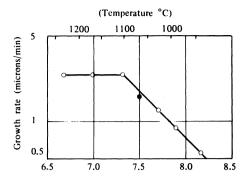

Pyrolysis of Silane Silane is a gas that spontaneously ignites when it comes in contact with air, but is often stored in tanks diluted by hydrogen. The silane or silane/hydrogen mixtures are injected directly into the reactor where the following reaction takes place:

$$SiH_4(g) \rightarrow Si(s) + 2H_2(g)$$

(5-3)

The growth rate as a function of temperature for this reaction is shown in Figure 5-10. Deposition of epitaxial silicon using silane is usually performed in the 1000°-1100°C range. This deposition temperature range results in less diffusion of previously present heavily doped regions

Reciprocal absolure temperature

Figure 5-10 Growth rate of silicon vs. temperature for SiH<sub>4</sub>.

than the use of the higher deposition temperatures required for SiCl<sub>4</sub> deposition.

#### GROWTH OF AN EPITAXIAL LAYER

The deposition sequence normally followed in an epitaxial process is given below.

- 1. Substrate Clean. The substrates receive a solvent degreasing operation (which may include a physical scrubbing) followed by a series of acid cleaning steps (H<sub>2</sub>SO<sub>4</sub>, HNO<sub>3</sub>: HCl, and HF is a common sequence) and a drying operation. This clean is of great importance, since any residual particles may give rise to imperfections in the deposited layer.

- 2. Wafer Load. Following the completion of the cleaning sequence, extreme care must be taken to insure that the front side of the wafer is not subsequently touched. The use of vacuum wands on the backside of the wafers is the recommended procedure. Equal care must be taken to guarantee that the cleaned substrates never leave regions bathed with filtered air from laminar flow hoods. While placing the substrates on the wafer holder or susceptor, proper precautions will insure that no particles from the susceptor are transferred to the fronts of the substrates.

- 3. Heat-up. Once the epitaxial system has been sealed, a flow of nitrogen purges any residual gases from the system. Following the purge, the reactor heating system is turned on and heat-up begins. Until a temperature of approximately 500°C is reached, nitrogen may be used as the gas flowing through the system. However, since nitrogen begins to etch silicon at elevated temperatures, hydrogen is used to replace the nitrogen at higher temperatures.

- **4.** HCl Etch. Once the heat-up cycle is completed and the temperature has been verified using an optical pyrometer or other means, removal of a thin region of damaged silicon at the surface of the wafer using an HCl etch (as previously described) takes place. The amount of silicon removed is carefully controlled to guarantee that the characteristics of the devices being fabricated are not adversely affected.

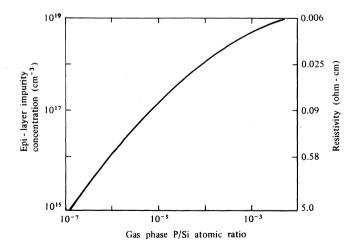

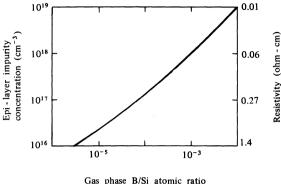

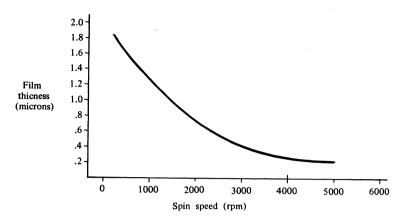

- **5.** Deposition. The deposition step results in an epitaxial layer with the desired thickness and resistivity. Thickness control is obtained by depositing the layer using growth conditions that minimize the error caused by the slight differences encountered in every run. The desired doping concentration is obtained by adding small concentrations of a dopant gas to the main gas flow. The epitaxial layer doping concentration as a function of the dopant to silicon ratio is shown for phosphorus and boron in Figures 5-11 and 5-12.

Figure 5-11 Phosphine in gas phase vs. phosphorus in epitaxial layer.

Gas phase B/Si atomic ratio

Figure 5-12 Diborane in gas phase vs. boron in epitaxial layer.

- 6. Cool-down. Following the completion of the growth phase of the process, the temperature is reduced while maintaining the hydrogen gas flow. At approximately 500°C, the gas is switched from hydrogen to nitrogen, and the remainder of the cool-down cycle is completed.

- 7. Unloading. The same degree of care must be taken in the unloading of the silicon wafers as was taken in their loading. The best procedure is to immediately oxidize these wafers to protect their surfaces from possible contamination.

### REVIEW EXERCISES: EPITAXIAL DEPOSITION I

- 1. Must an epitaxial layer be deposited on a substrate of the same composition?

- 2. Using Figure 5-5, determine the misalignment angle that will result in the highest deposition rate.

- 3. What is the maximum percentage of HCl that could be used at 1,250°C without resulting in a pitted surface?

- **4. a.** Determine the mole fraction of SiCl<sub>4</sub> resulting in a maximum film growth rate?

- b. Why isn't epitaxial silicon grown under these conditions?

- 5. What two conditions must be met before epitaxial deposition can occur?

- **6.** How are nucleation sites created in a silicon wafer?

#### 42 Epitaxial Deposition I

- 7. Describe two disadvantages of vacuum epitaxial deposition.

- **8.** Write the reaction equations and give a brief explanation for the two most widely industrial epitaxial deposition techniques.

- 9. Determine the thickness of the resulting epitaxial layer using silane at 1,050°C for 5 minutes.

#### REFERENCES

- 1. S. K. Tung, "The Effects of Substrate Orientation on Epitaxial Growth." J. Electrochem. Soc. 112 (April 1965), pp. 436-438.

- 2. K. E. Bean and P. S. Gleim, "Vapor Etching Prior to Epitaxial Deposition of Silicon." Paper presented at the Fall meeting of the ECS, 1963.

- 3. G. A. Lang and T. Stavish, "Chemical Polishing of Silicon with Anhydrous Hydrogen Chloride," R.C.A. Review 24 (December 1963), pp. 488-498.

- 4. K. J. Miller and N. J. Frieco, "Epitaxial P-type Germanium and Silicon Films by the Hydrogen Reduction of GeBr<sub>4</sub>, SiBr<sub>4</sub> and BBr<sub>3</sub>." J. Electrochem. Soc. 110 (December 1963), pp. 1252–1256.

- 5. H. C. Theuren, "Epitaxial Silicon Films by the Hydrogen Reduction of SiCl<sub>4</sub>." J. Electrochem. Soc. 108 (July 1961), pp. 649-653.

- 6. B. A. Joyce and R. R. Bradley, "Epitaxial Growth of Silicon from the Pyrolysis of Monosilane on Silicon Substrates," J. Electrochem. Soc. 110 (December 1963), pp. 1235–1240.

- 7. R. M. Warner, Jr., ed., Motorola, Inc. Semiconductor Products Division, *Integrated Circuits* (New York: McGraw-Hill), 1965.

# Epitaxial Deposition II

#### 6-1 INTRODUCTION

Equipment for epitaxial deposition must meet a severe set of requirements. Since silicon is deposited on substrates from the gaseous state, the reaction chamber must be free from leakage over an extended temperature range. This requirement is usually met by using a quartz reaction chamber. The flow of gases into the reaction chamber is controlled and monitored at all times. The wafers in the reaction chamber rest on a holder called a susceptor. In addition to supporting the wafers, the susceptor serves as the local source of heat if the reactor is heated using a radio frequency (RF) generator. Radio frequency (or induction) heated reactors work by inductively coupling an electromagnetic field into the susceptor. Susceptors usually have a graphite (carbon) body with a thin coating of silicon carbide over the outer surface. The silicon carbide coating prevents the contamination of device wafers with carbon. The wafers resting on the susceptor are heated because they are physically in contact with it. In an epitaxial process, the deposition proceeds most rapidly on the hottest surfaces in the chamber, which are the front surfaces of the wafers and the susceptor. Deposition on the cooler chamber walls proceeds at a considerably lower rate.

An alternate method of heating wafers for epitaxial deposition is to use ultraviolet energy. Special light bulbs that emit large amounts of ultraviolet radiation heat the substrates through a transparent quartz window. The ultraviolet radiation directly heats the wafers and the susceptor that supports them. The desired temperature is maintained using

### 44 Epitaxial Deposition II

a temperature sensor and a controller that corrects for deviations from a predetermined value.

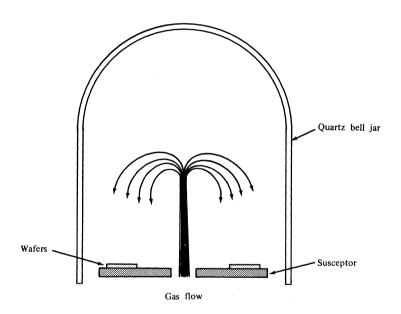

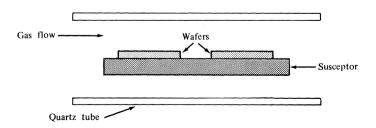

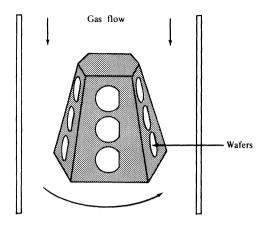

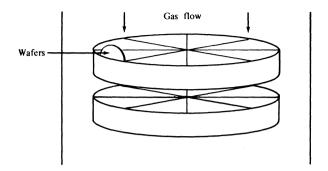

Three general configurations of epitaxial reactors are currently being used in industrial applications. These systems are known as:

| 1. Vertical systems           | (Figure 6-1) |

|-------------------------------|--------------|

| 2. Horizontal systems         | (Figure 6-2) |

| 3. Barrel or cylinder systems | (Figure 6-3) |

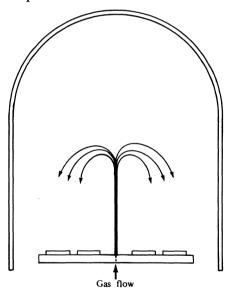

Figure 6-1 Vertical epitaxial reactor.

Figure 6-2 Horizontal epitaxial reactor.

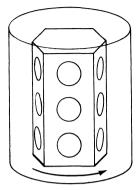

Figure 6-3 Barrel or cylinder reactor.

In a vertical epitaxial deposition system, the gases enter the chamber near the bottom and swirl in the chamber to react at the surface of the susceptor. The susceptor rotates, helping to maintain a uniform temperature on the susceptor and distributing the gases throughout the reaction chamber. The gases exhaust from the bottom of the chamber.

In a horizontal system, the gases enter the chamber at one end and are exhausted at the other. Care is taken to guarantee that the required temperature profile is maintained. The susceptor is often inclined a few degrees to produce a gas-flow profile that introduces an unused gas stream at every position on the susceptor as shown in Figure 6-2.

A barrel system combines features of both the horizontal and the vertical reactor. In a barrel system, wafers are placed on the faces of a rotating susceptor. Each face of the susceptor is thus the equivalent of one susceptor in a horizontal system. The main advantage this configuration offers is the ability to deposit epitaxy on a large number of wafers simultaneously.

A fourth type of reactor is in design, though additional work is necessary to make it commercially available. This type of reactor has been called a carousel, since wafers are held in a carousel-like wafer holder (Figure 6-4 page 46).

#### 6-2 EVALUATION OF EPITAXIAL LAYERS

The three important parameters in epitaxial deposition are:

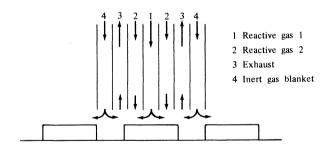

Figure 6-4 The gases pass through the tiers of rotating carousels.

- 1. The thickness of the deposited layer, and its variation across the wafer and the run.

- **2.** The concentration of desired impurities and its variation across the wafer and the run.

- **3.** The density and distribution of crystal defects in the deposited layer.

All of these parameters must be within certain bounds for the epitaxial layer to successfully perform its intended purpose.

Epitaxial layer thickness can be measured in a number of ways. Three of these ways are outlined below.

1. Angle lap and stain (or groove and stain). The epitaxial layer is deposited on a substrate of the opposite conductivity type (p on n or n on p). This epi-layer is then grooved or polished beyond its boundary with the substrate. A staining solution is applied to the exposed junction to delineate the junction by darkening either the p-type or the n-type surface. Monochromatic light is then used with a glass cover to generate interference fringes which determine the junction depth. The junction depth is related to the number of fringes by the formula:

$$d=\frac{n\,\lambda}{2}$$

where  $\lambda$  = the wavelength of the monochromatic light

n = the number of interference fringes

d =the junction depth

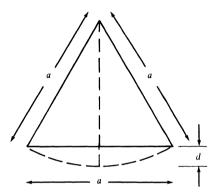

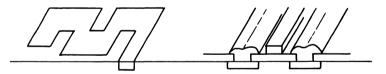

2. Etch pit depth. The presence of defects at the interface between the substrate and the epitaxial layer generates defects that propagate to the surface of the wafer along the crystal planes. A preferential etch is used to delineate the etch pits. The thickness of the epitaxial layer is geometrically related to the length of the sides of the exposed etch pits. For <111> silicon shown in Figure 6-5, d=.816 a.

Figure 6-5 Etch pit determination of epitaxial layer thickness.

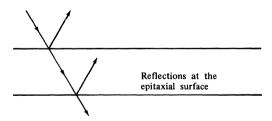

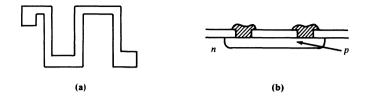

3. Infrared interference. The boundary between the substrate and the epitaxial layer represents an interface that reflects light rays of the correct length. By determining the wavelength of light that produces certain interference responses, the thickness can be determined as shown in Figure 6-6.

Figure 6-6 Use of infrared interference to determine epitaxial layer thickness.

The impurity concentration can be determined using various techniques. Unfortunately, they are all rather time-consuming and tedious.

- 1. Sectioning. The layers of silicon are removed from the surface of the wafer using anodic oxidation or etching, and the sheet resistance of the newly exposed surface is determined. This data can be mathematically manipulated to give the impurity concentration.

- 2. Reverse bias C-V technique. A layer of metal is deposited on the surface of the layer to form a Schottky barrier diode. This diode is reverse biased, and the capacitance as a function of reverse-biased voltage (C-V) is determined. This information is then mathematically manipulated to give the impurity concentration.

- **3.** Lap and spreading probe. The profile to be measured is exposed using a lapping technique, and a fine probe is used to determine the resistivity of the material at positions along the exposed surface of the profile as shown in Figure 6-7.

**Figure 6-7** Lap and spreading probe technique for determining impurity concentration.

In a fashion similar to that described above, the data are reduced, resulting in a plot of the dopant profile as a function of depth into the wafer.

The quality of the epitaxial layer is measured using an etch technique that preferentially exposes defects in the crystal structure. The number, location, and kind of defect determines the crystal quality of the epitaxial layer, as was discussed in Chapters 3 and 4.

## REVIEW EXERCISES: EPITAXIAL DEPOSITION II

- 1. Name and discuss two methods of heating wafers in an epitaxial reactor.

- **2.** Why is epitaxial deposition done using a cold-wall reactor?

- 3. What are three important parameters in epitaxial deposition?

- 4. The wavelength of light used to determine a junction depth is  $.3\mu$ . If 8 fringes are present, what is the epitaxial layer thickness?

- 5. List and describe two methods of determining the thickness of an epitaxial layer.

- 6. Determine the thickness for (111) silicon of an epitaxial layer in which the sides of the etch pits are 1.838  $\mu$ m.

# Oxidation I

#### 7-1 INTRODUCTION

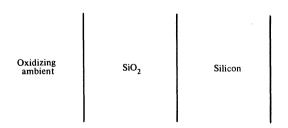

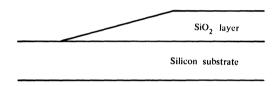

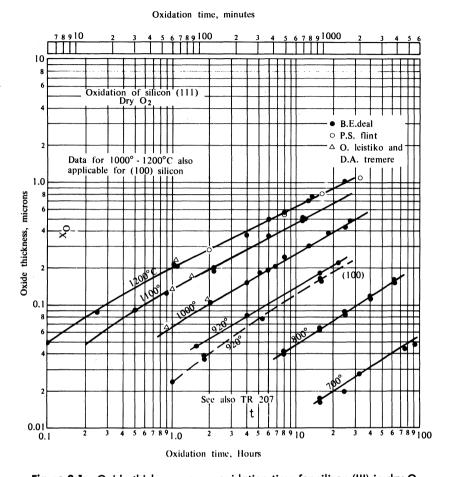

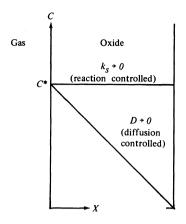

The ability to grow a chemically stable protective layer of silicon dioxide ( $SiO_2$ ) on silicon, makes silicon the most widely used semiconductor. This protective layer is grown in atmospheres containing either oxygen ( $O_2$ ) or water vapor ( $H_2O$ ) at temperatures in the range of  $900^\circ-1300^\circ C$ . The process of oxidation can be investigated by considering a surface of silicon with an already existing layer of silicon dioxide on it. (Figure 7-1).

Figure 7-1 Silicon with a layer of silicon dioxide on its surface.

Except for the first few moments, a silicon slice will nearly always have a SiO<sub>2</sub> layer on it, so this assumption is a valid one. Oxida-

tion takes place when either oxygen or water vapor reacts with the silicon as shown in the chemical equations,

$$Si + O_2 \rightarrow SiO_2 \tag{7-1}$$

$$Si + 2H_2O \rightarrow SiO_2 + 2H_2 \tag{7-2}$$

For the silicon and the oxidizing species to react, one of the following must take place:

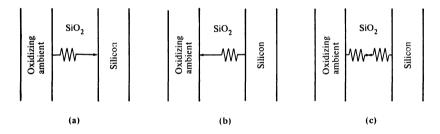

- 1. The oxidizing species must diffuse through the layer of SiO<sub>2</sub> to reach the silicon-SiO<sub>2</sub> interface where the reaction takes place (Figure 7-2a).

- 2. The silicon must diffuse through the layer of SiO<sub>2</sub> to the interface between the silicon dioxide layer and the oxidizing atmosphere where the reaction takes place (Figure 7-2b).

- 3. The two active species meet somewhere in the SiO<sub>2</sub> layer where the reaction takes place (Figure 7-2c).

Figure 7-2 Potential reaction mechanisms in the oxidation of silicon; (a) oxidizing species diffuses through the SiO<sub>2</sub> layer interface; (b) silicon diffuses through the SiO<sub>2</sub> surface; (c) the oxidizing species and the silicon meet in the SiO, layer.

Experiments have disclosed that in the thermal oxidation of silicon, the first process, the diffusion of the oxidizing species (either  $O_2$  or  $H_2O$ ) through the existing layer of  $SiO_2$ , occurs.

The assumption is that we can oxidize through the SiO<sub>2</sub> layer on the surface of the silicon slice. It is necessary to make this assumption since virtually all silicon wafers, once created, will always have a surface layer of SiO<sub>2</sub>.

Experiments verify that we can oxidize through this initial thin layer to create thicker oxides and partially consume the silicon.

#### 7-2 EQUIPMENT FOR THERMAL OXIDATION

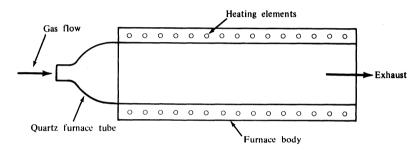

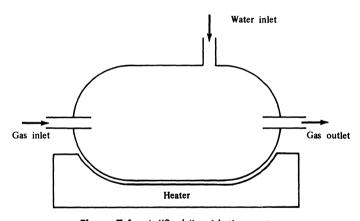

Thermal oxidations are performed in furnaces in which the temperature is carefully controlled (limits of  $\pm \frac{1}{2}$  °C are typical). Furnaces generally contain three or four sets of coils, each with its own set of controls and quartzware. The coils are heated electrically, and the current is adjusted and controlled to provide the required constant temperature. A quartz tube (or occasionally a tube made from another material such as silicon or silicon carbide) rests inside the coils, providing an envelope around the wafers in which the atmosphere can be controlled. A cross section of a typical oxidation furnace is shown in Figure 7-3.

Figure 7-3 Cross section of an oxidation furnace.

#### 7-3 THE OXIDATION PROCESS

The thermal oxidation of silicon must be preceded by a cleaning sequence designed to remove all contamination. Particular care must be taken during this handling to guarantee that the wafers do not contact any source of contamination, particularly inadvertent contact with a person. (Humans are a potential source of sodium, the element most often responsible for the failure of devices due to surface leakage.) The cleaned wafers are dried, loaded into a quartz water holder called a "boat," and are ready for oxidation.

Thermal oxidation using dry oxygen involves controlling the flow of oxygen into the quartz tube to guarantee that an excess of oxygen is available for the silicon. A source of high-purity oxygen makes sure that no unwanted impurities become incorporated in the layer of oxide as it grows. Oxygen or an oxygen/nitrogen mixture is used for growing the layer of oxide. The use of nitrogen decreases the total cost of running the oxidation process, as it is less expensive than oxygen.

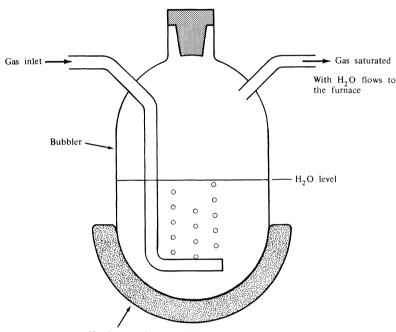

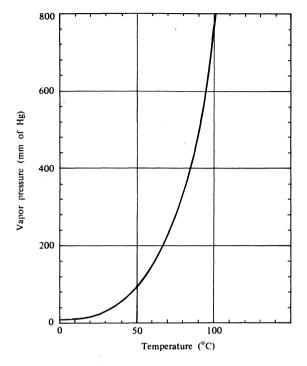

Three methods of introducing water vapor are commonly used when water is the oxidizing species. Water may be placed in a container called a "bubbler" and maintained at a constant temperature below its boiling point (100°C). A bubbler is shown in Figure 7-4 with a heating mantle that keeps it at a predetermined temperature.

Heating mantle to maintain constant temperature

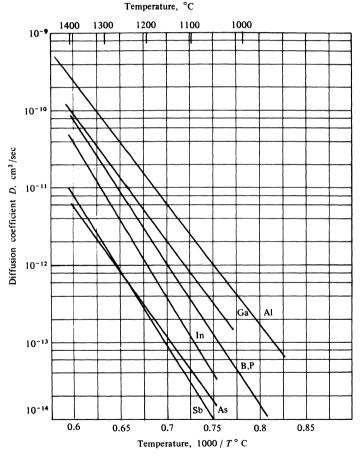

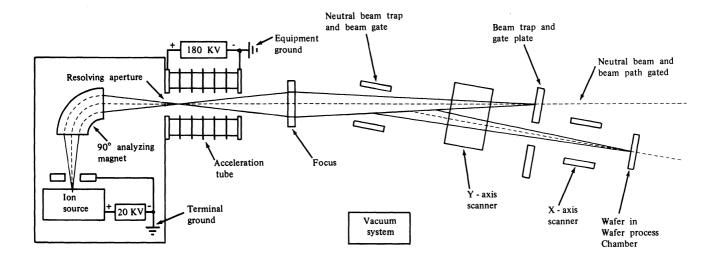

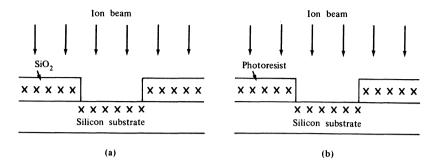

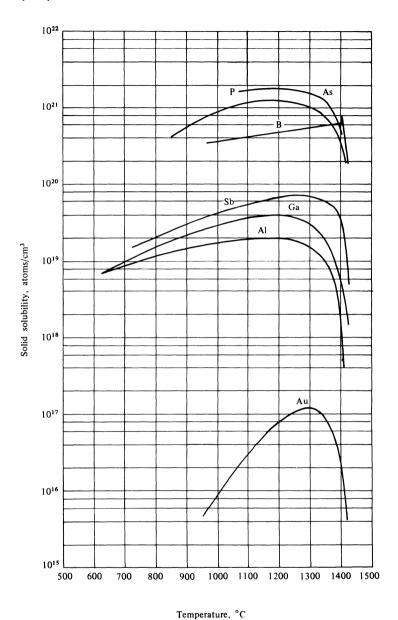

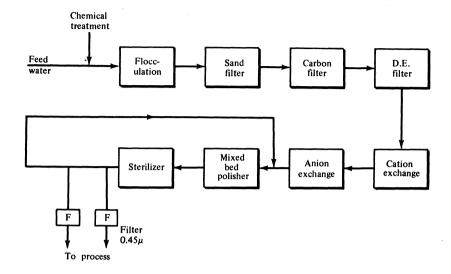

Figure 7-4 A bubbler for a wet oxidation system.