# ACQUISI G CONDUCTOR

1995

# CRYSTAL SEMICONDUCTOR DATA ACQUISITION DATABOOK

itt

A REAL PROPERTY AND A REAL

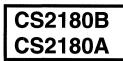

| CS2180A/B     | 4-15  |

|---------------|-------|

| CS3310        |       |

| CS4110/11     | 3-21  |

| CS4112        | 3-22  |

| CS4215        | 3-23  |

| CS4216        |       |

| CS4225        | 3-25  |

| CS4231A       | 3-26  |

| CS4232        | 3-27  |

| CS4248        | 3-29  |

| CS4303        |       |

| CS4328        |       |

| CS4329        | 3-10  |

| CS4330/1/3    | 3-11  |

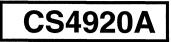

| CS4920A       | 3-19  |

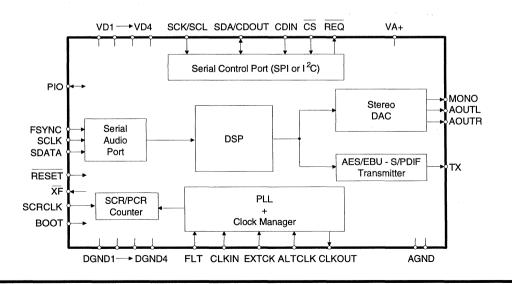

| CS4921        | 3-20  |

| CS5012A/14/16 | 2-7   |

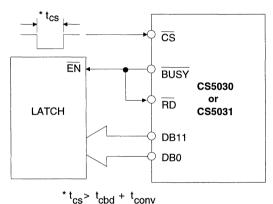

| CS5030/31     | 2-55  |

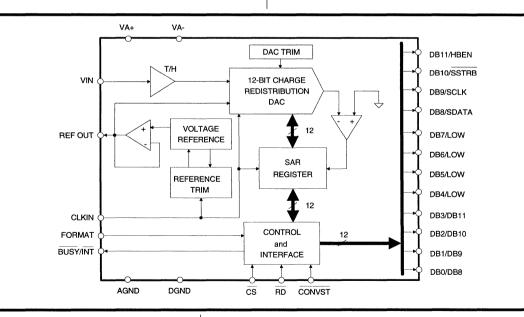

| CS5032        | 2-81  |

| CS5101A/2A    | 2-113 |

| CS5126        | 2-159 |

| CS5317        | 2-189 |

| CS5321        | 2-219 |

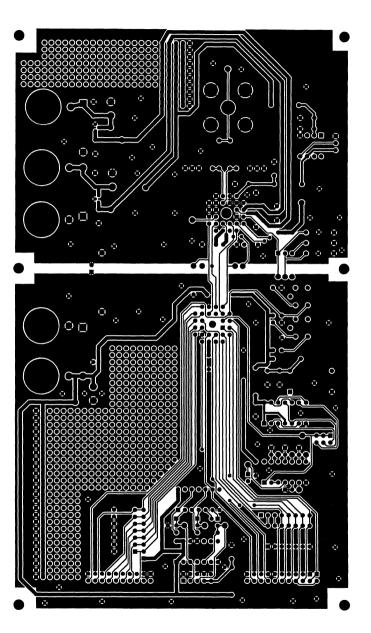

| CS5322/23     | 2-245 |

| CS5324        | 2-283 |

| CS5330        |       |

| CS5336/8/9    | 3-13  |

| CS5389        |       |

| CS5390        | 3-15  |

| CS5412        | 2-315 |

| CS5480        |       |

| CS5481        | 2-355 |

| CS5490        | 2-365 |

| CS5501/032-367    |

|-------------------|

| CS55042-421       |

| CS5505/6/7/82-451 |

| CS55092-489       |

| CS5516/202-519    |

| CS55422-559       |

| CS55432-561       |

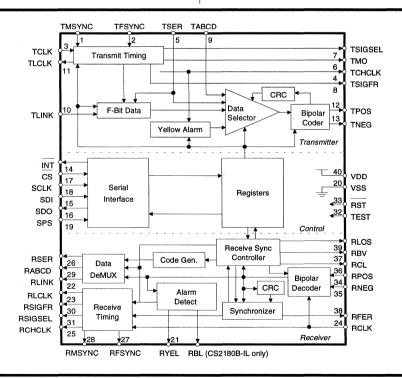

| CS61304A 4-16     |

| CS61305A 4-17     |

| CS61535/35A 4-18  |

| CS61574A/754-19   |

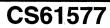

| CS61577           |

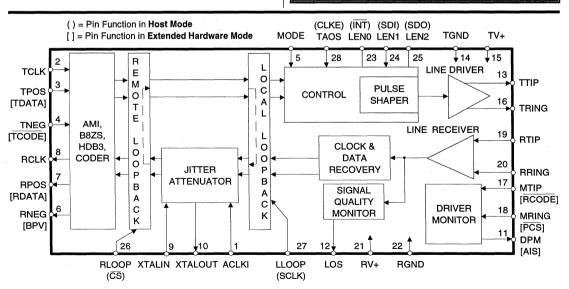

| CS61584           |

| CXT6176/81924-22  |

| CS64004-7         |

| CS64014-8         |

| CS64504-11        |

| CS6453            |

| CS7870/752-563    |

| CS81304-6         |

| CS83C92A/C 4-13   |

| CS8401A/2A3-16    |

| CS8411/12         |

| CS8425            |

| CS8900            |

| CS8905C 3-30      |

| CS92333-31        |

| CDBCAPTURE 2-597  |

| CWDRGNTT 3-36     |

| CWECAXB           |

| CWMNLG 3-37       |

| DIAGNOSTICS 3-35  |

| DRIVERS 3-34      |

|                   |

DADB9.0

## **Crystal Semiconductor Corporation**

## Data Acquisition Products Data Book

## March 1995

This publication neither states nor implies any warranty of any kind, including, but not limited to, implied warrants of merchantability or fitness for a particular application. Crystal assumes no responsibility for the use of any circuitry other than the circuitry in a Crystal product. No circuit patent licenses are implied.

The information in this publication is believed to be accurate in all respects at the time of publication but is subject to change without notice. Crystal assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Crystal assumes no responsibility for the functioning of undescribed features or parameters.

#### © Copyright 1995 Crystal Semiconductor Corporation. ALL RIGHTS RESERVED.

#### LIFE SUPPORT AND NUCLEAR POLICY

CRYSTAL SEMICONDUCTOR PRODUCTS ARE NOT AUTHORIZED FOR AND SHOULD NOT BE USED WITHIN LIFE SUP-PORT SYSTEMS OR NUCLEAR FACILITY APPLICATIONS WITHOUT THE SPECIFIC WRITTEN CONSENT OF CRYSTAL SEMICONDUCTOR.

Life Support Systems are equipment intended to support or sustain life and whose failure to perform when properly used in accordance with instructions provided can be reasonably expected to result in personal injury or death. Users contemplating applications of Crystal Semiconductor products in Life Support Systems are requested to contact Crystal Semiconductor factory headquarters to establish suitable terms and conditions for these applications. Crystal Semiconductor's warranty is limited to replacement of defective components and does not cover injury to persons or property or other consequential damages.

Examples of devices considered to be life support devices are neonatal oxygen analyzers, nerve stimulators (whether used for anesthesia, pain relief, or other purposes), autotransfusion devices, blood pumps, defibrillators, arrhythmia detectors and alarms, pacemakers, hemodialysis systems, peritoneal dialysis systems, neonatal ventilator incubators, ventilators for both adults and infants, anesthesia ventilators, and infusion pumps, as well as other devices designated as "critical" by the FDA. The above are examples only and are not intended to be conclusive or exclusive of any other life support device.

Examples of nuclear facility applications are applications in (a) a nuclear reactor, or (b) any device designed or used in connection with the handling, processing, packaging, preparation, utilization, fabricating, alloying, storing, or disposal of fissionable material or waste products thereof.

## TRADEMARKS

Crystal Semiconductor Corporation has made every effort to supply trademark information about company names, products, and services mentioned in this book. Trademarks indicated below are derived from various sources.

"C" (stylized) is a registered trademark of Crystal Semiconductor Corporation.

CRYSTAL, SMART *Analog*, Crystal Clear, and CrystalWare are trademarks of Crystal Semiconductor Corporation.

Other trademarks in this book belong to their respective companies.

## PATENTS

Products in this book may be covered by one or more of the following patents. Additional patents are pending.

#### <u>USA</u>

4,709,225; 4,746,899; 4,748,418; 4,804,863; 4,805,198; 4,849,662; 4,851,841; 4,918,454; 4,939,516; 4,941,156; 4,943,807; 4,988,954; 5,012,244; 5,039,989; 5,055,846; 5,061,925; 5,068,660; 5,079,550; 5,087,914; 5,088,107; 5,111,451; 5,117,200; 5,121,080; 5,140,279; 5,150,386; 5,157,395; 5,172,115; 5,187,390; 5,196,850; 5,198,782; 5,208,597; 5,212,659; 5,220,483; 5,239,210; 5,245,344; 5,247,210; 5,248,970; 5,257,026; 5,258,758; 5,268,651; 5,274,375; 5,319,319; 5,319,370; 5,339,067; 5,351,050; 5,376,936

#### **GERMANY**

P3642070.0; P3733682.7; P3736735.8; P3737279.3; P3933552.6; P4002871.2; P4200745.3; P4202180.4

#### **GREAT BRITAIN**

2184621; 2195848; 2198305; 2198306; 2223879; 2232547; 2247370; 2252459; 2252829; 2253754; 2253756; 2254504; 2261561

#### **FRANCE**

8617487; 8713769; 8715552; 8715553

#### **JAPAN**

1684670; 1736807; 1747931; 4-25778

## **GENERAL INFORMATION**

## DATA ACQUISITION

General Purpose Industrial Measurement Seismic High Speed

## **AUDIO PRODUCTS**

Consumer/Professional Broadcast Multimedia

## **COMMUNICATIONS PRODUCTS**

Infrared Transceiver Echo Cancellers Communications Codecs Ethernet/Cheapernet Telecom

## **APPLICATION NOTES**

## **APPENDICES**

Product Category Levels Reliability Calculation Methods Package Mechanical Drawings Standard Military Drawings

## SALES OFFICES

2

| 1. | GENERAL INFORMATION                                                                                                                                                                                                                        |   |   |   |       |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|-------|

|    | - Company Information and Part Numbering Convention                                                                                                                                                                                        |   |   | • | 1-3   |

|    | - Quality and Reliability Information                                                                                                                                                                                                      |   |   |   |       |

| 2. | DATA ACQUISITION PRODUCTS                                                                                                                                                                                                                  |   |   |   |       |

|    | - Introduction, Contents and User's Guide                                                                                                                                                                                                  |   |   |   | 2-1   |

|    | - CS5012A/4/6 16, 14, & 12-Bit, Self-Calibrating A/D Converters .                                                                                                                                                                          |   |   |   |       |

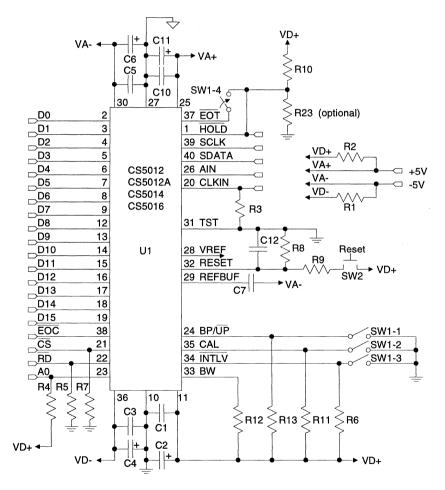

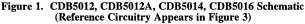

|    | - CDB5012A/4/6 Evaluation Board for CS5012A/4/6                                                                                                                                                                                            |   |   |   |       |

|    | NEW - CS5030/1 12-Bit, 500 kHz, Sampling A/D Converters                                                                                                                                                                                    |   |   |   |       |

|    | NEW - CS5032 12-Bit, 500 kHz, Sampling A/D Converters                                                                                                                                                                                      |   |   |   |       |

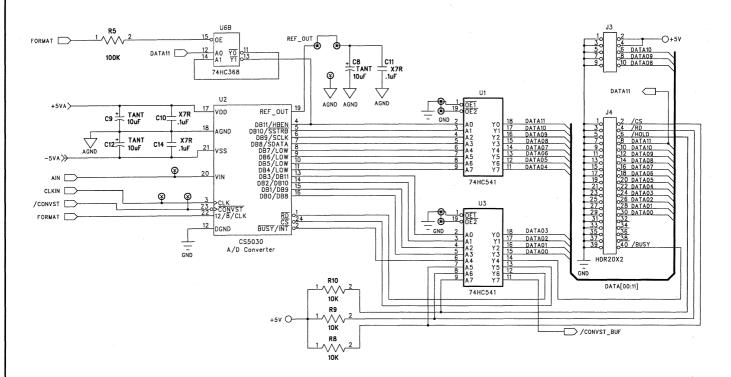

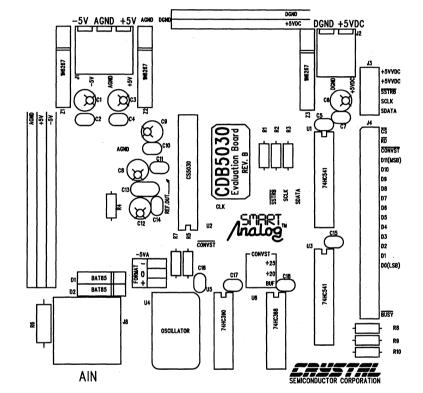

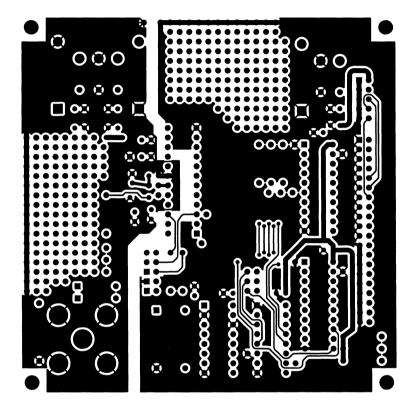

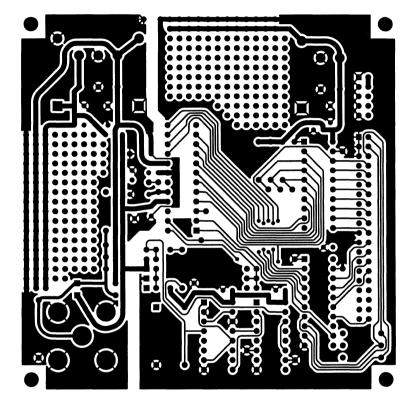

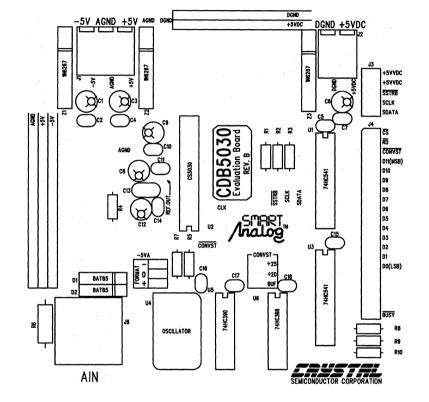

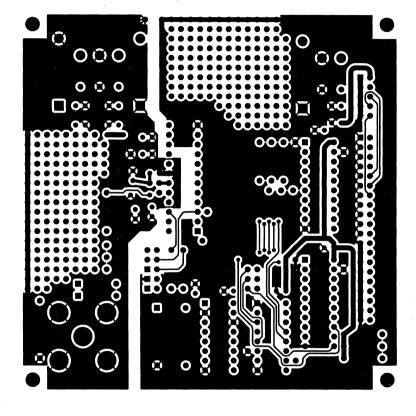

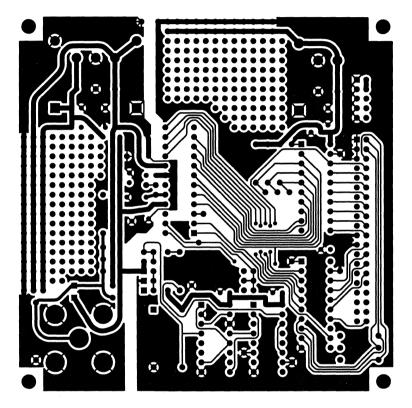

|    | - CDB5030/1/2 Evaluation Board for CS5030/1/2                                                                                                                                                                                              |   |   |   |       |

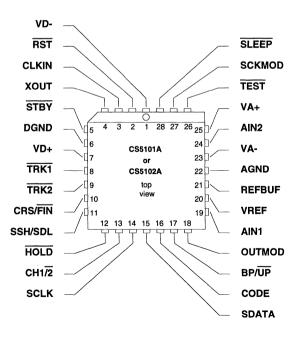

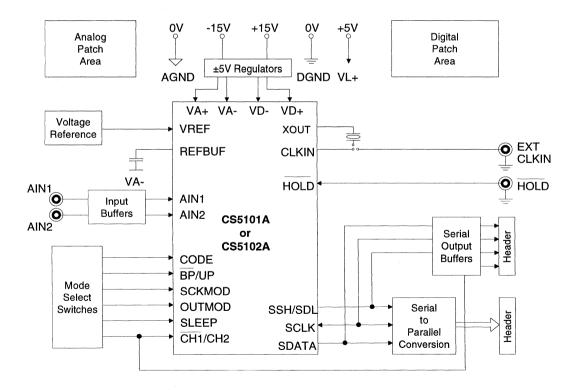

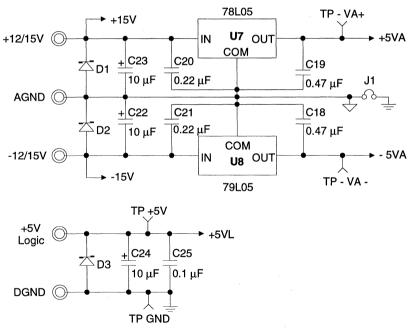

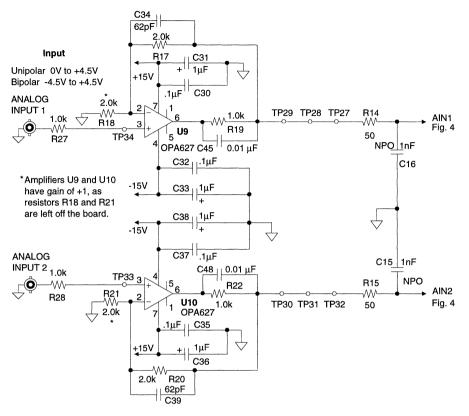

|    | - CS5101A/2A 16-Bit, 100 kHz/20 kHz A/D Converters                                                                                                                                                                                         |   |   |   |       |

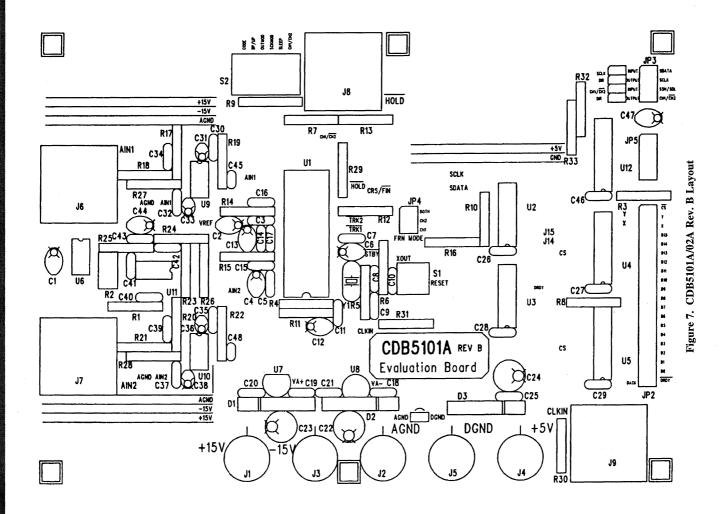

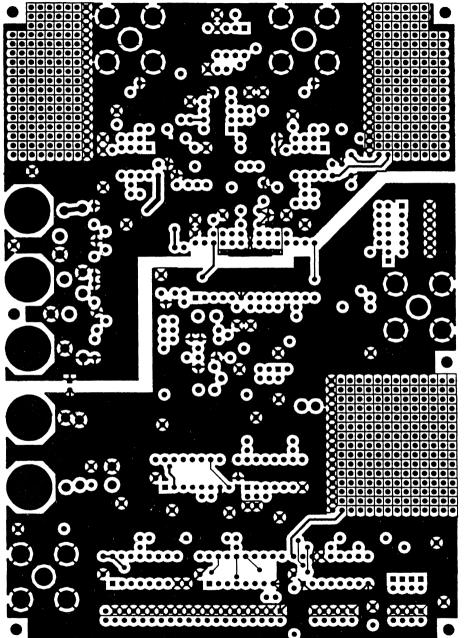

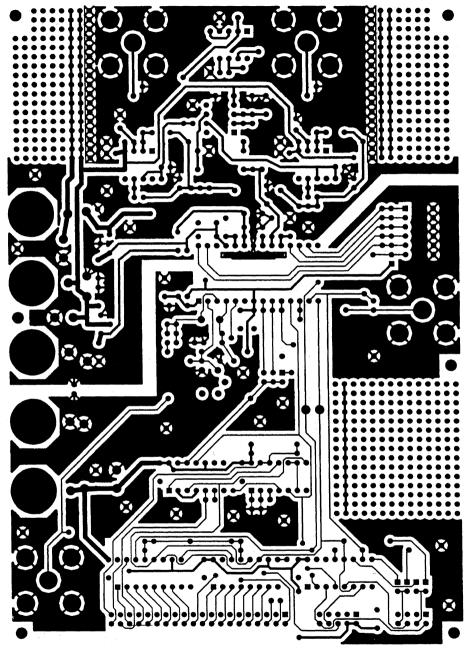

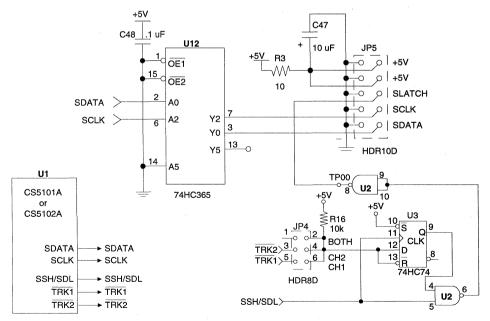

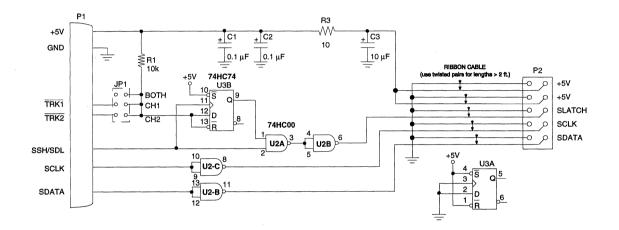

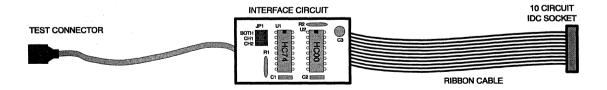

|    | - CDB5101A/2A Evaluation Board for CS5101A/2A                                                                                                                                                                                              |   |   |   | 2-149 |

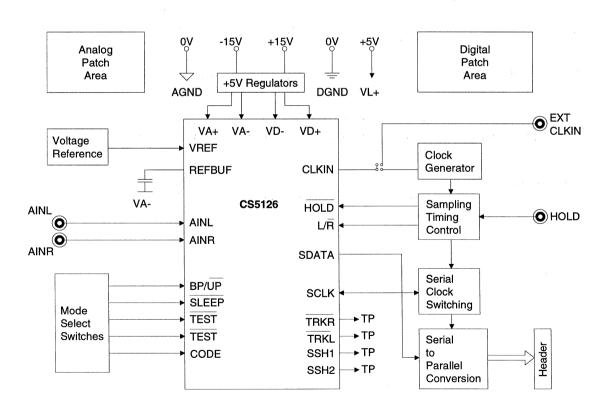

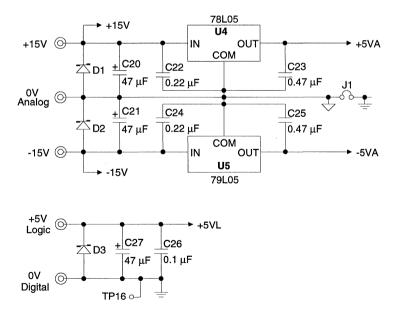

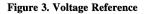

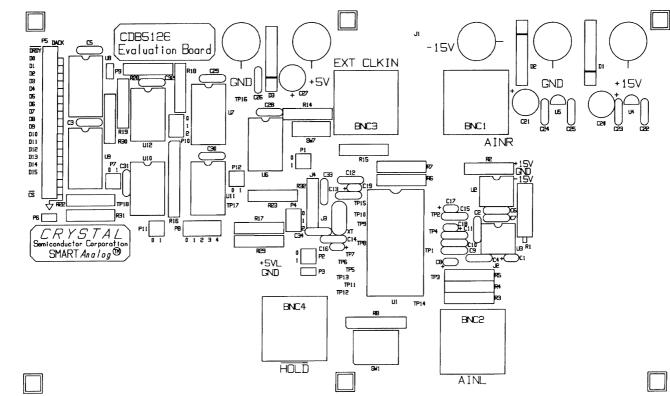

|    | - CS5126 16-Bit, Stereo A/D Converter for Digital Audio                                                                                                                                                                                    |   |   |   |       |

|    | - CDB5126 16-Bit, Stereo A/D Converter for Digital Audio                                                                                                                                                                                   |   |   |   |       |

|    | - CS5317 16-Bit, 20 kHz Oversampling A/D Converter                                                                                                                                                                                         |   | • |   | 2-189 |

|    | - CDB5317 Evaluation Board for CS5317                                                                                                                                                                                                      |   |   |   |       |

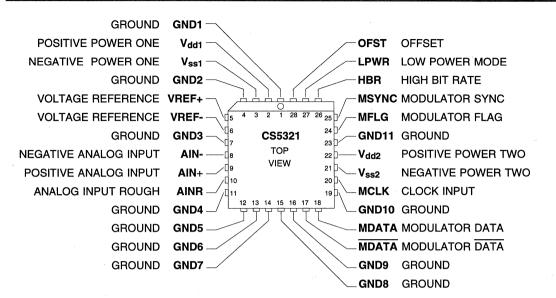

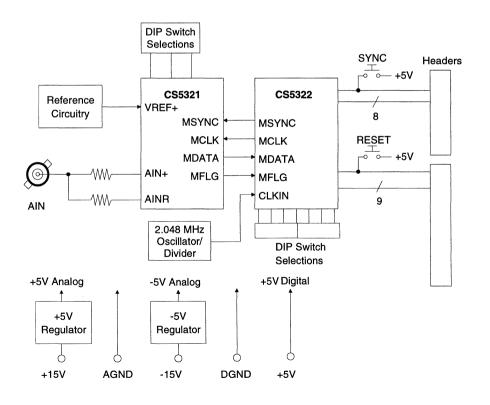

|    | NEW - CS5321 High Dynamic Range Delta-Sigma Modulator                                                                                                                                                                                      |   |   |   | 2-219 |

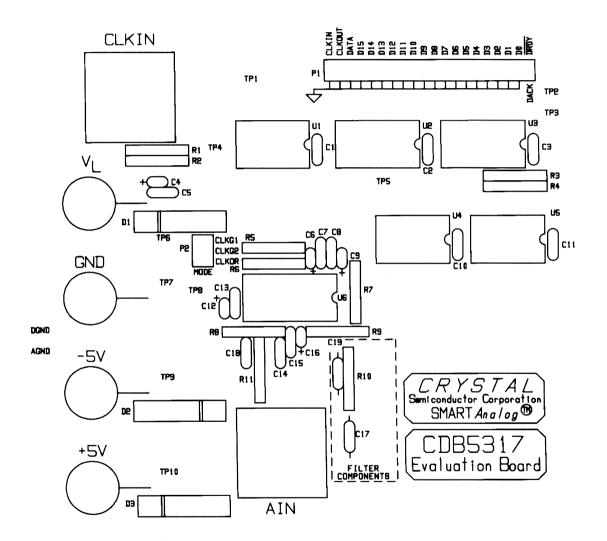

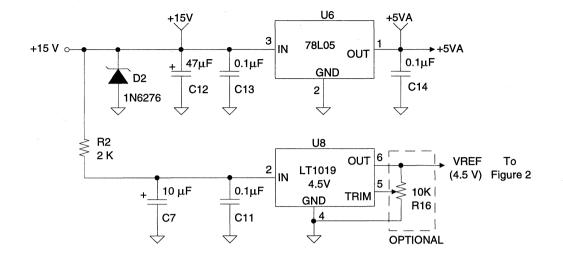

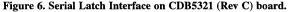

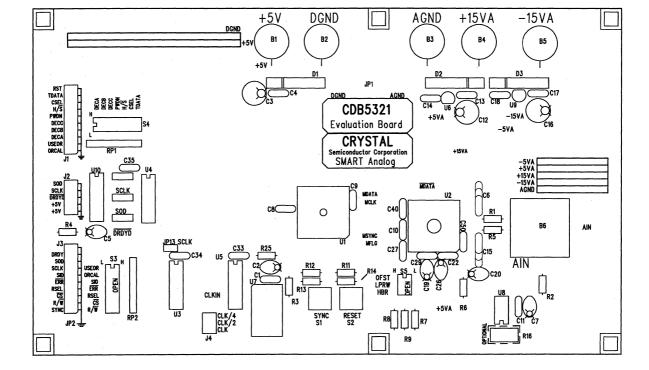

|    | - CDB5321 Evaluation Board for CS5321                                                                                                                                                                                                      |   |   |   | 2-233 |

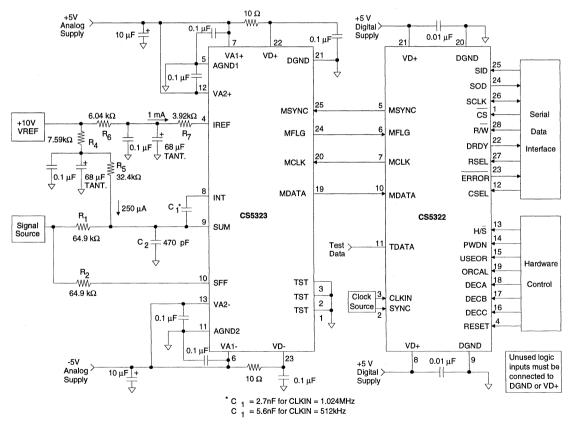

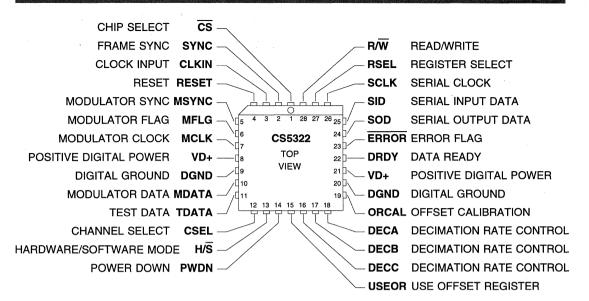

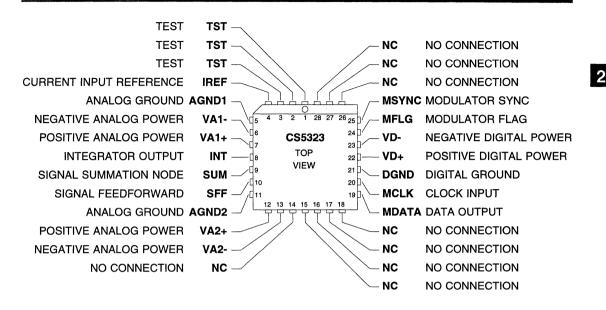

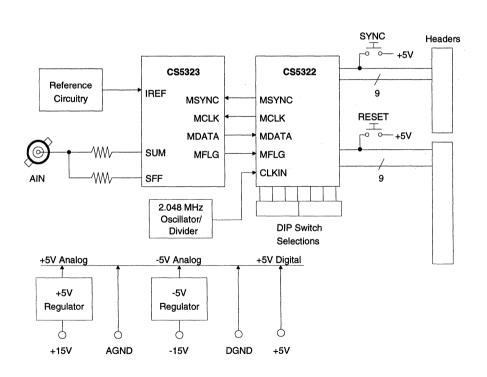

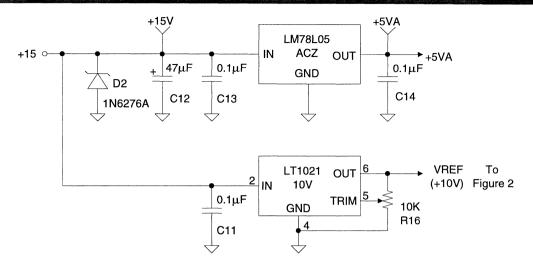

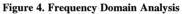

|    | - CS5322/3 24-Bit Variable Bandwidth A/D Converter                                                                                                                                                                                         |   |   |   | 2-245 |

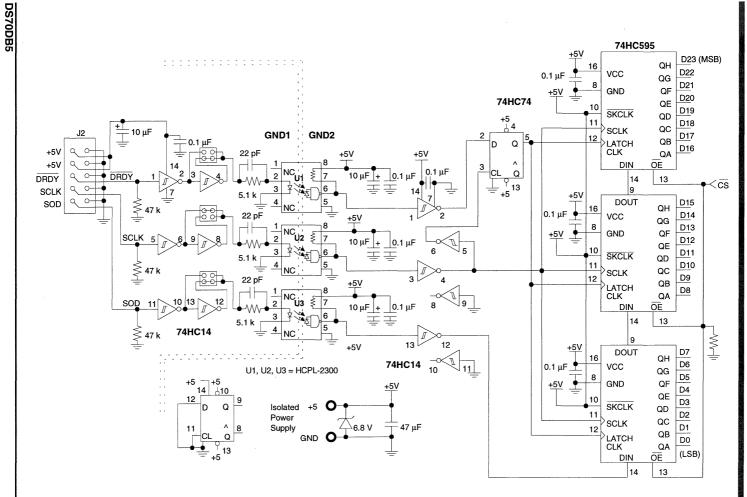

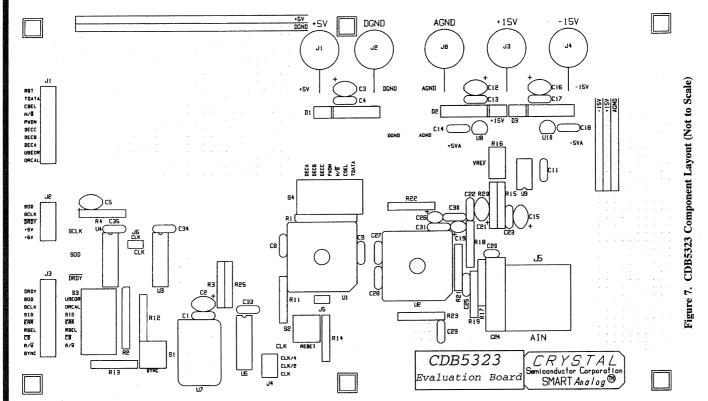

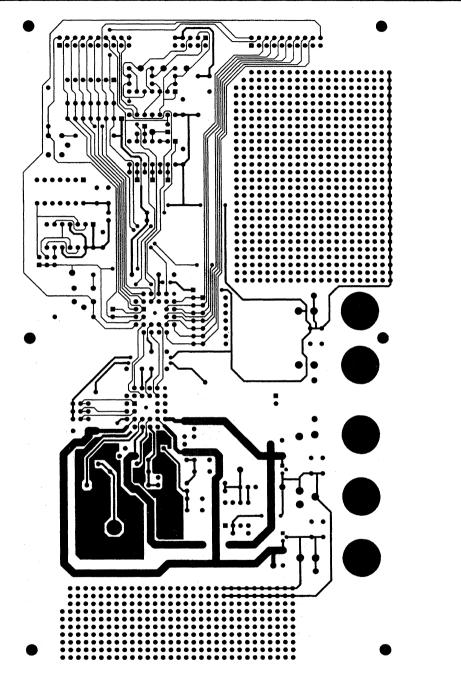

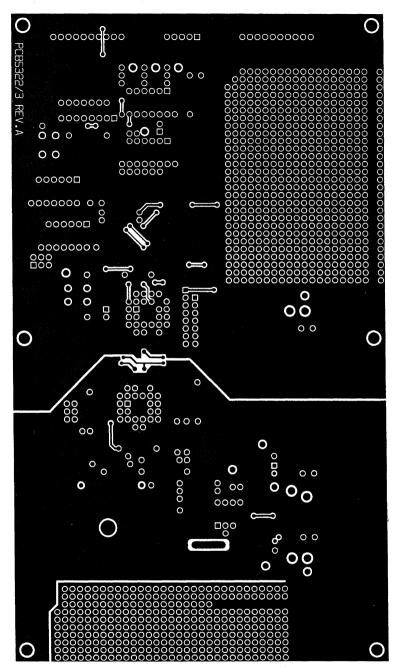

|    | - CDB5322/3 Evaluation Board for CS5322/3                                                                                                                                                                                                  |   |   |   | 2-272 |

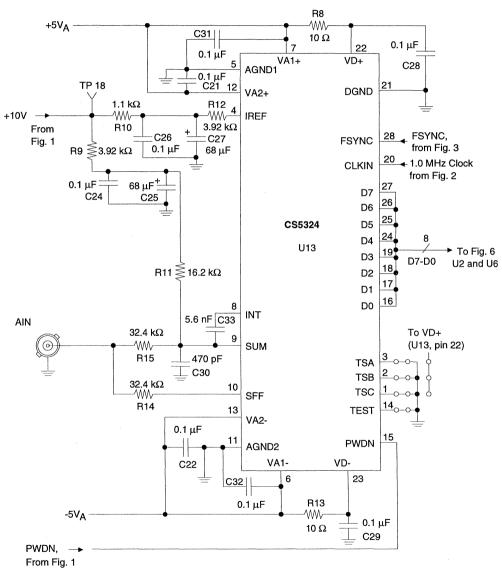

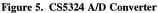

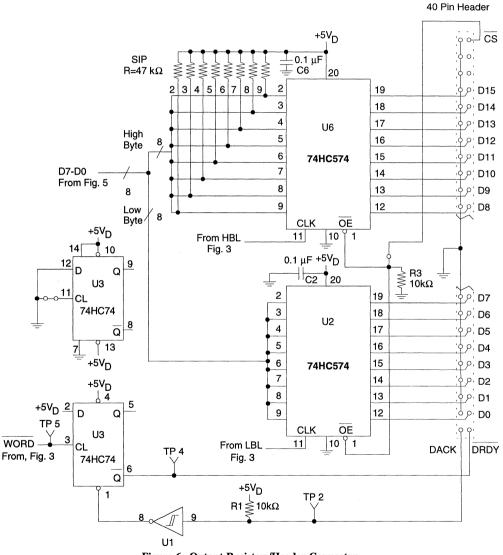

|    | - CS5324 120 dB, 500 Hz Oversampling A/D Converter                                                                                                                                                                                         |   |   |   | 2-283 |

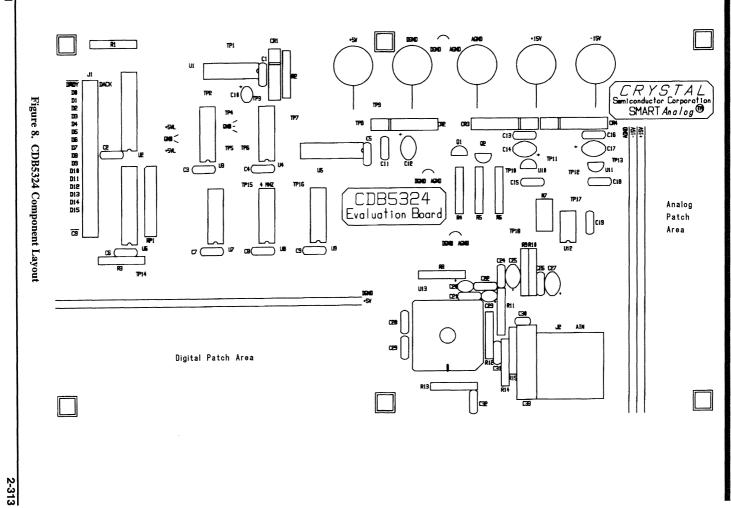

|    | - CDB5324 Evaluation Board for CS5324                                                                                                                                                                                                      |   |   |   | 2-305 |

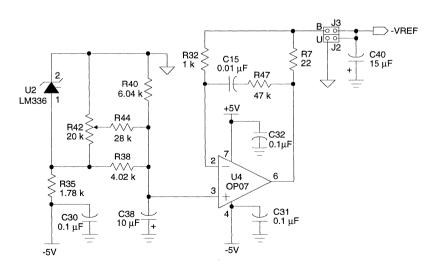

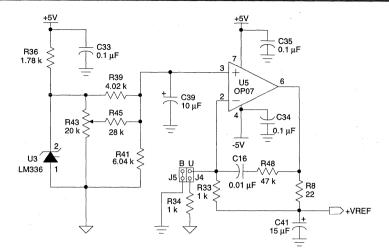

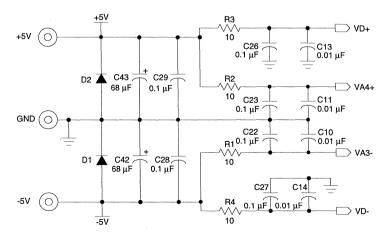

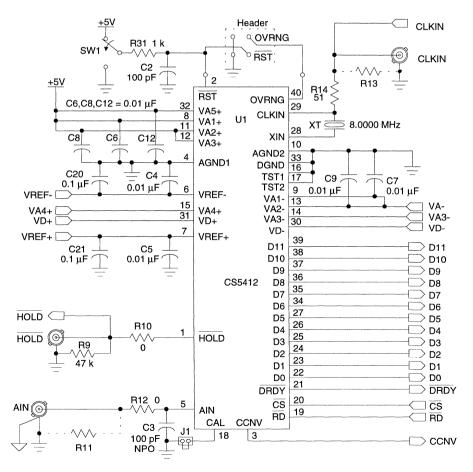

|    | - CS5412 12-Bit, 1MHz Self-Calibrating A/D Converter                                                                                                                                                                                       |   |   |   | 2-315 |

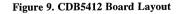

|    | - CDB5412 Evaluation Board for CS5412                                                                                                                                                                                                      |   |   |   | 2-335 |

|    | NEW       - CS5480 10-Bit, 40 MHz, A/D Converter         NEW       - CS5481 10-Bit, 10 MHz, A/D Converter         NEW       - CS5490 12-Bit, 20 MHz, A/D Converter         - CS5501/3 Low-Cost       16 & 20-Bit Measurement A/D Converter |   |   |   | 2-345 |

|    | <b>NEW</b> - CS5481 10-Bit, 10 MHz, A/D Converter                                                                                                                                                                                          |   |   |   | 2-355 |

|    | <b>NEW</b> - CS5490 12-Bit, 20 MHz, A/D Converter                                                                                                                                                                                          |   |   |   | 2-365 |

|    | - CS5501/3 Low-Cost, 16 & 20-Bit Measurement A/D Converter .                                                                                                                                                                               |   |   |   | 2-367 |

|    | - CDB5501/3 Evaluation Board for CS5501/3                                                                                                                                                                                                  |   | • |   | 2-407 |

|    | NEW - CS5504 Low Power, 20-Bit A/D Converter                                                                                                                                                                                               |   |   |   | 2-421 |

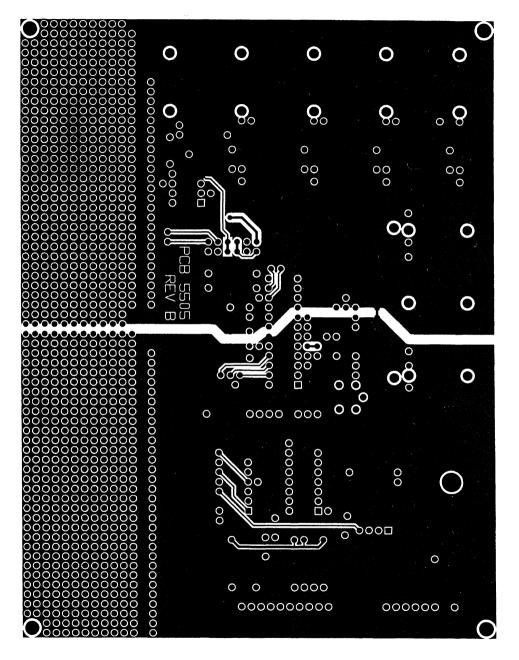

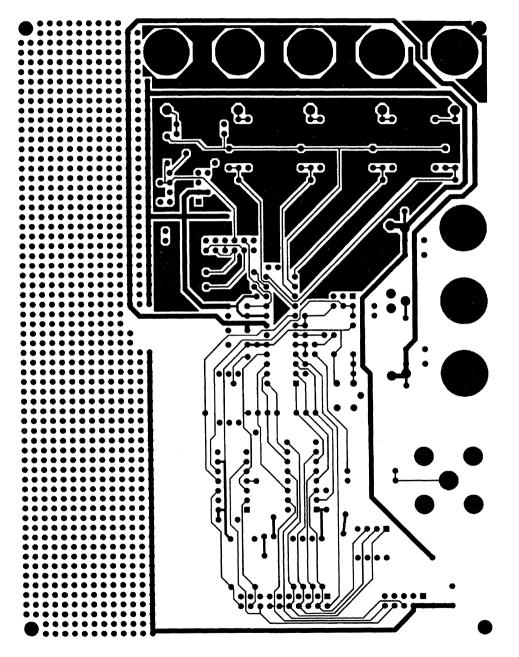

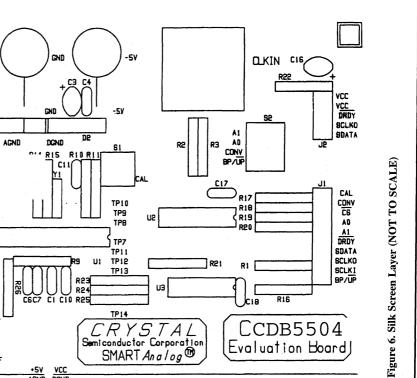

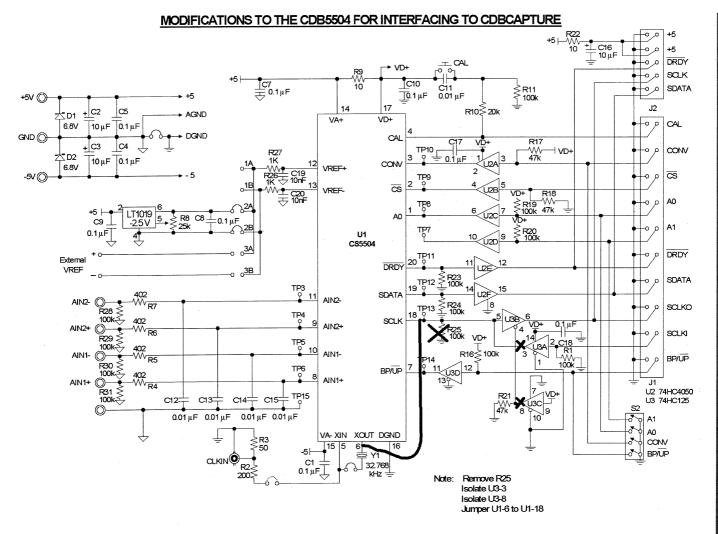

|    | - CDB5504 Evaluation Board for CS5504                                                                                                                                                                                                      |   |   |   |       |

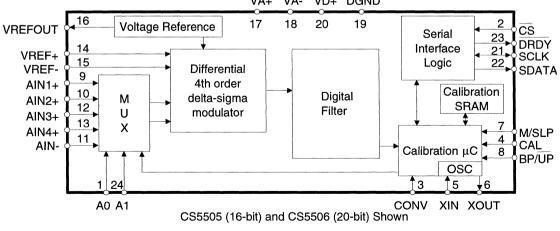

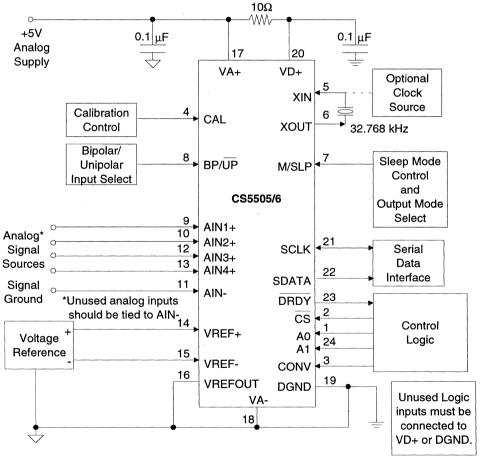

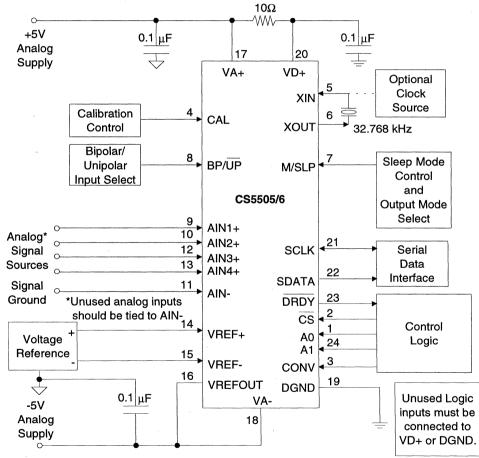

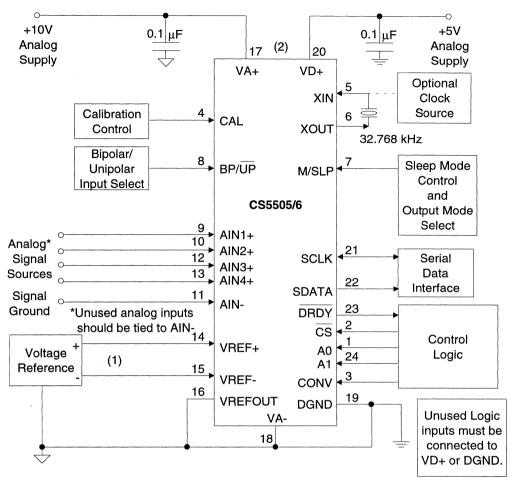

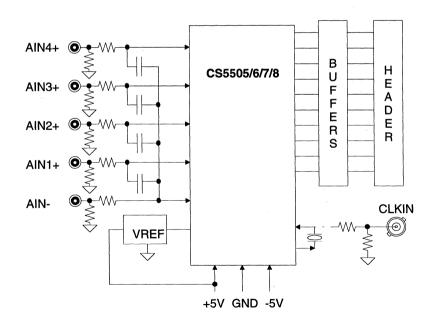

|    | - CS5505/6/7/8 Very Low Power, 16-Bit and 20-Bit A/D Converters                                                                                                                                                                            |   |   |   | 2-451 |

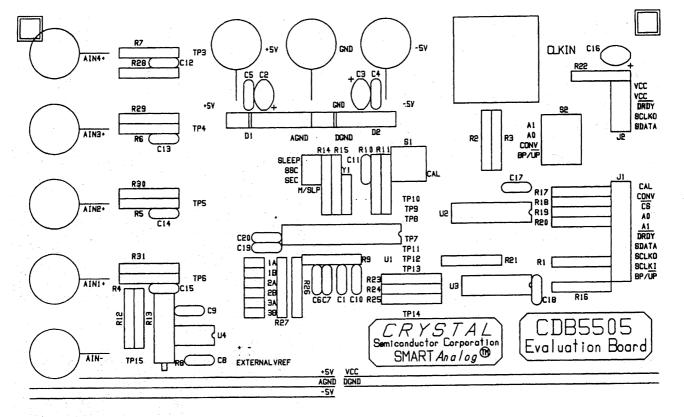

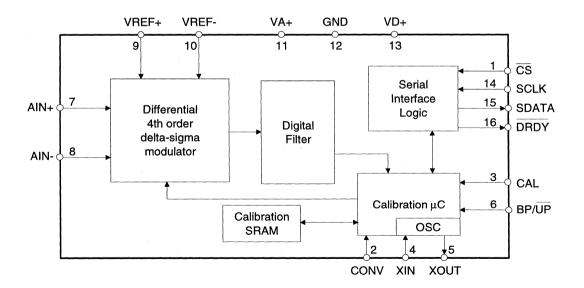

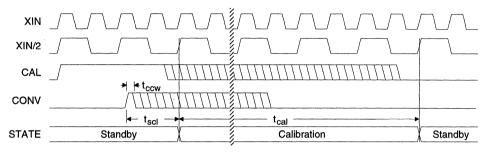

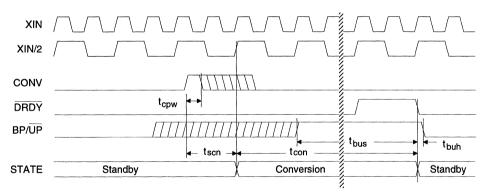

|    | - CDB5505/6/7/8 Evaluation Board for CS5505/6/7/8                                                                                                                                                                                          |   |   |   |       |

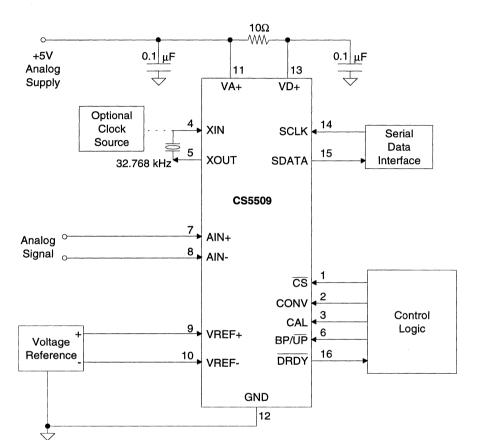

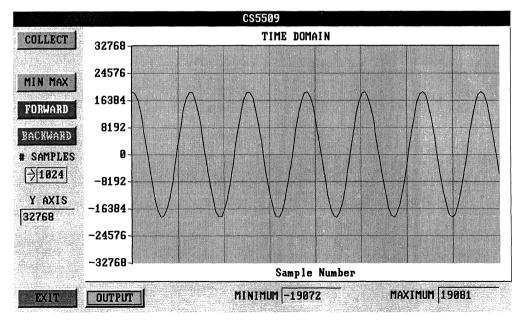

|    | NEW - CS5509 Single Supply, 16-Bit A/D Converter                                                                                                                                                                                           |   |   |   | 2-489 |

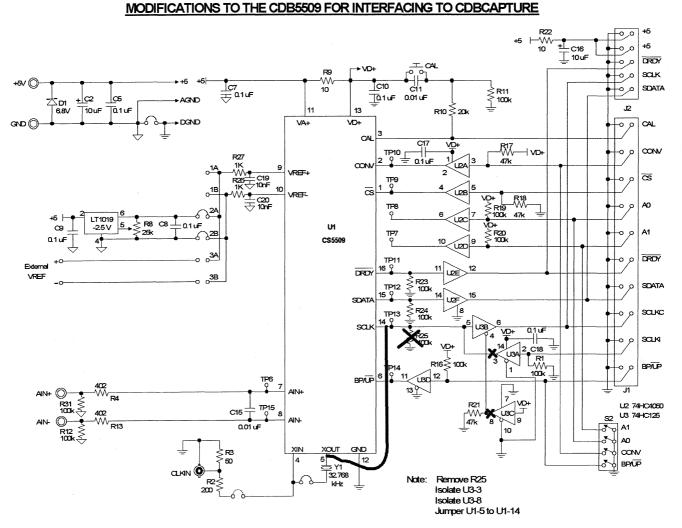

|    | - CDB5509 Evaluation Board for CS5509                                                                                                                                                                                                      |   |   |   | 2-511 |

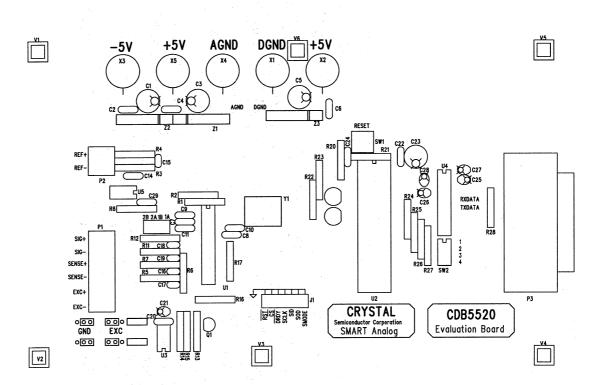

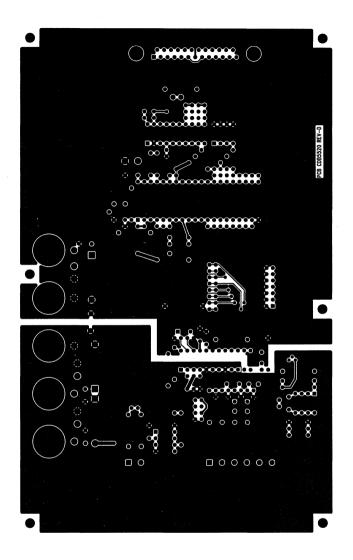

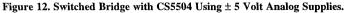

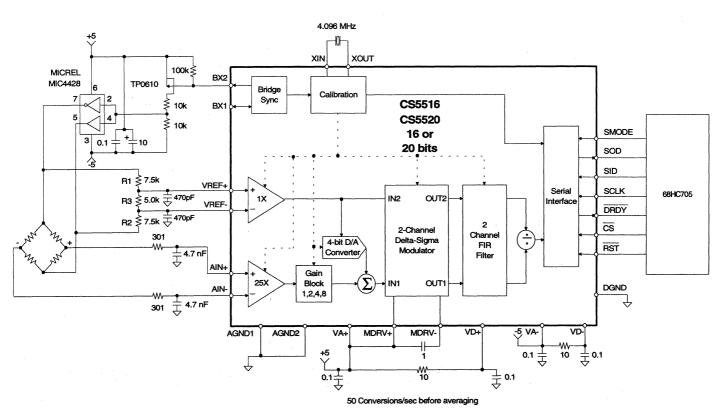

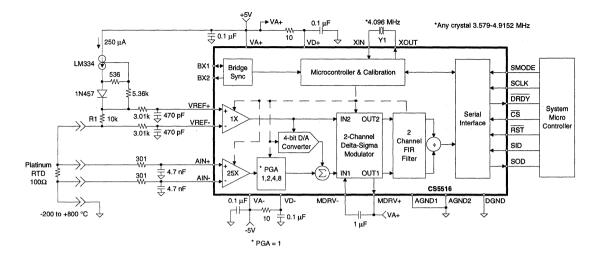

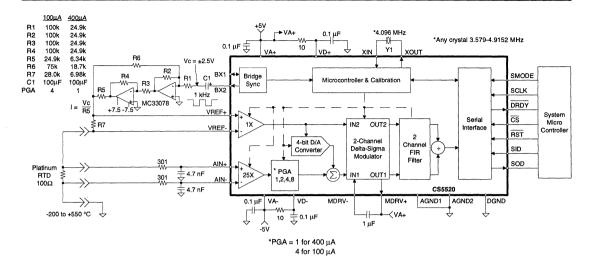

|    | - CS5516/20 16-Bit/20-Bit Bridge Transducer A/D Converters                                                                                                                                                                                 | • | • |   | 2-519 |

|    | - CDB5516/20 Evaluation Board for CS5516/20                                                                                                                                                                                                | · | • |   | 2-549 |

|    | NEW - CS5542 Dual Channel Current-Input Modulator                                                                                                                                                                                          |   |   |   |       |

|    | NEW - CS5543 8-Channel Digital Decimation Filter                                                                                                                                                                                           |   |   |   |       |

|    | NEW - CS7870/5 12-Bit, 100 kHz Sampling A/D Converter                                                                                                                                                                                      |   | • | • | 2-563 |

|    | - CDB7870/5 Evaluation Board for CS7870/5                                                                                                                                                                                                  |   | • |   |       |

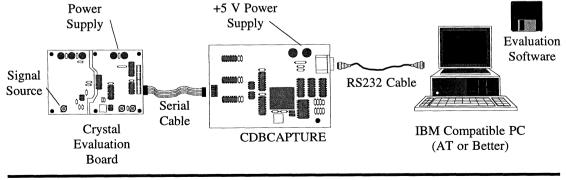

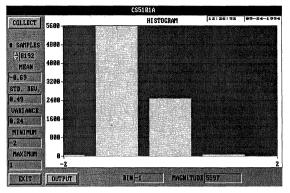

|    | - CDBCAPTURE Evaluation Board                                                                                                                                                                                                              |   |   |   | 2-597 |

## CONTENTS

4.

## 3. AUDIO CONVERSION PRODUCTS

|        | - Chapter Introduction                                 |   |   |   |   |   | 3-2          |

|--------|--------------------------------------------------------|---|---|---|---|---|--------------|

|        | Consumer/Professional                                  |   |   |   |   |   |              |

|        | - CS3310 Stereo Digital Volume Control                 | • |   |   |   |   | 3-7          |

|        | - CS4303 Digital to Analog Converter                   |   |   |   |   |   | 3-8          |

|        | - CS4328 Digital to Analog Converter                   |   |   |   |   |   | 3-9          |

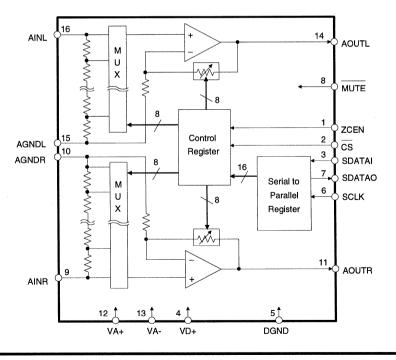

| NEW    | - CS4329 Digital to Analog Converter                   |   |   |   |   |   | 3-10         |

|        | - CS4330/1/3 Digital to Analog Converter               |   |   |   |   |   | 3-11         |

| NEW    | - CS5330 Analog to Digital Converter                   |   | • |   |   |   | 3-12         |

|        | - CS5336/8/9 Analog to Digital Converter               |   |   |   |   |   | 3-13         |

|        | - CS5389 Analog to Digital Converter                   |   |   |   |   |   | 3-14         |

| NEW    | - CS5390 Analog to Digital Converter                   |   |   |   |   |   | 3-15         |

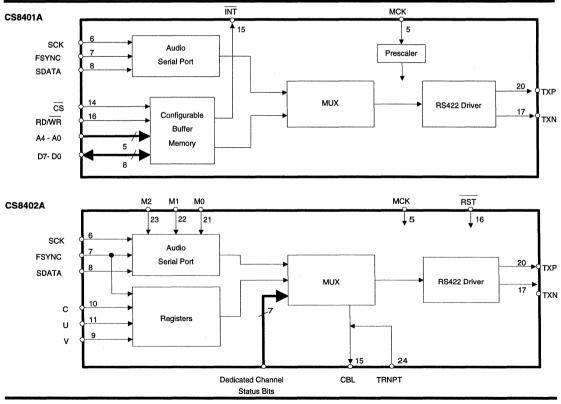

|        | - CS8401A/02A Digital Audio Transmitter                |   |   |   |   |   | 3-16         |

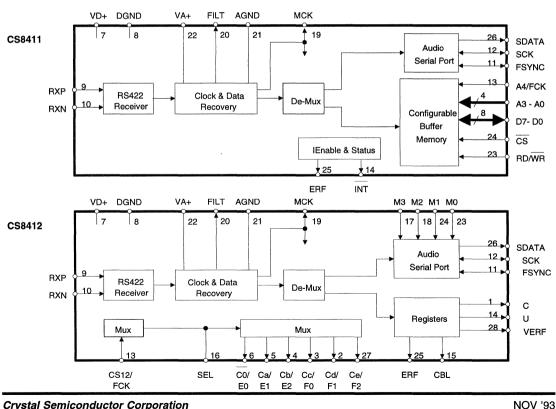

|        | - CS8411/12 Digital Audio Receiver                     |   |   |   | • | • | 3-17         |

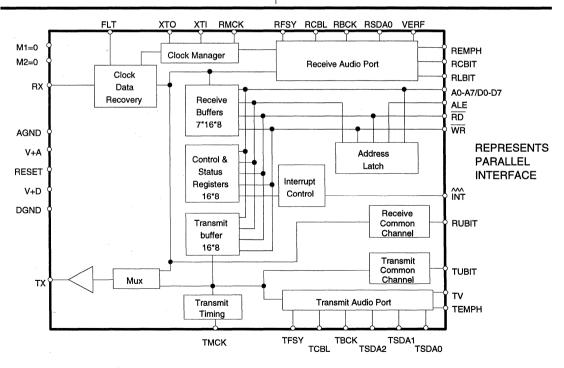

|        | - CS8425 A-LAN Transceiver                             | • | • | • | • | • | 3-18         |

|        | Broadcast                                              |   |   |   |   |   |              |

|        | - CS4920/CS4920A Multi-Standard Audio Decoder-DAC .    | • | • | • | • | • | 3-19         |

| NEW    | - CS4921 MPEG 1 & MPEG 2 Audio Decoder-DAC             | • | • | • | • | • | 3-20         |

|        | Multimedia                                             |   |   |   |   |   |              |

|        |                                                        |   | • |   |   |   | 3-21         |

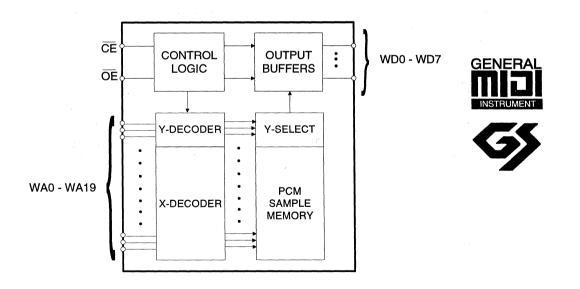

|        | - CS4112 Wavetable Sample ROM for Music Synthesis      | · | · | · | · | • | 3-22         |

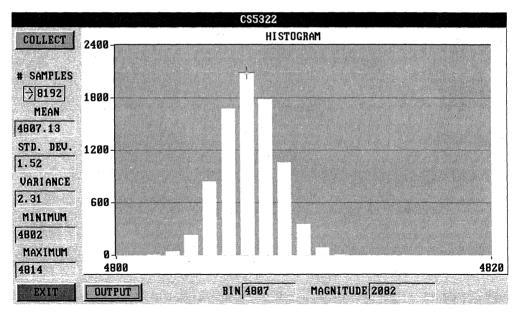

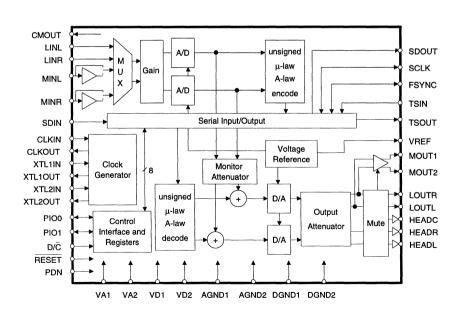

|        | - CS4215 Multimedia Audio CODEC                        |   |   |   |   |   | 3-23         |

|        | - CS4216 Stereo Audio CODEC                            |   |   |   |   |   | 3-24         |

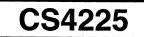

|        | - CS4225 Digital Audio Conversion System               | • | · | • | ٠ |   | 3-25         |

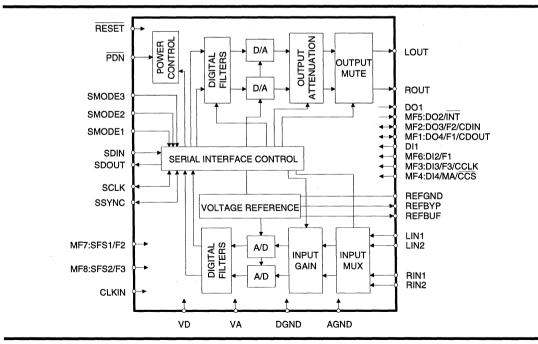

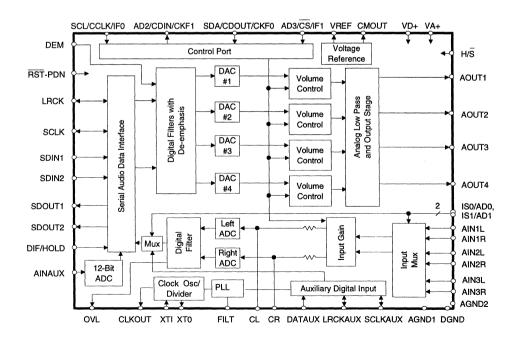

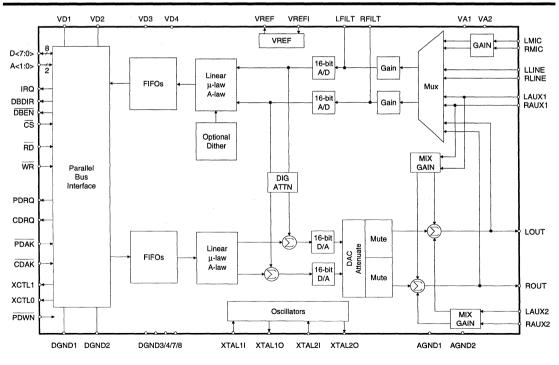

|        | - CS4231A Enhanced PC Bus Interface CODEC              |   |   |   |   |   | 3-26         |

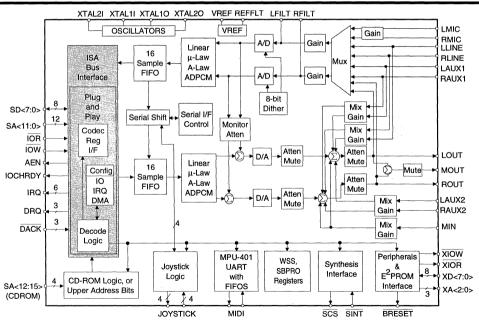

| NEW    | - CS4232 Games Compatible Plug-and-Play Audio System . |   |   |   |   |   | 3-27         |

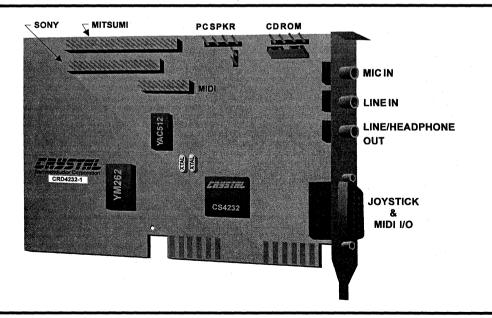

|        | - CRD4232-1 Low-Cost Reference Design                  |   |   |   |   |   | 3-28         |

|        | - CS4248 PC Bus Interface CODEC                        |   |   |   |   |   | 3-29         |

| NUMBER | - CS8905C Programmable Effects Processor               |   |   |   |   |   | 3-30         |

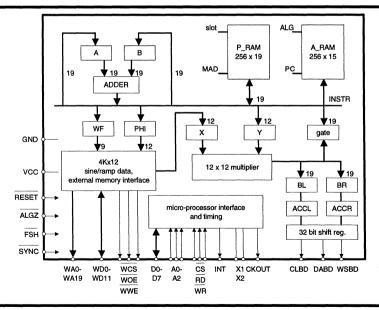

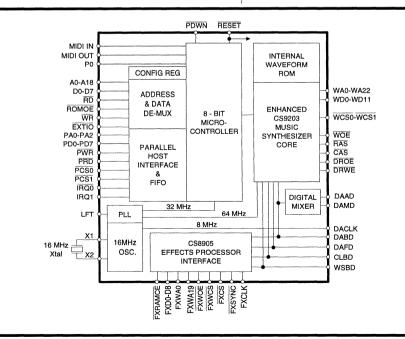

| NEW    | - CS9233 Integrated Wavetable Synthesizer              |   |   |   |   |   | 3-31         |

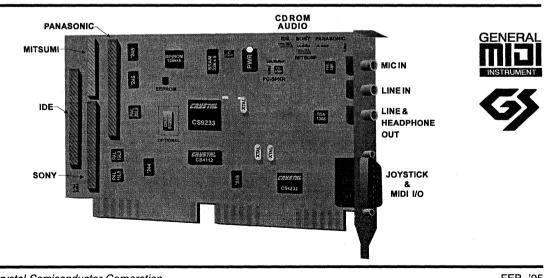

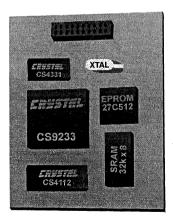

|        | - CRD9233-1 Wavetable/Audio Reference Design .         |   |   |   |   |   | 3-32         |

|        | - CRD9233-2 GM/GS Music Synthesizer Daughtercard       |   |   |   |   |   | 3-33<br>3-34 |

|        | - DRIVERS Software                                     |   |   |   |   |   | 3-34         |

|        | - DIAGNOSTICS Software                                 |   |   |   |   |   | 3-35         |

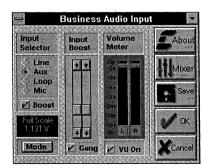

|        | - CWDRGN11 Software                                    |   |   |   |   |   | 3-30         |

|        |                                                        | • | • | • | • | · | 5-57         |

| COM    | MUNICATION PRODUCTS                                    |   |   |   |   |   |              |

|        | - Chapter Introduction                                 | • |   | • | • |   | 4-1          |

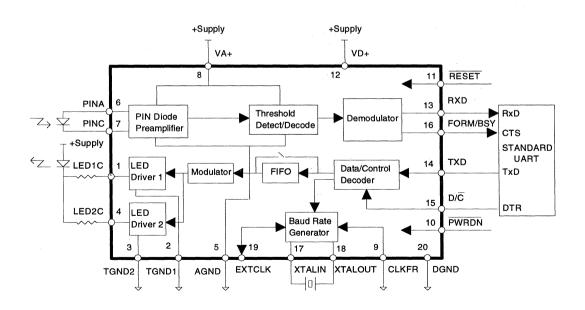

|        | Infrared Transceiver                                   |   |   |   |   |   |              |

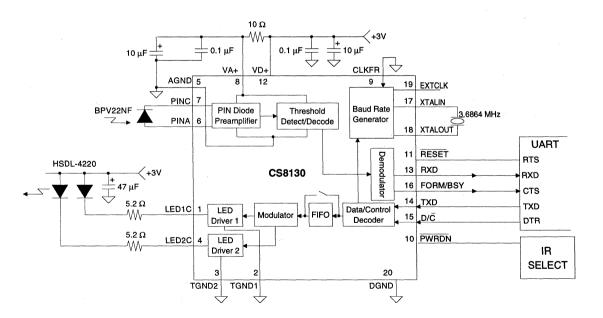

| NEW    | - CS8130 Infrared Transceiver                          | • |   |   |   | • | 4-6          |

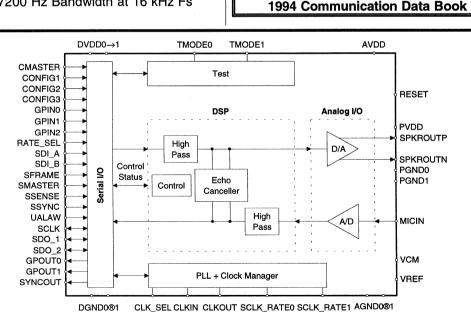

|        | Echo Cancellers                                        |   |   |   |   |   |              |

|        | - CS6400 Echo Cancelling Codec                         | • | • |   | • | · | 4-7          |

| NEW    | - CS6401 Programmable Echo Canceller                   | • | • | • | • | ٠ | 4-8          |

# CRYSTAL

|    |         | CWECAND Executable Code for the CS(401                                       | 4.0   |

|----|---------|------------------------------------------------------------------------------|-------|

|    |         |                                                                              | 4-9   |

|    |         |                                                                              | 4-10  |

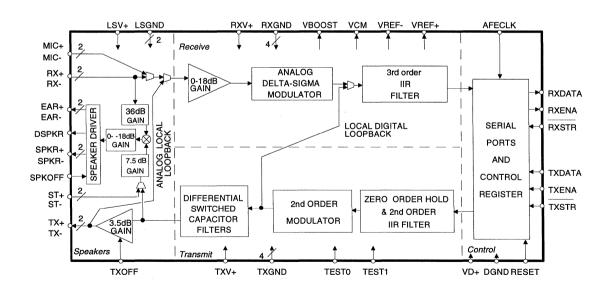

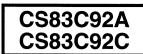

|    | NIEXX   | Communication Codecs                                                         | 4 1 1 |

|    |         |                                                                              | 4-11  |

|    | INE W   |                                                                              | 4-12  |

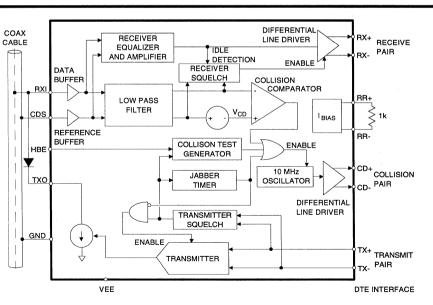

|    |         | Ethernet/Cheapernet                                                          | 4 10  |

|    | NITINA  |                                                                              | 4-13  |

|    | NEW     |                                                                              | 4-14  |

|    |         | Telecom                                                                      | 4.15  |

|    |         |                                                                              | 4-15  |

|    |         |                                                                              | 4-16  |

|    | NEW     |                                                                              | 4-17  |

|    |         |                                                                              | 4-18  |

|    |         |                                                                              | 4-19  |

|    |         |                                                                              | 4-20  |

|    | NEW     |                                                                              | 4-21  |

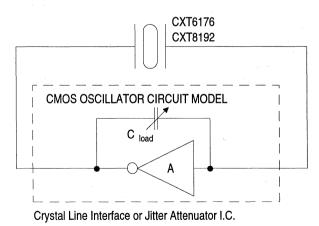

|    |         | - CXT6176/8192 Pullable Quartz Crystals                                      | 4-22  |

| 5. | APPL    | ICATION NOTES                                                                |       |

|    |         | - Layout and Design Rules for Data Converters and Other Mixed Signal Devices | 5-3   |

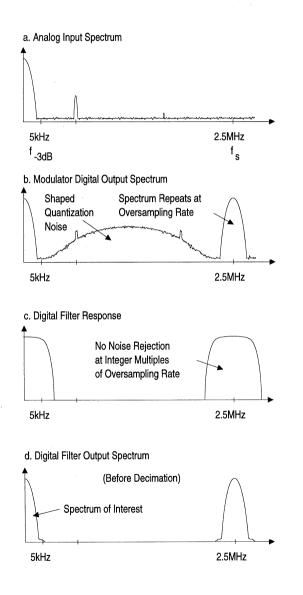

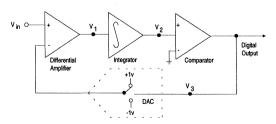

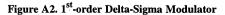

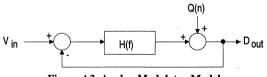

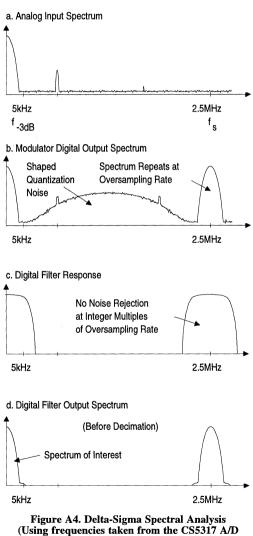

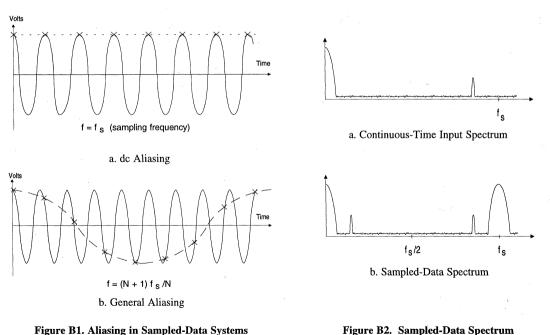

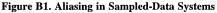

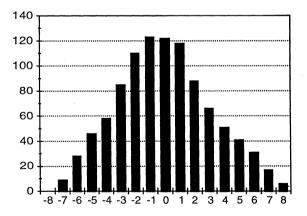

|    |         | - Delta-Sigma A/D Conversion Technique Overview                              |       |

|    | NEW     | - The CS5504 Family Characteristics                                          |       |

|    |         | - CS5516 and CS5520: Overcoming Errors in Bridge Transducer Measurement .    |       |

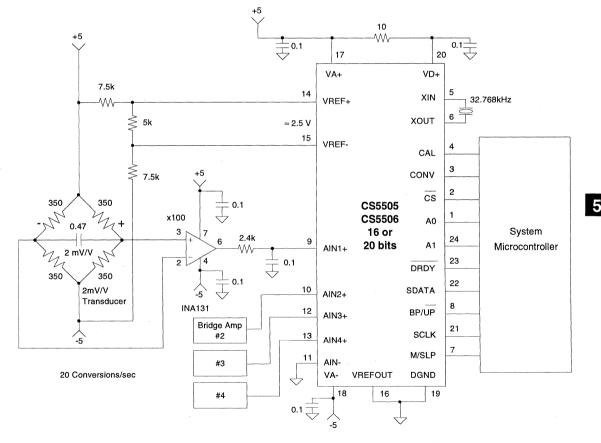

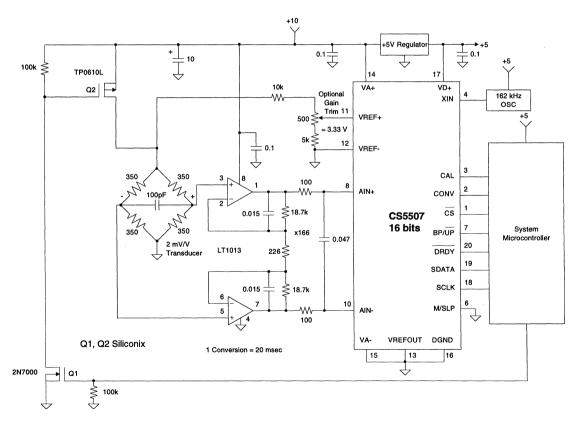

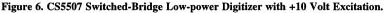

|    |         | - A Collection of Bridge Transducer Digitizer Circuits                       |       |

|    |         | - CS5516 and CS5520: Answers to Application Questions                        |       |

|    |         | - Precision Temperature Measurement using RTDs (Resistance Temperature       |       |

|    |         | Detectors) with the CS5516 and CS5520 Bridge Transducer A/D Converters .     | 5-67  |

|    | NEW     |                                                                              | 5-71  |

|    |         |                                                                              | 5-73  |

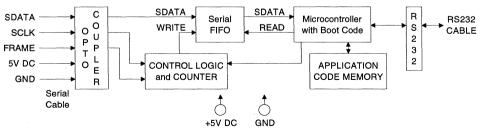

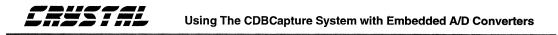

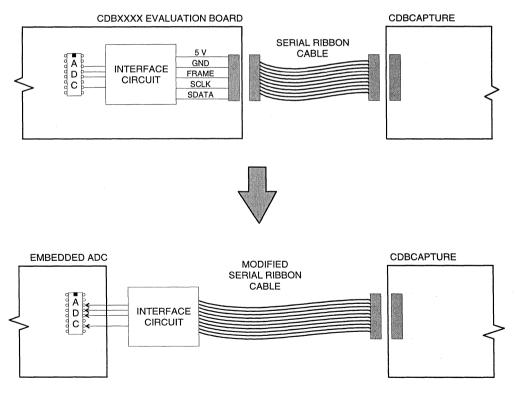

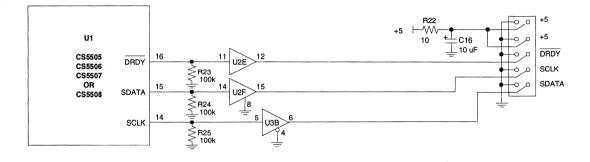

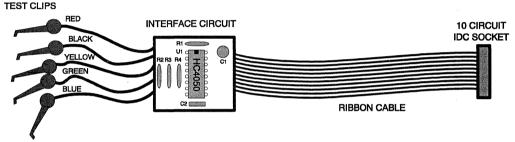

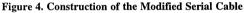

|    |         | - Using The CDBCAPTURE System With Embedded A/D Converters                   |       |

|    |         |                                                                              | 5-89  |

|    |         | •                                                                            | 5-91  |

|    |         |                                                                              | 5-93  |

|    |         |                                                                              | 5-105 |

|    |         |                                                                              | 5-109 |

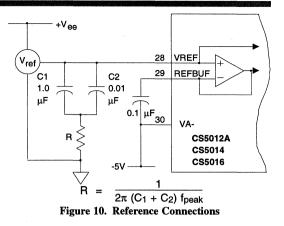

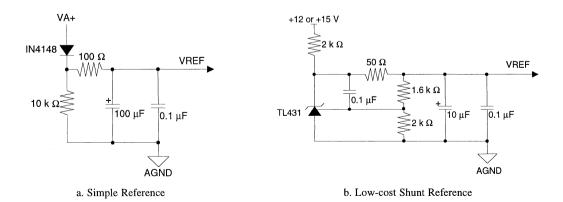

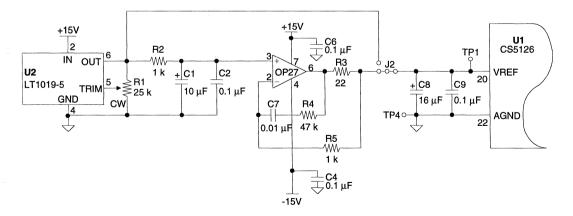

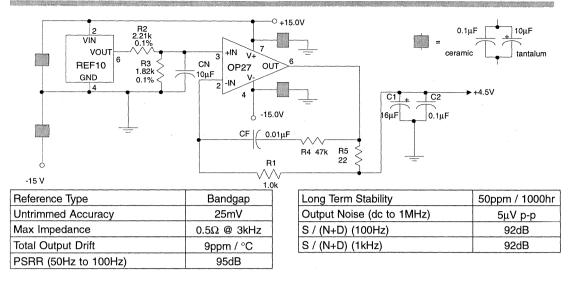

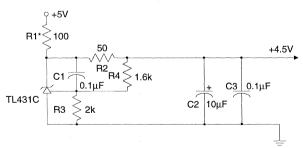

|    | 1,12,11 | - Voltage References for the CS5012A/CS5014/CS5016/CS5101A/CS5102A/          | 5 107 |

|    |         | CS5126 Series of A/D Converters                                              | 5-115 |

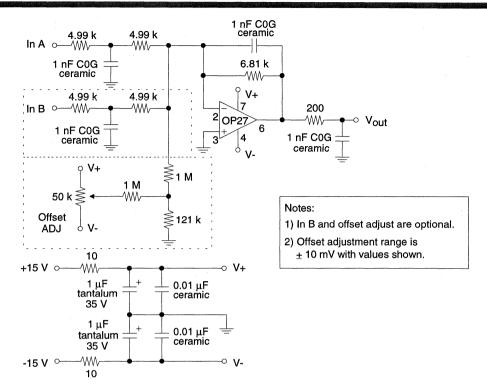

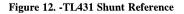

|    |         | - Buffer Amplifiers for the CS5012A/CS5014/CS5016/CS5101A/CS5102A/           | 5 115 |

|    |         | CS5126 Series of A/D Converters                                              | 5-127 |

|    |         |                                                                              | 5-151 |

|    |         | - A concetion of Application times for the CSJOTA Series of AD converters .  | 5-151 |

## 6. APPENDICES

|    | - Contents                      |  |  |  |  |   |  |  | 6-2 |

|----|---------------------------------|--|--|--|--|---|--|--|-----|

|    | - Product Category Levels .     |  |  |  |  |   |  |  | 6-3 |

|    | - Reliability Methods           |  |  |  |  |   |  |  | 6-4 |

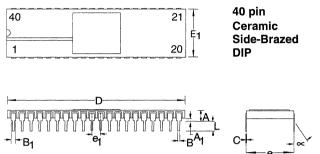

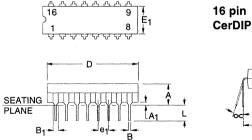

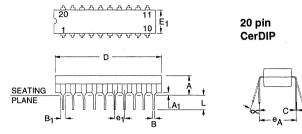

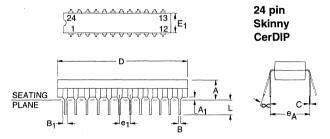

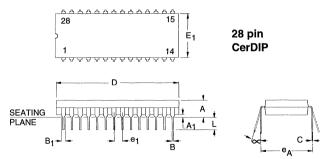

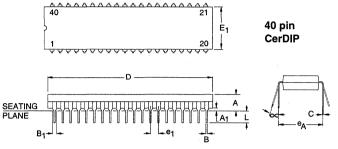

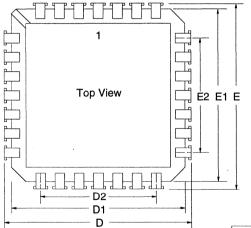

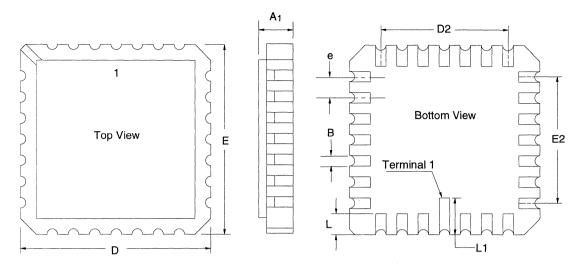

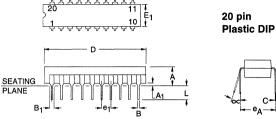

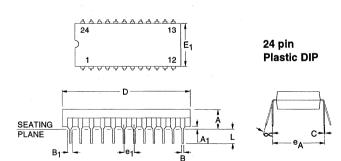

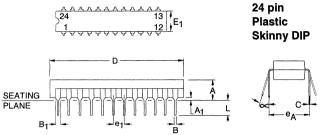

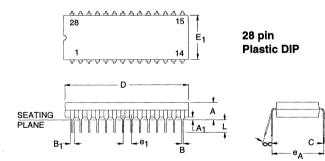

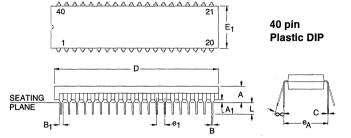

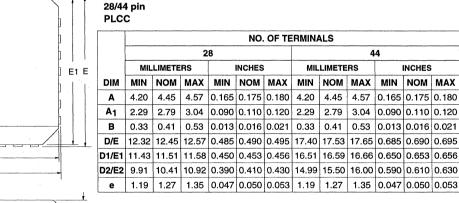

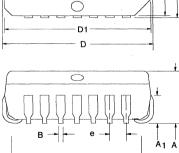

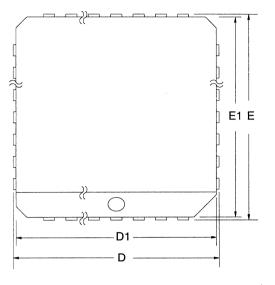

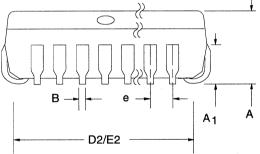

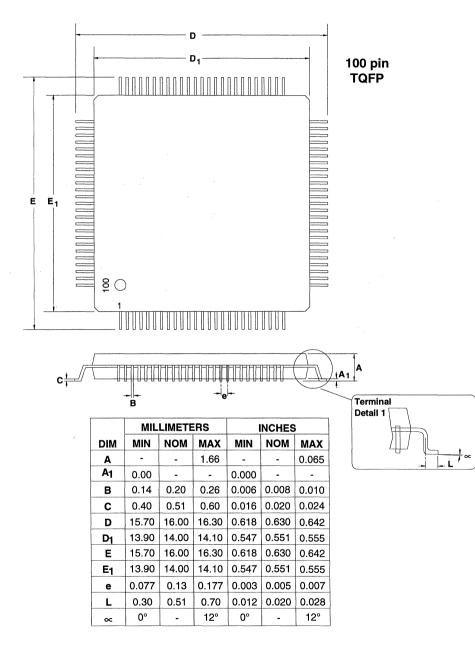

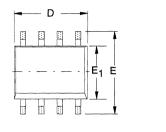

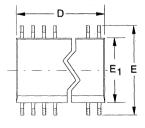

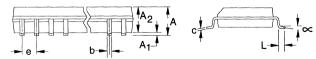

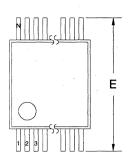

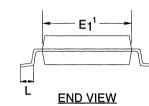

|    | - Package Outlines              |  |  |  |  |   |  |  |     |

|    | - Standard Military Drawings    |  |  |  |  |   |  |  |     |

| 7. | SALES OFFICES                   |  |  |  |  |   |  |  |     |

|    | - Crystal Area Sales Offices    |  |  |  |  |   |  |  | 7-3 |

|    | - United States Representatives |  |  |  |  |   |  |  |     |

|    | - United States Distributors .  |  |  |  |  |   |  |  |     |

|    | - Canada Representatives .      |  |  |  |  |   |  |  | 7-9 |

|    | - Europe Sales Offices          |  |  |  |  |   |  |  |     |

|    | - Europe Representatives .      |  |  |  |  | • |  |  | 7-9 |

|    | - Far East Representatives .    |  |  |  |  |   |  |  |     |

|    | - Japan Sales Office            |  |  |  |  |   |  |  |     |

|    | - Japan Distributors            |  |  |  |  |   |  |  |     |

## **GENERAL INFORMATION**

## DATA ACQUISITION

General Purpose Industrial Measurement Seismic

**High Speed**

## **AUDIO PRODUCTS**

**Consumer/Professional**

Broadcast

Multimedia

## COMMUNICATIONS PRODUCTS

Infrared Transceiver Echo Cancellers Communications Codecs Ethernet/Cheapernet Telecom

## **APPLICATION NOTES**

## APPENDICES

Product Category Levels Reliability Calculation Methods Package Mechanical Drawings Standard Military Drawings

## SALES OFFICES

1

4

## CONTENTS

| Company Information and Part Num    | berin | g C | onvo | enti | on | • | • | • | • | • | 1-3 |

|-------------------------------------|-------|-----|------|------|----|---|---|---|---|---|-----|

| Quality and Reliability Information |       |     |      |      |    |   | • |   |   |   | 1-5 |

## **COMPANY INFORMATION**

Crystal's proprietary SMART Analog<sup>™</sup> design technique, incorporating analog and digital circuitry in monolithic CMOS devices, represents a powerful new technology in the semiconductor industry. This innovative approach to design eliminates many of the sources of inconsistent performance in traditional analog circuitry.

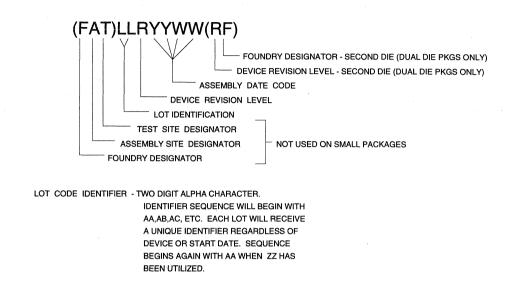

Maximum system performance is built-in from initial research on end-user requirements through product definition. Product quality and reliability is designed into the device architecture and is further assured through rigorous standards for fabrication, assembly and testing. Crystal's part numbering scheme is as follows:

# CRYSTAL

In addition to the part number, all Crystal parts have a second line of marking, which can be decoded as follows:

#### **COMPANY BACKGROUND**

Crystal Semiconductor Corporation was founded in 1984 with the goal of supplying the industry with high-performance, mixed analog/digital CMOS circuits. In 1991, Crystal became a wholly owned subsidiary of Cirrus Logic.

To meet its objectives, Crystal recruited a staff of renowned CMOS analog design engineers, a scarce resource in the industry, and teamed them with designers trained in system architecture development.

By coupling this design staff with highly qualified application and test engineers and seasoned management, Crystal has achieved several industry firsts. Systems designers now benefit from the performance and cost savings of Crystal breakthroughs such as self-calibrating ADCs, monolithic T1 interfaces and the industry's first implementations of "delta sigma" oversampling A-to-D converters.

Headquartered in Austin, Texas, Crystal sells its products worldwide through a network of manufacturer's representatives. Crystal's entire marketing and sales organization is committed to providing quality products and reliable, rapid service.

## **QUALITY AND RELIABILITY INFORMATION**

Crystal Semiconductor is committed at every level of the company to the highest possible standards of quality and reliability in its products. This commitment is evident in all phases of operations: initial product definition, design, fabrication, assembly, test, qualification and customer service. Product quality and reliability are active concerns of each Crystal employee. Quality is ingrained in every operation throughout the product life cycle. Some of the key operations are discussed below.

#### In Product Definition

To ensure maximum system performance, Crystal works with users to identify and quantify the parameters, including quality and reliability issues, that best serve customer needs. Quality and reliability become part of the design goals, along with electrical performance and cost.

#### In Design

Conservative CMOS design rules are the basis for all current Crystal products. In addition, extensive use is made of proven standard cells to drastically reduce the possibility of design errors.

Each pin in every SMART *Analog* product is designed to meet ESD levels of at least 2500V when tested per MIL STD 883C, Method 3015. Each pin is also designed to withstand more than 200mA of DC latch-up current.

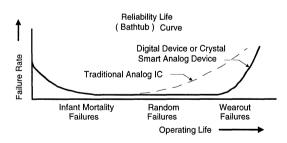

Crystal SMART *Analog* design architectures provide quality and reliability comparable to leading digital devices and memories. This is far superior to traditional analog ICs and hybrids. Designs which use digital error correction achieve stable performance over time and temperature by taking advantage of digital controls that are insensitive to parametric analog problems such as leakages and shifts in threshold voltage. Using Crystal devices, designers have fewer error sources to consider. The result is a less complicated, more reliable system.

#### In Fabrication and Assembly

Crystal ensures reliable delivery of quality parts by accessing established foundries in multiple locations worldwide. Each fabrication facility is qualified by Crystal. Assembly is performed both domestically and offshore under carefully documented and well-controlled conditions.

Wafer fabrication and assembly processes undergo in-line quality inspections. Wafers are inspected optically to guidelines based on MIL STD 883C, Method 2010. Each die is electrically tested using proprietary test circuits that verify key parameters. Following assembly, packages are subjected to a variety of mechanical inspections to verify integrity and insure high quality. (For example, x-ray inspection is one of the standard production tests.)

#### In Test

In a break from traditional analog components, Crystal's SMART Analog products include basic test capabilities designed into each chip. Crystal's in-process quality assurance program uses this designed-in testability to monitor and track the performance and quality of these complex circuits. Finished packaged components are tested 100 percent electrically, over temperature where critical parameters are involved. With these extensive quality programs, Crystal guarantees outgoing electrical quality levels on all data sheet specifications to a 0.065 percent AQL level over the full specified temperature range.

Throughout the assembly and test phases, traceability to the original wafer lot is carefully maintained.

#### In Product Qualification

Before any Crystal product is released to production and shipped in volume, it must undergo a thorough qualification program. Crystal has separate qualification criteria to address both long-term reliability and infant mortality so that the sources of failure are identified and eliminated. Crystal uses military specifications as the guidelines for reliability tests, methods and procedures. (See Qualification Criteria Table)

To ensure reliability of the design and processes, full qualification requires that three non-consecutive lots are used during the qualification program. Fabrication and assembly facilities are audited every six months and routinely monitored. Any major design or process changes are re-qualified.

These steps guarantee that Crystal products maintain the high standards of reliability designed-in from the start.

#### In Customer Service

Compliance with purchasing requirements is ensured through the use of Crystal's computerized system "Compass" (Crystal Online Marketing, Production, and Sales System). This processing system ensures that all orders are entered correctly, scheduled properly, produced according to schedule, and shipped with zero discrepancies.

All systems and procedures at Crystal Semiconductor are aimed at continuously improving the quality and reliability of our products and services to meet the needs of our customers.

Crystal's philosophy on quality is to anticipate problems and develop systems and controls to alleviate possible problems. It is a well stated fact by Juran and Deming, two of the nation's foremost experts on quality, that 85% of all quality problems are system related and 15% are worker related. Therefore, Crystal devotes its major quality efforts toward preventing system related quality problems.

Crystal has a very aggressive audit program in place. Monthly internal audits are performed to insure compliance to the extensive documentation of instructions and criteria for testing and inspection. Semi-annual vendor audits are performed on the assembly and fabrication foundries. Vendor audits insure the adequacy and compliance of specifications, product flow, training, process controls and cleanliness. All internal and external audits have provisions for ratings and a system for corrective action requirements. These frequent audits by assembly, fabrication and quality engineers maximize system quality compliance.

As an added measure of continued high quality from assembly and fabrication foundries, thorough incoming inspections are performed. Wafer level optical inspection is based upon guidelines of MIL STD 883C, METHOD 2010. Test die or scribe line monitors are electrically tested to verify compliance to key process parameters based upon design rule specifications. These electrical parameters include threshold voltages, breakdown voltages, material resistance, and contact resistance. Assembly packaging inspection includes external visual, marking permanency, solderability, x-ray, hermeticity, die shear, wirepull and internal visual.

Preventive measures are very much in force in the final test area. Equipment calibration and preventive maintenance procedures are strictly adhered to. Handling procedures for Electrostatic Discharge are in place throughout the test areas. Non-conforming material is segregated until disposition by a material review board. There are controlled procedures for releasing new test programs and new test equipment to the production environment. In summary, Crystal Semiconductor is committed to meet the quality requirements of its customers.

## **Qualification Criteria Table**

| <b>Qualification Criteria Table</b>                                                                                                                                                                                                                   |                 |                                         |            | World       |                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------------------------|------------|-------------|--------------------------------|

|                                                                                                                                                                                                                                                       |                 | Production                              | Production | Class       |                                |

|                                                                                                                                                                                                                                                       | Method          | Level III                               | Level II   | Level       | Units                          |

| Quality Performance                                                                                                                                                                                                                                   | 1               |                                         |            |             |                                |

| Outgoing Quality (elec./vis-mech/ship.)                                                                                                                                                                                                               | Crystal Spec.   | 1000                                    | 500        | 100         | DPM                            |

| Fault Coverage (Digital)                                                                                                                                                                                                                              |                 | n/a                                     | n/a        | 95%         | %                              |

| Datasheet Test Coverage (Digital)                                                                                                                                                                                                                     | Datasheet       | 100%                                    | 100%       | 100%        | %                              |

| Datasheet Test Coverage (Analog)                                                                                                                                                                                                                      | Datasheet       | 100%                                    | 100%       | 100%        | %                              |

| ESD - Human Body Model                                                                                                                                                                                                                                | MIL 3015        | 1500                                    | 2000       | 4000        | l v                            |

| ESD - Machine Model                                                                                                                                                                                                                                   | MIL3015         |                                         |            | 300         | V                              |

| Latchup - Power Supply <sup>1</sup>                                                                                                                                                                                                                   | JEDEC 17        | Vcc+1V                                  | Vcc+50%    | Vcc+50%     | V                              |

| Latchup - I/O <sup>1</sup>                                                                                                                                                                                                                            | JEDEC 17        | ±50                                     | ±100       | ±200        | mA                             |

|                                                                                                                                                                                                                                                       |                 |                                         |            |             | ·                              |

| Reliability Performance                                                                                                                                                                                                                               |                 |                                         |            |             |                                |

| Infant Mortality (48hrs@125°C or equiv.) <sup>2</sup>                                                                                                                                                                                                 | MIL 1005        |                                         |            | 1000        | DPM                            |

| Early Life (168hrs@125°C or 1yr. equiv.) <sup>3</sup>                                                                                                                                                                                                 | MIL 1005        | 1/167 <sup>4</sup>                      | 500        | 300         | FITS                           |

| Operating Life (1000hrs@125°C or 10yr, equiv.) <sup>3</sup>                                                                                                                                                                                           | MIL 1005        | 500                                     | 300        | 100         | FITS                           |

|                                                                                                                                                                                                                                                       |                 |                                         |            |             |                                |

| Moisture Performance                                                                                                                                                                                                                                  |                 |                                         |            |             | -                              |

| Moisture Resistance - THB (plastic pkgs)                                                                                                                                                                                                              | JEDEC 22B       | 500/5%                                  | 1k/5%      | 1k/3%       | hrs/%LTPD per lot <sup>5</sup> |

| Autoclave (plastic pkgs)                                                                                                                                                                                                                              | JEDEC 22B       | 96/5%                                   | 144/5%     | 144/3%      | hrs/%LTPD per lot <sup>5</sup> |

|                                                                                                                                                                                                                                                       |                 |                                         |            |             |                                |

| Mechanical Performance                                                                                                                                                                                                                                | •••••           | r                                       |            |             | 1 <b>-</b>                     |

| Temp Cycle (plastic pkgs)                                                                                                                                                                                                                             | MIL 1010        | 500/5%                                  | 1k/5%      | 1k/3%       | #cy/%LTPD per lot <sup>5</sup> |

| Thermal Shock (plastic pkgs)                                                                                                                                                                                                                          | MIL1011         | 200/5%                                  | 500/5%     | 1k/3%       | #cy/%LTPD per lot <sup>5</sup> |

| Temp Cycle w/ Hermeticity (hermetic pkgs)                                                                                                                                                                                                             | MIL1010/14      | 500/5%                                  | 1k/5%      | 1k/3%       | #cy/%LTPD per lot <sup>5</sup> |

| Thermal Shock w/ Hermeticity (hermetic pkgs)                                                                                                                                                                                                          | MIL 1011/14     | 200/5%                                  | 500/5%     | 1k/3%       | #cy/%LTPD per lot <sup>5</sup> |

| Soak &VPR (surface mount plastic pkgs)                                                                                                                                                                                                                | Crystal Spec.   | 3/5%                                    | 3/3%       | 3/1%        | #cy/%LTPD per lot <sup>5</sup> |

| Xray                                                                                                                                                                                                                                                  | Crystal Spec.   | 2.50%                                   | 2.50%      | 0.65%       | %AQL per lot <sup>5</sup>      |

| Dimensions                                                                                                                                                                                                                                            | MIL 2016        | 2.50%                                   | 2.50%      | 0.65%       | %AQL per lot <sup>5</sup>      |

| Solderability                                                                                                                                                                                                                                         | MIL 2003        | 2.50%                                   | 2.50%      | 0.65%       | %AQL per lot <sup>5</sup>      |

| Lead Integrity & Lead Pull                                                                                                                                                                                                                            | MIL 2004        | 2.50%                                   | 2.50%      | 0.65%       | %AQL per lot <sup>5</sup>      |

| Mark Permanency                                                                                                                                                                                                                                       | MIL2015         | 2.50%                                   | 2.50%      | 0.65%       | %AQL per lot <sup>5</sup>      |

| <b>.</b>                                                                                                                                                                                                                                              |                 |                                         |            |             |                                |

| Product Integrity                                                                                                                                                                                                                                     |                 |                                         |            |             | 1                              |

| Design Rule and LVS Checks                                                                                                                                                                                                                            | Crystal Spec.   | yes                                     | yes        | yes         |                                |

| Design for Reliability & Packaging                                                                                                                                                                                                                    | Crystal Spec.   | yes                                     | yes        | yes         |                                |

| Product Characterization                                                                                                                                                                                                                              | Crystal Spec.   | limited                                 | full       | statistical |                                |

| Test guardbands                                                                                                                                                                                                                                       | Crystal Spec.   | some                                    | 100%       | 100%        | l                              |

| Construction Analysis                                                                                                                                                                                                                                 |                 |                                         |            |             |                                |

| Construction Analysis                                                                                                                                                                                                                                 | · Orvetel Oreco |                                         |            |             | 1                              |

| Wafer cross section & topo                                                                                                                                                                                                                            | Crystal Spec.   | yes                                     | yes        | yes         |                                |

| SEM metallization                                                                                                                                                                                                                                     | MIL 2018        | yes                                     | yes        | yes         |                                |

| Package                                                                                                                                                                                                                                               | Crystal Spec.   | yes                                     | yes        | yes         | ]                              |

| Notes: 1. at High Temperatures (exc. Lev.IV)<br>2. Point Estimate<br>3. 55°C, 0.7eV, 60%UCL<br>4. #accept/n<br>5. LTPD and AGL criteria in table above<br>CUM LTPD and AQL numbers are als<br><u>Individual Lot</u><br>5% LTPD<br>3% LTPD<br>2.5% AQL |                 | evel II:<br><u>uirement</u><br>PD<br>PD |            |             |                                |

|                                                                                                                                                                                                                                                       | 1.0 % A         |                                         |            |             |                                |

# • Notes •

## DATA ACQUISITION DATA BOOK CONTENTS

| GENERAL INFORMATION                                                                                                                   | 1 |

|---------------------------------------------------------------------------------------------------------------------------------------|---|

| DATA ACQUISITION<br>General Purpose<br>Industrial Measurement<br>Seismic<br>High Speed                                                | 2 |

| AUDIO PRODUCTS<br>Consumer/Professional<br>Broadcast<br>Multimedia                                                                    | 3 |

| COMMUNICATIONS PRODUCTS<br>Infrared Transceiver<br>Echo Cancellers<br>Communications Codecs<br>Ethernet/Cheapernet<br>Telecom         | 4 |

| APPLICATION NOTES                                                                                                                     | 5 |

| APPENDICES<br>Product Category Levels<br>Reliability Calculation Methods<br>Package Mechanical Drawings<br>Standard Military Drawings | 6 |

| SALES OFFICES                                                                                                                         | 7 |

#### **GENERAL PURPOSE A/D CONVERTERS**

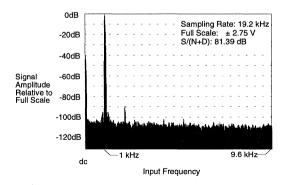

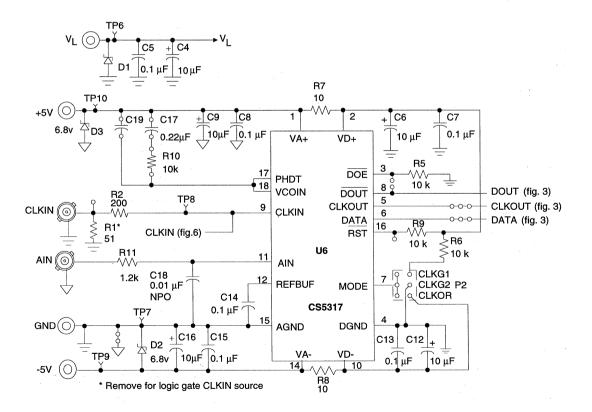

#### CS5317 16-bit Voice Band ADC

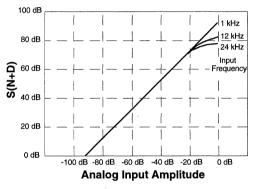

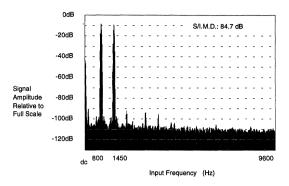

The CS5317 is well suited for a wide range of voiceband applications, from speech recognition to passive sonar. An on-chip PLL/Clock generator makes the part perfect for high-performance modems. The device features a 20 kHz word rate, a 10 kHz bandwidth, 84 dB dynamic range and 80 dB THD.

#### CS5012A, CS5014, CS5016 SAR Family

The CS5012A, CS5014 and CS5016 converters have 12, 14 & 16 bits of resolution respectively, with conversion times of 7  $\mu$ s to 16  $\mu$ s. On-chip self-calibration ensures that linearity, offset and full-scale errors remain within specification, with no missing codes.

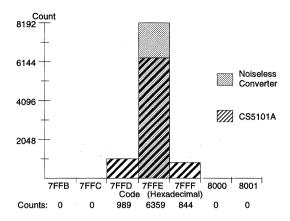

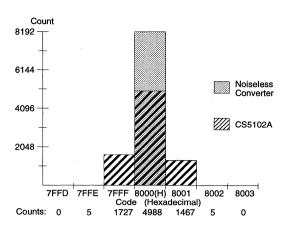

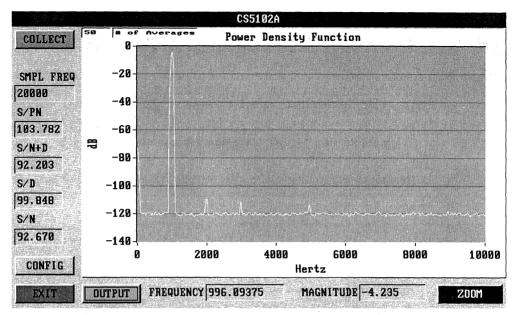

#### CS5102A 16-bit 20 kHz Low Power ADC

The CS5102A is a low power version of the CS5101A. Requiring only 44 mW from  $\pm 5$  V supplies, along with a 1 mW power down mode, the CS5102A is ideal for battery powered applications.

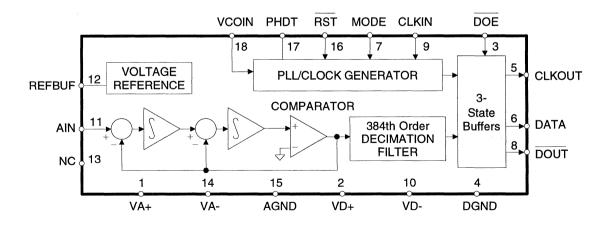

#### CS5101A, CS5126 16-bit 100 kHz ADC

The CS5101A is a 16-bit ADC capable of converting in 8  $\mu$ s, yielding sample rates of 100 kHz. A 2-channel analog input mux is included. The CS5126 is a low-cost version of the CS5101A, intended for signal processing applications.

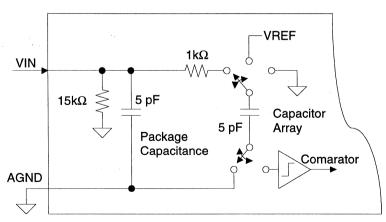

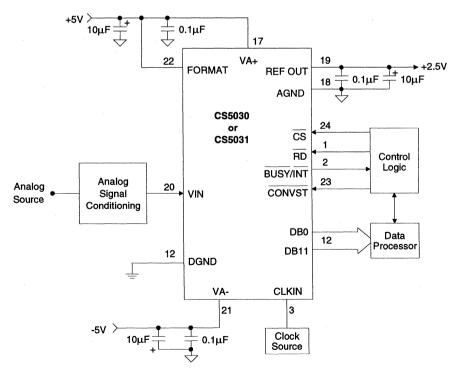

#### CS5030, CS5031, CS5032 12-bit 500kHz ADCs

The CS5030/1 feature a 1 ppm/°C on-chip reference. This yields a 12-bit ADC which has a total unadjusted error (including reference error) of  $<\pm0.5$  LSB over the military temperature range. The CS5032 is a low cost version with a 60 ppm/°C reference.

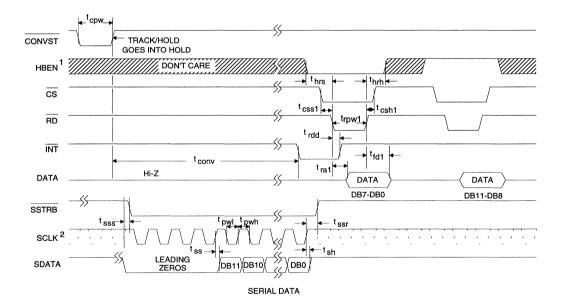

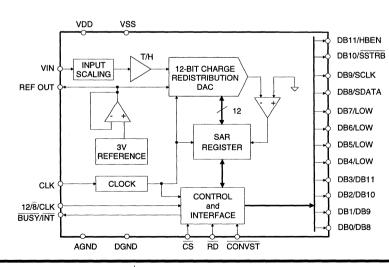

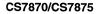

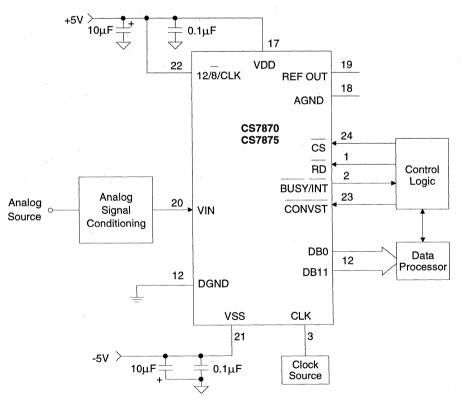

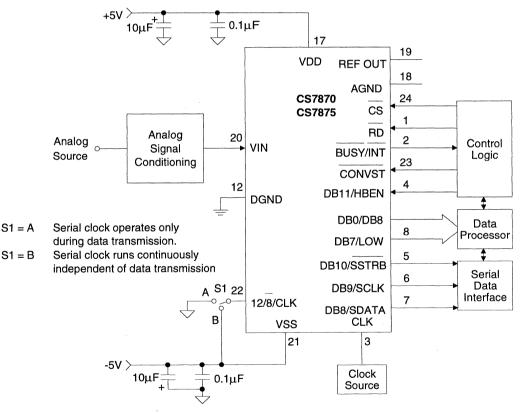

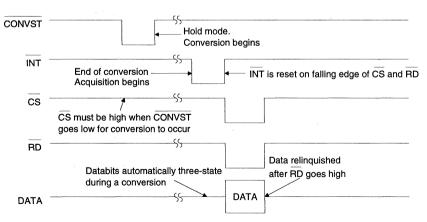

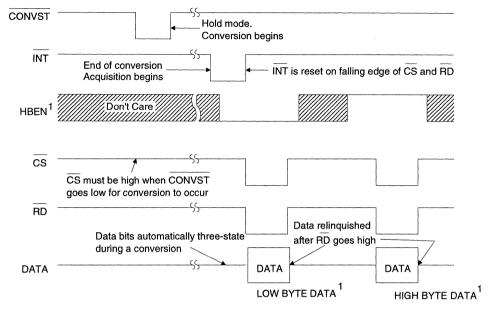

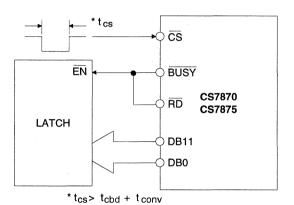

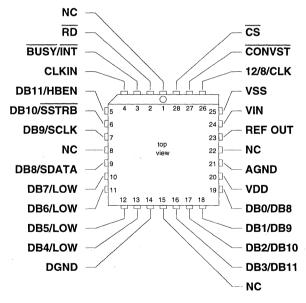

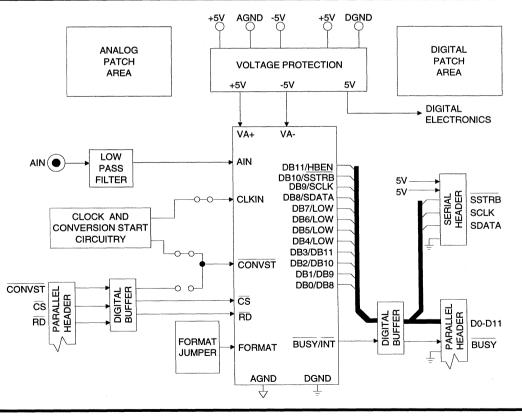

#### CS7870, CS7875 12-bit 100 kHz Sampling ADC

The CS7870 and CS7875 are complete monolithic CMOS ADCs providing 100 kHz throughput. Conversion results are available in either 12-bit parallel, two 8-bit bytes, or serial data. The CS7870 has a  $\pm 3V$  analog input range while the CS7875 accepts input signals from 0V to +5V.

| Specifications                          | CS5317         | CS5012A<br>CS5014<br>CS5016 | CS5102A            | CS5101A<br>CS5126  | CS5030<br>CS5031<br>CS5032 | CS7870<br>CS7875 |

|-----------------------------------------|----------------|-----------------------------|--------------------|--------------------|----------------------------|------------------|

| Resolution (bits)                       | 16             | 12/14/16                    | 16                 | 16                 | 12                         | 12               |

| Application                             | Modem          | GP                          | GP                 | GP ·               | GP                         | GP               |

| Throughput (kHz)                        | 20             | 100/56/50                   | 20                 | 100                | 500                        | 100              |

| Conversion Time (µs)                    | -              | 7/14/16                     | 40                 | 8                  | 2                          | 10               |

| Integral Non-Linearity                  | -              | .006/.002/<br>.001%         | .0015%             | .0015%             | .25 LSB                    | 0.25 LSB         |

| Differential (±LSB)<br>Non-Linearity    | NMC            | 0.25/0.25/<br>NMC           | NMC                | NMC                | 0.5                        | 0.5              |

| No Missing Codes                        | 16             | 12/14/16                    | 16                 | 16                 | 12                         | 12               |

| Total Harmonic<br>Distortion (%)        | .007           | .008/.003/<br>.001          | .001               | .001               | .01                        | .01              |

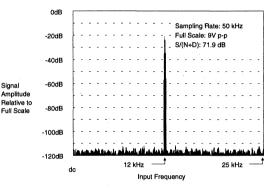

| Signal-to-Noise<br>plus Distortion (dB) | 80             | 73/83/92                    | 92                 | 92                 | 72                         | 72               |

| Dynamic Range (dB)                      | 84             | 73/83/92                    | 92                 | 92                 | 72                         | 73               |

| Power Needed (mW)                       | 220            | 150                         | 44                 | 280                | 85                         | 88               |

| Conversion Method                       | Delta<br>Sigma | Succ.<br>Approx.            | Succ.<br>Approx.   | Succ.<br>Approx.   | Succ.<br>Approx.           | Succ.<br>Approx. |

| Power Down Mode                         | -              | -                           | 1                  | 1                  | -                          | -                |

| On-Chip Sample<br>and Hold              | 1              | 1                           | 1                  | 1                  | 1                          | 1                |

| On-Chip V. Ref                          | 1              | -                           | -                  | -                  | 1                          | 1                |

| Statically Tested                       |                | 1                           | 1                  | 1                  | 1                          | 1                |

| Dynamically Tested                      | 1              | 1                           | 1                  | 1                  | 1                          | 1                |

| Temperature Range                       | Com<br>Ind     | Com<br>Ind<br>Mil           | Com<br>Ind<br>Mil  | Com<br>Ind<br>Mil  | Ind<br>Mil                 | Ind<br>Mil       |

| Number of Pins (DIP)                    | 18             | 40                          | 28                 | 28                 | 24                         | 24               |

| Packages                                | DIP<br>SOIC    | DIP<br>PLCC<br>LCC          | DIP<br>PLCC<br>LCC | DIP<br>PLCC<br>LCC | DIP<br>SOIC                | DIP<br>PLCC      |

#### INDUSTRIAL MEASUREMENT AND SEISMIC A/D CONVERTERS

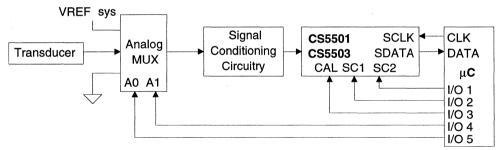

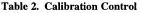

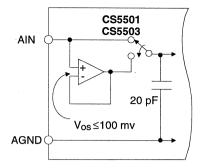

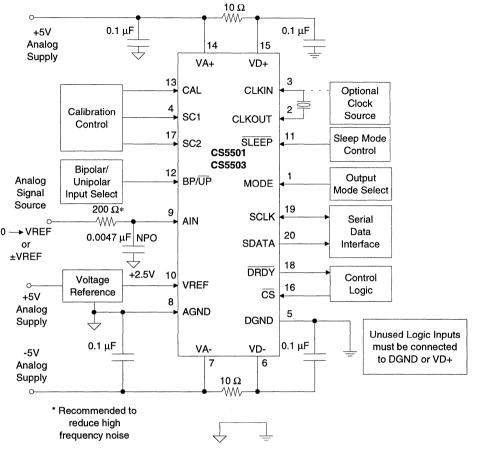

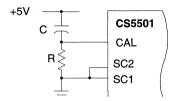

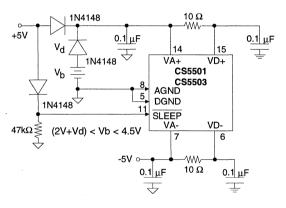

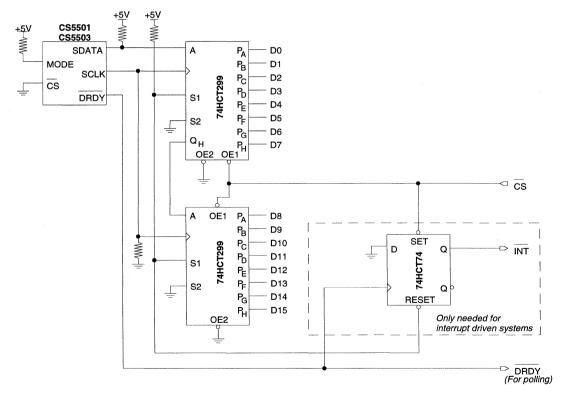

#### CS5501, CS5503 16/20-bit DC Measurement ADC

The CS5501 and CS5503 feature an on-chip, 6pole, low-pass filter, with adjustable corner frequencies from 0.1 Hz to 10 Hz. The ADC's achieve linearity errors of 0.0007%, with no missing codes. A highly flexible serial interface, along with 25 mW power consumption, all in a 20 pin package, make the parts ideal for weigh scale and process control applications.

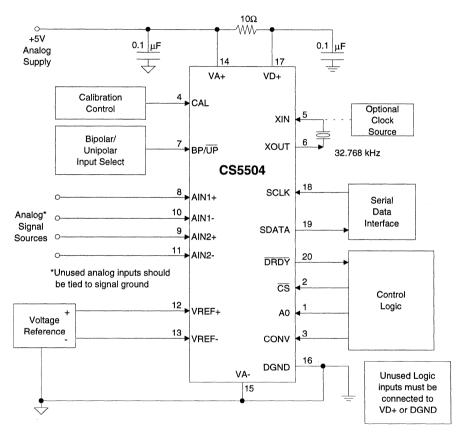

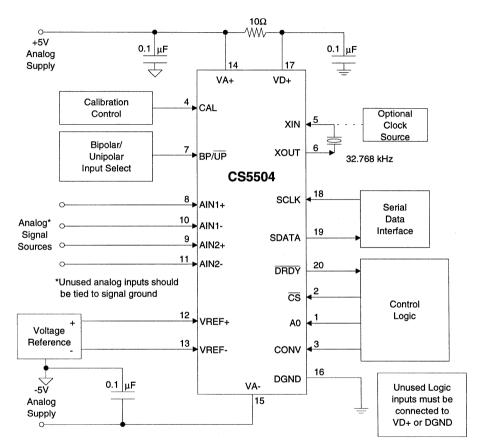

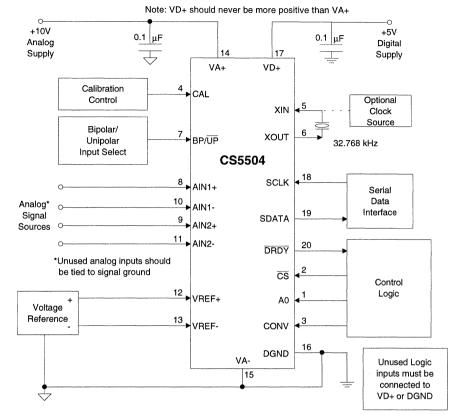

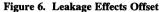

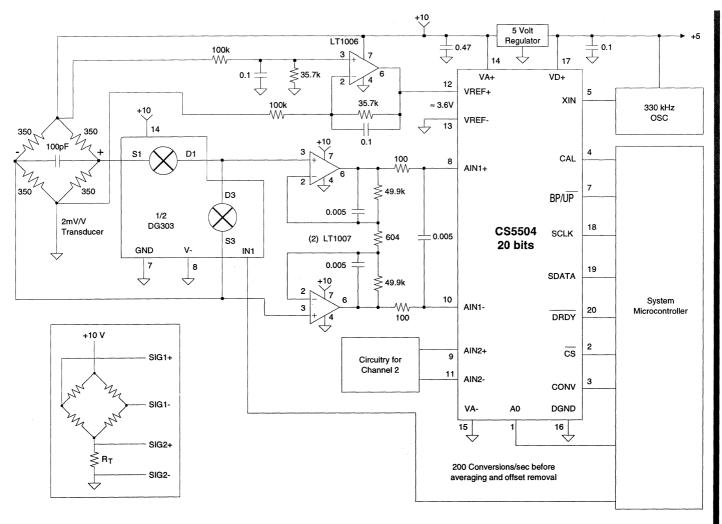

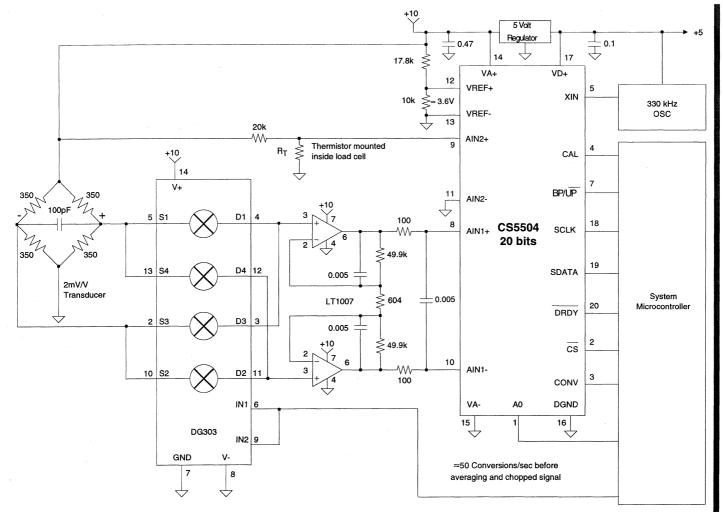

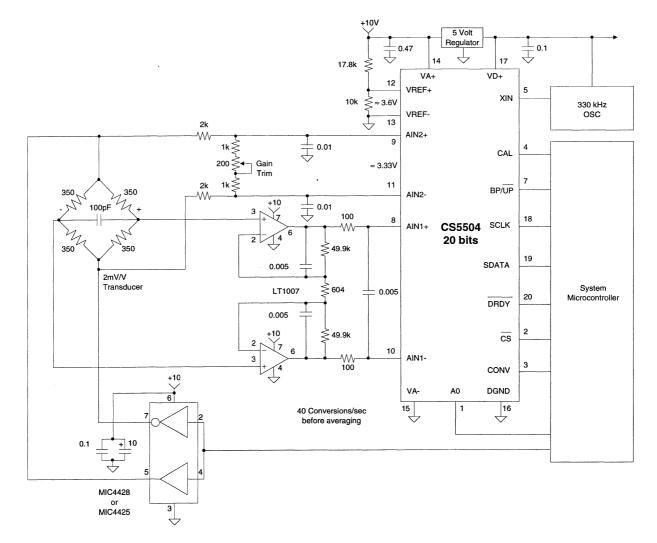

#### CS5504/5/6/7/8/9 1, 2 & 4-channel, 16/20-bit DC Measurement ADC

Very low power consumption of 1.7 mW, along with an optional 1, 2, or 4-channel input mux, make this part ideal for process control and hand held meter applications. These ADC's are available in 16 or 20 bit versions.

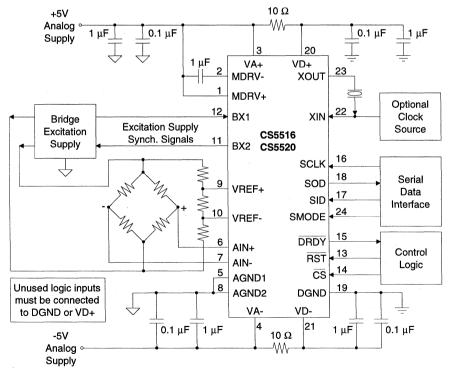

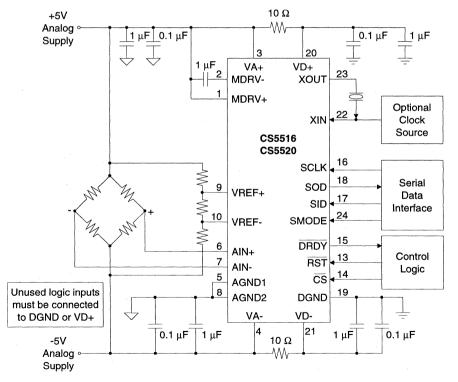

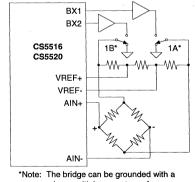

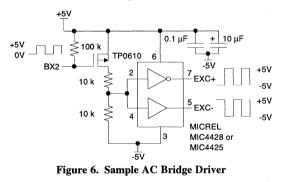

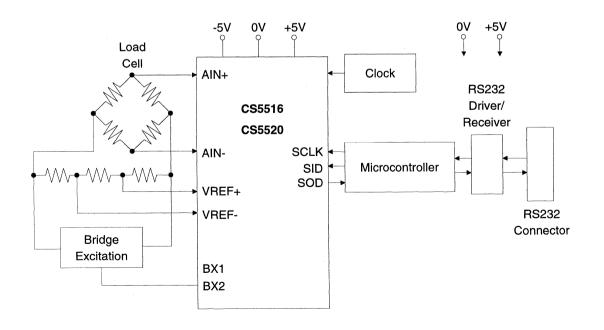

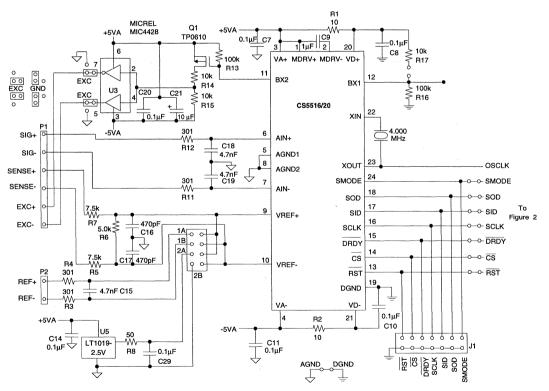

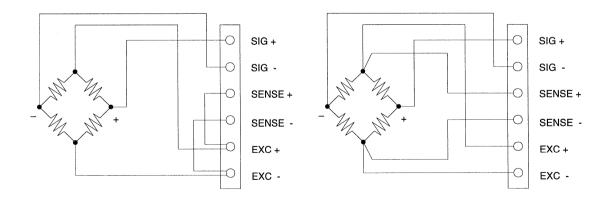

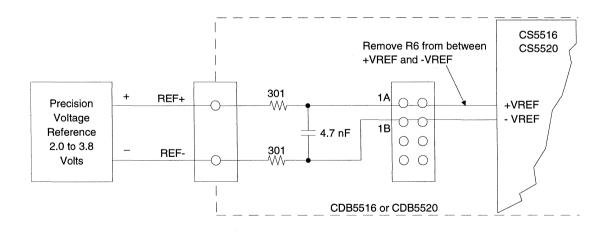

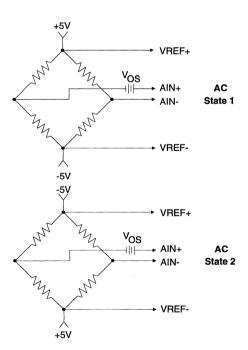

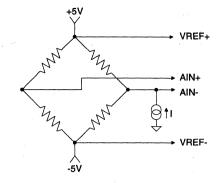

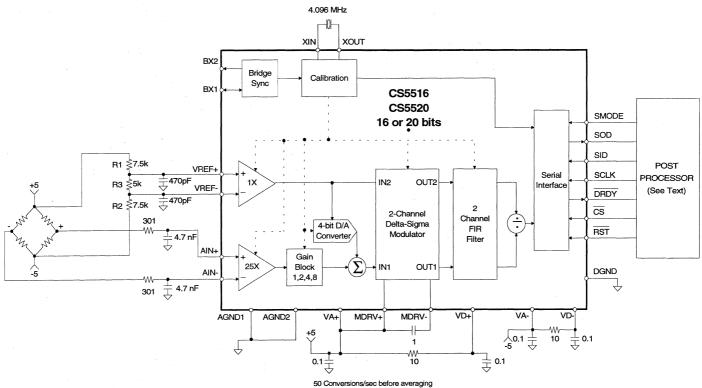

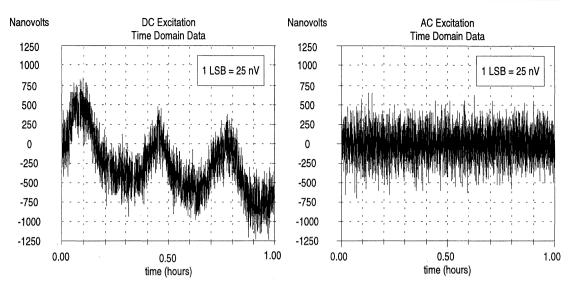

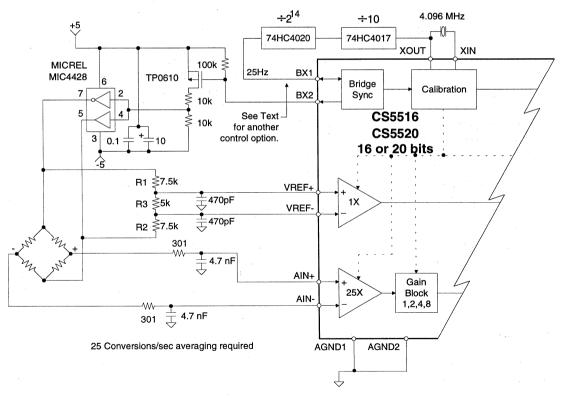

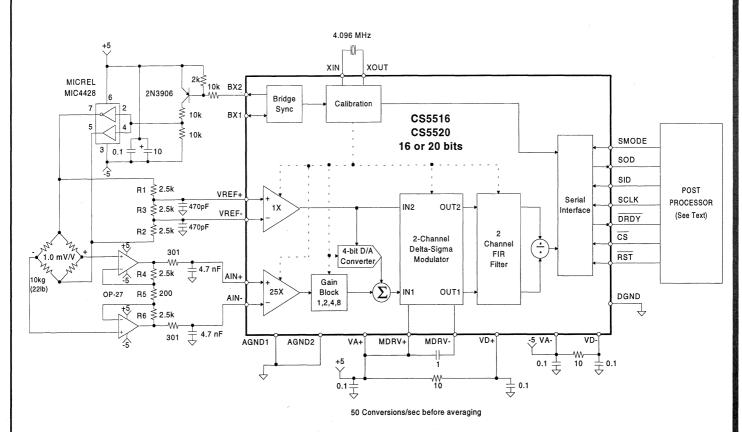

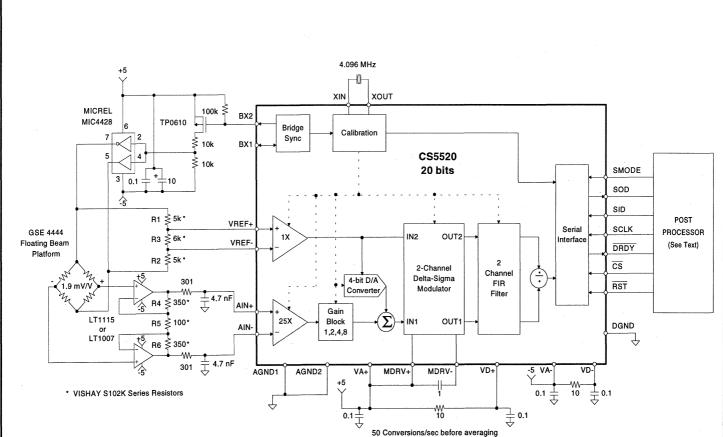

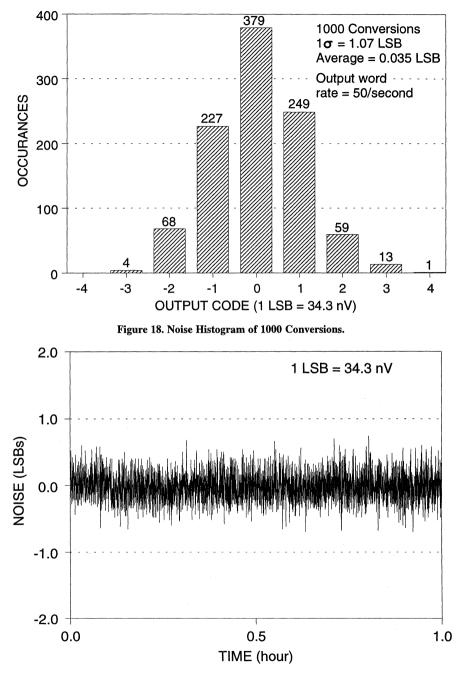

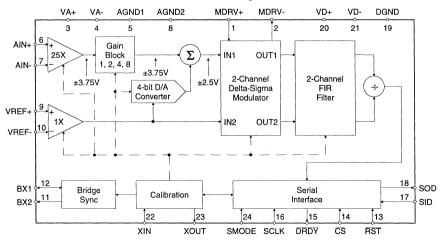

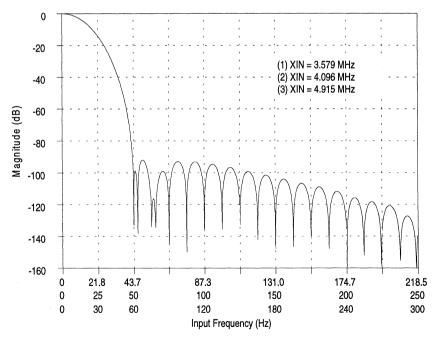

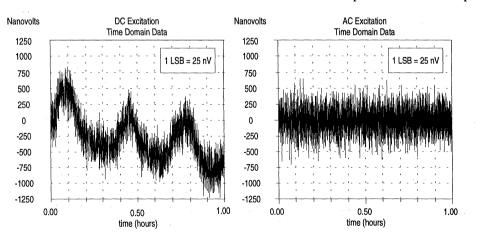

#### CS5516, CS5520 16/20-bit Bridge Transducer ADC

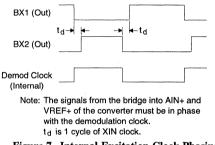

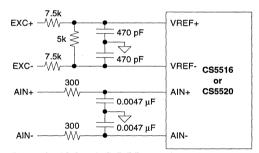

The CS5516 and CS5520 are complete solutions for digitizing low level signals from strain gauges, load cells and pressure transducers. The devices offer an on-

chip software programmable instrumentation amplifier, choice of AC or DC bridge excitation, software selectable reference and signal demodulation.

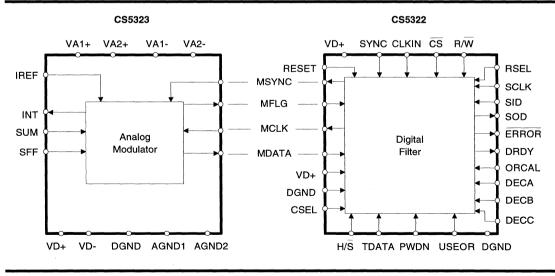

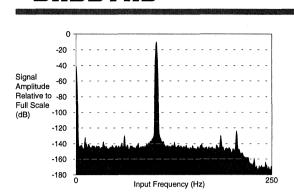

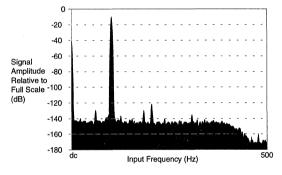

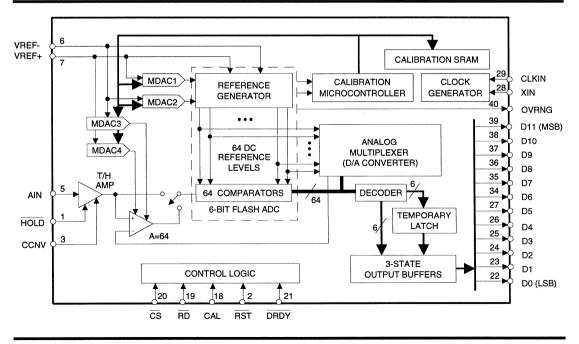

### CS5321, CS5322, CS5323, CS5324 24-bit Variable Bandwidth ADC

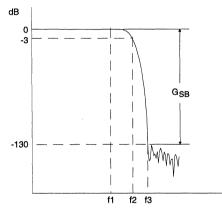

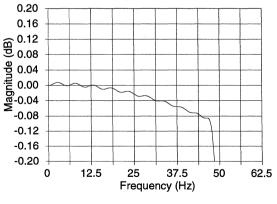

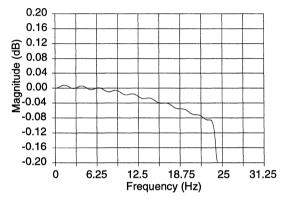

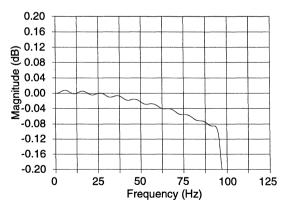

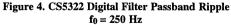

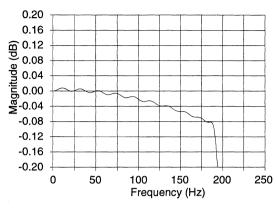

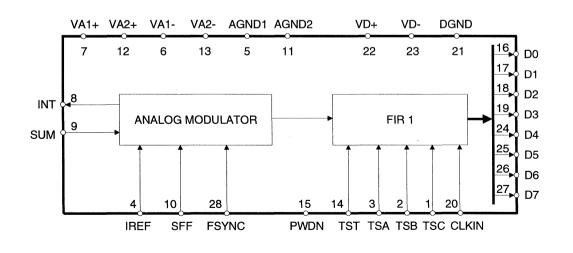

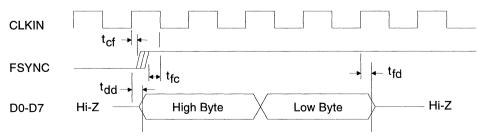

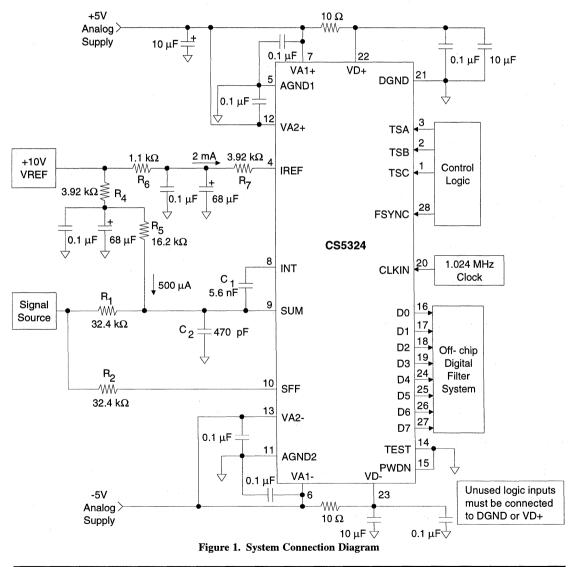

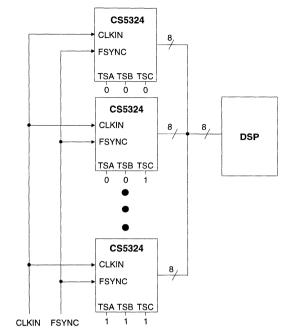

The CS5321 or CS5323 modulator, combined with the CS5322 digital filter, offers >120 dB dynamic range in the DC to 500 Hz frequency band. Seven different filter corner frequencies and output update rates are offered, allowing the ADC to be optimized for different types of seismic measurements. The CS5324 includes a modulator and the first stage of digital filtering, allowing users to implement their own final filter stage.

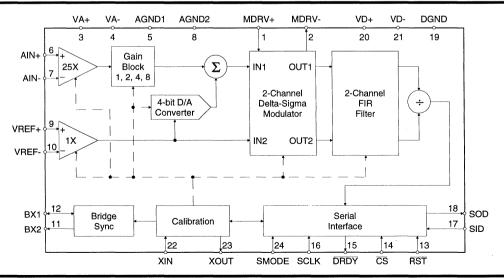

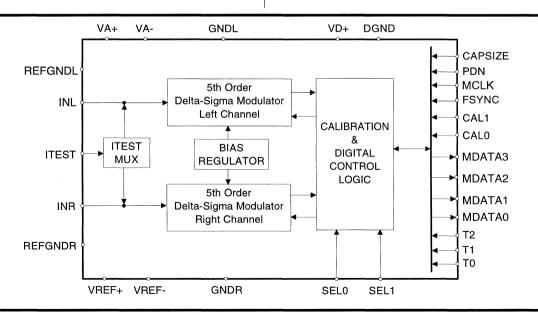

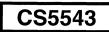

# CS5542, CS5543, 22-bit, 8-channel Data Acquisition System

The CS5542 is a 2-channel, 5th order delta-sigma modulator intended for direct digitization of transducer currents. The CS5543 is an 8-channel digital FIR filter. Up to four CS5542's may be connected with one CS5543 to form an 8-channel data acquisition system. The output word rate is 1000 Hz per channel.

| Specifications                       | CS5501<br>CS5503 | CS5504 CS5507<br>CS5505 CS5508<br>CS5506 CS5509 | CS5516<br>CS5520 | CS5321 CS5323<br>CS5322 CS5324 | CS5542<br>CS5543 |

|--------------------------------------|------------------|-------------------------------------------------|------------------|--------------------------------|------------------|

| Input Bandwidth                      | 10 Hz            | 10 Hz                                           | 12 Hz            | 500 Hz                         | 250/500 Hz       |

| Resolution (bits)                    | 16/20            | 16/20                                           | 16/20            | 24                             | 22               |

| Application                          |                  | DC Measurement                                  |                  | Seismic                        | DC Measurement   |

| Throughput (kHz)                     | 4                | 100/200Hz                                       | 60Hz             | -                              | 1KHz             |

| Integral Non-Linearity               | .0007%           | .0015%                                          | .0007%           | -                              | .001%            |

| Differential (±LSB)<br>Non-Linearity | 0.125/<br>NMC    | 0.125                                           | 0.5              | NMC                            | 0.5              |

| Total Harmonic<br>Distortion (%)     | -                | -                                               | -                | .0003                          | -                |

| Dynamic Range (dB)                   | -                | -                                               | -                | 120                            | 113              |

| Power Needed (mW)                    | 25               | 3                                               | 40               | 150                            | 80/75            |

| Conversion Method                    | Delta<br>Sigma   | Delta<br>Sigma                                  | Delta<br>Sigma   | Delta<br>Sigma                 | Delta<br>Sigma   |

| Power Down Mode                      | 1                | 1                                               | 1                | 1                              | 1                |

| On-Chip Sample<br>and Hold           | 1                | 1                                               | 1                | 1                              | 1                |

| On-Chip V. Ref                       | -                | 1                                               | -                | -                              | -                |

| On-Chip Filtering                    | 1                | 1                                               | 1                | 1                              | 1                |

| Temperature Range                    | Ind, Mil         | Ind                                             | Ind              | Ind                            | Ind              |

| Number of Pins (DIP)                 | 20               | 20/24                                           | 24               | 28                             | 28/44            |

| Packages                             | DIP<br>SOIC      | DIP<br>SOIC                                     | DIP<br>SOIC      | PLCC                           | PLCC             |

NMC = No Missing Codes

#### **HIGH SPEED A/D CONVERTERS**

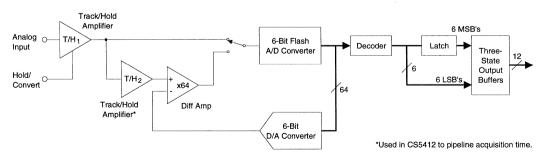

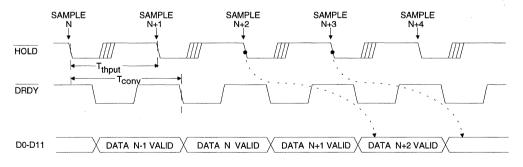

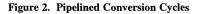

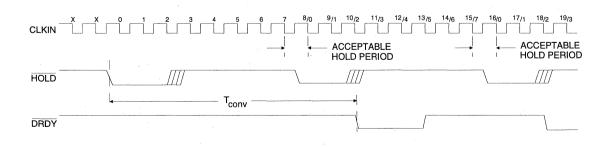

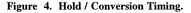

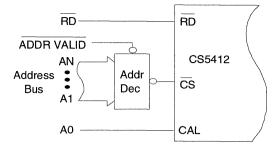

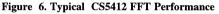

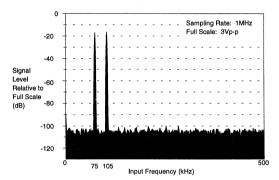

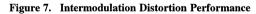

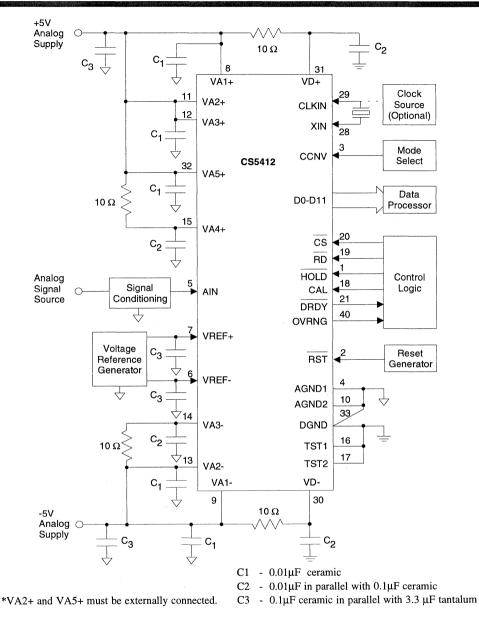

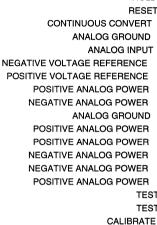

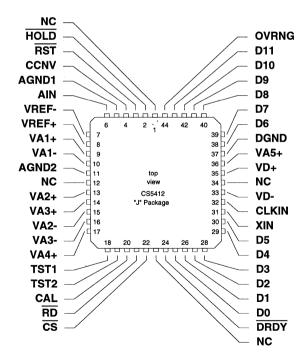

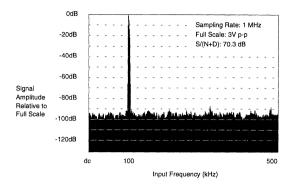

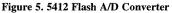

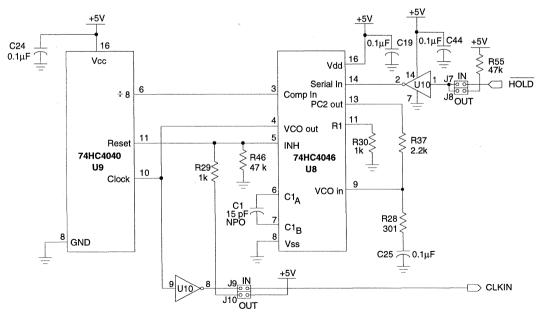

#### CS5412 12-bit 1 MHz ADC

Using a 2-step flash approach, the CS5412 achieves 12-bit performance at a 1 MHz sample rate. Self calibration ensures accuracy over time and the military temperature range. Available in both DIP and J-lead LCC packages, with on-chip S/H, the IC offers a very compact ADC solution.

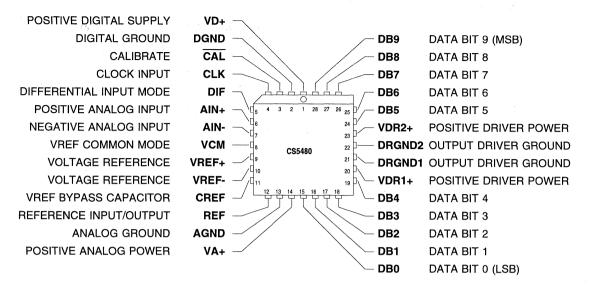

#### CS5480, CS5481 10-bit 40/20 MHz ADC

The CS5480 is a monolithic CMOS 10-bit sampling ADC capable of 40 Msps conversion rates. The CS5481 is a 10-bit sampling ADC capable of 20 Msps conversion rates. Digital inputs are CMOS and TTL compatible, and the digital outputs are CMOS compatible. Output data is available in offset binary format.

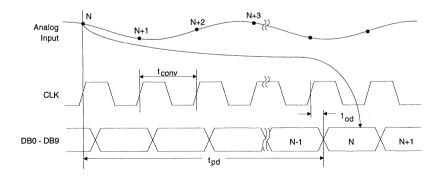

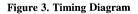

#### CS5490 12-bit 20MHz ADC

The CS5490 is a 12-bit sampling ADC capable of 20 Msps conversion rates. Digital inputs are CMOS and TTL compatible, and the digital outputs are CMOS compatible. Output data is available in offset binary format.

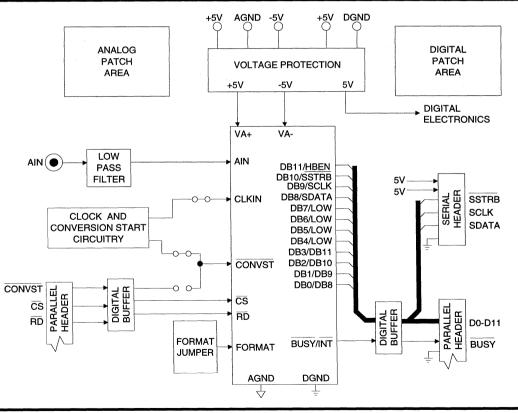

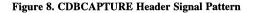

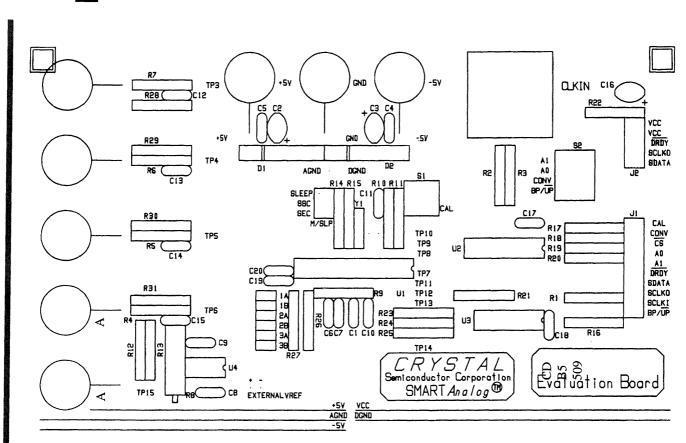

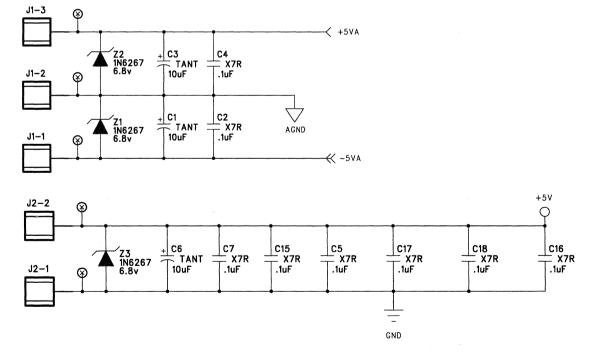

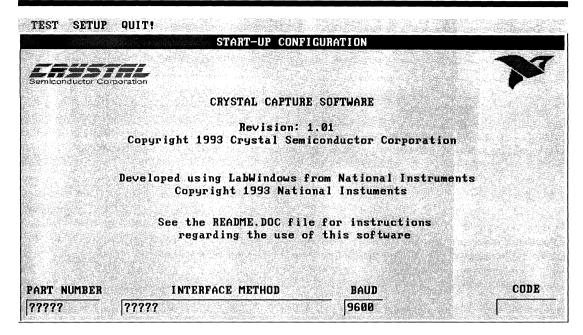

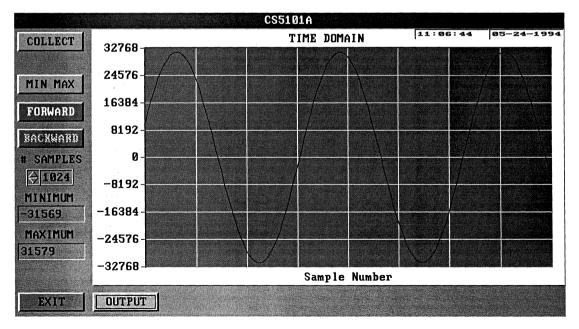

#### **CDBCAPTURE SYSTEM**

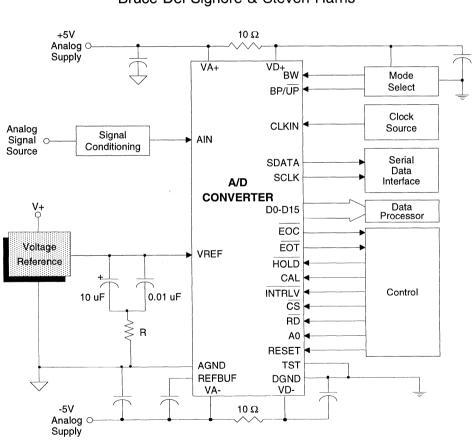

#### Data Capture and Interface Board for a PC

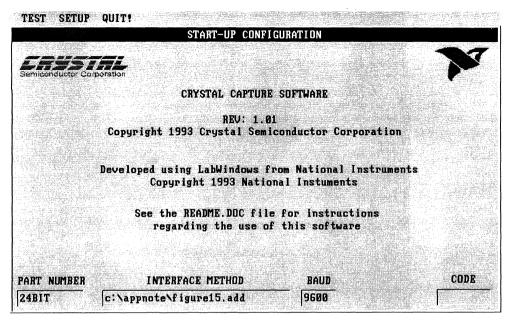

The CAPTURE interface board is a development tool that can be easily interface to Crystal Semiconductor Evaluation boards. Application software, developed with Lab Windows, adjusts the CAP-TURE interface board for the appropriate signal timing and polarity, coding format and number of bits.

| Specifications                       | CS5412            | CS5480     | CS5481     | CS5490     |

|--------------------------------------|-------------------|------------|------------|------------|

| Input Bandwidth                      | 4 MHz             | 200 MHz    | 200 MHz    | 200 MHz    |

| Resolution (bits)                    | 12                | 10         | 10         | 12         |

| Application                          | GP Fast           | High Speed | High Speed | High Speed |

| Throughput                           | 1 MHz             | 40 MHz     | 20 MHz     | 20 MHz     |

| Integral Non-Linearity (±LSB)        | 1                 | 1          | 1          | 1          |

| Differential Non-Linearity (±LSB)    | 0.9               | 0.5        | 0.5        | 0.5        |

| No Missing Codes                     | 12                | 10         | 10         | 12         |

| Total Harmonic Distortion            | -78 dB            | -54 dB     | -54 dB     | -63 dB     |

| Signal-to-Noise plus Distortion (dB) | 70                | 58         | 58         | 62         |

| Dynamic Range (dB)                   | 70                | 62         | 62         | 70         |

| Power Needed (mW)                    | 750               | 375        | 225        | 225        |

| Conversion Method                    | 2-Step<br>Flash   | Pipeline   | Pipeline   | Pipeline   |

| On-Chip Sample and Hold              | /                 | 1          | 1          | 1          |

| On-Chip V. Ref                       | -                 | 1          | 1          | 1          |

| Temperature Range                    | Com<br>Ind<br>Mil | Ind        | Ind        | Ind        |

| Number of Pins                       | 40/44             | 28         | 28         | 44         |

| Packages                             | DIP<br>JLCC       | PLCC       | PLCC       | PLCC       |

NMC = No Missing Codes

GP = General Purpose

## DATA ACQUISITION PRODUCTS

|     | - Introduction, Contents and User's Guide                       |   |  |   | 2-1   |

|-----|-----------------------------------------------------------------|---|--|---|-------|

|     | - CS5012A/4/6 16, 14, & 12-Bit, Self-Calibrating A/D Converters |   |  |   | 2-7   |

|     | - CDB5012A/4/6 Evaluation Board for CS5012A/4/6 .               |   |  |   | 2-48  |

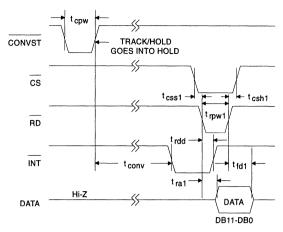

| NEW | - CS5030/1 12-Bit, 500 kHz, Sampling A/D Converters             | • |  |   | 2-55  |

| NEW | - CS5032 12-Bit, 500 kHz, Sampling A/D Converters               |   |  |   |       |

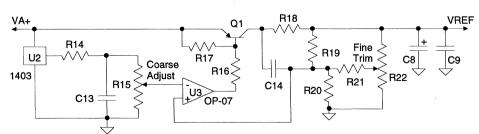

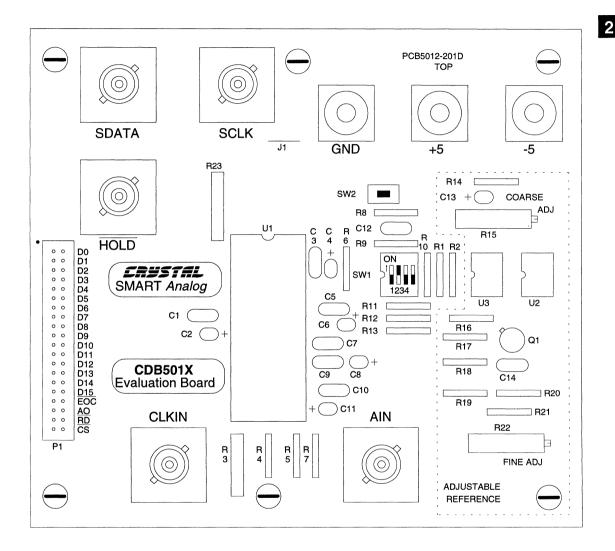

|     | - CDB5030/1/2 Evaluation Board for CS5032                       |   |  |   | 2-104 |

|     | - CS5101A/2A 16-Bit, 100 kHz/20 kHz A/D Converters              |   |  |   |       |

|     | - CDB5101A/2A Evaluation Board for CS5101A/2A .                 |   |  |   | 2-149 |

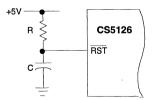

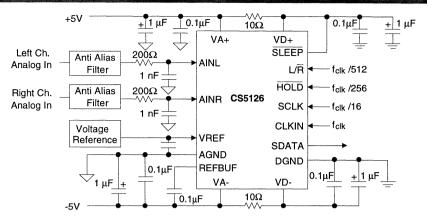

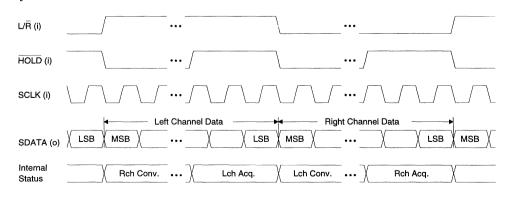

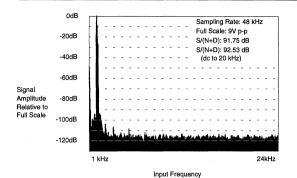

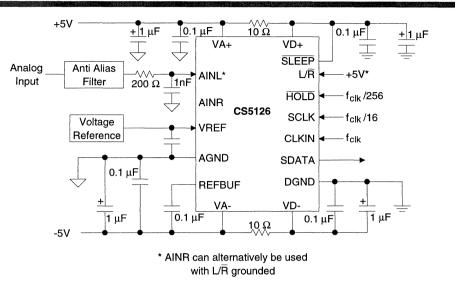

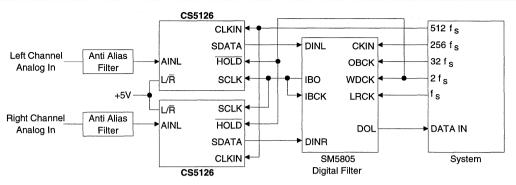

|     | - CS5126 16-Bit, Stereo A/D Converter for Digital Audio         |   |  |   | 2-159 |

|     | - CDB5126 16-Bit, Stereo A/D Converter for Digital A            |   |  |   |       |

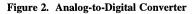

|     | - CS5317 16-Bit, 20 kHz Oversampling A/D Converter              |   |  |   | 2-189 |

|     | - CDB5317 Evaluation Board for CS5317                           |   |  |   | 2-212 |

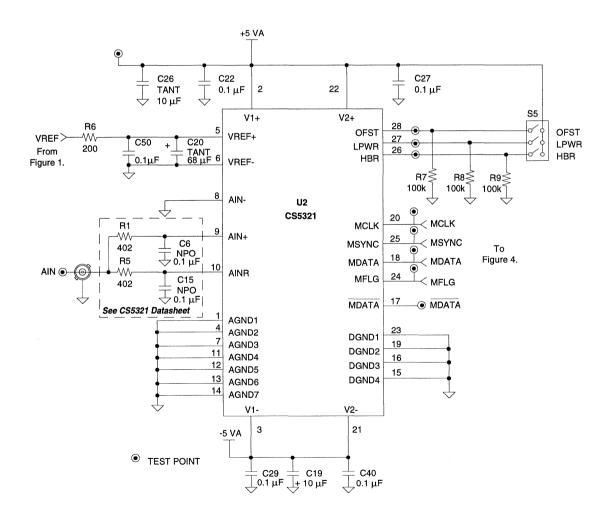

| NEW | - CS5321 High Dynamic Range Delta-Sigma Modulator               |   |  |   | 2-219 |

|     | - CDB5321 Evaluation Board for CS5321                           |   |  |   | 2-233 |

|     | - CS5322/3 24-Bit Variable Bandwidth A/D Converter              | • |  |   | 2-245 |

|     | - CDB5322/3 Evaluation Board for CS5322/3                       |   |  |   | 2-272 |

|     | - CS5324 120 dB, 500 Hz Oversampling A/D Converter              |   |  |   |       |

|     | - CDB5324 Evaluation Board for CS5324                           |   |  |   |       |

|     | - CS5412 12-Bit, 1MHz Self-Calibrating A/D Converter            |   |  |   |       |

|     | - CDB5412 Evaluation Board for CS5412                           |   |  |   | 2-335 |

| NEW | - CS5480 10-Bit, 40 MHz, A/D Converter                          |   |  |   | 2-345 |

| NEW | - CS5481 10-Bit, 20 MHz, A/D Converter                          |   |  |   | 2-355 |

| NEW | - CS5490 12-Bit, 20 MHz, A/D Converter                          |   |  |   |       |

|     | - CS5501/3 Low-Cost, 16 & 20-Bit Measurement A/D Converter      |   |  |   |       |

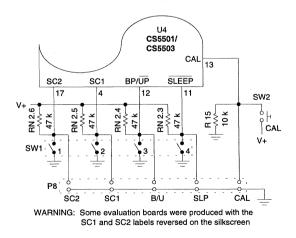

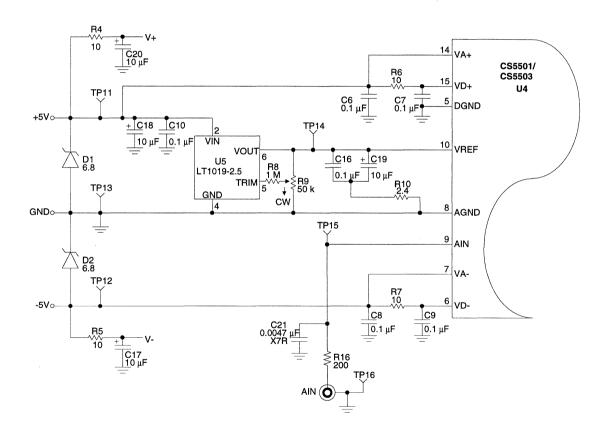

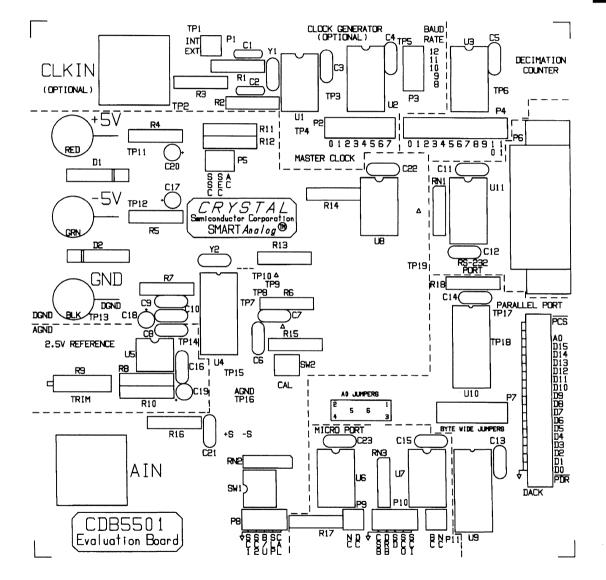

|     | - CDB5501/3 Evaluation Board for CS5501/3                       |   |  | • | 2-407 |

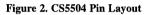

| NEW | - CS5504 Low Power, 20-Bit A/D Converter                        |   |  |   | 2-421 |

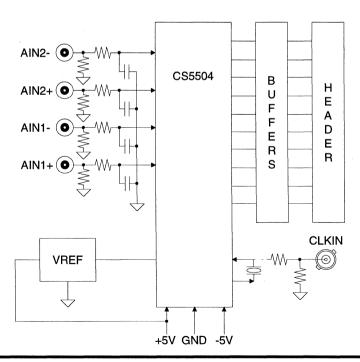

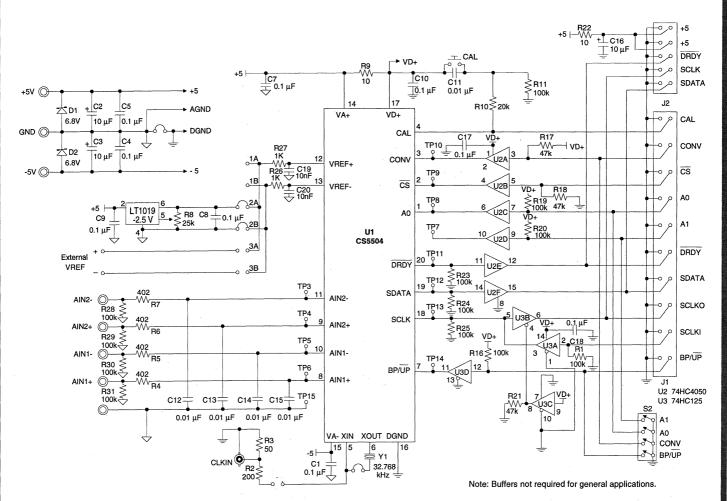

|     | - CDB5504 Evaluation Board for CS5504                           |   |  |   | 2-444 |

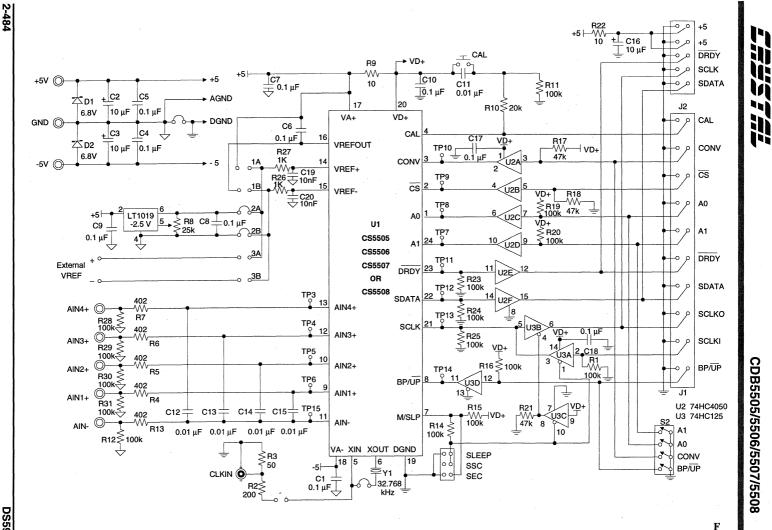

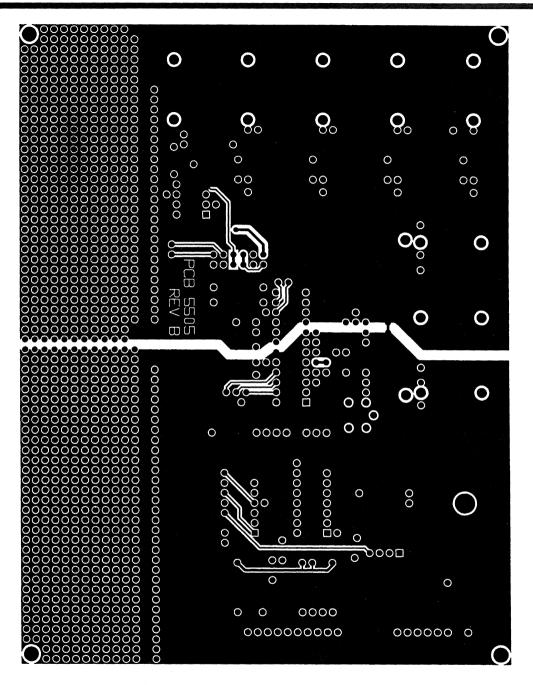

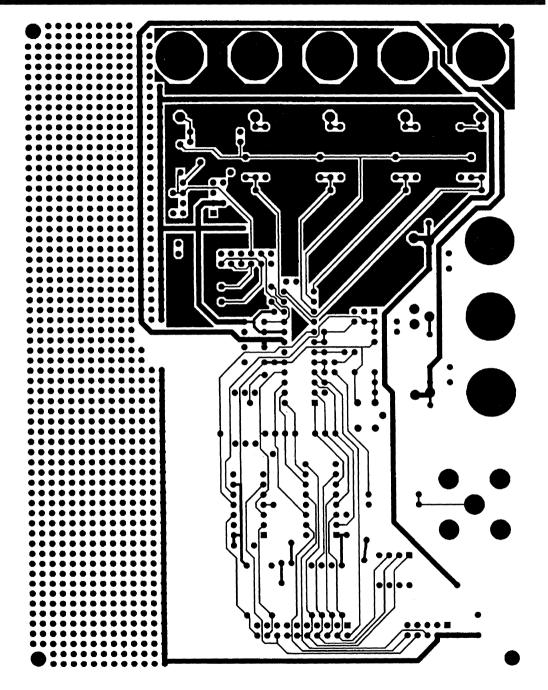

|     | - CS5505/6/7/8 Very Low Power, 16-Bit and 20-Bit A/D Converted  |   |  |   |       |

|     | - CDB5505/6/7/8 Evaluation Board for CS5505/6/7/8               |   |  |   |       |

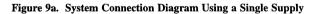

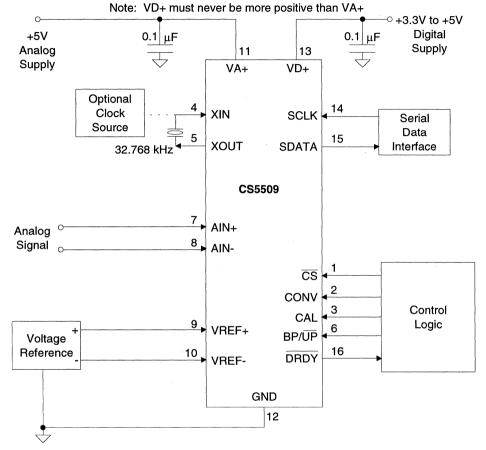

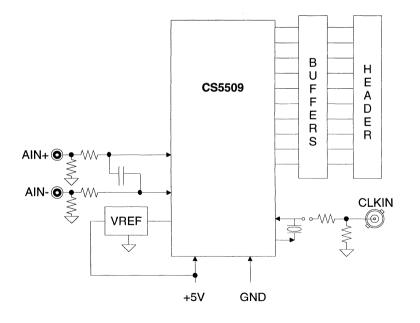

| NEW | - CS5509 Single Supply, 16-Bit A/D Converter                    | • |  |   | 2-489 |

|     | - CDB5509 Evaluation Board for CS5509                           | • |  | • | 2-511 |

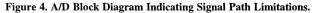

|     | - CS5516/20 16-Bit/20-Bit Bridge Transducer A/D Converters .    |   |  |   |       |

|     | - CDB5516/20 Evaluation Board for CS5516/20                     |   |  |   |       |

| NEW | - CS5542 Dual Channel Current-Input Modulator                   | • |  |   | 2-559 |

| NEW | - CS5543 8-Channel Digital Decimation Filter                    |   |  |   | 2-561 |

| NEW | - CS7870/5 12-Bit, 100 kHz Sampling A/D Converter               |   |  |   | 2-563 |

|     |                                                                 |   |  |   |       |

|     | - CDBCAPTURE Evaluation Board                                   |   |  |   |       |

# • Notes •

## 16, 14 & 12-Bit, Self-Calibrating A/D Converters

## Features

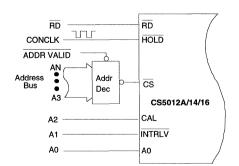

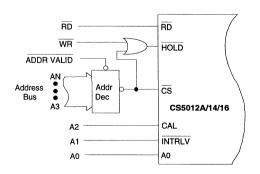

- Monolithic CMOS A/D Converters Microprocessor Compatible Parallel and Serial Output Inherent Track/Hold Input

- True 12, 14 and 16-Bit Precision

- Conversion Times: CS5016 16.25 μs CS5014 14.25 μs CS5012A 7.20 μs

- Self Calibration Maintains Accuracy Over Time and Temperature

- Low Power Dissipation: 150 mW

## **General Description**

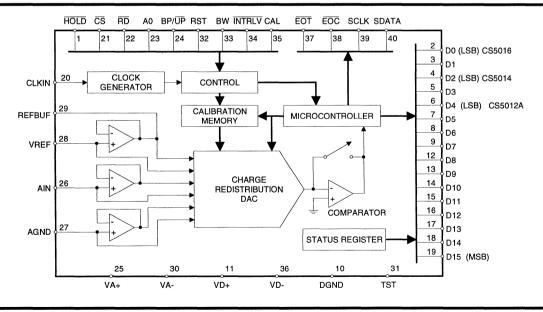

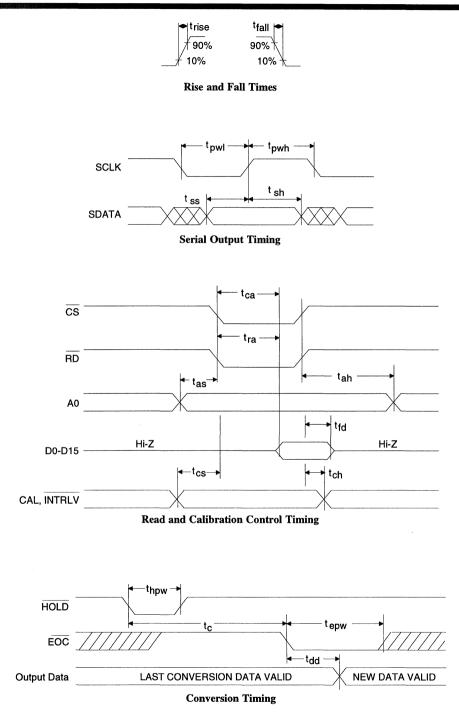

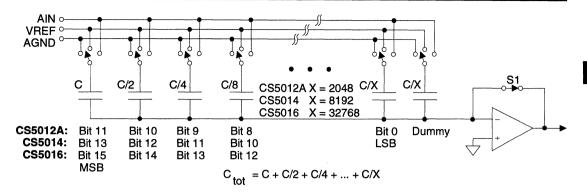

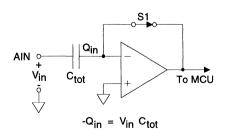

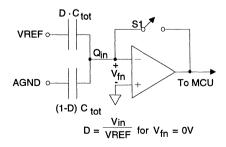

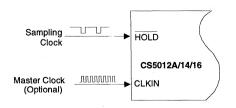

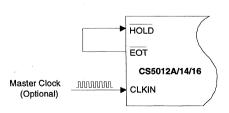

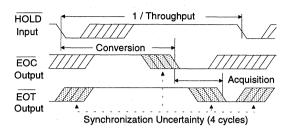

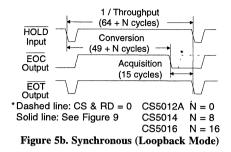

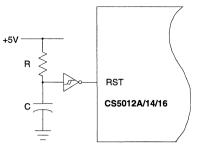

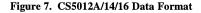

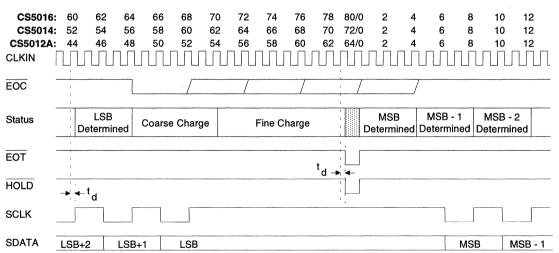

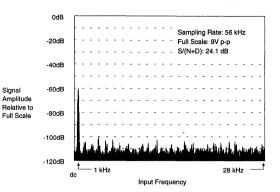

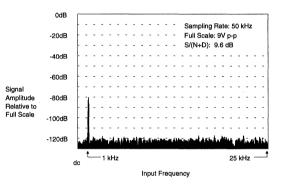

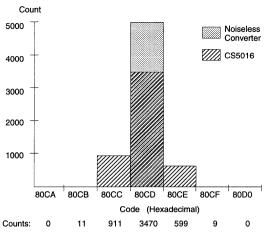

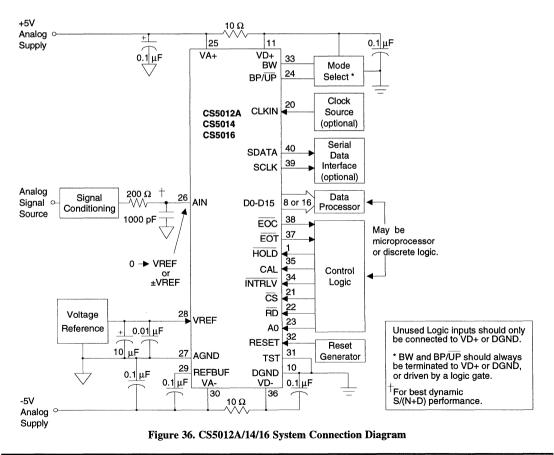

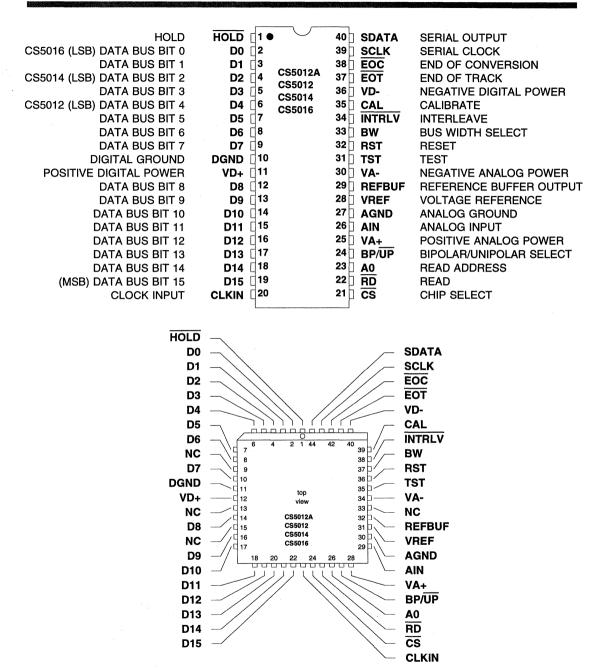

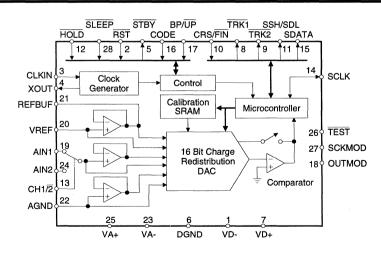

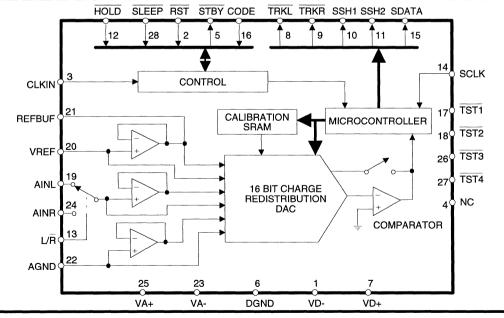

The CS5012A/14/16 are 12, 14 and 16-bit monolithic analog to digital converters with conversion times of 7.2 $\mu$ s, 14.25 $\mu$ s and 16.25 $\mu$ s. Unique self-calibration circuitry insures excellent linearity and differential non-linearity, with no missing codes. Offset and full scale errors are kept within 1/2 LSB (CS5012A/14) and 1 LSB (CS5016), eliminating the need for calibration. Unipolar and bipolar input ranges are digitally selectable.

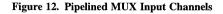

The pin compatible CS5012A/14/16 consist of a DAC, conversion and calibration microcontroller, oscillator, comparator, microprocessor compatible 3-state I/O, and calibration circuitry. The input track-and-hold, inherent to the devices' sampling architecture, acquires the input signal after each conversion using a fast slewing on-chip buffer amplifier. This allows throughput rates up to 100 kHz (CS5012A), 56 kHz (CS5014) and 50 kHz (CS5016).

An evaluation board (CDB5012/14/16) is available which allows fast evaluation of ADC performance.

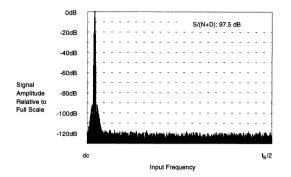

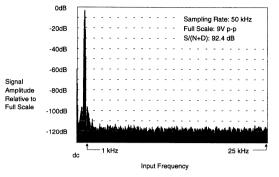

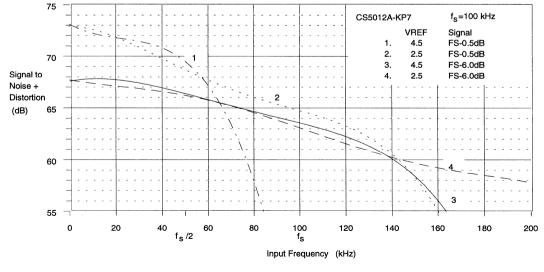

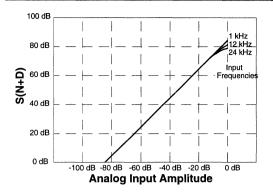

Low Distortion

ORDERING INFORMATION: Pages 2-45, 2-46, & 2-47

Crystal Semiconductor Corporation P.O. Box 17847, Austin, TX 78760 (512) 445 7222 FAX: (512) 445 7581

Copyright © Crystal Semiconductor Corporation 1995 (All Rights Reserved) MAR '95 DS14F6 **2-7**

## **CS5012A ANALOG CHARACTERISTICS** ( $T_A = T_{MIN}$ to $T_{MAX}$ ; VA+, VD+ = 5V;

VA-, VD- = -5V; VREF = 2.5V to 4.5V; fclk = 6.4 MHz for -7, 4 MHz for -12; Analog Source Impedance = 200Ω)

|                                                                                           |                       | C        | S5012A        | -K   | C        | S5012A        | -В   | C        | S5012-        | Т    |                                        |

|-------------------------------------------------------------------------------------------|-----------------------|----------|---------------|------|----------|---------------|------|----------|---------------|------|----------------------------------------|

| Parameter*                                                                                |                       | Min      | Тур           | Max  | Min      | Тур           | Max  | Min      | Тур           | Max  | Units                                  |