## **PALASM 4 VERSION 1.5 RELEASE NOTES**

Л

© 1992 Advanced Micro Devices, Inc. P.O. Box 3453 Sunnyvale, CA 94088-3453 TWX: 910339-9280 TELEX: 34-6306 TOLL FREE: 800-538-8450

APPLICATIONS HOTLINE: 800-222-9323

Advanced Micro Devices reserves the right to make changes in specifications at any time and without notice. The information furnished by Advanced Micro Devices is believed to be accurate and reliable. However, no responsibility is assumed by Advanced Micro Devices for its use, nor for any infringements of patents or other rights of third parties resulting from its use. No license is granted under any patents or patent rights of Advanced Micro Devices.

MS-DOS and Windows are trademarks of Microsoft Corporation.

PAL and PALASM are registered trademarks, and MACH a trademark of Advanced Micro Devices, Inc.

QEMM is a registered trademark of Quarterdeck Office Systems. DR-DOS is a trademark of Digital Research

| CHAPTER 1. PALASM 4 VERSION 1.5 GENERAL NOTES                        |                                       |

|----------------------------------------------------------------------|---------------------------------------|

| 1.1 Operating System Compatibility                                   |                                       |

| 1.1.1 MS-DOS™ 5.0                                                    |                                       |

| 1.1.2 Memory Managers and the Extended Memory Version PALASM 4       |                                       |

| 1.1.3 DR-DOS                                                         |                                       |

| 1.1.4 Microsoft Windows®                                             | 5                                     |

| 1.1.5 IBM OS/2™                                                      | 5                                     |

| 1.1.6 Networks                                                       |                                       |

| 1.2 Changes to the Installation Program                              | 5                                     |

| 1.3 Installing From an Alternate Drive                               |                                       |

| 1.4 Extended Memory Problems Reported With IBM/AT®s and Compatibles  | 5                                     |

| 1.4.1 Designs Not Compiling                                          | 5                                     |

| 1.4.2 BIOS ROMs and Early IBM/AT Compatibles                         | 6                                     |

| 1.5 Documentation Errors                                             |                                       |

|                                                                      |                                       |

| CHAPTER 2. GENERAL OPERATION                                         |                                       |

| 2.1 Menu Changes - Minimizer                                         |                                       |

| 2.2 Simulator Usage Notes                                            |                                       |

| 2.2.1 Devices Still Supported by the Old Simulator (SIM)             |                                       |

| 2.2.2 Assumptions Made by Previous Versions of the Current Simulator |                                       |

| 2.2.3 Correct Modeling of Registers and Latches                      |                                       |

| 2.2.4 Programer Emulation at Power-Up                                |                                       |

| 2.2.5 Power-Up Sequence                                              |                                       |

| 2.2.6 Software Preload Sequence                                      |                                       |

| 2.2.7 Full Evaluation of Input Pins                                  |                                       |

| 2.2.8 Driving Active-Low and Active-High Clocks for the MACH215      | 11                                    |

| 2.2.9 Product-Term-Driven Clocks                                     |                                       |

| 2.2.10 Simultaneous Events                                           |                                       |

| 2.2.11 Power-up Preload on Floating Pins                             |                                       |

| 2.2.12 Simulation of Three-State Pins for Input and Output           |                                       |

| 2.2.13 Input Signal Ordering                                         |                                       |

| CHAPTER 3. AMD MACH FITTER VERSION 1.5                               |                                       |

| 3.1 General Operation                                                |                                       |

| 3.1.1 Fitting Process                                                |                                       |

| 3.1.2 Tristate Resources in MACH 1 Devices                           |                                       |

| 3.1.3 How to Use Latches on MACH Devices                             |                                       |

| 3.1.4 Save Old Versions of the AMD Fitter and PALASM Software        |                                       |

| 3.2 New Behavioral Features of the AMD MACH Fitter                   |                                       |

| 3.2.1 Product Term Reservation for Logic Functions                   |                                       |

| 3.2.2 Unused Input Registers Now Ignored by the Fitter               |                                       |

| 3.2.3 Reduced Block Limits                                           |                                       |

| 3.2.4 Product Term Redistribution                                    |                                       |

|                                                                      | · · · · · · · · · · · · · · · · · · · |

| 3.3 MACH Fitting Options Menu Changes                                                 | 24       |

|---------------------------------------------------------------------------------------|----------|

| 3.3.1 Partition and Re-Fit                                                            |          |

| 3.3.2 "Default Fuse Options" Controlling the Logic State Unused Pins Are Driven To    |          |

| 3.3.3 Extra Macrocell Assignment Iterations                                           |          |

| EXTRA Option                                                                          |          |

| STD Option                                                                            |          |

| 3.4 Changes to the Fitter Report File                                                 |          |

| 3.4.1 Report File Changes - "Run Until 1st Success" Intermediate Error Counts         |          |

| 3.4.2 Calculation of Total Block Fanout                                               |          |

| 3.4.3 Run Until 1st Success: EXTRA Fitting Option Lists Multiple .RPT Files           | 31       |

| 3.4.4 Block Partitioning Results Table                                                | 31       |

| 3.4.5 Block Signals List Table                                                        | 31       |

| 3.4.6 Block Input List                                                                |          |

| 3.4.7 Using the Block Input and the Block Signal Lists to Manually Partition a Design | 33       |

| CHAPTER 4. MACH230 DEVICE                                                             |          |

| 4.1 MACH230 General Notes                                                             | 35       |

| 4.1.1 MACH230 Buried Macrocells Drive Only Sibling Blocks                             | 35       |

| 4.1.2 Manually Partitioning a MACH230 Design                                          |          |

| More Complex Manual Partitioning Process                                              |          |

| MACH230 Grouping Controls                                                             |          |

| 4.1.3 MACH230 Input Registers and Latches                                             |          |

| 4.2 MACH230 Fitter Features                                                           |          |

| 4.2.1 Buried Logic and I/O Macrocell Partitioning                                     |          |

| 4.2.2 Buried Logic and I/O Macrocell Assignment                                       |          |

| 4.2.3 Block Relettering                                                               |          |

| 4.2.4 Input Storage Removal                                                           | 40       |

| CHAPTER 5. MACH215 DEVICE                                                             |          |

| 5.1 MACH215 Silicon Information                                                       |          |

| 5.2 Control of Special MACH215 Features                                               |          |

| 5.3 MACH215 Input Macrocell Behavior                                                  | 42       |

| 5.4 MACH215 Fitter Issues                                                             | 43       |

| 5.4.1 PAIRing in the MACH215 Can Restrict the Fitter                                  |          |

| 5.4.2 Input Setup Times Affected by Clock Functions Implemented Through Clock         |          |

| Product Term Resources                                                                | 43       |

| 5.4.3 SET, RESET and CLK Product Term Resources Not Supported Within Input            |          |

| PAIR Statements                                                                       | 44       |

| 5.4.4 Changes to the Fitting Algorithm for Assigning Clocks                           |          |

| 5.5 MACH215 Design Example - Flag Register                                            |          |

| Part 1) Sequential Differences                                                        |          |

| Part 1) Sequential Differences                                                        | 40<br>A7 |

| Fait 2) Output from the Eitter                                                        | 4/       |

| Part 3) Output from the Fitter<br>Part 4) Resource Displays from .RPT file            | 4/       |

|                                                                                       |          |

| Chapter 6 - MACH220 Device                                                            |          |

| 6.1 MACH220 Silicon Information                                                       |          |

| 6.2 Documentation Error in PALASM 4 User's Manual                                     | 49       |

| Appendix 1 - PALASM 4 Version 1.5 Fitter Messages                      | 51 |

|------------------------------------------------------------------------|----|

| "F065 - Unused pins default to outputs"                                | 51 |

| "F130 - Extra pin or node declarations"                                | 51 |

| "F170 - No Set/Reset initialization function found! - <n> missing"</n> | 51 |

| "F176 - MACH230 Block Reletter"                                        | 51 |

| "F177 - Pair Declaration Ignored"                                      | 52 |

| "F178 - Pair Declaration Ignored"                                      |    |

| F178 Warning Conditions                                                | 52 |

| Multiple PAIRing                                                       |    |

| No MACH1XX Reg Inp                                                     | 52 |

| Transfer Eq. Missing                                                   | 52 |

| Unused node                                                            |    |

| No PAIRing with CLK                                                    | 52 |

| Physically impossible                                                  | 53 |

| Xfer Ops                                                               | 53 |

| Eqs. not Same                                                          | 53 |

| "F180 - User Pre-placement Ignored"                                    | 53 |

| F180 Warning Conditions                                                | 53 |

| Block Letter too high                                                  | 53 |

| Not a clock pin                                                        | 53 |

| Pin is not within Block                                                |    |

| PAIR Placements                                                        |    |

| "F210 - Design contains both floating and fixed placements"            | 53 |

| "F570 - Invalid signal for MACH architecture"                          | 54 |

| F570 Warning Conditions                                                |    |

| No TRST on Buried Eq                                                   | 54 |

| No CLKF on Comb Eq                                                     | 54 |

| No SETF on Comb Eq                                                     | 54 |

| No RSTF on Comb Eq                                                     | 54 |

| No Node1 Logic Eq                                                      | 54 |

| No Aux Eq. on Input                                                    | 54 |

| Output Always Disabled                                                 | 54 |

| Invalid Clk Eq                                                         | 54 |

| CLKf -> IOM                                                            | 54 |

| Logic on Clkf                                                          | 54 |

| clkf Product Terms                                                     | 54 |

| trst Product Terms                                                     | 54 |

| setf Product Terms                                                     | 54 |

| rstf Product Terms                                                     | 55 |

| Inverted Aux Eq                                                        |    |

| Too many TRST/Bank                                                     | 55 |

| APPENDIX 2 - KNOWN PROBLEMS WITH PALASM 4 VERSION 1.5                  | 57 |

| General                                                                |    |

| Pre-processing                                                         |    |

| Minimizer                                                              |    |

| Fitting MACH devices                                                   |    |

| Fitting PAL devices                                                    |    |

| Simulation                                                             |    |

| Backannotating MACH designs                                            |    |

| Pinouts                                                                |    |

|                                                                        |    |

| APPENDIX 3 - PALASM 4 .PDS FILE - MACH215 APPLICATION EXAMPLE  | 61 |

|----------------------------------------------------------------|----|

| MACH215 Application Example - Flag Register                    | 61 |

| MACH215 Application Example - Flag Register Simulation Results |    |

٠

PALASM® 4 version 1.5, an upgrade to PALASM 4 version 1.4, supports the new MACH220 and MACH215 devices as well as existing AMD PAL® and MACH™ devices. PALASM 4 users need only read the portion of the release notes that pertain to the device(s) they currently use in their designs.

- If you are <u>not</u> using MACH devices, read chapters 1 and 2.

- - MACH230 devices, read chapter 4

- MACH215 devices, read chapter 5

- MACH220 devices, read chapter 6

The appendices explain error messages and describe known problems.

Related documents -

- MACH Family Data Book (PID #14051 revision F or later)

- PALASM 4 User's Manual

- MACH Technical Briefs (PID #15972)

- 1992 PAL Device Data Book (PID #10173)

To obtain a copy of the latest databook or MACH Technical Briefs, contact your local AMD sales representative or call AMD Literature at (800) 222-9323.

## CHAPTER 1. PALASM 4 VERSION 1.5 GENERAL NOTES

| IC What to read in Chapter 1                                                                                                                                                                                                                               | lf yo      | ou are a<br>Previous PALASM 4 v1.4 user<br>New user                                                         | read sections 1.1.2 - 1.5<br>read all of chapter 1 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 1.1 Operating System<br>Compatibility                                                                                                                                                                                                                      |            |                                                                                                             |                                                    |

| 1.1.1 MS-DOS™ 5.0                                                                                                                                                                                                                                          | PAI        | ASM 4 is compatible with MS-D                                                                               | OS™ version 5.0.                                   |

| 1.1.2 Memory Managers and<br>the Extended Memory Version<br>PALASM 4                                                                                                                                                                                       | mei        | e extended memory version of PA<br>mory manager such as Microsoft<br>arterdeck's QEMM. Two tested co<br>ow. | 's EMM386 or                                       |

| CONFIG.SYS file<br>DEVICE=C:\SYS\SETVER.EXE<br>DEVICE=C:\SYS\HIMEM.SYS<br>DOS=high,umb<br>device=C:\sys\emm386.exe 2<br>break = on<br>buffers = 10<br>files = 35<br>device=C:\sys\smartdrv.sys<br>devicehigh=C:\sys\ansi.sys<br>shell c:\command.com /e:15 | 048<br>20- | 48 1024                                                                                                     | ∕manager:                                          |

Table 1. CONFIG.SYS for Microsoft EMM386

**Note** that the suggested CONFIG.SYS for QEMM (below) has changed; the information published in the PALASM 4 version 1.4 Release Notes was incorrect:

CONFIG.SYS file for Quarterdeck's QEMM memory manager: DEVICE=C:\QEMM\QEMM386.SYS EXTMEM=4096 RAM rem DEVICE=C:\QEMM\QEMM386.SYS RAM MAPS=12 HANDLES=96 NS -incorrect!!! SHELL =c:\COMMAND.COM /E:880 /P DOS=HIGH,UMB break=on FILES=20 BUFFERS=20 rem install= c:\qemm\loadhi.com /tsr /r:3 c:\dos\fastopen.exe c:=80 /x

Table 2. CONFIG.SYS File compatible with MS-DOS 5.0 and EMM386

These configurations have been tested on a system configured with most utilities and device drivers in a \sys directory. Your system may be different.

1.1.3 DR-DOS

PALASM 4 version 1.5 is not supported under Digital Research's DR-DOS.

However, some users have run PALASM 4 successfully under DR-DOS 6.0 with QEMM 6.0, using the configuration below. AMD has not completely tested this configuration and therefore cannot assume responsibility for supporting customers in this environment.

| DR-DOS Configuration - AUTOEXEC.BAT                                                                                                                                                                                                                                                                                                                                                                           |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <pre>@echo off<br/>:DRDOSBEG<br/>PATH C:\DRDOS;c:\QEMM;C:\pc;C:\PALASM\EXE;<br/>@<br/>LOADHI BUFFERS=40<br/>LOADHI FILES=40<br/>LOADHI=FCBS 4,4<br/>VERIFY OFF<br/>PROMPT \$p\$g<br/>SET PALASM=C:\PALASM\<br/>SET ORCAD=c:\ORCAD\<br/>@<br/>rem LOADHI C:DRDOS\SHARE.EXE /L:40 MUST BE REMOVED!!!<br/>cls<br/>ECHO PALASM 4 Software - (c)Copyright AMD 1992 All Rights Reserved<br/>rem<br/>:DRDOSEND</pre> |  |

| DR-DOS Configuration - CONFIG.SYS<br>DEVICE=C:\QEMM\QEMM386.SYS RAM NOSH<br>SHELL =c:\COMMAND.COM C:\ /P /E:512<br>BREAK=ON<br>BUFFERS=1<br>FILES=10<br>FCBS=4,4<br>FASTOPEN=512<br>LASTDRIVE=E<br>HISTORY=ON, 256, ON, OFF, OFF<br>COUNTRY=001,,C:\DRDOS\COUNTRY.SYS<br>HIDOS=ON<br>DEVICE=C:QEMM\LOADHI.SYS C:\DRDOS\ANSI.SYS                                                                               |  |

Table 3. AUTOEXEC.BAT and CONFIG.SYS files for DR-DOS 6.0 with QEMM 6.0

Again, AMD has not completely tested this configuration and cannot assume responsibility for supporting customers in this environment.

1.1.4 Microsoft Windows® PALASM 4 version 1.5 is not a WINDOWS program and must be run as a stand-alone program. PALASM 4 version 1.5 is not supported under and is not 1.1.5 IBM OS/2™ compatible with OS/2. 1.1.6 Networks PALASM is not supported for use in networked environments. 1.2 Changes to the PALASM 4 version 1.5 software takes 5-7 MB hard disk space, depending on whether the regular or extended memory version Installation Program is installed. Beginning with this release, the INSTALL program now asks whether to load the Examples and On-line Help files. Not loading these files will save disk space. Install Examples 350KB (Y/N) ? Y Install On Line Help 750KB (Y/N) ? Y Even if the Examples are not installed, the \PALASM\EXAMPLE subdirectory and its associated subdirectories are still created by the INSTALL program. These empty subdirectories may be deleted. The same is true of the On-Line Help. The INSTALL program creates subdirectories within \PALASM\DOC directory, even if the On-line Help is not installed. With the exception of the LOOKUP.HLP file (used the PALASM 4 menu system), the empty subdirectories under \PALASM\DOC may be deleted. 1.3 Installing From an To install PALASM 4 or the MACH Libraries from a drive other Alternate Drive than "A", use the letter of the drive you are installing from both before and after the INSTALL command. For example: B:INSTALL B: This command will install the software from the B drive onto whatever hard drive is chosen later in the installation program. 1.4 Extended Memory **Problems Reported With**

#### 1.4.1 Designs Not Compiling

**IBM/AT®s and Compatibles**

Problems have been reported running the extended memory version of PALASM 4 on IBM AT (80286) compatibles. These same PCs are able to run the standard memory version successfully. When the problem occurs, compilation of a design would begin under the extended memory version, only to have the menu reappear in a few seconds with no error message or results.

The problem occurs because the INSTALL program, which calls a "tuning" program, did not successfully adapt the

extended memory version of PALASM 4 to your PC. The tuning program is not called if you are using extended memory memory manager or a machine-specific memory access program.

Work Around: Try "tuning" PALASM 4 manually. After installing this release, type:

#### C:> TUNE\_MAN 1

The numerical arguments 1, 2 or 3 implement different tuning strategies effective on many PCs. If the same problem in running the extended memory version of PALASM 4 continues, try running the TUNE\_MAN program again using the numerical argument 2 or 3 instead. PALASM 4 must be already installed in order to use TUNE\_MAN. It does not have to be installed again from floppy disks each time, or re-run each time you reboot or reprocess a design.

1.4.2 BIOS ROMs and Early IBM/AT Compatibles Some customers with early IBM/AT compatibles have reported problems with the extended memory version of PALASM 4. The problem has been traced to problems in early versions of the ROM BIOS shipped with IBM/AT compatibles manufactured before 1989. If you have one of these PCs, consider upgrading the BIOS ROMs. This inexpensive investment will solve problems with many software packages, not just PALASM 4.

## **1.5 Documentation Errors** The following error appears in all copies of the PALASM 4 User's Manual.

page 11-167 Defining Clock Pins: Pin 16 should be listed as CLK1 for the MACH120 and 220 devices, not pin 17.

The errors listed below (previously described in PALASM 4 version 1.4) appear in older, three-hole-punched PALASM 4 User's Manuals acquired prior to August 1992.

| page 11-169 | Pin Declaratio | n Segn   | nent: Pin      | 4 should  | be REGIS      | TERE             | D, not CO  | OMBINATORIAL. |

|-------------|----------------|----------|----------------|-----------|---------------|------------------|------------|---------------|

|             | Pin            | 4        | 102            | COM       | BINATORI      | <del>al</del> Ri | EGISTEI    | RED           |

| page 11-170 | Top of page: ( | Change   | the T-reg      | istered s | signal inside | e the N          | ote as fo  | ollows        |

|             | A6.T: =        | = {IO2.7 | Γ}             |           |               |                  |            |               |

| page 11-171 | Top of page: ( | Change   | e the Pin D    | eclaratio | ons as follo  | ws               |            |               |

|             | Pin            | ?        | <del>lO2</del> | 101       | REG           |                  |            |               |

|             | Node           | ?        | A4             |           | PAIR          | 102              | IO1        | REG           |

| page 11-171 | Middle of page | e: Char  | nge the Pi     | n Declar  | ation to add  | I PAIR           | A3 to Pi   | in 33         |

|             | Pin            | 33       | 14             |           | PAIR A        | 3                |            |               |

| page 11-172 | Top of page: ( | Change   | e the Pin D    | eclaratio | on to add P   | AIR A3           | 8 to Pin 3 | 33            |

|             | Pin            | 33       | l4             |           | PAIR A        | 3                |            |               |

What to read in Chapter 2

2.1 Menu Changes -Minimizer If you are a ....

Previous PALASM 4 v1.4 user read just section 2.2 New user read all of chapter 2

Beginning with PALASM 4 version 1.4, a new Minimizer was added which has a new Logic Synthesis menu option and two improvements. The two improvements are -

- It reduces the memory utilization of most designs by 50% or more.

- The old Minimizer "hung" if more than 14 variables were used in an equation, while the new one is guaranteed to reduce 32 variable equations.

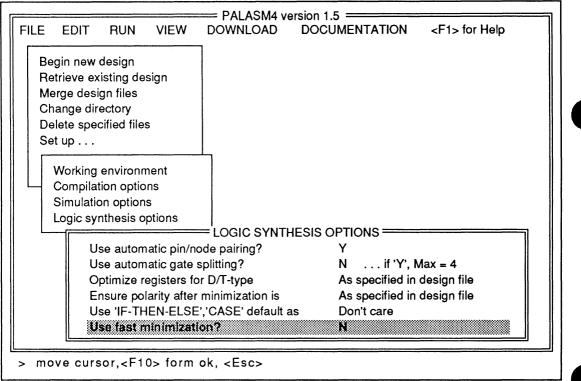

The menu option shown in Figure 1, *Use fast minimization*, allows the user to run an abbreviated version of the new Minimizer. If it is OFF, a more exhaustive minimization is performed. It should be turned ON only if an *Out of memory* error is generated or Minimizer compilation times are unusually long, since the *fast minimization option* may produce equations with more product terms than the standard Minimizer does.

Figure 1. Logic Synthesis Options Menu.

## **2.2 Simulator Usage Notes** The Simulator has been revised for PALASM 4 version 1.5. Most devices, including MACH devices are affected.

## 2.2.1 Devices Still Supported by the Old Simulator (SIM)

The following devices are supported by the old Simulator and are not affected by the changes discussed in sections 2.2.3 through 2.2.11:

- PAL16RA8

- PAL20RA10

- PAL22IP6

- AMPAL23S8

- PAL32R16

- PAL64R32

2.2.2 Assumptions Made by Previous Versions of the Current Simulator (PLDSIM) The revised PALASM 4 version 1.5 Simulator is less tolerant of incompletely specified simulation files. Some previously clean simulation files may now generate error messages and simulation miscompares, or fail programmer JEDEC verification <u>if</u> the simulation file is incompletely specified.

Previous versions of this Simulator (PLDSIM) made several assumptions based on the evaluation of the programmer at power-up that sometimes resulted in devices being modeled incorrectly:

- Registers and latches were incorrectly modeled:

- Registers powered up to a known state regardless of the state of the input pins.

- The effect of the control signals on the state of the registers was not evaluated at power-up.

- Clocks were triggered if clock fan-in went from a low or an unknown to a high.

- MACH devices were incompletely modeled.

- After preload, there was no evaluation of the effect of the control signals on the state of the registers.

- An unknown SET or RESET or CLOCK had no effect on the state of the registers.

- Pins that where unassigned were not evaluated.

The PALASM 4 version 1.5 Simulator corrects modeling problems with registers and latches:

- Register and latches with unknown SET, PRE-SET or CLK/LE signals now generate an unknown state at the output Q.

- The clock will now trigger only if it rises from a low to a high in the case of an active high clock, or from high to a low in the case of an active-low clock.

- The Simulator now reflects the specifications in the MACH Family Data Book. For example, it is legal to have SET and RESET signals high at the same time.

- For devices with preload pins, asserting PRELOAD with SET or RESET results in an unknown fanout at the register output Q.

PLD programmers and testers forced a default test condition on pins set to unknown logic states. On some programmers the default test condition value is programmable. The JEDEC format for the default test condition is "X0\*" for a LOW state, and "X1\*" for a HIGH state. This field must be placed before the first test vector and after the number of pins (QP) and the number of fuses (QF) fields.

Nearly all AMD approved programmers support the default test condition X0\*. The new Simulator assumes that all pins are

PALASM 4 VERSION 1.5 RELEASE NOTES

#### 2.2.3 Correct Modeling of Registers and Latches

## 2.2.4 Programer Emulation at Power-Up

forced to a SOFT-LOW before power-up, and places a "X0\*" before the first test vector.

The unknown state cannot be realized in a physical sense in hardware. Individual programmers can set pins HIGH or LOW, and some programmers are even able to set pins to float (normally not done because the effect of a floating pin cannot be determined for all devices and test cases).

Uninitialized pins are generally set to the default test condition before the power is turned on to the device under test. Programmers cannot determine which pins are inputs and which are outputs, and therefore must use "soft conditions". Under soft conditions, pins are driven high or low by a resistance low enough to drive an input pin but not low enough to override or destroy an output pin.

The Simulator shows the default test condition for uninitialized pins in the history file. However, uninitialized pins remain as "X"s or unknown in the JEDEC test vectors because some testers have a limit on the amount of pins that can be toggled on each single vector.

# 2.2.5 Power-Up Sequence A two stage power-up routine was added to the Simulator to simulate the behavior of registered devices better. The routine evaluates the device state before the first user vector is applied, and takes in account all control signals connected to registers.

Stage 1

- Load all inputs with the default condition (currently 0) and enter affected signals into event queue.

- Load all registers with power-up preload value and enter affected signals into event queue.

- Fix registers so they will not change in response to control signals CLK/ LE, SET, RESET, or PRELOAD.

- Evaluate until steady state.

Stage 2

- Load all inputs with the default condition (currently 0) and enter affected signals into event queue.

- Allow registers to be affected by control signals.

- Evaluate until steady state.

A two stage preload routine was added to the Simulator for the same reasons as at power-up. Control signals such as

PALASM 4 VERSION 1.5 RELEASE NOTES

#### 2.2.6 Software Preload Sequence

SET, RESET, CLK/LE and output enables can affect the register states after they have been preloaded.

Stage 1

- Load all registers with the preload value and enter affected signals into the event queue.

- Fix registers so they will not change in response to the control signals CLK/LE, SET, RESET, and PRELOAD.

- Evaluate until steady state.

Stage 2

- Allow registers to be affected by control signals.

- Evaluate until steady state.

When the software encounters the PRELOAD statement, test vectors are no longer appended to the JEDEC file.

#### 2.2.7 Full Evaluation of Input Pins

2.2.8 Driving Active-Low and Active-High Clocks for the MACH215  All input pins are assumed to be initialized to the default test conditions at power-up.

• The effect of all input pins is now evaluated upon power-up.

The MACH215 and future MACH devices with active-low clocks can be driven with an active-low clock signal at the pin. An active-low clock (a JEDEC "K" clock) is a high-to-low-to-high pulse.

Polarity conventions are consistent with the polarity convention for the SETF command:

- To generate a JEDEC "C" clock force for the active-high pin, CLK, use the simulator command "CLOCKF CLK". If the pin CLK is active-low, use the simulator command "CLOCKF /CLK".

- To generate a JEDEC "K" clock force for the active-high pin, CLK, use the simulator command "CLOCKF /CLK". If the pin CLK is active-low, use the simulator command "CLOCKF CLK".

An example is shown on the following page.

| PIN 1 CLK1<br>PIN 2 /CLK2 | ; Active-high pin<br>; Active-low pin |

|---------------------------|---------------------------------------|

| SIMULATION                | , Accure for prin                     |

| ; For active-high pins    |                                       |

| SETF CLK1                 | ; Generates JEDEC "1" force           |

| SETF / CLK1               | ; Generates JEDEC "O" force           |

| ; For active-low pins     |                                       |

| SETF CLK2                 | ; Generates JEDEC "O" force           |

| SETF / CLK2               | ; Generates JEDEC "1" force           |

| ; Global clock            |                                       |

| CLOCKF                    | ; Generates JEDEC "C" clock           |

| ; For active-high pins    |                                       |

| CLOCKF CLK1               | ; Generates JEDEC "C" clock           |

| CLOCKF / CLK1             | ; Generates JEDEC "K" clock           |

| ; For active-low pins     |                                       |

| CLOCKF CLK2               | ; Generates JEDEC "K" clock           |

| CLOCKF / CLK2             | ; Generates JEDEC "C" clock           |

Table 4. Active-Low and Active-High Clocks for the MACH 215

| Waveform | Test<br>Condition | Description                        |

|----------|-------------------|------------------------------------|

|          | 0                 | Drive input low                    |

|          | 1                 | Drive input high                   |

|          | С                 | Drive input low, high, low         |

|          | D                 | Drive input low, fast transistion  |

|          | к                 | Drive input high, low, high        |

|          | U                 | Drive input high, fast transistion |

Table 5. Driving Test Conditions.

Errors are generated if a "C" clock is asserted on a pin whose state is initially high, or if a "K" clock is asserted on a pin whose state is initially low.

#### 2.2.9 Product-Term-Driven Clocks

The PALASM 4 version 1.5 Simulator supports JEDEC "U" and "D" transitions for dedicated clock pins. If a transition occurs on a dedicated clock pin it is translated to a "U" or "D" transition. The purpose of "U" and "D" clocks is to allow data from all other inputs to be stable before a latch enable or clock transition occurs. Some dedicated clock pins can be used both as clock and as data pins. The user should be aware that on a JEDEC tester this can cause some data lines to be driven at the same time or later than clock signals.

To avoid potential test problems with the simulator command "SETF" the data and CLOCK/LE transitions should occur in separate test vectors. "C" and "K" clock transitions should be used to drive pins that affect register clocks.

The version 1.5 Simulator supports both fast rise and fall transitions for dedicated clock pins on all devices controlled by the SETF syntax. Data from all other inputs must be stable before a latch enable or a clock transition occurs.

Because some dedicated clock pins can be used as both clock and data pins, customers should be aware that some data lines could be driven at the same time or later than clock signals on a JEDEC tester, leading to differences between simulated and observed programmer behavior.

To avoid this problem, Simulator SETF commands and test patterns should be written so that data and CLOCK/LE transitions occur in separate vectors. AMD recommends that CLOCKF commands drive pins that affect register clocks.

Fast rise and fall transitions are not supported for devices with non-dedicated clock pins driving product term clock resources. Unless the programmer is set up to create fast edges on all input transitions, input changes are too slow to properly trigger CMOS storage elements on devices such as the MACH215. Any JEDEC vector verification errors must be individually analyzed to determine the cause of the miscompare.

2.2.10 Simultaneous Events While the MACH devices allow the application of SET and RESET signals at the same time, removing both signals at the same time results in an unknown state. Because the PALASM Simulator is a functional simulator, not a timing simulator, it cannot detect simultaneous events. Take care to remove SET and RESET signals in separate vectors.

2.2.11 Power-up Preload on Floating Pins The PALASM 4 version 1.5 Simulator requires a physical location to preload pins with a power-up state. If there are floating pins, the register value will be set to "X" (the unknown value) at start-up. As a result, some test cases will generate different results if they are executed with floating pins. The work around is to manually place registered pins and nodes.

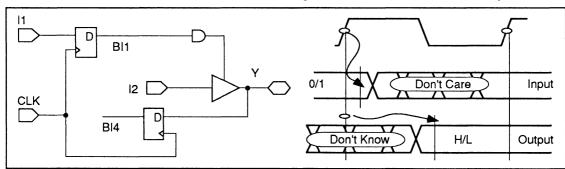

#### 2.2.12 Simulation of Three-State Pins for Input and Output

The PALASM 4 version 1.5 Simulator may not always properly chose the input symbol set over the output one when a common clock is used to both load an input register and control the output enable.

When the effect of using a single vector for both input and output operations is considered, the problem becomes apparent. When a pin changes from an input logic state (represented by "0" or "1" in the JEDEC signal vector) to an output (represented by "H" or "L") a conflicts arises between which symbol should be used to denote the signal level during that window. Erroneous results may occur:

To avoid this problem, separate the three-state control from the clock event on the input register by adding an extra input to the three-state control PT.

#### 2.2.13 Input Signal Ordering

Programmers apply inputs to a device in different sequences. Some apply inputs in sequential pin order, some apply them in groups of eight pins at a time, and others follow still other patterns. With so many possibilities, no simulator can handle all situations.

Therefore, users should define vectors with device logic in mind, avoiding potential races in vector definition so that any variation in the input sequences will produce the same result. In conventional synchronous logic, this is not a problem - all data input transitions are applied before the device is clocked. However, simultaneous clock events should be avoided.

The problem is more difficult for asynchronous logic designs. Control functions like set and reset should be applied and removed in separate vectors with an "idle" state in between, so that even if input changes are skewed, both will not be applied simultaneously. Likewise, data changes should be separated from storage-enabling or clocking events, so that the ordering of input changes is less likely to have an effect on the output.

## CHAPTER 3. AMD MACH FITTER VERSION 1.5

| what to read in Chapter 2    | Kusu are using MACII devices and are a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IS What to read in Chapter 3 | If you are using <u>MACH devices</u> and are a<br>Previous PALASM 4 v1.4 user <i>read sections 3.1.3, 3.2,</i><br><i>3.2.1, 3.2.2, 3.2.3, 3.3,</i><br><i>3.3.1, 3.3.2, 3.3, 3.4, 3.4.1</i><br><i>and 3.4.2</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                              | New user read all of chapter 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.1 General Operation        | <ul> <li>This section describes the MACH fitting process section (3.1.1) and two traits of the AMD Fitter. These are -</li> <li>If more than two tristates are used in a MACH1XX block, the logic may not fit. See section 3.1.2.</li> <li>Some designs which fit when compiled under previous versions of PALASM 4 may not fit when compiled with subsequent versions. See section 3.1.3.</li> </ul>                                                                                                                                                                                                                                                                                                                                      |

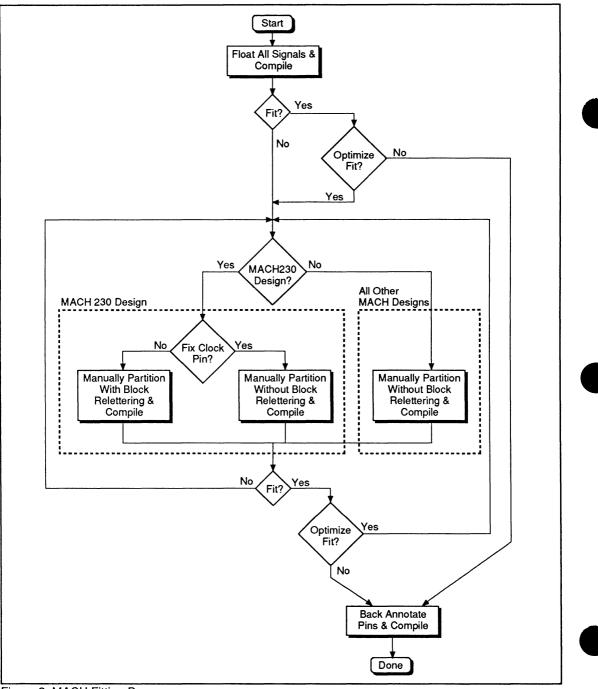

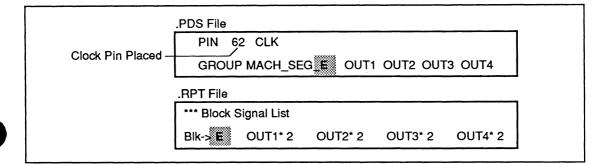

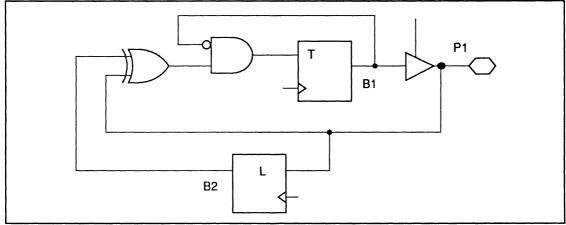

| 3.1.1 Fitting Process        | <ul> <li>Pin and node locations should not be specified before the design is compiled. Users should follow the following steps- <ul> <li>First, float pins in the design and compile.</li> <li>Next, manually partition the design and recompile (if necessary).</li> <li>After the design is fitted, back-annotate pin and node locations and re-compile.</li> </ul> </li> <li>Figure 3 shows the processes for fitting MACH230 and other MACH designs. Note that optimization of fitted designs is done so that a design meets speed requirements and is more likely to accept future design modifications without changing the pinout. (Refer to the MACH Technical Brief titled, "Designing for Change with MACH Devices".)</li> </ul> |

Figure 3. MACH Fitting Process.

The fitting process differs if the pinout is fixed. When changes must be implemented to the design after the pinout for the design has been fixed, the process illustrated in Figure 3 is not applicable. In order to maintain the existing pinout, the design should be compiled with the pins corresponding to the original design fixed. New signals may be floated to aid in fitting. Once the design is fitted, all pins should be backannotated and the design re-fitted.

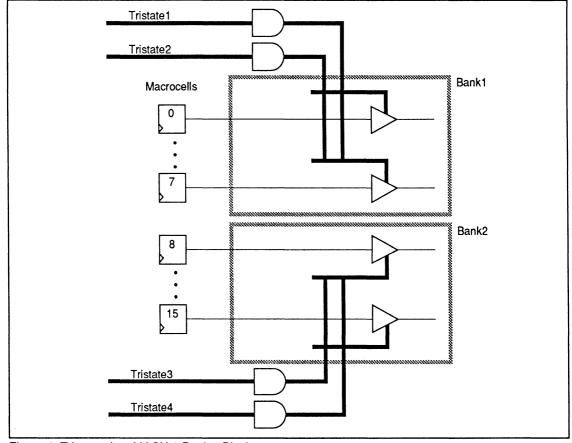

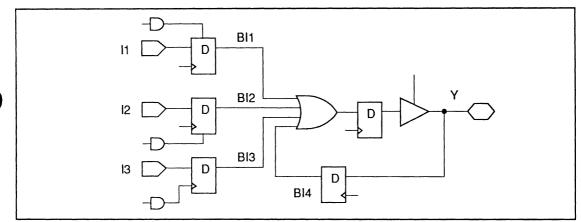

# 3.1.2 Tristate Resources in MACH 1 Devices

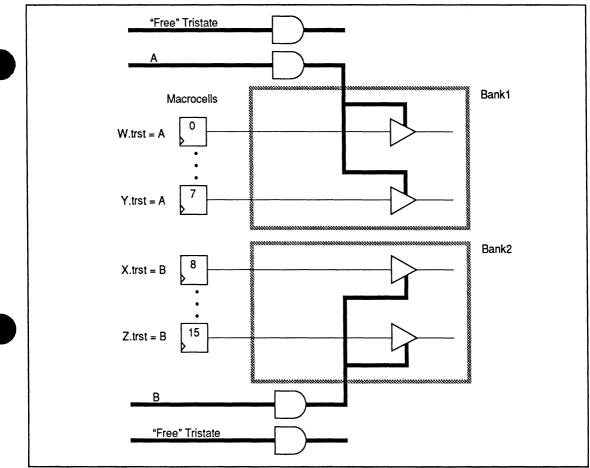

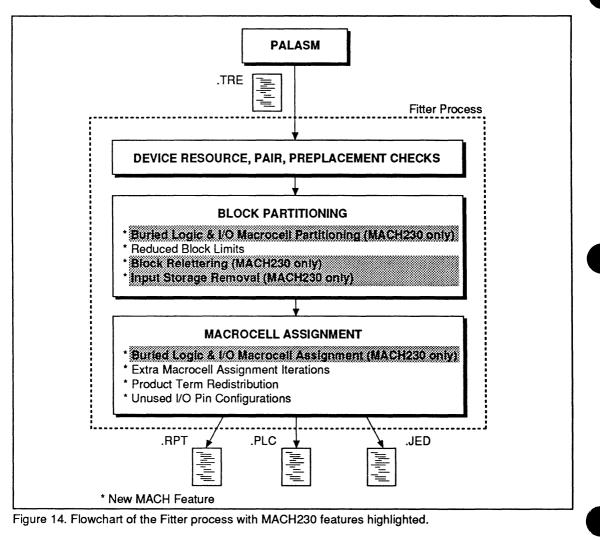

The tristate resources in a MACH 1 device blocks are segmented into two banks of macrocells, one bank associated with macrocells 0-7 and the other associated with macrocells 8-15. Two tristate resources are provided for each bank, as shown in Figure 4.

If two or fewer independent tristate resources are used in a block, tristate placement will not affect fitting. However, if more than two tristates are used in a block, macrocells using common tristates must be placed in the same bank. Since the Fitter doesn't take banking into account, it may place equations into a block so that only two tristate signals are available per block.

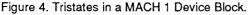

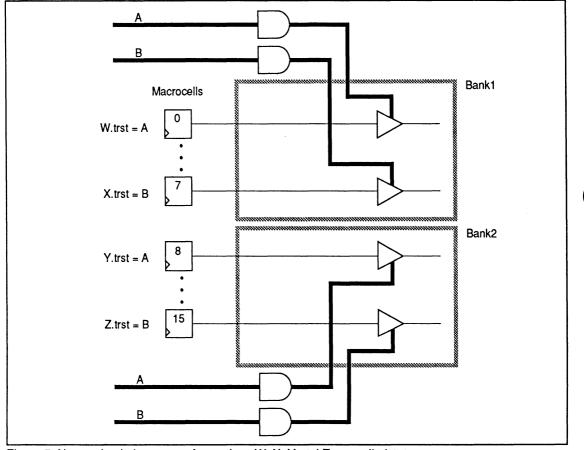

An example will clarify this. Consider the case where two equations (X & Z) use tristate signal A, and two (W & Y) use tristate signal B. By placing equations using both tristate signals into each bank as illustrated in Figure 5, the Fitter uses all tristate resources in that block.

Figure 5. Non-optimal placement of equations W, X, Y and Z uses all tristates.

If, however, the two equations using tristate A are placed in one bank and the two equations using tristate B are placed in the other, two "free" tristate resources are still available for use. See Figure 6.

Figure 6. Optimal placement of equations W, X, Y and Z leaves 2 "Free" Tristates.

The following steps should be taken to guide the Fitter in placing logic when three or four tristate signals are used in a block and an error message indicates that too many tristates are used -

- Refit the design with the tristate signals removed from the design file, then fit the design with pin placements from this design back-annotated and the tristate signals added.

- If this doesn't result in a successful fit, the equations should be placed in appropriate banks

by specifying pin numbers for them in the declaration section of the design file.

If the design still will not fit, partition it into blocks manually to move tristate resources into other blocks. (Refer to the "MACH Devices - Manual Logic Partitioning" MACH Technical Brief.)

#### ■ 3.1.3 How to Use Latches on MACH Devices

MACH1XX and 2XX devices, excluding the MACH215, only support active low latches. The correct syntax for the latch enable for these MACH devices is listed below:

/signal.clkf =

The MACH215 device, however, has both active low and active high latches. The correct syntax for enabling active-low and active-high latches is listed below:

| /signal.clkf = | ;active low  |

|----------------|--------------|

| signal.clkf =  | ;active high |

The following example shows how to use latch enables in design files for MACH devices other than the MACH215:

Pin ? AO LATCHED ; output Node ANO LATCHED ; output Pin ? LATCH Pin ? BO ; input Pin ? B1 ; input Pin ? LE ; input AO \*= BO + B1 ANO \*= {AO} /LATCH.CLKF = LE

Because the MACH110, 120, 130, 210, 220 and 230 devices do not support active high latches, if an active high latched equation such as:

LATCH.CLKF = LE

is used in this example, the Fitter will generate the following error message:

>ERROR F570 - Invalid Signal for MACH Arch. (Logic on Clk Eq) - ANO

\_\_\_\_\_

An Auxiliary equation's (Trst/Clk/Setf/Rstf) logic configuration was detected that is not compatible with the MACH device architecture. Please correct the design & rerun all processing steps.

3.1.4 Save Old Versions of the AMD Fitter and PALASM Software

New versions of the AMD Fitter software are not guaranteed to fit designs which old versions did. Old versions of the software used to fit existing designs should be saved in case changes must be made to the design.

As a precaution, save the original PALASM 4 software disks from other releases.

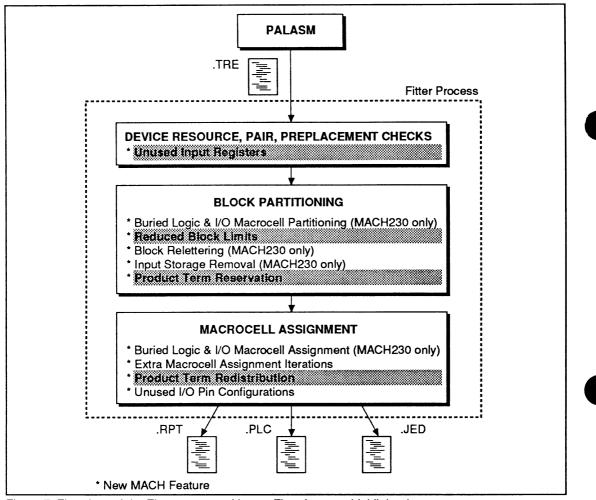

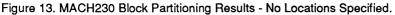

Several new features, applicable to all MACH devices, have been added to the Fitter with PALASM 4 version 1.5, in addition to those previously added with version 1.4:

- New Fitter features in PALASM 4 version 1.5

- Product Term Reservation for Logic Functions (section 3.2.1)

- Unused Input Registers are now ignored by the Fitter (section 3.2.2)

- Reduced block limits. This feature was first implemented in PALASM 4 version 1.4. Turning off "Maximize packing of logic blocks" limits the amount of logic the Fitter places in a block. The resource limits table has been updated to include the new MACH215 device (section 3.2.3).

- New Fitter Features in PALASM 4 version 1.4

- Product Term Redistibution. Beginning with PALASM 4 version 1.4, the Fitter redistributes product terms within a block until a fit is found (section 3.2.4).

### 3.2 New Behavioral Features of the AMD MACH Fitter

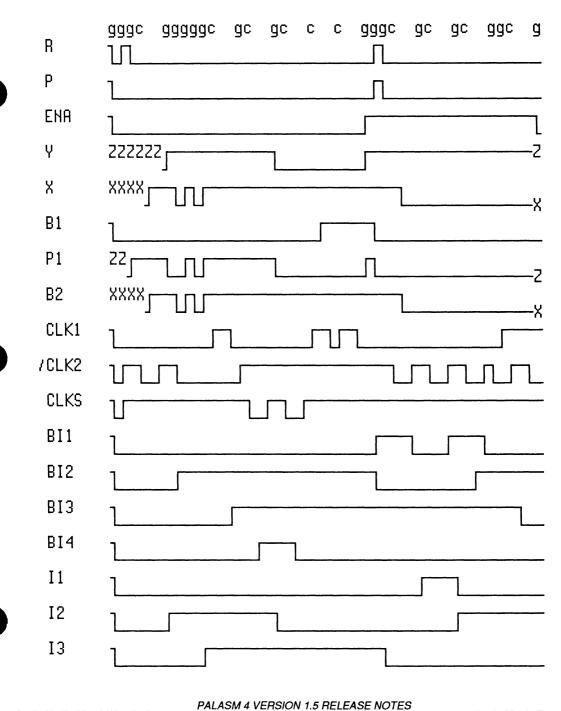

Figure 7. Flowchart of the Fitter process with new Fitter features highlighted.

The MACH230 specific features are discussed in Chapter 4.

If you are already familiar with PALASM 4 version 1.4, read sections 3.2.1 through 3.2.3 before moving to section 3.3.

# 3.2.1 Product Term Reservation for Logic Functions

In the past, all logic functions placed by the Fitter were allocated only the exact number of product term clusters needed to realize the desired logic. The new "Product Term Reservation" feature allows you to choose a placement of free product terms directly for a particular logic function.

The syntax for product term reservation is similar to definition of logical groups:

GROUP MACH\_PTS\_8 Sig\_List

The number used with the GROUP MACH\_PTS statement (i.e. 8) sets the <u>minimum</u> space allocated to each of the signals listed.

Allocating additional terms to logic functions can use up available resources within a block and can reduce the chances of a successful fit. As a reminder, PALASM 4 will generate the informational message below whenever Product Term Reservation is used and a design fails to fit:

|                                                                | pansion was enabled for this design, and the<br>ou may want to reevaluate the PT expansion used<br>sign.                                                                                             |

|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                | See also the MACH Technical Brief titled "Designing for Change with MACH Devices".                                                                                                                   |

| I 3.2.2 Unused Input<br>Registers Now Ignored by the<br>Fitter | Unused pins, buried nodes and input registers are now ignored in all fitting operations.                                                                                                             |

|                                                                | In the past these items were connected using conventional<br>array logic transfers and consumed PT resources. Unused<br>registered inputs are now highlighted with the following<br>warning message: |

| > WARNING F179 - Pair                                          | Declaration Ignored: (Unused RI) - Sig_Name                                                                                                                                                          |

\_

**3.2.3 Reduced Block Limits** Early versions (pre-PALASM 4 version 1.4) of the Fitter sometimes partitioned too much logic into one block even when other blocks were unused, and then could not fit the design. By reducing block limits, the software attempts to overcome this problem through limiting how much logic the Fitter places in a block.

If the *Maximize packing of logic blocks* Fitter flag is OFF, this feature is enabled and the Fitter uses reduced resource limits to determine how much logic to place in a block, as illustrated in Table 6. If, in contrast, the *Maximize packing of logic blocks* flag is ON, the Fitter uses the limits listed in the ">70%" column.

| Resource                            | D.U.<50% | 50%>D.U.<70% | D.U.>70% |

|-------------------------------------|----------|--------------|----------|

| 🕞 Array Inputs (MACH120,130,220,3   | 230) 23  | 25           | 26       |

| Array Inputs (MACH110,210,215)      | 19       | 21           | 22       |

| Product Terms (MACH110,130,210,230) | 48       | 56           | 64       |

| Product Terms (MACH120,220)         | 32       | 40           | 48       |

| Product Terms (MACH215)             | 16       | 24           | 32       |

| I/O Macros (MACH110,130)            | 14       | 15           | 16       |

| I/O Macros (MACH210,230)            | 6        | 7            | 8        |

| I/O Macros (MACH12O)                | 10       | 11           | 12       |

| I/O Macros (MACH220)                | 4        | 5            | 6        |

| I/O Macros (MACH215)                | 6        | 7            | 8        |

Table 6. Reduced Block Limits (Maximize packing of logic blocks flag OFF).

The benefit of this approach is that it spaces logic evenly among blocks in a MACH device, allowing designs to fit that otherwise would not.

The drawback is that this Fitter may not successfully partition some high utilization designs which previous versions did.

To prevent the software from reducing block limits, run the Fitter with the *Maximize packing of logic blocks* flag ON using the *Select one combination* Fitter option or manually partition the design.

# 3.2.4 Product Term Redistribution Previous versions of the Fitter allocated product terms to macrocells within a block using a fixed algorithm that did not redistribute product terms if a particular allocation would not fit. In contrast, the PALASM 4 version 1.4 Fitter redistributes product terms within a block until a fit is found.

The benefit of this feature is that the PALASM 4 version 1.4 software fits some designs that earlier versions could not.

### 3.3 MACH Fitting Options Menu Changes

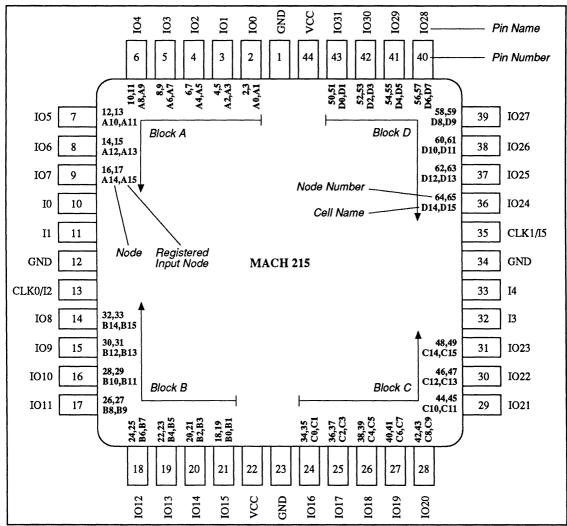

Changes to the MACH Fitting Options menu in both PALASM 4 version 1.4 and version 1.5 have added extra functionality to the Fitter, as shown in Figure 8.

| MACH FITTING OP                                                                                                                                                     | TIONS                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| OUTPUT:<br>Report level                                                                                                                                             | Detailed                                                    |

| SIGNAL PLACEMENT:<br>Float all signals and ignore grouping?<br>Use placement data from<br>Save last successful placement<br>Press <f9> to edit file containing</f9> | N<br>Design file<br><f3><br/>Last successful placement</f3> |

| PARTITION and Re-Fit?<br>DEFAULT FUSE OPTIONS:<br>Unused I/O pins configured as outputs?                                                                            | Y<br>Y if 'Y', Level = H                                    |

| FITTING OPTIONS:<br>When compiling                                                                                                                                  | Run until 1st success: EXTRA                                |

Figure 8. MACH Fitting Options Menu.

Changes made to the MACH Fitting Options menu in PALASM 4 version 1.5

- Partition and Refit improves the likelihood of finding logic partitions after an unsuccessful fit for MACH110, MACH210, MACH130, MACH120, and MACH220 devices (section 3.3.1).

- Default Fuse Options allow you to control the logic state unused pins are driven to (section 3.3.2).

Changes made to the MACH Fitting Options menu in PALASM 4 version 1.4

Improve the chance of fitting by running extra iterations for macrocell assignment (section 3.3.3).

If you are already familiar with PALASM 4 version 1.4, read sections 3.3.1 and 3.3.2 before moving to section 3.4.

**3.3.1 Partition and Re-Fit** After obtaining an unsuccessful fit with the PALASM 4 version 1.5 Fitter, you now have the option of calling an improved partitioning program for solving such problems. This new fitting option - "Partition and Refit" - can be used with all MACH devices <u>except the MACH215 and MACH230</u> devices.

| OUTPUT:                                 |                              |

|-----------------------------------------|------------------------------|

| Report level                            | Detailed                     |

| SIGNAL PLACEMENT:                       |                              |

| Float all signals and ignore grouping?  | Ν                            |

| Use placement data from                 | Design file                  |

| Save last successful placement          | <f3></f3>                    |

| Press <f9> to edit file containing</f9> | Last successful placement    |

| PARTITION and Re-Fit?                   | Y                            |

| DEFAULT FUSE OPTIONS:                   |                              |

| Unused I/O pins configured as outputs?  | Y if 'Y', Level = H          |

| FITTING OPTIONS:                        |                              |

| When compiling                          | Run until 1st success: EXTRA |

By using the "Partition and Refit" option, you will have a somewhat higher success rate in finding logic partitions. The improved partitioning program optimizes the block placement of logic functions to minimize the required interconnect. It continues to swap functions while improving the chance of a successful fit.

The "Partition and Re-fit" option can only be used <u>after</u> running the Fitter and getting an <u>unsuccessful</u> fit.

When enabled, the Partition and Re-Fit option asks if the block partitions (GROUP MACH\_SEG commands) used in the design file should be kept:

Partition option: KEEP GROUP MACH\_SEGs (Y/N)? N

Choosing "N" allows the Fitter to freely move all signals as needed. Choosing "Y" allows the Fitter to move only those signals not declared in GROUP MACH\_SEG statements in the design file, and possibly keep much of the old pinout.

#### ■ 3.3.2 "Default Fuse Options" Controlling the Logic State Unused Pins Are Driven To

Unused device pins can potentially conduct switching noise into the logic arrays and float between logic thresholds, dissipating additional power. Proper signal termination with a pull-up resistor (> $20k\Omega$ ) can prevent this from happening, but at the cost of additional components. New MACH devices such as the MACH220 and MACH215 have

internal pull-ups, but older MACH devices, such as the MACH110, 210, 130, 230 and 120 do not.

PALASM 4 version 1.5 allows the user to choose the logic state (high or low) that unused pins are driven to from the MACH Fitting Options menu:

| ILE MACH F                             | ITTING OPTIONS                  |

|----------------------------------------|---------------------------------|

| OUTPUT:                                |                                 |

| Report level                           | Detailed                        |

| SIGNAL PLACEMENT:                      |                                 |

| Float all signals and ignore grou      | uping? N                        |

| Use placement data from                | Design file                     |

| Save last successful placemen          | t <f3></f3>                     |

| Press <f9> to edit file containir</f9> | ng Last successful placement    |

| PARTITION and Re-Fit?                  | Y                               |

| DEFAULT FUSE OPTIONS:                  |                                 |

|                                        | is outputs? Y if 'Y', Level = H |

| FITTING OPTIONS:                       |                                 |

| When compiling                         | Run until 1st success: EXTRA    |

Figure 10. MACH Fitting Options - Default Fuse Options.

Note: PALASM 4 version 1.4 allowed the user to configure unused I/O pins as inputs, but did not allow the user to control what state they were driven to.

An informational message is produced when DEFAULT FUSE OPTIONS is set to "Y":

INFORMATION F065 - Unused pins default to outputs - High

Explanation:

. Unused pins are being defaulted to be outputs and enabled.

- . This diminishes the coupling of external noise into the MACH device

- . and removes the need for external resistor pull-up terminations.

Note that unused pins associated with buried logic are still not enabled. Any internal logic changes would cause the pin to change, dissipating additional power and "broadcasting" the buried signal for all to see.

3.3.3 Extra Macrocell Assignment Iterations

**EXTRA** Option

This Fitter feature is enabled from the PALASM 4 compilation menu.

The new *Run until 1st Success: EXTRA* option executes extra macrocell assignment iterations. When the *EXTRA* Fitter option is selected, the Fitter process is altered. The state of the *Maximize packing of logic blocks* flag, which controls block partitioning, is determined before macrocell assignment occurs.

| FILE       EDIT       RUN       VIEW       DOWNLOAD       DOCUMENTATION <f1> for Help         Begin new design       Retrieve existing design       MACH FITTING OPTIONS         Merg       OUTPUT:       Brief         Chan       OUTPUT:       Brief         Delett       SIGNAL PLACEMENT:       Float all signals and ignore grouping?       N         Use placement data from       Design file       Save last successful containing         Sin       Press <f9> to edit file containing       Use all fitting options         Mun until fat success: STD       Run until fat success: EXTRA         DEFAULT FUSE OPTIONS:       Unused I/O pins configured as ou       Select one combination         FITTING OPTIONS:       When compiling       Run until 1st success: STD</f9></f1> |   |                      |                                                         |                                                                                          |                                                                                                                          |                                                                                                          | SM4 ve                                   | rsion 1.5                                                                                                                   |                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------|---------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| Retrieve existing design       MACH FITTING OPTIONS         Merg       OUTPUT:         Chan       OUTPUT:         Delet       Brief         SignAL PLACEMENT:       Float all signals and ignore grouping? N         Use placement data from       Design file         Co       Save last successful containing         Press <f9> to edit file containing         Log       DEFAULT FUSE OPTIONS:         Unused I/O pins configured as ou       Select one combination         FITTING OPTIONS:       Select one combination</f9>                                                                                                                                                                                                                                                            | F | ILE                  | EDI                                                     | T RUN                                                                                    | VIEW                                                                                                                     | DOWNLO                                                                                                   | DAD                                      | DOCUMENTATION                                                                                                               | <f1> for Help</f1>                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | Re<br>Mi<br>Cł<br>De | etrieve<br>erg<br>an<br>elet<br>et u<br>Wc<br>Co<br>Sin | existing of<br>OUTPU<br>Re<br>SIGNAL<br>Flo<br>Us<br>Sa<br>Pro<br>DEFAU<br>Un<br>FITTINO | T:<br>port level<br>PLACEMI<br>e placement<br>ve last suc<br>ass <f9> to<br/>LT FUSE C<br/>used I/O p<br/>G OPTIONS</f9> | ENT:<br>Is and ignor<br>t data from<br>cessful cont<br>o edit file con<br>OPTIONS:<br>ns configure<br>S: | e group<br>aining<br>ntaining<br>ed as o | Brief<br>bing? N<br>Design file<br>Use all fitting option<br>Run until 1st succ<br>Run until 1st succ<br>Select one combina | ns<br>sess: STD<br>sess: EXTRA<br>ation |

Figure 11. Fitting Options Menu.

If during the fitting process the design is fitted or an error occurs which causes the Fitter to abort, the process is terminated. A message is included in the final error count of the .RPT file which indicates whether the Fitter has aborted:

"%% FITR %% Program Aborted - Errors: 1, Warnings: 0"

If the Fitter does not abort, the process works as follows:

Initially the *Maximize packing of logic blocks* flag is OFF. If the design is successfully partitioned, the macrocell assignment iterations in Table 7 are run. If it fails partitioning, the *Maximize packing of logic blocks*

flag is turned ON and partitioning is re-run. If the design is then successfully partitioned, the macrocell assignment iterations in Table 7 are run. If not, the design has failed to fit.

If the design has failed to fit with the *EXTRA* iterations, the *Run until 1st success: STD* Fitter iterations (see *STD* option) are then executed.

The macrocell assignment iterations in Table 7 include four *STD* Fitter flag combinations and four *EXTRA* iterations. The extra iterations attempt placements which cannot be duplicated using the *Run until first success: STD* or *Select one combina-tion* menu options. Therefore, it may be necessary to backannotate pins in order to duplicate *Run until 1st success: EXTRA* Fitter runs using these menu options.

| Expand small PT spacing<br>N | Expand all PT spacing<br>N | <u>Comments</u><br>same as <i>STD</i>    |

|------------------------------|----------------------------|------------------------------------------|

| Ŷ                            | N                          | same as <i>STD</i>                       |

| N                            | Ŷ                          | same as <i>STD</i><br>same as <i>STD</i> |

| N                            | N                          | 1st EXTRA Iteration                      |

| N                            | N                          | 2nd EXTRA Iteration                      |

| N                            | N                          | 3rd EXTRA Iteration                      |

| N                            | N                          | 4th EXTRA Iteration                      |

Table 7. EXTRA option fitting flags.

The benefit of the *EXTRA* Fitter option is that additional macrocell assignments are attempted for a given block partition, allowing designs to fit that otherwise would not.

The drawbacks of the option are that compilation times are longer and a larger .RPT file is generated. It is larger because it includes all Fitter iterations (see section 3.4.2).

STD Option

The Run until 1st success: STD Fitter option operates the same as the PALASM 4 Version 1.2 Run until first success option. It does not execute extra macrocell assignment iterations. When the STD option is selected, the Fitter executes up to eight iterations, each using a different combination of the three Fitter flags: Expand small PT spacing, Expand all PT spacing and Maximize packing of logic blocks. Fewer than eight iterations will be run if the design is fitted or an error occurs which causes the Fitter to abort.

The *STD* option creates a .RPT file reflecting the last Fitter iteration.

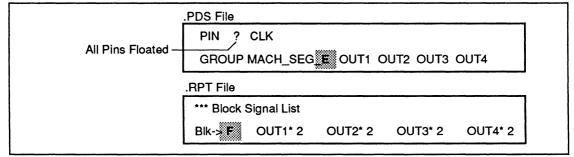

3.4 Changes to the Fitter Several changes were made to the Fitter report (.RPT) file for PALASM 4 version 1.4 and version 1.5: **Report File** Report file changes for PALASM 4 version 1.5 "Run Until 1st Success - EXTRA" Intermediate Error Counts (section 3.4.1) "Total Block Fanout" (section 3.4.2) Report file changes for PALASM 4 version 1.4 The Run Until 1st Success: EXTRA fitting option lists multiple .RPT files (section 3.4.3) **Block Partitioning Results table** (section 3.4.4) Block Signal List Table (section 3.4.5) Block Input List (section 3.4.6) Using the Block Input List and the Block Signal List Table to Manually Partition a Design (section 3.4.7) If you are already familiar with PALASM 4 version 1.4, just read sections 3.4.1 and 3.4.2 before moving on to Chapter 4. 3.4.1 Report File Changes -The wording of the informational message about "partial" error counts given by the Run Until 1st Success: EXTRA "Run Until 1st Success" fitting option has been changed to "intermediate" error Intermediate Error Counts counts:

|> INFORMATION F085 - Intermediate Error Count: %1, Warning Count: %2 Explanation: . The Fitter has calculated an intermediate total of all error(s) and . warning(s) detected to this point in the processing sequence. It will . try different placement and assignment options automatically for the . user. The error count is reset to zero before beginning this additional . processing.

# 3.4.2 Calculation of Total Block Fanout

A complete description on how the total incremental current due to switching inputs  $(i_{i\tau})$  is calculated is presented in the General Information section of the MACH Family Data Book (revision F or later), under "Approximiating Actual Application Supply Current".

The AMD MACH Fitter reports the fanout for each individual input in the "Blocks" column on the far right side of the "Signals - Tabular Information" portion of the MACH report file. The total block fanout - the sum of all the fanouts of the individual inputs - is listed just above that table as part of an informational message from the Fitter. For example:

INFORMATION F058 - Total Block Fanout (all Signals) \*: 40

| ) | 3.4.3 Run Until 1st Su<br>EXTRA Fitting Option<br>Multiple .RPT Files | 1st Suce<br>Run Un<br>combine<br>.RPT file | A single .RPT file is created during compilation if the Run Until<br>1st Success: STD fitting option is chosen. However, when the<br>Run Until 1st Success: EXTRA option is chosen, the Fitter<br>combines the .RPT files from all fitting attempts in one large<br>.RPT file. This provides the user with more fitting information,<br>but uses additional disk space. |                                                                                                         |                                                                                         |                                                                                                             |                                                 |   |

|---|-----------------------------------------------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------|---|

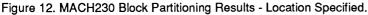

|   |                                                                       |                                            | Two tec<br>•                                                                                                                                                                                                                                                                                                                                                            | Select the B<br>Until 1st Suc                                                                           | ninimizing the<br>rief report leve<br>ccess: EXTRA<br>n Until 1st Suc                   | el when using<br>A fitting option                                                                           | the Run                                         |   |